Copyright © 1983, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# PRECISION VOLTAGE REFERENCING TECHNIQUES IN MOS TECHNOLOGY

by

.

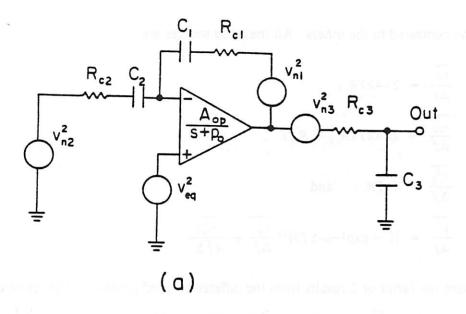

·

Bang-Sup Song

Memorandum No. UCB/ERL M83/17

14 March 1983

# PRECISION VOLTAGE REFERENCING TECHNIQUES IN MOS TECHNOLOGY

by

Bang-Sup Song

Memorandum No. UCB/ERL M83/17

14 March 1983

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720 Precision Voltage Referencing Techniques in MOS Technology

By

# Bang-Sup Song

B.S. (Seoul National University, Korea) 1973 M.S. (Korea Advanced Institute of Science) 1975

# DISSERTATION

Submitted in partial satisfaction of the requirements for the degree of

DOCTOR OF PHILOSOPHY

in

Engineering

in the

GRADUATE DIVISION

OF THE

UNIVERSITY OF CALIFORNIA, BERKELEY

. . . . . . . . . . .

Mach 14/1985 Approved: Date Fa

# PRECISION VOLTAGE REFERENCING TECHNIQUES IN MOS TECHNOLOGY

Ph. D.

Bang-Sup Song

Department of Electrical Engineering and Computer Science

.

Chairman of Commis Signature :

## ABSTRACT

With the increasing complexity of functions on a single MOS chip, precision analog circuits implemented in the same technology are in great demand so as to be integrated together with digital circuits. The future development of MOS data acquisition systems will require precision on-chip MOS voltage references. This dissertation will probe two most promising configurations of on-chip voltage references both in NMOS and CMOS technologies.

In NMOS, an ion-implantation effect on the temperature behavior of MOS devices is investigated to identify the fundamental limiting factors of a threshold voltage difference as an NMOS voltage source. For this kind of voltage reference, the temperature stability on the order of  $20ppm/^{\circ}C$  is achievable with a shallow single-threshold implant and a lowcurrent, high-body bias operation.

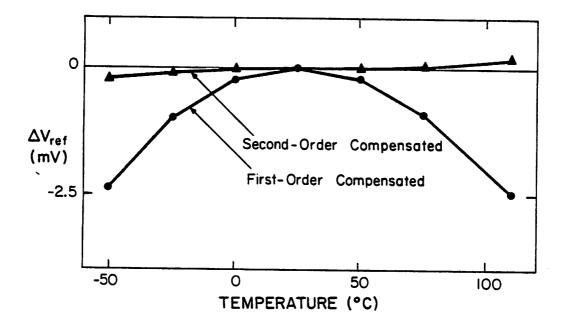

In CMOS, a monolithic prototype bandgap reference is designed, fabricated and tested which embodies a curvature compensation and exhibits a minimized sensitivity to the process parameter variation. Experimental results imply that an average temperature stability on the order of  $10ppm/^{\circ}C$  with a production spread of less than  $10ppm/^{\circ}C$  is feasible over the commercial temperature range.

# ACKNOWLEDGEMENT

I would like to express my deepest appreciations to the thoughtful guidance and the continuous support that I have been privileged to receive from my adviser, Prof. Paul R. Gray. I also would like to thank Prof. David A. Hodges for his friendly advice and encouragement, and Prof. Robert G. Meyer, Prof. John R. Whinnery and Prof. Le Cam for sparing their time in my qualifying exam.

Many thanks go to all the colleagues who shared the old room 401; R. Castello, T. Choi, J. Hui, R. Kaneshiro, H. Lee and P. Li for their help, and specially to H. Khorramabadi for her kindness to teach me IC processing in person. The technical assistances from D. McDaniel, D. Rogers, J. Duffy, R. Hamilton and T. King are also appreciated.

This research was supported by the National Science Foundation under Grant ECS-8023872, Xerox Corp., Intel Corp., IBM Corp. and MICRO Project.

# **DEDICATION**

I dedicate this dissertation to my wife Kyung-Sook and two love kids Juwan and Selin. Their love, endurance and sacrifice they have been filling me with every single day in the monotonicity of the Albany village life enabled me to concentrate on my work.

I also dedicate this dissertation to my late father who would be more delighted than anyone else if he is still in this world and my old mother in Korea who has been waiting so long for her youngest son to finish his Ph.D. work.

# TABLE OF CONTENTS

•

•

.

| List of Symbols                                                                                                                                                                                                                                                                                                                                                             |          |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Chapter 1. General Introduction                                                                                                                                                                                                                                                                                                                                             | l        |  |

| 1.1. Historical Research Survey                                                                                                                                                                                                                                                                                                                                             | 2        |  |

| Chapter 2. Threshold Voltage Difference as an NMOS Voltage Source                                                                                                                                                                                                                                                                                                           | 4        |  |

| <ul> <li>2.1. Introduction</li> <li>2.2. Threshold Voltage of IGFET's and its Temperature Dependence</li> <li>2.2.1. IGFET at Threshold</li> <li>2.2.2. Channel-to-Bulk Built-In Potential</li> </ul>                                                                                                                                                                       | ц<br>6   |  |

| <ul> <li>2.2.3. Threshold Voltage Temperature Dependence</li> <li>2.3.1. Enhancement-Type Implantation</li> <li>2.3.2. Depletion-Type Implantation</li> </ul>                                                                                                                                                                                                               | 12       |  |

| 2.4. Temperature Drift of the Threshold Voltage Difference<br>2.4.1. Enhancement Implant<br>2.4.2. Depletion Implant                                                                                                                                                                                                                                                        | 18       |  |

| <ul> <li>2.4.3. Double Implant (Enhancement and Depletion)</li> <li>2.5. Validity of a Depletion Approximation</li> <li>2.6. Temperature Measurement of IGFET Characteristics</li> <li>2.6.1. Threshold Voltage Difference</li> <li>2.6.2. Gate-Source Voltage Difference</li> <li>2.6.3. Device Test Results</li> </ul>                                                    | 27<br>28 |  |

| Chapter 3. Si Bandgap as a CMOS Voltage Source                                                                                                                                                                                                                                                                                                                              | 38       |  |

| <ul> <li>3.1. Introduction</li> <li>3.2. Silicon Energy Gap and its Temperature Dependence</li> <li>3.2.1. Energy Gap Narrowing with Impurity Concentration</li> <li>3.2.2. Shift of Energy Gap with Lattice Dilation</li> <li>3.2.3. Shift of Energy Gap with Electron-Phonon Interaction</li> <li>3.2.4. Empirical Temperature Dependence of the Si Energy Gap</li> </ul> | 33<br>39 |  |

| <ul> <li>3.3. Temperature Dependence of Substrate PNP Transistors</li> <li>3.3.1. Temperature Variation of the Emitter-Base Potential</li> <li>3.3.2. Temperature Variation of the Transistor Current Gain</li> </ul>                                                                                                                                                       | 46       |  |

| <ul> <li>3.4. Temperature Dependence of Components</li> <li>3.4.1. Temperature Variation of Diffused Resistors</li> <li>3.4.2. Temperature Variation of Capacitors</li> <li>3.4.3. Temperature Variation of MOS Transistor Mismatches</li> </ul>                                                                                                                            | 50       |  |

| <ul> <li>3.5. Conventional CMOS bandgap Reference and its Error Sources</li> <li>3.5.1. Op Amp Offset</li> <li>3.5.2. Bias Current Variation</li> <li>3.5.3. Current Gain and Base Resistance</li> <li>2.5.4. Finite On Amp Cain</li> </ul>                                                                                                                                 | 57       |  |

3.5.4. Finite Op Amp Gain3.5.5. Curvature in the Bandgap Reference

| 3.5.6. Others<br>3.6. Temperature Compensation Technique<br>3.6.1. First-Order Temperature Compensation | 63       |  |

|---------------------------------------------------------------------------------------------------------|----------|--|

| 3.6.2. Second-Order Temperature Compensation                                                            |          |  |

|                                                                                                         | 67       |  |

| Chapter 4. Design of a Precision CMOS Bandgap Reference                                                 | 67       |  |

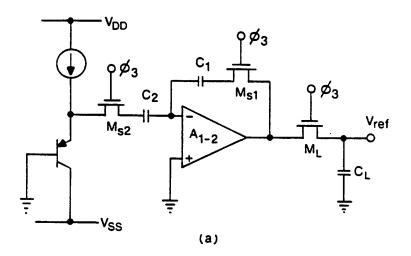

| 4.1. A Precisior: CMOS Bandgap Reference                                                                | 67       |  |

| 4.1.1. Curvature Compensation                                                                           |          |  |

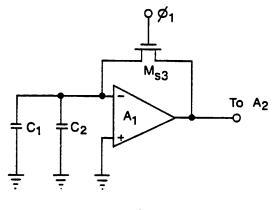

| 4.1.2. Bias Current Generation<br>4.1.3. Offset-Free Amplification                                      |          |  |

| 4.1.4. Base Current and Base Resistance Cancellation                                                    |          |  |

| 4.2. Op Amp Design                                                                                      | 77<br>81 |  |

| 4.3. Error Analysis<br>4.3.1. Spread of Resistor Temperature Coefficients                               | 10       |  |

| 4.3.2. Gate-Source Voltage Mismatches                                                                   |          |  |

| 4.3.3. Leakage from the Op Amp Summing Node                                                             |          |  |

| 4.3.4. Bias Current Instability                                                                         |          |  |

| 4.3.5. Others<br>4.4. Noise Analysis                                                                    | 90       |  |

| 4.4.1. Effects of a Correlated Double Sampling                                                          | 90       |  |

| 4.4.2. Op Amp Thermal Noise and $1/f$ Noise                                                             |          |  |

| 4.4.3. Noise of Substrate PNP Transistors                                                               |          |  |

| 4.4.4. Output Noise and its Spectral Density                                                            |          |  |

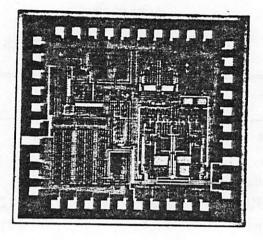

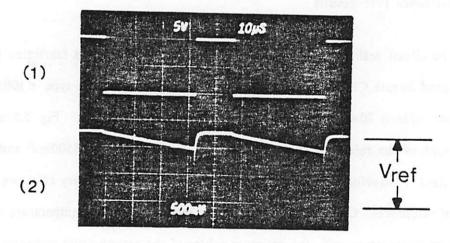

| Chapter 5. Experimental Results for a CMOS Bandgap Reference                                            | 105      |  |

| 5.1. Design Considerations                                                                              | 105      |  |

| 5.1.1. Trimming Accuracy                                                                                |          |  |

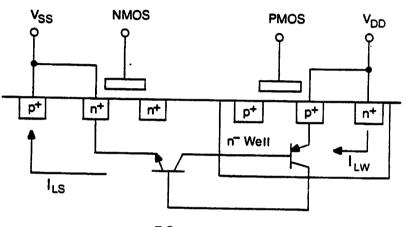

| 5.1.2. Latch-Up Prevention                                                                              |          |  |

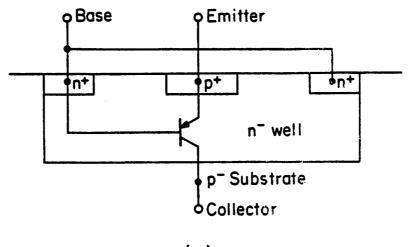

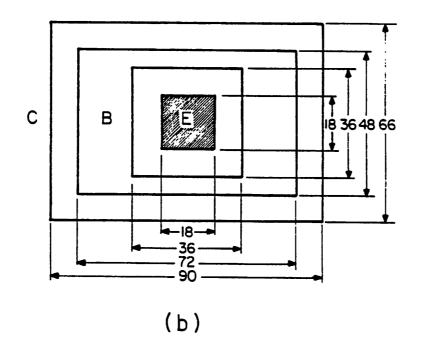

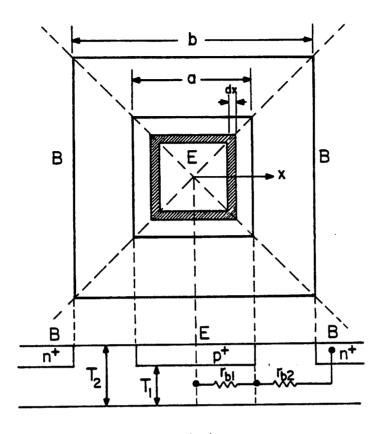

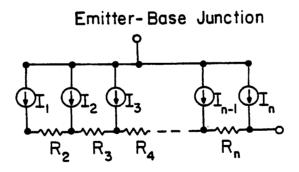

| 5.1.3. MOS Switches<br>5.2. Substrate PNP Transistor Design                                             | 115      |  |

| 5.2.1. Base Spreading Resistance Limitation                                                             | /        |  |

| 5.2.2. Current Gain Limitation                                                                          |          |  |

| 5.3. Component Measurement Results                                                                      | 121      |  |

| 5.4. Reference Test Results                                                                             | 125      |  |

| Chapter 6. Conclusions                                                                                  | 131      |  |

| Appendix I. MOS Threshold Equations : Special Case of Step Profiles                                     | 133      |  |

| Appendix II. Intrinsic Carrier Concentration and Mobility                                               |          |  |

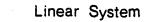

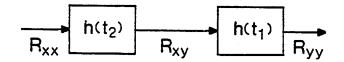

| Appendix III. Input-Output Spectral Density Relation of a Linear System                                 |          |  |

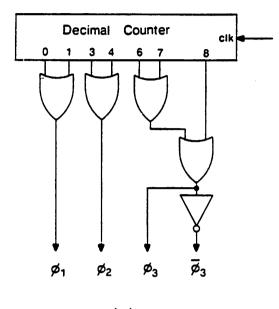

| Appendix IV. Test Fixture                                                                               |          |  |

| Appendix V. Self-Aligned Si-Gate CMOS Process                                                           |          |  |

|                                                                                                         | 147      |  |

iv

-

\$

<u>ب</u>

•

.

# LIST OF SYMBOLS

Subscripts U, E, D and B on the following symbols stand for unimplanted, enhancement, depletion and double-implant, respectively.

| A                 | Emitter area ratio.                                                                |

|-------------------|------------------------------------------------------------------------------------|

| Cox               | Gate oxide capacitance per unit area, $\epsilon_{OX}/t_{OX}$ .                     |

| $E_g$             | Si energy gap.                                                                     |

| $\tilde{E_{gi}}$  | Linearly-extrapolated Si energy gap at $0^{\circ} K$ .                             |

| I.                | Temperature-independent bias current.                                              |

| I <sub>s</sub>    | Reverse saturation current.                                                        |

| $I_{B,E,C}$       | Base, emitter or collector current.                                                |

| ID                | Bias current of $V_{BE}$ .                                                         |

| I <sub>T</sub>    | PTAT(Proportional To Absolute Temperature) bias current.                           |

| kT/q              | Thermal voltage, $\approx 26 mV$ at $300^{\circ} K$ .                              |

| KVT               | PTAT correction voltage.                                                           |

| $FV_T^2$          | PTATS(PTAT Squared) correction voltage.                                            |

| n                 | Exponent in the mobility temperature variation of $T^{-n}$ .                       |

| n,                | Intrinsic concentration, $\approx 1.4 \times 10^{10} cm^{-3}$ at $300^{\circ} K$ . |

| Na                | Bulk dopant concentration.                                                         |

| Nai               | Enhancement acceptor implant density.                                              |

| N <sub>di</sub>   | Depletion donor implant density.                                                   |

| N <sub>peak</sub> | Peak carrier density in the channel at threshold.                                  |

| <i>q</i>          | $1.6 \times 10^{-19} Coul.$                                                        |

| Qd                | Depleted charge density per unit area at threshold.                                |

| Q,                | Implanted charge density per unit area.                                            |

| Q.s               | Fixed charge at the Si-Si dioxide interface.                                       |

| Q <sub>B</sub>    | Total built-in base charge per unit area.                                          |

| r <sub>b</sub>    | Base resistance of one unit transistor cell.                                       |

| tox               | Gate oxide thickness.                                                              |

| Τ                 | Temperature in °K.                                                                 |

| V <sub>BE</sub>   | Emitter-base or base-emitter potential.                                            |

| $V_{g1}$          | Linearly-extrapolated Si bandgap voltage at 0° K.                                  |

| V <sub>g2</sub>   | Quadratically-extrapolated Si bandgap voltage at $0^{o} K$ .                       |

| V <sub>m</sub>    | Gate-source voltage mismatch of a pair of IGFET's.                                 |

| Vo                | Bandgap voltage for the internal bias purpose.                                     |

| V <sub>os</sub>   | Offset voltage of an op amp.                                                       |

|                   |                                                                                    |

| Vref | Output | reference | voltage. |

|------|--------|-----------|----------|

|------|--------|-----------|----------|

- *V<sub>th</sub>* Gate threshold voltage.

- $V_{GS}$  Gate to source voltage.

- V<sub>SB</sub> Source to bulk body bias voltage.

- $V_T$  Thermal voltage kT/q.

- $X_1$  Depth of the maximum potential point.

- $X_d$  Depth of the depletion edge at threshold.

- $X_i$  Depth of the enhancement implant.

- $X_i$  Depth of the depletion implant.

- $\alpha$  Exponent in the bias current temperature variation of  $T^{\alpha}$ .

- β Current gain of bipolar transistors.

- $\gamma$  4-*n* where  $n = 3/2^{-5}/2$ .

- $\epsilon_s$  Permittivity of Si,  $\approx 10^{-12} F/cm$ .

- $\epsilon_{OX}$  Permittivity of the gate oxide,  $\approx 3.5 \times 10^{-13} F/cm$ .

- $\overline{\mu}$  Average channel mobility.

- $\Phi_{bi}$  Channel to bulk built-in potential at threshold.

- $\Phi_E$  Channel to bulk built-in potential in enhancement devices.

- $\Phi_D$  Channel to bulk built-in potential in depiction devices.

- $\Phi_X$  Potential drop from the maximum potential point to the surface.

Unless otherwise specified, the following data are employed for numerical calculations :

| $Q_{iE}$              | $2 \times 10^{11} cm^{-2}$ , |

|-----------------------|------------------------------|

| $Q_{iD}$              | $6 \times 10^{11} cm^{-2}$ , |

| Na                    | $5 \times 10^{14} cm^{-3}$ , |

| Nai                   | $5 \times 10^{15} cm^{-3}$ , |

| N <sub>di</sub>       | $10^{17} cm^{-3}$ ,          |

| Х,                    | 400 <i>nm</i> ,              |

| <b>X</b> <sub>j</sub> | 60 <i>nm</i> ,               |

| tox                   | 100 <i>nm</i> and            |

| V <sub>SB</sub>       | 5V.                          |

# CHAPTER 1

# **GENERAL INTRODUCTION**

To meet the growing integration trend of analog and digital LSI functions, the development of precision analog components has been accelerated in MOS technology [1]. An essential element of the analog and digital interface function is a voltage reference to control the scale factor of conversion. The absolute accuracy of data conversion systems is limited by the accuracy of the voltage references used in the systems. The temperature stability of a reference source is a key factor in the accuracy of the overall data acquisition function. In reality, the performance of voltage references has not been able to catch up with those of other data acquisition functions. Therefore, the ability to integrate an entire data acquisition function within a single MOS VLSI chip is contingent upon the ability to realize an MOS-compatible voltage reference with a very low temperature drift.

This thesis explores the best-performing configurations of on-chip voltage references both in NMOS and CMOS technologies. In the first part (Chapter 2), an analysis of the effect of ion-implantation on the IGFET threshold temperature drift is presented, and simple design equations for predicting the threshold voltage temperature coefficients of implanted devices relative to those of unimplanted devices are developed. In the second part (Chapters 3, 4 and 5), a precision curvature-compensated switched-capacitor bandgap reference is described which employs a standard digital CMOS process and achieves a temperature stability significantly lower than has previously been reported for CMOS circuits without critical trim requirements. The theoretically achievable temperature stability of the reference output approaches  $10ppm/{}^{o}C$  over the commercial temperature range utilizing a straight-forward room temperature trim procedure and the estimated production spread is less than  $10ppm/{}^{o}C$ . Experimental data from monolithic prototype samples are presented which fit the theoretical predictions reasonably well.

### 1.1. Historical Research Survey

Since its introduction by Widlar [2], the bandgap referencing technique has been applied for implementing a voltage source in bipolar integrated circuits. The temperature stability of a bandgap reference has been continuously improved via new circuits and technology innovation such as a curvature compensation and a laser trimming [3]-[6].

In NMOS technology, however, due to the lack of a forward-biased diode, the bandgap referencing scheme is not directly applicable. To date, the only technique actually utilized commercially for implementing NMOS reference sources has been based on developing the difference between the threshold voltages of two devices with different implants in the channel [7]-[8]. The temperature stability of such a voltage source depends on the details of the effect of the channel implant on the temperature coefficient of the device threshold. The temperature variation of the uniformly-doped device has been studied by many authors [9]-[11]. The temperature dependent behavior of the depletion device was analyzed by Gaensslen and Jaeger, numerically [12] and analytically [13]. Their work emphasizes the low temperature carrier freezeout phenomena and is not suitable for a circuit application in the commercial and military temperature ranges.

In CMOS technology, the bandgap referencing technique has been directly applied [14]-[15] and many versions of on-chip voltage references have been introduced during the past few years [16]-[17] using the well-known bipolar bandgap referencing technique. The flat-band voltage difference [18] resulting from different gate materials and the work-function difference [19] resulting from different gate dopings have also been proposed as reference sources. Unlike the bipolar implementation of a bandgap reference, however, the development of a high performance CMOS bandgap reference has been hindered by several factors such as the peculiarities of the bipolar devices available in a standard CMOS process, the high offset and drift of CMOS op amps that make up the circuit as well as the inherent curvature problem in the bandgap reference.

Table I summarizes the features of the several voltage reference works published in the chronical order. Note that the high performance in the bipolar reference is achievable through the use of thin film resistors and a laser trim technology. Due to the lack of these features and the existing problems unique to CMOS, a high-precision CMOS voltage source has been unattainable.

# TABLE I

#### T.C. Feature Correct Noise Tech. Vref Author (V) $(ppm/^{o}C)$ $(\mu V)$ 5 40 Thin film lst Widlar 200 Bipolar (1971) (-55<sup>-</sup>125°C) order (100 kHz). 70 9.88 4 Thin film Kujik $(0^{-}60^{\circ}C)$ -(1973) Laser tr. . 2.5 Brokaw 5-60 (-55<sup>-</sup>125°C) (1974) Palmer 5 2.2 2nd . (1981) order 0.45 Ni-Cr Meijer 1.158 (1982) (-25<sup>85°</sup>C) 200 3.167 4.9 NMOS Blauschild (1978) (-55<sup>-</sup>125°C) (10kHz)100 CMOS Tsividis 1.105 Weak inv. lst • (1978) . order . Ħ 1.2 70 p well (1979) $(0^{-}60^{\circ}C)$ Weak inv. Vittoz 1.3 110 (1979) (-50<sup>-100°</sup>C) Gregorian 1.1-1.3 40 p well $(0^{-}70^{\circ}C)$ (1981)

## **HISTORICAL SURVEY**

3

# CHAPTER 2 THRESHOLD VOLTAGE DIFFERENCE AS AN NMOS VOLTAGE SOURCE

## 2.1. Introduction

Ion-implantation has been widely employed to adjust the threshold voltage of MOS transistors made on low conductivity substrates. The only commercially available NMOS voltage source relies on the threshold voltage difference of two devices with different threshold implants. However, the temperature variation of device characteristics associated with the channel implantation has not been fully understood. This chapter begins with an analysis of the temperature variations of the four types of implanted devices typical of those available in NMOS technology and the theoretical results are compared with experimental data. In this analysis, only the relative temperature variations of the implanted devices with respect to the unimplanted devices are considered.

In Section 2.2, the general threshold condition of IGFET's is described and, assuming the channel is gradual, the one-dimensional Poisson's equation based on a depletion approximation is solved for general non-uniform doping profiles. Also, the built-in potential difference and its effect on the threshold voltage temperature variation of the implanted devices will be discussed. In Section 2.3, the threshold voltage shifts resulting from various channel implants are calculated based on the threshold definition described in Section 2.2. In Section 2.4, using the analysis of Section 2.3, simplified explicit expressions for the temperature coefficients of the implanted devices relative to those of the unimplanted devices will be developed using a step profile approximation. In Section 2.5, the validity of the depletion approximation is discussed and, in Section 2.6, experimental results are compared with the theoretical results developed in Section 2.4.

4

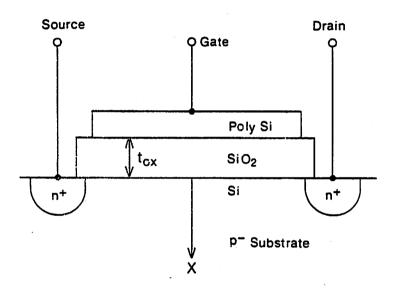

Fig. 2.1. N-channel Si-gate IGFET.

# 2.2. Threshold Voltage of IGFET's and its Temperature Dependence

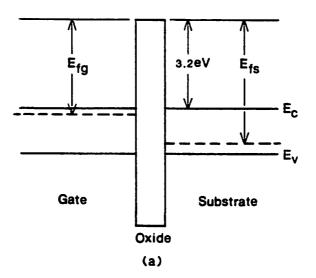

The profile of an n-channel insulated gate field effect transistor (IGFET) is shown in Fig. 2.1. The heavily  $n^+$ -doped poly-Si gate is isolated from the substrate by the thermally-grown thin Si-oxide layer. The energy band diagram of the MOS system of Fig. 2.1 is illustrated in Fig. 2.2(a). As the gate voltage is increased above the flat-band voltage, the field at the surface of the Si increases and the energy band begins to bend. In the surface region, the majority carriers (holes) have been depleted and generation of carriers will therefore exceed recombination. The generated hole-electron pairs are separated by the field, the holes being swept into the bulk and the electrons moving to the oxide-Si interface where they are held because of the oxide energy barrier. The IGFET threshold voltage is defined as a potential drop from the gate to the substrate when a certain number of carriers exist in the channel. At this time, the potential drop from the point where potential is maximum to the substrate is defined as a built-in potential  $\Phi_{b_1}$  as shown in Fig. 2.2(b).

### 2.2.1. IGFET at Threshold

For a long-channel MOS transistor, the gate-substrate potential drop at threshold is the sum of the potential drop  $V_{OX}$  across the gate oxide and the potential  $\Phi(x=0)$  at the surface. That is,

$$V_{ih} = V_{OX} + \Phi(x=0)$$

(2.1)

The potential drop across the gate oxide is also given by

$$V_{OX} = V_{FB} - \frac{Q_d}{C_{OX}} = \Phi_{MS} - \frac{Q_{ss}}{C_{OX}} - \frac{Q_d}{C_{OX}}$$

(2.2)

where  $Q_d$  is the space-charge density per unit area,  $C_{OX}$  is the gate oxide capacitance per unit area, and  $V_{FB}$  is the flat-band voltage which is determined by the metal-semiconductor

Fig. 2.2. Energy-band diagram : (a) at flat band and (b) at threshold.

work function difference  $\Phi_{MS}$  and the fixed interface charge per unit area  $Q_{ss}$ , etc.. From Fig. 2.2(a), the metal-semiconductor work function difference  $\Phi_{MS}$  is simply

$$\Phi_{MS} = \Phi_M - \Phi_S = E_{fg} - E_{fs}$$

$$= -\frac{kT}{q} \ln \frac{N_{poly} N_a}{n_i^2}$$

(2.3)

where  $\Phi_M$  and  $\Phi_S$  are the work functions of the gate and the substrate,  $E_{fg}$  and  $E_{fs}$  are the potential difference from the oxide conduction-band edge to the Fermi potentials of the gate and the substrate, respectively, as shown in Fig. 2.2(a), and  $N_{poly}$  and  $N_a$  are the dopant concentrations of the gate and the substrate, respectively.

Assuming charge neutrality beyond the depletion edge and neglecting minority carriers, the one-dimensional Poisson's equation and the boundary conditions in the Si bulk are

$$\frac{d^2\Phi(x)}{dx^2} = 0 \quad \text{and} \quad \frac{d\Phi(x)}{dx} \bigg|_{x=X_d} = 0$$

(2.4)

where  $X_d$  is the depletion region edge and N(x) is the total charge density as a function of depth from the Si surface. The solution of (2.4) is

$$\Phi(x) = -\frac{q}{\epsilon_s} \left[ x \int_{\chi_d}^x N(t) dt - \int_{\chi_d}^x t N(t) dt \right].$$

(2.5)

The depleted charge density per unit area at threshold is also given by

$$Q_d = -q \int_0^{x_d} N(x) dx$$

(2.6)

where the negative sign indicates the polarity of the space charge left over after the free carriers are depleted.

# 2.2.2. Channel-to-Bulk Built-In Potential

The channel-to-bulk built-in potential is defined as the potential difference between the peak potential of the conducting channel and the substrate potential. The potential with reference to the intrinsic Fermi level is a logarithmic function of the electron concentration so that

$$\Phi(x) = \frac{kT}{q} \ln \frac{n(x)}{n_i}$$

(2.7)

where n(x) is the electron concentration at x. The definition of the built-in potential coincides with the definition of the peak-carrier density in the channel at threshold.

For the unimplanted (uniform channel doping) device without the body bias, the built-in potential between the maximum potential point in the channel and the bulk at threshold has traditionally been defined as the strong inversion value of

$$\Phi_{b_{l}} = \frac{kT}{q} \ln \frac{N_{a}^{2}}{n_{l}^{2}} \quad . \tag{2.8}$$

The same definition has been extended previously to the implanted devices [20]-[21]. This definition is equivalent to defining the threshold condition as that condition in which the concentration of electrons in the channel at the maximum potential point is the same as the concentration of holes in the bulk.

The built-in potential in the non-uniformly doped devices with channel implantations has been defined in two different ways. One definition is

$$\Phi_{bi} = \frac{kT}{q} \ln \frac{N_{doped} N_a}{n_i^2}$$

(2.9)

where  $N_{doped}$  is the actual dopant density at the potential maximum point [22]-[24]. The other definition is

$$\Phi_{bi} = \frac{kT}{q} \ln \frac{N(X-X_d)^2}{n_i^2}$$

(2.10)

where  $N(X=X_d)$  is the dopant density at the edge of the depletion region [25]-[27]. Equation (2.10) is only valid when the implantation is deep and the body bias is low, and it coincides with (2.8) as far as the depletion region extend beyond the implantation depth. Equations (2.9) and (2.10) heavily depend on the depletion approximation and the strong inversion condition. Usually, it results in a high channel conductance at threshold. The generalization of the above definition leads to

$$\Phi_{bi} = \frac{kT}{q} \ln \frac{N_{peak} N_a}{n_i^2}$$

(2.11)

where  $N_{peak}$  is the peak electron density in the channel at threshold.

The above definitions are based on an arbitrary definition of the strong inversion. There is no way to define the threshold condition analytically other than the definitions mentioned. We can not say which one is better than the others absolutely. As a rule of thumb, however, the peak carrier density  $N_{peak}$  is defined as equal to the bulk doping concentration  $N_a$ . Whatever the definitions are, the calculated threshold voltages are close to each other due to the logarithmic relation as indicated by (2.7).

### 2.2.3. Threshold Voltage Temperature Dependence

The threshold voltage temperature dependence of the unimplanted IGFET has been investigated in many works [9]-[11], [28]-[30], especially at low temperature [31]-[33]. Assume the fixed interface charge is independent of temperature, the differentiation of (2.1) with respect to temperature yields

$$\frac{dV_{ih}}{dT} = \frac{d\Phi_{MS}}{dT} - \frac{1}{C_{OX}}\frac{dQ_d}{dT} + \frac{d\Phi_{bi}}{dT}$$

(2.12)

for the unimplanted device.

The second term of (2.12) is adjustable by increasing the body bias and scaling down the gate oxide. However, the major contributions are from  $\Phi_{MS}$  and  $\Phi_{br}$ . Therefore, the direct dimension scaling of MOS devices does not scale the temperature drift of  $V_{th}$ . This may pose a problem in the low supply voltage operation of scaled MOS devices. From (2.11) and (AII.16), the built-in potential temperature dependence is given by

$$\frac{d\Phi_{bi}}{dT} = \frac{1}{T} \left[ \Phi_{bi} - \frac{1}{q} \left( E_g - T \frac{dE_g}{dT} \right) - 3 \frac{kT}{q} \right]$$

$$\approx \frac{1}{T} \left( \Phi_{bi} - \frac{1}{q} E_{gl} \right)$$

(2.13)

where the linearly-extrapolated Si energy gap  $E_{g1}$  at  $0^{\circ}K$  is

$$E_{g1} = E_g - T \frac{dE_g}{dT}$$

$$\approx 1.205 \ eV \quad \text{for } T = 300^{\circ}K$$

For the substrate doping of  $N_a = 5 \times 10^{14} cm^{-3}$ , the temperature drift of the built-in potential is approximately

$$\frac{d\Phi_{br}}{dT}\Big|_{T_o} = \frac{1}{T_o} (\Phi_{br} - 1.205)$$

$$\approx \frac{1}{300} (0.545 - 1.205)$$

$$\approx -2.2 \ mV/^oC \quad \text{for } N_{peak} = N_a = 5 \times 10^{14} \ cm^{-3} \ .$$

(2.14)

The metal-semiconductor work function difference  $\Phi_{MS}$  in (2.3) assumes the same form as  $\Phi_{bi}$  in (2.11) and therefore its temperature drift is

$$\frac{d\Phi_{MS}}{dT}\Big|_{T_o} = -\frac{1}{T_o} (0.862 - 1.205)$$

$$\approx 1.14 \ mV/^oC \quad \text{for} \quad N_{poly} \approx 10^{20} \ cm^{-3} \quad .$$

(2.15)

The space-charge density  $Q_d$  is proportional to  $(\Phi_{b_1} + V_{SB})^{V_2}$  where  $V_{SB}$  is the source-tobulk body bias. Therefore, we obtain

$$\frac{dQ_d}{dT} = \frac{Q_d}{2C_{OX}(\Phi_{br} + V_{SB})} \frac{d\Phi_{br}}{dT}$$

(2.16)

$$\approx -\frac{\left[2 \times 1.6 \times 10^{-19} \times 10^{-12} \times 5 \times 10^{14} (0.545 + V_{SB})\right]^{V_2}}{2 \times 3.5 \times 10^{-8} (0.545 + V_{SB})} \times (-2.2 \ mV/^{\circ}C)$$

$$\approx 0.52 \ mV/^{\circ}C \quad \text{for} \quad V_{SB} = 0 \ V$$

$$\approx 0.17 \ mV/^{\circ}C \quad \text{for} \quad V_{SB} = 5 \ V$$

where (AI.6) is used for the approximation. Also note that the temperature variation of  $Q_d$  decreases as  $V_{SB}$  increases.

Based on the above simple analysis from (2.12) to (2.16), the temperature coefficient of  $V_{th}$  is estimated by

$$\frac{dV_{ih}}{dT} \approx 1.14 - 0.54 - 2.2 = -1.6 \ mV/^{\circ}C \quad \text{for} \quad V_{SB} = 0 \ V \tag{2.17}$$

$$\approx 1.14 - 0.17 - 2.2 = -1.23 \ mV/^{\circ}C \quad \text{for} \quad V_{SB} = 5 \ V \ .$$

The above estimations are close to the experimentally observed temperature coefficients of the unimplanted devices. Specifically, the body bias effect on the threshold temperature variation fits well with the experiment.

# 2.3. Threshold Voltage Shifts by Ion-Implantations

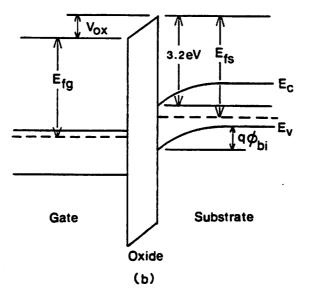

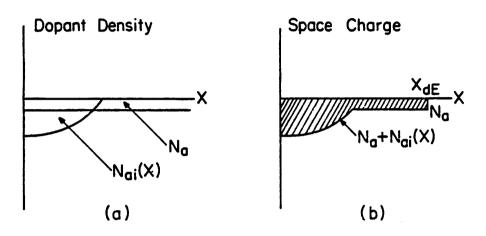

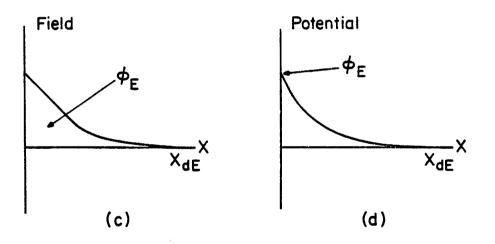

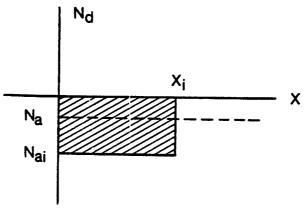

In a typical enhancement/depletion NMOS technology, up to four types of devices are available depending on the dopant profiles as shown in Fig. 2.3. Using a depletion approximation, the dopant density, the space charge, the field distribution and the potential distribution at threshold for the enhancement device and the depletion device are illustrated in Fig. 2.4 and 2.5, respectively. At threshold, the surface of the enhancement-mode device is depleted of mobile free carriers, and minority carriers start to build up due to the polarity inversion at the surface where the potential peaks. In the depletion-mode device, a

Fig. 2.3. Illustration of the four basic types of devices in NMOS technology. Dopant profiles of (a) unimplanted, (b) enhancement, (c) depletion and (d) doubly-implanted devices.

conducting channel is already formed by the depletion implant. Therefore, at flat band condition, there still exists a conducting channel under the surface. These free carriers must be cleared by pulling down the gate voltage. At threshold, the implanted conducting channel is depleted and the pinch-off condition occurs. The potential peaks at the subsurface as shown in Fig. 2.5(d) and free electrons accumulate at this peak potential point.

The threshold voltage shifts resulting from various channel implants are described for the enhancement device in numerical forms [25]-[26], [34] and in analytic forms [21], [27] and [35], for the depletion device in numerical forms [20], [36]-[37] and in analytic forms (22]-[24], respectively. In the following subsections, the equations describing the threshold voltage shifts resulting from the enhancement-type and the depletion-type channel implants are derived based on the depletion approximation discussed in Section 2.2.

### **2.3.1.** Enhancement-Type Implantation

The threshold voltage of the unimplanted device is shifted due to the enhancement implant by

$$\Delta V_{th} = \Delta \Phi_{bi} - \Delta Q_d / C_{OX} \tag{2.18}$$

where  $\Delta \Phi_{bi}$  is the built-in potential difference of the enhancement device and the unimplanted device at threshold and is given from (2.11) by

$$\Delta \Phi_{bi} = \Phi_E - \Phi_U = \frac{kT}{q} \ln \frac{N_{peak-E}}{N_{peak-U}}$$

(2.19)

and  $\Delta Q_d$ , the depleted charge difference between them at threshold, is

$$\Delta Q_d = Q_{dE} - Q_{dU} = -q \int_0^{X_{dE}} \left[ N_{a_i}(x) + N_a \right] dx + q \int_0^{X_{dU}} N_a dx . \qquad (2.20)$$

The depletion region edges of the enhancement device and the unimplanted device,  $X_{dE}$ and  $X_{dU}$ , respectively, can be obtained implicitly from the following relations;

Fig. 2.4. Enhancement device at threshold. Sketches of (a) dopant density, (b) space charge, (c) field and (d) potential.

.

$$\Phi_E + V_{SB} = \frac{q}{\epsilon_s} \int_0^{x_{dE}} x \left[ N_{a_i}(x) + N_a \right] dx$$

(2.21)

and

$$\Phi_U + V_{SB} = \frac{q}{\epsilon_s} \int_0^{x_{dU}} x N_a dx$$

(2.22)

where  $\Phi_E$  and  $\Phi_U$  are the built-in potentials of the enhancement device and the unimplanted device, respectively.

## 2.3.2. Depletion-Type Implantation

Under the same set of assumptions, the threshold voltage shift due to the depletion implant is

$$\Delta V_{ij} = \Delta \Phi_{bi} + \Phi_X - \Delta Q_d / C_{OX}$$

(2.23)

where  $\Delta \Phi_{b_i}$  is the built-in potential difference of the unimplanted device and the depletion device at threshold and is given from (2.11) by

$$\Delta \Phi_{U} = \Phi_U - \Phi_D = \frac{kT}{q} \ln \frac{N_{peak-U}}{N_{peak-D}} , \qquad (2.24)$$

the potential drop from the maximum potential point to the surface,  $\Phi_X$ , in the depletion device is

$$\Phi_{\chi} = \frac{q}{\epsilon_s} \int_0^{\chi_1} x \left[ N_{d_l}(x) - N_a \right] dx$$

(2.25)

and  $\Delta Q_d$ , the depleted charge difference of the unimplanted device and the depletion device at threshold, is

$$\Delta Q_d = Q_{dU} - Q_{dD} = -q \int_0^{X_{dU}} N_a dx - q \int_0^{X_1} [N_{di}(x) - N_a] dx . \qquad (2.26)$$

Unlike the enhancement device, there is an additional potential drop  $\Phi_X$  from the max-

16

Fig. 2.5. Depletion device at threshold. Sketches of (a) dopant density, (b) space charge, (c) field and (d) potential.

imum potential point  $X_1$  to the surface as shown in Fig. 2.5(d). This occurs because the same type of impurity as the channel is implanted and there exists a p-n junction at  $x=X_j$  where  $N_{di}(X_j)=N_a$ . The maximum potential point,  $X_1$ , and the depletion region edge of the depletion device,  $X_{dD}$ , can be obtained implicitly from the following relations;

$$\int_{X_1}^{X_1} \left[ N_{di}(x) - N_a \right] dx = \int_{X_j}^{X_{dD}} N_a dx$$

(2.27)

and

$$\Phi_D + V_{SB} = \frac{q}{\epsilon_s} \int_{\chi_1}^{\chi_{dD}} x \Big[ N_{di}(x) - N_a \Big] dx \qquad (2.28)$$

where  $\Phi_D$  is the built-in potential of the depletion device. For the doubly-implanted device, the equations (2.23) to (2.28) hold after substituting  $N_{ai}(x)+N_a$  for  $N_a$ .

As shown in (2.18) and (2.23), the threshold voltage shifts resulting from the channel implantations consist of the built-in potential difference and the depleted charge difference. To the first order, the built-in potential differences (2.19) and (2.24) exhibit no dependence on other parameters except the peak carrier densities in the channels of two devices at threshold while the depleted charge differences (2.20), (2.25) and (2.26) depend on the body bias as well as process parameters. The equations in this section are also summarized in Appendix I employing a step profile approximation.

### 2.4. Temperature Drift of the Threshold Voltage Difference

If a difference in the built-in potentials of two devices exists, the built-in potential difference will contribute a constant temperature drift which is determined by the ratio of the peak carrier densities in the channels of two devices at threshold as shown in (2.19) and (2.24). For example, if the peak carrier densities of two devices at threshold differ from each other by a factor of 2, the temperature drift due to this difference is

$(K/q)\ln 2=0.06mV/^{\circ}C$  at 300°K. The above temperature drift is introduced by the builtin potential difference of only  $(kT/q)\ln 2=18mV$  at 300°K. A small difference in the definition of the built-in potentials is negligible in estimating the threshold voltage. However, in the temperature analysis, even a very small difference in the definition of the built-in potentials is likely to defeat the validity of the whole analysis, especially in analyzing the differential temperature coefficient of two threshold voltages. In this work, the built-in potentials are defined as the same for all types of devices, and the temperature drift of the threshold voltage difference of two devices is assumed to be dominated by the variation of the depleted charge difference of two devices. This assumption is justified by the following argument.

The temperature coefficient of the depleted charge difference of two devices is the temperature coefficient difference of the depleted charges of each device at threshold. The temperature coefficient of the depleted charge of one device is proportional to the temperature coefficient of the built-in potential of the device at threshold because the depleted charge depends on the built-in potential. That is, if  $\Phi_{bi1}$  and  $\Phi_{bi2}$  are the built-in potentials of two devices, the temperature coefficient of the depleted charge difference of two devices is approximated by

$$T.C. = C_a \frac{d\Phi_{bi1}}{dT} - C_b \frac{d\Phi_{bi2}}{dT}$$

$$\approx \left[ (C_a - C_b) + \eta \frac{(C_a + C_b)}{2} \right] \frac{d\Phi_{bi}}{dT} \approx (C_a - C_b) \frac{d\Phi_{bi}}{dT}$$

(2.29)

where  $C_a$  and  $C_b$  are assumed to be constant. The built-in potential difference  $\Delta \Phi_{bi}$  is

$$\Delta \Phi_{bi} = \Phi_{bi1} - \Phi_{bi2} \quad , \tag{2.30}$$

and the following relation holds from (2.13);

$$\eta = \left| \frac{d\Delta\Phi_{bi}}{dT} / \frac{d\Phi_{bi}}{dT} \right| = \left| \frac{\Delta\Phi_{bi}}{(\Phi_{bi} - 1.205)} \right|$$

(2.31)

$$\approx$$

3.3 % for  $\Delta \Phi_{bi} = 18 mV$

For example, from (2.31), if the built-in potential of one device is different from that of the other device by 18mV,  $d\Delta\Phi_{bi}/dT$  is only 3.3% of  $d\Phi_{bi}/dT$ . In (2.29), the  $\Delta\Phi_{bi}$  contribution is neglected since  $C_a - C_b$  is actually much bigger than the other term and the 18mVdifference corresponds to the difference of the peak carrier densities of two devices by a factor of 2. Therefore, even though the built-in potentials are defined to be the same for all types of devices at threshold, it makes little difference in the calculation of the relative temperature coefficient contributed by the depleted charge difference of two devices. By defining  $\Phi_{bi} - \Phi_E - \Phi_D - 2(kT/q)\ln(N_a/n_i)$ , the analyses of the individual channel implants based on a step profile approximation will be discussed in the following subsections.

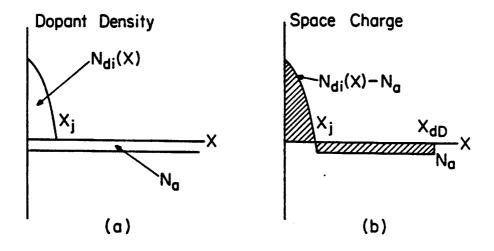

### 2.4.1. Enhancement Implant

In this subsection, the temperature coefficient of the threshold voltage shift which results from the enhancement implant is calculated. Assuming a step enhancement implant as shown in Fig. 2.6(a) with an implant depth of  $X_i$  and a constant dopant density of  $N_{ai}$  and using (2.18)-(2.22), the threshold voltage shift by the enhancement implant is

$$\Delta V_{ih} = \frac{Q_{iE}}{C_{OX}} + \frac{\left[2q\epsilon_s N_a(\Phi_{bi} + V_{SB})\right]^{\prime h}}{C_{OX}} \left\{ \left[1 - \frac{qN_{ai}X_i^2}{2\epsilon_s(\Phi_{bi} + V_{SB})}\right]^{\prime h} - 1 \right\}$$

(2.32)

where the enhancement-implant charge density per unit area  $Q_{iE}$  is given by

$$Q_{iE} = q N_{ai} X_i \tag{2.33}$$

and is independent of temperature. The implant dose  $N_{ai}X_j$  only shifts up the threshold voltage by approximately 1 V. The enhancement implant also contributes a higher field in the bulk due to the ionization of the implanted charge. Therefore, the depletion depth of the enhancement device is shorter than that of the unimplanted device with the same bulk concentration. 3

(a)

Fig. 2.6. Step profile approximation : (a) enhancement implant and (b) depletion implant.

.

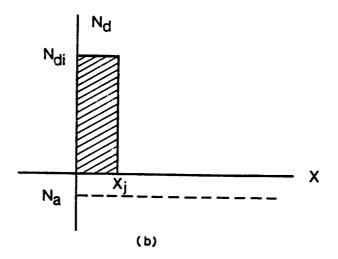

If a derivative of (2.32) is taken with respect to temperature, the temperature coefficient of the threshold voltage shift due to the enhancement implant is given by

$$T.C. = \frac{\epsilon_s}{C_{OX}} \left[ \frac{qN_a}{2\epsilon_s (\Phi_{bi} + V_{SB})} \right]^{V_c} \left[ \frac{1}{\left[ 1 - \frac{qN_{ai} X_i^2}{2\epsilon_s (\Phi_{bi} + V_{SB})} \right]^{V_c}} - 1 \right] \frac{d\Phi_{bi}}{dT} .$$

(2.34)

Since  $\Delta V_{th}$  in (2.32) and T.C. in (2.34) all depend on  $1/C_{OX}$  or  $t_{OX}$ , the temperature coefficient in  $ppm/^{o}C$  unit is thus insensitive to the oxide thickness  $t_{OX}$ . Note that the temperature drift is mainly a function of process parameters such as  $C_{OX}$ ,  $N_a$  and  $N_{a_1}$ , etc.. The only non-process parameter is the body bias  $V_{SB}$ . The depleted charge difference is reduced by increasing the body bias and the temperature coefficient of the threshold voltage shift due to the enhancement implant decreases correspondingly as shown in Fig. 2.7(a). As the implant depth is made shallower, the temperature coefficient of the enhancement device relative to that of the unimplanted device approaches zero.

In the figure, the incompleted part at a low body bias is when the depletion edge falls within the implant depth. Therefore, in applying (2.34), care must be taken for the depletion edge not to fall within the implant depth. If  $X_{dE} < X_i$ , the enhancement device is merely an unimplanted device with a higher bulk density and (2.34) no longer holds. For this case, (2.32) must be modified to

$$\Delta V_{ih} = \frac{kT}{q} \ln \frac{N_{ai} + N_a}{N_a} + \frac{[2q\epsilon_s N_a (\Phi_{bi} + V_{SB})]^{V_i}}{C_{OX}} \left[ (1 + \frac{N_{ai}}{N_a}) - \right] \quad . \tag{2.35}$$

There is a discontinuity in using (2.32) and (2.35) around  $X_{dE} \approx X_i$ . In case the depleted edge is comparable to the implanted depth, the depletion approximation fails inherently. In this analysis, this limiting case is not treated.

2

Fig. 2.7. Temperature coefficients of the threshold voltages of implanted devices relative to those of the unimplanted device : (a) enhancement implant and (b) depletion implant.

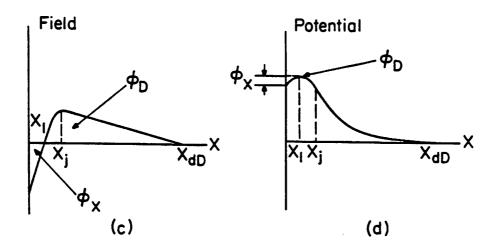

### 2.4.2. Depletion Implant

In this subsection, the temperature coefficient of the threshold voltage shift which results from the depletion implant is calculated. The depletion device is represented by a donor implant with an implant depth of  $X_j$  and a constant dopant density of  $N_{d_i}$  in a step profile approximation as shown in Fig. 2.6(b). Using (2.23)-(2.28), the threshold voltage shift by the depletion implant is

$$\Delta V_{ih} = \frac{Q_{iD} + Q_{iL}}{C_{OX}} + \Phi_X + \frac{[2q\epsilon_s N_a(\Phi_{bi} + V_{SB})]^{V_i}}{C_{OX}} \left[1 - (1 - \frac{N_a}{N_{di}})\right]$$

(2.36)

where the depletion-implant charge density per unit area  $Q_{iD}$  is given by

$$Q_{iD} = -qN_{di}X_j \tag{2.37}$$

which is independent of temperature, and only shifts down the threshold voltage by -3 Vafter compensating the equivalent bulk charge density of

$$Q_{ill} = q N_a X_i \quad , \tag{2.38}$$

and  $\Phi_X$  is the potential drop from the potential maximum point  $(X=X_1)$  to the surface (X=0) given by (AI.14). Since  $\Phi_{bi}$  has a negative temperature coefficient, the depth  $X_1$  increases as temperature rises. Therefore, the potential drop  $\Phi_X$  has a positive temperature coefficient and is a dominant source of the temperature variation of the threshold voltage shift by the depletion implant.

Assuming  $N_a/N_{di}$  is small enough, the differentiation of (2.36) with respect to temperature gives the temperature coefficient of the threshold voltage shift due to the depletion implant of

$$T.C. = \left\{ \frac{N_a}{N_{di}} - X_j \left[ \frac{qN_a}{2\epsilon_s (\Phi_{bi} + V_{SB})} \right]^{V_1} \right\} \frac{d\Phi_{bi}}{dT} .$$

(2.39)

The temperature coefficient calculated from (2.39) is shown in Fig. 2.7(b). As in the enhancement implant case, the temperature coefficient of the depletion device relative to

3

that of the unimplanted device approaches zero as the body bias increases and the implant depth is made shallower. Equation (2.39) consists of two temperature variations which are proportional to  $N_a$  and  $N_a^{V_c}$ , respectively. These variations cancel each other. Unlike the enhancement implant case,  $C_{OX}$  does not affect T.C. given by (2.39) while  $\Delta V_{th}$  in (2.36) depends on  $1/C_{OX}$ . Therefore, the temperature coefficient in  $ppm/{}^oC$  increases as the oxide thickness  $t_{OX}$  decreases. If all other parameters are fixed, a shallow single implant and a high body bias help reduce the temperature coefficient given by (2.39).

Let us further examine the body bias sensitivity of the threshold voltage shift due to the depletion implant. The differentiation of (2.36) with respect to the body bias yields

$$\frac{d\Delta V_{ih}}{dV_{SB}} = \frac{N_a}{N_{di}} - X_j \left[ \frac{qN_a}{2\epsilon_s (\Phi_{bi} + V_{SB})} \right]^{V_2}$$

$$\approx -0.02 , \quad \text{for} \quad V_{SB} = 2V$$

$$\approx -0.01 , \quad \text{for} \quad V_{SB} = 5V .$$

(2.40)

For example, if the body bias changes from 2V to 2.1V,  $\Delta V_{ih}$  changes by -2mV which may be intolerable in a precision circuit. If the body bias is increased to 5V, the  $\Delta V_{ih}$  variation is reduced by half compared to the 2V body bias case for the same amount of the body bias change. Hence, the high body bias helps reduce the body bias sensitivity of the threshold voltage difference. This argument applies to all types of devices.

In applying (2.39), we have to consider the non-pinchoff problem. Equation (2.39) does not hold when  $X_1$  reaches  $X_{1,max}$  [22]-[23] which is approximately

$$X_{1,max} = \left[\frac{2\epsilon_s kT}{q^2 (N_{d_l} - N_a)} \ln \frac{(N_{d_l} - N_a) N_a}{n_l^2}\right]^{\frac{1}{2}}$$

$$\approx 92.6 \ nm \quad \text{for} \quad N_{d_l} = 10^{17} \ cm^{-3} \ \text{at} \ 300^{\circ} K \ .$$

(2.41)

For the shallow implant of less than 100nm, the non-pinchoff problem is not present. For

the typical values of  $X_j = 100 nm$ ,  $N_{d_i} = 10^{17} cm^{-3}$  and  $N_a = 5 \times 10^{14} cm^{-3}$ , the following equation from (2.39) will estimate the temperature drift of the threshold voltage shift due to the depletion implant.

$$T.C. = -0.011 + 0.14(0.545 + V_{SB})^{V} mV/{}^{o}C$$

$$\approx 0.077 mV/{}^{o}C \quad \text{for} \quad V_{SB} = 2 V$$

$$\approx 0.046 mV/{}^{o}C \quad \text{for} \quad V_{SB} = 5 V \text{ at } 300^{\circ}K .$$

(2.42)

#### 2.4.3. Double Implant (Enhancement and Depletion)

In this subsection, the temperature coefficient of the threshold voltage shift which results from the double implant is calculated. The doubly-implanted device has a combination of acceptor and donor implants. That is, the four parameters,  $X_i$  and  $N_{ai}$ ,  $X_j$  and  $N_{di}$ , are involved in a step profile approximation. Generally, what has been done in the depletion implant case is applied in this case. However, due to the combination of two implementations, the equations are more complex. Using (2.23)-(2.28) and assuming  $X_j < X_i$ , the threshold voltage shift by the double implant is

$$\Delta V_{ih} = \frac{Q_{iD} + Q_{iE} + Q_{iU}}{C_{OX}} + \Phi_X$$

$$+ \frac{\left[2q\epsilon_s N_a (\Phi_{bi} + V_{SB})\right]^{V_i}}{C_{OX}} \left\{ 1 - \left(1 - \frac{N_a}{N_{di} - N_{ai}}\right) \left[1 - \frac{qN_{ai} N_{di} (X_i - X_j)^2}{2\epsilon_s (\Phi_{bi} + V_{SB}) (N_{di} - N_{ai})}\right]^{V_i} \right\}$$

(2.43)

where  $\Phi_X$  is given by (AI.11).

Assuming  $N_a/(N_{d_l}-N_{a_l})$  is small enough, the differentiation of (2.43) with respect to temperature gives the temperature coefficient of the threshold voltage shift due to the double implant of

$$T.C. = \left[\frac{N_a}{N_{d_l} - N_{a_l}} + \left[\frac{qN_a}{2\epsilon_s(\Phi_{b_l} + V_{SB})}\right]^{V_c} \left\{\frac{\epsilon_s}{C_{OX}}\right\}$$

(2.44)

ę

$$- \frac{\left[\frac{\epsilon_s}{C_{OX}} + X_j - \frac{N_{ai}(X_i - X_j)}{N_{di} - N_{ai}}\right]}{\left[1 - \frac{qN_{ai}N_{di}(X_i - X_j)^2}{2\epsilon_s(\Phi_{bi} + V_{SB})(N_{di} - N_{ai})}\right]^{\frac{1}{2}}}\right] \frac{d\Phi_{bi}}{dT} .$$

Equation (2.44) is basically similar to the equation for the depletion implant (2.39) except that the enhancement implant is involved. Thus, the general discussion on the depletion implant holds in the double implant case.

#### 2.5. Validity of a Depletion Approximation

For the convenience of analysis, semiconductor potential barriers are usually represented by two discrete regions such as a depletion region where no free carrier exists and a quasi-neutral region where the charge neutrality is assumed. Generally, the depletion approximation based on the above assumption is not valid within a few Debye lengths from the depletion edge since a free carrier density cannot change abruptly. The free carrier distribution is characterized by the Debye length which is a function of the doping density so that

$$L_D = \left(\frac{2kT\epsilon_s}{q^2N_i}\right)^{V_i}$$

(2.45)

where  $N_i$  is the impurity concentration. Therefore, the application of the depletion approximation to the shallow implant case needs considerations.

The potential difference between two points where the carrier concentrations are  $n_1$ and  $n_2$ , respectively, is a logarithmic function of the ratio,  $n_1/n_2$ , :

$$\Delta \Phi = \frac{kT}{q} \ln \frac{n_1}{n_2} \quad . \tag{2.46}$$

Table II lists the calculated parameter values in the shallow depletion implant case. For example, if  $X_j=28nm$ , the carrier density difference between the field zero point  $X_1$  and the

| Π | Ľ | BI | ٧ | L |

|---|---|----|---|---|

|---|---|----|---|---|

| L¥<br><sup>I</sup> dxə | Φ <sup>x</sup> (λ) | ( <i>wu</i> ) <sup>a</sup> 7 | ( <i>wu</i> ) <sup>1</sup> X | ( <i>wu</i> ) <sup><i>f</i></sup> X | ( <sub>t</sub> _w)"N |

|------------------------|--------------------|------------------------------|------------------------------|-------------------------------------|----------------------|

| Ĺ                      | 150.0              | <i>L</i> .2                  | ٤.11                         | 14                                  | 2×101<br>2×10        |

| ٢5                     | 201.0              | 8                            | 52.6                         | 58                                  | ۲.5×10 <sup>17</sup> |

| 5.2×10*                | 852.0              | 1.21                         | 8.92                         | 02                                  | 1×101 <sub>11</sub>  |

| 901×7.1                | 275.0              | 15.2                         | £.18                         | 100                                 | <u>عا</u> 01×2/      |

| 9×10 <sub>8</sub>      | 122.0              | 81                           | 114.2                        | 140                                 | 2×10 <sub>19</sub>   |

| 2×1010                 | £\$9`0             | 8.91                         | 138.9                        | 0/1                                 | 4×10 <sub>16</sub>   |

| 101×2.8                | 928.0              | 22.5                         | 180.2                        | 220                                 | 3×10 <sub>19</sub>   |

A DEPLETION APPROXIMATION A DEPLETION APPROXIMATION A DEPLETION APPROXIMATION

surface is only a factor of 52. That is,

(5.47)

$$\frac{1}{10} = \frac{1}{10} = \frac{$$

This means free carriers cannot be accumulated like a delta function and the distribution of free carriers is characterized by the Debye length. Therefore, it is reasonable to define the threshold condition of the depletion device in the same way as in the enhancement device.

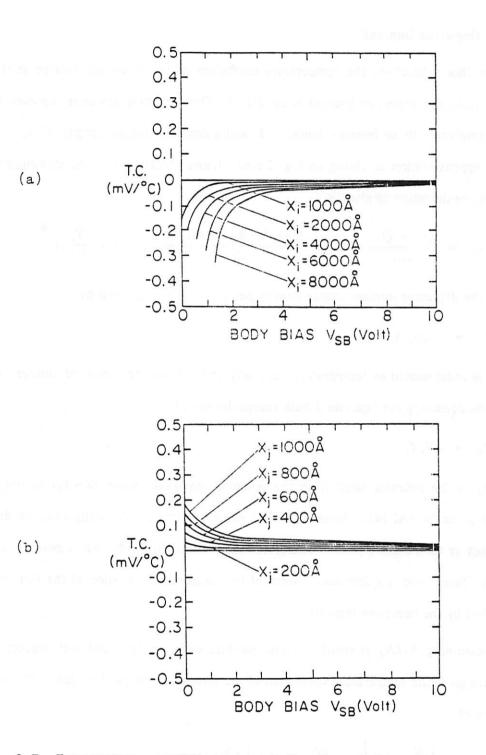

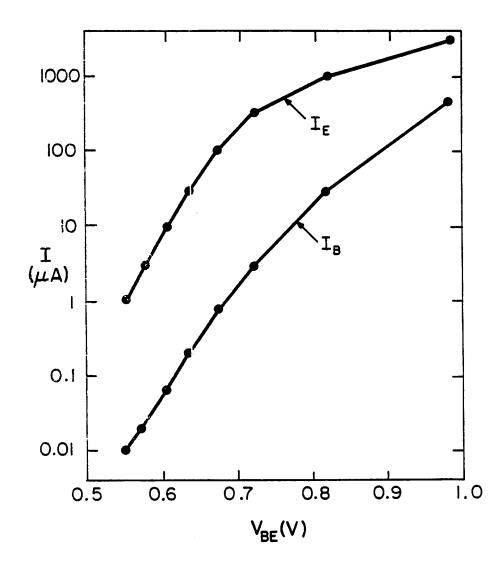

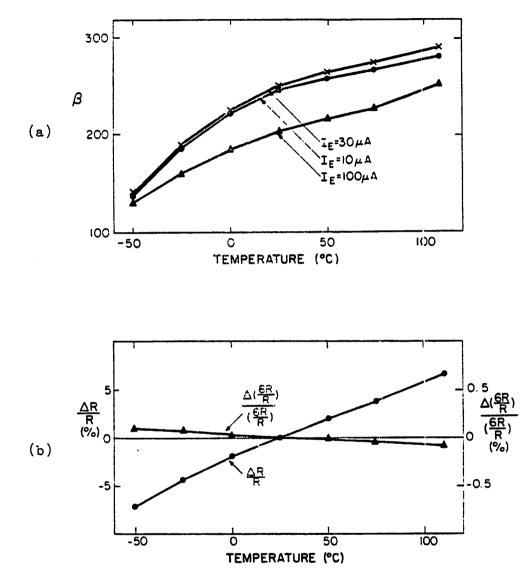

## 2.6. Temperature Measurement of IGFET Characteristics

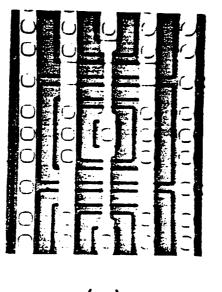

The l-V characteristics of five samples of the four basic types of devices are measured with drain-source voltage kept constant by 4V from -30 to  $110^{\circ}$  C. The samples are prepared employing a typical Si-gate NMOS process on a 25-30  $\Omega$ -cm Boron doped p-type <100> substrate with an oxide thickness of 100nm, a gate width of  $50\mu m$  and a gate length of  $7\mu m$ . The five sets of measured  $I-V^{\circ}$  data are averaged and fitted employing the linear regression method to give the typical temperature variations of the four threshold

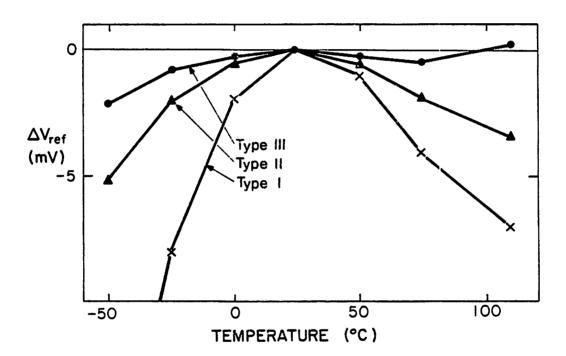

Fig. 2.8. Typical measured temperature variations of the four devices in NMOS technology.

voltages as shown in Fig. 2.8. At room temperature, the threshold voltages of the unimplanted device, the enhancement device, the depletion device and the doubly-implanted device are about 0, 1, -3 and -1V, respectively. Table III summarizes typical process parameters simulated by the process simulation program SUPREM [38]. The implant depth in a step profile approximation of a Gaussian profile is approximated by  $R+2\Delta R$  as in [27] where R is a range and  $\Delta R$  is a straggle.

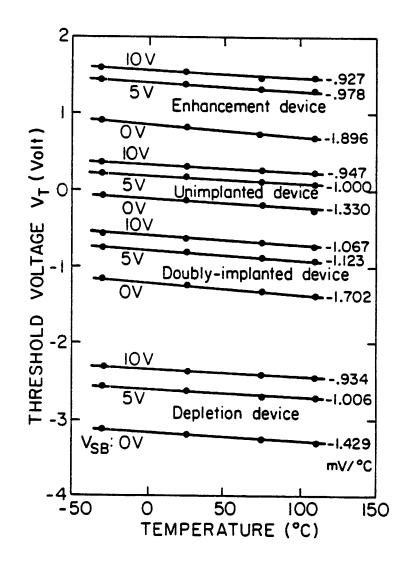

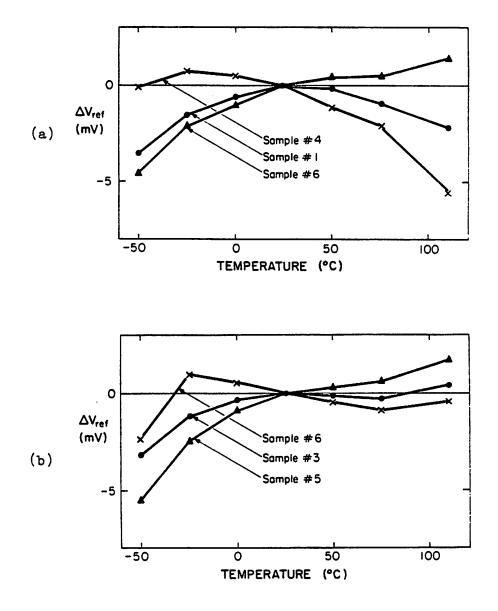

## 2.6.1. Threshold Voltage Difference

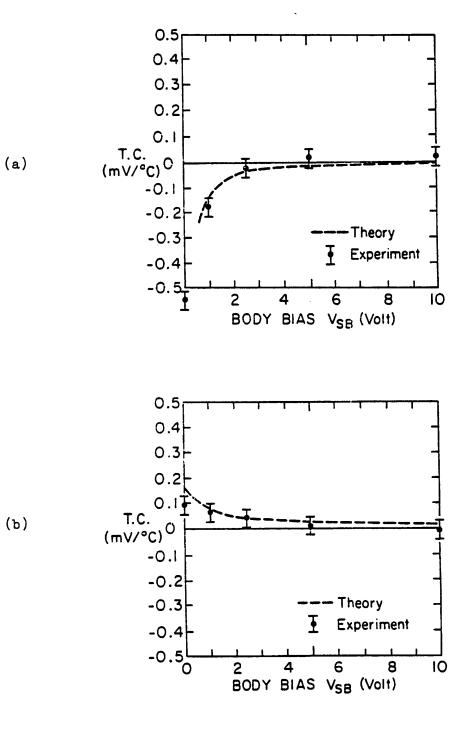

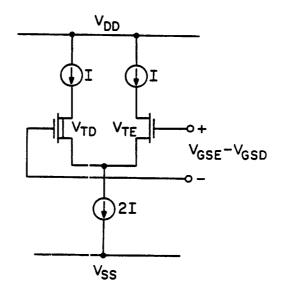

The measured temperature coefficients of each threshold voltage are processed to give the temperature coefficients of the implanted devices relative to those of the unimplanted device. The dashed lines in Figs. 2.9(a), (b) and (c) show the theoretical temperature coefficients of the enhancement device, the depletion device and the doubly-implanted device relative to those of the unimplanted device, respectively. The dots with the error bars represent the measured values of the relative temperature coefficients. The theoretical

## TABLE III

| Parameters                   | Enhancement | Depletion | Double-implant |         |

|------------------------------|-------------|-----------|----------------|---------|

|                              | Boron       | Arsenic   | Boron          | Arsenic |

| Dose $(10^{11} cm^{-2})$     | 2.6         | 14        | 2.6            | 9       |

| Energy (KeV)                 | 50          | 180       | 50             | 180     |

| t <sub>OX</sub> (nm)         | 103         | 103       | 103            | 103     |

| Range (nm)                   | 160         | 94.5      | 160            | 94.5    |

| Straggle (nm)                | 55.1        | 33.2      | 55.1           | 33.2    |

| % in Si*                     | 94          | 57        | 94             | 57      |

| Depth in step                |             |           |                |         |

| Approximation ( <i>nm</i> )* | 300         | 80        | 300            | 80      |

# PROCESS PARAMETERS (SUPREM SIMULATION)

\*Note : Values after drive-in of 30 Min. at 900°C and 30 Min. at 1000°C.

Fig. 2.9. Measured temperature coefficients of the threshold voltages of implanted devices relative to those of the unimplanted device : (a) boron-implanted device and (b) arsenic-implanted device.

Fig. 2.9. Continued : (c) boron- and arsenic-implanted device and (d) boron-implanted device relative to the arsenicimplanted device.

curves are calculated at 300° K using (2.34), (2.39) and (2.44) based on the process data listed in Table III. The error bar indicates an equivalent temperature variation of an estimated 1 mV measurement error.

In the experimental results, the effect of the body bias on the relative temperature coefficients is as expected. However, the body bias independent constant temperature drifts are observed in all types of devices, especially in the doubly-implanted device (Fig. 2.9(c)). In both the enhancement device and the depletion device, the temperature coefficient deviations from the theoretical values (Figs. 2.9(a) and (b)) are small compared to the measurement error. In the double implant case (Fig. 2.9(c)), however, the measured deviation is on the order of  $0.1 mV/^{\circ}C$  and is much bigger than expected. This deviation corresponds to the temperature coefficient contributed by the 30mV built-in potential difference of the unimplanted device and the doubly-implanted device at threshold. In the enhancement and depletion implant cases, the temperature coefficient deviations from the theoretical values are around  $0.02mV/^{\circ}C$  with one in the positive direction and the other in the negative direction. These deviations cancel each other out if two temperature coefficients are added as shown in Fig. 2.9(d).

#### 2.6.2. Gate-Source Voltage Difference

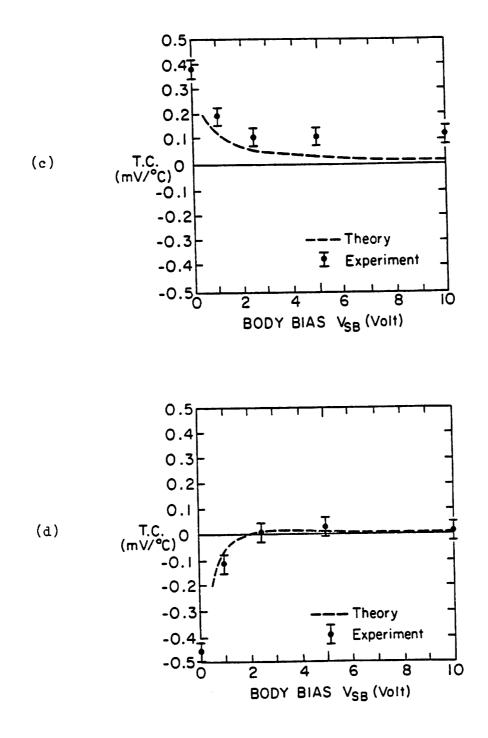

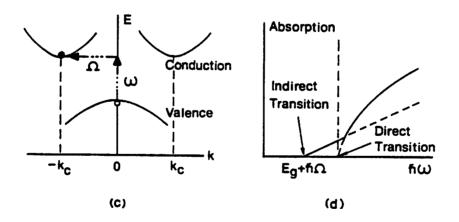

The gate-source voltage of IGFET's is the sum of the threshold voltage and a voltage which depends on the bias current and the channel mobility. Therefore, the channel mobility temperature variation [39] will effect the temperature characteristics of IGFET's. Figure 2.10(a) shows a differential pair voltage reference using the devices with different channel implants. The gate-source voltage difference of two devices with the equal bias current *I* is

$$\Delta V_{GS} = \Delta V_{th} + [\Delta(\frac{2}{K})^{V_2}]I^{V_2}$$

(2.48)

where  $K = \overline{\mu} C_{OX}(W/L)$  and (W/L) is the ratio of the channel width to the channel length. The temperature variation at a high bias current level is mainly due to the mismatch in the

(a)

Fig. 2.10. (a) Differential pair composed of two devices with different channel implants. (b) Measured temperature coefficients of the gate-source voltage difference.

channel mobilities of two devices while the temperature variation at a low bias current level is dominated by the threshold voltage difference of two devices.

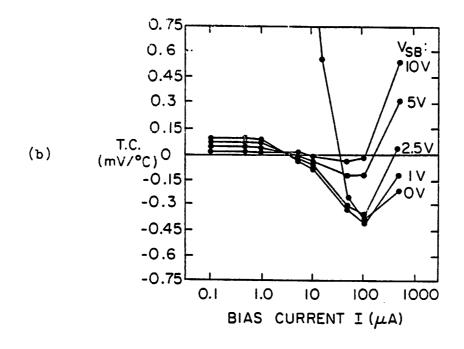

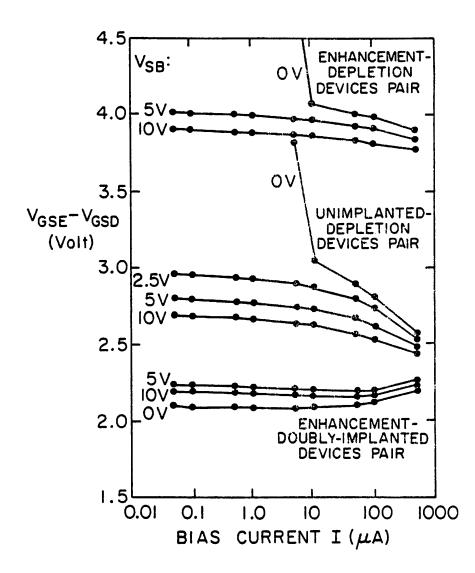

As an example, Figure 2.10(b) shows the measured temperature coefficient of the gate-source voltage difference for the differential pair composed of the unimplanted device and the depletion device. At a low bias current level, the temperature variation observed is close to that of the threshold voltage difference. On the other hand, at a high bias current level, the temperature variation is quite steep and unpredictable because the mobility mismatch of two devices is involved. As the bias current is lowered, the temperature variation is reduced. Notice that the gate-source voltage difference also changes due to the bias current as well as the body bias as shown in Fig. 2.11. A low bias current operation helps reduce the bias current sensitivity and the temperature drift of the gate-source voltage difference. However, if a device is biased at too low a current level, the device enters the subthreshold region and difficulties are expected in an actual circuit design. The bias current and body bias sensitivities of the gate-source voltage difference may be critical in a precision voltage reference circuit such as proposed by Blauschild et al. [8]. The steep variation at zero body bias (Figs. 2.10(b) and 2.11) in the depletion device is due to the non-pinchoff problem discussed in [22]-[23].

## 2.6.3. Device Test Results

From the theory developed in Section 2.4 and the discussions of two previous subsections (2.6.1 and 2.6.2) based on the temperature measurements of I-V characteristics in saturation region, the following conclusions can be drawn.

1. The temperature coefficient introduced by a double implant is much bigger than that by a single implant.

2. The body bias helps reduce the temperature drift of both the gate-source voltage difference and the threshold voltage difference of two devices.

Fig. 2.11. Typical measured gate-source voltage differences as a function of bias current and body bias.

3. The temperature drift of the threshold voltage shift resulting from the channel implantation is noticeably lowered in a single implant case when the body bias is increased.

4. Below the bias current level of  $10\mu A$ , the temperature drift of the gate-source voltage difference is very low in a single implant case.

Considering the analysis and the above experimental observations, the threshold voltage difference temperature drift as well as the instability in the bias current and in the body bias will limit the overall performance of the voltage reference circuit based on the threshold voltage difference. So as to achieve a performance predicted, we must

1. make the bias current low and constant,

- 2. apply a high body bias and keep it constant, and

- 3. use a single channel implant for the threshold shift.

## **CHAPTER 3**

# SI BANDGAP AS A CMOS VOLTAGE SOURCE

#### 3.1. Introduction

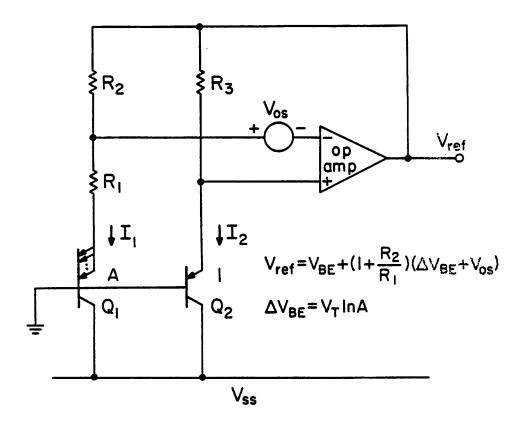

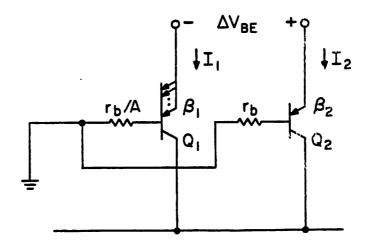

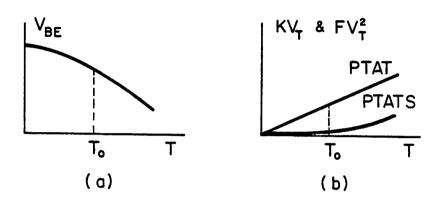

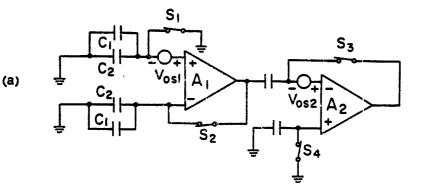

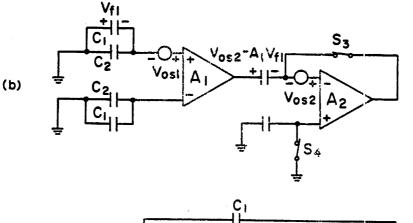

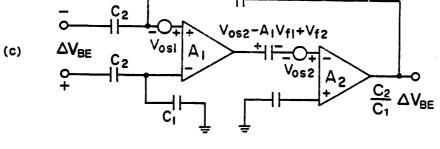

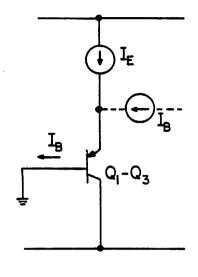

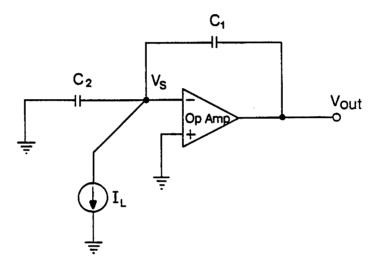

Precision bandgap references have been successfully implemented in bipolar technology. However, the performance achievable in bipolar has never been achieved in CMOS. In Chapters 3, 4 and 5, one circuit approach to implement a precision curvaturecompensated switched-capacitor CMOS bandgap reference which is compatible with a standard digital CMOS process and achieves a temperature stability on the order of  $10ppm/^{\circ}C$ over the commercial temperature range will be described. In the reference, a temperaturestable voltage is developed by adding a linear and a quadratic temperature correction voltages to the forward-biased diode which is obtained from the substrate pnp transistors available in CMOS process. The linear temperature correction voltage is proportional to the absolute temperature (commonly called PTAT) while the quadratic temperature correction voltage is proportional to the absolute temperature squared (PTATS). They are independently adjustable to set the reference output voltage for a minimum temperature drift.

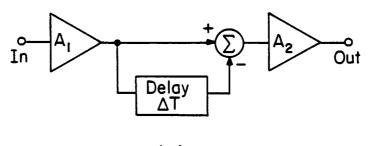

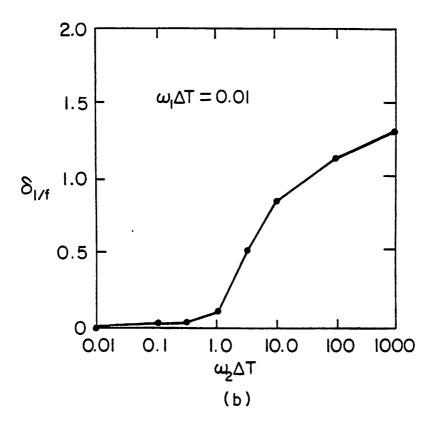

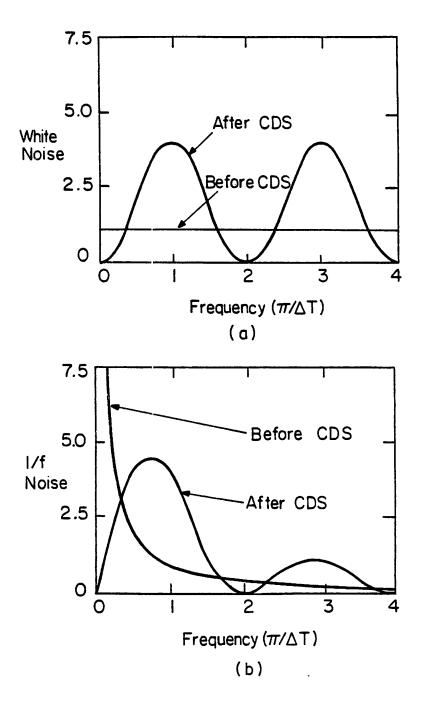

The offset voltage of a CMOS op amp is eliminated using the correlated-double sampling (CDS) technique [40]. The finite current gain and the base spreading resistance of the native substrate pnp transistors in a standard CMOS process are canceled to the first order and the amplification ratio is set by a capacitor ratio rather than by a resistor ratio. Due to the cyclic behavior of the offset cancellation in this technique, the output reference voltage is not valid at all times. However, the reference can be operated synchronously with other elements of the systems. Since the periodic offset sample and subtraction cycle effectively removes the low frequency 1/f noise of a CMOS op amp along with its offset, the dominant noise source is the thermal noise of a CMOS op amp which is designed to be on the order of  $100\mu V$  (rms) at the output in the 500 kHz bandwidth.

In Section 3.2, the Si bandgap is treated qualitatively to understand its temperature dependence. In Sections 3.3, 3.4 and 3.5, the temperature characteristics of the substrate pnp transistor and other components are investigated theoretically and the primary limitations in a conventional CMOS bandgap reference implementation are discussed. In Section 3.6, a temperature compensation technique suitable for a CMOS bandgap reference is introduced.

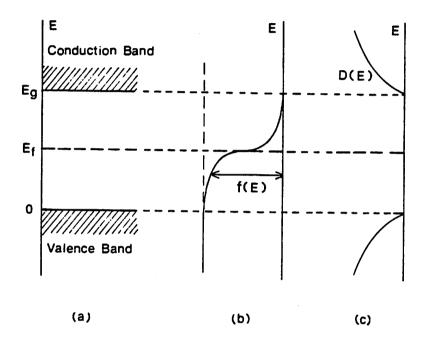

#### 3.2. Silicon Energy Gap and its Temperature Dependence

For any semiconductor, there is a forbidden energy region in which no allowed states can exist. Above and below this forbidden energy gap are permitted energy bands. The upper bands are called the conduction bands, and the lower bands the valence bands. The separation between the energy of the lowest concluction band and that of the highest valence band is called the bandgap,  $E_g$  (1.12eV for Si at room temperature). The bandgap varies noticeably with temperature. There are two reasons for its temperature dependence. First, the crystal lattice expansion (dilation) due to external stress, pressure or temperature accounts for the change of the energy gap since the energy band depends on the distance between neighboring ions. Second, the electron-lattice interaction energy which results from the indirect optical transition of Si reflects the change of the energy gap with temperature. Although there exist qualitative theoretical analyses describing the temperature dependence of the energy gap, theoretical analyses do not exhibit the accuracy that many empirical equations have, and heavily depend on the parameters obtained from direct measurements such as elastic constant, mobility, compressibility and volume expansion coefficient, etc.. Especially, the quantitative analysis of the second-order temperature dependence is not available.

The concepts of effective mass, density of states, intrinsic carrier concentration and mobility are summarized in Appendix II and, in the following subsections, the qualitative treatment of the Si energy gap is given based on Appendix II for the understanding of the temperature dependence of the Si bandgap.

### 3.2.1. Energy Gap Narrowing with Impurity Concentration

As impurity concentration increases, the Fermi level approaches the allowed bands, impurity states broaden, and the intrinsic bandgap is narrowed (so called band-edge trailing). The extreme case is the degenerate semiconductor when the impurity concentration is greater than the effective density of states ( $N_c$  or  $N_v$ ). In this case, the Fermi level is located within the conduction or valence band. The conduction or valence band edge is not sharp, and it tails off gradually into the forbidden energy gap. This is due to the fact that the distribution of impurity changes from a delta function to an impurity band. This broadened band joins the conduction or valence band. This makes the band edges trail into the bandgap.

In Si, the energy gap narrowing becomes important at impurity concentrations greater than about  $10^{17} cm^{-3}$ . The experimentally derived Si bandgap narrowing as a function of the impurity concentration N, was proposed by Slotboom and De Graaff [41]:

$$\Delta E_{g1}(N_i) = 9 \times 10^{-3} \left[ \ln \frac{N_i}{10^{17}} + \left( \ln^2 \frac{N_i}{10^{17}} + 0.5 \right)^{1/2} \right]$$

(3.1)

where  $E_{g1}$  represents the linearly-extrapolated Si bandgap at 0°K. For example, the Si bandgap narrows by approximately 68eV for the impurity concentration of  $9 \times 10^{19} cm^{-3}$ .

#### 3.2.2. Shift of Energy Gap with Lattice Dilation

The band structure varies with a lattice constant for a crystal such as Si or Ge. In these crystals, a decrease in a lattice constant increases the separation between the valence

band and the conduction band. The deformations of lattice such as compression and dilation which are caused by external strain, pressure or temperature, etc. result in the change of energy gaps in semiconductors. Bardeen and Shockley [42] treated the effect of a lattice expansion on the energy gap for the non-polar crystals such as Si and Ge.

When a cubic crystal is subject to a homogeneous strain, the energy gap can be expressed in the form of

$$E_g = E_{og} + E_{1g} \Delta \tag{3.2}$$

where  $\Delta$  is the lattice dilation and  $E_{1g}$  is dependent on the lattice deformation while  $E_{og}$  is not. The energy gap change per unit dilation  $E_{1g}$  is given approximately by [42]

$$E_{1g} = V \frac{dE_g}{dV}$$

$$= -(|E_{1c}| + |E_{1v}|) \approx -17.8 \ eV/\text{unit dilation for Si}$$

(3.3)

where  $E_{1c}$  and  $E_{1v}$  are the changes of the conduction and valence bands per unit dilation of lattice, with the values of 6.5 and 11.3 per unit dilation, respectively. From the above equation, we can estimate the thermal-expansion effect, or what is often called the dilation contribution, which accounts for the effects of the change of a lattice constant on the energy gap. That is, if it is assumed that the temperature variation is entirely due to the thermal expansion, the temperature variation of the energy gap with dilation can be obtained by multiplying the volume expansion coefficient of  $10 \times 10^{-6/0} C$  for Si, so that

$$\frac{dE_g}{dT} = E_{1g} \frac{1}{V} \frac{dV}{dT} \approx -1.78 \times 10^{-4} \ eV/^{\circ}K \quad . \tag{3.4}$$

However, this dilation effect on the temperature dependence of the energy gap does not explain the typically measured temperature drift of  $-2.4 \times 10^{-4} eV/^{\circ} K$  of the Si bandgap. The other factor for the extra drift is due to the electron-lattice interaction which will be discussed in the next subsection.

The temperature dependence of conductivity will be dominated by the exponential dependence  $\exp(-E_g/2kT)$  since the conductivity is proportional to the product of *n*, in (AII.16) and  $\mu$  in (AII.20), with  $\mu$  being proportional to  $T^{-3/2}$ . Therefore, the conductivity  $\sigma$  is given by

$$\sigma = \sigma_{\infty} \exp(-\frac{E_{\kappa}}{2kT})$$

(3.5)

where the conductivity  $\sigma_{\infty}$  is independent of temperature. If  $\sigma_{\infty}$  is assumed to be independent of pressure, the differentiation of (3.5) with respect to pressure gives the pressure dependence of the energy gap so that

$$\frac{dE_g}{dp} = E_{1g} \frac{1}{V} \frac{dV}{dp} = -2kT \frac{1}{\sigma} \frac{d\sigma}{dp} \qquad (3.6)$$

The energy gap can be estimated from two conductivities  $\sigma_1$  and  $\sigma_2$  measured at temperatures,  $T_1$  and  $T_2$  ( $T_2 > T_1$ ):

$$E_g = 2K \ln(\frac{\sigma_2}{\sigma_1}) \left(\frac{1}{T_1} - \frac{1}{T_2}\right)$$

(3.7)

where  $E_g$  is assumed to remain constant for  $T_1$  and  $T_2$ . The value obtained in this way can be combined with the compressibility data (the change of volume with pressure) to estimate the change in the energy gap with dilation,  $E_{1g}$ . For Si, the bandgap decreases with pressure typically at a rate of  $2.4 \times 10^{-6} eV - cm^2/Kg$ .

## 3.2.3. Shift of Energy Gap with Electron-Phonon Interaction

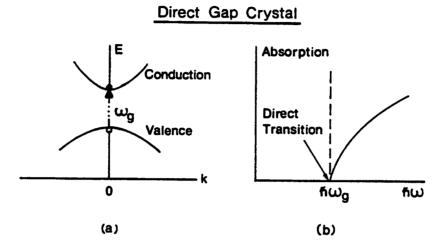

The bottom of the conduction band in Si appears along <100> axes while the valence bands are degenerate at the zone center (000). The direct transition between the valence band and the conduction band occurs in most semiconductors as illustrated in Fig 3.1(a) and (b). In Si, electrons at the lowest energy in the conduction band have a nonzero momentum. Since the holes at the valence-band edge do have a zero momentum, an indirect transition that conserves both energy and momentum is impossible without

Indirect Gap Crystal

Fig. 3.1. Comparison between the direct optical transition (a) -(b) and the indirect optical transition (c)-(d).

a lattice interaction occurring simultaneously. Thus, the indirect transition across the forbidden energy gap corresponds to a simultaneous interaction of three particles; the electron, the hole and a phonon that represents the lattice interaction as illustrated in Fig. 3.1(c) and (d). The threshold of continuous optical absorption at the frequency  $\omega_g$  determines the bandgap  $E_g = \hbar \omega_g$  in the direct absorption process because the absorbed photon has a very small wavevectors. However, in the indirect absorption process, generated electrons and holes (exitons) are separated by a substantial wavevector  $\vec{k_c}$ . For the energy and momentum conservation, the following relations hold depending on the absorption (-) and the emission (+) of phonons.

$$\hbar\omega = E_g - E_{ex} \pm \hbar\Omega \tag{3.8}$$

and

$$\vec{k}(photon) = \vec{k}_c + \vec{K} \approx 0 \tag{3.9}$$

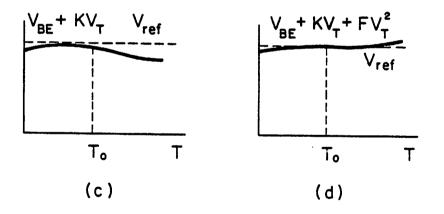

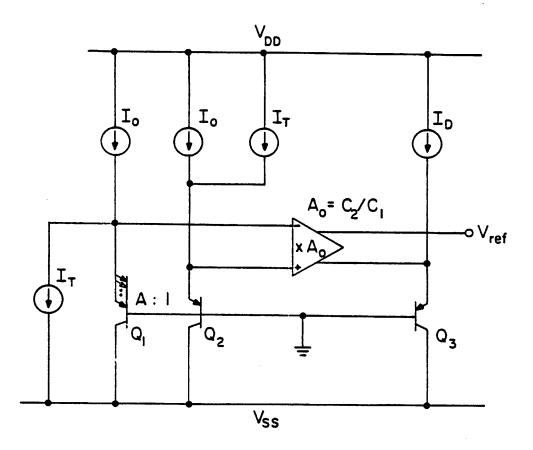

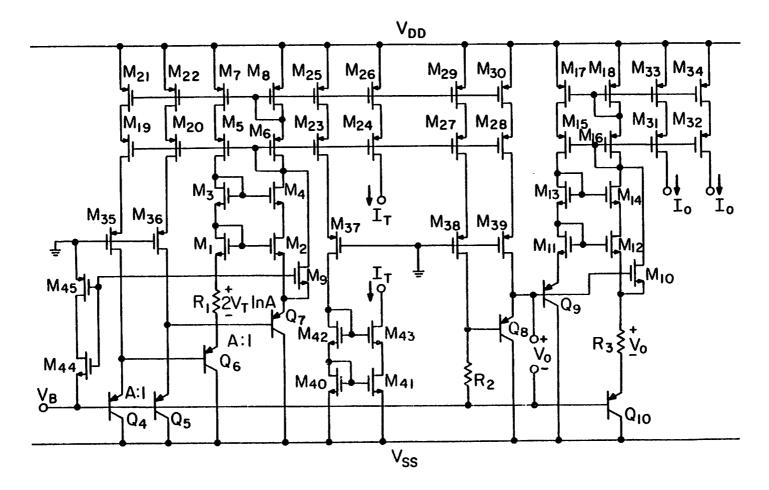

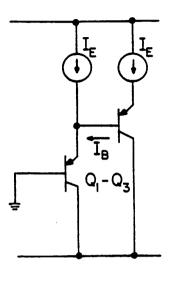

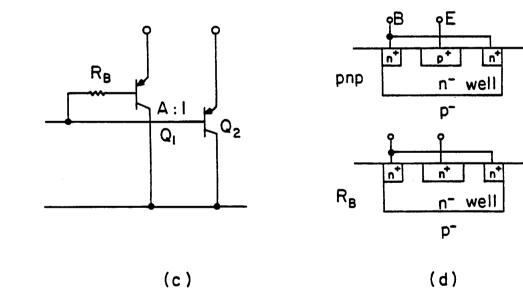

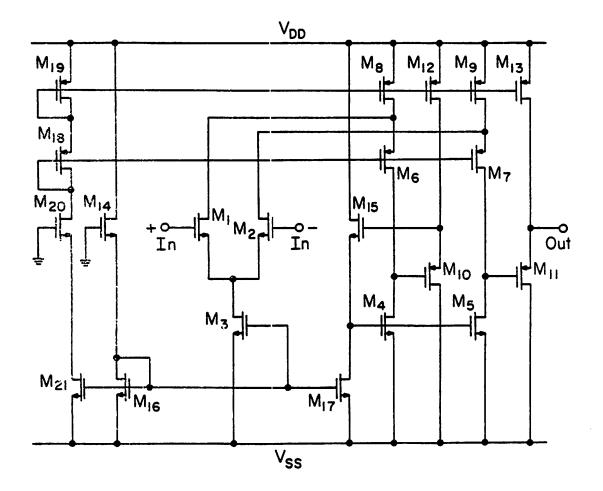

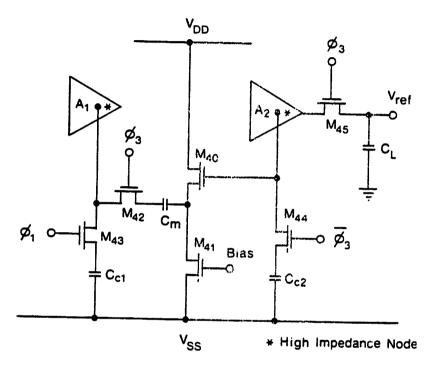

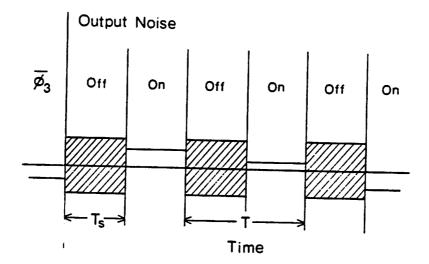

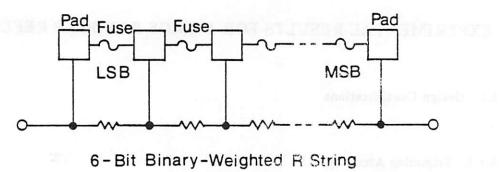

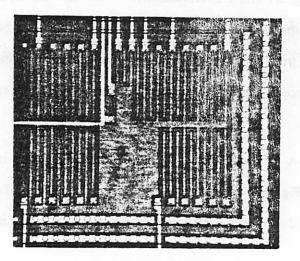

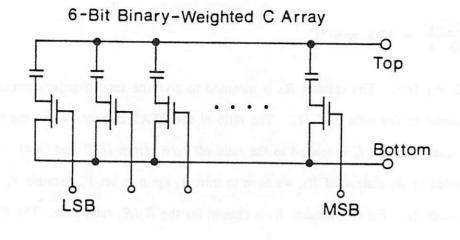

where  $E_{ex}$  ( $\approx 14 meV$ ) is the exiton dissociation energy,  $\#\Omega = 57.3 meV$ , and  $\overline{K}$  is the wave vector of a phonon [43].