Copyright © 1983, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# DELIGHT: AN INTERACTIVE SYSTEM FOR OPTIMIZATION-BASED ENGINEERING DESIGN

by

William T. Nye

Memorandum No. UCB/ERL M83/33

31 May 1983

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

Research sponsored by the Joint Services Electronics Program Contract F49620-79-C-0178.

. •

M83/33 385 Pages Velo Bind

# DELIGHT: AN INTERACTIVE SYSTEM FOR OPTIMIZATION-BASED ENGINEERING DESIGN

by

William T. Nye

Memorandum No. UCB/ERL M83/33

31 May 1983

#### DELIGHT: An Interactive System for Optimization-Based Engineering Design

Ph.D.

William T. Nye

EECS Dept.

Signature: Aller Signature: Committee Chairman

#### ABSTRACT

DELIGHT is an interactive system for applying optimization techniques to engineering design. With DELIGHT, designers can use optimization algorithms to improve the performance of their designs by automatically adjusting design parameters. DELIGHT offers the capability of optimizing arbitrary performance criteria as well as of studying complex tradeoffs between multiple competing objectives, while simultaneously satisfying multiple constraint specifications.

The use of optimization in engineering design was proposed in the sixties, especially for discrete electrical circuits such as filters. However, its use has not become as widespread as one would expect. We examine the shortcomings of several applications of classical optimization techniques to engineering design and develop design criteria for a computer-aided design system that should overcome these difficulties. These criteria, and the intention of serving a wide range of users from designers to optimization experts and system-support personnel, are used in the design of DELIGHT.

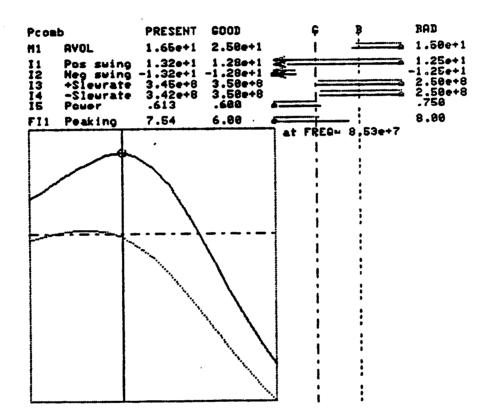

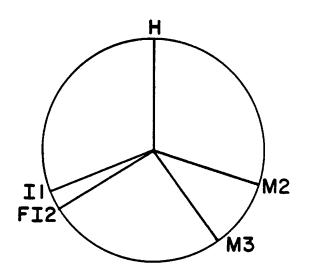

The various aspects of the DELIGHT system—the RATTLE language, RATTLE extensibility through defines and macros, the library of optimization algorithms, the problem description facilities, a set of high-level matrix macros, and terminal-independent color graphics — are introduced and described in detail. A novel feature of the DELIGHT system is a new multiple objective problem formulation that provides a means of effectively classifying and conveying the relative importance of design specifications. A methodology for performing design tradeoffs when using this formulation is introduced that uses a new graphical display called the performance comb.

The DELIGHT system is intended to be used in many different areas of engineering design. Hence, we introduce a simulation interface methodology and other necessary features that facilitate the coupling of DELIGHT to existing simulation programs. We then take a look at several application areas and demonstrate the usefulness of the system by detailing the optimization of two electronic integrated circuits. Successful optimization of several industrial circuits and of systems in other engineering areas are reported that further show the effectiveness of the system.

## Acknowledgements

I would like to express my deepest gratitude to Professor A. Sangiovanni-Vincentelli, my research advisor, and Professor L. Polak for introducing and giving me the opportunity to work in optimization and computer-aided design. They have supported me with enthusiasm and were available for numerous discussions throughout the course of my graduate study at Berkeley. Also, it is a pleasure to thank them, along with Professor K. Pister, for serving on my dissertation committee.

The special contributions by A. Sangiovanni-Vincentelli to cultivating my ability to make clear presentations, both verbally and in writing, will have lifelong value. I will always remember those occasions when, after expressing my excitement over something I had just written, he would peer over the top of his glasses and say, "let —me —see —it —first!"

The rewarding discussions I have had with fellow graduate students and others have contributed many useful ideas to this research. R. Balling, G. De Micheli, N. English, T. Essebo, Andrew Heunis, M. Karandikar, K. Keller, J. Kleckner, P. Labuhn, E. Lelarasmee, Sharad Nandgaonkar, P. Nicklin, R. Oliver, T. Quarles, Dave Riley, P. Siegel, James Spoto, Andre Tits, V. Visvanathan, Y. Wardi, and T. Wuu, are just a few of the names that come to mind. Andre Tits, in particular, has had a major influence on this work. Special thanks to the brave students who took EECS 241 in the fall of 1982 and provided their feedback on the results of this work.

i

My occasional acquaintances with W. Joy in Computer Science have inspired me to try to provide just a fraction of the benefit that he has given to mankind through his work with UNIX.

I take great pleasure in showing my appreciation of the friendship extended by G. Brand, C. Courcoubetis, J. Dorfman, E. Eschen, L. Guy, T. Hull, J. Jones, M. Loo, L. Gast, A. Neirynck, I. Ratiu, T. Salcudean, S. Sastry, R. Silva, D. Stimler, E. Szeto, A. Vladimirescu, professors P. R. Gray, D. A. Hodges, A. R. Newton, and D. O. Pederson, and many others, and also by the entire staff of the Electronics Research Laboratory and the Department of Electrical Engineering and Computer Science at Berkeley. Many other friends at Harris Semiconductor too numerous to mention are also appreciated. Special thanks to T. King for assisting with the figures.

My association with Professors A. Brodersen and S. Director during my early years in Electrical Engineering at the University of Florida created important foundations necessary for my doctoral work at Berkeley.

I would like to acknowledge research grants from Harris Corporation and thank, in particular, J. Cornell and J. Spoto of Harris Semiconductor for providing an ideal environment in which to demonstrate the industrial applicability of my work. The support of the Air Force Office of Scientific Research, the Joint Services Electronic Program, the National Science Foundation, and MICRO is also recognized.

Finally, I wish to express my gratitude to my parents, Sylvia and Thomas.

# Table of Contents

| CHAPTER 1: Introduction                                         | 1  |  |  |  |  |

|-----------------------------------------------------------------|----|--|--|--|--|

| 1.1. The Nature of Engineering Design                           |    |  |  |  |  |

| 1.2. Examples of Design Problems Addressed                      |    |  |  |  |  |

| 1.3. Dissertation Outline                                       | 7  |  |  |  |  |

| CHAPTER 2: Overview of Optimization-Based Computer-Aided-Design | 8  |  |  |  |  |

| 2.1. Early Efforts                                              | 8  |  |  |  |  |

| 2.2. Recent Design Systems                                      | 14 |  |  |  |  |

| 2.3. Limitations of These Systems                               | 19 |  |  |  |  |

| CHAPTER 3: Goals and Design Criteria of DELIGHT                 | 25 |  |  |  |  |

| 3.1. Setting the Stage                                          | 25 |  |  |  |  |

| 3.2. Classes of Users Supported                                 |    |  |  |  |  |

| 3.3. Needs of the Various Users                                 | 27 |  |  |  |  |

| 3.4. Resulting Design Criteria                                  | 31 |  |  |  |  |

| CHAPTER 4: DELIGHT System Features                              | 32 |  |  |  |  |

| 4.1. Introduction and Overview                                  | 32 |  |  |  |  |

| 4.2. RATTLE Language                                            | 34 |  |  |  |  |

| 4.2.1. Functions of the Interactive Language in DELIGHT         | 35 |  |  |  |  |

| 4.2.2. Why a New Language is Needed                             | 37 |  |  |  |  |

| 4.2.3. Why RATTLE is Similar to Ratfor                          |    |  |  |  |  |

| 4.2.4. Preliminary Design Decisions                             | 41 |  |  |  |  |

| 4.2.5. Basic Language Statements and Features                   | 45 |  |  |  |  |

i

| 4.2.6. Interrupts and Run-Time Errors                             | 55         |

|-------------------------------------------------------------------|------------|

| 4.2.7. Incremental Program Development                            | 59         |

| 4.2.8. Extensibility: Defines and Macros                          | 62         |

| 4.2.8.1. Character Stream View of I/O and Pushback                | <b>6</b> 4 |

| 4.2.8.2. Defines and Extensions                                   | 67         |

| 4.2.8.3. Compile-Time Macros                                      | 72         |

| 4.3. Matrix Macros                                                | 77         |

| 4.4. Problem Input Language                                       | 80         |

| 4.4.1. Mathematical Programming Formulations                      | 80         |

| 4.4.1.1. Classical Single Cost with Constraints                   | 81         |

| 4.4.1.2. Multiple Objectives with Constraints                     | 83         |

| 4.4.2. DELIGHT Problem Description Facilities                     | 98         |

| 4.4.2.1. Classical Problem Description                            | <b>9</b> 8 |

| 4.4.2.2. Multiple Objective, Engineering-Oriented Problem         |            |

| Description                                                       | 106        |

| 4.5. Optimization Algorithms and Problem/Algorithm Interfaces     | 115        |

| 4.5.1. Introduction to the RATTLE Optimization Algorithms Library |            |

| •••••••••••••••••••••••••••••••••••••••                           | 118        |

| 4.5.1.1. Purpose and Structure                                    | 118        |

| 4.5.1.2. Structure of Optimization Algorithms                     | 121        |

| 4.5.1.3. Basic Feasible Directions Algorithms                     | 127        |

| 4.5.2. Enhanced Feasible Directions Algorithms for Engineering    |            |

| Design                                                            | 132        |

| 4.5.2.1. Why Feasible Directions Algorithms are Good for En-      |            |

| gineering Design                                                  | 132        |

.

.

ü

.

•

.

.

|                                                              | 105         |

|--------------------------------------------------------------|-------------|

| 4.5.2.2. Enhanced Phase I-II-III Algorithm                   | 135         |

| 4.5.3. Details of the RATTLE Optimization Algorithms Library | 142         |

| 4.5.3.1. Detailed Structure of Library Entries               | 142         |

| 4.5.3.2. Listing of Library Entries                          | 146         |

| 4.5.3.3. Exploring and Substituting Sub-Block Choices        | 149         |

| 4.5.4. Problem/Algorithm Interface                           | 151         |

| 4.5.4.1. The solve Command                                   | 151         |

| 4.5.4.2. Problem Interface: Normalizations and Stored Values |             |

|                                                              | 155         |

| 4.5.4.3. Problem Interface for Surrogate Cost                | 161         |

| 4.5.5. Running an Optimization                               | 164         |

| 4.6. Graphics                                                | 165         |

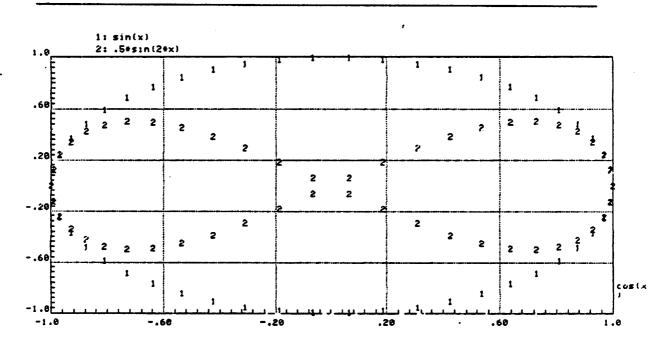

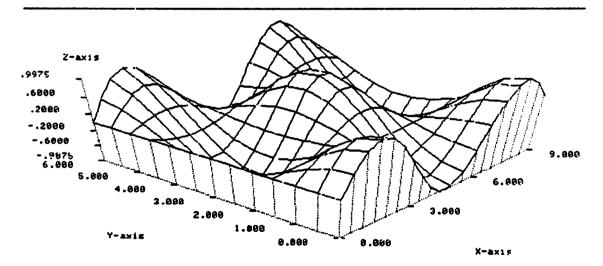

| 4.6.1. General Graphics Features                             | <b>16</b> 6 |

| 4.6.2. Graphics for Observing Problem Performance            | 183         |

| 4.6.3. Graphics for Observing Algorithm Performance          | 189         |

| 4.7. Simulation Interface                                    | 194         |

| 4.7.1. Functions and Goals                                   | 195         |

| 4.7.2. Simulation-Dependent Part                             | 199         |

| 4.7.3. Simulation-Independent Part                           | 205         |

| 4.8. Miscellaneous DELIGHT Features                          | 209         |

| CHAPTER 5: DELIGHT Applications                              | 215         |

| 5.1. Electronic Circuit Applications Featuring DELIGHT.SPICE | 216         |

| 5.1.1. Nature of Electronic Circuit Design                   | 218         |

| 5.1.2. Circuit Design Problem Formulations                   | 223         |

.

iii

| 5.1.3. Additional DELIGHT.SPICE-Specific Features                     |             |  |  |  |  |

|-----------------------------------------------------------------------|-------------|--|--|--|--|

| 5.1.4. Circuit Design Examples                                        |             |  |  |  |  |

| 5.2. Other Engineering Applications                                   |             |  |  |  |  |

| 5.2.1. Digital Filter Design                                          | 284         |  |  |  |  |

| 5.2.2. SISO and MIMO Control Systems                                  |             |  |  |  |  |

| 5.2.3. Earthquake-Resistant Structures                                |             |  |  |  |  |

| CHAPTER 6: Conclusions and Future Research                            | 294         |  |  |  |  |

| REFERENCES                                                            | 299         |  |  |  |  |

| APPENDIX A: DELIGHT Implementation                                    | 309         |  |  |  |  |

| A.1. RATTLE Language                                                  | 309         |  |  |  |  |

| A.1.1. RACC Compiler-Compiler                                         |             |  |  |  |  |

| A.1.2. Dynamic Arrays                                                 |             |  |  |  |  |

| A.2. Parser and Parse/Execute Loop                                    |             |  |  |  |  |

| A.3. Device-Independent Graphics                                      |             |  |  |  |  |

| APPENDIX B: DELIGHT Application Package Development Features          | 335         |  |  |  |  |

| B.1. Adding Built-in Routines                                         | 335         |  |  |  |  |

| B.2. Accessing Fortran Variables                                      | <b>34</b> 0 |  |  |  |  |

| APPENDIX C: DELIGHT Machine-Dependent Primitives                      | 343         |  |  |  |  |

| APPENDIX D: DELIGHT: An Optimization-Based Computer-Aided Design      |             |  |  |  |  |

| System                                                                | 351         |  |  |  |  |

| APPENDIX E: The Design of Digital Filters Using Interactive Optimiza- |             |  |  |  |  |

| tion                                                                  | 857         |  |  |  |  |

| APPENDIX F: An Enhanced Methodology for Interactive Optimal           |             |  |  |  |  |

| Design                                                                | 360         |  |  |  |  |

| APPENDIX G: DELIGHT.SPICE: An Optimization-Based System for the       |             |  |  |  |  |

iv

| • .           |             |                            |            |

|---------------|-------------|----------------------------|------------|

|               |             |                            | <b>v</b> . |

|               | 363         |                            |            |

| - <del></del> | APPENDIX H: | DELIGHT for Beginners      | 370        |

|               | APPENDIX I: | DELIGHT.SPICE User's Guide | 429        |

• • • •

**~**

---

•

.

ja,

.-

## CHAPTER 1

## Introduction

#### 1.1. The Nature of Engineering Design

For our purposes, engineering design can be considered as a three-phase iterative process. The designer must:

- derive objectives and specifications from the requirements of the system being designed,

- select a structure or configuration which has the best chance of meeting the specifications, and

- 3. determine values of system parameters that optimize the possibly competing design objectives while satisfying the constraint specifications.

For a particular design problem, the designer may go back and forth between the three phases many times until a satisfactory design has been achieved.

It is natural to try to use the computer to aid designers in performing the steps above. While there exist design procedures for limited classes of problems in which system structure and parameter values are synthesized simultaneously [149, 153], generally the selection of system configuration is a very creative and experience-based part of the design process and may not be very amenable to computer assistance. Similarly the derivation and evaluation of objectives and

specifications, in quantifying such questions as:

- 1. What quantities must be "specified"?

- 2. What criteria are used to define a "good design"?

- 3. What defines "acceptable performance"?

is also a very creative and subjective aspect of design which certainly requires the experience and intuition of the designer. For large complex systems, however, the selection of the values of a large number of system parameters is often time-consuming and is usually stopped short of the design's best performance. This is usually due to the difficulty of designers in predicting the effect of parameter changes on system performance without simplifying engineering approximations or numerous computer simulations.

That this parameter value determination phase can greatly benefit from computer assistance is the result of a declining cost of computing power and of significant advances, in the past 15 years, in two relatively separate research areas. The first of these advances is in the area of optimization algorithms for nonlinear programming. Algorithms have emerged which have many desirable properties that are particularly suited to engineering design. Many have guaranteed convergence properties which depend on rather mild conditions which are satisfied by many engineering design problems. There are several algorithms which optimize an objective subject to constraints and even some which solve problems involving *functional* constraints which must be satisfied over an interval of an independent parameter such as time, temperature, or frequency. Recently algorithms have been developed which allow multiple objectives to be optimized while simultaneously satisfying constraints.

The second area of advance is in system simulation or analysis programs.

Advances in accuracy, efficiency, and reliability of these programs lead, on the one hand, to the ability of engineers to simulate larger systems (or portions thereof). On the other hand, these advances also make it economically feasible to repeatedly simulate smaller portions of a system for the purpose of varying parameters to improve its performance. Computer simulation has become a popular and in many instances indispensable tool in engineering design.

This simulation power has lead many designers to believe that general analysis programs are all that is required, for with them designers may continue to use the popular cut-and-try methods as in the precomputer era—only faster, cheaper, and with greater accuracy. In the design of electronic circuits, the simulation program replaces the breadboard and the cut-and-try method is similar to "pot-tweaking". While such design methods have worked in the past, they are less likely to succeed in the future as system complexity and the number of parameters increases or as more performance is expected.

In this dissertation, the DELIGHT system, designed and implemented to combine the two areas of optimization and simulation, is presented to provide engineering designers with a powerful new computer-aided design (CAD) tool in which engineer and computer are complementary as they work together to optimize the performance of designs. In particular, DELIGHT uses *parametric optimization* in the numeric parameter determination phase of design in which the system configuration remains fixed. Used in this way, optimization algorithms may be viewed as a way of effectively managing the cut-and-try process by taking advantage of the computer's ability to assimilate much information about the current design from automatically performed simulations in order to determine the best set of parameter modifications. Optimization thus frees the designer from the difficult and tedious task of making these modifications and

§1.1

allows him to concentrate on the more creative aspects of the design process.

There are several additional benefits of applying parametric optimization to engineering design. By freeing the designer from the highly repetitive aspects of the parameter selection process, he may apply his creativity, intuition, and experience in other ways:

- He may devote more time to the derivation of objectives and constraint specifications and the definition of acceptable performance measures. This enhances the first phase of design by allowing a more rapid determination of whether they are suitable for meeting the requirements of the design.

- 2. He may concentrate on the structural aspects of the design by considering several alternate configurations without being bound by the usually prohibitive time required to compare the best performance of each.

- 3. He may provide a good initial guess for the design parameters. This may be obtained by other computer techniques as well as by manual design procedures.

- 4. Decisions about which constraints are most important to satisfy must be made. An indication of the admissible severity in violating each constraint must be given.

- 5. The designer may devote his time to evaluating and comparing the results of trading off competing objectives in a particular configuration. This exploration of tradeoffs is usually essential to any modern design methodology.

- 8. By monitoring the optimization process, the engineer can go through a learning experience about his system's performance that otherwise might be missing if manual design techniques were stopped short of the system's

best capabilities.

Another benefit is that in formulating the objectives and specifications of his design, the designer may address design problems more closely to their origin: the limitations of classical design approximation techniques may be avoided. Many design "tricks" which prior to the existence of an optimization-based approach were necessary in order to perform the mathematical manipulations of the design process, may no longer be considered a necessary part of the designer's repertoire. Instead, the designer's grab-bag contains, for example, his experience with the optimization process in knowing what type of problem formulations lead to rapid convergence of the optimization algorithms used.

#### 1.2. Examples of Design Problems Addressed

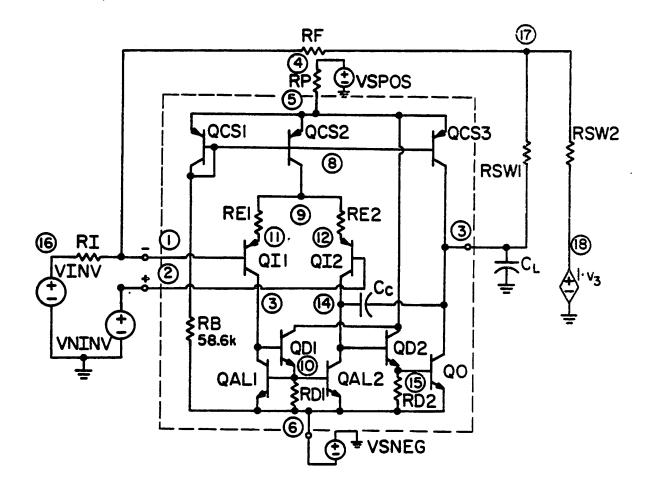

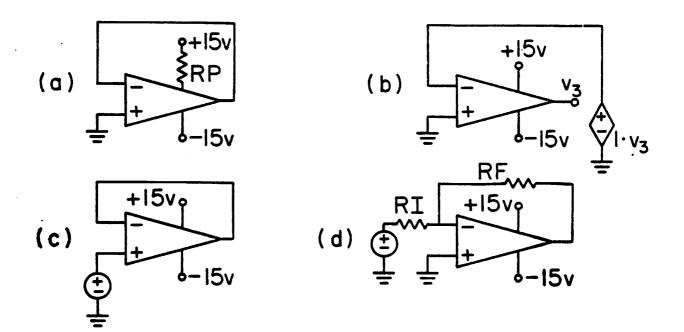

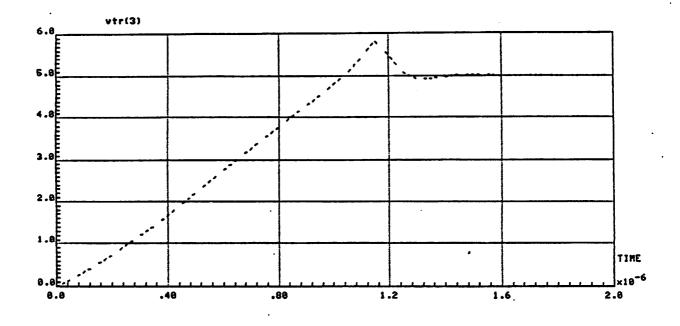

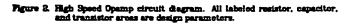

Examples of design problems which fall into the class of problems handled by the DELIGHT system can be found in many areas of engineering. In the area of analog electronic integrated circuit design, a common problem in amplifier design is to maximize bandwidth subject to constraints on stability or on total power consumption. The design parameters whose values must be determined might be resistors, capacitors, or transistor device geometries. The structure of the network would be determined a priori by the designer and would remain fixed throughout the optimization process.

Another electronic circuit design problem involves digital cells of VLSI (very large scale integration) systems. One common scenario is to minimize circuit switching times subject to fan-in/fan-out requirements and again to constraints on power consumption. For these types of problems, the design parameters are usually device geometries only.

In the area of single input/single output (SISO) and multiple input/multiple

output (MIMO) control systems there are many different types of design problems which can benefit from optimization techniques. For example, one may wish to minimize the energy fed into the plant of a feedback system, subject to constraints. These constraints might be bounds on compensator parameters, overshoot and settling time constraints on the time-domain step response of the closed loop system, stability requirements that the poles of the closed loop system lie in certain regions in the complex plane, and requirements that the system be insensitive to output disturbances. Some of these requirements result in constraints which require very special optimization algorithms.

A final design problem example is found in the area of structural design in which braced frame buildings must withstand small earthquakes with no damage and large ones without collapse [18]. A common objective is to reduce construction cost by reducing the weight of the structure. This is done by minimizing the cross sectional area of the frame members subject to several groups of constraints. The designer may formulate one group of constraints corresponding to a static model subjected to gravity loads and another group corresponding to a dynamic model whose goal is to limit the relative floor displacements over the entire duration of a whole family of moderate and severe earthquake ground motions. The system structure remains fixed throughout the optimization process in that the permissible design variables may only affect element properties; thus, for example, the position of the frames and the distance between nodes must remain constant with changes in the design parameters. An example of element properties which may be design parameters are section area, strain hardening ratio, or section moment of inertia, for the beam-column element.

§1.2

#### 1.3. Dissertation Outline

§1.2

The plan of this dissertation is as follows. We begin with an overview of optimization-based computer-aided-design in chapter 2. This leads from early efforts to recent design systems and ends with the limitations of both early and recent efforts. By examining the needs of various classes of users to be supported by the DELIGHT system; chapter 3 results in a set of design criteria for the system. Chapter 4 then surveys DELIGHT features which meet these design oriteria. This includes DELIGHT's RATTLE programming language, the way design problems are specified to DELIGHT, a discussion of optimization algorithms and libraries, and other features which enhance the design process while using DELIGHT. In chapter 5 we present several applications of DELIGHT to engineering design. The foremost of these is DELIGHT.SPICE for electronic circuit design. We conclude in chapter 6 with a summary of the main contributions of this work followed by directions for future research. Appendices are included which explain several DELIGHT implementation issues and show the details of several DELIGHT features for developing application packages.

#### CHAPTER 2

#### Overview of Optimization-Based Computer-Aided-Design

#### 2.1. Early Efforts

Since it is difficult to survey the early use of optimization in all areas of engineering design, we restrict ourselves for the most part to a few representative areas. One of the earliest uses of optimization in engineering design was to solve problems that had been formulated as matching or curve fitting problems [11, 26] in which the goal was to match a calculated and a desired system response. This was probably due to the fact that, by following Aaron [11] and defining "best" as the minimum of the sum of the squares of the errors between desired and calculated responses, matching problems could easily be formulated as linear or nonlinear least squares problems. These could then be solved using either specialized techniques or available general purpose algorithms and routines for simple unconstrained optimization, that were developed much earlier than ones for constrained or multiple objective optimization. Another error criterion was "equal ripple" approximation in which the absolute magnitude of the error was minimized.

The least squares matching problem was usually considered as follows. Defining  $\mathbf{x}$  as the vector of design parameters,  $f(\mathbf{x}, \mathbf{z}_i)$  as the calculated response at the i'th value of an independent parameter  $\mathbf{z}$  as i ranges from 1 to n (where  $\mathbf{z}$  may be i itself), and  $F(\mathbf{z}_i)$  as the desired response (or measured in the case of model parameter determination), then the goal of having  $f(\mathbf{x}, \mathbf{z}_i)$  equal  $F(z_i)$  for every i was formulated as the following least squares problem:

minimize

$$\sum_{i=1}^{n} (f(\mathbf{x}, z_i) - F(z_i))^2$$

In the special case that the number of parameters in  $\mathbf{x}$  exactly equaled n, the number of  $z_i$  data points, ordinary Newton iteration was sometimes used [26]. Otherwise, either generalized Gauss-Newton methods (previously called Taylor Series Methods) [11], Marquardt enhancements to these methods [96], or other general unconstrained minimization techniques such as steepest descent [35] were used.

Early use of the above solution techniques is now illustrated. A typical computer program which combined the techniques above was SUPROX [48], an acronym for SUccessive apPROXimation program, developed at Bell Laboratories in the middle sixties. As explained by Golembeski [53], the program determined the unknown parameters via two "slope-following" techniques, the method of steepest descent and a generalized Newton-Raphson technique, which were used consecutively, although either technique could be used alone. The steepest descent method was used initially since it converged rapidly when the parameters were far from optimum. When the overall minimum was neared, i.e., there was less than 5 percent reduction in the error function per iteration, the generalized Newton-Raphson method was substituted because it had quadratic convergence when started with good initial parameter values. This program was used in a number of different applications of interest to designers.

Examples of engineering problems which were formulated as matching problems include model parameter determination for modeling system performance for computer simulation, black box techniques [102], and the design of electronic filters and microwave integrated circuits. The goal of the first of these, modeling, is to represent physical structures or phenomena by idealized, but mathematically tractable models. Modeling becomes a matching problem once a fixed structure model is chosen and it is desired to minimize the error difference between responses calculated by the model and measured responses. The independent parameter in the least squares formulation ( $\mathbf{x}$  above) are various external stimuli which bring into play the ways in which the model will be

Black box techniques, which have now evolved into present-day macro modeling, were methods which were required to cope with the system size limitations of early simulation programs [102]. In this approach, calculated or measured discrete data from a complex part of a system were replaced by standard functions whose parameters were determined by a curve fitting process. The data hopefully captured how external stimulus at input "ports" produced responses at output ports. The particular functions used were either determined by the application, for example hyperbolic functions for uniform transmission lines or orthogonal polynomials for certain mechanical systems, or chosen by the designer from several standard functions supplied by the curve fitting program. For the latter, the choice was a compromise between availability of function subroutines to do the fitting, system size, and efficiency and accuracy of the resulting black box.

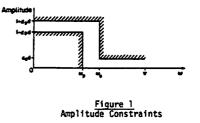

For the design of electronic filters, the filter response functions to be matched against desired curves were usually the magnitude and phase of transfer functions (including input and output impedances) discretized over the independent parameter frequency. One interactive optimization program for designing electrical filters was TRANSFIT [103]. It was written in Fortran for the GE-605 time-shared computer system and was an adaptation of a program given

used.

by Calahan [27] for fitting ratios of polynomials to frequency-domain characteristics. The fit was accomplished through the use of a Fletcher-Powell optimization method [49] with Fibonacci Search. The user could interact in the optimization process by changing the initial guess for the polynomial coefficients and the weights at different frequencies.

A more recent filter (and microwave) design system is COMPACT [6], a question/answer style interactive optimization program. It allows designers to minimize a weighted scalar error function consisting of the sum of the squared deviations between several frequency-domain properties of circuits. These properties include two-port scattering parameters, noise figure, and input port phase shift. Control of this fixed problem formulation is accomplished by adjusting the weights or simply setting them to zero to remove their respective terms from the error function. If the designer cannot provide an initial guess, COM-PACT does a coarse search to find an approximate global minimum followed by the steepest descent method to find the actual minimum. This could be very time-consuming for a large number of design parameters. However, typically the circuits optimized are relatively small. Since COMPACT contains no DC or time-domain analysis and handles only bipolar transistors, its use in general circuit optimization is limited.

Another design program which emphasizes frequency-domain matching for electronic filters is OPNODE [3]. It uses the following adaptive search technique. The search begins in a purely random manner. Each error function evaluation updates stored probabilities for that direction. Thus, the search algorithm "learns" by trial and error how to vary parameters to minimize the error function. An interesting feature of OPNODE is how a designer interacts with the program. OPNODE runs on an HP minicomputer and allows a user to flip panel switches to turn on or off performance plotting, parameter value display, and other algorithm controls during each trial error function evaluation. Also, since the program is written in Basic, it enjoys the interactive benefits of any interpreted language. One of these is that execution may be interrupted at any time, any program statements changed, and execution resumed from the same point.

The sheer number of references on the subject of computer-aided filter design suggests that in the electrical engineering area, it was the heaviest user of early optimization techniques.

An extension of the use of optimization in electronic circuit design to consider both DC biasing effects as well as frequency-domain matching was first accomplished by Dowell [44] at Berkeley. Shortly thereafter, his colleague McCalla [99] combined the automated DC biasing techniques of Dowell with the previous work of Walsh [151] and Wooley [161] in optimizing small-signal frequency responses without bias point variation. Thus, McCalla's optimization considered the direct AC dependence of design parameters as well as the indirect DC dependence through transistor biasing. The optimization performance function was again the sum of the squared errors between actual and desired responses summed over frequency. The Fletcher-Powell method [49] with cubic interpolation line search was added to the circuit simulator SLIC [68] and passive element values only were allowed as design parameters. An experiment tried by McCalla was to minimize the temperature sensitivity of his circuits by summing deviations at two different temperatures. After poor results, he concluded that optimization could not be effectively extended to optimizing temperature sensitivity due to the expense of computing the necessary second order derivatives. Another startling conclusion he made was that all of his optimization results could have been reached without the aid of the automated approach, just more slowly.

The next step in the evolution of optimization in engineering design was the formulation of certain design problems as general nonlinear programming problems. This approach required the formulation of a single performance function (cost) to minimize subject to a set of inequality constraints, as in the following standard form:

minimize

$$\{f(\mathbf{x}) \mid g(\mathbf{x}) \leq 0\}$$

There was little use, however, of what few constrained optimization algorithms existed; in many cases [136, 86] the constrained problem was transformed into an unconstrained minimization problem using, for example, the penalty function approach of Fiacco and McCormick [47]. Indeed, many researchers who described algorithmic procedures did not even mention how this important transformation might be carried out. An early review paper by Director [41] simply states that the first step of an automated network design procedure requires "a [scalar] performance function which embodies the design criterion." For the time-domain design problem, the integral performance function

$$\varepsilon = \int_{0}^{T} e(\mathbf{w}, \mathbf{q}, \mathbf{p}, t) dt$$

and the Fletcher-Powell [49] or Fletcher-Reeves [50] optimization methods were suggested.

In parallel with the increased use of nonlinear programming in design came great improvements in the efficiency of calculating the gradients necessary for the most useful optimization algorithms. For electronic circuits, Rohrer and Hachtel [132, 57] first showed how the computation of the gradient of a performance function at a single frequence point with respect to every design parameter could be accomplished in just two network analyses; previously it had been thought that this computation required an additional analysis for each design parameter. Shortly thereafter, Director and Rohrer showed a similar result by introducing the *adjoint network approach* [39, 40]. It used a derivation that, although somewhat more general by not requiring a state variable formulation, was easily understood and the adjoint approach was used by many others as a means of calculating gradients for a wide variety of applications as well as for optimization.

These highly efficient methods for gradient computation have not been used as much as might be expected in other areas of engineering. Recently, however, there has been an interest in adding these methods to the ANSR [101] general purpose structural simulator [38].

#### 2.2. Recent Design Systems

The maturation of simulation and optimization techniques have caused several computer-aided design systems to appear over the past few years. The first one to be discussed, ISPICE, provides only analysis functions whereas the remainder, A2OPT, INTEROPTDYN, and APLSTAP, are explicitly designed for engineering optimization applications.

ISPICE (for Interactive SPICE [5,7]) is mentioned here because it was the first interactive design system used extensively by this author and its elegant interactive man-machine interface has had a significant influence on the design of DELIGHT. ISPICE is a user-friendly design tool which was created by combining the SPICE circuit analysis program [105] with the interactive and laborsaving aspects of AEDCAP [1]. One particularly interesting feature of ISPICE relevant to the design of DELIGHT is that it has no internal size limits. Rather than allocating fixed size arrays or storage regions, ISPICE adapts to the circuit being simulated and obtains from the operating system whatever resources are required; simulations have been performed on circuits containing thousands of elements. An important novelty of ISPICE is the way circuit elements are assigned values in the circuit description file. A general expression capability allows almost any *VALUE* in the circuit file to be a constant, an arithmetic expression, a function reference, a variable parameter, or any combination of these. Another feature is the truly interactive way ISPICE communicates its results to the designer. Instead of following batch SPICE and dumping out reams of data on *all* the circuit elements, the program responds to user queries for various subsets of the available output data. The human-engineering of ISPICE interactive commands is seen in the following samples:

SWEEP VIN FROM -10V TO 10V BY 1V AT 10MEGHZ PLOT VM(1) VS FREQ FROM 1MEGHZ to 100MEGHZ DEC 15 DISPLAY ELEMENTS R\* Q101 QPAIR1 QPAIR2

The SLICE interactive program [9] in use at Harris Semiconductor was originally conceived by this author and was initially patterned after ISPICE. The capabilities have since then been considerably expanded and SLICE is currently used at Harris by many designers.

A20PT [58] was an optimization-based CAD system for electronic circuits which added constrained optimization features to the ASTAP [2] network analysis program. It was probably the first system to allow designers to specify easily a wide range of objectives and constraints as arbitrary expressions of circuit outputs. While A20PT was for the most part a batch program (ASTAP was strictly batch), an important feature was the limited interactive capability in which the designer could interrupt and influence the course of the optimization. He could alter either (1) the optimization weights, (2) ASTAP run controls, or (3) parameters which control the optimization routine itself. The program combined the weighted sum of several objective or constraint functions, the latter using penalty functions, into a single scalar function which was minimized using the variable metric rank-one update method due to Cullum [32]. The program also included box constraints, i.e., upper and lower bounds, on the design parameters. The choice of weights was somewhat haphazardous, being adjusted experimentally by the designer after observing initial optimization performance. Because A2OPT constraints were actually the integral of the designer-specified expression, instantaneous violations might occur but be averaged out so that the constraint was actually satisfied; ways of circumventing this problem were suggested in [58].

In the digital circuit design experiments performed by the authors of [58] several points were made. One was the difficulty in initially adjusting the weights; often several optimization reruns were required. This could be very costly if the circuit size was large. Another point was their discovery that the design parameters and the objective functions were somewhat decoupled. This, they said, is inherent in the design of a mixed nonsaturating and saturating digital circuit in which the design specifications are a function of a single node. This point shows that designers must pay close attention to the specifications they formulate. Although A2OPT initially showed great promise, the lack of truly interactive features as well as the authors' limited drive to recruit users caused it to never be used extensively by practicing circuit designers.

Recently a research team at Berkeley put together the INTEROPTDYN design package [21] to enhance the use of optimization algorithms for engineering design and to study the methodology needed for man-machine interaction and graphical display. It combined a particularly powerful optimization code OPTDYN [20], INTRAC-C, an extension of the INTRAC [155] language-interpreter construction module developed at the Lund Institute of Technology, and various application-dependent codes such as the CDP classical design package [33] from Imperial College in London. The INTEROPTDYN package allowed the user to write his own color or black-and-white graphical display programs as macro files. By inserting certain "call for interaction" INTRAC calls into the existing OPTDYN subroutine, the creators of INTEROPTDYN allowed the user to control the flow of computation by executing the optimization algorithm one step or one cycle of steps at a time. Computation could be interrupted and a matrix "scratch pad" used for diagnostic calculations in the middle of a run.

In the INTEROPTDYN-SISO version [124] for the design of single-input singleoutput linear feedback systems, the objective and constraints of the design problem formulation were fixed, with the designer only providing numeric parameter values for his performance goals. These parameters controlled: (1) an envelope on the closed loop step response, (2) frequency-domain criteria, (3) upper and lower bounds on the plant input and its derivative from a step input, and (4) design parameter box constraints. The built-in objective function to minimize was the integral squared error of the closed loop step response. The design parameters were limited to coefficients of the numerator and denominator polynomials of the compensator transfer function. INTEROPTDYN-SISO and other versions of INTEROPTDYN were used successfully for several different design applications but the difficulty in coding arbitrary objectives or constraints limited their use to academic circles at Berkeley. Of importance, however, is the fact that INTEROPTDYN helped to clarify ideas about what type of interactive language and man/machine communication through graphics is necessary in such a design system.

The APLSTAP system [60] developed at IBM is an interactive design system which can operate in conjunction with an arbitrary existing simulation package. Presently APLSTAP algorithms written in APL exercise control over the ASTAP [2] circuit analysis program. They attempt to mathematically mimic the common practice by designers of trading off several performance objectives by linear extrapolation of their expected performance. Through interactive iterations with a novel computationally inexpensive linear programming (LP) step, key tradeoffs between multiple objective and constraint functions are revealed to the user. He uses this assistance and his knowledge and experience about the various functions to select a maximally effective LP step. Thus, the designer is constantly making tradeoff decisions in a design process in which emphasis is placed on getting the most from the first few optimization steps rather than on a completely convergent sequence of steps; in many design situations particularly involving large problems, convergence is computationally too expensive or not justified on the basis of model accuracy.

The APLSTAP system may be used for both optimizing multiple objectives and for improving the worst case performance of multiple objectives over the variations of a specified set of *worst case* statistically uncertain parameters. In each of these design problems the LP step may be used in either of two modes. *MIN-MAX mode* attempts to find the smallest values of all the objective functions over a user specified set of box constraints on the design parameters. These box constraints are an estimate by the designer of the range of linearity of the objective functions over each parameter. *MINBOX mode* attempts to find the smallest change in the design parameters which will achieve a user specified desired improvement in each of the objective functions. The MINBOX LP step either produces the smallest change which achieves those improvements or states that they are not possible.

Since APLSTAP is a relatively recent system that has not yet been extensively used by practicing designers, the success of its approach is not yet known.

#### 2.3. Limitations of These Systems

In some cases such as electronic filter design, early efforts were successful. But for more complex present-day design situations, both early as well as recent optimization-based design systems have many weaknesses which limit their use by practicing engineers. This section categorizes these weaknesses as those stemming from:

- 1. difficulties encountered by designers,

- 2. shortcomings of existing algorithms,

- 3. shortcomings of programs implementing algorithms,

- 4. difficulties encountered by optimization experts, and

- 5. shortcomings of simulation programs.

Recognition of these weaknesses leads to a set of goals and design criteria for DELIGHT in chapter 3.

**Designers.** The simplest reason why optimization was not used much for design is that many designers were (and still are) reluctant to use even CAD *analysis* tools. Those designers who did recognize the benefits a computer could provide were usually not trained in the areas of optimization or computer programming and thus had to use others' computer programs. Many times it just wasn't possible to access such programs, especially ones which contained the algorithms they needed. When access was possible, it was often difficult for designers to formulate their design problems as well-posed optimization problems and to understand how to successfully use the algorithms which had been implemented. Brayton and Spence [23] emphasize these difficulties in listing the following objections design engineers might have to viewing their design problems as nonlinear programming problems:

1. "Design problems are not this simple."

- 2. "There is more than one design objective to be [improved]."

- "It is not possible to state the design objectives in terms of mathematical functions."

Another point worth mentioning is that very often a "guru" of an institution would be the first to try to use a particular optimization program and if it did rot quickly and easily yield success, he might make an initial conclusion which other engineers would accept as doctrine. This point is brought out by Paul Weil [152] about computer-aided design in general in an amusing article about his laments as a computer-aided design researcher.

**Existing Algorithms.** During the time period of most of the efforts described in sections 2.1 and 2.2, the best known optimization algorithms were usually inadequate to solve the complex design problems which faced many designers. Often multiple performance objective functions were combined into a scalar objective function to minimize using the *weighted sum* method. This was precisely the approach used by COMPACT and many other programs [6]. As pointed out by Lightner and Director [94], this may yield a poor design no matter what weights are chosen or what optimization technique is used for the minimization. As mentioned in sections 2.1 and 2.2, inequality constraints were often handled by penalty functions, an approach prone to have all kinds of problems. Penalty functions are also far too primitive to solve design problems involving functional constraint specifications which must be satisfied for all values of an independent parameter over an interval.

Other difficulties with existing algorithms were that they often converged very slowly and sometimes not at all. It was not rare to find popular algorithms without any *guaranteed* convergence behavior whatsoever. Also, in cases of slow convergence, few algorithms were originally designed so that they had parameters which could be used to tune their performance to the particular class of problems being solved. In A20PT [58] and others that did have such parameters, it was probably next to impossible for practicing engineers to understand how to adjust them.

**Programs Implementing Algorithms.** The main shortcoming of many early optimization programs was that they offered a fixed problem formulation which was inadequate to handle widely varying design requirements. Examples are the TRANSFIT [103] and COMPACT programs [6] mentioned in section 2.1. Designers could only supply desired curves to be matched by their filter or circuit transfer functions; they could not introduce additional constraints on, say, the pole locations of their desired filters. Another example is the fixed problem formulation of the INTEROPTDYN-SISO package [124] discussed in section 2.2. Although the formulation may have reflected the goals of many feedback system designs, the rigidity of the package not only made it difficult to add new constraints, but also, in early versions, forbid even a simple swap of a particular constraint and the cost. Thus, a designer could not minimize the rise time of his system subject to constraints on the integral square error of the closed loop step response.

Another deficiency of optimization programs was that they did not provide

any feedback to the user (especially powerful graphical feedback) on how well the algorithm was performing. Slow convergence can be caused by algorithm parameter values which cause sub-steps of the algorithm to run very poorly on a particular design problem. There are usually other values of these parameters which can greatly enhance algorithm efficiency. However, a designer usually had no way of knowing which ones to modify. Also, the algorithm might have contained adjustable parameters but the program implementation did not make them accessible to the user. Both of these shortcomings usually resulted in many optimization iterations or, in the case of batch programs, many reruns, costly both in computer resources and designer time.

**Optimization Experts.** Lack of emphasis by developers of optimization algorithms on certain aspects of real-world design problems may have caused their algorithms or programs implementing them to have less practical value to designers. For example, any program which did not put heavy emphasis on parameter and constraint scaling would probably perform poorly on real-world problems in which constraints or parameters sometimes take on values which may be orders of magnitude apart. The algorithms or programs reported in [21, 39, 136, 20, 58, 103] do not appear to have given this emphasis. Other things which algorithm developers may have lacked were (are) programming expertise and the time or interest to write a complete, user-oriented optimization package containing, for example, clear error messages and sufficient documentation. Even with programming expertise, the time required to code, debug, and test an algorithm was usually very long. Moreover, most optimization programs were usually written in Fortran, with its well-known deficiencies.

A review of the literature reveals the curious and popular notion by early optimization experts that optimization techniques were supposed to completely automate the design process. In other words, they did not perceive the needs or the advantages of interactive computing, in which user and computer are complementary as they work together to carry out an optimization. This notion can be seen in the following partial quotations:

(... will result in a) completely automated third (parameter adjustment) phase [28, page 242].

... methodology of "automated" or "hands-off" design, where "algorithm" replaces "insight" [27, page 139].

Work is now in progress with the hope of constructing a set of *optimize* functions and weights so that the program may optimize from 300ns to 107ns in a single optimization run without user intervention [58, page 503].

Is it any wonder that early programs did not provide user feedback or a means of tuning algorithm performance ... their developers did not even expect the designer to be part of the optimization process!

One reason regarding "optimization experts" of why optimization has not "caught on" sooner is that after a few of them tried it in the early seventies with primitive algorithms that did not perform well, they consequently reached unfavorable conclusions<sup>1</sup>.

Simulation Programs. The shortcomings of both past and present simulation programs are not a limitation of optimization-based design systems but are a reason why optimization has not been used more widely in design. The first shortcoming is that coupling to simulation programs is usually very difficult to achieve. Most simulators have not been designed to behave as function evaluation routines for an optimization process. Even when they have rerun capabilities for modified input parameter values, it is either through interaction as in

<sup>&</sup>lt;sup>1</sup> See, for example, the conclusions of McCalla's dissertation [99].

ISPICE [5, 7] or through additional input "cards" as in ASTAP [2] or a recent version of SPICE [105], and not from a capability of receiving new input parameter values from a subroutine call by an algorithm. The already encountered difficulties in coupling DELIGHT to the SPICE [105] and ANSR [101] simulators bear out this point. Recently, however, work has begun on SPICE3 [129] with precisely the goal of having all access to a central "kernel" of analysis routines via a well-defined set of subroutines, including ones for parameter value update.

A further deficiency of most simulators is that they do not compute gradients needed by widely used optimization algorithms. As a result, gradient calculations are performed using finite differences, leading to a large increase in the time needed to perform an optimization.

Finally, the large number of different design environments in engineering means that there is a correspondingly large number of different simulation programs. Since the coupling of a successful algorithm subroutine to any particular simulator is usually very complex and interwoven, it can be difficult to extract the successful algorithm code for the purpose of using it with another simulator. Thus the spread of optimization to different areas is very slow.

In the next chapter, we shall consider the limitations discussed in this section in formulating a set of goals and design criteria for the DELIGHT system.

# CHAPTER 3

# Goals and Design Criteria of DELIGHT

#### 3.1. Setting the Stage

In this chapter we discuss the goals of the DELIGHT system and the resulting set of design criteria intended to meet these goals. In creating these design criteria, we try to avoid the various limitations and pitfalls pointed out in the previous chapter.

The goals of DELIGHT fall generally into four broad categories. The first and foremost desire is that the system be easy to use. This goal is essential to the success of any large system intended to be used by many types of users. Computer operating systems such as UNX<sup>1</sup> [131] and Interlisp [147] have long recognized the importance of a friendly user interface. Recently, many researchers have also been stressing this importance [89]. Singer et al. [140], in describing the design of a recent interactive environment for PASCAL programming, emphasizes this point. They recognized that human engineering must have top priority in the design of a system from the outset; it cannot be grafted on later. Our second goal is that DELIGHT be *versatile*. It must be useful in many different areas of engineering design, particularly in industrial environments. Third, the DELIGHT system must be relatively *efficient*, that is, make good use of limited computer resources. Our last goal is that the entire system be *portable* from one computer environment to another. The importance of this goal is

25

<sup>&</sup>lt;sup>1</sup> UNIX is a Trademark of Bell Laboratories.

recognized more and more today and was one of the major underlying motivations for the design of the new programming language ADA [88,8] by the Department of Defense.

One of the original DELIGHT objectives was to create a system that would facilitate its use by several different types of users. It is convenient to discuss the goals of DELIGHT by considering the needs of three classes of users. Our plan is to first describe the three classes in section 3.2. In section 3.3 we particularize the needs of each of these classes while section 3.4 summarizes the chapter by listing the resulting set of design criteria.

#### 3.2. Classes of Users Supported

The DELIGHT system is intended to provide congenial support to the following three classes of users:

- 1. Optimization Experts

- 2. Engineering Designers

- 3. System Personnel and Application Program Developers

Optimization experts create or modify the optimization algorithms used by designers. They usually work with the actual algorithm implementations and peripheral user-interface routines which allow algorithm progress to be easily observed and controlled by designers. When a special problem arises that cannot be handled by an existing algorithm, they are usually the ones who are called upon to tailor it or create a new algorithm.

Engineering designers use the DELIGHT system to assist their day-to-day design efforts. The types of designers to be supported by DELIGHT include those who are not computer experts and want to use the system in the simplest manner, as well as advanced users. Advanced DELIGHT users, who usually have a much greater understanding of system features and operation, often seek new capabilities from the support personnel. During an optimization they also try to insure that they are using the system in the most efficient manner.

There are several subclasses of system personnel. One class contains those whose main task is to support the enhancement of non-algorithmic aspects of the system. This includes meeting the requests of users and porting the system to new computer environments. Another class includes those extending DELIGHT into new areas of engineering by developing the required applicationspecific versions of the system. The easier this development is to accomplish, the greater the possibility of spreading the use of optimization to many areas.

#### 3.3. Needs of the Various Users

In this section, we consider the needs of the three classes of DELIGHT users. Our purpose is to lead to the set of design criteria presented in section 3.5.

**Optimization Experts.** The needs of optimization experts and algorithm developers are many. The most important need is the ability to create new algorithms easily. This calls for an interactive high-level programming language that can execute user-written code *very soon* after it has been written. To be interactive, the language can either be interpreted or compiled into a machine-independent intermediate form. A programming language environment brings with it the need for test and debugging aids. There must be the ability to interrupt execution from the terminal, check the values of variables, etc., and resume execution from the point interrupted. Also, the system must be very forgiving to errors that will invariably occur during algorithm development. These include floating point overflows, out-of-bounds array subscripting, and

inversion of singular matrices. Many of these needs appear in general programming systems such as the Wilander [156] or the Carnegie Mellon GLIDE 2 [45] PASCAL systems.

Another wish of algorithm developers to ease the implementation of new algorithms is to have their program code be compact and resemble as much as possible the mathematical description of the algorithm being implemented. Consequently, most of the usual coding errors would be eliminated and the programming time shortened tremendously. This requires high-level *readable* access to an arsenal of common mathematical manipulation and numerical analysis software. Since the mathematics used in optimization algorithms is so diverse, however, a language that is *extensible* [141], i.e., can be extended to resemble new mathematical syntax, is needed.

A final desire is to have *practicing* engineering designers use their algorithms. This leads to the requirement that all DELIGHT application packages be able to use any general algorithms that may be developed.

**Engineering Designers.** The most pressing need of engineering designers is to gain access to optimization in the many different design environments in which they work. The resulting requirement that DELIGHT be able to interface easily to many different simulators is discussed below.

Other wishes of designers include the following. It must be easy to convey their design specifications to DELIGHT. There must be a way for them to categorize design goals as either objectives to improve or as constraints that must be satisfied. Also, it must be possible to indicate the relative importance of the various specifications. Lightner and Director [94] emphasize this requirement in one of their approaches to solving multiple criterion optimization problems. The system must allow *arbitrary* formulation of these specifications. This calls for a general expression capability similar to that discussed in ISPICE [5,7] and A2OPT [58] in section 2.2. Also, the problem formulation must be independent of any particular optimization algorithm selected. The need to be able to easily input their design problem to DELIGHT calls for a powerful *useroriented problem entry facility*.

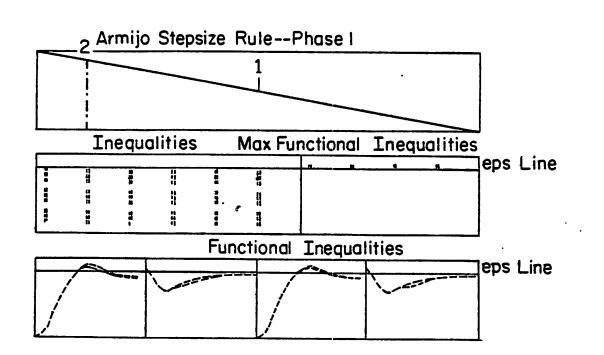

Engineering designers have several requirements that pertain to the optimization algorithms that they will use. The first is that there must be a way of selecting a "good" algorithm easily. This selection must be based on an interactive exploration of choices available in a library of algorithms. Moreover, these algorithms must be able to solve complex design problems, have guaranteed convergence behavior, and have parameters which can tune their performance to the particular problem. In order to carry out the tuning of the algorithm, designers must be given knowledge of how well the algorithm is performing. The performance can be very sensitive to the initial values of the design parameters and the conditioning of the problem formulation as well as to the values of the internal tuning parameters. Due to the complex information that must be conveyed, this necessitates graphical feedback on algorithm performance, most effective in color. Myers [104] discusses the perception of symbols, the avoidance of cluttering, character fonts, and other important considerations needed in such graphics design. After a designer detects that the algorithm is performing poorly he needs: (1) to be able to stop execution and adjust algorithm or design parameters, modify his problem formulation, or even select a different algorithm, (2) to know how to make these modifications, and (3) to be able to resume the optimization after any of these changes. These requirements call for graphical output to show why the algorithm is not performing well and, as for algorithm developers, an ability to interrupt execution from the computer terminal.

Another reason designers need interaction is that typically they cannot specify a priori the relative importance of each of several design objectives until the best capabilities of the design have been determined. This exploration of tradeoffs, essential to any modern design methodology, is much more efficient in an interactive environment.

System Personnel and Application Program Developers. The final class of DELIGHT users consists of system personnel and application program developers. Along with the extensibility needs of system personnel for molding such things as problem entry facilities or application-specific commands of DELIGHT into different design environments, are other needs which pertain to the portability of DELIGHT. A logical requirement for the design of DELIGHT to follow is to force all machine dependencies to occur either in a small set of primitive routines that can be easily implemented on many computers, or in preprocessor substitution macros. These techniques have become quite popular recently. For example, achieving portability through the use of macroprocessors is reported by Brown [25], Hall et al. [61] list the primitive subroutines they used for implementing their portable UNIX-like shell in Ratfor<sup>2</sup>, while Stewart [143] discusses both preprocessors and primitives. To be able to easily develop DELIGHT applications packages, it must be easy to interface DELIGHT to any existing simulation program. This requires a well-defined simulation interface methodology which at the least consists of two features. One is the ability to easily add existing routines to a set of DELIGHT built-in routines which are callable from the interactive programming language. The second is the ability to

<sup>&</sup>lt;sup>2</sup> See appendix C for a list of DELIGHT primitives.

access variables from the built-in routines so that they can be manipulated in the same manner as ordinary variables of the interactive programming language.

### 3.4. Resulting Design Criteria

In this section we summarize the previous sections of this chapter by listing the set of design criteria for the DELIGHT system. These criteria are that an optimization-based computer-aided design system must contain:

- an interactive high-level programming language and associated test and debug aids,

- for easy extension, a language parser which is generated by an automated parser generator (or compiler-compiler),

- language extensibility which allows algorithms to resemble mathematical descriptions and eases the entry of the system into new areas,

- a built-in library of common mathematical software such as from LIN-PACK [43] or the Harwell Subroutine Library [10].

- a user-oriented problem entry facility allowing: (1) arbitrary problem formulation through a general expression capability, and (2) a means of conveying the relative importance of design specifications,

- a methodology for performing tradeoff of problem specifications,

- a library of optimization algorithms,

- the ability to tune or substitute algorithms in the middle of an optimization run,

- color graphics features for displaying algorithm and problem performance that are independent of the particular graphical display device used,

- a simulation interface methodology that allows easy interfacing to existing simulation programs, and

- machine dependencies which have been grouped to allow easily porting to other computer systems.

In the next chapter we survey various DELIGHT features which help it meet the above criteria.

## CHAPTER 4

# **DELIGHT System Features**

#### 4.1. Introduction and Overview

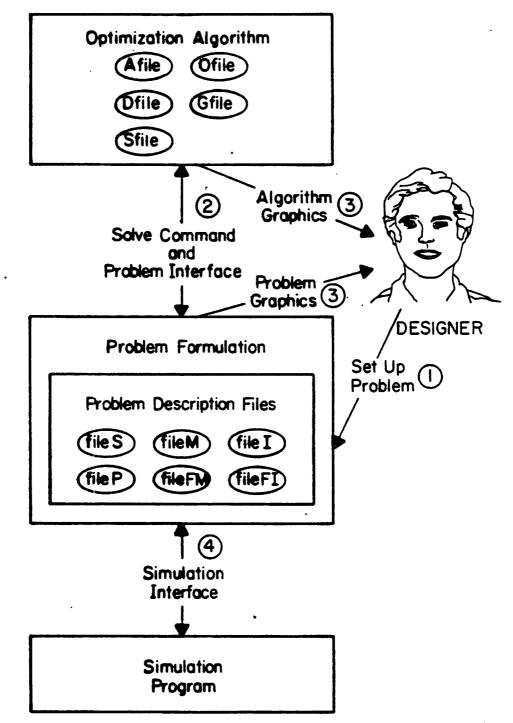

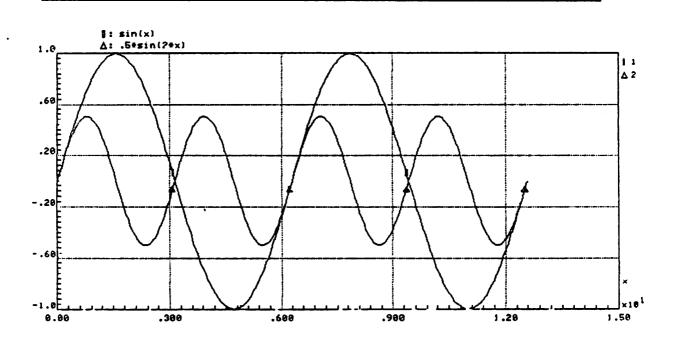

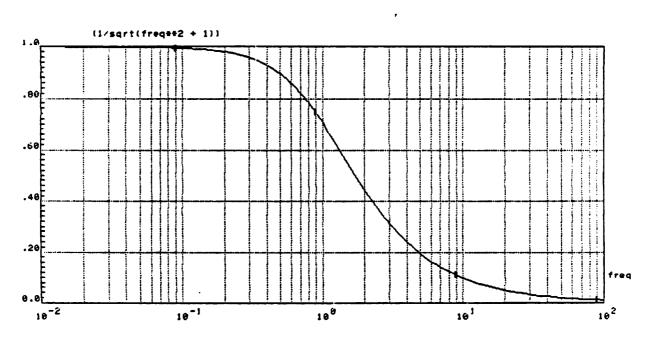

We have considered the benefits of applying optimization to engineering design and identified many shortcomings of previous attempts to achieve this goal. In this chapter we survey various DELIGHT features that help to meet the design criteria given in section 3.4. In order to explain more easily other features of the system, the chapter begins with a top-to-bottom description of RATTLE, the built-in programming language of DELIGHT. This description begins with such fundamental notions as what it is to be used for and why it was created, followed by a description of the syntax of several statements that will be used many times throughout this dissertation. Additions needed to make RATTLE an interactive language include the ability to interrupt execution and to catch certain run-time errors such as numeric overflows. The *define* and *macro* extensibility features of RATTLE are presented and used to create powerful matrix operation macros. Such macros help achieve the goal that algorithm RATTLE code resemble its mathematical description.

The primary purpose of the DELIGHT system—to apply optimization techniques to engineering design— is presented in two parts: the problem side in section 4.4 and the algorithms side in section 4.5. The problem side is considered first because the mathematical programming formulations and their corresponding problem description facilities presented influence the algorithms

32

and graphical displays needed to solve them. First, a single-cost problem formulation is presented, capable of handling a broad class of optimization problems. However, to serve better our purpose in a design environment, a new multiple objective formulation is proposed that attempts to capture the essence of how a designer would like his design objectives to tradeoff. The crucial interaction between a designer and the optimization process as well as humanengineered graphics to support this interaction are described later in the chapter.

Optimization algorithms capable of solving complex design problems and having guaranteed convergence properties form a cornerstone of the DELIGHT system. We first introduce a library of optimization algorithms. After giving the structure of a typical algorithm found in the library, we demonstrate this structure by presenting an important class of algorithms known as *methods of feasible directions*. These methods are particularly good for engineering design problems. In fact, the algorithm we describe in section 4.5.2.2 for solving problems posed using our multiple objective formulation consists of several enhancements to the basic method of feasible directions. We conclude this part with how the optimization problem set up and the optimization algorithm chosen are coupled. This involves user aspects as well as a special software interface that allows algorithms to be clearly written while maintaining efficiency.

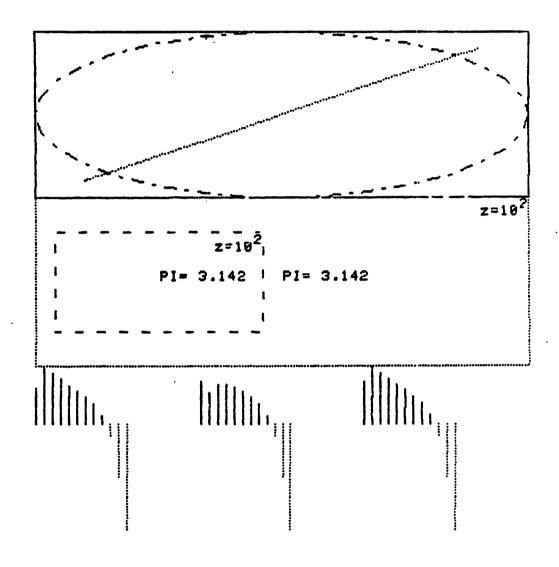

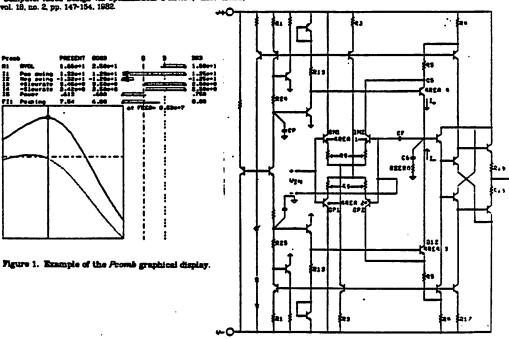

Due to the complex information that must be conveyed about both problem and algorithm performance during an optimization run, graphical displays are needed. General graphics features in DELIGHT are first presented in section 4.6.1. We then introduce several graphical displays, constructed from the basic graphics primitives, that are used to exhibit this performance. The performance comb display introduced is instrumental in allowing design problem tradeoffs to be made and their effects to be observed. Using this display, we emphasize a tradeoff methodology that has been applied successfully to significant practical problems such as those covered in chapter 5. Furthermore, in engineering design it is usually far too costly to obtain a truly optimum solution. Whereas in the past, most uses of optimization in engineering design stressed finding such a solution, we strive for *performance improvement* in the first few optimization iterations. The methodology we introduce insures that a designer's wishes are accurately reflected during each and every iteration of an optimization run.

Since the DELIGHT system is intended for many different areas of engineering design, we close the chapter by introducing a simulation interface methodology and other necessary features that facilitate the coupling of DELIGHT to existing simulation programs. Part of the simulation interface exploits the compile-time macro feature mentioned above to carry out certain table lookup operations just once thus ensuring greater efficiency during the actual optimization execution.

#### 4.2. RATTLE Language

In order to meet the various goals of DELIGHT, an interactive programming language is needed with very particular features. The subsections under section 4.2 give an overall description of the design and features of the *RATTLE* language. RATTLE is an acronym for "RATfor Terminal Language Environment". The functions of RATTLE in the DELIGHT design system are discussed in subsection 1. Subsection 2 explains why a new language is required by first considering the need for a non-standard language compiler and then discussing why existing languages are unsatisfactory. The question of execution efficiency is taken up at the end of the subsection. In subsection 3, we discuss why RATTLE was designed to be similar to the existing language Ratfor [78]. Several preliminary decisions in the design of RATTLE are discussed in subsection 4. In subsection 5 we illustrate basic RATTLE language statements and other necessary and helpful language features. Arrays whose sizes may vary at run-time is a feature that facilitates the implementation of optimization algorithms. Interactively generated interrupts for stopping RATTLE execution are presented in subsection 6. Subsection 7 discusses the nature of RATTLE interactive execution and its importance to *incremental program development*. Finally, subsection 8 delves into the various aspects of DELIGHT extensibility, including Ratfor-like *defines* with extensions and compile-time *macros*.

# 4.2.1. Functions of the Interactive Language in DELIGHT

The interactive programming language must serve several functions in the DELIGHT computer-aided design system. The first is for describing design problem objectives and constraints. Since in engineering design these will often depend upon outputs of a simulation program, we may view them as composite functions — in which the "outer functions" are coded in the DELIGHT language and the "inner functions" are provided by the simulator. Since the parts of a design problem formulation to be coded in the DELIGHT language must be coded by designers, the language must be fairly easy to learn. One way of accomplishing this is to make it similar to a popular existing language. Being easy to learn is also a requirement of designers for the second function of the language — the implementation of problem-dependent output procedures. These procedures display on the terminal screen problem performance in whatever form desired

by the particular designer. They are automatically invoked after each major step in DELIGHT optimization algorithms. Finally, throughout an optimization run, designers will use the language to perform scratch pad calculations. The purpose of these may be to verify further the performance of their design or to determine how well the optimization algorithm itself is performing.

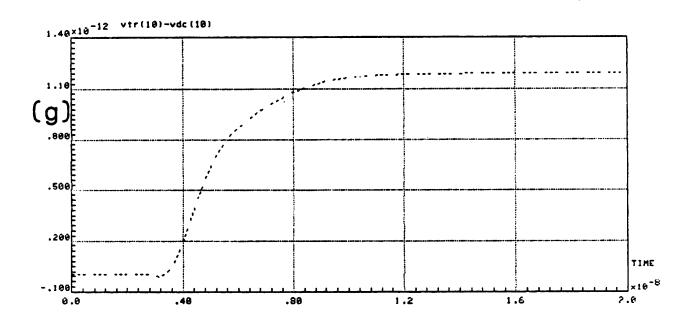

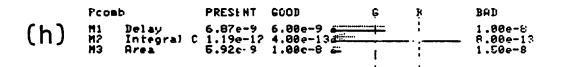

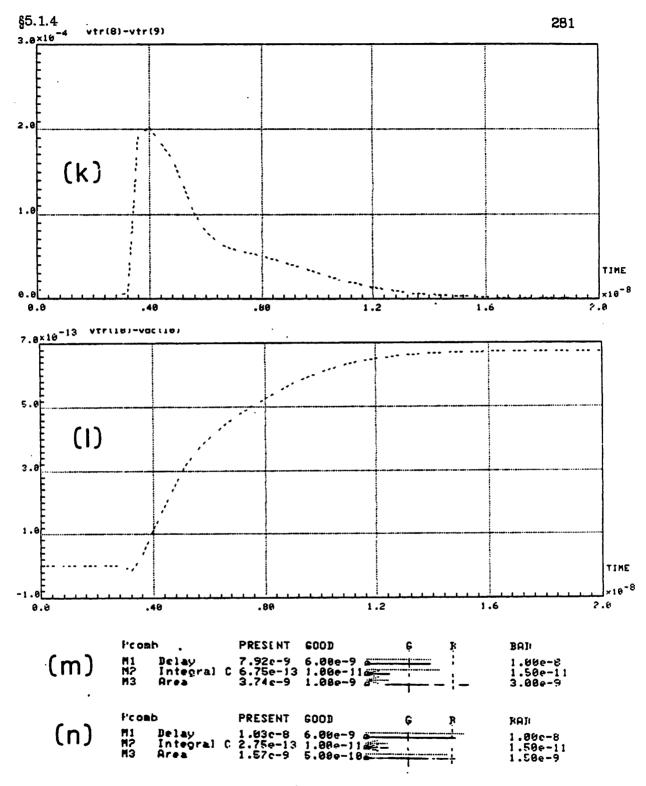

An important function of the programming language in DELIGHT is to implement optimization and other computer-aided design algorithms. This function embodies both the development of algorithms as well as their execution by designers. The requirements in this regard for both optimization experts as well as designers have been covered previously in section 2.3. Related issues are also discussed in the next section.