### Copyright © 1984, by the author(s). All rights reserved.

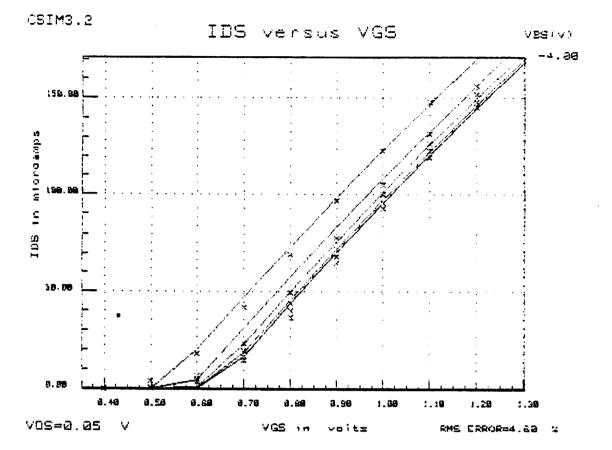

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

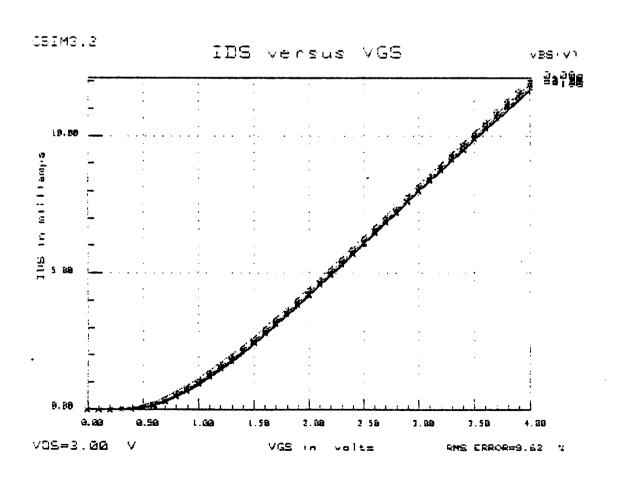

## A FULLY AUTOMATED MOS DEVICE CHARACTERIZATION SYSTEM FOR PROCESS-ORIENTED INTEGRATED CIRCUIT DESIGN

bу

Brian Scott Messenger

Memorandum No. UCB/ERL M84/18 30 January 1984

# A FULLY AUTOMATED MOS DEVICE CHARACTERIZATION SYSTEM FOR PROCESS-ORIENTED INTEGRATED CIRCUIT DESIGN

by

Brian Scott Messenger

Memorandum No. UCB/ERL M84/18

30 January 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

### BRIAN SCOTT MESSENGER Author

A FULLY AUTOMATED MOS DEVICE

CHARACTERIZATION SYSTEM FOR PROCESS—

ORIENTED INTEGRATED CIRCUIT DESIGN

Title

#### RESEARCH PROJECT

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II.

Approval for the Report and Comprehensive Examination:

| Committee: | Danid G. Hodeco | , Research Advison |

|------------|-----------------|--------------------|

| -          | Jan 30, 1984    | Date               |

|            | 0 y Scharlette  |                    |

| •<br>•     | Jan 30,1984     | Date               |

#### A FULLY AUTOMATED MOS DEVICE CHARACTERIZATION SYSTEM FOR PROCESS-ORIENTED INTEGRATED CIRCUIT DESIGN

Brian Scott Messenger

Department of Electrical Engineering and Computer Sciences University of California, Berkeley

#### **ABSTRACT**

A fully automatic MOS device parameter extraction system has been developed to provide a systematic, reproducible and accurate means of determining device parameters for a new compact short channel MOSFET model. The system also provides the capability of evaluating parameter variations with device geometry for the purpose of generating process files which can model spectrums of device sizes. The parameter extraction software has been merged with device measurement, interactive graphics, and automatic prober capabilities to provide a powerful tool for device research and for statistical analysis of integrated circuit processes. Use of the model and the extraction system to analyze devices from various processes, has resulted in excellent simulations for devices with gate oxides ranging from 200 Angstroms to 700 Angstroms, and for channel lengths extending down to onemicron drawn dimensions. The parameter extraction system can be used for research, or in a production environment by a technician with no prior device physics background. This fully automatic MOS device characterization capability is expected to result in significant increases in integrated circuit design productivity.

January 31, 1984

#### ACKNOWLEDGEMENTS

I wish to thank my thesis advisors, Professor David A. Hodges and Dr. Don L. Scharfetter, for their encouragement, support and technical advice throughout the entire course of my research. Dr. Scharfetter provided invaluable technical background for the development of the Automatic Characterization System, and was responsible for the organization and management of the entire CSIM model team at Berkeley. I would also like to thank Bing Sheu, Ralph Liu and Jeff Burns who provided valuable technical discussions in the process of interfacing our collective efforts.

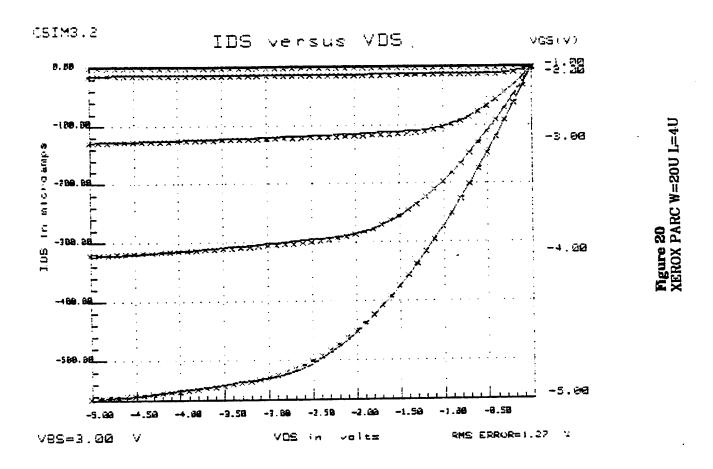

I am grateful to Dr. Lynn Roylance and Dr. Fred Perner of Hewlett-Packard Laboratories for the work opportunities, exposure, and insight to device modeling and characterization that they provided. I would like to thank Xerox Palo Alto Research Center, and especially Dr. Bob Tremain for technical discussions, and for sample wafers provided. Professor Ping Ko of U.C. Berkeley and previously of Bell Labs also provided experimental test wafers for analysis. Hewlett Packard Corporation and Xynetics/Electroglas Corporation made this project possible through generous equipment donations which are greatly appreciated. A portion of this research was also supported by the Semiconductor Research Corporation, Grant #82-11-008.

I deeply appreciate the years of help, support and encouragement that my parents, Miles and Frances, have provided me.

#### TABLE OF CONTENTS

| 1. INTRODUCTION.                                                   | 1  |

|--------------------------------------------------------------------|----|

| 2. CSIM MODEL AND PROCESS FILE DESCRIPTION                         | 6  |

| 2.1. CSIM Model Relationship to the Parameter Extraction Strategy  | 7  |

| 2.2. CSIM Threshold Voltage Model                                  | 8  |

| 2.3. Modeling the Transconductance with CSIM                       | 9  |

| 2.4. The Parameter 'a' and its Function in the CSIM Model          | 9  |

| 2.5. Handling Depletion Mode MOS Devices                           | 10 |

| 2.6. Parameter Extraction Sequence.                                | 10 |

| 2.7. Process File Development                                      | 11 |

| 3. AUTOMATIC MOS DEVICE PARAMETER EXTRACTION SYSTEM HARDWARE       | 13 |

| 3.1. The 4145 Parameter Analyzer                                   | 13 |

| 3.2. 2001X Automatic Wafer Prober.                                 | 14 |

| S.3. 2671G Thermal Printer                                         | 16 |

| S.4. 9836 Computer and VAX Link                                    | 16 |

| 4. AUTOMATIC MOS DEVICE PARAMETER EXTRACTION SYSTEM SOFTWARE       | 17 |

| 4.1. Parameter Extraction Routines                                 | 18 |

| 4.1.1. Linear Region Extraction of Beta0x, U0x, and Vtx            | 18 |

| 4.1.2. Extraction of the Parameter 2Phif                           | 20 |

| 4.1.3. General Linear Region Threshold Analysis and Data Reduction | 22 |

| 4.1.4. Saturation Region Extraction of Beta0sat, Vthsat, and U1sat | 23 |

| 4.1.5. Saturation Region Data Reduction                            | 24 |

| 4.2. Device Measurement Software                                   | 25 |

| 4.2.1. Device Type Measurement.                                    | 25 |

| 4.2.2. Device Functionality Verification.                          | 27 |

| 4.2.3. Device Measurement for Parameter Extraction                 | 28 |

| 4.2. Presses File Percelanment Software                            | 30 |

| 4.4. Interactive Graphics Software                             | 31 |

|----------------------------------------------------------------|----|

| 4.5. Automatic Prober Software                                 | 33 |

| 5. SAMPLE PROGRAM EXECUTION                                    | 36 |

| 5.1. Initial Program Mode Selection                            | 36 |

| 5.2. User Input Lists                                          | 37 |

| 5.3. Continuous Extraction Display                             | 38 |

| 5.4. Graphic Subprogram Interaction                            | 39 |

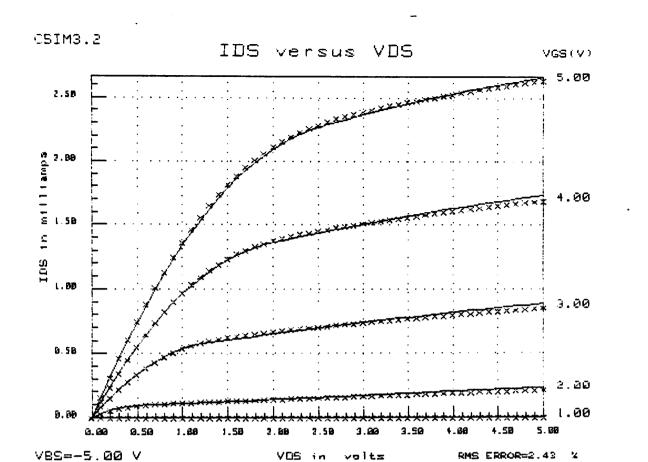

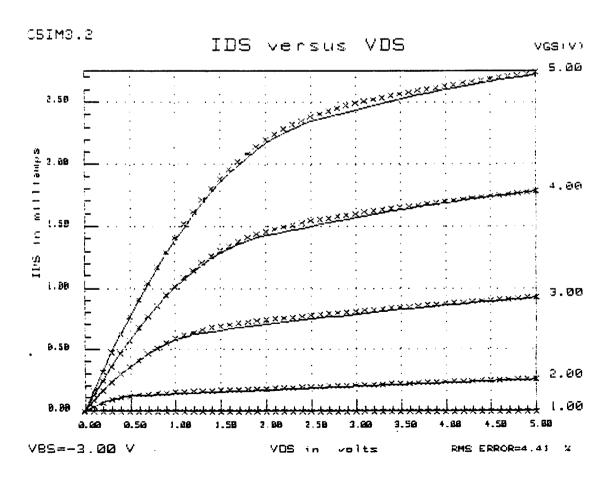

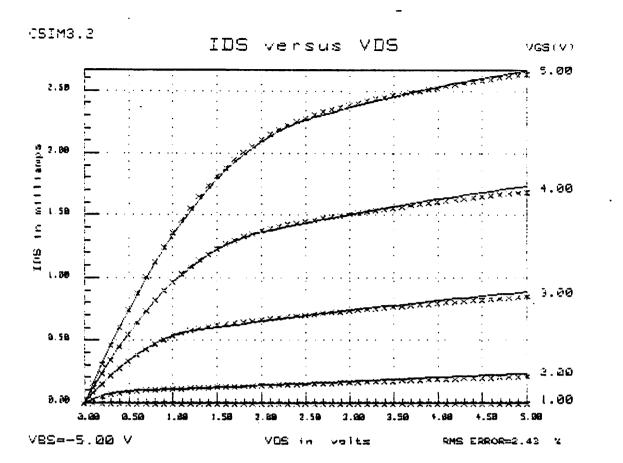

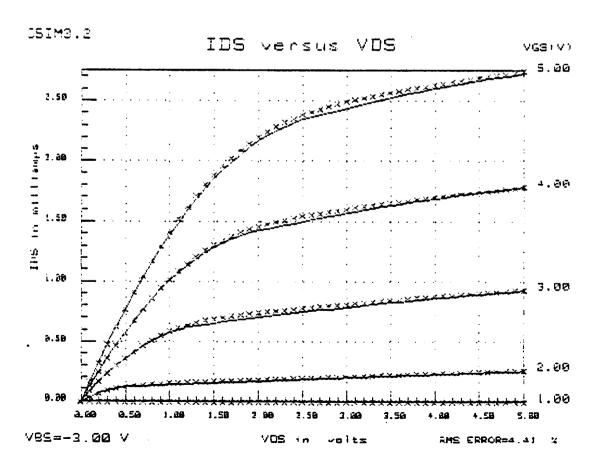

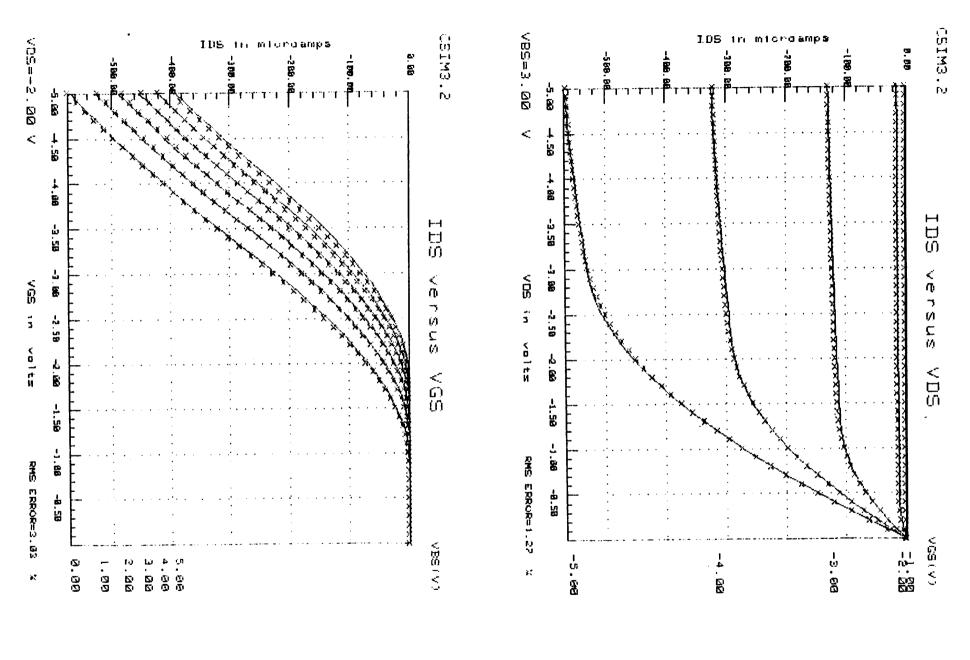

| 5.5. Experimental Results for Various Devices                  | 40 |

| 6. POSSIBLE FUTURE PROGRAM ENHANCEMENTS                        | 42 |

| APPENDIX 1. PARAMETER EXTRACTION SYSTEM SETUP INSTRUCTIONS     | A1 |

| APPENDIX 2. LAYOUT CONSIDERATIONS FOR AUTOMATIC PROBING        | A2 |

| APPENDIX 3. INSTRUCTIONS FOR AUTOMATIC PROBER FILE DEVELOPMENT | A3 |

| APPENDIX 4. CSIM SOFTWARE SOURCECODE (Available on Request)    | A4 |

| 4.4. Interactive Graphics Software                             | 31        |

|----------------------------------------------------------------|-----------|

| 4.5. Automatic Prober Software                                 | 33        |

| 5. SAMPLE PROGRAM EXECUTION                                    | 36        |

| 5.1. Initial Program Mode Selection                            | 36        |

| 5.2. User Input Lists                                          | 37        |

| 5.3. Continuous Extraction Display                             | 38        |

| 5.4. Graphic Subprogram Interaction                            | 39        |

| 5.5. Experimental Results for Various Devices                  | 40        |

| 6. POSSIBLE FUTURE PROGRAM ENHANCEMENTS                        | 42        |

| APPENDIX 1. PARAMETER EXTRACTION SYSTEM SETUP INSTRUCTIONS     | A1        |

| APPENDIX 2. LAYOUT CONSIDERATIONS FOR AUTOMATIC PROBING        | A2        |

| APPENDIX 3. INSTRUCTIONS FOR AUTOMATIC PROBER FILE DEVELOPMENT | A3        |

| APPENDIX 4. CSIM SOFTWARE SOURCECODE (Available on Request)    | <b>A4</b> |

|                                                                |           |

#### 1. INTRODUCTION

With the introduction of integrated circuit computer aided design programs such as SPICE in the late 1960's, there arose a critical need for accurate models to simulate the electrical characteristics of transistors. The means to extract consistent and reproducible sets of model parameters was and still remains an essential requirement for successful integrated circuit simulation. An analysis of the present state of affairs in MOS device modeling discloses a diverse collection of parameter sets in use by various universities and corporations. The means by which these organizations extract their model parameters is equally varied, and include such methods as: rapid curve tracer estimates, elaborate time-consuming device physics analysis studies, and global optimization routines providing for model generality. To fully understand the benefits of fully automatic parameter extraction, it is necessary to understand the limitations and shortcomings of the types of methods which are presently in use.

In many instances, a circuit designer is confronted with the need to extract a set of device parameters before any circuit simulations can be attempted. Unless this person has access to, and is familiar with, some form of computer controlled system to lead him through parameter extraction, the designer will likely resort to using a curve tracer to determine rough values for parameters such as threshold voltage, transconductance, etc.. The very nature of this method of parameter extraction induces a large degree of uncertainty, and non-reproducability. Error may be introduced in the actual visual extraction of the device parameters from the measured characteristics, or it may occur that the model and the choice of parameters are not sufficient for simulating all of the observed device properties.

At the opposite end of the modeling spectrum from the simple device model user, stands the device physicist who analyzes and develops models to explain recently observed device phenomena. This theoretician is generally not involved

with computer aided circuit design, and may develop models which can not be feasibly used in simulators such as SPICE. When extensive device models have been developed, the option is present to translate the elaborate set of model parameters into a smaller subset suitable for circuit simulation. This translation can create uncertainty, and this alone makes this method of parameter extraction undesirable. The fact that the methods used to extract large sets of parameters may require extensive time and knowledge places the greatest limitation on this approach. The probability that parameter extraction for a very complicated model can be done fully automatically and can handle devices over an entire range of device types and geometries is very slim.

In some instances programs have been written to systemize device parameter extraction using global optimization algorithms. This method allows for simple model modification, and is preferable to the previously mentioned approaches. Assuming a suitable model and parameter set are chosen, a set of parameters can be generated which, as a group, will generally simulate the measured device characteristics. Unfortunately, there are pitfalls that may arise when using a global optimization method. A major problem encountered is that limits on the variation of the parameters in the parameter set must be specified to enable the global optimizer to converge to an accurate solution. The designer may not have an intuitive feel for the acceptable ranges of some parameters, and these limits will be device type and device geometry dependent. Depending upon the initial selection of allowable parameter ranges, it is possible for various sets of parameters to be extracted. This results in the situation that though a set of parameters can be derived to model the electrical characteristics of an isolated device, it is very difficult to corelate the extracted model parameters with device geometry. The global optimization approach is not a method that can be easily automated for testing multiple devices of

with computer aided circuit design, and may develop models which can not be feasibly used in simulators such as SPICE. When extensive device models have been developed, the option is present to translate the elaborate set of model parameters into a smaller subset suitable for circuit simulation. This translation can create uncertainty, and this alone makes this method of parameter extraction undesirable. The fact that the methods used to extract large sets of parameters may require extensive time and knowledge places the greatest limitation on this approach. The probability that parameter extraction for a very complicated model can be done fully automatically and can handle devices over an entire range of device types and geometries is very slim.

In some instances programs have been written to systemize device parameter extraction using global optimization algorithms. This method allows for simple model modification, and is preferable to the previously mentioned approaches. Assuming a suitable model and parameter set are chosen, a set of parameters can be generated which, as a group, will generally simulate the measured device characteristics. Unfortunately, there are pitfalls that may arise when using a global optimization method. A major problem encountered is that limits on the variation of the parameters in the parameter set must be specified to enable the global optimizer to converge to an accurate solution. The designer may not have an intuitive feel for the acceptable ranges of some parameters, and these limits will be device type and device geometry dependent. Depending upon the initial selection of allowable parameter ranges, it is possible for various sets of parameters to be extracted. This results in the situation that though a set of parameters can be derived to model the electrical characteristics of an isolated device, it is very difficult to corelate the extracted model parameters with device geometry. The global optimization approach is not a method that can be easily automated for testing multiple devices of

various device types and sizes to gain meaningful statistical data.

It is easily perceived that a fully integrated solution which encompasses the entire range from device modeling to automatic parameter extraction and subsequent circuit simulation would greatly increase productivity and reliability in the field of circuit design. The university environment provides the perfect opportunity to develop, introduce, and enhance such a solution.

The approach to be outlined here revolves around a new compact short channel insulated gate field effect transistor model (CSIM) which was initially developed, at Bell Labs by H. Poon [1], and was enhanced at Berkeley and Xerox PARC by Bing Sheu et. al. [2]. The model is compact to allow for reasonable execution speed using SPICE, and has been implemented in SPICE version 2G.6 by Ralph Liu [3]. The means to automatically generate device parameters without requiring any initial parameter estimates or parameter ranges, was of prime importance in the development of the CSIM model. The use of a consistent reproducible parameter extraction approach allows for the modeling of parameter variations with device geometry. This device geometry dependent modeling is used to develop a **process file** which can model devices of a given device type over process ranges of channel lengths and widths.

The process file approach allows the circuit designer to consider a design in terms of the physical mask dimensions of a layout. This method of analysis replaces the cumbersome approach of requiring the circuit designer to determine parameters to model every device and section of interconnect encountered in an integrated circuit layout. In the case of a MOS integrated circuit, a process file would describe the following: all NMOS and PMOS devices categorized as being enhancement, depletion or zero-threshold, diffusion interconnects, polysilicon levels of interconnect, and metal levels of interconnect. A designer

will enter device and interconnect dimensions, and will provide the SPICE simulation program with a process file name. The electrical parameters determined by the automatic parameter extraction program described in this report are used directly in a CSIM Capacitance model under development by Bing Sheu. Programs to automatically determine the parasitic resistance and capacitance values to which model device interconnect will be the subject of future work at Berkeley.

The following report introduces the structure of the CSIM model, and the process file approach. It relates how the development of the model was linked to the need for a fully automatic parameter extraction capability, and how the program extracts all initial parameter estimates prior to final parameter optimization. The hardware implementation of the parameter extraction system at the University of California at Berkeley is described, and system setup and use are explained in the Appendices.

The integrated system parameter extraction software is written in Pascal, and has been partitioned into six major sections. The measurement of devices is fully program controlled, requiring the user to input only the supply voltage which will be used in circuit operation. The parameter extraction software is fully self contained, and requires the user to supply only the physical parameters of the gate oxide thickness and the temperature of the wafer test chuck before full parameter extraction can proceed. An extensive graphics package is described which allows the user to view firsthand the simulated extracted model parameter characteristics and compare them to the actual measured device electrical characteristics. Incorporated within the software is the capability to develop process files after multiple devices have been measured. These process files are transported to a mainframe computer to be accessed by SPICE.

will enter device and interconnect dimensions, and will provide the SPICE simulation program with a process file name. The electrical parameters determined by the automatic parameter extraction program described in this report are used directly in a CSIM Capacitance model under development by Bing Sheu. Programs to automatically determine the parasitic resistance and capacitance values to which model device interconnect will be the subject of future work at Berkeley.

The following report introduces the structure of the CSIM model, and the process file approach. It relates how the development of the model was linked to the need for a fully automatic parameter extraction capability, and how the program extracts all initial parameter estimates prior to final parameter optimization. The hardware implementation of the parameter extraction system at the University of California at Berkeley is described, and system setup and use are explained in the Appendices.

The integrated system parameter extraction software is written in Pascal, and has been partitioned into six major sections. The measurement of devices is fully program controlled, requiring the user to input only the supply voltage which will be used in circuit operation. The parameter extraction software is fully self contained, and requires the user to supply only the physical parameters of the gate oxide thickness and the temperature of the wafer test chuck before full parameter extraction can proceed. An extensive graphics package is described which allows the user to view firsthand the simulated extracted model parameter characteristics and compare them to the actual measured device electrical characteristics. Incorporated within the software is the capability to develop process files after multiple devices have been measured. These process files are transported to a mainframe computer to be accessed by SPICE.

Routines have been developed to allow for fully automatic probing of devices across entire wafers to develop a statistical base of process parameters. A set of simple menus provides a designer having no prior experience in device parameter analysis with the capability of selecting various system options, and of performing full reproducible parameter extractions. After the project implementation is discussed, a sample program execution session is presented. Experimental results for various integrated circuit processes are reported.

The parameter extraction system described here represents a key link in a fully integrated solution which has been developed to remove major bottlenecks in the process of achieving fast and accurate MOS circuit design. It is hoped that this entire integrated solution will evolve into a standard industry wide approach that can unify modeling, parameter extraction and simulation for MOS integrated circuits.

#### 2. CSIM MODEL AND PROCESS FILE DESCRIPTION

The development of the CSIM model was intimately connected to the development of a fully automatic MOS device parameter extraction capability. It was essential to construct a model whose parameters could be determined using sets of local optimizations, to avoid the inherent difficulties in using global optimization for parameter extraction. The effects of mobility degradation due to increased vertical electric field in the channel and velocity saturation due to increased transverse electric fields in the channel, are modeled with CSIM. Velocity saturation is essentially nonexistent at very small drain-source bias potentials, while it may be a dominating factor with drain source bias on the order of the supply voltage, depending upon the supply voltage and the device geometry. This is a critically important fact, since it permits the decoupling of the velocity saturation and the low field mobility degradation effects in doing parameter extraction. Mobility degradation parameters can be extracted at very low drain-source bias, and can then be used in extracting the velocity saturation parameters at high drain-source biases. Experimentation with parameter extraction using the CSIM model has shown that by using drain-source biases near zero, and drain-source biases near the supply voltage, a set of parameters can be extracted which can accurately model the entire range of drain-source biases.

The CSIM model consists of 17 parameters which are used to simulate the electrical characteristics of a single device. Of these 17 parameters, eight primary parameters represent well understood phenomena such as transconductance or mobility reduction. These eight parameters make up a first order set of parameters which can be used as a complete set of device parameters. The remaining nine secondary parameters represent the variations of some primary parameters with drain-source and bulk-source potentials and provide a second-

#### 2. CSIM MODEL AND PROCESS FILE DESCRIPTION

The development of the CSIM model was intimately connected to the development of a fully automatic MOS device parameter extraction capability. It was essential to construct a model whose parameters could be determined using sets of local optimizations, to avoid the inherent difficulties in using global optimization for parameter extraction. The effects of mobility degradation due to increased vertical electric field in the channel and velocity saturation due to increased transverse electric fields in the channel, are modeled with CSIM. Velocity saturation is essentially nonexistent at very small drain-source bias potentials, while it may be a dominating factor with drain source bias on the order of the supply voltage, depending upon the supply voltage and the device geometry. This is a critically important fact, since it permits the decoupling of the velocity saturation and the low field mobility degradation effects in doing parameter extraction. Mobility degradation parameters can be extracted at very low drain-source bias, and can then be used in extracting the velocity saturation parameters at high drain-source biases. Experimentation with parameter extraction using the CSIM model has shown that by using drain-source biases near zero, and drain-source biases near the supply voltage, a set of parameters can be extracted which can accurately model the entire range of drain-source biases.

The CSIM model consists of 17 parameters which are used to simulate the electrical characteristics of a single device. Of these 17 parameters, eight primary parameters represent well understood phenomena such as transconductance or mobility reduction. These eight parameters make up a first order set of parameters which can be used as a complete set of device parameters. The remaining nine secondary parameters represent the variations of some primary parameters with drain-source and bulk-source potentials and provide a second-

order, high-accuracy model. The CSIM approach analyzes the parameters that are extracted for devices of various channel lengths and widths, and models their variations with device geometry to create a process file which can describe an entire range of device geometries.

#### 2.1. CSIM Model Relationship to the Parameter Extraction Strategy

The structure of the CSIM model was developed to allow three parameters to be extracted at small drain-source biases, and three parameters to be extracted at drain-source biases near the supply voltage. Given the structure of the model, it was possible to use a **Linear Least Square** algorithm in the process of determining these sets of three parameters. The optimization was performed using a combination of a **Newton-Raphson** algorithm and the Linear Least Square Algorithm to converge rapidly to a solution.

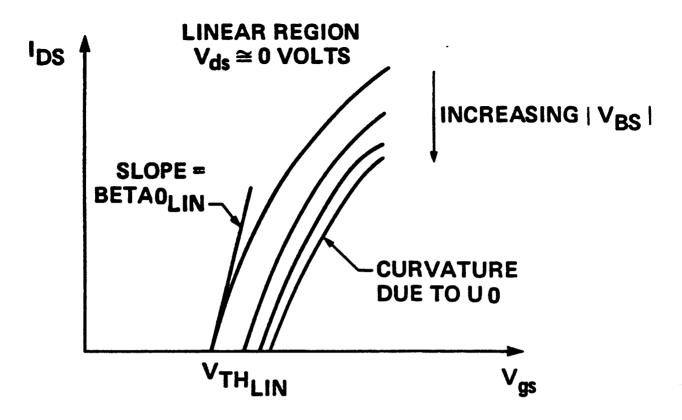

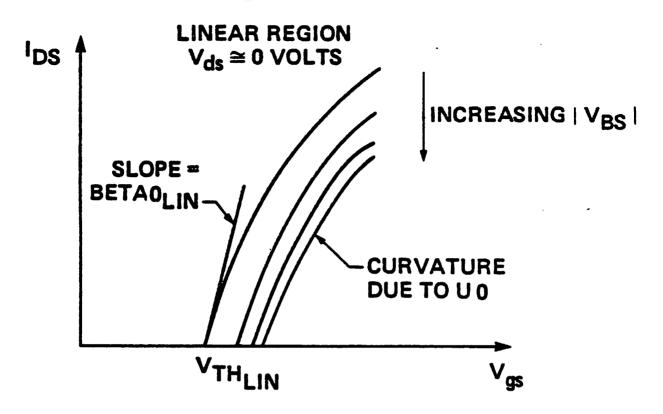

At small drain-source biases, values of gate-source bias are chosen so that a MOSFET under test is in the linear region of operation. The drain-source current in the linear region(Equation 1) contains three parameters which are extracted: the transconductance (BetaOlin), the threshold voltage (Vthlin), and the mobility reduction parameter (UO). The parameter **a** is a function of *Vbs* and its derivation will be described later.

$$Ids_{lin} = \frac{Beta \, 0lin}{(1 + U0^* (\,Vgs - Vthlin\,))} (\,Vgs - Vthlin - \frac{a}{2} \,Vds\,) \,Vds \tag{1}$$

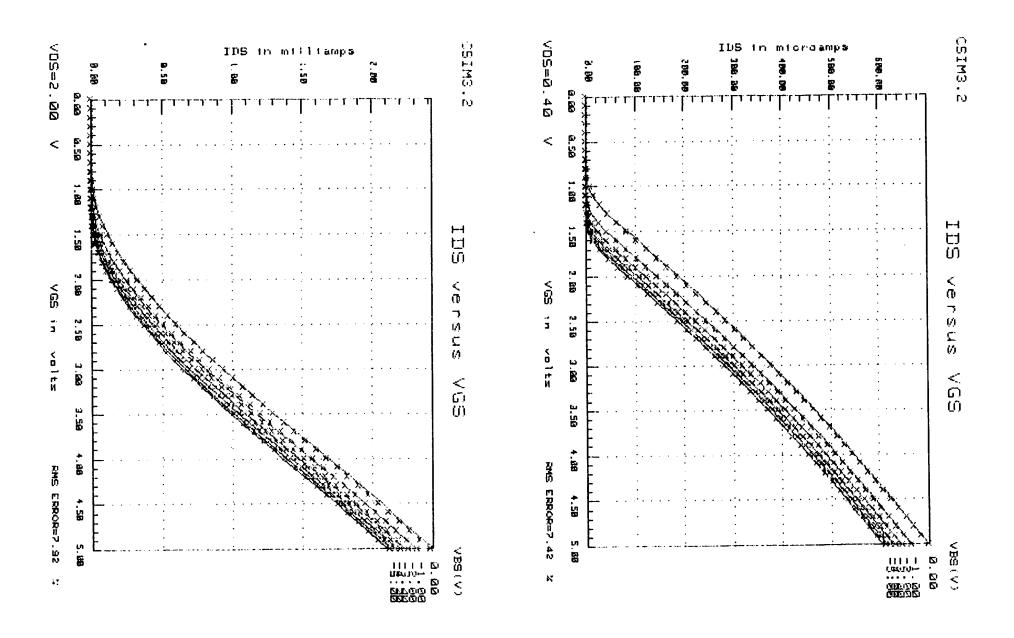

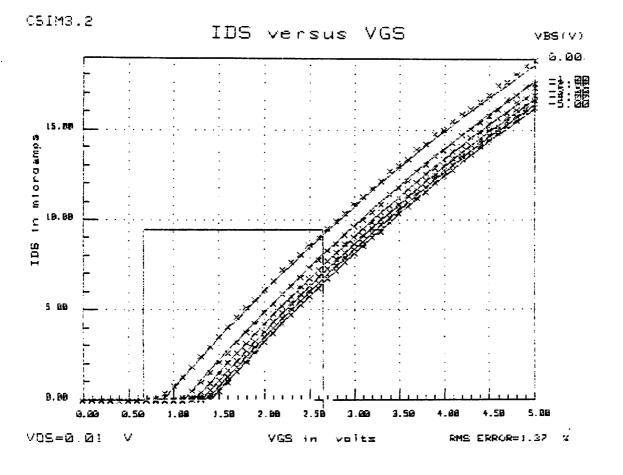

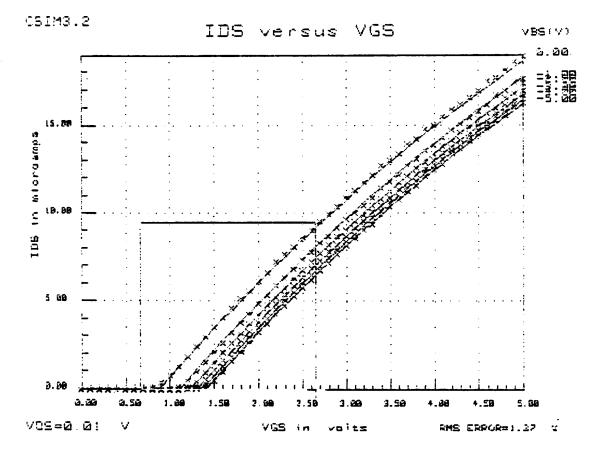

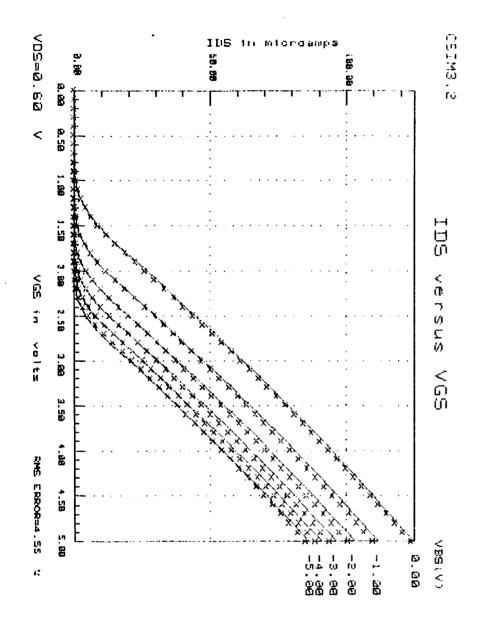

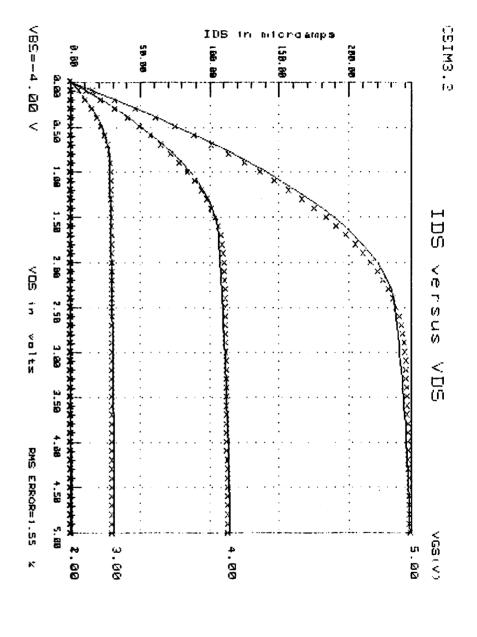

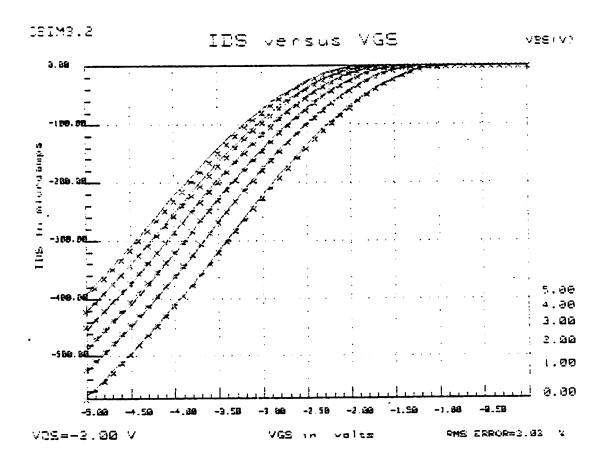

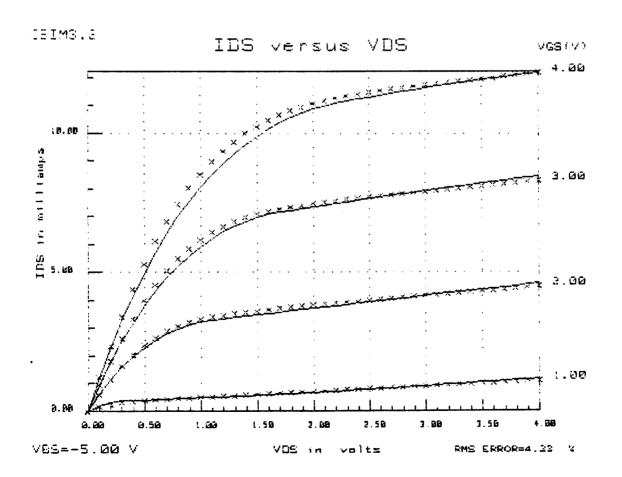

For parameter extraction purposes, the linear region equation for drain-source current is transformed to the equation for the conductance in the linear region. Figure 1 shows how curves of the conductance versus gate-source potential reflect the values of the linear region parameters.

At large drain-source potentials, an enhancement MOSFET under test will operate in the saturation region. Special considerations for depletion MOSFETs

Figure 1

Figure 2

Figure 1

Figure 2

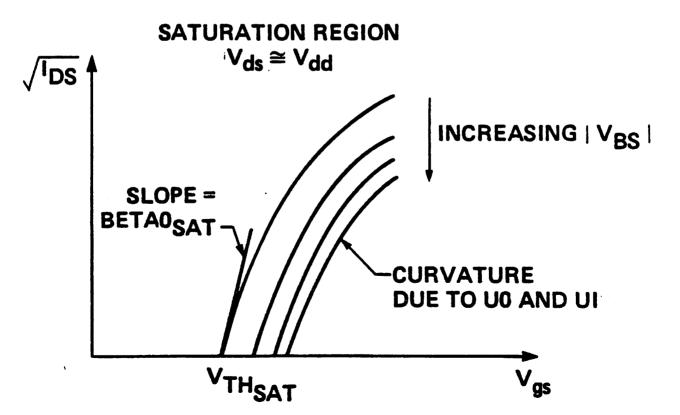

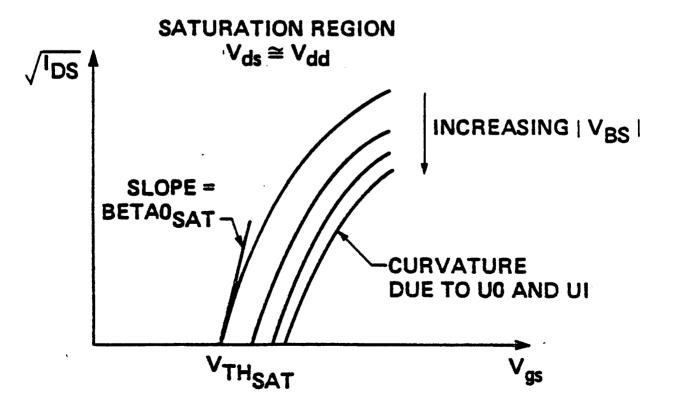

are discussed later. The drain-source current in the saturation region (Equation 2) contains three additional parameters which are extracted: the transconductance in saturation (BetaOsat), the threshold voltage in saturation (Vthsat), and the velocity saturation parameter U1. The velocity saturation model development for CSIM was done by Don Scharfetter, and is reported by Bing Sheu et. al.[2]. The voltage Vdssat at which saturation occurs is modeled in Equation (3).

$$Ids_{sat} = \frac{Beta \, 0sat \, (Vgs - Vthsat)^{2}}{(1 + U0(Vgs - Vthsat))a \, (1.0 + \frac{U1}{a \, (Vgs - Vthsat)} + \sqrt{1.0 + \frac{2.0 * U1}{a \, (Vgs - Vthsat)}})}$$

$$Vdssat = \frac{2(Vgs - Vth)}{a \, \sqrt{1 + \frac{U1 * (Vgs - Vth)}{a} + (1 + \frac{2U1(Vgs - Vth)}{a})^{\frac{1}{2}}}}$$

(3)

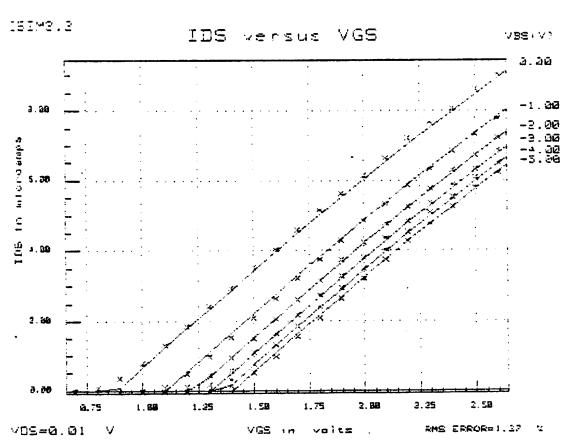

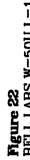

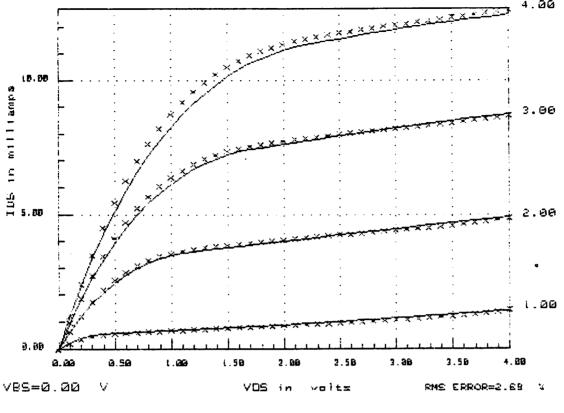

Figure 2 shows how plots of the square-root of drain-source current reflect the values of the saturation parameters.

#### 2.2. CSIM Threshold Voltage Model

There are five primary CSIM parameters which model the threshold voltage: VFB which is the flatband voltage, 2Phif which reflects the channel doping level, K1 which models the bulk doping effect, and the combination of K2 and ETA which model the drain induced barrier lowering effect. The basic CSIM threshold voltage equation (Equation 3) parameters are extracted from the values of Vthlin and Vthsat which have been determined at various Vds and Vbs bias conditions. The parameter ETA is modeled with three CSIM parameters (Equation 4) to reflect variations with Vbs and Vds bias.

$$Vth = VFB + 2Phif + K1*(2Phif - Vbs)^{1/2} - K2*(2Phif - Vbs) - ETA*(Vds)$$

(4)

$$ETA = ETA_0 + X2ETA^*(2Phif - VBS) + X3ETA^*(Vdd - Vds)$$

(5)

#### 2.3. Modeling the Transconductance with CSIM

Modeling the transconductance of a MOS device is critical, and to reflect this importance, five CSIM parameters are used to model this device parameter. The values of BetaOlin which are extracted over ranges of Vos and Vds biases are used to extract the parameters BETAO and X2BETAO to model the transconductance in the linear region (Equation 6).

$$Beta O_{linear} = BETAO + X2BETAO * Vbs$$

(6)

In a similar fashion the values of BetaOsat which have been extracted are used to extract the CSIM parameters BETAOSAT, X2BETAOSAT, and X3BETAOSAT which model BetaO in the saturation region (Equation 7).

$$Beta O_{sat} = BETA OSAT + X2BETA OSAT * Vbs + X3BETA OSAT * (Vds - Vdd)$$

(7)

Using the parameters BETAO, BETAOSAT, and X3BETAOSAT, a parabolic fit for the transconductance versus Vds bias is performed. Allowing the transconductance to vary with bias, as is done in CSIM, provides greater accuracy, and has the added advantage that it can absorb some effects that may not be accounted for explicitly in the model. In this manner, phenomena associated with very short channel devices may be implicitly handled with the CSIM approach well before the device physics causing these effects can be well understood and modeled.

#### 2.4. The Parameter 'a' and its Function in the CSIM Model

The basic first order charge theory for a MOS device, derived by Ihantola and Moll[4], contains 3/2 power terms (Equation 8) which are computationally very time consuming in circuit simulators such as SPICE.

$$IDS_{lin} = BETAO((Vgs - 2phif - Vfb)Vds - \frac{Vds^{2}}{2} - \frac{2\sqrt{2qe_{si}N_{A}}}{3C_{ox}}(T))$$

$$T = (Vds + 2phif - Vbs)^{3/2} - (2phif - Vbs)^{3/2}$$

(8)

#### 2.3. Modeling the Transconductance with CSIM

Modeling the transconductance of a MOS device is critical, and to reflect this importance, five CSIM parameters are used to model this device parameter. The values of BetaOlin which are extracted over ranges of Vos and Vds biases are used to extract the parameters BETAO and X2BETAO to model the transconductance in the linear region (Equation 6).

$$Beta O_{linear} = BETA O + X2BETA O * Vbs$$

(6)

In a similar fashion the values of Beta0sat which have been extracted are used to extract the CSIM parameters BETA0SAT, X2BETA0SAT, and X3BETA0SAT which model Beta0 in the saturation region (Equation 7).

$$Beta O_{sat} = BETA OSAT + X2BETA OSAT^*Vbs + X3BETA OSAT^*(Vds - Vdd)$$

(7)

Using the parameters BETAO, BETAOSAT, and X3BETAOSAT, a parabolic fit for the transconductance versus Vds bias is performed. Allowing the transconductance to vary with bias, as is done in CSIM, provides greater accuracy, and has the added advantage that it can absorb some effects that may not be accounted for explicitly in the model. In this manner, phenomena associated with very short channel devices may be implicitly handled with the CSIM approach well before the device physics causing these effects can be well understood and modeled.

#### 2.4. The Parameter 'a' and its Function in the CSIM Model

The basic first order charge theory for a MOS device, derived by Ihantola and Moll[4], contains 3/2 power terms (Equation 8) which are computationally very time consuming in circuit simulators such as SPICE.

$$IDS_{lin} = BETAO((Vgs - 2phif - Vfb)Vds - \frac{Vds^{2}}{2} \frac{2\sqrt{2qe_{si}N_{A}}}{3C_{ox}}(T))$$

$$T = (Vds + 2phif - Vbs)^{3/2} - (2phif - Vbs)^{3/2}$$

(8)

In the CSIM model, the three-halves power terms are replaced through the use of the term a shown in Equation (9). The parameter a was derived numerically by H. Poon [1], using a power series expansion about Vos and Vds.

$$\alpha = 1.0 - \frac{1.0}{1.744 + 0.8364(2phif - Vbs)} \frac{K1}{2} \sqrt{2phif - Vbs}$$

(9)

The use of the term **a** is needed in the linear region parameter extraction for the purpose of interpolating the threshold voltage and mobility reduction parameters to their values at zero drain-source bias. Equations 1,4 and 9 are solved simultaneously to derive the linear region parameters Beta0, U0, VFB, 2Phif, K1, and K2. This procedure is described in detail in the *Parameter Extraction Software* section.

#### 2.5. Handling Depletion Mode MOS Devices

With Vils values near the supply voltage, a Depletion Mode transistor may or may not be in the saturation region of operation, depending upon the value of Vgs. In order to handle Depletion Mode devices with the same routines, and to extract the same parameters as in the case of Enhancement Mode devices, program modifications were necessary. At every value of Vgs which is analyzed, it is necessary to determine within the optimization routines whether the device is in the linear region or the saturation region. Once this is known, the coefficients for the Linear Least Square algorithm can be properly determined, and the optimization can continue to derive the necessary parameters.

#### 2.6. Parameter Extraction Sequence

The parameter extraction strategy results in a set of 17 device parameters. The parameters VFB, 2Phif, K1, K2, BETAO, X2BETAO, U0 and X2U0 are derived from the linear region extraction, and in the case of BETAO and X2BETAO are

modified to account for the effects due to some saturation parameters. X2U0 is described in Equation (22). After the linear region threshold parameters have been derived, it is possible to perform parameter extraction for the saturation region which represents drain-source biases near *Vdd*. Analysis of the saturation region data results in the parameters U1, X2U1, X3U1, ETA, X2ETA, X3ETA, BETAOSAT, X2BETAOSAT, and X3BETAOSAT. Once the 17 CSIM parameters have been determined for a device, they are stored for later development of a process file.

The prefixes X2 and X3 used throughout this report and the CSIM model deserve further explanation. Parameters with the prefix X2 represent the bulk-source dependency of one of the eight main CSIM parameters, while those parameters with the prefix X3 represent the drain-source dependency of one of the eight main CSIM parameters. The reader should refer to Equations (29) through (33) for examples of these parameters.

#### 2.7. Process File Development

The fact that variations between devices in close proximity on a wafer are usually quite small allows devices of varying sizes at the same die location to be analyzed to create a **process file**. Each type of device which is present on an integrated circuit test die is modeled using 54 parameters which are generated by the automatic parameter extraction program. As an example, a typical CMOS process file would have 54 parameters to model all NMOS enhancement devices present on a given test die, and 54 parameters to model all PMOS enhancement devices present on the same test die. This approach allows statistical analysis to be done on the process parameters that have been generated across a wafer to model variations in parameters such as substrate doping levels.

modified to account for the effects due to some saturation parameters. X2U0 is described in Equation (22). After the linear region threshold parameters have been derived, it is possible to perform parameter extraction for the saturation region which represents drain-source biases near *Vdd*. Analysis of the saturation region data results in the parameters U1, X2U1, X3U1, ETA, X2ETA, X3ETA, BETAOSAT, X2BETAOSAT, and X3BETAOSAT. Once the 17 CSIM parameters have been determined for a device, they are stored for later development of a process file.

The prefixes X2 and X3 used throughout this report and the CSIM model deserve further explanation. Parameters with the prefix X2 represent the bulk-source dependency of one of the eight main CSIM parameters, while those parameters with the prefix X3 represent the drain-source dependency of one of the eight main CSIM parameters. The reader should refer to Equations (29) through (33) for examples of these parameters.

#### 2.7. Process File Development

The fact that variations between devices in close proximity on a wafer are usually quite small allows devices of varying sizes at the same die location to be analyzed to create a process file. Each type of device which is present on an integrated circuit test die is modeled using 54 parameters which are generated by the automatic parameter extraction program. As an example, a typical CMOS process file would have 54 parameters to model all NMOS enhancement devices present on a given test die, and 54 parameters to model all PMOS enhancement devices present on the same test die. This approach allows statistical analysis to be done on the process parameters that have been generated across a wafer to model variations in parameters such as substrate doping levels.

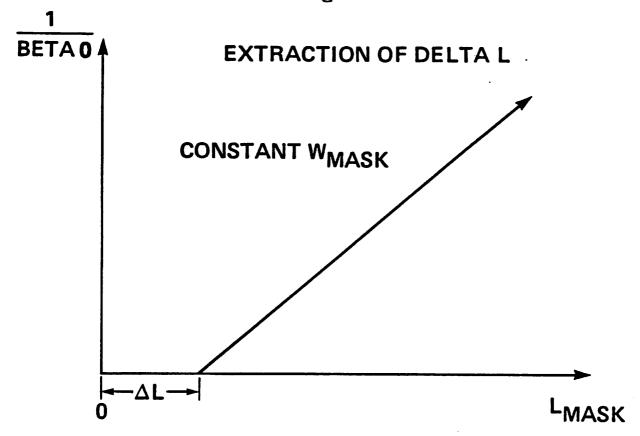

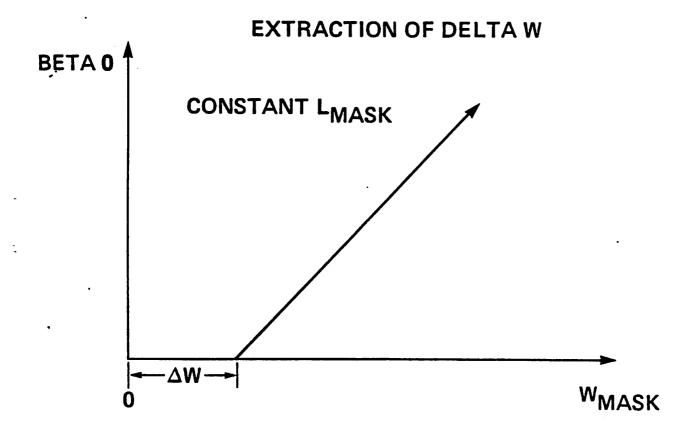

Figure 3

Figure 4

Process parameters are determined through analysis of the variation in the 17 CSIM model parameters with device channel length and width. The first calculation performed analyzes BETAO versus drawn length and drawn width (Equation 10) to determine DELTAL and DELTAW

$$BETA0 = \mu_n Cox \frac{(W_m + \Delta W)}{(L_m + \Delta L)}$$

(10)

Figures 3 and 4 show the relationships between BETAO and drawn width and drawn length that are used to determine DeltaL and DeltaW. The low field mobility, DELTAL and DELTAW are stored in the process file and are used by SPICE in determining the device gain.

Once DELTAL and DELTAW have been determined, they are used to convert all values of Mask length and width to the corresponding values of electrical channel length and width. At this point, the remaining 16 CSIM parameters are modeled versus electrical channel length and width using three parameters: PO PL, and PW (Equation 11).

$$Parameter(W,L) = P0(1 + \frac{PL}{L_o} + \frac{PW}{W_o})$$

(11)

The values of P0, PL and PW for the remaining 16 parameters are added to the process file. The user supplied operating voltage, temperature, and oxide thickness when added to the other process parameters result in a 54 parameter file for any given device type on a test die location.

Process parameters are determined through analysis of the variation in the 17 CSIM model parameters with device channel length and width. The first calculation performed analyzes **BETAO** versus drawn length and drawn width (Equation 10) to determine **DELTAL** and **DELTAW**

$$BETA0 = \mu_n Cox \frac{(W_m + \Delta W)}{(L_m + \Delta L)}$$

(10)

Figures 3 and 4 show the relationships between BETAO and drawn width and drawn length that are used to determine DeltaL and DeltaW. The low field mobility, DELTAL and DELTAW are stored in the process file and are used by SPICE in determining the device gain.

Once DELTAL and DELTAW have been determined, they are used to convert all values of Mask length and width to the corresponding values of electrical channel length and width. At this point, the remaining 16 CSIM parameters are modeled versus electrical channel length and width using three parameters: PO PL, and PW (Equation 11).

Parameter

$$(W,L) = P0(1 + \frac{PL}{L_e} + \frac{PW}{W_e})$$

(11)

The values of P0. PL and PW for the remaining 16 parameters are added to the process file. The user supplied operating voltage, temperature, and oxide thickness when added to the other process parameters result in a 54 parameter file for any given device type on a test die location.

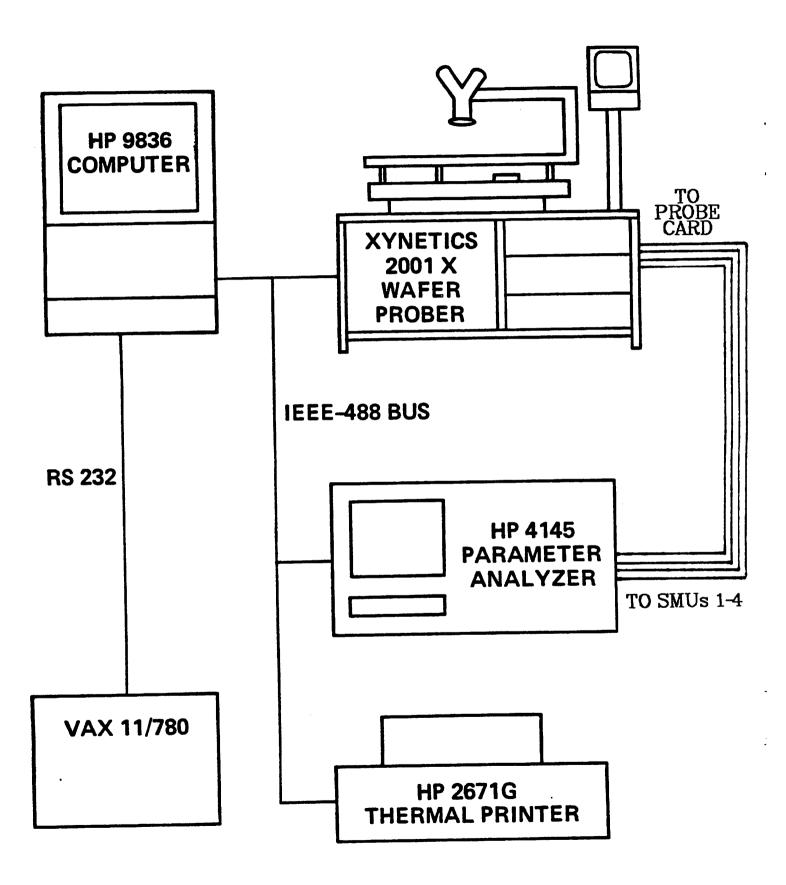

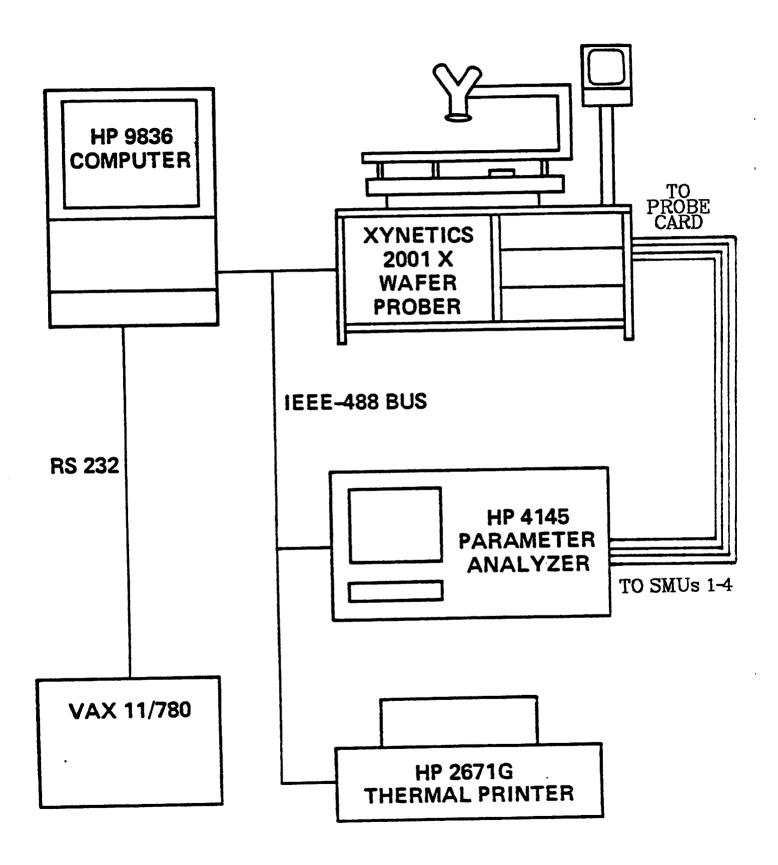

#### 3. AUTOMATIC MOS DEVICE PARAMETER EXTRACTION SYSTEM HARDWARE

The automatic parameter extraction system at Berkeley consists of five integrated elements: a Hewlett-Packard 9836 desktop computer, a Xynetics/Electroglas 2001X fully automated wafer prober, a Hewlett Packard 4145 Semiconductor Parameter Analyzer, a Hewlett Packard 2671G Graphics Thermal Printer, and a link to a network of Digital Equipment VAX 11/780 and VAX 11/750 computers (Figure 5). The elements of this system, with the exception of the VAX mainframes, are linked together with an IEEE-488 Bus. The VAX mainframes communicate with the 9836 Desktop computer over a separate RS-232 connection. For a majority of the system functions, as in the case of device measurements, the 9836 computer acts as a controller while a peripheral such as the 4145 parameter analyzer is under remote supervision.

#### 3.1. The 4145 Parameter Analyzer

All device measurements are taken with the 4145 Semiconductor Parameter Analyzer which, for the purposes of the automatic parameter extraction system, is operated in a programmable digital curve tracer fashion. Once the 9836 automatic extraction program has been given the supply voltage and device terminal connections to the 4145, all measurement setup for the 4145 and data aquisition from the 4145 is automatically controlled by the 9836. Preparing the 4145 for use with the extraction system is discussed in Appendix 1. This instrument has some limited MOS parameter extraction capabilities, and internal graphics that permit it to be used as a stand alone system for device analysis and research. Since the 4145 lacks major programming capabilities, it was not possible to exploit some of its features in developing an automatic extraction facility.

Figure 5

Figure 5

Fortunately, the 4145 is a flexible, high accuracy instrument which is ideal for measuring single transistors. It has four stimulus measurement units capable of being setup as constant or stepped voltage or current sources. These units can be programmed to set voltage levels up to 100V, or current levels from 1pA to 100mA. In addition to these four channels, two programmable voltage sources, and two voltage monitor channels are available to be used when needed for testing more complex structures. The major extraction system limitation resulting from the use of the 4145 as opposed to a more elaborate tester, lies in the fact that any test structure is limited to at most eight connections, and in some instances even less than eight are allowed.

To allow for layout flexibility, but within the constraints of the 4145 limitations, the extraction software allows any of the four required MOS device terminals to be connected to any of the four stimulus measurements. For best results this generally requires that test transistors be laid out in a regular pad arrangement. In general it is not recommended that any pads connected to device terminals be shared, as this may make fully automatic wafer probing impossible. Instructions concerning pad layout, and potential layout procedures to avoid are found in Appendix 2. A solution to these layout difficulties would be the use of a good quality programmable switching matrix. A Hewlett Packard 4062 parameter analyzer system comes with such a switching matrix, and would allow more general and extensive test structure characterization.

#### 3.2. 2001X Automatic Wafer Prober

The 2001X wafer prober in use at Berkeley is a precision programmable wafer prober with full capability for external control from the 9836 computer. As in the case of the 4145, the 2001X prober has extensive internally programmed wafer stepping and probing capabilities, many of which were not

necessary for the automatic parameter extraction project, but could find use in a number of other applications at Berkeley. The automatic prober setup, which is required prior to external control by the 9836, involves turning on the prober, initializing the prober I/O system, and aligning a wafer. This is described in Appendix 1, and takes approximately two minutes for an experienced user.

To provide for flexibility in use of the prober the parameter extraction software provides for three different modes of prober operation: fully automatic, semi-automatic, and single device. Fully automatic and semi-automatic prober operation are used to test multiple devices for the purpose of generating process files, while single device operation is organized towards model experimentation and analysis. Fully automatic or semi-automatic prober operation requires that a prober file containing such information as die size, device locations, and device sizes be stored on the 9836 computer system. Presently, any die pattern contained within a 20 by 20 square array of die, can be tested, and provisions are provided to test up to 20 total devices per die location. Both of these limits are easily expandable, but they are reasonable maximums considering the memory available on the 9836 for process file and device parameter storage. Details of the prober file organization and use are explained in Appendix 3.

The semi-automatic prober mode of operation was never intended to be used in a fully operating system, but is included as an interim solution to be used when pad layout is not compatible with system requirements. This mode of operation uses a prober file, but stops the program after steps between devices to allow the user to manually switch probe card edge connector cables which are routed to the 4145. In single device prober operation, as opposed to automatic or semi-automatic prober operation, the prober is used for the sole purpose of contacting to a device, and it does not receive any external commands.

necessary for the automatic parameter extraction project, but could find use in a number of other applications at Berkeley. The automatic prober setup, which is required prior to external control by the 9836, involves turning on the prober, initializing the prober 1/0 system, and aligning a wafer. This is described in Appendix 1, and takes approximately two minutes for an experienced user.

To provide for flexibility in use of the prober the parameter extraction software provides for three different modes of prober operation: fully automatic, semi-automatic, and single device. Fully automatic and semi-automatic prober operation are used to test multiple devices for the purpose of generating process files, while single device operation is organized towards model experimentation and analysis. Fully automatic or semi-automatic prober operation requires that a prober file containing such information as die size, device locations, and device sizes be stored on the 9836 computer system. Presently, any die pattern contained within a 20 by 20 square array of die, can be tested, and provisions are provided to test up to 20 total devices per die location. Both of these limits are easily expandable, but they are reasonable maximums considering the memory available on the 9836 for process file and device parameter storage. Details of the prober file organization and use are explained in Appendix 3.

The semi-automatic prober mode of operation was never intended to be used in a fully operating system, but is included as an interim solution to be used when pad layout is not compatible with system requirements. This mode of operation uses a prober file, but stops the program after steps between devices to allow the user to manually switch probe card edge connector cables which are routed to the 4145. In single device prober operation, as opposed to automatic or semi-automatic prober operation, the prober is used for the sole purpose of contacting to a device, and it does not receive any external commands.

#### 3.3. 2671G Thermal Printer

A 2671G thermal graphics printer provides the extraction system user with the capability of obtaining fine quality plots off the screen of the 9836. This is a preferred means of documenting measured or simulated device characteristics. The extraction system permits the user to simultaneously analyze measured and simulated characteristics, and examples of 2671G hard-copy plots for these graphs are shown in the sample execution section. The Berkeley extraction system, also has a Hewlett Packard 82905B dot matrix printer which can be used to obtain hard-copy of text such as parameter lists which appear on the 9836 screen.

## 3.4. 9836 Computer and VAX Link

The 9836 desktop computer is a Motorola 68000 based machine, and is used as the parameter extraction system controller. The Berkeley 9836 contains approximately 1.4MByte of RAM, which is useful in program development and parameter extraction system execution. Process file storage and manipulation is orders of magnitude faster if done in RAM instead of with floppy disc accesses. The amount of RAM present in a system will limit the number of devices and die which can be tested between file transfers to a VAX mainframe.

The 9836 connection to the network of VAX computers is done by using a Video Terminal Emulator Program called 'VT2' which was written by Hewlett Packard to connect the 9836 to a variety of mainframe computers. This program handles file transfers to and from the 9836, and is used to send process files to the VAX where SPICE simulations are performed.

#### 4. AUTOMATIC MOS DEVICE PARAMETER EXTRACTION SYSTEM SOFTWARE

The parameter extraction software for the 9836 desktop computer is written in Hewlett-Packard Pascal Version 2.0. Pascal was chosen due to the fact that it is faster executing and easier to modify and maintain than is BASIC. These benefits are derived due to the fact that Pascal is compiled as opposed to interpreted, and is modular in form. New versions of BASIC are slowly adapting some of the better features of Pascal, and in the future, BASIC may be a better choice for developing programs such as the one described here. Hewlett-Packard Pascal employs some procedures which are not available in Standard Pascal, but software modifications to use the entire software package on a non-Hewlett-Packard Pascal system would not be extremely difficult.

The software has been divided into six distinct sections:

parameter extraction,

device measurement control,

interactive graphics.

process file development,

automatic prober routines.

and menu and display handling.

The parameter extraction software, with the exception of continuous display updating procedure calls, is written entirely in standard Pascal, and could be transported with very little effort to any Pascal system. The other sections incorporate I/O and graphics modules that have been written by Hewlett-Packard to control its equipment. These modules would have to be simulated in software if another machine and interface setup were to be used.

## 4. AUTOMATIC MOS DEVICE PARAMETER EXTRACTION SYSTEM SOFTWARE

The parameter extraction software for the 9836 desktop computer is written in Hewlett-Packard Pascal Version 2.0. Pascal was chosen due to the fact that it is faster executing and easier to modify and maintain than is BASIC. These benefits are derived due to the fact that Pascal is compiled as opposed to interpreted, and is modular in form. New versions of BASIC are slowly adapting some of the better features of Pascal, and in the future, BASIC may be a better choice for developing programs such as the one described here. Hewlett-Packard Pascal employs some procedures which are not available in Standard Pascal, but software modifications to use the entire software package on a non-Hewlett-Packard Pascal system would not be extremely difficult.

The software has been divided into six distinct sections:

parameter extraction,

device measurement control,

interactive graphics,

process file development,

automatic prober routines,

and menu and display handling.

The parameter extraction software, with the exception of continuous display updating procedure calls, is written entirely in standard Pascal, and could be transported with very little effort to any Pascal system. The other sections incorporate I/O and graphics modules that have been written by Hewlett-Packard to control its equipment. These modules would have to be simulated in software if another machine and interface setup were to be used.

## 4.1. Parameter Extraction Routines

For the purpose of parameter extraction, the voltages and currents of a PMOS device are negated to conform to the sign convention of a NMOS transistor. From this point on, all voltage designations will refer to NMOS devices unless otherwise noted. Prior to parameter extraction, a three dimensional array of Ids currents is measured, corresponding to six Vbs, five Vgs, and four Vds voltage biases. The Vbs values are equally spaced between -Vdd and OV. The Vgs bias values are optimally determined in a threshold voltage estimation routine, and are spaced between a point exceeding the threshold and Vdd. Details of the Vgs bias determination and device measurement are described in the Device Measurement Control section. Vds biases of 0.1V and 0.2V are chosen for use in the linear region extraction, while biases of Vdd -0.5V, and Vdd are chosen for the saturation region extraction routines. These bias levels can be changed through very simple program modifications. In the case of Depletion Mode Devices these same biases are used in the saturation extraction routines where provisions have been made to handle devices which may not be operating in the saturation region.

## 4.1.1. Linear Region Extraction of Beta0x, U0x, and Vtx

The Linear Region Extraction revolves around the general equation for the trans-conductance in the linear region (Equation 12).

$$G = \frac{Ids}{Vds} = \frac{Beta \, 0x (Vgs - Vtx)}{1 + U \, 0x (Vgs - Vtx)} \tag{12}$$

Linear region extraction is performed on all combinations of *Vds* and *Vbs* biases that have been measured, to determine the parameters UOX, Vtx and BetaOx. These parameters are stored in arrays corresponding to the *Vds* and *Vbs* values used. The parameters BetaOx, Vtx and UOx include dependencies upon *Vds* bias

which can be removed once a value for a is determined. In keeping with the philosophy of not requiring the user to supply any initial parameter estimates, two routines are used to determine initial estimates for Beta0x, Vtx and U0x. These estimates are then used as inputs to the local optimization routine for the linear region.

Initial estimates for Beta0x and Vtx are determined by approximating G as a quadratic in Vgs for the smaller values of Vgs that have been measured, and by setting U0x equal to zero. A plot of G versus Vgs (Figure 6) shows that the intercept is an excellent approximation to Vtx, and the slope at the intercept is similarly an excellent approximation to Beta0x. This quadratic fit is done using a linear least square algorithm for two variables.

An initial estimate for U0x is calculated using a similar approach on a slightly modified equation. (Equation 12) In this instance U0x and Beta0x are variables, while the value of Vtx is a constant taken from the previous estimation.

$$\frac{Vgs - Vtx}{G} = \frac{1}{Beta \, 0x} + \frac{U0x}{Beta \, 0x \, (Vgs - Vtx)} \tag{13}$$

The linear least square method is employed to solve for both U0x, and Beta0x, but only the value of U0x is saved for use in the final linear region optimization.

The final values of Beta0x, U0x, and Vtx are determined through the use of Equation 14.

$$f(x) = \frac{G + G^* U 0 x^* (Vgs - Vth)}{Vgs - Vth} - Beta 0x = 0$$

$$f(X) = \Delta Beta 0x - \frac{\partial f(x)}{\partial Vtx} \Delta Vtx - \frac{\partial f(x)}{\partial U 0x} \Delta U 0x \tag{14}$$

This equation is solved at a given Vds and Vbs bias over the range of Vgs values measured. A combination linear least square algorithm with three variables, and Newton-Raphson algorithm is used. The linear least square algorithm is

which can be removed once a value for a is determined. In keeping with the philosophy of not requiring the user to supply any initial parameter estimates, two routines are used to determine initial estimates for Beta0x. Vtx and U0x. These estimates are then used as inputs to the local optimization routine for the linear region.

Initial estimates for Beta0x and Vtx are determined by approximating G as a quadratic in Vgs for the smaller values of Vgs that have been measured, and by setting U0x equal to zero. A plot of G versus Vgs (Figure 6) shows that the intercept is an excellent approximation to Vtx, and the slope at the intercept is similarly an excellent approximation to Beta0x. This quadratic fit is done using a linear least square algorithm for two variables.

An initial estimate for U0x is calculated using a similar approach on a slightly modified equation. (Equation 12) In this instance U0x and Beta0x are variables, while the value of Vtx is a constant taken from the previous estimation.

$$\frac{Vgs - Vtx}{G} = \frac{1}{Beta 0x} + \frac{U0x}{Beta 0x(Vgs - Vtx)}$$

(13)

The linear least square method is employed to solve for both U0x, and Beta0x, but only the value of U0x is saved for use in the final linear region optimization.

The final values of Beta0x, U0x, and Vtx are determined through the use of Equation 14.

$$f(x) = \frac{G + G^* U 0 x^* (Vgs - Vth)}{Vgs - Vth} - Beta 0x = 0$$

$$f(X) = \Delta Beta 0x - \frac{\partial f(x)}{\partial Vtx} \Delta Vtx - \frac{\partial f(x)}{\partial U 0x} \Delta U 0x \tag{14}$$

This equation is solved at a given Vds and Vbs bias over the range of Vgs values measured. A combination linear least square algorithm with three variables, and Newton-Raphson algorithm is used. The linear least square algorithm is

used to determine the next set of partial derivatives for the following iteration of the Newton-Raphson algorithm. At the completion of each iteration by the Newton-Raphson algorithm, a test is made to detect whether a certain level of convergence has been reached. Full convergence has been defined based on accuracy requirements, and when it is reached or if a certain limit on the number of iterations is reached, the iteration is stopped and the estimates are stored in arrays corresponding to the terminal biases. During the iteration process, U0x is not allowed to be forced negative, and if this is occurring, the value of U0x is alternatively divided by ten. In the limiting case, U0x will become 0 which matches the physical situation of no mobility reduction.

#### 4.1.2. Extraction of the Parameter 2Phif

The parameter 2Phif is a direct measure of the effective channel doping level, and its accurate derivation is essential for process analysis. The different modes of program operation utilize various methods to derive this parameter, with the highest degree of accuracy resulting from fully automatic wafer level probing. In the case of single device analysis, it is necessary for the user to specify either 2Phif or the channel doping level Na. This value should have been previously determined for a given die using the Fully Automatic or the Manual Modes of Prober operation. Using these modes, the device with the largest area and the largest minimum length or width is chosen to determine 2Phif. If multiple die are tested, further accuracy in measuring 2Phif is derived due to the fact that a better analysis of the parameter K1 has been performed.

The parameter K1 is dependent on 2Phif, temperature, oxide thickness, and device geometry. Equations 15, 16, and 17 represent the expressions for K1, the substrate doping, and the K1 geometry dependence term s respectively.

$$K1=s^*\sqrt{\frac{2^*q^*e^*Na}{Cox}}$$

(15)

$$Na = ni * e^{\frac{2Phif}{2^{\circ}k^{\circ}Temp^{\circ}q}}$$

(16)

$$s = 1 + \frac{LK1}{L_{mask} + \Delta L} + \frac{WK1}{W_{mask} + \Delta W}$$

(17)

The parameters LK1 and WK1 are the parameters derived when a process file is constructed. It is evident from the expression for s that a large Lmask and a large Wmask will result in the expression for s being approximately unity. For the first die measured on a test chip, s is set to unity, and the largest device available is used to extract 2Phif. The value of 2Phif extracted for the largest device of a given device type on a die, is used as the value of 2Phif for all other devices of the same device type on the same die. For all subsequent die, the geometry dependent terms in the expression for s are known, and can be used to derive a more accurate value of 2Phif for the largest device on the die.

The actual extraction of 2Phif involves the solution of the basic CSIM threshold voltage equation (Equation 17) over various Vbs biases at a fixed Vds value using the Newton-Raphson, Linear Least Square approach.

$$Vtx = \frac{a}{2} * Vds + (VFB - ETA * Vds) + 2Phif + K1 * \sqrt{2Phif - Vbs} - (K2) * (2Phif - Vbs) (18)$$

An analysis of the threshold equation shows that the terms a and K1 can be evaluated using the latest iteration value of 2Phif. Initially, 2Phif is set at 0.6V as a reasonable estimate. The terms VFB and ETA\*Vds will be constant over all values of Vbs, and therefore they cannot be distinguished from each other. K2 represents further, the effect on the threshold voltage due to drain induced barrier lowering. The solution of the threshold equation results in the parameters (VFB-ETA\*Vds), 2Phif, K1, and K2 which are evaluated for Vds=0.1V and Vds=0.2V.

$$Na = ni^*e^{\frac{2Pnif}{2^*k \sqrt[a]{emp^*q}}}$$

(16)

$$s = 1 + \frac{LK1}{L_{mask} + \Delta L} + \frac{WK1}{W_{mask} + \Delta W}$$

(17)

The parameters LK1 and WK1 are the parameters derived when a process file is constructed. It is evident from the expression for s that a large Lmask and a large Wmask will result in the expression for s being approximately unity. For the first die measured on a test chip, s is set to unity, and the largest device available is used to extract 2Phif. The value of 2Phif extracted for the largest device of a given device type on a die, is used as the value of 2Phif for all other devices of the same device type on the same die. For all subsequent die, the geometry dependent terms in the expression for s are known, and can be used to derive a more accurate value of 2Phif for the largest device on the die.

The actual extraction of 2Phif involves the solution of the basic CSIM threshold voltage equation (Equation 17) over various Vbs biases at a fixed Vds value using the Newton-Raphson, Linear Least Square approach.

$$Vtx = \frac{\alpha}{2} * Vds + (VFB - ETA * Vds) + 2Phif + K1 * \sqrt{2Phif - Vos} - (K2) * (2Phif - Vos) (18)$$

An analysis of the threshold equation shows that the terms a and K1 can be evaluated using the latest iteration value of 2Phif. Initially, 2Phif is set at 0.6V as a reasonable estimate. The terms VFB and ETA\*Vds will be constant over all values of Vbs, and therefore they cannot be distinguished from each other. K2 represents further, the effect on the threshold voltage due to drain induced barrier lowering. The solution of the threshold equation results in the parameters (VFB-ETA\*Vds), 2Phif, K1, and K2 which are evaluated for Vds=0.1V and Vds=0.2V.

## 4.1.3. General Linear Region Threshold Analysis and Data Reduction

With the exception of the largest device of a given device type on a die, 2Phif is not extracted. In general, VFB-ETA\*Vds, K1 and K2 are calculated using a Linear Least Square Fit to the threshold equation (Equation 19) for the range of Vbs values measured at a given Vds value.

$$Vtx - 2Phif - \frac{\alpha}{2} Vds = (VFB - ETA * Vds) + K1 * \sqrt{2Phif - Vbs} - K2 * (2Phif - Vbs)$$

(19)

Once the parameter K1 is known, it is possible to calculate the parameter a for a given Vbs bias. Knowing a, the values of U0x and Vtx can be adjusted to remove the threshold dependency on a/2\*Vds using Equations (20) and (21).

$$Vth(Vds, Vbs) = Vtx(Vds, Vbs) - \frac{a(Vds, Vbs)}{2} * Vds$$

(20)

$$U0(Vds, Vbs) = \frac{U0x(Vds, Vbs)}{1 - U0x(Vds, Vbs) * \frac{a(Vds, Vbs)}{2} * Vds}$$

(21)

U0 and X2U0 (Equation 21) are derived using a linear least square algorithm to model the Vbs and Vds dependencies of U0. The parameter X3U0 is not saved as a CSIM parameter, but is used to determine the values of U0(Vds, Vbs) in the limit of Vds=0.

$$U0(Vds, Vbs) = U0 + X2U0*Vbs + X3U0*Vds$$

(22)

VFB, 2Phif, K1 and K2 are determined in Equations (23) to (26) using the values for Vds=0.1V and Vds=0.2V as the inputs to a Linear Least Square algorithm with two variables.

$$VFB(Vds) = VFB + (discarded\ term) * Vds$$

(23)

$$2Phif(Vds)=2Phif+(discarded\ term)*Vds$$

(24)

$$K1(Vds)=K1+(discarded\ term)*Vds$$

(25)

$$K2(Vds)=K2+(discarded\ term)*Vds$$

(26)

In summary, the threshold parameters are determined by requiring that the term a be explicitly included in the linear region parameters, allowing those parameters to be extrapolated to Vds=0. This allows the parameters VFB, K1, K2, 2Phif U0 and X2U0 to be extracted without the use of any approximation relating to measurements employing finite values of Vds.

## 4.1.4. Saturation Region Extraction of Beta0sat, Vthsat and U1sat

The Ids currents measured corresponding to Vds=Vdd and Vds=Vdd-0.5V are used to determine Beta0sat, Vthsat and U1sat as functions of Vds and Vbs. A combination Newton-Raphson algorithm, Linear Least Square algorithm is used to solve Equation (27) at each Vds and Vbs bias.

$$Ids_{meas} - Ids_{sim} = \frac{\partial Ids_{sim}}{\partial Beta \, 0sat} * \Delta Beta \, 0sat + \frac{\partial Ids_{sim}}{\partial V thsat} * \Delta V thsat + \frac{\partial Ids_{sim}}{\partial \, U \, 1sat} * \Delta U \, 1sat \, (27)$$

The initial estimate for Beta0sat is set to be the value of Beta0 at the same Vbs bias but with Vds=0.2V as was determined in the Linear Region Extraction. Vthsat can be determined initially from the values of VFB, Phif2, K1, and K2 that are known from the Linear Region Extraction, while U1 is initially approximated as zero.

As previously mentioned, depletion mode MOS devices may not be operating in the saturation region, and this required program modification. It has to be determined whether a device is in saturation or linear operation and this is done by evaluating Equation (3) and comparing Vdssat to the Vds bias. Analytical expressions for the derivatives in Equation (27), and the equation for Ids are selected based on saturation or linear region operation.

If the value of U1 is driven negative while the optimization is being performed, the value is divided by 10 and the optimization continues. In the limit, this reflects the case where there is no velocity saturation. If U1 is equal to zero In summary, the threshold parameters are determined by requiring that the term a be explicitly included in the linear region parameters, allowing those parameters to be extrapolated to Vds=0. This allows the parameters VFB, K1, K2, 2Phif U0 and X2U0 to be extracted without the use of any approximation relating to measurements employing finite values of Vds.

## 4.1.4. Saturation Region Extraction of Beta0sat, Vthsat and U1sat

The Ids currents measured corresponding to Vds=Vdd and Vds=Vdd-0.5V are used to determine Beta0sat, Vthsat and U1sat as functions of Vds and Vbs. A combination Newton-Raphson algorithm, Linear Least Square algorithm is used to solve Equation (27) at each Vds and Vbs bias.

$$Ids_{meas} - Ids_{sim} = \frac{\partial Ids_{sim}}{\partial Beta \, 0sat} + \frac{\partial Ids_{sim}}{\partial V hsat} + \frac{\partial Ids_{sim}}{\partial V hsat} + \frac{\partial Ids_{sim}}{\partial U \, 1sat} + \Delta U \, 1sat \, (27)$$

The initial estimate for BetaOsat is set to be the value of BetaO at the same Vbs bias but with Vds=0.2V as was determined in the Linear Region Extraction. Vthsat can be determined initially from the values of VFB, Phif2, K1, and K2 that are known from the Linear Region Extraction, while U1 is initially approximated as zero.

As previously mentioned, depletion mode MOS devices may not be operating in the saturation region, and this required program modification. It has to be determined whether a device is in saturation or linear operation and this is done by evaluating Equation (3) and comparing *Vdssat* to the *Vds* bias. Analytical expressions for the derivatives in Equation (27), and the equation for *Ids* are selected based on saturation or linear region operation.

If the value of U1 is driven negative while the optimization is being performed, the value is divided by 10 and the optimization continues. In the limit, this reflects the case where there is no velocity saturation. If U1 is equal to zero

when the saturation region extraction converges, a special routine to handle this condition is executed. This is necessary, because the values of Beta0sat and Vthsat may not be optimal, and is done by simplifying Equation (27) through eliminating the U1 terms and U1 derivatives. Equation (27) is then resolved with a Newton-Raphson/Linear Least Square algorithm to determine more optimal values for Beta0sat and Vthsat. Beta0sat, Vthsat, and U1sat are all determined over the range of Vbs biases, and the saturation region Vds biases. The parameter Vthsat is used to determine the entries for the array ETA[Vds,Vbs] in the saturation region, through the use of Equation (28).

$$ETA[Vds,Vbs] = \frac{(VFB + 2Phif + K1*\sqrt{2Phif - Vbs} - K2*(2Phif - Vbs)) - Vthsat}{Vds}$$

(28)

## 4.1.5. Saturation Region Data Reduction

For parameters such as Beta0sat, U1 and ETA which are of much greater significance for Vds values in the proximity of Vdd, it is preferred to extract the parameters Vds dependence to Vdd as Vds=0V. The U1 data array is modeled by this means (Equation 29) and it has been experimentally determined that the Vds dependency can be sufficient enough to warrant the inclusion of the parameter X3U1 in the CSIM model.

$$U1[Vds, Vbs] = U1 + X2U1*Vbs + X3U1*(Vdd - Vds)$$

(29)

The threshold drain induced barrier lowering term, ETA, is modeled with both Vds and (Phif2-Vbs) dependency. Since this term is insignificant at low Vds biases, only the saturation region extracted values for ETA[Vds,Vbs] are used to to determine ETA, X2ETA and X3ETA as is shown in Equation (30).

$$ETA[Vds,Vbs] = ETA + X2ETA^*(Phif 2-Vbs) + X3ETA^*(Vds-Vdd)$$

(30)

## CSIM PARAMETER EXTRACTION FLOWCHART

DETERMINE USING OPTIMIZATION BETA $\phi$ X(Vds, Vbs) VTX (Vds, Vbs) AND U $\phi$ X (Vds, Vbs) OVER LINEAR REGION Vds VALUES AND ALL Vbs VALUES

LINEAR REGION ANALYSIS EXTRACT: PHIF2 (V<sub>ds</sub>), KI (V<sub>ds</sub>)

VFB (V<sub>ds</sub>), AND K2 (V<sub>ds</sub>)

FROM VTX (V<sub>BS</sub>) AT

CONSTANT V<sub>ds</sub> VALUES

REDUCE ALL ARRAYS TO V<sub>ds</sub> = 0 VOLT VALUES

EXTRACT PHIF2, KI, VFB, K2, U $\phi$ , AND X2U $\phi$

DETERMINE USING OPTIMIZATION BETA $\phi$ SAT ( $V_{ds}$ ,  $V_{bs}$ ) VTHSAT ( $V_{ds}$ ,  $V_{bs}$ ) UISAT ( $V_{ds}$ ,  $V_{bs}$ ) OVER SATURATION REGION  $V_{ds}$  VALUES AND ALL VBS VALUES

SATURATION REGION ANALYSIS

DEVELOP ETA ARRAY FOR SATURATION VALUES MODEL BETA $\phi$ SAT, ETA AND UI AT  $V_{ds} = V_{dd}$

INCLUDE EFFECT OF UI ON BETA  $\phi$

MODEL BETA AS A PARABOLA VERSUS VDS

**END OF EXTRACTION**(

## CSIM PARAMETER EXTRACTION FLOWCHART

DETERMINE USING OPTIMIZATION BETA $\phi$ X(V<sub>ds</sub>, V<sub>bs</sub>) VTX (V<sub>ds</sub>, V<sub>bs</sub>) AND U $\phi$ X (V<sub>ds</sub>, V<sub>bs</sub>) OVER LINEAR REGION V<sub>ds</sub> VALUES AND ALL V<sub>bs</sub> VALUES

LINEAR REGION ANALYSIS EXTRACT: PHIF2 (V<sub>ds</sub>), KI (V<sub>ds</sub>)

VFB (V<sub>ds</sub>), AND K2 (V<sub>ds</sub>)

FROM VTX (V<sub>BS</sub>) AT

CONSTANT V<sub>ds</sub> VALUES

REDUCE ALL ARRAYS TO V<sub>ds</sub> = 0 VOLT VALUES

EXTRACT PHIF2, KI, VFB, K2, Uφ, AND X2Uφ

DETERMINE USING OPTIMIZATION BETA $\phi$ SAT ( $V_{ds}$ ,  $V_{bs}$ ) VTHSAT ( $V_{ds}$ ,  $V_{bs}$ ) UISAT ( $V_{ds}$ ,  $V_{bs}$ ) OVER SATURATION REGION  $V_{ds}$  VALUES AND ALL VBS VALUES

SATURATION REGION ANALYSIS

DEVELOP ETA ARRAY FOR SATURATION VALUES MODEL BETA $\phi$ SAT, ETA AND UI AT  $V_{ds}$  =  $V_{dd}$

INCLUDE EFFECT OF UI ON BETA¢

MODEL BETA AS A PARABOLA VERSUS VDS

**END OF EXTRACTION (**

A final data manipulation for both the array of Beta0[Vds,Vbs] and Beta0sat[Vds,Vbs] is necessary to remove the effects of U1 on these parameters as they were extracted.

$$Beta[Vds, Vbs] = Beta[Vds, Vbs] * (1 + (U1 + X2U1 * Vbs) * Vds)$$

(31)

Once this is complete, the Beta0 array is modeled as in Equation (32) and the Beta0sat array is modeled as in Equation (33).

Beta 0 [Vds, Vbs] = BETA 0 SAT + X2BETA 0 \* Vbs + (discarded term) \* Vds (32)

Beta 0 sat [Vds, Vbs] = BETA 0 SAT + X2BETA 0 SAT \* Vbs + X3BETA 0 SAT \* (Vds - Vdd()33)

## 4.2. Device Measurement Software

For the purpose of automatic parameter extraction, it is important to have the capability to detect those devices which are affected by any one of a variety of error conditions. Such a procedure can save valuable testing time, and helps to eliminate the possibility that parameter extraction will be attempted on devices exhibiting anomalous electrical behavior. The program described here employs the user specified supply voltage for the purpose of setting up the 4145 to obtain an accurate analysis of a device over its expected operating range. Prior to parameter extraction, independent 4145 measurement setups are used to: check for error conditions, determine device functionality, and establish the measurement data base necessary for the extraction software.

## 4.2.1. Device Type Measurement

The initial 4145 measurement setup analyzes the source-body and drain-body junctions, and checks for gate to terminal shorts (TABLE 1).

| TABLE 1 Device Type Measurement Setup |              |  |

|---------------------------------------|--------------|--|

| Terminal                              | Voltage      |  |

| Drain                                 | 0.0V         |  |

| Source                                | 0.0V         |  |

| Gate                                  | Vdd          |  |

| Body                                  | -Vdd and Vdd |  |

In the process of verifying that the source-body and drain-body junctions are present and are not shorted, the program uses the polarity of the junctions to determine whether a NMOS or a PMOS device is present. By setting the gate potential at a distant level from the potentials of the source, drain or bulk, and by measuring the gate current, a short to one of the other terminals can be detected. The program definitions for tolerable junction and gate leakage currents (TABLE 2) are not dependent on device geometry. They have been set for the purpose of detecting obvious shorts and are presently not intended for screening junction or gate leakage currents. In the case of either gate or junction leakage currents, the noise affecting the measurement setup may be significantly greater than the actual leakage current, depending upon the type of cables and connections used.

| TABLE 1 Device Type Measurement Setup |              |  |

|---------------------------------------|--------------|--|

| Terminal                              | Voltage      |  |

| Drain                                 | 0.0V         |  |

| Source                                | 0.0V         |  |

| Gate                                  | Vdd          |  |

| Body                                  | -Vdd and Vdd |  |

In the process of verifying that the source-body and drain-body junctions are present and are not shorted, the program uses the polarity of the junctions to determine whether a NMOS or a PMOS device is present. By setting the gate potential at a distant level from the potentials of the source, drain or bulk, and by measuring the gate current, a short to one of the other terminals can be detected. The program definitions for tolerable junction and gate leakage currents (TABLE 2) are not dependent on device geometry. They have been set for the purpose of detecting obvious shorts and are presently not intended for screening junction or gate leakage currents. In the case of either gate or junction leakage currents, the noise affecting the measurement setup may be significantly greater than the actual leakage current, depending upon the type of cables and connections used.

| TABLE 2 Device Type Measurement Results                |                            |  |

|--------------------------------------------------------|----------------------------|--|

| Condition                                              | Message                    |  |

| Igate>0.1uA                                            | ERROR **Gate Short**       |  |

| abs(Ibody)>10uA for both Vbs=Vdd and Vbs=-Vdd          | ERROR **Shorted Junction** |  |

| abs(Ibody)<10uA for both Vbs=Vdd and Vbs=-Vdd          | ERROR **No Junction**      |  |

| None of the above errors, and Ibody>10uA for Vbs=Vdd   | DEVICE=NCHANNEL            |  |

| None of the above errors, and Ibody<-10uA for Vbs=-Vdd | DEVICE=PCHANNEL            |  |

## 4.2.2. Device Functionality Verification