# Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# COMPACT SHORT-CHANNEL IGFET MODEL (CSIM) And A COMPACT IGFET CHARGE MODEL

by

B. J. Sheu, D. L. Scharfetter and H. C. Poon *And* B. J. Sheu, D. L. Scharfetter, C. Hu and D. O. Pederson

Memorandum No. UCB/ERL M84/20

12 March 1984

Couci

# COMPACT SHORT-CHANNEL IGFET MODEL (CSIM)

by

B. J. Sheu, D. L. Scharfetter and H. C. Poon

AND

A COMPACT IGFET CHARGE MODEL

by

B. J. Sheu, D. L. Scharfetter, C. Hu and D. O. Pederson

Memorandum No. UCB/ERL M84/20 12 March 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

### Compact Short-Channel IGFET Model (CSIM)

Bing J. Sheu, Don L. Scharfetter

Department of Electrical Engineering and Computer Sciences and Electronics Research Laboratory University of California, Berkeley CA 94720

H. C. Poon

AT&T Bell Laboratories Allentown, PA 18103

#### ABSTRACT

The Compact Short-Channel IGFET Model (CSIM), described in this report, was especially formulated to have four important features: First, it is derived from basic device physics, and therefore characterizations can provide a link to process understanding and control. Second, it is compact and therefore suitable for incorporation in computer-aided circuit simulation programs. Third, it is hierarchical, where the lower levels are analogous to the Ebers-Moll to Gummel-Poon hierarchy established for bipolar models. However, at the highest level, model parameter values are extractable from measurements in a fully automated fashion. This important characteristic allows state-of- the-art processes to be characterized, for circuit design applications, without detailed analytical models of any higher-order device physics effects. In affect, a lower-order device physics model, with tabled entries for appropriate model parameters is employed to achieve accuracy, when the device physics understanding and modeling lags the process evolution. Fourth, the automated characterization applies to devices of various sizes, which results in an associated set of process models, formulated as a standard process file. The process file can be combined with appropriate mask dimensions, to calculate the set of electrical parameters for a particular device size within a circuit simulation program. This new model coupled with its inherent autocharacterization characteristics and immediate applicability to new processess, can form the basis for a standard interface between IC process facilities and integrated circuit designers.

This work was supported in part by Semiconductor Research Corporation.

#### LIST OF SYMBOLS

conductance degradation coefficient oxide capacitance per unit area process compensation of device length/width Eczi critical field for velocity saturation I<sub>DS</sub> coefficient of average body effect on drain current drain current Ideat K1 K2 L LD LM NB drain current at saturation region body effect coefficient of Vth with short- and narrow- channel effects source/drain depletion charge sharing effect coefficient channel length lateral diffusion of source and drain junctions masked channel length substrate doping concentration N\_ surface state density  $\mathbf{n}_1$ intrinsic carrier concentration q T<sub>ox</sub> electronic charge oxide thickness  $U_0$ mobility degradation coefficient  $U_{0B}$ sensitivity of Un to substrate bias Unz Uo at zero substrate bias U<sub>1</sub> U<sub>1</sub>B velocity saturation coefficient sensitivity of U1 to substrate bias  $U_{1D}$ sensitivity of U1 to drain-source voltage, at VDS=VDD U<sub>1Z</sub> V<sub>BS</sub> U<sub>1</sub> at zero substrate bias substrate-source voltage  $V_{DS}$ drain-source voltage VDSAT saturation voltage VPB flat-band voltage  $V_{GB}$ gate-substrate voltage Vas gate-source voltage  $V_{\mathbf{th}}$ threshold voltage Vω threshold voltage for  $V_{BS} \& V_{DS} = 0$ W channel width WM masked channel width B conductance coefficient βo intrinsic conductance coefficient  $\beta_{\rm Z}$  $\beta_0$  at zero substrate and drain-source biases  $\beta_{ZB}$ sensitivity of  $\beta_0$  to substrate bias at  $V_{DS} = 0$ βs  $\beta_0$  at zero substrate bias and  $V_{DS} = V_{DD}$  $\beta_{SB}$ sensitivity of  $\beta_0$  to substrate bias at  $V_{DS} = V_{DD}$ sensitivity of  $\beta_0$  to drain-source bias at  $V_{DS} = V_{DD}$  $\beta_{\text{3D}}$ intrinsic surface mobility  $\mu_{n0}$ surface potential at strong inversion **P**S gate to semiconductor work function Ø me drain-induced barrier lowering coefficient 77 mat zero substrate bias and VDD VZ. sensitivity of  $\eta$  to substrate bias 77B pensitivity of  $\eta$  to drain-source voltage TD

### L Introduction

With the current rapid development of high performance MOS IC technology, the minimum feature size has advanced from  $10\mu$ m in production in 1971 to  $2.5\mu$ m in 1981 [1]. The process of device shrinkage is continuing and is expected to result in a minimum feature size in the submicron domain, in the late 1980's. This continuous reduction in minimum feature size makes possible the explosive growth in the scale of circuit integration, and 1,000,000 transistor chips may become the norm in the future.

The purpose of the work reported herein is the development of an MOS transistor model, which will be the cornerstone of a facility for process-oriented circuit design, applicable over this period. This facility include a fully automated process characterization system and an IC process-oriented version of SPICE circuit simulation program. These latter efforts are described elsewhere [2][3]. The process-oriented simulator accepts the process file produced by the auto-characterization system. Designers need only describe the layout geometries of devices and parasitic elements, to execute process-oriented circuit simulations.

Many articles on IGFET modeling have appeared in the literature [4]-[13] and efforts to model ever smaller and more complex IGFET devices continue at a rapid pace. We begin by discussing the zero-order model, used in the early pMOS circuit simulation, where

$$I_{DS} = \beta_0 (V_{GS} - V_t - \frac{V_{DS}}{2}) V_{DS}$$

(1)

below saturation and

$$I_{DS} = \frac{100}{2} (V_{CS} - V_t)^2$$

(2)

above saturation, and here the threshold voltage  $V_t$  is a constant. Saturation occurs when sufficient drain-source votage  $(V_{DSAT})$  is applied to pinch off the

channel at the drain,  $V_{DSAT} = V_{CS} - V_t$ .

The zero-order model neglects a fundamental effect, which is the consequence of finite resistivity of the substrate. This bulk-doping or body effect acts as a back gate. That is, after the channel (in an n-channel device) is established, an "n-p" junction is formed at the back side of the channel. The p value is, of course, the substrate doping.

As a current flows in the channel, the "I-R" drop in effect induces a reverse bias across this n-p junction. The depletion region charge associated with this back gate must be accounted for according to Gauss Law. The result is a charge term varying as the square root of potential, which, when integrated along the channel from the source to drain, with potential as the running variable, leads to the following first-order model [2]:

$$I_{DS} = \beta_0 \left[ (V_{GS} - \varphi_S - V_{FB}) V_{DS} - \frac{V_{DS}^2}{2} - \frac{2\sqrt{2q\epsilon_{st}N_B}}{3C_{ox}} \right]$$

$$* \left[ (V_{DS} + \varphi_S - V_{BS})^{\frac{3}{2}} - (\varphi_S - V_{BS})^{\frac{3}{2}} \right]$$

(3)

The 3/2 power terms result from the integration of the square root dependent bulk-doping effect evaluated at the two limits of the integration. Furthermore, the threshold voltage (the value at which the above expression yields current) is

$$V_{t} = V_{to} + \frac{\sqrt{2 q z_{ai} N_{B}}}{C_{ox}} \left[ \sqrt{\varphi_{S} - V_{BS}} - \sqrt{\varphi_{S}} \right]$$

(4)

where  $V_{t0}$  is the threshold voltage for zero substrate bias.

The expression for the saturation voltage  $V_{DSAT}$  for this first-order model is quite complex but is very simply defined. One differentiates the expression for  $I_{DS}$  with respect to  $V_{DS}$ ; sets this to zero and solves for the resulting values of  $V_{DS}$  ( $V_{DSAT}$ ) and  $I_{DS}$  ( $I_{DSAT}$ ). For values of  $V_{DS}$  greater than this,  $I_{DS}$  is constant (saturated) at the value  $I_{DSAT}$ .

For many years the first-order theory was quite adquate for accurate IC design. Problems began appearing as more and more two-dimensional effects had to be taken into account for small size transistors.

A new approach, suitable for design, is the direct utilization of I-V tables for circuit simulation models [14]. This at first sounds attractive, but suffers from several fundamental problems. First, it is highly desirable to be able to evolve the proper device sizes while evolving the design. The direct table look-up approach assumes the number of device sizes to be employed in a design is known and small and I-V curves are available. Second, interpolation between points assumes noise-free and glitch-free data, neither of which can be guaranteed. Third, relatively little feedback to process and device engineers results from this approach. This point is very important when considering the level of characterization necessary to support a high performance MOS process.

The electrical characterization of IC processes must serve two areas, the process area and the design area. It is desirable that the chosen modeling and parameterization be suitable for both. The reason for this is to avoid the undesirable consequence of having two separate approaches which leads to potential confusion and resulting serious mistakes. The approach proposed in this paper is to characterize devices of different sizes and reduce this data to a device size independent set of process parameters. This "process file" provides feedback for control of the process. For circuit simulations, the process file is combined with the appropriate mask dimensions and the device electrical model parameters calculated in a simple front-end section of code. The new MOS device model, described in this paper, was especially constructed to meet the above criterion. It is accurate yet relatively simple. It relates to the fabrication process yet is especially suitable for circuit design. And finally, it lends itself to fully automatic characterization (extraction of the parameter values for the process file) from conventional I-V measurements. Such a model is referred to

as suitable for the support of Process-Oriented IC Design.

A process-oriented short-channel IGFET model is presented in this paper. This model builds upon an extended form of the Bell Labs CSIM (Compact Short-channel IGFET Model) [15]-[18]. The extensions include a term in the threshold voltage expression which accounts for the effects of depletion charge sharing by the source and drain [19], and incorporation of the effects resulting from a continuous velocity saturation characteristic. It is also extended to include the case of an ion-implanted channel device where a steplike profile for the impurity distribution is assumed. This profile proves to be adequate for the shallow implanted layers commonly encountered in modern IC technology.

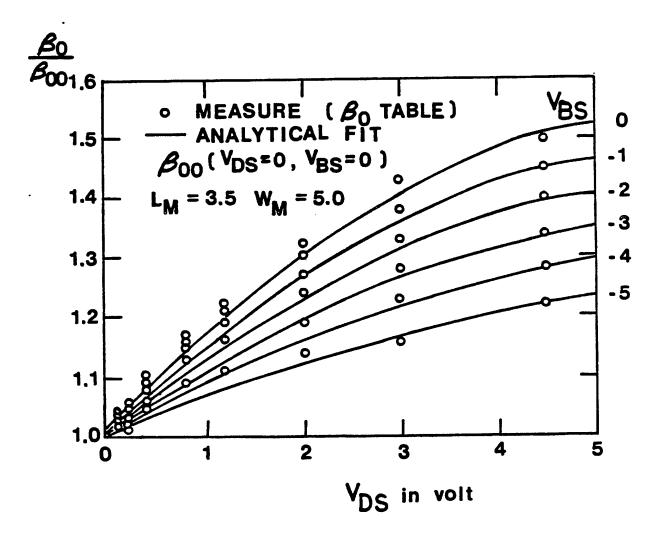

In practice, it is found that some electrical parameters have dependence on drain-source (VDS) and substrate-source (VDS) applied voltages. Details of the formulaton will be given later, but at this stage the concept of table structured model coefficients is introduced. A simple illustration is given by the representation of  $\beta_0$ , from Eq.(1), as a table of entries, with a different entry for each applied value of  $V_{DS}$  and  $V_{BS}$ . The coefficient  $\beta_0$  becomes a 2-D table  $[V_{DS}, V_{BS}]$ . The  $V_{GS}$  dependence is represented by an analytical formula, for example Eq.(1), while accuracy inherent in full 3-D  $(V_{DS}, V_{BS}, V_{GS})$  table look-up model is obtained by a 2-D table,  $(\beta_0[V_{DS}, V_{BS}])$ , for the coefficient of the analytical formulation. Regional extraction is employed to obtain coefficient values (table entries) for parameters assured strictly constant in other models. In some cases the 2-D table is reduced to a 1-D one. For example, mobility is characterized in the limit as VDs approaches zero, while velocity saturation (for suitably shortchannel devices) is characterized as VDs approaches the VDD value for the process. In this way, the 2-D table formulation for some coefficients are reduced to an empirical analytical form, generally depending only on VBS.

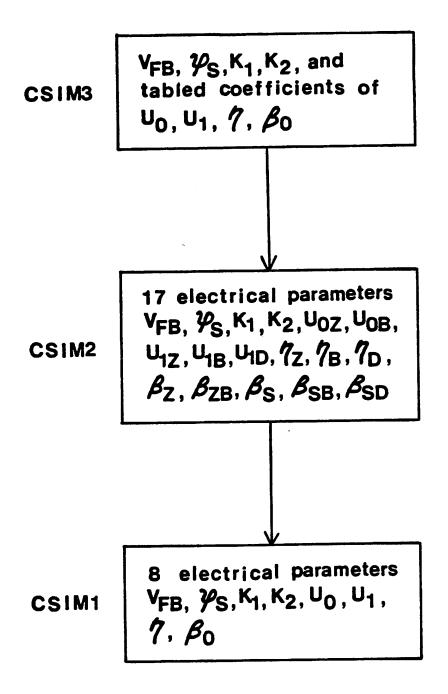

The extended CSIM has 8 electrical model parameters, four of which are found to have some bias (V<sub>DS</sub> and V<sub>DS</sub>) dependencies. In the process of examining the characteristics of a wide variety of p- and n-channel devices, ranging to sub-micron effective dimensions, an analytical representation with 17 electrical model parameters, per device size, evolved as the model CSIM2, reported herein.

The short-channel drain current model, with equations as simple as the zero-order model, is proposed in section II. Section III describes the 8 electrical parameters and their relationships with the process parameters. The characteristics of the 8 electrical parameters are analyzed and an extension to a 17 electrical parameter model is developed in section IV. Section V addresses the issue of combining design information (layout) with the process file information to generate the linked list of required electrical model parameters for accurate process-oriented circuit analysis. In section VI, comparison between simulated and measured data confirms the validity of the model. Conclusions are stated in section VII.

### II. CSIM1 Model

The CSIM model evolved from an effort to describe compactly and accurately the characteristics of short-channel insulated gate field effect transistors (IGFET's) for efficient utilization in circuit analysis programs and also to directly relate these electrical (device) model parameters with process (the process file) parameters via a parameter calculator. An important additional aspect of the work is a technique of extracting values of the electrical (device) and process parameters from measurements on test structures.

The original CSIM model, called CSIMO, is defined by 8 model parameters [17,20]: the intrinsic conductance coefficient  $\beta_0$ , the flat-band voltage  $V_{FB}$ , the surface inversion potential  $\varphi_S$ , the body effect coefficient  $K_1$ , the source/drain

depletion charge sharing effect coefficient  $K_2$ , the mobility degradation coefficient  $U_0$ , the velocity saturation coefficient  $U_1$ , and the drain-induced barrier lowering coefficient  $\eta$ .

In this work, we rederive this model as CSIM1. The detailed derivation is described in the appendix. The drain current equations are as follows:  $\text{Cut-off Region [V_{GS} < V_{th}]},$

$$I_{DS}=0. (5)$$

Triode Region [ $V_{GS} > V_{th}$  and  $0 < V_{DS} < V_{DSAT}$ ],

$$I_{DS} = \frac{\beta}{(1 + U_1 \cdot V_{DS})} \left[ (V_{CS} - V_{th}) V_{DS} - \frac{a}{2} V_{DS}^2 \right]$$

(6)

where

$$\beta = \frac{\beta_0}{1 + U_0 \left( V_{CS} - V_{th} \right)}$$

(7)

Saturation Region [ $V_{CS} > V_{th}$  and  $V_{DS} > V_{DSAT}$ ],

$$I_{DS} = \frac{\beta (V_{GS} - V_{th})^2}{2aK} \tag{8}$$

where

$$K = \frac{1 + v_c + \sqrt{1 + 2v_c}}{2}$$

,  $v_c = \frac{U_1(V_{GS} - V_{th})}{a}$

and

$$V_{DSAT} = \frac{V_{GS} - V_{th}}{a\sqrt{K}}$$

(9)

The conductance coefficient  $\beta$ , conductance-degradation coefficient a, and threshold voltage  $V_{th}$ , which models small-geometry effects, are functions of bias. Additional detail on the derivation of CSIM1 model can be found in the appendix.

### III. Characteristics of the Model Parameters

Electrical characteristics are controlled by the values of 8 electrical model parameters, for a particular (coded) device size (channel width, W and length, W). The first 5 electrical parameters, which model the threshold voltage, are extracted from electrical measurements of the threshold voltage,  $V_{th}$ .

$$V_{th} = V_{FB} + \varphi_S + K_1 \sqrt{\varphi_S - V_{BS}} - K_2 (\varphi_S - V_{BS}) - \eta V_{DS}$$

$$V_{FB} \text{ is related to processing by}$$

(10)

$$V_{FB} = \varphi_{ms} - \frac{q N_{ss}}{C_{ox}} \tag{11}$$

₽s is related to processing by

$$\varphi_{S} = 2 \frac{kT}{q} \ln \left( \frac{N_{B}}{n_{i}} \right) \tag{12}$$

For the case of an ion-implanted channel device, an effective  $\varphi_S$  corresponding to a step doping profile [21] is used.

K1 is related to processing by

$$K_{i} = \frac{\sqrt{2q \, \epsilon_{si} \, N_{B}}}{C_{cor}} \tag{13}$$

The physical effect modeled by this term is the bulk doping (back-gate bias) effect.

The physical effect modeled by  $K_2$  and  $\eta$  is the terminated depletion charges by electrical field lines starting from the source and drain. This effect is equivalent to effectively lowering the dopant concentration and is in general a function of channel length L. A group of analytical models which predict the reduction in the threshold voltage compared to the long-channel value assume geometric form for the source and drain depletion regions and how they merge with the gate-induced depletion region. While this approach is helpful for estimates of parametric behavior, it has limited validity to device design because it depends on the assumed geometry for the depletion regions. Ratnakumar, et al [19] developed a short-channel threshold voltage model based on an analytical solution to the two-dimensional Poisson equation in the depletion region of an MOS transistor. This threshold voltage lowering effect for short-channel devices is modeled by parameter  $K_2$  and  $\eta$  in the CSIM model.

$\eta$  is extracted from electrical measurements of threshold voltage and is related to processing approximately by

$$\eta = \eta_0 + \eta_n \frac{T_{ox}}{L} \tag{14}$$

where  $\eta_0$  is a small empirical parameter, whereas  $\eta_n$  is approximately  $\frac{\mathcal{E}_{\text{ext}}}{\pi \, \mathcal{E}_{\text{ext}}}$ . The physical origin of this term is similar to the  $K_2$  effect. For short-channel devices, as  $V_{DS}$  is increased the associated two-dimensional drain-induced field lines terminate on charges in the channel region and, indeed, induce additional charges. This results in finite output conductance in the saturation region or alternately, a reduction in threshold voltage with increasing  $V_{DS}$ .

The last 3 electrical parameters model the drain current. The effective conductance coefficient  $\beta$  is defined by

$$\beta = \frac{\beta_0}{1 + U_0 (V_{GS} - V_{th})}$$

(15)

$\beta_0$  is extracted from electrical measurements and has the classical form  $\beta_0 = \mu_n C_{ox} \frac{W}{L}$ , where  $\mu_n$  is the low field electron mobility in an inverted IGFET channel.

U<sub>0</sub> is an extracted parameter. It models the degradation of channel mobility with increases in gate-source voltage above threshold. The two components modeled are associated with the vertical and horizontal components of the electrical field.

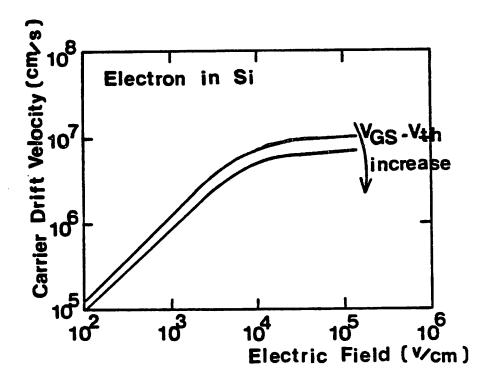

As devices are scaled to smaller dimensions, without an associated reduction in supply voltages, short-channel characteristics become dominated by carrier saturation effects. The consequence is a reduction in saturation current and a linear rather than a square dependence on  $(V_{GS}-V_{th})$ . In the extended CSIM model, the dependence of carrier velocity on horizontal electrical field takes the form

$$v = \mu_n E_y = \frac{\mu_{n0} E_y}{\left[1 + \frac{E_y}{E_{crit}}\right]}$$

(18)

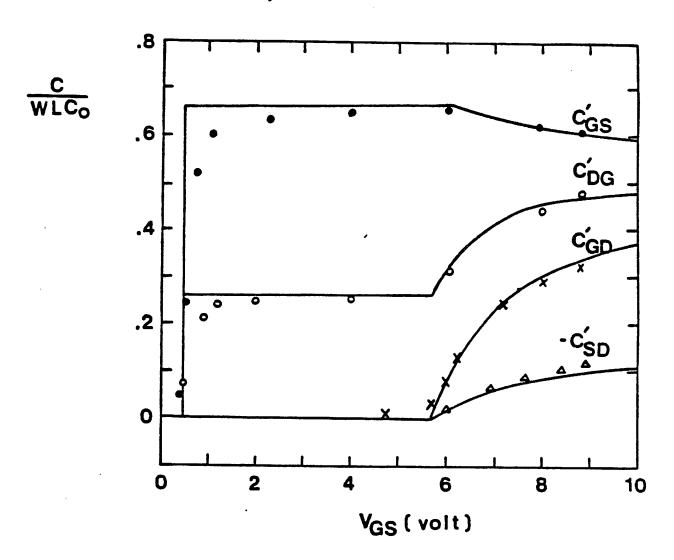

where  $E_{crit} = v_{sat}/\mu_{n0}$ . Fig.1 shows the velocity versus electric field charateristic [22]. The velocity saturation coefficient  $U_1$  is defined by

$$U_1 = \frac{1}{E_{\text{cut}} L} \tag{17}$$

This model, which is referred to as CSIM1, contains eight electrical parameters. However, four of the parameters strictly model the threshold voltage characteristic is a function of back-gate bias ,V<sub>BS</sub>, at zero drain-source voltage, V<sub>DS</sub>. The other four parameters are truly constants only in a theoretical sense.

# IV. Extension of the 8 Electrical Parameter CSIM1 Model to the 17 Electrical Parameter CSIM2 Model

The generalization of CSIM1 to one of tabled model coefficients is referred to as CSIM3. The reduction of these table to a form suitable for efficient circuit simulation is referred to as CSIM2. Fig.2 shows the hierarchy of CSIM-1, 2, and 3. The rationale for this is described below.

Device physics models suitable for integrated circuit design, evolve behind the IC process. This pattern has persisted for many years and is expected to continue indefinitely. The merchant semiconductor companies cope with this condition by close coupling of their process and circuit development teams. In the future this mode of new product development will become increasingly supplemented by what is referred to as design into silicon foundries. This creates a new pressure upon device model generation. We are approaching a period of rapid growth in applications and utilization of IC processes by a rapidly growing number of non-traditional designers. Competition in the market place will force a significant number to seek to employ relatively recent IC process generations, where adquate models are lacking for accurate circuit simulation. In many

cases the designer is not directly affiliated with the organization providing the process fabrication, greatly increasing the likelihood of incomplete or misinterpreted characterization information. The result is less than optimal exploitation in a timely fashion of the industries evolving capabilities.

The CSIM models proposed in this paper were developed specially to attack this problem by development of a fully automated MOS device characterization facility, which generates table-look-up models for device parameters, if the new process has evolved beyond the adequacy of the current models. This is similar to the direct utilization of I-V tables for circuit simulation models [12], but differs in that the analytical form of the model is still retained and exploited, and a table-look-up is only resorted to if necessary. Furthermore the tables are not current  $I_{DS}(V_{DS}, V_{BS}, V_{CS})$ , i.e. three dimensional, but are of model parameters, and are two dimensional, i.e.  $\beta_0(V_{DS}, V_{BS})$ . This greatly reduces the amount of data required to characterize a MOS process over a wide range of device sizes.

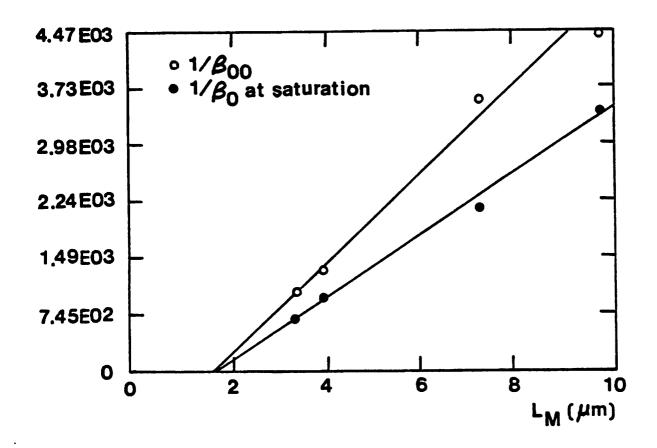

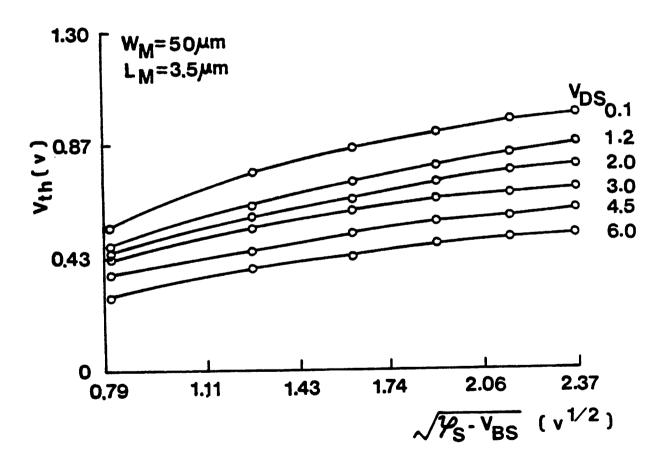

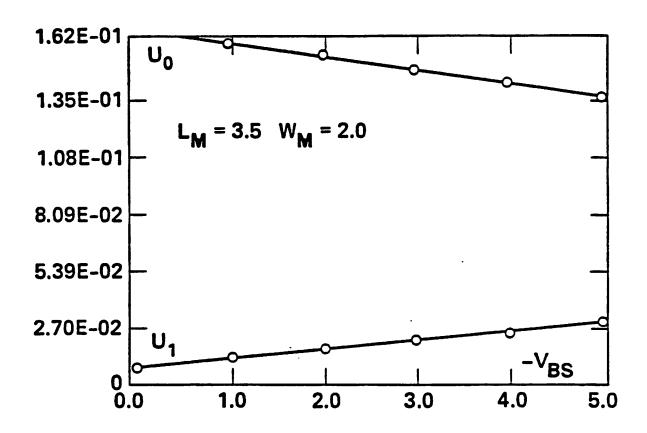

Shown in Fig. 3 is a typical example of the  $\beta_0/\beta_{00}$  as a function of  $V_{DS}$  and  $V_{BS}$ , where  $\beta_0$  is the value extrapolated to  $V_{GS} = V_{th}$  and  $\beta_{00}$  is the value extracted to  $V_{GS} = V_{th}$  and  $V_{DS} = V_{BS} = 0$ . Note that the conductance coefficient in saturation region is some 50% greater than that in the linear region. Shown in Fig. 4 is the conventional plot of inverse  $\beta_0$  versus masked channel length. Note that the electrical channel lengths obtained are essentially the same as extrapolated from linear ( $\beta_{00}$ ) and saturation ( $\beta_0$  for  $V_{DS} = 5v$  and  $V_{BS} = 0$ ) values. Fig. 5 displays the threshold voltage charateristic for this device. The drain-induced barrier lowering coefficient  $\eta$ , which models the effect of  $V_{DS}$  on the threshold voltage, has a dependence on  $V_{DS}$  and  $V_{BS}$ . Fig. 6 shows the extracted  $U_0$  and  $U_1$  charateristics for this device respectively.

Based on the observed electrical parameter characteristics, the 8parameter CSIM1 model can be extended to a 17-parameter CSIM2 model to accurately reflect the characteristics of modern MOS devices. The bias dependencies of the 4 CSIM1 parameters are described below, and form the basis for the 17 parameter model, CSIM2.

Un can be modeled by two parameters:

Uoz, the value at zero substrate bias, and

$U_{0B}$ , the sensitivity of  $U_0$  to substrate bias.

U<sub>1</sub> can be modeled by two parameters:

$U_{1Z}$ , the value at zero substrate bias,

U<sub>1B</sub>, the sensitivity of U<sub>1</sub> to substrate bias, and

$U_{1D}$ , the sensitivity of  $U_1$  to drain-source voltage, at  $V_{DS} = V_{DD}$ .

$\eta$  can be modeled by three parameters:

$\eta_{Z}$ , the value at zero substrate bias and  $V_{DS}=V_{DD}$

$\eta_{\rm B}$ , the sensitivity of  $\eta$  to substrate bias, and

$\eta_D$ , the sensitivity of  $\eta$  to drain-source bias, at  $V_{DS} = V_{DD}$ .

$\beta_0$  can be modeled by five parameters:

$\beta_{Z}$ , the value at zero substrate and drain-source biases,

$\beta_{ZB}$ , the sensitivity of  $\beta_0$  to substrate bias at  $V_{DS} = 0$ ,

$\beta_{S}$ , the value at zero substrate bias and at  $V_{DS}=V_{DD}$ .

$\beta_{SB}$ , the sensitivity of  $\beta_0$  to substrate bias at  $V_{DS} = V_{DD}$ , and

$\beta_{SD}$ , the sensitivity of  $\beta_0$  to drain-source bias at  $V_{DS} = V_{DD}$ .

### V. Parameter Calculation

Each CSIM2 electrical parameter P is related to device size by

$$\mathbf{P} = \mathbf{P_0} \left[ 1 + \frac{\mathbf{P_L}}{\mathbf{L}} + \frac{\mathbf{P_W}}{\mathbf{W}} \right] \tag{18}$$

where  $P_0$ ,  $P_L$  and  $P_W$  are obtained by analysis of P values over ranges of electrical channel length (L) and channel width (W). Note that the length (L) and width (W) of the device are the effective channel length and width. The masked length  $L_M$ .

and width  $W_{M}$ , are converted to the effective channel length and width by the following equations.

$$L = L_{u} + dL \quad W = W_{u} + dW \tag{19}$$

where dL and dW is the difference between the final electrical and masked channel length and width.

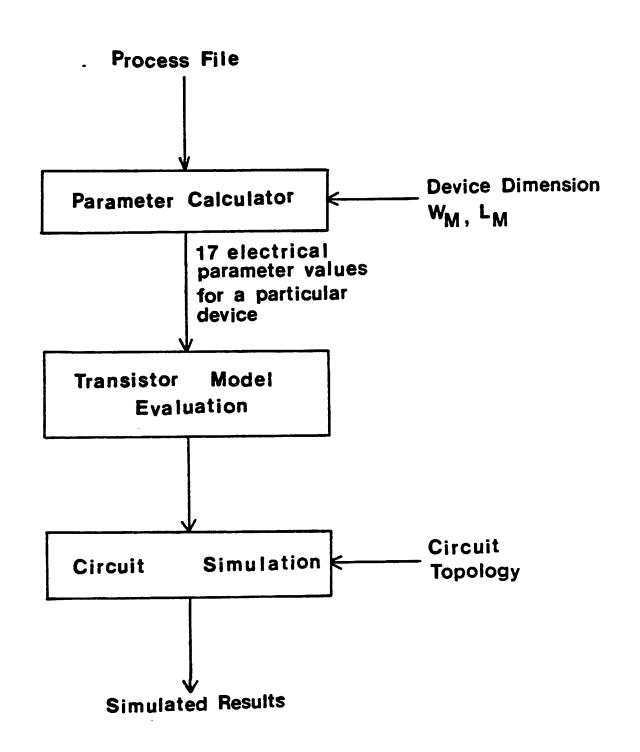

The file containing the 54 parameter values (with P<sub>0</sub>, P<sub>L</sub>, P<sub>W</sub> for each of the 17 parameters plus user supplied information for operating voltage, temperature, and gate oxide thickness) constitutes a "process file" for one type of device (enhancement- and depletion- mode nMOS and n- and p- channel CMOS). The process file is combined with the appropriate mask dimensions to generate 17 electrical parameter values for a particular device size. Fig. 7 shows how the CSIM2 model fits into circuit simulation programs such as SPICE [23].

During the model evaluation in circuit simulation, the eight electrical parameters are calculated out of the 17 CSIM2 parameters for a specific bias condition as follows:

V<sub>PB</sub>, φ<sub>S</sub>, K<sub>1</sub>, K<sub>2</sub> are bias-independent,

$$U_0 = U_{0Z} + U_{0B}V_{BS} \tag{20}$$

$$U_1 = U_{12} + U_{1B}V_{BS} + U_{1D}(V_{DS} - V_{DD})$$

(21)

$$\eta = \eta_0 + \eta_B V_{BS} + \eta_D (V_{DS} - V_{DD})$$

(22)

$\beta_0$  is obtained by quadratic interpolation through three data,  $\beta_0$  at  $V_{DS}=0$ ,  $\beta_0$  at  $V_{DS}=V_{DD}$ , and the sensitivity of  $\beta_0$  to  $V_{DS}$  at  $V_{DS}=V_{DD}$ , where

$$\beta_0 (at V_{DS} = 0) = \beta_2 + \beta_{ZB} V_{BS}$$

(23)

$$\beta_{\rm D}(\text{ at V}_{\rm DS} = V_{\rm DD}) = \beta_{\rm S} + \beta_{\rm SB} V_{\rm RS} \tag{24}$$

### VI. Experimental Results

Experiments were carried out through a newly developed automatic parameter extraction system for CSIM2 model [2]. Sample wafers, fabricated with an

advanced CMOS process as well as a standard nMOS process in Xerox.PARC, were used in the experiments. Gate oxide thickness of the CMOS process is 300 A, while the standard nMOS process has a gate oxide thickness of 700 A.

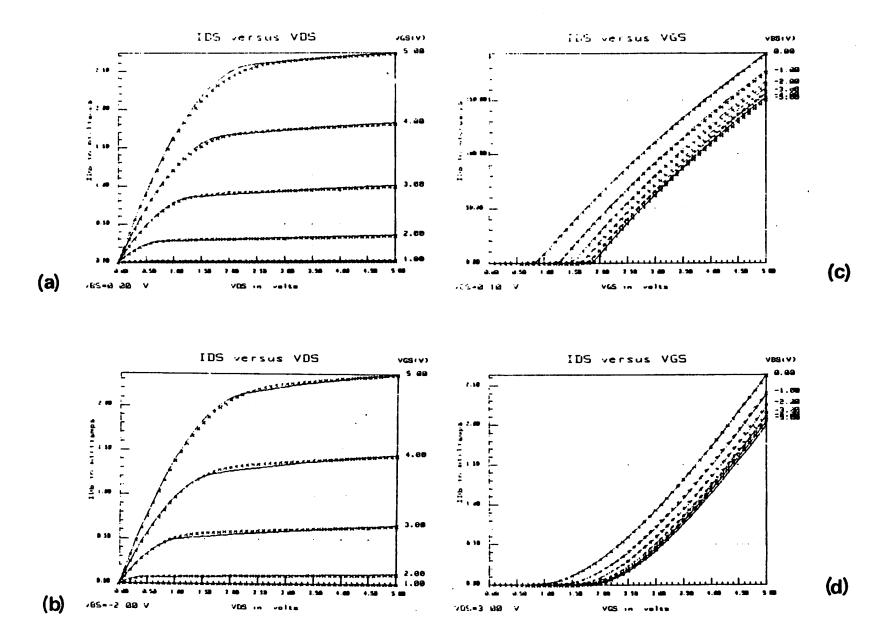

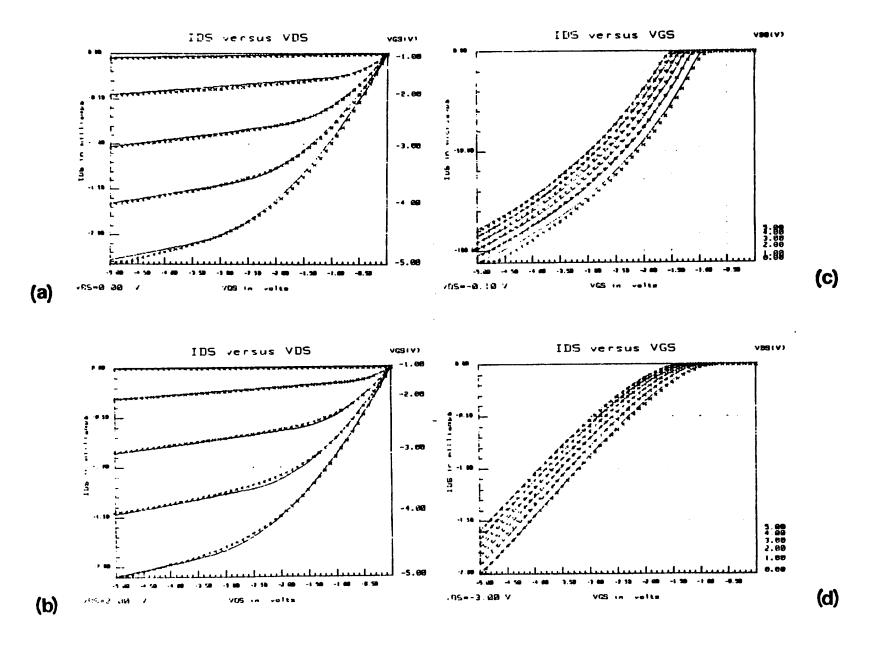

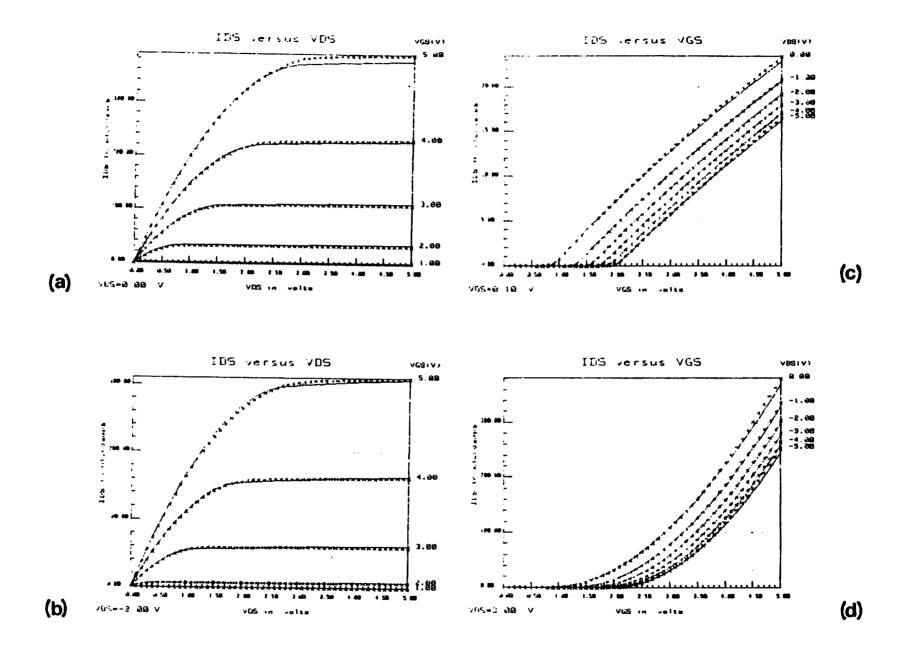

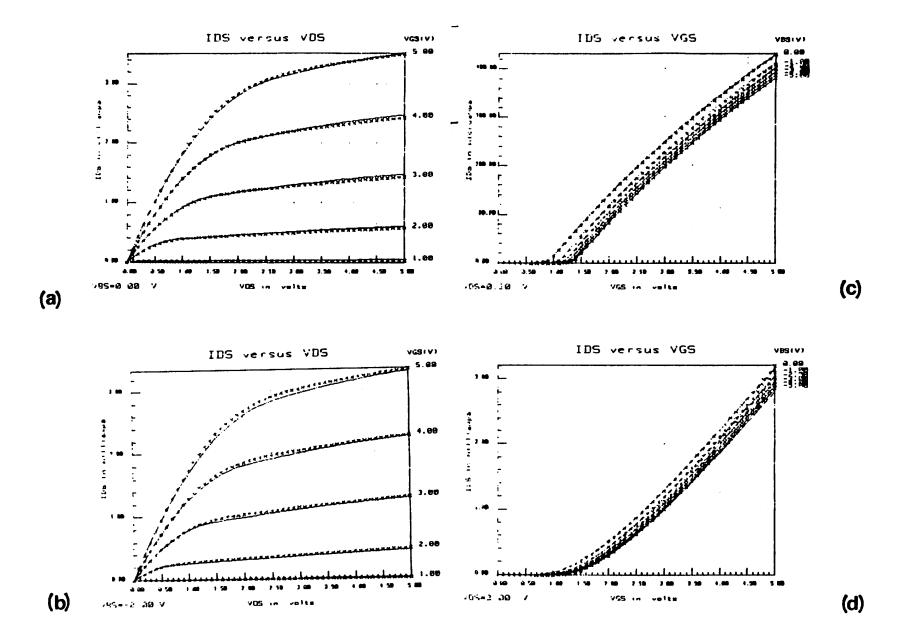

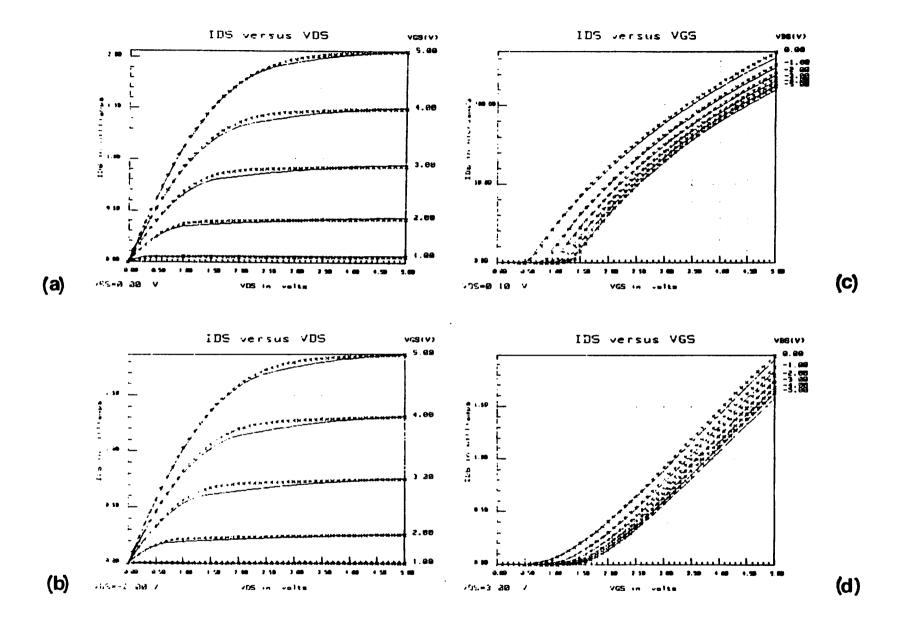

Fig. 8 shows output characteristics of a width/length= $20\mu$ m/3.5 $\mu$ m nMOS transistor. Simulated data are plotted with solid lines while measured data are displayed with cross marks. Fig. 9 shows similar plots for a  $20\mu$ m/2 $\mu$ m pMOS transistor. The output characteristics of long-channel transistors are shown in Fig. 10 and 11 for nMOS and pMOS  $20\mu$ m/20 $\mu$ m transistors. Fig. 12 depicts similar plots for a  $50\mu$ m/3.5 $\mu$ m nMOS transistor fabricated with the standard nMOS process.

As IGFET device size continues to shrink, the degradation of electrical characteristics induced by hot electron effects becomes increasingly severe. Device breakdown and substrate current due to impact ionization become a problem for these small devices. Recent work on lightly doped drain-source devices show the efforts to alleviate the above problems. In the LDD structure, self-aligned n-regions are introduced between the channel and the n+ drain-source diffusions. This structure increases the breakdown voltage and reduces impact ionization (and thus hot electron effects) by allowing the high electric field at the drain pinch-off region to extend into the n-region.

LDD test structures were fabricated on a P-type silicon wafer with resistivity of 1-2  $\Omega$ -cm in the HP IC Lab [24]. The n- region is formed by implanting 5E12 cm<sup>-2</sup> phosphorus at 80Kev, followed by  $0.3\mu m$  oxide spacer. Subsequent steps are similar to the process for the conventional device fabrication. Fig. 13 shows output characteristics of a  $10\mu m/1.5\mu m$  nMOS transistor. The agreement between measured and simulated results, for conventional as well as LDD IGFET's, clearly indicate the power of CSIM2 and the auto-characterization system.

### VII. Conclusion

A simple and accurate model for short-channel IGFET's has been presented. It is compact for efficiency in circuit simulation, and includes the depletion charge sharing, continuous velocity saturation, and nonuniform doping effects. The process file approach used in this model provides a powerful interface between fabrication capabilities and circuit designers. Simulated results agree with measured results at various bias conditions for different device sizes and gate oxide thicknesses. Therefore, this process-oriented CSIM model is well suited for circuit analysis, as well as for process monitoring.

### Appendix A: Derivation of CSIM Model [15,16]

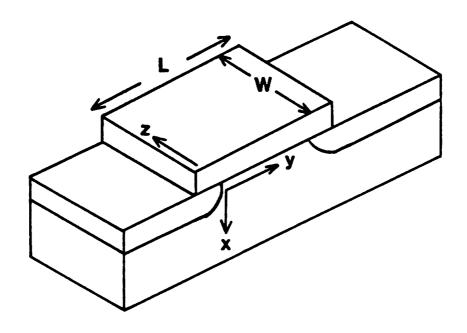

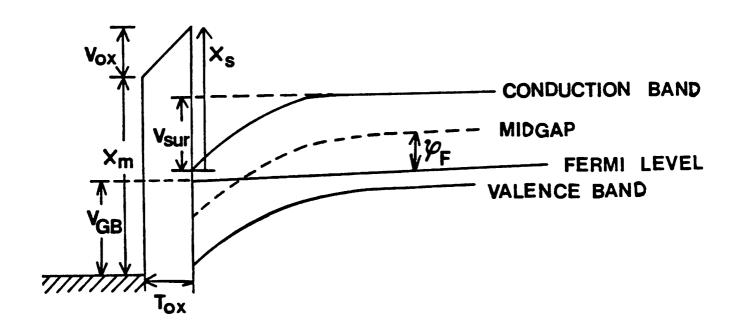

An idealized n-channel MOSFET with the coordinate system is illustrated in Fig. 14. The relationship between the electric field  $(E_{cx})$  in the oxide, the gate voltage  $(V_{CB})$  (with respect to the substrate potential), and the electrostatic potential  $(V_{sur})$  at the oxide-semiconductor interface can be understood by considering the energy band diagram in Figure 11. By summing up the voltages on both the gate and the semiconductor side, one obtains

$$V_{cx} + X_m = V_{CB} + \varphi_F + \frac{E_C}{2} - V_{sur} + X_s$$

(A.1)

where  $X_m$  and  $X_s$  are respectively the gate and semiconductor work functions,  $V_{ex}$  the voltage across the oxide,  $E_G$  the energy bandgap. The gate to semiconductor work function  $\varphi_{ms}$  is defined as

$$\varphi_{ms} = X_m - X_s - \varphi_F - \frac{E_G}{2}$$

(A.2)

Combining Equations (A.1) and (A.2), we obtain

$$V_{\text{ex}} = T_{\text{ex}} E_{\text{ex}}$$

$$= V_{\text{GB}} - V_{\text{sur}} - \varphi_{\text{ms}} \qquad (A.3)$$

where  $T_{ox}$  is the gate oxide thickness. To determine the relationship between  $E_{ox}$  and the charge in the semiconductor, let us assume:

- (1) The ratio  $T_{ex}/L$  is much smaller than 1. This assumption implies that  $E_{ex}$  is perpendicular to the gate plane.

- (2) The horizontal (parallel to the channel) component  $E_y$  of the electric field in the semiconductor at the oxide-semiconductor interface is much smaller than its vertical component  $E_z$ . This assumption is reasonable in the region where the channel charge  $Q_c$  is substantial, but it is incorrect in the pinch-off regon where  $Q_c$  is small. Our main interest is to compute the drain current which is proportional to the integral of  $Q_c$  along the channel. In the pinch-off region, where the above assumption is invalid, the contribution to the integral is small. Hence, this assumption is reasonable for drain current computation.

By Gauss's law and assumptions 1 and 2, one obtains

$$\varepsilon_{\mathbf{a}} \mathbf{E}_{\mathbf{a}} = \varepsilon_{\mathbf{c}\mathbf{x}} \mathbf{E}_{\mathbf{c}\mathbf{x}} + \mathbf{Q}_{\mathbf{a}\mathbf{a}} \tag{A.4}$$

where  $z_{ox}$  and  $z_{s}$  are the dielectric constants of the oxide and the semiconductor, and  $Q_{s}$  the surface charge.  $E_{s}$  consists of three components

$$\varepsilon_{\mathbf{z}} \mathbf{E}_{\mathbf{z}} = \mathbf{Q}_{\mathbf{c}} + \mathbf{Q}_{\mathbf{b}} + \varepsilon_{\mathbf{z}} \mathbf{E}_{\mathbf{1}} \tag{A.5}$$

where Q<sub>b</sub> is the depletion charge in the semiconductor and, using the abrupt junction approximation, is given by

$$Q_{\rm h} = \sqrt{2q\,\epsilon_{\rm s}\,N_{\rm B}V_{\rm max}} \tag{A.6}$$

For short channel devices, this expression is modified due to the influence of the source and drain junction field.  $E_g$  in Eq.(A.5) contains a third component  $E_1$  which originates from the drain and will be discussed in detail later.

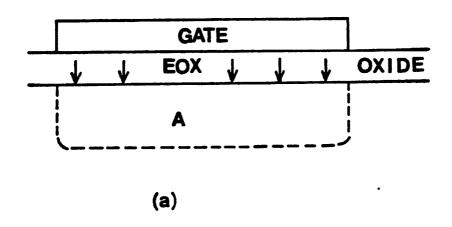

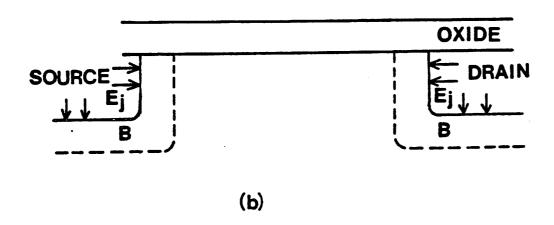

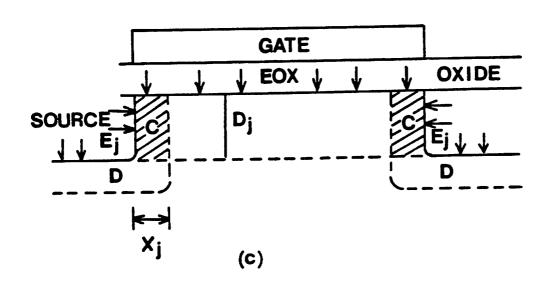

A qualitative expression for the bulk charge can be derived by considering a MOS structure where alternatively, the source and drain, and the gate are ignored (Fig. 16a and 16b). These diagrams illustrate the influence of source and drain junction field on the bulk charge. According to Gauss's law (Fig. 16a), the electric field Equ at the oxide-semiconductor interface will be balanced by the surface charge  $Q_{as}$ , the channel charge  $Q_{c}$ , and the negative charge  $Q_{b}$  in the depletion region (A) of the substrate. In the absence of the gate (Fig. 16b), the electric field E at the junction will be balanced by the charge in the depletion layer (B) near the junction. Now consider the complete structure where the drain, source and substrate are at the same potential and a positive voltage is applied to the gate as shown in Fig. 16c. The depletion charge shown in area (C) has to balance both the electric field Equ coming in from the oxidesemiconductor interface and E due to the source or drain to substrate junction. Let a fraction, t, of the charge (C) be used to balance E<sub>j</sub>. Since this fraction of charge will not be available to balance Eox, one could say the doping of the substrate is effectively lowered. This fraction, t, will depend on the position along the channel. As an approximation, t should be proportional to the ratio of charge in (C) to the total depletion charge of  $2X_j/L$ . Since  $X_j$  is proportional to  $1/(L\sqrt{N_A})$ . Therefore, the effective fraction of charge f(L,N) that is available to balance  $E_{ox}$  can be expressed by

$$f(L,N) = 1 - \frac{K_{vt}}{L\sqrt{N_R}} \tag{A.7}$$

where  $K_{vt}$  is a constant. A more elaborate function for f(L,N) and a more rigorous derivation can be found in [8] and [25] which show that f(L,N) is also a function of  $V_{BS}$ . However, we found that the additional  $V_{BS}$  dependence tends to complicate the formulation and does not add much accuracy to the model. With the modified charge, Eq.(A.5) becomes

$$\varepsilon_e E_e = Q_c + f(L,N) \sqrt{2q \varepsilon_e N_A V_{sur}}$$

(A.8)

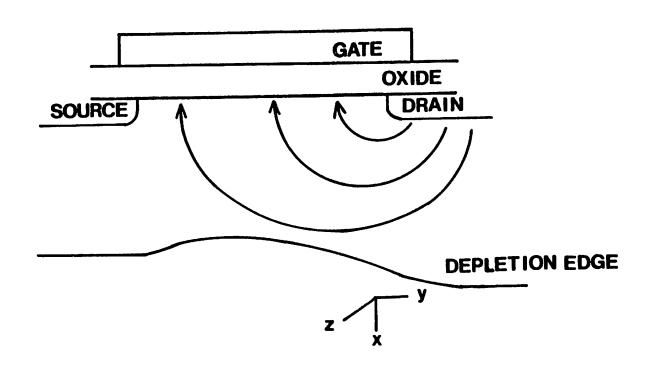

To derive the third component  $E_1$  of the electric field  $E_p$  let us consider the case that  $V_{DS}$  is zero but  $V_{CB}$  and  $V_{BS}$  are non-zero. The substrate is depleted according to the solution of the Poisson equation. When  $V_{DS}$  is non-zero, an additional potential will be imposed in the region already depleted. Since no additional charge appears in the Poisson equation (solution for  $V_{DS}=0$ ), this additional potential will satisfy the Laplace equation. This Laplace equation can be solved under certain simplifying assumptions and the solution gives the additional electric field as shown in Fig. 17. This electric field terminates at the channel and induces additional channel charges which enhance the drain current and result in a finite output conductance in the saturation region.

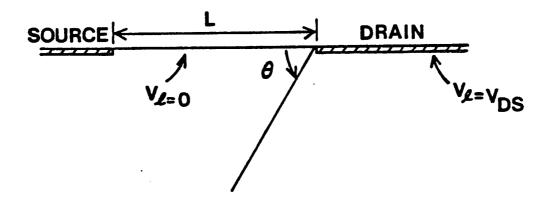

The following approximations are made to derive a simple expression for  $E_1$ .

(1) The source and drain junction depths are small compared to channel length.

(2) Approximate boundary conditions for the Laplace equation (solution denoted by  $V_l$ ) are  $V_l=0$  at the oxide-semiconductor interface and  $V_l=V_{DS}$  at the drain region. This approximation is illustrated in Fig. 18.

By substitution, it can be shown that

$$V_1 = V_{DS} \frac{\Theta}{\pi} \tag{A.9}$$

satisfies the Laplace equation in cylindrical coordinates,

$$\left[\frac{d^2V_l}{dr^2}\right] + \left[\frac{1}{r}\right] \left[\frac{dV_l}{dr}\right] + \left[\frac{1}{r^2}\right] \left[\frac{d^2V_l}{d\theta^2}\right] = 0 \tag{A.10}$$

and the boundary conditions. By differentiating  $V_1$  with respect to y at the source, one obtains

$$E_1 = -\frac{V_{DS}}{\pi L} \tag{A.11}$$

With the addition of E1, Eq.(A.8) becomes

$$\varepsilon_{\rm g} E_{\rm g} = Q_{\rm o} + f(L,N) \sqrt{2q N_{\rm A} V_{\rm sur}} + \varepsilon_{\rm g} E_{\rm l}$$

(A.12)

Combining Eq.(A.3), (A.4), and (A.12), one can express Qc in terms of  $V_{\text{GB}}$  and  $V_{\text{sur}},\,$

$$Q_{c} = C_{ox} \left[ V_{GB} - V_{sur} - V_{FB} - K_{1} \sqrt{V_{sur}} \right] - \varepsilon_{s} E_{1}$$

(A.13)

where

$$V_{FB} = \varphi_{ms} - \frac{Q_{es}}{C_{ox}}$$

(A.14)

and

$$K_1 = f(L,N) \frac{\sqrt{2q\epsilon_{si}N_A}}{C_{cor}}$$

(A.15)

When the surface is inverted, the surface potential V<sub>sur</sub> is approximately given by

$$V_{\text{sur}} = \varphi_{\text{n}} + \varphi_{\text{S}} - V_{\text{BS}} \tag{A.16}$$

where  $\varphi_n$  is the electron quasi-Fermi level. Then Eq.(A.13) becomes

$$Q_{c} = C_{ex} \left[ (V_{GS} - \varphi_{n} - \varphi_{S} - V_{FB}) - K_{1} \sqrt{\varphi_{n} - V_{BS} + \varphi_{S}} \right] - \varepsilon_{s} E_{1}$$

(A.17)

where

$$V_{GS} = V_{GB} + V_{BS} \tag{A.18}$$

To derive an expression for the drain current, the current flow is assumed to be parallel to the y axis such that

$$\left(\frac{d\varphi_n}{dx}\right) = 0 \tag{A.19}$$

and

$$J = q \mu_n n \left[ \frac{d \varphi_n}{d y} \right] \tag{A.20}$$

where  $\mu_n$  is the electron mobility and n the electron density. When Eq.(A.20) is integrated with respect to x and z, one obtains

$$I_{DS} = \mu_n \, W \, Q_c \left[ \frac{d \, \varphi_n}{d \, y} \right] \tag{A.21}$$

Integrating Eq.(A.21) with respect to  $y^*$  and  $\varphi_{n^*}$

$$I_{DS} \int_{0}^{L} dy = \mu_{n} W \int_{0}^{V_{DS}} Q_{o} d\varphi_{n}$$

(A.22)

•If channel shortening, due to finite extent of drain depletion region is included, the upper limit is accordingly reduced.

Combining Eq.(A.17) and (A.22), the drain current is given by

$$I_{DS} = \beta \int_{0}^{V_{DS}} \left[ \left( V_{GS} - \varphi_{n} - \varphi_{S} - V_{FB} \right) - K_{1} \sqrt{\varphi_{n} + \varphi_{S} - V_{BS}} + \eta V_{DS} \right] d\varphi_{n}$$

(A.23)

where  $\beta$  is the conductance coefficient and  $\eta$  is the drain-induced barrier lowering coefficient.

When Eq.(A.23) is integrated with respect to  $\varphi_n$  in the triode region, one obtains

$$I_{DS} = \beta \left[ (V_{GS} - \varphi_S - V_{FB}) V_{DS} + (\eta - \frac{1}{2}) V_{DS}^2 - \frac{2}{3} K_1 \left[ (V_{DS} + \varphi_S - V_{BS})^{\frac{3}{2}} - (\varphi_S - V_{BS})^{\frac{3}{2}} \right] \right]$$

(A.24)

Note that Eq.(A.24) is exactly the Ihantola-Moll model [2] if  $\eta=0$  and  $K_1 = \sqrt{2q\epsilon_{si}N_B}/C_{ox}$ , i.e., f(L,N)=1.

### Expansion of Bulk Doping Term

The 3/2 power term can be approximated as shown below:

The function

$$\mathbf{F}(V_{DS}, \varphi_{S} - V_{BS}) = \frac{2}{3} \left[ (V_{DS} + \varphi_{S} - V_{BS})^{\frac{3}{2}} - (\varphi_{S} - V_{BS})^{\frac{8}{2}} \right]$$

(A.25)

can be approximated numerically in the range

$$0 < V_{DS} < 10 \text{ volts}$$

and

$$0.7 < \varphi_S - V_{RS} < 20.7 \text{ volts}$$

by

$$F(V_{DS}, \varphi_S - V_{BS}) = \sqrt{\varphi_S - V_{BS}} V_{DS} + \frac{0.25 \,\mathrm{g} \,V_{DS}^2}{\sqrt{\varphi_S - V_{BS}}}$$

(A.26)

where

$$g = 1 - \frac{1}{1.744 + 0.8364 (\varphi_S - V_{BS})}$$

(A.27)

The details of this approximation are discussed in appendix B. Using approximation (A.27), the drain current in the triode region is given by

$$I_{DS} = \beta [(V_{GS} - V_{th})V_{DS} - \frac{a}{2}V_{DS}^2]$$

(A.28)

where

$$V_{1h} = V_{FB} + \varphi_S + K_1 \sqrt{\varphi_S - V_{BS}} - K_2(\varphi_S - V_{BS}) - \eta V_{DS}$$

(A.29)

and

$$a=1+\frac{gK_1}{2\sqrt{\varphi_S-V_{BS}}} \tag{A.30}$$

The factor "a" given by equation (A.30) represents the bulk doping effect. The origin of the K<sub>2</sub> term has been explained in the text.

### Channel Charge Modeling with Above Formulation

After (A.29) and (A.30) has been inserted into (A.17), the channel charge has the simplifying form

$$Q_c = -C_{ox}(V_{GS} - V_{th} - a\varphi_n)$$

(A.31)

Integrating Eq.(A.23) with continuous velocity saturation characteristic (see

Eq.21), one obtain the drain current in triode region to be

$$I_{DS} = \beta \left[ (V_{GS} - V_{th} - I_{DS} R_{sat}) V_{DS} - \frac{a}{2} V_{DS}^{2} \right]$$

(A.32)

where

$$R_{\text{mat}} = \frac{1}{W \, v_{\text{mat}} \, C_{\text{cor}}} \tag{A.33}$$

Equation (A.32) can be rearranged as

$$I_{DS} = \frac{\beta}{(1 + U_1 \cdot V_{DS})} \left[ (V_{GS} - V_{th}) V_{DS} - \frac{a}{2} V_{DS}^2 \right]$$

(A.34)

where

$$U_1 = \beta R_{\text{soft}} = \frac{1}{E_{\text{cont}} L}$$

(A.35)

The conventional definition of saturation voltage,  $V_{DSAT}$ , is obtained as from (A.31) with  $Q_c=0$ . This condition is not realistic for modern short-channel devices. A more realistic assumption is that at the point in the channel where  $\varphi_n$  goes to  $V_{DSAT}$ , the channel current is limited by velocity saturation, i.e.,

$$Q_{c} = \frac{I_{DSAT}}{W_{V_{ent}}} = C_{ox}(V_{GS} - V_{th} - a V_{DSAT})$$

(A.36)

Substitution of the above into (A.31) yields an upper limit for the integral (A.23) as

$$\varphi_{\rm n} \longrightarrow V_{\rm DSAT} = \frac{1}{a} [(V_{\rm GS} - V_{\rm th}) - I_{\rm DSAT} R_{\rm sat}]$$

(A.37)

Integrating (A.23) with Eq.(A.37) as the upper limit yields the following expression for the drain current in saturation:

$$I_{DSAT} = \beta \left[ \left( V_{CS} - V_{th} - I_{DSAT} R_{sat} \right) V_{DSAT} - \frac{a V_{DSAT}^2}{2} \right]$$

(A.38)

Eq.(A.38) can be rearranged as

$$I_{DSAT} = a\beta \left( V_{CS} - V_{th} - I_{DSAT} R_{sat} \right)^2$$

(A.39)

hence, a quadratic equation for  $l_{DSAT}$ . To facilitate comparison to the usual expression, we define

$$I_{DSAT} = \frac{\beta (V_{GS} - V_{th})^2}{2aK}$$

(A.40)

where K is obtained by substitution of (A.40) into (A.39), i.e.,

$$K^{2} - K\left[1 + \frac{(V_{GS} - V_{th})}{a E_{crit} L}\right] + \frac{(V_{GS} - V_{th})^{2}}{(2 a E_{crit} L)^{2}} = 0$$

(A.41)

סר

$$K = \frac{1 + v_c + \sqrt{1 + 2v_e}}{2}$$

(A.42)

whereas

$$v_c = \frac{(V_{GS} - V_{th})}{a E_{crit} L} \tag{A.43}$$

If  $v_c \ll 1$ , then

$$K \longrightarrow 1 + \frac{(V_{GS} - V_{th})}{a E_{crit} L}$$

(A.44)

If  $v_c \gg 1$ , then

$$K \longrightarrow \frac{(V_{GS} - V_{th})}{2aE_{crit}L}$$

and  $I_{DSAT} \longrightarrow C_{ox}v_{sat}W(V_{GS} - V_{th})$  (A.45)

The above expression is well known, and states that in the limit of carrier velocity fully saturated at  $v_{sat}$ , the current in saturation is linear and not squared with respect to  $(V_{GS}-V_{th})$ , and that its value is independent of channel length.

One can obtain the saturation drain voltage VDSAT from (A.37) and (A.40).

$$V_{DSAT} = \frac{V_{CS} - V_{th}}{a\sqrt{K}}$$

(A.46)

In the case when  $\frac{V_{GS}}{E_{crit}L} \ll 1$ .

$$V_{DSAT} \longrightarrow \frac{V_{GS} - V_{th}}{a} \tag{A.47}$$

In the case when  $\frac{V_{GS}}{E_{crit}L} \gg 1$ ,

$$V_{DSAT} \longrightarrow \left[ \frac{2(V_{CS} - V_{th}) E_{crit} L}{a} \right]^{\frac{1}{2}}$$

(A.48)

## Appendix B: Numerical Approximation of Function $F(V_{DS}, \varphi_S - V_{BS})$

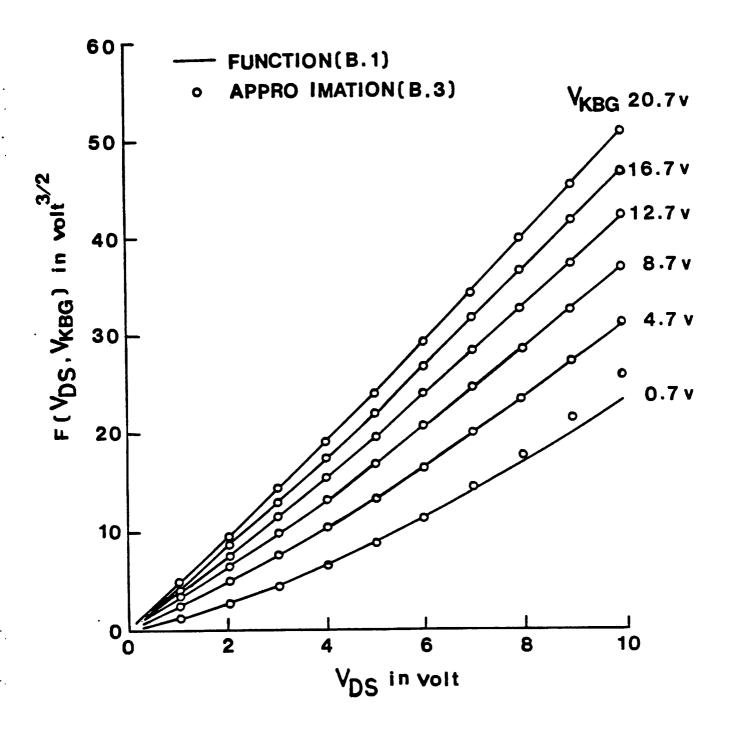

The aim is to find an accurate approximation of  $F(V_{DS}, \varphi_S - V_{BS})$  over a reasonable voltage range of  $V_{DS}$  and  $(\varphi_S - V_{BS})$ . For convenience, let  $V_{KBG} = (\varphi_S - V_{BS})$ . For small  $V_{DS}$ , the function  $F(V_{DS}, V_{KBG})$ .

$$K_1 F(V_{DS}, V_{KBG}) = \frac{2}{3} K_1 \left[ (V_{DS} + V_{KBG})^{\frac{3}{2}} - (V_{KBG})^{\frac{3}{2}} \right]$$

(B.1)

can be expanded as

$$F(V_{DS}, V_{Jbg}) = \sqrt{V_{KBC}} V_{DS} + \frac{0.25 V_{DS}^2}{\sqrt{V_{KBC}}} + ....$$

(B.2)

The above expansion is invalid when  $V_{KBG}$  is much greater than  $V_{DS}$ . To alleviate this problem, the expansion is modified to

$$F(V_{DS}, V_{KBG}) = \sqrt{V_{KBG}} V_{DS} + \frac{0.25 \, g \, V_{DS}^2}{\sqrt{V_{KBG}}}$$

(B.3)

where  $g(V_{KBG})$  is determined by requiring the expansion (B.3) to give the best fit to  $F(V_{DS}, V_{KBG})$  in the desired voltage range.

The value of  $V_{KBG}$  are considered in the range 0.7 to 20.7 volts at 2-volt increments. For each fixed  $V_{KBG}$ , a parameter g is determined such that the expansion

$$\sqrt{V_{KBG}} V_{DS} + \frac{0.25 \, g \, V_{DS}^2}{\sqrt{V_{KBG}}}$$

(B.4)

will give the best fit to  $F(V_{DS}, V_{KBC})$  in a least-square sense, over a range of  $V_{DS}$  from 0 to 10 volts at 0.5-volt increments. Having determined g as a function of  $(V_{KBC})$ , it is found that it can be accurately represented by

$$\frac{1}{1-g} = P_1 + P_2 V_{KBG} \tag{B.5}$$

where  $P_1$  and  $P_2$  are determined by a least-square fitting over the range of  $V_{KBG}$  from 0.7 to 20.7 volts. The result is

$$P_1 = 1.744$$

(B.6)

$$P_2 = 0.8364$$

(B.7)

The root-mean-square error of approximation (B.3) using the above value of  $P_1$  and  $P_2$  is 2% and is illustrated by Fig. 19.

### REFERENCES

- [1] VLSI Laboratory-Texas Instruments Inc., "Technology and Design of MOS VLSI." IEEE Journal of Solid State Circuits, vol. SC-17, no. 3, pp. 442-448, June 1982.

- [2] B. S. Messenger, "A Fully Automated MOS Device Charaterization System for Process-Oriented Integrated Circuit Design," M.S. Report, University of California, Berkeley, EECS, 1984.

- [3] R. C.-L. Liu, "An IC Process-Oriented Circuit Simulator Developed From SPICE2G.6 Using the CSIM MOSFET Model," M.S. Report, University of California, Berkeley, EECS, 1984.

- [4] H. K. J. Ihantola and J. L. Moll, "Design Theory of a Surface Field Effect Transistor," Solid-State Electronics, vol. 7, pp. 423-430, Jun. 1964.

- [5] H. C. Pao, C. T. Sah, "Effects of Diffusion Current on Characteristics of metal-oxide (insulator)-semiconductor transistors (MOST)," Solid-State Electronics, vol. 9, pp. 927-937, 1966.

- [6] Y. A. El-Mansy, "Modeling of Insulated-Gate Field-Effect Transistors," Ph.D. dissertation, Carleton Univ., Ottawa, Ont., Canada, Nov. 1974.

- [7] J. R. Brews, "A Charge-Sheet Model of the MOSFET," Solid-State Electronics, vol. 21, pp. 345-355, 1978.

- [8] R. M. Swanson, and J. D. Meindl, "Ion-Implanted Complementary MOS Transistor in Low Voltage Circuits," IEEE Journal of Solid State Circuits, vol. SC-7, pp. 146-153, April 1972.

- [9] R. R. Troutman, "Subthreshold Design Considerations for IGFET's," IEEE Journal of Solid State Circuits, vol. SC-9, no.2, pp.55-60, Apr. 1974.

- [10] G. W. Taylor, "Subthreshold Conduction in MOSFET," IEEE Trans. Electron Devices, vol. ED-25, vol.3, pp. 337-350, Mar. 1978.

- [11] A. Vladimirescu, S. Liu, "The Simulation of MOS Integrated Circuits Using SPICE2," Memo. UCB/ERL M80/7, Oct. 1980.

- [12] G. W. Taylor, "A Unified Device Model for a Short-Channel MOSFET," presented at the 39th Annu. Device Res. Conf., 1981.

- [13] W. Fichtner, "Three-Dimensional Numerical Modeling of Small-Size MOSFET's," presented at the 39th Annu. Device Res. Conf., 1981.

- [14] T. Shima, T. Sugawara, S. Moriyama, and H. Yamada, "Three-Dimensional Table Look-Up MOSFET Model for Precise Circuit Simulation," IEEE Journal of Solid State Circuits, vol. SC-17, no. 3, pp. 449-454, June 1982.

- [15] H. C. Poon, L. D. Yau, R. L. Johnston, and D. Beecham, "DC Model for Short-Channel IGFETs," IEEE IEDM Technical Digest, pp. 156- (1973), and H. C. Poon, Asilomar Conf. Circuits, Systems and Computers, Pacific Grove, CA, Dec. 1977, pp. 508-512.

- [16] H. C. Poon, "Vth and Beyond," Workshops on Device Modeling for VLSI," Burlingame, CA, March 29, 1979.

- [17] H. C. Poon, "A Compact Short-Channel IGFET Model (CSIM)," Internal Bell Labs memorandum, April 2, 1976.

- [18] D. L. Scharfetter, "Device Model for ICL Process Characterization," Inter-Office Xerox.PARC Memorandum, Dec 30, 1982.

- [19] K. Ratnakumar, J. D. Meindl, D. L. Scharfetter, "New IGFET Short Channel Threshold Voltage Model," IEEE IEDM Technical Digest, pp. 204-206, 1981.

- [20] S. Liu, L. W. Nagel, "Small-Signal MOSFET Models for Analog Circuit Design," IEEE Journal of Solid State Circuits, vol. SC-17, no. 6, pp. 983-998, Dec. 1982.

- [21] A. S. Grove, Physics and Technology of Semiconductor Devices. New York:

Wiley, 1967.

- [22] S. M. Sze, Physics of Semiconductor Devices. New York: Wiley-Interscience, 1981.

- [23] L. W. Nagel, "SPICE2: A Computer Program to Simulate Semiconductor Circuits," Univ. California, Berkeley, ERL Memo, ERL-M520, May 1975.

- [24] F.-C. Hsu, and H. R. Grinolds, "Structure-Dependent MOSFET Degradation Due to Hot-Electron Injection," Tech. Dig. IEDM, pp. 742-744, 1983.

- [25] L. D. Yau, "Simple I-V Model for Short-Channel IGFETs in the Triode region," Electronics letters, vol. 11, pp. 44-45, Jan. 1975.

Fig.1 Carrier velocity versus electric field. (22)

Fig.2 The hierarchy of CSIM-1, 2 and 3.

Fig.3  $\frac{\beta_0}{\beta_{00}}$  against drain-source voltage.

Fig.4 plot of inverse  $\beta_0$  against masked channel length.

Fig.5 Threshold voltage against  $\sqrt{\varphi_S - V_{BS}}$ .

Fig. 6 U<sub>0</sub> and U<sub>1</sub> against substrate-source voltage.

Fig.7 Parameter manipulations in a circuit simulator.

Fig.8 Output characteristics of a  $W_{I\!\!J}/I_{I\!\!J}=20\mu m/3.5\mu m$  masked size nMOS transistor.  $T_{cx}=300A$ . (a)  $I_{DS}$  versus  $V_{DS}$  at  $V_{BS}=0.0v$ , (b)  $I_{DS}$  versus  $V_{DS}$  at  $V_{DS}=2.0v$ , (d)  $I_{DS}$  versus  $V_{CS}$  at  $V_{DS}=3.0v$ .

Fig.9 Output characteristics of a  $20\mu m/2\mu m$  masked size pMOS transistor.  $T_{oz}=300A$ . (a)  $l_{DS}$  versus  $V_{DS}$  at  $V_{BS}=0.0v$ . (b)  $l_{DS}$  versus  $V_{DS}$  at  $V_{DS}=2.0v$ . (d)  $l_{DS}$  versus  $V_{CS}$  at  $V_{DS}=-0.1v$ . (d)  $l_{DS}$  versus  $V_{CS}$  at  $V_{DS}=-3.0v$ .

Fig. 10 Output characteristics of a  $20\mu m/20\mu m$  masked size nMOS transistor.  $T_{oz}$ =300A. (a)  $l_{DS}$  versus  $V_{DS}$  at  $V_{BS}$ =0.0v, (b)  $l_{DS}$  versus  $V_{DS}$  at  $V_{DS}$ =2.0volt, (c)  $l_{DS}$  versus  $V_{GS}$  at  $V_{DS}$ =0.1v, (d)  $l_{DS}$  versus  $V_{GS}$  at  $V_{DS}$ =3.0v.

Fig.11 Output characteristics of a  $20\mu m/20\mu m$  masked size pMOS transistor.  $T_{ox}$ =300A. (a)  $l_{DS}$  versus  $V_{DS}$  at  $V_{BS}$ =0.0v, (b)  $l_{DS}$  versus  $V_{DS}$  at  $V_{DS}$ =-0.1v, (d)  $l_{DS}$  versus  $V_{GS}$  at  $V_{DS}$ =-3.0v.

Fig. 12 Output characteristics of a  $50\mu m/3.5\mu m$  masked size nMOS transistor.  $T_{ox}=700A$ . (a)  $l_{DS}$  versus  $V_{DS}$  at  $V_{BS}=0.0v$ , (b)  $l_{DS}$  versus  $V_{DS}$  at  $V_{DS}=2.0$ volt, (c)  $l_{DS}$  versus  $V_{CS}$  at  $V_{DS}=3.0v$ .

Fig. 13 Output characteristics of a  $10\mu m/1.5\mu m$  masked size nMOS transistor with LDD structure.  $T_{ox}=200A$ . (a)  $I_{DS}$  versus  $V_{DS}$  at  $V_{BS}=0.0v$ , (b)  $I_{DS}$  versus  $V_{DS}$  at  $V_{DS}=2.0v$ , (d)  $I_{DS}$  versus  $V_{CS}$  at  $V_{DS}=3.0v$ .

Fig.14 An idealized n-channel MOSFET.

Fig.15 An energy band diagram.

Fig. 16 Diagram illustrating the effect of drain and source junction fields.

Fig.17 Diagram illustrating the drain modulation effect.

Fig.18 Diagram illustrating the simplified boundary condition for the Laplace equation.

Fig. 19 Approximating the function  $F(V_{DS}, \varphi_S - V_{BS})$ .

## A Compact IGFET Charge Model

Bing J. Sheu, Don L. Scharfetter, Chenming Hu, and Donald O. Pederson

Department of Electrical Engineering and Computer Sciences and Electronics Research Laboratory University of California, Berkeley CA

#### **ABSTRACT**

A new IGFET charge model, consistent with the recently published Compact Short-Channel IGFET Model [1][2], is presented. It is simple, accurate, and suitable for circuit simulation applications. Charge conservation is guaranteed by using charge as the state variable. The partitioning of channel charge into drain and source components is given significant attention. This partitioning changes smoothly from 40/60 in the saturation region asymptotically to 50/50 in the triode region. The terminal charges are well behaved over all regions of operation. This charge model and its DC characteristic counterpart, derived from the same considerations of MOS device physics, form a unified model previously unavailable.

February 22, 1984

Research sponsored by Semiconductor Research Corporation and DAPRA under Contract N00039-81-0251

# A Compact IGFET Charge Model

Bing J. Sheu, Don L. Scharfetter, Chenming Hu, and Donald O. Pederson

Department of Electrical Engineering and Computer Sciences and Electronics Research Laboratory University of California, Berkeley CA

#### I. Introduction

Much work has been devoted to the subject of modeling the DC characteristic of the MOS transistor. These models all show agreement between simulated and experimental results to within a few percent. However, insufficient effort has been devoted to obtaining satisfactory charge models suitable for transient and AC small signal circuit simulations. The issue of modeling MOS transistor charge storage [3].[4] has attracted the attention of IC designers since Ward and Dutton [5] pointed out that charge non-conservation could occur if the MOSFET capacitance model is not correctly formulated. This effect may cause serious errors in the simulations of switched-capacitor circuits, certain dynamic circuits, and other circuits sensitive to capacitive components of the MOSFET currents. Although there have been various solutions proposed in the literature, there is unanimous agreement that the solution to the charge non-conservation problem is to employ a charge-oriented capacitive coefficient model, i.e. a model based on the charge functions:

$$Q_G(V_G, V_S, V_D, V_B)$$

$$Q_B(V_C, V_S, V_D, V_B)$$

$$Q_S(V_C, V_S, V_D, V_B)$$

$$Q_D(V_G, V_S, V_D, V_B)$$

$Q_G$ ,  $Q_B$ ,  $Q_S$ ,  $Q_D$  are the charges associated with the gate, bulk (body), source, and drain terminals, and the capacitive current component of  $I_G$ ,  $I_B$ ,  $I_S$ ,  $I_D$ , is the derivative of  $Q_G$ ,  $Q_B$ ,  $Q_S$ ,  $Q_D$  with respect to time. The quasi-static approximation

has been assumed in formulating the above expressions.

Both transport current components and capacitive current components exist due to charge storage in the MOS transistor. Therefore the dc I-V model and charge model should be consistently derived. Some MOS models used in circuit simulators have a DC model part and a charge model part derived from different aspects. This has been confusing circuit designers for many years. In this paper, we present a charge model which shares the same information obtained from the DC characteristic measurements. The DC and charge models, derived from the same considerations of MOS device physics, form a unified model previously unavailable. The partitioning of channel charge into drain and source components is given significant attention. Body bias effects are properly incorporated and the physics behind the charge storage in the device are modeled and described.

### II. DC Characteristic Counterpart of the Charge Model

The DC characteristic model in this paper is an evolution of the Bell Labs CSIM (Compact Short-Channel IGFET Model). A detailed description of that model can be found in the appendix of [1]. The dc current expressions are briefly summarized, with some notation changes, in the following [1]:

1) Cut-off Region [ V<sub>GS</sub> < V<sub>th</sub> ]:

$$I_{DS} = 0 \tag{1}$$

2) Triode Region [ VGS > Vth and 0 < VDS < VDSAT ]:

$$I_{DS} = \beta [(V_{CS} - V_{th}) V_{DS} - \frac{\alpha_x}{2} V_{DS}^2]$$

(2)

3) Saturation Region [  $V_{\text{CS}} > V_{\text{th}} \ \text{and} \ V_{\text{DS}} > V_{\text{DSAT}}$  ]:

$$I_{DS} = \frac{\beta}{2\alpha_x} (V_{CS} - V_{th})^2$$

(3)

The threshold voltage "Vth" is defined by the equation

$$V_{th} = V_{FB} + \varphi_S + K_1 \sqrt{\varphi_S - V_{BS}} - K_2 (\varphi_S - V_{BS}) - \eta V_{DS}$$

$$\tag{4}$$

The last two terms in the right hand side of (4) result from the short channel drain-induced barrier lowering effect.

The saturation voltage "VDSAT" is defined by

$$V_{DSAT} = \frac{V_{GS} - V_{th}}{\alpha_{\tau}} \tag{5}$$

The effective conductance coefficient " $\beta$ " is defined by the equation

$$\beta = \frac{\beta_0}{1 + U_0 \left( V_{CS} - V_{th} \right)} \tag{6}$$

The conductance-degradation coefficient " $a_{\mathbf{z}}$ " is defined by the equation

$$\alpha_{x} = a[1 + U_{1}(V_{GS} - V_{th})]$$

(7)

where

$$\mathbf{a} = 1 + \frac{\mathbf{g} \, \mathbf{K}_1}{2\sqrt{\varphi_{\mathbf{S}} - \mathbf{V}_{\mathbf{BS}}}} \tag{8}$$

$$g = 1 - \frac{1}{1.744 + 0.8364 (\varphi_S - V_{BS})}$$

(9)

The body-effect coefficient "a" makes CSIM a close numerical approximation of the standard textbook model over a reasonable range of  $V_{DS}$  and  $V_{BS}$ .

## III. The Charge Model

The expressions for the charge densities are similar in form to those of [6]. However, due to different ways of treating the physics behind the transistor operation, the functional dependence of  $\alpha_x$  and channel charge partitioning are quite different. The charge equations in different regions are given below.

### 1) Triode Region:

$$q_{\mathbf{g}}(\mathbf{y}) = C_{\mathbf{o}}(V_{\mathbf{GS}} - V_{\mathbf{FB}} - \varphi_{\mathbf{S}} - V_{\mathbf{y}}) \tag{10}$$

$$q_c(y) = -C_o(V_{GS} - V_{th} - \alpha_x V_y)$$

(11)

$$q_{b}(y) = -C_{o}[V_{th} - V_{FB} - \varphi_{S} - (1 - \alpha_{x})V_{y}]$$

(12)

where  $V_y$  is the electron quasi-Fermi potential with respect to the source. Observe that

$$q_e + q_c + q_b = 0 \tag{13}$$

This follows the constraint of charge neutrality in the one dimensional MOS

capacitor structure.

Total stored charge contained in each of the gate, bulk, and channel regions is easily obtained by integrating the distributed charge densities,  $q_g$ ,  $q_b$ , and  $q_c$  over the area of the active gate region (from y=0 to y=L and z=0 to z=W).

$$Q_{G} = W \int_{0}^{L} q_{g}(y) dy$$

(14)

$$Q_{C} = W \int_{0}^{L} q_{c}(y) dy$$

(15)

$$Q_{B} = W \int_{0}^{L} q_{b}(y) dy$$

(16)

Combining (10)-(12) into (14)-(16) and replacing the differential channel length "dy" with the corresponding differential potential drop "dV", we obtain the following expressions for the total gate, channel, and bulk charges in static equilibrium.

$$Q_{C} = W \int_{0}^{L} C_{o} (V_{CS} - V_{FB} - \varphi_{S} - V_{y}) dy$$

$$= W L C_{o} \left\{ V_{CS} - V_{FB} - \varphi_{S} - \frac{V_{DS}}{2} + \frac{V_{DS}}{12} \frac{\alpha_{x} V_{DS}}{(V_{CS} - V_{th} - \frac{\alpha_{x}}{2} V_{DS})} \right\}$$

$$Q_{C} = -W \int_{0}^{L} C_{o} (V_{CS} - V_{th} - \alpha_{x} V_{y}) dy$$

$$= -W L C_{o} \left\{ V_{GS} - V_{th} - \frac{\alpha_{x}}{2} V_{DS} + \frac{\alpha_{x} V_{DS}}{12} \cdot \frac{\alpha_{x} V_{DS}}{(V_{CS} - V_{th} - \frac{\alpha_{x}}{2} V_{DS})} \right\}$$

$$Q_{B} = -W \int_{0}^{L} C_{o} [V_{th} - V_{FB} - \varphi_{S} - (1 - \alpha_{x}) V_{y}] dy$$

$$= W L C_{o} \left\{ -V_{th} + V_{FB} + \varphi_{S} + \frac{(1 - \alpha_{x})}{2} V_{DS} - \frac{(1 - \alpha_{x}) V_{DS}}{12} \cdot \frac{\alpha_{x} V_{DS}}{(V_{CS} - V_{th} - \frac{\alpha_{x}}{2} V_{DS})} \right\}$$

$$(19)$$

It is clear that the three total stored charge components of the MOSFET, (17)-(19), also exhibit charge neutrality.

$$Q_C + Q_C + Q_B = 0 \tag{20}$$

It is necessary to partition channel charge into charge associated with the drain terminal "Q<sub>D</sub>" and charge associated with the source terminal "Q<sub>S</sub>". The question of charge partitioning has so far been dealt with by gross approximate partitioning or use of an arbitrary factor. Ward and Dutton [5] already noted this difficulty. They described many possibilities and chose the estimate of 50/50 partition between Q<sub>D</sub> and Q<sub>S</sub>, although their device simulation had indicated a 40/60 partition in the saturation region. Yang, et al [6] proposed to make the partition so as to satisfy the condition that Q<sub>D</sub> and Q<sub>S</sub> and their derivatives be continuous throughout the triode and saturation regions. They failed to note, however, that there are infinite ways to partition the charge to satisfy that requirement. Furthermore, they adopted the incorrect premise that Q<sub>D</sub> is zero at the saturation region (0/100 partition).

A sound theoretical model for channel charge partitioning is of particular importance because if the partitioning is performed through the use of a parameter, then that parameter (actually a function of the bias voltage) is unusually difficult to extract from device measurements. In this work, the issue of channel charge partitioning is appropriately handled. It changes smoothly from 40/60 in the saturation region asymptotically to 50/50 in the triode region.

A physically meaningful channel charge partitioning method has been presented by Oh, et al [7] and is used here.

$$Q_{S} = -W \int_{0}^{L} \left(1 - \frac{y}{L}\right) q_{c}(y) dy$$

(21)

$$Q_D = -W \int_0^L \frac{y}{L} q_e(y) dy = Q_C - Q_S$$

(22)

Carrying out the integrations in (21) and (22), with  $q_c$  replaced by (11), we obtain the total charge associated with the source terminal and drain terminal,

$$Q_{S} = -WLC_{e} \left[ \frac{V_{GS} - V_{th}}{2} + \frac{\alpha_{x}V_{DS}}{12} \cdot \frac{\alpha_{x}V_{DS}}{(V_{GS} - V_{th} - \frac{\alpha_{x}}{2}V_{DS})} - \frac{\alpha_{x}V_{DS}}{(V_{GS} - V_{th} - \frac{\alpha_{x}}{2}V_{DS})^{2}} \left[ \frac{(V_{GS} - V_{th})^{2}}{6} - \frac{\alpha_{x}V_{DS}(V_{GS} - V_{th})}{8} + \frac{\alpha_{x}^{2}V_{DS}^{2}}{40} \right] \right]$$

$$Q_{D} = -W L C_{o} \left[ \frac{V_{GS} - V_{th}}{2} - \frac{\alpha_{x} V_{DS}}{2} + \frac{\alpha_{x} V_{DS}}{(V_{GS} - V_{th} - \frac{\alpha_{x}}{2} V_{DS})^{2}} \left[ \frac{(V_{GS} - V_{th})^{2}}{6} - \frac{\alpha_{x} V_{DS} (V_{GS} - V_{th})}{8} + \frac{\alpha_{x}^{2} V_{DS}^{2}}{40} \right] \right]$$

(23)

2)Saturation Region:

$$Q_{G} = W L C_{o} (V_{GS} - V_{FB} - \varphi_{S} - \frac{V_{GS} - V_{th}}{3 \alpha_{x}})$$

(25)

$$Q_{B} = W L C_{o} (V_{PB} + \varphi_{S} - V_{th} + \frac{(1 - \alpha_{x})(V_{GS} - V_{th})}{3 \alpha_{x}})$$

(26)

$$Q_{C} = -\frac{2}{3} W L C_{o} (V_{CS} - V_{th})$$

(27)

$$Q_{S} = -\frac{2}{5} W L C_{o} (V_{GS} - V_{th})$$

(28)

$$Q_{D} = -\frac{4}{15} W L C_{o} (V_{GS} - V_{th})$$

(29)

3) Subthreshold Region [ $V_{FB} + V_{RS} \le V_{CS} \le V_{th}$ ]:

Let

$$K_{\text{eff}} \sqrt{\varphi_{S} - V_{BS}} = K_1 \sqrt{\varphi_{S} - V_{BS}} - K_2 (\varphi_{S} - V_{BS}) - \eta V_{DS}$$

(30)

then

$$Q_{G} = W L C_{o} \frac{K_{eff}^{2}}{2} \left[ -1 + \sqrt{1 + \frac{4(V_{GS} - V_{FB} - V_{BS})}{K_{eff}^{2}}} \right]$$

(31)

$$Q_{B} = -Q_{C} \tag{32}$$

$$Q_{C} = 0 \tag{33}$$

### 4) Accumulation Region:

$$Q_{G} = W L C_{o} (V_{GS} - V_{FB} - V_{BS})$$

$$(34)$$

$$Q_{\rm B} = -Q_{\rm G} \tag{35}$$

$$Q_{C} = 0 \tag{36}$$

# IV. Comparison with Experiments and Conclusion

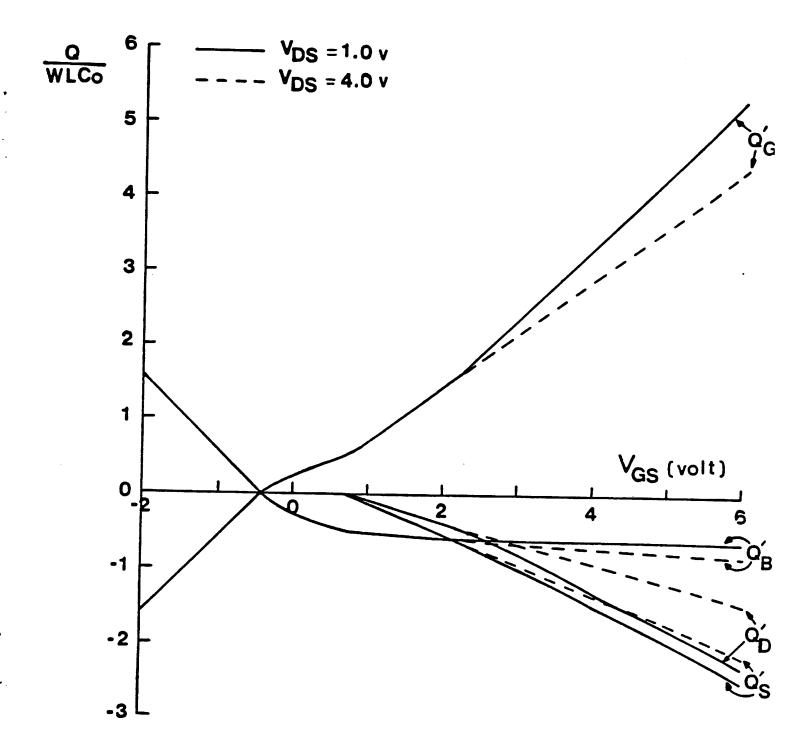

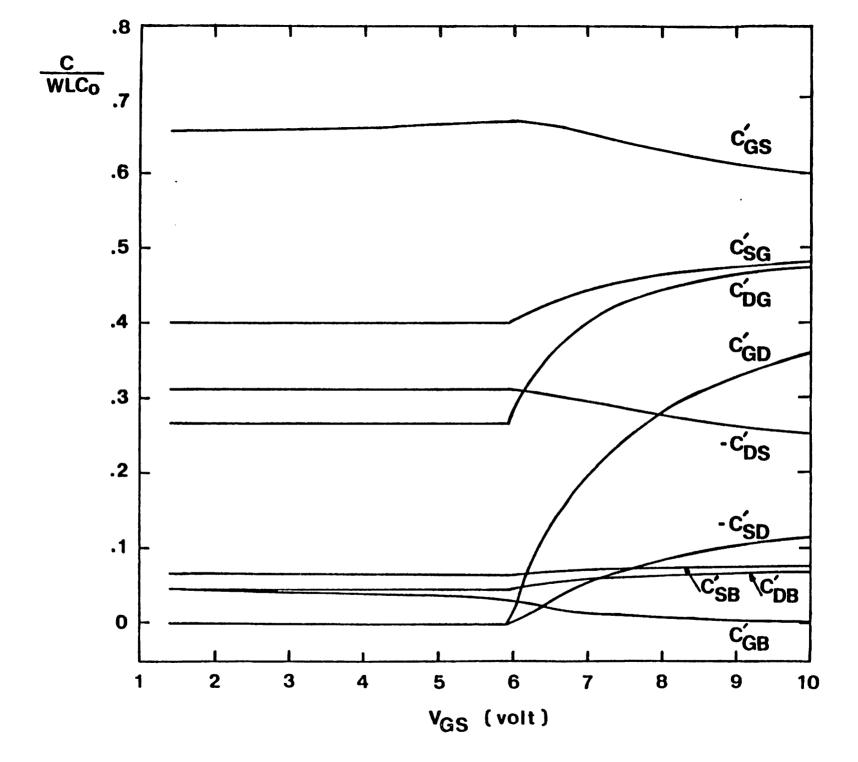

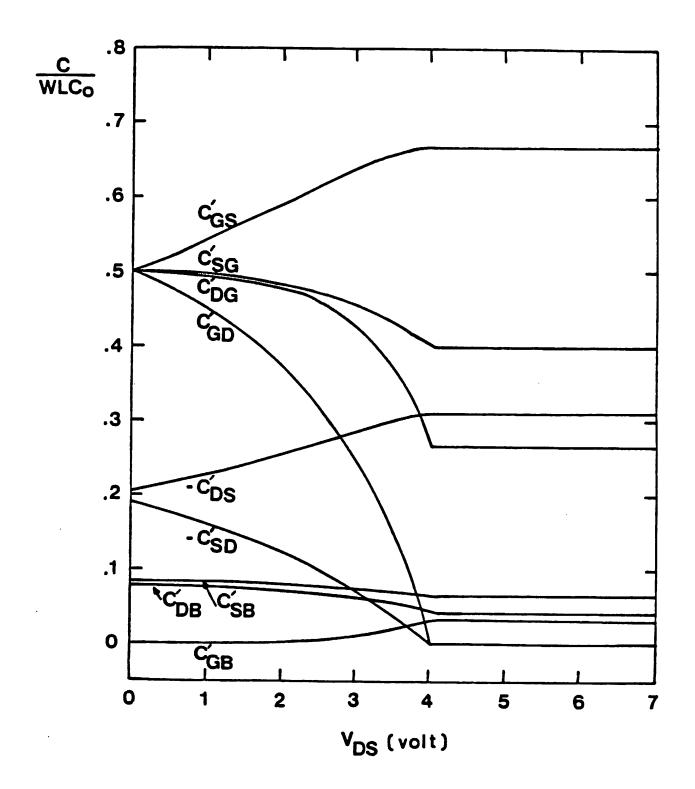

Fig. 1 shows the plots of the four normalized terminal charges. The dependence of normalized transcapacitive coefficients on the gate-source voltage and drain-source voltage are given in Fig. 2 and 3, respectively. Note that the charges and transcapacitive coefficients are all continuous at the boundary of the triode and saturation regions. Fig.4 compares theoretical calculations with the measurements given in [8] for a long channel device. Good agreement is found.

Of great significance in obtaining the accurate model for the charges and capacitances is the utilization of the Poon CSIM model [1], as extended [2], to model the DC characteristic and associated charge storage. Poon makes a close numerical approximation to the body effect. This simplies the DC characteristic model to a form similar to the Shichman-Hodges first order model. The charge and capacitance model also benifits from this approximation and has very simple expressions, as derived in this paper. This new set of IGFET model equations, with the DC characteristic part derived in [1],[2] and the charge-capacitance part derived here, is simple, accurate, and hence very suitable for circuit simulation applications.

### Acknowledgment

One of the authors, B. J. Sheu, wishes to thank Prof. Paul R. Gray for his continuous encouragement and many helpful discussions in the subject of charge storage in MOSFET's.

#### REFERENCES

- [1] S. Liu, L. W. Nagel, "Small-Signal MOSFET Models for Analog Circuit Design," IEEE Journal of Solid-State Circuits, vol. SC-17, no. 6, pp. 983-998, Dec. 1982.

- [2] B. J. Sheu, D. L. Scharfetter, and H. C. Poon, "Compact Short-Channel IGFET Model (CSIM)," Univ. of California, Berkeley, ERL memo, to be published.

- [3] D. E. Ward: "Charge-Based Modeling of Capacitance in MOS Transistor," Ph. D. Dissertation, Technical Report G 201-11, Integrated Circuit Laboratory, Stanford University, June 1981.

- [4] R. Conilogue, C. Viswanathan, "A Complete Large and Small Signal Charge Model for an M.O.S. Transistor," Tech. Dig. IEDM, pp. 654-657, 1982.

- [5] D. E. Ward, R. W. Dutton, "A Charge-Oriented Model for MOS Transient Capacitances," IEEE Journal of Solid-State Circuits, vol. SC-13, no. 5, pp. 703-707, Oct. 1978.

- [6] P. Yang, B. D. Epler, and P. K. Chatterjee, "An Investigation of the Charge Conservation Problem for MOSFET Circuit Simulation," IEEE Journal of Solid State Circuits, vol. SC-18, no. 1, pp. 128-139, Feb. 1983.

- [7] S.-Y. Oh, D. E. Ward, and R. W. Dutton, "Transient Analysis of MOS Transistors," IEEE Journal of Solid State Circuits, vol. SC-15, no. 4, pp. 636-643, Aug. 1980.

- [8] Y. Tsividis, "Problems with Precision Modeling of Analog MOS LSI," Tech. Dig. IEDM, pp. 274-277, 1982.

## Figure Captions

- Fig.1 Charges associated with gate, bulk, source, and drain terminals. The parameters are  $V_{BS}$ =0.0v,  $V_{DS}$ =1.0v, a=1.224,  $V_{th}$ =0.70v,  $K_1$ =0.633,  $\varphi_S$ =0.625.

- Fig.2 Normalized transcapacitive coefficients against gate-source voltage. The parameters are  $V_{BS}$ =-3.0v,  $V_{DS}$ =4.0v, a=1.131,  $V_{th}(V_{BS}$ =-3.0v)=1.40v,  $K_1$ =0.633,  $\varphi_S$ =0.625.

- Fig.3 Normalized transcapacitive coefficients against drain-source voltage. The parameters are  $V_{BS}$ =-3.0v,  $V_{CS}$ =6.0v, a=1.131,  $V_{th}(V_{BS}$ =-3.0v)=1.40v,  $K_1$ =0.633,  $\varphi_S$ =0.625.

- Fig.4 Comparison of several measured [8] and calculated transcapacitive coefficients against gate-source voltage. The parameters are  $V_{BS}$ =0.0v,  $V_{DS}$ =4.0v.

model

• • × A experiment