Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# NEGATIVE RESISTANCE CURVE TRACER

2

by

L. O. Chua and G-Q. Zhong

Memorandum No. UCB/ERL M84/29

9 April 1984

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## NEGATIVE RESISTANCE CURVE TRACER<sup>T</sup>

# Leon O. Chua and Guo-Qun Zhong<sup>++</sup>

### Department of Electrical Engineering and Computer Sciences and the Electronics Research Laboratory University of California, Berkeley, CA 94720

#### Abstract

Tracing the negative resistance characteristics of 2-terminal and 3-terminal devices often ended in failure due to jump phenomenon, hysteresis, and oscillation resulting from the tracing circuit. All of these problems are overcome in the curve tracer described in this paper. A detailed <u>nonlinear</u> dynamic circuit analysis is used to develop a simple method for quenching oscillations and other exotic phenomena.

Our curve tracer is designed to trace either <u>voltage-controlled</u> or <u>current-controlled</u> negative resistance characteristics of both 2-terminal and 3-terminal devices. All six representations which completely characterized a 3-terminal or 2-port nonlinear resistor are allowed. In particular, using a novel approach for implementing a nullator and norator, transmission (chain) characteristics of 3-terminal and 2-port devices have been successfully traced for the first time.

<sup>&</sup>lt;sup>†</sup>Research sponsored in part by the Office of Naval Research under Contract N00014-76-C-0572 and National Science Foundation Grant ECS-8313278.

<sup>&</sup>lt;sup>++</sup>Guo-Qun Zhong is a visiting scholar at the University of California, Berkeley, on leave from Guangzhou Research Institute of Electronic Technology, Academia Sinica. Guangzhou, People's Republic of China.

#### 1. INTRODUCTION

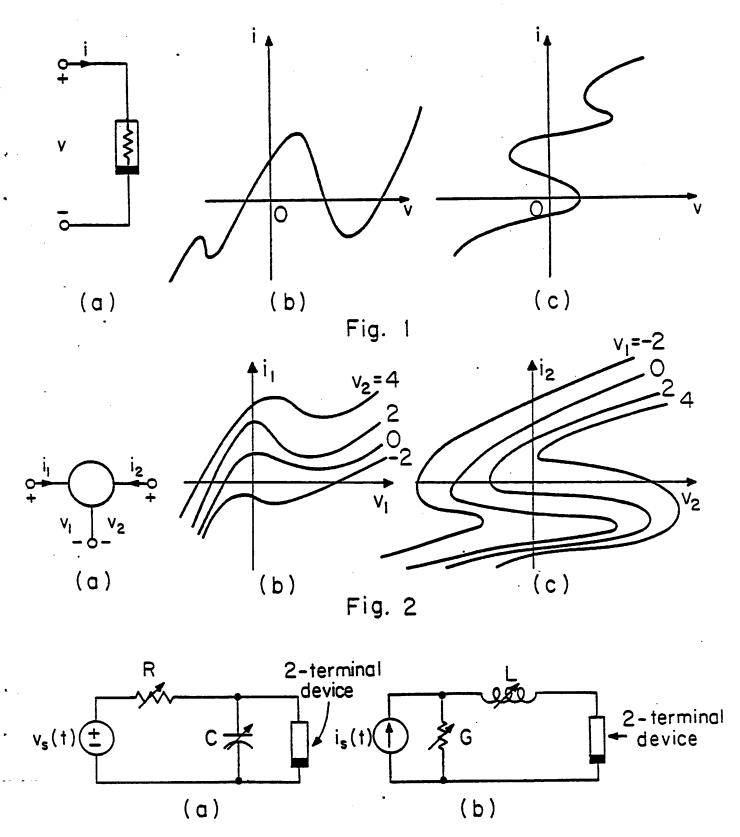

A 2-terminal negative resistance device (Fig. 1(a)) is one whose voltage versus current (v-i) characteristics exhibits a negative slope over some region of the device's operating range. Since the v-i characteristic of any <u>physical</u> device must eventually lie in the first and third quadrant (i.e., they must be eventually passive) even if the device is biased by batteries,<sup>†</sup> a 2-terminal negative-resistance device characteristic is either <u>voltage-controlled</u> (<u>type N</u>) as shown by the hypothetical curve in Fig. 1(b), or <u>current-controlled</u> (<u>type S</u>) as shown by the hypothetical curve in Fig. 1(c).

2

A 3-terminal negative resistance device (Fig. 2(a)) is one whose family of characteristics has at least one curve in the  $v_1 - i_1$  plane or  $v_2 - i_2$  plane exhibiting a negative slope region. A hypothetical example of a family of 3-terminal negative-resistance device characteristics is shown in Fig. 2(b) for the voltage-controlled type, and in Fig. 2(c) for the current-controlled type.

Numerous 2-terminal negative resistance devices have been reported in the literature, the most well known being the tunnel diode, which is a type N device, and a glow tube, which is a type S device. An extensive catalog of such devices is listed in [1]. Indeed, with the systematic method for designing negative resistance devices using existing solid state devices developed in [1-2], there is now available virtually thousands of such 2-terminal negative resistance devices.

Examples of 3-terminal negative resistance devices are also frequently reported, specially in the recent literature. For example, a 2- $\mu$ m gate length GaAs MESFET with N<sub>D</sub> = 6 × 10<sup>16</sup> cm<sup>-3</sup> has been observed to exhibit a voltage-controlled negative resistance characteristic [3]. An older example is the unijunction transistor which has a current-controlled negative resistance characteristic [4]. Indeed, with the recent advances in material technology on GaAs and other materials having a <u>negative</u> differential drift velocity versus electric field characteristic [4], many more 3-terminal negative resistance devices are emerging over the horizon. In addition, a systematic circuit approach for generating new 3-terminal negative resistance devices having a "tailored" characteristic has just been reported [5].

In spite of the existence of a wide variety of negative resistance devices, very few scope tracings of such characteristics have appeared in the literature.

<sup>&</sup>lt;sup>†</sup>This is because physical batteries have an internal resistance and are themselves eventually passive.

The reason is that the "negative resistance" often caused jump phenomenon, hysteresis, and oscillation in the tracing circuitry. Indeed, all commercially available curve tracers are based on the concept of applying a "sweeping" voltage source over the device's dynamic range and then monitoring the device current [6]. This technique will never work for <u>current controlled</u> devices because the load line representing the voltage source and its internal resistance will intersect their v-i characteristics (Figs. 1(c) and 2(c)) at several points during part of the tracing cycle, resulting at best in a jump phenomenon. This problem can be easily overcome by using a <u>current</u> source sweep instead. A much more serious problem is the perennial oscillation and instability that occur in many negative resistance devices.

Our objective in this paper is to design a curve tracer which is capable of tracing the voltage-controlled or current-controlled characteristics of both 2- and 3-terminal negative resistance devices. In the case of a 3-terminal device, our design will allow the device to be traced in any one fo the following six standard representations listed in Table 1.

| Current-controlled representation | Voltage-controlled representation |

|-----------------------------------|-----------------------------------|

| $v_1 = \hat{v}_1(i_1, i_2)$       | $i_1 = \hat{i}_1(v_1, v_2)$       |

| $v_2 = \hat{v}_2(i_1, i_2)$       | $i_2 = \hat{i}_2(v_1, v_2)$       |

| Hybrid-1 representation           | Hybrid-2 representation           |

| $v_1 = \hat{v}_1(i_1, v_2)$       | $i_1 = \hat{i}_1(v_1, i_2)$       |

| $i_2 = \hat{i}_2(i_1, v_2)$       | $v_2 = \hat{v}_2(v_1, i_2)$       |

| Transmission-1 representation     | Transmission-2 representation     |

| $v_1 = \hat{v}_1(v_2, -i_2)$      | $v_2 = \hat{v}_2(v_1, i_1)$       |

| $i_1 = \hat{i}_1(v_2, -i_2)$      | $-i_2 = \hat{i}_2(v_1, i_1)$      |

Table 1. Equations for the six representations of a 3-terminal or 2-port device

Whereas the methods for tracing the first 4 representations are a simple extension of the 2-terminal case, tracing the two <u>transmission</u> (<u>chain</u>) representations require some special techniques so that a voltage source <u>and</u> a current source can be simultaneously applied across the <u>same</u> pair of terminals! Indeed, to the best of our knowledge, no one has been able to trace the transmission characteristics of any 3-terminal or 2-port device before, let alone its negative resistance.

In order not to distract those readers interested only in using our tracer to trace negative resistance devices, the complete schematic diagram is first given in <u>Section 2</u> along with numerous examples illustrating its use. The theory for quenching the oscillation and instability is developed in <u>Section 3</u>. This theory is crucial to the successful design of our tracer. The special technique developed for tracing the <u>transmission</u> representation is described in <u>Section 4</u>. Details on the design of the various components of the complete curve tracer circuit in Section 2 are described in <u>Section 5</u> and in the <u>Appendix</u>.

P

8

### 2. THE CURVE TRACER: A USER'S GUIDE

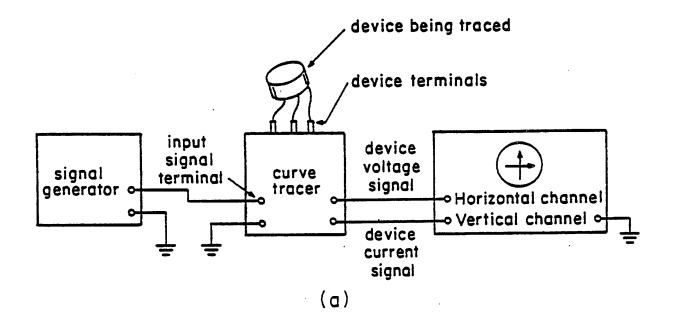

#### A. External Description

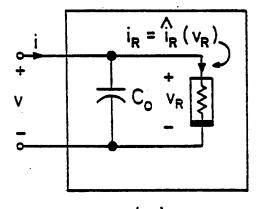

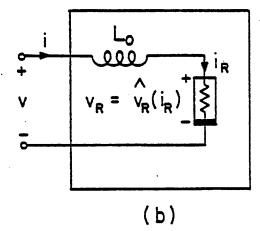

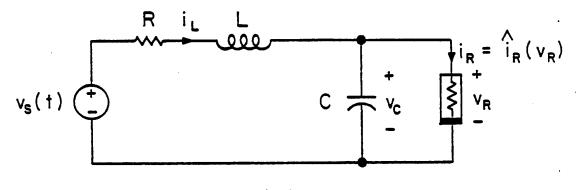

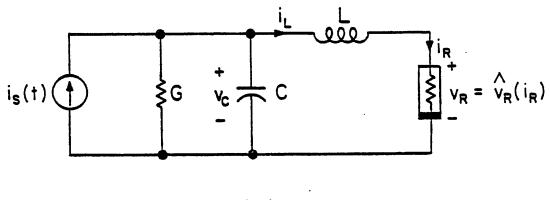

In its simplest form, the circuit for tracing a 2-terminal negative resistor is shown in Fig. 3(a) for the voltage-controlled case, and in Fig. 3(b) for the current-controlled case. The series resistance R in Fig. 3(a) can be interpreted as the internal resistance of the voltage source  $v_s(t)$  and should ideally be kept as small as possible. The shunt conductance G in Fig. 3(b) can be interpreted as the internal conductance of the current source  $i_s(t)$  and should should ideally be kept as small as possible.

The capacitance C in Fig. 3(a) and the inductance L in Fig. 3(b) are needed to quench any oscillation and other more complicated forms of instability. It will be shown in Section 3 that by choosing a <u>large enough</u> value of C and L, no instability will occur provided the tracing signal <u>frequency</u> is sufficiently small: The larger the value of C and L, the smaller the allowable frequency. Since too low a frequency would result in flicker in the oscilloscope tracing, a minimum frequency of 60 Hz is recommended. This implies that the value of C and L should be chosen as small as possible.

It will also be shown in Section 3 that there is a trade off between the values of R and C, and between G and L: increasing R over a limited range allows

-4-

us to decrease C and increasing G over a limited range allows us to decrease L. Since the trade off depends on the device characteristic itself, it is essential to allow both R and C in Fig. 3(a), and G and L in Fig. 3(b) to be <u>adjustable</u> externally.

The same basic circuits in Fig. 3 can be used to trace the negative resistance characteristics of a 3-terminal device (for the first 4 representations in Table 1) by simply applying a <u>staircase</u> voltage or current waveform to the other terminal. The increment in each step in the staircase signal determines the "spacing" between the curves in the family of characteristics. Since this choice depends on the nature of the device, the incremental step must also be externally adjustable.

Finally, since different devices have different dynamic ranges, the amplitude of the tracing signal  $v_s(t)$  and  $i_s(t)$  should also be adjustable.

To summarize, any general purpose curve tracer must have external switches and knobs for adjusting, at the very least, the following parameters:

| Voltage-controlled device          | Current-controlled device                    |  |

|------------------------------------|----------------------------------------------|--|

| 1. R                               | 1. G                                         |  |

| 2. C                               | 2. L                                         |  |

| 3. incremental step ∆i or ∆v       | 3. incremental step $\Delta v$ or $\Delta i$ |  |

| 4. amplitude of v <sub>s</sub> (t) | 4. amplitude of i <sub>s</sub> (t)           |  |

|                                    |                                              |  |

In addition, the following external terminals are needed:

- 1. Device terminals: for connecting 2-terminal or 3-terminal device being traced.

- Input signal terminals: to be connected to a periodic signal generator, usually a sinusoidal signal.

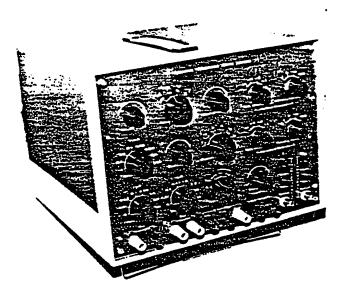

- 3. Output terminals: for connecting the device voltage signal to the horizontal plate and the device current signal to the vertical plate of the oscilloscope. A symbolic diagram illustrating how these terminals are connected in an actual measurement setup is shown in Fig. 4(a). A photograph of the curve tracer designed with the above features is shown in Fig. 4(b).

#### B. Complete Circuit Schematic Diagram

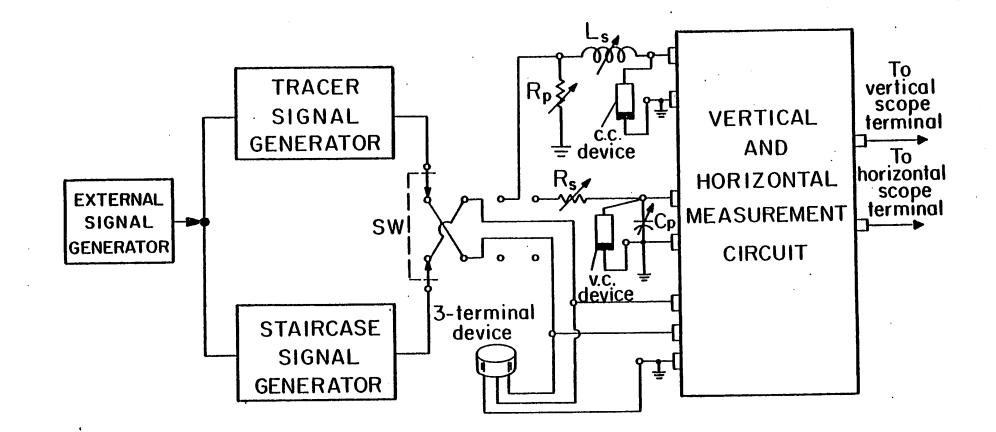

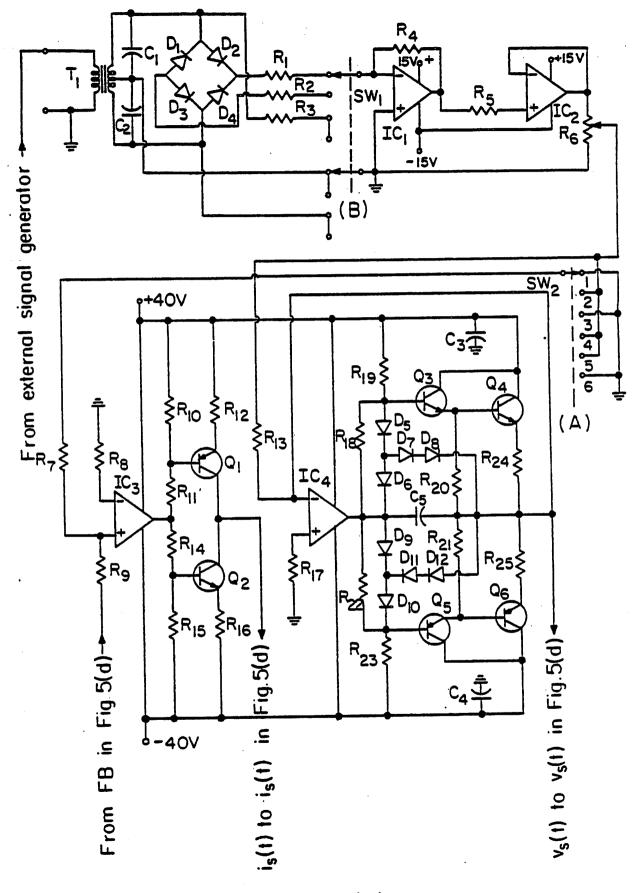

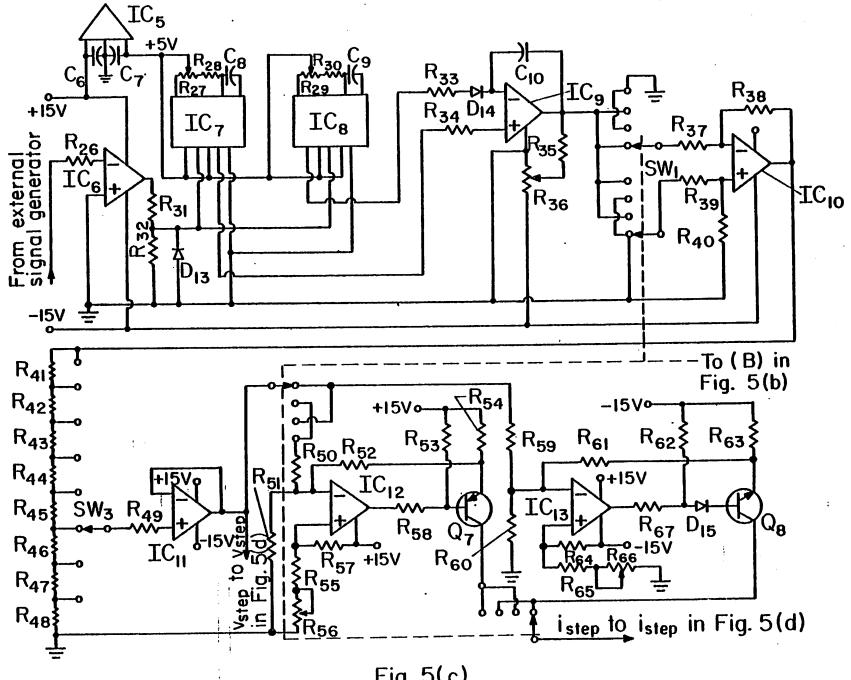

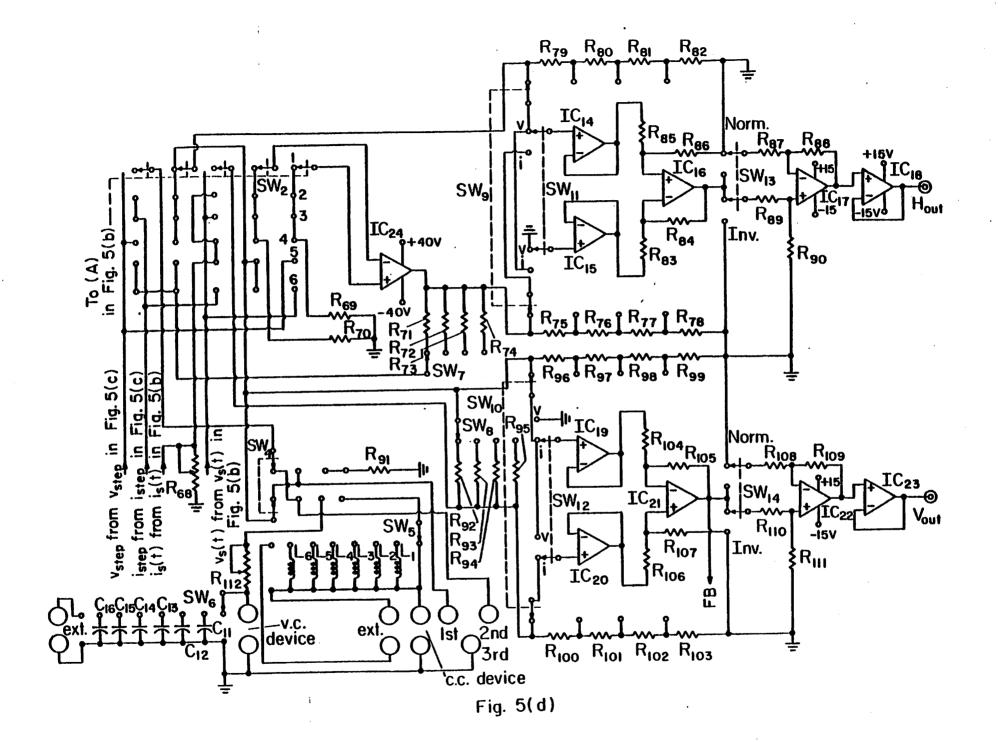

For users interested in building this curve tracer, a complete schematic diagram is shown in Figs. 5(a), (b), (c) and (d). For clarity purpose, this diagram is broken up into 3 parts and labelled as Figs. 5(b), (c) and (d), respectively. All components are clearly labelled for easy duplication. The complete list of components and their specifications are given in Appendix A.

The switches mounted on a common shaft are connected by dotted broken lines. For example, switch SW in Fig. 5(a) is a 2-pole 4-position switch mounted on a common shaft.

1

Fig. 5(a) is the block diagram of the curve tracer. It consists basically of three parts such as tracing signal generator, staircase signal generator and vertical and horizontal channel measurement circuit. There is a 2-pole 4-position switch sw which is used to switch the tracing signal and staircase signal to different terminals of the device being traced. Inductor  $L_s$  is used to adjust the inductance in series with current-controlled 2-terminal device. Potentiometer  $R_p$  is used to adjust the shunt resistance. Potentiometer  $R_s$  and capacitor  $C_p$  are used to adjust the resistance in series and capacitance in parallel with the voltage-controlled 2-terminal device being traced, respectively. The input signal for driving the tracer signal generator and the staircase signal generator are supplied by an external signal generator which is usually a sinusoidal signal generator. The output signals of the vertical and horizontal channel measurement circuit are applied to the vertical and horizontal terminals of the oscilloscope, respectively.

Figures 5(b), (c) and (d) form the complete circuitry of the curve tracer. Figure 5(b) shows the tracer signal generator circuit which transforms the input signal into a voltage source or current source having several optional waveforms (e.g., positive half sine wave, negative half sine wave, etc.) useful on various occasions.

Figure 5(c) shows the staircase signal generator circuit which is used to generate the voltage or current increment signals so that the <u>family</u> of characteristics describing a 3-terminal or 2-port device can be traced in a single measurement set up.

Figure 5(d) shows the vertical and horizontal channel measurement circuit which measures the current and the voltage associated with the device under test. Switch  $SW_2$  switches the different tracer and staircase signals to the associated terminals of the 3-terminal device so that the families of

-6-

characteristics associated with any one of the 6 representations of the device may be traced in a single set up. Position 1 (present position of the arrow in Fig. 5(d)), 2, 3 or 4 corresponds to selecting the voltage-controlled, current-controlled, hybrid-2 or hybrid-1 (as shown in Table 1) representation of the device. Position 5 or 6 corresponds to selecting the transmission-1 or transmission-2 representation of the device.

When tracing a 2-terminal voltage-controlled (type N) device,  $SW_2$  should be switched to position 1, and when tracing a 2-terminal current-controlled (type S) device,  $SW_2$  should be switched to position 2.

The position of switch  $SW_{11}$  and  $SW_{12}$  depends on whether voltage or current is measured, respectively, i.e., to measure the voltage across the associated terminals of the device, we set  $SW_{11}$  to position v, and to measure the current through the associated terminals of the device, we set  $SW_{11}$  to position i.

The banks of capacitors and inductors in Fig. 5(d) correspond to C and L in Figs. 3(a) and (b), respectively. An extra position (ext.) in each switch allows the user to connect a capacitor or inductor (whose value is not available internally) across an external terminal pair.

### C. Sample Tracings of 2-Terminal Negative Resistance Devices

Hundreds of negative resistance device characteristics have been successfully traced with our curve tracer. The following is a sample of some of these devices with interesting v-i characteristics. Most of these tracings require a "stabilizing" capacitance or inductance and could not have been traced by existing commercial curve tracers.

1. Voltage-controlled (type N) devices:

Figure 6(a) shows the scope tracing of a commercial 1N3717 tunnel diode (made by General Electric Co.) taken without the shunt capacitor in Fig. 3(a). Note that the negative resistance region looks like a mess although superficially its outline seems to suggest a smooth typical tunnel diode characteristic with a single peak and a single valley point [4]. Applying our theory from <u>Section 3</u>, we know the instability phenomenon in Fig. 6(a) can be quenched by connecting a sufficiently large capacitance C in parallel with the tunnel diode provided the frequency is low enough. The characteristic in Fig. 6(b) was successfully traced with a <u>40</u> Hz sinusoidal tracing signal and a 1  $\mu$ F shunt capacitance. This v-i curve came as a big surprise as it differs drastically

-7-

from the expected conventional tunnel diode characteristic.

To ensure that this v-i curve is indeed the true device characteristic, we have made a point-by-point  $\underline{dc}$  measurement and used multiple exposure to capture the points on film, as shown in Fig. 6(c). They coincide exactly with the "ac" tracing in Fig. 6(b). To ensure that the tracing circuit is not oscillating at a frequency beyond the bandwidth of our oscilloscope, we have checked the waveforms using a high frequency (200 MHz bandwidth) scope and found no discernible oscillation.

We have repeated our experiment with several other tunnel diodes (e.g., 1N3720) and found all of them to be characterized by a double-peak double-valley characteristic. We conclude therefore that at least for the batch of tunnel diodes we have traced, they are characterized by a v-i curve somewhat different from those published in textbooks. While this characteristic is more interesting and potentially more useful as a harmonic generator, any circuit design based on the conventional characteristic would clearly be in serious error!

t.

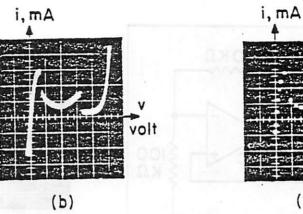

Consider next the voltage-controlled negative resistance one-port shown in Fig. 7(a). The v-i curve in Fig. 7(b) is traced without a shunt capacitance. Note the instability near the negative resistance region. By adding a 0.1  $\mu$ F shunt capacitance, we obtained the "clean" v-i curve in Fig. 7(c).

The preceding v-i characteristics lie in the first and third quadrants, as expected, since the devices are passive and unbiased.

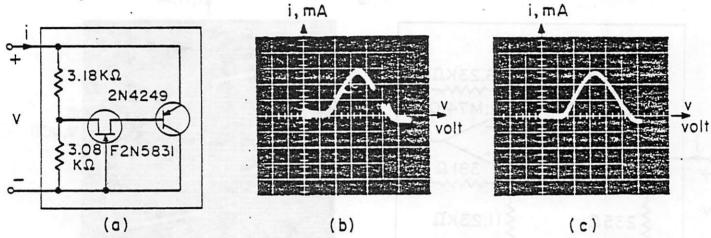

Consider next the 2-transistor one-port shown in Fig. 8(a) which is biased by a 10 V battery. The v-i curve in Fig. 8(b) is again all messed up. The clean characteristic in Fig. 8(c) is traced with a 0.1  $\mu$ F shunt capacitance. Note that unlike the previous characteristics, this device is not passive because there are points in the second and fourth quadrants. However, it is eventually passive, as expected.

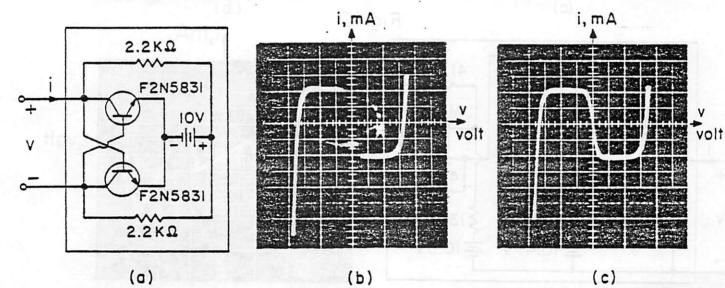

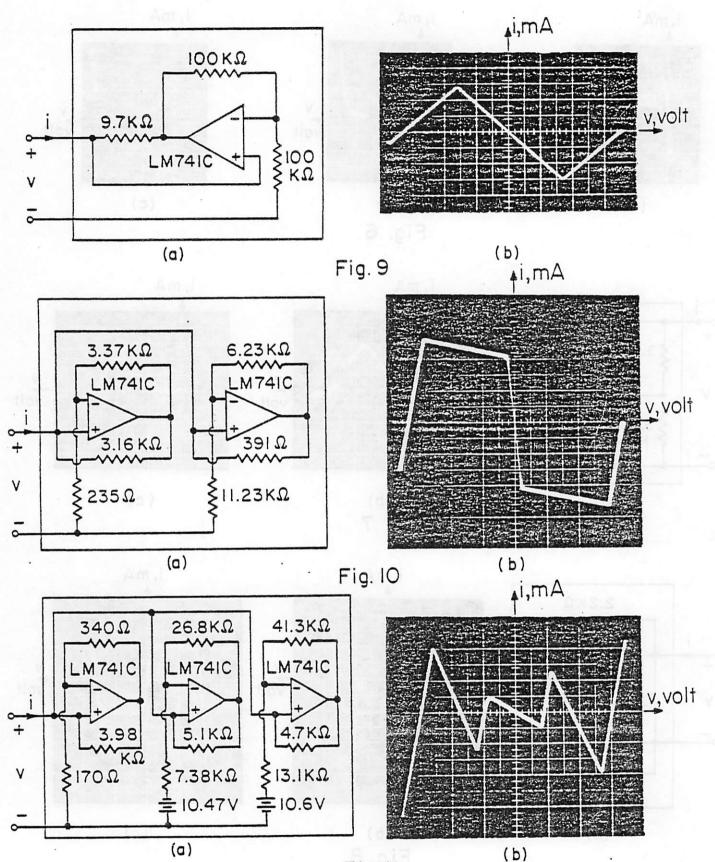

To show that the parameters of some negative resistance devices, especially those made of op amps, are such that a stable v-i characteristic can be traced without the shunt capacitance, three different op amp one-ports are shown in Fig. 9, 10 and 11, along with their respective voltage-controlled negative resistance characteristics.

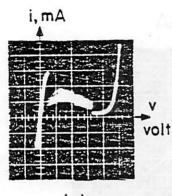

#### 2. Current-controlled (type S) devices:

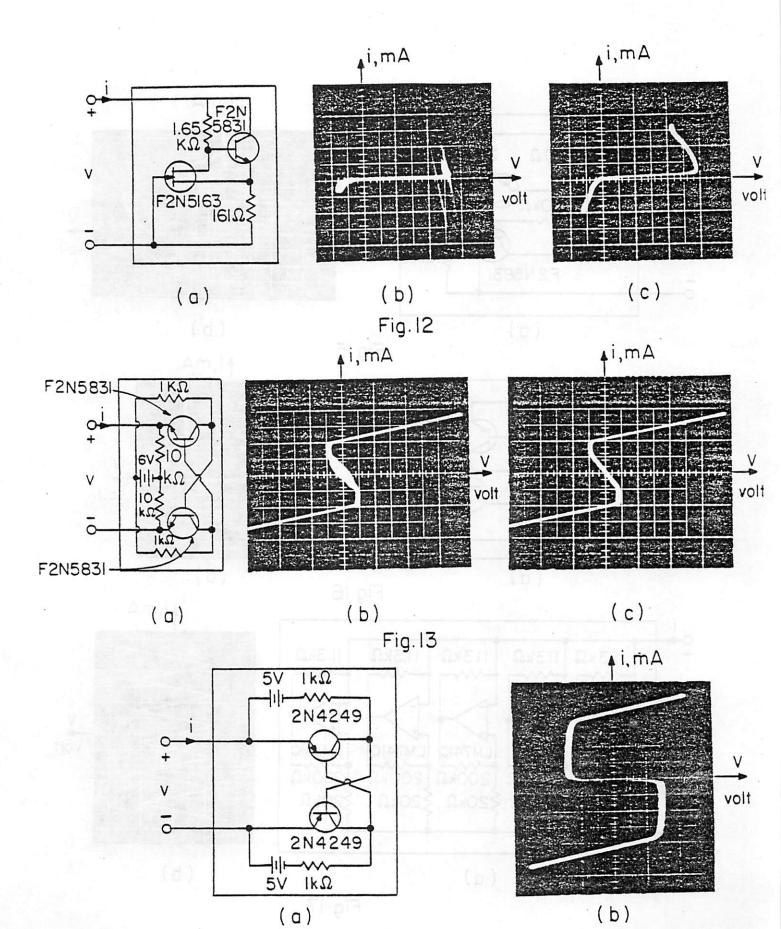

Consider the one-port shown in Fig. 12(a). Its v-i characteristic traced without a series inductance is shown in Fig. 12(b). Note the oscillation due to the tracing circuit wiped out the most interesting portion of the v-i

-8-

characteristic. The same one-port traced with a 2 mH series inductance and  $G = 8.8 \times 10^{-6}$  mho is shown in Fig. 12(c).

Consider next the two-transistor one-port shown in Fig. 13(a). Its v-i characteristic traced in Fig. 13(b) without a series inductance leads to oscillation within the negative resistance region. By connecting a 3 mH inductance in series, we obtain the sharp v-i characteristic in Fig. 13(c).

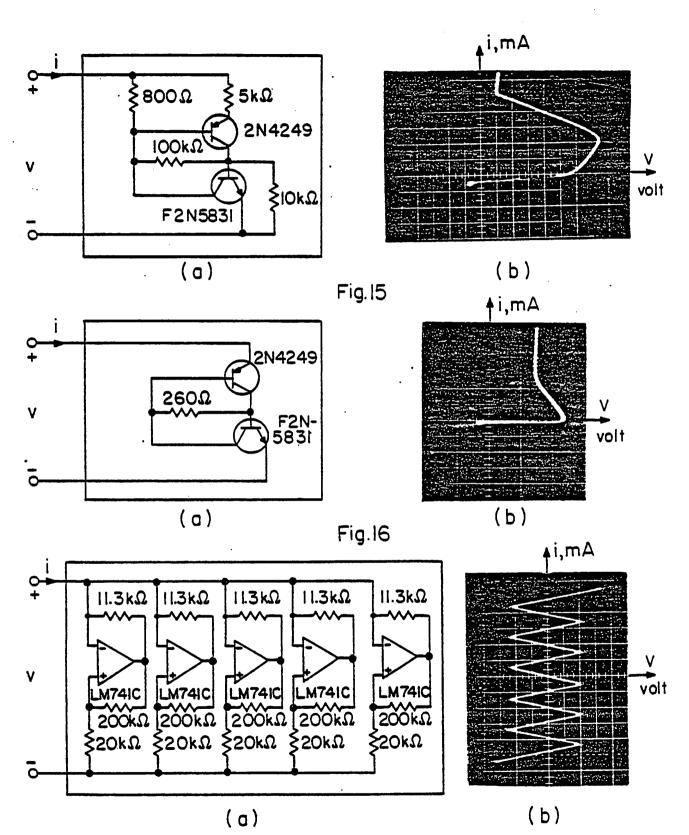

Figures 14 through 17 show 4 different current-controlled negative resistance one-ports which were successfully traced without a series inductance. Observe that none of the current-controlled characteristics in Figs. 12-17 could be obtained by commerical curve tracers based on a voltage sweep.

#### D. Sample Tracings of 3-Terminal or 2-Port Negative Resistance Devices.

Numerous 3-terminal and 2-port negative resistance devices have been succesfully traced using our curve tracer. The following is a sample of some of these devices.

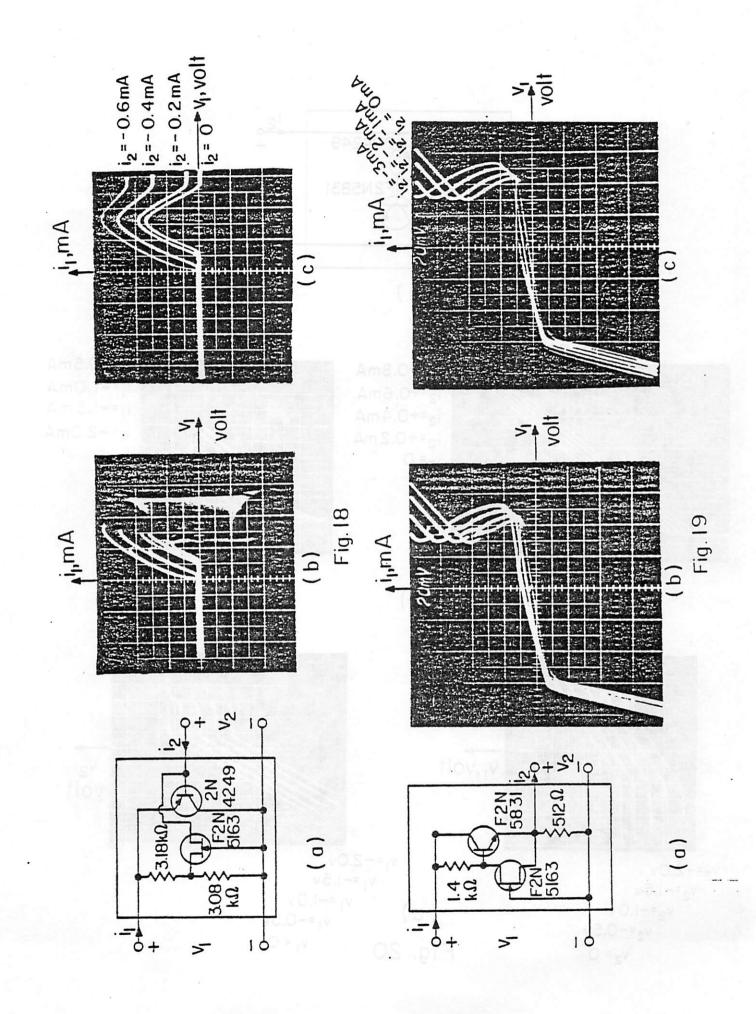

Consider the 2-port shown in Fig. 18(a). Tracing the v-i characteristics with  $i_2$  as a parameter (see hybrid-1 representation from Table 1) without a shunt capacitance, we obtain the messy characteristics in Fig. 18(b). Since each v-i curve in Fig. 18(b) is <u>voltage-controlled</u>, we can quench the oscillation by adding a shunt capacitance across port 1. The resulting family of characteristics  $i_1 = \hat{i}_1(v_1, i_2)$  is shown in Fig. 18(c).

Consider next the 2-port shown in Fig. 19(a). Tracing the  $i_1 - v_1$  characteristic with  $i_2$  as a parameter (see hybrid-1 representation from Table 1) without a series inductance, we obtained the messed up characteristics in Fig. 19(b). Since each v-i curve in Fig. 19(b) is <u>current-controlled</u>, we can quench the oscillation by adding an inductance in series with port 1. The resulting family of characteristics is shown in Fig. 19(c).

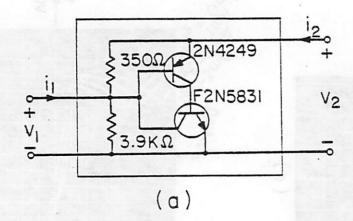

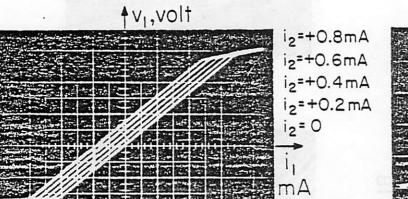

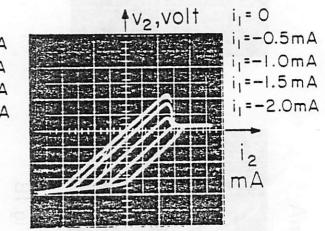

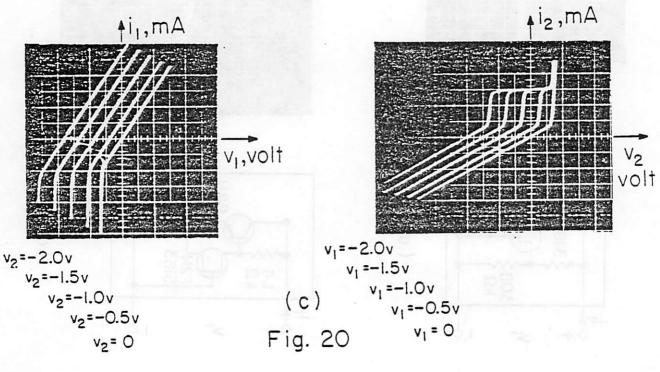

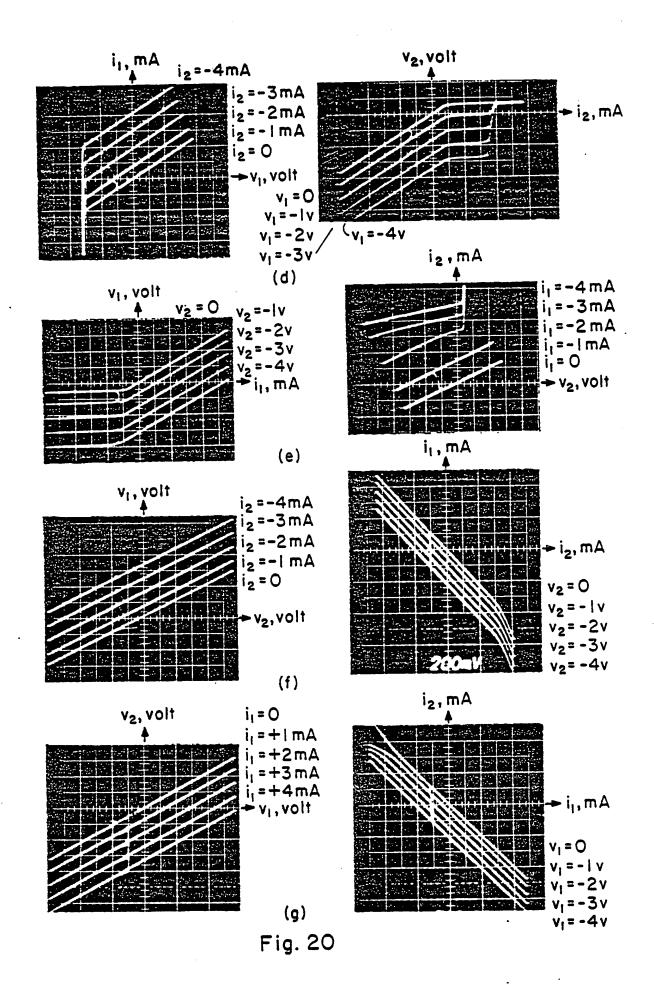

To demonstrate that our curve tracer can indeed trace the characteristics of a 3-terminal or 2-port device in any of the 6 representations, consider the two-transistor 2-port shown in Fig. 20(a). The 2 families of characteristics corresponding to each of the 6 distinct representations in Table 1 are shown in Figs. 20(b), (c), (d), (e), (f) and (g), respectively. These characteristics are all traced without any shunt capacitance or series inductance. The two transmission (chain) representations shown in Figs. 29(f) and (g) are as clear as the others, thereby demonstrating the possibility of tracing these two families of characteristics. To the best of our knowledge, this measurement had never been made before.

-9-

Just as the chain matrix is extremely useful in analyzing and designing two or more linear 2-ports connected in cascades, the possibility of measuring the <u>nonlinear</u> transmission characteristics could be equally useful in analyzing and designing nonlinear 2-ports connected in cascades. The resulting transmission characteristics in this case will be just the composition of the respective transmission characteristics.

#### 3. QUENCHING THE OSCILLATION

No physical device is purely resistive. The oscillation or other unstable behavior that often plagued the tracing circuitry is strictly a <u>dynamic</u> phenomenon and can only be quenched by carrying out a detailed analysis using a realistic dynamic circuit model for the device. Using a device physics approach [4] or a circuit-theoretic approach [7], we can derive the following basic result:

Negative Resistance Device Modeling Principle

- Every <u>voltage-controlled</u> (type N) negative resistance device must be modelled with a capacitor in parallel with a type N negative resistor, as shown in Fig. 21(a), and possibly additional dynamic elements at higher frequencies.

- Every current-controlled (type S) negative resistance device must modelled with an inductor in series with a type S negative resistor Fig. 21(b), and possibly additional dynamic elements at higher frequencies.

We have found the models given in Fig. 21 are adequate for our purpose in this paper.

In order to analyze and develop a method to quench oscillations and other instability phenomena frequently encountered in conventional curve tracers, we have found that it is necessary to include at least a series <u>parasitic</u> inductance  $L_p$  to the type N device model in Fig. 21(a), and a shunt parasitic capacitance  $C_p$  to the type S device model in Fig. 21(b), in order to account for the small but <u>non-zero</u> line inductance and stray capacitance of the connecting wires. Hence, the <u>simplest</u> realistic circuit model of our negative-resistance curve tracer is as shown in Fig. 22(a) for a type N curve tracer, and Fig. 22(b) for a type S curve tracer. Since these 2 circuits are <u>dual</u> of each other [8], we will analyze only the type N circuit.

The state equation for the type N curve tracer circuit model in Fig. 22(a) is given by

$$\frac{dVc}{dt} = \frac{1}{C} [i_L - \hat{i}_R (v_c)]$$

$$\frac{di_L}{dt} = \frac{1}{L} [v_s(t) - Ri_L - v_c]$$

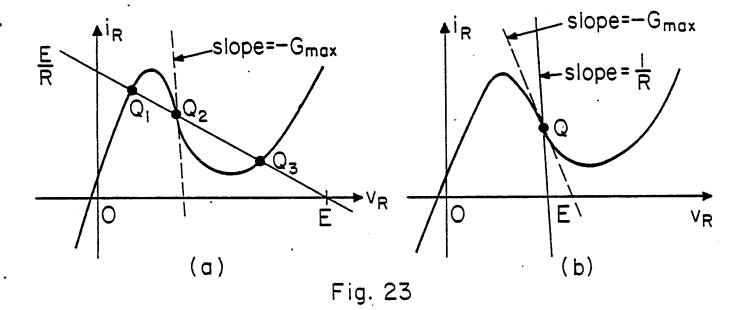

In order to uncover the source of the oscillation, it suffices to replace the voltage source  $v_s(t)$  by a battery E so that we can analyze the stability of each equilibrium point. For the circuit in Fig. 22(a), the equilibrium points are identical to the dc operating points obtained by the load line method, as illustrated in Fig. 23 using a typical tunnel diode v-i characteristic. Observe that there are 3 equilibrium points in Fig. 23(a) but only one in Fig. 23(b). The bifurcation parameter is given by

(1)

$$R = \frac{1}{G_{max}}$$

(2)

where

$G_{max} \triangleq magnitude$  of maximum negative slope of the  $v_R^{-i}$  characteristic (3)

In order for the curve tracer to work properly, it is <u>necessary</u> that each equilibrium point be <u>locally asymptotically stable</u> [8-9] for all values of E within the dynamic range of interest. To derive the conditions for satisfying this requirement, consider the Jacobian matrix associated with (1) about an equilibrium point Q:

$$\underbrace{J}_{Q} = \begin{bmatrix} -\frac{1}{C} \hat{i}_{R}^{\dagger}(V_{Q}) & \frac{1}{C} \\ -\frac{1}{L} & -\frac{R}{L} \end{bmatrix}$$

(4)

where  $\hat{i}_{R}^{\prime}(V_{Q})$  denotes the slope at  $v_{R} = V_{Q}$ . The necessary and sufficient conditions for the equilibrium point Q to be locally asymptotically stable are given by [8-9]:

$$T_{0} \triangleq -\frac{R}{L} - \frac{1}{C} \hat{i}_{R}(V_{0}) < 0$$

(5)

$$\Delta_{Q} \stackrel{\Delta}{=} \frac{R}{LC} \hat{i}_{R}^{\prime}(V_{Q}) + \frac{1}{LC} > 0$$

(6)

Since R > 0, L > 0, and C > 0, conditions (5) and (6) are always satisfied if  $\hat{i}_{R}^{\prime}(V_{0}) \geq 0$ . Hence all equilibrium points falling on the <u>non-negative</u> slope region of the  $v_R - i_R$  characteristic are always loacally asymptotically stable. This explains why it is easy to trace monotone-increasing v-i characteristics.

However, both (5) and (6) are easily violated in negative resistance characteristics especially when the negative slope is steep, i.e., when  $\hat{i}_{R}^{\prime}(V_{Q}) << 0$ . Since (5) and (6) must be satisfied at all operating points in the negative resistance region, the most critical situation occurs at the "steepest" point where the slope

$$\hat{i}_{R}'(V_{Q}) = -G_{max}$$

is <u>most negative</u>, where  $G_{max}$  as defined in (3) is a positive number. Using this notation, conditions (6) and (5) can be recast into (8) and (9), respectively, and restated in words as follows:

(7)

#### Stability Theorem

The necessary and sufficient conditions for all oeprating points of the type N curve tracer model in Fig. 22(a) to be locally asymptotically stable are:

$$R < \frac{1}{G_{max}}$$

$$R > (LG_{max}) \frac{1}{C}$$

(8)

(9)

Since  $G_{max}$  is fixed for a given device and L, being the parasitic inductance, can <u>not</u> be reduced below some minimum value, the conflicting demands of (8) and (9) often can not be satisfied by adjusting only the parameter R alone, especially when the negative slope is steep, as in the examples in Figs. 6-8. Observe, however, that so long as  $G_{max} < \infty$ , conditions (8) and (9) can always be satisfied by choosing a sufficiently large value for C. This is easily met by connecting an adjustable capacitance  $C_1$  <u>in parallel</u> with the device so that  $C = C_0 + C_1$ , as shown in Fig. 3(a).<sup>†</sup>

In the R-C parameter plane, conditions (8) and (9) define the stable region shown in Fig. 24(a) for a typical value of L. The <u>minimum</u> capacitance  $C_{min}$  needed to quench the oscillation occurs at the intersection between the

<sup>&</sup>lt;sup>†</sup>Since  $C_0$  is very small in a typical device,  $C = C_0 + C_1 \approx C_1$ . Hence we will neglect  $C_0$  from our subsequent discussion for simplicity.

two bifurcation curves  $\Delta = 0$  and T = 0. Note that the shaded region shifts to the right as L increases, as shown in Fig. 24(b) for a somewhat larger value of L. Hence  $C_{\min}$  increases with L.

To minimize  $C_{min}$ , therefore, we must keep the connecting wires as short as possible.

Choosing the parameters R and C within the shaded region in Fig. 24 guarantees that the equilibrium point will be either a <u>stable node</u> or a <u>stable</u> <u>focus</u> [8] for each dc input voltage E.

For each equilibrium point  $V_c = V_q$  and each initial condition  $V_c(0)$ , the transient decay rate is determined by the <u>real</u> part  $\sigma$  of the eigenvalues

$$s_{1,2} = -\frac{1}{2} \left[ \frac{R}{L} + \frac{\hat{i}_{R}^{\dagger}(V_{Q})}{C} \right] \pm \frac{1}{2} \sqrt{\left[ \frac{R}{L} + \frac{\hat{i}_{R}^{\dagger}(V_{Q})}{C} \right]^{2}} - \frac{4}{LC} \left[ R\hat{i}_{R}^{\dagger}(V_{Q}) + 1 \right]$$

(10)

if  $V_{\rm C} = V_{\rm Q}$  is a focus, or by the <u>smaller</u> real natural frequency  $\sigma$  (corresponding to choosing the negative sign in (10)) if  $V_{\rm C} = V_{\rm Q}$  is a node. A typical relationship between  $\sigma$  and C as calculated from (10) using a fixed value for R, L and  $\hat{i}_{\rm R}'(V_{\rm O})$  is shown in Fig. 25. Note that  $|\sigma|$  is largest at C = C<sub>opt</sub>.

Now the transient will for all practical purposes be negligible after 5 time constants  $\tau$ , where  $\tau = \frac{1}{|\sigma|}$ . Hence, it is possible to trace the v-i characteristic using a <u>periodic</u> ac voltage source v<sub>s</sub>(t) provided its frequency  $\omega$  is chosen so that

$$\omega < \frac{1}{5} |\sigma| \tag{11}$$

Since  $\sigma = 0$  when  $C = C_{\min}$  in Fig. 25, where  $C_{\min}$  corresponds to the intersection between the two bifurcation curves T = 0 and  $\Delta = 0$  in Fig. 24(a), it follows from (11) that we must choose C greater than  $C_{\min}$ . The maximum allowable frequency occurs when we choose  $C = C_{opt}$ . Any larger value of C must be accompanied by a decrease in  $\omega$ . We can now summarize our preceding analysis as follows:

Oscillation Quenching Guidelines for Type N Device (Fig. 3(a)) 1. Choose R <  $\frac{1}{G_{max}}$ . 2. Choose C > C<sub>min</sub>.

- Decreasing R must be accompanied by an increase in C.

- Increasing C beyond Cont must be accompanied by a decrease in the tracing frequency ω.

By duality, we can state:

- Oscillation Quenching Guidelines for Type S Device (Fig. 3(b)) 1. Choose G <  $\frac{1}{R_{max}}$ , where  $R_{max}$  is the magnitude of the slope of  $\hat{v}'_{R}(i_{R})$  at its steepest point.

- Choose L >  $L_{min}$ , where  $L_{min}$  corresponds to  $C_{min}$  in Fig. 24(a). 2.

- Decreasing G must be accompanied by an increase in L. 3.

- 4. Increasing L beyond L<sub>opt</sub> must be accompanied by a decrease in the tracing frequency  $\omega,$  where  $L_{\mbox{opt}}$  corresponds to  $C_{\mbox{opt}}$  defined above.

#### 4. TRACING THE TRANSMISSION REPRESENTATION

The two transmission representations listed in Table 1 are the nonlinear generalization of the well-known chain matrix representations for linear timeinvariant 2-ports, namely,

|                     | transmission-l                                                                                                                                                | transmission-2                                                                                                                                                |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| linear<br>2-port    | $\begin{bmatrix} v_1 \\ i_1 \end{bmatrix} = \begin{bmatrix} t_{11} & t_{12} \\ t_{21} & t_{22} \end{bmatrix} \begin{bmatrix} v_2 \\ -i_2 \end{bmatrix} (12a)$ | $\begin{bmatrix} v_2 \\ -i_2 \end{bmatrix} = \begin{bmatrix} t_{11} & t_{12} \\ t_{21} & t_{22} \end{bmatrix} \begin{bmatrix} v_1 \\ i_1 \end{bmatrix} (12b)$ |

| nonlinear<br>2-port | $v_1 = \hat{v}_1 (v_2, -i_2)$ (13a)<br>$i_1 = \hat{i}_1 (v_2, -i_2)$                                                                                          | $v_{2}^{'} = \hat{v}_{2}(v_{1}, i_{1})$<br>$-i_{2} = \hat{i}_{2}(v_{1}, i_{1})$ (13b)                                                                         |

The two matrices in Eqs. (12a) and (12b) are called <u>chain matrices</u>.<sup> $\dagger$ </sup> The transmission representation is most conveniently used when two or more linear 2-ports are connected in cascade. In this case the transmission matrix of the composite 2-port is just the product of the respective chain matrices. Likewise, when two or more resistive 2-ports are connected in cascade, the transmission representation of the composite 2-port is just the composition of the respective This remarkable property is of immense help in both transmission functions.

<sup>†</sup>The chain matrix in Eq. (12a) is usually denoted by

in the literature.

analysis and design.

Unfortunately, manufacturers never specify a nonlinear 3-terminal device by its transmission representation. The reason is simple: no measurement technique, let alone a dedicated instrument, is available.

One obstacle here is due to the fact that <u>both</u> independent variables ( $v_2$  and  $-i_2$  in the transmission 1 representation;  $v_1$  and  $i_1$  in the transmission 2 representation) in Eqs. (13a) and (13b) pertain to the same port.

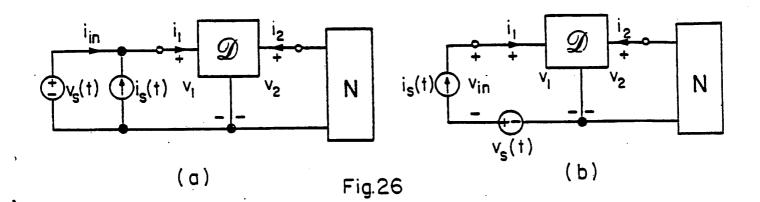

For example, to measure the transmission 2 representation, it is necessary to apply an independent voltage source  $v_s(t)$  and an independent current source  $i_s(t)$  to port 1 of the 3-terminal device D so that  $v_1 = v_s(t)$  and  $i_1 = i_s(t)$ . The only two ways for connecting these two sources <u>directly</u>, as shown in Fig. 26, are not feasible because whereas  $v_1 = v_s(t)$  in Fig. 26(a),  $i_1 \neq i_s(t)$ unless  $i_{in} \equiv 0$ ; and whereas  $i_1 = i_s(t)$  in Fig. 26(b),  $v_1 \neq v_s(t)$  unless  $v_{in} \equiv 0$ .

Another serious obstacle is encountered at port 2; namely, the load N in Fig. 26 must <u>not</u> present any constraint between the two <u>dependent</u> port variables  $v_2$  and  $i_2$  because both  $v_2$  and  $i_2$  are defined <u>uniquely</u> by the transmission functions via Eq. (13b). Note that open circuiting port 2 is not allowed because  $i_2$  would then be constrained to zero. Likewise, short circuiting port 2 is not allowed because  $v_2$  would then be constrained to zero. In fact, N can <u>not</u> be any ordinary one-port because such a one-port would be described by a relationship between  $v_2$  and  $i_2$ , thereby creating an implicit constraint between these two <u>dependent</u> variables.

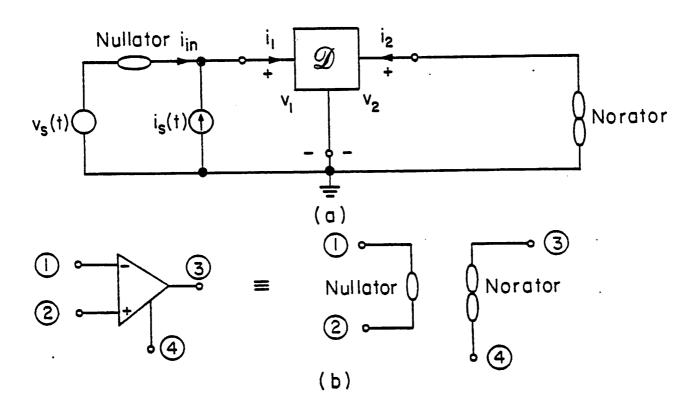

The first obstacle can be overcome by inserting a <u>nullator</u><sup>†</sup> in series with the voltage source  $v_s(t)$  as shown in Fig. 27(a), thereby clamping  $i_{in} = 0$ . Moreover, since the voltage across the nullator is zero, we still have  $v_1 = v_s(t)$ .

The second obstacle can be overcome by choosing the load N to be a norator,<sup>††</sup> as shown in Fig. 27(b). Since this element imposes no constraint in either  $v_2$  or  $i_2$ , the port current  $i_2$  and port voltage  $v_2$  depend only on  $v_1$  and  $i_1$ . Hence, the norator is functioning like a "slack" variable in linear programming.

Although individually, nullators and norators can not be realized by any physical circuit, together they can be simulated by an op amp operating in its linear region, as shown by the ideal op amp model in Fig. 27(b). Hence,

<sup>&</sup>lt;sup>†</sup>The <u>nullator</u> is a <u>singular</u> circuit element defined by a single point at the origin, namely, v = 0, i = 0 [10-11].

<sup>&</sup>lt;sup>++</sup>A <u>norator</u> is a <u>singular</u> circuit element defined by all points in the v-i plane [10-11].

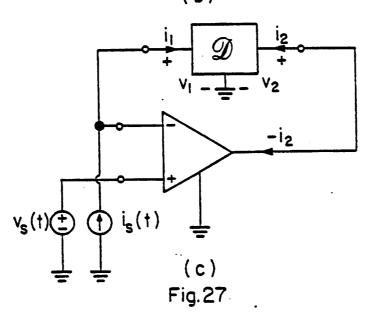

replacing the nullator and norator in Fig. 27(b) by an op amp, we obtain the practical circuit in Fig. 27(c) for tracing the transmission 2 characteristics of a 3-terminal device  $\mathcal{D}$ .

To trace the <u>transmission 2</u> characteristics of a 3-terminal device  $\mathcal{D}$  using the circuit in Fig. 27(c), we first apply the signal  $v_s(t)$  to the horizontal channel and the signal  $v_2$  to the vertical channel of the oscilloscope. A staircase signal  $i_s(t)$  is then applied to obtain the first family of characteristics; namely,  $v_2 = \hat{v}_2(v_1, i_1)$ . To obtain the second family of transmission characteristics, we repeat the above measurement but with  $i_2(t)$  applied to the vertical channel through a small current sensing resistor.

To obtain the <u>transmission 1</u> characteristics, we simply use the same circuit in Fig. 27(c) but with terminal 1 and 2 of the 3-terminal device D interchanged. The transmission characteristics shown in Figs. 19 and 20 are all measured using this simple tracing circuit. Our experience has shown that this circuit is rather robust and stable, in spite of the fact that the nullator and norator are highly pathological. This circuit is also interesting because it illustrates how a purely abstract concept can become indispensable in the design of a practical circuit. Indeed, we do not know of any other way for measuring the transmission characteristics.

#### 5. DESIGN DETAILS

As mentioned above in Section 2, the complete circuit of the curve tracer consists basically of three parts: the tracer signal generator, the staircase signal generator and the vertical and horizontal channel measurement circuit. The tracer signal generator shown in Fig. 5(b) includes a full-wave rectifier, an amplifier, a voltage source, and a current source. Push-pull transformer  $T_1$  is used to apply the signal from the external signal generator to the full-wave rectifier consisting of four diodes  $D_1$ ,  $D_2$ ,  $D_3$  and  $D_4$ . Capacitors  $C_1$  and  $C_2$  are used to avoid potential parasitic oscillations. The load of the full-wave rectifier is a voltage amplifier IC<sub>1</sub> which has different gain for different waveforms so that the amplitudes of tis output voltages will be basically the same when the input voltage of the push-pull transformer  $T_1$  is constant. The output stage IC<sub>2</sub> is a buffer.

The operational amplifier  $IC_3$  amplifies the input signal from switch  $SW_2$ . The output voltage of  $IC_3$  is applied to transistors  $Q_1$  and  $Q_2$ . Transistor  $Q_1$  will conduct when the input voltage of  $IC_3$  is negative, and  $Q_2$  will conduct when the input voltage of  $IC_3$  is positive, respectively. The feedback of  $IC_3$  is from the output current of the tracer current source via resistor  $R_0$ .

The high-voltage op amp  $IC_4$  amplifies the input signal from potentiometer  $R_6$ . Meanwhile,  $SW_2$  will ground the input terminal of  $IC_3$  so that the current source will not interfere with other circuits. Transistors  $Q_3$  and  $Q_5$  are the driver stages of the tracer voltage source, and transistors  $Q_4$  and  $Q_6$  are the power output stages of the tracer voltage source. Transistors  $Q_3$  and  $Q_4$  will conduct when the input signal of  $IC_4$  is negative, and  $Q_5$  and  $Q_6$  will conduct when the input signal of  $IC_4$  is positive, respectively. Diodes  $D_5$ ,  $D_6$ ,  $D_9$  and  $D_{10}$  provide biasing for the output stages, and  $D_7$ ,  $D_8$ ,  $D_{11}$  and  $D_{12}$  are used for overload protection. Resistors  $R_{24}$  and  $R_{25}$  connected to the emitters of  $Q_4$  and  $Q_6$ , respectively, are current-limiting resistors.

Figure 5(c) shows the circuit diagram of the staircase signal generator which consists of three parts: the staircase voltage generator, the staircase voltage source, and the staircase current source.  $IC_6$ ,  $IC_7$ ,  $IC_8$ , and  $IC_9$  form the staircase voltage generator. The op amp  $IC_6$  is used as a zero-crossing detector. The input signal of  $IC_6$  is the same as that of transformer  $T_1$  in the tracer signal generator so that the staircase signal is synchronized to the tracing signal.

The output pulses of the zero-crossing detector are used as triggers for the monostable multivibrators  $IC_7$  and  $IC_8$ . The negative output pulses of  $IC_6$ will be clipped by diode  $D_{13}$ .  $IC_5$  is a +5 volt regulator that is used as a DC power supply for the monostable multivibrators  $IC_7$  and  $IC_8$ . The output (positive) pulses of  $IC_7$  charge capacitor  $C_{10}$  of the integrator (formed by  $IC_9$ , resistor  $R_{34}$  and capacitor  $C_{10}$ ) to generate a staricase voltage between the output terminals of  $IC_9$ . The output (positive) pulses of  $IC_8$  will discharge the integrator so that a periodic staircase voltage will be obtained. By adjusting the width of output pulses of  $IC_7$  (by adjusting potentiometer  $R_{27}$ ), we can change the "increment" in the steps. The "number" of steps can be changed by adjusting the width of the output pulses of  $IC_8$  (by adjusting potentiometer  $R_{29}$ ).

Diode  $D_{14}$  is used to avoid a premature discharge of the capacitor  $C_{10}$  while generating the step voltages. The network formed by resistor  $R_{35}$  and potentiometer  $R_{36}$  is used to adjust the zero step of the output staircase voltage of the integrator. Op amp IC<sub>10</sub> and IC<sub>11</sub> form a voltage source with positive and negative voltage output. In fact, IC<sub>10</sub> is used as a phase

-17-

inverter and  $IC_{11}$  is a voltage follower. There is a voltage divider between  $IC_{10}$  and  $IC_{11}$  to change the step increment. The positive step voltage from the integrator is fed to the inverting input or non-inverting input of  $IC_{10}$  by switch  $SW_1$  so that positive and negative step voltages can be obtained. Op amp  $IC_{12}$  and transistor  $Q_7$  with the associated resistors form a positive staircase current source to which the positive staircase voltage from  $IC_{11}$  is applied through  $SW_1$ . Potentiometer  $R_{56}$  is used to adjust the zero step of the positive staircase current signal. Op amp  $IC_{13}$  and transistor  $Q_8$  with the associated resistors form a positive staircase current signal.

Figure 15(d) is the circuit diagram of the vertical and horizontal channel measurement circuit. In fact, the vertical and horizontal channels are basically the same. To improve the precision of the measurement circuit, we use JFET input quad op amp followers  $IC_{14}$ ,  $IC_{15}$ ,  $IC_{19}$  and  $IC_{20}$  as the input stages of these two channels so that the current through the device being traced will be almost equal to that through the current sensing resistor. There are four voltage dividers formed by resistors  $R_{75}-R_{78}$ ,  $R_{79}-R_{82}$ ,  $R_{96}-R_{99}$  and  $R_{100}-R_{103}$ , respectively, so that the op amp followers  $IC_{14}$ ,  $IC_{15}$ ,  $IC_{19}$  and  $IC_{20}$  would not saturate within the dynamic range of the device being traced. The division factors are 1, 2, 5 and 10, respectively. Hence, the input voltages of these followers will be reduced by 1, 2, 5 or 10 times so that the voltage amplitude displayed on the scope is equal to 1,  $\frac{1}{2}$ ,  $\frac{1}{5}$ , or  $\frac{1}{10}$  of the actual amplitude of the output voltage, depending on the positions of the switches  $SW_q$  and  $SW_{10}$ . When measuring current through the device being traced, the voltage across the current sensing resistor  $R_{92}-R_{95}$  (or  $R_{71}-R_{74}$ ) is applied to the differential amplifier  $IC_{21}$  (or  $IC_{16}$  for the horizontal channel). Current sensing resistors  $R_{71}-R_{74}$  and  $R_{92}-R_{95}$ are both chosen equal to 1 K, 500, 100 and 10 ohm, respectively. Hence, there is 1,2,10 and 100 mA of current through the device being traced for a 1 volt voltage across the resistors, respectively, depending on the positions of the switches SW7 and  $SW_8$ . Op amp  $IC_{22}$  (or  $IC_{17}$ , for the horizontal channel), is a phase inverter. Op amp  $IC_{23}$  (or  $IC_{18}$  for the hosizontal channel) is a voltage follower serving as the output stage of the curve tracer. The polarities of the output signals of the vertical and horizontal channel can be changed by switches  $SW_{14}$  and  $SW_{13}$ , respectively. While measureing voltage, switch  $SW_{12}$  (or  $SW_{11}$  for the horizontal

channel) will ground the inverting input of the differential amplifier  $IC_{21}$  (or  $IC_{16}$ , in horizontal channel).

Op amp IC<sub>24</sub> is playing the role of both nullator and norator when tracing the transmission characteristics of a 3-terminal device.

Potentiometer  $R_{68}$  is used as the shunt resistance in the tracing current source, and inductors  $L_1$  through  $L_6$  are connected in series with the device being traced, respectively. Both the shunt resistance and inductance are used to quench the oscillation when tracing a current-controlled 2-terminal device. Similarly, the potentiometer  $R_{112}$  connected in series and capacitors  $C_{11}$  through  $C_{16}$  connected in parallel with the device, respectively, are used to quench the oscillation when tracing a voltage-controlled 2-terminal device, as already described in Section 3.

#### REFERENCES

- [1] L. O. Chua, J-B Yu, and Y-Y Yu, "Negative resistance devices," <u>Interna-</u> <u>tional Journal of Circuit Theory and Applications</u>, Vol. 11, 1983, pp. 161-186.

- [2] L. O. Chua, J-B Yu, and Y-Y Yu, "Bipolar-JFET-MOSFET negative resistance devices," <u>IEEE Trans. on Circuits and Systems</u>, to appear in 1985.

- [3] J. J. Barnes, R. J. Lomax, and G. I. Haddad, "Finite element simulation of GaAs MESFET's with lateral doping profiles and submicron gates," <u>IEEE</u> <u>Trans. on Electron Devices</u>, Vol. ED-23, Sept., 1976, pp. 1042-1048.

- [4] S. M. Sze, <u>Physics of Semiconductor Devices</u>, John Wiley & Sons, New York, 1981.

- [5] J-B Yu, C-Q Zhang, and Z-S Kang, "Controlled negative resistance devices," <u>International Symposium on Circuits and Systems</u>, May 7-10, 1984, Montreal, Canada.

- [6] J. Mulvey, <u>Semiconductor Device Measurements</u>, Tektronix, Inc., Beaverton, Oregon, 1968.

- [7] L. O. Chua, "Device Modelling via Basic Nonlinear Circuit Elements," <u>IEEE</u> <u>Trans. on Circuits and Systems</u>, Vol. CAS-27, November, 1980, pp. 1014-1044.

- [8] L. O. Chua, <u>Introduction to Nonlinear Network Theory</u>, McGraw Hill Book Company, New York, 1969.

- [9] L. O. Chua, "Dynamic nonlinear network: state-of-the-art," <u>IEEE Trans. on</u> Circuits and Systems, Vol. CAS-27, Nov. 1980, pp. 1059-1087.

- [10] H. J. Carlin and A. B. Giordano, <u>Netowrk Theory</u>, Prentice Hall, Inc., Englewood Cliffs, New Jersey, 1964.

- [11] L. Bruton, <u>RC Active Circuits: Theory and Design</u>, Prentice Hall, Inc., Englewood Cliffs, New Jersey, 1980.

# APPENDIX A: THE CATALOG OF COMPONENTS

•

| Part No.                         | Model Description           | Part No.                         | Model Description             |

|----------------------------------|-----------------------------|----------------------------------|-------------------------------|

| R <sub>1</sub>                   | 10 KΩ ± 10% 1/4 W           | R <sub>33</sub>                  | 3 KΩ ± 10% 1/4 W              |

| R <sub>2</sub>                   | 10 KΩ ± 10% 1/4 W           | R <sub>34</sub>                  | 30 KΩ ± 10% 1/4 W             |

| R <sub>3</sub>                   | 62 KΩ ± 10% 1/4 W           | R <sub>35</sub>                  | 2.2 K $\Omega$ ± 10% 1/4 W    |

| R <sub>4</sub>                   | 330 KΩ ± 10% 1/4 W          | <sup>R</sup> 36                  | 10 K $\Omega$ potentiometer   |

| R <sub>5</sub>                   | 20 KΩ ± 10% 1/4 W           | R <sub>37</sub>                  | 100 KΩ ± 10% 1/4 W            |

| R <sub>6</sub>                   | 10 K $\Omega$ potentiometer | <sup>R</sup> 38                  | 100 KΩ ± 10% 1/4 W            |

| R <sub>7</sub>                   | 10 KΩ ± 10% 1/4W            | R <sub>39</sub>                  | 100 KΩ ± 10% 1/4 W            |

| R <sub>8</sub>                   | 10 KΩ ± 10% 1/4 W           | R <sub>40</sub>                  | 100 KΩ ± 10% 1/4 W            |

| R <sub>9</sub>                   | 100 KΩ ± 10% 1/4 W          | R <sub>41</sub>                  | 500 KΩ ± 1% 1/4 W             |

| R10                              | 3.9 KΩ ± 10% 1/4 W          | R <sub>42</sub>                  | 300 KΩ ± 1% 1/4 W             |

| R <sub>11</sub>                  | 22 KΩ ± 10% 1/4 W           | R <sub>43</sub>                  | 100 KΩ ± 1% 1/4 W             |

| R <sub>12</sub>                  | 680 $\Omega$ ± 10% 1/2 W    | R <sub>44</sub>                  | 50 KΩ ± 1% 1/4 W              |

| <sup>R</sup> 13                  | 10 KΩ ± 10% 1/4 W           | R <sub>45</sub>                  | 30 KΩ ± 1% 1/4 W              |

| <sup>R</sup> 14                  | 22 KΩ ± 10% 1/4 W           | 45<br>R <sub>46</sub>            | 10 KΩ ± 1% 1/4 W              |

| R <sub>15</sub>                  | 3.9 KΩ ± 10% 1/4 W          | <sup>40</sup><br><sup>R</sup> 47 | 5 KΩ ± 1% 1/4 W               |

| R <sub>16</sub>                  | 680 Ω ± 10% 1/2 W           | R <sub>48</sub>                  | 5 KΩ ± 1% 1/4 W               |

| R <sub>17</sub>                  | 10 KΩ ± 10% 1/4 W           | <sup>48</sup><br><sup>R</sup> 49 | 20 KΩ ± 10% 1/4 W             |

| R <sub>18</sub>                  | 2.2 KΩ ± 10% 1/2 W          | <sup>4</sup> 50                  | $1~M_{\Omega}~\pm~10\%~1/4~W$ |

| R <sub>19</sub>                  | 22 KΩ ± 10% 1/2 W           | 851                              | 100 KΩ ± 10% 1/4 W            |

| R <sub>20</sub>                  | 100 Ω ± 10% 1/2 W           | R <sub>52</sub>                  | $1 M\Omega \pm 10\% 1/4 W$    |

| R <sub>21</sub>                  | 100 $\Omega$ ± 10% 1/2 W    | <sup>52</sup><br><sup>R</sup> 53 | 20 KΩ 1 10% 1/4 W             |

| R <sub>22</sub>                  | 2.2 KΩ ± 10% 1/2 W          | <sup>8</sup> 54                  | 1KΩ± 10% 1/4 W                |

| R <sub>23</sub>                  | 22 KΩ ± 10% 1/2 W           | R <sub>55</sub>                  | 91 KΩ ± 10% 1/4 W             |

| R <sub>24</sub>                  | 1Ω±10%,1W                   | <sup>8</sup> 56                  | 10 K $\Omega$ potentiometer   |

| R <sub>25</sub>                  | ΙΩ±10%ΙW                    | <sup>8</sup> 57                  | $1 M\Omega \pm 10\% 1/4 W$    |

| <sup>25</sup><br><sup>R</sup> 26 | 20 KΩ ± 10% 1/4 W           | <sup>57</sup><br><sup>R</sup> 58 | 20 KΩ ± 10% 1/4W              |

| <sup>R</sup> 27                  | 10 K $\Omega$ trimpot       | <sup>56</sup><br><sup>R</sup> 59 | 1 MΩ ± 10% 1/4 W              |

| R <sub>28</sub>                  | 100 $\Omega$ ± 10% 1/4 W    | <sup>8</sup> 60                  | 100 KΩ ± 10% 1/4 W            |

| 28<br>R <sub>29</sub>            | 50 K $\Omega$ trimpot       | 80<br>R <sub>61</sub>            | $1 M\Omega \pm 10\% 1/4 W$    |

| <sup>29</sup><br><sup>R</sup> 30 | 1 KΩ± 10% 1/4 W             | R <sub>62</sub>                  | 20 KΩ ± 10% 1/4 W             |

| 80<br>R <sub>31</sub>            | 10 KΩ ± 10% 1/4 W           | 62<br>R <sub>63</sub>            | 1 KΩ ± 10% 1/4 W              |

| R <sub>32</sub>                  | 5.6 KΩ ± 10% 1/4 W          | <sup>R</sup> 64                  | $1 M\Omega \pm 10\% 1/4 W$    |

| •                                                                  |                                            | · •                                                |                                   |

|--------------------------------------------------------------------|--------------------------------------------|----------------------------------------------------|-----------------------------------|

|                                                                    | •                                          |                                                    |                                   |

|                                                                    |                                            |                                                    |                                   |

| Part No.                                                           | Model Description                          | Part No.                                           | Model Description                 |

| R <sub>65</sub>                                                    | 91 KΩ ± 10% 1/4 W                          | <sup>R</sup> 108                                   | 30 KΩ ± 1% 1/4 W                  |

| R <sub>66</sub>                                                    | 10 K $\Omega$ potentiometer                | <sup>R</sup> 109                                   | 30 KΩ ± 1% 1/4 W                  |

| R <sub>67</sub>                                                    | 20 KΩ ± 10% 1/4 W                          | R <sub>110</sub>                                   | 30 KΩ ± 1% 1/4 W                  |

| R <sub>68</sub>                                                    | l MΩ potentiometer                         | R <sub>111</sub>                                   | 30 KΩ ± 1% 1/4 W                  |

| R <sub>69</sub>                                                    | 30 KΩ ± 10% 1/4 W                          | c                                                  | 0.1 µF 100V DC ceramic            |

| <sup>R</sup> 70                                                    | 30 KΩ ± 10% 1/4 W                          |                                                    | 0.1 μF 100V DC ceramic            |

| <sup>7</sup> 0<br><sup>R</sup> 71                                  | 1 KΩ ± 1% 1/2 W                            | ດ້                                                 | 0.1 $\mu$ F 100V DC ceramic       |

| R <sub>72</sub>                                                    | 500 Ω ± 1% 1/4 W                           | с <sub>2</sub><br>с <sub>3</sub><br>с <sub>4</sub> | 0.1 μF 100V DC ceramic            |

| R <sub>73</sub>                                                    | 100 Ω ± 1% 1/4 W                           | C <sub>5</sub>                                     | 0.01 μF 100V DC ceramic           |

| R <sub>74</sub>                                                    | 10 Ω ± 1% 1/4 W                            | с <sub>5</sub><br>с <sub>6</sub>                   | 0.2 $\mu\text{F}$ 100V DC ceramic |

| <sup>74</sup><br><sup>R</sup> 75, <sup>R</sup> 79                  |                                            | С <sub>7</sub>                                     | 0.1 $\mu\text{F}$ 100V DC ceramic |

| <sup>R</sup> 96 <sup>, R</sup> 100                                 | $5~M\Omega~\pm~1\%~1/4~W$                  | Ċ,                                                 | 0.01 $\mu$ F 100V DC ceramic      |

|                                                                    |                                            | с <sub>7</sub><br>с <sub>8</sub><br>с <sub>9</sub> | 10 $\mu$ F 20V DC tantalum        |

| <sup>R</sup> 76 <sup>, R</sup> 80                                  | 3 MΩ ± 1% 1/4 W                            | с <sub>10</sub>                                    | 0.01 µF 100V DC ceramic           |

| <sup>R</sup> 97 <sup>, R</sup> 101                                 | ·                                          | C <sub>11</sub>                                    | 0.01 $\mu$ F 100V DC ceramic      |

| R <sub>77</sub> , R <sub>81</sub>                                  |                                            | C <sub>12</sub>                                    | 0.05 µF 100V DC ceramic           |

| <sup>R</sup> 98 <sup>, R</sup> 102                                 | $1 M\Omega \pm 1\% 1/4 W$                  | C <sub>13</sub>                                    | 0.1 μF 100V DC ceramic            |

| R <sub>78</sub> , R <sub>82</sub>                                  |                                            | <sup>13</sup><br><sup>C</sup> 14                   | 0.56 $\mu$ F 100V DC orange drop  |

| <sup>R</sup> 99 <sup>, R</sup> 103                                 | 1 M $_{\Omega}$ ± 1% 1/4 W                 | C <sub>15</sub>                                    | 1 $\mu$ F 100V DC orange drop     |

| <sup>R</sup> 83 <sup>,R</sup> 84                                   | 30 KΩ ± 1% 1/4 W                           | <sup>15</sup><br><sup>C</sup> 16                   | 2.2 $\mu F$ 50V DC tantalum       |

| R <sub>85</sub>                                                    | 30 KΩ ± 1% 1/4 W                           |                                                    | 0.01 mH fixed inductor            |

| <sup>R</sup> 86                                                    | 30 KΩ ± 1% 1/4 W                           |                                                    | 0.1 mH fixed inductor             |

| <sup>R</sup> 87 <sup>, R</sup> 88                                  | <b>30 KΩ ± 1% 1/4 W</b>                    | L <sub>3</sub>                                     | 0.47 mH fixed inductor            |

| <sup>8</sup> / <sup>3</sup> 88<br><sup>8</sup> 89 <sup>,8</sup> 90 | 30 KΩ ± 1% 1/4 W                           |                                                    | ] mH fixed inductor               |

| <sup>R</sup> 112                                                   | l KΩ precision potentiometer               | L <sub>5</sub>                                     | 2.2 mH fixed inductor             |

| <sup>R</sup> 91                                                    | 1 KΩ ± 10% 1/4 W                           | L <sub>6</sub>                                     | 10 mH fixed inductor              |

| <sup>R</sup> 91                                                    | 1 KΩ ± 1% 1/2 W                            | о<br>Т <sub>1</sub>                                | 1:1 push-pull transformer         |

| <sup>R</sup> 93                                                    | 500 $\Omega$ ± 1% 1/4 W                    | D <sub>1</sub> -D <sub>4</sub>                     | 1N4448 100 mA 75 volt             |

| <sup></sup> 93<br><sup>R</sup> 94                                  | $100 \ \Omega \pm 1\% \ 1/4 \ W$           | D <sub>5</sub> -D <sub>12</sub>                    | 1N4003 1 A 200 volt               |

| <sup>R</sup> 95                                                    | $10 \ \Omega \pm 1\% \ 1/4 \ W$            | D <sub>13</sub>                                    | 1N34a Germanium diode             |

| <sup>8</sup> 95<br><sup>R</sup> 104                                | 30 KΩ ± 1% 1/4 W                           | D <sub>14</sub>                                    | 1N4448 100 mA 75 volt             |

| _                                                                  | $30 \text{ K}\Omega \pm 1\% 1/4 \text{ W}$ | D <sub>15</sub>                                    | 1N4448 100 mA 75 volt             |

| R <sub>105</sub>                                                   | $30 \text{ K}\Omega \pm 1\% 1/4 \text{ W}$ | Q <sub>1</sub>                                     | 2N4888 Si pnp transistor          |

| <sup>R</sup> 106<br><sup>B</sup>                                   | 30 KΩ ± 1% 1/4 W                           | Q <sub>2</sub>                                     | F2N5831 Si npn transistor         |

| <sup>R</sup> 107                                                   |                                            | 72                                                 |                                   |

..

ŝ

| Part No.         | Model Description                 | Part No.         | Model Description    |

|------------------|-----------------------------------|------------------|----------------------|

| Q <sub>3</sub>   | 2N3666 Si npn transistor          | IC <sub>10</sub> | LM741C               |

| Q <sub>4</sub>   | 2N5979 Si npn power trans.        | IC               | LM741C               |

| 9 <sub>5</sub>   | 2N4033 Si pnp transistor          | IC <sub>12</sub> | 1/4 LM2900n quad amp |

| Q <sub>6</sub>   | 2N5976 Si pnp power trans.        | IC <sub>13</sub> | LM741C               |

| Q <sub>7</sub>   | 2N4249 Si pnp transistor          | IC <sub>14</sub> | 1/4 TL074C quad amp  |

|                  | F2N5831 Si npn transistor         | IC <sub>15</sub> | 1/4 TL074c           |

| 98<br>101<br>101 | LM741C \ general purpose          | IC <sub>16</sub> | 1/4 TL074C           |

| IC <sub>2</sub>  | LM741C∫ op amp                    | IC <sub>17</sub> | 1/4 TL074C           |

|                  | LM143H high voltage op amp        | IC <sub>18</sub> | 1/4 TL074C           |

| IC <sub>4</sub>  | LM143H high voltage op amp        | IC <sub>19</sub> | 1/4 TL074C           |

| IC <sub>5</sub>  | LM340-5 +5 <sup>V</sup> regulator | IC <sub>20</sub> | 1/4 TL074C           |

| IC <sub>6</sub>  | LM741C                            | IC <sub>21</sub> | 1/4 TL074C           |

|                  | 74121 ( monostable                | IC <sub>22</sub> | 1/4 TL074C           |

| 10 <sup>8</sup>  | 74121∫ multivibrator              | IC <sub>23</sub> | 1/4 TL074C           |

|                  | 1/4 LM2900n quad amp              | IC <sub>24</sub> | LM143H               |

#### FIGURE CAPTIONS

- Fig. 1. (a) A 2-terminal device with associated reference directions for vand i.

- (b) A hypothetical voltage-controlled negative resistance device.

- (c) A hypothetical current-controlled negative resistance device.

- Fig. 2. (a) A 3-terminal device with associated reference directions for  $v_1$ ,  $v_2$ ,  $i_1$  and  $i_2$ .

- (b) A hypothetical family of voltage-controlled negative resistance characteristics.

- (c) A hypothetical family of current-controlled negative resistance characteristics.

- Fig. 3. (a) Basic circuit for tracing a voltage-controlled negative resistance device.

- (b) Basic circuit for tracing a current-controlled negative resistance device.

- Fig. 4. (a) Set up for actual measurement.

- (b) Photograph of curve tracer.

- Fig. 5. (a) Block diagram of curve tracer.

- (b) Tracer signal generator circuit.

- (c) Staircase signal generator circuit.

- (d) Vertical and horizontal measurement circuit. (a) Unstable tracing of a 1N3717 tunnel diode without shunt capacitor. Fig. 6. (b) v-i characteristic traced by a 40 Hz sinusoidal signal with a 1  $_{

m UF}$ shunt capacitance.

- (c) v-i characteristic traced by a point-by-point dc measurement with a 1 µF shunt capacitance. All curves are traced with the same series resistance  $R = 6 \Omega$ . Horizontal scale: 0.2 volts per division, Vertical scale: 3.3 mA per division.

- Fig. 7. (a) One-port made of a pnp transistor and an n-channel JFET.

- (b) Unstable tracing without shunt capacitor.

- (c) Stable tracing with 0.1  $\mu$ F shunt capacitance. All curves are traced with the same series resistance R = 5  $\Omega$ . Horizontal scale: 2 volts per division, Vertical scale: 20 mA per division.

- (a) One-port made of 2 npn transistors and a battery. Fig. 8.

- (b) Unstable tracing without shunt capacitor. (c) Stable tracing with 0.1  $\mu$ F shunt capacitance. All curves are traced with the same series resistance  $R = 5 \Omega$ . Horizontal scale: 0.4 volts per division, Vertical scale: 4 mA per division.

- Fig. 9. (a) One-op-amp negative-resistance one-port. (b) v-i characteristic traced without shunt capacitance;  $R = 100 \Omega$ . Horizontal scale: 4 volts per division, Vertical scale: 0.5 mA per division.

- Fig. 10. (a) Two-op-amp negative resistance one-port.

- (b) v-i characteristic traced without shunt capacitor;  $R = 100 \Omega$ . Horizontal scale: 4 volts per division. Vertical Scale: 2.5 mA per division.

- (a) Three-op-amp negative resistance one-port. Fig. 11.

- (b) v-i characteristic traced without shunt capacitor; R = 100  $\Omega$ .

| Fig. 12       | Horizontal scale: 4 volts per division.<br>Vertical scale: 0.5 mA per division.<br>. (a) A current-controlled negative resistance one-port made of an npn                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -             | transistor and an n-channel JFET.<br>(b) v-i characteristic traced without series inductance.                                                                                                       |

|               | (c) v-i characteristic traced with 2 mH series inductance.                                                                                                                                          |

|               | All curves are traced with $G = 8.8 \times 10^{-6}$ mho.<br>Horizontal scale: 2 volts per division.                                                                                                 |

| Fig. 13       | Vertical scale: 10 mA per division.<br>(a) A current-controlled negative resistance one-port made of 2 npn                                                                                          |

| <b>J</b>      | transistors.                                                                                                                                                                                        |

|               | <pre>(b) v-i characteristic traced without series inductor.<br/>(c) v-i characteristic traced with 3 mH series inductance.</pre>                                                                    |

|               | All curves are traced with $G = 8.8 \times 10^{-6}$ mho.                                                                                                                                            |

|               | Horizontal scale: 1 volt per division.                                                                                                                                                              |

| Fig. 14       | Vertical scale: 0.5 mA per division.<br>. (a) A current-controlled negative resistance one-port made of 2 pnp                                                                                       |

| 119.14        | transistors                                                                                                                                                                                         |

|               | (b) v-i characteristic traced without series inductance; G = 8.8 x 10 <sup>-1</sup> mho<br>Horizontal scale: 0.4 volt per division.                                                                 |

| Fig. 15       | Vertical scale: 2 mA per division.<br>. (a) A current-controlled negative resistance one-port made of an npn                                                                                        |

|               | transistor and a nun transistor                                                                                                                                                                     |

|               | (b) v-i characteristic traced without series inductor; $G = 8.8 \times 10^{-6}$ mho.                                                                                                                |

|               | Horizontal scale: 2 volts per division.<br>Vertical scale: 0.5 mA per division.                                                                                                                     |

| Fig. 16       | (a) A current-controlled negative resistance one-port made of an npn<br>and a npn transistor                                                                                                        |

|               | (b) v-i characteristic traced without series inductor; G = 8.8 x 10 <sup>-0</sup> mho.<br>Horizontal scale: 0.4 volts per division.                                                                 |

| Fig. 17       | Vertical scale: 2 mA per division.<br>(a) A current-controlled negative resistance one-port made of five                                                                                            |

| J             | OD-amps                                                                                                                                                                                             |

|               | <ul> <li>(b) v-i characteristic traced without series inductor; G=8.8 x 10<sup>-6</sup> mho.</li> <li>Horizontal scale: 1 volt per division.</li> <li>Vertical scale: 5 mA per division.</li> </ul> |

| Fig. 18       | 3. (a) A voltage-controlled negative resistance 2-port.                                                                                                                                             |

|               | (b) $v_1-i_1$ characteristics (with $i_2$ as parameter) traced without shunt                                                                                                                        |

|               | capacitor.                                                                                                                                                                                          |

|               | (c) v <sub>1</sub> -i <sub>1</sub> characteristics (with i <sub>2</sub> as parameter) traced with 0.1 μF capacitor; R = 10 Ω.                                                                       |

|               | Horizontal scale: 2 volts per division.                                                                                                                                                             |

|               | Vertical scale: 20 mA per division.                                                                                                                                                                 |

| <b>Fig</b> 10 | Current step: -0.2 mA per step.                                                                                                                                                                     |

| Fig. 19       | <ul> <li>(a) A current-controlled negative resistance 2-port.</li> <li>(b) v<sub>1</sub>-i<sub>1</sub> characteristics (with i<sub>2</sub> as parameter) traced without series</li> </ul>           |

|               | inductance.                                                                                                                                                                                         |

|               | <pre>(c) v<sub>1</sub>-i<sub>1</sub> characteristics (with i<sub>2</sub> as parameter) traced with 6.7 mH<br/>series inductance; G = 8.8 x 10<sup>-6</sup> mho.</pre>                               |

|               | Horizontal scale: 1 volt per division.                                                                                                                                                              |

|               | Vertical scale: 2 mA per division.                                                                                                                                                                  |

•

•

ş

.

Fig. 20. (a) A 2-port made of a pnp transistor and an npn transistor. (b) Current-controlled representation. Horizontal scale: 1 mA per division. Vertical scale: 5 volts per division. (c) Voltage-controlled representation. Horizontal scale: 1 volt per division. Vertical scale:  $i_1$ : 2 mA per division,  $i_2$ : 5 mA per division. (d) Hybrid-1 representation. Horizontal scale:  $v_1$ : 5 volts per division,  $i_2$ : 4 mA per division. Vertical scale:  $i_1$ : 2 mA per division,  $v_2 = 2.5$  volts per division. (e) Hybrid-2 representation. Horizontal scale:  $i_1$ : 4 mA per division,  $v_2$ : 2 volts per division. Vertical scale:  $v_1$ : 2.5 volts per division,  $i_2$ : 1 mA per division. (f) Transmission-1 representation. Horizontal scale:  $v_2$ : 0.5 volt per division,  $i_2$ : 1 mA per division. Vertical scale:  $v_1$ : 1 volt per division,  $i_1$ : 1 mA per division. (g) Transmission-2 representation. Horizontal scale: v1: 0.5 volt per division, i1: 1 mA per division.

Vertical scale: v2: 1 volt per division, i2: 1 mA per division.

(a) Circuit model for a type N device. Fig. 21. (b) Circuit model for a type S device. Fig. 22. (a) Curve tracer circuit model for type N device. (b) Curve tracer circuit model for type S device. (a) When  $R > \frac{1}{G_{max}}$ , load line intersects the  $v_R^{-i}$  characteristic at Fig. 23. 3 points. (b) When  $R < \frac{1}{G_{max}}$ , load line intersects the  $v_R^{-i}$  characteristic at only one point. (a) Shaded region shows allowed parameter range for R and C for small L. Fig. 24. (b) Shaded region shows allowed parameter range for R and C for large L. Real part of s plotted as a function of C with all other parameters Fig. 25. held constant. (a) Connecting a voltage source  $v_s(t)$  and a current source  $i_s(t)$  in parallel with port 1 is equivalent to just connecting the voltage Fig. 26. source  $v_s(t)$  alone. (b) Connecting a current source  $i_s(t)$  and a voltage source  $v_s(t)$  in series with port 1 is equivalent to just connecting the current source  $i_s(t)$  alone. Fig. 27. (a) Connecting a nullator in series with the voltage source and a norator across port 2. (b) Ideal op amp model in the linear region with infinite gain. (c) Practical op amp circuit for tracing the transmission representation 2.

Fig. 3

(Ь)

Fig. 4

Fig. 5(a)

Fig. 5(.b)

2.

Fig. 5(c)

(a)

Fig. 6

volt

Fig. 7

(b) Fig. 8

Fig. II

. . .

Fig.14

Fig. 17

(b)

( a )

(a)

Fig. 22