# Copyright © 1984, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

LOW-VOLTAGE LOW-POWER MOS SWITCHED-CAPACITOR SIGNAL-PROCESSING TECHNIQUES

by

R. Castello

Memorandum No. UCB/ERL M84/67 20 August 1984

207

LOW-VOLTAGE LOW-POWER MOS SWITCHED-CAPACITOR SIGNAL-PROCESSING TECHNIQUES

bу

R. Castello

Memorandum No. UCB/ERL M84/67 20 August 1984

# LOW-VOLTAGE LOW-POWER MOS SWITCHED-CAPACITOR SIGNAL-PROCESSING TECHNIQUES

by

R. Castello

Memorandum No. UCB/ERL M84/67

20 August 1984

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# LOW-VOLTAGE LOW-POWER MOS SWITCHED-CAPACITOR SIGNAL-PROCESSING TECHNIQUES

Ph. D.

Rinaldo Castello

Department of EECS

Paul R. Gray

Chrisman of Committee

### **Abstract**

To date Switched-Capacitor (S.C.) filters satisfying the PCM channel filter specifications consume approximately 1 mW per-pole and use a  $\pm 5 V$  supply voltage.

From a fundamental stand point, the absolute minimum achievable power dissipation in a voiceband filter with a dynamic range of 90 db in a 3-micron technology operated from a  $\pm 5 V$  supply is less than one microwatt per pole. A very large margin for improvement is therefore available. Reduced power consumption is important in battery operated analog/digital interfaces and it will be even more so as larger and more complex systems are integrated on the same chip. At the same time, as a consequence of the scaling of MOS technology, supply voltages will have to be reduced. This fact, and the desire of having an analog/digital compatible technology, creates a strong motivation for developing analog circuits more suitable for low voltage operation.

Although many low power and/or low-voltage S.C. MOS circuits have been presented, no low-voltage, low-power filter meeting the PCM channel filter requirement have been reported to date.

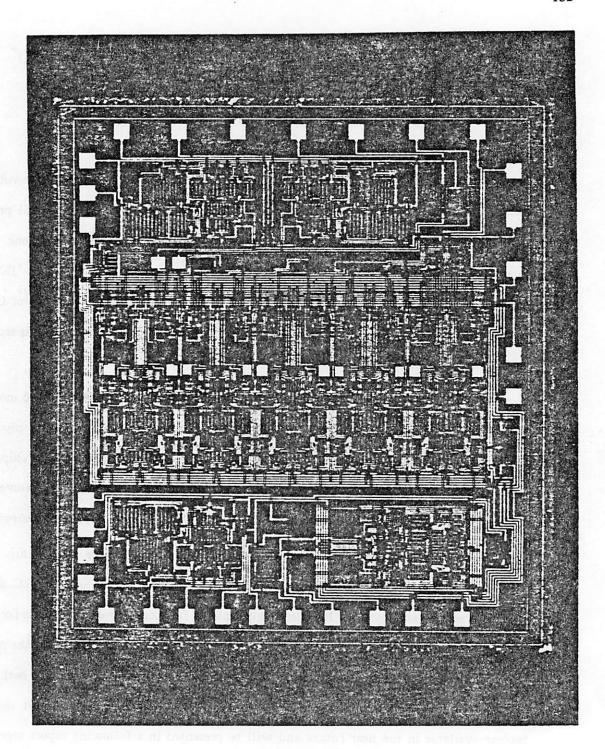

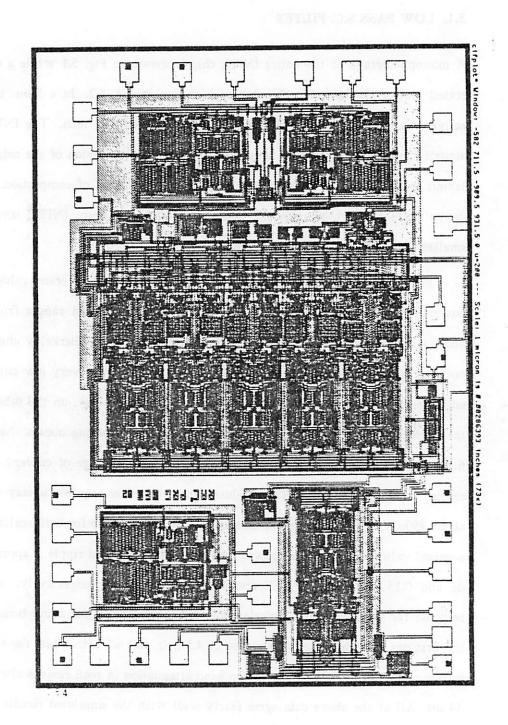

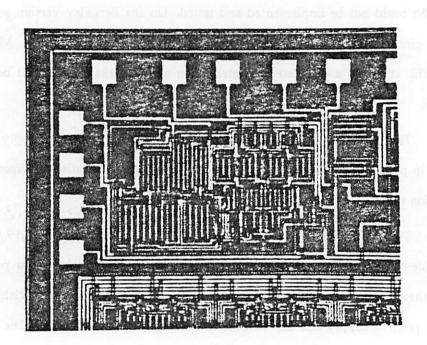

This dissertation describes a new 5<sup>th</sup> order CMOS PCM channel filter operating from a single 5 Volt supply and dissipating 70  $\mu Watt$  per pole. The realized

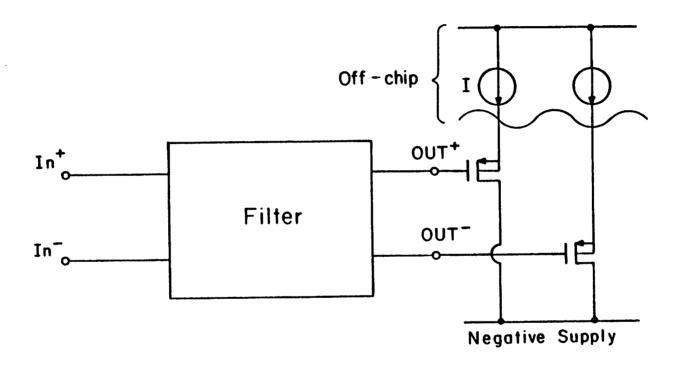

experimental prototype shows that a level of performance comparable or improved with respect to commercially available 10 Volt realizations is feasible. Together with the filter a low power buffer amplifier, also operating from a 5 Volt supply, and able to drive off-chip loads was realized.

# **ACKNOWLEDGEMENTS**

I wish to express my thanks and appreciation to my advisor Prof. Paul Gray for the continuous support that he has given me during the course of my Ph. D. studies. During these years I have grown to appreciate not only his deep insight in the field of LC. design, and his rigorous scientific ethic, but also his personal concern and caring toward other people which lies below his apparently reserved manners. I feel privileged to have been able to work with him.

I would also like to express my sincere thanks to both Professors Robert Meyer and Dave Hodges for having been always so available to discussing problems and offering suggestions during these years. The help of Professors Alberto Sangiovanni-Vincentelli and Rainer Sachs is also gratefully acknowledged.

The help and friendship of many fellow graduate students was very important in making my research effort successful. In particular a note of thanks goes to my two office mates of these years Ron Kaneshiro and Lee-Chung Yiu for their patience and understanding. Hae-Seung Lee and Ping Li also deserve special mention for helping me so much with the processing of my chip. Each and every one of the students making up the LC. group was helpful to me in ways ranging from technical cooperation to personal support and encouragement. Having been able to establish with them a rapport of friendship and trust is for me as important as the successful completion of my research. Here is a probably incomplete list of them: Paul Hurst, John Fattaruso, Devid Soo, Haideh Khorramabadi, Tat Choi, Kuang-Lu Lee, Chorng-Kuang Wang, Cheng-Chung Shih, Max Hauser, Bang Song, Jesus Guinea, Reza Kazerounian, Nanni De Micheli, Dan Senderowicz.

The cooperation of both Micheal Wong and W. E. Wallace with the testing and layout of the chip helped to keep the duration of my graduate study within reasonable limits.

Special thanks goes also to the microelectronic lab staff for their help and patience: Dot McDaniel, Don Rogers, Bob Hamilton, Dick Chan, Kim Chan, and Christy Atases. The cooperation provided by INTEL corporation by successfully fabricating one of the two experimental chip prototypes is also gratefully acknowledged.

Last but not least, Prof. Paolo Antognetti bears most of the merit and the responsibility for my decision to come to Berkeley to pursue a graduate degree.

Research sponsored by the National Science Foundation Grants ECS-8023872/ECS-8100012/ECS-8L00L2.

### CHAPTER 1

# INTRODUCTION

Switched-Capacitor (S.C.) filter performance has been steadily improving in the last several years and many prototypes satisfying the stringent PCM channel filter requirement have been reported [1-6]. However, in the most recent commercial implementation the required power-per-pole is in the neighborhood of 1 mW and a relatively high double polarity ( $\pm 5 V$ ) supply voltage is needed.

It will be shown in this dissertation that, from a fundamental stand point, the absolute minimum achievable power dissipation in a voiceband filter with a dynamic range of 90 db in a 3-micron technology operated from a  $\pm 5 V$  supply is less than one microwatt per pole [23]. A very large margin for improvement is therefore available and new structures that more closely approach the theoretical minima seem to be feasible. A reduction in the power consumption is important in the realization of battery operated analog/digital interfaces and could prove to be even more important in the future as larger and more complex systems are integrated on the same chip [7].

At the same time, as a consequence of the continuous scaling of MOS technology, supply voltages will have to be reduced if analog interfaces are to take advantage of this scaling [8]. This fact, and the desire of having an analog/digital compatible technology, create a strong motivation for developing new approaches in the design of analog circuits to make them more suitable for low voltage operation.

Recently many low power MOS circuits suitable for S.C. applications have been presented [9-15]. Of these, some are also intended to be used from a low voltage supply [10-13,15]. All of them, however, are for special purpose applications, use a low frequency clock (with the exception of [12]), and have relatively low performance. In fact no low-

voltage, low-power filter meeting the PCM channel filter requirement have been reported to date.

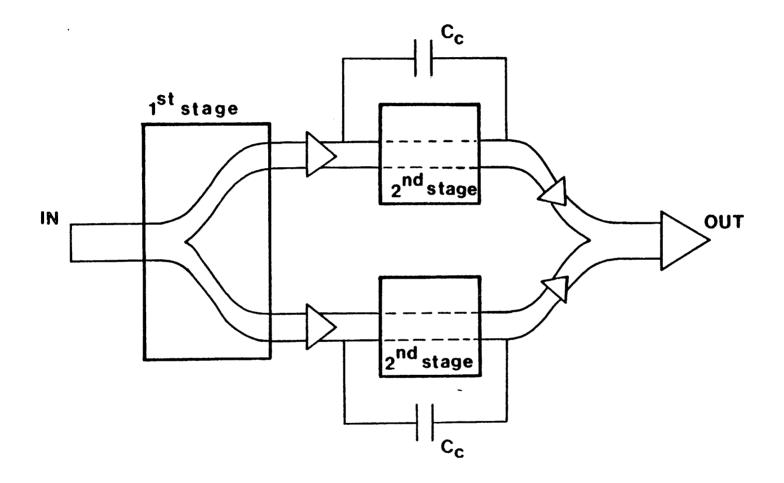

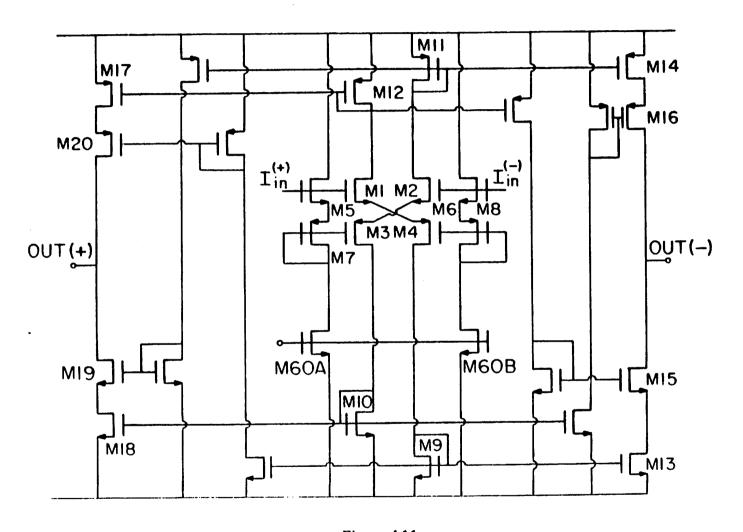

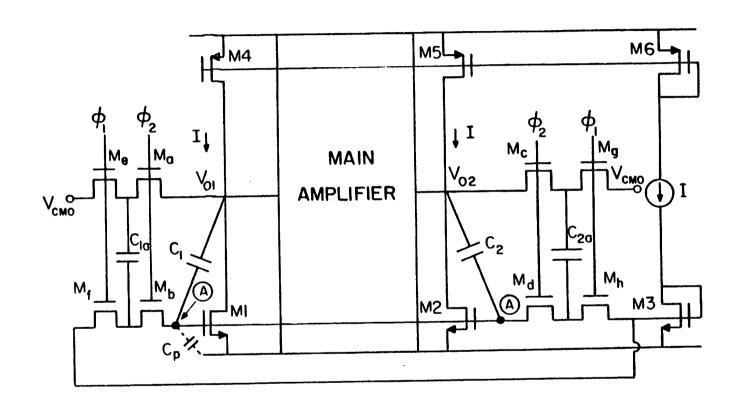

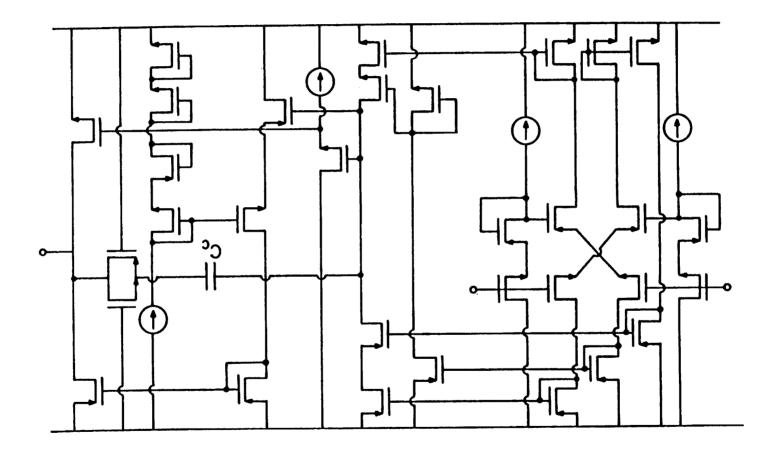

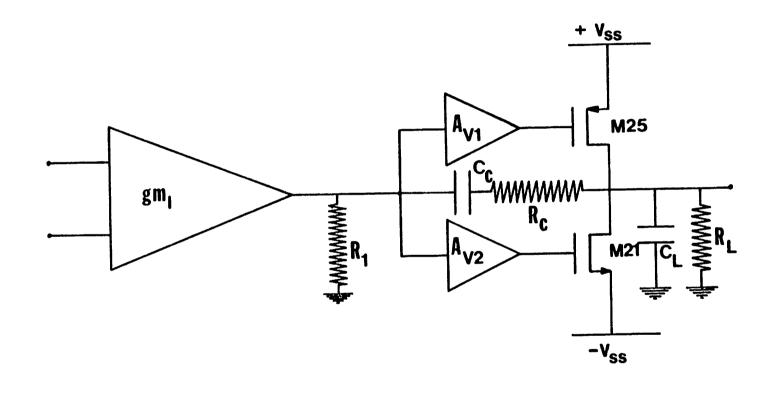

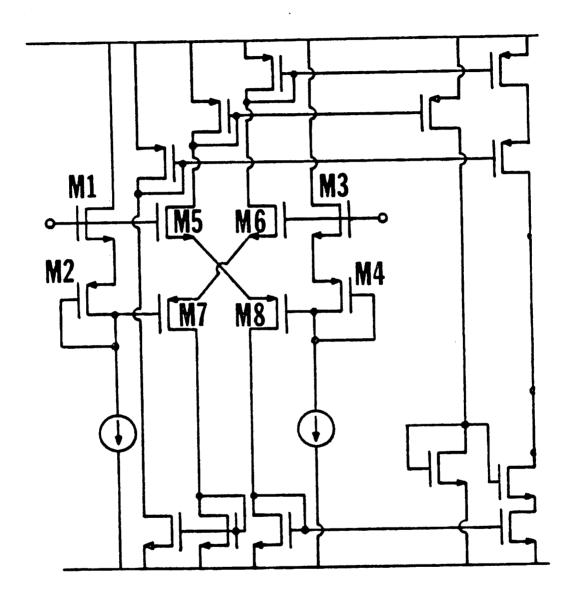

This dissertation describes a new  $5^{th}$  order CMOS PCM channel filter prototype operating from a single 5 Volt supply and dissipating 70  $\mu$ Watt per pole. By utilizing a combination of circuit techniques including input-to-output class A/B amplifier design, fully differential topology, dynamic biasing, switched capacitor common mode feedback, etc, a level of performance comparable or improved with respect to commercially available 10 Volt commercial realizations is shown to be feasible. Together with the filter a low power buffer amplifier, also operating from a 5 Volt supply, and able to drive off-chip loads was realized.

# CHAPTER 2

# PERFORMANCE LIMITATIONS IN SWITCHED-CAPACITOR FILTER

# 2.1. INTRODUCTION

Despite their relatively short history, switched capacitor (S.C.) circuits are already fairly mature. Most of their specifications have improved substantially since the first monolithic S.C. filters using S.C. integrators were designed and fabricated in 1977 [26][27].

In particular the power dissipation per pole has been reduced from about 10 to 20 mW in the first NMOS prototypes to less than 1 mW in the CMOS filters in production today [1]. These figures refer to general purpose systems working from a  $\pm 5$  Volts supply and with clock rates of 128 kHz or more. For special purpose applications, on the other hand, much smaller values have been achieved [9]-[14].

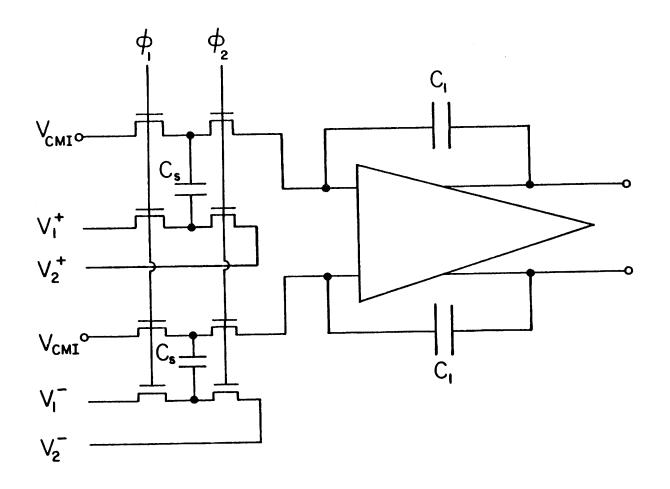

Another aspect that has been extensively investigated is the improvement of the dynamic range of the filter. To this end techniques like fully differential circuit design and noise frequency translation via chopper stabilization have been proposed. This has produced a filter with a dynamic range of 102 db [28]. To achieve such a result, however, a large increase in the chip area occupied by the filter was necessary.

Finally the total die area occupied by the filter has been substantially reduced. This has allowed the integration on a single chip of many S.C. filters together with other components [2][3][7][29].

Almost all of these results have been achieved by improving the performance of the operational amplifiers (op amps) in the filter [1], [30]-[32]. It is likely that better and better op. amps. will be designed in the future allowing this trend to continue. Eventually, however, some fundamental limitations other than those coming from the op. amps. will come

into play. Such limitations cannot be overcome by circuit or process improvements; therefore they determine the ultimate performance limit of the filter. This paper analyzes these fundamental limitations with reference to low pass filters.

Section 2 focuses on the S.C. integrator which is the building block of most S.C. filters. Under certain assumptions, the minimum area and power requirements, and the maximum achievable dynamic range are obtained as a function of relatively few parameters that are dependent on both the technology and the circuit used. It is shown that both the minimum power and area requirement vary proportionally to the square of the achievable dynamic range.

Section 3 analyzes the performance limitations of a low-pass S.C. filter. The theory of section 2 is extended to any low-pass ladder structure without introducing further approximations. The obtained results, while intuitively interesting, are function of the particular filter under consideration and cannot be related to each other in a general way.

By introducing additional approximations, which in most practical cases cause only a small error, and normalizing the results to the order of the filter, several simple relationship are obtained. Logarithmic plots showing the dependence of the minimum area and power requirement versus the achievable dynamic range are also provided.

On the basis of such plots state-of-the-art filters can be compared with the theoretical minima. As an example, for a  $5^{th}$  order voiceband filter with 95 db of dynamic range assuming a  $\pm 5Volts$  supply the minimum area required is approximately  $7300\mu m^2$  and the minimum power  $8.5\mu W$ . This is about two to three orders of magnitude smaller than the typical actual values for both power and area.

Finally in Section 4 the effect of the op amp non-idealities which were ignored in the derivation of the previous sections are considered. The op amp fundamental limitations are very difficult to exactly quantize and this is part of the reason why they were first ignored, nonetheless some upper bounds for the absolute minimum power, area, and noise

can be obtained with reference to a particularly simple but relistic op amp configuration.

This shows how the op amp limitations should not affect the ultimate filter performance in most practical cases.

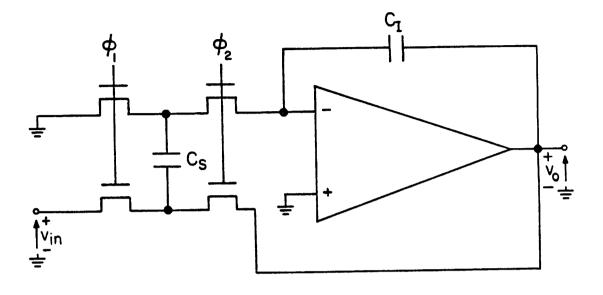

# 2.2. PERFORMANCE LIMIT FOR THE IDEAL INTEGRATOR

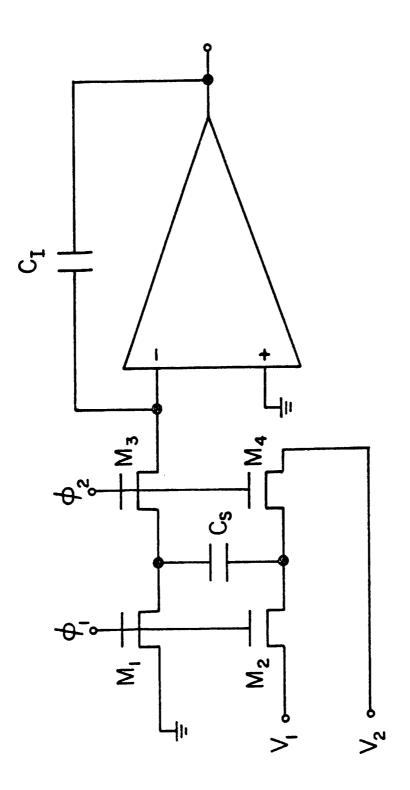

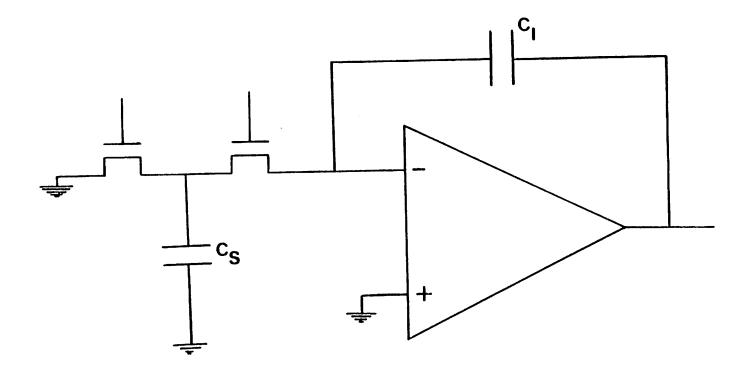

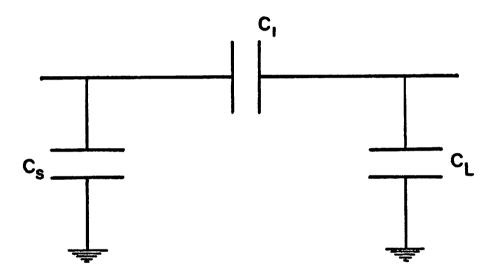

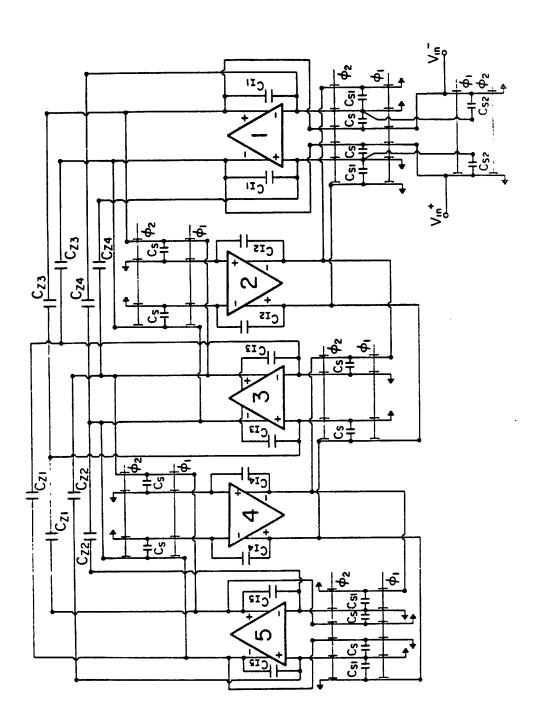

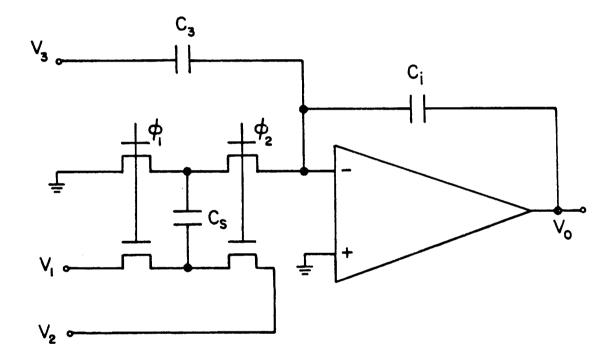

In this section the S.C. integrator is analyzed to obtain limits for the minimum power consumption and chip area requirement and for the maximum dynamic range achievable together with their interrelations. All of the following calculations refer to the so called differential bottom plate integrator shown in Fig. 2.1. Such a circuit was chosen for sake of concreteness, since it is insensitive to parasitic capacitance and has been used extensively in the literature [1][4][28]. However the extension of the theory to other S.C. integrator configurations is very straightforward and yields similar results.

The following basic assumptions will be used throughout the paper.

1. The op. amp. in the integrator is assumed to be ideal in the sense that it does not contribute any noise to the filter, it does not use any D.C. power, and it occupies no chip area. The reason for such drastic assumptions is that there are no fundamental limits, identifiable a priori, for the minimum value that can be achieved, via process and/or circuit design improvements, for any of the op. amp. non idealities mentioned above.

The only potential exception to this comes from the op. amp. white noise. It has however been shown [33] that its contribution, when is not negligible, can be added to that of the  $\frac{k}{C}$  noise since both can be represented in the same way. In this paper the op amp white noise is neglected for the sake of simplicity; however, because of the above considerations, the following analysis can be easily extended to include it, if a specific op. amp. configuration is given. In section 4 the validity of these assumptions will be discussed in more detail.

Figure 2.1

Bottom Plate S.C. Integrator.

2. The integrator capacitor is assumed to be much larger than the sampling capacitor i.e.

$$\frac{C_i}{C_r} \gg 1 \tag{2.1}$$

where  $C_s$  and  $C_i$  are the sampling and integration capacitors as shown in Fig.1. Making use of the following basic equation for the S.C. integrator [35]:

$$\frac{C_s}{C_i} = \frac{2 \pi f_{unity}}{f_{clock}} \tag{2.2}$$

where  $f_{unity}$  is the unity gain frequency of the integrator and  $f_{clock}$  is the clock frequency, condition (2.1) becomes:

$$\frac{f_{clock}}{f_{unity}} \gg 2\pi \tag{2.3}$$

Assumption (2.3) is almost always valid if the integrator is part of a low-pass vioceband S.C. filter. In such a case, in fact, each integrator has a unity-gain frequency which is comparable in value with the band edge of the filter, while the clock frequency is typically many times larger than the filter band edge to avoid warping effects in the transformation from the z to the s domain [34] and to ease anti-aliasing requirements.

On the basis of the above assumptions, the absolute minimum integrator area is approximately equal to the area of  $C_i$ . Assuming to have a symmetrical power supply equal to  $\pm V_s$  Volts and that the capacitor dielectric has a maximum electric field before break-down equal to  $E_{max}$  and a dielectric constant equal to  $\epsilon_{diel}$ , the minimum thickness of the capacitor is:

$$t_{\min} = 2 \frac{V_s}{E_{\max}} \tag{2.4}$$

The minimum area required to realize a capacitor of value  $C_i$  is therefore:

$$AREA_{\min} = \frac{t_{\min}C_i}{\epsilon_{diel}} = \frac{2 V_s C_i}{E_{\max} \epsilon_{diel}}$$

(2.5)

The maximum amount of energy that can be stored in the integrator  $\epsilon_{max}$  is given by

$$\epsilon_{\text{max}} = \frac{1}{2} (2 V_s)^2 C_i = 2 V_s^2 C_i$$

(2.6)

Substituting Eq. 2.6 into Eq. 2.5 gives the minimum area as a function of the maximum stored energy:

$$AREA_{\min} = \frac{\epsilon_{\max}}{V_s E_{\max} \epsilon_{diel}}$$

(2.7)

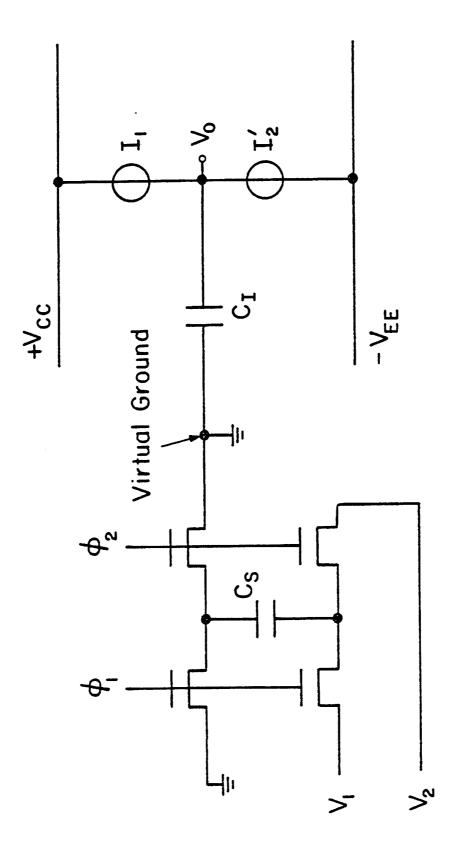

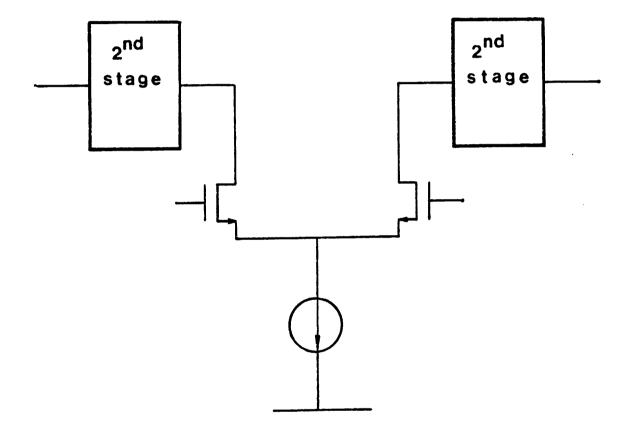

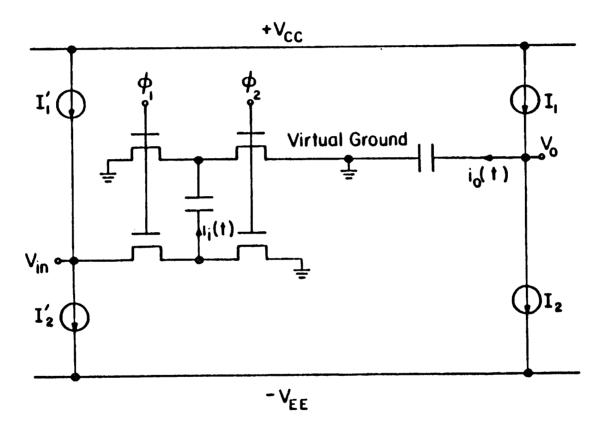

Next, the absolute minimum power consumption is computed. To this end the integrator of Fig. 2.1 can be represented as in Fig. 2.2. Furthermore the left hand side of the circuit of Fig. 2.2 can be modified as shown in Fig. 2.3. The only potential source of error in such a substitution is the phase difference existing between the two input of the integrator. Such a difference, however, does not effect power dissipation. The two current sources  $I_1$  and  $I_2$  are used to model an ideal class B Op. Amp. To guarantee zero quiescent power dissipation, as it was assumed,  $I_1$  must be equal to zero when  $I_2 \neq 0$  and vice versa. The same is valid for  $I_1$  and  $I_2$ .

The total power dissipation is given by the amount of energy per unity of time drown from the supplies by the two portions of the circuit i.e.

- 1. The amount of energy that  $C_s$  draws from one supply and than damps into the amplifier virtual ground.

- 2. The amount of energy that  $C_I$  draws from the other supply, through the action of the Op. Amp., to be damped again into the virtual ground. Assuming that the input signal  $v_i$  is a pure sinusoid with frequency f and peak amplitude  $V_i$ , the energy dissipated during one period of the signal can be computed as in Appendix A and is equal to:

Figure 2.2

Circuit Used to Compute the Power Drown From the Supplies.

$$\epsilon_{cycle} = \frac{4}{\pi} V_i V_s C_s \frac{f clock}{f}$$

(2.8)

The average power dissipated is obtained multiplying the energy per cycle by the frequency of the signal i.e.

$$P = \frac{4}{\pi} V_i V_s C_s f_{clock}$$

(2.9)

The input to output transfer function of the integrator is given by the following equation [35]

$$V_i = \frac{f}{f_{unity}} = \frac{2 \pi f C_i}{f_{clock} C_s} V_o$$

(2.10)

From Eq. 2.10 it can be seen that for a in-band signal, i.e.  $f \leq f_{unity}$ , the maximum amplitude of the input signal that does not cause any clipping at the output is a function of the input frequency. For this reason it is convenient to express the power consumption as a function of the output signal. This can be done by substituting Eq. 2.10 into Eq. 2.9 obtaining

$$P = 8 V_c V_o f C_i \tag{2.11}$$

For a maximum amplitude sinusoid at the output, i.e.  $V_o = V_s$  the power dissipation becomes

$$P = 8 f C_i V_s^2 (2.12)$$

Using Eq. 2.6 into Eq. 2.12 gives

$$P = 4 \in_{\max} f \tag{2.13}$$

the minimum power consumption for a full swing sinusoidal output is therefore proportional to the maximum energy stored in the integrator times the frequency of the signal.

Last, the dynamic range is considered. While the power consumption and the area requirement can be uniquely defined for a stand-alone S.C. integrator, the dynamic range is

Equivalent Circuit of Fig. 2.3.

Figure 2.3

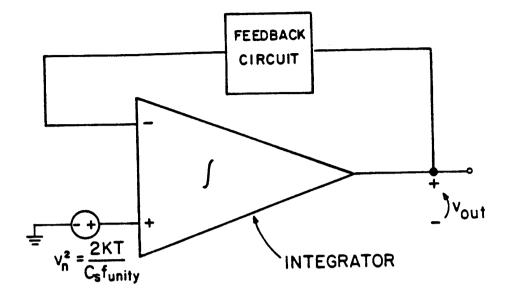

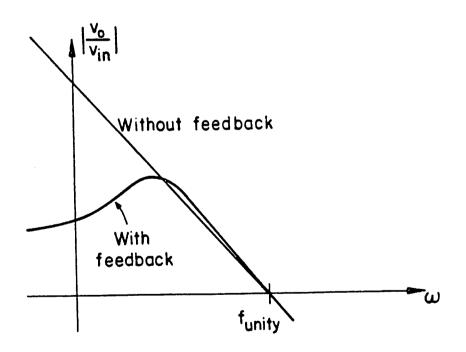

a function of the particular circuitry that surrounds it. In any practical case the integrator must be part of a feedback loop in order to guarantee a stable DC operating point. This is shown schematically in Fig. 2.4 together with the input-to-output transfer function with and without feedback. Both the total output noise, and the dynamic range, must be expressed as a function of the particular feedback configuration.

Having assumed an ideal op. amp, the only sources of noise are the MOS switches. The noise contributed by the left hand side switch is sampled by  $C_s$  every clock cycle. The signal appearing across capacitor  $C_s$  is therefore a sampled first order low-pass filtered white noise. It has been shown that for a properly operating S. C. circuit, i.e. the time constants associated with the switches and the capacitors are much smaller than the clock period, such a discrete random process has a white spectral distribution and a total noise power (variance) equal to  $\frac{k}{C_s}$  [38]. Discrete time linear system theory can therefore be used to determine the output noise variance  $n_i$  obtaining the following result [36]

$$n_i^2 = \frac{kT}{C_s} \sum_{m=0}^{\infty} h^2(m)$$

(2.14)

where h (m) is the impulse response from the noise source to the output. Using Parseval's theorem [36] in Eq. (2.14) gives the final result

$$n_i^2 = \frac{kT}{C_s} \frac{1}{2\pi} \int_{-\pi}^{\pi} H(e^{j\omega}) H(e^{-j\omega}) d\omega$$

(2.15)

where H ( $e^{j\omega}$ ) is the z transform of h (m) evaluated on the unit circle. By introducing the the following definition

$$B_o = \frac{f_{clock}}{2\pi} \int_{-\pi}^{\pi} H(e^{j\omega}) H(e^{-j\omega}) d\omega \qquad (2.16)$$

and making use of Eq. (2.2), Eq. (2.15) can be written as

Figure 2.4

Closed Loop S.C. Integrator.

$$n_i^2 = \frac{1}{2\pi} \frac{kT}{C_i} \frac{B_o}{f_{unity}}$$

(2.16b)

The quantity  $B_o$  is the effective noise bandwidth from the input of the switched capacitor integrator to the integrator output for the particular feedback configuration considered. It is the integral of the magnitude squared of the frequency response of the sampled data feedback circuit from the integrator input to the output, taken around the unit circle. For lowpass filters where the clock rate is far above the passband, this is equivalent to the integral over the passband of the transfer function from the integrator input to the output for the continuous equivalent circuit. In the following  $B_o$  will be called the noise bandwidth to the output.

The noise contributed by the right hand side switch is also sampled by  $C_s$ . However, in this case, the resulting signal cannot rigorously be considered as a first order low pass filtered noise. The reason is that the circuit through which the white noise of the switch is sampled does not have a single pole roll-off since it contains also the op. amp. The amount of noise transferred to the output is, to first order, proportional to the ratio between the op. amp. unity gain bandwidth and the bandwidth of the circuit formed by the switch resistance and the sampling capacitor[36]. For simplicity it is assumed to have an ideal op. amp. (infinite bandwidth). In such case the two switches behave in the same way and the total output noise,  $n^2$ , becomes

$$n^{2} = \frac{1}{\pi} \frac{kT}{C_{i}} \frac{B_{o}}{f_{unity}}$$

(2.17)

Assuming that the maximum undistorted output signal is approximately equal to the supply voltage  $V_s$ , i.e.  $\sqrt{2} V_s$  rms, the dynamic range of the integrator, (DR), becomes:

$$(DR)^2 = \frac{s^2}{n^2} = \frac{\pi}{2} \frac{V_s^2 C_i}{kT} \frac{f_{unity}}{B_0}$$

(2.18)

Eq. (2.18) can be rewritten as follows by making use of Eq.(2.6)

$$(DR)^2 = \frac{\pi}{4} \frac{\epsilon_{\text{max}}}{kT} \frac{f_{\text{unity}}}{B_0}$$

(2.19)

Eq. (2.19) suggests that the square of the dynamic range is given by the ratio between the maximum energy stored in the integrator and the unity of thermal energy kT, modified by the ratio between the noise bandwidth to the output and the unity gain bandwidth of the integrator.

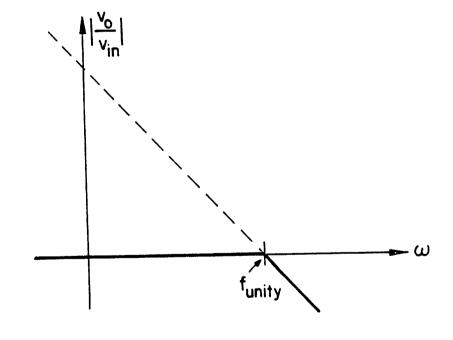

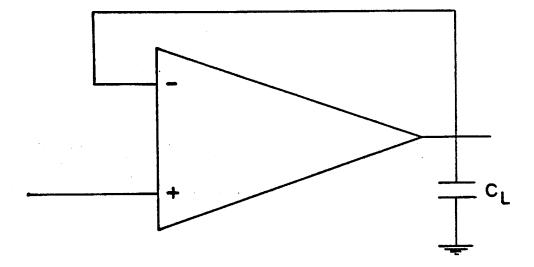

As an example consider the unity gain feedback circuit shown in Fig. 2.5. This is the simplest configuration in which the S.C. integrator can be operated. It corresponds to a first order low pass filter whose z domain transfer function from  $C_s$  to the output is given by

$$H(z) = \frac{\frac{C_s}{C_i}}{1 - z^{-1} + \frac{C_s}{C_i}}$$

(2.20)

H (  $e^{\int \omega T}$  ) is approximately shown in Fig. 2.5b. In this simple case  $B_o$  can be easily computed by making use of Cauchy residue theorem with the following result

$$B_o = f_{clock} \frac{C_s}{C_s + 2C_i}$$

(2.21)

Assuming condition (2.1) to be valid and using Eq. (2.2) in Eq. (2.21) gives the following result

$$B_o = \frac{f_{clock}}{2} \frac{C_s}{C_i} = \pi f_{unity}$$

(2.22)

As expected, for this simple case,  $B_o$  is just the effective noise bandwidth of the single-time constant low-pass filter whose transfer function is shown in Fig. 2.5. Using the above result the circuit dynamic range becomes.

$$(DR)^2 = \frac{V_s^2 C_i}{2 kT}$$

(2.23)

which is a particularly simple result. Note that this ratio is simply the maximum energy

Figure 2.5

One Pole S.C. Filter.

stored on the integrating capacitor divided by kT. This result has strong implications for the ultimate limit on the ability to scale switched capacitor filters with technological feature size. In effect, silicon dioxide can only store a certain amount of energy per unit volume as dictated by the maximum field strength of silicon. For a given oxide thickness and power supply voltage this dictates a maximum energy storage per unit area, which dictates a minimum area for a given dynamic range and power supply voltage. Such a minimum value can be computed in the more general case by combining Eq. (2.19) and Eq. (2.7) with the following result

$$(DR)^2 = \frac{\pi}{4} \frac{V_s \epsilon_{diel} E_{max} AREA}{kT} \frac{f_{unity}}{B_0}$$

(2.24)

This indicates that the ultimately achievable dynamic range is proportional to the square root of the product of the power supply voltage and the area.

Since the absolute minimum achievable level of power dissipation is proportional to  $\epsilon_{\text{max}}$ , as it was shown in Eq. (2.13), a relationship similar to Eq. (2.24) between dynamic range and power consumption must exist. Mathematically such a relationship can be obtained by combining Eq. (2.13) and Eq. (2.19) to obtain te following result

$$(DR)^2 = \frac{\pi}{16} \frac{P}{kT B_o} \frac{f_{unity}}{f}$$

(2.25)

Thus the dynamic range is proportional to the square root of the minimum power dissipation necessary to charge and discharge the sampling and integrating capacitors from the power supply.

Notice that Eq. (2.25) is only valid for  $f \leq f_{unity}$  since outside this range the gain of the integrator is less than 1 and therefore it is not possible to have  $V_o = V_s$  for an input signal  $v_i$  smaller than the supply voltage. It is easy to see that the absolute maximum for P ( $P_{max}$ ), when both  $V_i$  and  $V_o$  are not allowed to exceed the supply voltage, corresponds to  $f = f_{unity}$ . In this case Eq. (2.24) becomes

$$(DR)^2 = \frac{\pi}{16} \frac{P_{\text{max}}}{kT B_0}$$

(2.26)

It can be shown that Eqs. (2.24)-(2.26) are valid for both single ended and fully differential integrators [33].

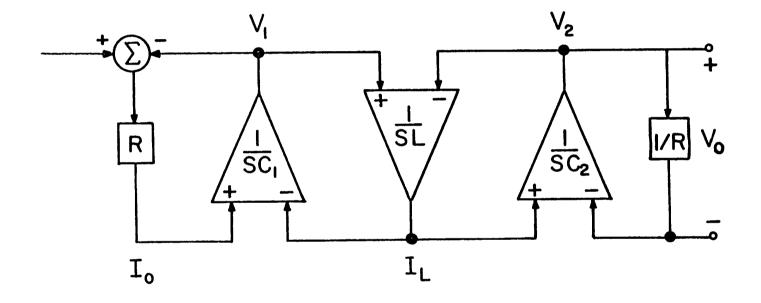

#### 2.3. APPLICATION OF THE THEORY TO A LOW PASS S. C. FILTER

In this Section the previous analysis is extended to the case of low-pass ladder S. C. filters.

It is known that for a ladder active filter the basic building block is the integrator which, if the filter is implemented via S. C. techniques, can be realized by the circuit of Fig. 2.1 or by some other similar structure.

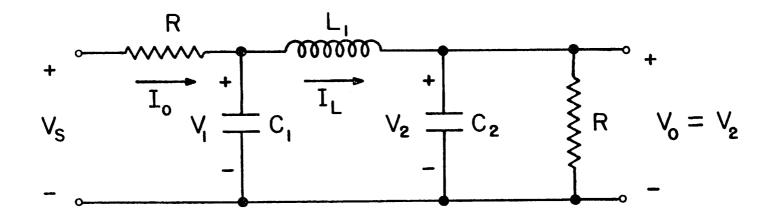

To apply the results of the previous section to te entire filter, it is first shown that there is a-one to-one correspondence between the order of the filter (number of poles) and the number of integrators required to realize it. This is easily done with the help of a simple example.

Fig. 2.6 shows the passive ladder prototype for a 3<sup>rd</sup> order low-pass filter. This circuit can be represented in terms of integrator summers and multiplyers as in Fig. 2.7 [16]. The flow diagram of Fig. 2.7 shows that each integrator output corresponds to one of the state variables of the filter, i.e. a voltage across a capacitor or a current through an inductor. Therefore the number of integrators will be equal to the number of state variables, which also coincides with the order of the filter.

The above situation can be immediately generalized to an  $n^{th}$  order structure as long as the number of state variables coincides with the number of reactive elements. Even when this is not the case (due to the presence of loops of capacitors or cut-sets of inductors), however, it is still possible to modify the passive prototype so that the number of

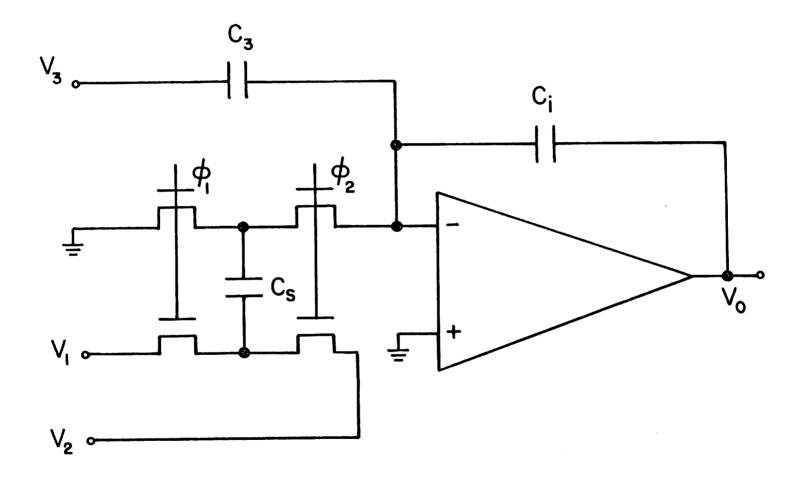

Figure 2.6

integrators will coincide with the order of the filter by introducing some voltage-controlled voltage sources in the circuit [35]. In a S.C. implementation such controlled generators can be realized by simply substituting the basic integrator of Fig. 2.1 with the integrator-summer of Fig. 2.8 [35]. All the results of Section 2 can be extended with no changes to the structure of Fig. 2.8 if the extra area due to capacitor  $C_3$  is neglected.

From the above considerations and from the results of Section 2 follows immediately that the minimum amount of area required for a  $n^{th}$  order S.C. filter is:

$$AREA_{tot} = 2 \frac{V_s}{E_{\max} \epsilon_{diel}} \sum_{i=1}^{n} C_i = \frac{\sum_{i=1}^{n} \epsilon_{\max_i}}{V_s E_{\max} \epsilon_{diel}}$$

(2.27)

Where  $\epsilon_{max_i}$  is the maximum amount of energy that can be stored in the  $i^{th}$  integrator.

To compute the total power dissipated in the filter for a sinusoidal input of frequency f and peak amplitude equal to the supply voltage  $V_s$ , use can be made of Eq. (2.11) provided that the gain from the input of the filter to the output of the  $i^{th}$  integrators,  $G_i$  (f), is known for each integrator. This gives:

$$P_{tot} = 8 \ f \ V_s^2 \sum_{i=1}^n G_i \ (f \ ) C_i = 4 \ f \ \sum_{i=1}^n G_i \ (f \ ) \in_{\max_i}$$

(2.28)

where  $f_i^{unity}$  is the unity gain frequency if the  $i^{th}$  integrator. Notice that in Eq. (2.28) it is implicitly assumed that  $G_i$  (f)  $\leq 1$  for every i. This condition must be verified to be able to process a full swing (supply to supply) input signal without unacceptably large distortion. Such an assumption will be discussed further later in the paper.

Finally the total output noise contribution can be computed from Eq. (2.17) provided that the value of the noise bandwidth from the input of integrator i to the output of the filter,  $B_i$ , is known for all the n integrators.

$$n_{tot}^{2} = \frac{1}{\pi} kT \sum_{i=1}^{n} \frac{B_{i}}{f_{i}^{unity} C_{i}}$$

(2.29)

Figure 2.7

Block Diagram for the Circuit of Fig. 2.6.

This gives for the filter dynamic range

$$(DR_{tot})^{2} = \frac{\pi V_{s}^{2}}{2 kT \sum_{i=1}^{n} \frac{B_{i}}{f_{i}^{unity} C_{i}}} = \frac{\frac{\pi}{4}}{\sum_{i=1}^{n} \frac{kT}{\epsilon_{max_{i}}} \frac{B_{i}}{f_{i}^{unity}}}$$

(2.30)

where the in-band input-to-output gain of the filter has been assumed to be equal to one and the maximum output swing to be equal to the supply voltage( $\sqrt{2} V_s$  rms).

This is generally true in a S. C. low-pass filter since the 6 db in-band loss of the passive prototype can be easily eliminated by making the capacitor that samples the input voltage twice as big as the other sampling capacitor in the first integrator.

An alternative way to express the dynamic range in term of the sampling capacitors which will be useful later is shown in Eq. (2.31)

$$(DR_{tot})^{2} = \frac{V_{s}^{2} f_{clock}}{4 kT \sum_{i=1}^{n} \frac{B_{i}}{C_{s_{i}}}}$$

(2.31)

where  $C_{s_i}$  is the sampling capacitor in the  $i^{th}$  integrator.

The above equations involve almost no approximations and can be used if all of the required parameters are known. The results, however, are a function of the particular filter design adopted and are in a form that does not show any particular relationship between the various performances. More insight on the problem can be gained by introducing some approximations.

First, it is assumed that the sampling capacitors are identical for all the integrators, with the exception of the one that samples the input voltage, which was assumed to be twice as big as the others.

Next the following approximation is introduced:

Figure 2.8

Bottom Plate Integrator/Summer.

$$\sum_{i=1}^{n} \frac{1}{f_i^{unity}} \approx \frac{n}{f_{max}} \tag{2.32}$$

where  $f_{\rm max}$  is the band edge of the filter. Physically this means that the average value of the time constants of all the integrators in the filter coincide with the time constant associated with the band edge of the filter. In a typical low-pass ladder filter the error introduced by Eq. (2.32) rarely exceed  $\pm$  30%.

Table 1, for example, shows the values of the integrators unity gain frequency together with  $f_{\text{max}}$  for a commercial PCM low-pass filter (INTEL 2912). In this case the approximation introduces only about 2% error.

From Eqs. (2.27), (2.2), and (2.32) it follows that:

$$AREA_{tot} = \frac{2 V_s n}{E_{\max} \epsilon_{diel}} \frac{f_{clock} C_s}{2 \pi f_{\max}} = \frac{2 V_s n}{E_{\max} \epsilon_{diel}} C_I = \frac{n \epsilon_{\max}^I}{E_{\max} \epsilon_{diel} V_s}$$

(2.33)

where the following two definitions have been introduced

$$C_I = \frac{f_{clock} C_s}{2 \pi f_{max}} \tag{2.34}$$

$$\epsilon_{\max}^{I} = 2V_s^2 C_I \tag{2.35}$$

From Eq. (2.2)  $C_I$  can be interpreted as the integration capacitance necessary to obtain an integrator whose unity gain frequency is  $f_{\text{max}}$ .  $\epsilon_{\text{max}}^I$  is the maximum amount of energy that can be stored in  $C_I$ .

In order to obtain a single numerical value for the power dissipated in the filter Eq. (2.28) is evaluated for  $f = f_{\text{max}}$ ; therefore obtaining an upper bound for the minimum power requirement. At that frequency, for a properly designed filter, the gain from the input to each intermediate node can be assumed, with good approximation, to be equal to 1 i.e.  $G_i$  ( $f_{\text{max}}$ ) = 1 for  $i = 1 \cdots n$  [16].

To understand why this is in most cases a good approximation notice that to avoid saturation, which will reduce the maximum usable amplitude of the input signal, the gain

TABLE I

|       | f <sub>i</sub> (kHz) | l/ f <sub>i</sub> (μs) | ΔC <sub>i</sub> /C <sub>I</sub> | $(\Delta C_i/C_I)^2$ |

|-------|----------------------|------------------------|---------------------------------|----------------------|

| i =   | 4.715                | 212.1                  | 2789                            | .077                 |

| i = 2 | 2.227                | 449                    | .527                            | .277                 |

| i =3  | 5.186                | 192.8                  | 344                             | .118                 |

| i =4  | 4.0415               | 247. 4                 | .159                            | .025                 |

| i = 5 | 2.965                | 337.3                  | 147                             | .0216                |

| Σ/5   | 3.826                | 287.5                  | 021                             | .1037                |

from the input to each internal node must be less or equal to one for all frequency. On the other hand the value of the gain from all the intermediate nodes to the output should be minimum, to minimize the total output noise contribution. A good compromise between these two requirements is to set the peak value of each intermediate gain to one. Since peaking typically occurs in the proximity of the band edge the above assumption is justified.

Eq. (2.32) can be substituted in Eq. (2.28) to give:

$$P_{tot} (f_{max}) = 8 n V_s^2 f_{max} C_I = 4 n \in I_{max} f_{max}$$

(2.36)

The total output noise is obtained by using Eq. (2.31), with the condition that all the sampling capacitors are equal:

$$n_{tot}^{2} = \frac{4 kT}{C_{s} f_{clock}} \sum_{i=1}^{n} B_{i} = \frac{2}{\pi} \frac{kT}{C_{I} f_{max}} \sum_{i=1}^{n} B_{i}$$

(2.37)

this implies a dynamic range for the filter (  $DR_{tot}$  ) of:

$$(DR_{tot})^{2} = \frac{\pi V_{s}^{2} C_{I} \quad f_{\text{max}}}{2 k T \sum_{i=1}^{n} B_{i}} = \frac{\pi}{4} \frac{\epsilon_{\text{max}}^{I}}{k T} \frac{f_{\text{max}}}{\sum_{i=1}^{n} B_{i}}$$

(2.38)

Eqs. (2.33), (2.36), and (2.38) can be normalized to obtain the equivalent area, power, and dynamic range per pole as follows:

$$AREA_{pole} = \frac{AREA_{tot}}{n} = \frac{\epsilon_{max}^{I}}{E_{max} \epsilon_{diel} V_{s}}$$

(2.39)

$$P_{pole} = \frac{P_{tot}}{n} = 4 \in \text{max} \ f \text{max}$$

(2.40)

$$(DR_{pole})^2 = n (DR_{tot})^2 = \frac{\pi}{4} \frac{\epsilon_{max}^I}{kT} \frac{f_{max}}{\frac{1}{n} \sum_{i=1}^n B_i}$$

(2.41)

Eqs. (2.39), (2.40), and (2.41) can be related to each other in the same way as it was done for Eqs. (2.7), (2.13), and (2.19) to obtain:

$$(DR_{pole})^2 = \frac{\pi}{16} \frac{P_{pole}}{kT \frac{1}{n} \sum_{i=1}^{n} B_i}$$

(2.42)

$$(DR_{pole})^2 = \frac{\pi}{4} \frac{V_s \in_{diel} E_{max} AREA_{pole}}{kT} \frac{f_{max}}{\frac{1}{n} \sum_{i=1}^{n} B_i}$$

(2.43)

Comparing Eqs. (2.42) and (2.43) with Eqs. (2.24) and (2.25) it can be seen that they have the same physical interpretation with  $f_{\text{max}}$  and  $\frac{1}{n} \sum_{i=1}^{n} B_i$  playing the role of  $f_{\text{unity}}$  and  $B_o$  respectively.

In Eq. (2.42) and (2.43)  $\frac{1}{n} \sum_{i=1}^{n} B_i$  is the only term that depends on the particular circuit architecture used. It turns out, however, that in practical cases its value is relatively constant. In fact the following approximation can be introduced

$$\frac{1}{n} \sum_{i=1}^{n} B_i = \delta \ 2 \ f_{\text{max}} \tag{2.44}$$

where  $\delta$  is a parameter that depends on the particular filter implementation whose average value is can be assumed to be equal to .75 with a worst case inaccuracy of about  $\pm 40\%$ . For the filter of Table 1, for instance,  $\delta$  is equal to .9.

Using (2.44) with  $\delta = .75$  in (2.42) and (2.43) gives:

$$(DR_{pole})^2 = \frac{\pi}{24} \frac{P_{pole}}{kT f_{max}}$$

(2.45)

$$(DR_{pole})^2 = \frac{\pi}{6} \frac{V_s \epsilon_{diel} E_{max} AREA_{pole}}{kT}$$

(2.46)

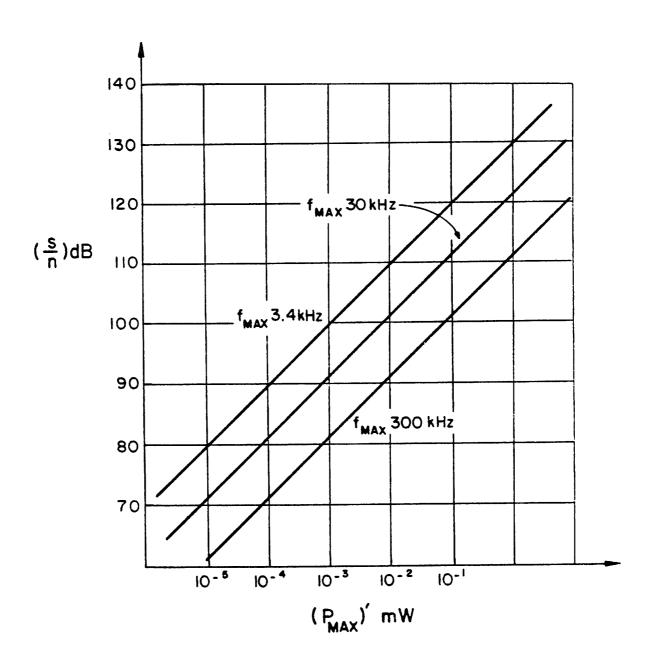

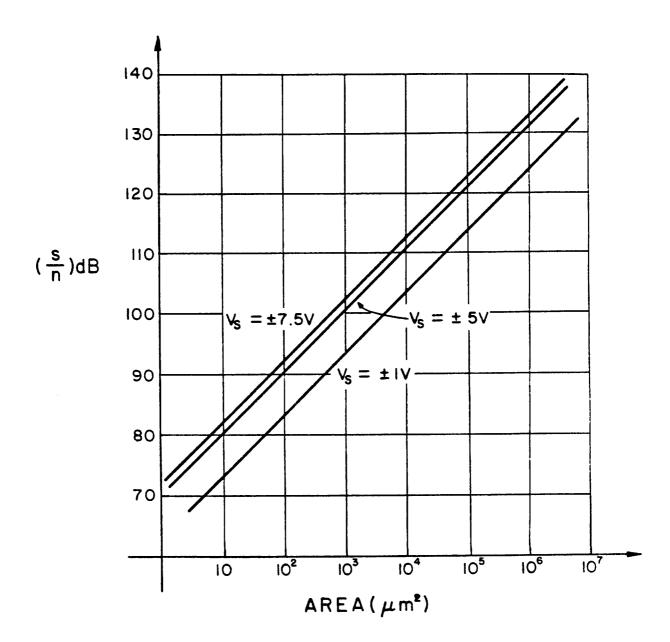

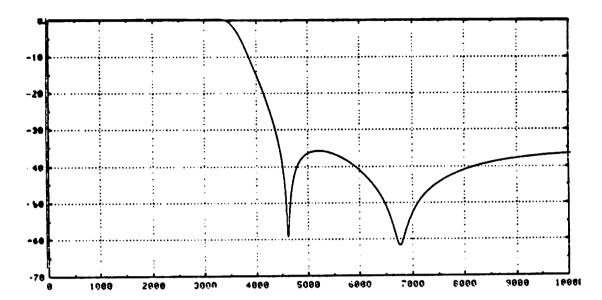

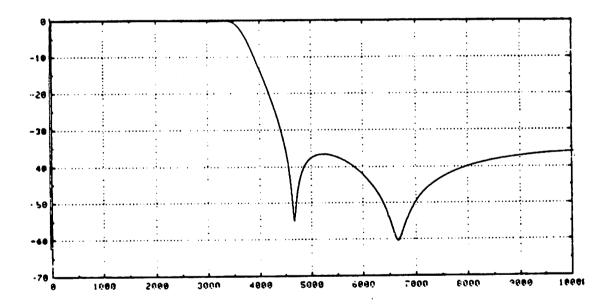

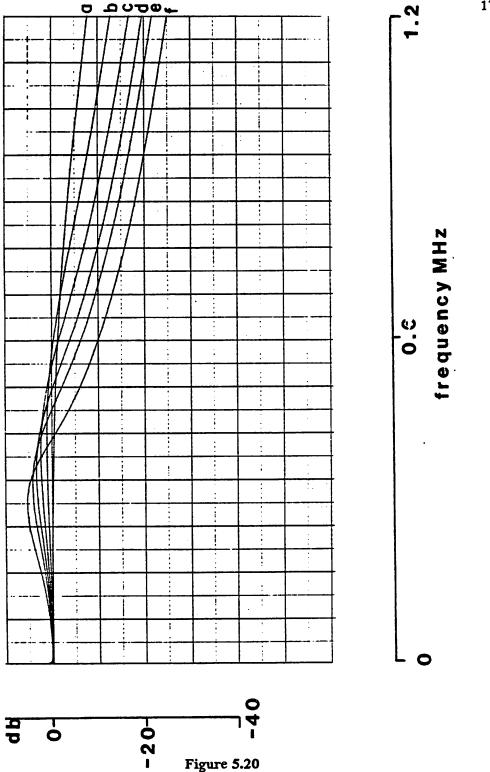

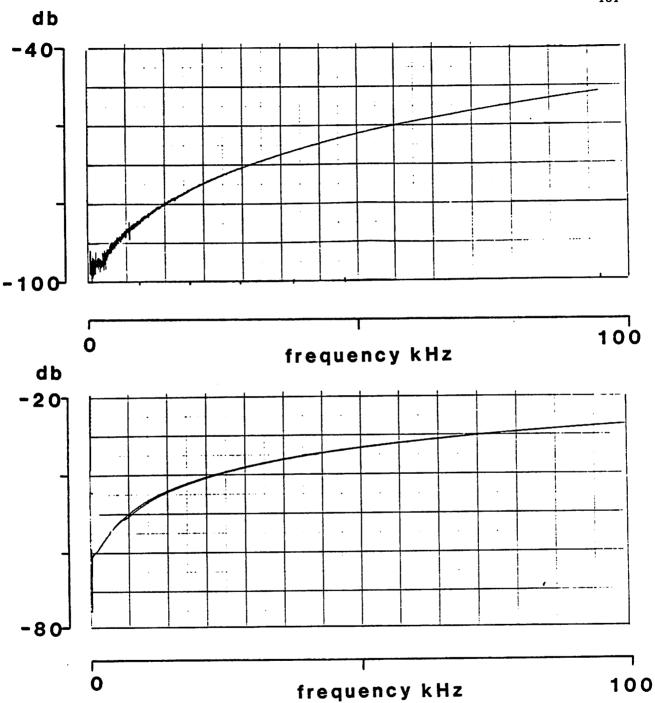

From Eqs. (2.45) and (2.46) the logarithm of  $P_{pole}$  and  $A_{pole}$  can be plotted versus the achievable dynamic range,  $DR_{pole}$ , expressed in db with  $f_{max}$  or  $V_s$  used as a parameter respectively. This is shown in Fig. 2.9 and 10 in the case that the capacitor dielectric is silicon dioxide with  $E_{max}=5\ 10^6 \frac{V}{cm}$ .

Figure 2.9  $\label{eq:max-power} \mbox{Minimum Power Dissipation vs. Dynamic Range for Different Values of } f \ \mbox{ }_{\mbox{max}}.$

The plots of Figs. 9 and 10 can be used for both single ended and fully differential filter configurations.

On the base of the above results the power consumed and the area occupied by any low pass S.C. filter can easily be compared with the theoretical minima.

As an example consider a PCM  $5^{th}$  order low-pass elliptic filter with a cut-off frequency of 3.4 kHz, a supply voltage of  $\pm 5$  Volts and a signal-to-noise ratio of 95 db. Typical values for such a filter are a power per pole of about 1 mW, and an area per pole of about 6.25  $10^5 \,\mu^2$  (  $1000 \, mils^2$  ). Using Eq. (2.41) the dynamic range per pole can be determined from the overall dynamic range of the filter as follows:

$$(DR_{pole}) = 95db + 10 \log 5 = 102 db$$

(2.47)

The plots of Fig. 2.9 and 10 for a  $\pm 5$  Volts supply and a dynamic range of 102 db give a minimum area requirement of approximately 1400  $\mu^2$  and a minimum power requirement of approximately 1.7  $\mu W$ .

The actual values are approximately 2 to 3 orders of magnitude larger than the theoretical minima showing that there is a strong motivation to further reduce the area occupied and the power consumed by the core amplifier. Finally from the above results it immediately follows that to achieve a dynamic range of 95 db in a  $5^{th}$  order voiceband filter operating from a  $\pm 5Volts$  supply the minimum area required is approximately  $7300\mu m^2$  and the minimum power  $8.5\mu W$ . On the other hand the absolute maximum dynamic range that can be achieved for the same filter as above assuming a total area of  $5000mil^2$  and a total power dissipation of 5mW is approximately 121 db.

### 2.4. EFFECT OF AMPLIFIER NONIDEALITIES

As stated in Section 2 all of the above results were based on the assumption of having an op amp with ideal characteristics, i.e. zero power consumption, zero area, zero noise con-

tribution. Such an ideal situation was to be achieved by continuously scaling the feature size, provided that the  $\frac{1}{f}$  noise could be eliminated by some technique like chopper stabilization. In actuality practical constraint will result in other limitations on the level of op amp performance achievable. The ultimate minimum value for the above op amp characteristics is very difficult to define. It is however possible, based on a simple model, to obtain upper bounds for the limit values of the above quantities. This is done in this section. The obtained results show that the op amp fundamental limitations should not substantially effect the the ultimate performance of the filter in all practical cases.

# 2.4.1. Power Dissipation

In the following the minimum amount of power requested by the op amp for a given clock frequency is compared with the result of Eq. (2.12). The minimum op amp power consumption is obtained under the following assumptions:

1) The limiting factor in the op amp settling time ( $T_{set}$ ) is given by the linear portion of the step response as opposed to the slewing portion. As a consequence the following equation is valid

$$T_{set} = \delta \tau \tag{2.48}$$

where  $\delta$  is a number (typically between 5 and 10) that depends on the accuracy required in the step response, and  $\tau$  is the time constant of the closed loop step response of the op amp (a single pole step response is assumed). If  $C_I \gg C_s$  and no large capacitance is attached at the integrator summing node it follows that

$$\tau \approx \frac{1}{\omega_u} \tag{2.49}$$

where  $\omega_u$  is the unity gain frequency of the amplifier. The above assumption is quite reasonable since class A/B amplifiers that do not exhibit any slewing behavior and have a power dissipation which is only a few percent higher than their stand by values can be

emploied.

2) The devices are operated in the subthreshold region. This corresponds to the maximum possible transconductance for a certain current level I i.e.

$$\frac{gm}{I} = \frac{q}{n \ kT} \tag{2.50}$$

where n is the subthreshold slope factor whose value is typically between 1 and 2.

- 3) The time allowed for the op amp to settle is assumed to be  $\frac{1}{2 f_{clock}}$  i.e. 50% duty cycle is assumed

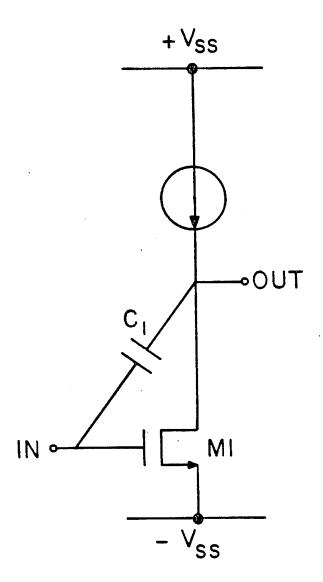

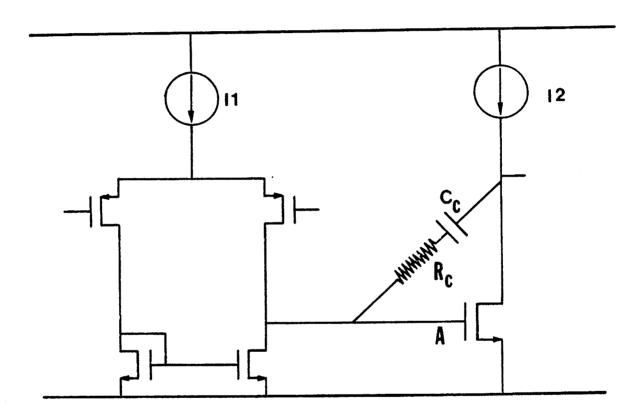

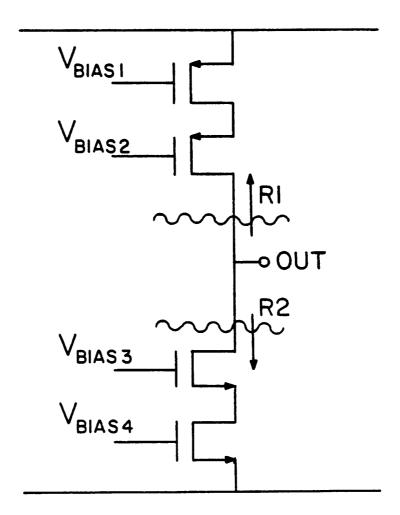

- 4) The most simple inverter like structure of Fig. 2.11 is assumed for the op amp with the possibility of using cascode devices to enhance the voltage gain.

- 5) The load capacitance of the integrator is assumed to be equal to  $2 C_s$  i.e. the sampling capacitor of the next stage plus the effective capacitive load at the output due to the feedback circuit which is the series of  $C_I$  and  $C_s$ .

From assumptions 4) and 5) follows that

$$\omega_u = \frac{gm_l}{2C_s} \tag{2.51}$$

where  $gm_I$  is the transconductance of the driver device M1. Using assumption 3) in Eq. (2.51) gives

$$\frac{gm_l}{2C_s} \geqslant 2 \delta f_{clock} \tag{2.52}$$

The absolute minimum value of  $gm_I$  ( $gm_{min}$ ) is

$$gm_{\min} = 4 \delta C_s f_{clock} \tag{2.53}$$

using assumption 2) the absolute minimum stand-by current level  $I_{\min}$  becomes

$$I_{\min} = 4 n \delta C_s f_{clock} \frac{kT}{q}$$

(2.54)

Figure 2.11

Simple Inverting Amplifier.

which gives a minimum power consumption  $P_{\min}$  of

$$P_{\min} = 8 n \delta V_s C_s f_{clock} \frac{kT}{q}$$

(2.55)

Using Eq. (2.2) in Eq. (2.55) gives

$$P_{\min} = 16 \pi n \delta V_s C_i f_{unity} \frac{kT}{q}$$

(2.56)

Comparing the above result with the result of Eq. (2.12) in which the signal frequency is assumed to be  $f_{unity}$  gives the following result

$$\frac{P}{P_{\min}} = \frac{8 \ f_{\text{unity}} \ C_1 \ V_s^2}{16 \ \pi \ n \ \delta \ V_s \ C_i \ f_{\text{unity}} \ \frac{kT}{q}} = \frac{V_s}{2 \ \pi \ \delta \ n \ \frac{kT}{q}}$$

(2.57)

for n = 1.5 and  $\delta = 7$  Eq. (2.57) gives

$$\frac{P}{P_{\min}} = \frac{V_s}{21 \,\pi \,\frac{kT}{q}} = \frac{V_s}{1.7 \,V} \tag{2.58}$$

From Eq. (2.58) follows that, for a  $\pm 5$  Volt supply, the error introduced in the calculation of the absolute minimum power required by an S.C. integrator (Eq. (2.12)) by assuming that the op amp does not consume any power is smaller or equal than about 35%. Ideally, at least, such an error should be much less the the above value since from a fundamental stand point the absolute minimum power required by the op amp is considerably less than the value given by Eq. (2.56). The reason is that the unity gain bandwidth of the simple structure of Fig. 2.11 does not approach the fundamental speed limit of MOS transistor M1 which is given be the inherent  $f_T$  of the device for the particular bias condition used. This is because the parasitic capacitance of M1 is typically much smaller than the load capacitance  $C_s$ , as it will be shown in the next section. It is, at least conceptually, possible to increase the value of the unity gain bandwidth of an op amp up to a more close fraction of the  $f_T$  of the devices used. One possible way to reach such a goal for the simple structure of Fig. 2.11 is to use positive feedback around M1 in order to obtain a larger

transconductance for the same value of the current level and device size.

All of the above considerations suggests that the ultimate limit in the power dissipation of an S.C. integrator does not come from the op amp consistently with the assumption of section 2.

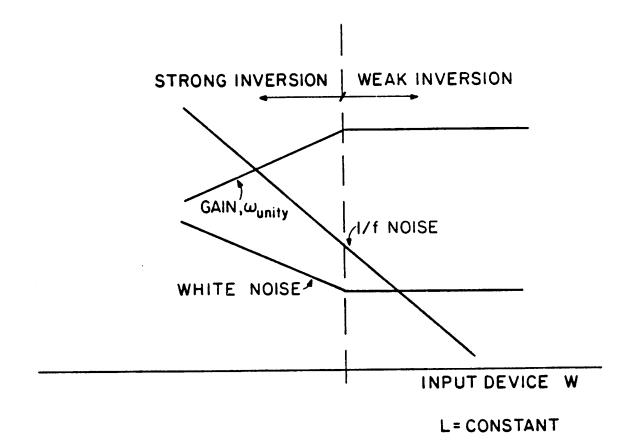

# 2.4.2. Amplifier Noise and Finite Bandwidth

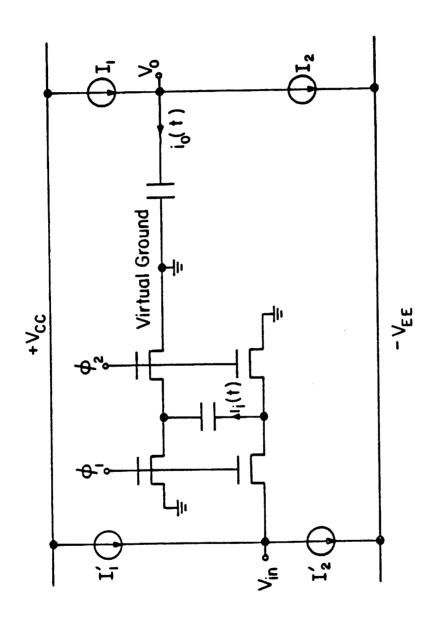

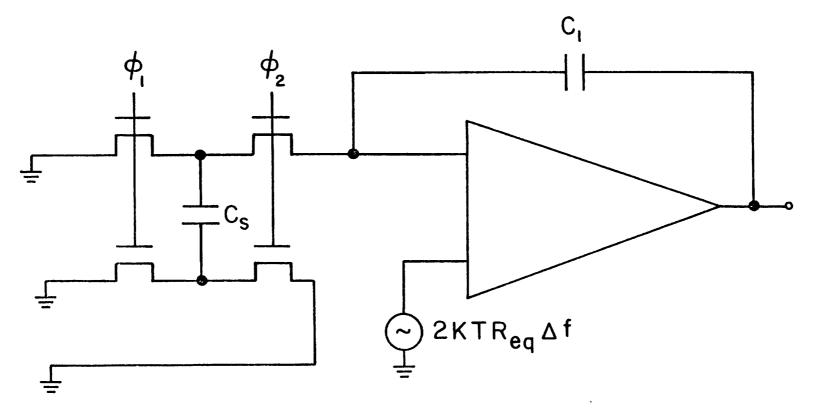

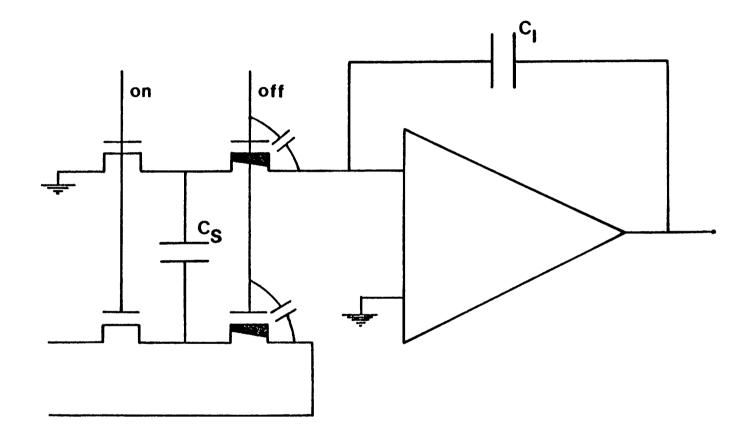

The only fundamental noise associated with the op amp is the white portion. As it was said in Section 2 this noise component can be expressed in the same form as the  $\frac{kT}{C}$ one. The relative importance of the amplifier noise with respect to the noise of the MOS switches is considered in this section. The total noise of an S.C. integrator (both MOS switches and op amp contribution) depends on the relative value of the op amp unity gain bandwidth,  $\omega_u$ , and the cut-off frequency of the low pass filter formed by the switch resistance and the sampling capacitor  $\omega_{on}$  whose value is given by  $\omega_{on} = \frac{1}{R_{oni} C_s}$  where  $R_{oni}$  is the on resistance of the i<sup>th</sup> MOS switch. With reference to Fig. 2.12 two extreme cases exist. The first case is the one considered in Section 2 where an infinite op amp bandwidth has been assumed. This gives the same noise contribution for both the left and right hand side switches and a negligible contribution from the op amp assuming a finite total noise energy in the amplifier. On the other extreme case the op amp bandwidth is assumed to be much smaller than  $\omega_{on}$ . By performing a simplified analysis as it was done by Gobet and Knob [36] both the noise contributed by the right hand side switches  $(n_R^2)$ and by the op amp  $(n_{OP}^2)$  can be expressed as a fraction of the noise contributed by the left hand side switches  $(n_L^2)$ , which was calculated in Section 2, as follows.

$$\frac{n_R^2}{n_I^2} \approx \frac{\omega_u}{\omega_{cc}} = \frac{gm_I}{2C_c} R_{on 1} C_S = \frac{gm_I R_{on 1}}{2}$$

(2.59)

Figure 2.12

S.C. Integrator with Amplifier White Noise.

$$\frac{n_{OP}^2}{n_L^2} \approx \frac{\frac{R_{eq}}{R_{on 2}}}{2 \frac{\omega_{on}}{\omega_{u}}} = \frac{gm_l \ R_{eq}}{2}$$

(2.60)

in the derivation of both Eqs. (2.59) and (2.60) Eq. (2.51) was used and  $R_{eq}$  is the equivalent input noise resistance of the op amp. From Eq. (2.59) making use of the assumption that  $\omega_{on} \gg \omega_u$  it can be concluded that the contribution of the right hand switches is negligible. On the other hand assuming that the op amp noise is contribute primarily by the input device M1 and that no high frequency second stage noise contribution occurs it follows that  $R_{eq} = \frac{2}{3} \frac{1}{gm_I}$  and Eq. (2.59) gives  $\frac{n_O_P^2}{n_L^2} \approx \frac{1}{3}$ . Between the two extreme case there is only about 30% change in the total output noise contribution, furthermore if a source coupled pair is assumed at the op amp input such a change is reduce to only about 15%. From the above results it seems reasonable to conclude that in any practical situation Eq. (2.17) will be reasonably accurate.

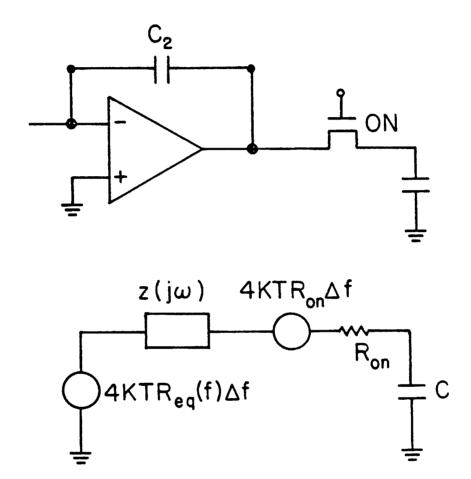

In reality one more potential source of noise degradation exist when the output of the S.C. integrator is sampled by another circuit of the same kind, which is the case in any S.C. filter configuration. This is due to the continuous time noise that is transmitted to the output by the amplifier independently of which phase of the clock is high. Such a wide band component can be aliased into the baseband by the next stage sampling operation. Fortunately for the case of a single stage transconductance amplifier the above noise contribution combines with the thermal noise of the MOS switches of the following stage in such a way that the variance of the total noise sampled is unchanged. The reason for such a behavior can be explained as follows. Consider the circuit shown in Fig. 2.13. Here a sampling capacitor and switch are sampling the output of a previous integrator. The integrator circuit consisting of the operational amplifier together with the feedback capacitor can be represented as a Thevinin source having some effective output impedance vs frequency and some equivalent noise resistance which is also a function of frequency. One can identify

Figure 2.13

Sampling of an Integrator Output by the Following Stage.

one limiting case in which the output impedance is a pure resistance, and the noise equivalent resistance is equal to the output resistance. In this case the bandwidth of the sampling circuit is reduced by the same factor that the noise power spectral density is increased, and one obtains the result that the op amp noise adds no noise over and above the fundamental kT/C noise contributed by the switch on resistance, to be discussed in the next section. This limiting case is approximated by a wideband transconductance operational amplifier with no output stage.

## 2.4.3. Amplifier Area

In this section the minimum amount of area required for the op amp is compared with the result of Section 2. The simple structure of Fig. 2.11 is again assumed. The area of the amplifier is assumed to be approximately equal to the area of M1 i.e. the load device is assumed to be much smaller than M1 and therefore neglected in the area calculation. The total area of the transistor is assumed to be equal to  $\beta$  times the area of its gate. Typical values for  $\beta$  can be taken to be between 2 and 5. In the following to obtain numerical results  $\beta = 3$  is used. Such a value can be achieved in practice by folding the transistor many times in order to have sources and drains sharing the same diffusion area. M1 is assumed to be operating in subthreshold. This is done to be consistent with the assumption used in the section dealing with the op amp power and also to insure a reasonable amount of gain in the amplifier.

The maximum current level in weak inversion for a given aspect ratio is roughly given by [25]

$$I = \mu C_{ox} \frac{Z}{L} \left(\frac{kT}{q}\right)^2 \tag{2.61}$$

Eq. (2.61) defines the minimum value of the aspect ratio  $\frac{Z}{L}$  of an MOS transistor for which the devices is still operating in weak inversion for any given current level. Minimum aspect ratio corresponds to minimum gate area for a given technology therefore

the above condition is used in the following calculation. Combining Eq. (2.50) with Eq. (2.61) an expression for the device transconductance is obtained.

$$gm = \mu C_{ox} \frac{Z}{L} \frac{kT}{q n}$$

(2.62)

Substituting in Eq. (2.53) for  $gm_{min}$  the expression of Eq. (2.62) and making use of Eq. (2.2) gives

$$\mu C_{ox} \frac{Z}{L} \frac{kT}{g n} = 4 \delta C_s f_{clock} = 8 \pi \delta C_l f_{unity}$$

(2.63)

Multipling both sides of Eq. (2.63) by  $L^2$  and solving for the gate area of M1 i.e.  $Z \times L$  gives

$$Z x L = \frac{8 \pi \delta q n f_{unity} L^2}{kT \mu} \frac{C_I}{C_{ox}}$$

(2.64)

Noticing that  $\frac{C_I}{C_{ox}}$  is nothing but the area of  $C_I$  follows that

$$\frac{Z \times L}{Area \ of \ C_I} = \frac{8 \pi \delta \ q \ n \ f_{unity} \ L^2}{kT \ \mu} \tag{2.65}$$

The op amp area was assumed to be equal to  $\beta$  times the area of the gate of M1 therefore

$$\frac{Area\ of\ Op\ Amp}{Area\ of\ C_I} = \frac{\beta\ 8\ \pi\ \delta\ q\ n\ f_{unity}\ L^2}{kT\ \mu} \tag{2.66}$$

Using  $\mu = 800 \frac{cm^2}{V \text{ sec}}$   $n = 1.5 \delta = 7 \beta = 3 \text{ in Eq. (2.66) gives}$

$$\frac{Area \ of \ Op \ Amp}{Area \ of \ C_I} = 38 \ L^2 \ f_{unity} \tag{2.67}$$

Assuming a  $1 \mu m$  minimum channel length technology it follows from Eq.(2.68) that  $\frac{Area\ of\ Op\ Amp}{Area\ of\ C_I}=1$  for  $f_{unity}\approx 2.6\ MHz$ . These results show that for future scaled technologies i.e.  $1\ \mu m$  or less minimum channel length, the dominant factor in determining the ultimate limits in the minimum achievable area of an S.C. integrator is

given by the size of the integration capacitor and not by the op amp area up to filter bandwidths well into the MHz range. This again is consistent with the assumptions of Section 2.

### CHAPTER 3

## DESIGN ALTERNATIVES FOR MICROPOWER MOS AMPLIFIERS

In this chapter we will examine some of the alternatives available in the design of core amplifiers and buffer amplifiers in MOS technology. This will give us some general design criteria which will be used in the following chapters where the actual realized circuits will be described. In all the following we exclusively refer to circuits to be used in S.C. systems, however, most of our discussion will be quite general and therefore could be applied to other situations as well.

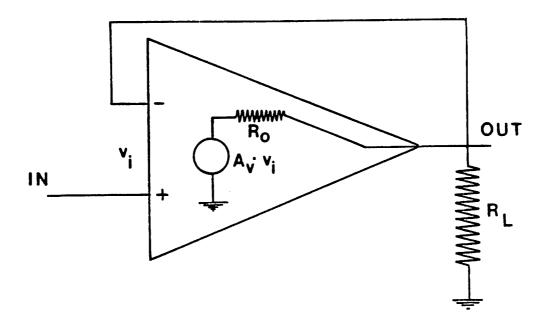

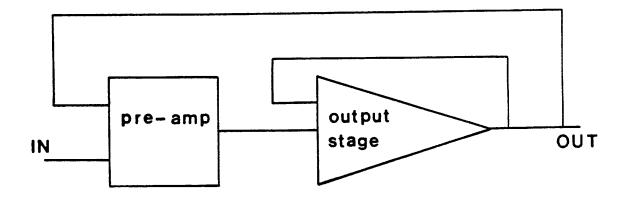

Since there is no generally accepted terminology we first define the class of circuits to which we refer in our study. We use the name core amplifier to indicate an amplifying circuit which is designed to drive only modest capacitive loads (few picofarads) and no resistive loads. Obviously the output of a Core Amplifier will never be connected directly off-chip, this fact motivates the name which has been given to it. The performance of an S.C. integrator, which is the basic building block of any S.C. circuit, is heavely dependent on the characteristic and limitations of the core amplifier used on it. This explains why we are devoting so much attention to this circuit.

A buffer amplifier, as the name suggests, on the other hand, is supposed to interface the on-chip circuitry to the off-chip world. Because of its application, a buffer amplifier has to be able to drive a relatively large capacitive load or a relatively small resistive load or both.

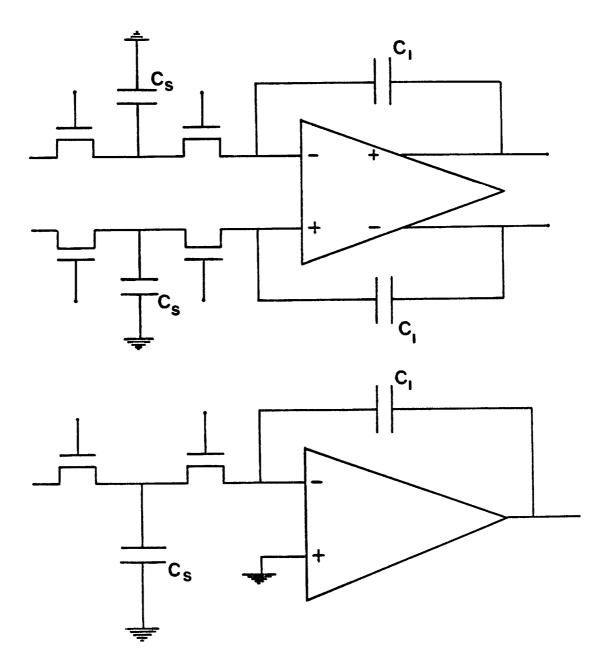

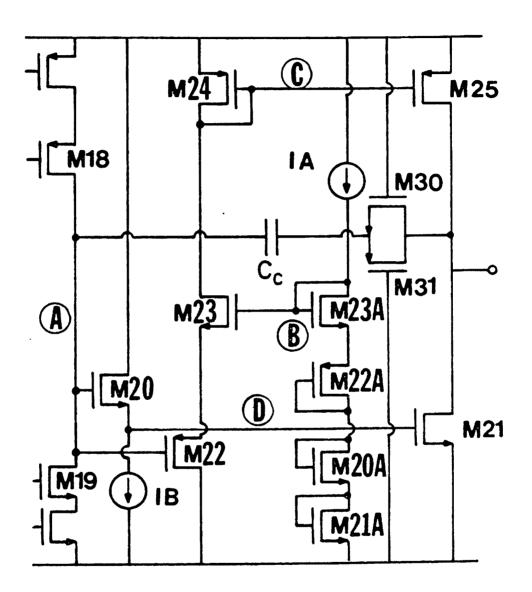

#### 3.1. DESIGN ALTERNATIVES FOR MICROPOWER CORE AMPLIFIERS

Table 3.1 shows a typical set of performance requirement for a core amplifier. The reported values are typical for an S.C. integrator [1], however, they are also representative of the performance required in other applications e.g. A/D and D/A converters [40][41]. Some comments are necessary: the minimum amount of gain required is a function of the acceptable DC error in the integrator, the quoted value of 1000 corresponds to an error of about .1% which is typical in S.C. lowpass filters [16]. For high Q bandpass applications, however, the required gain may be considerably larger. Among the specifications relating to the amplifier speed (bandwidth, phase margin, and, settling time) the most critical one is the settling time since it dictates the maximum clock frequency that can be used [42][43]. The required value of  $2.5 \,\mu$ sec or less to a precision of .1% is quite standard and allows for a clock of 128 kHz or more. All the other requirements vary from case to case depending on the particular application therefore, for the sake of generality, we only indicate some typical range of values [39]. We are, however, referring to micropower applications as can be seen from the value chosen for the power consumption.

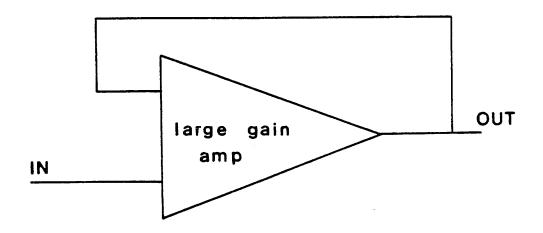

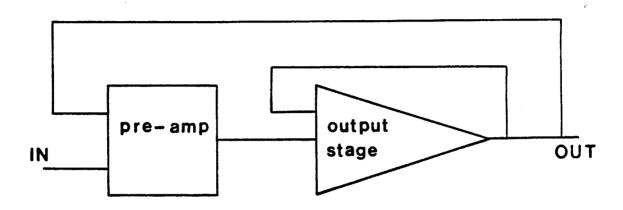

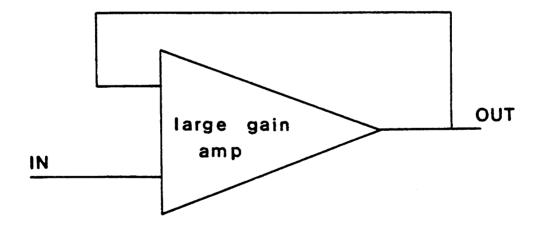

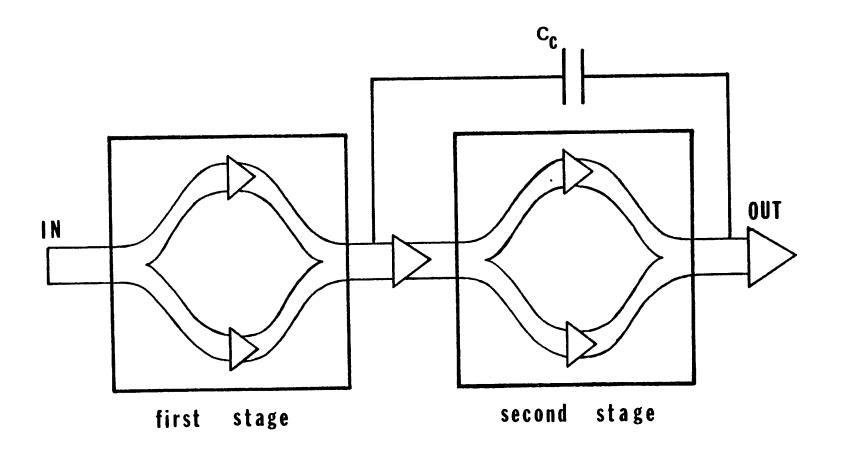

# 3.1.1. One Stage Versus Two Stages Topology

Since core amplifiers are expected to drive only relatively small capacitive loads there are no requirements on the value of their output resistance which in turn implies that no output stage is necessary. On the other hand there is a choice between a multiple stage and a single stage design. Table 3.2 compares one stage and two stage circuits listing their respective advantages. For simplicity we chose not to consider circuits with 3 or more stages because of their stability problems and the corresponding difficulty in compensating them. Such a choice seems to be well justified for CMOS circuits because of their sufficiently large gain per stage but may not always be so in NMOS [44].

| CORE AMPLIFIER TYPICAL DESIGN SPECIFICATIONS (Capacitive load only 3-5 pF) |                                                                                          |  |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| GAIN                                                                       | > 1000                                                                                   |  |

| SETTLING TIME TO .1%                                                       | < 2.5 μsec                                                                               |  |

| BANDWIDTH                                                                  | NON CRITICAL (1 - 5 MHz)                                                                 |  |

| PHASE MARGIN                                                               | NON CRITICAL                                                                             |  |

| C.MR.R.                                                                    | 70 - 90 db                                                                               |  |

| P.S.R.R.                                                                   | 80 - 100 db @ DC<br>30 - 60 db @ 100 kHz                                                 |  |

| OUTPUT SWING                                                               | .5 to 1 VOLTS FROM SUPLIES                                                               |  |

| SUPPLY VOLTAGE                                                             | 5 VOLTS ONLY or ± 5VOLTS                                                                 |  |

| POWER CONSUMPTION                                                          | <200 μW                                                                                  |  |

| INPUT NOISE                                                                | $100 \frac{nV}{\sqrt{Hz}} @ 1 \text{ kHz}$ $50 - 100 \frac{nV}{\sqrt{Hz}} \text{ WHITE}$ |  |

| RANDOM OFFSET                                                              | 2 - 10 mV                                                                                |  |

| AREA                                                                       | 80 - 300 mils <sup>2</sup>                                                               |  |

Table 3.1 Typical Core Amplifier Design Specifications

| ONE STAGE                                            | TWO STAGES                             |

|------------------------------------------------------|----------------------------------------|

| Simpler                                              |                                        |

| Better Swing                                         |                                        |

| No Compensation                                      | Better Swing<br>(If a Cascode is Used) |

| Smaller Area                                         |                                        |

| Better P.S.R.R.<br>at High Frequency                 | ÷                                      |

| No Second Stage High<br>Frequency Noise Contribution | Larger gain                            |

| Better Slewing Behavior                              |                                        |

| Easier to Make Class A/B                             |                                        |

Table 3.2

One Stage Versus Two Stages Comparison

The single stage configuration is discussed first. The terminology used is clarified at the outset to avoid confusion. With the general name of single stage amplifier is intended a circuit in which there is only one high impedance node (the output one) so that the load capacitance always present at the output determines the dominant pole. Both the classical common emitter and the common emitter common base (cascode) configurations belong to such a category. The main problem with the former is the limited amount of gain that it can achieve. In particular a simple common emitter circuit which satisfies the gain requirement of table 1 will require to operate the driver device in the subthreshold region and to use extremely long channel devices in order to achieve enough output resistance. The latter condition however will drastically lower the frequency of the second pole therefore reducing the achievable bandwidth of the circuit [39].

Because of the above considerations we believe that the cascode configuration has a decisive advantage with respect to the common emitter one particularly for micropower applications and therefore we will exclusively refer to it in the following.

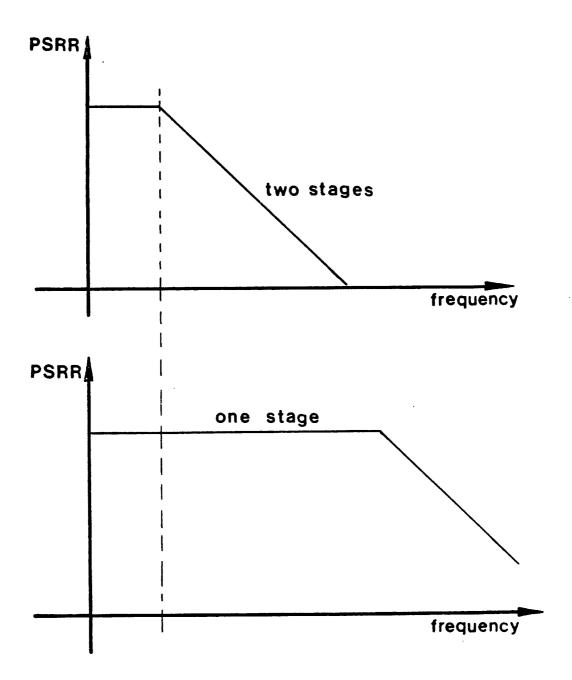

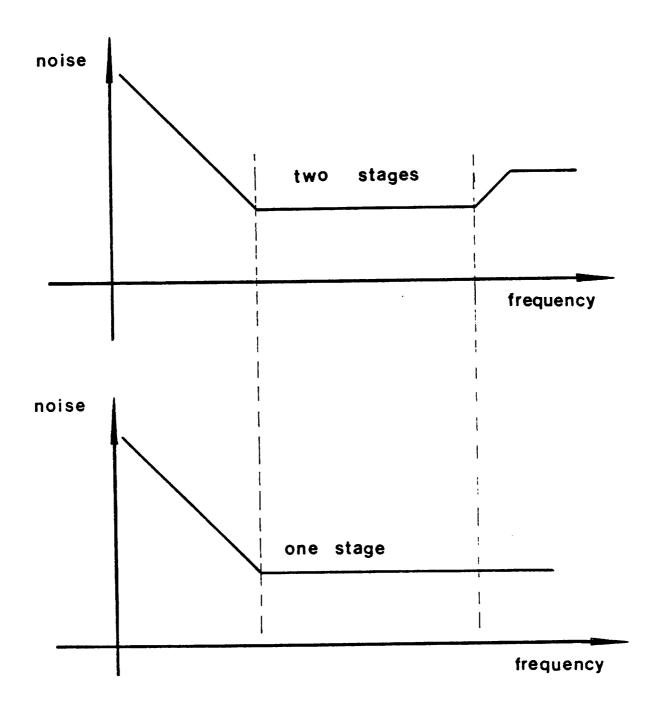

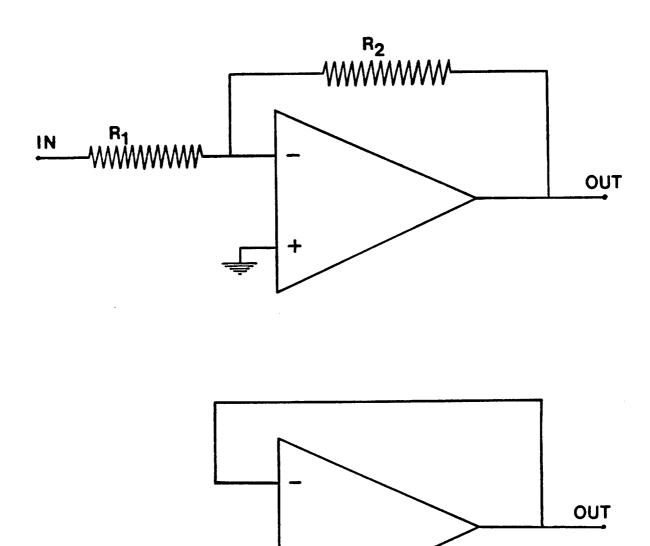

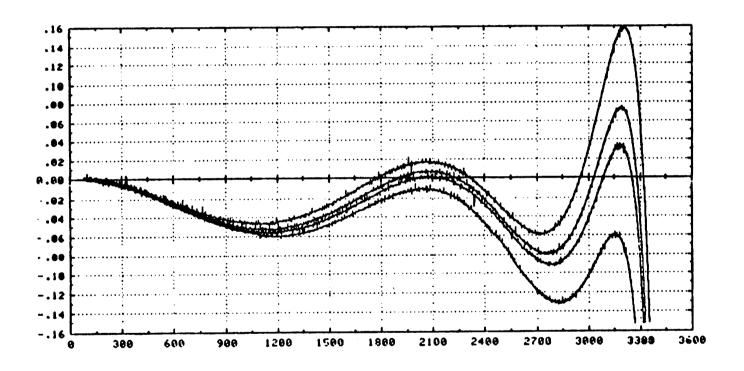

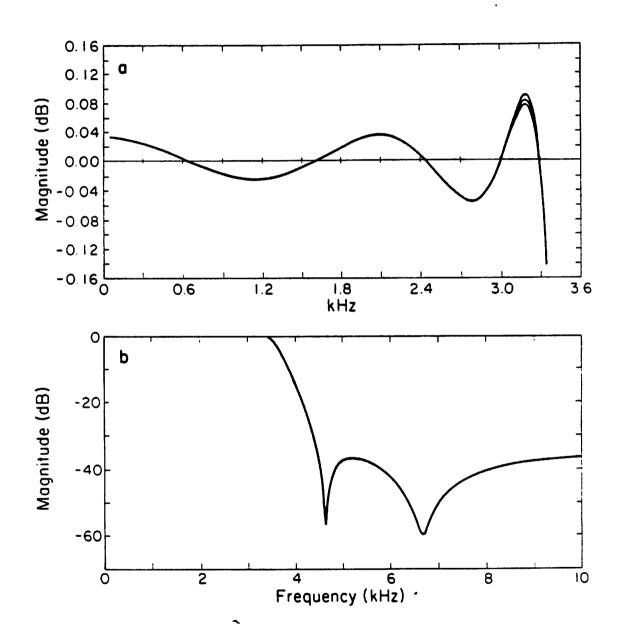

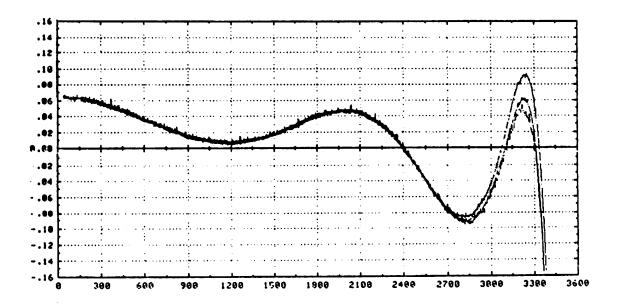

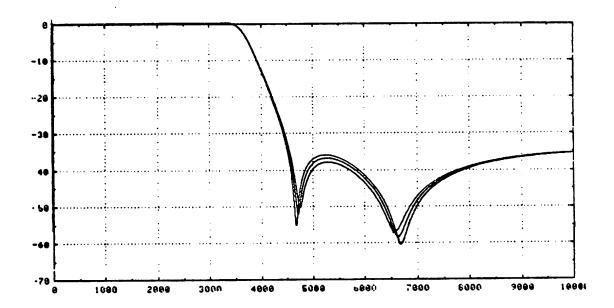

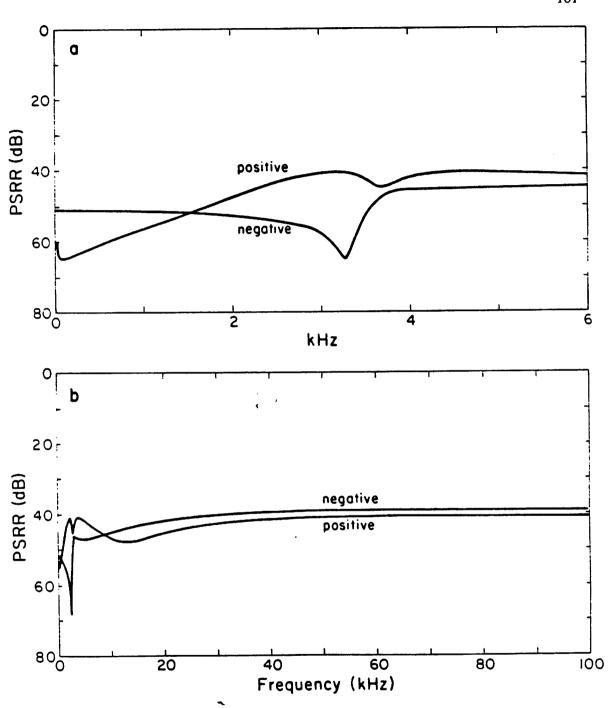

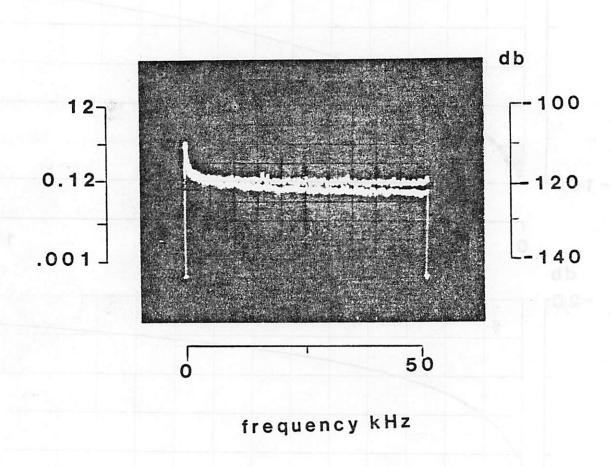

In a single stage amplifier due to the presence of only one high impedance node the load capacitance stabilizes the circuit so that in many cases no extra compensation is needed. This makes the amplifier simpler and tend to reduce the chip area requirement. Furthermore, and probably more important, due to the absence of the capacitive coupling between the supply and the output via the compensation capacitor, the high frequency power supply rejection ratio (PSRR) is improved with respect to the multistage case. This point is illustrated in Fig. 3.1 where a plot of PSRR versus frequency is shown for a single stage and a two stage amplifier assuming the same DC value. For the two stage case, Fig. 3.1 refers to the supply that gives the worse behavior between the two. The 20 db per decade roll-off for frequency above the dominant pole in the case of a two stage amplifier is due to the fact that, in this frequency range, while the input to output gain is falling, one of the two supplies is essentially shorted to the output by the compensation capacitance. This

Figure 3.1

PSRR Versus Frequency for One Stage and Two Stage Amplifiers

situation does not occur for a single stage amplifier. The reason is that the dominant pole, being associated with the output node, appears in the input-to-output transfer function as well as in the transfer function from either supply to the output. As shown in Fig. 3.1b eventually the PSRR starts to decrease even for the single ended case due to parasitic capacitive coupling from the supplies to the output. This, however, occurs for a frequency which is much higher than that of the dominant pole.

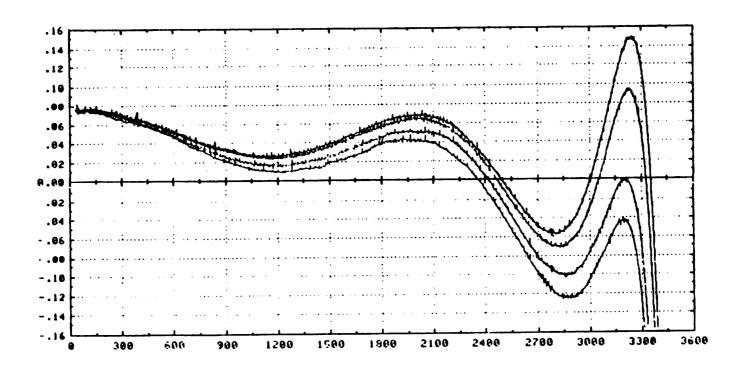

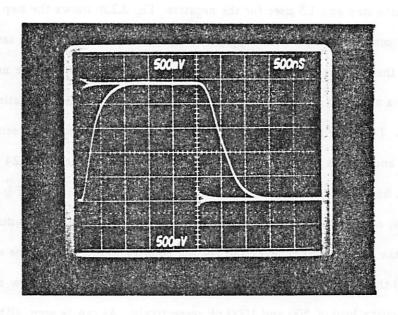

The noise behavior for the two stage and one stage circuit, is illustrated with the help of Fig. 3.2 where the input referred noise for the two possible configurations is shown assuming the same low frequency value. The extra high frequency component in the two stage case is caused by the second stage and starts to become important when the input stage gain becomes sufficiently small, such a contribution obviously does not appear for a single stage configuration. The presence of extra high frequency noise is particularly undesirable in sampled date systems since it can be aliased in the baseband by the sampling operation. Also due to the fact that no compensation is required the slew rate problem is potentially alleviated which is particularly important for micropower applications.

The final point on table 3.2, i.e. the advantage of single stage configurations when a class A/B topology is used, is particularly true if class A/B behavior is achieved by splitting the signal in two paths as is done in the design described in chapter 4. We will discuss this point in greater details in section 3.2.1 with reference to buffer amplifiers.

The right hand side of table 3.2 shows the advantages of a two stages configuration, they are: a potentially large gain even for relatively short channel devices and a larger output swing for the same supply voltage when compared with the single stage case using a cascode configuration. This last point is of fundamental importance when a large dynamic range is required and becomes more and more important as the supply voltage is reduced. In fact unless some special design techniques are adopted the use of a cascode configuration becomes impractical for a total supply voltage smaller than 5 Volts or so and a two stage

Figure 3.2

Input Referred Noise for One Stage and Two Stage Amplifiers

solution becomes the only viable alternative. This point will be discussed in greater detail in Ch.4.

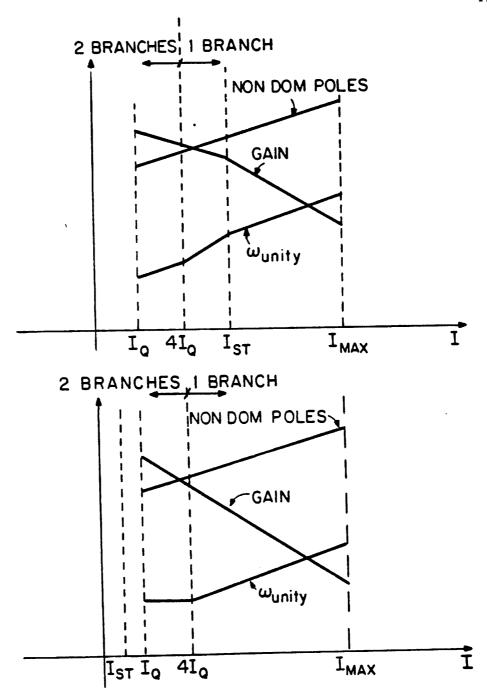

## 3.1.2. Class A Versus Class A/B Topology

Table 3 compares two other possible architectural alternatives in the design of micropower core amplifiers i.e. class A versus class A/B. Some clarification in the terminology used is again in order. We call class A a circuit whose power consumption and output current availability are fixed independently of the value of the signal applied to it. On the other hand, we call input to output class A/B, or simply class A/B, a circuit whose power dissipation, and current availability, are a function of the applied signal with peak values that can be many times larger than the stand-by ones.

The main reason to use a class A/B circuit is to reduce, and if possible eliminate, the highly nonlinear slewing portion of the amplifier step response. This is particularly important in micropower circuits due to the fact that the relative importance of the slewing portion of the settling time with respect to the linear portion increases as the current is reduced. The above point will be discussed in detail in the following.

While the main advantage of class A/B circuits in micropower applications is their low power consumption for a given speed requirement or alternatively their fast response for a given power level, they also have a large gain and the possibility of trading some of the gain for a larger bandwidth, a good output swing and a relatively low offset. This favorable behavior is a consequence of the very low stand-by current of class A/B circuits and of the fact that, in S.C. applications, all of the above characteristics are relevant only at the instant in which the output signal is sampled by the next stage therefore they have to be evaluated a the stand-by current level.

| CLASS A/B                                                  | CLASS A                                         |

|------------------------------------------------------------|-------------------------------------------------|

| Very low power                                             | Simpler structure<br>(Both design and Analysis) |

| No Slewing Problems  Large Gain (Can Trade Gain for Speed) | Easier to Use From<br>Low Voltage Supplies      |

| Better Output Swing                                        | ·                                               |

| Low Offset                                                 | Easier to Make Fully<br>Differential (CMFB)     |

Table 3.3

Class A/B versus class A comparison

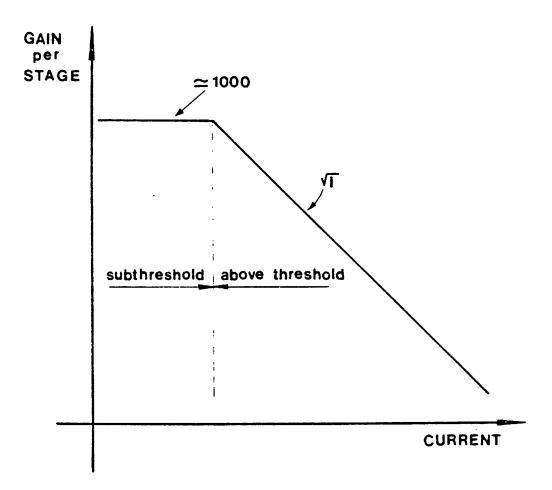

The large gain can be understood immediately from Fig. 3.3 where the maximum gain per stage is plotted as a function of the current level. The decreasing portion of the curve which varies, at least to the first order, like  $\frac{1}{\sqrt{I}}$  is due to the fact that while the transconductance of an MOS device increases with increasing current as  $\sqrt{I}$  its output resistance decreases as  $\frac{1}{I}$  [19]. The above relations are valid if the devices are operating

Figure 3.3

Gain Per-Stage Versus Current Level

well above threshold. For a sufficiently low value of the current, however, the larger device (the driver) enters the subthreshold region of operation and its transconductance becomes directly proportional to I [25]. From this point on the gain become independent from the current as it is shown in the figure.

The potentially lower input offset can be explain in the same way. For a differential pair configuration the input referred offset due to the mismatch in all the devices but the input ones can be shown to be inversely proportional to the value of  $\frac{gm}{I}$  for the input devices [19]. Since this quantity varies with I in the same exact way as the gain, it follows that by reducing the current level the reflected back offset will also be reduced untill the subthreshold region is reach. In practise this effect is not very important since the main contribution to the offset comes from the input devices. The good output swing is also a consequence of the low current level, which in turn means low  $V_{GS} - V_{I}$ , in the output devices.

The basic advantage of class A circuits is their greater simplicity from the point of view of both design and analysis. This is because they do not experience the large variations in the current level (30 to 1 and more depending on the supply voltage) which are the essence of class A/B behavior, therefore small signal considerations are guaranteed to be accurate except during the slewing mode which is, however, fairly simple to model [45][46]. Furthermore for a class A amplifier it is much easier to predict the region of operation of all the active devices during the transient and to prevent them from being cut-off or entering the triode mode when this is undesirable.

Easier design problem typically gives topologically simpler solutions which in turn means a smaller number of devices and the likelyhood of not having to stack many of them on top of each other which is very important if the circuit is powered by a low supply voltage. Finally if a fully differential configuration is used the design of the common mode feedback circuit is generally simpler for a class A solution.

Figure 3.4

Circuit Used to Show the Variation of Slew Delay with Current

The reasons why class A/B configurations are particularly suited for micropower applications are now explained in detail. Furthermore we will develop some very practical criteria for comparing in a quantitative way class A and class A/B amplifiers in terms of their achievable speed given the particular application for which they are intended and the level of power dissipation to be achieved.

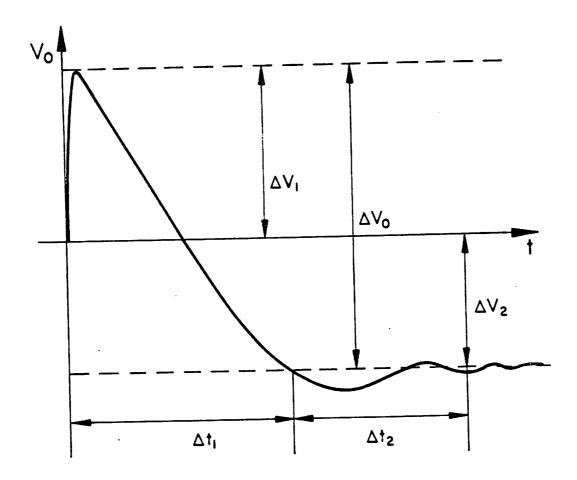

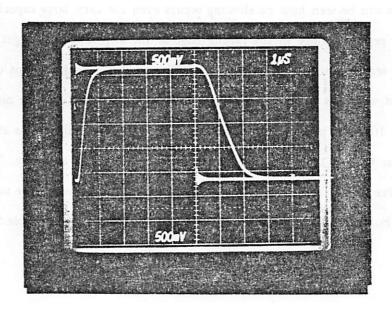

The behavior of the circuit of Fig. 3.4 when it is driven by a large voltage step at the input is analyzed for different values of the total supply current I to show the characteristic behavior of MOS operational amplifiers. The circuit under test is assumed to be using a standard class A topology.

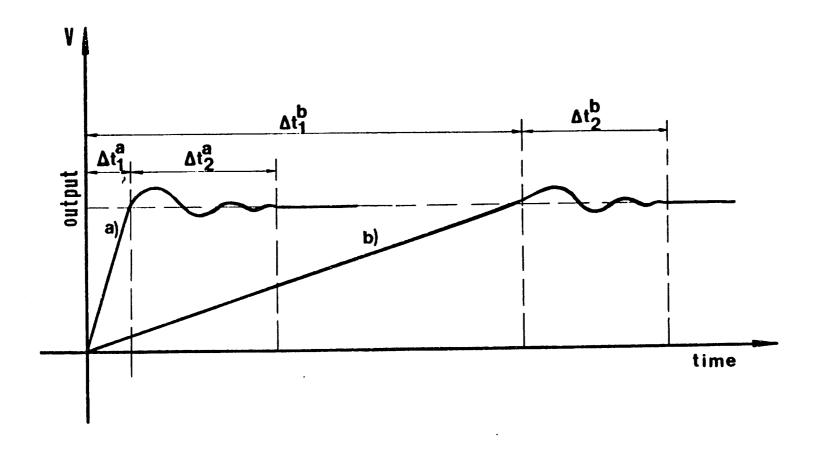

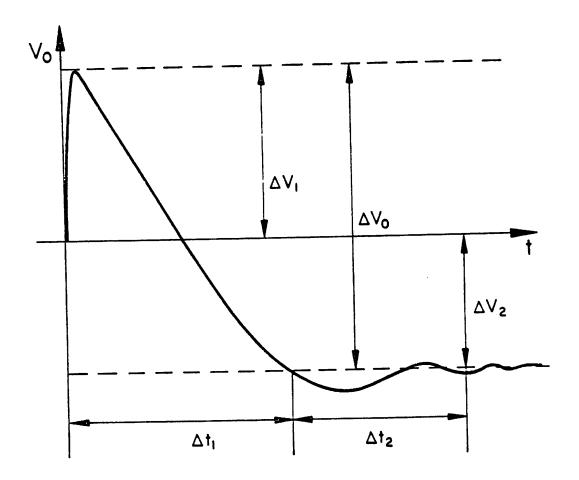

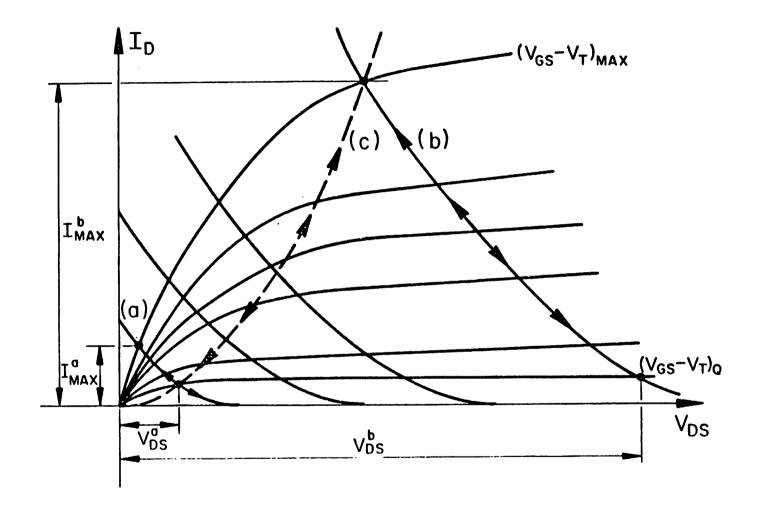

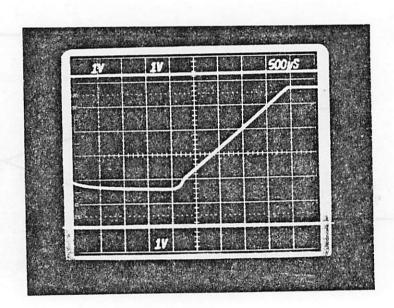

Curve a) in Fig. 3.5 is is a plot of the output voltage as a function of time in response to an input step of height  $\Delta V_i$  for a total supply current I. Curve b) in Fig. 3.5 is a plot of the voltage at the same node and for the same input but for a total supply current equal to  $\frac{I}{100}$ . Notice that the horizontal axis has been normalized to the close loop time constant of the amplifier  $\tau$  which is defined as follows:

$$\tau = \frac{1}{\omega_{unity}} = \frac{1}{2\pi f_{unity}} \tag{3.1}$$

with  $f_{unity}$  being the amplifier unity gain frequency.

The basic message of Fig. 3.4 is that the amount of time spent by the output node slewing toward its final value, relative to the total settling time, becomes more and more important as the supply current (and therefore the power) is reduced. Qualitatively this can be explained as follows. The linear portion of the settling time,  $\Delta t_1$  is proportional to  $\tau$  which in turn is proportional to  $\frac{1}{gm}$ , where gm is the transconductance of the input devices, assuming that gm is proportional to  $\sqrt{I}$ ,  $\Delta t_1$  becomes proportional to  $\frac{1}{\sqrt{I}}$ . On the other hand the slewing portion  $\Delta t_2$  is proportional to  $\frac{1}{I}$ . The ratio between  $\Delta t_2$  and  $\Delta t_1$  is therefore proportional to  $\sqrt{I}$ . A more quantitative analysis is carried out in

Figure 3.5

Output Voltage for the Circuit of Fig. 3.4

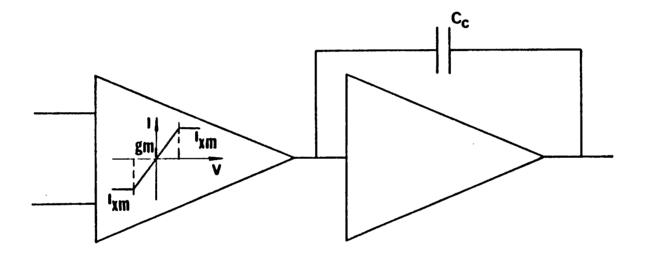

appendix A under the following assumptions which are consistent with the model used by Chuang[45]

- 1) The slew rate of the amplifier is limited by the input stage current available to charge the compensation capacitor

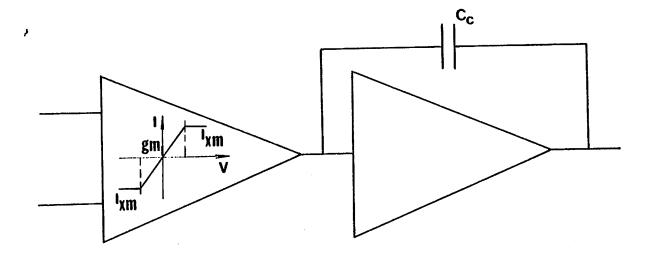

- 2) The input stage is modeled as shown in Fig. 3.6 with a maximum available current  $I_{xm}$  and a transfer characteristic with slope  $gm_I$  for values of the input signal smaller than  $\frac{I_{xm}}{gm_I}$ .

- 3) The amplifier ac transfer function is well represented by a two pole system i.e. the singularities beyond the second pole contribute a negligible phase shift at the unity gain frequency,  $\omega_{unity}$ .

- 4)  $\frac{\omega_2}{4} < \omega_{unity} < \omega_2$  i.e.  $1 > \xi > \frac{1}{2}$  where  $\omega_2$  is the frequency of the second pole and  $\xi$  is the dumping factor of the closed loop step response.

The basic result of appendix A is shown in Eq. (3.1)

$$\left(\frac{\Delta t_{2}}{\Delta t_{1}}\right) = \frac{\frac{\Delta V_{o} \ 2 \ \xi^{2}}{(V_{GS} - V_{T})_{inp}}}{\ln \frac{1000 (V_{GS} - V_{T})_{inp}}{\Delta V_{o}}}$$

(3.1)

where  $(V_{GS} - V_T)_{inp}$  is the voltage overdrive for the input devices at equilibrium and a settling accuracy equal to .1% of the voltage step amplitude has been assumed.

Although Eq. (3.1) was derived for a particular amplifier topology, it is much more general. In fact it is valid for all class A amplifiers using an emitter coupled pair as input stage provide that assumptions 1) through 4) are valid (which is the case for most of the class A amplifier reported in literature) [1][17][26][28][30][31][44]. Furthermore in some cases when a more complicated differential stage is used Eq. (3.1) needs only some minor modification to maintain its validity. As an example for a structure like the  $\mu A$  741 op

Figure 3.6

Op Amp Model for the Analysis of the Step Response of the Circuit of Fig. 3.4.

amp [39] an extra factor of  $\frac{1}{2}$  should be added to the right hand side of Eq. (3.1).

From Eq. (3.1) it may seem that the simplest way to reduce  $(\frac{\Delta t_2}{\Delta t_1})$  is to reduce  $\xi$ . In practice, however, due to the presence of higher order singularities, in doing so the linear portion of the settling time is degraded. It turns out that there is an optimum value of the ratio  $\frac{\omega_2}{\omega_{unity}}$  (and therefore of  $\xi$ ) for which the total settling time is minimum. Such an optimum value changes from case to case and can typically be determined only by time domain simulation of the step response. In the majority of the practical cases, however,  $\frac{\omega_2}{\omega_{unity}}$  is within the limit of validity of Eq. (3.1).

As an example of the information provided by Eq. (3.1) assuming  $(V_{GS}-V_T)_{inp}=200mV \text{ and } \xi=\frac{\sqrt{3}}{2} \text{, i.e. } \omega_{unity}=\frac{\omega_2}{3} \text{, follows that } \Delta t_2>\Delta t_1 \text{ for } \Delta V_o \geqslant 760mV \text{.}$

Assuming that the above analysis is valid for any current level, it can be concluded that continuing to reduce the power consumption will eventually lead to a situation in which the slewing delay is dominant. In reality when the current becomes sufficiently low the op amp input devices enter the subthreshold region of operation. From this point on the transconductance becomes proportional to the current level and the ratio between  $\Delta t_2$  and  $\Delta t_1$  reaches its maximum and remain constant independently from any further reduction of the current [25]. The value of this maximum as a function of the output step amplitude is easily shown (Appendix A) to be equal to:

$$\left(\frac{\Delta t_2}{\Delta t_1}\right)_{\text{max}} = \frac{\frac{\Delta V_o \ \xi^2 q}{n \ kT}}{\ln \frac{1000 \ 2 \ n \ kT}{q \ \Delta V_o}}$$

(3.2)

where n is the subthreshold coefficient defined as follows:

$$n = 1 + \frac{C_d}{C_{ox}}$$

where  $C_d$  is the surface depletion capacitance per unit area and  $C_{ox}$  is the oxide capacitance also per unit area. For a state of the art process 1 < n < 2 [25].

Using the same values as in the previous example in Eq. (3.2) and assuming n=1.5 gives the following result:  $\Delta t_2 > \Delta t_1$  for  $\Delta V_o > 280 \, mV$ . This shows that in micropower circuits the slew delay starts to be important from a relatively small value of the voltage step.

For a class A/B structure the above theory does not apply since the amount of current available to charge either the load or the compensation capacitance is not limited to the quiescent value but can be many times larger (up to 30 times and more) for a large input signal. In fact for a class A/B circuits the slewing delay is grately reduced if not totally eliminated i.e.  $\Delta t_1 \rightarrow 0$ .

Since class A/B circuits generally require more complicated topologies, they become attractive only when using a classical approach would yield a response in which  $\Delta t_1$  is a substantial fraction of the total settling time. The above theory gives a quantitative basis to decide between the two possible alternative (class A versus class A/B).

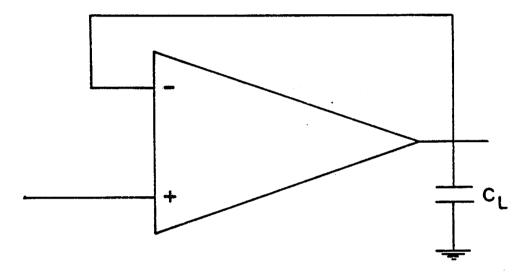

We will now try to extend the above results to the case of an S.C. integrator as shown in Fig. 3.7. Two situations should be considered depending on the structure of the amplifier. In the first case the op amp used in the S.C. integrator is assumed to have a single stage topology. In this case Eq. (3.1) can be applied unchanged provided that

- 1.  $C_i \gg C_s$  so that a feedback loop gain of 1 can be assumed for the circuit of Fig. 1

- 2. The proper value of  $\Delta V_o$  is used as explained below.

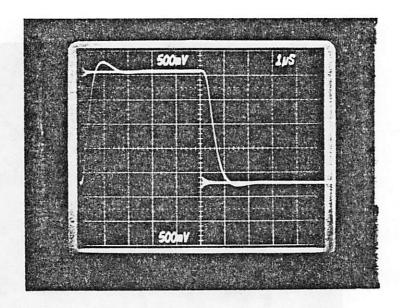

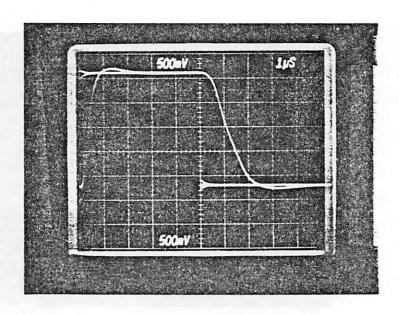

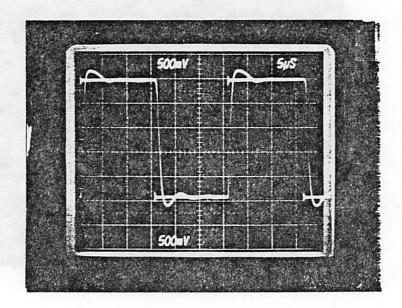

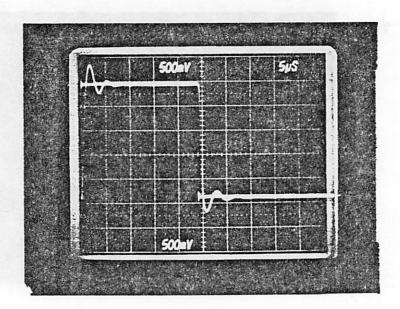

Fig. 3.8 shows the SPICE simulated output waveform for the structure of Fig. 3.7 when MOS switch M1 is closed and the charge on  $C_s$  is integrated onto  $C_i$ . As can be

Figure 3.7

Switched-Capacitor Integrator.

Figure 3.8

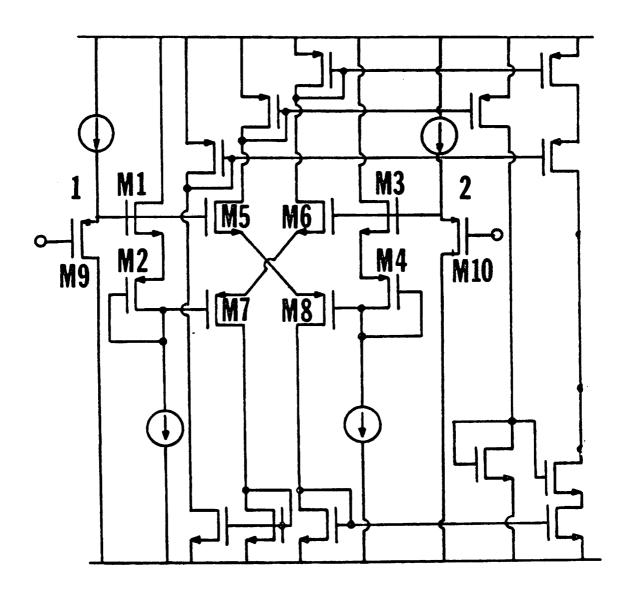

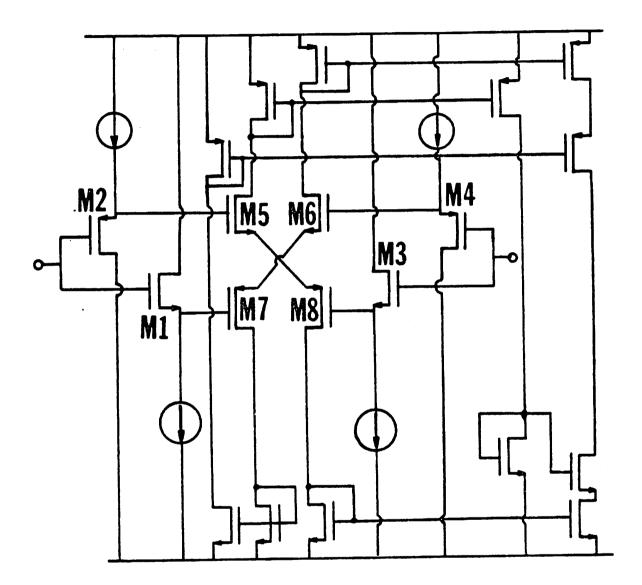

Output voltage for the circuit of Fig. 3.7 when the input switches are closed.