## Copyright © 1985, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

SPECIFYING INTEGRATED CIRCUIT PHOTOLITHOGRAPHY

PROCESSES USING HEURISTIC AND ALGORITHMIC TECHNIQUES

by

Michael Frank Klein

Memorandum No. UCB/ERL M85/73 10 September 1985

# SPECIFYING INTEGRATED CIRCUIT PHOTOLITHOGRAPHY PROCESSES USING HEURISTIC AND ALGORITHMIC TECHNIQUES

by

Michael Frank Klein

Memorandum No. UCB/ERL M85/73

10 September 1985

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# Specifying Integrated Circuit Photolithography Processes Using Heuristic and Algorithmic Techniques

Copyright © 1985

Michael Frank Klein

## Specifying Integrated Circuit Photolithography Processes Using Heuristic and Algorithmic Techniques

#### Michael Frank Klein

#### ABSTRACT

In synthesizing the fabrication process for an integrated circuit (IC), process engineers spend a great deal of time manually "integrating" existing CAD tools, algorithms, technical literature, and advice from local experts. Because of its difficulty and scope, this "integration" is rarely performed completely, and is usually only performed for a few alternative IC processes.

An expert computer-aided design system called Cameo has been developed that interactively leads the user through the synthesis steps for IC photolithography. At each step, Cameo offers the user a unique "mini-expert" from its knowledge base which reflects the method an expert would use to synthesize the process step. Thus the different kinds of knowledge used to synthesize an IC fabrication process may be integrated into a single system. The user may also provide his own solution, and may ask for further information and references on the step. Cameo is exceptionally easy to use, and allows the user to synthesize and evaluate photolithography alternatives with the SAMPLE process simulator in a matter of minutes.

Cameo is a specific application of a general framework which partitions a knowledge base consisting of heuristics, algorithms, graphs, and/or formulas

into individual mini-experts, each of which can be assigned to a single design decision. The framework allows new mini-experts to be added or the system's decision structure to be modified quickly and easily. Its knowledge base is highly modular, leading to easy modification and maintenance. Its data base structure reflects the tentative, hierarchical nature of engineering design and allows the user to incorporate previously-developed photolithography steps from libraries. Cameo is implemented in Hewlett-Packard's HPRL I and the University of Utah's Portable Standard Lisp, and presently runs on an H-P 9836 desktop computer.

Chairman

Dand a. Ho

## Contents

| 1 | Inti | roducti | tion                     |   | 1      |

|---|------|---------|--------------------------|---|--------|

|   | 1.1  | Motiv   | vation for This Research | • | <br>2  |

|   | 1.2  | Resear  | arch Contributions       | • | <br>3  |

|   | 1.3  | A Rur   | nning Example            | • | <br>5  |

|   | 1.4  | Outlin  | ne of Dissertation       |   | <br>5  |

| 2 | Sur  | vey of  | f Previous Approaches    |   | 7      |

|   | 2.1  | Simula  | lators                   | • | <br>8  |

|   |      | 2.1.1   | SPICE                    | • | <br>9  |

|   |      | 2.1.2   | SAMPLE                   | • | <br>9  |

|   |      | 2.1.3   | SUPREM-III               | • | <br>10 |

|   |      | 2.1.4   | PISCES II                | • | <br>11 |

|   |      | 2.1.5   | FABRICS II               |   | <br>12 |

|   | 2.2 | Integrated CAD Systems              | 12 |

|---|-----|-------------------------------------|----|

|   | 2.3 | AI-Based CAD                        | 14 |

|   | 2.4 | Mixed Approaches                    | 16 |

|   | 2.5 | Other Approaches                    | 18 |

|   |     | 2.5.1 Symbolic Algebra              | 19 |

|   |     | 2.5.2 Deep Reasoning                | 19 |

| • |     | 2.5.3 Constraint Propagation        | 20 |

|   | 2.6 | Other Important Work                | 21 |

|   | 2.7 | Chapter Summary                     | 21 |

| 3 | Ter | minology and General Background     | 23 |

|   | 3.1 | IC Processing Terminology           | 24 |

|   | 3.2 | Software Terminology                | 25 |

|   |     | 3.2.1. Artificial Intelligence      | 25 |

|   |     | 3.2.2 Object-Oriented Programming   | 31 |

| 4 | Cha | racteristics of an Ideal CAD System | 33 |

|   | 4.1 | Part of an Integrated System        | 33 |

|   | 4.2 | Specific Characteristics for IC CAD | 37 |

|   | 4.3 | The System Must be Flexible         | 40 |

|   | 4.4 | Interface to Other Resources        | 41 |

|   | 4.5 | Chapter Summary                     | 42 |

| 5 | The | Design Process for IC Photolithography             | 44 |

|---|-----|----------------------------------------------------|----|

|   | 5.1 | The IC Process                                     | 44 |

|   | 5.2 | IC Photolithography Design                         | 48 |

|   | 5.3 | Initial Planning Decisions                         | 48 |

|   |     | 5.3.1 Choosing the Aligner :                       | 49 |

|   |     | 5.3.2 Choosing the Etch Method                     | 50 |

|   |     | 5.3.3 Choosing the Resist Scheme                   | 52 |

|   | 5.4 | Refining the Initial Plan                          | 53 |

|   | 5.5 | The Example                                        | 54 |

| 6 | Ove | rview of Cameo's Structure                         | 56 |

|   | 6.1 | Features Differentiating Cameo                     | 56 |

|   | 6.2 | Overall Description of Cameo                       | 58 |

|   |     | 6.2.1 Implementation                               | 58 |

|   |     | 6.2.2 Appearance of Cameo to the User              | 59 |

|   |     | 6.2.3 Organization of the Knowledge and Data Bases | 60 |

|   | 6.3 | Description of HPRL and PSL                        | 62 |

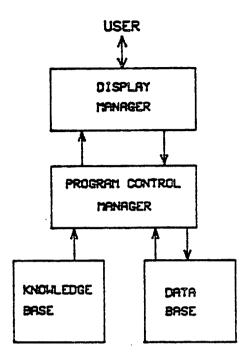

|   | 6.4 | Overall Structure                                  | 64 |

|   | 6.5 | The Display Manager                                | 66 |

|   | 6.6 | The Program Control Manager                        | 66 |

|   | 6.7     | The Knowledge Base                       | 69                   |

|---|---------|------------------------------------------|----------------------|

|   | 6.8     | The Data Base                            | 72                   |

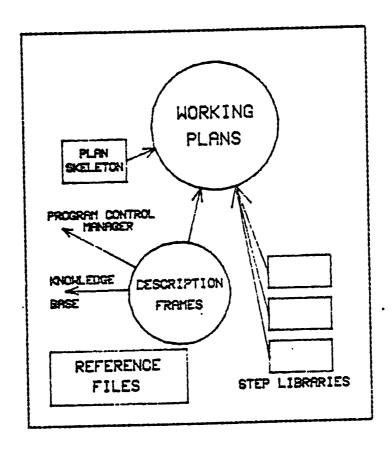

|   |         | 6.8.1 The Plan Skeleton                  | 72                   |

|   |         | 6.8.2 The Working Plans                  | 73                   |

|   |         | 6.8.3 The Description Frames             | 74                   |

|   |         | 6.8.4 The Step Libraries                 | 76                   |

|   |         | 6.8.5 The Reference Files                | 76                   |

|   | 6.9     | Chapter Summary                          | 77                   |

|   |         | $\cdot$                                  |                      |

| 7 | Can     | neo's Knowledge Base                     | 82                   |

| 7 | Can 7.1 | neo's Knowledge Base  Kinds of Knowledge | 82<br>83             |

| 7 |         |                                          |                      |

| 7 |         | Kinds of Knowledge                       | 83                   |

| 7 |         | Kinds of Knowledge                       | 83<br>84             |

| 7 |         | Kinds of Knowledge                       | 83<br>84<br>87       |

| 7 |         | Kinds of Knowledge                       | 83<br>84<br>87<br>91 |

| 7 | 7.1     | Kinds of Knowledge                       | 83<br>84<br>87<br>91 |

| 8 | Can | neo's I | Data Base                       | 107   |

|---|-----|---------|---------------------------------|-------|

|   | 8.1 | Eleme   | nts of the Data Base            | 107   |

|   |     | 8.1.1   | The Plans Data Base             | . 108 |

|   |     | 8.1.2   | The Description Frames          | . 115 |

|   |     | 8.1.3   | The Step Libraries              | 120   |

|   |     | 8.1.4   | The Reference Files             | 122   |

|   | 8.2 | An Ex   | ample                           | 123   |

|   | 8.3 | Chapte  | er Summary                      | 128   |

| 9 | Can | neo's l | Jser Interface                  | 130   |

|   | 9.1 | Import  | tance of the User Interface     | 131   |

|   | 9.2 | User I  | nterface Design Considerations  | 132   |

|   |     | 9.2.1   | Conceptual Operations           | 132   |

|   |     | 9.2.2   | Data Presentation               | 134   |

|   |     | 9.2.3   | Psychological Issues            | 135   |

|   | 9.3 | User I  | nterface Description            | 136   |

|   | 9.4 | Implem  | nentation of the User Interface | 137   |

|   | 9.5 | Examp   | ole                             | 142   |

|   |     | 9.5.1   | Expand Previous Heading         | . 142 |

|   |     | 9.5.2   | Show References on the Item     | . 143 |

•

|    |      | 9.5.3 Derive an Answer                           |

|----|------|--------------------------------------------------|

|    | 9.6  | Chapter Summary                                  |

| 10 | The  | Application 147                                  |

|    | 10.1 | Choosing a Specific Application                  |

|    | 10.2 | Understanding the Application                    |

|    |      | 10.2.1 The Causes of Linewidth Variation         |

|    |      | 10.2.2 Estimating Linewidth Variation            |

|    | 10.3 | Implementing the Application                     |

|    |      | 10.3.1 Implementing the Decision Sequence        |

|    |      | 10.3.2 Implementing the Mini-Experts             |

|    | ·    | 10.3.3 Verification or Simulation                |

|    | 10.4 | Chapter Summary                                  |

| 11 | Con  | clusions 169                                     |

|    | 11.1 | Contributions                                    |

|    | 11.2 | Observations                                     |

|    |      | 11.2.1 Observations from Potential Users         |

|    |      | 11.2.2 Observations from Cameo's Development 173 |

|    | 11.3 | Directions for Future Work                       |

|    |      | 11.3.1 Extending Cameo                           |

|      | 11.3.2  | Increase Cameo's Portability  | •  | • | •   | • | • | ٠ | • | • | • | • | • | • | • | • | 176 |

|------|---------|-------------------------------|----|---|-----|---|---|---|---|---|---|---|---|---|---|---|-----|

|      | 11.3.3  | General System Improvement    | s  |   | •   | • | • | • | • | • | • | • | • | • | • | • | 177 |

| 11.4 | Other : | Applications for Cameo's Fran | ne | w | or! | k |   |   | • |   | • |   |   |   |   |   | 184 |

## List of Figures

| 2.1 | SAMPLE output example                       | 10  |

|-----|---------------------------------------------|-----|

| 4.1 | Data Base Design for Ideal CAD/CAM System   | 36  |

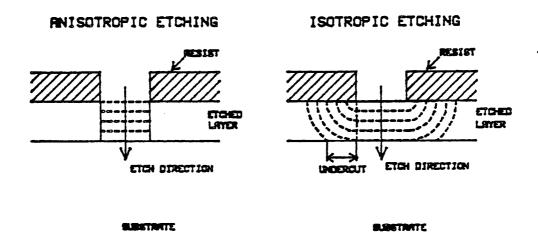

| 5.1 | Isotropic and Anisotropic Etching           | 51  |

| 6.1 | Cameo's overall software structure          | 65  |

| 6.2 | Screen example from actual running of Cameo | 78  |

| 6.3 | The main components of the data base        | 80  |

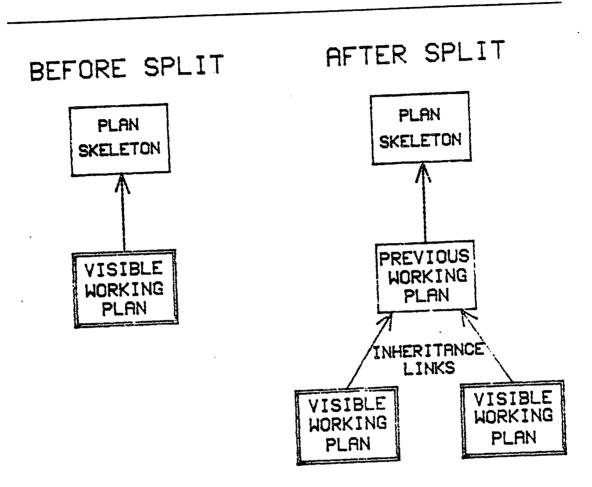

| 6.4 | Splitting a working plan                    | 81  |

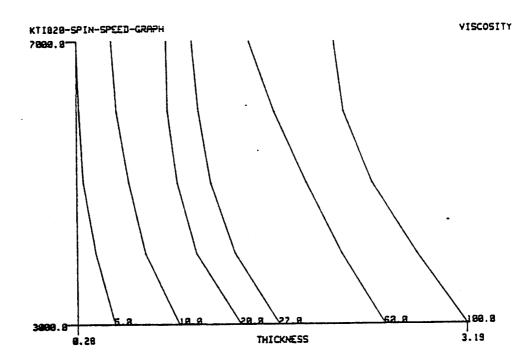

| 7.1 | Plot of spin speed graph for KTI 820 resist | 90  |

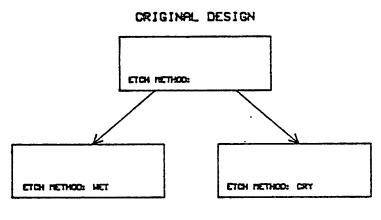

| 8.1 | Splitting a design                          | 109 |

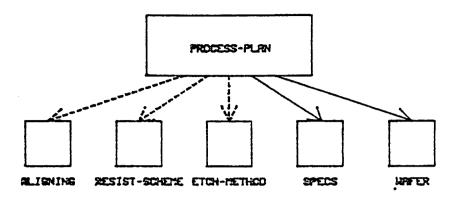

| 8.2 | Structure of the plan skeleton              | 111 |

| 8.3 | Splitting a working plan                    | 116 |

| 8.4  | Links between frames after choosing library step | • | • | • | • | • | • | • | 123 |

|------|--------------------------------------------------|---|---|---|---|---|---|---|-----|

| 8.5  | Detail of links of split working plan            |   | • | • | • | • | • |   | 124 |

| 8.6  | Example of a reference file                      | • | • | • | • | • | • | • | 125 |

| 8.7  | Reference file for viscosity design decision     | • |   | • | • | • | • | • | 127 |

| 9.1  | Complete screen example                          | • | • | • | • | • | • | • | 138 |

| 9.2  | Structure of browser item objects                |   | • | • |   | • | • | • | 140 |

| 10.1 | Screen example of estimating linewidth variation | • | • | • | • | • | • |   | 155 |

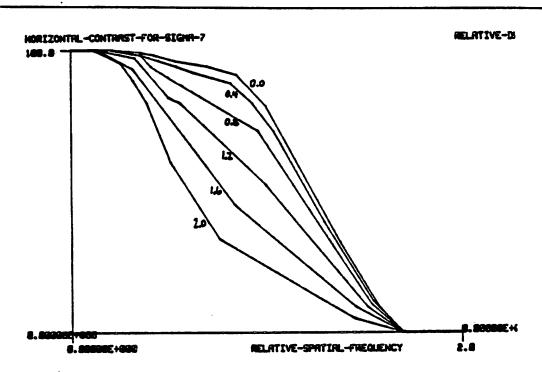

| 10.2 | Graph for finding horizontal contrast            | • | • | • |   | • | • | • | 163 |

| 10.3 | Plan verified with SAMPLE                        |   | • | • |   |   | • | • | 166 |

| 10.4 | SAMPLE input file                                |   | • | • | • | • | • | • | 167 |

| 10.5 | SAMPLE output                                    |   | _ |   |   |   |   |   | 168 |

## List of Tables

| 6.1  | Operations supported by Cameo's Display Manager | • | • | • | • | • | 67  |

|------|-------------------------------------------------|---|---|---|---|---|-----|

| 6.2  | Knowledge in the form of a symbolic table       | • | • | • | • | • | 71  |

| 7.1  | Knowledge in the form of a symbolic table       | • | • | • | • | • | 93  |

| 7.2  | Mini-expert types summary                       | • | • | • | • | • | 106 |

| 9.1  | Browser object messages                         | • | • | • | • | • | 141 |

| 11.1 | Improved internal structure                     |   | • |   |   |   | 182 |

## List of Code Lists

| 6.1 | Example of a rule and rule domain in the knowledge base | 79  |

|-----|---------------------------------------------------------|-----|

| 7.1 | Example of a rule and rule domain in the knowledge base | 85  |

| 7.2 | The solve-specific method for backward chaining         | 101 |

| 7.3 | Example of a three-dimensional numeric table            | 102 |

| 7.4 | The solve-specific method for the three-d-graph-control |     |

| •   | object                                                  | 103 |

| 7.5 | An excerpt from the code defining a symbolic table      | 103 |

| 7.6 | Example of a formula mini-expert                        | 104 |

| 7.7 | Example of meta knowledge rule                          | 104 |

| 7.8 | Rule for deciding whether HMDS is needed                | 105 |

| 7.9 | Rule for choosing KTI 820 viscosity                     | 106 |

| 8.1 | Example of the plan skeleton's process-plan frame       | 112 |

| 8.2 | Excerpt from a plan skeleton's step frame               | 113 |

| 8.3  | Description frame example                     | 117 |

|------|-----------------------------------------------|-----|

| 8.4  | Example library step frame                    | 121 |

| 8.5  | Rule for finding mini-expert for viscosity    | 127 |

| 10.1 | Mini-expert for vertical contrast calculation | 159 |

| 10.2 | Code for horizontal contrast graph            | 162 |

| 10.2 | A sule for generating SAMDIE input            | 164 |

## Acknowledgments

The first votes of thanks must go to the IC processing experts at UC Berkeley's Electronics Research Laboratory who volunteered much time and effort during all phases of this research. They are Gino Addiego, Prof. Ping K. Ko, Dr. Ping Wai Li, Prof. Andrew Neureuther, Prof. William G. Oldham, and Dr. Yosi Shacham. It is their collective expertise that forms the backbone of this research.

I also thank the people in Hewlett-Packard's Expert Systems Project, led by Dr. Steven Rosenberg, for helping me learn the basics of HPRL and the development system running on the H-P 9836 computer, and for arranging for the donation of the system I used. I would also like to thank Drs. Jeff Y.-C. Pan, Harry G. Barrow, and Jay M. Tenenbaum, and the others at Schlumberger's Laboratory for Artificial Intelligence Research for the stimulating exchanges of ideas we had in the early phases of this research.

Special thanks go to Professor David A. Hodges, my research advisor, for his support and advice, and for the just-enough guidance he gave to this

research's direction. Professors Randy Katz and Frederick E. Balderston, the other members of my thesis committee, made many substantive and stylistic suggestions on drafts of this dissertation that greatly helped its focus.

Cliff Lob, whose RUBICC circuit critic was an inspiration that AI-based CAD systems can be successful, deserves thanks for his help in getting me off the ground. It is impossible to thank everyone else who helped during my years at UC Berkeley individually, but I must make special mention of Ron Gyurcsik, Dr. Mark Hoffman, Karti Mayaram, Peter Moore, Tom Quarles, Rick Spickelmier, and Christopher Williams.

And, of course, to June, my wife, whose continuous support throughout this research allowed me to concentrate on doing the best I could.

This research was supported in part by a grant from the Semiconductor Research Corporation, and in part by a grant from Xerox Corporation with a matching grant from the University of California's MICRO program.

### Introduction

Many computer aided design (CAD) tools are available to the integrated circuit (IC) fabrication process designer. Other resources, such as local experts and technical literature, are also often easily available. But in most cases, these design resources are isolated from each other and therefore can not be used to their fullest potential.

Some areas of engineering design have been well addressed by CAD research and now have integrated CAD systems available for designers. Others, including IC process design, have not yet had the same research activity aimed at them. The main intent of the research described in this dissertation is to tie together these many IC process design resources using a wide selection of computer-based techniques.

### 1.1 Motivation for This Research

Research in IC processing is a major thrust at the Electronics Research Laboratory (ERL) of the University of California at Berkeley. Over 50 students and 10 professors are engaged in IC process research. A wealth of valuable resources exists at UC Berkeley's ERL for IC process design, such as computer-based tools like circuit, device, and process simulators, technical literature, and local experts in all phases of IC processing.

Because these resources are not tied together, however, they cannot be used to their fullest potential. The resources are difficult to find and may be difficult to apply to particular design problems. These limitations often apply to all users, even experienced IC process researchers. A CAD system that serves to tie together existing resources would be an important contribution to the UC Berkeley Electronic Research Laboratory's IC process design community.

When this research project began in 1983, its goal was to develop a CAD system for IC process design, with emphasis on investigating the usefulness of artificial intelligence (AI) techniques for this specific problem. AI techniques, particularly those of expert systems, were considered to be useful for this application because of the great deal of heuristic 1 knowledge that appeared to separate the expert designer from the beginner.

Heuristic describes solution methods that are learned by observing the solution methods to other problems [Poly57], or those learned by experience. In the context of Al, heuristic specifically refers to the "rules of thumb" knowledge that experts in an area build from experience [Haye83].

Developing a complete CAD system for IC process design is far too ambitious a task for one person to undertake. Instead, this research has concentrated on the photolithography steps of the overall IC process. Three reasons make this a good choice for this system. First, the photolithography steps are repeated once for every mask layer in the fabrication process, and thus improving this one step can provide great leverage. The second reason is that this is the area of IC processing in which UC Berkeley's ERL has the most local expertise. Lastly, photolithography is a relatively bounded area that can be considered independently of many other facets of IC processing without oversimplification.

Closely related to this research is a parallel effort to provide a computer aided manufacturing (CAM) system for the Berkeley integrated circuit fabrication laboratory. While well beyond the scope of this research project, the eventual integration of these CAD and CAM systems is a primary design goal for both research projects. The eventual system should provide integrated services spanning design, fabrication, fabrication equipment control and monitoring, yield and other engineering data analysis, cost analysis, and inventory.

### 1.2 Research Contributions

The contributions of the research described in this dissertation are three-fold. First, an investigation was undertaken to learn what kind of CAD system would be most useful for the particular environment at UC Berkeley's IC

laboratory. The initial work was along the lines of a typical expert system where the system consists of a large knowledge base and an inference engine (these terms will be explained in Section 3.2.1 on Page 25). The system would ask the user some questions and would eventually generate its "best" solution. As work progressed, goals were revised in response to user reactions, and the system's structure evolved into a highly interactive, step-by-step design advisor under the user's control.

Second, it is shown that the overall photolithography design process can be decomposed into subproblems, each of which can have a "best" solution method assigned to it. The decomposition relies on assembling an IC process from libraries of previously-used process steps, then refining the steps to customize them to the specific requirements the user has entered. This decomposition, while admittedly limiting the set of solutions that may be found with it, helps the user find a starting point for his IC process design, a valuable contribution in itself. In the case of IC process design, the design process itself is not well structured and can benefit from a system that helps designers structure the problem as an expert might.

Third, a system called Cameo has been implemented that reflects these observations and provides a useful service to IC process designers. Cameo is really a specific application built on an underlying framework developed as a result of the initial work described just above. The framework allows a large and complex synthesis problem to be broken into small, manageable, relatively-independent subproblems and assigns a specialized "mini-expert"

to each one. The "mini-expert" may represent the knowledge for solving each subproblem in whatever way is most appropriate. It was found that an equally important contribution was the set of "reference files," short, descriptive files explaining the how and why of each subproblem. A reference file can be seen by the user at any time with a single keystroke.

## 1.3 A Running Example

After Cameo's framework was designed and implemented, an application was chosen to evaluate it. More about the choice is discussed in Chapter 10. In short, Cameo was made to be an expert on linewidth control for the metal and polysilicon layers, for a linewidth of 2  $\mu$ m.

This example will be referred to or expanded upon in many of the remaining chapters of this dissertation to help ground the discussion to a real problem. Chapter 10 is devoted to a detailed discussion of the application.

## 1.4 Outline of Dissertation

Chapters 2 through 5 are largely descriptive chapters introducing many concepts and current work in the fields of artificial intelligence, computer-aided design, and IC processing. Chapters 6 through 9 describe the specific structure of Cameo and its major contributions.

Readers interested in a short summary of the research work and results should probably read first this chapter and the concluding chapter (Chapter 11). For an introduction to Cameo's structure with some but not overwhelming detail, Chapter 6 ("Overview of Cameo's Structure") is most useful. The remaining chapters will be of varying interest to readers depending on their backgrounds and interests. A short description of each chapter follows.

Chapter 2 presents a short survey of current approaches to CAD systems, with the aim of finding a direction that a new AI-based CAD system should take. Chapter 3 introduces terminology used throughout the dissertation and gives general background on the application of those terms in this dissertation. Chapter 4 examines an abstract view of the design process and how an ideal (but realistic) CAD system might look. Chapter 5 gives a very short overview of IC processing and describes a typical design process for IC photolithography. Chapter 6 introduces the structure of the system developed for this project, and describes the tools and development system used. Chapters 7 and 8 describe the knowledge base and data base of the system, respectively, in detail. Chapter 9 explains the importance and describes the structure of the user interface. Chapter 10 describes the specific application addressed by this research in detail. Chapter 11 summarizes conclusions about the research done for this project and points to areas for further work.

## Survey of Previous Approaches

Most previous contributions to IC processing CAD have been simulation programs. Outside of IC processing, previous CAD systems have ranged from simulation programs to a CAD "toolbox" whose tools are integrated by a standardized data format or a data base and a consistent, often graphic, user interface. These approaches to CAD tools and systems can be called algorithmic, since they are based on either numeric or algorithmic computations or algorithms provided for special data structures.

A few CAD systems based on artificial intelligence (AI) techniques are beginning to appear. These may be divided into two categories: those that use solely or predominantly Al techniques, and those that freely mix Al techniques and conventional tools. However, the dividing line between Al and non-Al techniques is often hazy.

#### 2.1 Simulators

Simulation programs (simulators) model physical processes. Using simulators allows many alternative processes to be investigated and data from any point in the physical process to be studied. This is especially valuable when the physical process is difficult to carry out or data is difficult to collect. An example is simulating the stress points of a bridge under many different loading conditions. The physical process itself is extremely costly to carry out, and measuring all the important stress points is essentially impossible.

For IC process design, simulation programs are as valuable as for bridge design. It is impossible to measure all the changes that a semiconductor wafer undergoes during a processing step. It is also expensive and time-consuming to route wafers through a sufficiently complete set of alternative processing steps to characterize an IC process. A simulator can provide access to a "virtual" IC processing line that has ideal measuring instruments on every wafer at every point on the processing line.

It is important to remember that simulation programs have limitations. Assuming accurate physical models, simulators may accurately simulate the world described by the user's input, but they cannot indicate whether the input describes a "reasonable" world, or whether it comes close to satisfying the user's design requirements. Thus simulators are most valuable when used as verification tools for designs arrived at by other means. One problem noted during this research is that many IC process designers tend to use simulation programs too early and too often in the design cycle.

Some popular and important simulation programs for IC processing are described in the following sections. All of these programs have contributed greatly to the state of IC processing and form a rich base of resources to build upon.

#### 2.1.1 SPICE

Originally developed as an assemblage of class projects in a computer simulation class at UC Berkeley, SPICE [Nage75] has evolved to become perhaps the best-known circuit simulation program, currently in use at over 2000 locations. Its main virtues are its popularity and its robustness [Gyur85]. Input to SPICE is a sequence of text lines describing the circuit interconnections, models for devices, and analysis commands. Output is line-oriented ASCII, either as a table or as rough plots of node voltages or currents at each time step.

#### 2.1.2 SAMPLE

SAMPLE Oldh79,Oldh80] is a two-dimensional IC process simulator also developed at UC Berkeley to study the IC fabrication processes that shape the topography on a wafer [Nand84]. SAMPLE's development philosophy was to take advantage of recent advances in the availability of computing resources to allow the simulator to be "substituted" for the actual physical processes, ideally making operation of the simulator transparent to the user. SAMPLE simulates the lithographic, deposition, and etching processing steps.

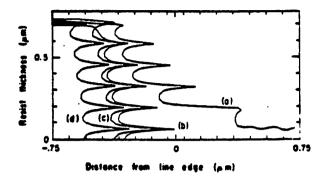

Figure 2.1: SAMPLE output example. This example shows the simulated resist line-edge profiles for two resist thicknesses and development times. This figure is Figure 9 of [Oldh79].

Designed for interactive use, SAMPLE's input format is more flexible than that of SPICE. Output can be in the forms of SPICE or as standard graphics commands suitable for interpretation by a graphics display device such as a Hewlett-Packard 2648A graphics terminal. A typical output graph from SAMPLE (see Figure 2.1) would be a cross section of the photoresist layer on a wafer after exposure and developing for a range of developing times, showing the shape and extent of the developed region for each develop time.

#### 2.1.3 SUPREM-III

SUPREM-III, developed at Stanford University, is also an IC process simulator [Ho83,Anto79]. While it is strictly one-dimensional, being able to report only on thicknesses of layers and the distribution of impurities in those layers

as a function of depth, SUPREM-III can simulate most steps of a complete IC process. Input to SUPREM-III is similar to that of SAMPLE, in that IC process parameter values are entered in a flexible command language. Output is either line-oriented ASCII or graphic.

#### 2.1.4 PISCES II

PISCES II, recently developed at Stanford University, simulates the behavior of individual devices (transistors, for the most part) as opposed to circuits like SPICE does or physical processes like SAMPLE and SUPREM-III do [Pint84]. It does so by simultaneously solving the fundamental equations for charge and electric current for two-dimensional finite elements throughout the semiconducting material described in the input. Each element is assumed to have constant material properties inside it. The elements can be of different shapes and sizes so that smaller elements can represent parts of the material where its properties vary more widely over small regions.

Some initial decisions in PISCES II are based on heuristics (rules of thumb) which help PISCES II converge quickly to an initial starting point for further simulation. This knowledge is built into the code and is not separate as in an expert-system knowledge base.<sup>1</sup>

Input to PISCES II can be in the form of line-oriented ASCII input, or a preprocessor may be used to enter the same information in an interactive

One of the major distinctions between expert systems and conventional programs is the explicit separation of the knowledge needed to solve a problem from the mechanism that solves it. More about this is presented in Chapter 3.

graphic form. Output is in tabular ASCII form, but plotting postprocessors are available for graphic output.

#### 2.1.5 FABRICS II

FABRICS II is different from all other simulators discussed so far, in that it simulates the variances in outcomes of an IC process due to disturbances or random perturbations in the process [Nass83]. Output includes probability distributions of outcomes such as yield as a function of sheet resistance [Stro84]. It uses simplified analytic models of the steps of the IC process derived from solving boundary conditions of the complete analytic models to keep computation time to a minimum.

### 2.2 Integrated CAD Systems

Many recent CAD systems have taken the approach of providing an easy-to-use "front end" to a CAD toolbox. These systems vary a great deal in how open their architecture is. An open architecture allows others to add capabilities to the system, while a "turnkey" closed architecture is available only as a monolithic system with continued product and customer support a major part of the system's cost.

Commercial integrated CAD systems abound, of which General Electric's Calma system is the most widely used. The Calma system, like other commercially available systems, has a closed architecture. In contrast, most research CAD systems have open architectures. This difference is mainly

due to strategic reasons. The vendor of a monolithic turnkey system knows that customers will incur high "switching costs" to switch from one system to another and are therefore reluctant to do so. Most customers of the commercial systems would prefer a turnkey monolithic system to avoid potential support problems, while the research community usually prefers the flexibility an open architecture provides and is not as concerned about compatibility and support, and is concerned about being locked in to any particular commercial product.

As part of a major research program at the Massachusetts Institute of Technology in computer aided manufacturing, a program called MASTIF [Boni85] has been developed. MASTIF uses graphics and a window-oriented user interface to tie together existing simulation, synthesis, and analysis tools in a uniform fashion. Quoting from the abstract to [Boni85],

MASTIF provides a common, interactive user interface to different process simulators (both one- and two-dimensional)... MASTIF provides process design tools including incremental Process Description development and analysis, as well as version management of Process Descriptions and physical cross-sections.

MASTIF helps solve one of the major problems in IC process CAD, the inaccessibility and incompatibility of many of the available IC processing CAD tools.

A widely used open-architecture IC layout system called Kic [Kell82a], developed at UC Berkeley, is a good example of an integrated CAD system. It provides a central CAD data base (Squid [Kell82b]) and a graphics-oriented user interface. Special programs that perform specific tasks like simulation,

layout rule checking, layout compaction, PLA generation, and so on, are easily interfaced with the data base and user interface. Another important toolbox-based CAD system, also developed at UC Berkeley, is the Magic layout editor [Oust84].

An optimization program that serves as a front end for other specialized programs that is in use at UC Berkeley is DELIGHT [Nye83]. DELIGHT consists of optimization algorithms and an interface language that links other programs such as simulators with the optimization algorithms in well-defined ways. DELIGHT is used less interactively than the previous examples.

### 2.3 AI-Based CAD

Whereas an integrated toolbox CAD system provides the tools needed to perform a design task, most recent AI-based CAD systems help the user find a design strategy. The design strategy can then be carried out using a CAD toolbox system. Some AI-based CAD systems perform only strategic decisions, while others (detailed in Section 2.4) mix AI techniques with conventional CAD tools.

The VLSI Design Automation Assistant (DAA) being developed at Carnegie-Mellon University uses heuristic knowledge to generate a technology-independent layout description of a VLSI system given an algorithmic description [Kowa83]. DAA first decides on the system's "global allocations," such as the number of global registers and ports, and establishes constraints and timing information if not all of these are supplied. It

then iteratively makes decisions about dividing the system into modules and routing the data path. When this is done, global improvements are made such as removing or combining redundant registers and logic. DAA is implemented almost exclusively in OPS5 [Forg81]. Its designers recognized the need for algorithmic routines such as counting, cost estimation for evaluating choices, and checking set membership of elements, and rewrote rules for these operations as procedures in the C language [Kowa85].

A research group at the Massachusetts Institute of Technology has been applying AI techniques to VLSI circuit and systems design and layout since 1979 [Suss79]. This group has emphasized the development of integrated systems, decomposing complex design problems into hierarchical or other structured abstractions in order to simplify the problems. The current direction of their work is to develop "junior assistant" systems where the system works interactively with the user, using its knowledge about the design problem to be able to offer timely and relevant help to the user. This approach is modeled after work done to develop a "programmer's apprentice," also at MIT [Rich79].

An interesting application of expert systems to circuit design is RUBICC [Lob84]. RUBICC uses knowledge about NMOS digital circuit design to act as a circuit critic, pointing out possible errors in a design such as floating nodes, too many threshold drops, and other typical design problems. Work on a more general, technology-independent version of RUBICC is described in [Spic85].

Another AI approach to CAD focuses on developing "consultation systems" for a specific problem, where the user answers a series of questions and the system generates one or more plausible solutions. The usage of this type of system is less interactive than with the junior assistant system. The consultation system relies on an extensive knowledge base about its application field, so may be difficult to maintain in a fast-changing field.

One system using AI techniques for IC processing was developed at Hewlett Packard Laboratories for diagnosing problems with photolithography while the wafers are undergoing processing [Clin85]. This is a diagnosis system as opposed to a design or synthesis system.

## 2.4 Mixed Approaches

A mixed approach to a CAD system is one that uses a combination of algorithmic and AI-based approaches smoothly integrated into a single system. The appeal of a mixed approach is that the "best" solution method—AI, algorithmic, or a combination—can be used for each problem in the decomposition of the overall design problem. This is an area of active current research.

A major effort in this area is ARSENIC, the work of Prof. Daniel Gajski at the University of Illinois at Urbana-Champaign [Gajs84]. ARSENIC is a "quasi-expert system" for IC system and layout design. Gajski has decomposed the IC design problem into a three-level hierarchical design process.

ARSENIC consists of a library of specialized silicon compilers that are assigned to subproblems of this decomposed IC design process. A combination of heuristics and algorithms determines the assignment of these silicon compilers to the subproblems. The system is highly interactive. As will be seen, there are many similarities between ARSENIC's and Cameo's design philosophies.

A major research program in VLSI chip design is proceeding at Schlumberger's Laboratory for Artificial Intelligence Research [Kram85]. This research combines ideas from a number of areas being researched at both Schlumberger and Stanford University, including developing representations for designs, using these design representations to reason about the design. and incorporating the reasoning mechanisms with other synthesis and analysis tools. Current and previous work relevant to this research includes the Palladio system, a circuit design environment [Brow83]; MARS, a hierarchical rule-based circuit simulator [Sing83]; Corona, a design description language [Sing84]; and DIRT, a program that derives heuristic rules describing a device's behavior from a functional description of the device [Kram84].

Another research program at CMU is developing an expert-system-based VLSI design environment [Bush85]. ULYSSES (Unified LaYout Specification and Simulation Environment for Silicon) accepts IC descriptions as logic equations and analog circuit descriptions. With assistance from the designer, it will produce a geometric layout for the design, then verify that the layout meets desired electrical specifications. The emphasis is on controlling existing CAD tools rather than writing new CAD tools. Current

and previous research work relevant to this project includes the Palladio system described above [Brow83]; a hardware description language called DIF [Bush83b]; Delilah, a graphic user interface [Bush83a]; OPS5, the knowledge representation language used [Forg81]; the Designer's Workbench, an early design environment developed at Bell Laboratories [ONei79]; Demeter, a design methodology and environment for the highest levels of computer and computer network design [Siew83]; and SRL (Schema Representation Language), used in ULYSSES for archival storage of designs [Wrig83].

The SRC-CMU Center for Computer-Aided Design at Carnegie-Mellon University has been investigating mixed and otherwise integrated approaches to developing a large CAD and Computer Aided Manufacturing (CAM) system for VLSI [Dire81].

Much work in a large integrated CAD system defies easy categorization into AI-based vs. algorithmic approaches, however. A chip routing or placement program certainly incorporates some heuristic knowledge in addition to algorithmic routines. Many layout design rule checkers, to ensure flexibility in the face of constantly changing technology, express knowledge about allowed and disallowed layout combinations as "layout rules" separate from the control and algorithms of the rest of the program.

#### 2.5 Other Approaches

Other approaches that do not fall cleanly into AI-based approaches, algorithmic approaches, or a combination of the two are currently active research

areas. The work at MIT referred to earlier (Section 2.3 on Page 15) mixes a number of approaches, including those detailed below.

#### 2.5.1 Symbolic Algebra

Most programs can perform some aspects of algebra by repetitively plugging values into a given equation to find answers. Others can solve complex systems of linear equations once the equations' coefficients have been entered. Symbolic algebra programs like MACSYMA [Math77], however, work with the actual symbolic representations of the equations. These programs can perform operations on the equations by factoring, algebraic simplification, definite and indefinite integration, etc. Thus a system incorporating symbolic algebra might be able to mimic an expert's approach to a problem by performing the same algebraic operations on equations that the expert might.

#### 2.5.2 Deep Reasoning

Deep reasoning systems use special models to simulate the systems they represent [Brow77,Pan83]. Often these models are qualitative in nature, specifying the behavior of the system in inexact terms.<sup>2</sup>

While this is a similar approach to the algorithmic simulators discussed earlier, deep reasoning systems use some Al techniques in their operation.

<sup>&</sup>lt;sup>2</sup>An example is describing a resistor by saying that the voltage across it increases as the current through it increases.

primarily the separation of the application-specific knowledge from the control portion of the program, and the qualitative, often heuristic, models used.

A very good example of a deep reasoning system is described in [Pan83]. This system uses its deep knowledge about the specific application to diagnose multiple dependent failures, something most diagnosis systems cannot do.

#### 2.5.3 Constraint Propagation

Any two or more variables that are not completely independent of each other are somehow constrained in the sets of values they take [deKl80]. Whenever any variable in an equation takes a value, this immediately constrains each of the remaining variables to a smaller set of values. For most useful constraints of N variables, if N-1 variables have taken values, the value of the Nth variable can be immediately determined.

Typically one variable will take part in more than one constraint, analogous to most analytic problems where any one variable appears in more than one equation. Thus a single variable changing can cause a rippling effect throughout all variables related to it. When one variable's value is assigned or changed, the constraint propagation system checks to see if any other variables or parameters can be calculated or updated. Constraint propagation can be used to maintain correct system state under changing conditions.

<sup>&</sup>lt;sup>3</sup>Multiple dependent failures occur when a primary failure, such as a transistor shorting causes secondary failures, such as a resistor burning and a fuse blowing, to occur. A simple-minded diagnosis system might simply suggest replacing the fuse or the resistor, or may not even be able to diagnose anything since this particular combination of failures does not match anything it is programmed for.

#### 2.6 Other Important Work

One important factor in Cameo's development was work done by Clancey [Clan84] on Classification Expert Systems. These systems do not attempt to piece together a complete solution to a problem from scratch but instead have coded into them a number of potential solutions expressed in highly general ways; their job is to choose from among these solutions by classifying the problem to fit the known solutions, and to refine the chosen solution(s) until the desired level of specificity is reached.

Clancey's work led to the idea of using step libraries (as explained in Section 6.8.4 on Page 76) of "canned" photolithography steps. After choosing one or more steps from libraries, the system would concentrate on refining the choices.

#### 2.7 Chapter Summary

Simulation programs are very valuable tools but their limitations must be kept in mind. They are best used as verification tools.

Open-architecture integrated CAD systems appear to have great promise in improving designer productivity. The main reasons are that they provide a standardized data structure and consistent user interface to a host of special tools, and their open architecture allows new users to add special-purpose tools of their own. This latter capability is essential for most CAD systems since the technology they address is constantly changing.

Recent integrated CAD system efforts emphasize integrating existing tools rather than developing yet more new tools. Integrated CAD systems built with a "toolbox" approach assume that the design process itself has been decomposed into phases that can each be addressed by a special-purpose tool.

Most CAD systems surveyed cannot answer a user's question of why a certain step should be performed a certain way. Most assume a quite competent level of user expertise in the design field. Often the novice designer must find his own way through the trees to see the forest.

Al techniques hold great promise in addressing certain problems where heuristic knowledge, rather than numeric or algorithmic routines, is the predominant method of solving problems. A few systems have recently appeared that mix Al techniques and conventional CAD tools. Like recent integrated non-Al CAD systems, these emphasize the integration of existing CAD tools. The Al techniques are usually used to help the user make initial design decisions and choose appropriate tools for further designing.

A successful design philosophy for this CAD system may be one that combines all these observations. It should offer a standardized data structure and a user interface that tie various special-purpose tools together. Its architecture should be open, allowing users and future system developers to add tools easily. It should be able to mix conventional and Al-based tools, depending on the specific problem the tool addresses. The user should be able to ask "Why?" of the system.

# Terminology and General Background

Since this research combines technical concepts and terminology from the two diverse areas of IC processing and computer science, and readers will probably be more familiar with one area than the other, some explanation of terminology is in order. In the following two sections, some of the most common terms used in this dissertation are described. Other terms used less commonly will be described as they are introduced in context.

The first section of this chapter introduces terms used in IC processing, while the second section concentrates on software terminology. Both sections introduce terms that are used extensively throughout the remainder of this dissertation. While intimate familiarity is certainly not required of either area, some understanding will help greatly in following the discussions in the rest of the dissertation. Thus some terms are defined rather narrowly, reflecting only the context in which they will be used in this dissertation.

## 3.1 IC Processing Terminology

An integrated circuit (IC) process is the set of fabrication steps that a semiconductor wafer goes through to become a finished product. A complete IC process normally consists of about 8 to 16 major process steps, each of which consists of a photolithography step and a processing step.

Photolithography is the step that transfers an image from a mask to the wafer. The photolithography step defines regions on the wafer corresponding to patterns on the mask, and is usually followed by the actual processing step that affects those regions.

IC process design is the design activity that results in a set of process steps, often called the process flow. In most cases, IC process design is separate from circuit or system design and physical layout design of the IC. It is strictly involved with the fabrication process, and assumes that the person performing the processing already has a set of masks generated by other CAD resources like layout tools.

However, all three of these IC design phases are interrelated, although the extent to which they interrelate varies: One extreme is the case where an IC design pushes the state of the art in all three areas. In this case, design of the circuitry, layout, and processing steps cannot be considered separately at all and iterative design of all three phases must be done. This is also the matter of course when the final product is a high volume item and sales volume will justify the cost of iterative development. Primary examples are dynamic memories and analog circuits.

The other extreme is beginning to appear, where a "silicon foundry" provides a standardized IC process. It publishes the specifications for that process, and anyone using it must adhere to its requirements. This affects both the circuit or system design and the physical layout of the chip, as compromises may have to be made in both these areas to accommodate the given IC process.

For the purposes of this dissertation, the result of the process design activity is a process plan, since the result looks very much like a step-by-step description of actions to take. Usually the goal of IC process design is a complete IC process, but sometimes it is just one or a few specific process steps that might form a subset of the overall IC process.

#### 3.2 Software Terminology

## 3.2.1 Artificial Intelligence

Cameo is an expert system, a system that has some amount of knowledge built into it that enables it to perform certain limited tasks as well as or better than a human expert in the same area. Expert systems combine many results of artificial intelligence research into areas such as knowledge representation and the human decision method. Expert systems are specifically intended to emulate human performance in a very narrow area.

A number of properties are generally accepted as differentiating an expert system from conventional software systems, among them:

- Expert systems separate the method of solving problems from the information used by the solution methods. Most computer programs are written with knowledge and method intertwined in the same code. An expert system separates the two into a knowledge base and an inference engine. The inference engine is intended to be general purpose and ideally makes no assumptions about the content of the knowledge base, while the knowledge base customizes the expert system to its specific application. The price to pay for this flexibility is execution speed.

- Expert systems can deal with complex application fields by using heuristic knowledge to narrow the set of solutions to a problem to a much smaller set that deserve further investigation.

- Most of the knowledge entered into an expert system is surface knowledge, or superficial knowledge. This knowledge is often in the form of indirect cause-and-effect relationships gained by experience, and is not based on rigorous application of theory. Most conventional programs use deep knowledge, like circuit simulators that use precise models of devices to simulate their behavior.

- Most expert systems are goal-directed, in that the user specifies a goal for the system to solve, and the system uses its store of knowledge in whatever order is needed to attempt to "prove" that goal. In contrast, most conventional programs work through a sequence of steps determined by the input data to arrive at an answer. In other words, most

conventional programs are deterministic, whereas expert systems are not.

Most expert systems rely heavily on pattern matching instead of numeric computation to identify the bits of knowledge in their knowledge base that might aid in proving a goal.

Most expert systems are goal-directed, using a process called backward chaining. A goal is given to the system to attempt to prove. All parts of Cameo's knowledge base that employ Al techniques are based on the goal-directed model of reasoning.

In backward chaining, the expert system follows the following steps until it has succeeded or failed to prove the goal:

- 1. If the goal matches an item that is already in its data base, then the goal is already proven and backward chaining is finished.

- 2. If the goal does not yet exist in the expert system's data base, its knowledge base is consulted to find any bits of knowledge that might prove the goal. These bits of knowledge are most often expressed as production rules, or "IF... THEN..." rules. If the "THEN" part of the rule matches the goal, then the "IF" part of the rule is adopted as another goal and the system runs through these same steps with it.

A short example will illustrate. Suppose it is known that Bill is going to London and he is trying to decide whether to take a raincoat. Bill would

ask his expert system whether a raincoat is necessary in London. Further suppose that the expert system has the following rules already entered into it:

IF the weather is raining,

THEN you will need a raincoat.

IF you are in London,

AND it is winter,

THEN the weather is raining.

The expert system finds that the successful conclusion of the first production rule would prove the goal, so it uses it. The premise of this rule (IF the weather is raining) is then checked against the data base to see if this fact already exists. It does not, so the expert system adopts it as a goal and attempts to prove it.

The second rule's conclusion could prove the new goal, so it is now selected. Bill has already told the system that he will be in London, so the first part of the premise exists in the data base. The data for the second part is not anywhere to be found (assuming the system is not tied into a weather information service), so the system asks Bill, "Is it winter?" If Bill replies "Yes," then the second rule's premise is satisfied, so it concludes successfully. This now satisfies the premise of the first rule, so it concludes successfully in turn, informing Bill that he will need a raincoat.

Some expert systems are data-directed and use what is known as forward chaining. Whenever a new fact is entered into a data-directed expert system, all rules whose premises contain that data are checked to see if their entire premises are satisfied. If so, the rules conclude successfully and the data specified in their conclusions are added to the system's data base. This may in turn cause other rules to become satisfied, and so on.

There are many ways to implement expert systems. One way is by using frames as data structures to hold data in the data base [Robe77a,Robe77b].

A frame data base is the major part of Cameo's internal structure.

A frame is much like a record in Pascal or a structure in C with two important exceptions:

- A frame's members (slots) can appear and disappear dynamically.

- Frame systems use the properties of hierarchical inheritance.

A data base of frames most closely resembles a hierarchical data base Date81], but frame systems allow referring to frame members or to other frames by their names instead of by pointers or addresses. This allows the dynamic nature of such a system to be more easily implemented since address and size information is not kept with the link itself.

Whereas Pascal's records and C's structures are fixed data structures with explicitly defined members, a frame can both vary in size after its initial definition and can appear to have slots that were defined in another frame. The inheritance properties of frames are well suited to expressing data in

a manner more natural to people. When a frame is defined as a child of another frame, the new frame "inherits" all the structure and data of the other frame, and may also add members and data of its own. People like to classify things and then make statements that are applicable to all members of a classification. We know, for instance, that all mammals have hair, so we define a classification called "mammal" all of whose "children" have hair. We store the information about hair with the definition of the mammal class, not with the definition of every single mammal.

Frames with inheritance allow expressing data in the same fashion. One might define a frame called "mammal" (which in turn might be a child of the "animal" frame) where one of the slots is called "hair" and the data stored in that slot is "yes." Any frame which inherits from the "mammal" frame will automatically appear to have its own slot called "hair" with the data "yes." The elephant frame might also define additional slots like "trunk."

One of the most important results of expressing data with inheritance frames is that rules can be written about whole groups of things at once. It might have been better to express the fact about hair as a rule that said

IF the thing is a mammal,

THEN the thing has hair.

Either forward- or backward-chaining would be able to apply this rule to any child of the "mammal" frame and immediately conclude that the mammal in question has hair.

#### 3.2.2 Object-Oriented Programming

Another programming technique used heavily in Cameo is object-oriented programming. This type of programming involves defining objects, which are independent packages of data and code. The major difference between object-oriented programming and conventional programming is that in object-oriented programming, each object type may define its own set of operations that it can perform. The real advantage occurs when many different types of objects define operations that are called by the same name.

Again, an example will illustrate. In most programming languages, a system call is provided that can print a few types of data, such as numbers and strings. One cannot usually print the contents of a graphics screen by using the same system call. In an object-oriented programming system, each data type would define its own "print" method. If the message "print" is sent to that object, it would run its "print" method, as defined for that object.

Now imagine that all objects in the system that might ever be printed have all had "print" methods defined. Whenever the programmer would like an object printed, he simply sends it the "print" message. Two very important advantages result from using object-oriented programming:

- A high degree of consistency.

- Since each object has its own implementation of its methods, a high degree of modularity is preserved. One object's method might be altered but its effect is strictly local.

32

The major disadvantage of object-oriented programming is a decrease in potential performance as measured by speed of execution of the finished system. Unless the system has been intelligently compiled, locating the actual code for each method requires two lookups instead of one: first to find the object's type, then to find the code in the object that executes the method.

Most object-oriented programming systems also implement a form of inheritance, like frames. The idea is almost identical, in that an object defined as a child of another one inherits all its data (local variables) and also its methods (code). The child object may also add data and methods of its own, or may override those that it inherited. For instance, an object called "number" might be defined that defines local variables such as "value," and a method for adding two numbers. Most children of the "number" object, like integers and reals, will probably not change anything inherited from the "number" object, but the object "complex" will add local variables like "real-part" and "imaginary part," and will override the method for addition.

# Characteristics of an Ideal CAD System

## 4.1 Part of an Integrated System

An ideal solution to the problems faced by IC process designers is an easily used, easily accessible CAD system that is part of a comprehensive, integrated design and manufacturing system. It must be equally useful for beginning fabricators as well as experts, must be easy to modify incrementally, and must interface with arbitrary other resources. The ideal CAD system provides a complete design environment.

The key to a fully integrated design and manufacturing system is the organization of data [Beeb83]. The different applications or services all work from a central data base, converting the data in it to forms which they can use. Communication between applications is largely through the data base. An overview of data base requirements for engineering design is contained in [East81].

The "central data base" may be implemented exactly as such, on a large mainframe computer with high-speed networks linking it to the computers running applications, or the entire system may be implemented on a large, high-performance computer. An alternative, currently being considered for UC Berkeley's integrated CAM system, is to distribute the data base among many smaller computers running the applications, linked by a high-speed local area network, and provide each application with data interface routines that convert requested data from one application's format to the requesting application's format. Another computer on the network would perform conventional data base functions in addition. Figure 4.1 illustrates this approach to a CAD/CAM system.

A distinct advantage of this approach is its inherent modularity. Each individual application contains its own data base in whatever form is optimal for it; all that is required for integration with the rest of the system is the ability to convert its data from its own format to the format required by the requesting application. The potential drawbacks are those afflicting all distributed data-base systems, such as problems with concurrent access of the data base, stale data, duplicated data, etc. The planned implementation uses concepts from object-oriented operating systems. It is hoped that many of these drawbacks can be minimized or eliminated, since in a pure object-oriented operating system, data can only be received by requesting it from another object in the system; all objects have complete control over their own data.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>This is a new research area and no published information is available. Faculty members in charge are Professors D.A. Hodges and L. Rowe.

An example of a large, successful CAD and CAM system is one in place at the Boeing Commercial Airplane Company and is described in [Beeb83]. The title of the paper describing this system, "The Heart of Integration: A Sound Data Base," leaves no doubt about the most important component of such a system.

One application in this ideal integrated system would be the design function—the system described in this dissertation. Another would be a verification function using a modeler or simulator. Others might include a critique function analogous to the critiquing performed by RUBICC [Lob84,Spic85] on digital circuits, an execution function that controls fabrication equipment, a statistical analysis function using a program such as FABRICS [Nass83], a scheduling function to help the user schedule critical equipment use, and inventory and other bookkeeping functions.

The user's interaction with the design application of the system must be intuitively straightforward and not impede the user's natural design process. It should be modeled after the structure that an expert designer assigns to the design problem, supporting the same abstractions, decompositions, and fundamental design activities the expert designer performs. Hopefully good hardware and software performance allows the user interaction to be modeled after what is best for the user's efficiency, not the machine's.

An ideal CAD system allows the user to explore potential solutions to his design problem comfortably. The following principle was referred to when making decisions that affect the user interface of the system:

Figure 4.1: Data base design for ideal CAD/CAM system based on a distributed approach. Communication is between applications by converting data formats.

No matter what sort of data structuring is used internally by the system, it must present the data to the user in a manner intuitively understood by the user and provide operations that manipulate this presentation of the data consistent with the expectation of the user.

Much recent research has been directed at producing more concrete guidelines for user interfaces for interactive computer systems. An excellent

overview of this subject, with many useful references, is contained in [Shne80]. A recent paper that should prove to be of great use in identifying the theoretical underpinnings of user interfaces for interactive technical applications is [Fole84]. Although this paper deals specifically with identifying fundamental properties of interactive graphics interfaces, the methods used in the research described by the authors are applicable to many other interactive computer applications.

This aspect of the ideal CAD system assumes very low cost of computing resources and high information bandwidth to and from the system's display. While this is a valid assumption for this research, it may not be so universally. Appropriate tradeoffs must be recognized in the design of the user interface. For instance, users for whom computing resources are very expensive will probably prefer to forego this principle in exchange for investing considerably more of their own effort in using the system.

## 4.2 Specific Characteristics for IC CAD

Two kinds of wishes about the capabilities of the system were expressed by people consulted during this research. One I will call the "professor's view," which was that beginning students tended to spend too much time doing detailed investigation of IC process designs that were not always close to a good solution, and not enough time on exploring general directions of process designs. This view held that a CAD system that would help students make the beginning planning decisions of process design would be highly desirable.

The other view, the "student's view," held that the most valuable contribution of an IC process CAD system would be to help the IC fabricator while he was in the midst of a fabrication process (at UC Berkeley, students perform most of the steps of the IC fabrication process themselves). The students envisioned a system that would allow them to enter the steps they had already performed and ask, "What should I do next?" This question often comes up when something in their process has not worked quite the way it should have, and they would like to find out if it is possible to compensate now or in a future step.

In an industrial environment, these two conflicting requirements are equally evident but take different forms. A typical company will only have a few different IC processes available for fabricating ICs due to the enormous difficulty of fine-tuning a process for acceptable yield and performance. Because of the difficulty of designing new processes, most industrial processes are essentially perturbations or relatively slight modifications on earlier successful processes. If an advanced CAD system along the lines of the professor's view were available, new processes optimized for a certain set of requirements could be quickly investigated for feasibility. These processes could be entirely unlike previous ones.

On the other hand, there are many times when a very useful capability would be investigating the slight perturbations on an existing process. This is the kind of work most often performed by industrial process engineers. A CAD system modeled after the student's view would be most helpful here.

These are two very different requirements for a CAD system, and not many (if any) current systems address them equally well. Many systems assume the user to be an expert in the field, and provide specialized tools relieving the user of some design details. Primary examples of systems like this are most VLSI layout editors, which present the design on a graphics screen as it would look physically, and provide cell abstraction features, automatic replication of cells, data base functions, and sometimes layout rule checking. The user must still begin with an architecture and chip topology or floor plan before a VLSI layout editor can be used.

Another type of system is the expert system. An expert system is supposed to mimic a human expert's performance in a very narrow field, or domain. The design philosophy behind some expert systems tends to be opposite that of conventional CAD systems, in that the expert systems assume the user to be a novice, and are designed to make high-level or initial decisions. Often these systems first ask the user some questions and then give him its solutions. Other expert systems perform tasks that are helpful to more expert users. This type of expert system keeps track of design context and is able to perform appropriate actions when requested to do so by the user. Most expert systems are limited to using heuristic knowledge, and are not easily able to integrate conventional CAD capabilities.

Each of these system types is geared toward a certain user sophistication, but neither one alone can serve all kinds of users. An ideal CAD system would be able to provide services both at the initial, high-level planning stage and

at later stages where most of the work is algorithmically oriented. Expert users must be able to bypass the initial stages since these users will often have their own process design already developed. Novice users must be able to find the system useful for initial planning.

## 4.3 The System Must be Flexible

Building a CAD system for a fast-changing field like IC process design presents some sharp contrasts. The ideal CAD system must be useful for both novices and experts. These groups of users have very different CAD needs. Another sharp contrast is that the overall design procedure for IC processes changes slowly over time, but the specific steps of a design, like which exposure machine to use, change quickly in response to constant technology changes. The design of the system must allow for these contrasts.

The CAD system should be structured around the way that an expert approaches the design problem, but allow its individual elements to be easily changed. In other words, the system's framework can be designed assuming a certain method of use, but must allow almost arbitrary modules to be connected into the framework.

A good analogy would be a technical book. While books are all largely made in the same way, their contents (which are easily changed by the printer) define their subject. An expert and a novice can use the same book; the novice probably reads it by leafing through the table of contents and reading introductory and concluding sections, while the expert probably leafs through the index to find the specific section he needs.

# 4.4 Interface to Other Resources

The ideal CAD system interfaces to the many other elements of the integrated design and manufacturing environment. This might include entering data from measurement equipment to analyze intermediate results of the process while it is in progress. In keeping with the model of the system shown in Section 4.1 with applications clustered around a central data base, integration of this sort is accomplished through the data base interface routines of each separate application.

A researcher may be considering the next step in his process after the application of photoresist. To derive specific values for the next steps (exposure intensity and time, developing time), he will need to know the precise thickness of the photoresist coating. He may also need to know the variation of the photoresist thickness over the wafer. An ideal CAD system would be able to interface directly with the film thickness measurement instrument, and use the results of the measurement in future steps.

An ideal integrated system, once a process step is designed, can also interface directly to control the fabrication equipment for that step. The results of the fabrication step are recorded and noted, and can be saved, to be used to help design future processes. This particular goal is the most far reaching, for two reasons:

• Few manufacturers of IC fabrication equipment provide consistent computer interfaces to their equipment.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>A communications standard, SECS II, has been developed specifically for IC fabrication

Attainment of this goal assumes that an intelligent system capable of a limited form of learning can be built and its performance relied upon, which has not yet been shown.

A more limited but still useful goal is to provide instructions for the operator of the fabrication equipment. The operator would actually operate the equipment and note the results.

## 4.5 Chapter Summary

An ideal CAD system, which at this point in the development of CAD technology is probably not possible to build, is a part of an integrated design and manufacturing system. The heart of the integrated system is a universally accessible data base, either physically centralized or distributed among the applications. Each application (the CAD function is but one) ideally interfaces only with this data base. Other applications would include a verification or simulation application, a critiquing application, a control or process execution application, a scheduling application, and inventory and other bookkeeping applications.

equipment. At present, however, few IC equipment manufacturers are incorporating the SECS II standard into their equipment. Another equipment interface standard has evolved from automobile manufacturing. The MAP equipment interface jointly developed by General Motors and many of its computing and manufacturing equipment suppliers. This appears to be becoming a de facto standard among manufacturers of certain types of equipment due to GM's purchasing power. It remains to be seen whether this standard can be carried over into the IC fabrication equipment arena. See [Leop84, Gene84] for further information.

Two apparently conflicting desires for an ideal IC process CAD system are often expressed. The first, the experts' view, implies that the system be able to make initial decisions about the direction of the resulting design. The other, the novices' view, asks that the system be able to understand a fairly complete process design and advise the user on the current step of the process. The ideal CAD system can address both these requirements equally well.

# The Design Process for IC Photolithography

This chapter begins with a short description of the integrated circuit (IC) fabrication process and how IC photolithography fits into it. Then a typical design process for the photolithography steps is described for a particular set of goals, and more details are added to the example design problem introduced in Section 1.3 on Page 5.

#### 5.1 The IC Process

The IC fabrication process consists of from roughly 8 to 16 major separate sequential fabrication steps. Each step consists of transferring an image to the wafer, and performing an actual processing step on the wafer that affects the regions of the wafer that were defined by the image-transfer operation.

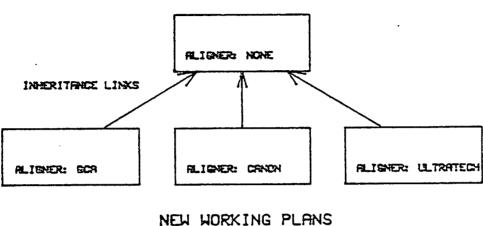

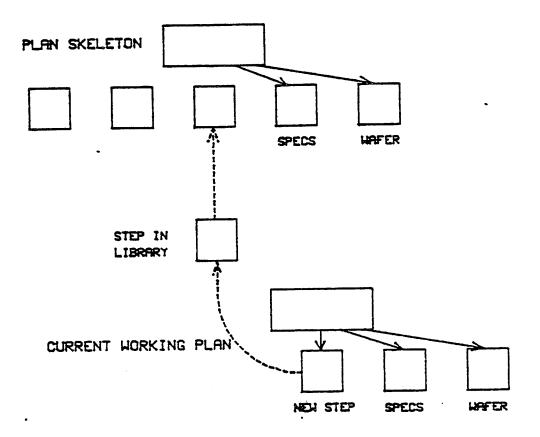

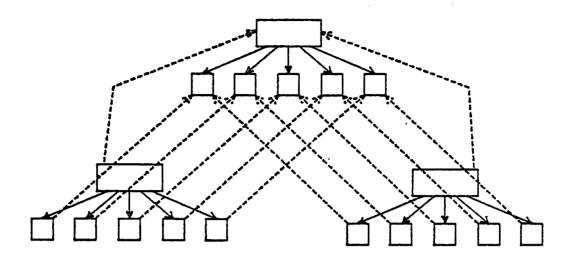

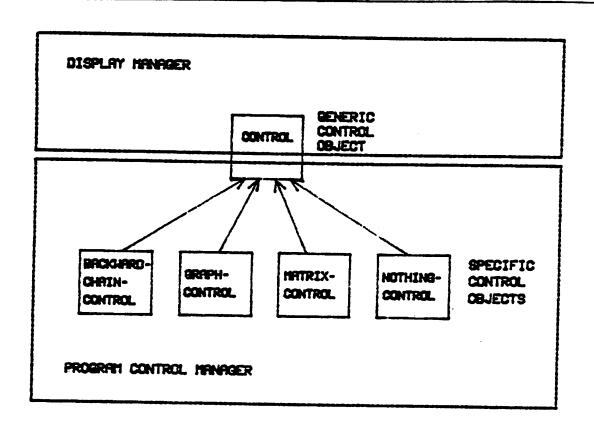

The accurate transfer of this image is crucial to the final function of the IC being fabricated.