# Copyright © 1986, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

TOPOLOGICAL OPTIMIZATION OF MULTIPLE LEVEL ARRAY LOGIC

by

Srinivas Devadas

Memorandum No. UCB/ERL M86/95

12 December 1986

#### TOPOLOGICAL OPTIMIZATION OF MULTIPLE LEVEL ARRAY LOGIC

by

Srinivas Devadas

Memorandum No. UCB/ERL M86/95

12 December 1986

ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## . TOPOLOGICAL OPTIMIZATION OF MULTIPLE LEVEL ARRAY LOGIC

bу

Srinivas Devadas

Memorandum No. UCB/ERL M86/95

12 December 1986

**ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## **ACKNOWLEDGEMENTS**

I am indebted to my research advisor Professor Richard Newton for his encouragement and support throughout the course of this work. I am also grateful to Professors Alberto Sangiovanni-Vincentelli and Carlo H. Sequin for the interest they have shown in my research project.

This work is supported in part by the Digital Equipment Corporation, the Semiconductor Research Corporation, and the Defense Advanced Research Projects Agency under contract N00039-86-R-0365. Their support is gratefully acknowledged.

All the members of the "CAD group" here at Berkeley have helped me in many ways over the past two years — I wish to especially thank Tony Ma, Karti Mayaram. Jeff Burns, Fabio Romeo, Albert Wang, George Jacob and Dr. Ruey-sing Wei.

Last but not the least. I thank Almighty God for unflagging moral support during the ups and downs in my life at UCB.

#### **ABSTRACT**

A generalized topological optimization tool for array based layout styles is presented. This tool can be used for automated layout synthesis of logic networks in a variety of technologies and design styles, including static CMOS, static NMOS and dynamic CMOS Domino structures. Results obtained compare favorably with technology and design-style-specific synthesis systems.

The topological optimization tool is a generalized array optimizer, which can be used for the multiple constrained folding of Programmable Logic Array, Gate Matrix. Weinberger Array, Multi-Level Matrix, and Storage/Logic Array structures. The optimizer uses simulated-annealing-based algorithms and performs as good as or better than existing specialized PLA folding programs and Gate Matrix folders. The different layout style alternatives allow area-efficient synthesis of logic circuits in various technologies. Layout for sequential logic in the form of Storage/Logic Arrays has been automated for the first time.

A multi-processor implementation of the simulated-annealing-based algorithms for generalized array optimization has been developed on the Sequent Balance 8000 multi-processor. Dynamic windowing and dynamic partitioning techiques have resulted in an efficient parallel implementation of simulated annealing.

## TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                         | 1    |

|-------------------------------------------------|------|

| 1.1 Automatic Layout of Logic Circuits          | 1    |

| 1.2 Previous Work in Automatic Layout           | 2    |

| 1.3 Organization of this report                 | 3    |

| 1.4 Results Achieved                            | 4    |

| CHAPTER 2: ARRAY BASED LAYOUT STRUCTURES        | 6    |

| 2.1 Programmable Logic Array                    | 6    |

| 2.2 Weinberger Array                            | 8    |

| 2.3 Gate Matrix                                 | 9    |

| 2.4 Multi-Level Matrix                          | 11   |

| 2.5 Storage/Logic Array                         | 14   |

| 2.6 Generalized Array Optimization              | 15   |

| 2.6.1 Defining the Problem                      | 16   |

| 2.6.2 GENIE: A Generalized Array Optimizer      | 17   |

| CHAPTER 3: SIMULATED ANNEALING                  | 18   |

| 3.1 Introduction to Simulated Annealing         | 18   |

| 3.2 Theoretical Results                         | 20   |

| 3.3 Previous Applications                       | 21   |

| 3.3.1 Logic Partitioning                        | 21   |

| 3.3.2 Global Wiring                             | 22   |

| 3.3.3 Cell Placement                            | . 23 |

| 3.3.4 Channel Routing                           | . 24 |

| 3.4 Conclusions                                 |      |

| CTARGER 4. CENTER A GENERALIZED ARRAY OPTIMIZER | . 27 |

| 4.1 A Generalized Array Compaction Algorithm        | 28           |

|-----------------------------------------------------|--------------|

| 4.1.1 The problem of generalized array optimization | 28           |

| 4.1.2 Array Optimization using simulated annealing  | 29           |

| 4.1.3 Annealing the Matrix                          | 35           |

| 4.1.4 Generating New States                         | 36           |

| 4.1.5 The Cost Function                             | 39           |

| 4.1.6 The Stopping and Inner Loop Criteria          | 40           |

| 4.1.7 Temperature Profile                           | 41           |

| 4.1.8 Routing the Horizontal Nets                   | 41           |

| 4.1.9 Routing the Vertical Nets - The Final Stage   | 42           |

| 4.1.10 A Brief Description of Approach 2            | 44           |

| 4.1.11 Splitting Long Nets                          |              |

| 4.1.12 Parameter Extraction                         | 46           |

| 4.1.13 Temperature versus Cost Graphs               | 47           |

| 4.2 Examples, Comparisons and Implementation        | <i>5</i> 0   |

| 4.2.1 Implementation Details                        | <i>5</i> 3   |

| 4.2.2 Comparisons with Existing Tools               | 56           |

| 4.3 Storage/Logic Array Compaction                  | 62           |

| 4.3.1 Modifications for SLA Compaction              | 63           |

| 4.3.2 Constraints During the Annealing              | . 65         |

| 4.3.3 Aspect Ratio Sizing                           | . 66         |

| 4.3.4 Examples                                      | . 66         |

| 4.4 Conclusion                                      | . <b>7</b> 0 |

| CHAPTER 5: WEINBERGER ARRAY AND GATE MATRIX LAYOUT  | . 71         |

| 5.1 Weinberger Array Layout Optimization            | . 73         |

| 5.1.1 Ordering the Gates                            | . 75         |

| 5.1.2 Generating New States                         | . 76         |

| 5.1.3 The Cost Function 7                                  | 16 |

|------------------------------------------------------------|----|

| 5.1.4 Loop Criteria and Temperature Profile                |    |

| 5.1.5 Ordering the rows                                    |    |

| 5.1.6 Aspect Ratio Sizing                                  |    |

| 5.1.7 Merging the Stages                                   |    |

| 5.1.8 Dealing with large fanin gates                       |    |

| 5.2 Gate Matrix Layout Optimization                        |    |

| 5.2.1 Ordering the Signals                                 | 83 |

| 5.2.2 Expanding the Rows                                   |    |

| 5.2.3 Dealing with Dense Signals                           |    |

| 5.2.4 The P and the N parts of the Gate Matrix             |    |

| 5.3 Examples and Results                                   |    |

| 5.3.1 Time and Temperature Profiles                        |    |

| 5.4 Conclusions                                            |    |

| CHAPTER 6: MULTIPROCESSOR IMPLEMENTATION OF SA ALGORITHMS. |    |

| 6.1 Simulated Annealing on Multiprocessors                 | 94 |

| 6.2 Dynamic Windowing                                      |    |

| 6.3 Implementation                                         | 96 |

| 6.4 Results1                                               |    |

| 6.5 Conclusions1                                           |    |

| CHAPTER 7: CONCLUSIONS1                                    |    |

| REFERENCES                                                 |    |

#### CHAPTER 1

#### Introduction

Much work has gone into automating the integrated circuit design process over the past few years (e.g. [park79] [newt81] [bray85]). Logic synthesis tools and tools for automatic layout of logic networks are very desirable from a viewpoint of a fast design turnaround time. However, these automatically generated designs are invariably less efficient area-wise or speed-wise than manual designs, or do not meet critical performance requirements. The large number of possible design styles, static or dynamic, single MOS or CMOS, complicate the automation process. In this report, a framework for topological optimization during automatic logic network layout in the form of array-based structures is presented. The system produces designs under various constraints and a variety of design styles resulting designs as good are as good as, or better than, corresponding manual designs.

## 1.1. Automatic Layout of Logic Circuits

Given a gate level description, the goal of automatic layout is to synthesize a corresponding layout implementing the logic in the input description while taking into account constraints on the area and speed of the finished module. Optimization steps are crucial in a automatic layout system to ensure that the resulting layouts are area and speed efficient.

The automatic layout step involves many decisions. Depending on the technology, a layout style has to be chosen. Two broad choices exist a standard cell place and route method[souk81], or adopting a regular array-based layout

style[wein67][lope81] [pati75][hofm85a][wood79]. Array-based layout styles are relatively easy to automate but topological compaction steps are essential. The type of electrical design-style chosen is also technology dependent. For example, a Weinberger array[wein67] is suitable for single MOS technologies, whereas a Gate Matrix[lope81] is suitable for CMOS. Multi-level matrices are best for dynamic CMOS or Domino[hofm85a].

Two phases exist in the automatic layout of regular arrays: symbolic topological compaction and actual layout generation. The logic network is represented as a symbolic array (a PLA can be represented as a matrix of 0's and 1's and don't-connects) and then area-optimized by the topological reordering of the gates and signals. The topological compaction step is typically the bottleneck as regards area optimization. It is important that the tools for area compaction be very efficient if the resulting design is to compare favorably with manually generated designs.

Array based layout structures are compacted using a technique known as folding[wood79.hach80]. Layout generation is performed using tile packing methods[mayo83]. The compacted symbolic layout is converted into tiles using a context-based tiler and the tiles are then stitched together. The tiler makes local decisions only, since the global compaction step has been taken care of.

## 1.2. Previous Work in Automatic Layout of Array Structures

Structured forms of layout for combinational logic include Weinberger Arrays[wein67]. Programmable Logic Arrays[flei75] (PLA) and Gate Matrices[lope81]. Sequential logic can be realized as a Storage/Logic Array[pati79] (SLA). Methods of automatic layout in the form of arrays can be termed as tiled methods because connection between cells is by abutment. like tiling a floor.

Topological compaction of array based structures is possible by means of a flavors, simple technique known as folding. Folding comes two in folding[hofm80.hach80] and multiple folding. In simple folding at most two signals can occupy the same row. In multiple folding, there is no limit to the number of signals which can occupy the same row. Constrained folding allows constraints on where the signals are to appear outside the array. Multiple constrained folding of PLAs was first proposed by De Micheli[demi83] and implemented in program PLEASURE. PLEASURE row and column folds PLAs under various constraints. Folding is also possible in Gate Matrices and Weinberger arrays. This is one dimensional folding as opposed to two dimensional PLA folding. Algorithms for optimal been have dimensional interval an one packing on investigated[asan82.ohts79.wing82].

Most of proposed algorithms are based on graph-theoretic interpretations and are easily trapped in local minima. These algorithms also break in highly constrained situations since they have been designed primarily for the unconstrained cases. Most algorithms for Gate Matrix layout have no provision for constraints on the signals and differing sizes of transistors in the matrix. SLAs have resisted automated implementation until now because of their very complicated structure and widely varying cell sizes.

## 1.3. Organization of this report

The six following chapters are organized as follows. Various regular array-based layout styles are described in Chapter 2 and previous work in topological compaction of the different structures is reviewed. The combinatorial optimization techniques known as Simulated Annealing is introduced in Chapter 3, and theoretical work done in the field of probabilistic hill climbing (PHC) algorithms as well

as previous applications of simulated annealing the physical design of integrated circuits are reviewed.

A generalized array optimization program GENIE, based on simulated annealing, for two dimensional multiple constrained folding of PLAs. Multi-Level Matrices, and SLAs is described in Chapter 4. Comparisons with specialized array compaction programs are drawn. Modified algorithms for one dimensional multiple constrained folding also based on simulated annealing are presented in Chapter 5. These algorithms can be used for Gate Matrix and Weinberger array compaction. The multi-processor implementation of these simulated annealing based algorithms using dynamic windowing and partitioning schemes to preserve the convergence properties of simulated annealing to the global minimum are described in Chapter 6. Conclusions are drawn and directions for future work indicated in Chapter 7.

#### 1.4. Results achieved

An automatic layout system consisting of a topological optimization tool. GENIE. a context based tiler ELECTRA, and a layout generator MKARRAY[krin86] has been developed. This system produces efficient layouts and encompasses a wide range of array based layout styles.

GENIE is a generalized array optimizer which can be used for the multiple folding of PLAS. as well as for compacting Gate Matrix layouts. SLA. and Weinberger arrays. The cells in the array can be of non-uniform sizes and any sort of constraint can be placed on the input and output terminals. GENIE uses the combinatorial optimization technique called Simulated Annealing. Results obtained are uniformly better than existing specialized array optimizers and folding programs, particularly when the input locations are constrained. GENIE is the first program

for automated SLA compaction.

GENIE has been compared with a number of existing tools for topological folding and compaction of array logic. TWIST, a part of the MAMBO pipeline[hofm85a] is a program for the folding of multi-level connectivity matrices. Results up to 50% better than TWIST have been obtained. PLEASURE[demi83] is a PLA folding program also developed at Berkeley. GENIE typically produces better results than PLEASURE more so in constrained cases which are more likely in real chip designs. Up to 30% better results have been obtained in constrained examples. Detailed comparisons with specialized array compacters can be found in Chapters 4 & 5.

A multi-processor implementation of the simulated-annealing-based algorithms in the array optimizer GENIE has been developed on the Sequent Balance 8000 multi-processor. Dynamic windowing and dynamic partitioning schemes have been used to preserve the global convergence properties of simulated-annealing-based algorithms to the global minimum and efficiences of up to 75% have been achieved over 8 processors. This implementation is described in Chapter 6.

#### CHAPTER 2

## Array Based Layout Structures

Logic circuits in various technologies and design styles can be implemented as regular arrays. Array-based layout structures have been extensively used for large scale integration of Mos logic [wein67,flei75,pati79,lope81]. These structures are used to retain a reasonably fast design turnaround time and to permit the design steps to be automated. However, standardized layouts obtained by synthesizing the logic circuits as arrays are area efficient compared to manual random logic designs only if topological compaction algorithms are applied. The algorithms do not change the logic function of the circuit but instead try to find an optimal ordering of gates, signals or transistors, as the case may be, so as to minimize the eventual area. Compaction is achieved by a process called *folding* where more than one signal or more than one gate can occupy a single row or column of the array.

#### 2.1. Programmable Logic Array

Programmable logic arrays (PLA) are two dimensional arrays implementing a two-level combinational logic function[flei75]. The PLA consists of two planes the AND plane and the OR plane. The AND plane maps the primary inputs into minterms (product terms) required and the OR plane maps the minterms into the outputs. In practice, both these planes are implemented as NOR structures in dynamic CMOS or NMOS technologies. An array can be programmed for any arbitrary two level combinational logic function by the presence or absence of transistors in various AND or OR locations. The functionality of a PLA can be represented as a 0-1 matrix. PLA folding algorithms work on this symbolic representation using the

information as to the presence or absence of transistors at each array node. Various architectures exist for implementing PLAs[demi83].

The area of a PLA is optimized by means of row and column folding[hach82]. The technique reported in [hach82] is referred to as simple folding. A generalization of simple folding is multiple folding. All previous techniques for PLA folding rely on a graph theoretic interpretation of the problem. Multiple/simple constrained/unconstrained folding is possible in PLEASURE[demi83]. In PLEASURE a column intersection graph (CIG) is defined whose nodes are in one-to-one correspondence with the columns of the logic array. Nodes have edges between them if the corresponding columns have a transistor in the same row. Folded columns are represented by a directed edge between the two corresponding nodes. The problem is now to find disjoint clusters of nodes in the graph, fold columns without creating alternating cycles (alternating cycles render the PLA unimplementable). Constraints on the positions of rows and columns, as well as ordering constraints on the rows and columns can be handled by this technique. Unfortunately, like most heuristic techniques, this method is easily trapped by local minima. Good heuristics however ameliorate the problem and PLEASURE produces area efficient folded PLAs with reasonable cpu time expenditure.

Simulated annealing has been applied to the PLA folding problem[moor85,wong86]. In [moor85] heuristics similar to the ones used in PLEAS-URE are applied initially, but when folding pairs become more difficult to find hill climbing moves are generated in an effort to escape local minima. [Wong86] gives an algorithm based on simulated annealing to solve a column folding problem — their approach cannot be used for general two-dimensional row and column PLA folding.

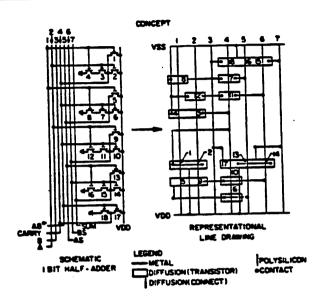

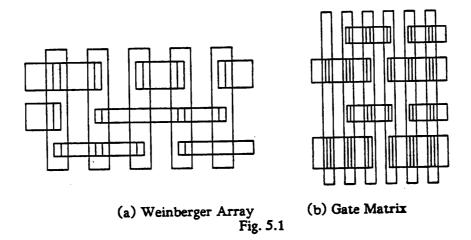

#### 2.2. Weinberger Array

Weinberger arrays are one-dimensional structures for standardized layout of multi-stage combinational logic networks[wein67]. In a Weinberger array a gate occupies a column, and signals occupy rows. The gates are elongated structures and the output of the gate can be tapped at any location. Thus, it is not necessary to have signals cross each other (similar to the PLA). Figure 2.1 shows a Weinberger array from [wein67]. The array usually has diffusion/metal columns and poly/metal rows. It is possible to order the gates in a Weinberger array so as to have more than one signal occupy a single row. Like in the PLA rows can be folded. Algorithms for optimal packing on a one dimensional interval have been investigated[asan82,ohts79]. Asano[asan82] describes an exact algorithm for ordering the gates of a one dimensional array to minimize row cardinality. The algorithm searches for an optimal net ordering as opposed to a gate ordering. The gate sequence corresponding to the net ordering obtained is easily constructed. Optimality-preserving pruning methods, namely branch and bound are used. Ohtsuki et. al[ohts79] give a graph-theoretic interpretation to the one dimensional packing problem. Unlike a PLA, the transistors in a Weinberger array may be of varying sizes. The algorithms mentioned above assume all the transistors are of equal sizes and minimize for row cardinality instead of row height. The optimization does not include minimizing total net length. Net length may be important when delay through the circuit must be considered.

Weinberger arrays are area efficient for single MOS (e.g. NMOS, PMOS) technologies. In a complementary MOS static technology the signals have to drive two transistors instead of one. Using a Weinberger array this can be accomplished by duplicating all the signals for the p-channel and n-channel devices but this reduces area efficiency. A layout style more suitable for a static CMOS technology

is Gate Matrix.

#### 2.3. Gate Matrix

In a Gate Matrix[lope81] the p-channel transistors and n-channel transistors occupy different halves of the matrix. The transistors are transposed in such a fashion so all those having a common input are placed on a common polysilicon line. This common line serves a dual purpose, i.e. it is the gate of many transistors which lie on the line and it serves as the common contact among the transistors

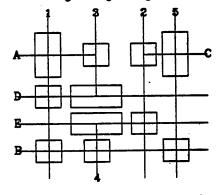

Fig. 2.1 Weinberger Array

which have a common input. The polysilicon lines which are all parallel become the columns of the gate matrix. The rows are formed by grouping together those transistor diffusions which associate with each other in a series or parallel fashion. The Gate Matrix layout style is the complement of the Weinberger array layout style in a sense — logic gates occupy rows and signals occupy columns. Thus each signal drives both the n and p transistors of the gates. Figure 2.2 shows a Gate Matrix.

The one-dimensional placement algorithms for a Weinberger array apply equally well to a gate matrix. Here the problem is to find an ordering of signals so the gates can be maximally folded. However, gate matrices have evolved to support complex gates like AND-OR-INVERT and pass transistors and the relatively straightforward techniques described above have to be modified. Wing et. al [wing82,wing85] give a graph-theoretic algorithm for compacting gate matrix layouts for complex gates and pass transistors. The technique involves formulating two assignment functions f and h such that the layout L(fh) requires the minimum number of rows as a gate matrix. The function f maps the distinct gates of the transistors to the columns of the gate matrix and the function h maps the nets of the circuit to the rows such that all the vertical diffusion runs which connect nets on different rows are realizable. A two stage approach is used which first obtains layout without regard to the vertical constraints and then permutes the rows to satisfy the constraints.

The algorithms proposed thus far for gate matrix layout have no provision for constraints on the signal columns. For example, it may be desirable to have an input signal near the right end of the matrix as opposed to the left end or middle. Also, like the Weinberger array case, transistors are all assumed to be of the same size; row cardinality alone is minimized disregarding total row height.

Fig. 2.2 Gate Matrix

#### 2.4. Multi-Level Matrix

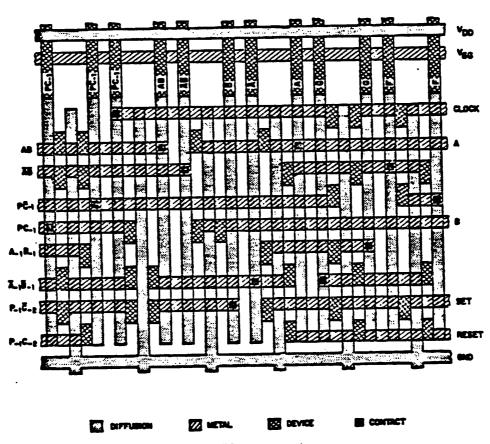

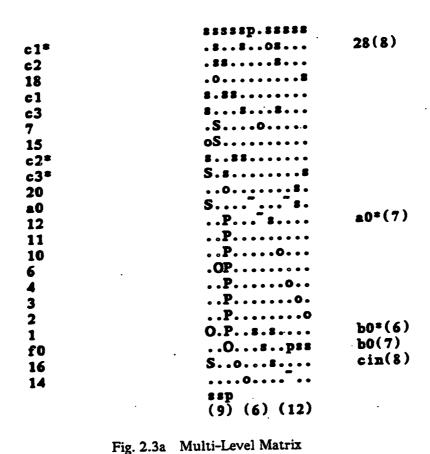

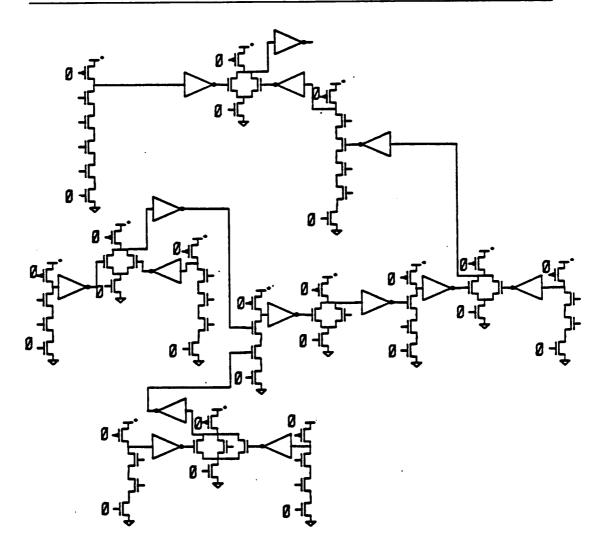

A new layout style suitable for NMOS and Domino logic circuits was proposed by Hofmann[hofm85a]. A Multi-Level Matrix (MLM) is a two dimensional structure like a PLA but supports multi-stage logic circuits unlike a PLA. It is a hybrid structure having characteristics of both gate matrix and Weinberger array structures and allows mixing of static and dynamic functions. In a MLM more than one gate can occupy a column ( like a gate matrix), and more than one signal can occupy a row (like a Weinberger array). Figure 2.3a shows a symbolic representation of a folded MLM. The characters s and S denote a series transistor in the first and second gates on a column respectively, similarly characters p and P denote parallel transistors in the first and second gates on a column, and the characters o and O denote output connections. Figure 2.3b shows the actual layout of the MLM in a technology with two levels of metal interconnect.

Like a PLA a MLM can be both row and column folded. The intermediate inputs can be multiply folded without any area penalty. Hofmann et.al[hofm85b] proposed an algorithm similar to [demi83] for MLM folding. TWIST is a program for multiple constrained folding of MLMs. Rows are multiply folded in TWIST but the layout style constrains the columns to be simply folded. The load devices for an NMOS circuit would be on top or bottom of the matrix as would be the buffers and clocked load of a Domino circuit. The ordering of signals is significant in TWIST as delay optimization is performed along with folding. Also, since signals are ordered relative to the output buffer when columns are folded, the ordering of

signals to the flipped gate need to be inverted. The necessity to invert or "flip" constraints when a column is folded differentiates the folding of these arrays from other structured arrays like PLAs or gate matrices.

Fig. 2.3b Layout of Multi-Level Matrix in Fig. 2.3a

#### 2.5. Storage/Logic Array

Storage/Logic Arrays were first described in 1975[pati75]. They are a form of structured logic derived from PLA where the AND and OR planes of the PLA are folded into a single plane. The SLA supports multi-stage combinational logic with embedded memory elements. Memory elements are placed on the grid itself and can be randomly distributed within the SLA logic. Columns may also contain boolean combinations of state values. Using columns to generate these boolean expressions permits multiple levels of logic. All columns and rows can be broken at arbitrary locations.

SLAs are ideally technology independent. That is, one SLA program should be portable, without change, between different process technologies. Unfortunately, this is not the case and it becomes necessary to select a particular process and implementation based on the individual circuit needs[smit82]. For example  $I^2L$  is extremely limited in allowing large number of actions being controlled by a row or column because of poor fanout. NMOS can handle heavy loads, but at the price of low speed. CMOS overcomes these objections but needs a more complex process and larger inverters. CMOS SLAs appear the most popular.

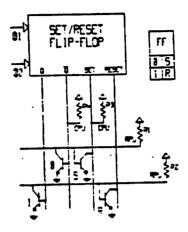

An SLA program is a two-dimensional array of symbols that specifies the placement of cells for a given circuit. The elements of the SLA program are taken from an SLA cell set which is predefined and dependent on the given technology which has been chosen. The SLA cell set will include memory elements, inverters, combinational elements for the folded AND-OR plane, row and column breaks, and row and column connection cells. The memory elements might be as sophisticated as a set/reset read/write-enabled master/slave flip-flop or as simple as a set/reset latch. Figure 2.4 shows a SLA program and the physical realization of an oscillator[smit82]. A more complicated SLA realization of and adder/subtractor is

Fig. 2.4 SLA program and physical realization of an oscillator

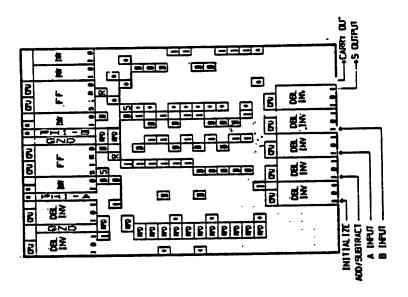

#### shown in Figure 2.5.

Topologically compacting an SLA is much more difficult than folding a PLA. The cells in the SLA are of widely differing sizes; one may be ten times the area of the other. Defining large cells to be multiple cells causes adjacency constraints on the constituent cells. Ordering constraints on cells exist due to the presence of inverting buffers ( a buffer cannot be placed after a transistor it is feeding into). PLA optimization techniques fail to produce good results for SLAs. No efficient program for automated SLA compaction existed before GENIE.

## 2.6. Generalized Array Optimization

A generalized array optimizer should perform multiple folding of PLA. Weinberger Array. Gate Matrix, MLM, and SLA structures under various constraints. The array optimizer should minimize for total row and column height and not for row or column cardinality.

Fig. 2.5 The USCM adder/subtractor

#### 2.6.1. Defining the Problem

The initial unfolded array can be represented as a matrix, M; non-zero elements denote the existence of a cell in the corresponding array. Each location in the matrix is a record consisting of four elements: the length of the cell in the actual array location, the width of the cell, the initial column number of the cell (in the unfolded matrix) and the initial row number of the cell. (entry.length, entry.width, entry.hor\_net, entry.ver\_net)

Two matrices can be derived from this matrix. Row and Col, the row and column constraint matrices. Physically, they represent the constraint that nets/cells may not overlap. The constraint matrices have entries corresponding to the extent of the horizontal or vertical nets i.e. if a horizontal net extends from (1.1) to (3.1) the entries  $Row_{11}$ ,  $Row_{21}$  and  $Row_{31}$  would be incremented by 1. No

element of the constraint matrix can be greater than unity.

$$Row_{ij} \leq 1 \text{ for all } i, j$$

(1a)

$$Col_{ij} \leq 1 \text{ for all } i, j$$

(1b)

The area of a matrix is measured as the sum of row heights times the sum of column widths. The row height is the maximum of the heights of the cells in the row and the column width is the maximum of the widths in the column. If no cells exist on a row the height is obviously zero.

$$Height = \sum_{i=1}^{N_r} max (M_{ij} length)$$

$$Width = \sum_{j=1}^{N_c} max (M_{ij} .width)$$

$$A = Height * Width$$

The problem is thus to find an arrangement of cells which satisfies the constraint matrix condition (1), and minimizes area A.

## 2.6.2. GENIE: A Generalized Array Optimizer

GENIE is a generalized array optimization package using simulated-annealing-based algorithms which performs the above tasks. GENIE needs a symbolic representation of the array in the form of a connectivity matrix and information about the sizes of the cells, to produce a compact simply/multiply folded layout. Adjacency constraints among rows(columns), ordering constraints on rows(columns), edge constraints on signals and bounded row(column) constraints are provided for by GENIE.

GENIE is the first program to produce efficient automated SLA implementations. For the PLA and MLM case GENIE produces better results than the best specialized folders available for comparison.

#### CHAPTER 3

## Simulated Annealing

The subject of combinatorial optimization aims at developing techniques to find the minimum or maximum values of a function of very many independent variables. A function, usually called the cost function or objective function, represents a quantitative measure of the quality of the solution. The number of variables may be of the order of tens of thousands and the number of possible solutions may be equally large.

Most of the combinatorial optimization problems dealing with the physical design of integrated circuits are NP-complete (nondeterministic, polynomial-time complete) which means that no method for an exact solution with a computing effort bounded by a power of N has been found for any of these problems. Optimal solutions to these problems generally require exponentially bounded or worse computing time. Heuristic methods with computational requirements proportional to small powers of N have been developed for many of these problems. These techniques are rather problem specific: there is no guarantee that a heuristic procedure for finding near-optimal solutions for one NP-complete problem will be effective for another.

#### 3.1. Introduction to Simulated Annealing

Kirkpatrick, Gelatt and Vecchi[kirk83] showed there was a deep and useful connection between the behavior of systems with many degrees of freedom in thermal equilibrium at a finite temperature and multivariate or combinatorial optimization. The analogy drawn is as follows: Atoms in a solid always try to

move toward a configuration of lowest possible energy (maximum stability). If a solid is heated to a high temperature and cooled very slowly. which is the physical annealing process, the annealed solid has better mechanical properties than the original, because the atoms are now in a lower energy (more stable) state. Heating to a high temperature increases the thermal motion of atoms in the solid allowing them to redistribute themselves into a more stable configuration. At a high temperature. the atoms are likely to move to higher energy positions, but as the temperature is lowered, the movement of atoms is restricted to locations of lower energy. The physical annealing process, for best results, should have a cooling process which is very gradual and a high starting temperature. In the combinatorial optimization problem, the energy of the configuration corresponds to the cost. function, thermal motion to randomly generated moves, and the temperature corresponds to the parameter controlling the acceptance of these moves. While at a high temperature, hill climbing moves which increase the cost function are accepted, but the probability of accepting these moves reduces as the temperature is lowered. Thus the physical annealing process is being simulated to solve the combinatorial optimization problem.

The general structure of the basic simulated annealing algorithm is shown below.

```

T = T<sub>0</sub>:

X = Starting_Configuration:

while("cost is changing") {

for("a certain number of times") {

Generate_New_State(j)

if(accept(c(j).c(X).T)) {

X = j:

}

}

T = update(T);

}

```

Whether or not a new state is accepted is determined by the function accept():

```

accept(c(j),c(i),T) {

change_in_cost = c(j) - c(i);

if (change_in_cost < 0 ) return(1);

else {

Y = exp(-change_in_cost/T);

R = random(0,1);

if ( R < Y ) return(1);

else return(0);

}

}</pre>

```

There are two loops in the simulated annealing algorithm which correspond to changing the temperature and generating a number of random states at a given temperature point. The temperature profile depends on the number of states generated in the inner loop and the function update. The acceptance function accept shown is the well known exponential acceptance function, variations exist.

#### 3.2. Theoretical Results

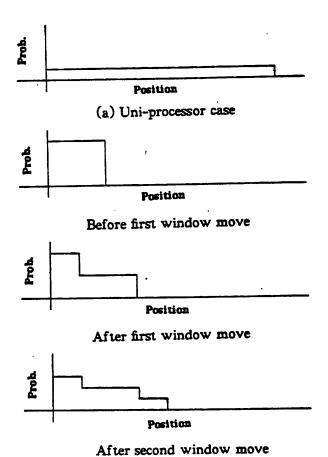

Markov chains have been proposed as a mathematical model for simulated annealing[lund84.gema84.rome84] Using these mathematical models, simulated annealing has been shown to be a special form of a general class of algorithms called probabilistic hill climbing algorithms[rome84] having the same asymptotic properties. The asymptotic properties underline the fact that under certain assumptions on the number of moves generated by the algorithm at a certain temperature, simulated annealing produces the global optimal solution with probability 1.

Romeo et al[rome85] provide results to estimate how many steps should be attempted for each value of T. These results give necessary conditions to preserve the global convergence properties of the simulated annealing algorithm. One particular result which gives the expected value of the number of iterations to leave a state is reproduced from [rome84] below.

Proposition: Let i be a state such that  $P_{ii}(T) < 1$ , where

$$P_{ii}(T) = G_{ii}(T) * f(C_{ii},T)$$

$G_{ij}(T)$  is the probability of generating state j being in state i and  $C_{ij}$  is c(j) - c(i). The expected value of the number of iterations required to leave i. N is given by

$$N_i = 1/(1 - P_{ii}(T))$$

A conservative estimate of the  $P_{ii}(T)$  is obtained by assuming that  $C_{ij}$  is constant and equal to  $C_{kl}$  where k is the worst configuration and l the best configuration found thus far.

Unfortunately, these results are asymptotic and indicate that an infinite number of moves have to be generated in order to obtain a globally optimal solution with probability 1, which is in fact worse than exhaustive search. However, these results provide information as to what kind of cooling schedules need to be used in order to obtain good solutions minimizing cpu time requirements[huan86].

#### 3.3. Previous applications

Simulated annealing has been applied to various problems relating to the physical design of integrated circuits like global wiring[vecc83]. cell placement[sech84.sech85] and channel routing[wong85]. It has also been proposed as a tool for logic partitioning[kirk83]. Techniques used in these applications are reviewed.

#### 3.3.1. Logic Partitioning

One of the simplest applications of simulated annealing is logic partitioning.

The problem is to partition a set of modules into two or more groups such that

the interconnections between the groups are minimized. Heuristic

algorithms[kern70,fidu82] have been used to solve this problem.

The annealing begins on a random set of partitions. Moves can be generated in two ways: (1) two modules in different partitions are interchanged (2) a module is displaced from one partition to another. The cost function is the total number of nets across the partitions. In general, it is desirable that the partitions should be of the same size. Moves can be allowed only if this constraint is satisfied within a tolerance limit.

#### 3.3.2. Global Wiring

Given a placement of modules, the problem is to construct a "global" or coarse scale routing for each connection from which the ultimate detailed wiring can be completed[souk81]. Package technologies and structured image chips have prearranged areas of fixed capacity for the wires. For the global routing to be successful, it must not call for wire density which exceeds this capacity.

The global routing problem is modeled by lumping all actual pin positions into a regular grid of  $N_x$  x by  $N_y$  points which are treated as sources and sinks of all connections. The wires are to be routed along the links which connect adjacent grid points. Pre-placed components are modeled by prefilling some of the links.

The problem is to choose paths for routable connections in such a way that the likelihood of "overflows" or wires which don't fit into the eventual detailed package is minimized. This means that the most uniform possible distribution of wires plus existing blockages is sought. The objective function used is that which rewards the most balanced arrangement, and is obtained by calculating the square of the numbers of wires on each link of the package, and summing the results over the links.

$$F = \sum_{\nu=1}^{n} m_{\nu}^2$$

The path between two points of a connection can be an L-shaped path (a path with one bend) or a Z-shaped path (a path with one or two bends). The moves can be L-shaped moves or Z-shaped moves. For the L-shaped moves. F. the objective function has a relatively simple form. The computational effort required to obtain a good result for Z-shaped paths is larger than that for L-shaped paths because of the larger number of states available for each connection. For the same reason, a better solution can be reached for the wiring problem by allowing Z-shaped paths. So instead of using time-consuming annealing from high temperatures with the full set of Z-shaped paths two stages of annealing are performed. First, a annealing from high temperatures is performed using L-shaped paths. Then, the resulting configuration is used as a starting point for another annealing process using Z-shaped paths, but only from low temperatures. The time required for generating good solutions is thus modest. Global wiring optimization for 3000 nets on a 11 by 11 grid required just 2 seconds on a IBM VM/370 system with a 3033 processor[vecc83].

#### 3.3.3. Cell Placement

TimberWolf[sech84.sech85] is a placement and global routing package for integrated circuits. TimberWolf is a set of programs for standard cell placement. gate array placement, macro-cell placement and standard cell global routing, which uses simulated annealing based algorithms. The standard cell placement program in TimberWolf places standard cells into rows and/or columns in addition to allowing user-specified macro blocks and pads. The results obtained by TimberWolf are on the average, better than other existing placement packages.

The TimberWolf program begins with a random initial placement of cells. A new state is generated by either exchanging two fundamental units or displacing a

unit to another location. Moves are randomly generated. New states can also be generated by orientation changes of standard cells. Interchanges and displacements are controlled by a range limiter. The range of interchange/displacement of a cell is dynamically changed during the annealing process.

The objective function in TimberWolf consists of many parts. The net length calculated as the Manhattan distance between the furthest pins of the net is one constituent. Since cells can be of different sizes, interchanges may result in cell overlap. Rather than disallow these moves, the penalty function approach is used. When two cells overlap a penalty is assessed is which is proportional to the square of the quantity of linear overlap plus an offset parameter. The objective function has an additional term which controls block lengths. The sum of the actual lengths of the cells in a particular block is compared to the actual block length. A penalty is assessed which is equal to the absolute value of the difference times a parameter value.

#### 3.3.4. Channel Routing

Wong et al[wong85] proposed a scheme for channel routing using simulated annealing. The basic technique is to find a valid set of partitions ( $V_1$ ,  $V_2$ ,  $V_w$ )  $V_i$  containing all the nets on track i, where w is the channel width, such that w is minimized i.e. the number of tracks is minimized.

Moves are generated in three ways: (1) two subnets belonging to different groups  $V_i$  and  $V_j$  can be interchanged. (2) a subnet can be moved from group  $V_i$  to group  $V_j$ . (3) a subnet can be removed from group  $V_i$  and form a new group by itself. Vertical and horizontal constraint violations can occur during the annealing process. (1) leaves the channel width unchanged. (2) may decrease channel width and (3) increases the channel width.

The objective function is as follows:

$$C(\pi) = w^2 + \lambda_p * p^2 + \lambda_u * U$$

where w is the number of groups, p is the longest path in  $G(\pi)$  and  $\lambda_p$  and  $\lambda_n$  are constants. The channel width w obviously has to be minimized. The quadratic dependence places a higher penalty on solutions with large w's and lower penalty for solutions with small w's. The reason for the second term is that p is a lower bound on the number of wiring tracks needed for all the solutions derived from  $\pi$  by further merging of subnets. U is defined as

$$U = \sum_{i=1}^{w} u_i^2 \text{ where}$$

$$u_i = 1 - 1/l \sum_{v} e^{n}_i |v|$$

l is the channel length and |v| is the length of the horizontal segment of subnet v. Here,  $u_i$  is the fraction of the track i that is unoccupied. Thus, U is a measure of the sparsity of all the tracks in the corresponding routing solution. Intuitively, all good routing solutions are densely packed, and hence have small U values.

The annealing schedule can only start from a valid partition. At each temperature, enough moves are tried until there are either N downhill moves or the number of moves exceeds 2N where  $N=\lambda_N*m^2$ . The annealing process is terminated if the number of downhill moves is less than 5% of all the accepted moves or the temperature is too low. If at any time a solution with d tracks is reached, which is clearly optimal the annealing is terminated.

This particular application of simulated annealing is interesting but has little or no practical value because very good heuristic techniques for general multi-layer channel routing have been developed[brau86] which produce optimal solutions with small cpu time expenditure.

#### 3.4. Conclusions

Simulated annealing has been applied to a variety of NP-complete problems with encouraging results. The only disadvantage with probabilistic hill climbing algorithms is cpu time expenditure. This can be partly alleviated by intelligent choices of data structures (to keep cost evaluation incremental) and annealing schedules to maximize efficiency. The main advantage of PHC algorithms as opposed to heuristic algorithms is their relative immunity to local minima traps.

In the next two chapters GENIE, a generalized array optimization package, which uses simulated annealing based algorithms for the multiple constrained folding of PLAS, Gate Matrix, Weinberger Arrays, MLMs and SLA, is described.

#### CHAPTER 4

## GENIE: A Generalized Array Optimizer

In this chapter, a generalized, simulated-annealing-based array optimization scheme is presented that has been applied to PLA. Gate Matrix, Weinberger Array, and SLA problems[deva86a]. In all cases, the program has obtained as good or better results than the best tools available to us for comparison. In practical circuits, where a number of constraints on terminal positions were involved, our new approach reduced the area of the final layout by up to 50% compared with our previous best techniques. For results of comparable area, GENIE uses comparable CPU time to the previous approaches.

The approach begins with a planar connectivity graph which represented the circuit to be connected. The nodes in the graph represent circuit components, or tiles, in the final layout and the arcs represent the connections among those components. The nodes may represent single transistors, as in the case of a PLA or domino CMOS implementation, or they may represent collections of transistors and interconnect, as in the case of flip-flops in a SLA. The scheme is independent of the nature of the components — it works with a connectivity matrix description of the circuit and topologically compacts it producing a fully routed result. The matrix can be of a highly regular PLA-like structure with uniform cell sizes or it can be a representation of a multi-level logic function in gate matrix form whose cells are of varying sizes. Constraints can be placed on the positions of various input and output terminals if required. The constraints may specify a particular edge for the terminal, a particular fixed location, a particular ordering of terminals, or a combination of these constraints. Terminals may also be required to be

available on more than one edge, as in the case of bus-through connections, for example. Constraints on the aspect ratio of the folded array are also taken into account during the optimization step. The eventual result will have simply or multiply folded rows and columns in a minimum area configuration; no routing is necessary.

The basic simulated annealing algorithm was described in the previous chapter. In the following section the topological compaction algorithm is described. Illustrative examples are given in Section 4.2 and implementation details are discussed. Section 4.3 is devoted to Storage/Logic Array compaction.

## 4.1. A Generalized Array Compaction Algorithm

# 4.1.1. The problem of generalized array optimization

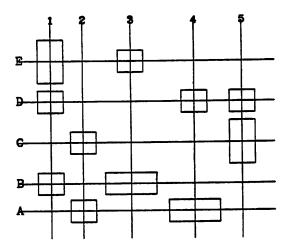

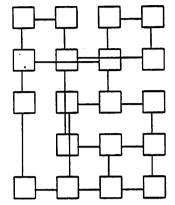

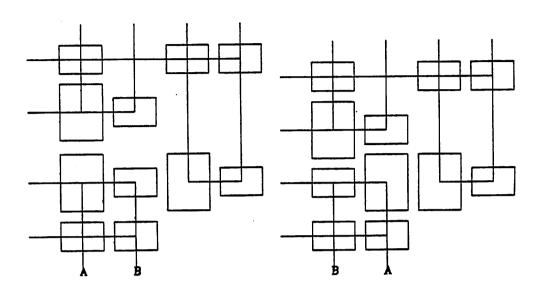

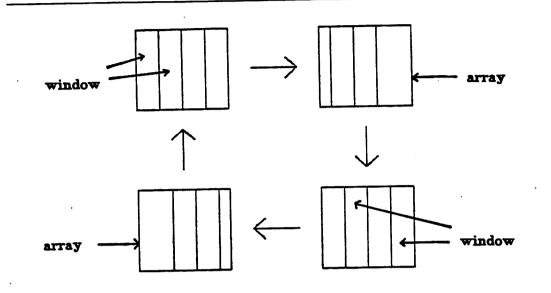

The problem of generalized array optimization is illustrated in Figure 4.1. An unfolded general array is shown in Figure 4.1a. Note that the cells in the array are of varying dimensions. Initially, all the signals in the array occupy distinct rows and columns. It is possible to rearrange the horizontal signals without disrupting the cell connectivity in the array and fold disjoint vertical signals on to the same column. Similarly, the vertical signals can be rearranged, so as to fold horizontal signals on to rows. One folded version of the array is shown in Figure 4.1b. The array has been both column and row folded.

Since the cells are of varying sizes, merely minimizing row and column cardinality does not guarantee minimum area. This is illustrated in Figure 4.1c, where another folded version of the array in Figure 4.1a is shown. Though this result has the same row and column cardinality as the previous result in Figure 4.1b its

area is smaller.

Thus, a generalized array optimization algorithm must take into account the varying dimensions of the cells.

## 4.1.2. Array optimization using simulated annealing

The primary difference between the approach described here and the heuristic folding algorithms developed in the past (e.g. [hach82,chuq82,hach80]) is the existence of hill climbing moves during the optimization process, i.e. moves which increase the cost of the configuration (worsen the solution) are accepted based on a random criterion in an effort to escape local minima.

In GENIE the basic structure is a cell. Cells are interconnected by nets. We intend that the output of GENIE be the input to a tiling program, like PANDA[mah84] or TINKER[hofm85a], for actual layout. The cell denotes the existence of a transistor, or a collection of transistors, at that particular location. Cells may have different sizes depending on the width and length of devices and existence of multiple devices or internal contacts.

Nets are of two kinds, vertical and horizontal. Cells are connected to two nets — one horizontal and one vertical. Special pad cells are connected to input and output nets, including nets that must connect to peripheral load devices, and they serve as ports. Location of pads are constrained to the periphery of the array throughout the annealing process. As explained later, constraints on the locations of input and output terminals are implemented as additional pads.

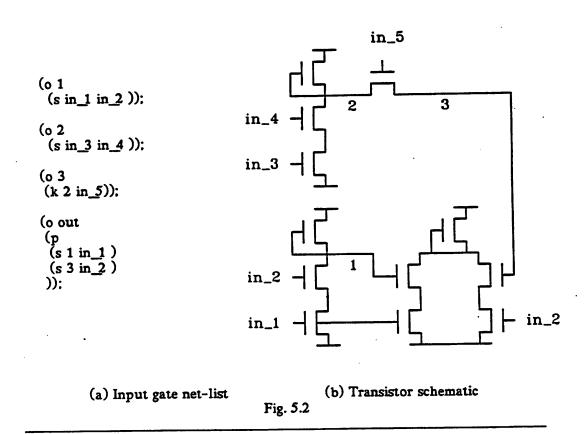

An example of an input to GENIE is shown in Figure 4.2[hofm85a] The connectivity matrix shown in Figure 4.2b has been derived from the Domino CMOS gate diagram shown in Figure 4.2a. Similar personality matrices can be derived from gate diagrams for static CMOS/NMOS design styles. In this format, the

(a) Unfolded General Array

(b) After folding disregarding cell dimensions

(c) After folding taking cell dimensions into account

Fig. 4.1 Generalized Array Optimization

Fig. 4.2(a) Domino CMOS gate diagram.

### new 36 27

| A   | SSS                                   |

|-----|---------------------------------------|

| 11  | s                                     |

| 6   | · · · · · · · · · · · · · · · · · · · |

| 8   |                                       |

| 15  | os                                    |

| В   | ss                                    |

| C   | 8                                     |

| D   | sp                                    |

| 26  | .op                                   |

| 14  | os                                    |

| 13  | p.o                                   |

| out | 0                                     |

| 12  | 80                                    |

| C*  | \$\$                                  |

| 19  |                                       |

| A*  |                                       |

| B*  |                                       |

| 17  | OS                                    |

| 18  | p                                     |

| 23  | p.o                                   |

| 16  |                                       |

| 22  |                                       |

| 5   | 08                                    |

| 4   |                                       |

| 7   |                                       |

| 27  |                                       |

| 9   |                                       |

| 10  |                                       |

| 25  | popo                                  |

| 24  | 80                                    |

| D*  |                                       |

| 3   |                                       |

| 20  | po                                    |

| 2   | po.                                   |

| 21  |                                       |

| 1   |                                       |

|     |                                       |

Fig. 4.2(b) Personality Matrix input to Genie

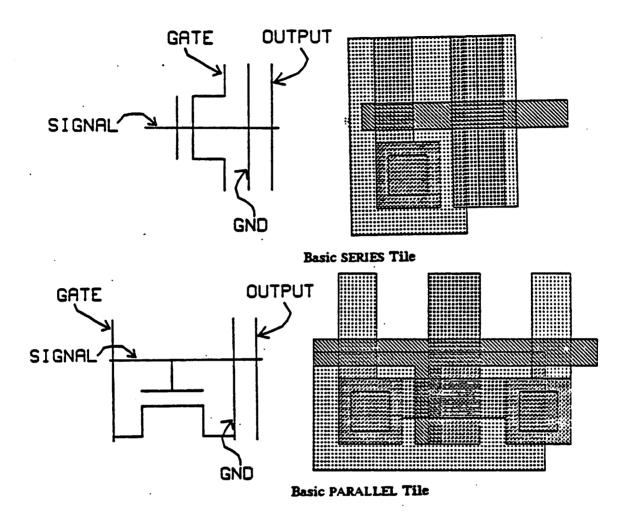

character s declares that the gate in this column is series, or AND, in nature in its top level. Similarly the character p declares that the cluster in this column is parallel, or OR, in nature at its top level. The character o indicates a gate-column

output connection to a signal row; the . character indicates that signals are bussed through this tile without connection to the current gate. The addition of the character ~ . interpreted to mean toggle, allows two-level logic in a single gate to be expressed symbolically. Toggling implies the switching between series and parallel nature in a gate. Two-level structures may need two columns to be represented and realized. A typical set of tiles that these symbols represent for a double-metal technology is illustrated in Figure 4.3.

The problem of array optimization differs from that of placement because in the former case routability is a primary consideration. Our result must be fully routed with the nets perfectly straight and non overlapping. This complicates the problem since simulated annealing is apt to generate random unacceptable configurations like overlapped cells. staggered nets or overlapping nets. Cell displacements can cause staggering of nets unless cells are constrained to move only in a particular direction through out the annealing process. We cannot disallow these configurations, if the power of simulated annealing is to be exploited fully, since the convergence properties of simulated annealing algorithms to the global optimum improves with the enlargement of the configuration space, but these configurations are not allowed in the final compacted array.

Three approaches to the compaction problem were tried using different means of generating new configurations:

- (1) Net displacements.

- (2) Net and constrained cell displacements.

- (3) Unconstrained cell displacements.

In (3) nets at any point may be bent and may overlap each other. Constraining cell displacements to either the X or Y directions alone in (2) may result in either the vertical nets or the horizontal nets being staggered and/or overlapping. In the

Fig. 4.3. Tiles for a double-metal, CMOS Domino implementation

case of (1) the nets are always perfectly straight but they may be overlapping.

All three approaches were implemented and it was found that (1), where the horizontal and vertical nets alone are displaced or interchanged with each other, produced the best results overall. Approach (2) yielded reasonably good results but was wasteful of CPU time and Approach (3) was discarded almost immediately as being unacceptable, again for CPU time reasons.

In (1), there is a three stage compaction process with a first stage of simulated annealing and two stages of routing nets. The routing stages are necessary for removing cell/net overlaps if they exist. Briefly these steps are:

Anneal\_Matrix():

Route\_Horizontal\_Nets():

Route\_Vertical\_Nets():

These three steps are described in detail in the remainder of the section. Approach (2) is described briefly at the end of the section.

#### 4.1.3. Annealing the matrix

The program begins with the initial configuration of nets, cells, number of rows and columns, as specified by the unfolded matrix. The objective is to reduce the total width of the columns and total length of the rows to as great an extent as possible, thus minimizing area. In the case of varying cell dimensions the column width is deemed to be the width of the widest cell on the column and the row length is the length of the longest cell in the row, since these cells set the column or row pitch respectively. All the primary inputs and outputs which are constrained to be at any edge of the matrix are terminated by pads. Pads are fixed cells restricted to lie at the periphery of the array. Adjacency constraints may also be included. For example, in a PLA the input and its complement should lie side-by-side in the folded matrix for an efficient implementation. This constraint to the program takes the form of an extra vertical net connecting two dummy

cells in the input and it's complement rows during annealing.

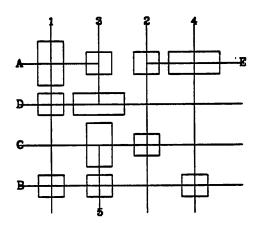

#### 4.1.4. Generating New States

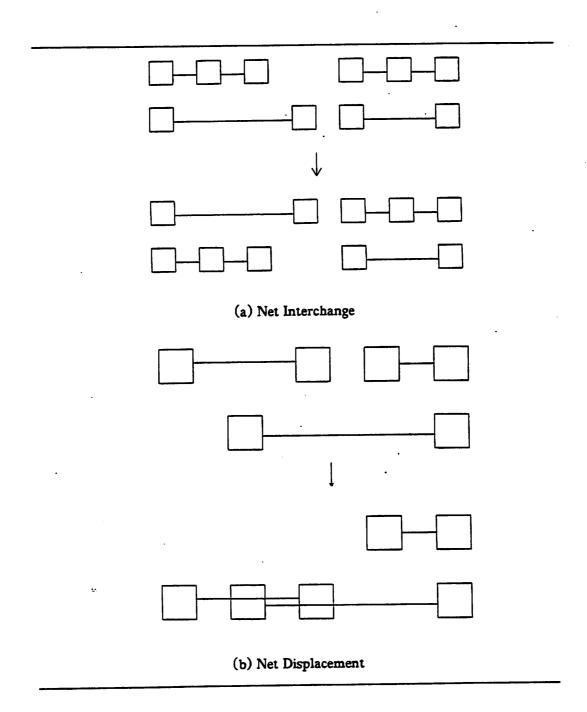

A new state is generated in this stage of annealing process by either exchanging two fundamental units or moving a unit to another location. The fundamental units in this case are vertical or horizontal nets. The overlap of horizontal and vertical nets is penalized, as is cell overlap. The penalty-function approach was first described in [kirk83]. Thus there are four different ways of generating new states: moving a vertical net and all of its cells on it to another column, interchanging two vertical nets on different columns, moving a horizontal net with all its cells into another row, and interchanging two horizontal nets (i.e. interchanging all the cells on two nets). Pads are treated the same as cells but are only connected to a horizontal net and hence the x location of a pad can never change. Pads can be left-pads or right-pads depending on whether they are constrained to the left or the right of the array. A particular horizontal net may have both left and right pads if necessary as in the case of bussed through input signals in connectivity matrices. Net interchanges and displacements are illustrated in Figure 4.4a and 4.4b.

The selection of new states is based on the following considerations:

- (1) A random number between one and the total number of nets is generated.

- (2) A second random number is generated between one and the number of nets times RATIO1 (typically 5).

- (3) If the second number happens to be less than the number of nets and the nets corresponding to the two numbers happen to be both horizontal or both vertical then the two nets represented by the two numbers are interchanged.

(4) Otherwise, the net corresponding to the first number is displaced: vertically if it is a horizontal net to a new row, horizontally if it is a vertical net to a new column.

The final solution is affected by the ratio of net displacements to net interchanges i.e. the number RATIO1. A value of 5 has been experimentally found to be effective in all test cases. The area of an array is reduced only by net displacements and not net interchanges. Net interchanges are useful in removing violations which represent unroutable configurations for example, overlapped nets and overlapped cells. Since the goal is a minimum area configuration, net displacements are in higher proportion.

The displacement of a net to a new row or column is controlled by a range limiter[sech85], which limits the range of displacement of a net either vertically or horizontally. The new location is selected randomly within the acceptable range. The range limiter is used because in the latter stages of the annealing the displacement of a net has very little chance of being accepted unless it is local. So to generate states which have high probability of being accepted, the range of possible displacement of a horizontal(vertical) net is gradually reduced from the total number of columns(rows) at the beginning to a single column(row) when the temperature approaches zero as a logarithm function of the temperature. The logarithm function was experimentally found to be very effective. Net interchanges are also allowed only over a small range toward the end of the annealing process using the range limiter.

The range limiter is also used for implementing bounded column or bounded row constraints. The range of displacement or interchange of a gate is restricted to

the specified bounds by not generating any states which violate the constraints.

#### 4.1.5. The Cost Function:

The cost function is made up of several components. The first portion is total net length which is defined as the distance between its extreme cells. Nets may be weighted differently in which case the cost function is the length times the net weight. Critical nets, which must be kept short, can be weighted heavily (typically, 3-5 times higher) so as to minimize their length in the final layout. As mentioned above, adjacency constraints embody themselves as vertical nets and these nets are weighted highly.

The second portion of the cost is the sum of overlap penalties of all the cells. If a cell or pad is at the same location as any other, a penalty is assessed. This penalty is the sum of all the cell overlaps times a overlap parameter which is large (typically, 30-50) so as to obtain a final configuration without any overlaps.

The third portion is the area penalty for increasing the number of rows or columns in the array. Since the eventual objective is to reduce area, not just wire length, every time a net moves to an empty row(column) a penalty is assessed. Similarly, a negative penalty, or gain, is assessed if a net moves out of a row(column) leaving it empty. There is a corresponding area penalty parameter as in the overlap case (typically 5-10).

The fourth portion is the *net overlap penalty*. This portion exists because net overlap is directly related to routability and is assessed for both horizontal and vertical nets. Two horizontal/vertical nets lying on top of each other represents an unroutable configuration and hence the configuration is penalized.

The fifth portion is required when cells have non-uniform sizes. At every stage the width of each column and length of each row is stored. As mentioned

before, the width of a column is the width of the widest cell on it; likewise for rows. If a net displacement or interchange increases or decreases the width(length) of a column(row) then a penalty or gain is assessed similar to the area penalty. In the case of non-uniform cell width, this serves to minimize the total width and length of the array, rather than simply the number of rows and columns, which is what is needed is to minimize area.

# 4.1.6. The Stopping and Inner Loop Criteria:

A certain number of states (moves) per fundamental unit are generated in the inner loop, which corresponds to a temperature point in the physical annealing process. Horizontal and vertical nets represent fundamental units. The best results were obtained when the cost function attained equilibrium at every temperature point. However, at high temperatures, equilibrium is attained faster, i.e. in a fewer number of generated states, hence the number of states per fundamental unit is gradually increased from a low value (typically 2) to a high value (typically 10) near the end of the annealing process. The value is computed an inverse function of the logarithm of the temperature.

$$S(T) = S_i + (S_i - S_f)^* \log(T) / \log(T_0)$$

where S(T),  $S_i$ ,  $S_f$  are the present, initial and final values of the number of generated states in the inner loop, and T is the present temperature.

The annealing process ends when the cost function has not changed for a cer-

tain number of temperature points at a sufficiently low temperature.

#### 4.1.7. Temperature Profile

The function update determines to a certain extent the quality of the final result. Initially, when the cost of the configuration is increasing the temperature is decreased quickly. At every step the temperature becomes a fraction ALPHA (typically 0.8) of what it was at the previous step. This fraction ALPHA is gradually increased to about 0.90 as the rate of increase of the cost function slows down and begins to decrease. The cost function should attain equilibrium at every temperature point for best results[rome85]. Since equilibrium is reached relatively quickly at high temperatures, initially the temperature is decreased quickly.

### 4.1.8. Routing the Horizontal nets

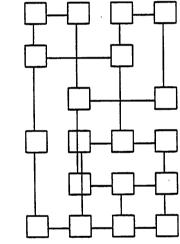

After annealing, the vertical nets and horizontal nets may overlap each other.

A possible overlapped configuration is illustrated in Figure 4.5a. In this second stage all the overlap of the horizontal nets is removed with the minimum change in the placement of cells produced by the anneal.

The straightening procedure is as follows. First the horizontal nets are sorted in the order of decreasing length. All locations are free at the beginning. A net is picked and if it lies on free locations alone it is fixed in its position along with its cells. If any of the locations it lies on isn't free then a new row has to be found for the net. An attempt is made to place the net in any of the other rows without altering the x coordinates of its cells and such that there is no resulting overlap due to this move. If more than one row exists where the net can be placed, the row whose height is closest to the present net's height is chosen. If this is not

possible, a new row is added beside the net's initial row and all the cells of the net are placed on this new row again without changing their x coordinates. The net and the locations are then fixed on this new row. This process is repeated till all the horizontal nets have been placed.

The result of removing horizontal net overlap in the configuration of Figure 4.5a is shown in Figure 4.5b. Vertical net overlap, however, still exists.

# 4.1.9. Routing the Vertical Nets - The Final Stage

At the end of this stage the array is compacted, fully routed and all cell and net overlaps have been eliminated. Typically, the simulated annealing produces a good placement of cells and horizontal nets minimizing vertical net violations. However those violations that do exist must be removed. This stage of routing is more complicated than the previous stage of horizontal net routing as the vertical nets have to be separated from each other without disturbing the horizontal nets. Care must be taken while routing these nets that unnecessary columns are not added.

First the nets are ordered according to decreasing number of cells on the net. They are routed in this order. As before all locations are freed initially. If the chosen net and has no overlaps and lies on free locations it is merely locked in place. If a violation exists then various columns adjacent and neighboring it are examined to see if the net can be placed on that column without overlapping other vertical nets and without causing horizontal net overlap. Thus there is a more stringent condition here for an acceptable column than in the previous case of acceptable rows. If many columns are available for placing the vertical net the column closest to the present one is chosen. If more than one column satisfies this condition, the column whose width is closest to the present net's width is chosen.

(a) Array after Annealing with Overlaps

(b) Horizontal Net Overlap removed

(c) Vertical Net Overlap removed Fig. 4.5

If no existing column satisfies the condition then a new column is added next to the original location and the net with its cells is placed on the column. The final result with all overlap removed of the configuration of Figure 4.5a is shown in Figure 4.5c.

The aspect ratio of the folded matrix depends to a certain extent on whether horizontal net straightening precedes vertical net straightening or vice versa. Relatively speaking, in the former case more rows are folded than in the latter. The same can be said for column folding in the latter case in comparison to the former. The order can be decided upon depending on initial row and column sparsity, initial aspect ratio and final desired aspect ratio. The multiplicative row and column penalty parameters in the cost function also control to a certain extent the relative number of row and column folds.

# 4.1.10. A Brief Description of Approach 2

In this approach, two annealing stages are performed. The generation of states proceeds differently in the two stages. In the first stage (a) horizontal nets are displaced vertically or interchanged with other horizontal nets and (b) cells are displaced horizontally on a row. After the first stage of annealing, the vertical nets may be staggered and overlapping, but the horizontal nets will be straight though horizontal overlap may exist. The cost function has an added constituent in this approach, vertical net stagger. If a net is not straight because all its attached cells are not in the same column, a penalty is assessed. This penalty is proportional to the horizontal distance between the leftmost and rightmost cells. After the annealing, all horizontal net overlap is removed using techniques described earlier in the section.

The second stage of annealing attempts to minimize vertical net stagger and overlap without causing any horizontal net violations. Generation of states is constrained to horizontal cell displacements within the range of the cell's horizontal net. Displacement within the range of the net ensures that horizontal net overlap does not occur. Nets are not interchanged. The cost function in this stage is the vertical net stagger and overlap. After this second annealing stage, vertical net violations due to vertical nets not being straight or overlapping are removed and the compaction process is ended.

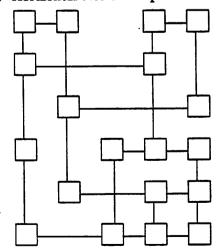

#### 4.1.11. Splitting long nets

The minimum possible area after folding is bounded by the length of the longest nets, horizontal or vertical. One single input feeding to many product terms in a PLA can constrain the final size of the array even if the rest of the array is very sparse. Similar problems can occur in other array structures.

A solution to this problem for the general case is possible in GENIE by preprocessing the array to split the nets possessing a number of cells greater than a

threshold value into two or more subnets. Route-through-cells are inserted to

connect up the different subnets. If a horizontal net is split, two route-throughcells are appended, one to each subnet and connected up by a vertical route net.

Vertical nets can be similarly treated. If the array is a PLA, it now becomes a

pseudo MLM. It has been found that this technique results in large improvements

over the conventional techniques for sparse PLAs with some long nets. An example

### (a) Long Vertical Net constraining Folding

(b) Result after splitting net in two Fig. 4.6

of how splitting a long net can reduce area is shown in Figure 4.6.

#### 4.1.12. Parameter extraction

The cost function has many components and each component has an associated weight given by its parameter. For example, the overlap penalty parameter is typically in the range of 10-50 units and the gain for reducing the number of rows/columns is in the range of 5-10 units. Finding the absolute best set of parameters for a array or a given set of arrays is very difficult. The problem is further compounded by the fact that the efficacy of a particular set of parameters is dependent on the annealing profile i.e. the number of states generated per temperature point and the temperature profile. Also, the size and sparsity of arrays is

a variable factor affecting the parameter efficacy.

However, it is universally true that provided certain inequalities in parameter values are satisfied, if a sufficient number of states are generated per temperature point and if the temperature is decreased sufficiently slowly, the quality of the final solution shows a remarkable insensitivity to the actual parameter values. When CPU time is a factor and the annealing process is short absolute parameter values become important. The relative values of the row and column gain/penalty parameters, however, affect the aspect ratio of the final result and this fact is used to advantage to obtain a desirable aspect ratio as is explained in greater detail in Section 4.2.2.

With these in mind, extraction of parameters for four different array types was done for short annealing times. The four different types were small-dense, small-sparse, large-sparse, and large-dense arrays. The solutions obtained for a wide range of parameter values are summarized in Table 4.1. The parameter values marked with an asterisk were hardwired into the program.

The table gives normalized sets of values for three parameters. These parameters are associated with the gain for reducing rows/columns, the penalty for net overlap and the penalty for cell overlap. Normalization was done so the percentage changes in parameter values could be directly found. The absolute values are 1, 10 and 50 respectively.

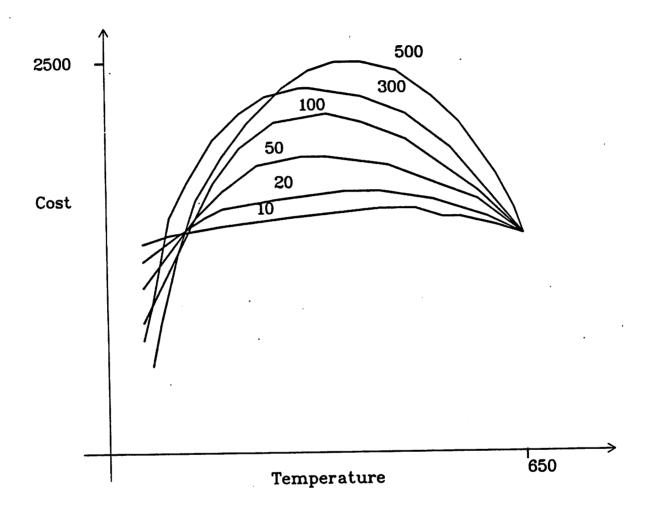

## 4.1.13. Temperature versus Cost Graphs

It is interesting to study temperature-cost graphs for an annealing process to determine the point at which one would like to operate. The marginal utility of simulated annealing goes down as the temperature profile becomes more and more

| parameter         | in1   | in2   | in3   | in4_  | in5   | in6   | in7   |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| TOW               | 0     | 0     | 0     | 1     | 1     | 1     | 1*    |

| net               | 0     | 1     | 1     | 0     | 0     | 1     | 1*    |

| cell              | 1     | 0     | 1     | 0     | 1     | 0     | 1*    |

| gm0.mat(34/20)    | 33/20 | 34/19 | 34/20 | 32/19 | 28/19 | 28/19 | 28/16 |

| apla.mat(42/22)   | 25/20 | 24/19 | 29/19 | 28/19 | 22/20 | 23/20 | 19/16 |

| xcpla1.mat(73/72) | 43/61 | 42/64 | 50/61 | 45/61 | 33/63 | 31/64 | 27/59 |

| ex15(68/52)       | 43/52 | 65/52 | 64/52 | 60/51 | 42/52 | 41/52 | 37/52 |

| parameter         | in8   | in9   | in10  | in11  | in12  | in13  | in14  |

|-------------------|-------|-------|-------|-------|-------|-------|-------|

| IOM               | 1     | 1     | 1     | 1     | 1     | 1     | 1*    |

| net               | 1     | 1     | 0.8   | 1     | 1     | 1     | 1°    |

| cell              | 0.2   | 0.5   | 1     | 0.2   | 0.5   | 0.8   | 1*    |

| gm0.mat(34/20)    | 28/19 | 28/19 | 29/18 | 27/19 | 27/18 | 28/17 | 28/16 |

| apla.mat(42/22)   | 22/20 | 21/19 | 18/17 | 22/19 | 21/15 | 18/19 | 19/16 |

| xcpla1.mat(73/72) | 30/62 | 28/64 | 28/60 | 31/60 | 30/59 | 26/60 | 27/59 |

| ex15(68/52)       | 42/52 | 42/52 | 40/52 | 41/52 | 41/52 | 39/52 | 37/52 |

Table 4.1 - Parameter variations

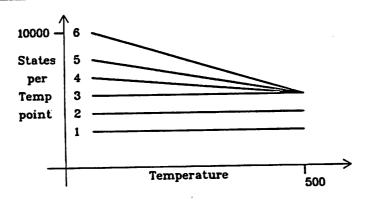

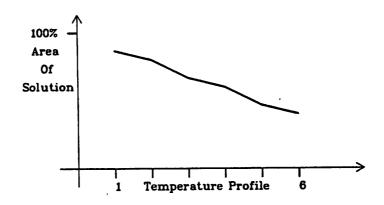

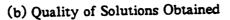

gradual as the solution is getting closer and closer to the global minimum. Ideally, one operates at a point where the cpu times involved are reasonable, and the solutions being obtained very close to the global minimum. Various temperature versus cost graphs for different temperature profiles all starting at the same temperature on one particular example are shown in Figure 4.7. In each of these cases, during the annealing the number of states generated per temperature point was a constant and is indicated above the corresponding curve. The parameter ALPHA was also held constant at 0.90 throughout the annealing process. The final costs are smaller for the temperature profiles with a larger number of states generated, but the difference becomes less and less marked as the number of states per temperature point increases.

Fig. 4.7 Temperature versus Cost Graphs

## 4.2. Examples, Comparisons and Implementation

In this section we first give illustrative examples of compaction of various array structures using GENIE. Due to the complexity of the general folding problem, the only way to measure the performance of a new approach is to compare it with the best methods known previously. GENIE is compared with existing, specialized layout/folding programs.

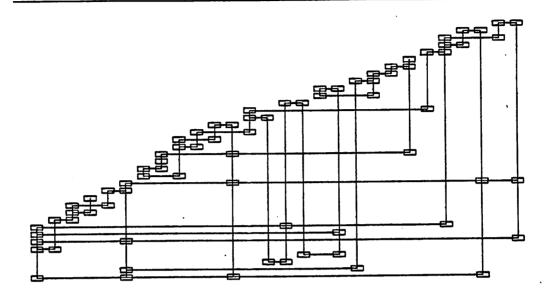

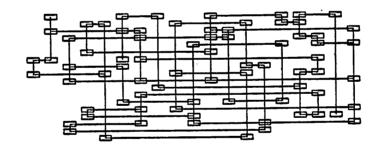

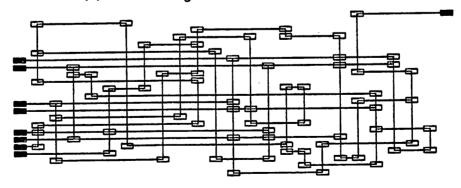

The Gate-Matrix layout of the CMOS Domino circuit of Figure 4.2 is shown in Figure 4.8a. The folded Gate Matrix without any constraints is shown in Figure 4.8b. Constraining all the inputs to the left of the matrix and all the outputs to the right of the matrix the layout shown in Figure 4.8c was obtained. Measuring area as the number of rows multiplied by the number of columns and ignoring the area occupied by peripheral circuits, unconstrained folding reduced the area to 33% of the original as compared to 43% for the constrained case. Additional area is required for the routing of the inputs/outputs in the first case which can cause the total area, including routing, to be larger in the unconstrained result.

While the above example was for CMOS Domino logic, gate structures in static CMOS or static NMOS can be represented similarly in a multi-level matrix form. Gates can be two or more levels deep. Multi-level gates do complicate matters since more than one column may be required for each gate.

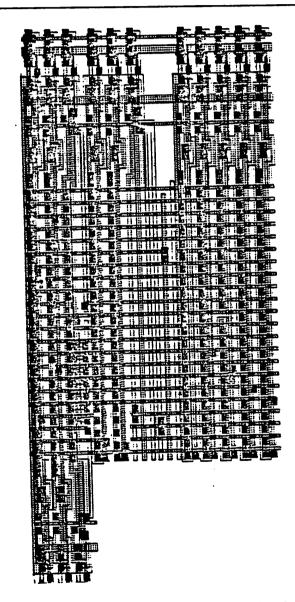

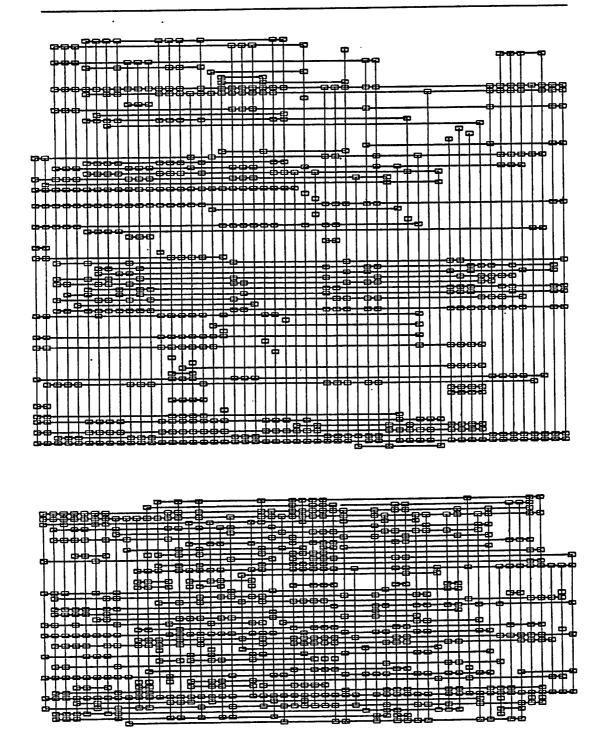

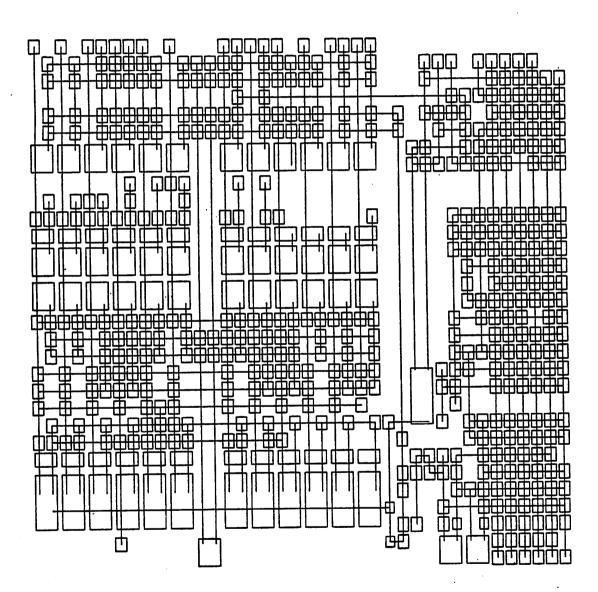

The unfolded and folded layouts of a large circuit are shown in Figure 4.9. There are a total of 647 single-transistor cells in the circuit. The area has been reduced to almost half (53%) of the original in this case. The final layout was obtained in approximately 14 minutes on a DECVAX 8600 running Berkeley UNIX<sup>1</sup> 4.3. A slightly larger layout was obtained in 8 minutes on the same

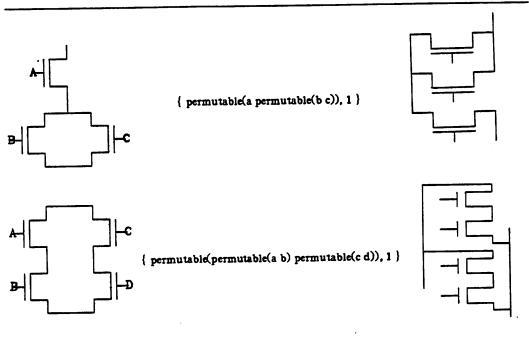

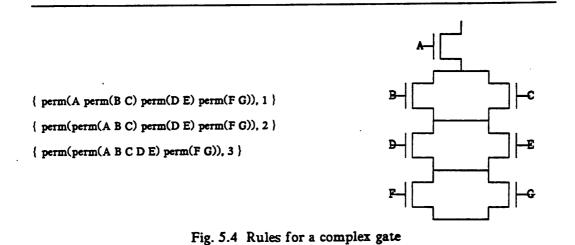

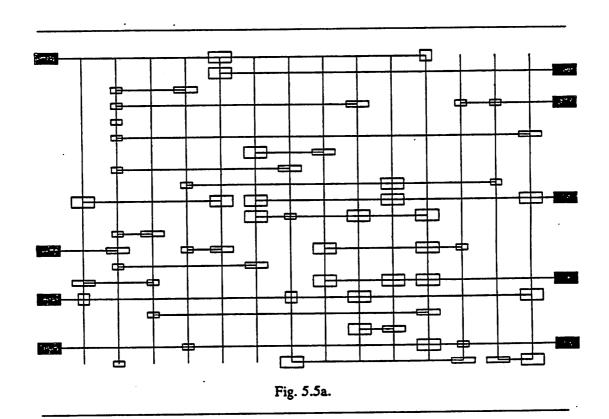

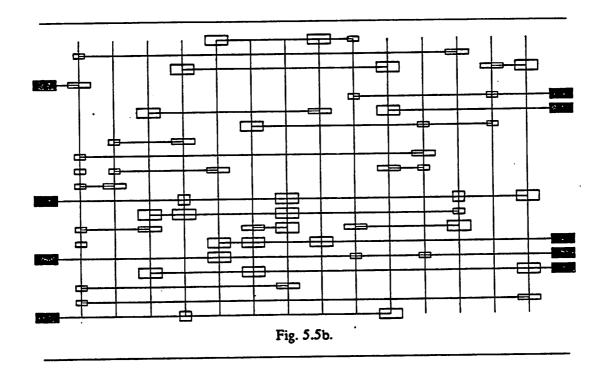

<sup>1</sup> UNIX is a Trademark of AT&T Bell Laboratories