Copyright © 1987, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# DIRECT METHODS IN CIRCUIT SIMULATION USING MULTIPROCESSORS

by

George K. Jacob

## Memorandum No. UCB/ERL M87/67

7 October 1987

# DIRECT METHODS IN CIRCUIT SIMULATION USING MULTIPROCESSORS

by

George K. Jacob

Memorandum No. UCB/ERL M87/67

7 October 1987

## ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

# DIRECT METHODS IN CIRCUIT SIMULATION USING MULTIPROCESSORS

by

George K. Jacob

Memorandum No. UCB/ERL M87/67

.

7 October 1987

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### DIRECT METHODS IN CIRCUIT SIMULATION USING MULTIPROCESSORS

George K. Jacob

Ph.D.

Department of Electrical Engineering and Computer Science

Sponsors: DARPA, SRC, Cal State Micro

in Signature

Donald O. Pederson Committee Chairman

### ABSTRACT

Circuit simulation, the solution of a set of nonlinear ordinary differential equations (ODE's) that describe a circuit's behaviour, continues to be an important tool for the design of integrated circuits (IC's). However, circuit simulation speeds have not kept pace with the increasing number of transistors and complexity of IC's. Parallel processing, the technique of partitioning a large problem into sub-problems and solving the sub-problems simultaneously, is a potential method of improving the speed performance of circuit simulators. This dissertation addresses the issue of applying parallel-processing methods to reduce circuit-simulation runtimes.

The nonlinear ODE's in circuit simulation are commonly solved using either direct or mixed direct-relaxation methods. Since relaxation methods provide an implicit partitioning scheme which makes parallel processing easy, the performance of a node-based relaxation circuit simulator implemented on the BBN Butterfly Parallel Processor is studied and indicates that relaxation-based circuit simulation is an application well-suited to parallel processing. However, relaxation methods alone are not appropriate for the simulation of all circuits and direct methods continue to be important.

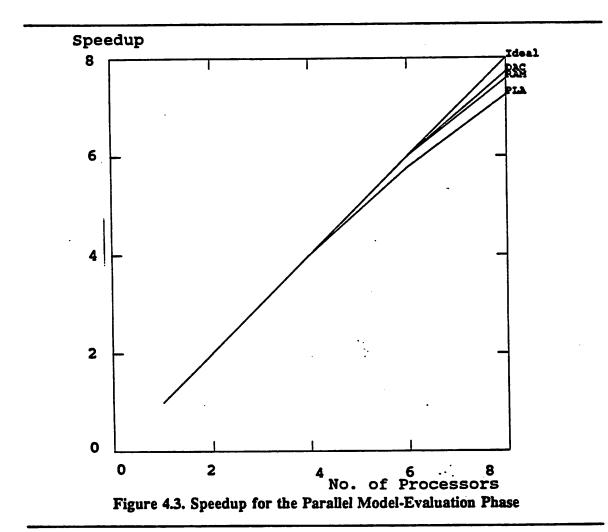

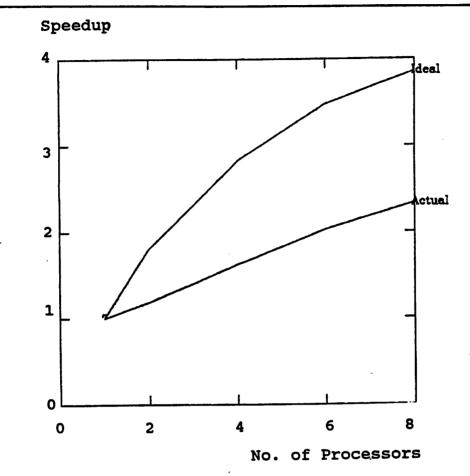

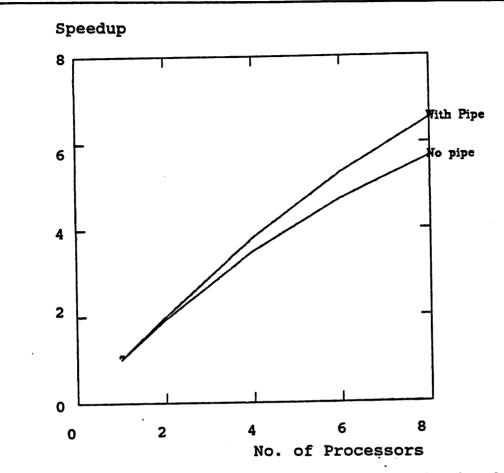

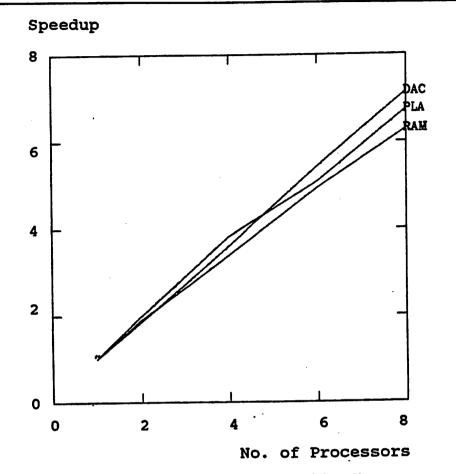

The parallelization of a direct-method circuit simulator is studied on the Sequent Balance B8000 parallel processor. The major time-consuming phases of direct-method circuit simulation, model evaluation and linear-equation solution, are evaluated for their suitability to parallel processing. Model-evaluation time is observed to decrease almost linearly with increasing numbers of processors, proving it is well-suited to parallel processing. Linearequation solution and synchronization points between the two phases are identified as obstacles to the efficient parallelization of direct-method simulators. A new pipelined directmethod algorithm is presented that eliminates the synchronization point between model evaluation and linear-equation solution, thereby improving parallel performance.

#### ACKNOWLEDGEMENTS

This dissertation has been made possible through the efforts of a number of people, although attributed to but one. The following acknowledgements are an attempt to express my immeasurable gratitude to those without whom this document would not have been. To the numerous unmentioned due to constraints of space, time and, alas, memory, my apologies and silent thanks.

Prof. Pederson, my thesis advisor, has been an able mentor and guide, providing advice when I needed it and allowing me (or goading me, if the situation demanded!) to stand on my feet when this was important. Prof. Newton has, through his constant demand for excellence, pushed me to the conclusion of tasks that I might have been wont to leave half-done. Beyond the guidance towards my research and dissertation, I have received from my advisors presentation skills, an appreciation for good work and a sense of perspective that I shall always value. This dissertation serves as adequate testament. I am grateful to Prof. Sangiovanni-Vincentelli for his support, and along with Profs. Pederson and Newton, for the excellent CAD-group environment they have built at Berkeley. The financial support of the California State MICRO program, the Semiconductor Research Corporation and DARPA are gratefully acknowledged.

I thank Prof. Jewell for his support and for reviewing this dissertation. I also thank Profs. Randy Katz, Larry Carter and Jeanne Ferrante for their support of my work. I am grateful to a number of people at Bolt, Beranek and Newman, especially John Goodhue, Bob Thomas, Walter Milliken and Will Crowther, for introducing me (gently) to the wonderful world of multiprocessing, and to Jon Payne for introducing me to Jove. I am also grateful to Tony Magpayo and the folks at Sequent for putting up with the many questions I had about the Balance.

Karti Mayaram, Theo Kelessoglou, Wayne Christopher, Jeff Burns, Srinivas Devadas, Lorraine Layer, Res Saleh, Ron Gyurcsik and Ileana Ocneanu have been constant sources of information, good cheer, humour and inspiration and I thank them for their steady support and wonderful company. I am grateful to Don Webber, Young Kim, Seung Hwang, Ken Kundert, Shelley Sprandel, Tom Boot and everyone in the CAD group for assistance at times when I didn't have the foggiest idea of what was happening to the world around me, and to Randy Cieslak, Tim Salcudean, Myra Boenke, Ted Baker, Güntekin Kabuli, Barbara Mills, John Kunze, Roger Hale, and Herve' and Annick Da Costa for being around to talk to and divert my attention when I found out. I am also grateful to the many who permitted me to vent my frustrations ("research-derived?"; "nay, sir, surely ye jest") on the squash or tennis court.

I thank my room-mates, Amit Bhaya, Aniruddha Das, Nazli Glindes and Sunil Kumar for putting up with and without me, and Vidula Kirtikar, Susan Chacko, and Deb, Bruce and Stephen Smith for their constant love and support. Most of all, I am grateful to my brothers, Jonathan and Rahul, for keeping me humble yet letting me believe I knew who was boss, and to my parents, Jake and Sheila, for picking me off the street.

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                                    | 1  |

|------------------------------------------------------------|----|

| CHAPTER 2: DIRECT-METHOD CIRCUIT SIMULATION                | 7  |

| 2.1 Algorithmic Techniques                                 | 7  |

| 2.1.1 Problem Construction                                 | 10 |

| 2.1.2 Integration Schemes                                  | 11 |

| 2.1.3 The Newton-Raphson Method                            | 14 |

| 2.1.3.1 Linearization                                      | 15 |

| 2.1.3.2 Sparse Linear-Equation Solution                    | 16 |

| 2.2 Hardware-based Acceleration Techniques                 | 18 |

| 2.2.1 Vector and Array Processors                          | 20 |

| 2.2.1.1 CLASSIE: Circuit Simulation on the CRAY-1          | 21 |

| 2.2.1.2 Improvements due to Gather-Scatter Hardware        | 22 |

| 2.2.2 Special-purpose Hardware for Parallel Simulation     | 24 |

| 2.2.2.1 MMAP                                               | 25 |

| 2.2.2.2 BLOSSOM                                            | 27 |

| 2.2.2.3 Special-purpose Subcircuit Solver                  | 29 |

| 2.2.3 Multiprocessor Sparse Linear-Equation Solution       | 30 |

| 2.2.3.1 Linear-Equation Solution: Dynamic Pivot Ordering   | 30 |

| 2.2.3.2 Linear-Equation Solution: Static Dependence Graphs | 32 |

| 2.3 Conclusions                                            | 33 |

| CHAPTER 3: PARALLELISM LIMITS IN CIRCUIT SIMULATION        | 34 |

.

.

| 3.1 Motivation for using MSPLICE                     | 36 |

|------------------------------------------------------|----|

| 3.2 Algorithms                                       | 37 |

| 3.2.1 Iterated Timing Analysis                       | 38 |

| 3.2.2 The MSPLICE Algorithm                          | 41 |

| 3.2.3 The Ideal Gauss-Seidel Machine                 | 42 |

| 3.3 The BBN Butterfly Parallel Processor             | 43 |

| 3.3.1 Architecture                                   | 44 |

| 3.3.2 Programming Environment                        | 48 |

| 3.4 Benchmark Circuits                               | 51 |

| 3.5 The MSPLICE1 Program                             | 53 |

| 3.5.1 Multiple-Queue Dynamic Scheduling              | 53 |

| 3.5.2 Multiple-Queue Static Scheduling               | 55 |

| 3.5.3 Globally Shared Data in MSPLICE1               | 57 |

| 3.6 The MSPLICE2 Program                             | 59 |

| 3.6.1 Differences between MSPLICE1 and MSPLICE2      | 59 |

| 3.6.2 Single-Queue Dynamic Scheduling                | 60 |

| 3.6.3 Limitations of the Ideal Gauss-Seidel Machine  | 63 |

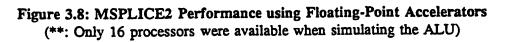

| 3.6.4 Performance using Floating-Point Accelerators  | 65 |

| 3.6.5 Parallel Processing and Iteration Counts       | 68 |

| 3.6.6 MSPLICE Simulating Tightly Coupled Circuits    | 70 |

| 3.7 Conclusions                                      | 71 |

| CHAPTER 4: PARALLEL DIRECT-METHOD CIRCUIT SIMULATION | 74 |

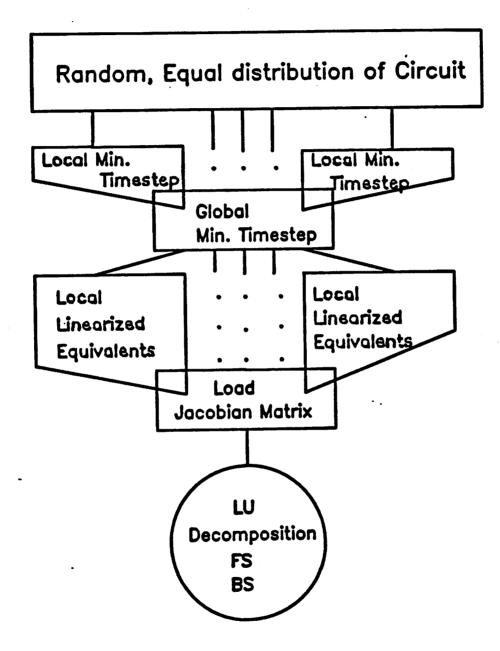

| 4.1 Parallel Direct-Method Algorithms                | 75 |

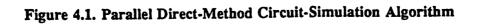

| 4.2 The Sequent Balance B8000                        | 79 |

-

| 4.2.1 Architecture                                                | כ  |

|-------------------------------------------------------------------|----|

| 4.2.2 Programming Environment 82                                  | 2  |

| 4.3 Parallel Model Evaluation                                     | 3  |

| 4.3.1 Algorithm                                                   | 3  |

| 4.3.2 Performance                                                 | 5  |

| 4.4 Parallel Linear-Equation Solution                             | 7  |

| 4.4.1 Sparsity Considerations                                     | B  |

| 4.4.2 Pivot Dependency Graph Algorithm                            | 9  |

| 4.4.3 Performance and Analysis                                    | 4  |

| 4.5 Conclusions                                                   | 5  |

| CHAPTER 5: PARALLEL SPARSE LINEAR-EQUATION SOLUTION               | 7  |

| 5.1 Pivot-based Parallel Linear-Equation Solution                 | 7  |

| 5.2 Row-based Parallel Triangulation10                            | 1  |

| 5.3 Parallel Back Substitution                                    | 4  |

| 5.4 Pipelined Triangulation and Back Substitution10               | б  |

| 5.5 Conclusions                                                   | 0  |

| CHAPTER 6: INTER-PHASE SYNCHRONIZATION BOTTLENECKS                | .3 |

| 6.1 Pipelining Model Evaluation and Linear-Equation Solution      | 4  |

| 6.1.1 Algorithm                                                   | .4 |

| 6.1.2 Performance Analysis11                                      | .8 |

| 6.2 Pipelined Linear-Equation Solution and Convergence Checking11 | 8  |

| 6.2.1 Algorithm                                                   | 20 |

| 6.2.2 Performance Evaluation12                                    | 23 |

|                                                                   |    |

•.

.

.

.

.

| CHAPTER 7:  | CONCLUSIONS                                  | 130 |

|-------------|----------------------------------------------|-----|

| APPENDIX A: | PDSPLICE3 Source Listing                     | 133 |

| APPENDIX B: | MSPLICE1 Source Listing                      | 134 |

| APPENDIX C: | MSPLICE2 Source Listing                      | 135 |

| REFERENCES  | **** **** **** **** **** **** **** **** **** | 136 |

•

.

•

**.**

....

:

.

.

-

### **CHAPTER 1**

### INTRODUCTION

Simulators are used extensively by Very Large Scale Integrated (VLSI) circuit designers in order to study circuit behaviour prior to fabrication. An accurate circuit simulator reads an input description detailing a circuit's connectivity and element parameters and assembles a set of non-linear ordinary differential equations (ODE's) to represent the circuit behaviour. For a prescribed set of input signals over a desired time period, a circuit simulator numerically solves the non-linear ODE's to yield the simulated circuit behaviour, typically presented graphically as output-signal waveforms. Circuit designers study the output waveforms and then modify circuit elements or connectivity until the output signals meet the required design specifications.

Fast circuit simulation is important for the design of electronic circuits, and reliance on circuit simulators is expected to continue as circuit designs and device technologies become more sophisticated. Today's commonly used circuit simulators, e.g., ADVICE, ASTAP, SLATE and SPICE [1,2,3,4] which use direct methods to solve the circuit equations, and SAMSON, SPLICE and RELAX [5,6,7,8,9,10] which use mixed directrelaxation techniques, are not able to simulate 100,000-transistor VLSI circuits within a reasonable time and are growing increasingly inadequate as part of a circuit designer's design-simulate-redesign cycle, especially for certain classes of circuits, e.g., mixed analog-digital circuits and dynamic memories. As a result, significant research is being conducted towards building faster circuit simulators using hardware accelerators [11, 12, 13, 14, 15, 16, 17, 18]. Previous techniques for speeding up circuit simulators include generation of specialpurpose microcode for linear-equation solution [19], software [6, 20, 21, 22] and hardware [23] table-lookup for empirical model evaluation, and the use of vector processors [24, 25] such as the CRAY-1 [26] and array processors [27, 28] such as the FPS-164 [29]. For practical circuits, the overall speed improvement of the simulation has been well under two orders of magnitude compared to SPICE2G [30]. The hardware-related studies [23, 24, 25, 28] are particularly interesting as they show that a significant amount of parallelism is present during the linearization of the circuit matrix.

In [24], it was shown that the sparsity and irregular structure of the circuit matrix caused the data gather-scatter time to dominate simulation time on vector processors. A dominant *gather-scatter* time implies that simply fetching and storing data from and to memory take longer than the actual computation using the data. More recently, vector processors such as the CRAY X-MP, the Hitachi S-810 and the CDC CYBER-205 [31, 32, 33] have been developed with special-purpose hardware for gather-scatter operations and have been utilized to overcome the gather-scatter problem in circuit simulation [34]. However, the Single Instruction Multiple Data (SIMD) operation mode of vector processors [35] results in inefficient utilization of processors during model evaluation, since differing regions of transistor operation necessitate program branches [36]. Thus, efficient parallel techniques must exploit the inherent parallelism of circuit simulation while simultaneously keeping as many processors busy as possible.

Parallel processing, the technique of decomposing a large problem into a number of (smaller) subproblems that are solved by a number of processors in parallel, provides one effective solution to both, the gather-scatter and the SIMD problems. The gather-scatter

bottleneck is avoided because distributed processors access distributed data, rather than initially distributed data being gathered to and scattered from centralized processors (as is the case with vector processors). Since parallel processors operate in Multiple Instruction Multiple Data (MIMD) [35] mode, processors can simultaneously evaluate transistors that are in different regions of operation, thereby exploiting more parallelism than can the SIMD vector processors. As a result, parallel processing appears well-equipped to improve the speed performance of circuit simulators. Parallel processing is made even more attractive by the recent emergence of a number of commercially viable multiprocessors that are built using inexpensive microprocessors, such as the BBN Butterfly Parallel Processor, the Intel iPSC and the Sequent Balance B8000 [37, 38, 39] or special-purpose IC chips for parallel processing, as in the Alliant and ELXSI machines [40, 41]. The introduction of these multiprocessors also makes available a number of different parallel processor architectures, providing users with an opportunity to examine the fit between particular applications and the different architectures.

Efficient parallel processing for speedup requires the selection of an algorithm that displays a high degree of parallelism. Today's circuit simulators use either direct or mixed relaxation-direct algorithms. Direct-method simulators solve all the circuit equations together simultaneously (as a single vector system), including those describing inactive parts of a circuit, and have not proved efficient for rapid simulation of large digital circuits with high levels of latency. Latency of a circuit is defined in terms of both space and time: latency in space refers to the signals in the circuit that are inactive at a given timepoint during a simulation, while latency of a signal in time indicates those timepoints when the signal is inactive during the simulation period. Mixed relaxation-direct circuit simulators decompose a circuit into subcircuits, solving *active* subcircuits using direct

3

methods and iterating between subcircuits, using relaxation, until they converge to a correct solution [42]. Relaxation simulators initially appear better suited to parallel processing than do direct-method simulators, as they naturally partition a circuit into subcircuits that can be solved independently in parallel. However, since subcircuits are assembled on the basis of coupling strength between circuit elements, there is often a large variance in subcircuit size. As a result, balancing load between processors is difficult because processors assigned small subcircuits become idle while other processors continue to work on large subcircuits [10,43]. Thus, for efficient load balancing, the (direct-method) subcircuit solutions themselves must be sub-divided into smaller subtasks which, in turn, can be processed in parallel. Also, direct methods continue to be important for the simulation of tightly coupled circuits, as well as for dc analysis and for circuits that contain elements that are not easily handled by relaxation methods. The parallel potential of direct-method circuit simulation is investigated in this dissertation, through the use of the direct-method subcircuit solver in the parallel Iterated Timing Analysis (ITA) relaxation simulator, PSPLICE3 [43]. In order to distinguish the simulation program developed and described in this dissertation from the unparallelized subcircuit solver in PSPLICE3, the program developed here and listed in Appendix A is referred to as PDSPLICE3. PDSPLICE3 includes both, the parallel relaxation algorithms installed by Res Saleh in PSPLICE3, as well as the parallel direct-method algorithms described in this dissertation.

An introduction to direct-method circuit simulation techniques is presented in Chapter 2. Previous work towards accelerating direct-method circuit simulation through the use of parallel architectures is also described in Chapter 2. This presentation of uniprocessor, direct-method algorithms and previous parallelization experiments provides background as well as direction for the current study. Experiments to increase the efficiency of a multiprocessor-based relaxation circuit simulator, MSPLICE, are described in Chapter 3. This description presents useful guidelines for programming a large multiprocessor system, hence the parallel programming techniques used for the MSPLICE experiment are applied to the parallelization of direct methods. In addition, MSPLICE's performance indicates that node-based relaxation simulators are highly parallelizable, as has been verified in [44]. The efficient parallelization of MSPLICE also helps to identify load balancing as the cause for the inadequate parallel performance of subcircuit-based relaxation simulators as in [10,43].

The first step towards parallelizing an application is the straightforward development of a parallel algorithm based on the best sequential algorithm for the application. Chapter 4 describes a parallel implementation of the most commonly used direct-method circuitsimulation algorithm on the Sequent bus-based Balance multiprocessor. The two most computationally expensive phases of direct-method simulation are the steps of the Newton-Raphson iterative loop, i.e., linearization and linear-equation solution, which are focussed on in this chapter. The linearization phase is demonstrated to lend itself easily to parallelization, with minor task-clumping modifications for efficiency on the Balance. A dataflow method using pivot-dependence graphs (PDG's) similar to those presented in [45] is utilized as a straightforward means of parallelizing sparse linear-equation solution, but it is shown to yield a small degree of parallelism which is difficult to realize on the Sequent Balance.

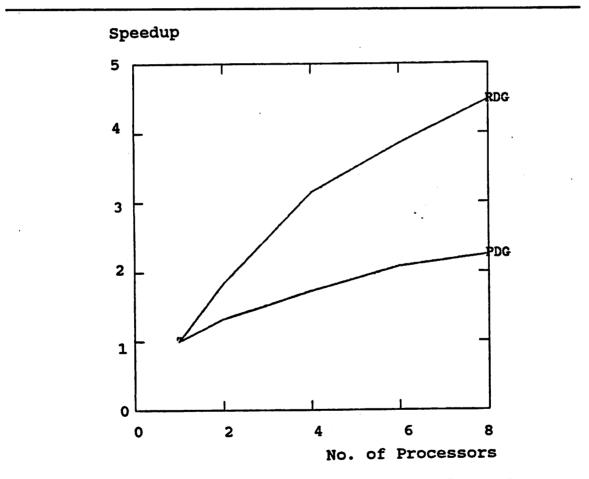

With parallelization of sparse linear-equation solution identified as a bottleneck in the performance of a parallel direct-method circuit simulator, further approaches to parallelizing linear-equation solution are described in Chapter 5. Theoretical limits to the parallelism available using different algorithms are calculated, displaying that the PDG technique provides a larger degree of parallelism as circuit size increases. Further, row-based techniques are shown to have greater parallel potential than pivot-based methods, especially as the density of the circuit matrix increases. A row-dependence graph (RDG) algorithm is presented that efficiently exploits the limited parallelism available during sparse linearequation solution and results are presented for an implementation on the Sequent Balance.

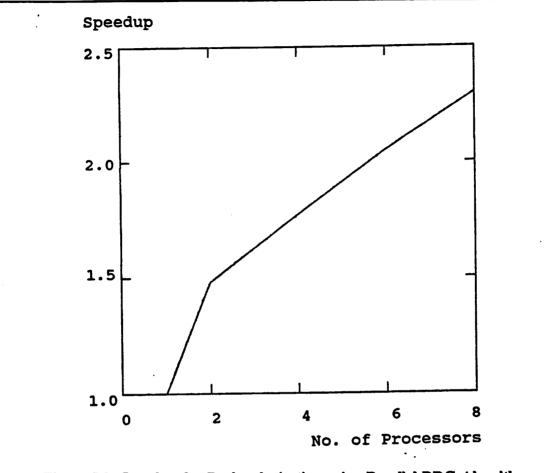

In spite of the efficient exploitation of parallelism in both the linearization and linear-equation solution phases, however, it is evident that the overall speedup for simulation is still limited by the low degree of parallelism during linear-equation solution and by synchronization bottlenecks between the phases. Removal of inter-phase bottlenecks by the use of pipelining improves the potential for parallelizing circuit simulation as a whole. In Chapter 6, a global parallelization scheme that pipelines the highly parallel linearization with the less-parallel linear-equation solution is presented. Pipelining simultaneously removes the synchronization point between the two phases of the Newton-Raphson method and improves the overall parallel potential. In addition, algorithms for parallel convergence checking and for pipelining back-substitution (during linear-equation solution) and convergence checking are presented, which lead to improvements in parallel performance for the direct-method solver as well as for the parallel relaxation simulator that utilizes the directmethod solver only for subcircuit evaluations.

The work described in this dissertation provides insights into parallelizing directmethod circuit simulation. The major conclusions of this study and possible directions for future research are listed in Chapter 7.

### **CHAPTER 2**

### DIRECT-METHOD CIRCUIT SIMULATION

Transient analysis, one of the most commonly used tools in circuit design [6, 19, 24], involves the solution of a system of nonlinear ordinary differential equations (ODE's) that describe the dynamic behaviour of a circuit. These equations may be written in the form

$$F(\dot{x}, x, t) = u(t), \quad x(0) = X_0 \tag{2.1}$$

where x is the vector of circuit variables, F represents a mapping function, u(t) is the vector of input variables at time t, and  $X_0$  represents the values of the circuit variables at time, t = 0 [46]. Techniques for constructing and solving Equation 2.1 using direct methods are described in Section 2.1. In Section 2.2, a number of hardware-based approaches to enhance the speed performance of direct-method circuit simulators are described and evaluated, providing a basis and direction for this study.

### 2.1: Algorithmic Techniques for Direct-Method Circuit Simulation

A -complete representation of a circuit uses Kirchchoff's Voltage Law (KVL), Kirchchoff's Current Law (KCL) and branch equations for each element in the circuit, assembled as the Sparse Tableau [47] shown in Equation 2.2:

$$\begin{bmatrix} A & 0 & 0 \\ 0 & I & -A^{t} \\ B_{i} & B_{v} & 0 \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ S \end{bmatrix}$$

(2.2)

where A is the reduced incidence matrix,  $B_i$  and  $B_v$  are submatrices that contain branch equation coefficients for current and voltage, respectively, and S is the vector of independent source currents and voltages. Programs, such as ASTAP [2], solve this system using Sparse Tableau Analysis [48]. However, a sparse-tableau representation contains n+2b equations, where n is the number of nodes and b is the number of branches in the circuit, while other techniques result in far smaller systems, e.g., Nodal Analysis has only n equations. Because of their compactness, nodal and loop analysis techniques, presented in Section 2.1.1, are better suited for computers with limited memory sizes. As a result, most circuit simulators use Modified Nodal Analysis [49], a mixed nodal- and loop-analysis technique, which is described in Section 2.1.1.

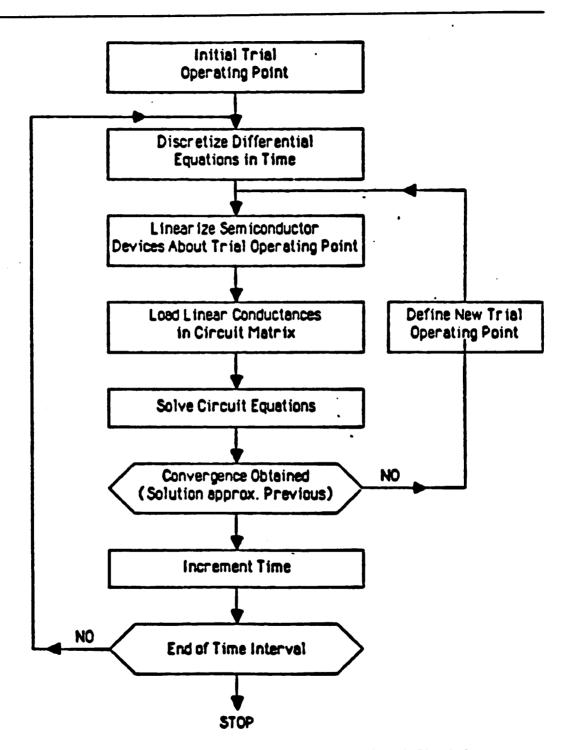

Given the system of nonlinear ODE's describing the circuit behaviour, the simulation proceeds over the desired time period as follows (also shown pictorially in Figure 2.1):

(a) At each timepoint, the nonlinear ODE system is integrated numerically to obtain a nonlinear algebraic system that represents the circuit at that timepoint;(b) The system of nonlinear algebraic equations are iteratively solved using the

Newton-Raphson method, i.e.,

(i) the nonlinear equations are linearized about the old solution point;

(ii) the resulting sparse system of linear equations is solved using LUdecomposition, forward- and back-substitution and yields voltage and current values for a new solution point.

(iii) convergence is checked for by comparing the old and new solution points: if the two points are within allowed tolerances of each other, simulation proceeds at the next timepoint; else, the Newton-Raphson process is continued at the same timepoint.

Figure 2.1. Standard Algorithm for Direct-Method Circuit Simulation

#### 2.1.1 – Problem Construction

The two techniques commonly used to reduce the dimensions of the Sparse Tableau system of circuit equations are Nodal Analysis and Loop Analysis. *Nodal Analysis* [4,49] starts with the KCL equations at each circuit node, which equate the sum of all the branch currents entering each node to zero. Branch current-voltage relationships transform the KCL equations to a set of equations in terms of branch voltages, which are then converted using KVL to a system described by the circuit node voltages [47]. Since this system is over-determined, a single node is assigned as the datum node (at zero potential), and all other node voltages are calculated with respect to the datum node. The second technique, *Loop Analysis*, is analogous to Nodal Analysis, but starts with the KVL equations: the KVL equations are assembled for each loop in the circuit, and branch voltages are replaced using the branch relations and KCL, resulting in a system described by the loop currents.

VLSI circuit devices, e.g., diodes, bipolar and metal-oxide semiconductor (MOS) transistors, tend to be voltage-controlled and are therefore more easily represented by a technique that describes a circuit in terms of voltages, such as Nodal Analysis, than a representation in terms of currents, as in Loop Analysis. Hence, most circuit simulators use Nodal Analysis as a basis to assemble the circuit equations [50, 4, 5, 7, 10].

Nodal Analysis, however, is unable to handle either current-controlled devices or devices without current terms in their branch equations, e.g., independent voltage sources and voltage-controlled voltage sources, since branch relations for the former elements contain no voltage term while branch relations for the latter do not contain a term for current. In addition to the Nodal Analysis equations, these *non-nodal* elements require Loop Analysis equations of their branches. The resulting technique is known as *Modified Nodal*

### Analysis [49] (MNA).

The MNA technique first uses Nodal Analysis to describe the circuit behaviour, ignoring currents for those branches with non-nodal elements. Then, branch equations for the non-nodal elements are added to describe the system completely. As a result, the final system to be solved has more than n-1 equations but is still significantly smaller than the sparse tableau. This is illustrated in Equation 2.3 below:

$$\begin{bmatrix} Y_n & A \\ B & C \end{bmatrix} \begin{bmatrix} e \\ i' \end{bmatrix} = \begin{bmatrix} I_s \\ E_s \end{bmatrix}$$

(2.3)

where  $Y_N$  is the  $n-1 \times n-1$  nodal admittance matrix,  $I_s$  is the  $n-1 \times 1$  vector of independent current sources, e is the  $n-1 \times 1$  vector of node voltages, A is an  $n-1 \times y$  matrix representing the effect of the y irreducible branch currents in nodal analysis, B and C are  $y \times n-1$ and  $y \times y$  matrices that give the branch equations for the irreducible branches, i' is the  $y \times 1$  vector of irreducible branch currents, and  $E_s$  is the  $y \times 1$  vector of independent voltages sources in the irreducible branches. Circuit simulators use numerical techniques to solve Equation 2.3.

#### 2.1.2 – Integration Schemes

Numerical integration is employed to convert the nonlinear ODE system to a set of nonlinear algebraic equations. For circuit simulation, the numerical integration techniques used are *linear*, *multistep methods*, which divide the simulation interval into a number of timesteps [51]. Then, for each timestep, the system's behaviour is approximated by a linear function of past and present voltages, currents and charges. Thus, a linear, multistep method starts from the known dc solution for the circuit, calculates the circuit variables at the end of the first timestep and continues this process till the end of the simulation period,

while limiting the error at each step. The procedure of numerical integration is illustrated below using a single ODE for simplicity.

Given a first-order ODE of the following form:

$$\dot{y} = f(y,t)$$

linear, multistep methods divide the simulation period, T, into a number, n, of periods,  $t_n$ , such that:

$$t_0 = 0, \cdots, t_{n+1} = t_n + h_{n+1}, \cdots, t_N = T, n = 0, 1, \dots, N$$

where  $h_n$  is the timestep taken to arrive at the end of the *n*th period. Multistep methods compute  $y_{n+1}$  on the basis of y and  $\dot{y}$  at p previous time points, in the following form:

$$y_{n+1} = \sum_{i=0}^{p} a_i y_{n-i} + \sum_{i=-1}^{p} h_{n-i} b_i \dot{y}_{n-i}$$

(2.4)

An example of an explicit method, where  $b_{-1} = 0$ , is the Forward Euler (FE) method, which is described by

$$y_{n+1} = y_n + h_{n+1} \dot{y}_n \tag{2.5}$$

Note that the FE method, as with all explicit methods, requires merely a function evaluation in Equation 2.5. Implicit methods, like the commonly used Backward Euler and Trapezoidal methods, have  $b_{-1} \neq 0$  and require iterative solutions. For example, the *Backward Euler (BE)* method is described as

$$y_{n+1} = y_n + h_{n+1} \dot{y}_{n+1} \tag{2.6}$$

while the Trapezoidal (TR) method can be represented as

$$y_{n+1} = y_n + (h_{n+1}/2) (\dot{y}_{n+1} + \dot{y}_n)$$

(2.7)

Implicit methods, due to the "feedback loop" in their formulation, are generally more stable than explicit methods and provide error control and are hence preferred for integration.

-----

Since an integration method approximates a continuous function by a linear equivalent, an error may be introduced due to truncation of the function. At each timestep, the truncation error due to a multistep method is dependent on the errors in the values calculated at the previous steps and is termed the Global Truncation Error. However, it is possible to compare the accuracy of integration schemes in an approximate manner merely by comparing their respective Local Truncation Errors (LTE's), where the LTE is defined as the error between the calculated and actual values of the function at a given timestep, assuming that solutions at all previous timesteps were exact. The LTE of an integration method is a function of the timestep, the coefficients of the method, and the order of the method (determined by the polynomial of the highest degree exactly solvable by the method). Therefore, circuit simulators control the LTE at each timestep by controlling the size of the timestep. In the limit, as the timestep tends to zero, the error tends to zero as well; however, this increases the number of timesteps taken during the simulation period. As a result, circuit simulators take the largest timestep possible to keep the simulation time small, yet ensure that the LTE at each node in the circuit is always less than a certain preassigned constant.

In spite of restricted LTE's at each timepoint, an integration method may sometimes be unstable, i.e., its use results in predictions of instability for stable systems. It can be shown [46] that the FE method is stable for only a certain range of timesteps; the BE method is over-stable, i.e., it will make unstable systems appear to be stable, thereby quelling real oscillations; and the TR method is A-stable, i.e., it represents stable and unstable systems as being stable and unstable, respectively, regardless of the timestep used. The TR method is commonly used in circuit simulators. Due to the many independent energy storage elements in a circuit, there is often more than a single time constant associated with a circuit. The chosen integration scheme should thus be *stiff* [46], i.e., it should be able to handle a wide range of time constants. If the integration method were only stable for small timesteps, as is the FE method, then the simulation would require many timesteps, even though the signals in the circuit may not be changing rapidly. A *stiffty stable* integration scheme, such as BE and TR, is stable for any size of timestep, and thereby facilitates the use of small timesteps when circuit signals are changing rapidly, or large timesteps when circuit activity is slow.

Once the nonlinear ODE's have been integrated numerically, they yield a set of nonlinear algebraic equations. These equations are then solved directly, using the Newton-Raphson method.

#### 2.1.3 – The Newton-Raphson Method

The Newton-Raphson (NR) method is an iterative technique used to solve a nonlinear equation. Each iteration proceeds as follows:

(a) Estimate an initial solution to the equation,

(b) Linearize the equation around the estimated solution, and

(c) Calculate the solution to the linear equation.

This process is repeated, using the solution from one iteration as the estimated initial solution for the next iteration, until the difference between the last two solutions is smaller than the weighted sum of an absolute tolerance and the product of the current solution with a relative tolerance, when the method is said to have *converged* to a solution.

### 2.1.3.1 – Linearization of the Circuit Matrix

At each iteration, i, the NR method involves determining a solution, x', to the following equation

$$x^{(i+1)} = x^{i} - J(x^{i})^{-1} f(x^{i})$$

(2.8)

where the elements of the Jacobian,  $J(x^{i})$ , represent linearized circuit elements that would be obtained by linearizing each branch equation independently at  $x^{i}$ . Given that J(x) is Lipschitz-continuous, i.e., J(x) is continuous and its rate of change is bounded and that J(x') is non-singular, the NR method converges provided the initial estimate is close to x'. Further, the NR method converges quadratically in the immediate vicinity of x', i.e., the error decreases quadratically with successive iterations. Hence, the NR method has a high rate of convergence when the estimated solution is close to the true solution, underlining the need for a good initial estimate.

When the estimated solution is distant from the true solution, the NR method does not converge rapidly and may not converge at all, e.g., when oscillations occur between two or more incorrect estimates. This problem may be addressed by methods that increase the region of convergence. For example, the source-stepping method allows sources to be activated in small steps, thereby reducing the distance between the initial estimate and the final solution.

While using the NR technique, it is possible to obtain some values of the local gradient (within the Jacobian matrix) that are high and predict unrealistic future values for certain circuit variables. On a computer, this results in numerical overflow and must be limited to allow the simulation to continue. The technique used in a number of circuit simulators to handle this problem is that of voltage and current *limiting*. Limiting schemes are imposed only when predicted circuit variables, namely voltages and currents, rise above a certain threshold. In such cases, the highest-valued variables are reduced to a limiting value, and all other predicted variables are adjusted proportionately.

Since circuit model evaluation is expensive, a number of techniques have been employed to reduce the time taken for the linearization phase. It has been shown that table lookup reduces model-evaluation time significantly, by eliminating the need for repeated calculation of device-function coefficients [20,21,23,52]. Some circuit simulators save time by not updating the Jacobian matrix at each NR iteration, arguing that the Jacobian matrix is inaccurate when distant from the solution, while close to the solution the Jacobian matrix's accuracy makes frequent updates unnecessary [53,10]. Finally, it has been experimentally shown [6] that an *element-bypass* technique, where models are only evaluated if their input voltages and currents have changed by a significant amount, can result in significant savings, especially for predominantly digital circuits with large degrees of latency. If all elements are by-passed, and only the right-hand-side vector is updated, this approach is equivalent to the Jacobian bypass scheme.

### 2.1.3.2 – Sparse Linear-Equation Solution

. . .

Gaussian Elimination (GE) is one of the most efficient algorithms available to solve a system of linear equations represented as

$$Ax = b \tag{2.9}$$

where A is a non-singular  $n \times n$  matrix, and x and b are n-dimensional vectors for the unknowns and right-hand side, respectively. LU-decomposition, a technique that uses the same number of operations as Gaussian Elimination, is commonly used in circuit simulators because, unlike GE, it does not necessitate modification of the right-hand side and is hence useful for analyses where multiple right-hand sides are used. LU-decomposition involves decomposing the system in Equation 2.9 to

$$LUx = b \tag{2.10}$$

where L is a lower-triangular matrix and U is an upper-triangular matrix. Then, the system

$$Ly = b \tag{2.11}$$

is solved for the unknown y using Forward Substitution, following which the system

$$Ux = y \tag{2.12}$$

is solved for the unknown x by *Back Substitution*. LU-decomposition is attractive when the Jacobian matrix is not updated at each iteration, since the linear-equation solution involves only forward and back substitution and the decomposition need not be repeated until the Jacobian matrix is updated.

Circuit simulators employ strategies to maintain the sparsity that characterizes circuit matrices. Typically, a circuit matrix has three or four non-zero elements per row or column, usually such that the matrix has an irregular structure. The Markowitz technique [54], commonly used to determine pivoting order, assigns each pivot candidate a Markowitz row count and a Markowitz column count, which are the number of non-zeroes in the row or column other than the pivot candidate itself. Then, the pivot candidates are ordered to be eliminated in order of increasing Markowitz product (the product of the Markowitz row count and the Markowitz column count). For circuit simulation, the pivoting order is usually determined once each for dc solution and for transient analysis, although it is possible that circuit dynamics may necessitate re-ordering during a transient analysis. Circuit matrices are re-ordered during transient analysis only if the magnitude of one of the diagonal elements in the matrix falls below a certain threshold. .

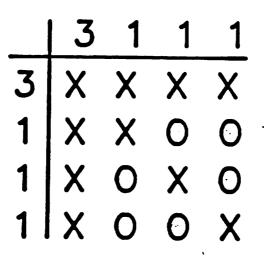

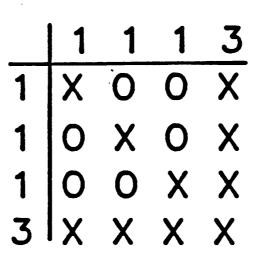

The example matrix shown in Figure 2.2(a) illustrates the ordering of a small matrix using the Markowitz criterion. In Figure 2.2(a), non-zeroes in the matrix are denoted by X's and zeroes are denoted by O's. With the configuration in Figure 2.2(a), after the first row has been eliminated, all the zeroes in the matrix are filled in, and the matrix is subsequently 100% dense, resulting in a total of 36 floating-point operations on the matrix. However, using the Markowitz criterion, the configuration in Figure 2.2(b) is arrived at, no fill-ins are created and a total of 16 floating-point operations are performed during the LU-decomposition.

The diagonal elements of the matrix A, known as *pivots* when selected during matrix ordering to stay on the diagonal, are crucial to the accuracy of linear-equation solution since the elements in a row are divided by the corresponding pivot element. Thus, if a pivot element is much smaller than the rest of the elements in the row, inaccuracies may occur due to computer finite-precision arithmetic. As a result, circuit simulators employ *pivoting strategies*, to determine which matrix elements should be used as pivots in order to ensure accuracy through the simulation [55].

#### 2.2: Hardware-based Acceleration Techniques

While a number of algorithmic techniques [5, 6, 9, 10, 43, 50, 52] have led to electrical circuit simulation that is almost two orders of magnitude faster than SPICE, large-scale improvement in the speed performance of circuit simulators continues to depend on hardware-based approaches, presented in this section.

In Section 2.2.1, work on vector and array processors is described [24, 27], revealing that a high degree of parallelism is *available* in model evaluation, but that early vector and

Figure 2.2(a) Non-optimal Ordering of Example Matrix

Figure 2.2(b) Ordering of Example Matrix using Markowitz Criterion

array processors were not able to exploit this parallelism due to the gather-scatter bottleneck, as is detailed in Section 2.2.1.1. Further research on vector processors with special-purpose hardware for gather-scatter operation, described in Section 2.2.1.2, reveals that pre-processing of a sparse matrix can accelerate the sparse linear-equation solution process [34]. Special-purpose hardware approaches to parallel circuit simulation are presented in Section 2.2.2. Research with special-purpose hardware that efficiently exploits the high parallelism in the model-evaluation phase [23] is detailed in Section 2.2.2.1. In Section 2.2.2.2, a special-purpose hardware configuration designed for parallel linearequation solution is described [56]. A hardware subcircuit-solver co-processor for use in a mixed relaxation-direct circuit-simulator multiprocessor system [17] is detailed in Section 2.2.2.3 and provides a hardware-based complement to the software approach to parallel processing taken in this dissertation. While the parallelism inherent in model evaluation has long been recognized [24], parallel sparse linear-equation solution has proven to be a more intractable problem. In Section 2.2.3, different approaches to parallel circuit simulation are described. An attempt at parallel, sparse linear-equation solution on a generalpurpose multiprocessor is described in Section 2.2.3.1, serving to highlight some of the pitfalls to be avoided [56]. In Section 2.2.3.2, a parallel sparse linear-equation solution using dependence graphs proposed in [45] is described. A parallel version of the direct-method simulator, ADVICE [1] running on the Alliant FX-8 [40] is described in Section 2.2.3.3.

#### 2.2.1 - Vector and Array Processors

ina. Na si s

> Early vector processors, such as the CRAY-1 [26], were the first parallel computers available and used the Single-Instruction Multiple-Data (SIMD) stream mode of parallel computation. Thus, the pioneering work on developing parallel circuit simulators was

performed on vector and array processors and is described in this section. The first parallel circuit simulator, CLASSIE [24], was implemented on the CRAY-1 and is described in Section 2.2.1.1. CLASSIE performance indicated that the sparse irregular nature of the circuit matrix hindered efficient parallel simulation, thereby underlining the need for special-purpose hardware to handle the gathering and scatterring of data between processing units and memory banks. The introduction of special-purpose hardware for gather-scatter operations resulted in significant improvement of circuit-simulation speeds on vector processors and one example of this improvement [34] is described in Section 2.2.1.2.

### 2.2.1.1 – CLASSIE: Circuit Simulation on the CRAY-1

A prototype circuit simulator, CLASSIE (implemented on the CRAY-1), is presented in [24] as a means of performing fast, accurate, hierarchical analysis of large-scale integrated circuits on vector computers. CLASSIE employs user-defined node tearing [57] to decompose a circuit into cells, according to functional (and structural) hierarchy, at the nonlinear-equation level. Identical cells are analyzed in parallel using vector operations.

In addition to vectorization, CLASSIE provides a number of modifications to standard circuit-simulation algorithms that improve its performance on a uniprocessor as well. Firstly, CLASSIE orders semiconductor devices by models, thereby saving time while gathering model parameters. Secondly, by decomposing a circuit into smaller subcircuits, CLASSIE circumvents the linear-equation solution-time problem of standard circuit simulators. This is because sparse linear-equation solution time in standard circuit simulators, which increases superlinearly with the number of nodes in a circuit, only dominates overall circuit-simulation time for large circuits (over 2000 nodes) [58]. It is believed that the

superlinear solution time is due primarily to longer searches through the sparse-matrix pointer structure (which would be aggravated by increased paging) and CLASSIE avoids this problem by reducing the dimension of individual sparse matrices. As in [19], CLAS-SIE employs code generation to reduce linear-equation solution time. Due to these modifications, CLASSIE runs twice as fast as SPICE2 on a VAX 11/780 uniprocessor for large circuits.

Although CLASSIE (on the CRAY-1) in its vector mode runs faster than it does in scalar mode and speed-up increases as circuit size grows, its performance is not encouraging on the whole. In particular, it is observed that data gather-scatter time for a bipolar junction transistor (BJT) takes as much as 75% of the total model-evaluation time. As a result, vectorized model evaluation in CLASSIE on the CRAY-1 yields a speed-up of about 1.5 for mixed BJT-diode circuits and about 2 for a MOS benchmark circuit. Vectorization results in a speed-up factor of under 2 for linear-equation solution, resulting in an overall simulation speed-up of less than an order of magnitude.

Thus, while the CLASSIE experiment indicates that substantial gains are available by decomposing and solving circuit-simulation problem data in parallel, the gather-scatter problem in vector processors such as the CRAY-1 makes realization of these gains difficult.

### 2.2.1.2 - Vector Circuit Simulation with Gather-Scatter Hardware

In [25], it is shown that matrix computation, the dominant part of large-scale simulation, is difficult to vectorize due to the sparse, irregular nature of the matrix. This corroborates the results obtained in [24] and described above in Section 2.2.1.1. However, it has since been shown [34] that vectorized LU-decomposition can result in significant gains in simulation speed, *if the vector processor has special-purpose hardware for gatherscatter operations* (referred to as the "indirectly indexed vector feature"). Further, while CLASSIE processes structurally identical subcircuits in parallel, the vectorization algorithms used in [34] do not require user-defined subcircuits but automatically detect parallelism within the irregular structure of the matrix. The Block Vectorization Algorithm and Maximal Vectorization Algorithm used in [34] and their performance on the Hitachi S-810 [32] are described below.

The Block Vectorization Algorithm (BVA) for LU-decomposition identifies parallelism in blocks of consecutive columns of a matrix pre-ordered using the Markowitz criterion [54], such that the columns within a block can be decomposed independently of each other. Parallelism is exploited within each block using vectorized divide  $(A_{ji} = A_{ji}A_{ji})$  and update  $(A_{jk} = A_{jk} - A_{ji} * A_{ik})$  operations. This algorithm allows the use of more efficient parallel dense-matrix operations towards the end of the LUdecomposition.

The Maximal Vectorization Algorithm (MVA) is derived from the BVA but attempts to locate parallelism *all over the matrix at every step of the LU-decomposition* and is not limited by the Markowitz ordering. The MVA computes a data reference level for each element, according to the earliest step at which the element can undergo division or updating. The LU-decomposition is then performed symbolically for the entire matrix and elements which produce the same data reference level are grouped together. Then, during the actual decomposition, all elements in the same group are processed in the same vector step. In addition to the implementation of the BVA and MVA on the Hitachi S-810, the LU-decomposition is also accelerated through the use of code generation. For a 2132 MOS-transistor circuit, a factor of 16.5 speedup is achieved in matrix solution due to code generation alone. With the BVA and the MVA, overall speedups of 75.7 and 82.4 are achieved for matrix solution, indicating speedups of 4.59 and 5.0 due to the BVA and MVA respectively. While these results are encouraging and it is evident from [34] that the speedups increase with circuit size, the actual speed improvement due to exploitation of parallelism is still relatively small indicating the need for alternative algorithms. In addition, vector processors, being SIMD machines, require the static scheduling inherent in both the BVA and MVA and *force* all elemental operations to be of the same length. A general-purpose parallel processor, using an MIMD architecture, allows more flexibility in scheduling and can perform individual elemental operations according to their respective requirements, optimizing through the use of local memory.

### 2.2.2 - Special-purpose Hardware for Parallel Circuit Simulation

As a result of the increasing sophistication and reduced cost of VLSI, applicationspecific integrated circuits (ASIC's) are becoming feasible. Thus, it is now economical to synthesize hardware for the express purpose of performing a certain set of operations that would previously have been performed using software. To this end, numerous designs have been proposed that replace computation-intensive sections of circuit-simulation programs with special-purpose hardware. Descriptions of a scheme for parallel MOS model evaluation as well as one for large-scale parallel sparse linear-equation solution, both using attached processors, are presented below.

## 2.2.2.1 - MMAP: An Attached Processor for Parallel Model Evaluation

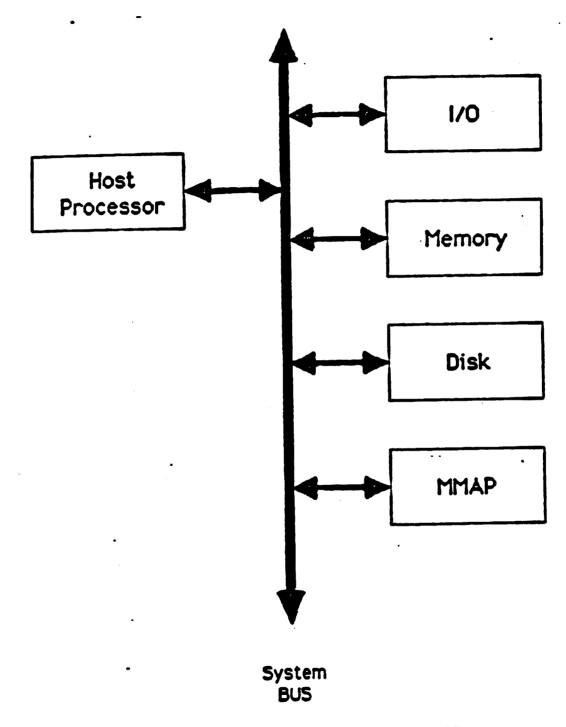

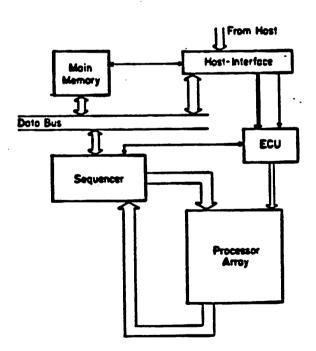

To exploit the high degree of parallelism inherent in the linearization or modelevaluation phase of circuit simulation [24, 25, 28, 36] a special-purpose attached processor (MOS-Model Attached Processor, MMAP) that evaluates the dc-MOS transistor equations has been designed and evaluated in [23]. The special-purpose processor is attached to an IBM PC-XT personal computer, and the circuit simulator used is BIASC [59], a subset of SPICE written in the programming language C and designed to run on the IBM PC. A prototype MMAP utilizes pipelining and local memory to evaluate linear models for four MOSFET devices simultaneously. Experimental results indicate a high efficiency for parallel model-evaluation, limited by the 8-bit data bus of the IBM PC. The architecture of a system using the MMAP is shown in Figure 2.3.

The MMAP operates as follows: Transistor-model information is stored in the MMAP's local memory. When the host computer requires the evaluation of a transistor, it sends the transistor's input data, namely the model reference, terminal voltages and channel scale factor, to the MMAP, which evaluates the device coefficients at the operating point and returns the results to the host computer. Through the use of multiple-stage pipelined hardware, the MMAP is able to work simultaneously on several transistors. A novel empirical model, designed for use with the pipelined MMAP, enables model evaluation without conditional branching and uses only floating-point addition, subtraction and multiplication.

Figure 2.3 Architecture of the MOS-Model Attached Processor

While experiments with the prototype MMAP show that it incurs a 20% communication overhead, simulations of the MMAP indicate that with efficient operation of the system this overhead would be 60%, highlighting the slow transfer rate for floating-point data over the 8-bit data bus as well as the need for a wider and faster bus. In addition, it was observed that 40% of the MMAP's active time was spent transferring data between the Model Processing Unit (MPU) and the MMAP's memory, which were on separate chips, indicating that a single-chip implementation of the MPU with coefficient memory would significantly enhance attached-processor efficiency.

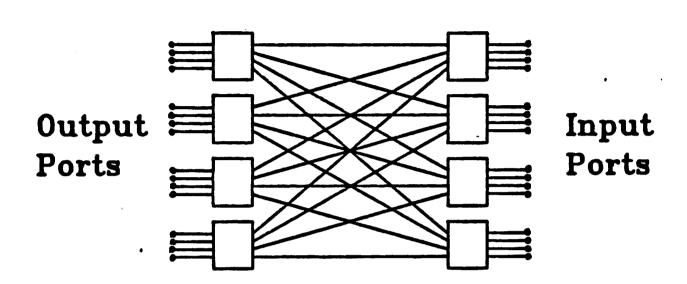

#### 2.2.2.2 – BLOSSOM: A Systolic Array for Parallel Linear-Equation Solution

A comprehensive study of various techniques for the solution of large-scale linear systems of equations has been conducted in [56]. This study includes analyses of the best uniprocessor algorithms, as well as special-purpose hardware and multiprocessor algorithms obtained by mapping the best uniprocessor algorithms on to different architectures. The various techniques are compared on the basis of numerical stability, sparsity preservation, computational complexity and convergence rates, while recognizing the dependence of parallel-algorithm performance on the parallel-processing environment, which is difficult to model accurately.

For large-scale systems, in the interests of preserving sparsity and maintaining low computational complexity, Gaussian elimination with pivoting is identified as the most efficient means of solving sparse linear equations. Further, block LU-factorization, using inverses of the diagonal submatrices rather than of their L and U factors, is selected as the basis for the proposed special-purpose hardware for parallel linear-equation solution. BLOSSOM, the special-purpose architectural system proposed for parallel, sparse linear-equation solution, comprises of a reconfigurable systolic array connected to a host computer. BLOSSOM uses its own memory, data bus and executive control unit to operate independently once the system to be solved has been loaded into its local memory by the host. Submatrix operations to be performed by the processors in the systolic array are assumed to be implemented as microprograms in the processors. The system architecture with the BLOSSOM unit is shown in Figure 2.4.

Results from a software simulator of the BLOSSOM system indicate that most of the partitions are 2×2 submatrices; for a 1957×1957 matrix (from the simulation of a memory

Figure 2.4 Architecture of the BLOSSOM Linear-Equation Solution System

۰,

28

circuit) it is seen that a  $2\times25$  processor array solves the system 9.25 times faster than a  $2\times2$  array, indicating 74% efficiency. Given the high efficiency of the BLOSSOM system, even without exploiting the parallelism that would be available by pipelining the submatrix operations, it is evident that such a hardware-based approach shows promise for rapid parallel sparse linear-equation solution.

The BLOSSOM experiment displays potential for accelerating sparse linear-equation solution through the use of costly special-purpose hardware. A more inexpensive alternative is the use of general-purpose multiprocessors, as is described in Section 2.2.3.

#### 2.2.2.3 – A Special-Purpose Subcircuit Solver

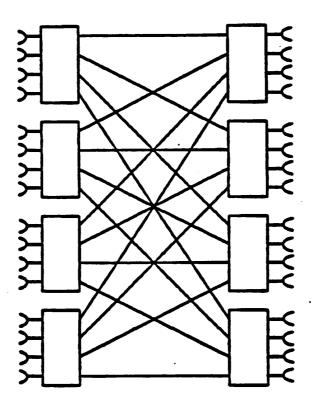

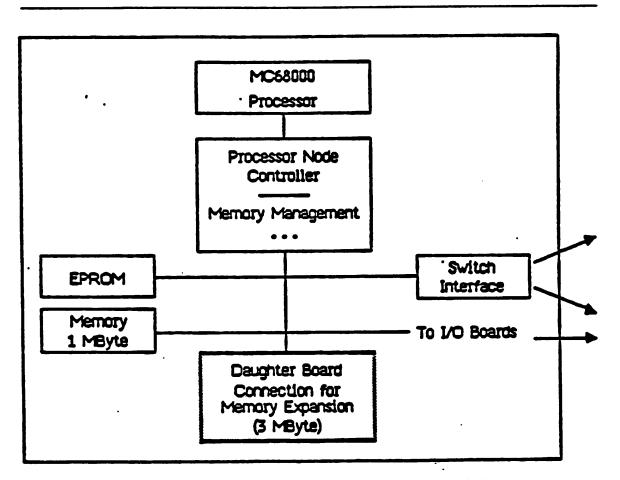

As mentioned in Chapter 1, there are circuit simulators, such as SPLICE and RELAX, that utilize a mix of direct and relaxation methods to solve the circuit equations. While subcircuits in a direct-relaxation scheme can be solved concurrently using relaxation [60], each of the subcircuit solutions itself is a direct-method solution and is not suited as well to parallel processing. Thus, a specialized subcircuit solver to perform the direct-method solution in parallel has been designed [17] and is discussed briefly below.

The special-purpose subcircuit solver is a five-way parallel processor operating in pipelined mode on independent instruction streams, with 512k bytes of local memory and a 128-bit datapath to memory. The pipelined implementation here, as in MMAP, circumvents the need for branching due to dependencies. The 512k bytes of memory are shared between the 5 processors as well as the host processor, eliminating the need to transfer data after a subcircuit solution, while the wide datapath is designed to accommodate a (64bit) double-precision floating-point number in conjunction with a 32-bit pointer and a 32bit integer. This permits simultaneous processing on all three fields of the data, allowing the co-processor to step through a linked list while performing operations on matrix elements, which is useful when working with sparse matrices.

Although no results are published in [17], it is evident that the subcircuit solver exploits parallelism primarily during the model-evaluation phase. This is appropriate since subcircuits typically contain a small number of circuit nodes (less than 100) hence model evaluation dominates overall simulation time. However, this approach will not work efficiently for large circuits since then sparse linear-equation solution dominates overall simulation time.

## 2.2.3 – Multiprocessor Sparse Linear-Equation Solution

As stated early in Chapter 1, parallel processing is attractive as a technique to reduce circuit-simulation runtimes for large VLSI circuits. As shown in Section 2.2.2, a number of researchers have identified and successfully exploited the parallelism available in the model-evaluation phase of circuit simulation, but sparse linear-equation solution, which dominates simulation time for large circuits, continues to be difficult to parallelize. In this section, two techniques that utilize general-purpose multiprocessors to exploit the parallelism in sparse linear-equation solution are described.

## 2.2.3.1 - Parallel Linear-Equation Solution: Dynamic Pivot Ordering

On multiprocessor systems, it has been shown that Gaussian elimination can be efficiently parallelized when solving dense, large-scale linear systems [61] and that nested dissection techniques allow efficient parallel solution of well-ordered sparse linear systems [11]. However, circuit matrices, in addition to their extreme sparsity (three to four non-zero elements per row or column), have an *irregular* nature that makes most decomposition techniques, including nested dissection, difficult to use [57].

In [56] a parallel algorithm based on LU-decomposition, called Segmented Partial Pivoting (SPP), is implemented on the BBN Butterfly Parallel Processor as a first step towards parallelizing the solution of irregular, sparse linear systems. In the SPP algorithm, each processor is assigned a block of rows from the system matrix; for each column in the matrix, all the processors work within their assigned blocks to determine local pivot candidates and then to eliminate other non-zero elements in the column. Next, the processors compete to set a lock. The local pivot of the processor use the global pivot to eliminate their own local pivots. This process is repeated until the system matrix is triangular. Forward elimination is also performed in parallel, as is back substitution. These operations employ parallel multiplication (by matrix coefficients) and subtraction (from the right hand side) after an unknown has been solved for, as well as parallel solution (division) which is made possible by the sparsity of the matrix.

Experimental results using the SPP algorithm on the BBN Butterfly indicate a high speed-up using up to about ten processors, but no improvement beyond that. Further, the competitive global pivot-selection scheme results in a large number of fill-ins, indicating that even with the parallelism exploited parallel solution may not be faster than efficient uniprocessor linear-equation solution. This study thus leads to two conclusions: first, there is a relatively low degree of parallelism available in the parallel linear-equation solution for circuit matrices; secondly, schemes that attempt to exploit as much of the small parallelism inherent in this solution process may result in excessive fill-ins, thereby nullifying their advantage.

#### 2.2.3.2 – Linear-Equation Solution: Static Dependence Graphs

As shown in Section 2.2.3.1, significant cost is associated with allowing fill-ins during LU-decomposition for circuit matrices. Thus, even for parallel solutions, a scheme that attempts to minimize the number of fill-ins, such as the Markowitz criterion, is desirable. In [45] a task system represented by an acyclic directed graph is statically built *after* the matrix has been ordered to minimize fill-ins. The task graph is assembled representing *divide* and *update* operations as nodes, and inter-element dependences as arcs.

For a 400x400 microwave-amplifier sparse matrix of density 0.8%, simulations indicate that 100 processors could be kept busy 73% of the time for matrix triangulation and 33.8% of the time for back-substitution. The results also indicated that solution time decreases inversely with the number of processors for small numbers of processors (10-20% of the order of the matrix); however, as the number of processors increases the amount of parallelism in the matrix is unable to keep the processors busy and the time for triangulation is limited by D, the depth of the task graph (the number of tasks along the critical path of the graph). These results are noteworthy because they demonstrate that a significant amount of parallelism is available in sparse linear-equation solution using standard sparsity-directed ordering of the matrix. The Pivot Dependency Graph (PDG) scheme used in this dissertation, described in Chapters 4 and 5, is similar to the task graph scheme and provides insight into practical issues associated with implementing dependence-graph algorithms for sparse linear-equation solution.

## **2.3: Conclusions**

While different algorithmic techniques have proved more efficient than standard direct methods for the simulation of certain classes of circuits, direct-method simulators continue to be important. In the first section of this chapter a brief overview of direct-method simulation algorithms is provided. A number of hardware-based acceleration techniques, described in Section 2.2, have been studied towards reducing runtimes for direct-method simulation. All of these techniques, however, have been restricted to either *special-purpose hardware* or single phases of the direct-method algorithm. In this dissertation, parallel algorithms for direct-method circuit simulation are studied using general-purpose multiprocessors.

## **CHAPTER 3**

## PARALLELISM LIMITS IN CIRCUIT SIMULATION

Prior to parallelizing a particular technique for solving a problem, it is helpful to establish theoretical limits to the basic parallelism available in the problem. Theoretical limits can be determined by studying the realizable parallelism in the most-parallel algorithm known for the solution of the problem. If the theoretical study shows the mostparallel algorithm has poor potential for parallelism, all parallel algorithms are bound to perform poorly. Conversely, high theoretical parallelism limits, although not an assurance of good performance, indicate that further research into other algorithms may not be fruitless.

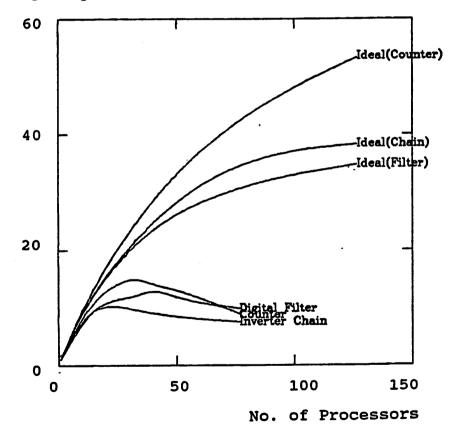

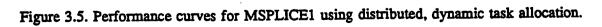

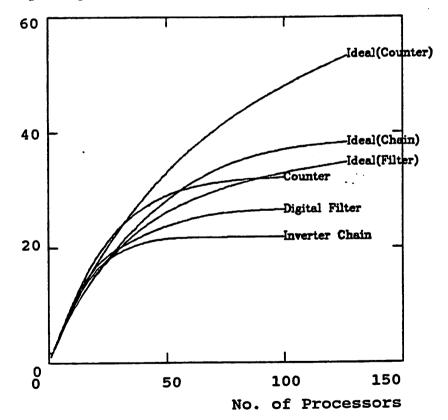

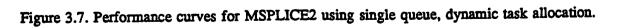

To determine a limit to parallelism in circuit simulation, a node-based relaxation circuit-simulation algorithm, MSPLICE, has been implemented [62, 63, 64] on the BBN Butterfly Parallel Processor [37]. Various scheduling and shared-memory storage schemes have been investigated using both the initial implementation of MSPLICE (MSPLICE1) as well as an improved implementation (MSPLICE2 [65]). Listings of MSPLICE1 and MSPLICE2 are provided in Appendices B and C respectively. While the initial implementation of MSPLICE described in [62] was developed for an early version of the Chrysalis Operating System [66], MSPLICE1, although using the same algorithms, is a modified version of MSPLICE designed to run on the Chrysalis 2.2 version of the Butterfly operating system [67]. Analysis of empirical data from the MSPLICE experiment described in this chapter verifies that circuit simulation is well-suited to parallel processing at the node-based (or fine-grained) level. This fact justifies further research into parallelizing general-purpose circuit simulators.

MSPLICE1 has been implemented on both the Digital VAX 11-780 and the BBN Butterfly machine. Only a 10-processor implementation of the Butterfly was available for initial MSPLICE1 development [62]. Further results using MSPLICE1 running on up to 78 processors are presented here. With such a large number of processors, additional insights into multiprocessor-based circuit simulation have been obtained and significant bottlenecks in MSPLICE1 have been removed in the new implementation, MSPLICE2. Further, a version of the Butterfly multiprocessor has been developed which supports up to 256 processors [67]. Consequently, the upgraded program, MSPLICE2, has the capability of utilizing up to 256 processors in parallel. MSPLICE2 results presented in this chapter are for the 101 processors of a 128-processor Butterfly system that were functional at the time benchmark studies were performed. In addition to the Ideal Gauss-Seidel Machine presented in [62], a new technique has been developed [68] to determine the maximum amount of latency available in the test circuits. Together, these meters provide a meaningful upper bound for measuring the parallel performance of MSPLICE with various benchmark circuits.

In Section 3.1, the motivation for selecting the MSPLICE algorithm to measure parallelism limits is provided. The Iterated Timing Analysis (ITA) and MSPLICE algorithms are reviewed in Section 3.2, while the Butterfly architecture and programming environment are described in Section 3.3 and the benchmark circuits used in this study are introduced in Section 3.4. An analysis of the parallel performance of MSPLICE1 on up to 78 processors is presented in Section 3.5. Based on MSPLICE1 performance, algorithmic modifications were made to create the program MSPLICE2, which circumvents bottlenecks identified in the original implementation. The modifications and results from the new implementation are described in Section 3.6, and the conclusions observed through the MSPLICE experiment are summarized in Section 3.7.

#### 3.1: Motivation for using MSPLICE as a measurement tool

For any parallel algorithm, there are a number of factors that determine the efficiency with which the algorithm will perform. The four most important factors are listed below:

(1) The amount of parallelism in the algorithm, i.e., the number of tasks that can be executed independently at any stage of the computation,

(2) The ratio of task computation time to intertask communication and synchronization time,

(3) The granularity of the tasks, i.e. the size of the smallest tasks, and

(4) Load balancing, or distribution of tasks between processors.

The selection of a node-based relaxation simulator has been made in light of these four factors and is described below.

The MSPLICE algorithm is well-suited to parallelization primarily because it uses relaxation which intrinsically provides a high degree of parallelism. Since a relaxation simulator decouples the circuit equations, it solves them *independently* of each other, iterating to ensure convergence to the correct solution. Thus, relaxation simulators provide an implicit partitioning of a problem into a number of independent tasks. This is important for parallel processing since each task can be executed on a separate processor, with no inter-processor communication or synchronization. Inter-processor communication degrades parallelization as it requires processors to synchronize with each other, thereby inhibiting uninterrupted program execution.

In addition to being node-based, the MSPLICE algorithm was also selected as a testbed to measure limits to parallel circuit simulation due to its node-based nature. A nodebased simulator intrinsically partitions a circuit into small and fairly uniform tasks, which results in efficient load balancing. *Load balancing*, the equal distribution of work across a number of processors, is best illustrated by the following analogy: given the job of placing either grains of sand or (larger) stones in a number of jars, the grains of sand provide for a more equitable weight distribution between the jars. Efficient load balancing is important for parallel processing as it ensures that all the processors finish their work at approximately the same time, thereby reducing time wasted at synchronization barriers.

Although it is node-based and uses relaxation, both qualities desirable for parallel processing, MSPLICE has not yet proven to be a generally applicable circuit-simulation algorithm. MSPLICE is used only to determine the *potential for parallelism* in circuit simulation, with the recognition that it may not always be efficient as a simulation algorithm.

#### **3.2:** Algorithms used in MSPLICE

MSPLICE is a parallel algorithm based on the *Iterated Timing Analysis* (ITA) [7] relaxation-based approach. The ITA method, described briefly in Section 3.2.1, is a successive-over-relaxation Newton method which uses event-driven analysis and selective-trace to exploit the temporal sparsity of the electrical network [7]. Because event-driven, selective trace techniques are employed, the algorithm lends itself to implementation on a data-driven computer. The MSPLICE worker algorithm that runs on each processor is

described below in Section 3.2.2.

### 3.2.1 – Iterated Timing Analysis (ITA)

The ITA method is a form of electrical analysis derived from timing simulation [7,69]. The starting point for a description of ITA is the electrical circuit equation formulation. A Nodal Analysis [47] formulation will be used to illustrate the ITA algorithms. The following assumptions are used:

- All resistive elements, including active devices, are characterized by constitutive equations where voltages are the controlling variables and currents are the controlled variables.

- All energy storage elements are two-terminal, possibly nonlinear, voltage-controlled capacitors.

- All independent voltage sources have one terminal connected to ground or can be transformed into independent current sources with the use of the Norton transformation.

In the nodal network equations there are N equations in N unknown node voltages. For the circuit N + 1 nodes are present, where node N+1 is the reference node, or ground. The equations can be written as:

$$C(v, u)\dot{v} = -f(v, u)$$

(2.1)

$$v(0) = V.$$

where  $v(t) \in \mathbb{R}^n$  is the vector of node voltages at time  $t, \dot{v}(t) \in \mathbb{R}^n$  is the vector of time derivatives of  $v(t), u(t) \in \mathbb{R}^n$  is the input vector at time  $t, C(\bullet) : \mathbb{R}^n \to \mathbb{R}^{n \times n}$  represents the nodal capacitance matrix,  $f : \mathbb{R}^n \times \mathbb{R}^n \to \mathbb{R}^n$ , and:

where

$$f_i(v(t), u(t))$$

is the sum of the currents charging the capacitors connected to node

*i*. The differential equations are converted to a set of nonlinear, algebraic difference equa-

tions using a stiffly stable integration formula to give:

$f(v(t), u(t)) = [f_1(v(t), u(t)), \cdots, f_N(v(t), u(t))]^T$

g(x) = 0 (2.2) where  $x \in \mathbb{R}^N$  is the vector of node voltages at time  $t_{n+1}$  and g() is the non-linear function. An iterative method, e.g., Gauss-Jacobi or Gauss-Seidel relaxation, is used to solve the equations. However, unlike timing analysis where a single relaxation iteration is used per time-point, in the ITA approach *the relaxation process is continued to convergence* at a time-point.

Only one Newton-Raphson iteration is used to approximate the solution of each nodal equation per relaxation iteration. Event-driven selective-trace techniques may still be used to exploit latency, as for timing simulation. Since in ITA the nonlinear circuit equations are solved by an iterative method until satisfactory convergence is achieved, the numerical properties of the integration methods used to discretize the circuit equations are retained. Thus, the stability and the accuracy problems typical of the timing simulation algorithms are not an issue here [42].

The following algorithm, written in "Pidgin 'C'" [70], illustrates the principle steps involved in ITA analysis, using a Gauss-Seidel iteration, for use on a conventional computer. At each time at which one or more nodes are scheduled to be processed, two event lists,  $E_k(t_n)$  and  $E_{k+1}(t_n)$  are used to separate the nodes to be processed in successive iterations, k and k + 1, of the Gauss-Seidel-Newton process.

39

```

Gauss-Seidel-Newton Iteration:

```

```

Put all nodes that are connected to independent sources in event list E_k(0);

t_n = 0;

while (t_n < TSTOP) {

k \leftarrow 0;

while (event list E_k(t_n) is not empty) {

foreach (i \text{ in } E_k(t_n)) {

v_i^{k+1} = v_i^k - \frac{g_i(\tilde{v}^{k+1,i})}{g_i'(\tilde{v}^{k+1,i})};

where \tilde{v}^{k+1,i} = [v_1^{k+1}, \cdots, v_i^{k+1}, v_{i+1}^k, \cdots, v_N^k]^T

if (|v_i^{k+1} - v_i^k| \le \varepsilon; i.e., \text{ convergence is achieved }) {

use LTE to determine the next time, t_i, for processing node i;

add node i to event list E_k(t_s);

} else {

add node i to event list E_{k+1}(t_n);

add fanout nodes of node i to event list E_k(t_n) if not already on E_k(t_n);

ł

}

E_k(t_n) \leftarrow E_{k+1}(t_n);

E_{k+1}(t_n) \leftarrow \text{empty};

k \leftarrow k + 1;

}

t_n \leftarrow t_{n+1};

where t_n is the present time for processing and t_{n+1} is the next time in the time queue at

which an event was scheduled. In this way, the "time-step" is handled independently for

each node. The foreach construct requires that the block be executed for each member of

```

the set in a specified order.

This simplified algorithm does not illustrate how such issues as time-step reduction and local truncation-error estimation are handled. These and other important details of the algorithm are described elsewhere [7]. While a nodal formulation was used to describe the approach, a Modified Nodal formulation [49] can also be derived.

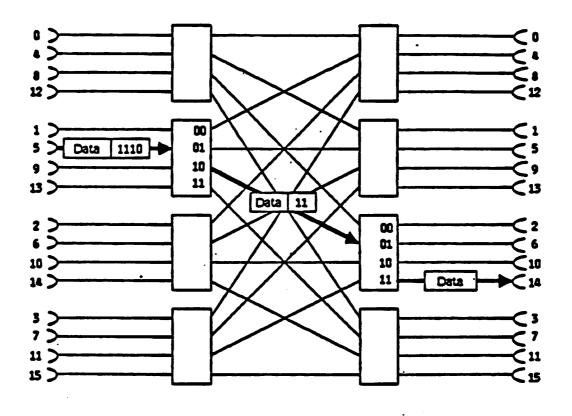

#### 3.2.2 – The MSPLICE Algorithm

MSPLICE uses the data partitioning approach to multiprocessing, where a number of processors perform identical functions on separate parts of the problem data. Nodes described using Nodal Analysis methods are statically stored in the memories of different processors. Typically, the number of nodes in the circuit greatly exceeds the number of processors in the multiprocessor system. Thus, a number of circuit nodes are allocated to each processor's memory. Having allocated data pertaining to particular nodes in the different processors, one can choose either of two approaches to task scheduling. A task is defined as the evaluation of a particular node voltage and is described below. In MSPLICE1, task scheduling can be done either statically, where a processor is responsible for evaluating voltages of all nodes that reside in its memory, or dynamically, where a processor is assigned a task when it becomes free. In the event of dynamic scheduling, which aids load balancing, a central scheduler can be used to distribute tasks to processors. This produces a serialization bottleneck. Instead, both the MSPLICE implementations, as described in Sections 3.5 and 3.6, use distributed schedulers, where each processor is responsible for its own scheduling.

In MSPLICE, a single global variable called *GlobalRemainingNets* is used to coordinate the processors at a given time point. It is incremented whenever a node is scheduled at a particular time point and is decremented when a node has finished being processed. When *GlobalRemainingNets* reaches zero, all processors move to the next time point of the simulation.

From the point of view of a single processor, P, once it has been allocated a set of electrical nodes, M, it proceeds as follows at time  $t_n$ :

41

```

foreach (node i in M scheduled at t_n) {