## Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# HIGH-FREQUENCY MONOLITHIC PHASE-LOCKED LOOPS

by

Mehmet Soyuer

Memorandum No. UCB/ERL M88/10

9 February 1988

## HIGH-FREQUENCY MONOLITHIC PHASE-LOCKED LOOPS

by

Mehmet Soyuer

Memorandum No. UCB/ERL M88/10

9 February 1988

## ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

#### Acknowledgements

I am very grateful to my research advisor, Professor Robert G. Meyer, for his guidance and support throughout this study. I would like to thank Signetics Inc., and William Mack for their help in fabricating the test chip. I would also like to acknowledge the valuable discussions with my friendly colleague Ting-Ping Liu, and with my fellow graduate students.

I appreciate the opportunity and the financial support given to me by the Scientific and Technical Research Council of Turkey to study abroad. This research was also supported by the U.S. ARO under Grant DAAL03-87-K-0079.

Finally, I wish to express my deep appreciation to my parents, and to my wife, Deniz, for their love and patience. My son, Ege, made my last year in Berkeley even more enjoyable.

### **Table of Contents**

| CHAPTER 1  | INTRODUCTION                                      | 1   |

|------------|---------------------------------------------------|-----|

| CHAPTER 2  | PLL DESIGN PARAMETERS                             | 4   |

|            | 2.1 Introduction                                  | 4   |

|            | 2.2 Static Phase Error                            | 6   |

|            | 2.3 Dynamic Phase Error                           | 7   |

|            | 2.4 Pull-In Range                                 | 8   |

|            | 2.5 Noise Bandwith                                | 11  |

|            | 2.6 Stability                                     | 13  |

| CHAPTER 3  | VOLTAGE CONTROLLED OSCILLATORS                    | 17  |

|            | 3.1 Introduction                                  | 17  |

|            | 3.2 Negative Resistance and Frequency Limitations | 19  |

|            | 3.3 Varactor Design                               | 26  |

|            | 3.4 VCO Design                                    | 32  |

|            | 3.5 Loop Amplifier and Bandgap Reference          | 40  |

| CHAPTER 4  | PHASE DETECTORS                                   | 45  |

|            | 4.1 Introduction                                  | 45  |

|            | 4.2 Analog Phase Detectors                        | 47  |

|            | 4.3 Digital Phase Detectors                       | 55  |

|            | 4.4 Non-Phase Sensitive Effects                   | 59  |

| CHAPTER 5  | MEASURED RESULTS AND DISCUSSION                   | 63  |

|            | 5.1 Introduction                                  | 63  |

|            | 5.2 Varactor Measurements                         | 65  |

|            | 5.3 Open-Loop PLL Measurements                    | 70  |

|            | 5.4 Closed-Loop PLL Measurements                  | 76  |

|            | 5.5 Discussion                                    | 77  |

| CHAPTER 6  | CONCLUSIONS                                       | 81  |

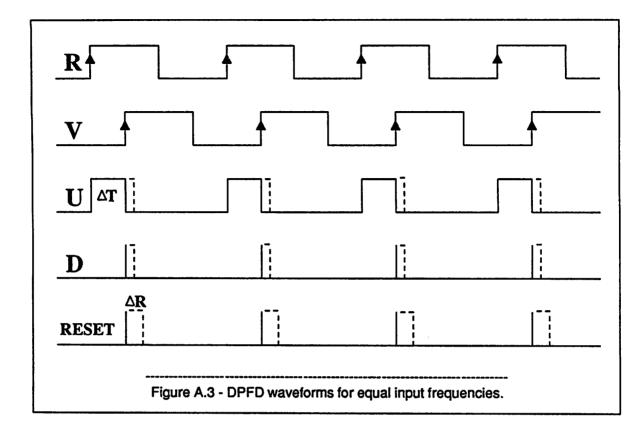

| APPENDIX A | ANALYSIS OF A DIGITAL PHASE-FREQUENCY DETECTOR    | 83  |

| APPENDIX B | A DIGITAL ROTATIONAL-FREQUENCY DETECTOR DESIGN    | 92  |

| REFERENCES |                                                   | 100 |

1

#### High-Frequency Monolithic Phase-Locked Loops

Ph.D.

Mehmet Soyuer

Department of EECS

(Prof. Robert G. Meyer)

Committee Chairman

#### **ABSTRACT**

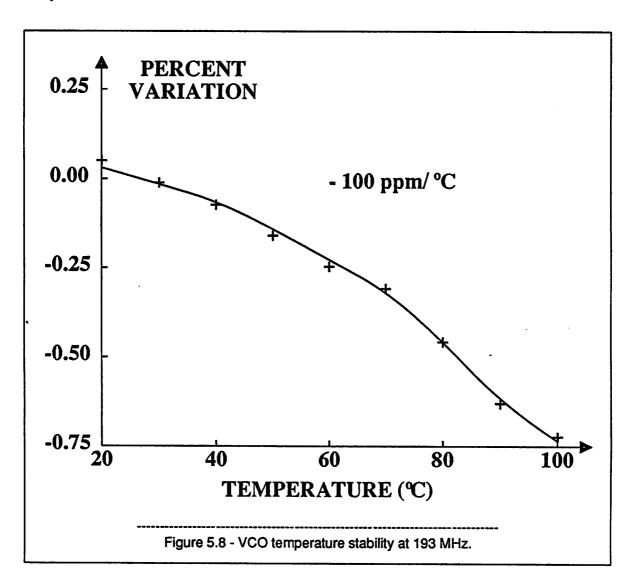

This thesis describes research concerned with the design and realization of monolithic phase-locked loops (PLLs) at frequencies of 100 MHz and above using silicon bipolar technology. Several types of oscillators and phase detectors have been simulated and their performances compared with a special interest in narrowband filtering applications. Varactor-tuned LC-oscillators are preferred at frequencies above 100 MHz since they have low jitter and small temperature coefficient (TC). Analog phase detectors have been shown to perform better than digital phase detectors at these frequencies. Analysis and simulations showed that it was feasible to implement a monolithic PLL above 500 MHz using analog circuit design techniques and a 10-GHz bipolar process.

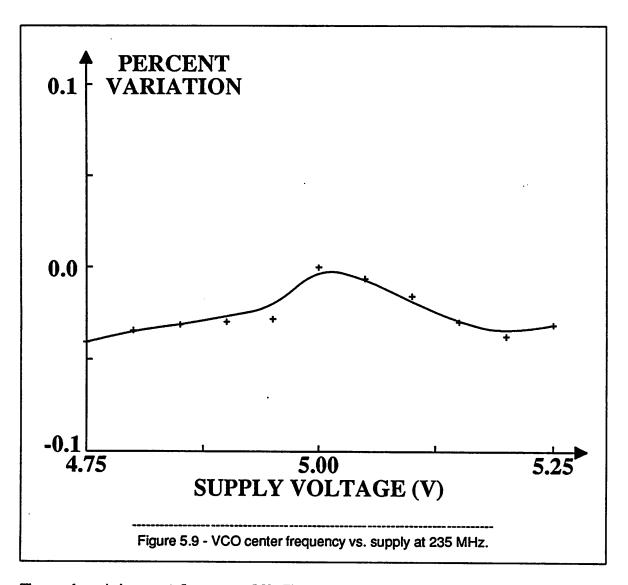

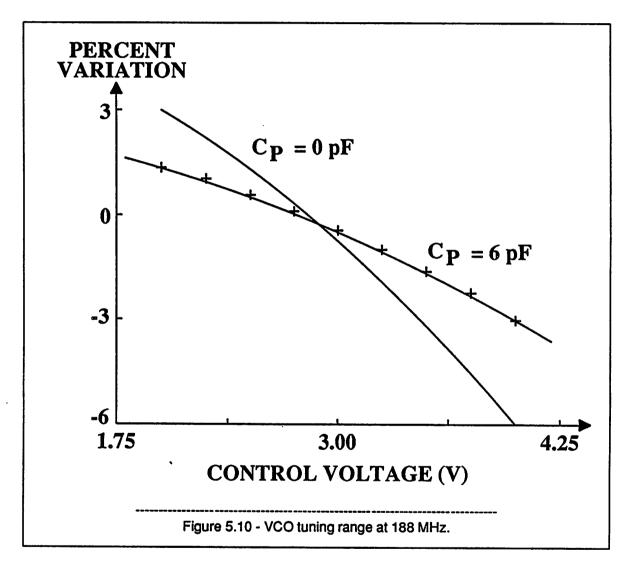

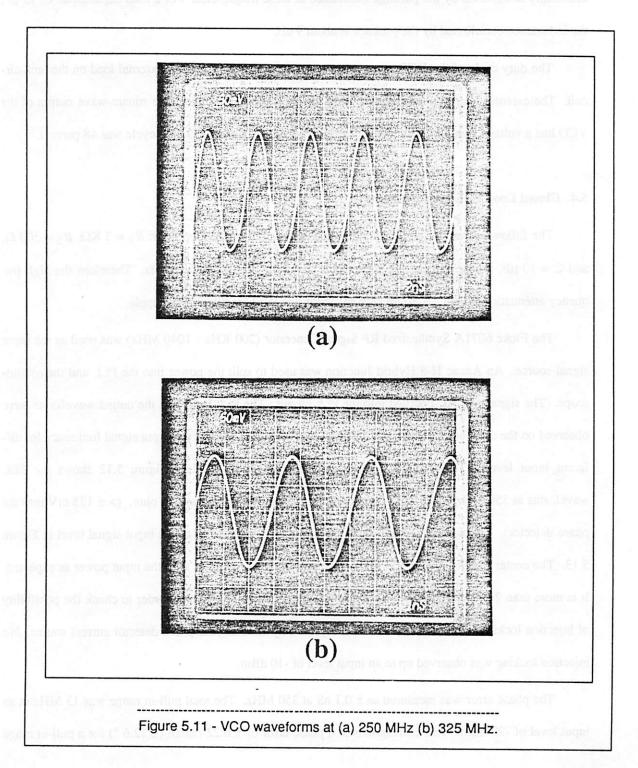

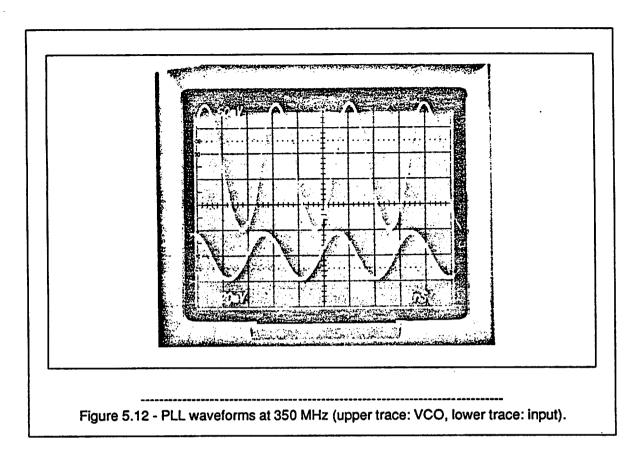

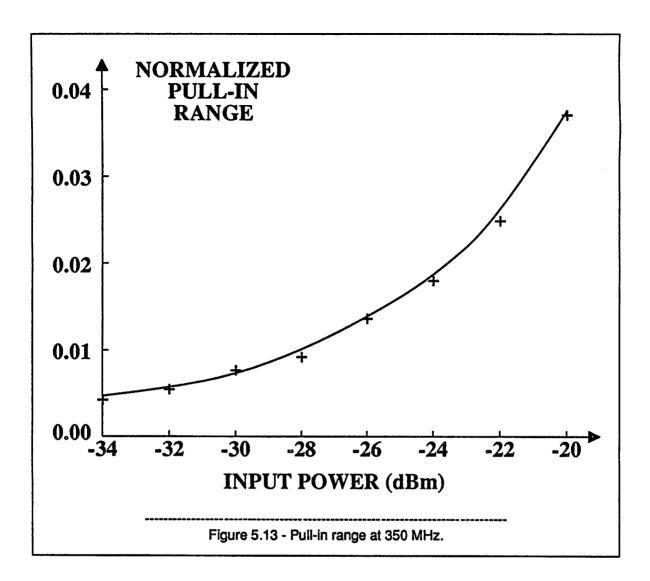

A 2-micron oxide-isolated bipolar process was used to fabricate a monolithic PLL test circuit. A varactor-tuned VCO and an analog phase detector have been utilized as building blocks. An on-chip varactor diode has been designed using the junctions available in the bipolar process with temperature and supply compensation provided by a band-gap reference. There is a good correlation between the measurements and the simulation results. The VCO has a voltage coefficient of 0.3 percent/volt and a TC of -100 ppm/°C over 20 to 100°C up to 250 MHz. When housed in a 40-pin DIL package, the maximum VCO center-frequency was 350 MHz, and the PLL pull-in range was larger than ±1 percent. The monolithic PLL circuit has the potential to be used as a narrowband filter (Q > 100) at 500 MHz with an optimum package.

#### **CHAPTER 1**

#### INTRODUCTION

Phase Locked Loop (PLL) circuits are widely used in various communications and control systems applications, including frequency synthesis, clock signal (timing) recovery, modulation and demodulation of signals. As the frequency of interest goes higher, (e.g., cable and fiber optic data links), there is a greater need for monolithic circuits that can operate at these frequencies. Several technologies are possible candidates for operating frequencies into the GHz range and beyond. Silicon bipolar, [1]-[6], and NMOS, [7], as well as GaAs MESFET, [8]-[9], and heterojunction bipolar, [10], technologies are among the contenders. As the ultra-high frequency VLSI technologies become available, there is a strong motivation to include several subsystems on the same chip. However, the maximum operating range of most currently available monolithic PLL circuits is limited to frequencies below 150 MHz, [11]-[16]. Therefore, this research is concerned with the realization of monolithic PLLs above 100 MHz using high-frequency silicon bipolar technology. Silicon bipolar, being the most mature high-frequency technology, offers higher speed and larger transconductance through its exponential nonlinearity and smaller offsets through its well-controlled thermal voltage,  $\frac{kT}{q}$ . A balanced analog circuit topology similar to Emitter Coupled Logic (ECL) in digital circuits is a good choice throughout the design for optimum speed and matching. Although, higher speed means more power dissipation in general, [17]-[21], the circuits should be able to operate with a single 5 V supply to keep the power consumption low.

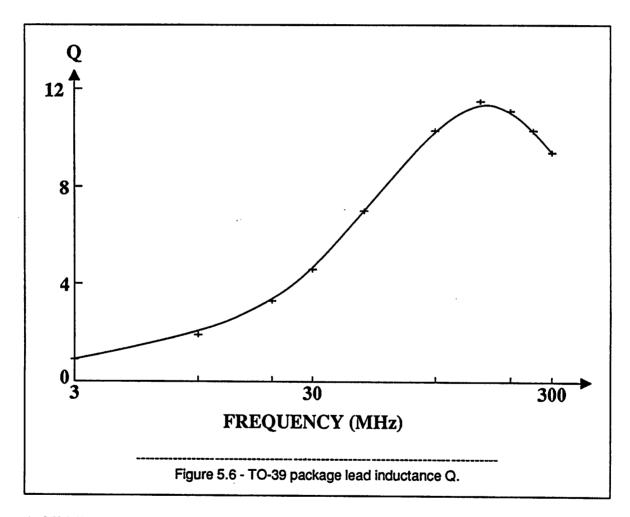

At high-frequencies, good isolation is hard to achieve and parasitic losses cannot be ignored. Therefore, the package performance has to be considered together with the inherent device limitations, [22]-[23]. Especially, inductive parasitics and coupling can deteriorate the high-frequency performance. Another common isolation problem is the unwanted coupling between the capacitive paths (crosstalk) which becomes worse as the frequency of operation increases. The silicon substrate is also susceptible to resistive coupling since it is a poor insulator. At very high-frequencies, skin-effect becomes significant

and that increases the resistive losses. Therefore, the quality factors of energy storage elements are degraded. Careful circuit design, layout and packaging can be used to circumvent some of these problems. It may be helpful to model the critical components in the high-frequency path as distributed RC-sections or lossy transmission lines. Applying a high-frequency signal or delivering it out may become easier if the reflections are minimized by using proper terminations.

There are several outputs available from a PLL which can be useful depending on the application. In demodulation of the FM signals, the loop filter output provides the modulating signal. In timing recovery applications, the VCO-output waveform is used as the recovered clock signal and the ultimate goal is to minimize the phase error between the input signal and the VCO and at the same time to filter out the noise components. In general, PLL itself must contribute much less noise than is present at its input. To minimize the jitter (dynamic phase error) caused by the input noise, the loop bandwith must be made very small compared to the input frequency. This, in turn, reduces the pull-in range available from the loop. The VCO center-frequency drift is one of the main contributors to the static phase error together with the dc-offsets in the phase detector and loop amplifier. Therefore, it should be minimized against temperature and supply variations. When used as a narrowband filter as in timing-recovery applications, a PLL with a stable VCO requires a relatively narrower pull-in range and this makes the filter design easier. Also, a high-frequency crystal is not required if the VCO can be compensated for temperature and supply variations. Although this design approach involves a trade-off between different PLL parameters, most significantly between pull-in range and noise bandwith, it is relatively easy to implement such a PLL without any extra circuitry for frequency acquisition. Furthermore, it is possible to minimize the noise contribution of the PLL by employing a VCO with a small noise bandwith. Since relaxation oscillators have large noise bandwith and jitter, [24], small noise bandwith requirement dictates the use of harmonic oscillators in which one of the tank circuit reactances or the phase shift through the active element is variable.

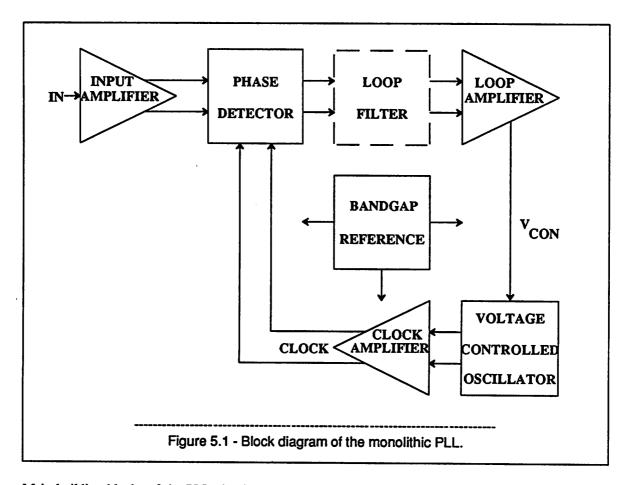

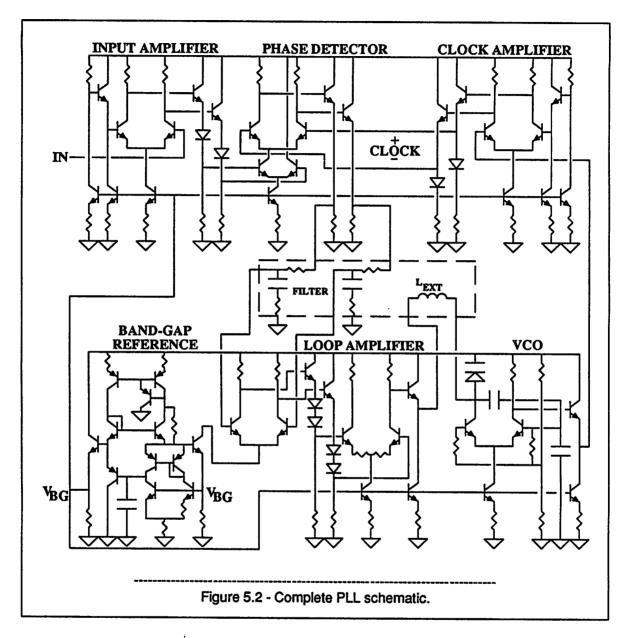

The main purpose of this research is to investigate the frequency limitations of main PLL components with a special interest in timing recovery applications, and then to use integrated circuit design types of PLL building blocks are designed. Their performances are compared by extensive computer simulations. Digital as well as analog phase detectors are considered. In the monolithic implementation of the test circuits, an on-chip varactor diode is used to control the VCO frequency. Its quality factor is optimized by minimizing the resistance-capacitance product per area. The VCO stability is achieved by canceling the temperature dependence of the varactor diode capacitance to a first order approximation. For this purpose, a conventional band gap reference is used to derive the loop amplifier bias currents so that the reverse bias across the diode has a positive temperature coefficient which opposes the temperature coefficient of the built-in potential and dielectric constant of silicon. In this way, it is also possible to take the contribution of the phase detector and amplifier offsets to the VCO control voltage into account. An analog phase detector and input/output amplifiers complete the test circuit.

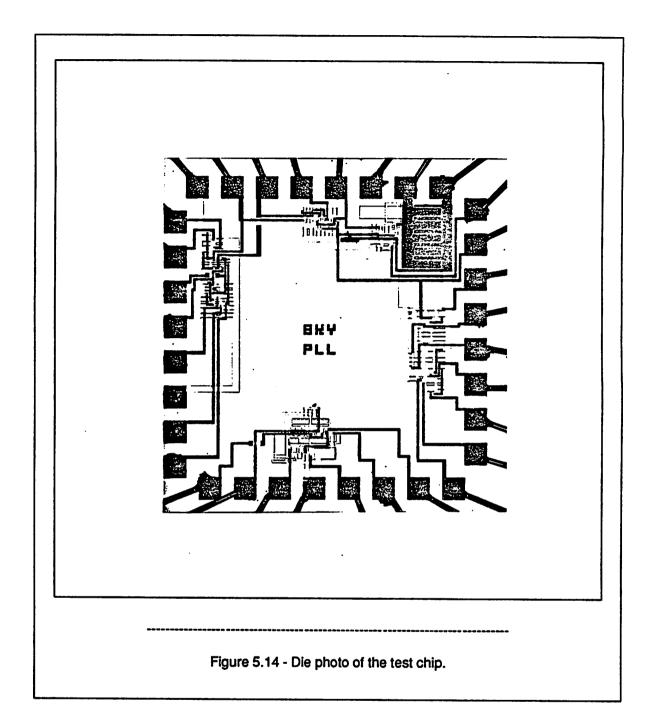

Chapter 2 gives an overview of the PLL parameters involved in a high-gain second-order loop design. The central question of how to design a stable high-frequency PLL with small phase error and noise bandwith and with large pull-in range is tried to be answered in that chapter. The importance of high-gain second-order loops is emphasized. Alternative approaches are also included. The main building blocks of the PLL are discussed in Chapters 3 and 4. An initial comparison is made among different possible topologies and their frequency limitations are assessed. The optimization procedure for each block and crucial component is described in detail. The design techniques used to improve the circuit performance are given in these chapters. In Chapter 5, measurement results for open loop and closed loop operation are presented for a 2-micron oxide-isolated bipolar technology. Possible improvements are also suggested. It is shown that the frequencies above 300 MHz are easily achieved with an on-chipvaractor controlled oscillator and an analog phase detector even when the circuit is housed in a 40-pin DIL-package. The circuit contains less than a hundred active devices and occupies an area of 0.5 mm<sup>2</sup>. It dissipates 270 mW with a single 5 V supply and can be integrated into a larger subsystem.

#### **CHAPTER 2**

### **PLL DESIGN PARAMETERS**

#### 2.1. Introduction

There are several books, [25]-[29], and many papers, [30]-[33], written on the theory of phase-locked loops. Their integrated circuit implementations are also covered in different books, [34, ch. 10]-[35, ch. 12]. In this chapter, an overview of the PLL theory will be given and its important design parameters will be discussed.

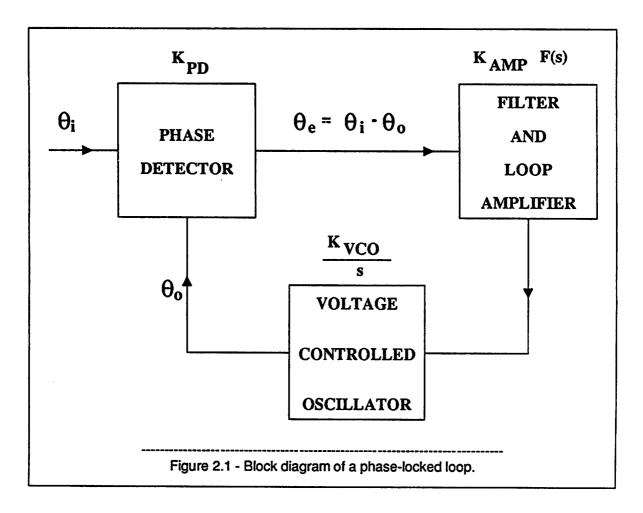

A PLL circuit is essentially a negative feedback control system, Figure 2.1.

The frequency of the voltage-controlled oscillator (VCO) is controlled by the phase detector output through the feedback loop and is made equal to the frequency of the input signal with a phase difference. There are two main regions of operation during the frequency and phase capturing process. Initially, the two frequencies are not equal and the circuit operates in a non-linear fashion. If the initial frequency difference is small enough, the negative feedback loop pulls the VCO frequency close to the input frequency until they become equal. This is the second region of operation or the quasi-linear mode. Assuming linear mode of operation, one can assign gain constants to each of the PLL building blocks. Hence,  $K_{PD}$  is the phase detector gain in volts per radian,  $K_{VCO}$  is the VCO gain in radians/second per volt, and  $K_{AMP}$  is the loop amplifier gain. If the loop filter has the transfer function F(s), the DC-loop gain is defined as:

$$K_{DC} = K_{PD} K_{VCO} K_{AMP} F(0)$$

(2.1.1)

$K_{DC}$  has the dimensions of radians per second similar to an inverse RC-time constant, and it is an important parameter of the PLL. Together with the loop filter time constants, the DC-loop gain determines the dynamic properties of the PLL.

The range of frequencies that an initially unlocked PLL can lock onto is called the pull-in (also capture or frequency acquisition) range,  $\Delta\omega_P$ . The range of frequencies which a locked PLL can hold onto is called the hold-in (also hold or lock) range,  $\Delta\omega_H$ . In principle, the hold-in range is greater than or equal to the DC-loop gain and is always larger than the pull-in range. In practice, it is usually limited by the saturation of the loop amplifier for a high-gain loop.

Since VCO essentially performs an integration on frequency, the PLL transfer function has a pole at the origin even without any loop filter, and therefore it is called a first-order PLL. In order to obtain a second-order PLL, a loop filter with a single pole is necessary. An ideal integrator in the loop filter would provide an infinite DC-loop gain.

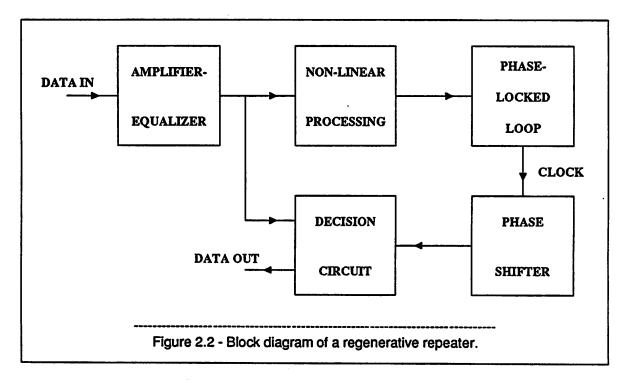

A typical application of a PLL as a narrowband filter would be as the timing-recovery filter in a regenerative repeater, as shown in Figure 2.2. If a discrete line at the clock frequency is not present in the input spectrum, non-linear processing must be performed before filtering. The recovered clock can

be used in the decision circuit. The statistical properties of timing jitter in regenerative digital transmission is extensively analyzed in the literature, [36]-[43].

For most applications, it is necessary to build a high-gain second-order PLL. In the following sections, the reasons behind this necessity will be investigated.

#### 2.2. Static Phase Error

Depending on the phase detector type used, there is a constant phase difference, usually 0, 90 or 180 degrees, between the input and the VCO under locked conditions. This phase difference is not a phase error and it may be called as the stable operating point of the PLL. However, unless ideal (hence unrealizable) building blocks are used, there will always be another component of phase difference between the input and the VCO. This component is termed as the phase error.

The phase error has two parts, a static part and a dynamic part (jitter), [36]. The static phase error is given by:

$$\Theta_e = \frac{V_{OS}}{K_{PD}} + \frac{\Delta\omega}{K_{DC}} \tag{2.2.1}$$

where  $V_{OS}$  is the combined offset voltages of the phase detector and loop amplifier and  $\Delta\omega$  is the initial frequency difference between the input and the VCO. This component actually can be termed as the quasi-static phase error since all the terms in the equation above are temperature and supply dependent. As it can be seen, a high-gain PLL with a stable VCO and small DC-offsets is necessary to minimize the static phase error.

#### 2.3. Dynamic Phase Error

There are two main sources of jitter, the first one is external to the PLL (input noise) and the second one is internal (PLL noise). Input noise may contain a white noise component, and a pattern dependent noise component if a random data signal is present at the input. To filter out the noise components, a loop filter must follow the phase detector. Therefore, only a high-gain second-order PLL is useful as a narrowband filter. Higher order loops suffer from the stability problems. PLL noise is mainly due to the VCO phase noise, [25, ch. 6].

Assuming that the pattern dependent noise dominates the additive noise at the PLL input, and that the VCO phase noise is negligible, dynamic component of the phase error can be expressed as:

$$\overline{\Delta\Theta_{\epsilon}^2} = a \frac{\Theta_{\epsilon}^2}{Q_{PII}} + b \frac{1}{Q_{PII}}$$

(2.3.1)

where  $\overline{\Delta\Theta_e^2}$  is the total mean-square value of the jitter at the PLL output with regard to the nominal input phase, "a" represents the amplitude effects of the random data, "b" represents the phase effects of the random data, and  $Q_{PLL}$  is the quality factor of the PLL, [36]. For a given random data pattern, numerical integration techniques are usually necessary to estimate the PLL jitter, [40]-[41], [44].

If a pilot tone is transmitted for clock recovery, then the variance of the VCO output phase due to the input noise can be expressed as:

$$\overline{\Delta\Theta_o^2} = \frac{W_i B_L}{P_r} \tag{2.3.2}$$

where  $P_s$  is the input signal power in watts and  $W_i$  is the noise power spectral density in watts/Hz, [25,

ch. 3]. Accordingly, for a given PLL output jitter,  $B_L$  must be minimized to account for the worst case, i.e. the lowest, level of the pilot tone.

Similar to an LC-filter, the quality factor of the PLL is given by:

$$Q_{PLL} = \frac{\pi}{4} \frac{f_C}{B_I} \tag{2.3.3}$$

where  $f_C$  is the input clock frequency and  $B_L$  is the noise bandwith of the PLL, [36]. For equal number of poles and zeroes in the loop filter, the noise bandwith can be approximated as:

$$B_L \approx \frac{1}{4} K_{DC} \frac{F(\infty)}{F(0)} \tag{2.3.4}$$

where  $F(\infty)$  is the value of the loop filter transfer function at very high frequencies, [25, ch. 3].

A significant advantage of the PLL-filter over the passive filters is that static and dynamic phase errors can be minimized independently. Again, a second-order high-gain PLL is required for this purpose. The DC-loop gain must be increased to minimize the static phase error, and the loop filter attenuation must be increased to minimize the dynamic phase error. Implications of this on the pull-in range will be discussed in the next section.

#### 2.4. Pull-In Range

Self-acquisition of frequency is called pull-in or capture. Due to the non-linear time-varying nature of the PLL-system during frequency acquisition, an analytical solution for pull-in is only possible for the first-order loop, [45]. Qualitatively, the VCO frequency is frequency modulated by the difference frequency, also called the beat note, during the capture process. Therefore, the phase detector output has a non-zero DC-average which enables pull-in to occur. If the DC-average is large enough compared to the undesired DC-offsets, negative feedback will pull the VCO frequency toward the input frequency.

Pull-in behavior is a strong function of the DC-loop gain, loop filter time constants and the type of the phase detector used. In the following discussion, a high-gain loop with a single-pole single-zero filter and a multiplier type phase detector is assumed. Second and higher order loops are best analyzed with the help of a computer, [46]. An approximate analysis yields the following result for a second-order loop, [25, ch. 5]:

$$\Delta \omega_P \approx K_{DC} \sqrt{2 \frac{F(\infty)}{F(0)}}$$

(2.4.1)

A sinusoidal-multiplier is assumed for the phase detector. However, when combined with a high-gain amplifier, saturation effects may result in a trapezoidal or even a binary phase detector. The latter case is analyzed by J. F. Oberst, [47], and the end result for a passive lag-lead filter is:

$$\Delta\omega_{P} \approx 2 K_{DC} \sqrt{\frac{F(\infty)}{F(0)}}$$

(2.4.2)

Therefore, the binary type phase comparator improves the pull-in range by a factor of  $\sqrt{2}$ . In practice, the pull-in range may be assumed between these two limits.

The next question is how large a pull-in range is required. Obviously, it should be large enough to cover any initial VCO frequency offset. Therefore, one needs:

$$\Delta \omega_P \ge K_{DC} \Theta_e \tag{2.4.3}$$

In theory, an active filter would provide almost an infinitely large pull-in range, since it has a pole close to the origin. In practice, however, offset voltages in the phase detector and the loop amplifier will be integrated until the amplifier is saturated driving the VCO outside the capture range. Therefore, either external frequency acquisition or DC-feedback around the amplifier is necessary. Charge pump circuits can also be used for the same purpose, [48]. They do not require an amplifier to provide a pole at the origin. But usually they require complementary devices, and therefore they are limited in frequency, [13].

Comparing the equations for the pull-in range with the noise bandwith equation, it can be seen that they cannot be optimized independently. Therefore, either a compromise must be made in the loop filter design or the frequency acquisition capability of the PLL must be improved. Although the first approach is actually implemented in this study, it is worth mentioning some of the alternatives to realize the second approach.

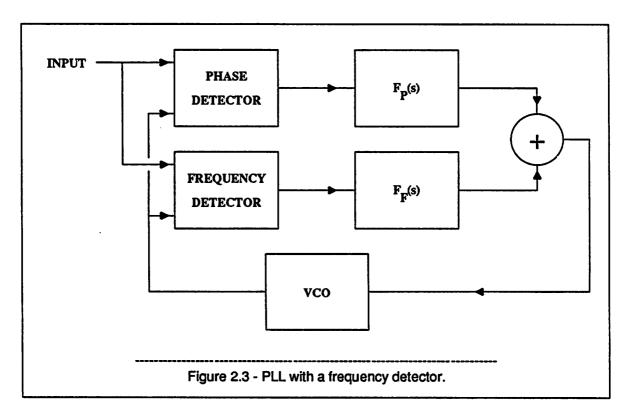

The frequency acquisition can be aided by an additional frequency detector, [2], [13], [14], [21], [45], [49]-[52], by frequency sweeping, [25, ch. 5], by bandwith switching, [53]-[54], or by injection locking, [55]-[57]. Frequency detectors can have analog, [2], [14], [45], [49]-[50], or digital [13], [21], [51]-[52], implementations. A typical block diagram for a PLL with a frequency detector is shown in Figure 2.3.

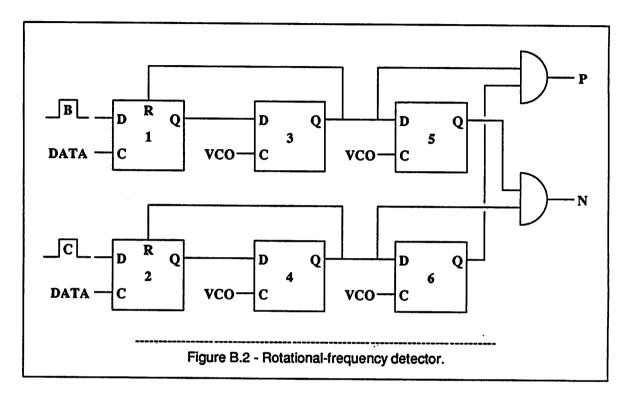

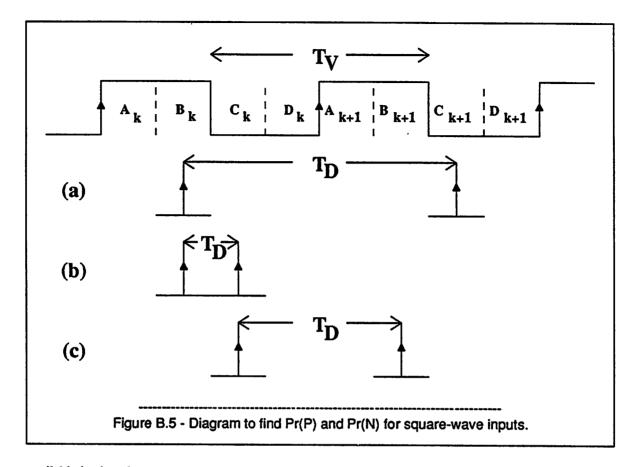

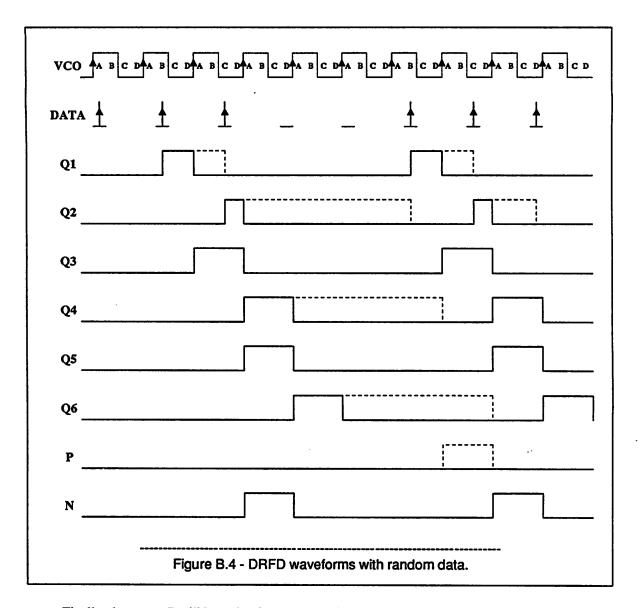

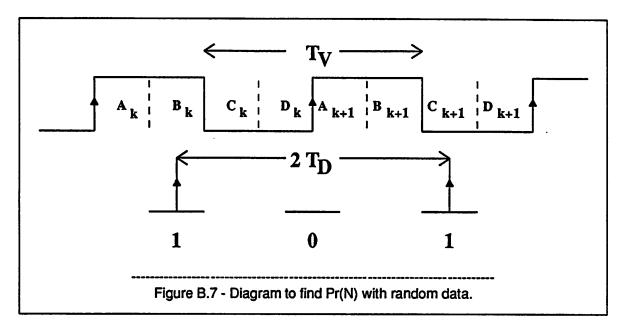

In some cases, both the frequency and the phase detector may share the same filter. Actually, almost all the digital phase detectors with memory, i.e. sequential type phase detectors, can also provide frequency capability, [58]-[62]. This topic will further be discussed in Chapter 4 and Appendix A. A digital frequency detector design example using the rotational frequency detector concept, [51], is given in Appendix B. In analog implementations, the extra circuitry may include multipliers, filters and differentiators, [14], [49]-[50], and/or limiters, phase shifters and monostable multivibrators, [2]. Frequency sweeping can be achieved by introducing a constant current into the loop filter. Then, the control voltage is a ramp that sweeps the VCO frequency. Bandwith can be changed by gain switching either in the phase detector or the loop amplifier, or by switching the filter resistors. If the phase detector gain is proportional to the

signal level, automatic gain control circuits may replace the switches. Finally, signal injection into the VCO can improve pull-in behavior if carefully controlled. Injection is always present in any practical circuit especially at high frequencies due to poor isolation.

All these methods require extra circuitry and may degrade the PLL frequency performance. They also require more power consumption and larger chip area. In addition, switching noise from the digital circuits may create problems for the analog parts of the PLL. Therefore, the best strategy for the high frequencies seems to be that one should keep the circuits simple enough so that they can easily be implemented.

#### 2.5. Noise Bandwith

It is already shown that reducing the noise bandwith is essential to minimize the jitter. However, the VCO phase noise puts a theoretical lower limit on the noise bandwith that can be achieved. To generalize, internal noise always puts an upper limit on the quality factor of any narrowband filter. For example, let us take the case of a PLL with a varactor-tuned LC-type VCO. In this case, the PLL noise bandwith has to be larger than the VCO noise bandwith.

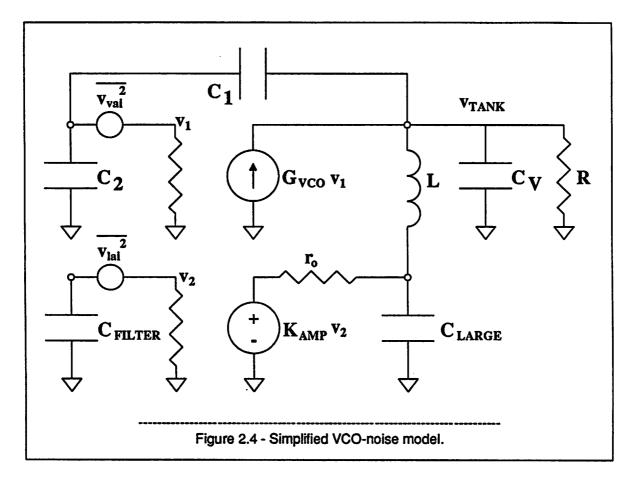

In order to obtain some numerical values, the simplified model shown in Figure 2.4 will be used for the varactor-tuned VCO circuit. Assume that the only internal noise sources are the loop amplifier that generates the control voltage, and the amplifier stage employed within the VCO. First, let us try to estimate and compare the relative contribution of each amplifier to the tank circuit noise. To simplify the problem, one can break the positive feedback loop around the VCO, and also assume that the loop amplifier is band limited to  $B_{LA}$  by the bypass capacitor,  $C_{LARGE}$ . Let  $B_{TANK}$  be defined as the tank-circuit bandwith. Then, following a similar analysis as in Section 11.4 of Gray and Meyer, [34], one can show that:

$$\frac{v_{va}}{v_{la}} \approx \sqrt{\frac{W_{va}}{W_{la}}} \frac{B_{TANK}}{B_{LA}} \tag{2.5.1}$$

where  $v_{va}$  and  $v_{la}$  are the rms-voltages across the tank circuit resulting from the VCO and loop amplifier,

respectively.  $W_{va}$  is the noise power density of the VCO amplifier output at the high frequencies, and  $W_{la}$  is the noise power density of the loop amplifier output at the low frequencies. For  $W_{la} = 20W_{va}$ , and  $B_{TANK} = 10B_{LA}$ ,  $v_{la}$  is three times larger than  $v_{vco}$ . It should be mentioned that this analysis is oversimplified since the non-linear effects and the flicker noise components are neglected.

Next, we close the positive feedback loop around the VCO-gain stage. According to Edson [63, ch. 15], the VCO noise bandwith due to the thermal noise in the load resistor is:

$$B_{VCO} = 2\pi kT \frac{K_o^2 f_o^2}{P Q^2}$$

(2.5.2)

where  $K_o$  is the amplification at the nominal operating frequency  $f_o$ , P is the power dissipated across the load, and Q is the tank circuit quality factor. For  $K_o = 10$ ,  $f_o = 300$  MHz, P = 0.04 mW, and Q = 10,  $B_{VCO}$  is 58.7 Hz. However, when the noise from the amplifiers included,  $B_{VCO}$  will increase considerably since the noise bandwith is proportional to the noise density, [64, ch. 1]. Assuming that the noise density

increases by a factor of 400, a very rough upper limit for  $Q_{PLL}$  will be about  $10^4$  with the values assumed above.

Obviously this value is very optimistic. As it was discussed in the preceding section, the pull-in range requirements would put stringer limits on  $Q_{PLL}$ . For example, if the pull-in range is one percent of  $f_o$  and the loop filter attenuation is ten percent, then from equations (2.3.3)-(2.4.1),  $Q_{PLL}$  turns out to be 225.

Typical Q values for different narrowband filters are less than 80 for LC-filters, [65, ch. 10], between 80 to 500 for PLLs, [5], [37], 500 to 1000 for SAW-filters, [66], and more than 1000 for dielectric resonator filters, [67], and for PLLs with crystal VCOs, [4], [68]. Reference [66] also provides a good comparison between the PLLs and SAW-filters. PLLs have less loss and better bandwith control, and they do not require a special substrate. But they are relatively difficult to implement at high-frequencies. In digital PCM transmission link repeaters, a Q of 200 to 250 is considered to be adequate to control the jitter down to 0.1 radian, [5], [37]. However, in general, jitter is a strong function of the coding of the random data as mentioned previously.

Another limitation that arises from employing a narrowband filter is the large pull-in time. For a high-gain PLL, the pull-in time is proportional to the square of the initial frequency difference, and inversely proportional to the cube of the noise bandwith, [25, ch. 5]. Therefore, for one percent pull-in range at 300 MHz and a pull-in time less than a millisecond,  $Q_{PLL}$  must be less than 1100. Consequently, PLLs with crystal-VCOs have longer pull-in times. Pull-in time can be reduced by several orders of magnitude by inserting an antiparallel diode pair between the phase detector and the loop filter, [69].

#### 2.6. Stability

Stability of the PLL in locked condition can be analyzed using the Laplace Transform and the Bode plots. Referring to Figure 2.1, the open-loop gain of a PLL can be written as:

$$G(s) = K_{PD} K_{AMP} - \frac{K_{VCO}}{s} F(s)$$

(2.6.1)

Then the closed-loop transfer function is:

$$H(s) = \frac{\Theta_o}{\Theta_i} = \frac{K_{PD}K_{AMP}K_{VCO}F(s)}{s + K_{PD}K_{AMP}K_{VCO}F(s)}$$

(2.6.2)

Therefore, a high-gain second-order loop performs a low pass filtering operation on phase inputs.

Any extra delay in the loop also creates poles that must be included in the stability analysis. Usually, the ripple filter used to minimize the phase detector output ripple and/or the limited bandwith of the loop-amplifier introduces a non-negligible pole which is smaller than the DC-loop gain.

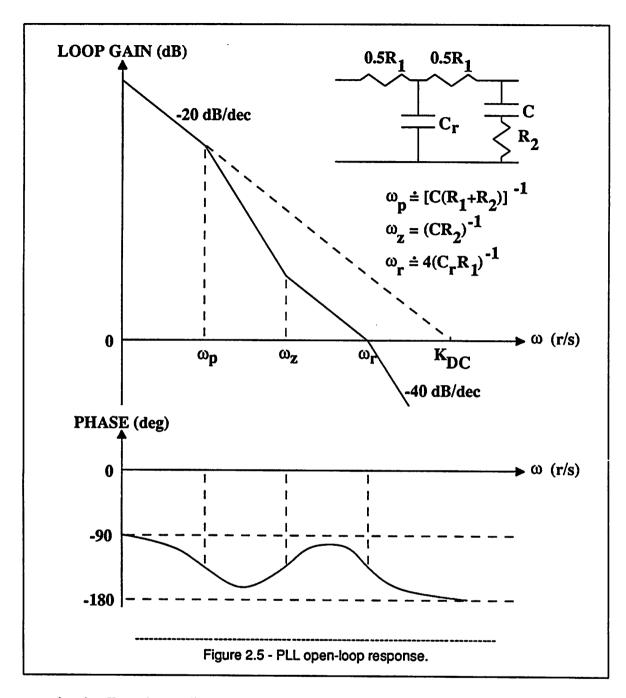

A typical Bode plot of a second-order loop with a ripple filter is shown in Figure 2.5.  $C_r$  is the ripple filter capacitor. The loop filter transfer function including the ripple filter can be written as:

$$F(j\omega) = \frac{1 + j - \frac{\omega}{\omega_{zero}}}{1 + j - \frac{\omega}{\omega_{pole}}} \frac{1}{1 + j - \frac{\omega}{\omega_{ripple}}}$$

(2.6.3)

Strictly speaking, the loop is third order now, but choosing the ripple filter pole large compared to the loop filter zero enables us to analyze the loop as a second-order PLL. It can easily be shown that for a phase margin greater than 45°, the ripple filter pole is given by:

$$\omega_{ripple} \ge \frac{K_{DC}}{2} \frac{\omega_{pole}}{\omega_{zero}}$$

(2.6.4)

Therefore, a good rule of thumb is:

$$\frac{K_{DC}}{2} \frac{\omega_{pole}}{\omega_{em}} \gg \omega_{zero} \gg \omega_{pole} \tag{2.6.5}$$

For example, if  $K_{DC} = 0.1\omega_o$ ,  $\omega_{pole} = 10^{-5}\omega_o$ , and  $\omega_{zero} = 2x \cdot 10^{-4}\omega_o$ , then the ripple filter pole must be larger than  $2.5x \cdot 10^{-3}\omega_o$ . Actually, the approximations involved in the derivation of equation (2.3.4) for the noise bandwith also put similar restrictions to those in equation (2.6.5). But they are easily satisfied if equation (2.6.5) is followed as a rule. Note that for the values above,  $Q_{PLL}$  is 100.

Before concluding this chapter, it might be interesting to check the scaling of the several PLL parameters with frequency.  $K_{DC}$  is proportional to the operating frequency  $\omega_o$ , in radians per second,

assuming that  $K_{VCO}$  changes linearly with  $\omega_o$ . Therefore, for a given  $K_{PD}$ ,  $K_{AMP}$  and filter attenuation ratio,  $Q_{PLL}$  is independent of frequency from equations (2.3.3) and (2.3.4). On the other hand, pull-in range increases with frequency from equation (2.4.1) or (2.4.2). It seems that it is easier to obtain a given  $Q_{PLL}$  at higher frequencies if the VCO stability can be maintained constant throughout the frequency range of interest. However, as the frequency continues to increase, more extra poles will approach to

$$\frac{K_{DC}}{2} \frac{\omega_{pole}}{\omega_{zero}}$$

Hence, if nothing else, stability degradation will limit the maximum frequency that can be scaled in a simple way.

#### **CHAPTER 3**

#### **VOLTAGE-CONTROLLED OSCILLATORS**

#### 3.1. Introduction

An oscillator is a circuit that produces a periodic signal at its output. An active circuit and a positive feedback network are the two essential parts of an oscillator. Oscillators can be analyzed either as two-port feedback networks or as one-port negative-resistance circuits. The design and analysis of oscillators are well covered in different books, [34]-[35], [70]-[72]. The amplitude of oscillation is usually determined by the nonlinearity in the active circuit. The frequency of oscillation is determined by the energy storage components, the voltage and current levels and by the phase shift or delay in the oscillator circuit. Therefore, varying any one of these quantities in a well-defined manner will result in an oscillator whose frequency can be controlled as desired. Voltage-controlled oscillator (VCO) is the general name used for such an oscillator.

There are several ways to implement a monolithic VCO. Depending on the controlling variable and the principle governing the dynamics of oscillations, they can be classified into four groups:

- 1. Varactor-controlled harmonic VCOs, [19]-[20], [50], [73],

- 2. Phase shift controlled harmonic VCOs, [13]-[14], [53]-[54],

- 3. Current-controlled relaxation VCOs, [11]-[12], [15]-[16], [74],

- 4. Delay-controlled ring VCOs, [7], [21], [75].

Harmonic oscillators employ an inductor, L, and a capacitor, C, for frequency selection. Therefore, varying the value of either one of these energy storage elements will result in a harmonic VCO. Since variable capacitors (varactors) are readily available in a monolithic process as junction capacitors, varactor-controlled VCOs are very attractive from the integrated circuit point of view. Unfortunately, inductors are not presently available in monolithic Si technology, and they have to be external to the

circuit. Using the two-port feedback approach, one of the required conditions for the oscillations to start is that the fed-back signal has to be in phase with the input signal. In other words, the total phase shift around the loop has to be zero. Therefore, any phase shift in the active circuit has to be compensated in the L-C tank circuit. This forces the operating frequency to shift depending on the tank circuit phase sensitivity with respect to frequency. Hence, it is possible to control the VCO frequency by introducing a deliberate phase shift into the active part of the oscillator and this may require some extra circuitry to introduce and control the phase shift. Moreover, at high frequencies, there already exists some phase shift associated with the parasitics of the active device used. All these can make the temperature compensation of the circuit quite difficult. In general, a frequency detector will be very useful when a phase shift controlled VCO is employed in the PLL, [13]-[14]. On the other hand, a varactor-controlled VCO essentially requires the compensation of its varactor capacitance. This task can be made easier if an on-chip junction capacitance with a known temperature dependence is used as the varactor. The phase shift can also be controlled by using R-C sections in the feedback network and without employing an inductor. However, the frequency selectivity becomes poor which, in turn, increases the noise bandwith of the oscillator.

As explained in the second chapter, the noise bandwith of a harmonic oscillator is inversely proportional to the square of the tank circuit quality factor,  $Q_T$ , and to the signal amplitude. Since the amplitude of oscillation is limited by other circuit constrains such as the requirement of forward active region of operation for active devices etc., it is best to keep the quality factor of tank circuit large, i.e. greater than ten, if possible. The same condition is also necessary to filter out the harmonics of the signal created by the nonlinearities in the circuit. Too much distortion will shift the oscillations to a lower frequency making the frequency control more difficult. The quality factor for a parallel tank circuit is given by:

$$\frac{1}{Q_T} = \frac{1}{Q_L} + \frac{1}{Q_C} \tag{3.1.1}$$

where  $Q_L$  and  $Q_C$  are the quality factors of L and C, respectively. Any other loading from the rest of the oscillator circuit will further lower the  $Q_T$ . Therefore, assuming a low-loss inductor, a high-quality varactor is essential for achieving a high-performance varactor-tuned harmonic VCO. This topic will be

discussed in detail in section 3.3. Even when a crystal can be used replacing the inductor, the losses in the varactor will reduce the  $Q_T$ .

Relaxation and ring oscillators have one significant property in common, that is, they are both broad band switching circuits. One of the storage elements which make the harmonic oscillators narrowband, L, is missing in relaxation and ring oscillators, and therefore, they are much more prone to noise. [64]. They also tend to have large temperature coefficients at high frequencies, [11], [15]-[16], [74]. Ideally, they are useful in obtaining square wave outputs. In a relaxation oscillator, a constant current source charging a timing capacitor reverses its polarity when a threshold voltage determined by the voltage drops in the circuit is reached. The switching behavior in each half cycle is described by a fast transition and a slow relaxation. If the current can be controlled through a voltage to current converter, a VCO is obtained. In general, the frequency is a linear function of the current and a very wide range of frequency control can easily be achieved compared to the varactor-tuned and ring-type VCOs. In a ring oscillator, odd number of inverter stages are cascaded in a ring formation. The delay through each stage multiplied by the number of stages gives the half period of oscillations. Frequency can be controlled by changing the delay which is a complicated function of several R-C time constants for a given inverter. In bipolar technology, the ECL gate and emitter follower bias currents are possible candidates to vary the gate delay, [17]-[18]. The process, temperature and supply variations strongly influence the frequency of oscillation since all the parasitics contribute to the gate delay. Multiple modes of oscillation encountered in ring oscillators is another common problem that must be addressed, [7], [75].

Consequently, varactor-controlled harmonic VCOs seem to be the best choice for high-frequency narrowband PLL implementations in monolithic technology if one desires low jitter and low TC. Therefore, the rest of this chapter is devoted to the discussion of varactor-controlled VCOs.

#### 3.2. Negative Resistance and Frequency Limitations

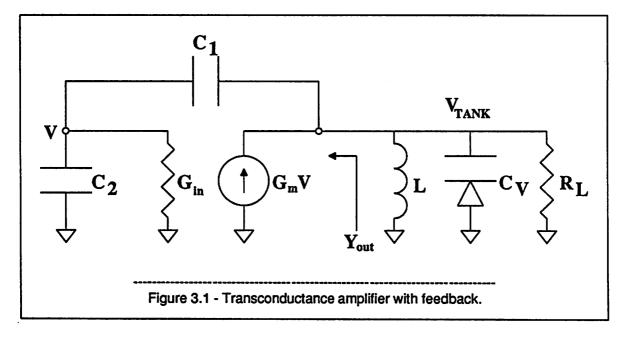

As mentioned in the preceding section, every harmonic oscillator needs a gain stage and a feedback network. Since it is relatively straightforward to fabricate wideband transconductance amplifiers and

low-loss capacitive transformers using a silicon bipolar technology, a typical configuration that might include these components is shown in Figure 3.1.

Assuming a negative conductance is available at the output, loading the amplifier with a a parallel tank circuit will result in a harmonic oscillator.

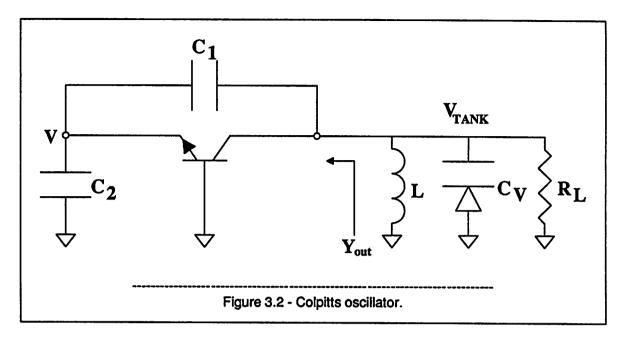

The next question that comes to mind is that for what frequency range one can assume an output impedance with a negative real part from this amplifier with capacitive feedback. It can easily be shown that for an ideal amplifier with infinite input impedance and with no other loading at its input, the output impedance of the circuit is always capacitive with a negative real part. Therefore, the only frequency limitation will come from the bandwith of the amplifier depending on how large a negative resistance required for a given loss in the tank circuit. A logical step would be to choose a common-base amplifier configuration since it has a very wide bandwith, [34, ch. 7]. This results in the well-known common-base Colpitts circuit as shown in Figure 3.2. Since the input conductance,  $G_{in}$ , of a common-base stage is close to its transconductance,  $G_m$ , one can show that the following equation has to be satisfied in order to obtain a negative output conductance which is larger than the shunt conductance,  $G_L$ , of the tank circuit:

$$\omega^2 > \frac{G_m^2}{C_1 C_2 G_m R_L - (C_1 + C_2)^2}$$

(3.2.1)

where  $R_L$  is the loading from the tank circuit. For  $I_C = 1$  mA,  $C_1 = 1$  pF,  $C_2 = 9$  pF,  $R_L = 1$  K $\Omega$ , the lower frequency limit turns out to be 390 MHz. Although only small-signal approximations are used so far, SPICE simulations agree very closely with the limits given by equation (3.2.1). Note that, for the values above,  $R_L$  has to be greater than 290 ohms so that the right-hand side of equation (3.2.1) is positive. Therefore, even though the bandwith of the common-base stage is very large, the loading from its input terminal restricts the useful bandwith of the circuit.

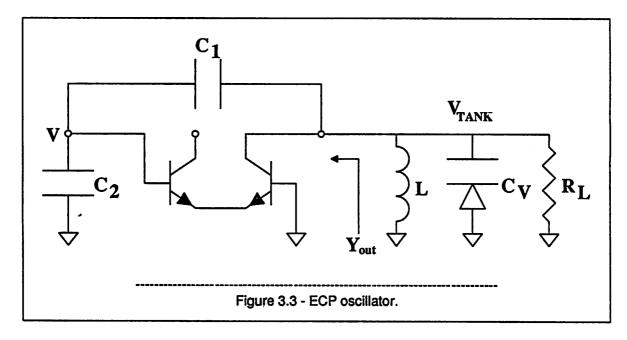

One way to decrease the loading on the capacitive transformer is to insert an emitter-follower stage as a buffer before the common-base stage. This results in an emitter-coupled pair (ECP) oscillator as shown in Figure 3.3. Now, the input conductance is decreased by a factor of transistor current gain,  $\beta$ , for the same amplifier transconductance,  $G_m$ . A similar expression can be derived for the ECP oscillator as it was done for the Colpitts. The final result is:

$$\omega^{2} > \frac{G_{m}^{2}}{\beta^{2} (C_{1} + C_{2}) [G_{m} R_{L} C_{1} - (C_{1} + C_{2})]}$$

(3.2.2)

For  $I_C = 2$  mA,  $C_1 = 1$  pF,  $C_2 = 9$  pF,  $R_L = 1$  K $\Omega$ , and  $\beta = 100$ , the lower frequency limit is equal to 3.6 MHz.

Next, we examine the imaginary part of the amplifier output impedance. For the Colpitts oscillator, it can easily be shown that the output impedance is always capacitive. However, for the ECP oscillator, there exists a frequency below which the output impedance is inductive. This frequency is given by:

$$\omega^2 = \frac{G_m^2}{\beta C_2 (C_1 + C_2)} \tag{3.2.3}$$

For the same values as above, the output impedance is capacitive if the frequency is greater than 64.5 MHz. This means that the circuit will self resonate at 64.5 MHz without a tank circuit at the output. Any capacitance in the tank circuit will reduce that frequency. However, even then, there will be a lower limit on the oscillation frequency for a given tank capacitance. This is so because of the fact that as the value of the inductor is made larger, the impedance of the tank inductor will be much larger than the inductive part of the amplifier output impedance at a low enough frequency. This puts an upper limit on the useful range of external inductance. In any case, ECP oscillator topology is a better choice than Colpitts for frequencies lower than a few hundred MHz.

Let us turn our attention to the higher end of the frequency range that can be achieved with the topologies considered. Since an ECP gain stage has a lower bandwith than a common-base stage, the ECP oscillator is expected to be more limited at the high-frequency end. The low-frequency models used

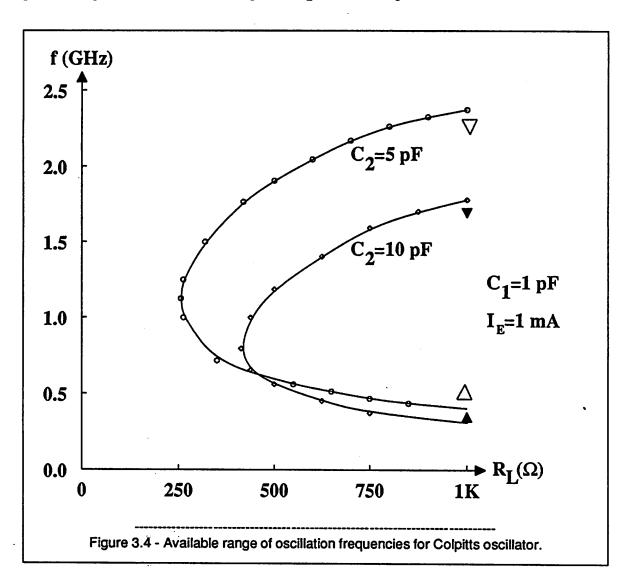

so far are not very useful any more and device parasitics have to be included in the models. Therefore, extensive computer simulations are required. Let us assume that the loading from the tank circuit is between 250 to 1000 ohms. This is a reasonable assumption since at very high frequencies the losses in the inductor and the varactor diode alone may impose the worst case limitations setting the maximum frequency of operation. To keep the value of  $C_1$  minimum, a practical value of 1 pF is chosen. First, let us examine the Colpitts oscillator. The range of frequencies for which the common-base configuration can provide a negative shunt conductance larger than  $G_L$  is shown in Figure 3.4, for a bias current of 1 mA.

Two curves for  $C_2$  being equal to 5 and 10 pF are shown. The area enclosed by each curve gives the useful range of frequencies for the corresponding value of  $C_2$ . The cut-off frequency of the device is close

to its optimum value of 11 GHz. As predicted, the lower frequency range does not extend below 300 MHz even with a 1 K $\Omega$  load. The useful range becomes more limited as the loading increased. Similar curves are obtained for different bias conditions and  $C_2$  values. Although the lower limit is always larger than 300 MHz, the upper limit can be more than 5 GHz for a load of 1 K $\Omega$ .

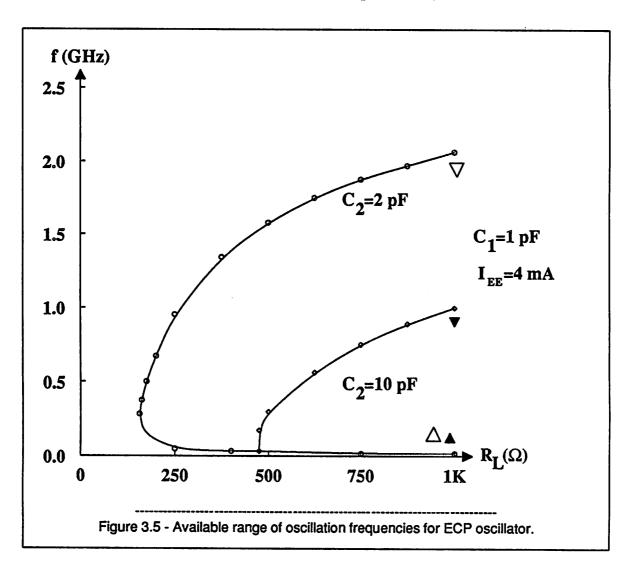

A similar set of curves are obtained from the SPICE analysis of the ECP oscillator. In order to obtain the same transconductance,  $G_m = \frac{1 \ mA}{26 \ mV}$ , from the ECP, the current in each transistor must be doubled. Two of these curves are plotted in Figure 3.5 for  $C_2 = 2$  and 10 pF.

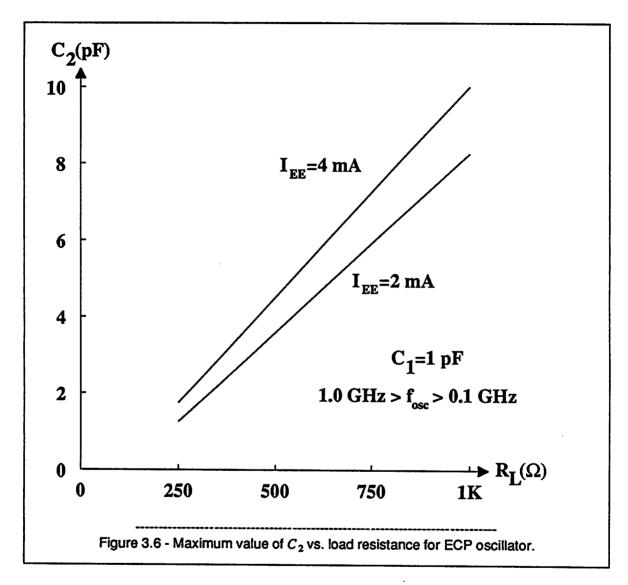

Both the upper and lower frequency limits are shifted down compared to the Colpitts gain stage. However, assuming that we are interested in the frequency range from 100 MHz to 1 GHz, it is possible to obtain a negative shunt conductance larger than  $G_L$  from the ECP stage by choosing a proper value of  $C_2$  for a given bias current,  $I_{EE}$ , and a load,  $R_L$ . The maximum design value of  $C_2$  that would result in a large enough negative conductance for the oscillations to start is plotted in Figure 3.6 for  $I_{EE} = 2$  mA and 4 mA.

For the worst case loading of 250 ohms, the required design values are less than 2 pF. Higher values can be used if a narrower range of frequencies is required from the design. The conclusion is that the ECP will perform better than the Colpitts for the mentioned frequency range of interest and for a load resistance less than 1000 ohms.

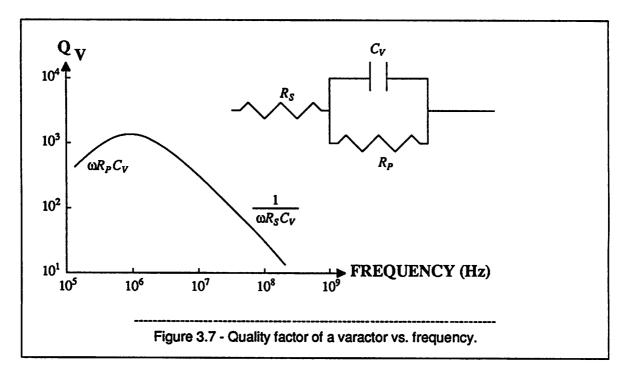

#### 3.3. Varactor Design

The depletion capacitance of a reverse-biased p-n junction is commonly used as a variable capacitance, [76, ch. 2]. The quality factor,  $Q_V$ , of a varactor is a function of bias and frequency. At low frequencies, the shunt conductance that represents the leakage current limits  $Q_V$ , whereas at high-frequencies, the series resistance is more significant. A typical curve for  $Q_V$  as a function of frequency would look like as shown in Figure 3.7.

The frequency at which the  $Q_V$  is maximum is usually less than a few MHz. Therefore, for frequencies greater than a few MHz,  $Q_V$  can be written as:

$$Q_V = \frac{1}{\omega R_S C_V} \tag{3.3.1}$$

Consequently, the  $R_S$ - $C_V$  product must be minimized to achieve high  $Q_V$  at high frequencies. Although  $Q_V$  increases with reverse bias, this increase is limited by the breakdown voltage and the minimum design value of  $C_V$ .

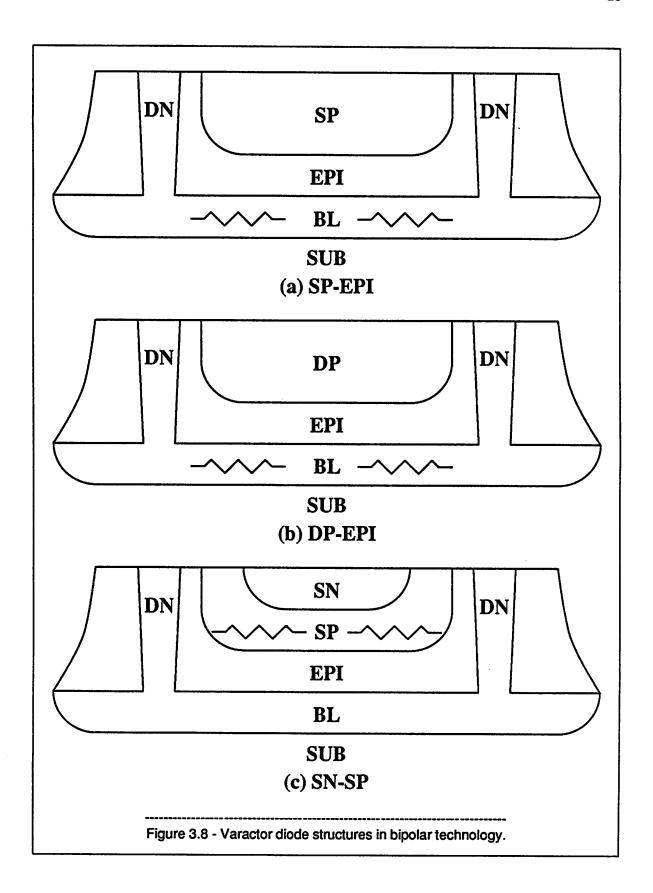

Several p-n junctions can be considered for a varactor structure if a high-frequency bipolar process is available. Usually, such a process has a deep-p (DP) implant (or diffusion) for the extrinsic base and a

shallow-p (SP) implant for the intrinsic base. It is assumed that both implants have low enough resistivity to form a good contact with the metal which is usually aluminum. Therefore, in conjunction with the n-type epi layer, they can be used to form a varactor diode without any extra processing steps. Another possibility is the junction formed by the shallow-n (SN) emitter implant and the SP implant. All three structures are shown in Figure 3.8. Double collector and base contacts are used to reduce the collector and base resistances, respectively. A pair of deep-n, (DN), plugs connect the buried layer, (BL), to the collector contacts. Neglecting the metal losses, the dominant sources of series loss are the epi and the buried layer regions, for the base-collector junctions, and the intrinsic base region under the emitter for the base-emitter junction. The sheet resistance of the base implant under the emitter can be as high as 10 to 12 K $\Omega$  per square, and therefore it is difficult to obtain a high-quality junction capacitance. Furthermore, the breakdown voltage is lower than that of the base-collector junctions. Although the one-sided abrupt junction approximation is commonly used, in reality, the junction capacitance is determined by the dopant densities on both sides of the junction. Therefore, for the same area, the SP-EPI junction will have a slightly reduced capacitance, hence a higher  $Q_V$ , compared to the DP-EPI junction.

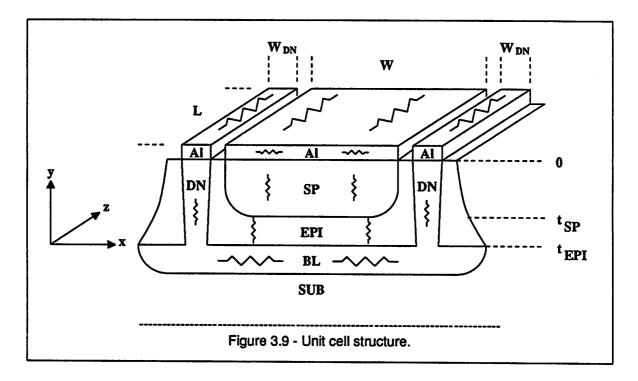

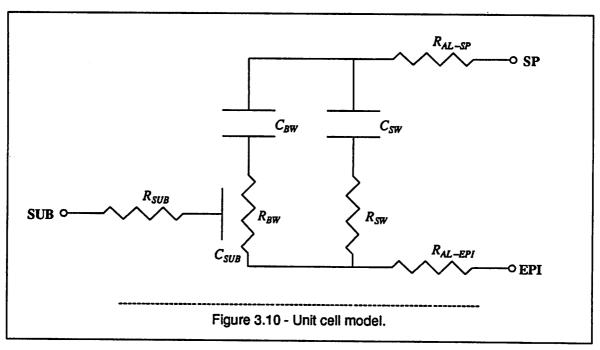

Let us consider the SP-EPI structure shown in Figure 3.9 as a unit cell. If the plane of cross-section is designated as the x-y plane, then, W and L are the width and length of the SP-implanted region in the x-(horizontal) and z-(perpendicular to the cross-section) directions, respectively. The maximum distance of interest in the y-(vertical) direction is the epi layer thickness,  $t_{EPI}$ .  $t_{EPI}$  is usually on the order of a few microns or less for a high-frequency process. If the  $R_S$ - $C_V$  product of this unit structure can be minimized with respect to W and L, then any number of these cells can be connected in parallel without degrading the optimum  $Q_V$ . This problem is obviously three dimensional, but some simplifying assumptions can still be made. First of all, the contact resistance between the metal (Al) and silicon (Si) will be neglected. Secondly, the skin effect for Al-metal lines will be assumed negligible below 1 GHz. The bottom-wall and the side-wall capacitances will be considered separately, as shown in Figure 3.10. The following resistivities may contribute to the series resistance,  $R_{BW}$ , of the bottom-wall capacitance,  $C_{BW}$ :

Horizontal:  $\rho_{Al}$  for SP,  $\rho_{BL}$  for EPI,

Vertical:  $\rho_{SP}$  for SP,  $\rho_{EPI}$  for EPI,

Perpendicular:  $\rho_{Al}$  for SP,  $\rho_{AL}$  for EPI.

Similarly, the side-wall capacitance,  $C_{SW}$ , has the following resistive components contributing to its

series resistance,  $R_{SW}$ :

Horizontal:  $\rho_{Al}$  for SP,  $\rho_{EPI}$  for EPI,

Vertical:  $\rho_{SP}$  for SP,  $\rho_{DN}$  for EPI,

Perpendicular:  $\rho_{Al}$  for SP,  $\rho_{Al}$  for EPI.

The metal losses in the perpendicular direction are modeled by  $R_{Al-SP}$  and  $R_{Al-EPI}$ , as shown in Figure 3.10. Among the other components, only  $\rho_{BL}$  and  $\rho_{EPI}$  will be assumed to contribute to  $R_{BW}$ , whereas  $R_{SW}$  will mainly be determined by  $\rho_{EPI}$ . The buried-layer component of  $R_{BW}$  can be modeled as a RC-transmission line, [77], and the total bottom-wall loss can be written as:

$$R_{BW} = \frac{1}{12} R_{\Box -BL} \frac{W}{L} + \rho_{EPI} \frac{d_{SP-BL}}{W L}$$

(3.3.2)

where  $d_{SP-BL}$  is the vertical distance between the SP and the BL regions. If the bottom-wall capacitance per area is  $C_{\square}$ , then one has:

$$C_{RW} = C_{\square} W L \tag{3.3.3}$$

One can also show that the side-wall resistance is given by:

$$R_{SW} = \frac{1}{2} \rho_{EPI} \frac{d_{DN-SP}}{L t_{SP}} \tag{3.3.4}$$

where  $d_{DN-SP}$  is the horizontal distance between the DN and the SP regions, and  $t_{SP}$  is the depth of the intrinsic base implant. Finally,  $C_{SW}$  can be written as:

$$C_{SW} = 2 C_l L \tag{3.3.5}$$

where  $C_l$  is the capacitance per length. Assuming that both branches have a quality factor larger than 10, the quality factor of their parallel combination is given by the following equation:

$$Q_{BW ||SW} = \frac{1}{\omega} \frac{C_{BW} + C_{SW}}{R_{BW} C_{BW}^2 + R_{SW} C_{SW}^2}$$

(3.3.6)

It can easily be shown that the equation above is a function of W but not L. Therefore, by taking the

derivative of equation (3.3.6) with respect to W, one can find  $W_{opt}$  which maximizes  $Q_{BW//SW}$ . Then, the effect of  $\rho_{Al}$  for a given number of unit cells, n, can be estimated using the following equations:

$$R_{Al-SP} = R_{\square-Al} \frac{L}{n W_{opt}} \tag{3.3.7}$$

and

$$R_{Al-EPI} = R_{\square-Al} \frac{L}{n W_{DN}} \tag{3.3.8}$$

where  $W_{DN}$  is the width of the DN region. Before giving a numerical design example, it is worth mentioning that the substrate capacitance,  $C_{SUB}$ , can have a very low quality factor. An AC-short circuit between the epi and the substrate terminals will minimize the effect of the substrate junction.

### **EXAMPLE**

Let us assume that the following parameters are specified for an oxide-isolated bipolar process:  $\rho_{EPI} = 0.3 \ \Omega/\text{cm}$ ,  $R_{\square -BL} = 32 \ \Omega/\square$ ,  $d_{SP-BL} = 0.6 \ \mu$ ,  $C_{\square} = 0.4 \ \text{fF}/\mu^2$ ,  $d_{DN-SP} = 3 \ \mu$ ,  $t_{SP} = 0.4 \ \mu$ ,  $C_l = 2 \ \text{fF}/\mu$ ,  $R_{\square -Al} = 0.05 \ \Omega/\square$ .

From equations (3.3.2) and (3.3.3),  $Q_{BW} > 10$  if W < 100  $\mu$  and f < 1.4 GHz. From equations (3.3.4) and (3.3.5),  $Q_{SW} > 10$  if f < 900 MHz. Substituting these equations into (3.3.6), one can obtain:

$$Q_{BW/ISW} = \frac{10^{15}}{\omega} \frac{0.4W + 4}{0.427W^3 + 288W + 72000}$$

where W is in microns. By taking the derivative of  $Q_{BW//SW}$  with respect to W and equating it to zero, one can get:

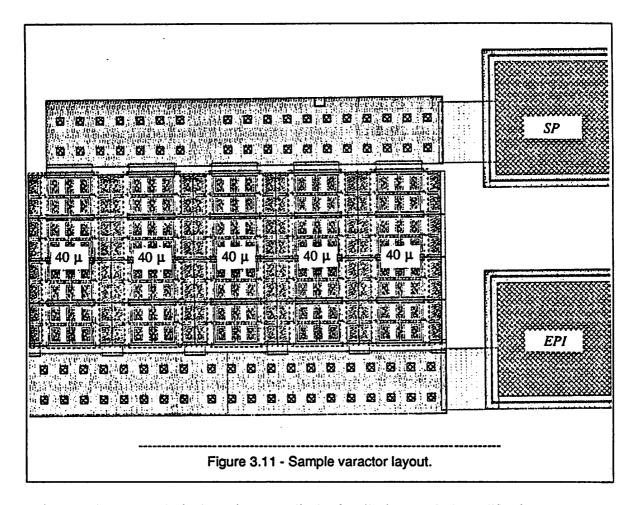

$$W_{opt} = 40 \,\mu$$

Substituting this value back into the equation for  $Q_{BW//SW}$ :

$$Q_{BW//SW} = \frac{28.7}{f}$$

where f is in GHz. Assuming that  $W_{DN} = 10 \,\mu$  and using equations (3.3.7) and (3.3.8):

$$R_{Al-SP} + R_{Al-EPI} = 0.00625 \frac{L}{n}$$

Now, for a zero-bias value of 10 pF, one can write:

$$10^4 \, fF = n \, \left( 0.4 \, W \, L + 4 \, L \right)$$

where W and L are in microns. Therefore, if W = 40  $\mu$ , then nL = 500  $\mu$ . Choosing n = 5 results in L = 100  $\mu$ . Then, one has:

$$R_{Al-SP} + R_{Al-EPI} = 0.125 \Omega$$

Since  $Q_{BW/ISW}$  is 28.7 at 1 GHz,  $R_{BW/ISW} = 0.555 \Omega$  for  $C_V = 10$  pF. In other words, the total series resistance,  $R_S$ , is 0.7 ohms. Therefore:

$$Q_V = \frac{1}{2 \pi 10^9 10^{-11} 0.7} = 23$$

A layout sample with n = 5 is shown in Figure 3.11. Because of the various assumptions made in modeling this three-dimensional distributed structure, the above results are optimistic and should be used with caution. However, they are useful in estimating an upper limit for  $Q_V$ .

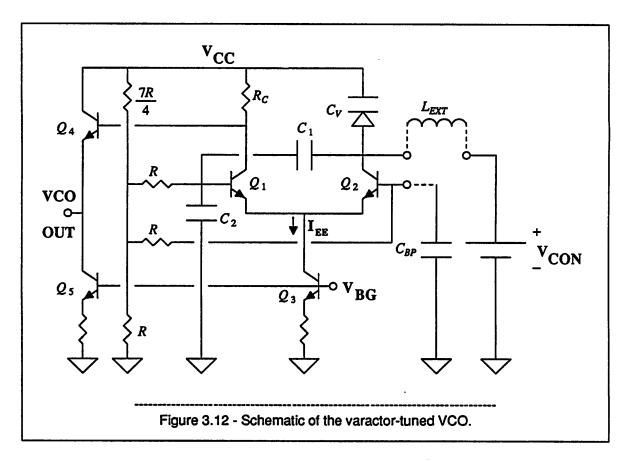

## 3.4. VCO Design

The complete VCO schematic is shown in Figure 3.12. For the reasons explained in section 3.2, an emitter-coupled pair is chosen as the gain stage for the VCO topology. This topology has the advantage of an isolated output from the tank circuit in addition to a gain stage with high input impedance. The total harmonic distortion is also smaller compared to a single-transistor oscillator since the tanh-nonlinearity of a differential pair has only odd harmonics. As mentioned before, a reverse biased shallow-base to collector-epi junction with buried-layer is used as the varactor diode in this design. The effect of the substrate junction is minimized by connecting the epi-side to the supply potential. Positive feedback is provided by the MOS capacitors C1 and C2. The worst case series resistance of the MOS capacitors can be estimated to be less than 5 ohms using a similar approach as it was done for the varactor. External inductance and capacitance can be used to adjust the center frequency and an external

resistor can be used to obtain the optimum amplitude of oscillation. A clock amplifier follows the VCO to provide a differential drive to the phase detector.

The amplitude of oscillation is a strong function of the losses in the varactor and the inductor at very high frequencies. For instance, if each of them has a Q of 30 with a series resistance of 1 ohm, the equivalent loading on the tank circuit will be 450 ohms. Then, the bias current,  $I_{EE}$ , and the transformer ratio,  $n = \frac{C_1 + C_2}{C_1}$ , have to be chosen accordingly for a given oscillation amplitude. Assuming a peak oscillation amplitude of 500 mV for a worst case loading of 400 ohms, the fundamental current component at the oscillation frequency has to be 1.25 mA. If the signal amplitude at the differential pair input is b times  $V_T$ , then, the product b times n must be equal to 20. Choosing b = 5 and n = 4 results in  $I_{EE} = 2.1$  mA from Table 4.6-2 of the reference [70, page 117]. For  $C_1 = 1$  pF,  $C_2$  should be 3 pF. From the negative resistance curves of Figure 3.6, the oscillations are possible almost up to 1 GHz. In reality,

the value of  $C_2$  is designed to be closer to 2.5 pF by taking the parasitic capacitances into account. The varactor capacitance must be much larger than the equivalent MOS capacitance of 0.75 pF for a wide tuning range. Furthermore, if one wants to achieve a loaded tank quality factor greater than 10 at 500 MHz, then:

$$C_V > \frac{10}{2\pi (500x \, 10^6) (400)} = 8 \, pF$$

Naturally, at lower frequencies, there will be less loading from the tuning elements of the tank circuit, and therefore, the amplitude will increase. Then, in order to limit the peak amplitude around 1 V, an external resistance of 1 K $\Omega$  is required. This, in turn, results in a  $Q_T$  of 10 at 200 MHz. The reflected loading from the amplifier input impedance and the bias resistors can be shown to be negligible. The output resistance of the ECP is larger than 20 K $\Omega$  for  $I_{EE} = 2$  mA. The extra phase shift introduced by the capacitive feedback circuit is less than 15 degrees down to 50 MHz. The base voltages of the ECP transistors are chosen to be  $2V_{BE}$  to keep the current source in the forward active region. Assuming that

the largest control voltage,  $V_{CON}$ , available is  $V_{CC} - V_{BE}$  and the peak oscillation amplitude is about one  $V_{BE}$ , the dynamic range of  $V_{CON}$  is limited to  $V_{CC} - 4 V_{BE}$  to keep the common-base transistor in the forward active region.

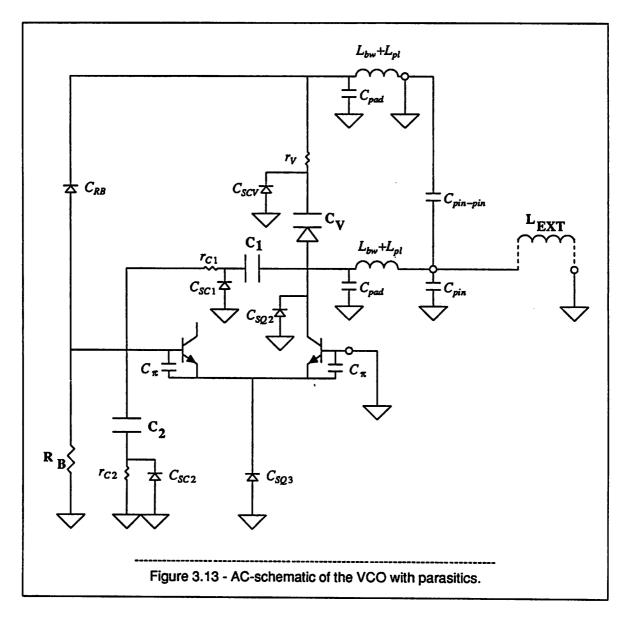

The AC-schematic of the VCO including the parasitics is shown in Figure 3.13.

Although a distributed L-C structure similar to a waveguide is a better model for frequencies approaching to 10 GHz, the lumped circuit model is assumed sufficient for frequencies less than 1 GHz. The center frequency of the VCO can be approximated as:

$$f_o = \frac{1}{2\pi \sqrt{(L_{EXT} + L_{bw} + L_{pl})(C_V + C_x)}}$$

(3.4.1)

where

$$C_{x} = \frac{C_{1}(C_{2} + C_{p})}{C_{1} + C_{2} + C_{p}} + C_{pad} + C_{pin} + C_{pin-to-pin}$$

(3.4.2)

and

$$C_{V} = \frac{C_{0}}{\left(1 + \frac{V_{R}}{V_{bi}}\right)^{m}}$$

(3.4.3)

In the equations above,  $C_p$  is the total parasitic capacitance across  $C_2$  including the input capacitance of the gain stage and the substrate capacitance of  $C_1$ , and  $C_0$  is the zero-bias value of the varactor capacitance,  $C_V$ . The epi-side of the capacitor  $C_1$  is connected to  $C_2$  in order not to load the tank circuit with its substrate capacitance. The epi-side of the capacitor  $C_2$  is connected to the ground potential. At high-frequencies, bonding wire and package lead inductance together with pad and pin capacitance will affect the frequency of operation, and therefore they are also included in the first two equations.

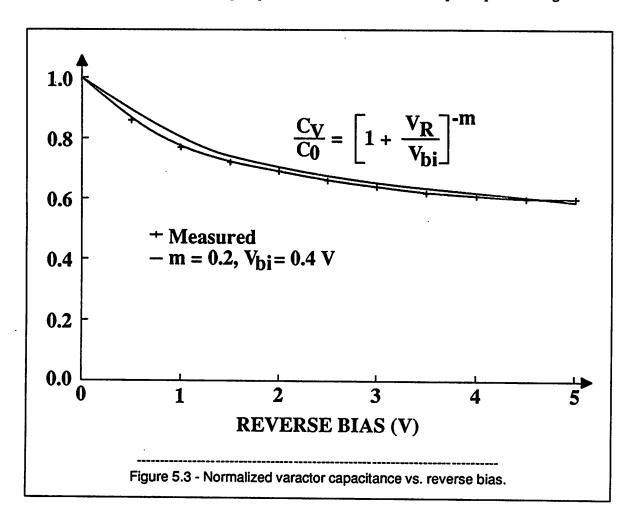

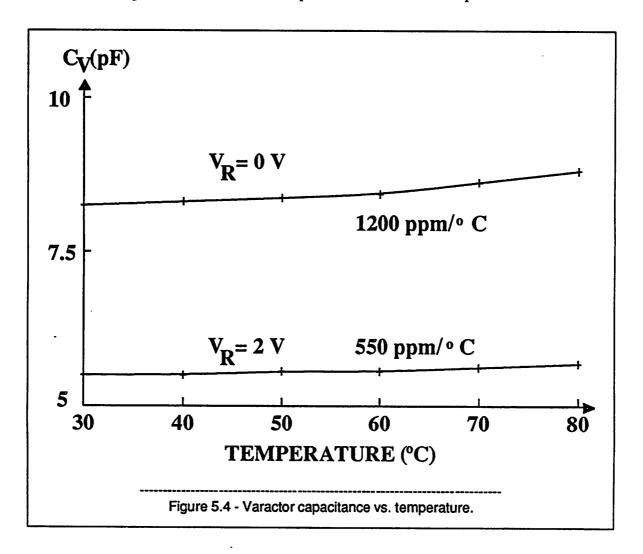

A built-in potential,  $V_{bi}$ , of 0.4 V and a grading coefficient, m, of 0.2 are specified for the process used to fabricate the test circuit. The grading coefficient is disappointingly lower than the initially assumed design values of 0.33 to 0.4 due to the outdiffusion from the buried layer into the thin epi region, [78]. If  $V_R$  is between 0.8 and 2.8 volts, then  $C_V$  varies between  $0.66C_0$  and  $0.80C_0$ . Since the minimum value for  $C_x$  is about 1.4 pF,  $0.66C_0$  should be at least 7 pF. In other words,  $C_0$  must be larger than 10.6 pF. The minimum tuning range that can be obtained with these values are -5 and +3 percent. Decreasing  $C_x$  or increasing  $C_0$  will achieve an upper limit of -5.8 and +3.7 percent. However, the lower limit on  $C_x$  depends on the package used and the upper limit on  $C_0$  depends on the practical values of external inductance, hence again on the package, if the chip area is not a crucial factor. For example, for a center-frequency of 500 MHz, a total inductance of 11.0 nH is required if  $C_0$  is 10.6 pF and  $V_R$  is 1.8 volts. If the package contributes a pin inductance of 2 nH, then the external inductance should be 9 nH. The varactor also has a series inductance of 2 nH due to the supply pin, and therefore, its self-resonance frequency is 1.3 GHz. Consequently, it will be useful to use multiple pins for the supply to reduce the parasitic inductance for frequencies above 500 MHz. This will also help to reduce the effect of the sub-

strate junction on the varactor impedance. In the final design, a  $C_0$  value of 13.5 pF is used. The estimated substrate capacitance is about 4.5 pF. Employing this varactor, the VCO will have a gain of  $-0.051\omega_o$  and  $+0.032\omega_o$  rad/(sec-volt). By shifting the  $V_R$  range to between 0.4 and 2.4 V, the the tuning range and the VCO gain can be increased to -6.9 and +3.9 percent, and  $-0.069\omega_o$  and  $+0.039\omega_o$  rad/(sec-volt), respectively. This would require limiting the oscillation amplitude to less than 400 mV.

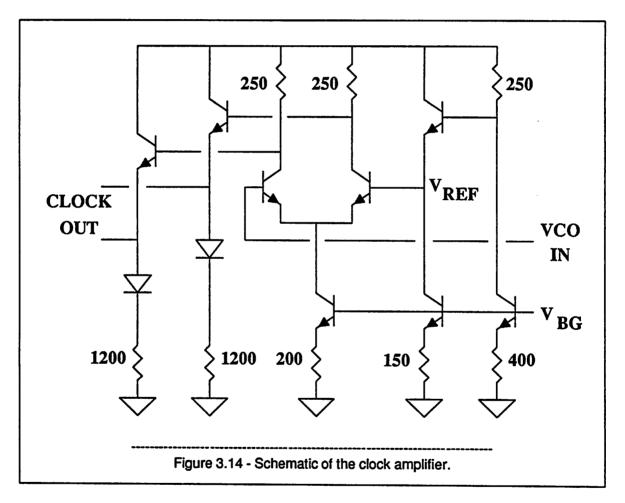

The schematic of the clock amplifier is shown in Figure 3.14.

It is a single-stage differential pair amplifier with a small-signal gain of 7.5 and a bandwith of 900 MHz. When considered together with the VCO, the clock amplifier behaves more like an ECL-NOR gate with complementary outputs to provide sufficient balanced drive to the phase detector. The input signal amplitude from the VCO can be made close to the oscillation amplitude by choosing an isolated-VCO-output gain of n, the turns ratio of the capacitive transformer. Then, for an oscillation amplitude of 100

mV or larger, the clock amplifier output is more than  $\pm$  400 mV. As the oscillation amplitude is increased beyond 200 mV, the differential clock output becomes equal to  $\pm$  500 mV by the limiting action of the clock amplifier.

Although the oscillations are nearly sinusoidal and the even-order nonlinearities are negligible, any asymmetry in the VCO gain stage and the clock amplifier will shift the duty cycle of the clock signal away from the ideal 50 percent. Apart from the random mismatches in the transistors of the differential pairs, the following sources contribute to the duty cycle shift:

- 1. Unequal switching times of the input transistor of the VCO gain stage which serves as a buffer for the common-base transistor. This mismatch between the turn-on and turn-off times becomes negligible as the frequency and the amplitude are decreased.

- 2. Different base-collector bias voltages and base terminations for the transistors of VCO differential pair.

- 3. The mismatch between the base voltages of the clock amplifier differential pair. The contribution from this mismatch becomes more significant as the oscillation amplitude is decreased. Therefore, the reference voltage of the clock amplifier must match the VCO output as close as possible.

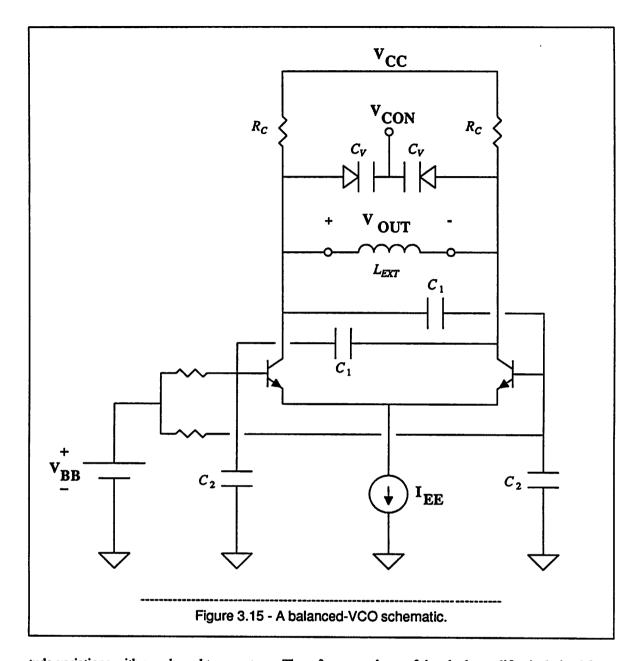

Under the worst case conditions, the clock waveform duty cycle at 500 MHz is expected to be between 48 and 52 percent from the SPICE simulations. A fully-balanced configuration which will be affected only by the random component mismatches is shown in Figure 3.15. However, any device mismatch in the VCO gain stage will create an offset voltage at the clock amplifier input similar to the third mismatch source mentioned above. Furthermore, the chip area used for the varactors must be increased by a factor of four to achieve the same varactor capacitance as before.

Since the transconductances of all gain stages employed in the VCO design are inversely proportional to the absolute temperature, all the current sources are designed to be proportional to the ratio of a PTAT (Proportional To Absolute Temperature) voltage to a resistor. This helps to minimize the ampli-

tude variations with supply and temperature. The reference voltage of the clock amplifier is derived from a bias circuit which mirrors the bias currents in the VCO. Therefore, it tracks the VCO output very closely with supply and temperature. The bandgap reference used to derive the PTAT voltages will be described in the next section.

## 3.5. Loop Amplifier and Bandgap Reference

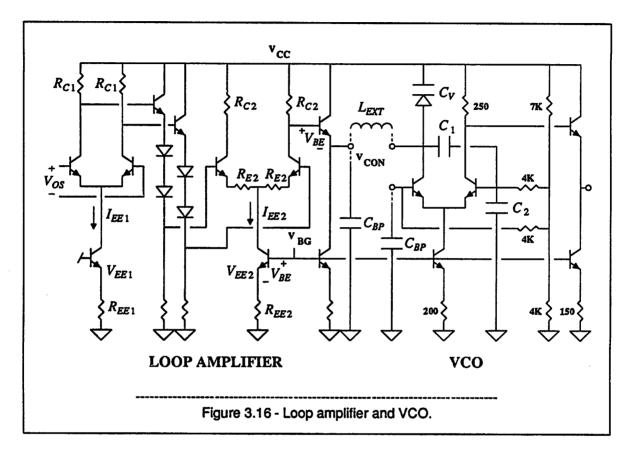

A two-stage loop-amplifier with a gain of 50 is designed to achieve a high-gain second-order PLL. Figure 3.16 shows the schematic of the loop amplifier and the VCO.

Assuming a worst case VCO gain of  $0.03\omega_o$  rad/(volt-sec) and a worst case phase detector gain of 0.1 volt/rad, a PLL with this loop-amplifier introduces a phase error less than 4 degrees for a pull-in range of  $\pm$  1 percent. For an equal contribution from the offset voltages, the total offset voltage from the loop amplifier and the phase detector must be less than 7 mV. In order to minimize the contribution of the level shifting diodes and the second stage to the input offset, the first stage gain is designed to be 20. Large area (10 times the minimum) devices are used to improve the matching throughout the loop amplifier. The bias current of the first stage should be kept low (1 mA or less) to minimize the input offset current and to maximize the input impedance. The bias currents of the second-stage ECP and the emitter follower are high (5 to 6 mA) to achieve a low output impedance. The output impedance is less than 10 ohms at low frequencies and becomes inductive at high-frequencies. The bandwith of the loop

amplifier is not very critical as long as it passes the largest frequency difference between the input and the VCO without much attenuation during capture. This difference is usually less than a few percent of the input frequency. The inherent 3-dB bandwith of the loop amplifier is around 150 MHz. A 10 nF chip capacitor at the output limits the bandwith to 2 MHz. This bypass capacitor is necessary not to degrade the quality factor of the external inductor and to provide some positive phase margin against any parasitic feedback around the loop amplifier.

The low-frequency control voltage at the amplifier output can be written as:

$$V_{CON} = V_{CC} - V_{BE} - 0.5 R_{C2} I_{EE2} - 0.5 \frac{0.5 I_{EE1} R_{C1}}{V_T} \frac{0.5 I_{EE2} R_{C2}}{V_T + 0.5 I_{EE2} R_{E2}} V_{OS}$$

(3.5.1)

where  $V_{OS}$  is the sum of the offset voltages from phase detector output and amplifier input. The reverse bias across the varactor diode is:

$$V_R = V_{CC} - V_{CON} \tag{3.5.2}$$

and this voltage appears in series with the built-in potential,  $V_{bi}$ , of the varactor diode. Therefore,

$$V_{bi} + V_R = V_{bi} + V_{BE} + 0.5 R_{C2} I_{EE2} + 0.125 \frac{I_{EE1} R_{C1}}{V_T} \frac{I_{EE2} R_{C2}}{V_T + 0.5 I_{EE2} R_{E2}} V_{OS}$$

(3.5.3)

Let us assume that

$$V_{OS} = \pm 0.2 V_T \tag{3.5.4}$$

$$I_{EE1} = \frac{V_{EE1}}{R_{EF1}} \tag{3.5.5}$$

and

$$I_{EE2} = \frac{V_{EE2}}{R_{EE2}} \tag{3.5.6}$$

where  $V_{EE1}$  and  $V_{EE2}$  are the required reference voltages. Then

$$V_{bi} + V_R \approx V_{bi} + V_{BE} + 0.5 V_{EE2} \frac{R_{C2}}{R_{EE2}} \pm 0.05 V_{EE1} \frac{R_{C1}}{R_{EE1}} \frac{R_{C2}}{R_{E2}}$$

(3.5.7)

One possible approach to minimize the temperature dependence of the expression above is to set

$$0.5 \frac{R_{C2}}{R_{EE2}} \frac{\partial V_{EE2}}{\partial T} = -\frac{\partial}{\partial T} (V_{bi} + V_{BE})$$

(3.5.8)

and

$$\frac{\partial V_{EE1}}{\partial T} = 0 \tag{3.5.9}$$

If

$$R_{C2} \approx 4 \, R_{EE2} \tag{3.5.10}$$

and

$$V_{EE2} = V_{BG} - n \ V_{BE} \tag{3.5.11}$$

then from (3.5.8):

$$n \approx 1 \tag{3.5.12}$$

assuming that  $V_{bi}$  and  $V_{BE}$  have the same TC. Consequently,  $V_{EE1}$  can be set equal to the band-gap reference voltage,  $V_{BG}$ , and  $V_{EE2}$  can be set equal to the voltage difference between  $V_{BG}$  and  $V_{BE}$ . In this way, the varactor capacitance, hence the VCO center-frequency, can be made independent of supply and temperature to a first order approximation. In general,  $V_{bi}$  and  $V_{BE}$  have different TCs and the TC of the dielectric constant of silicon,  $\varepsilon_S$ , cannot be neglected for large reverse bias. If the varactor capacitance can be written as:

$$C_V = \left[ \frac{K \, \varepsilon_S^{\alpha}}{V_{bi} + V_R} \right]^m \tag{3.5.13}$$

where K, a and m are constant with temperature, then, equation (3.5.10) can be modified as:

$$\frac{R_{C2}}{R_{EE2}} = 2 \frac{\left[ \frac{\partial V_{BE}}{\partial T} + \frac{\partial V_{bi}}{\partial T} - (V_{bi} + V_R) \alpha \frac{\partial \varepsilon_S}{\varepsilon_S \partial T} \right]}{\frac{\partial V_{BE}}{\partial T}}$$

(3.5.14)

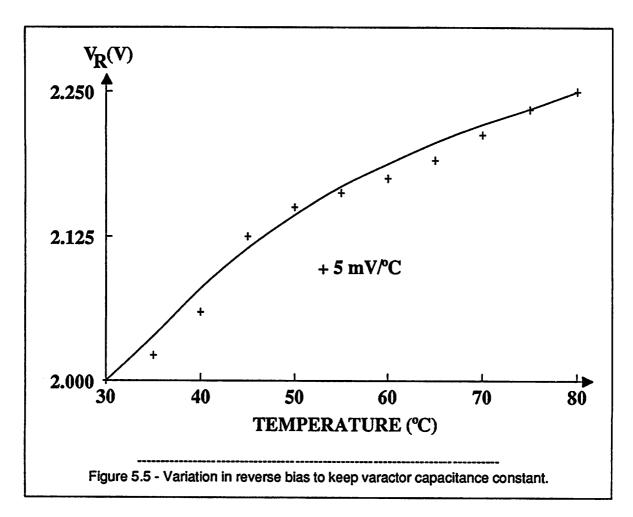

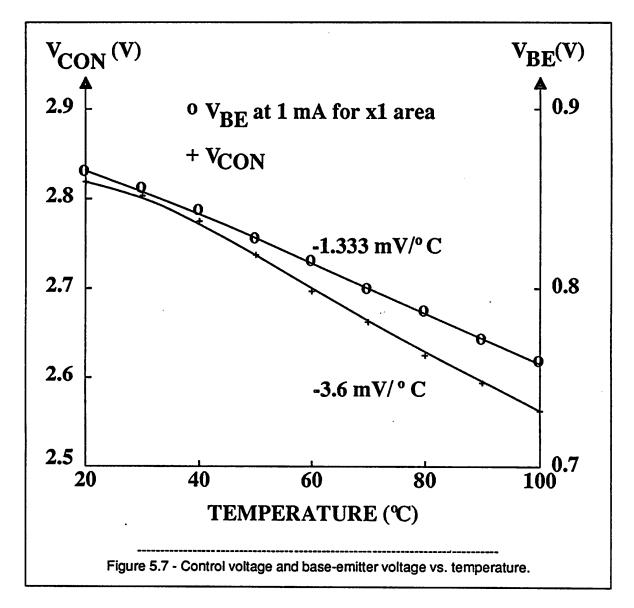

$\frac{\partial V_{BE}}{\partial T}$  is found to be -1.5 mV/°C from SPICE simulations at a bias current of 5 mA and over 0 to 100 °C.  $\frac{\partial V_{bi}}{\partial T}$  is found to be -2.9 mV/°C both from SPICE and using the equation (24) of [76, ch. 2] which assumes a linearly graded junction.  $\alpha$  and  $\frac{\partial \varepsilon_S}{\varepsilon_S \partial T}$  are assumed to be 2 and 200 ppm/°C, respectively, [79, ch. 2]. Then, from equation (3.5.14), the ratio  $\frac{R_{C2}}{R_{EE2}}$  is around 7 for  $V_{bi} = 0.4$  V and  $V_R = 2.0$  V. This ratio provides a dynamic range of 2.6 volts for the control voltage. Finally, the following resistor values are used in the design:  $R_{C1} = 1$  K $\Omega$ ,  $R_{EE1} = 1.2$  K $\Omega$ ,  $R_{C2} = 430$   $\Omega$ ,  $R_{EE2} = R_{E2} = 65$   $\Omega$ . With these design values and the assumptions made above, the TC of the VCO center frequency is ideally less than  $\pm$  6 ppm/°C for m = 0.2 and over 0 to 100 °C. A 10 percent design error in the resistor ratio increases these limits to  $\pm$  25 ppm/°C. Another 20 to 25 ppm/°C will be contributed by the phase shift in the VCO gain stage, the collector to emitter current gain of the devices, the resistor ratios, the MOS capacitors, the parasitic capacitors and the inductors. Considering all the assumptions made above, the TC of the VCO center frequency can be estimated to be between 50 to 100 ppm/°C.

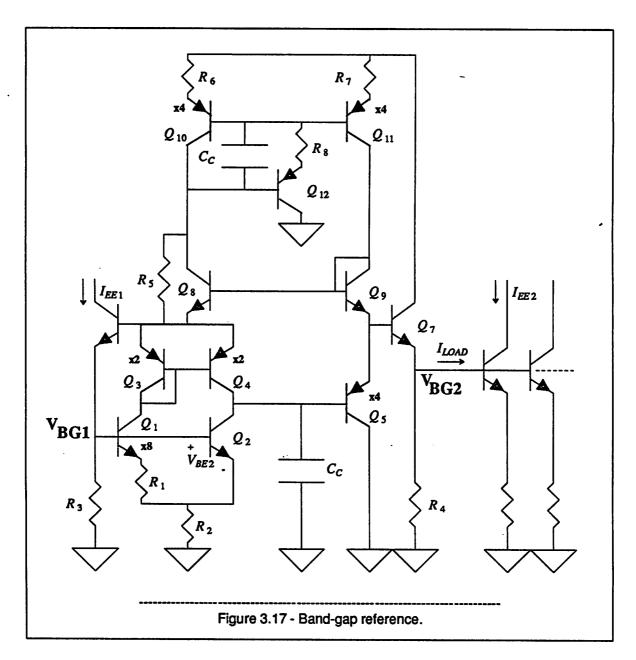

Figure 3.17 shows the schematic of the bandgap reference used in this design. It is a simple two-cell reference circuit without any second order correction, [74], [80].  $Q_1$  has 8 times the area of  $Q_2$ , and therefore, the voltage across  $R_1$  is  $V_T$  in 8 neglecting the device resistances. Due to the PNP current mirror, the current through  $R_2$  is 2  $\frac{V_T}{R_1}$  in 8. Hence, the bandgap voltage is given by:

$$V_{BG1} = V_{BE2} + 2 \frac{R_2}{R_1} V_T \ln 8 \tag{3.5.15}$$

Choosing  $R_1 = 530$  ohms results in  $I_{C1} = I_{C2} = 0.1$  mA. Then, for the process used to fabricate the test circuit, equation (3.5.15) gives  $R_2 = 4.3R_1 = 2280$  ohms. A second bandgap voltage,  $V_{BG2}$ , is derived through balancing the circuit with PNP current mirrors as shown in Figure 3.17. This voltage is used to derive all the bias currents in the PLL circuit except the first stage of the loop amplifier. The first stage current bias is set equal to 1 mA by the resistor  $R_3$ . The resistor  $R_4$  at the second bandgap output is set equal to  $\frac{R_3}{0.7}$  to allow for a load current of 0.3 mA. Several lateral PNP transistors are used in parallel to

improve the current gain and the matching of the devices. A vertical PNP is used to cancel the base currents of  $Q_{10}$  and  $Q_{11}$ .  $R_5$  is a 100 K $\Omega$  start-up resistor and  $C_C$  is a 1.3 pF compensation capacitor. SPICE simulations show a bandgap reference TC better than 65 ppm/°C from 0 to 100 °C. This will contribute less than 10 ppm/°C to the VCO frequency stability.

## **CHAPTER 4**

### PHASE DETECTORS

#### 4.1. Introduction

A phase detector, or a phase comparator, is a circuit which compares the phases of two inputs at the same frequency and gives an output voltage proportional to the phase difference. Analog phase locked-loops may employ either analog or digital phase detectors. As long as the control voltage derived from the filter is an analog quantity, one still has an analog PLL. Most common analog phase detectors are the modulator type. They compare the input waveforms over the whole cycle, and hence, are affected by the input amplitudes and duty-cycles. Digital circuits can be either of two types: combinatorial or sequential. An exclusive-OR gate is a combinatorial circuit but it essentially behaves as an overdriven modulator-type phase detector, and therefore, it should be classified as an analog phase detector. On the other hand, a flip-flop is a sequential circuit and affected only by the transition times of the inputs. Besides being insensitive to duty cycles, sequential type circuits have memory, adding significant characteristics to their properties which are not possessed by simple modulator or combinatorial type circuits. Since sequential phase detectors can remember the previous phase difference and compare it with the current one, they have an inherent frequency detection capability in addition to their phase detection property. In this thesis, only this type of circuit will be classified as a digital phase detector. Consequently, the frequency acquisition capability of the PLL strongly depends on the phase detector type used. Analog (modulator and combinatorial type) phase detectors are memoryless and do not have the inherent frequency detection property of the digital (sequential type) phase detectors with memory. Analog frequency detectors which employ R-C filters as memory elements will not be included in this discussion.

As was shown in Chapter 2, a large gain and a small offset are required from a phase detector to minimize the phase error. In order to reduce the phase detector offset voltage, large area devices should

be used whenever possible without degrading the frequency performance. The frequency performance of analog phase detectors is superior to digital phase detectors as will be discussed in the next sections.

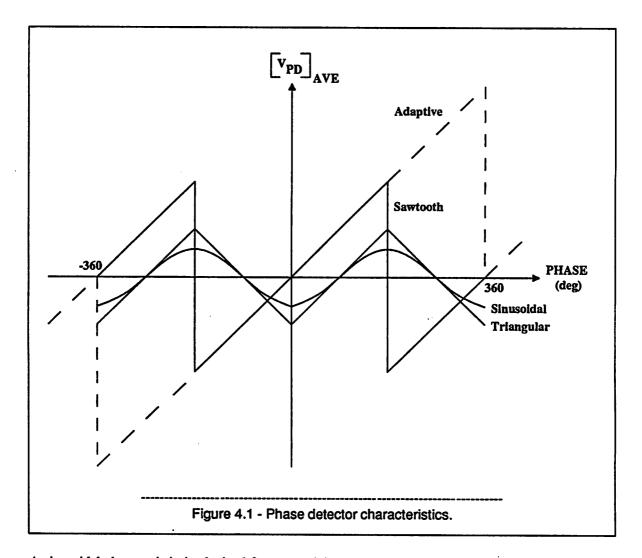

One can also classify phase detectors according to their transfer characteristics. Figure 4.1 shows four different phase detector characteristics: sinusoidal, triangular, sawtooth and adaptive.

A sinusoidal characteristic is obtained from a modulator type phase detector when the PLL input has a small amplitude. A triangular characteristic is obtained when the input amplitude is large, [25, ch. 6], [34, ch. 10]. Ideally, the operating stable point is 90 degrees for analog phase detectors. A sawtooth-shaped transfer curve is obtained when an edge-triggered flip-flop is used as a phase detector, [60]. The stable operating point can be at 0 or 180 degrees. Finally, adaptive phase detectors employ up-down counters and have nonperiodic, but repetitive transfer functions, [59]. They have 0 degrees as their stable

operating point. All these curves are valid for low-frequency and noise-free operation. Furthermore, any loop amplifier with a finite input dynamic range will modify the phase detector characteristics into a near-trapezoidal shape. At high-frequencies and with noise, the triangular characteristics of analog phase detectors degenerate into sinusoidal characteristics. The digital phase detectors function reliably only under low-noise conditions.

### 4.2. Analog Phase Detectors

The most common analog phase detectors are modulators or mixers. A double-balanced modulator forms the basis of well-known four-quadrant multiplier, [34, ch. 10]. Similarly, the core of a two-quadrant multiplier is a single-balanced modulator. Although it is possible to implement these circuits using either transistors or diodes, transistors are active devices and hence they are preferred for higher phase detector gain. They also possess the same matching properties as diodes in integrated circuit implementations. It is interesting to note that a double-balanced modulator and an exclusive-OR gate have the same truth table for large input signals. Similarly, a single-balanced modulator can be "implemented" using combinatorial logic gates for high-level signals. All of these implementations have the common property that the complete waveforms within a cycle are compared by the phase detector. One consequence of this property is that the average output of an analog phase detector is sensitive to the duty cycles of the input waveforms. Another consequence is that one can obtain a sinusoidal or a triangular characteristics depending on the input signal level.

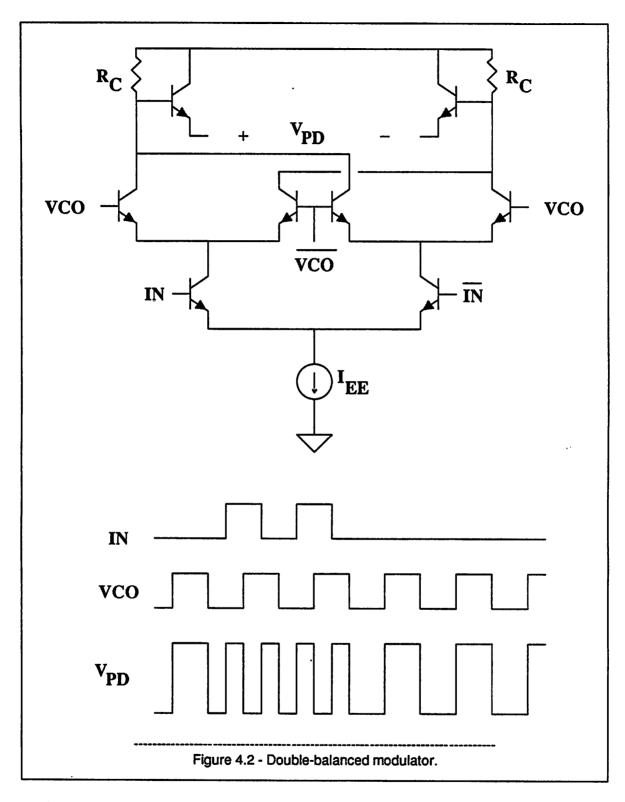

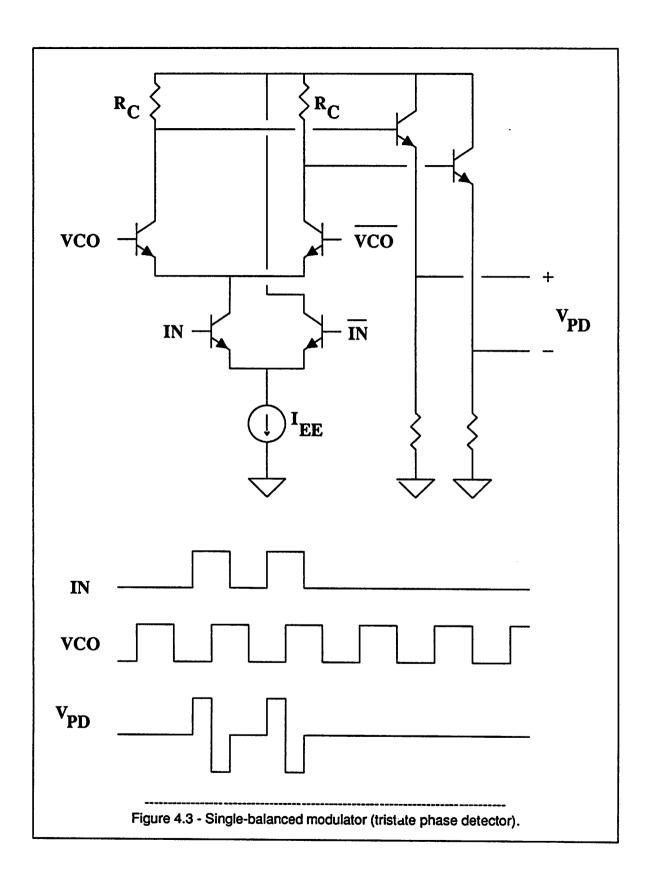

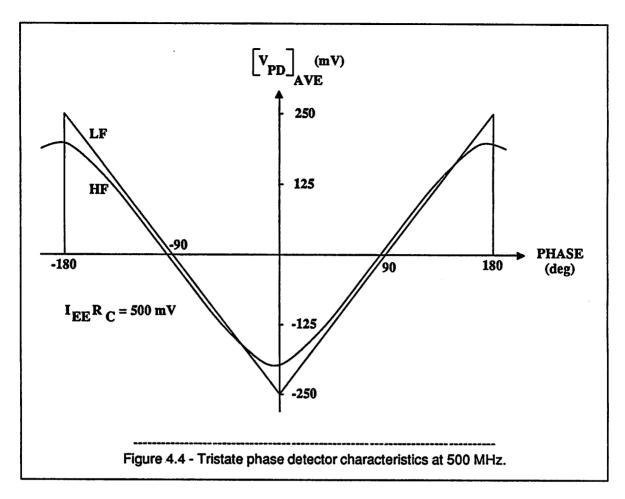

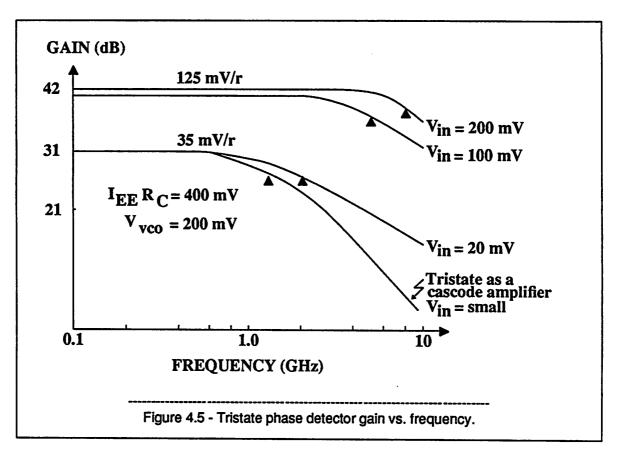

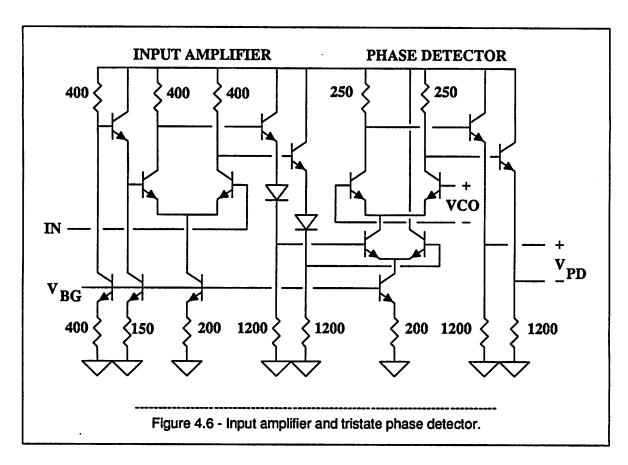

If a double-balanced modulator is used as the phase detector, the output is a replica of the VCO waveform when there is no input signal to the PLL as shown in Figure 4.2. Therefore, if the VCO does not have a 50 percent duty cycle, the phase detector output will have a DC-offset. A single-balanced modulator type circuit is proposed to eliminate this offset as shown in Figure 4.3. The differential output waveform can have three levels, hence this circuit is also called a tristate phase detector, [14]. Whenever there is no input signal, the phase detector output is ideally zero. Therefore, the VCO asymmetry has almost no effect on the tristate phase detector output for no input signal case. In the following para-

graphs, the static and dynamic performance of these two phase detector circuits will be compared in detail.

There are two parameters which define the static performance of a phase detector, its gain and DC-offset. First, let us assume that all the input transitions are present, i.e. the PLL input is a deterministic signal. It can be easily shown that the phase detector gain is:

$$K_{PD} = \frac{R_C I_{EE}}{\pi} \tag{4.2.1}$$

for a single-balanced modulator and

$$K_{PD} = 2 \frac{R_C I_{EE}}{\pi} \tag{4.2.2}$$

for a double-balanced modulator.