# Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# TECHNIQUES FOR OPTIMIZATION-BASED SYNTHESIS OF DIGITAL SYSTEMS

by

Srinivas Devadas

Memorandum No. UCB/ERL M88/54

12 August 1988

# TECHNIQUES FOR OPTIMIZATION-BASED SYNTHESIS OF DIGITAL SYSTEMS

#### Srinivas Devadas

#### **ABSTRACT**

A prototype framework which can automatically synthesize integrated circuits from behavioral descriptions has been developed. The system is characterized by the use of optimization tools at every level of the synthesis process to enhance the quality of the designs. The system proceeds through the various steps of hardware allocation, control specification, state assignment and combinational logic synthesis to produce optimized gate-level specifications. Formal verification and test strategies have been incorporated into the system.

Given a data flow specification, simulated-annealing-based algorithms which find a globally optimal placement of micro-instructions, thus producing an optimal datapath configuration, have been developed. Algorithms for state assignment of finite state machines targeted toward multi-level logic implementations have been proposed. A connection between multi-level and multiple-valued Boolean minimization has been established. Algorithms for Boolean decomposition, based on multiple-valued Boolean minimization, have been developed which decompose a PLA into a set of smaller interconnected PLAs such that the overall area of the resulting logic network is minimized. An efficient algorithm has been proposed for the verification of the equivalence of two sequential circuit descriptions at the same or differing levels of abstraction, namely at the register-transfer (RT) level, the State Transition Graph level or the logic level. An efficient deterministic sequential test pattern generation algorithm, effective for mid-sized sequential circuits, has been developed. This algorithm can be used in conjunction with an Incomplete Scan Design approach to test generation for large sequential circuits. Finally, the relationship between sequential logic synthesis has been explored and a connection between state assignment and the testability of a sequential machine has been established.

# elegio de especia deneral agrasse será que espersos. Nacembra a vivia el del

#### geografia e vogari

Language of the second of the **Dedicated to Lord Vishnu** in the action of the control of the second of the property of the **Dedicated to Lord Vishnu** in the action of the control of the second of the control of the control of the action of the control of the co

The problem of the state of the second secon

# **ACKNOWLEDGEMENTS**

I am indebted to my advisor Prof. Richard Newton for his friendship, guidance and unfailing support during my years at Berkeley. But for his enthusiasm and the inspiration he provided, much of this work would not have been possible.

I have greatly benefited due to my association and interaction with Professors Robert Brayton, Donald Pederson and Alberto Sangiovanni-Vincentelli. I thank them for their continuing interest in my research projects. I have also benefited from many discussions with Prof. Carlo Séquin of the Computer Science Department. Prof. Alberto Grünbaum of the Math Dept. was kind enough to serve on my thesis committee and read my dissertation.

I have had the good fortune of meeting many wonderful people at Berkeley. In particular, I would like to thank Tony Ma, my long time friend, research associate and office-mate, for things too numerous to enumerate.

Jeffrey Burns, George Jacob, Kartikeya Mayaram and Fabio Romeo have been, and will always be, good friends. I am especially grateful to Jeff and Karti for providing support during some difficult times.

I've had lots of great tennis games (the ones I won) with Bob Brayton, George Jacob, Theo Kelessoglou, Vedat Milor, Gordon Jacobs and Tom Quarles. I hope my constant aiming at Tom when he is near the net will not deter him from playing with me in the future!

Suresh Krishna, Kinson Ho, Su Tang and I have spent many fun-filled evenings in San Francisco and elsewhere. We remain good friends despite their constantly needling me about my car, my driving, my radio station, my choice of movies and...

Watson Chan, Randy Cieslak, Wayne Christopher, Abhijit Ghosh, Pramod Jain, Chuck Kring, Vijay Madisetti, Rick Spickelmier, Ruey-sing Wei and Albert Wang are a few of the great guys I've been lucky enough to meet over the years. Randy and Wayne, frequent dinner companions, introduced me to several nice restaurants around town. I thank Watson for putting up with me in his and Tony's apartment during my last two months at Berkeley.

I express my gratitude for the financial support that made this research possible. I acknowledge support from the Semiconductor Research Corporation in the summer of 1985 and the Digital Equipment Corporation in the summer of 1986, as well as the VAX-based computing environment I used to develop my experimental systems. I was supported in part by the Defense Advanced Research Projects Agency under contract N00039-86-R-0365 and in part by a grant from AT&T Bell Laboratories. While the work on testing described in this dissertation is not exactly what was intended when the AT&T-supported phase of the project began, their encouragement and support is gratefully acknowledged.

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                              | 1  |

|------------------------------------------------------|----|

| 1.1 Need for Synthesis Systems                       | 1  |

| 1.2 The Level of the Input Description               | 2  |

| 1.3 Inputs to Behavioral Synthesis Systems           | 3  |

| 1.4 Phases in Behavioral Synthesis Systems           | 5  |

| 1.5 Related Work                                     | 7  |

| 1.6 Summary                                          | 11 |

| CHAPTER 2: OVERVIEW                                  | 12 |

| 2.1 Input Description                                | 14 |

| 2.2 Datapath Synthesis                               | 14 |

| 2.3 Control Specification and Synthesis              | 16 |

| 2.3.1 State Assignment                               | 17 |

| 2.3.2 Multi-Level Logic Optimization                 |    |

| 2.4 Module Generation                                | 20 |

| 2.5 Place and Route                                  | 20 |

| 2.6 Verification                                     | 20 |

| 2.7 Testing                                          | 22 |

| 2.8 Relationship between Logic Synthesis and Testing | 23 |

| 2.9 Limitations and Future Work                      | 24 |

| 2.10 Organization of this Dissertation               | 25 |

| CHAPTER 3: AUTOMATED DATAPATH SYNTHESIS              | 26 |

| 3.1 Introduction                                     | 26 |

| 3.2 The Hardware Allocation Problem                  | 29 |

| 3.3 A Simulated Annealing Based Solution             | 42 |

|   | 3.4 Further Extensions                                       | 47  |

|---|--------------------------------------------------------------|-----|

|   | 3.5 Examples and Results                                     | 50  |

|   | 3.6 Synthesizing Pipelined Datapaths                         | 57  |

|   | 3.7 Conclusions                                              | 63  |

|   | CHAPTER 4: CONTROL SYNTHESIS: STATE ASSIGNMENT               | 65  |

|   | 4.1 Introduction                                             | 65  |

|   | 4.2 Preliminaries                                            | 66  |

|   | 4.3 Control Specification                                    | 68  |

|   | 4.4 State Assignment                                         | 69  |

|   | 4.4.1 Introduction                                           | 69  |

|   | 4.4.2 Need for new techniques of state assignment            | 73  |

|   | 4.4.3 State Assignment for Multi-level Logic Implementations | 74  |

|   | 4.4.4 The Basic Approach                                     | 77  |

|   | 4.4.5 Algorithms for Graph Construction                      | 82  |

| - | 4.4.6 The Embedding Algorithm                                | 89  |

|   | 4.4.7 Results                                                | 93  |

|   | 4.5 Conclusions                                              | 99  |

|   | CHAPTER 5: COMBINATIONAL LOGIC OPTIMIZATION                  | 100 |

|   | 5.1 Introduction                                             | 100 |

|   | 5.2 Preliminaries                                            | 103 |

|   | 5.3 Overall Strategy for PLA Decomposition                   | 104 |

|   | 5.4 Selection                                                | 109 |

|   | 5.5 Encoding                                                 | 114 |

|   | 5.6 Results                                                  | 119 |

|   | 5.7 Conclusions                                              | 122 |

|   | CHAPTER 6: VERIFICATION OF LOGIC CIRCUITS                    | 123 |

|   | 6.1 Introduction                                             | 122 |

| 6.2 Definitions of Equivalence                           | 125 |

|----------------------------------------------------------|-----|

| 6.2.1 Basic Definitions                                  | 125 |

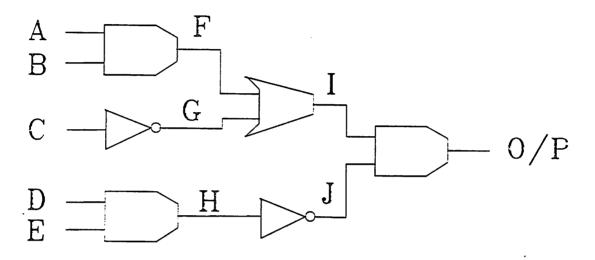

| 6.2.2 Combinational Logic Design Equivalence             | 127 |

| 6.2.3 Sequential Logic Design Equivalence                | 128 |

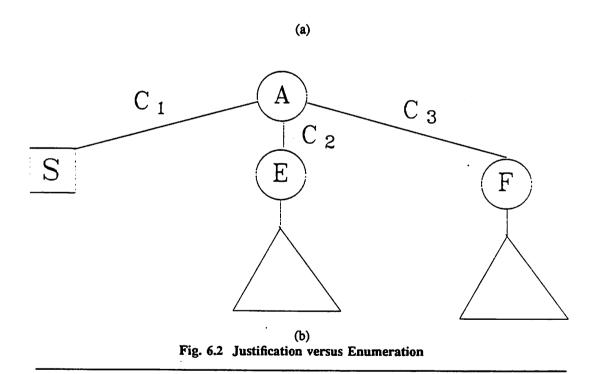

| 6.2.4 Segmentation: Single-Output Cone Extraction        | 130 |

| 6.3 Combinational Logic Verification Methods             | 130 |

| 6.3.1 Verification by Exhaustive Simulation              | 131 |

| 6.3.2 Verification using Testing Methods                 | 131 |

| 6.3.3 Symbolic Verification                              | 133 |

| 6.3.4 The LOVER Approach                                 | 134 |

| 6.4 Sequential Logic Verification                        | 136 |

| 6.4.1 Introduction                                       | 137 |

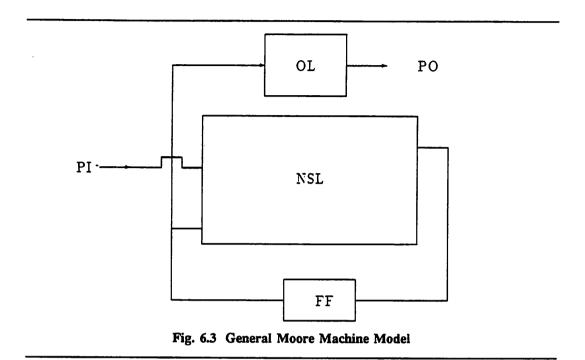

| 6.4.2 Extraction of Moore Machine State Graphs           | 139 |

| 6.4.3 Extraction from RTL Descriptions                   | 147 |

| 6.4.4 DFA Equivalence                                    | 150 |

| 6.4.5 Extension of Algorithms to Mealy Machines          | 155 |

| 6.4.6 Verification by Enumeration and Simulation         | 156 |

| 6.4.7 Examples and Results                               | 160 |

| 6.5 Conclusions                                          | 163 |

| CHAPTER 7: TESTING OF LOGIC CIRCUITS                     | 164 |

| 7.1 Introduction                                         | 164 |

| 7.2 The Sequential Testing Problem                       | 167 |

| 7.3 Previous Work in Sequential Testing                  | 168 |

| 7.3.1 The Extended D-Algorithm for Synchronous Circuits  | 168 |

| 7.3.2 Weighted random test-pattern generation            | 169 |

| 7.3.3 A new approach to sequential test generation       | 170 |

| 7.4 A Deterministic Sequential Test Generation Algorithm | 171 |

| 7.4.1 Introduction                                                    | 171   |

|-----------------------------------------------------------------------|-------|

| 7.4.2 The Test Generation Process                                     | 172   |

| 7.4.3 State Transition Graph Extraction                               | 175   |

| 7.4.4 The Fault-Excitation-and-Propagation Algorithm                  | 175   |

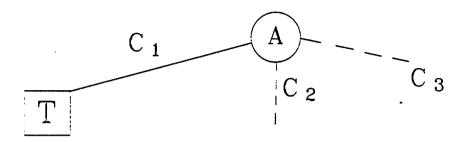

| 7.4.5 The State Justification Algorithm                               | 177   |

| 7.4.6 Detection of Redundant Faults                                   | 178   |

| 7.4.7 Results                                                         | 179   |

| 7.5 An Incomplete Scan Design Approach                                | 181   |

| 7.5.1 Introduction                                                    | 181   |

| 7.5.2 Overall Structure of Algorithm                                  | 182   |

| 7.5.3 The Heuristic Selection Process                                 | 184   |

| 7.5.4 Results                                                         | 186   |

| 7.6 Conclusions                                                       | 187   |

| CHAPTER 8: RELATIONSHIPS BETWEEN LOGIC SYNTHESIS AND TESTIN           | G 188 |

| 8.1 Introduction                                                      | 188   |

| 8.2 Relationship between combinational testing and logic minimization | 190   |

| 8.3 Preliminaries                                                     | 191   |

| 8.4 Fully and Easily Testable Moore Machines                          | 193   |

| 8.5 Fully and Easily Testable Mealy Machines                          | 199   |

| 8.6 Constrained State Encoding                                        | 201   |

| 8.7 Results                                                           | 202   |

| 8.8 Conclusions                                                       | 204   |

| CHAPTER 9: CONCLUSIONS                                                | 206   |

| REFERENCES                                                            | 210   |

| APPENDIX A                                                            | 224   |

# **CHAPTER 1**

# Introduction

A considerable research effort has focused on automating the integrated circuit (IC) design process over the past few years (e.g. [1] [2] [3] [4]). A variety of Computer-Aided Design (CAD) tools for the logic [5] [6] and physical design [7] of integrated circuits have been developed. It is clear that an integrated set of computer design aids coupled with an unified approach to data management is essential for VLSI design. To this end, research has focused on IC synthesis systems [8] i.e. systems which can automatically generate mask-level layout of integrated circuit chips from high-level, programming-language-like specifications. In this chapter, the necessity for, and the characteristics and requirements of, synthesis systems are presented and previous work in this area is reviewed.

# 1.1 Need for Synthesis Systems

There are integrated circuit applications, such as speech synthesis, bandwidth compression and recognition, modems and digital data transmission and digital control systems, where in order to achieve a complete and efficient integration of the system functions, it is necessary to design special-purpose chips which are to perform only a single task. Unfortunately, even though this can yield enormous savings in the size of the system and its power consumption, the design cost in both time and money can often be prohibitive. In addition, there are not many designers who have the expertise to design these system chips, which often require knowledge in both analog and digital circuit design as well as digital signal processing and computer architecture.

Semi-custom design techniques such as gate-arrays [9] and standard cells [10] offer an environment where faster turnaround can be guaranteed by design tools which can place and route complex functions in a short time. However, the task of logic design, i.e. specifying the gates and the interconnections which implement a certain behavior of the system, may still consume a large amount of design time.

Application-Specific Integrated Circuit (ASIC) synthesis systems have been proposed as a solution to the problem of automatic integrated circuit generation from a high-level behavioral or algorithmic description of the functions of the system to be implemented (e.g. [11] [12] [13] [8]). The demand for and use of ASIC synthesis systems is increasing at a rapid rate in the IC industry today.

# 1.2 The Level of the Input Description

The level of the input description to these synthesis systems varies – some systems require a relatively low register-transfer level description of the design, where information about required hardware resources (e.g. buses, arithmetic units) is explicitly available. For example, if the design in question is a pipelined datapath of a computer, the pipeline schedule has to be explicit in the input description. The overall structure of the circuit, i.e. the interconnection of the various modules can thus be inferred in a straightforward way from the description. Several *silicon compilers* have been developed (e.g. MACPITTS [13]), which automatically generate mask layout beginning from a register-transfer (RT) description of a datapath or a finite state machine (FSM) controller. These silicon compilers typically proceed through phases involving logic extraction, optimization and layout synthesis.

Behavioral synthesis systems, like the CMU-DA system [14] [1], begin from higher level algorithmic specifications where the behavior rather than the structure of the design is specified. The task of a behavioral synthesis system is thus more complicated than the typical silicon compiler task – a phase which allocates hardware resources and decides their spatial and temporal delineation (Section 1.3.1), thus specifying the structure of the design, precedes

the logic design and physical design phases. Complete synthesis systems also incorporate vitally important verification and test strategies. For example, synthesis and verification share a common methodology in the USC Design Automation System [15] [16].

It is important to note that the same language can be used in the context of specifying an input to a synthesis system at either of these two levels. For example, languages like ISPS [17] and BDS [18] are used for the functional specification (behavior) of a design or the register-transfer level specification of a design. Constructs in these languages are interpreted differently depending on the level of specification – e.g. variables in the language may be interpreted as existing registers or *values* which are to be stored and allocated in registers.

# 1.3 Inputs to Behavioral Synthesis Systems

Given that the input description specifies the behavior of the IC, different kinds of inputs to a synthesis system are possible. Possible inputs are purely architectural descriptions of the instruction sets of a general-purpose computers (with no information about the implementation). Another possibility would be software programs describing algorithms which are to be implemented in hardware. In either of these two cases, the task confronting the synthesis system is the same – datapaths executing these descriptions optimally, with associated control, have to be synthesized. However, the complexity in performing these tasks varies significantly, especially in the hardware resource allocation phase.

General-purpose computer descriptions are typically very detailed and and involve extensive bit manipulations. The instruction fetch-decode-execute loop takes only a few cycles and is usually constrained to be highly sequential. A lot of attention to detail must be paid in synthesizing from these descriptions and they tend to be uninteresting from a global optimization point of view. The decisions that can be taken during hardware allocation are tightly constrained by the input description – e.g. given the instruction set of a I-8080 microprocessor, there is virtually no parallelism between arithmetic operations and a second ALU in a hardware implementation would be useless. Control logic, on the other hand, is quite

complicated in large general-purpose computers.

One can also synthesize specialized processors which are designed to execute a given software description. For example, given a string hash table procedure or a MOSFET model evaluation routine, the goal would be to synthesize a datapath which would execute this program optimally. These descriptions are typically less detailed, less structured and not as constrained as compared to general-purpose sequential computer descriptions. Also, the associated control for these special-purpose machines is usually quite simple. Since parallelism in these programs is usually not explicitly specified, it must be extracted. A lot of potential for global optimization exists in synthesizing from these specifications – the allocation step (Section 1.3.1) involves many decisions and trade-offs. For example, the datapath executing a typical MOSFET model evaluation routine can use one to four ALUs. Depending on the execution speed and chip area constraints the optimal number of ALUs can be found during the resource allocation process.

# 1.3.1 Constraint Specification

Aside from the behavioral specification, the synthesis system is generally given constraints by the user which the final circuit implementation must satisfy. These constraints are typically constraints on the chip area (physical constraints) or on execution speed (delay constraints) of the resulting datapath, but may involve more complex considerations.

Depending on the needs of the user, the system may receive constraints of varying degrees and the effect of these constraints may be felt in different phases of the synthesis process. For example, a specific constraint on the number of ALUs or registers that the datapath can use affects the hardware allocation phase. Broader constraints, such as a constraint on the final chip area or a constraint on the clock period, are passed downward through all phases of design.

The specification of these constraints has traditionally been separated from the behavioral description. Constraints are typically tacked onto descriptions just before synthesis

and are rarely formalized. A unified framework allowing constraint-driven synthesis (propagating constraints across all synthesis tools) necessitates the development of a language supporting constraint specification across different levels of abstraction, namely behavioral, register-transfer and logic levels. Research, focusing on the development of such a language, is currently underway in various places, including Berkeley.

#### 1.4 Phases in Behavioral Synthesis Systems

#### 1.4.1 Hardware Allocation

The hardware allocation phase in behavioral synthesis, first described in [14], generates a datapath which can implement all the data transfers required by the original specification. This

step involves many decisions. For example, in a bus-style design, decisions involving both

the number and the interconnection of buses, arithmetic units and registers have to be made.

In the synthesis of pipelined computer datapaths, pipeline schedules satisfying required execution speed constraints must be found. A pipeline synthesis procedure was first published in

[19].

A wide variety of tradeoffs between execution speed and hardware resource cost of the synthesized datapath have to be explored in the allocation phase. Serial and parallel implementations of input data flow descriptions can result in vastly different datapath configurations. For example, a datapath, A, might be twice as fast as datapath B, but it might occupy three times the area.

## 1.4.2 Control Synthesis

After the hardware resource decisions have been taken and a datapath which implements the required data transfers has been synthesized, the associated control which, in conjunction with the datapath can execute the behavioral specification must be synthesized. Control can take the form of micro-code to be stored in ROM or RAM, a sequencer, or a FSM controller [20].

The specification of the control logic is easily derived given the original specification and the synthesized datapath. In some synthesis systems (e.g. [14]), micro-instruction scheduling decisions may be made at this stage, i.e. after datapath synthesis/hardware allocation. In other allocators like EMUCS [21], control specification is regarded as a by-product of data path synthesis and no major decisions are taken.

Optimization of control logic, be it in the form of a micro-coded ROM or PLA-based FSM, is a critical and difficult task. Micro-code compaction algorithms (e.g. [22]), logic optimization (see [23] for references), state assignment (e.g. [24] [25] [26]), input and output encoding algorithms (e.g. [26] [27] [28]) are necessary in synthesis systems for optimal control synthesis.

#### 1.4.3 Verification

It is important in this kind of environment to be able to verify that the optimization tools have not introduced any design errors during the synthesis process. The goal would be to formally verify that the generated layout implements the behavioral specification and satisfies the imposed constraints.

After the hardware allocation phase, logic verification tools (e.g. [29] [30]) can be used to verify equivalence of machine descriptions down to the gate/flip-flop level. This problem is NP-complete but a few algorithms have been shown to be practical even for large designs [29] [31] [32] [33]. Circuit and function extraction tools can be used to re-extract these gate/flip-flop descriptions from the synthesized layout to feed the logic verification tools. Timing

verifiers (e.g. [34]) can check that the constraints on the delay of the chip have been satisfied.

#### 1.4.4 Testing

After chip fabrication, a test strategy is required to ascertain functionality correctness. Testing can be a difficult task especially for unstructured sequential designs – combinational designs are easier to test. The testing task can be alleviated by using built in self-test (BIST) [35] techniques or using a constrained design style like Scan Design [36]. BIST involves adding extra logic to the various modules, in an effort to make the design easily testable. Scan Design, which has been widely adopted, makes all the sequential elements observable and controllable from the outside and transforms the sequential testing problem into a combinational logic testing problem.

Unfortunately, both these procedures have a substantial area penalty associated with them – a design using BIST or Scan Design may be 10-20% larger than the same design not using either [37]. Efficient test generation algorithms for sequential circuits are thus very attractive. Some algorithms have been proposed for sequential test generation in the past (e.g. [38] [39]).

#### 1.5 Related Work

Several synthesis systems operating from behavioral specifications have been developed in recent years. The CMU-DA [14] [1], Arsenic [40], Flamel [41] [42] and the USC Design automation project [15] [16] are typical examples and are reviewed here.

# 1.5.1 The CMU-DA System

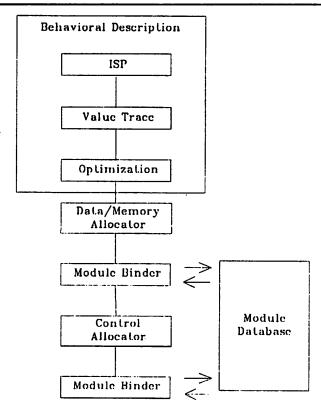

One of the earliest behavioral synthesis systems was the CMU-DA system [14], which began from the CMU RT-CAD project [43]. This system has evolved over the years and incorporates many computer-aided design tools for synthesizing circuits from high-level specifications [1] [21] [44] [45] [46] [47]. The basic design methodology underlying the CMU-DA system is shown in Figure 1.1.

The design methodology is hierarchical. Complexity is handled by describing a design at higher levels of abstraction which eliminates unnecessary detail, particularly during early phases of a design. In addition to taking a hierarchical approach, this methodology employs the concept of a design space. Given a set of metrics which characterize the quality of a design, the design space is defined as a Euclidean space whose coordinate axes correspond to the metrics. Alternative designs are represented by points in the design space. Through the study of a design space, the designer can efficiently direct his use of the design aids to produce better designs.

The design process begins with a behavioral specification of the digital system of to be designed in a hardware description language ISPS [48] [17]. Transformation heuristics similar to those used in compiler design are used to optimize the original description.

The next step in the design process is synthesizing from the behavioral description a structure in terms of physical modules which will implement the required behavior. This step is partitioned into datapath and control synthesis.

Datapath synthesis is further separated into an allocation and a module binding step.

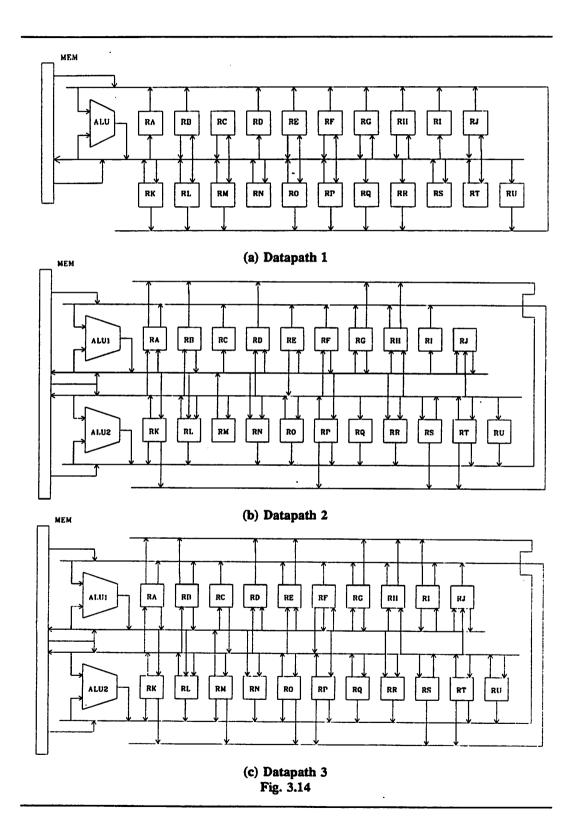

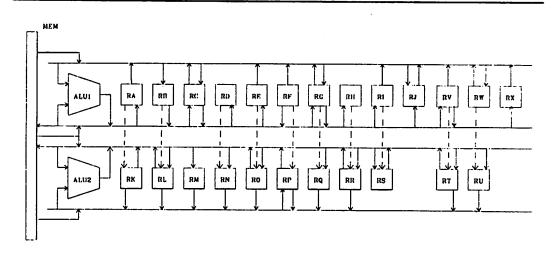

Many datapath allocators have been developed, employing various algorithms (e.g. [49] [50] [51] [52] [21] [46]). for generating the register-transfer structure. Different design styles can be employed, e.g. distributed, bus and pipeline style.

Control synthesis involves *control allocation* which produces an control engine evoking the datapath devices in an order consistent with the behavioral description and *module binding* which results in an implementation of the control engine which can be a ROM or a PLA.

While the ISP language is useful for describing the desired behavior of a system, such a description implies a certain data flow, through the use of assignment constraints, and a certain control flow, through the use of loops, conditionals and procedures. These flows can impact the resultant cost/performance characteristics of the design. In order to remove the bias which is inherent in an ISP description, the ISP description is transformed into an

alternative representation called the *Value Trace* or *VT* [53] [54]. A Value Trace is a connected graph made up of a series of blocks called VT-bodies [54]. Each VT-body represents a control environment in the ISP description which has a single entry point. The datapath and control allocators use the VT as their input rather than the ISP description.

This system operates from a module data base which is created using logic and layout optimization tools. Verification and test strategies are currently not incorporated into the system – however some of the optimizing transformations used in the system have been proved

Fig. 1.1 CMU-DA design methodology

to preserve behavioral equivalence [55].

#### 1.5.2 Arsenic

Synthesis in Arsenic, was originally developed at the University of Illinois [40] and continued at the University of California, Irvine [56], uses three steps across four levels of design, namely, algorithmic, register-transfer, abstract-cell and layout levels.

Arsenic begins synthesis with control step allocation, dividing the input specification into micro-instructions (MIs) at first, tentatively, so as to obtain maximum parallelism. The allocation of hardware is done for one MI at a time simultaneously with control step allocation.

The model of the control unit consists of a ROM and a sequencer.

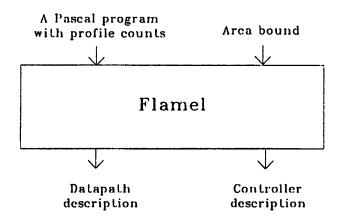

#### 1.5.3 Flamel

Flamel [41] [42] is a high-level hardware compiler which produces a hardware implementation of a given program minimizing the execution time of the implementation while meeting a user supplied constraint on the area of the hardware implementation. An overall picture of its operation is shown in Figure 1.2.

Flamel produces a datapath and a finite state machine controller. targeted for a bit-slice architecture. It performs a set of local block-level transforms on the input description in order to obtain maximum parallelism while meeting a resource (rather than a cost) bound. Depending on the user supplied area constraint, different kinds of time/area tradeoffs can be achieved.

# 1.5.4 The USC Design Automation Project

ADAM is a design automation system developed at USC, first described in [16], incorporating custom layout tools, and expert system for the design of testable circuits and a knowledge-based expert synthesis subsystem.

Fig. 1.2 Flamel's operation

The custom layout tools include a CMOS silicon compiler. The synthesis subsystem incorporates a clocking scheme and pipeline synthesizer [57] [19] and a datapath synthesis program [58].

Synthesis and verification share a common methodology in this system [15]. Verification is performed by verifying parts of the design which have been specified and synthesizing the missing elements.

# 1.6 Summary

In this chapter, provided an introduction to the problem of synthesizing integrated circuit chips from behavioral descriptions has been provided and some previous work in this area has been reviewed. In the next chapter, an overview of the behavioral synthesis system developed as part of this research will be presented. In the following chapters, a detailed description of the algorithms used in each phase of synthesis as well as the verification and test strategies incorporated into the synthesis system will be given.

# **CHAPTER 2**

# **Overview**

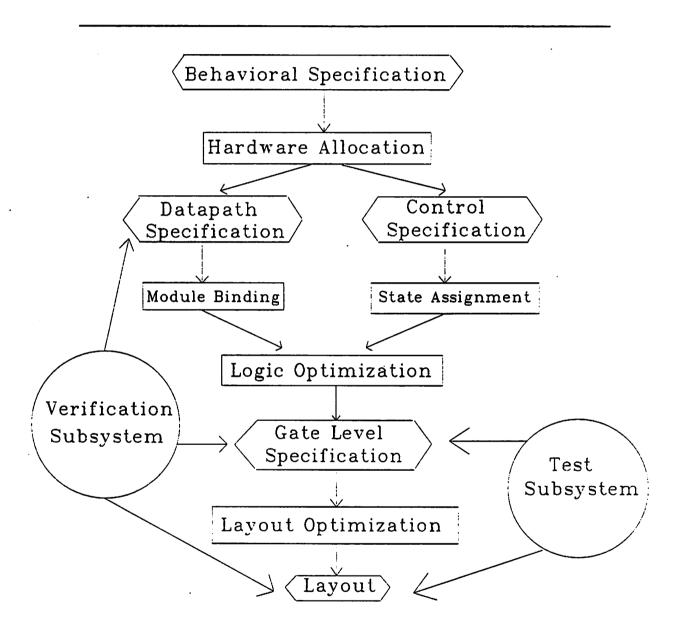

The behavioral synthesis system described in this chapter is the focus of this dissertation. A prototype framework which can synthesize automatically integrated circuits from behavioral descriptions has been developed and is illustrated in Figure 2.1. A number of tools for datapath and control synthesis have been developed – they have been incorporated into this system. Efficient verification algorithms have been developed to verify across the optimization tools in the synthesis pipeline. A strategy for testing the synthesized circuit has been developed. The relationship between logic synthesis and testability has been explored and a synthesis procedure to ensure fully testable sequential machines has been developed.

At this time, this system can be used for the synthesis of general-purpose computers, given instruction set specifications, or for the synthesis of specialized processors executing given algorithmic descriptions. Test cases described in this dissertation include a MOSFET model evaluation co-processor for a hardware simulation engine and digital signal processors. The system is characterized by the use of optimization tools at every level of the synthesis process to enhance the quality of the designs. These tools give the designer the ability to explore the complex tradeoffs in the design space and can be used to synthesize in different design styles. Rather than using a fixed library and incorporating module binding steps in synthesis, all logic blocks (ALUs, random logic and control) are assumed custom-designed using existing logic synthesis tools [6] [23] and existing layout generators [59] [60] [61] [62]. These blocks would then be placed and routed using a macro-cell layout system [63].

The input description, the tools developed for the datapath and control synthesis phases and some of the custom layout tools that have been used to complete the prototype system are described below. The verification and test strategies that have been developed and incor-

Fig. 2.1 Flowchart of the Behavioral Synthesis System

porated into the system are also described,

#### 2.1 Input Description

General-purpose computers have traditionally been specified in hardware description languages like AHPL [64], DDL [65] ISPS [17] and BDS [18], which are specifically designed for this purpose. More recently, a language called VHDL has become popular and appears to be an important new direction [66]. On the other hand, tasks like string hash table lookups are very easily written in programming languages like C [67] or PASCAL [68]. The input description to the system described here can be in either of these two forms – a BDS description of a computer or a C program implementing an algorithm.

This input description is translated into a intermediate textual description which consists of two parts. The first part is a data-flow description which specifies all the required data transfers between the program values. Some of these data transfers may be mutually exclusive due to conditional clauses in the input description. These relationships are specified in the data-flow description, but the control signals associated with these relationships are not. The second part of the description, which represents the control function, has this information. The partitioning of the description into separate control and data-flow is a common approach to the problem. The CMU-DA system was one of the first to take such an approach [14].

The translation to the intermediate description incorporates some optimizing transformations like dead code elimination and loop unwinding.

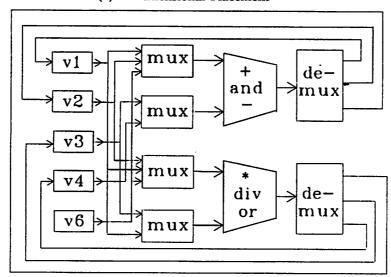

# 2.2 Datapath Synthesis

Given the intermediate description which specifies all the data transfers required, all precedence constraints between the various operations are extracted. Parallelism and sequentiality is explicitly introduced into the description following this analysis.

#### 2.2.1 Hardware Allocation

The hardware allocation step in datapath synthesis can be formulated as a two-dimensional placement problem of micro-instructions in space and time. The problem solved is to synthesize a datapath corresponding to the input data-flow specification such that a given, arbitrary function, f(T, C) of execution time T and hardware cost C, is minimized. The hardware costs are the sum total of the costs associated with registers, arithmetic units, buses and links in the datapath, based on required layout areas for placement and wiring. A given placement of micro-instructions corresponds to a unique datapath with a certain hardware cost and execution speed. Optimal conditional resource sharing is achieved by solving a constrained placement problem where disjoint instructions are allowed to occupy the same spatial and temporal location. Given a data-flow specification, simulated-annealing-based [69] algorithms have been developed, which find a globally optimal placement of micro-instructions, thus producing an optimal datapath configuration [70] [71].

Tradeoffs between execution speed and hardware cost of resulting datapaths are achieved by specifying different cost functions to the synthesis program. Thus, a variety of datapaths can be synthesized for any given input, with different time/area tradeoffs.

There are three main differences between this approach and others taken in the past [21] [58] [72] [41]. First, all the allocation subproblems, namely, arithmetic unit, register and interconnect allocation are tackled simultaneously, rather than sequentially or iteratively. Second, the optimization is completely global in nature, the entire sequence is optimized, and therefore the entire datapath. Third, I have used a probabilistic hill-climbing algorithm [73],

simulated annealing, which can avoid the traps of locally-minimum solutions.

## 2.2.2 Pipeline Synthesis

Pipeline synthesis entails both placement of the micro-instruction sequence as well as partitioning the sequence into phases. Hardware resources, like arithmetic units, cannot be shared across phases in a pipeline. The number of phases in a pipeline thus affects both the throughput and the hardware resources required.

The algorithms used in hardware allocation have been extended to handle pipelines. A partition of micro-instructions across phases and a placement of micro-instructions within each phase is found so as to minimize f(T, C), introduced earlier. Pipelining versus parallelism tradeoffs in the design space can be explored by varying the number of phases/partitions in order to vary throughput and hardware cost.

During synthesis, based on the required execution speed of the data path, decisions are made as to what the delay specifications of the different operations/micro-instructions should be. These specifications later become delay constraints on the logic synthesis and layout tools in the module generation subsystem.

# 2.3 Control Specification and Synthesis

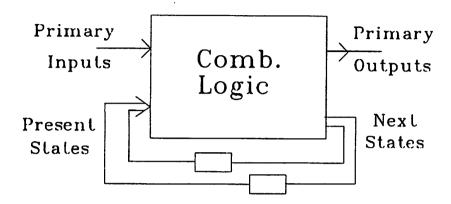

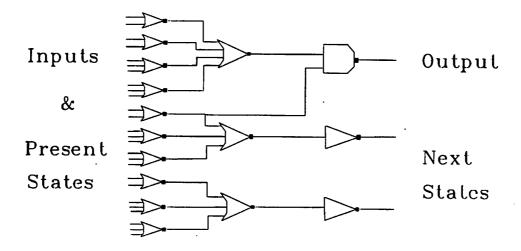

In this system, control specification is a by-product of the datapath synthesis step. After the hardware allocation step produces the placement of micro-instructions, sequences of values for the different control signals to the ALUs and registers can be easily found. Mutually exclusive operations will be executed based on the values of some control signal, usually the status bits of an ALU. A controller is synthesized as a PLA based FSM or using multi-level combinational logic and flip-flops.

Optimal control logic synthesis is a difficult task necessitating the use of powerful optimization algorithms. The FSM controller is typically implemented using combinational logic and feedback registers. The combinational logic can be implemented as a microcoded

ROM, PLA or as a multi-level logic network. Efficient state assignment algorithms can substantially reduce controller area. After state encoding, the resulting combinational logic specification is optimized in different ways depending on the targeted implementation. The goal of the state assignment step is to find an encoding of internal states of the FSM so as to minimize the final area of the machine *after* combinational logic optimization.

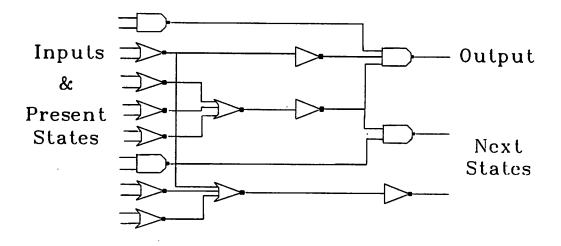

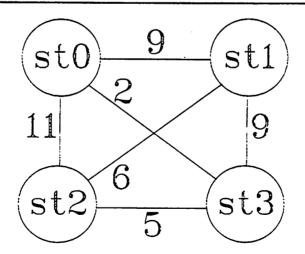

# 2.3.1 State Assignment

All previous techniques for optimal state assignment have been targeted toward two-level logic or PLA implementations [26] [28]. Algorithms for state assignment of finite state machines targeted toward multi-level logic implementations [74] [75] have been developed. These algorithms find a state assignment of a FSM which minimizes an estimate of the area used by a multi-level implementation of the combinational logic. The estimate considered here is consistent with the estimate used by multi-level logic optimization algorithms [76] [77] [6]: the number of literals in a factored form of the logic. The algorithms heuristically minimize the number of literals in the resulting combinational logic network after multi-level logic optimization.

Multi-level logic optimization programs like MIS [6] and SOCRATES [77] primarily use algebraic techniques for factorizing and decomposing the Boolean equations by identifying common sub-expressions. Heuristics have been proposed based on maximizing the number and size of common sub-expressions and minimizing the number of literals which exist in the Boolean equations that describe the combinational logic part of the FSM after the states have been encoded but before logic optimization. The state assignment algorithms find pairs or clusters of states which, if kept minimally distant in the Boolean space representing the encoding, result in a large number of common sub-expressions in the Boolean network.

Literal counts averaging 20-40% less than other state assignment techniques have been obtained.

A good encoding of input and output signals in the controller can substantially reduce its area. For example, depending on the codes assigned to different ALU operations, the controller would require different areas after logic optimization. Input and output encoding algorithms for two-level [28] and multi-level logic [74] implementations are used in this system.

## 2.3.2 Multi-Level Logic Optimization

Research done over the past 30 years has resulted in to efficient methods for implementing combinational logic in optimal two-level form using Programmable Logic Arrays (PLAs). However, many logic blocks are inappropriate for this kind of implementation. For example, there exist functions whose minimum two-level representation has  $2^n - 1$  product terms, where n is the number of primary inputs. In addition, even if a two-level representation contains a reasonable number of product terms, there are many cases in which a multi-level representation can be implemented in less area and generally as a much faster circuit.

Two basic methodologies have evolved for multi-level logic synthesis: 1) global restructuring, where the logic functions are "factored" into an optimal multi-level form with little consideration of the form of the original description (e.g. [6] [78]; 2) peephole optimization, where local transformations are applied to the user-specified (or globally-optimized) logic function (e.g. [79] [80]).

Global re-structuring procedures have been shown to be crucially necessary in producing optimal designs. Factoring algorithms have been proposed [76] [6] which are effective in partitioning complex logic functions.

The factoring algorithms proposed in [76] [6] are primarily based on algebraic techniques. Boolean factoring/division techniques can achieve superior results. However, techniques proposed so far for Boolean factoring and multi-level Boolean minimization (e.g [81]) require very large amounts of CPU time.

Multi-level logic networks can be realized by standard cell or gate array implementations. For small-medium (< 50 product terms) sized two-level representations the PLA is a very compact structure whose size is comparable (if not smaller) than a corresponding multilevel implementation. Topological optimization techniques like folding [82] can further reduce PLA area. A set of interconnected PLAs can thus exploit the layout compactness of PLAs without being constrained by the relative inflexibility of two-level logic structures.

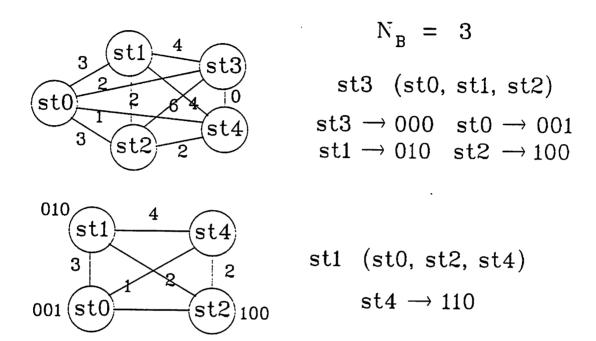

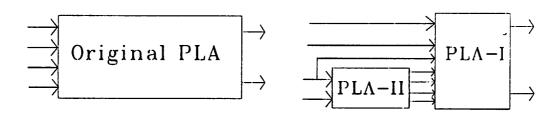

A PLA can be decomposed into a set of interconnected PLAs which feed into one another. To perform this decomposition, factoring algorithms are required. Algorithms for *Boolean decomposition* have been developed, which decompose a PLA into a set of smaller interconnected PLAs such that the overall area of the resulting logic network, deemed to be the sum of the areas of the constituent PLAs, is minimized [83] [84].

The proposed algorithms are based on multiple-valued minimization. Given a PLA, a subset of inputs to the PLA is selected. This selection step incorporates a new algorithm which selects a set of inputs such that the cardinality of the multiple-valued cover, produced by representing all combinations of these inputs as different values of a single multiple-valued variable, is much smaller than the original binary cover cardinality. A relatively small size for the multiple-valued cover implies that the number of good Boolean factors contained in this subset of inputs is large. The different cube combinations given by this subset of inputs are re-encoded to satisfy the constraints given in the multiple-valued cover, thus producing a binary cover for the original PLA whose cardinality equals the multiple-valued cover cardinality. The re-encoding process incorporates a new encoding algorithm which minimizes the number of bits required to satisfy all or a subset of the constraints produced by multiple-valued minimization.

These algorithms have produced excellent results over a wide range of examples. Total delays and/or areas of resulting PLAs after Boolean decomposition are invariably smaller than the original PLAs. This approach exploits the layout compactness of PLA structures to produce small, fast multi-level logic implementations. Large PLAs have been reduced by factors

of 2-3 in size and delay [83].

#### 2.4 Module Generation

Given the specification of a logic module, which may be an ALU, register file or random logic, the module generation subsystem generates a custom layout for the module. The logic synthesis tools used are, ESPRESSO, a two-level logic minimizer [85] and MIS, a multi-level logic optimization program [6]. Layout is generated after logic optimization in either standard cell, PLA or Gate Matrix styles. The layout optimization programs include TimberWolf, a standard cell placement program [61] and GENIE [86] a generalized array optimization program. Module generators are WOLFE [60], a standard cell place and route system which uses TimberWolf for placement and YACR [87] for routing, GEM [59] and OCTOPUS [62], Gate Matrix and PLA generators which use GENIE for topological optimization.

#### 2.5 Place and Route

Placement and routing of the logic modules is performed by the MOSAICO layout system. MOSAICO [63] is an integrated macro-cell layout system with tools for multi-layer channel routing [88], power and ground routing, channel definition and ordering, and floor-planning and placement. Tools in MOSAICO run and generate symbolic layout views of the design. A spacing program takes the results after detailed routing in symbolic form and produces mask geometries while guaranteeing that design rules are satisfied. The OCT data manager is used to store the design at each stage of the layout process.

#### 2.6 Verification

It is essential to be able to verify that the synthesized circuit implementation and the registertransfer level description actually represent the same machine. Several logic verification algorithms have been incorporated into the synthesis system for this purpose.

Many formal verification approaches have been taken to prove/disprove the equivalence of two combinational logic circuits, at the gate level and at differing levels (e.g. [89] [90] [91]

[92]). Only a few are practical for large circuits. Equivalence of combinational logic descriptions can be verified in the system described in this dissertation using the PROTEUS [29] logic verification package which has successfully verified large designs.

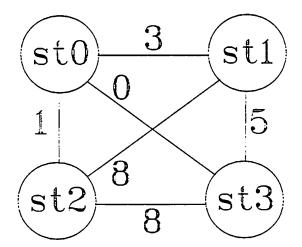

Very little work has gone into verifying sequential designs. An algorithm has been developed for the verification of the equivalence of two sequential circuit descriptions at the same or differing levels of abstraction, namely at the register-transfer (RT) level and the logic level [31]. The descriptions can represent general finite automata at the differing levels — a finite automaton can be described in an BDS-like language and its equivalence to a logic level implementation can be verified using my algorithm. Two logic level automata can be similarly verified for equivalence.

Previous approaches to sequential circuit verification have been restricted to verifying relatively simple descriptions with small amounts of memory. A new algorithm has been developed, which has been shown to be computationally efficient for much more complex circuits. The efficiency of this algorithm lies in the exploitation of don't care information derivable from the RTL or logic-level description (e.g invalid input and output sequences) during the verification process. Using efficient cube enumeration procedures at the logic level, I have been able to verify the equivalence of finite automata with a large number of states in small amounts of CPU time.

A two-phase enumeration-simulation algorithm has also been developed for verifying the equivalence of two logic level finite automata with the same or differing number of latches, given reset states or transfer sequences for the finite automata. This algorithm is as efficient as the general approach for verifying sequential machines described at different levels, but is much less memory-intensive. Using this algorithm, I have verified the equivalence

of finite state machines with more than 2500 states.

## 2.7 Testing

After the circuit has been synthesized, a test strategy is required to check that the chip satisfies its specification. A set of test sequences has to be found to pinpoint possible faults in the fabricated circuit, which is typically sequential in nature.

Test generation for sequential circuits is a difficult task. A popular approach to solving this problem is to make all the memory elements controllable and observable, i.e. Complete Scan Design [36] [37]. Scan Design approaches have been successfully used to reduce the complexity of the problem of test generation for sequential circuits by transforming it into one of combinational test generation, which is considerably less difficult. The design rules of Scan Designs also constrain the sequential circuits to be synchronous so that the normal operation of the sequential circuit is free of races and hazards. However, there are situations where the cost in terms of area and performance of Complete Scan Design is unaffordable. In addition, even though the general sequential testing problem is very difficult, there may be cases where test generation can be effective. Simply making all the memory elements scannable in a sequential circuit, without even first investigating how difficult the problem of generating tests for it is, could unduly incur unnecessary area cost.

Several approaches [93] [94] [39] [95] [96] [97] have been taken in the past to solve the problem of test generation for sequential circuits. They are either extensions to the classical D-Algorithm or based on random techniques [94] [96]. When the number of states of the circuit is large and the tests demand long input sequences, they can be quite ineffective for test generation. This is because no *a priori* knowledge of the length of the test sequence is available. In the extended D-Algorithm methods, a large amount of effort may be wasted in trying to find short sequence tests for faults that require long ones. Random testing techniques are based on continuous simulations and grading of test vectors according to simulation results. They can be very time consuming for difficult faults that have only a few long test sequences.

The new approach developed to test pattern generation [98] [99] [100] for sequential machines represents a significant departure from previous methods. First, using algorithms based on state space enumeration and information contained in a partial State Transition Graph (STG) of the machine, test sequences are generated to detect a large number of faults in the circuit. Then, an algorithm identifies a minimal subset of memory elements which if made scannable will result in easy detection of all remaining irredundant but difficult-to-detect faults. The identification of this subset is performed by analyzing the connectivity of the STG of the machine. Detection of all irredundant faults is guaranteed as in the Complete Scan Design case, but at much less area and performance cost, since much fewer lines, if any, need to be made observable.

#### 2.8 Relationship between Logic Synthesis and Testing

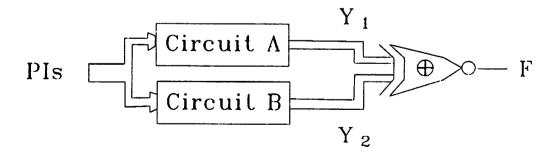

The relationship between combinational logic synthesis and test generation is well known – it has been comprehensively reviewed in [101] and [102]. In [81], a synthesis procedure which guaranteed fully testable irredundant combinational logic circuits was proposed. The tests for all single stuck-at faults in the combinational logic circuit are obtained as a by-product of the optimization procedure [81]. Equally intimate relationships between the more complicated problems of sequential circuit synthesis and test generation have been envisioned.

A synthesis and optimization procedure has been developed [103], which beginning from a State Transition Graph description of a Moore or Mealy finite automaton produces a 100% testable logic-level implementation of the machine. The test sequences for all single stuck-at faults in the machine can be derived using test generation algorithms on the combinational logic blocks of the machine.

I can show that a strong relationship exists between state assignment, logic optimization and testability of a sequential machine. A procedure of constrained state assignment and combinational logic optimization can ensure 100% testability for both Moore and Mealy finite state machines. Results obtained on benchmark examples show that the area penalties

incurred due to the constraints imposed during state coding and logic optimization are small. The performance of the resulting circuit is usually *better* than a unconstrained design (This is because one of the constraints imposed requires combinational logic partitioning in the machine).

#### 2.9 Limitations and Future Work

While the current system and the optimization tools in the system, described in the previous sections, represent significant advances and improvements in various areas, some limitations exist and should be addressed in the future.

A major limitation of datapath synthesis approaches, including the approach developed in this system, has to do with data-dependent loop exits. When loops are static and the number of iterations is known in advance, allocation algorithms can find an optimal schedule of operations that minimizes the hardware resource cost or a schedule that maximizes execution speed (or a combination of the two). However, allocation algorithms cannot solve the problem of finding an optimal schedule when the number of iterations in a loop is a variable, whose value is dependent on data inputs.

The state assignment algorithms presented in this dissertation produce significantly better results than other techniques, but are restricted in the sense that they model only the simple multi-level optimization of common cube extraction. Taking into account more complicated multi-level optimizations like common kernel extraction could improve the quality of results obtained. However, early approaches that use a kernel-only optimization strategy [104] have had limited success.

The algorithms for Boolean decomposition produce high-quality results and execute within reasonable CPU times for small to medium-sized circuits. Many steps in the algorithms have worst-case exponential time complexities. For large circuits, the CPU time requirements can become exorbitant. Also, the algorithms are presently restricted to begin from a two-level representation of a logic function. Developing fast algorithms for Boolean

decomposition, generalized to operate on multi-level circuits, represents a major challenge in combinational logic synthesis.

The deterministic sequential test generation algorithm developed [99] is considerably faster than algorithms proposed in the past. For datapaths, which are sequential circuits with a large number of latches, a State Transition Graph description is too large to store/generate and too cumbersome to manipulate. Different representations that are less memory intensive and which facilitate efficient state justification can speed up the test generation process.

The synthesis procedure of constrained state assignment that ensures fully and easily testable sequential machines is the first of its kind. Optimal combinational logic synthesis can ensure irredundant circuits without any area penalty. Optimal sequential synthesis procedures for fully testable non-scan sequential machines have not been proposed, at the time of this writing. Developing such procedures, represents a major theoretical challenge in this area.

# 2.10 Organization of this Dissertation

This dissertation is organized as follows. In Chapter 3, algorithms for hardware allocation for automatic datapath synthesis from behavioral descriptions are described. Problems of pipelined datapath synthesis are addressed. Control synthesis is the subject of Chapter 4 and 5. State assignment techniques for finite state machine controllers targeted toward multi-level logic implementations are described in Chapter 4. New algorithms for Boolean decomposition in multi-level logic optimization are described in Chapter 5. The verification and test subsystems in the behavioral synthesis system are described in Chapters 6 and 7 respectively. In Chapter 8, an optimization procedure which begins from a State Transition Graph description of a finite state machine and synthesizes a fully testable logic-level sequential machine is presented.

# **CHAPTER 3**

# **Automated Datapath Synthesis**

#### 3.1 Introduction

The goal of the datapath synthesis step in a behavioral synthesis system is to produce register-transfer (RT) level hardware designs from an architectural description of a computer or to produce an RT design which implements a given program described in a high-level language in hardware. Significant effort has gone into the development of techniques for automated datapath synthesis (e.g. [21] [41] [58] ) in recent years. However, even now, effective and versatile procedures are not available.

Initial work to tackle this problem included the development of a mathematical model for the datapath [49] to describe the conditions and relationships to be satisfied. Mixed integer-linear programming techniques were used. Unfortunately, even for very small specifications, the cost of generating a design exploded rapidly.

The expert system approach was taken in the DAA [45] [46] system. Design rules were collected, and based on these design rules, a rule-based data memory allocator was developed. As is the case with most rule-based techniques, only local optimization was possible and extensive changes could not be made to the input description to attain a globally optimal solution. Similar problems afflicted the allocators described and implemented in [47] [44]. Global optimization steps have been introduced into the expert system approach [105], but DAA has been used mainly to synthesize general-purpose computer datapaths where very little parallelism exists, and therefore little room for optimization during allocation.

A more global algorithmic approach to the allocation problem was first taken in [50] [52]. FACET is a automatic datapath synthesis program which minimizes the number of storage

elements, data operators and interconnection units. However, FACET performs these steps sequentially and independently of the following task(s). It thus does not provide for flexible area/time tradeoffs during allocation.

The USC MAHA system [58] uses critical path determination to perform hardware allocation. The heuristics used to guide scheduling are based on the concept of the *freedom* of an operation. A force-directed scheduling approach to hardware allocation has been taken in [72]. The optimization step is global and uses heuristics based on predecessor and successor *forces* on an operation. The different heuristics used in both these scheduling algorithms [58] [72] may result in locally-minimum solutions.

Synthesizing from arbitrary software descriptions (e.g. a MOSFET model evaluator in a circuit simulator) rather than the instruction-set specification of general-purpose computers offers considerably more room for optimization. As mentioned earlier, general-purpose computers tend to be rather uninteresting from an optimization point of view. Other than Trickey's work [41] [42] and synthesis of digital signal processor datapaths [19] [58], very little attention has been paid to the specialized processor synthesis problem.

In [42], the problem of extracting parallelism from a program and providing a maximal schedule of the operations in the program, while meeting a user-specified bound on each kind of processing unit(s), was addressed. In this chapter, I am concerned with the more general problem of hardware allocation, where the decisions on the number of processing units, storage elements and their interconnections are made; the scheduling problem is only a small part of the overall hardware allocation process.

In this chapter, new algorithms for the simultaneous cost/resource constrained allocation of registers, arithmetic units and interconnect in a datapath are presented. These algorithms operate under a wide variety of user-specified constraints on hardware resources and costs. There are three main differences between this approach and others taken in the past (e.g. [21] [58] [41]). First, all the allocation subproblems, namely, arithmetic unit, register and intercon-

nect allocation are tackled simultaneously, rather than sequentially or iteratively. Second, the optimization is global in nature, rather than the local optimizations of some previous approaches (e.g. [21]). The entire sequence is optimized and therefore the entire datapath. Third, a probabilistic hill-climbing algorithm [73], simulated annealing, which can avoid the traps of locally-minimum solutions, has been used. While simulated annealing is a general approach to combinatorial optimization, the key to its successful use in solving the hardware allocation problem has been the development of a multivariate formulation of this problem, along with a robust cost function, annealing schedule and an appropriate move set.

The hardware allocation problem in automatic datapath synthesis can be formulated as a two-dimensional placement problem of micro-instructions in space and time. The problem solved is to synthesize a datapath corresponding to the input data flow specification such that a given, arbitrary function of execution time and hardware cost, f(T, C), is minimized. The hardware costs are the sum total of the costs associated with registers, arithmetic units, buses and links in the datapath, based on required layout areas for placement and wiring. A given placement of micro-instructions corresponds to a unique datapath with a certain hardware cost and execution speed. Optimal conditional resource sharing is achieved by solving a constrained two-dimensional placement problem where disjoint instructions are allowed to occupy the same spatial and temporal location. Given a data flow specification, algorithms are presented which find an optimal placement of micro-instructions, thus determining the spatial and temporal delineation of resources and producing an optimal datapath configuration.

The datapath synthesis problem is formulated here as one of two-dimensional placement of micro-instructions and modifications to incorporate conditional resource sharing are presented. Given this formulation, a simulated-annealing-based approach to solve the allocation problem is presented in Section 3.3. These algorithms are extended to handle looping constructs present in general software programs in Section 3.4. Results and illustrative examples, including the synthesis of a specialized processor datapath for MOSFET model evalua-

tion, are presented in Section 3.5. Extensions to synthesize some forms of pipelined datapaths are described in Section 3.6.

#### 3.2 The Hardware Allocation Problem

In this section, the algorithms used in the allocation process are described. These algorithms take the architectural description of the machine or a software program and automatically synthesize the datapath corresponding to that description under specified hardware constraints and costs. In Section 3.2.1, some definitions are given. The input description used is described in Section 3.2.2. Basic allocation problems are described in Section 3.2.3, and the formulation of the datapath synthesis problem as a placement problem is presented in Sections 3.2.4-5. The cost function for this placement problem is described in Section 3.2.6. In Section 3.2.7, the placement formulation is extended to incorporate conditional resource sharing.

#### 3.2.1 Basic Definitions

A micro-instruction is deemed to have two coordinates, a spatial coordinate and a temporal coordinate. The spatial coordinate corresponds to the arithmetic unit that the micro-instruction is executed on. The temporal coordinate corresponds to the clock cycle that the micro-instruction begins to be executed. A space-time slot corresponds to a spatial and temporal coordinate pair. A time slot corresponds to a temporal coordinate and all spatial coordinates. A space slot corresponds to a spatial coordinate and all temporal coordinates. Note that a micro-instruction may take multiple clock cycles to execute. It will be assumed for the purposes of this section that a micro-instruction executes in one clock cycle. However, this constraint will be relaxed in Section 3.4.

Conditional clauses may exist in the input description. Conditional clauses specify mutual exclusion relationships between micro-instructions. If during a pass through a code sequence, the execution of micro-instruction A implies that micro-instruction B will not be executed in the same pass, then A and B are deemed to be mutually exclusive. Two micro-

instructions can occupy the same space-time slot if and only if they are mutually exclusive.

A two-dimensional placement of instructions specifies spatial and temporal coordinates for each micro-instruction.

The datapath that is synthesized is a clocked sequential circuit, with an associated finite state machine controller. It is assumed that all ALU ports are latched.

# 3.2.2 Input Description

The behavioral description to be synthesized from can be a description of the instruction set of a computer or the description of an algorithm in a subset of C. In either case, the description is converted into a code sequence where parallelism, sequentiality and mutual exclusion are explicitly stated. During this transformation, various compiler-like optimization techniques (e.g. dead code elimination, constant folding) are used. The code sequence produced only has information about the data transfers required between program values. The control signals which initiate these data transfers are not explicitly stated. This control signal information is used only when the specification of the state machine controller for the datapath has to be derived.

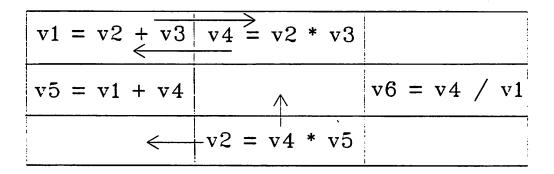

The serial blocks are due to the dependences associated with any description. Mutual exclusion is a result of the conditional clauses in the input description. An example of an input sequence is shown in Figure 3.1, with serial, parallel and disjoint blocks, which are the means of representing sequentiality, parallelism and mutual exclusion respectively. Each operation is represented in a lisp-like syntax given by (op oper1 oper2 .. operN result), where op is any arithmetic or Boolean operator. An additional kind of block is the implic block. Parallelism or sequentiality are not explicitly stated in the implic block – they are automatically derived by checking for data dependences prior to hardware allocation.

The INITIAL and FINAL declarations imply that the following variables are live in the beginning and the end of the sequence respectively. The SYMMETRIC declaration

```

(serial

(parallel

(add x1 y1 z1)

(add x2 y2 z2)

)

(parallel

(mult z1 y3 z3)

(minus z2 y4 z4)

)

(disjoint

(divide z3 x3 z5)

(divide z4 x4 z5)

)

)

INITIAL x1 x2 y1 y2

FINAL z5

SYMMETRIC mult add

```

Fig. 3.1 Input Description

enumerates all the operations whose operands are interchangeable.

## 3.2.3 Basic Allocation Problems

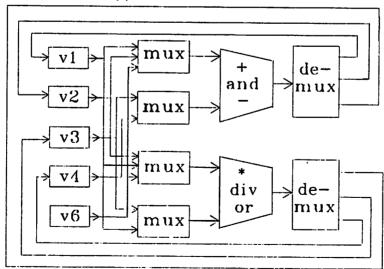

The hardware allocation process consists of a variety of subproblems. Register allocation deals with allocating variables in the given description to a minimum number of registers. Arithmetic unit allocation entails scheduling operations on a minimum number of ALUs, meeting a cost or an execution time constraint. During the allocation, an optimal grouping of arithmetic operators within each ALU is also found. For instance, one might have two ALUs, one performing arithmetic operations and the other performing Boolean operations. Typically, one would like each of the ALUs to perform disjoint sets of operations, but this is not always possible. Lastly, interconnect allocation deals with implementing the sets of data transfers required in each time frame and allocating buses and links or multiplexor and de-multiplexor connections in the datapath.

The basic tradeoff in hardware allocation is between serial and parallel implementations of data flow descriptions. Given an input code sequence, one can synthesize a maximally parallel datapath which is expensive in terms of hardware resource cost and uses a large number of registers and arithmetic units. On the other hand, one can synthesize a cheap, serial datapath with a single ALU, which is likely to take a lot longer to execute the same task. Hardware resource cost used in this context generally represents the layout area required to implement the different modules in the datapath after placement and wiring issues have been taken into account. Depending on the user's objective function, the optimal datapath configuration will lie somewhere between these two extremes. Thus, the allocation process must trade off hardware resource cost against the execution time of the code sequence in an effort to find an optimal solution.

## 3.2.4 A subproblem

First, a subproblem in the allocation process is defined and solved.

Given a code sequence with singly-assigned variables and precedence constraints between operations, assign the code operations to M ALUs so a given, arbitrary function of the number of registers required,  $N_r$ , and the execution time, T,  $f(T, N_r)$ , is minimized.

Since the datapath is a clocked sequential circuit, a maximally parallel description would use lots of registers, but would execute the fastest. A completely serial description would require a minimal number of registers, but would be slow. An algorithm based on clique partitioning presented in [50], optimizes the number of registers with a fixed code sequence schedule, while the goal here is to find the optimal sequence exploiting the extra degree of freedom of being able to change the schedule.

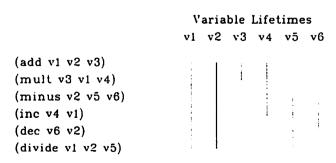

Given a code sequence the lifetimes of all the variables can be calculated. The *lifetime* of a singly assigned variable is the duration between its assignment and last use. The number of registers required would be proportional to the overlap of the live periods of the singly-assigned variables, or to put it differently, the number of registers required is the *maximal*

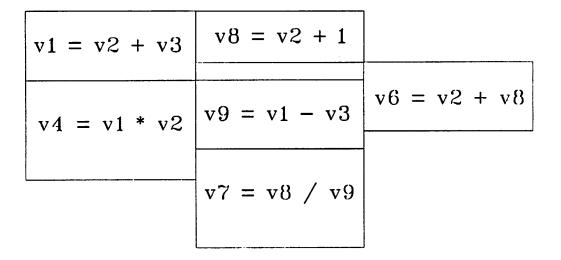

density of variable lifetimes across the entire sequence. This is illustrated in Figure 3.2.

Disjoint variables are those whose lifetimes do not overlap. The allocation of registers to singly-assigned variables entails finding the best possible grouping of disjoint variables in sets so as to minimize the number of sets.

There is freedom in the ordering of the code operations as long the precedence constraints are not violated and the constraint on the number of processing units is satisfied. Given a code sequence exploiting this freedom can result in a smaller set of registers being required. This is illustrated in Figure 3.3. In Figure 3.3(a), an example code sequence being executed on a single ALU is shown. Without changing the order of the operations in the code sequence, the minimum number of registers required is 4, as shown in Figure 3.3(b). Allowing re-ordering of operations within the sequence produces a 3 register solution in Figure 3.3(c).

Finding the optimal ordering of operations within a sequence, so as to allocate a minimum set of registers, reduces to the *PLA multiple folding problem*. The goal is to try to find an ordering of the rows (which correspond to the code operations) under certain ordering constraints (constraints due to dependences and processors) such that the maximum number of disjoint columns (each column corresponds to the lifetime of a variable) can be coalesced (the

Fig. 3.2 Densities of Variable Lifetimes

v1 = v2 + v3

v4 = v2 - v3

v5 = v1 \* v2

v6 = v4 and v3

v7 = v5 or v6

#### (a) Code sequence

R1 = R2 + R3

R4 = R2 - R3

R1 = R1 \* R2

R4 = R4 and R3

R4 = R1 or R4

#### (b) Register allocation without re-ordering

R1 = R2 + R3

R1 = R1 \* R2

R2 = R2 - R3

R2 = R2 and R3

R3 = R1 or R2

# (c) Register allocation with re-ordering Fig. 3.3

maximal number of variables can be merged). As mentioned earlier, there is a tradeoff between minimizing the execution time (the number of rows) and minimizing the number of registers (the number of columns). Therefore, in the general case of minimizing a function of execution time, T, and the number of registers,  $N_r$ , i.e.  $f(T, N_r)$ , an attempt is made to find an optimal aspect ratio of the PLA.

The PLA folding problem has been effectively solved using graph heuristics [106], simulated annealing [86] and exact branch and bound techniques [107]. These techniques can be used to solve the problem of register allocation as well. However, this formulation is merely representative of one part of the entire datapath synthesis process. An extended formulation is

now presented.

## 3.2.5 Formulation of the Entire Data Path Synthesis problem

The approach to synthesize a datapath described here is to give a general procedure which minimizes a given, arbitrary function of execution time and hardware cost. The entire cost of a datapath can be represented as:

$$C = p1 * (N_{alu}) + p2 * (T_{exec}) + p3 * (N_{reg}) + p4 * (N_{bus})$$

where  $N_{alu}$ ,  $N_{reg}$  and  $N_{bus}$  are the number of arithmetic units, registers and buses used in the design, respectively, and  $T_{exec}$  is the time required by the implementation to execute the given code sequence. The costs of the ALUs, registers and interconnect, given by the parameters p1 through p4, can be estimated taking into account layout area, placement and wiring issues. A procedure which minimizes C under constraints would synthesize an optimal datapath.

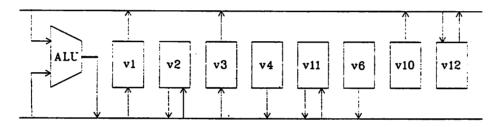

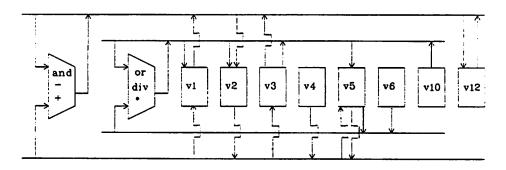

This problem can now be formulated as a placement problem of code operations in two dimensions, that of space and time. A given spatial and temporal placement of code operations represents a datapath and has a unique cost C. A two-dimensional grid where each vertical slice corresponds to a processing unit/ALU and each horizontal slice corresponds to a time slot is constructed, as shown in Figure 3.4. Code operations are placed in grid locations corresponding to a ALU and a time slot, under precedence constraints, due to the dependences associated between them. Nets connect the occurrences of variables in the code operation and also connect variables to arithmetic units in corresponding slots. The internal position of the variable in the code operation is also specified, e.g. in a binary ADD a variable can be in the first or second positions for a given configuration.

The execution time is related directly to the number of occupied horizontal time slots. The horizontal time slots may be of different widths, the widths would be proportional to the delays corresponding to the code operations occupying that slot. The issue of operations having different associated delays is elaborated on in Section 3.4.

| SPACE/TIME | ALU1             | ALU2              | ALU3          |

|------------|------------------|-------------------|---------------|

| TIME1      | (add x1 y1 z1)   | (mult x2 y2 z2)   | (equal x3 z3) |

| TIME2      | (minus z1 x2 k1) | (divide z2 x1 k2) |               |

| TIME3      | (or k1 z2 l1)    |                   | (inc k2 12)   |

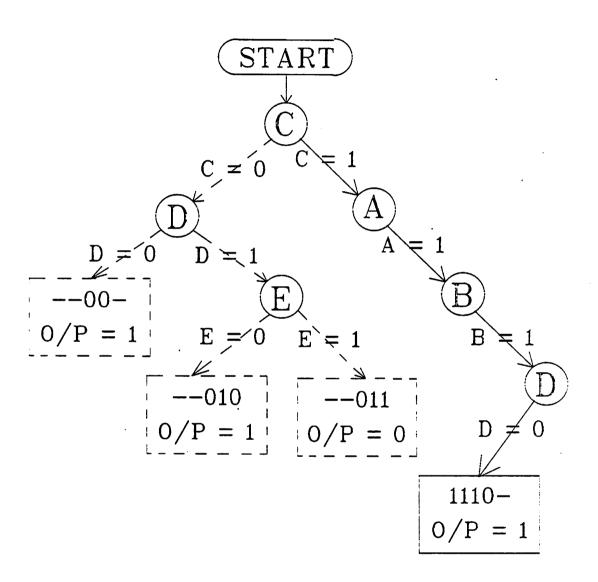

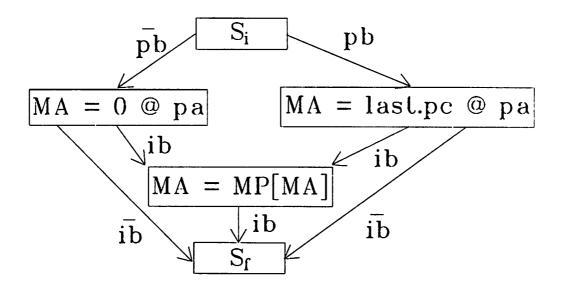

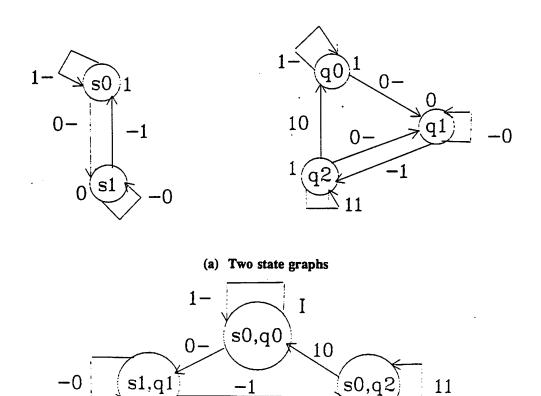

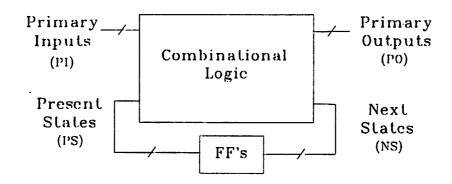

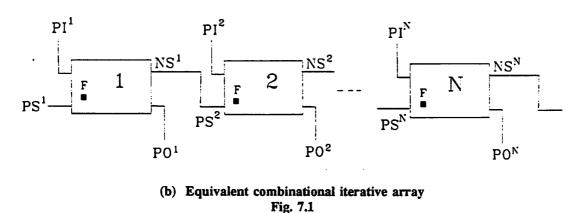

Fig. 3.4 2-Dimensional Grid of code operations