# Copyright © 1988, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# ALGORITHM AND ARCHITECTURE DESIGNS FOR HIGH SPEED DIGITAL SIGNAL PROCESSING

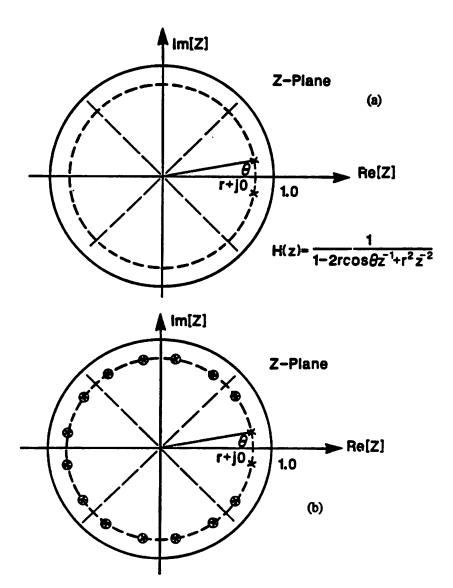

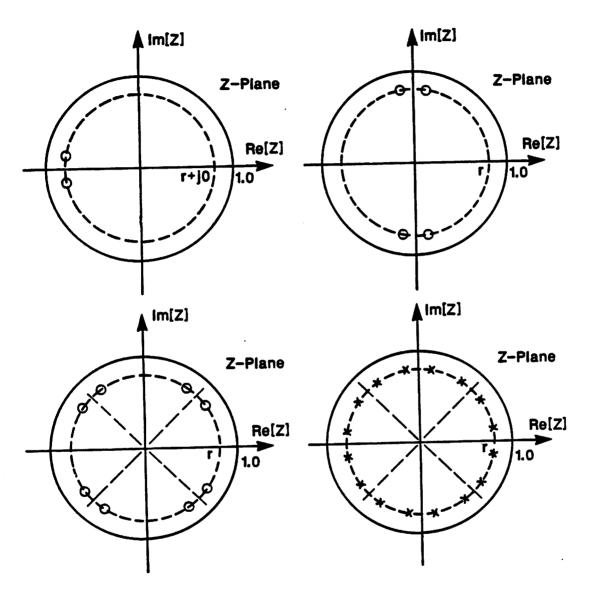

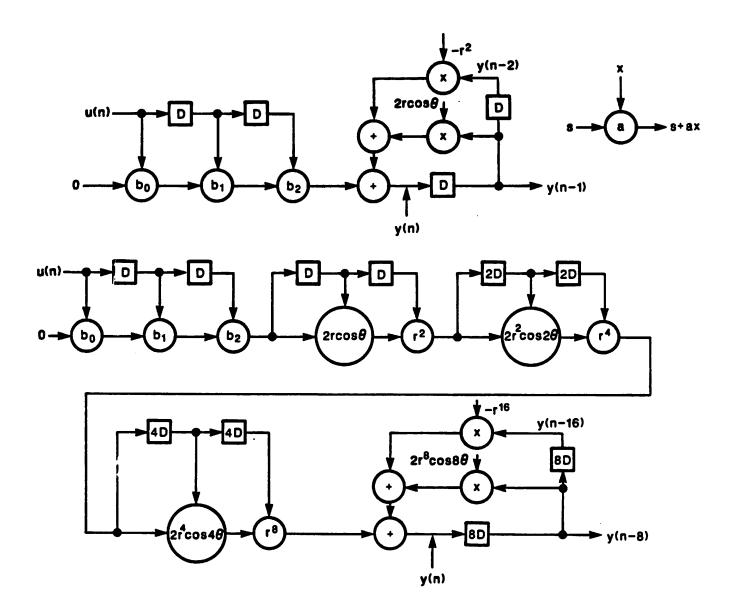

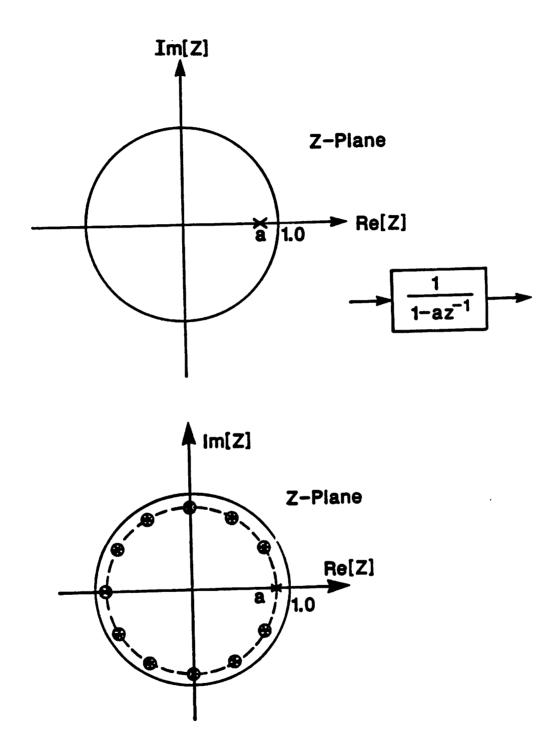

by

Keshab K. Parhi

Memorandum No. UCB/ERL M88/61

27 September 1988

# ALGORITHM AND ARCHITECTURE DESIGNS FOR HIGH SPEED DIGITAL SIGNAL PROCESSING

by

Keshab K. Parhi

Memorandum No. UCB/ERL M88/61

27 September 1988

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# ALGORITHM AND ARCHITECTURE DESIGNS FOR HIGH SPEED DIGITAL SIGNAL PROCESSING

Ph.D.

## Keshab K. Parhi

Department of EECS

#### **ABSTRACT**

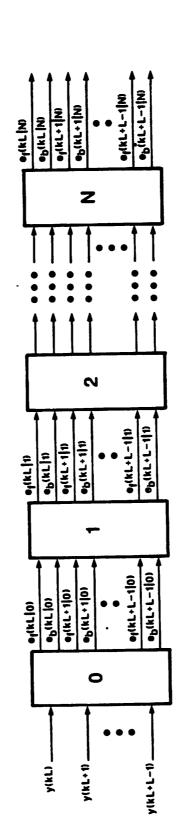

This thesis explores systematic approaches to design of high-speed algorithms and architectures for real-time signal and image processing in general, and for one- and two-dimensional recursive and adaptive digital filters in particular. First we address rate-optimal software-programmable multiprocessor implementation of signal processing algorithms described by data-flow programs. We introduce the notion of perfect data-flow programs, and prove that fully-static rate-optimal multiprocessor schedules can always be constructed for such programs using no retiming at all. We study properties of program unfolding transformations, and derive an expression for the optimum unfolding factor to reduce any data-flow signal processing program to an equivalent perfect data-flow program, which can then be scheduled rate-optimally in a fully-static manner. An upper bound on the number of processors to achieve a rate-optimal schedule is also derived.

Next we develop high-speed algorithms for one- and two-dimensional recursive and adaptive digital filters. Look-ahead algorithms are proposed to change the basic linear filter structures (while maintaining identical input-output behavior) and to create additional concurrency. Scattered look-ahead and decomposition algorithms are used to implement high-speed recursive and adaptive digital filters using fine-grain pipelining, with logarithmic increase in hardware for a linear increase in the sample rate. A

2

technique of incremental output computation is proposed and used to derive incremental

block digital filters of linear multiplication complexity in block size, as opposed to the

aquare multiplication complexity in all previous block filter structures. Two-dimensional

recursive digital filters inherently possess large amount of concurrency. An index map-

ping transformation is used to exploit this concurrency, and to derive fine-grain pipelined

and one-dimensional block implementation of two-dimensional recursive digital filters.

Look-ahead and incremental computation techniques are extended to two-dimensions,

and are used to derive an efficient incremental two-dimensional recursive block digital

filter architecture.

Look-ahead and program unfolding transformations are performed on general itera-

tive data-flow signal processing programs to increase concurrency. These transforma-

tions are useful where the designed algorithms are unable to meet the real-time require-

ments of the target application.

David G. Messerschmitt)

Chairman of Committee

# **ACKNOWLEDGEMENTS**

I am deeply indebted to my research advisor Prof. David G. Messerschmitt for his continuous advice, support and encouragement, and to Prof. David A. Hodges for his timely encouragement throughout the course of my study at Berkeley. I am also grateful to my thesis co-amittee members Prof. Robert W. Brodersen, and Prof. Robert Leachman.

I have benefited from interactions with many individuals; they include (in alphabetical order) Graham Brand, Wen-Lung Chen, Mordechay Ilovich, Rajeev Jain, Edward Lee, Vijay Madisetti, Teresa Meng, Rajiv Ramaswami, and Gilbert Sih of U.C. Berkeley; David Schwartz of Georgia Institute of Technology; Peter Cappello and Cheng-Wen Wu of U.C. Santa Barbara; Bryan Ackland, Mehdi Hatamian, Adriaan Ligtenberg, and Sailesh Rao of AT&T Bell Laboratories, Holmdel; and Hu Chao, Jung Herng Chang, Jean-Paul Jacob, Fred Mintzer, and Gideon Shichman of IBM T.J. Watson Research Center, Yorktown Heights; and to all of them I remain thankful. I am most grateful to the IBM Corporation for providing me an IBM fellowship and a summer job in 1986, and to the AT&T Bell Laboratories for offering me a summer job in 1987. Without the support from Bell Laboratories, the algorithms in this thesis could never have been implemented on IC chips. Finally, I am grateful to my family members, relatives and friends for their love, support and encouragement.

The research carried out in this thesis was supported by a U.C. Regents Fellowship, an IBM Graduate Fellowship, the Defense Advanced Research Project Agency monitored by Naval Electronics Systems Command (under contract number N00039-86-R-0365), and the National Science Foundation (under contract number DCI-85-17339).

# TABLE OF CONTENTS

| CHAPTER 1: INTRODUCTION                       |            |

|-----------------------------------------------|------------|

| 1.1. INTRODUCTION                             | 1          |

| 1.2. CONTRIBUTIONS OF THE THESIS              | 3          |

| 1.3. REFERENCES                               | 11         |

| CHAPTER 2: PROGRAM UNFOLDING                  |            |

| 2.1. INTRODUCTION                             | 13         |

| 2.2. ITERATIVE DATA-FLOW PROGRAM MODEL        | 16         |

| 2.3. ITERATION BOUND                          | 20         |

| 2.4. RETIMING                                 | 21         |

| 2.5. PERFECT DATA-FLOW PROGRAMS               | 23         |

| 2.6. UNFOLDED DATA-FLOW PROGRAM GRAPHS        | 35         |

| 2.7. FULLY-STATIC RATE-OPTIMAL SCHEDULING     | 43         |

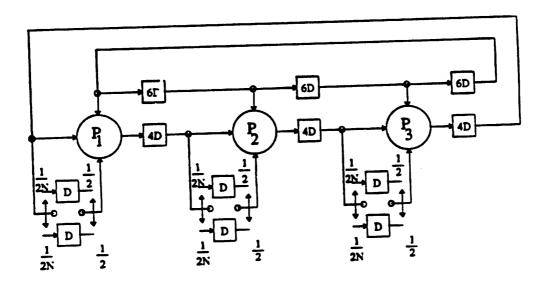

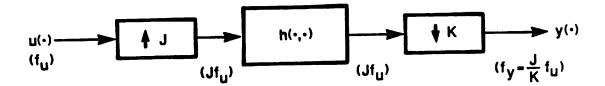

| 2.8. MULTIPLE-RATE DFGS                       | <b>5</b> 1 |

| 2.9. NON-HOMOGENEOUS PROCESSOR SCHEDULING     | 5          |

| 2.10. CONCLUSION                              | 59         |

| 2.11. REFERENCES                              | 6          |

| CHAPTER 3: PIPELINING IN RECURSIVE FILTERS    |            |

| 3.1. INTRODUCTION                             | 6          |

| 3.2. ITERATION BOUND REVISITED                | 6          |

| 3.3. PIPELINE INTERLEAVED DIGITAL FILTERS     | 6          |

| 3.4. PIPELINING DIRECT FORM RECURSIVE FILTERS | 8          |

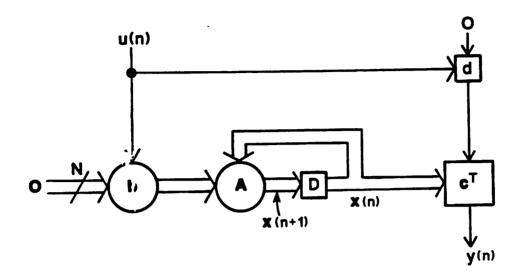

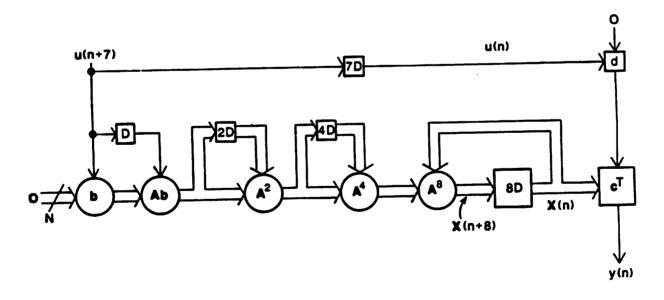

| 3.5. PIPELINING IN STATE SPACE FORM FILTERS   | 10         |

| 3.6. CONCLUSIONS                                      | 112 |

|-------------------------------------------------------|-----|

| 3.7. APPENDICES                                       | 113 |

| 3.8. REFERENCES                                       | 120 |

| CHAPTER 4: PIPELINED INCREMENTAL BLOCK FILTER         |     |

| 4.1. INTRODUCTION:                                    | 123 |

| 4.2. DIRECT FORM FLOCK FILTERS                        | 128 |

| 4.3. STATE SPACE BLOCK DIGITAL FILTERS                | 135 |

| 4.4. DIRECT FORM PIPELINED BLOCK RECURSIVE FILTERS    | 158 |

| 4.5. STATE SPACE FORM PIPELINED BLOCK DIGITAL FILTERS | 164 |

| 4.6. CONCLUSION                                       | 168 |

| 4.7. APPENDICES                                       | 169 |

| 4.8 REFERENCES                                        | 174 |

| CHAPTER 5: ADAPTIVE DIGITAL FILTERS                   |     |

| 5.1. INTRODUCTION                                     | 176 |

| 5.2. LOOK-AHEAD IN TIME-VARYING FILTERS               | 181 |

| 5.3. HIGH SAMPLE RATE ADAPTIVE FILTERING              | 185 |

| 5.4. COMPLEXITY AND LATENCY                           | 190 |

| 5.5. IMPLEMENTATION METHODOLOGY TRADEOFFS             | 192 |

| 5.6. CONCLUSIONS                                      | 197 |

| 5.7. REFERENCES                                       | 198 |

| CHAPTER 6: DIGITAL FILTERS FOR IMAGE PROCESSING       |     |

| 6.1. INTRODUCTION                                     | 200 |

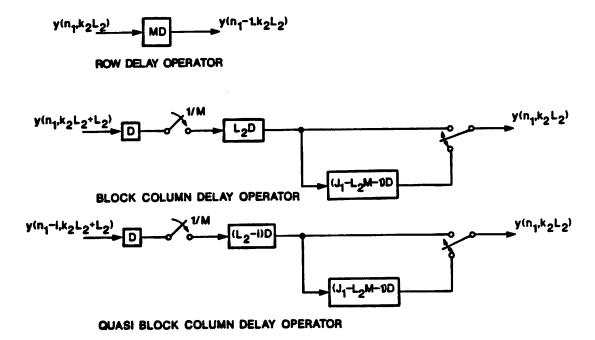

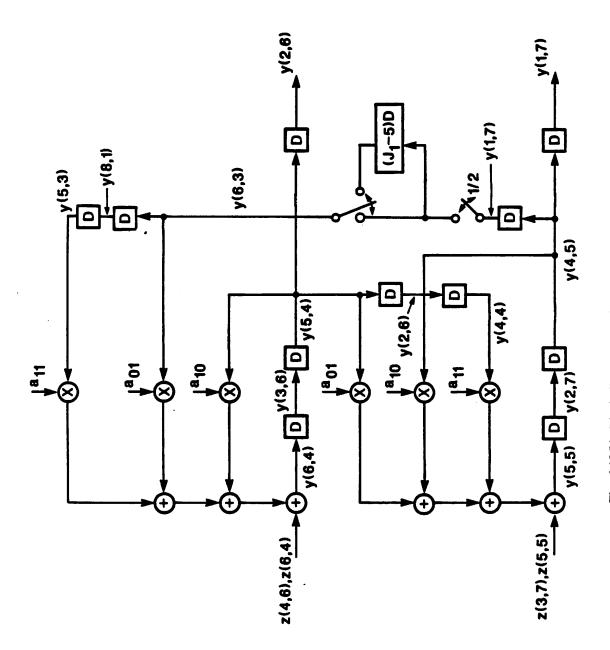

| 6.2. PIPELINING AND ONE-DIMENSIONAL BLOCK PROCESSING  | 204 |

| •   | •  |

|-----|----|

| - 1 | u  |

|     | ıv |

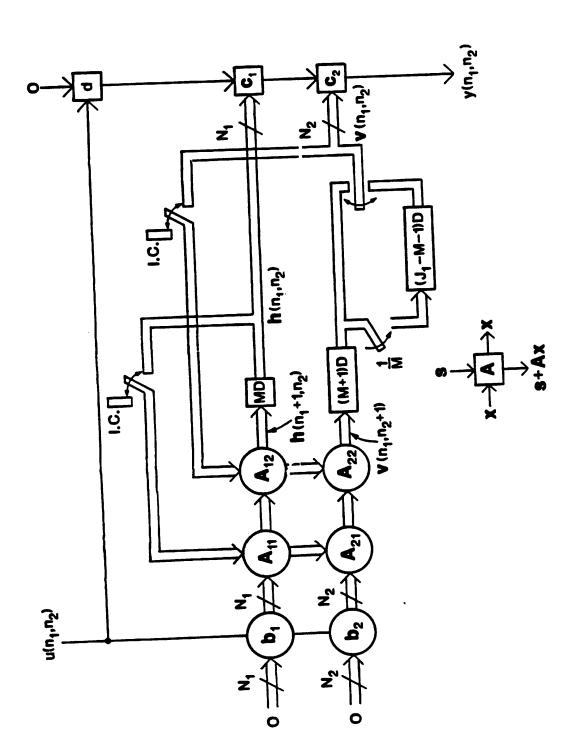

| 6.3. TWO-DIMENSIONAL INCREMENTAL BLOCK FILTER        | 231 |

|------------------------------------------------------|-----|

| 6.4. PIPELINING AND TWO-DIMENSIONAL BLOCK PROCESSING | 249 |

| 6.5. MULTIDIMENSIONAL RECURSIVE FILTERS              | 253 |

| 6.6. CONCLUSION                                      | 254 |

| 6.7. APPENDICES                                      | 255 |

| 6.8. REFERENCES                                      | 258 |

| CHAPTER 7: CONCURRENT DATA-FLOW SIGNAL PROCESSING    |     |

| 7.1. INTRODUCTION                                    | 262 |

| 7.2. SINGLE-NODE PROGRAMS                            | 264 |

| 7.3. SINGLE-RATE ITERATIVE PROGRAMS                  | 265 |

| 7.4. MULTIRATE ITERATIVE PROGRAMS                    | 267 |

| 7.5. CONCLUSION                                      | 269 |

| CHAPTER 8: FURTHER WORK                              | 270 |

# 1

## INTRODUCTION

### 1.1. INTRODUCTION

The continuing advancement of scaled VLSI technologies has made it possible to implement very complex functions on single chips at low cost. The computer aids for design of integrated circuits (ICs) have also advanced to a point that a designer can quickly design a chip starting with architecture design specifications. As an example, many designs that required two or three years of design time five years ago can be done within only two to three months today (for an identical size design team). However, in order to fully utilize the silicon area in an efficient manner for any specific application, it is necessary to optimize the algorithms and/or architectures by applying suitable transformations. For example, one can make more dramatic improvements in silicon area of an IC chip implementation by finding a more efficient algorithm or a better architecture of a given algorithm, as opposed to finding a minimum transistor circuit realization for the building blocks (such as adder units or memory cells) of the system.

While the process of chip design from architecture specifications has been well understood and fairly well automated, the algorithm and architecture design from application or problem specifications still remains a difficult task. Over the past decade, researchers have succeeded in systematically mapping a class of regular iterative

algorithms on systolic arrays starting with algorithm specifications (see [1-8]). However, finding efficient solutions to implementation of general irregular algorithms still remains an open problem. Several computer-aids for algorithm-specific custom implementations have also been developed in the last five years. Examples of these systems include the Lager design system at Berkeley [9], the Cathedral design system at IMEG, Belgium [10], and the silicon compiler developed at the GE R&D Center [11]. These design systems currently lack the ability to perform transformations on algorithms. These systems are also architecture-specific; they do not explore the entire algorithm and architecture design space.

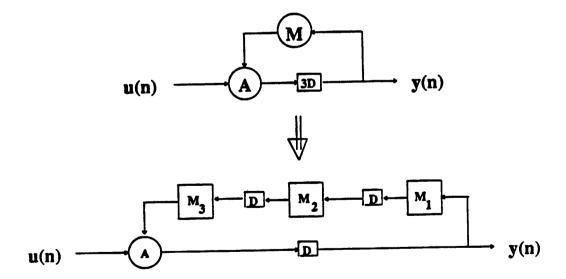

The goal of this thesis is to develop algorithm and architecture designs for high-speed real-time digital signal and image processing systems. Systematic approaches are explored to transform existing algorithms to create concurrency. These transformation schemes can be applied to a class of algorithms without altering their input-output behavior or functionality. The transformation schemes developed in this thesis can be basically divided into four broad categories. They are program unfolding, retiming, look-ahead and decomposition, and index mapping transformations. *Program unfolding* transformation increases the number of tasks, which can then be distributed more evenly among multiple processors. This transformation does not alter the basic algorithm, but does alter the sequencing or scheduling of the tasks of the algorithm. With an optimum unfolding factor, we can always construct a minimum-time or rate-optimal fully-static multiprocessor schedule. The *retiming transformation* involves moving around the delays in a data-flow program. This transformation can lead to a reduced iteration period, but cannot guarantee a rate-optimal schedule. The third category of transformation involves *look-ahead computation* schemes, which change the structures of linear

recursive algorithms (while maintaining identical input-output behavior) to create additional concurrency. The decomposition algorithms reduce the implementation complexity in these algorithms from linear to logarithmic (with respect to steps of look-ahead). The look-ahead schemes apply to linear recursive systems, and are demonstrated in this thesis in the context of digital filters. The index mapping transformation is used to exploit the inherent concurrency in the two-dimensional recursive digital filters.

These algorithm transformations can often result in an efficient high performance implementation (the efficiency measure is based on area-throughput tradeoff, and the throughput is assumed to be reflected by the sample rate of the system, and not necessarily the clock rate). This is because an algorithm transformation on a particular system can lead to a dramatic improvement in the implementation. The transformation techniques developed in this thesis can form the core of an architecture synthesis system, and can serve as the front end to one of the existing architecture-specific vertically-integrated computer-aided design systems.

### 1.2. CONTRIBUTIONS OF THE THESIS

Chapter 2 of this thesis concentrates on the program unfolding transformation, which leads to the construction of minimum-time fully-static multiprocessor schedules. The basic idea of this transformation is to exploit the repetitive nature of operation in signal and image processing systems (which operate on infinite time series). These systems and the corresponding iterative data-flow programs are non-terminating in nature. The scheduling and task sequencing issues have been studied in great detail over last two decades in the context of assembly line job scheduling and computer science. Minimizing the execution time over single pass of the program has been the goal in these sys-

tems. However, in signal and image processing systems, the same tasks are performed repetitively, and therefore we need to minimize the execution time of a single iteration while exploiting maximum possible overlap of successive iterations.

The loop or feedback or recursion in the algorithms described by iterative data-flow programs imposes a lower bound on the iteration or sample period. This bound is fundamental and cannot be broken even if infinite processors are available. The non-recursive systems do not have any feedback, and do not have any lower bound on the iteration period. The actual iteration period of any data-flow program may be much greater than the iteration bound. A retiming transformation can improve the iteration period, but cannot guarantee an iteration period equal to the iteration bound.

Unfolding a data-flow program leads to a new program with replicated tasks corresponding to successive iterations. For example, if a program contains 20 tasks and is unfolded by a factor of 5, then the unfolded program will contain 100 tasks belonging to 5 consecutive iterations. Unfolding of iterative data-flow programs can lead to greater concurrency in high performance implementations. Program unfolding increases the number of tasks to be executed, and these unfolded tasks can be more evenly distributed at compile time among multiple processors leading to reduced program execution time. Whether an iteration period equal to the iteration bound can always be achieved by program unfolding with a finite unfolding factor had remained an open question. We show that unfolding the program beyond a certain factor does not lead to any further reduction in the execution time. It is shown that this optimum unfolding factor is given by the least common multiple of the loop delay operators in the data-flow program graph. This unfolding factor leads to an exactly even distribution of the iterative tasks, and executes

the program in minimum possible time. We derive upper bounds on the number of processors to achieve minimum time schedules. In this context, we introduce the notion of a perfect data-flow program, which can always be executed in minimum time without requiring any unfolding or any retiming operation at all. We study properties of unfolded data-flow programs, and show that an unfolding operation with the optimum unfolding factor reduces any iterative data-flow program to an equivalent perfect data-flow program. We also present extensions to multiple rate data-flow programs, and applications to scheduling in non-homogeneous processor system implementations.

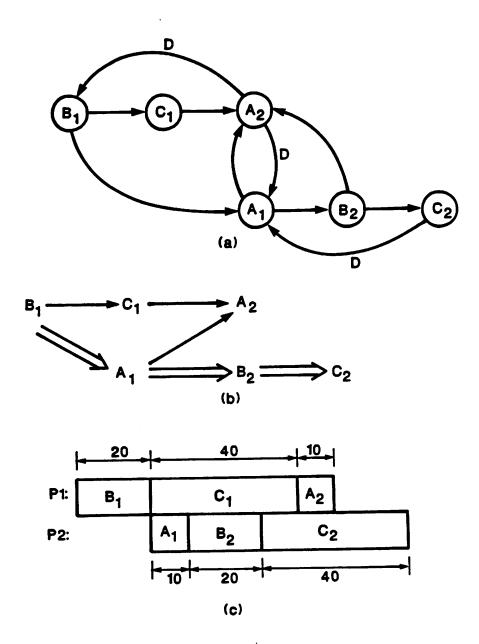

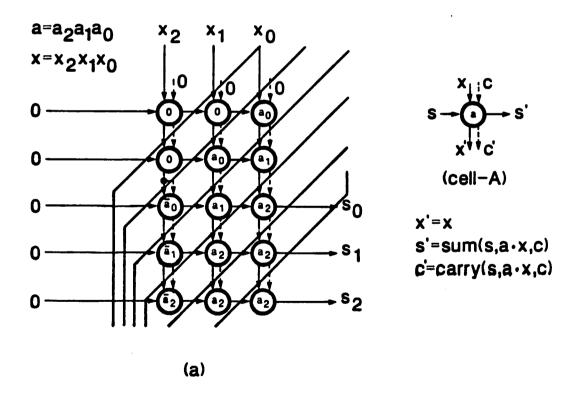

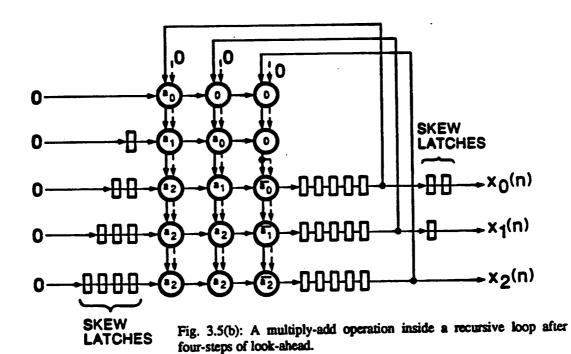

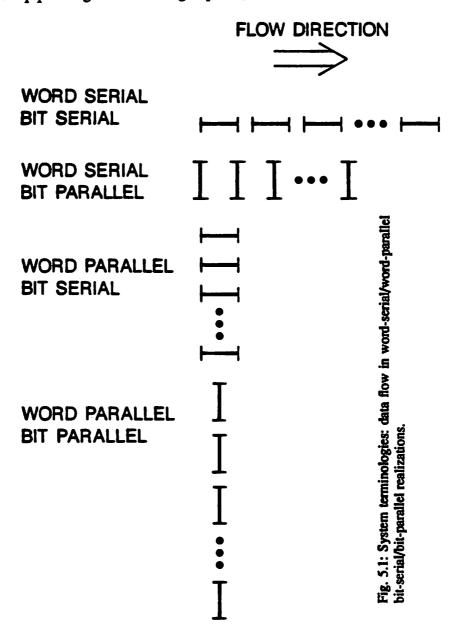

Many image processing, video signal processing, radar, sonar, and seismic signal processing applications require very high sample rate implementations. As an example, consider an implementation of a 5×5 convolver image processing system implementation. For a 512×512 frame size, and a frame rate of 30 frames per second, we need a computation rate of 200 million multiply operations per second, which can never be achieved by using a general purpose programmable signal processor implementation. These high performance systems can be implemented with low-cost (i.e. with low silicon area) by using dedicated custom IC chips, which use fine-grain pipelining and parallelism. Many dedicated chips have been implemented using fine-grain pipelining in general and bit-level pipelining in particular in the last two decades using bit-parallel [12-23] and bit-serial [24-33] approaches.

The two basic approaches to achieving concurrency are pipelining and parallelism or block processing. Suppose a single multiply/add operation can be clocked at 25 Mhz in some technology, and we require a sample rate of 100 Mhz. Then, one way to implement this system is to pipeline the multiply/add operation by four stages, i.e. insert four

pipeline delays or buffers or latches in intermediate portions of the multiply/add circuit. Another approach is to duplicate the hardware by four times. In this case, we can in each cycle operate on four input samples, and generate four output samples (the four non-overlapping samples form a block). With a clock period of 25 Mhz, and a block size of form, we can achieve an effective system system sample rate of 100 Mhz. Naturally, any combination of pipelining and parallelism can also be exploited. In the above example, yet another alternative would be to pipeline the multiply/add hardware by two stages, and duplicate the hardware by two times. In general, with M stages or levels of pipelining, and with a block size L, we can get an effective improvement in sample rate by a factor of LM. Pipelining is preferred to block processing, since pipelining exploits concurrency with reduced hardware penalty.

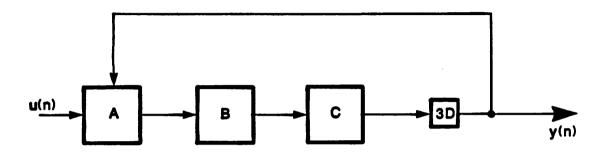

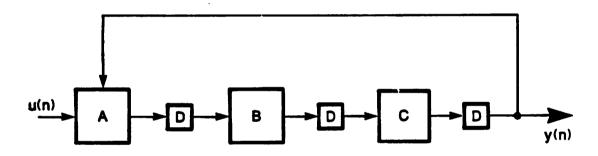

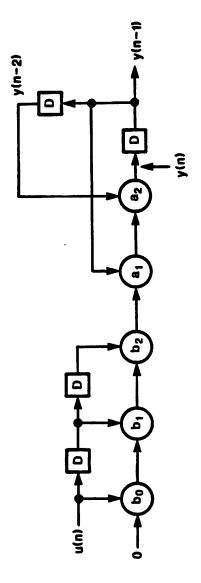

Exploiting fine-grain pipelining and block processing techniques in non-recursive systems is straightforward. However exploiting these techniques in recursive systems is a real challenge [23]. This is because the computational latency associated with the internal recursion or feedback in recursive systems limits the opportunities to use fine-grain pipelining and block processing techniques to achieve high sample rate realizations. In chapter 3, we develop techniques to pipeline recursive digital filters in an area-efficient manner. Fine-grain pipelining of recursive loops by simply inserting latches is useful for applications requiring moderate sample rates and where multiple independent computations are available to be interleaved in the pipeline; but not where a single recursive operation needs to be performed at very high sample rates.

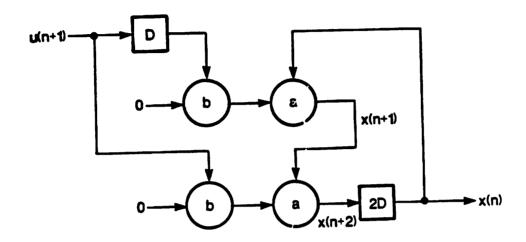

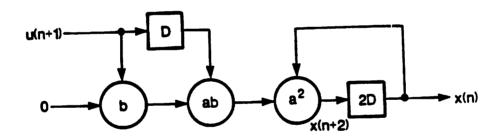

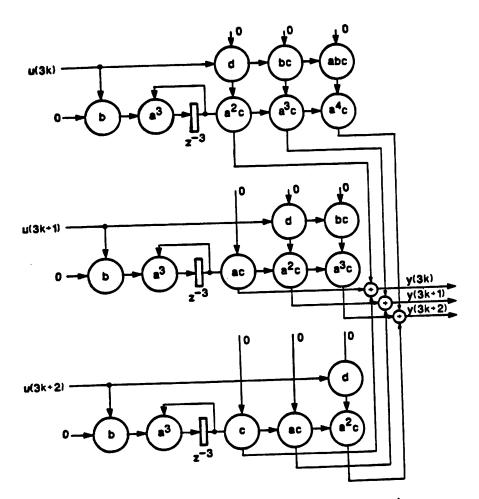

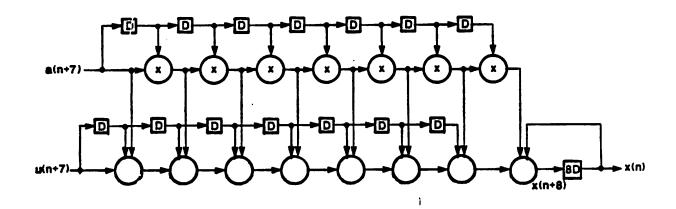

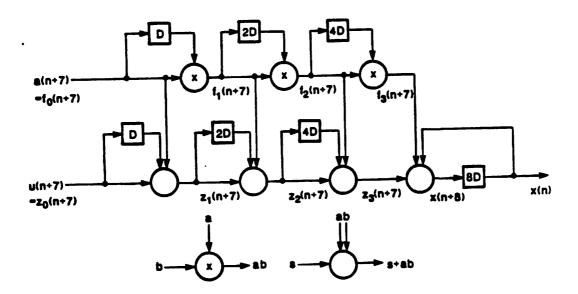

We introduce a new look-ahead approach (referred to as scattered look-ahead) to pipeline recursive loops. In the look-ahead algorithm, we iterate the recursive state

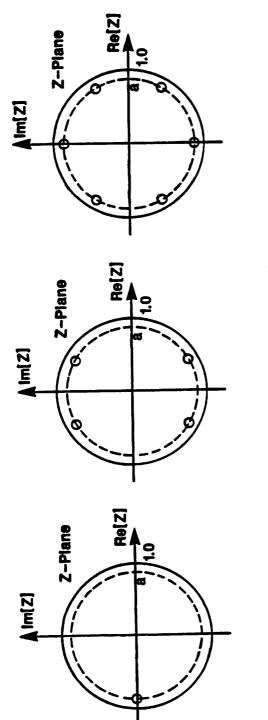

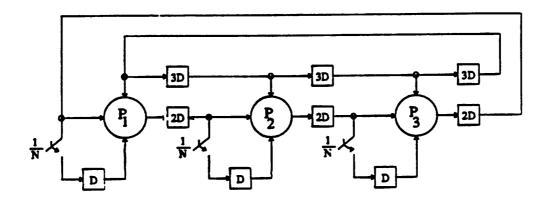

update representation, and implement the new recursion. This approach also improves the iteration bound of the realization. It is shown that the existing clustered look-ahead approach to pipelining recursive filters does not guarantee stability, whereas our new scattered look-ahead approach does guarantee stability. We also propose a new decomposition technique to implement the non-recursive portion (generated due to the scattered look-ahead process) in a decomposed manner (for cases where the number of loop pipeline stages can be expressed as a power of 2) to obtain concurrent stable pipelined realizations of logarithmic implementation complexity with respect to the number of loop pipeline stages (as opposed to linear). The upper bound on the roundoff error in these pipelined filters is shown to improve with an increase in the number of loop pipeline stages. We derive efficient pipelined realizations of both direct form and state space form recursive digital filters. Based on the scattered look-ahead technique, we present fully pipelined and fully hardware efficient linear bidirectional and unidirectional ring systolic arrays for recursive digital filters.

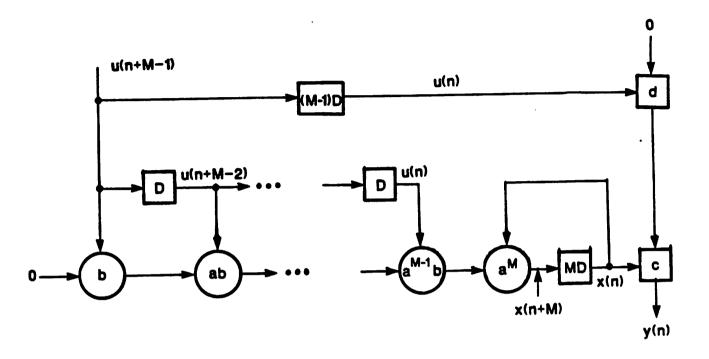

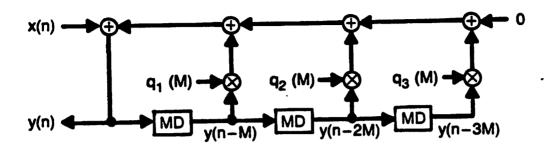

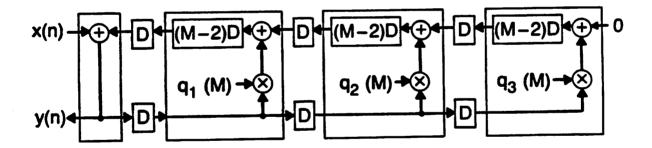

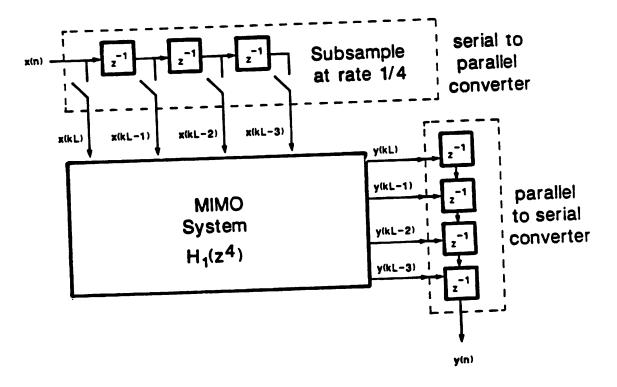

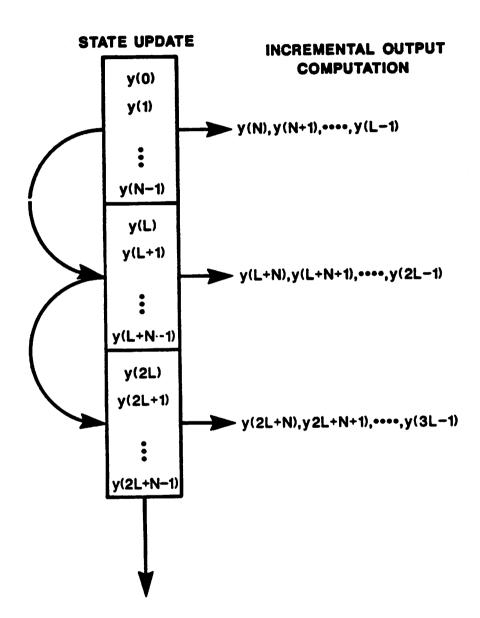

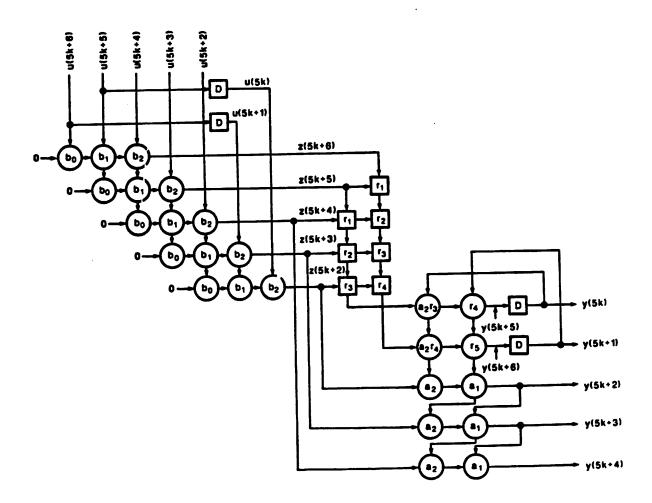

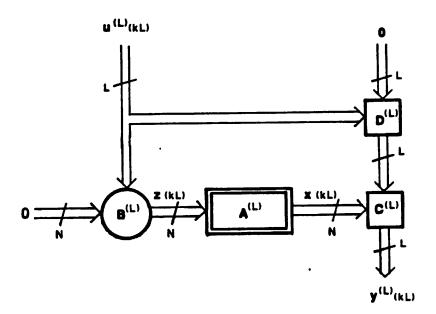

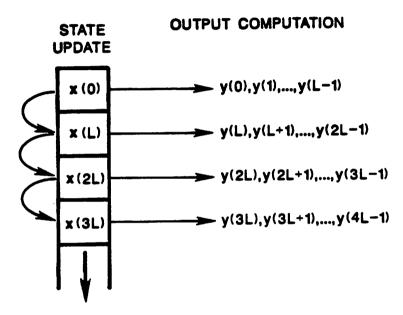

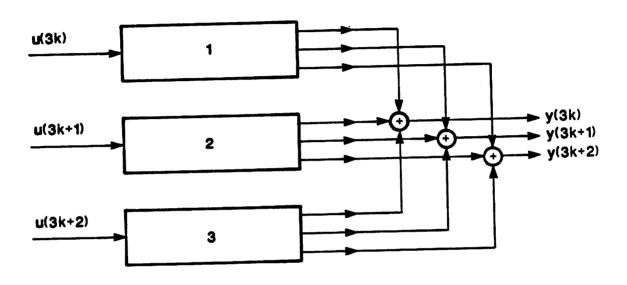

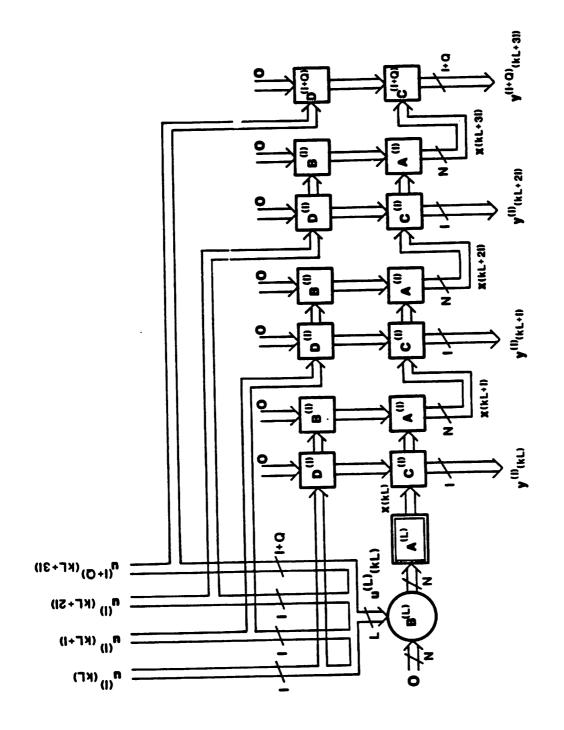

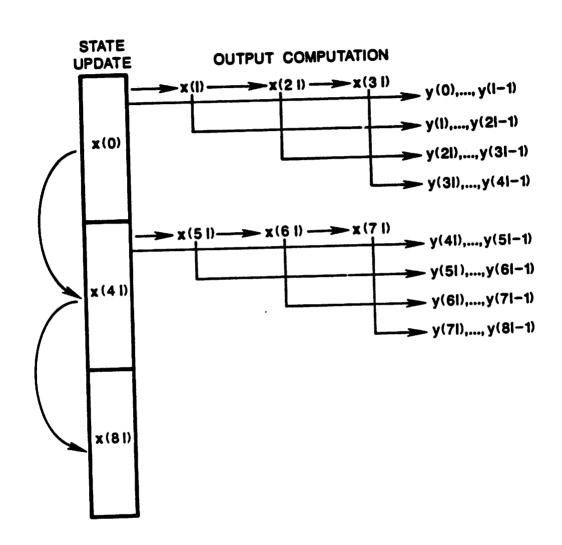

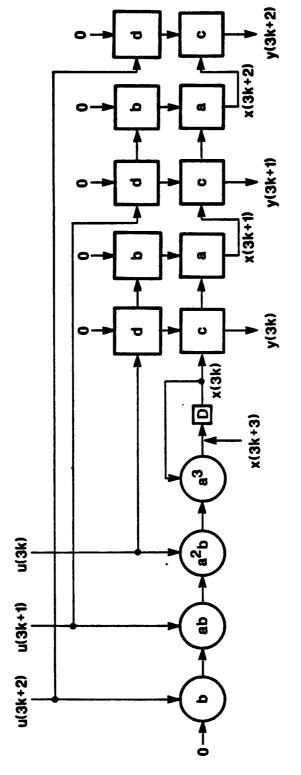

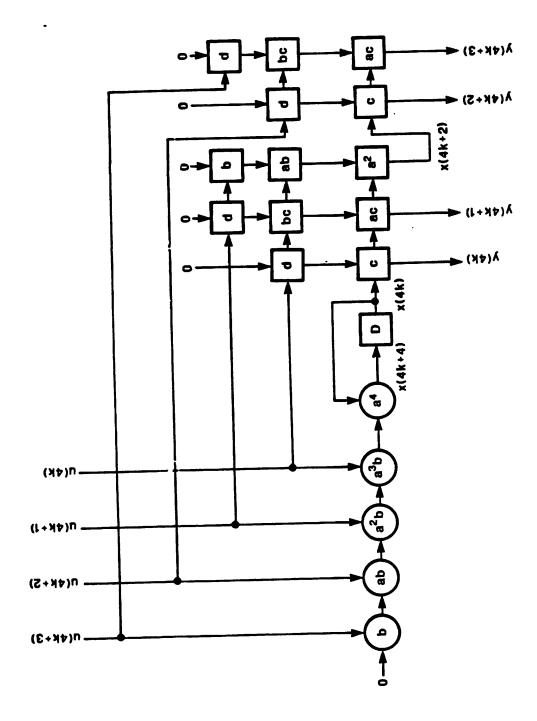

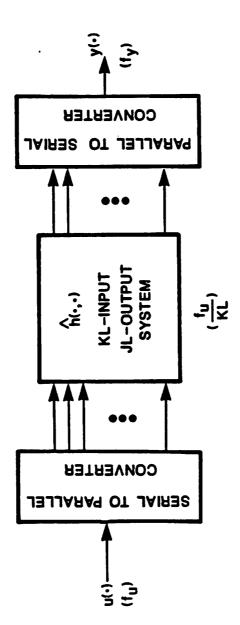

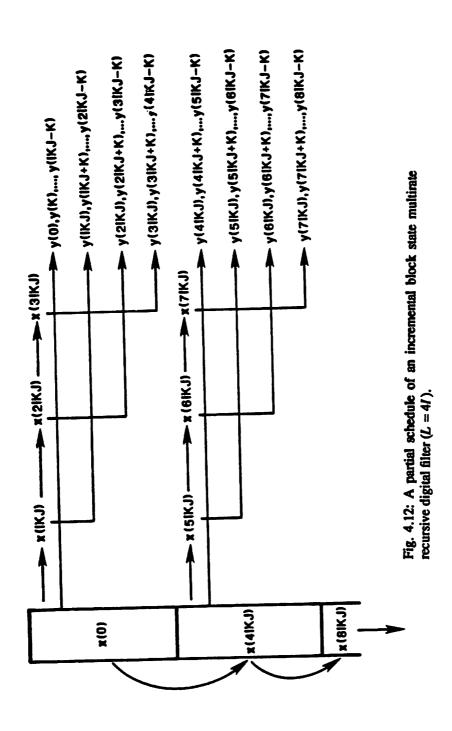

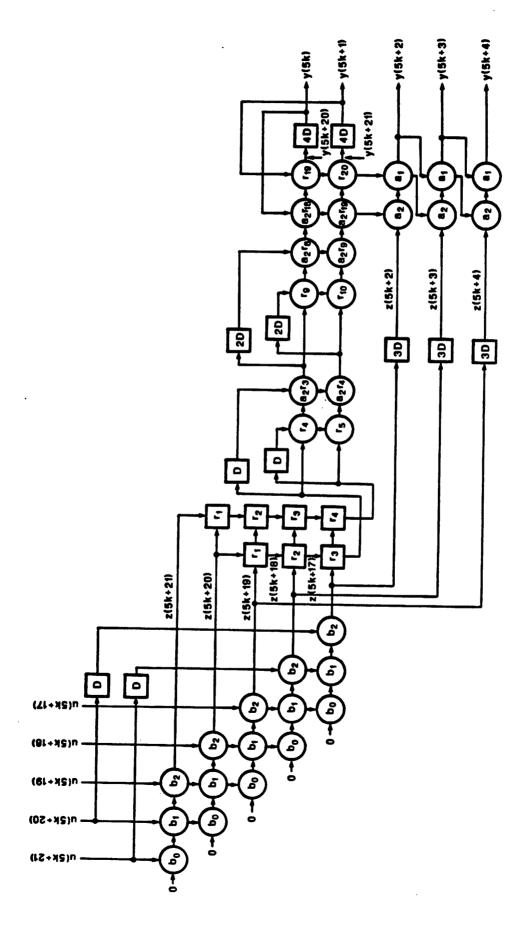

In chapter 4, we address block implementation and fine-grain pipelined block implementation of recursive digital filters. In a block implementation, we process samples in non-overlapping blocks. With a block size of L, we can increase the sample rate by a factor of L. We extend an existing linear complexity direct form block filter structure to higher order systems, and refer to it as the incremental block filter. Block implementation of state space recursive digital filters has been known for a long time. The two existing popular block structures are the block-state structure, and the parallel block-state structure. However the multiplication complexity of these structures is proportional to the square of the block size. The block state update operation in these filter structures is performed based on the clustered look-ahead computation, and requires a linear

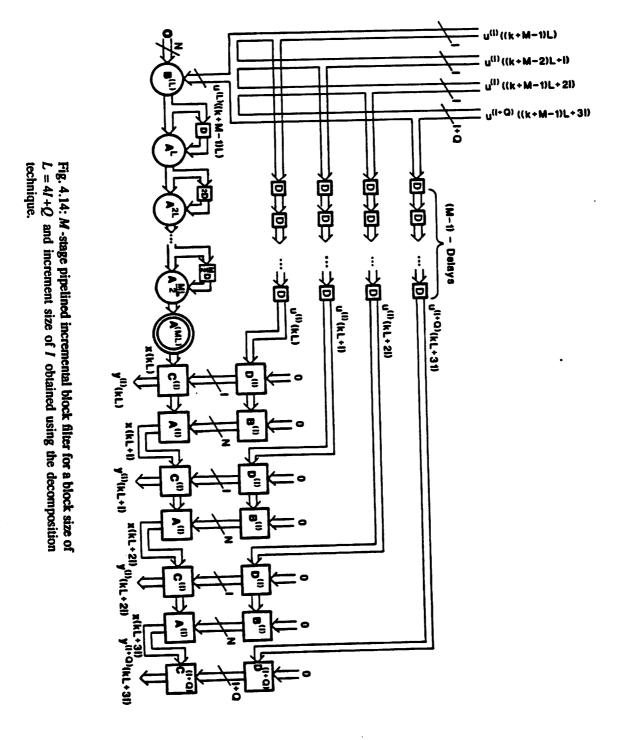

complexity in block size. But, the output computation of the complete block is done all at once and requires a square complexity in block size. We introduce a new technique of incremental output computation that has linear complexity in block size. Based on the clustered look-ahead and incremental output computation approaches, we derive our new incremental block-state structure for block implementation of state space filters of multiplication complexity linear in block size. The incremental block-state structure is also extended to the multirate recursive filtering case. We combine the techniques of scattered look-ahead, clustered look-ahead, decomposition, and incremental output computation to introduce several pipeline stages inside the recursive loop of the block filter. We derive deeply pipelined block filter structures for implementation of direct form and state space form recursive digital filters. The multiplication complexity of these deeply pipelined block filters is linear with respect to the block size, logarithmic with respect to the number of loop pipeline stages, and the complexities due to pipelining and block processing are additive. In summary, we can increase the sample rate in recursive digital filters by a factor LM with  $O(L)+O(\log_2 M)$  multiplication complexity using our techniques, as opposed to  $O(L^2M^2)$  multiplication complexity using previous approaches.

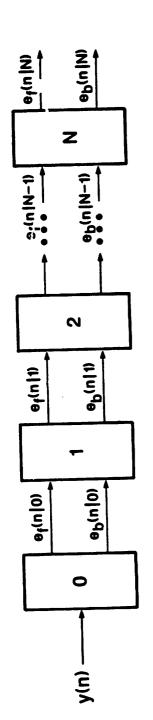

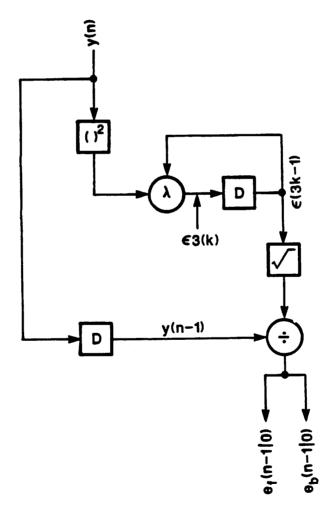

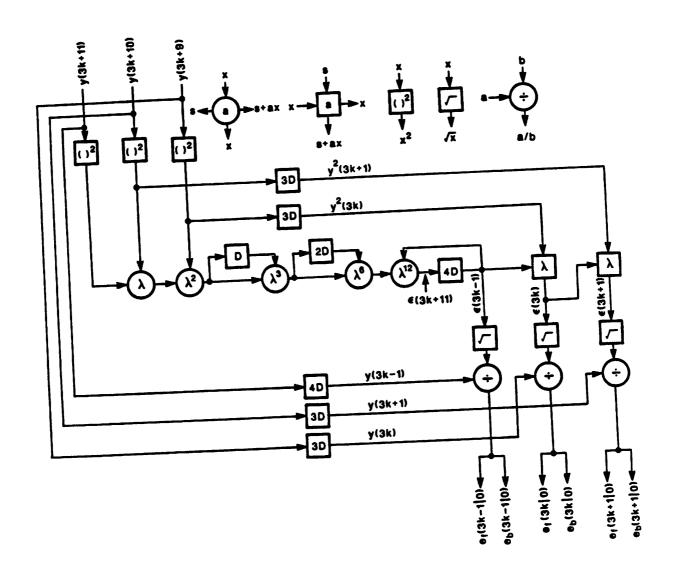

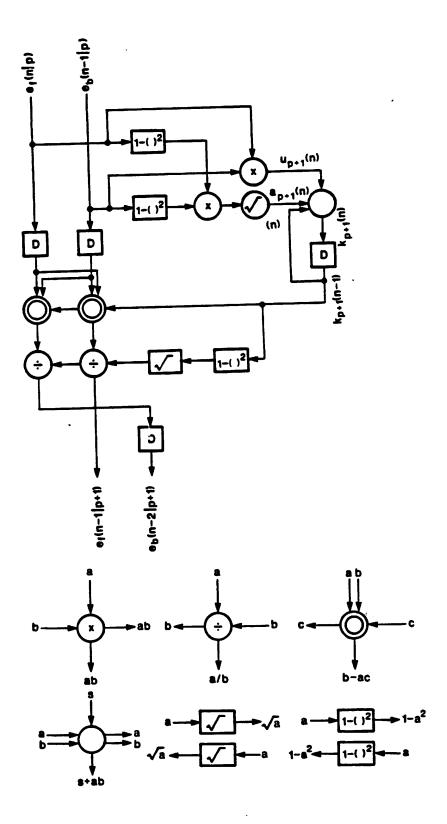

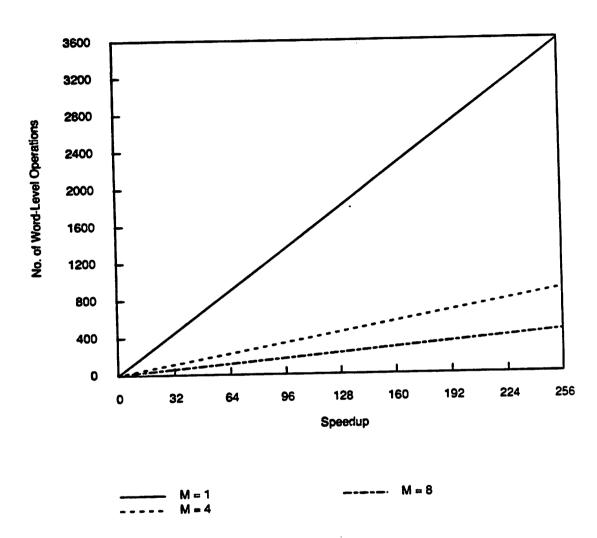

In chapter 5, we address high performance implementation of adaptive and time-varying recursive digital filters. We extend the look-ahead and decomposition algorithms to time-varying systems. Previous approaches to high sample rate adaptive lattice filter implementations have been based on word-level pipelined word-parallel (or "block") realizations. We show that adaptive filters can be implemented in an area-efficient manner by first using fine-grain pipelining, and then using block processing in combination with pipelining if further increase in the sample rate is needed. We show that with the use of the decomposition technique, high speed realizations can be achieved using

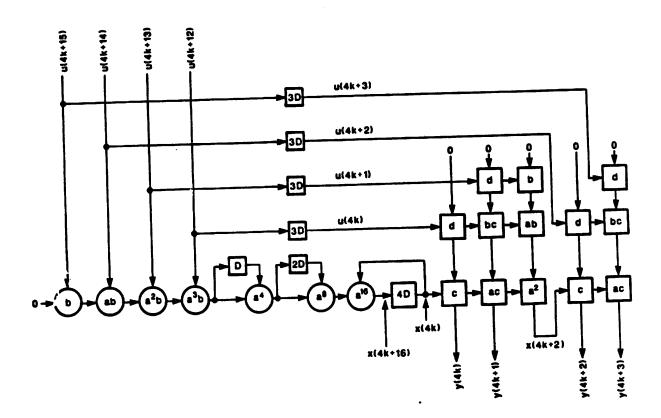

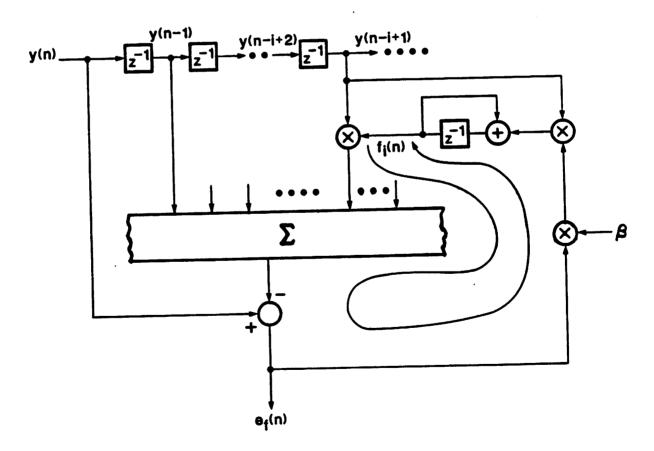

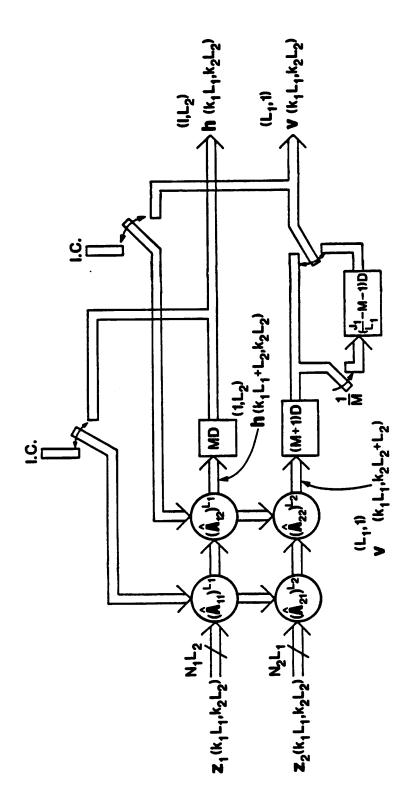

pipelining with a logarithmic increase in hardware (the block realizations require a linear increase). We derive pipelined word-parallel realizations of high sample rate adaptive lattice filters using the techniques of look-ahead computation, decomposed state update implementation, and incremental output computation. These three techniques combined together make it possible to achieve asymptotically optimal complexity realizations (i.e. asymptotically the same complexity as non-recursive systems) of high speed adaptive lattice filters (in both bit-serial and bit-parallel methodologies) and provide a "system solution" to high speed adaptive filtering. The adaptive lattice filter structures are ideal for high sample rate implementations, since the coefficients of a particular stage are adapted order-recursively based on the error innovations of the previous stage, and the coefficient update recursion inside each stage is linear in nature. An example of a normalized stochastic gradient adaptive lattice filter is presented, and its complexity, latency, and implementation methodology tradeoffs are studied.

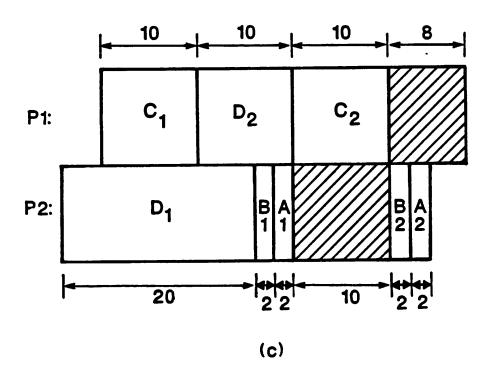

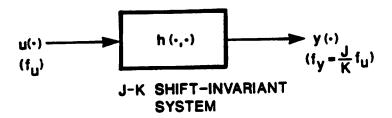

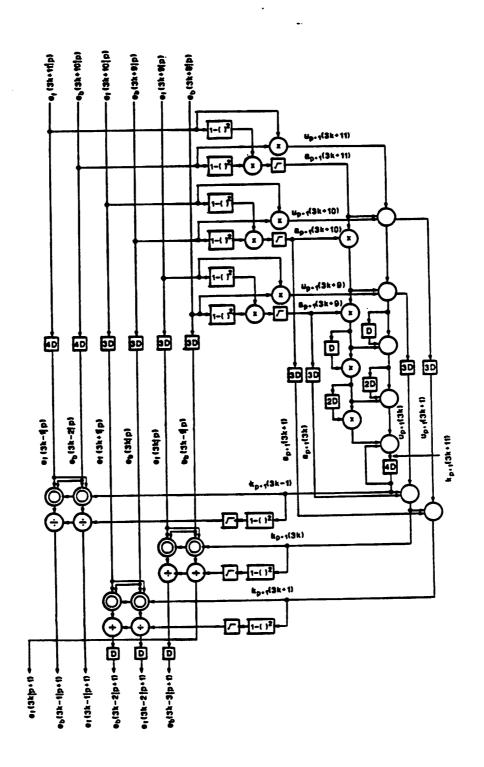

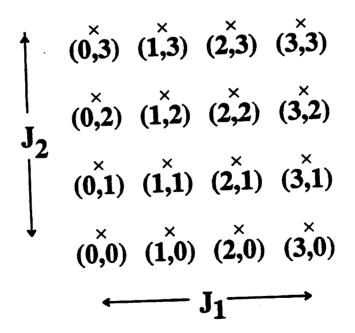

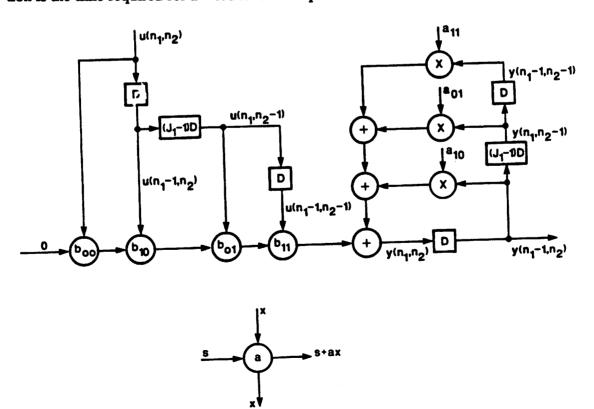

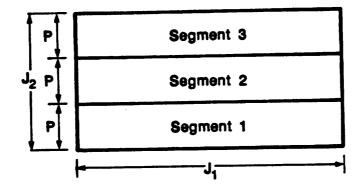

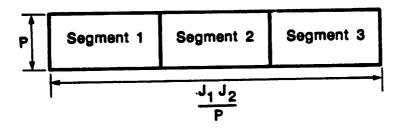

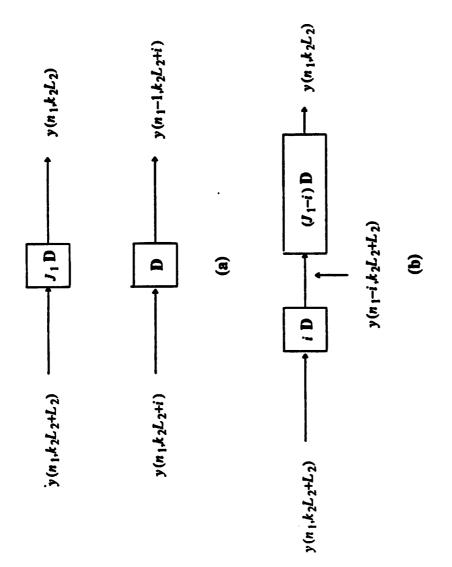

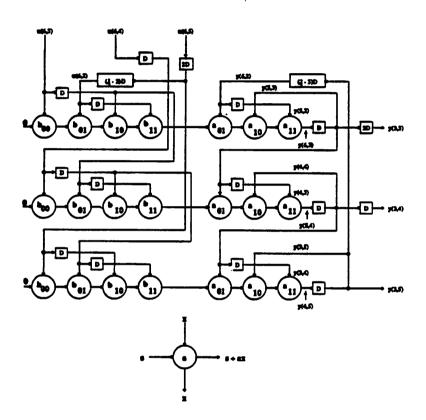

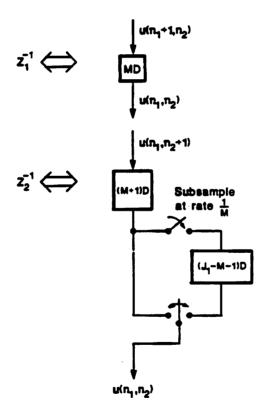

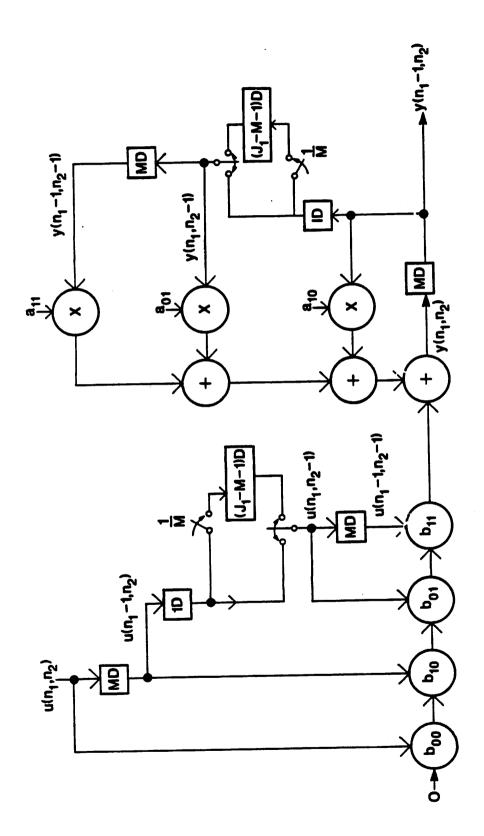

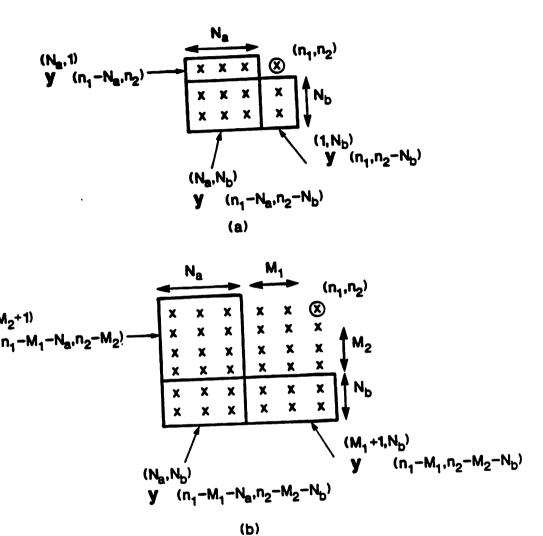

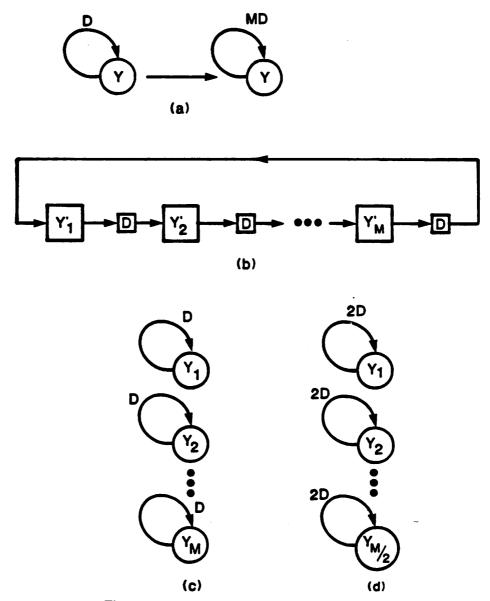

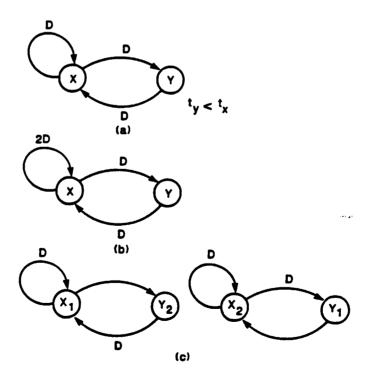

Chapter 6 focuses on exploiting concurrency in direct-form and local state-space form two-dimensional recursive digital filters to obtain efficient implementations. Unlike one dimensional recursive systems, two-dimensional recursive digital filter algorithms possess large amount of inherent concurrency, which can be exploited for fine-grain pipelining and/or parallelism. The locus of these concurrent computations is referred to as the concurrent computation region. We use an index mapping transformation to exploit this concurrency, and derive fine-grain pipelined and one-dimensional block filter architectures for the implementation of two-dimensional recursive digital filters. This transformation leads to appropriate interleaving (or indexing) of the input samples, and does not require any algorithm transformation, and does not lead to any hardware overhead.

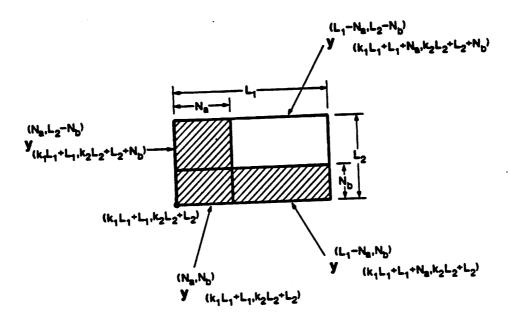

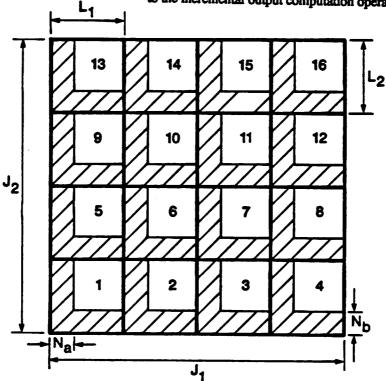

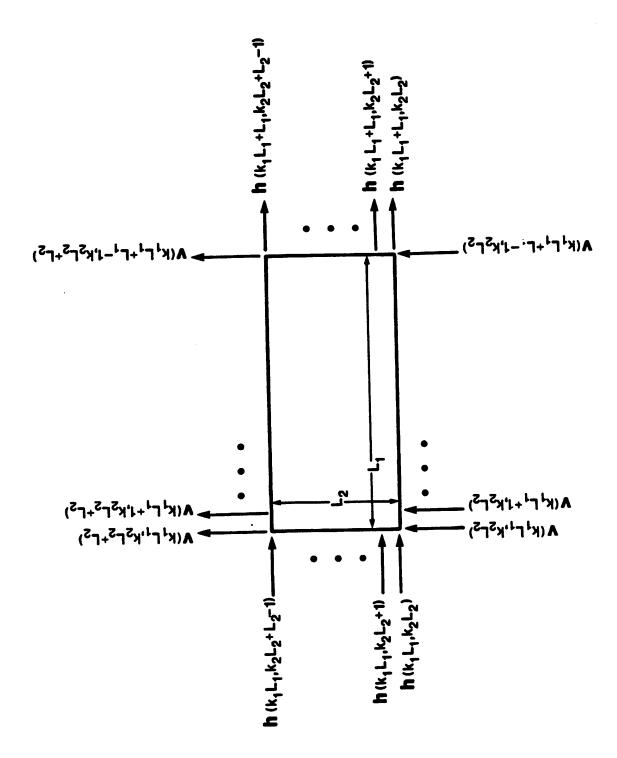

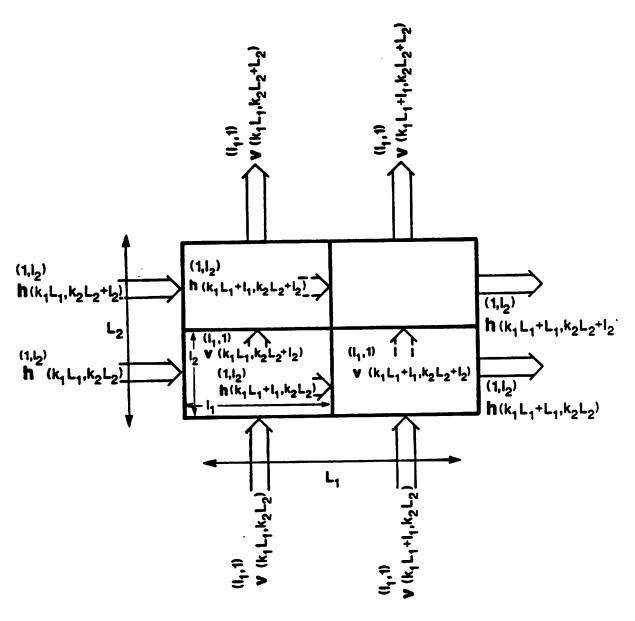

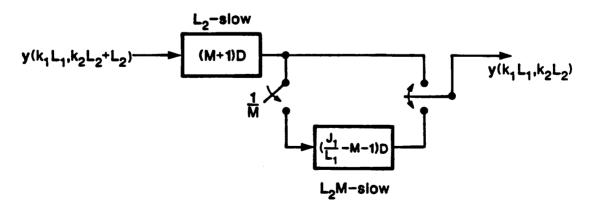

Another approach to achieving concurrency is by two-dimensional block processing using algorithm transformation techniques. We extend the look-ahead computation and the incremental output computation principles to the two-dimensional case, and derive a new two-dimensional incremental block filter structure. The multiplication complexity of our new incremental block filter with a block size  $L_1 \times L_2$  is  $O(Max(L_1^2L_2L_1L_2^2))$ , as opposed to  $O(L_1^2L_2^2)$  of the existing block-state filter structures. We then combine pipeline interleaving and incremental block filtering approaches to derive efficient filter structures. The notion of an index mapping function is used to derive the implementable delay and quasi delay operators for the concurrent pipelined and/or blocked two-dimensional architectures. The quasi delay operators represent delay operator in one dimension and an advance operator in the other. We show that for an N-dimensional recursive filter, the concurrent computation region corresponds to an (N-1)-dimensional hyperplane. The pipeline interleaving and the block processing concepts are also extended to higher dimensional cases.

In chapter 7, we create concurrency in general iterative data-flow programs by applying the look-ahead transformations locally to some critical nodes. This chapter uses the theory of program unfolding and look-ahead transformations developed in chapters 2 through 6 of the thesis. The local transformations of iterative data-flow programs are particularly useful in systems where the algorithms cannot meet the real-time constraints of the target application. Chapter 8 concludes the dissertation with suggestions for future work.

#### 1.3. REFERENCES

- (1) Kung, H.T., "Why Systolic Architectures", Computer, January 1982, pp. 37-45

- (2) Cappello, P.R., and Steiglitz, K., "Unifying VLSI Array Design with Linear Transformations of Space Time", Advances in Computers Research, Vol. 2, 1984, pp. 23-65

- (3) Quinton, P., "Automatic Synthesis of Systolic Arrays from Uniform Recurrent Equations", Proc. of 11th Annual Symposium on Computer Architecture, June 1984, pp. 208-214

- (4) Moldovan, D.I., and Fortes, J.A.B., "Partitioning and Mapping of Algorithms into Fixed Size Systolic Arrays", *IEEE Trans. on Computers*, January 1986, pp. 1-12

- (5) Li, G., and Wah, B.W., "The Design of Optimal Systolic Arrays", *IEEE Trans. on Computers*, Vol. 34, January 1985, pp. 66-77

- (6) Chen, M.C., "A Design Methodology for Synthesizing Parallel Algorithms and Architectures", Journal of Parallel and Distributed Computing, December 1986, pp. 461-491

- (7) Jagadish, H.V., Rao, S.K., and Kailath, T., "Array Architectures for Iterative Algorithms", *Proc. of the IEEE*, Vol. 75, No. 9, September 1987, pp. 1304-1321

- (8) Kung, S.Y., VLSI Array Processors, Prentice Hall, 1988

- (9) Rabaey, J.M., Pope, S.P., and Brodersen, R.W., "An Integrated Automatic Layout Generation System for DSP Circuits", *IEEE Trans. on CAD of ICs*, Vol. CAD-4, No. 3, July 1985, pp. 285-296

- (10) Canthoor, F. et al, "Architectural Strategies for an Application Specific Synchronous Multiprocessor Environment", *IEEE Trans. on Acoustics, Speech, and Signal Processing*, Vol. 36, No. 2, February 1988, pp. 265-284

- (11) Yassa, F. et al, "A Silicon Compiler for Digital Signal Processing: Methodology, Implementation, and Applications", Proc. of the IEEE, Vol. 75, No. 9, September 1987, pp. 1272-1281

- (12) McCanny, J.V., and McWhirther, J.G., "Completely Iterative Pipelined Multiplier Array Suitable for for VLSI", Proc. of Inst. of Elect. Eng., Vol. 129, Part G, No. 2, pp. 40-46, April 1982

- (13) Evans, R.A. et al, "A CMOS Implementation of a Multibit Convolver Chip", Proc. of VLSI'83, edited by F. Anceau and E.J. Aas, Elsevier, Amsterdam, 1983, pp. 227-235

- (14) Ulbrich, W. et al, "MOS-VLSI Pipelined Digital Filters for Video Applications", Proc. of the IEEE Int. Conf. on Acoustics, Speech, and Signal Processing, San Diego, March 1984, pp. 44.7.1-44.7.4

- (15) Cappell J. P.R., and Steiglitz, K., "A Note on Free Accumulation in VLSI Filter Architectures", IEEE Trans. on Circuits and Systems, Vol. 32, No. 3, March 1985, pp. 291-296

- (16) Cappeilo, P.R., and Wu, C.W., "Computer Aided Design of VLSI FIR Filters", *IEEE Proceedings*, Vol. 75, No. 9, September 1987, pp. 1260-1271

- (17) Hauck, C.E., Bamji, C.S., and Allen, J., "The Systematic Exploration of Pipelined Array Multiplier Performance", *IEEE Int. Conf. on Acoustics, Speech, and Signal Processing*, Tampa, FL, April 1985, pp. 1461-1464

- (18) Hatamian, M., and Cash, G.L., "A 70-MHz 8-bitX8-bit Parallel Pipelined Multiplier in 2.5 Micron CMOS", IEEE Journal of Solid State Circuits, Vol. 21, No. 4, August 1986, pp. 505-513

- (19) Hatamian, M., and Cash, G.L., "Parallel Bit-Level Pipelined VLSI Designs for High Speed Signal Processing", *IEEE Proceedings*, Vol. 75, No. 9, September 1987, pp. 1192-1202

- (20) Noll, T.G. et al, "A Pipelined 330 MHz Multiplier", IEEE Journal of Solid State Circuits, Vol. 21, No. 3, June 1986, pp. 411-416

- (21) Noll, T.G., "Semi-Systolic Maximum Rate Transversal Filters with Programmable Coefficients", Proc. of the International Conference on Systolic Arrays, July 2-4, 1986, Oxford, England

- (22) Jain, R., Ruetz, P.A., and Brodersen, R.W., "Architecture Strategies for Digital Signal Processing Circuits", Proc. of the 1986 VLSI Signal Processing Workshop, in VLSI Signal Processing II, IEEE Press, 1986

- (23) Parhi, K.K., and Hatamian, M., "A High Sample Rate Recursive Digital Filter Chip", in VLSI Signal Processing III, IEEE Press, November 1988

- (24) Jackson, L.B., Kaiser, J.F., and McDonald, H.S., "An Approach to Implementation of Digital Filters", *IEEE Transactions on Audio and Electroacoustics*, Vol. 16, No. 3, 1968, pp. 413-421

- (25) Lyon, R.F., "Two's Complement Pipelined Multipliers", IEEE Transactions on Communications, 1976, pp. 418-424

- (26) Freeny, S.L. "Special Purpose Hardware for Digital Filtering", *Proc. of IEEE*, Vol. 63, April 1975, pp. 633-648

- (27) Denyer, P.B., and Renshaw, D., VLSI Signal Processing: A Bit Serial Approach, Addison Wesley, Reading, MA, 1986

- (28) Denyer, P.B., Murray, A.F., and Renshaw, D., "FIRST: Prost ect and Retrospect", in VLSI Signal Processing I, ed. by P.R. Cappello, IEEE Press, NY, 1984

- (29) Smith, S.G., and Denyer, P.B., Serial Data Computation, Kluwer Academic Press, Boston, 1988

- (30) Powell, N.R., "Functional Parallelism in VLSI Systems and Computations", in VLSI Systems and Computations, ed. by Kung, Sproull, and Steele, Springer-Verlag, 1981

- (31) Van Ginderdeuren, J.K.J. et al, "Compact NMOS Building Blocks and a Methodology for Dedicated Digital Filter Applications", *IEEE Journal of Solid State Circuits*, Vol. 18, No. 3, June 1983, pp. 306-316

- (32) Jain, R. et al, "Custom Design of a VLSI PCM-FDM Transmultiplexor from System Specification to Circuit Layout using a Computer Aided Design System", *IEEE Journal of Solid State Circuits*, Vol. 21, No. 1, February 1986, pp. 73-85

- (33) Noujaim, S. et al, "30 Mhz Compiled Chipset for Graphics Computation", Digest of 1987 ISSCC, February 1987

## PROGRAM UNFOLDING

#### 2.1. INTRODUCTION

The data-flow representation of algorithms clearly exhibits the available concurrency, and forms a natural basis for program specifications in a multiprocessor environment. Although the concept of data-flow computation has existed for quite some time [1-2], only in recent years it has received wide attention [3-8]. In this chapter, we consider non-preemptible deterministic periodic scheduling of iterative static large-grain synchronous data-flow programs. In particular, we consider construction of minimumtime multiprocessor schedules for these programs. The iterative programs are assumed to be non-terminating in nature; in other words we assume the program is executed a very large number of times, such that it can be considered an infinite number of times. This nature of computation is frequently found in many real-time systems, typically in signal and image processing applications. The loops in these programs lead to a lower bound on the execution time of a single iteration, referred to as an iteration bound [9-11] (see also [8,12] in the context of asynchronous systems) in the remainder of the chapter. The execution time of a single iteration is referred to as an iteration period, and a schedule is said to be rate-optimal, if the iteration period is same as the iteration bound. Traditional multiprocessor scheduling of these iterative flow graphs are based on critical path methods, which minimize the iteration period over one iteration of the program [13-14]. These techniques do not exploit the repetitive nature of the program, and rarely achieve an iteration period equal to the iteration bound. Often the program can be retimed to achieve a reduced iteration period, but the retiming [15-17] of a program cannot guarantee a rate-optimal implementation.

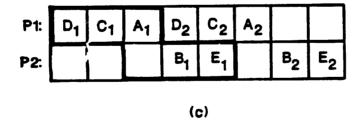

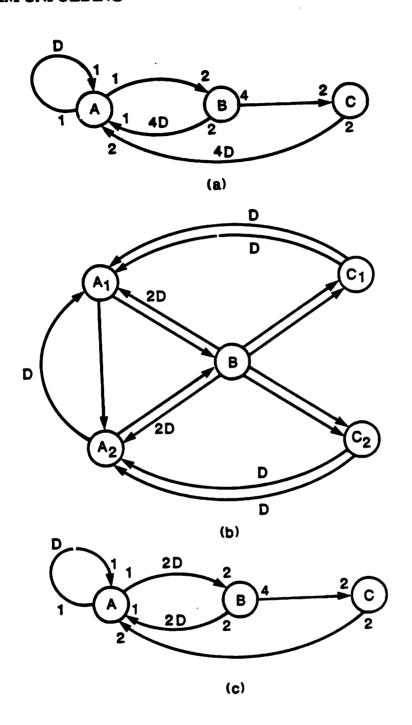

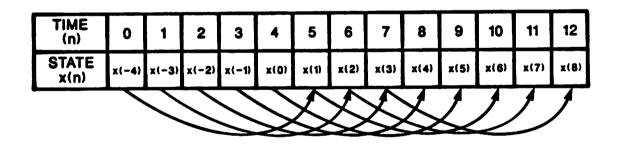

Past efforts towards rate-optimal scheduling of iterative flow graphs have been based on construction of cyclo-static schedules [18-22]. These schedules exploit the repetitiveness of the data-flow programs. A cyclo-static schedule is characterized by a lattice  $P \times T$ , where P corresponds to the processor displacement and T is the time displacement (same as the iteration period). A processor displacement P in a schedule implies that if the iteration i of a certain task is scheduled in processor p, then the iteration (i+1) of the same task is scheduled in processor (p+P) modulo  $P_N$ , where  $P_N$  is the end point of the processor lattice (which can be multidimensional). A time displacement T implies that if the iteration i of a task is scheduled at time t, then the iteration (i+1) of the same task is scheduled in time (t+T). Table 2.1 shows a partial schedule of two iterations of a cyclo-static schedule (from [18]). The symbol  $A_i$  denotes the i-th invocation or i-th iteration of task A. In the example of Table 2.1, there are 10 tasks in each iteration, and 4 processors arranged in a 1-D space. The processor displacement in this schedule is 2 units, and the time displacement or the iteration period is also 2 units. As an example, task  $3_1$  (i.e. iteration 1 of task 3) is scheduled in processor  $P_1$  at time unit 1, and task  $3_2$  in processor  $P_3$  at time unit 3. Task  $3_3$  can be scheduled in processor  $P_1$ (which is 3+2 modulo 4) at time unit 5 (not shown in the Table). The  $P \times T$  lattice for this schedule is  $2\times2$ .

Table 2.1: A Cyclo-Static Schedule

| Processor      |    | Schedules |    |    |     |    |     |

|----------------|----|-----------|----|----|-----|----|-----|

| $P_4$          | -  | -         | -  | 12 | 42  | 22 | 102 |

| P <sub>3</sub> | -  | -         | 32 | 72 | 82  | 92 | •   |

| P <sub>2</sub> | -  | 11        | 41 | 21 | 101 | •  | -   |

| $P_1$          | 31 | 71        | 81 | 91 | -   | -  | •   |

A schedule is *fully-static*, if the processor displacement is zero, i.e. P component of the P×T lattice is 0. In other words, all iterations or invocations of a specified node or task are scheduled in the same processor. Table 2.2 shows a partial schedule of two iterations of a fully-static schedule [18], which has a processor-time lattice 0×2. In a fully-static schedule, all tasks corresponding to a single iteration are first scheduled, and this schedule is then replicated for all other iterations with 0 processor displacement.

Table 2.2: A Fully-Static Schedule

| Processor      | Schedules |    |    |    |     |    |     |

|----------------|-----------|----|----|----|-----|----|-----|

| $P_4$          | -         | •  | -  | 21 | 101 | 22 | 102 |

| P <sub>3</sub> | -         |    | 41 | 91 | 42  | 92 | -   |

| $P_2$          | -         | 11 | 81 | 12 | 82  | -  | -   |

| $P_1$          | 3,        | 7, | 32 | 72 | -   |    | -   |

Whether fully-static rate-optimal multiprocessor schedules of iterative data-flow programs can always be constructed has so far remained an open question. In this chapter, we explore unfolding of these data-flow programs, and construction of fully-static rate-optimal schedules of the unfolded program. Unfolding of the program leads to an increased number of tasks, which can be more evenly distributed. Although unfolding or blocking of iterative data-flow programs has been considered in [7,18-22], systematic properties of unfolded data-flow graphs have so far not been studied. One question

remains to be answered in this context. Is it possible to find an unfolding factor which can guarantee a rate-optimal fully-static schedule? We study properties of unfolded data-flow programs, and prove that an unfolding factor equal to the least common multiple of the delays in the loops of the program always results in an admissible rate-optimal fully-static schedule. It is also shown that the worst-case complexity of constructing fully-static rate-optimal schedules is polynomial (in number of nodes), as opposed to the exponential complexity of constructing cyclo-static rate-optimal schedules [18-22].

The outline of the chapter is as follows. Section 2.2 describes the static data-flow program model, which are described by data-flow graphs. Section 2.3 reviews the notion of iteration bound. Section 2.4 reviews retiming of data-flow programs. In section 2.5, we introduce the notion of a perfect data-flow program. These perfect programs always achieve rate-optimal schedules requiring no unfolding and no retiming operations at all. Section 2.6 studies properties of unfolded data-flow programs. The construction of rate-optimal schedules by optimum unfolding of the data-flow program is addressed in section 2.7. Section 2.8 outlines extensions of retiming and program unfolding techniques to multiple-rate data-flow program graphs, and section 2.9 addresses applications of program unfolding techniques to scheduling in non-homogeneous processor implementations.

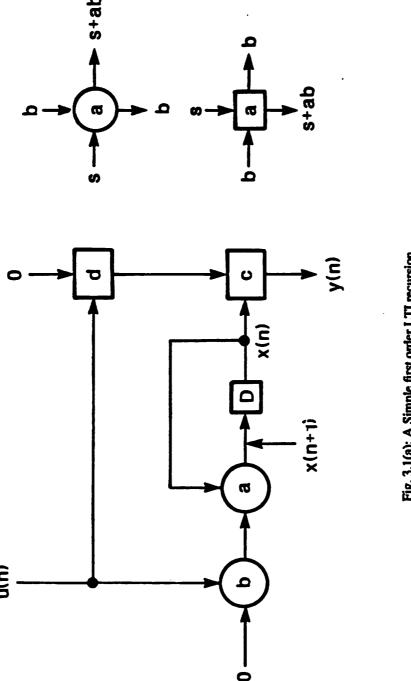

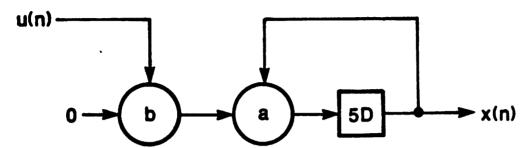

## 2.2. ITERATIVE DATA-FLOW PROGRAM MODEL

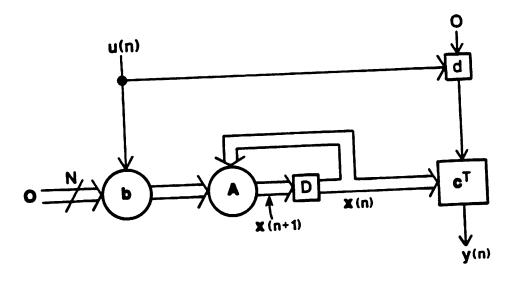

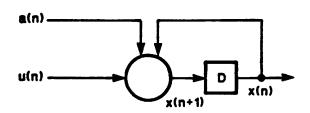

The iterative data-flow programs are assumed to be synchronous in nature, and are represented by data-flow graphs (DFGs). The nodes in the DFGs represent program or code segments or tasks, and execute the code when invoked. The *directed* arcs correspond to communication between the nodes, and have delays associated with them.

These delays represent the states in the DFG, and are dictated by initial conditions during the first iteration of the DFG. An arc with a single delay from node u to node v implies that the instance  $v_1$  depends upon  $u_0$ ,  $v_2$  depends upon  $u_1$  etc. By transitivity, this implies that  $v_i$  depends upon  $u_{i-1}$  and all other past instances or iterations of u. Similar argument applies to self loops also, i.e. where  $u_i$  depends upon  $u_{i-1}$ . Thus, if a task  $u_i$  is dependent upon  $u_{i-1}$ ,  $u_{i-2}$  etc., then we model this iterative computation with a self loop and a single delay around the loop (similar to the reduced dependence graph model [23]). It may be noted that modeling the program by reduced dependence is appropriate for large-grain parallel compilation. However, it is necessary to consider complete dependence to exploit fine-grain parallelism. The arcs without delays represent precedence relation, i.e., if there is an arc from node u to node v with no delay associated with it, then node v must be scheduled after execution of node u is complete. But the arcs with delays do not imply precedence. This is because if there is an arc from node u to node v with a delay, node v can be executed using the available state information due to the past iteration of u, and independent of the execution of the current iteration of u.

We assume the DFG to be computable, i.e. all loops in the DFG have one or more delays. We assume that the DFG performs repetitive tasks on infinite time series. In other words, we are concerned with non-terminating programs and periodic schedules. We assume the node computation times to be fixed, i.e. we are concerned with deterministic schedules. This is a natural model for most real-time signal and image processing systems. Each repetition of the DFG is referred to as an iteration, and the scheduling period of a single iteration is referred to as the iteration period. We assume that we cannot improve the functionality or granularity of any node in the DFG. By this it is meant that a node cannot be broken into two or more nodes. The DFGs considered in this

chapter correspond to large-grain synchronous data-flow graphs. These DFGs can correspond to either homogeneous or multiple sample rate systems. In a homogeneous sample rate system, each node in the DFG is invoked only once during an iteration, and produces a single sample to each of its outgoing arcs and consumes a single sample from each of its incoming arcs when invoked. In multiple sample rate systems, different nodes are invoked a different number of times in a single cycle (see [7] for theory of multiple-rate DFGs). Sections 2.3 through 2.7 are devoted to study of homogeneous DFGs, and the discussion of the multiple-rate DFGs is addressed in section 2.8.

Now we define some terminologies in a DFG.

Definition 2.1: A node in a DFG is an initial node, if and only if all of its incoming arcs have delays.

Definition 2.2: A node in a DFG is a terminal node, if and only if all of its outgoing arcs have delays associated with them.

Definition 2.3: A node v is a successor of node u, if there is a path from u to v with no delay in the path. Then node u is referred to as the predecessor of node v.

Definition 2.4: A node v is an immediate successor of node u, if there is a directed arc from u to v with no delay. Then, node u is an immediate predecessor of node v.

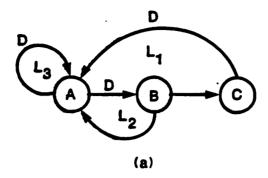

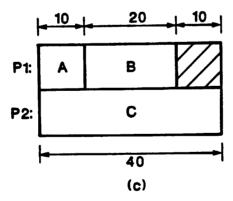

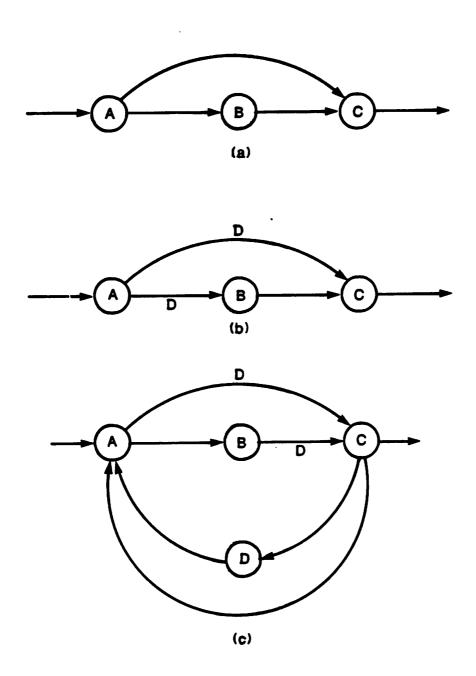

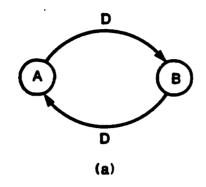

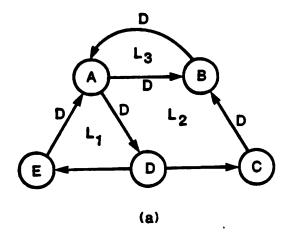

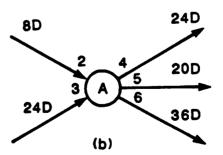

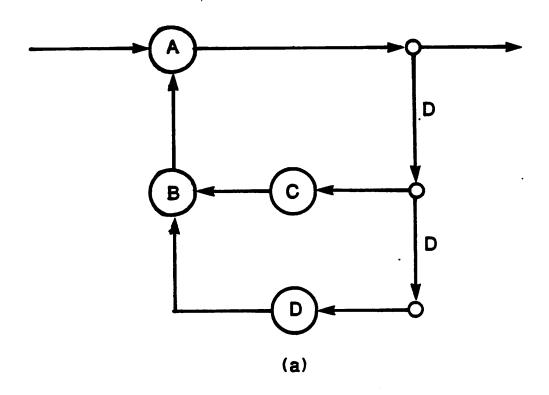

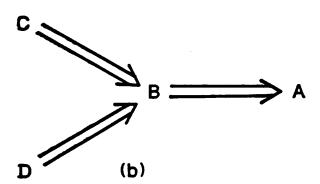

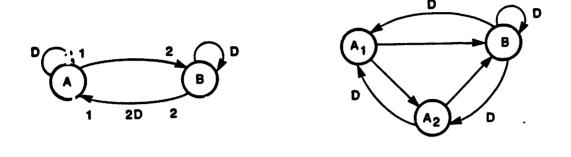

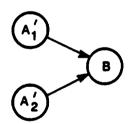

Any node which is simultaneously an initial node and a terminal node is represented as an isolated component in the acyclic precedence graph. In the DFG of Fig. 2.1(a), node B is an initial node, and nodes A and C are terminal nodes. The acyclic precedence graph of this DFG is shown in Fig. 2.1(b).

Fig. 2.1: (a) A DFG with three loops.  $L_3$  corresponds to a self loop. The node computation times are 10, 20 and 40 units for A, B, and C respectively. The iteration bound is 35 units, and loop  $L_1$  is the critical loop, (b) Directed acyclic precedence graph, (c): Schedule with iteration period of 60 units.

### 2.3. ITERATION BOUND

Any DFG involving loops or recursions or feedback has an upper bound on the computation rate or a lower bound on the iteration period [9-11]. This iteration period bound is given by

$$T_{\bullet} = Max \left\{ \frac{T_l}{D_l} \right\}, \qquad (2.1a)$$

where the maximum is taken over all loops l in the DFG, and  $T_l$  is the sum of the computation times associated with all the nodes in loop l, and  $D_l$  is the number of delay elements in loop l. The loop bound for the l-th loop can be written as

$$T_l \le D_l T_{\infty} \,. \tag{2.1b}$$

The loop  $l_0$  for which  $\frac{T_{l_0}}{D_{l_0}}$  is maximum is referred to as the *critical loop*, and the inequality becomes a strict equality for this loop.

Example 2.1: Consider the DFG in Fig. 2.1(a) with 3 loops. The bounds imposed on the iteration period by the three loops are respectively given by:

$$L_1: t_a + t_b + t_c \leq 2T_{\infty}$$

(2.2a)

$$L_2: t_a + t_b \le T_{\infty} \tag{2.2b}$$

$$L_3: t_a \leq T_{\infty},$$

(2.2c)

where  $t_a$ ,  $t_b$ , and  $t_c$  respectively represent the computation times associated with the nodes A, B, and C. The iteration bound is given by

$$T_{\infty} = Max(\frac{t_a + t_b + t_c}{2}, t_a + t_b, t_a). \quad \Box$$

(2.3)

Fig. 2.1(b) shows the acyclic precedence graph associated with the DFG. The double arrow represents the critical path in the precedence graph (a convention followed

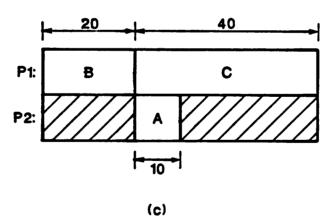

throughout this chapter). Since node B has a delay at its input, it can be invoked first. Nodes C and A can be invoked only after the execution of node B is complete. A two-processor schedule is shown in Fig. 2.1(c) for  $t_a = 10$ ,  $t_b = 20$ , and  $t_c = 40$ . The actual iteration period is 60 units, although the iteration period bound is only 35 units for this example. The loop  $L_1$  here is the critical loop.

## 2.4. RETIMING

Retiming was proposed by Leiserson, Rose, and Saxe to improve the clock rate in synchronous circuits (see [15]), and is applied here to improve the iteration period of multiprocessor schedules in DFGs. The process of retiming involves moving around the delays in the DFG such that the total number of delays in any loop remains unaltered, and the steady state input-output behavior of the system is preserved (see [15]). Removal of a fixed number of delays from each of the incoming arcs of any node, and addition of the same fixed number of delays to each of the outgoing arcs of the same node is an example of a valid retiming operation applied locally to a node. Note that this also corresponds to a cutset transformation around the node [16]. Thus, any local retiming operation can be performed at a node, only if all of its incoming arcs have delays associated with them. Any valid global retiming operation can always be described as a linear combination of such local retiming operations. Since the retiming operation preserves the number of delays in a loop [15] and the loop computation times, it also preserves the iteration bound of the DFG. The retiming operation can change the total number of delays in the DFG. This can be verified by locally retiming a node in a DFG, where

(p)

Fig. 2.2: (a) A retimed version of the DFG of Fig. 2.1(a), (b) Precedence graph, (c) Schedule with iteration period of 40 units.

the number of outgoing arcs is different from the number of incoming arcs.

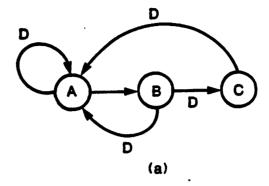

Fig. 2.2(a) shows a retimed version of the DFG of Fig. 2.1(a), obtained by performing retiming operation locally at node B. Note that the number of delays in each loop is unaltered (but, the total number of delays in the DFG has changed). The retiming process creates new initial conditions, and therefore, new precedence relations, new initial and terminal nodes and new schedules. The precedence graph and the schedule corresponding to the retimed DFG in Fig. 2(a) are respectively shown in Fig. 2.2(b) and Fig. 2.2(c). The iteration period of the retimed DFG is 40 units, which is 5 units greater than the iteration period bound, but 20 units less than the iteration period corresponding to the schedule in Fig. 2.1(c).

The retiming process attempts to evenly distribute the delays, i.e. it tries to equalize the computation times associated with all the nodes between any two delays in the critical loop. But it cannot guarantee an exactly even distribution of the delays, since an exactly even distribution would require splitting of nodes, which is not permitted. Because of this uneven distribution of delays, the actual iteration period is greater than the iteration bound.

#### 2.5. PERFECT DATA-FLOW PROGRAMS

In this section, we introduce the notion of perfect data-flow programs described by perfect graphs. We will make considerable use of these graphs in later sections.

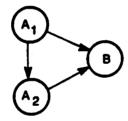

Definition 2.5: Any DFG which has one and only one delay in each loop is defined as a perfect graph.

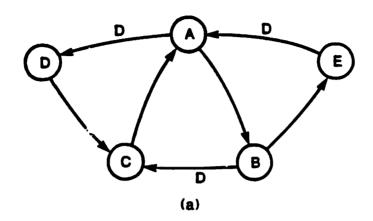

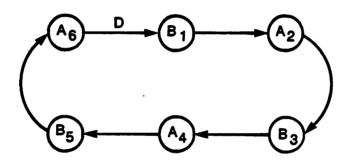

The DFG shown in Fig. 2.3(a) is an example of a perfect graph. This DFG has one initial

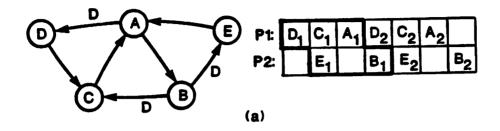

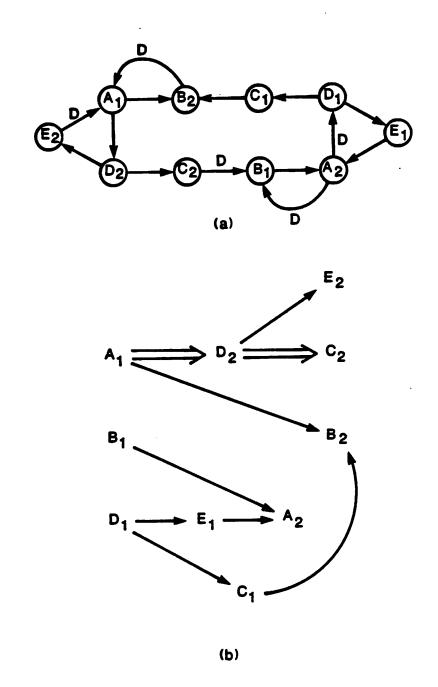

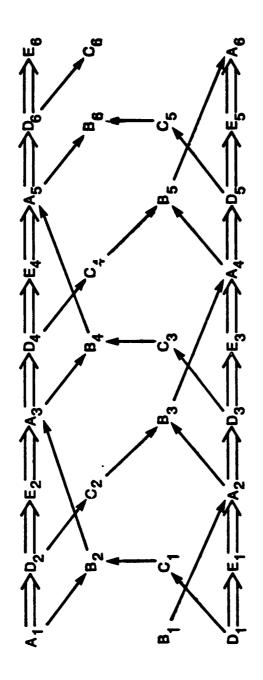

Fig. 2.3: (a) A Perfect Graph, (b) Precedence graph, (c) Partial schedule of two iterations. The iteration period of 3 units is obtained by overlapping two successive iterations. This schedule is rate-optimal.

node (node D), one terminal node (node E), and three loops, and all the loops are critical (assuming unit execution time for each node or task). The iteration bound for this DFG is 3 units of time (u.t.). The precedence graph for the DFG is shown in Fig. 2.3(b), and the length of the critical path is 5 u.t. Hence, any CPM schedule would require an iteration period of 5 u.t. However, we can exploit the periodicity or cyclic nature of the schedules, and overlap consecutive iterations to obtain a rate-optimal fully-static schedule as shown in Fig. 2.3(c). Note that the DFG did not need to be *retimed* to obtain a rate-optimal schedule. In fact, the perfect graphs have the property that they directly lead to rate-optimal fully-static schedules (and therefore completely eliminate the need for retiming or program unfolding), and it is this property that makes the notion of perfect graphs useful and important. The schedule in Fig. 2.3(c) has an iteration period of 3 (which is rate-optimal), and an input-to-output delay of 5 (the input-to-output delay is defined to be the maximum delay or latency from any initial node to any terminal node).

Fig. 2.4 shows several retimed versions of the DFG in Fig. 2.3(a), and the corresponding rate-optimal fully-static schedules. Even though all the schedules in Fig. 2.3 and 2.4 are rate-optimal, the schedule in Fig. 2.4(c) is only delay-optimal, which has an input-to-output delay of 3 u.t. Thus, retiming perfect graphs does not improve the iteration period, but may improve the input-to-output delay.

One might have already observed that not all the initial nodes necessarily start at the same time. For example, the executions of the starting nodes D and E in the perfect graph of Fig. 2.4(a) are skewed by one unit of time. The skewing of initial nodes permits overlap of consecutive iterations, and is often essential for construction of rate-optimal schedules.

Fig. 2.4: Several retimed versions of the perfect graph of Fig. 2.3(a), and corresponding rate-optimal schedules.

Definition 2.6: An arc from node u to node v is said to be transitive, if there is a path from node u to v, and the number of delays associated with the arc  $u \rightarrow v$  and the path from u to v are identical (similar to the definition in [24] for a directed acyclic graph). A single path can have more than one associated transitive arcs. The number of delays in the transitive arc  $u \rightarrow v$  can be either 1 or 0 in a perfect DFG.

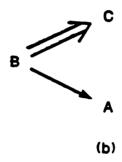

Example 2.2: See Fig. 2.5 for examples of transitive arcs. In Fig. 2.5(a) and Fig. 2.5(b), the path  $A \rightarrow B \rightarrow C$  and the arc  $A \rightarrow C$  contain equal number of delays (0 in Fig. 2.5(a) and 1 in Fig. 2.5(b)). Hence, the arc  $A \rightarrow C$  is transitive. In Fig. 2.5(a), the path  $A \rightarrow B \rightarrow C$  implies that there is a precedence constraint between invocations of task A and C. The transitive arc  $A \rightarrow C$  also dictates the same constraint, and is therefore redundant.  $\square$

Definition 2.7: A loop is said to be a maximal loop if it does not contain any transitive arcs. A loop which is not maximal is referred to as a non-maximal loop.

Example 2.3: The perfect graph in Fig. 2.5(c) has a single maximal loop. This is because the graph contains two transitive arcs, and after deletion of these two transitive arcs the DFG contains a single maximal loop, which is  $A \rightarrow B \rightarrow C \rightarrow D \rightarrow A$ . This maximal loop has 3 non-maximal loops associated with it. The loop bounds of the associated non-maximal loops can be derived from that of the corresponding maximal loop by deleting the computation times of the appropriate nodes. The loop bound for the maximal loop in Fig. 2.5(c) is given by

$$t_a + t_b + t_c + t_d < T_{\infty}. \tag{2.4a}$$

The loop bounds of the three associated non-maximal loops are given by

Fig. 2.5: Illustration of transitive arcs.

$t_a + t_b + t_c < T_{\infty}$ ,  $t_a + t_c < T_{\infty}$ ,  $t_a + t_b + t_c < T_{\infty}$ . (2.4b) The above non-maximal loop bounds are obtained by deleting the computation times of the appropriate nodes. Note that the loop bounds for the associated non-maximal loops are automatically satisfied if the loop bounds for the corresponding maximal loops are satisfied.  $\Box$

Lemma 2.1: The number of loop delays in a maximal loop and its associated non-maximal loops are same. This is true since the non-maximal loop consists of transitive arcs and from definition 2.6, the number of delays in a transitive arc and its associated path are same.

# Lemma 2.2: A non-maximal loop can never be a critical loop.

Proof: This follows from lemma 2.1 and definition 2.6. From lemma 2.1, the maximal loop and the associated non-maximal loops have the same number of delays, and from definition 2.6, the maximal loop contains all the nodes belonging to the associated non-maximal loop as well as additional nodes. The total computation time of the maximal loop is greater (for identical number of loop delay operators) than the non-maximal loop, and so the maximal loop has a more critical loop bound.

Lemma 2.3: A schedule for the graph obtained after deleting all the transitive arcs in the original DFG is an admissible schedule for the original DFG.

Proof: Deletion of a transitive arc does not alter the precedence constraints. Thus, deletion of all transitive arcs from the DFG does not alter its precedence constraints. Hence an admissible schedule for the graph obtained from the DFG after deletion of all the transitive arcs is also an admissible schedule for the original DFG.

Definition 2.8: A schedule of a list of Q nodes  $N_1 \rightarrow N_2 \rightarrow \cdots \rightarrow N_Q$  is said to be contiguous if the nodes are scheduled in that order without any intermediate gap or idle time. Note that any node can be scheduled in any processor in a multiprocessor implementation.

Now consider the following algorithm for scheduling of the recursive nodes of the perfect DFG (that is, the scheduling of the nodes not belonging to any loop is not considered).

Algorithm 2.1: First, we remove all the transitive arcs from the perfect graph, since the precedence relations due to these are automatically satisfied (see lemma 2.3). All the remaining loops of the DFG are maximal. The maximal loops are then ordered, and scheduled according to the decreasing order of their loop computation times. The nodes in each maximal loop are also ordered to form a list with the node containing the loop delay at its input arc as the leading node of the list, and the other nodes are placed so as to satisfy the precedence constraints. A separate processor is assigned for scheduling of each maximal loop. First, the nodes of the critical loop are scheduled contiguously in processor 1. Then, the nodes of the next critical loop are scheduled in processor 2 such that the schedules completed so far are preserved. In other words, if some of the nodes of this loop also belong to the critical loop (and therefore have already been scheduled in processor 1), then their schedule should remain unaltered. This process is repeated until scheduling of all the maximal loops is complete.

Remark: Note that we do not assume the scheduling of all the maximal loops to begin at the same time unit. In other words, the scheduling of the maximal loops in different processors can be skewed in time. This skewed scheduling separates consecutive iterations of the DFG by a non-vertical boundary. Also note that it is possible to merge the tasks of two or more processors to reduce the number of processors in a post-processing step, but this is not considered here as a part of the algorithm. The complexity of the above fully-static scheduling algorithm is polynomial in the number of nodes, whereas the complexity of the cyclo-static scheduling algorithm proposed in [18-22] is exponential.

Some properties of scheduling algorithm 2.1 are summarized in the following lemmas.

Lemma 2.4: Nodes in any maximal loop of a perfect DFG are scheduled non-contiguously (i.e. with intermediate gaps) if and only if a path consisting of nodes of this loop has an associated parallel path with a longer path computation time.

**Proof:** In algorithm 2.1, nodes of maximal loops are ordered to form a list with the node containing the loop delay as its leading node. A path corresponding to the maximal loop refers to a set of connected nodes, which are members of this list. To prove the "if" portion, consider the path  $N_1 \rightarrow N_2 \rightarrow N_4$  corresponding to some maximal loop, and its associated parallel path  $N_1 \rightarrow N_3 \rightarrow N_4$ , and assume the computation time of  $N_2$  to be shorter than that of  $N_3$ . This precedence results in a gap in scheduling of the nodes of this loop, since  $N_4$  can be scheduled only after the execution of  $N_3$  is complete. To prove the "only if" portion, assume that there exists some gap between completion of  $N_2$  and invocation of  $N_3$  in the scheduling of some path .... $\rightarrow N_1 \rightarrow N_2 \rightarrow N_3 \rightarrow N_4 \rightarrow ....$  (call this path  $P_1$ ) corresponding to a maximal loop. This would occur if the invocation of  $N_3$  is constrained by completion of another node (say  $N_5$ ). Denote the path ..... $\rightarrow N_5 \rightarrow N_3 \rightarrow .....$  as  $P_2$ . If  $N_3$  is the only common node

between  $P_1$  and  $P_2$  (i.e.  $P_1$  and  $P_2$  have no node in common to the left of  $N_3$ ), then the schedule of the nodes in the list .... $\rightarrow N_1 \rightarrow N_2$  could be right-shifted so that completion of  $N_2$  and  $N_5$  coincide. However, the existence of the gap in the schedule implies that the nodes to the left of  $N_3$  in paths  $P_1$  and  $P_2$  are dependent, and have at least one node in common. This implies the existence of an associated parallel path. This associated parallel path has a longer computation time.  $\square$

Remark: Two parallel paths in a perfect DFG must have the same number of delays (which can be either 1 or 0). If this were not the case, the two maximal loops containing the two parallel paths would have different number of loop delays, and the DFG would be imperfect.

Lemma 2.5: A contiguous scheduling of the nodes of the critical loop of the perfect DFGs is admissible.

Proof: From lemma 2.4, two parallel paths with different path computation times lead to a non-contiguous schedule, and the nodes of the path with less path computation time are scheduled with an intermediate gap. Since the paths of the critical loop have the largest path computation time, they can be scheduled without any intermediate gap. Any loop with gaps in the schedule must be non-critical.

Now we define two different types of processor idle time in the scheduling of the recursive nodes of a perfect DFG (recall recursive nodes are nodes which belong to at least one loop in the DFG).

Definition 2.9: The idle time of a processor is referred to as a gap delay (or gap time), if

this idle time is a result of a non-contiguous schedule (i.e. there exist two parallel paths with different path computation times). Any idle time, which is not a gap delay, is referred to as a *slack delay* or slack time (also referred to as skew delay or shimming delay).

Theorem 2.1: For any perfect graph, we can construct fully-static rate-optimal schedules without requiring any retiming transformation.

Proof: The nodes of the critical loop can be scheduled contiguously requiring a period equal to the critical loop computation time or the iteration bound. This schedule can be replicated over successive iterations with no gap at all in the same processor with a time displacement equal to the iteration bound. For each gap in the scheduling of nodes (of non-critical loops), there exists a path with longer computation time. This implies that the sum of the computation time and the gap time of any loop cannot exceed the critical loop computation time (or the iteration bound), and therefore the algorithm 2.1 results in a rate-optimal schedule. The schedule of the single iteration can be replicated with zero processor displacement and with a time displacement equal to the iteration period bound, and hence the schedule is fully-static. Note that this results in a non-negative loop slack time equal to the difference of the iteration bound and sum of the loop computation time and the loop gap time.

Theorem 2.2: The number of maximal loops in a perfect graph represents an upper bound on the number of processors to schedule the recursive nodes in a fully-static and rate-optimal manner.

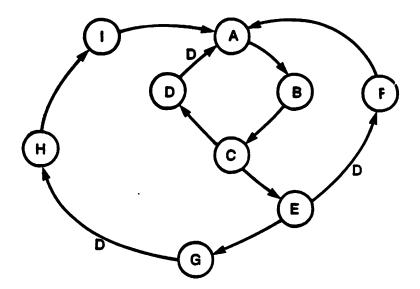

Fig. 2.6: A perfect graph with three loops.

Fig. 2.7: (a) Rate-optimal scheduling with three processors, (b) Rate-optimal schedule with two processors.

35

*Proof*: The scheduling algorithm 2.1 assigns a separate processor to each maximal loop. Hence, the upper bounds on the number of processors is equal to the number of maximal loops of the perfect DFG.

Example 2.4: Consider the DFG of Fig. 2.6, and the corresponding schedules in Fig. 2.7. The execution times of nodes D and F are 2 units each, and that of other nodes is 1 unit. The perfect graph has 2 initial nodes (nodes H and F), and two terminal nodes (nodes D and G). The loops are first ordered as HIABCEGH, FABCEF, and ABCDA. The critical loop HIABCEGH is first scheduled in processor P1 (see Fig. 2.7(a)). Then, the nodes of the next critical loop are scheduled in processor P2. Finally, the nodes of the last loop are scheduled in processor P3. We observe that we can merge the tasks in processors P2 and P3 to a single processor as shown in Fig. 2.7(b). This permits us to obtain a rate-optimal fully-schedule using 2 processors.  $\Box$

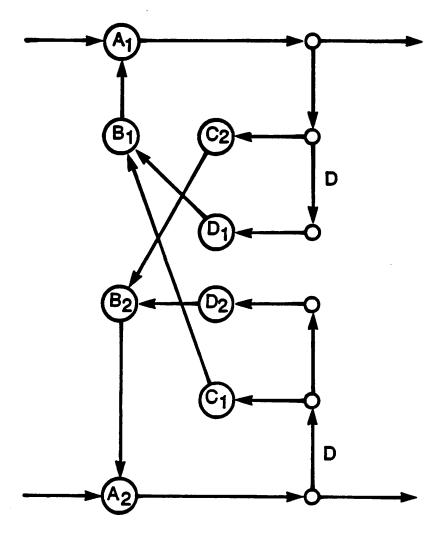

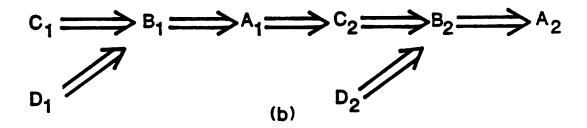

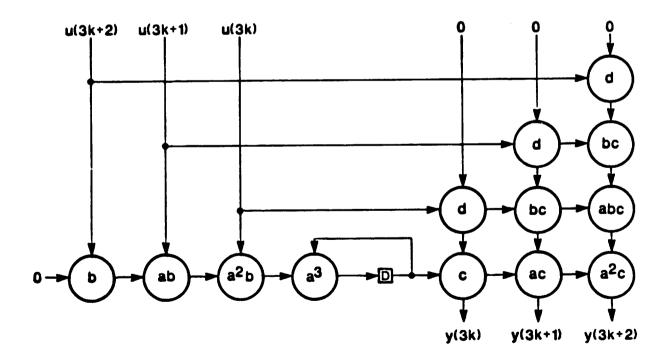

### 2.6. UNFOLDED DATA-FLOW PROGRAM GRAPHS

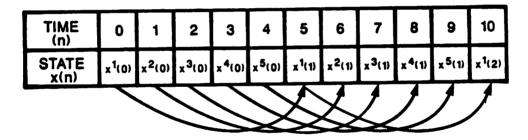

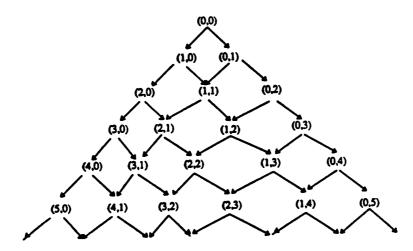

In this section, we study properties of unfolded or blocked data-flow program graphs. An unfolded DFG with an unfolding factor J contains J invocations of each node. The number of nodes and arcs in the unfolded DFG are respectively JN and JE, where N and E respectively represent the number of nodes and arcs in the original DFG. An execution cycle (or simply a cycle) of the unfolded DFG constitutes execution of JN nodes, and corresponds to merged execution of J successive iterations of the original DFG.

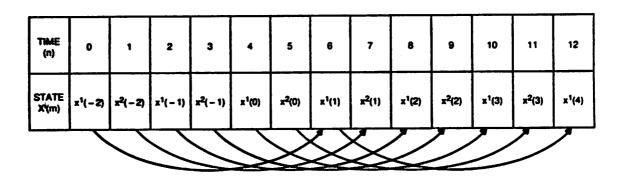

In the unfolded DFG, a node  $X_i$  computes the results of iteration  $x_{i+kJ}$  at the k-th cycle. As an example, let X be a node in the original DFG, and let  $X_1$ ,  $X_2$ , and  $X_3$  represent the corresponding three nodes in the unfolded DFG for J=3.

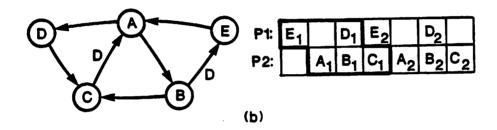

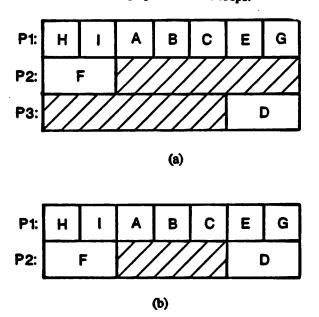

Fig. 2.8: (a) An equivalent unfolded DFG of the DFG in Fig. 2.1(a) for unfolding factor of two. This unfolded DFG is a perfect graph, (b) Precedence graph, (c) Rate-optimal schedule.

Then, the node  $X_1$  performs the iterations  $x_1$ ,  $x_4$ ,  $x_7$  in cycles 1, 2, and 3 respectively, node  $X_2$  performs the iterations  $x_2$ ,  $x_5$ ,  $x_8$  in cycles 1, 2, and 3 respectively, and similarly for  $X_3$ . We assume the convention that  $x_0$  is the initial condition. This implies that the output of any arc with a unit delay from the node  $X_3$  will correspond to the initial condition  $x_0$ . To be more precise, an arc with a delay from the node  $X_1$  will not correspond to  $x_0$ , but to  $x_{-2}$ . This block delay notion is important in the framework of this chapter. To conclude, a unit delay in the unfolded DFG is a J-slow delay.

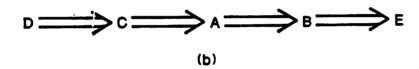

The unfolded DFG can be constructed very easily from the original DFG (see [18] for a systematic procedure). We illustrate this procedure here using the DFG of Fig. 2.1(a) as an example. Since each cycle in the unfolded DFG is periodic, and corresponds to J iterations of the original DFG, we need to consider only first J iterations. For J=2, we consider only the first two iterations of each node. The precedence constraints for the two iterations of the DFG of Fig. 2.1(a) are summarized as below:

$$A_1 = f_A(A_0, B_1, C_0), B_1 = f_B(A_0), C_1 = f_C(B_1),$$

(2.5a)

$$A_2 = f_A(A_1, B_2, C_1), B_2 = f_B(A_1), C_2 = f_C(B_2),$$

(2.5b)

where  $f_i(.)$  represents the functionality associated with the node i. The dependence relations in (2.5a) correspond to the first iteration, and those in (2.5b) for the next iteration. Note that the relations in (2.5b) are obtained from (2.5a) by shifting the indices appropriately. The unfolded DFG is constructed by incorporating the precedence relations in (2.5) and by inserting arcs with a unit delay from node  $A_2$  to  $A_1$  and  $B_1$ , and from  $C_2$  to  $A_1$  (to realize the initial conditions  $A_0$  and  $C_0$  respectively). The unfolded DFG is shown in Fig. 2.8(a). The only initial node of the DFG is  $B_1$ , and the terminal nodes are  $A_2$  and  $C_2$ . The precedence relations for this DFG are shown in Fig. 2.8(b). This unfolded DFG has several nice properties. One can verify that the DFG is indeed a perfect graph (this is

38

not a coincidence; systematic construction of perfect graphs from any DFG by unfolding is studied in section 2.7). Therefore, the unfolded DFG can be scheduled rate-optimally in a fully-static manner as shown in Fig. 2.8(c). Now we study some properties of the unfolded DFGs.

Lemma 2.6: The iteration bound associated with an unfolded DFG with an unfolding factor J is  $JT_{\infty}$ , where  $T_{\infty}$  is the iteration bound of the original DFG. The unfolded DFG schedules J iterations of the original DFG in  $JT_{\infty}$  units of time, and the iteration bound per iteration is not altered by unfolding.

Property 2.1: The number of delays in the unfolded DFG is exactly the same as that in the original DFG.

**Proof:** The delays represent initial states at the beginning of the execution. These delays activate the invocations, and are updated each cycle. Let  $D_T$  denote the total number of delays in the DFG. Then each iteration of the DFG updates  $D_T$  states to be used during the next iteration. We know that the termination of each iteration updates  $D_T$  values and the termination of the J-th iteration of the execution cycle of the unfolded DFG must also update  $D_T$  values to be used for the next execution cycle of the unfolded DFG. Thus unfolding conserves the number of delays in a DFG. As an example, the DFG in Fig. 2.1(a) and the unfolded DFG in Fig. 2.8(a) both contain 3 delays.  $\Box$

Property 2.2: Let  $T_i$  and  $D_i$  respectively correspond to the sum of all computation times and the delay count associated with the i-th loop in the unfolded DFG. Then

**39**

$$T_i \le JT \mathcal{L}_i \tag{2.6}$$

must hold.

*Proof*: Let  $T'_{\infty}$  be the iteration bound of the unfolded DFG. Then,  $T_i \leq T'_{\infty}D_i$  must hold. But,  $T'_{\infty} = JT_{\infty}$  (due to lemma 2.6), and hence (2.6) must hold.

Lemma 2.7: Any linear additive combination of the non-critical maximal loop bounds of the original DFG can never correspond to a critical loop bound of the unfolded DFG.

Proof: Consider three non-critical maximal loops  $L_1$ ,  $L_2$ , and  $L_3$ . Then,  $T_1 < T_{\bullet}D_1$  and  $T_2 < T_{\bullet}D_2$ , and  $T_3 < T_{\bullet}D_3$ . Thus the linear additive combination  $T_1 + T_2 + T_3 < T_{\bullet}(D_1 + D_2 + D_3)$  can never be a critical loop, since this contains a strict inequality, and a critical loop must contain a strict equality. The argument generalizes.  $\square$

Corollary: A critical loop bound in the unfolded DFG corresponds to a linear additive combination of critical loop bounds of the original DFG. However, any linear additive combination of loop bounds of the original DFG may not correspond to a critical loop bound of the unfolded DFG.

Property 2.3: Any loop bound relation of the type (2.6) in the unfolded DFG can be obtained either by multiplying a loop bound relation in the original DFG by a constant, or by taking linear additive combinations of the loop bounds of the original DFG such that the right side is a multiple of J.

*Proof*: The right side of the loop bound for any loop in the unfolded DFG must be a multiple of J (when expressed in terms of  $T_{\infty}$ , the iteration bound of the original

DFG) due to property 2.2. Assume that the i-th loop of the original DFG has a bound  $T_i \leq D_i T_{\infty}$ . Any linear additive combination of one or more loop bounds in the original DFG, which corresponds to a loop bound in the unfolded DFG, must be of the form

$$\sum_{i=1}^{N} \alpha_i T_i \le \left(\sum_{i=1}^{N} \alpha_i \ D_i\right) T_{\infty}, \tag{2.7}$$

where N is the number of loops of the original DFG, and  $\sum_{i=1}^{N} \alpha_i D_i$  is divisible by J. Any loop bound in the unfolded DFG, which is not of the form (2.7), will imply an entirely new loop bound in the original DFG. But this is not possible, since unfolding does not create new loop bounds.  $\square$

Note that any linear additive combination of the loop bounds of the original DFG of the form (2.7) may not correspond to a loop bound in the unfolded DFG. Now we discuss four important special cases of (2.7) in the context of a single loop bound. Let the loop bound of some loop in the original DFG be  $T \leq DT_{\infty}$ , where T is the loop computation time, D the loop delay count, and  $T_{\infty}$  the iteration bound of the original DFG. The iteration bound of the unfolded DFG is  $T'_{\infty} = JT_{\infty}$ .

Case I: J divisible by D: Let us assume J = QD and Q is an integer. Then a loop bound of the unfolded DFG will be of the form  $QT \le (JT_{-})$  or  $QT \le T'_{-}$ . This implies that one loop of the unfolded DFG will contain a single delay and Q instances of the nodes of the loop of the original DFG. Since the unfolded DFG contains J = QD instances of each node and D delays (due to delay conservation, property 2.1), it must contain D distinct loops with a single delay in each loop.

Case II: D divisible by J: Assume PJ = D. The loop bound of the unfolded DFG is of the form  $T \le PT'_{\infty}$ . The unfolded DFG contains J distinct loops, and P delays in each of these loops.

Case III: D and J coprime: For this case, a loop bound in the unfolded DFG is of the form  $JT \le D$  ( $JT_{\infty}$ ) or  $JT \le DT'_{\infty}$ . The unfolded DFG contains one distinct loop with D loop delays.

Case IV: General Case: Assume PJ = QD, where P and Q are coprime. The loop bound of the unfolded DFG is of the form  $QT \leq PT'_{\infty}$ . The unfolded DFG contains  $\frac{J}{Q} = \frac{D}{P}$  distinc: loops with P delays in each of these loops.

Example 2.5: Consider the DFG of Fig. 2.1(a) and its unfolded DFG of Fig. 2.8(a). The original loop bounds are

$$t_a \le T_{\infty}, t_a + t_b \le T_{\infty}, t_a + t_b + t_c \le 2T_{\infty}$$

. (2.8a)

The loop bounds of the unfolded DFG (with unfolding factor two) are

$$2t_a \le T'_{\infty}$$

,  $2t_a + 2t_b \le T'_{\infty}$ ,  $t_a + t_b + t_c \le T'_{\infty}$ ,  $2t_a + t_b \le T'_{\infty}$ , which are linear additive combinations of the original DFG loop bounds.  $\square$

Property 2.4: Any loop in the original DFG with D loop delays leads to D distinct loops in the unfolded DFG for an unfolding factor of KD. Each of these distinct loops contains a unit loop delay, and K instances of each node belonging to the loop in the original DFG.

*Proof*: This follows from special Case I of property 2.3.  $\square$

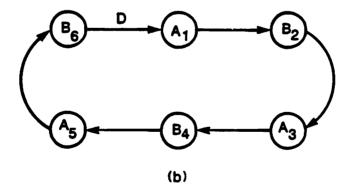

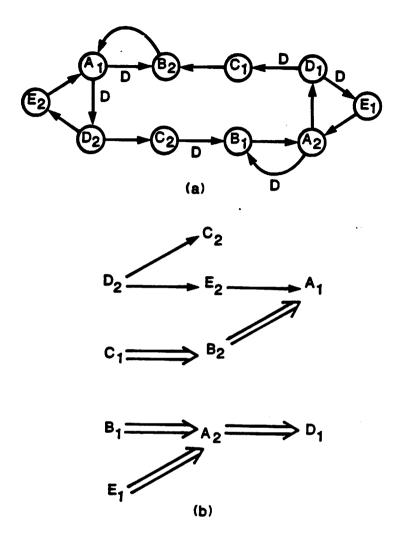

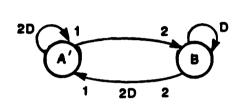

Fig. 2.9: (a) A DFG, (b) Equivalent unfolded DFG for unfolding factor 6.

Example 2.6: Consider the simple example of a two node DFG in Fig. 2.9(a). Fig. 2.9(b) shows an equivalent unfolded DFG for an unfolding factor 6. The original DFG has 2 delays in the loop, and the unfolded DFG has 2 distinct loops with a single delay in each loop. Each loop in the unfolded DFG contains 3 instances of the nodes of the original loop for an unfolding factor of 6.

## 2.7. FULLY-STATIC RATE-OPTIMAL SCHEDULING

This section uses the results of the previous sections to prove that the tasks of any DFG can be scheduled rate-optimally in a fully-static manner.

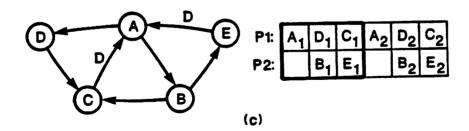

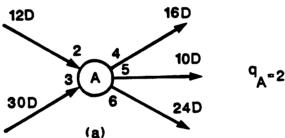

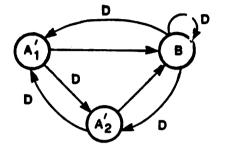

One might conjecture that we can always achieve a rate-optimal schedule by using an unfolding factor equal to the delay count in the critical loop and then by retiming the unfolded DFG. This is because, the critical loop in the equivalent unfolded DFG would contain a single delay, and the tasks in the critical loop of the unfolded DFG can then be evenly distributed. However, this conjecture is not true! Although the single delay in the critical loop permits an even distribution of the tasks in that loop of the unfolded DFG, another non-critical loop might suffer from an uneven distribution of tasks, and may lead to an iteration period greater than the iteration bound. This is illustrated using the DFG example in Fig. 2.10, where the loop delay counts in the DFG are 2 and 3 respectively. The execution times of nodes A, B, C, D, and E in Fig. 2.10(a) are respectively 20, 5, 10, 10, and 2, and the iteration bound is 16, and corresponds to the critical loop  $L_1$ . The precedence relation of the DFG is shown in Fig. 2.10(b), and the length of the critical path (or equivalently the iteration period for this DFG) is 20 units.

Fig. 2.10: (a) A DFG. The node execution times are 20, 5, 10, 10, and 2 units for nodes A, B, C, D, and E respectively, (b) Precedence graph.

Fig. 2.11: (a) Unfolded DFG for the DFG in Fig. 2.10(a) with unfolding factor 2, (b) Precedence graph

Since the number of delays in the critical loop is 2, we construct an equivalent unfolded DFG with J=2 as shown in Fig. 2.11(a). The precedence graph for the unfolded DFG is shown in Fig. 2.11(b), and leads to an iteration period of 20 units. We can improve the iteration period by retiming the unfolded DFG (since this unfolded DFG is not a perfect graph). Fig. 2.12(a) shows the retimed version of the unfolded DFG, and Fig. 2.12(b) shows the corresponding precedence relation. From the critical path in the unfolded DFG, we observe that the cycle time corresponds to 35 units, or equivalently the iteration period is  $\frac{35}{2} = 17.5$  units (which is greater than the bound by 1.5 units). This is the minimum iteration period that can be achieved with an unfolding factor of 2.

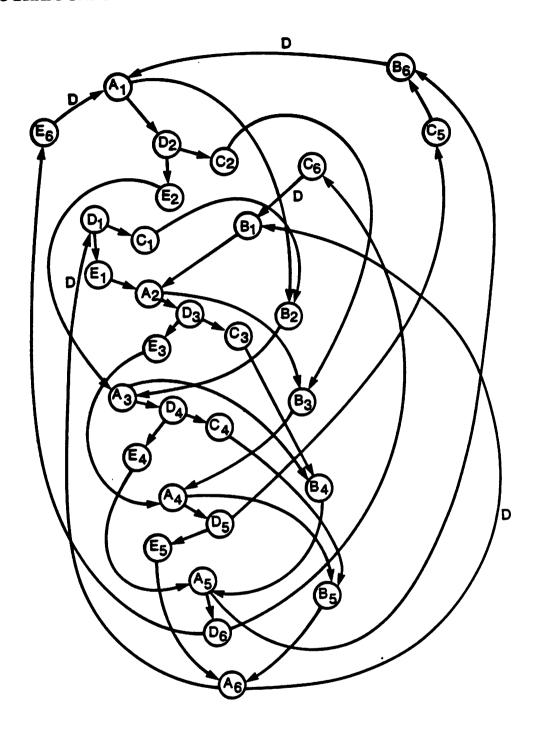

Now we proceed to prove that an unfolding factor given by the least common multiple of the number of delays of the loops in a DFG will lead to a perfect unfolded DFG, which can then be scheduled in a fully-static rate-optimal manner without requiring any retiming at all. Before we prove this, let us consider the example of the DFG in Fig. 2.10(a). Since the delay counts in the maximal loops are 2 ad 3 respectively, the least common multiple is 6, and hence we need an unfolding factor of 6 to obtain a rate-optimal schedule. The unfolded DFG is shown in Fig. 2.13(a) for an unfolding factor of 6, and one can verify that it is indeed a perfect graph. The precedence graph of this unfolded DFG is shown in Fig. 2.13(b), and the length of the critical path is 96, which corresponds to an iteration period of 16 units, equal to the iteration bound. Now we proceed to prove that fully-static rate-optimal scheduling of DFGs is admissible, and we then derive an upper bound on the number of processors to achieve a rate-optimal schedule.

Fig. 2.12: (a) Retimed version of the unfolded DFG in Fig. 2.11(a), (b) Precedence graph

Fig. 2.13(a): Unfolded DFG for the DFG in Fig. 2.10(a) for unfolding factor of six.

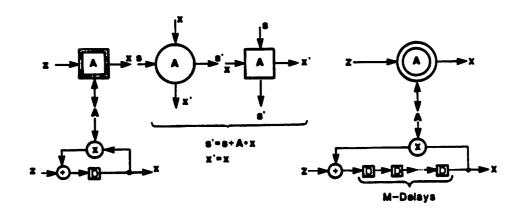

Theorem 2.3: Any unfolded DFG with an unfolding factor equal to the least common multiple of the loop delay counts of the original DFG corresponds to a perfect graph.

Proof: Since the unfolding factor is the least common multiple of the delay counts, it is a multiple of the delay count in every loop. From property 2.4, any loop with D delays must transform to D distinct maximal loops in the unfolded DFG, and all loops in the unfolded DFG must have a single delay inside each loop. Since all loop delay counts in the original DFG are less than the unfolding factor, any linear additive combination will also lead to a single loop delay in the unfolded DFG. Since every loop in the unfolded DFG has a single delay, the unfolded DFG is a perfect graph. From theorem 2.1, the nodes in perfect graphs can always be scheduled in a fully-static rate-optimal manner.  $\Box$