Copyright © 1989, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## A RETARGABLE MICROCODE GENERATOR FOR THE LAGER ENVIRONMENT

by

-

Monte F. Mar

Memorandum No. UCB/ERL M89/78

•

19 June 1989

## A RETARGABLE MICROCODE GENERATOR FOR THE LAGER ENVIRONMENT

by

Monte F. Mar

Memorandum No. UCB/ERL M89/78

19 June 1989

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## A RETARGABLE MICROCODE GENERATOR FOR THE LAGER ENVIRONMENT

by

Monte F. Mar

Memorandum No. UCB/ERL M89/78

19 June 1989

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Abstract

The ability to rapidly implement VLSI custom processor based systems is limited by the tools that can map high level language expressions into microcode for the new architectures. Past efforts have used dedicated code generators or simplified control structures not requiring code generators. A bottom up design approach has been used to develop a prototype self retargeting microcode generator for the Lager Silicon Assembly System. A graph tracing algorithm was developed and implemented as the basis of the code generator. By making use of structural information normally supplied for layout generation, the algorithm can map C language statements to a variety of architectures. The prototype code generator has been tested on parts of a multiprocessor fingerprint filtering system. Results show that the approach is feasible, but improvements are needed. The report discusses the design condsiderations and development of the prototype code generator. A tutorial example for the prototype microcode generator is presented in this report.

## Acknowledgements

I thank my family for encouraging and supporting me throughout the past 2 years. Special thanks to my father for his advice on technical writing.

I would like to thank Professor Rajeev Jain of UCLA for providing the opportunity to work on this project. He is responsible for introducing me to the world of CAD tools and design automation. I would also like to thank Professors Robert Brodersen and Jan Rabaey for reading the report and suggesting changes and improvements. Special thanks to Professor Brodersen for being my advisor during the project. I also acknowledge Paul Yang, Paul Tahjadi, and Phil Duncan of UCLA for their help in the effort to implement to smoothing processor of the fingerprint filter.

This research was sponsored by DARPA under the contract N00039-87- C-0182 .

## Contents

| 1       Introduction       5         1.1       Goals and Objectives       5         1.2       Outline       6         2       Basic Concepts for Microcode Generation.       6         2.1       An Overview of Microcode Generation.       7         2.2       Instruction Sets and Code Generation.       7         2.3       Silicon Compilation and Code Generation.       6         2.4       Microcode Generation and The Lager System.       10         2.4.1       Past Microcode Generation Work in the Lager System.       10         2.4.2       Background on Lager IV and the OCT database.       11         2.5       Summary       11         3.1       Objectives for a Lager IV Assembler.       11         3.2       Assumptions and Models for a Code Generation.       14         3.2.1       An Overview of the Approach to Code Generation.       14         3.2.2       The Architecture Model.       14         3.2.3       Affects of Assuming an Architecture Model.       14         3.3       A Behavioral Description.       14         3.4       Summary       14         3.4       Summary       14         3.4       Summary       14         3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ta | ble o | of Cont | ents                                        | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|---------|---------------------------------------------|----|

| 1.1 Goals and Objectives       1.2         1.2 Outline       1.2         2 Basic Concepts for Microcode Generation.       1.2         2.1 An Overview of Microcode Generation.       1.2         2.2 Instruction Sets and Code Generation.       1.2         2.3 Silicon Compilation and Code Generation.       1.2         2.4 Microcode Generation and The Lager System.       1.0         2.4.1 Past Microcode Generation Work in the Lager System.       1.1         2.4.2 Background on Lager IV and the OCT database.       1.1         2.5 Summary       1.1         3.1 Objectives for a Lager IV Assembler.       1.1         3.2.1 An Overview of the Approach to Code Generation.       1.4         3.2.2 The Architecture Model.       1.1         3.2.3 Affects of Assuming an Architecture Model.       1.1         3.3.4 Behavioral Description.       1.1         3.4 Summary       1.1         3.4 Summary       1.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Li | st of | Figure  | s                                           | 4  |

| 1.2 Outline       1.2 Outline         2 Basic Concepts for Microcode Generation.       1         2.1 An Overview of Microcode Generation.       1         2.2 Instruction Sets and Code Generation.       1         2.3 Silicon Compilation and Code Generation.       1         2.4 Microcode Generation and The Lager System.       16         2.4.1 Past Microcode Generation Work in the Lager System.       16         2.4.2 Background on Lager IV and the OCT database.       11         2.5 Summary       11         3.1 Objectives for a Lager IV Assembler.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         3.5 A Behavioral Description.       15         3.6 The Microcode Generator.       14         3.7 A Behavioral Description.       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1  | Intr  | oducti  | on                                          | 5  |

| 1.2 Outline       1.2 Outline         2 Basic Concepts for Microcode Generation.       1         2.1 An Overview of Microcode Generation.       1         2.2 Instruction Sets and Code Generation.       1         2.3 Silicon Compilation and Code Generation.       1         2.4 Microcode Generation and The Lager System.       16         2.4.1 Past Microcode Generation Work in the Lager System.       16         2.4.2 Background on Lager IV and the OCT database.       11         2.5 Summary       11         3.1 Objectives for a Lager IV Assembler.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         3.5 A Behavioral Description.       15         3.6 The Microcode Generator.       14         3.7 A Behavioral Description.       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 1.1   | Goals   | and Objectives                              | 5  |

| 2.1 An Overview of Microcode Generation.       2.2 Instruction Sets and Code Generation.       2.3 Silicon Compilation and Code Generation.       2.4 Microcode Generation and The Lager System.       1.6 Silicon Compilation and Code Generation.       2.4 Microcode Generation and The Lager System.       1.6 Silicon Compilation and Code Generation.       2.4 Microcode Generation and The Lager System.       1.6 Silicon Compilation and Code Generation.       1.6 Silicon Code Generation.                                                                                                                                                                                                                                                                                                                                                                                                  |    | 1.2   |         |                                             | 6  |

| 2.2       Instruction Sets and Code Generation.       8         2.3       Silicon Compilation and Code Generation.       9         2.4       Microcode Generation and The Lager System.       10         2.4.1       Past Microcode Generation Work in the Lager System.       10         2.4.2       Background on Lager IV and the OCT database.       11         2.5       Summary       12         3       Developing a Microcode Generator for LagerIV.       14         3.1       Objectives for a Lager IV Assembler.       14         3.2       Assumptions and Models for a Code Generator.       14         3.2.1       An Overview of the Approach to Code Generation.       14         3.2.2       The Architecture Model.       14         3.2.3       Affects of Assuming an Architecture Model.       14         3.3       A Behavioral Description.       14         3.4       Summary       14         3.4       Summary       14         3.4       Summary       14         3.4       Implementation Details of the Microcode Generator.       24         4       Implementation Details of the Microcode Generator.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  | Bas   | ic Con  | cepts for Microcode Generation.             | 7  |

| 2.3 Silicon Compilation and Code Generation.       9         2.4 Microcode Generation and The Lager System.       16         2.4.1 Past Microcode Generation Work in the Lager System.       16         2.4.2 Background on Lager IV and the OCT database.       16         2.5 Summary       16         3.1 Objectives for a Lager IV Assembler.       16         3.2 Assumptions and Models for a Code Generator.       16         3.2.1 An Overview of the Approach to Code Generation.       16         3.2.2 The Architecture Model.       16         3.2.3 Affects of Assuming an Architecture Model.       16         3.3 A Behavioral Description.       16         3.4 Summary       17         3.5 A Behavioral Description.       17         3.6 The Microcode Generator.       17         3.7 A Behavioral Description.       17         3.8 Summary       17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 2.1   | An Ov   | erview of Microcode Generation              | 7  |

| 2.4 Microcode Generation and The Lager System.       16         2.4.1 Past Microcode Generation Work in the Lager System.       16         2.4.2 Background on Lager IV and the OCT database.       16         2.5 Summary       12         3 Developing a Microcode Generator for LagerIV.       12         3.1 Objectives for a Lager IV Assembler.       12         3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.2   | Instruc | tion Sets and Code Generation               | 8  |

| 2.4.1 Past Microcode Generation Work in the Lager System.       10         2.4.2 Background on Lager IV and the OCT database.       11         2.5 Summary       11         3 Developing a Microcode Generator for LagerIV.       12         3.1 Objectives for a Lager IV Assembler.       14         3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 2.3   | Silicon | Compilation and Code Generation             | 9  |

| 2.4.2       Background on Lager IV and the OCT database.       12         3       Developing a Microcode Generator for LagerIV.       13         3.1       Objectives for a Lager IV Assembler.       14         3.2       Assumptions and Models for a Code Generator.       14         3.2.1       An Overview of the Approach to Code Generation.       14         3.2.2       The Architecture Model.       14         3.3.3       A flects of Assuming an Architecture Model.       14         3.4       Summary       14         4       Implementation Details of the Microcode Generator.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.4   | Microo  | ode Generation and The Lager System         | 10 |

| 2.5       Summary       12         3       Developing a Microcode Generator for LagerIV.       13         3.1       Objectives for a Lager IV Assembler.       14         3.2       Assumptions and Models for a Code Generator.       14         3.2.1       An Overview of the Approach to Code Generation.       14         3.2.2       The Architecture Model.       14         3.2.3       Affects of Assuming an Architecture Model.       14         3.3       A Behavioral Description.       14         3.4       Summary       14         4       Implementation Details of the Microcode Generator.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |       |         | - · · ·                                     | 10 |

| 3 Developing a Microcode Generator for LagerIV.       13         3.1 Objectives for a Lager IV Assembler.       14         3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       | 2.4.2   | Background on Lager IV and the OCT database | 11 |

| 3.1 Objectives for a Lager IV Assembler.       13         3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       15         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 2.5   | Summ    | ary                                         | 12 |

| 3.1 Objectives for a Lager IV Assembler.       13         3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       15         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3  | Dev   | elopin  | g a Microcode Generator for LagerIV.        | 13 |

| 3.2 Assumptions and Models for a Code Generator.       14         3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | -  |       | -       | -                                           | 13 |

| 3.2.1 An Overview of the Approach to Code Generation.       14         3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    | 3.2   | -       | •                                           | 14 |

| 3.2.2 The Architecture Model.       14         3.2.3 Affects of Assuming an Architecture Model.       14         3.3 A Behavioral Description.       14         3.4 Summary       14         4 Implementation Details of the Microcode Generator.       24         4.1 Overview.       24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |       |         | •                                           | 14 |

| 3.2.3 Affects of Assuming an Architecture Model.       12         3.3 A Behavioral Description.       12         3.4 Summary       12         4 Implementation Details of the Microcode Generator.       20         4.1 Overview.       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |       | 3.2.2   |                                             | 15 |

| 3.3 A Behavioral Description.       14         3.4 Summary       15         4 Implementation Details of the Microcode Generator.       20         4.1 Overview.       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |       | 3.2.3   |                                             | 18 |

| 3.4 Summary       1         4 Implementation Details of the Microcode Generator.       20         4.1 Overview.       21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    | 3.3   |         | •                                           | 18 |

| 4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |       |         | •                                           | 19 |

| 4.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 4  | Imr   | lemen   | tation Details of the Microcode Generator.  | 20 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _  | -     |         |                                             | 20 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 4.2   |         |                                             | 21 |

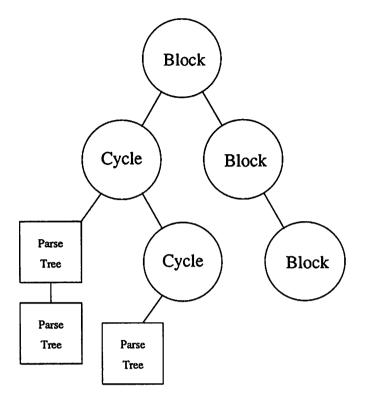

| 4.2.1 The Input Program Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |       |         | 0                                           | 21 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |         |                                             | 23 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 4.3   |         |                                             | 25 |

| The The black of the state of t |    | 2.0   |         |                                             | 25 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |       |         |                                             | 28 |

|                                                              |        | 4.3.3   | The initializer module                        | • |     | •   | ٠  | • | • | 30 |

|--------------------------------------------------------------|--------|---------|-----------------------------------------------|---|-----|-----|----|---|---|----|

|                                                              |        | 4.3.4   | The interface modules                         | • |     | •   | •  | • | • | 30 |

|                                                              | 4.4    | Summ    | ary                                           | • | • • | •   | •  | • | • | 31 |

| 5                                                            | Use    | of the  | Prototype Microcode Generator                 |   |     |     |    |   |   | 32 |

|                                                              | 5.1    | The D   | esign Process Using the Microcode Generator   | • |     | •   | •  | • | • | 32 |

|                                                              | 5.2    | An Ad   | Idress Calculation Unit Example               | • |     | •   | •  | • | • | 32 |

|                                                              |        | 5.2.1   | Examining the Algorithm                       | • |     | •   | •  | • | • | 34 |

|                                                              |        | 5.2.2   | Defining the System Architecture              | • |     | •   | •  | • | • | 34 |

|                                                              |        | 5.2.3   | Algorithm coding                              | • |     | •   | •  | • | • | 36 |

|                                                              |        | 5.2.4   | Microcode Generation                          | • | • • | •   |    | • | • | 37 |

|                                                              |        | 5.2.5   | Post processing.                              | • | • • | •   | •  | • | • | 37 |

|                                                              |        | 5.2.6   | Layout                                        | • | • • | •   | •  | • | • | 38 |

|                                                              | 5.3    | The F   | ingerprint Smooth Processor, a Second Example | • | •   | • • | •  | • | • | 38 |

| 6                                                            | Eva    | luatio  | n and Conclusions.                            |   |     |     |    |   |   | 39 |

|                                                              | 6.1    | Proble  | ems with the Current Implementation           |   |     |     |    |   |   | 39 |

|                                                              | 6.2    | Future  | e Work                                        |   | •   |     | •  | • |   | 40 |

|                                                              | 6.3    | Conclu  | usion                                         | • | •   | • • | •  | • | • | 41 |

| B                                                            | ibliog | graphy  |                                               |   |     |     |    |   |   | 42 |

| A                                                            | Use    | er's Ma | anual                                         |   |     |     |    |   |   | 44 |

| B Example Files for the Address Calculation Unit Example. 54 |        |         |                                               |   |     |     | 54 |   |   |    |

## List of Figures

| 2.1 | A Basic code generator.                               | 7 |

|-----|-------------------------------------------------------|---|

| 2.2 | Using data flow graphs to describe an add instruction | 9 |

| 2.3 | Design process using Lager IV                         | 2 |

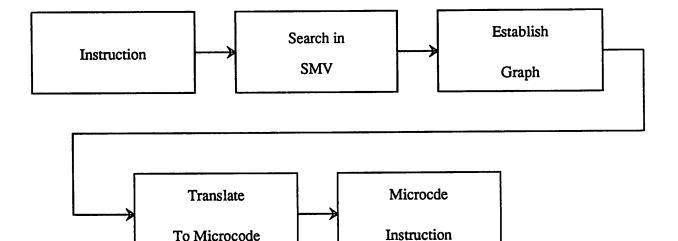

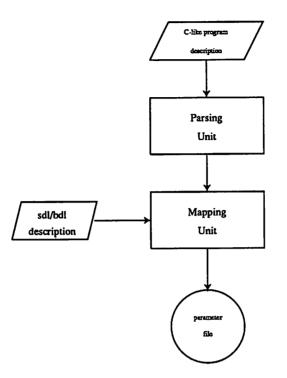

| 3.1 | Approach to microcode generation                      | 5 |

| 3.2 | Architecture model example                            | 3 |

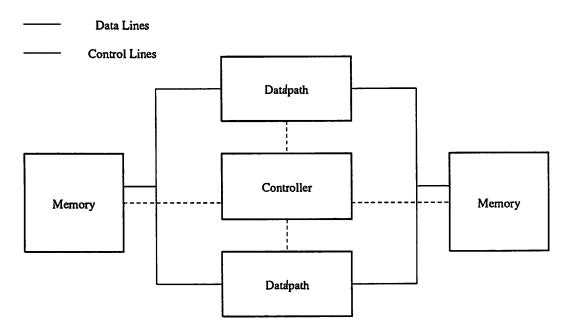

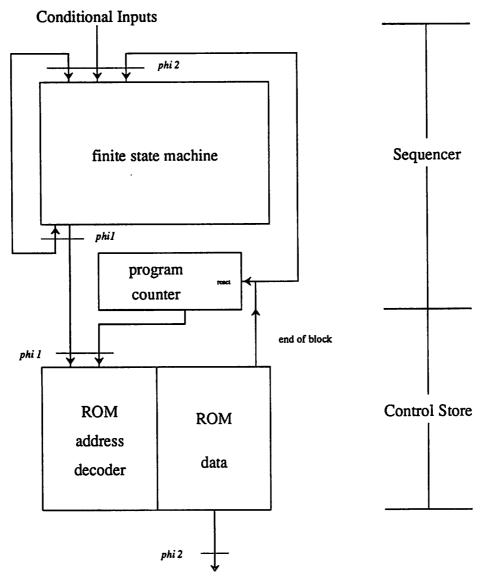

| 3.3 | Block Diagram of the Lager Kappa Controller           | 7 |

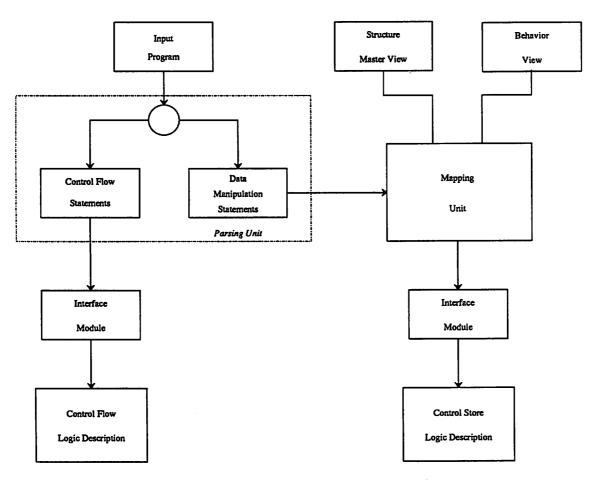

| 4.1 | Basic diagram of the microcode generator              | 1 |

| 4.2 | Block diagram of the microcode generator              | 2 |

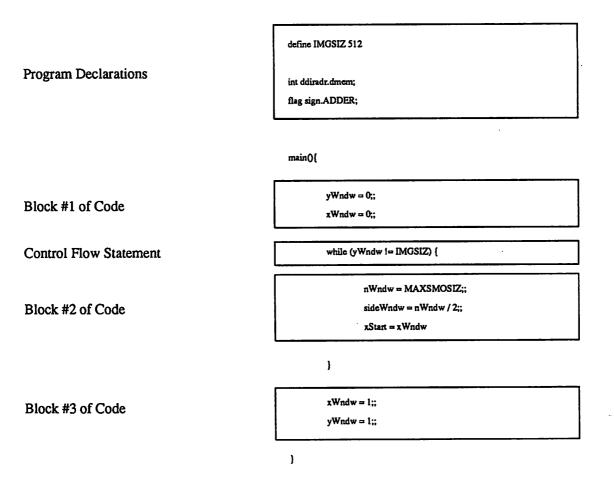

| 4.3 | Example of the program model                          | 3 |

| 4.4 | Data structure used in the parser                     | 5 |

| 4.5 | Mapping an algorithmic expression to control signals  | 7 |

| 5.1 | Flowchart for use of the microcode generator          | 3 |

| 5.2 | The address calculation unit datapath                 | 4 |

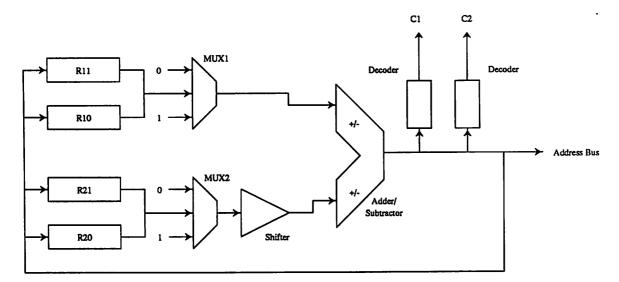

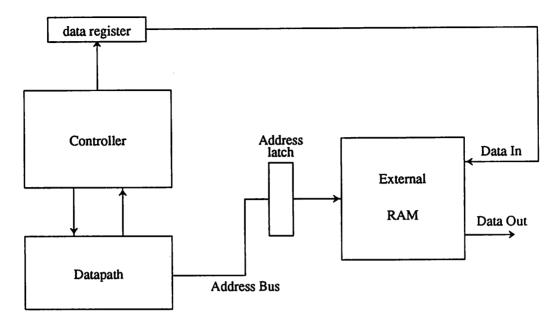

| 5.3 | System block diagram                                  | 5 |

## Chapter 1

## Introduction

A design of a filter for a fingerprint recognition system has shown that a custom multiprocessor architecture can provide a compact high throughput system that will process an image in about 10 seconds [1]. Using multiple Kappa processors from the Lager system [2], an optimistic estimate is about 25 seconds. On a VAX 8650, it takes 5 minutes [3]. The amount of speedup attained in this case is directly related to the amount of customization. Custom designs can provide higher performance, but the increase in performance is gained at the cost of increased design time and increased processor complexity.

The Lager IV Silicon Assembly system provides support for the development of complex integrated circuits. It is oriented towards structural compilation from hardware descriptions and currently provides support for a single processor architecture that can be slightly altered. The user pays a cost for making changes: the hardware description and the architecture descriptions necessary for both the compiler and microcode generator must be modified and then verified. In order to explore an entirely new architecture, the user must create several new description files and debug them before they will be useful for processor design.

## 1.1 Goals and Objectives

The problem examined in this research project was the generation of microcode for custom micro-programmed processors. This research was motivated by the implementation of a multiprocessor fingerprint filter system. The design of the processors had already been completed [1], but since each processor used a new architecture, none of the existing Lager tools could generate the microcode. Thus the objective of this research was to provide a means of mapping microcode descriptions to a class of architectures. Inherent in this objective was the desire to minimize the cost of retargeting the microcode generator when switching from architecture to architecture, allowing designers more freedom in their implementations without forcing them to use an existing target architecture or to rewrite existing tools.

The goal of this project was to create a prototype microcode generator that could retarget itself using information found in the design database. The designer would only have to specify the structure of the processor and provide a microprogram description. To aid the designer in microprogram verification, a simulator should be provided for microprogram descriptions. Finally, the prototype microcode generator should be able to generate the microcode for the 3 processors in the fingerprint filtering system.

## 1.2 Outline

This report consists of 6 chapters. Chapter 2 reviews concepts about retargetable microcode generators and their relation to silicon compilers. In Chapter 3, the basic approach to the problem is outlined. Some details of the implementation for the microcode generator developed in this project are discussed in chapter 4. Chapter 5 gives a tutorial example of using the microcode generator. The report concludes with a discussion of the results in chapter 6.

## Chapter 2

# Basic Concepts for Microcode Generation.

## 2.1 An Overview of Microcode Generation.

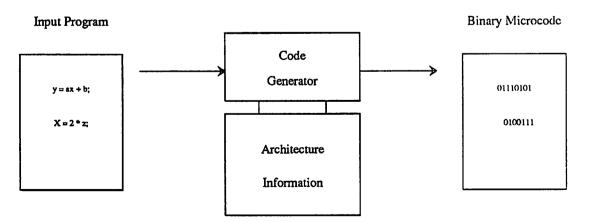

A basic code generator like the one shown in Fig. 2.1 translates an input description to binary machine code using information about the processor architecture. The architectural information includes the timing schemes used in the processor, the type of registers available, information about the controller, and the instruction set.

Software programmable processors use code generators that are optimized for a given target architecture. An example is the code generator in the Intel ASM86 assembler, which was written specifically to handle the peculiarities of the 8086 microprocessor [4].

Figure 2.1: A Basic code generator.

The fixed architecture of a general purpose processor allows software developers to apply established techniques for code generators used in assemblers and compilers. Heuristic approaches must be used for code generation because the complexity for generating optimal code is not known [5]. The appropriate code generation techniques for a given architecture are determined by the target machine and the instruction set.

ASIC designs encourage the development of new architectures that handle computations for algorithms in a dedicated and efficient manner. Since a code generator is a function of the instruction set and the target machine, the best code generator for an ASIC processor is an application specific one. Development of specialized code generators for every new ASIC would be costly, so a more generalized code generator is desired.

A solution is to develop a retargetable code generator which can generate microcode for many different target processors. Retargeting is performed by providing information about the new target machine. Generalized code generation techniques are applied which can lead to suboptimal code. Although the code is suboptimal, the gain in development time is substantial. Thus retargetable code generators provide the more generalized framework for ASIC processor design.

## 2.2 Instruction Sets and Code Generation.

The information necessary for code generation consists of the processor instruction set and the collection of binary control words defined by a hardware implementation of the instruction set. These 2 sets of information can be summarized in a behavioral description. Mueller has pointed out 2 approaches for expressing instruction sets [6]. One method is based on grammar descriptions while the other is based on data flow graphs.

In the grammar method, a set of micro-operations is defined. These microoperations are combined into lists to form instructions. The legal combinations of microoperations are defined by a grammar, much like the way that English grammar provides rules for combining words into sentences. Micro-operations are usually defined as mnemonic strings. During code generation, control words are assembled by translating the mnemonic strings to their binary equivalent.

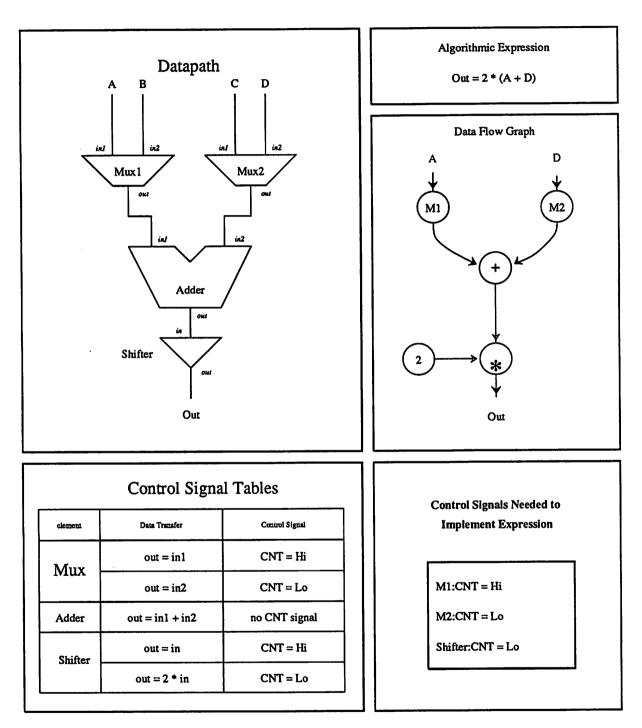

In the data flow method, instructions are expressed in terms of data flow graphs. Each node in the graph represents a micro-operation, while each edge represents data flowing from one node to the next. A collection of nodes and edges forms an equivalent data flow Algorithmic Expression Out = 2 \* (A + D) (A = D) (M1) (M2) (M2)

Figure 2.2: Using data flow graphs to describe an add instruction.

graph representing an instruction. Fig. 2.2 illustrates an example of assembling some nodes and edges to create an instruction representation. Since the instruction is represented in graphical form, an algorithm is needed to translate graphs to binary control words.

The data flow method provides a more generalized framework from which to build a retargetable code generator. With a data flow approach, an annotated graph of data flow in an architecture can be used to cleanly and uniquely describe instructions. The data flow approach has the advantage that more information can be stored in a graph then in a list of micro-operations. The arrangement of micro-operation nodes in the graph can reflect actual features in an architecture.

## 2.3 Silicon Compilation and Code Generation.

Retargetable code generators can be used in silicon compilers. For a given silicon compiler, various approaches give different results. No single approach seems to suit all the needs of the different code generation environments.

There are 2 types of silicon compilers. One type (structural compiler) uses struc-

Data Flow Graph

tural descriptions to generate a layout. The Lager System is an example of this type [13]. The second type (behavioral compiler) uses behavioral descriptions to synthesize the necessary hardware descriptions from information found in leafcell libraries [7] [8] [9] [10]. There is some control over the decisions made at each level of synthesis, but not as much as with the structural compiler, which allows full specification of the design at all steps.

The behavioral silicon compiler usually includes powerful synthesis tools that can essentially define the instruction set and account for other processor characteristics. Thus the required code generator is a translator that matches mnemonics and substitutes binary machine language code. The simplicity of this type of code generator is gained at the cost of developing complex synthesis tools which define the instruction set for the processor.

Two types of code generators can be developed for structural compilers. The first type requires the human designer to provide a description of the instruction set. The code generator uses this description to map the algorithm description onto the architecture. The second type of code generator uses the structural description and supplementary behavior descriptions to deduce the instruction set and generate the microcode. In the first case, a human must provide extra information in the form of an instruction set to retarget the generator, but in the second case, the generator deduces the instruction set.

## 2.4 Microcode Generation and The Lager System.

## 2.4.1 Past Microcode Generation Work in the Lager System.

The Lager I system was targeted to a single processor architecture [11] [12] for which a dedicated assembler and assembly language simulator were developed. A predefined and limited instruction set limited the scope of the problem so that an effective solution was obtained.

The Lager III system [13] provided a structural description language that could be used to describe general hardware configurations. A datapath compiler provided the potential for a user to explore and rapidly prototype new datapath designs [14].

The Lager III system supported the Kappa architecture [2]. The assembler for this architecture, rassCG, translated a grammar description of an instruction into the corresponding machine language. A compiler was also developed that could take a high level program description in a C like language and compile it into the input for rassCG [15]. Simulation of processor designs was performed using a simulator called DSIM, which was based on LISP submodules and was slow.

Lager IV is an enhanced version of Lager III. It is implemented in the C programming language and uses the OCT database to store information. Lager IV uses a modified version of the Lager III microcode generator.

#### 2.4.2 Background on Lager IV and the OCT database.

Before discussing the approach, it is necessary to review some of the basic concepts of the Lager IV system. The review presented here is limited. More information can be found in the Lager IV User's Manual and the OCT Tools Distribution Manual.

#### Lager IV.

Lager IV is a system used to perform the layout for ASIC designs. The user writes a structural description language (sdl) file describing the hardware configuration of the design. The sdl files can be written hierarchically. Directives in the sdl files dictate which layout generation tools will be used at each level of the hierarchy. The layout generation tools include a module generator, a place and route tool, and a datapath compiler. Designs can be parameterized to increase flexibility.

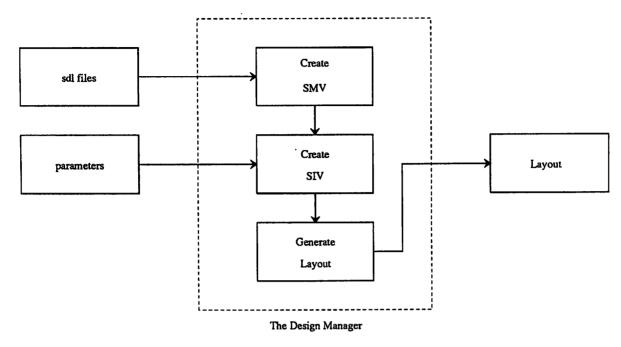

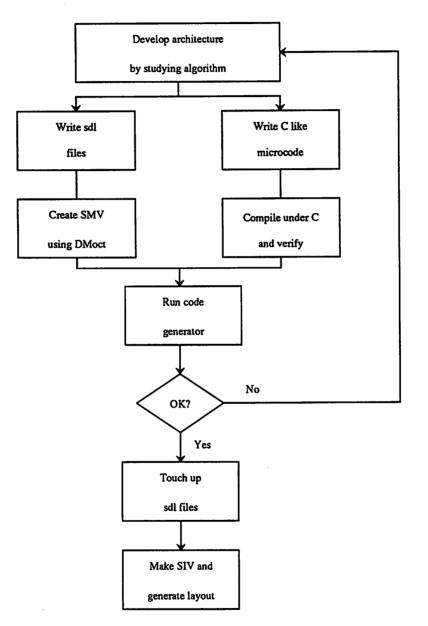

Fig. 2.3 shows the layout process which is directed by the Design Manager, the user interface for Lager IV. During the layout generation process, the Design Manager creates the structure master view (smv), the structure instance view (siv), and the physical view which are stored in the OCT database.

#### The OCT Database.