Copyright © 1989, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## MARINER: A SEA OF GATES LAYOUT SYSTEM

by

Wayne A. Christopher

Memorandum No. UCB/ERL M89/83

28 June 1989

## MARINER: A SEA OF GATES LAYOUT SYSTEM

by

Wayne A. Christopher

Memorandum No. UCB/ERL M89/83

28 June 1989

l'ille Proc

## ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## MARINER: A SEA OF GATES LAYOUT SYSTEM

by

Wayne A. Christopher

Memorandum No. UCB/ERL M89/83

28 June 1989

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Abstract

We have written a Sea of Gates layout system which uses an innovative sequence of global and detailed placement and routing steps. The first phase consists of global placement and routing. Global placement partitions the chip area into a grid of "leaf blocks" and assigns the cells to these blocks. This partitioning is accomplished by a modified Kernighan-Lin mincut algorithm known as quadrasection. Global routing by hierarchical refinement is done concurrently with this process. After the partitioning is completed, the global routing is removed and redone using a flat maze-routing algorithm, which yields better results than the hierarchical refinement algorithm. The leaf blocks are then placed and routed individually, using a simulated annealing algorithm that takes into account both netlength and routability, followed by detailed maze routing (currently done by Mighty). Mariner has been tested on and has yielded good results for small- to medium-sized examples, and our experiments suggest that substantially better results for larger chips could be achieved, given more sophisticated global routing algorithms.

### Acknowledgements

I would like to thank Lorraine Layer for her help with the Mariner project. She provided a lot of good advice. supplied common sense when I needed it. and most important. was a great friend.

Also. I would like to thank the other Sea of Gates researchers at Berkeley for their assistance. Brian Lee developed the **Hero** router. and provided me with a lot of valuable advice and feedback. Mitch Igusa and Mark Beardslee developed the **Orca** system. which I used to route the output of early versions of **Mariner**. Ren-Song Tsay wrote the **Proud** placement program and provided some of the examples used for this report. I would also like to thank Professor Newton for his support and encouragement. and professor Séquin for valuable advice.

Honorable mention goes to Randy "Xtrek" Cieslak. Abhijit "Tex" Ghosh. Steve "Kitten Heads" Procter. and Leah "Fang" Slyder. all of whom put up with me and are pretty cool people in general.

The members of the CAD group at Berkeley have made the last few years a lot of fun and very educational for me, in particular Professors Brayton, Sangiovanni-Vincentelli, and Pederson. Pranav Ashar. Jeff Burns. Srinivas Devadas, David Harrison. Beorn Johnson. Theo Kelessoglou. Chuck Kring. Tom Laidig. Tony Ma, Sharad Malik. Karti Mayaram, Peter Moore, Brian O'Krafka. Tom Quarles. Rick Rudell. Ellen Sentovich. Kanwar Singh. Rick Spickelmier, and Gregg Whitcomb.

Finally. I would like to thank my wife Susan. my aunt Alice. and Tom. Matt. and Pat for everything they've done for me.

# Contents

•

| Ac | knov  | vledgements                                       | 11        |

|----|-------|---------------------------------------------------|-----------|

| Ta | ble o | of Contents                                       | iii       |

| Li | st of | Figures                                           | v         |

| Li | st of | Tables                                            | vi        |

| 1  | INT   | RODUCTION                                         | 1         |

| -  | 1.1   | The Sea of Gates Layout Problem                   | 1         |

|    | 1.2   | Existing Sea of Gates Layout Systems              | 5         |

|    | 1.3   | The Mariner Philosophy                            | 7         |

|    | 1.4   | Overview of Mariner                               | 8         |

| 2  | РАТ   | RTITIONING                                        | 13        |

| -  | 2.1   | Partitioning                                      | 13        |

|    |       | 2.1.1 The Problem                                 | 14        |

|    | 2.2   | Quadrasection                                     | 18        |

|    |       | 2.2.1 Random Partitioning                         | 18        |

|    |       | 2.2.2 Clustering                                  | 19        |

|    | •     | 2.2.3 Kernighan-Lin-Fiduccia-Matheyses            | 19        |

|    |       | 2.2.4 Suaris-Kedem Quadrasection                  | 20        |

|    |       | 2.2.5 Simulated Annealing                         | 21        |

|    |       | 2.2.6 Adaptive Simulated Annealing                | 22        |

|    |       | 2.2.7 Adaptive Simulated Annealing with Net Moves | 22        |

|    |       | 2.2.8 Results                                     | 22        |

|    |       | 2.2.9 Control Strategy                            | <b>24</b> |

|    | 2.3   | Minimum Density Partitioning                      | 25        |

|    | 2.4   | When to Stop Partitioning                         | 28        |

| 3  | GI    | OBAL ROUTING                                      | 31        |

| J  | 3.1   | The First Global Routing Phase                    | 31        |

|    | 3.2   | Routing Area Prediction                           | 34        |

|    | 3.3   | The Second Global Routing Phase                   | 37        |

iv

|   |                                               | 3.3.1<br>3.3.2<br>3.3.3                                         | The Problem                                                                                                                       | 37<br>38<br>42                                     |

|---|-----------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 4 | DE<br>4.1<br>4.2<br>4.3<br>4.4                | Orderi<br>Adapt<br>The C                                        | ED PLACEMENT         sing the Detailed Placement Problems         tive Simulated Annealing         Cost Function         Move Set | <b>47</b><br>47<br>48<br>50<br>54                  |

| 5 | DE2<br>5.1<br>5.2<br>5.3                      | Routin<br>If Mig                                                | ED ROUTING<br>ing with Mighty                                                                                                     | 59<br>59<br>60<br>62                               |

| 6 | STA<br>6.1<br>6.2                             | Curren                                                          | , CONCLUSIONS, AND FUTURE WORK<br>ent Status                                                                                      | <b>65</b><br>65<br>67                              |

| A | A.1<br>A.2<br>A.3<br>A.4<br>A.5<br>A.6<br>A.7 | admir<br>checky<br>mflatt<br>mpady<br>pgrou<br>regen(<br>skippe | L PAGES FOR THE MARINER PROGRAMS<br>ral(1)                                                                                        | 71<br>72<br>74<br>75<br>76<br>78<br>79<br>80<br>81 |

|   | • 1. 1•                                       | raphy                                                           |                                                                                                                                   | 84                                                 |

.

.

·

# List of Figures

| 1.1        | The Gate Array Design Style                                |

|------------|------------------------------------------------------------|

| 1.2        | The Standard Cell Design Style                             |

| 1.3        | The Sea of Gates Design Style                              |

| 1.4        | The Mariner System                                         |

| 1.5        | Lorraine's Transistor Template                             |

| 1.6        | Lorraine's NAND3 12                                        |

| 2.1        | Partitions                                                 |

| 2.2        | Quadrasection                                              |

| 2.3        | Minimum Cut Vs. Minimum Density Partitions                 |

| 2.4        | The Function adjust                                        |

| 2.5        | A Block That is Too Small for its Cells                    |

| 3.1        | The $2 \times 2$ Routing Problem                           |

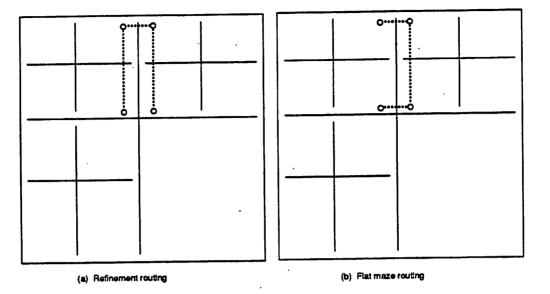

| 3.2        | Hierarchical vs Flat Routing 37                            |

| 3.3        | Two Representations of the Global Routing Problem          |

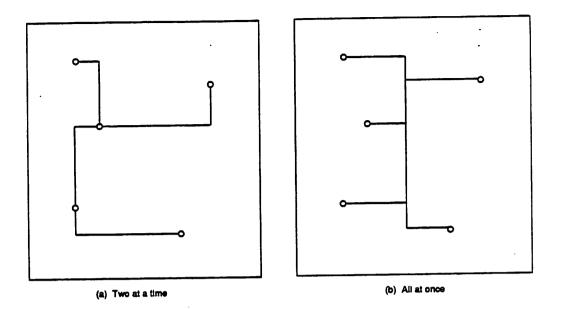

| 3.4        | Different Ways To Route A Multi-Pin Net                    |

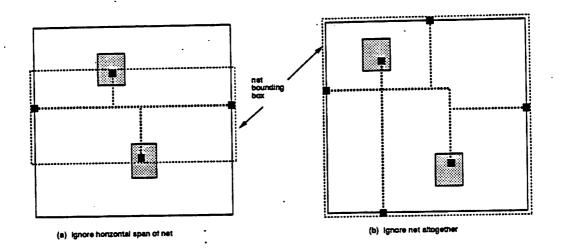

| 4.1        | Ignoring the X- or Y-spans of a Net                        |

| 4.2        | "Island" Patterns in Layout 53                             |

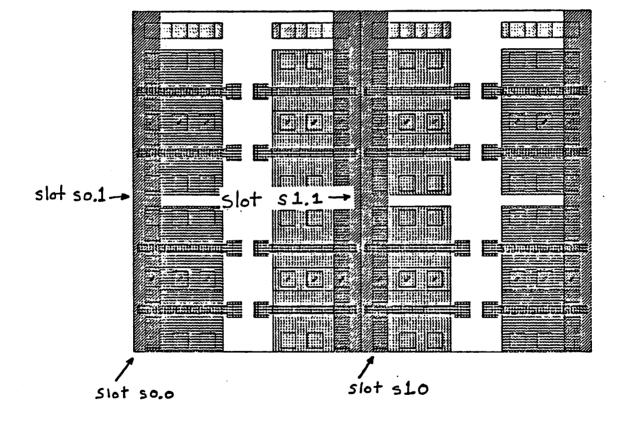

| 4.3        | Slots Possible for a nand2 Library Cell 55                 |

| <b>4.4</b> | A Cell "Spilling Over" Because of the Wrong Slot Choice 56 |

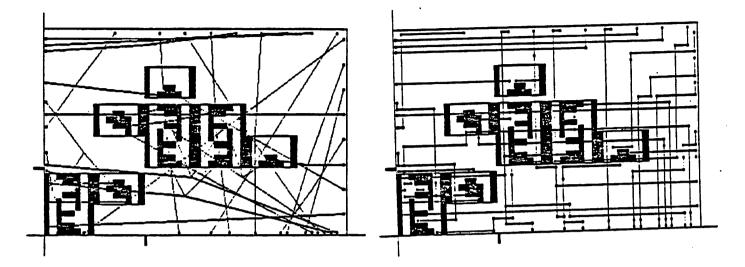

| 5.1        | Unrouted and Routed Blocks 60                              |

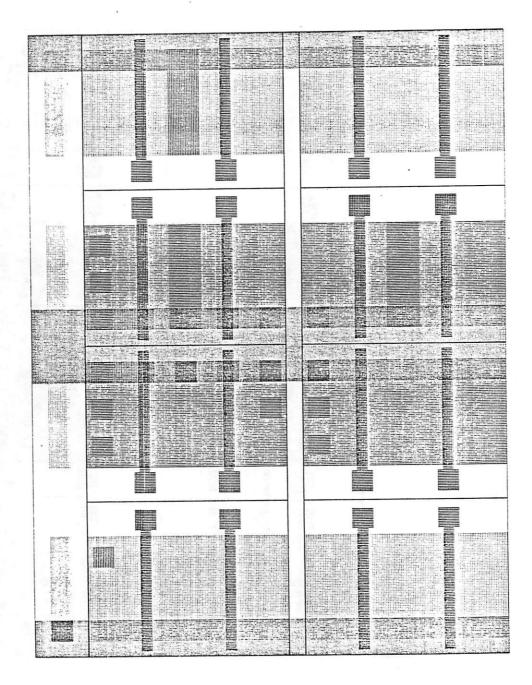

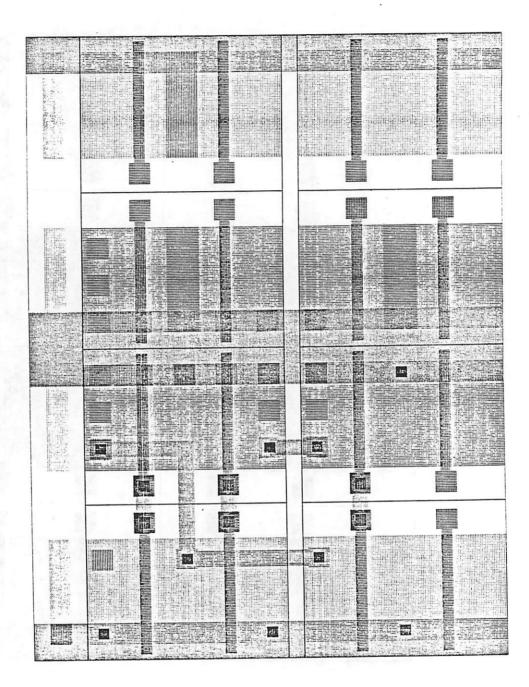

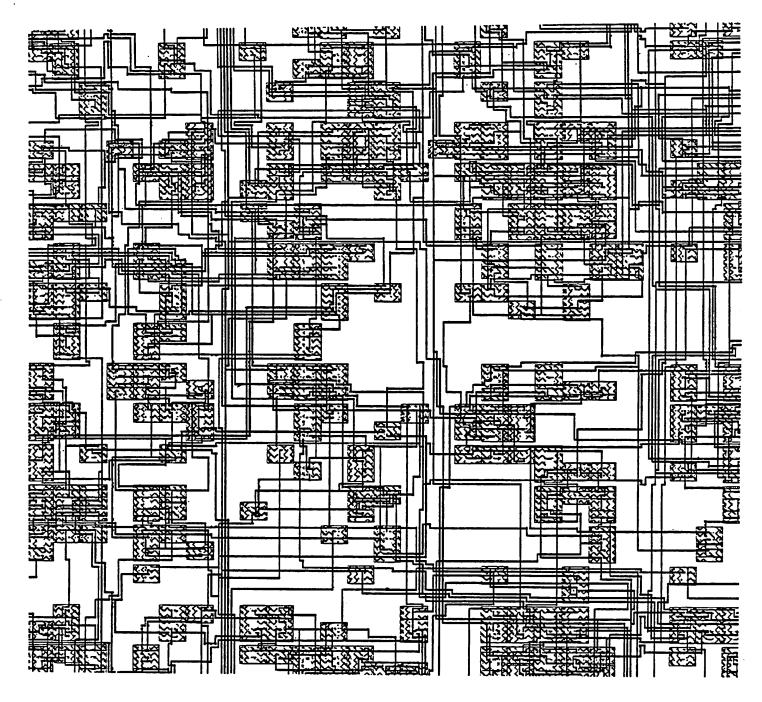

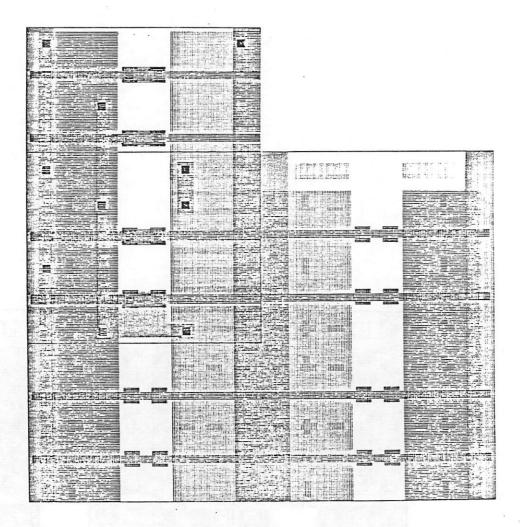

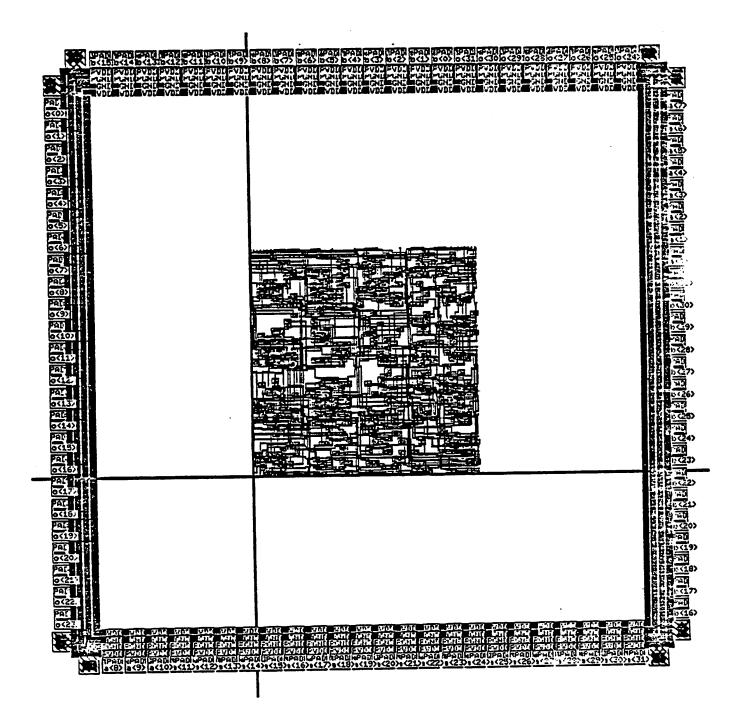

| 6.1        | The Adder32 Chip                                           |

| 6.2        | The DES Chip                                               |

| 6.3        | The Hughes Chip                                            |

# List of Tables

.

| 2.1 | Comparison of Difficulty Functions                       |

|-----|----------------------------------------------------------|

| 2.2 | Simulated Annealing Partitioning Parameters              |

| 2.3 | Partitioning Algorithm Results: Costs of Final Solutions |

| 2.4 | Partitioning Algorithm Times, in Seconds                 |

| 2.5 | Ripup and Re-partition Results                           |

| 2.6 | Results of Minimum Density Partitioning                  |

| 3.1 | Comparison of Initial Global Routing Cost Functions      |

| 3.2 | Empirically Determined Multiple Pin Equivalent Nets      |

| 3.3 | Cost Weights for Entering Nodes                          |

| 3.4 | Density Ratio Coefficients                               |

| 3.5 | Global Routing Ordering Strategies                       |

| 3.6 | Constant Values for Enter Cost and Arc Weight            |

| 4.1 | Ordering Strategies for Detailed Placement               |

| 4.2 | Pin Assignment Algorithm Results                         |

| 4.3 | Results for Different Weight Sets 58                     |

| 5.1 | Number of Detailed Layouts Completed at Each Iteration 6 |

| 5.2 | Costs for Blocks More or Less Constrained                |

| 6.1 | Final Results                                            |

| 6.2 | Runtime                                                  |

| 6.3 | Percent Utilization vs Percent Completion                |

# Chapter 1

# INTRODUCTION

In recent years, CAD software has been developed for automating the layout of many VLSI design styles. At Berkeley, a number of systems are being developed or are being used for the automated layout of macro-cell [12.4] and standard-cell [59.60] chips. Several systems are currently being developed for the automated layout of Sea of Gates chips, one of which is the Mariner system, the subject of this report.

The Sea of Gates design style is similar to gate array, except that there are no predefined routing regions. This makes it possible to achieve much higher transistor utilization percentages, especially when more than two customizable layers of high-quality interconnect (e. g. metal, polysilicide) are available.

With this added flexibility comes the requirement for more sophisticated layout algorithms. A number of different approaches have been tried. including a standard cell-like row-based approach, used by the **Proud** system [68], and a macro cell-like approach, used by the **Orca** system [5]. The **Mariner** system uses an innovative combination of top-down partitioning and low-level simulated annealing algorithm for placement, and performs both global and detailed routing concurrently with the placement.

## 1.1 The Sea of Gates Layout Problem

The Sea of Gates design style may be compared to other ASIC design styles. in particular gate array, standard cell. and macro cell. All these styles use standard *library cells* (called *macros*, for gate array and Sea of Gates), which have been optimized for speed and size. They rely heavily on automated layout systems, with minimal user intervention. 4

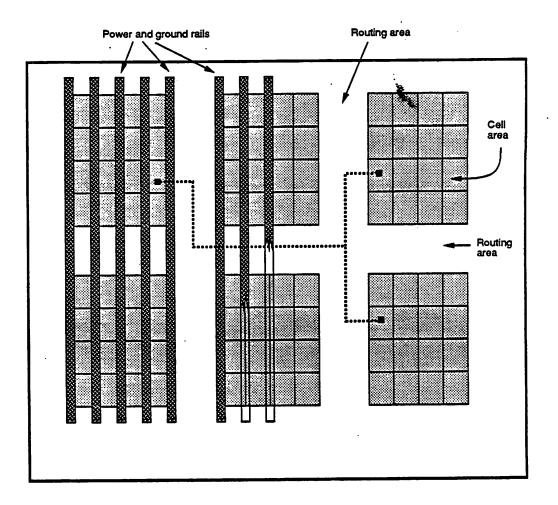

Figure 1.1: The Gate Array Design Style

Finally, they are often used for applications where fast turnaround time is essential, which means that efficient layout algorithms must be used.

The gate array design style, also referred to as master-slice, or uncommitted logic array (see Figure 1.1), is by far the most common programmable array designed by computer. In this approach, a two-dimensional array of replicated transistors is fabricated to a point just prior to the interconnection levels. A particular circuit function is then implemented by customizing the connections within each local group of transistors to define its characteristics as a basic cell, and by customizing the interconnections between cells in the array to define the overall circuit. Generally a two-level interconnection scheme is used for signals and, in some approaches, a third, more coarsely defined layer of interconnections is provided for power and ground connections. The interconnections are implemented on a rectilinear grid in the "channels" between the cells. In many cases, channels are also pro-

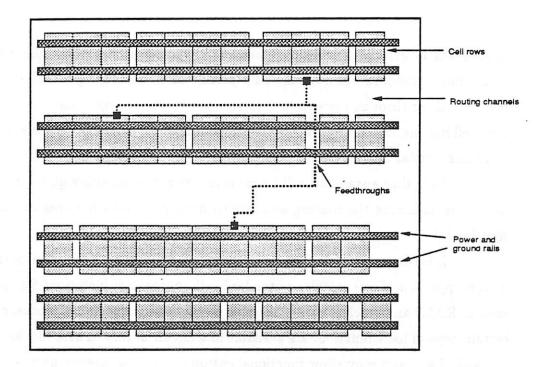

Figure 1.2: The Standard Cell Design Style

vided which run over the cells themselves. and in some arrays, wider channels are provided in the center of the array to alleviate the congestion often found in that area. Gate-arrays are used in many technologies, in particular bipolar and CMOS. and arrays containing many thousands of gates have been fabricated [28.14].

This design style is similar to Sea of Gates. except that gate array defines routing areas. and no cells may be placed in these areas. These additional constraints make it both harder and easier for the layout tools — there is more freedom with Sea of Gates to obtain a better solution, but the placement program must make more decisions. Unlike standard cell, and like Sea of Gates, in a gate array design it is possible to generate a cell placement which cannot be routed. It is also very difficult to modify a gate array placement in any global manner once it has been generated — any change is generally equivalent to a complete re-placement.

The "standard cell" (or polycell) approach (see Figure 1.2) refers to a design method where a library of custom-designed cells is used to implement a logic function. These cells are generally of the complexity of simple logic gates or flip-flops and may be restricted to constant height and/or width to aid packing and ease of power distribution. Unlike the programmable array approach. standard cell layout involves the customization of all mask layers. This additional freedom permits variable width channels to be used. While most standard cell systems only permit inter-cell wiring in the channels between rows of cells or through rows via pre-determined "feed-through" cells. some systems permit over-cell routing. Standard cell systems are also used extensively in a variety of technologies including bipolar and CMOS [51.70].

Note that a standard cell layout is always routable. although the goal of the layout tools is to minimize the routing area. which minimizes both the area of the chip and the signal delay.

It is often relatively inefficient to implement all classes of logic functions in a single design approach. For example, a standard cell approach is inefficient for memory circuits such as RAMs and stacks. In the "macro-cell" method, large circuit blocks, customized to a certain type of logic function, are available in a circuit library. These blocks are of irregular size and shape and may allow functional customization via interconnect, such as a PLA or ROM macro [33], or they can be parameterized with respect to topology as well [32.8.23]. With the parameterized cell, the number of inputs and outputs may be parameters of the cell. In some systems macro cells may also be embedded in gate-array or standard-cell designs.

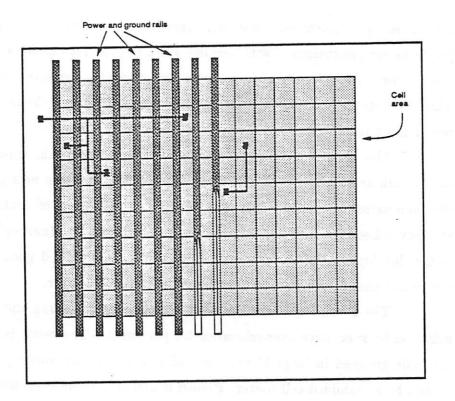

The Sea of Gates design style (see Figure 1.3) also makes use of pre-defined polysilicon layers and customizable metal layers. but there are no "bare-silicon" routing areas where cells may not be placed. Rather, the whole chip is covered with pre-fabricated transistors. and it is up to the layout tools to decide where to route nets and where to place cells. In most cases, it is also possible to route nets over the tops of the cells. For example, few cells in the Mariner library make extensive internal use of the second layer of metal, and there is at least one vertical track free per transistor where a wire on the first layer of metal may be routed.

The major reason that Sea of Gates is difficult to lay out is that once the cells are put in place, there is no realistic possibility of changing their position — whereas with another design style, the major blocks could be moved slightly apart, with Sea of Gates the minimum amount they can be moved is quite large. This is not a major concern at the detailed level, since it is generally possible to look ahead to the routing stage when doing low-level placement, but at the global level it is a serious problem. If there is a particular area where the congestion is too great, it is not possible to add any tracks without adding a large number of them, across the entire chip. Therefore the rough placement algorithm

Figure 1.3: The Sea of Gates Design Style

must be very intelligent and look ahead to both the global routing stage and the detailed placement and routing stages.

Cells in a Sea of Gates library cells typically have many feed-throughs and free routing tracks available. Thus much of the routing is over- and through-the-cell, and the detailed router must be able to handle routing problems with arbitrary blockages and pins both on the boundaries of the problem and in arbitrary places within the interior.

Because the transistor structure of a macro is fixed, there is a set of pre-defined positions and transformations on the chip that may be used for a given cell. The placement program must be aware of these constraints in order to generate legal placements. This is not so much a problem for the placement algorithm as an extra level of infrastructure that must be provided for the layout system.

## 1.2 Existing Sea of Gates Layout Systems

The Orca system [5] uses an approach similar to that used by macro cell systems. During the placement, cells are grouped in *clusters* in a hierarchical manner. These clusters

are placed by a mincut quadrasection algorithm similar to the one used by Mariner. The positions are approximate, with variable-sized routing regions between blocks. The router can ask for more space if necessary, by means of *spacing requests* to the placement program, which adjusts the locations of the macro blocks and returns the layout to the router. The router must request space in multiples of the template size.

The Orca router uses a maze-refinement approach, where the nets are routed on a rough grid, which is then successively refined, with the nets generally routed within the boundaries of the grid cells used by the previous level of routing. The basic routing strategy is Lee maze routing. This router was also used by Mariner during the early stages of the development of the placement algorithms, and yielded good results. Admiral did not utilize the spacing request feature of the router, however.

The **Proud** system [68] uses hierarchical partitioning and resistive network optimization by successive over-relaxation for placement. The result is an unrouted chip with the cells grouped in large blocks, each of which contains rows of cells. The chip is then routed by a standard cell router. **Proud** is designed to be used with three layers of metal [45], and has yielded good results for large industrial designs.

The program SoGOLaR [1] (Sea of Gates Optimized Layout and Routing) generates functional cells for static CMOS circuits in the Sea of Gates layout style. The input may be specified either as a list of boolean expressions where each expression specifies a multi-level AOI tree or as a schematic level netlist. For best results it places individual P/N-transistor pairs with simulated annealing using a suitable cost function to minimize netlength and to maximize diffusion sharing. Internal cell routing is performed by CODAR [69]. a congestion-directed router that combines global and detailed routing algorithms.

A system developed by C. P. Hsu et al. [30] uses techniques similar to those used by Mariner and Orca. It first flattens the netlist. then separates it into a number of smaller netlists by means of a clustering algorithm. These clusters are then assigned to regions of the chip, and are placed by means of a standard cell simulated annealing placement program. such as TimberWolf [59,60]. One advantage of such a system is that it can easily handle mixed-technology chips. In this case the clustering is based on the functionality of the component, rather than on connectivity alone. Unlike Mariner. however, this technique is not fully hierarchical. as it only does one level of clustering. This system has produced good results for large examples (51K cells with 69 % transistor utilization). These results were obtained using Hughes' triple-layer metal process [45], while our examples were produced

for the two-layer MOSIS CMOS process [67].

## 1.3 The Mariner Philosophy

Most prior layout systems have dealt with the place and route problem by first placing the cells. and then routing them. There may be some lookahead during the placement phase to the routing phase. but feedback from routing to placement is usually limited to very coarse changes. such as the expansion of routing channels. This is because placement is usually done in a top-down manner, and high-level decisions cannot easily be modified without invalidating all of the decisions made further down.

Usually both placement and routing in a top-down system are each divided into two phases: global and detailed. During the global phases. more attention is given to largescale optimization and less is given to low-level considerations such as exact locations and capacities. During the detailed phases, the problems have become much smaller. and it is possible to find exact solutions.

One of the goals of the Mariner project was to combine placement and routing into a single process, with much tighter coupling than is usually present in layout systems.

Instead of doing both of the placement phases before the routing phases, both of the global phases are completed before the detailed phases. In the global placement phase, the chip area and the netlist are decomposed into a grid of small placement problems, and during the global routing phase the nets are routed throughout this grid. In the detailed phases, we use simulated annealing to assign positions to the cells, taking into consideration our knowledge of the nets passing through the block, and then route the placed block with a maze router. Note that by doing global routing before detailed placement, we make less information available to the global router, thus making its solution less exact, but we make more routing information to the detailed placer.

In addition to interleaving the placement and routing phases in this manner. both placement phases look ahead to the next routing phase. The global placement algorithm routes nets by means of hierarchical refinement during partitioning, and the detailed placement phase performs pin assignment concurrently with cell placement.

## 1.4 Overview of Mariner

8

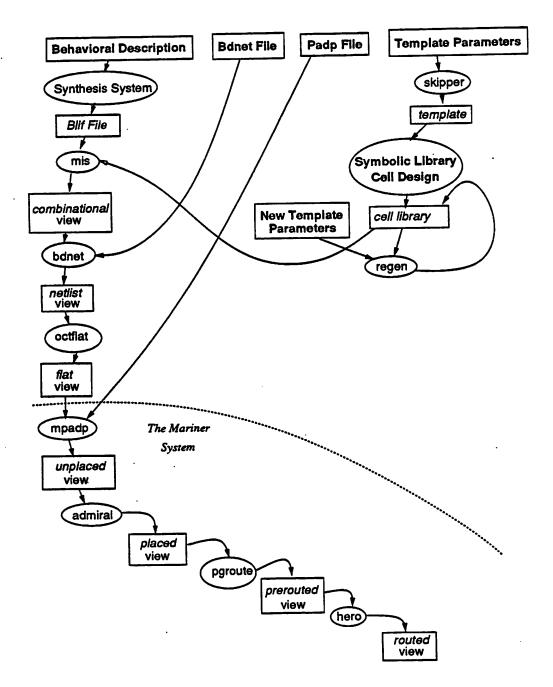

The Mariner system consists of the placement and global routing program. Admiral. the cell library. a number of small programs to maintain and update the library cells [41], and programs to accomplish pad placement and power and ground routing. The detailed router is called by Admiral, but it is not considered part of Mariner. Currently Mighty [62.61] is used for detailed routing. These programs are described briefly below in the order they would be run to generate a completed layout from a netlist view. All these programs read their input from and write their output to *oct* views [24], with the exception of the human-readable pad placement file.

The program Mpadp reads an oct view called *flat*. This view contains cells and pads from the library, none of which is placed, and nets. It also may read a *pad placement file*, in which the relative locations of the pads in the netlist and power and ground pads are specified. along with definitions of power and ground rings and the dimensions of the desired core cell area. If this file is not present. Mpadp orders the pads around the chip in the order they were read from the database. connects default power and ground rings. and calculates the area required to achieve a particular transistor utilization percentage, which may be specified on the command line. Mpadp outputs an oct view entitled *unplaced*. This view differs from the input view in that the pads now have locations. power and ground pads and rings have been added in the *contents* facet. and a box denoting the available area for cells and routing has been added to the PLACE layer in the *interface* facet of the array.

The Admiral program reads the *unplaced* view of the base array and generates either a *placed* view or a *routed* view. depending on whether the user requested routing or not. If routing was not requested, all the cells will have been given legal positions. If routing was requested, in addition, all the signal nets will have been given implementations as well (wires in the METAL-1 and METAL-2 layers connecting all the pins). If Admiral could not route some blocks (see Chapter 5), the nets in that block will have been implemented as "spiders" in the PLACE layer. If it could not globally route some nets (see Chapter 3), they will not have any geometry attached to them, and will be attached to a bag called UNROUTED\_NETS. Power and ground nets are ignored by Admiral.

The power and ground routing program, **Pgroute**, takes a *routed* or *placed* view and adds power and ground busses, connecting them to the power and ground rings around the outside of the chip. It produces a view called *final*. This view is the final output of

Figure 1.4: The Mariner System

the Mariner system. although it can be given as input to another detailed routing program. if routing was not provided by Admiral.

A transistor structure (or *template*) and a cell library for Sea of Gates have also been developed and described in detail in [41]. The cell library, based on the Mississippi State University Standard Cell Library [49], contains approximately 30 cells. and is used by the Berkeley logic synthesis tools [7] to generate netlists. The template we developed is shown in Figure 1.5. A 3-input NAND gate from the library is shown in Figure 1.6. There are two programs for maintaining the template and the cell library. These are Skipper, which generates a template from chip performance and size specifications and physical design rules, and **Regen**, which modifies the library to fit on a different template than the one it was designed on. Detailed descriptions of these programs may be found in [41].

Figure 1.5: Lorraine's Transistor Template

Figure 1.6: Lorraine's NAND3

# Chapter 2

# PARTITIONING

In order to effectively lay out increasingly large chips, placement algorithms must make use of hierarchy. Some layout systems make use of the hierarchy already present in the design [12.4]. Admiral does not use this approach for a number of reasons. First, there may be no such hierarchy. Many of our examples were generated by logic synthesis tools. which are now capable of producing netlists with many thousands of logic gates. Second, the partitioning imposed on the problem by the designer may not be the best partitioning from a layout perspective. It has been suggested [16] that a strict partitioning of a system into datapath and control sections can often lead to a sub-optimal final design, especially in gate array layout styles. Also, although the optimal shape in isolation for a circuit such as an ALU is a regular structure, there is no guarantee that this layout remains optimal in the context of the rest of the chip, especially if parts of the design have been passed through a logic optimizer. For these reasons, we have taken the approach of starting with a flattened netlist and hierarchically partitioning it according to connectivity considerations.

## 2.1 Partitioning

There are a number of different strategies available for partitioning networks. Among these are *clustering* [13], which is used to identify strongly-connected groups of nodes, and *dissection*. These algorithms are not suitable to partitioning a netlist for placement purposes, since we usually want to split the netlist into a small number of pieces of approximately equal size, and clustering and dissection gives us little control over the number or size of the partitions. A hybrid approach, using some clustering followed by partitioning. has been successful for placement [55]. and might also prove useful for Sea of Gates layout [11].

Our basic algorithm is a variant of min-cut partitioning known as *quadrasection* which was first used by Suaris and Kedem for standard-cell layout [65]. Quadrasection is used to split the netlist and the chip area into four pieces, and is then applied recursively to the sub-netlists until a set of "small" problems is obtained. What is meant by "small" is discussed in Section 2.4.

We investigated a number of algorithms for partitioning a netlist. subject to cell capacity constraints and external pin positions. The algorithms are described below, and the results are summarized in Table 2.3. Also, we tried an alternate formulation of the problem, where the quantity being minimized was wiring congestion, rather than total edge crossings. The results of this experiment are also described in Section 2.3.

## 2.1.1 The Problem

The N-way mincut partitioning problem can be described as follows. The inputs are a list of nets, a list of cells, and a list of partitions. A cell may reside in exactly one partition, and is considered a point to which the nets are attached. The information that may be specified about these items is as follows:

• nets

- 1. list of cells connected to the net

- 2. the *criticality* of the net. an externally specified value between 0 and 1000. which is used as a weighting factor in various places

- cells

- 1. cell area. in square wiring grid units

- 2. initial partition cell resides in

- 3. is cell fixed in that partition?

- partitions

- 1. total area available for cells

- 2. distance to all other partitions, using some metric

The problem is to place the cells in partitions, subject to the maximum cell area capacities of the partitions, in such a way as to minimize the total cost of the nets. The

Figure 2.1: Partitions

cost of a net may be measured in a number of ways: if there are only two partitions, then if the net contains cells in both partitions, it costs one unit, otherwise it costs nothing. The cost may be scaled by the net's criticality. If there are more than two partitions, the cost becomes more complex to determine, since the net really should be routed to see which partition boundaries it falls upon. Since doing an actual global route each time a cell is moved would be prohibitively slow, this process is simulated by using the minimum spanning tree of the partitions occupied. This is calculated using Kruskal's algorithm [2], and the results are cached for efficiency.

#### The Placement Problem

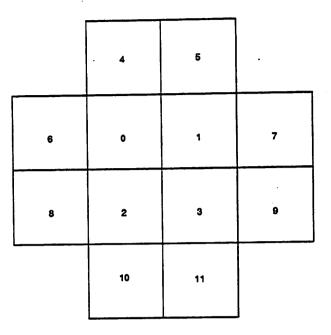

We must map the placement problem at a particular level to this abstraction of the partitioning problem. In order to do this some extra partitions must be constructed. The placement algorithm produces a problem consisting of four "real" partitions and eight "fake" partitions, which are introduced to contain external pins. The arrangement of these partitions are shown in Figure 2.1. Partitions 0 through 3 are empty, and represent the actual cell area available. Partitions 4 through 11 each contain one dummy cell, which is fixed in place. All nets that have external pins that reside on a particular side contain the dummy cell in the corresponding partition. If a pin is free to float along the top, for instance. the net connects the cells in partitions 4 and 5. and if it is constrained to the right side of the top edge (because the adjacent block has already been partitioned, or the pin corresponds to a pad which has a fixed position), it contains the cell in partition 5. Note that if information about the partitioning of a block is to be used to influence the partitions of neighboring blocks, the net containing that pin must be routed in the  $2 \times 2$  problem produced by the partition. For this reason, after each block is partitioned, the nets contained in it are globally routed by means of a hierarchical refinement algorithm. described in Section 3.1.

We can justify our use of Kruskal's algorithm to calculate the minimum spanning tree of the complete graph. instead of the minimum Steiner tree of the graph induced by the adjacencies of the partitions. by the way the placement code calculates the distances between partitions. The distance between a "fake" partition and a "real" partition that are adjacent is defined to be 1. The ratio of the distances between pairs of real partitions that have horizontal boundaries to those between pairs that have vertical boundaries is calculated to be roughly the same as the ratio between the vertical and the horizontal net and cell blockage factors. because we want to capture the relative difficulty of routing horizontal and vertical nets in the distance values. For all other pairs of partitions, the distance is defined to be the total distance along the minimum path between the partitions. using edges that already have distances defined. By doing this the cost of the minimum Steiner tree connecting the partitions is "pre-calculated".

Note that this formulation ignores the problem of congestion. It assumes that the minimum cost path for a net will always be available, while in practice not all nets that wish to take this path may be allowed to. The *minimum density* partitioning algorithm (see Section 2.3) was an attempt to address this facet of the problem more directly.

#### Unused Area

Another important issue is that of free area, which will be utilized for routing. If the partitioning algorithm is given the actual value of the amount of room available in each of the partitions, there will be no control over where the unused area appears. The goal of mincut partitioning is to minimize the number of edge crossings, and this may be done at the expense of distributing unused area very unevenly. For this reason, the partitioning algorithm must be given partitions whose total size is not very much larger than the total area of the cells to be placed. If a total amount of extra room equal to the number of real partitions times the maximum cell size is left in the partitions. we can be sure that all the partitioning algorithms described below will always be able to find a possible move. The problem then becomes where to add the remaining area. or *slack*.

Slack should be added to partitions based on the perceived difficulty of routing the sub-problem that will be produced. The amount of slack that each partition gets should be proportional to its *difficulty value*. Estimating this value is more difficult than estimating routing area (Section 3.2). since we don't even know what cells or nets are present in this partition. There are a few ways this value can be estimated. however. The first is based on the distance from the center of the block to the center of the chip. Since more nets tend to be routed through the center of the chip than the edges. a partition closer to the center will have a higher difficulty value and will need more routing area. This scheme has the advantage of being simple. On the other hand, the number of nets going through a partition can easily be measured more directly. All that is known at this point is the number of pins on each edge, and in some cases to which half of the edge the pin is restricted (if a neighboring block has already been partitioned). Define the *difficulty* of a partition p to be the sum for all the pins t on all the edges  $\epsilon$  of that partition of f(t), where

$f(pin) = \begin{cases} 0.5 & \text{if } t \text{ is floating} \\ 1 & \text{if } t \text{ is fixed to the half of } \epsilon \text{ adjacent to } p \\ 0 & \text{if } t \text{ is fixed to the half of } \epsilon \text{ not adjacent to } p \end{cases}$

That is, if it is known that a net must pass through this partition. it is given full weight. and if it is known that it might do so. it is given half weight. Thus the partitions that are likely to have a lot of external pins will get more slack.

This heuristic can be improved a bit more, however. A net entering a partition may or may not leave it. If a net enters a partition only to connect to a pin on a cell in that partition, it will take less routing area than a net that must exit on the other side. For this reason, a bit more can be added to f(t) if it is known that the net the pin is on has other external pins. A value of 0.25 has proved to work well.

In Table 2.1, these three methods of calculating difficulty are compared. The numbers given are the maximum and average net densities after the second phase of global routing is completed. The third method, taking into account the number of nets that both enter and leave the partition, seems to be the best overall. For these results, and in general

| Circuit | Center    | Nets      | Nets                 |

|---------|-----------|-----------|----------------------|

| Name    | Distance  | Entering  | Entering and Leaving |

| adder32 | 0.6 / 0.4 | 0.5 / 0.3 | 0.6 / 0.4            |

| pr1     | 1.0 / 0.4 | 0.9 / 0.5 | 0.8 / 0.6            |

| square  | 0.8 / 0.3 | 1.0 / 0.3 | 0.8 / 0.3            |

| des     | 1.1 / 0.5 | 1.3 / 0.5 | 0.9 / 0.5            |

Table 2.1: Comparison of Difficulty Functions

for net densities. the maximum values are more important than the average values. since a maximum value over 1.0 means that the routing cannot be done.

Another method of dealing with slack is to begin with all partitions having the same amount of slack, and then iterate, at each stage using the predicted wiring space required by the previous partition to determine how much slack to give it for the current iteration. The process would terminate when the quality of the solution. as measured by the "fairness" of the slack distribution, ceases to improve. We did not test this technique. but the iterative control structure for the partitioning described below has a similar effect.

## 2.2 Quadrasection

The quadrasection algorithms tested were random assignment. clustering. generalized Kernighan-Lin-Fiduccia-Matheyses (KLFM) partitioning. Suaris-Kedem quadrasection, simple simulated annealing, adaptive simulated annealing, and adaptive simulated annealing using net moves instead of cell moves. Note that all these algorithms, with the exception of Suaris-Kedem quadrasection, can partition a netlist into an arbitrary number of partitions, but our tests have been done for 4 partitions in all cases.

#### 2.2.1 Random Partitioning

Random assignment is simple: each movable cell is assigned in succession to a random partition that has space available. In general, care must be taken that a configuration isn't created that has enough total room for the last block, but no single partition has enough. However, the placement algorithm is careful to adjust the sizes so that this cannot happen.

### 2.2.2 Clustering

Clustering is performed as follows. A seed cell is first picked for each of the partitions at random. Then for each partition in succession the free cell which is most strongly connected to the other cells is added to that partition. if there is enough available space. This process is repeated until there are no more free cells. In order to determine the most highly connected cell for each partition. gain tables are maintained. much like those used in the KLFM algorithm.

## 2.2.3 Kernighan-Lin-Fiduccia-Matheyses

The Kernighan-Lin-Fiduccia-Matheyses (KLFM) algorithm [34] is conceptually simple. although its efficient implementation can be rather tricky. For the two-way case, the algorithm is as follows:

| WHILE (improvement made in cut-set size) {             |

|--------------------------------------------------------|

| WHILE (cells remain to be moved) {                     |

| c = the cell whose move to the other                   |

| partition would lead to the greatest                   |

| decrease in the size of the cut-set;                   |

| move c;                                                |

| }                                                      |

| restore the configuration to the best found this pass: |

| }                                                      |

The step of picking the cell with the best gain can be performed in constant time, using a bucket-sorting strategy which was described in [20]. Briefly, for each partition, an array of lists of *cell moves* from that partition to the other is maintained, where the position in the array corresponds to the *gain*, or decrease in cut-set size, that would be obtained if a move in that list were made. Since the range of possible gains is proportional to the maximum number of pins on a cell, the size of the array is relatively small. (If net criticalities are taken into account, the arrays would become larger.) Fiduccia and Matheyses have shown a way to update these gain tables in constant time whenever a move is made, which leads to the overall linear runtime of the KLFM algorithm.

The generalization to N partitions is straightforward [65]. The cost the sum of the sizes of the spanning trees, as described above. instead of the size of the cut-set. Instead of finding the best cell to move, the algorithm must pick the best (*cell. partition*) pair.

Figure 2.2: Quadrasection

where partition is the destination of the cell. For N partitions, a total of  $N \times (N-1)$  gain tables is required. The minimum cost move is chosen from these which do not violate the capacity constraints of the destination partition. If no move can be made which does not violate capacity, one move that does violate capacity is allowed, since the violation will very likely be eliminated by a future move. Note that although this situation cannot arise in the original partitioning problem produced by the placement algorithm, it can occur in one of the sub-problems produced by the quadrasection algorithm.

This algorithm is an *improvement* algorithm. and it needs a good starting partition in order to work well. We tried both the random and cluster algorithms for initial partitions. and both results are given in Table 2.3.

## 2.2.4 Suaris-Kedem Quadrasection

The quadrasection algorithm is essentially a control strategy for KLFM. It is specific to the case where the number of real partitions is four. although the technique could be easily generalized. The area to be partitioned is first divided into upper and lower halves. and then each of those halves is partitioned into right and left halves. (See Figure 2.2.) Previous placement algorithms have taken this as the final partition [18]. but following [65]. we apply a further 4-way improvement step. Statistics for the partition with and without this improvement step are given, as are statistics for random assignment and clustering as the initial strategy for the 2-way partitions. These statistics show that the improvement

| Parameter                                   | Value |

|---------------------------------------------|-------|

| initial temperature                         | 100   |

| moves per temperature per cell              | 10    |

| temperature decrease per point              | 0.9   |

| points without an accept before stop        | 3     |

| last temp point cap-violating moves allowed | 90    |

Table 2.2: Simulated Annealing Partitioning Parameters

step usually leads to an improvement in the final solution of between 10% and 30%. and using the clustering algorithm usually yields better solutions. although not as dramatically better as the improvement step.

### 2.2.5 Simulated Annealing

Simulated annealing is used both here and in the detailed placement phase. The general simulated annealing algorithm is described in Section 4.2. This section describes the application of simulated annealing to quadrasection.

The first simulated annealing algorithm makes use of fixed parameters for the cooling schedule and the inner-loop stopping criterion. This technique was used by early placement algorithms [35.59]. and although the adaptive algorithm described below yields better results, the fixed algorithm is much simpler. The parameters used are given in Table 2.2.

One move consists of moving a cell from one partition to another. Cells that cannot move are not considered for movement. and "fake" partitions are not considered as destinations. The cost function is the spanning tree cost described above. Moves are allowed to violate capacity, with a penalty of 1000 times the capacity violation. After a certain temperature point, such moves are disallowed. After a certain number of temperature points without a move accepted, the process is terminated.

This is a relatively simple annealing algorithm, and the parameters given above were chosen empirically, based on a small set of examples.

### 2.2.6 Adaptive Simulated Annealing

The general adaptive simulated annealing algorithm is described in Section 4.2. It uses the same move set and cost function as the regular simulated annealing algorithm described above. and will not be discussed further.

### 2.2.7 Adaptive Simulated Annealing with Net Moves

The second adaptive simulated annealing algorithm uses *net moves* instead of cell moves. Instead of choosing a cell to move from one partition to another. this algorithm selects a net and a destination partition, and then moves all the movable cells on that net into that partition. The rationale behind this is that the goal is to maximize the number of nets wholly contained in one partition, moving a net at a time seems like a more direct way to achieve this goal. Simulated annealing was chosen as the control framework for this algorithm since it was the easiest to use — an iterative hill-climbing algorithm like Kernighan-Lin might have worked better, but if the concept of net moves is a good one, it stands to reason that it would yield good results in the adaptive simulated annealing framework also.

## 2.2.8 Results

The results obtained by partitioning some large netlists with these algorithms are given in Table 2.3. The corresponding runtimes are given in Table 2.4. These times were obtained on a VAX 8650.

Note that although some of the results for the simulated annealing algorithms are comparable to the results of KLFM and quadrasection. the runtimes become prohibitively large for even medium-sized examples: no problems with size over 1000 cells were able to complete in a reasonable amount of time. Simulated annealing has been empirically found to take time that is roughly quadratic in the problem size to achieve good results. while KLFM runs in linear time.

Among the annealing algorithms, the adaptive annealing algorithm did the best. probably because of the finer control over the cooling schedule. The net-move algorithm also did worse than the regular adaptive algorithm. Although this could be in part a result of the adaptive algorithm's unsuitability as a control framework for this move set, it is probably an indication that the moves in the move set are too "coarse-grained", in the

| Circuit  | Num   | Random | Cluster | KLFM  | KLFM    | Quad  | Quad    | Simple | Adapt  | Net    |

|----------|-------|--------|---------|-------|---------|-------|---------|--------|--------|--------|

| Name     | Cells |        |         | Rand  | Cluster | Rand  | Cluster | Anneal | Anneal | Anneal |

| pr1      | · 841 | 1697   | 554     | 406   | 323     | 253   | 254     | -      | -      | -      |

| pr2      | 3022  | 3022   | 2190    | 1590  | 1107    | 1085  | 1050    | 1      | -      |        |

| hughes   | 19724 | 35582  | 9843    | 9426  | 4496    | 4235  | 1861    | -      | -      | -      |

| square   | 2508  | 8370   | 1543    | 983   | 1065    | 854   | 854     | -      | -      |        |

| adder8   | 70    | 172    | 142     | 96    | 98      | 92    | 94      | _      | 1      | -      |

| adder16  | 191   | 538    | 523     | 283   | 289     | 254   | 245     | -      | 1      | —      |

| adder32  | 384   | 1143   | 1110    | 524   | 503     | 441   | 465     | -      |        | —      |

| mult32   | 5979  | 10484  | 4555    | 2764  | 1575    | 1811  | 1117    | —      | _      |        |

| rand100  | 100   | 1740   | 1091    | 689   | 649     | 682   | 616     | 732    | 682    | 760    |

| rand200  | 200   | 3885   | 2274    | 1612  | 1481    | 1343  | 1338    | 1522   | 1396   | 1507   |

| rand500  | 500   | 9315   | 5477    | 3933  | 3894    | 3573  | 3666    | 3912   | 3608   | . 3836 |

| rand1000 | 1000  | 18614  | 11072   | 7439  | 7228    | 6961  | 6901    | 7187   | 7177   | 7798   |

| rand5000 | 5000  | 93085  | 54694   | 38890 | 39033   | 36704 | 36529   | -      | -      | —      |

Table 2.3: Partitioning Algorithm Results: Costs of Final Solutions

| Circuit  | Num   | Random | Cluster | KLFM | KLFM    | Quad | Quad    | Simple | Adapt  | Net    |

|----------|-------|--------|---------|------|---------|------|---------|--------|--------|--------|

| Name     | Cells |        |         | Rand | Cluster | Rand | Cluster | Anneal | Anneal | Anneal |

| prl      | 841   | 1.3    | 1.5     | 9.0  | 7.6     | 12.0 | 14.1    | _      | _      | _      |

| pr2      | 3022  | 5.1    | 6.1     | 50.0 | 29.2    | 101  | 56.7    |        | _      |        |

| hughes   | 19724 | 43.2   | 46.6    | 658  | 274     | 604  | 320     |        |        | _      |

| square   | 2508  | 4.8    | 5.0     | 29.1 | 26.0    | 35.2 | 32.7    | _      |        |        |

| adder8   | 70    | 0.1    | 0.1     | 0.3  | 0.3     | 0.2  | 0.4     |        |        | . —    |

| adder16  | 191   | 0.3    | 0.3     | 1.4  | 1.4     | 2.2  | 1.8     | _      |        |        |

| adder32  | 384   | 0.6    | 0.7     | 5.0  | 5.7     | 3.3  | 4.6     | -      |        |        |

| mult32   | 5979  | 9.7    | 12.0    | 76.0 | 43.5    | 136  | 89.3    |        | -      |        |

| rand100  | 100   | 0.1    | · 0.2   | 0.7  | 0.4     | 0.6  | 0.6     | 44.3   | 21.0   | 47.7   |

| rand200  | 200   | 0.2    | 0.2     | 1.3  | 1.0     | 1.8  | 1.2     | 103    | 88.0   | 208    |

| rand500  | 500   | 0.7    | 1.1     | 3.2  | 3.4     | 5.6  | 3.9     | 374    | 765    | 1396   |

| rand1000 | 1000  | 1.5    | 1.5     | 9.2  | 9.3     | 9.5  | 9.9     | 8179   | 3724   | 2966   |

| rand5000 | 5000  | 6.9    | 7.9     | 51.8 | 39.1    | 98.0 | 51.8    | _      | _      | _      |

Table 2.4: Partitioning Algorithm Times. in Seconds

sense that they change the configuration too drastically. There are not enough small moves to move out of "shallow bowls" [64] without moving too far, when the temperature is low. Perhaps an approach that provided both the large-scale net moves and the smaller-scale cell moves would work better.

It has been noted [34] that the KLFM algorithm is very sensitive to the initial partition given. This can be seen by comparing the columns "KLFM Cluster" with "KLFM Random". and "Quad Cluster" with "Quad Random". The clustering algorithm is much better than random partitioning, and for the larger examples. this difference in starting quality leads to a difference in quality of final results. For the smaller examples there seems to be little if any difference in the final quality. Also, in most of the examples the "KLFM" and "Quad" algorithms that use clustering for the initial partition take less time than the corresponding algorithms that use random initial partitions. This is because a better original solution leads to fewer passes.

The example "square" is an artificially constructed netlist. which could ideally be laid out in a rectangular  $50 \times 50$  mesh, each cell connecting only to its four neighbors. Thus the ideal partition should have 50 vertical and 50 horizontal crossings on the center lines. Although this cannot be seen from the data in Table 2.3. due to the weighting factors introduced by the placement algorithm and extra crossings due to external connections. the 4-way KLFM algorithm produced 56 and 54 horizontal and vertical crossings. respectively. and the quadrasection algorithm produced 52 and 52 crossings. A result so close to the known minimum for even one example gives confidence in the essential soundness of the algorithm.

### 2.2.9 Control Strategy

We tested a number of different control strategies for applying the partitioning algorithm. The first was depth-first: after a block is partitioned, partition each of its children in turn. This turned out to be too order-dependent, since the first sub-tree partitioned had much more freedom than the later sub-trees. The second approach tried was ordering all the sub-problems on a particular level according to their estimated complexity. This also turned out to be too order-dependent. The approach we settled upon is similar to that used by Suaris and Kedem, which is to partition the blocks, and then iterate ripping up and re-partitioning the blocks until there is no more improvement in quality. At that point

| Circuit  | Depth First | Random      | Est. Complexity | Iterated Rip-up |

|----------|-------------|-------------|-----------------|-----------------|

| Name     | max / avg   | max / avg   | max / avg       | max / avg       |

| adder32  | 0.88 / 0.55 | 1.11 / 0.58 | 0.81 / 0.53     | 0.79 / 0.53     |

| pr1      | 1.02 / 0.51 | 1.30 / 0.57 | 0.72 / 0.49     | 0.71 / 0.49     |

| pr2      | 1.10 / 0.67 | 1.25 / 0.65 | 0.89 / 0.52     | 0.85 / 0.51     |

| mult32   | 1.05 / 0.70 | 1.70 / 0.70 | 0.91 / 0.61     | 0.93 / 0.62     |

| rand1000 | 2.21 / 0.98 | 3.42 / 1.03 | 1.41 / 0.75     | 1.32 / 0.72     |

| rand5000 | 3.04 / 1.20 | 4.24 / 2.29 | 2.04 / 0.97     | 1.75 / 0.78     |

Table 2.5: Ripup and Re-partition Results

the next level down is partitioned. This approach was combined with initially ordering the sub-problems according to estimated complexity. The results of this comparison are given in Table 2.5. The figures are for the maximum and average global routing densities on the chip after the final global route is completed. The methods for estimating complexity are discussed in Section 3.2. The iterated rip-up algorithm performed the best overall. although ordering the blocks by estimated complexity did almost as well in many cases.

## 2.3 Minimum Density Partitioning

Another approach to partitioning that we tried was minimum-density partitioning. Preliminary trials indicated that this algorithm was not very promising. and we did not have time to implement it efficiently enough to collect extensive statistics on it. The algorithm is described below.

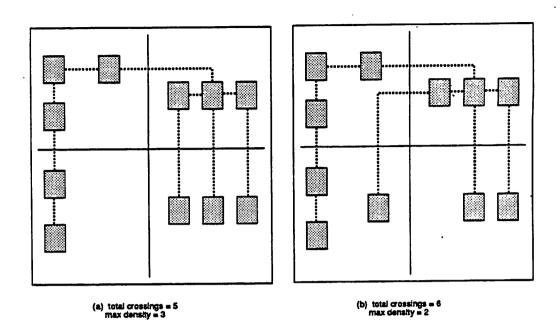

We made the observation that mincut partitioning does not take into account the complexity of the wiring within the partitions. nor does it consider the wiring density at the boundaries between partitions. There are cases where a partition has a lower total cost. using the min-cut metric, yet is less routable (has a higher maximum density) than one with a higher cost (see Figure 2.3). This lead us to ask whether we could devise a good partitioning algorithm that uses density directly as a cost function instead of cutsize, and if so, whether it would yield better results than mincut, in which the cost function is more loosely correlated to the value we want to optimize.

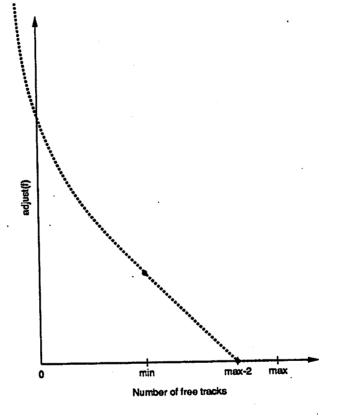

The cost function we chose has two terms in it. These were the number of tracks left in each partition,  $T_{h,i}$  and  $T_{v,i}$ . for  $i \in \{1, 2, 3, 4\}$ , and the cell area violations in each

Figure 2.3: Minimum Cut Vs. Minimum Density Partitions

partition.  $C_i$ . The cost is defined by

$$\text{cost} = W_{cell} \sum_{i=0}^{3} C_i + W_{wire} \sum_{i=0}^{3} (\text{adjust}(T_{h,i}, H_{max}) + \text{adjust}(T_{v,i}, V_{max}))$$

where  $W_{cell}$  and  $W_{wire}$  are 10 and 1 respectively. The function *adjust* is designed to give more weight to partitions that have close to 0 free tracks, and is shown in Figure 2.4. Note that this cost function assumes that the nets have already been globally routed, so the global routing information must be updated each time a cell move is made.

The terms in the cost function are straightforward to compute. The techniques for determining the number of tracks free are described in Section 3.2. The difficult part is computing the change to these values efficiently when a cell move is made. This can be accomplished by keeping careful track for each cell and net of what contributions they have made to each of the relevant values.

The available moves are cell moves and possibly cell swaps and net moves. Since none of the other partitioning algorithms uses cell swaps, and net moves were found to be ineffective, the moveset was limited to simple cell moves. After a cell is moved, the nets attached to that cell are globally rerouted in the  $2 \times 2$  grid.

Another major consideration is the speed of such an algorithm. KLFM partitioning has O(n) runtime per pass. For another partitioning algorithm to be practically useful. its

Figure 2.4: The Function adjust

| Circuit | No.   | Min Dens | Min Dens | Min Cut | Min Cut |

|---------|-------|----------|----------|---------|---------|

| Name    | Cells | Cost     | Runtime  | Cost    | Runtime |

| adder8  | 62    | 53       | 7        | 50      | 1       |

| adder16 | 191   | 449      | 121      | 317     | 8       |

| adder32 | 384   | 972      | 673      | 837     | 18      |

| pr1     | 841   | 3341     | 1991     | 2593    | 37      |

Table 2.6: Results of Minimum Density Partitioning

efficiency must be close to this. However, for testing our minimum density partitioning algorithm we used the adaptive simulated annealing framework. Although we would have to devise a better control strategy eventually, this experiment gave some indication of what sort of results we could expect.

This implementation was tested on some small examples. We compared both the runtime and the final quality with the adaptive annealing mincut partitioning algorithm. which has the same control framework. The results, which are given in Table 2.6. were not encouraging. They might be interpreted as follows. The density. although a more accurate cost function, is not only more difficult to maintain but is too uniform. The difference in density between two configurations will in general be much less than the difference in crossing count. since the density takes into account the cell and net blockages, which change more slowly than the crossings during the course of partitioning. Although minimum density partitioning eliminates the need for some of the heuristics that try to predict where the congestion will be, such as the division of "slack" before partitioning is done, this is not necessarily a good thing. It seems that in this situation, as is often the case, it is better to solve some sub-problems that approximate the real problem very well than to find an inferior solution to the real problem.

## 2.4 When to Stop Partitioning

Partitioning process terminates when a block that is a good candidate for detailed placement and routing is reached. There are a number of factors that must be considered when deciding whether a block is a leaf problem or not.

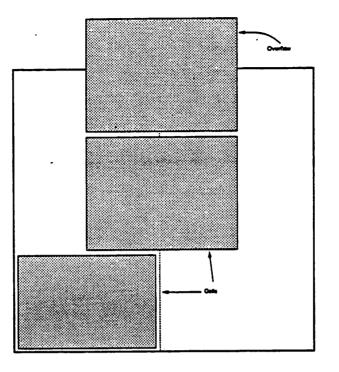

The first and most important one is whether partitioning the block further would make it impossible to place the cells in the block. Since all the cells in a block must reside

Figure 2.5: A Block That is Too Small for its Cells

entirely within the block. if the block is smaller than one of the cells. or small enough that the cells cannot be arranged within the block. even though the total area of the cells is less than the block area (as in Figure 2.5). its parent should not have been partitioned.

Also, partitioning a block restricts the possible layouts. Cells cannot stretch across block boundaries, and a net can have only one pin per edge of a leaf block (although after the second phase of global routing, it may have more than one pin on an edge of a higherlevel block). To reduce the effects of bad partitioning decisions, we tried using a "rip-up and re-place" heuristic. This consists of collapsing one level of the partition hierarchy and trying to solve the resulting larger problem.

This proved ineffective for several reasons. A placement problem that is four times larger takes much more than four times longer to run. and Mighty likewise scales more than linearly. Also, if a block is very difficult to lay out, the chances are that its neighbors will also be very difficult. so the overall complexity will not decrease much. Finally, because of the way we do the second phase of maze routing, when we collapse one level of block. nets might have more than one pin on an edge of the leaf block. This situation cannot be represented by the data structure currently used by the detailed placement system.

Based on these considerations, we have adopted a simple scheme for ending the

partitioning process. A block is considered a leaf block if either its width or its height is less than or equal to 4 times the width or height respectively of one *basic tiling unit* (see Figure 1.5). or of the largest cell in the block, whichever is larger. This makes it very unlikely that the sort of situation pictured in Figure 2.5 can occur.

## Chapter 3

# GLOBAL ROUTING

There are two phases of global routing performed before the detailed placement and detailed routing phases. These are initial hierarchical routing and global maze routing. The initial routing is performed purely to direct the partitioning process. The final global routing phase is performed after the initial routing has been ripped up. and uses a variation of the Lee maze-routing algorithm.

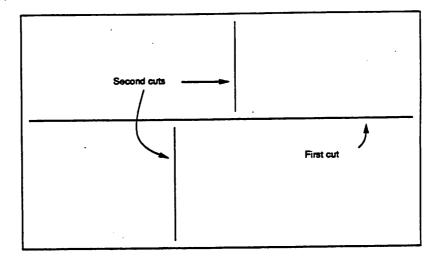

## 3.1 The First Global Routing Phase

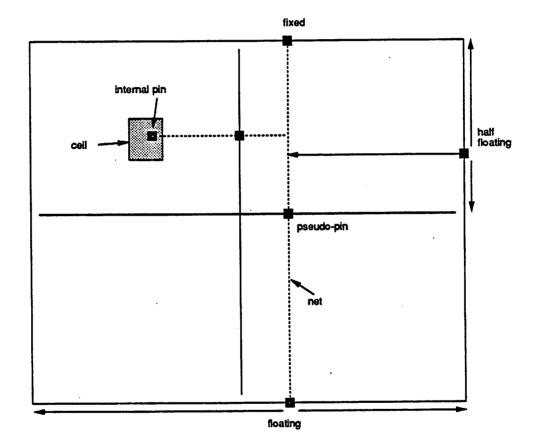

The initial global routing uses a hierarchical approach. similar to those of Burstein [10] and Suaris and Kedem [65]. It is performed concurrently with the partitioning process. After each block is partitioned, all the nets which pass through this block are assigned routes through the  $2 \times 2$  grid created by the quadrasection. Note that although we call this a  $2 \times 2$  routing problem, we also need to determine which direction a net takes from one of the partitions to the outside of the grid. Thus this is more general than the  $2 \times 2$  problem as described in [42]. A net may have pins on cells in any of the four sub-blocks, and may have a pin on any of the four sides. Furthermore, the pin may be floating along an edge, or restructed to either the first or the second half. (See Figure 3.1.) The pin location restriction may be a result of either an adjacent block which is already routed, in which case it is called *half-floating*, or an external pin on the edge of the chip by the position of the corresponding pad, in which case it is called *fixed*.

These conditions may be expressed as an S-tuple  $\{P_0, P_1, P_2, P_3, E_t, E_b, E_l, E_r\}$ , where the  $P_i$ 's are either 1 or 0 depending on whether the net has a pin in the i'th partition.

Figure 3.1: The  $2 \times 2$  Routing Problem

and the  $E_i$ 's take on one of the values {none, upper, lower, floating}. Thus there are  $2^{12}$  possible net types to route. Since enumerating all the possible routes for a particular net type may be a time consuming operation. a "memo function" is used to calculate the routes, which remembers all its past return values in an array of size  $2^{12}$ . Enumerating the possible routes for a particular configuration is not excessively expensive, though — the maximum number of routes is 256, but reasonable  $2 \times 2$  routing problems have only a few solutions.

The possible routes are calculated in the following manner. First. each of the 12 edge halves (internal and external) are marked with one of {yes, no, either, maybe}. where yes indicates that there must be a pin on that edge half. no indicates that a pin may not be on that edge half. either indicates that a pin must be on either that edge half or the other half of the edge. and maybe indicates that there may or may not be a pin on that edge half. The choices now are first. for every edge half that is either, whether to put the pin there or the other half, and second, for every pin that is maybe, whether to put a pin there or not. All such choices are then enumerated, and those that either contain cycles, contain disjoint components, or don't contain all the partitions that contain cells on the net are rejected.

A possible route for a net may be expressed as a 12-tuple  $\{X_0, X_1, ..., X_{11}\}$ , where  $X_i$  is 1 iff there is a pin on edge number *i*. If *i* is an internal edge, the pin is a *pseudo-pin*.

These choices are then given costs, and the lowest cost route for the net is chosen. We investigated two types of cost functions. The first takes into account the congestion at each edge. and sets the cost equal to

$$\sum_{i \in edges} \pi(i) f(ratio_i)$$

where  $ratio_i = density/capacity$  at edge i,

$\pi(i) = \begin{cases} 1 & \text{if the net has a pin on edge} \\ 0 & \text{otherwise} \end{cases}$

and

$$f(r) = \begin{cases} r & \text{if } r < C_{max} \\ F_{soft}r & \text{if } r >= C_{max} \text{ and } r < 1 \\ F_{hard}r & \text{if } r >= 1 \end{cases}$$

$C_{max}$ , the desired maximum capacity, is a value determined empirically to be 0.75 by examining the success patterns of the detailed placement and routing.  $F_{soft}$  (the "soft"

| Cost       | Fsoft | Fhard | Max / Avg   | Max / Avg  |

|------------|-------|-------|-------------|------------|

| • Function | Value | Value | Density     | Net Size   |

| Weighted   | 5     | 20    | 1.00 / 0.57 | 156 / 6.48 |

| Weighted   | 10    | 100   | 1.04 / 0.54 | 161 / 6.48 |

| Weighted   | 10    | 20    | 1.09 / 0.55 | 164 / 6.53 |

| Weighted   | 3     | 20    | 1.10 / 0.55 | 160 / 6.36 |

| Weighted   | 20    | 100   | 1.14 / 0.54 | 155 / 6.53 |

| Weighted   | 3     | 1     | 1.15 / 0.55 | 160 / 6.36 |

| Weighted   | 2     | 1     | 1.21 / 0.56 | 152 / 6.45 |

| Weighted   | 2     | 100   | 1.21 / 0.56 | 152 / 6.46 |

| Weighted   | 1     | 100   | 1.33 / 0.55 | 155 / 6.42 |

| Weighted   | 1     | 3     | 1.47 / 0.55 | 155 / 6.42 |

| Uniform    | -     | •     | 0.92 / 0.54 | 157 / 6.41 |

Table 3.1: Comparison of Initial Global Routing Cost Functions

penalty factor) and  $F_{hard}$  (the "hard" penalty factor) are 5 and 20 respectively, and are likewise empirically determined.

The second cost function uses the same sum, with f(ratio) = 1. That is, the route with the smallest number of crossings is always chosen.

Results for these two cost functions are given in Table 3.1. for some values of  $F_{soft}$  and  $F_{hard}$ . The second one works better although it takes no account of the congestion. The reason for this is that the purpose of this global routing phase is to direct the partitioning process. If many nets want to cross an edge on one half instead of the other, they should be allowed to cross there so that the next round of partitioning can take this fact into account, instead of being forced to take detours, which hides the better routes from the partitioning. The fact that the routes may violate capacity constraints does not matter, since these global routes are not actually used. Furthermore, using the cost function f(ratio) = 1 eliminates the problem of order dependence in this phase of global routing, since the value of the function doesn't depend upon the previous density of the edges crossed by the nets.

## **3.2** Routing Area Prediction

After the partitioning process is finished, we wish to estimate the routing capacities of each of the leaf blocks as accurately as possible, before doing the final global route of the nets. The X- or Y-capacity of a block is defined as the total number of routing tracks in that

| Number  | Equivalent |

|---------|------------|

| of Pins | Nets       |

| 2       | 1          |

| 3       | 1.2        |

| 4       | 1.4        |

| 5       | 1.6        |

| 6       | 1.8        |

| 7       | 2.0        |

| . 8     | 2.0        |

Table 3.2: Empirically Determined Multiple Pin Equivalent Nets

direction (not counting those used by power and ground busses). minus the total estimated blockages. An estimated blockage may be either a blockage from a cell or a blockage from a net internal to the block. Determining this value accurately is very difficult. since the placement is not known, so we err on the conservative side whenever necessary.

Blockages due to cells within the block may be estimated in a straightforward fashion. The total length of the obstacles in the appropriate direction is calculated. and then this is divided by the width or height of the block to produce the best-case number of tracks that would be blocked. That is, if there are a total of  $K\mu$ m of vertical wires in cells of the block, and the height of the block is  $H\mu$ m. K/H tracks are blocked. If a wire runs in the wrong direction, it is modelled as a series of length 1 wires.

This number is then multiplied by  $K_{cell}$ , an empirical constant which measures how much the actual value deviates from the best-case value calculated above. This has been determined to be approximately 1.4. The actual number of blockages is measured by noting how many external wires can be routed through this block by the detailed router.

Blockages due to nets are calculated in a more interesting manner. First. all multipin nets are expressed as a number of two-pin nets. which are equivalent with respect to netlength. The empirically derived values for these numbers are given in Table 3.2. Note that external pins are excluded from this count, since the number of available external connections to nets is precisely that which we are trying to determine.

The total number of equivalent two-pin nets.  $N_{equiv}$  is then multiplied by the average netlength for this block, which is calculated by the following formula, due to Donath

et al[17.25], who have derived it from Rent's rule[39].

$$H_{avg} = K_{net}C^{p-0.5}\sqrt{(C)}\frac{H_{free}}{(H_{free} + V_{free})}$$

$$V_{avg} = K_{net}C^{p-0.5}\sqrt{(C)}\frac{V_{free}}{(H_{free} + V_{free})}$$

where

| С     | = number of cells in the block                         |

|-------|--------------------------------------------------------|

| Hfree | = height – horizontal tracks blocked by cell blockages |

| Vfree | = width - vertical tracks blocked by cell blockages    |

| Knet  | = empirical constant. found to be approximately 1.2    |

| p     | = "parallelism factor" for netlist                     |

The parallelism factor for the netlist is usually between 0.5 and 0.75 for typical netlists. We do not attempt to estimate the parallelism factor. but rather allow the user to specify a value for it. After the layout is completed, the actual value found for this constant is printed, and the user may supply this to successive placement runs.

The total estimated routing tracks available for the block are thus

Vertical tracks =  $width - pgtracks - V_{cell} - V_{net}$

Horizontal tracks =  $height - H_{cell} - H_{net}$

where

| $H_{cell}$ | = the total number of horizontal cell blockages |

|------------|-------------------------------------------------|

| Vcell      | = the total number of vertical cell blockages   |

| Hnet       | = the total number of horizontal net blockages  |

| Vnet       | = the total number of vertical net blockages    |

| pgtracks   | = number of tracks used for power and ground    |

| height     | = height of the block in tracks                 |

| width      | = width of the block in tracks                  |

We have found this technique to be reasonably good for large sub-problems. but it becomes less accurate when it is applied to small sub-problems where the effects of detailed routing are much more pronounced. However, this effect is minimized by the fact that the global routing algorithms tend to work better on a small scale than a large scale. and the "rip up and re-place" technique can be applied. The above formulas were derived for standard-cell designs — a careful examination of their validity for gate array types of designs might lead to a better better interconnection model for Sea of Gates.

Figure 3.2: Hierarchical vs Flat Routing

## 3.3 The Second Global Routing Phase

After the partitioning process is completed, all the nets that span more than one block are ripped up and globally rerouted. This is done because the initial. four-way refinement global routing algorithm must make decisions early in the partitioning process that drastically affect available routes later on. without enough information to make the best choices. Also, the types of routes that can be generated by the simple refinement algorithm used here are a subset of the reasonable routes that one might consider. In Figure 3.2, route (a) is the best route that can be generated by our hierarchical refinement, but route (b) is a much better route. The reason that our hierarchical routing algorithm cannot generate route (b) is that at each level of the hierarchy, a net can cross any edge only once. Note that there are techniques for hierarchical routing that relax this restriction [44], but these are more complex and time-consuming. Instead of improving our hierarchical routing algorithm, we decided to use it only for directing the partitioning, and re-route all the nets after the partitioning has been completed.

## 3.3.1 The Problem

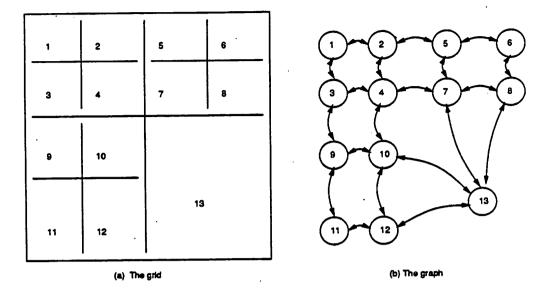

The routing problem is as follows. The area to be used for routing is a grid. as in Figure 3.3a. each of which has a certain number of vertical and horizontal feedthroughs.

Figure 3.3: Two Representations of the Global Routing Problem

These numbers are calculated by means of the routing area prediction algorithm described in Section 3.2. For any boundary between adjacent blocks, the capacity of that boundary is defined as the minimum of the number of horizontal or vertical feedthroughs for the two blocks, for vertical and horizontal boundaries, respectively. This grid can be thought of as an undirected graph, with edges having capacities (Figure 3.3b).

Nets contain pins which reside in graph nodes. External pins. which correspond to pads. are contained by the node corresponding to the block nearest to the pad. A net can contain pins in an arbitrary subset of nodes. The global routing problem thus becomes that of assigning Steiner trees to each net. such that some function of the sizes of the individual Steiner trees and the *density/capacity* ratios of the arcs in the graph is minimized.

This problem is in general an NP-complete problem. There has been a great deal of research to develop heuristic algorithms to solve this problem. none of which have been entirely satisfactory [38].

### 3.3.2 Maze Routing

One of the better and simpler classes of algorithms for solving this problem in its graph formulation is the Lee maze-routing algorithm [43.50]. The Lee algorithm and the similar Hightower line-search algorithm [26] have also been successfully applied to detailed

Figure 3.4: Different Ways To Route A Multi-Pin Net

routing [62]. The essential idea of the Lee algorithm is to expand from one or more nodes in the graph. keeping track of the path to each node so that once the destination is reached the path taken can be reconstructed.