Copyright © 1989, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# MULTILEVEL BEHAVIORAL VERIFICATION FOR VLSI DESIGN

by

Seung Ho Hwang

Memorandum No. UCB/ERL M89/85

18 July 1989

# MULTILEVEL BEHAVIORAL VERIFICATION FOR VLSI DESIGN

by

Seung Ho Hwang

Memorandum No. UCB/ERL M89/85

18 July 1989

Tine and

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# MULTILEVEL BEHAVIORAL VERIFICATION FOR VLSI DESIGN

đ

by

Seung Ho Hwang

Memorandum No. UCB/ERL M89/85

18 July 1989

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Multilevel Behavioral Verification for VLSI Design

by

Seung Ho Hwang

### Abstract

To narrow the gap between the theory and its application to real problems, this dissertation addresses the practicality of hardware design verification. This goal is achieved by dividing the verification problem into two subproblems: correctness checking of finite-state machines and equivalence checking of multilevel behavioral descriptions.

An efficient algorithm is presented for the correctness checking of finite-state machines. The algorithm checks to see if an implementation, given by a net-list of gates and latches, satisfies a specification given as a state transition table. When the implementation is incorrect, an input sequence that distinguishes the implementation machine from the specification machine is provided to help the user locate errors. Experimental results show that the method can be applied to fairly large systems.

For the equivalence checking of behavioral descriptions, a formal technique based on theorem proving methods is used. Because verification is performed by a formal technique, complete verification can be achieved without exhaustive simulation. Behavior is specified in a hardware description language that deals with timing and functionality in one paradigm using functional (denotational) semantics. Type definition mechanisms and macros are provided, along with recursive definitions. The behavioral verification system automatically handles type definitions and exploits hierarchy. Hierarchy is exploited when checking functional equivalence by using techniques such as inductive verification of recursive descriptions. Hierarchical timing verification is also supported by the abstraction of timing information by constraint propagation. During the abstraction of timing information, the availability of functional relations between signals eliminates the static-insensitizable-path problem.

Signature A. Riched liver Run

A. Richard Newton Committee Chairman

### ACKNOWLEDGEMENTS

I greatly acknowledge my research advisor, Professor Richard Newton, for his guidance, encouragement, and support throughout the course of this work. Without his enthusiasm and the inspiration he provided, this work would not have been possible.

I am also grateful to Professors Robert Brayton, Alberto Sangiovanni-Vincentelli and Carlo Sequin for their continuing interest in my research projects. Thanks are due to Professor James Sethian, who served on my qualifying examination from Mathematics Department.

I thank all CAD group members at the University of California, Berkeley. In particular, I wish to express appreciation to Gregg Whitcomb, Brian O'Krafka and Bill Lin for their critical reading of the manuscript of this dissertation. Rick Spickelmier, Tom Quarles, Peter Moore, Jeffrey Burns and Resve Saleh are some of the Berkeley CAD group members who were more than happy to help me whenever I needed it. I enjoyed the discussions with Tom Laidig, Srinivas Devadas and Tony Ma on relevant subjects.

I thank all former and current Korean EECS graduate students who I have been acquainted with for those wonderful time I had. Young Kim, Hyun Shin, Hyunchul Shin. Hong-June Park, Han Koh, Daebum Lee are a few of them.

My wife, Young Soon, my children, Jae-Won and Jae-Sun, have been the source of encouragement. I am also greatly indebted to my other family members and relatives for their continuous support. I express my gratitude for the financial support that made this research possible. I acknowledge support from the Semiconductor Research Corporation and the Digital Equipment Corporation.

٠

# TABLE OF CONTENTS

| CHAI | PTER 1: INTRODUCTION               | 1 |

|------|------------------------------------|---|

| 1.1  | Motivation                         | 1 |

| 1.2  | Hierarchical Design Methodology    | 2 |

| 1.3  | Timing and Functional Verification | 2 |

| 1.4  | Organization of the Dissertation   | 3 |

# CHAPTER 2: THE HARDWARE DESIGN VERIFICATION PROBLEM

| ••                                                        |                                                                                                | 5              |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|

| 2.1                                                       | Introduction                                                                                   | 5              |

| 2.2                                                       | Various Aspects of Design Verification                                                         | 7              |

| 2.3                                                       | Simulation and Formal Verification                                                             | 11             |

| 2.4                                                       | Hierarchy and Three Classes of Hardware Modules                                                | 16             |

| 2.5                                                       | Verification Problem                                                                           | 18             |

|                                                           |                                                                                                |                |

| СНАР                                                      | TER 3: FINITE-STATE MACHINE VERIFICATION                                                       | 20             |

| •                                                         | TER 5: FIGHTE-STATE MACHINE VERIFICATION                                                       | 20             |

| 3.1                                                       | Introduction                                                                                   | 20             |

|                                                           |                                                                                                |                |

| 3.1                                                       | Introduction                                                                                   | 20             |

| 3.1<br>3.2                                                | Introduction Definitions and Notation                                                          | 20<br>22       |

| <ul><li>3.1</li><li>3.2</li><li>3.3</li><li>3.4</li></ul> | Introduction Definitions and Notation Problem Formulation of Finite-State Machine Verification | 20<br>22<br>24 |

| 3.4.2    | .1 Example                            | 33 |

|----------|---------------------------------------|----|

| 3.4.2    | .2 Cube Simulation and Cube Splitting | 35 |

| 3.4.2    | .3 Cube Splitting Heuristics          | 36 |

| 3.4.2    | .4 Output Checking                    | 37 |

| 3.4.2    | .5 Detailed Algorithms                | 38 |

| 3.4.2    | .6 Remarks                            | 40 |

| 3.5 Exp  | erimental Results                     | 41 |

| 3.6 Con  | clusions                              | 45 |

| CHAPTER  | 4: RELATED WORK ON FORMAL TECHNIQUES  | 46 |

|          | duction                               | 46 |

|          | antics for Programming Languages      | 47 |

| 4.2 Sem  | antics for Programming Languages      |    |

| 4.2.1    | The Operational Approach              | 47 |

| 4.2.2    | The Denotational Approach             | 49 |

| 4.2.3    | The Axiomatic Approach                | 50 |

| 4.2.4    | Comparison of the Three Approaches    | 51 |

| 4.3 Prog | gram Specification Methods            | 53 |

| 4.3.1    | Algebraic Specifications              | 55 |

| 4.3.2    | State-Machine Specifications          | 56 |

| 4.3.3    | Abstract Model Specifications         | 58 |

| 4.3.4    | Comparison of the Three Techniques    | 59 |

| 4.4 Pro  | gram Verification Methods             | 60 |

v

•

| 4.4.1 The Inductive Assertion Method                        | 60 |

|-------------------------------------------------------------|----|

| 4.4.2 The Axiomatic Method of Hoare                         | 62 |

| 4.4.3 Verification Methods Based on Denotational Semantics  | 63 |

| 4.5 Previous Formal Hardware Verification Techniques        | 64 |

| 4.5.1 Symbolic Simulation                                   | 64 |

| 4.5.2 Predicate Logic                                       | 65 |

| 4.5.3 First-Order Logic Approaches                          | 66 |

| 4.5.4 Higher-Order Logic Approaches                         | 68 |

| 4.5.5 Temporal Logic Approaches                             | 69 |

| 4.5.5.1 Linear Time Temporal Logic                          | 71 |

| 4.5.5.2 Branching Time Temporal Logic                       | 72 |

| 4.5.5.3 Interval Time Temporal Logic                        | 73 |

| 4.5.6 Other Approaches                                      | 73 |

| 4.6 Conclusions                                             | 74 |

| CHAPTER 5: BEHAVIORAL DESCRIPTION LANGUAGE                  | 77 |

| 5.1 Introduction                                            | 77 |

| 5.2 Behavior and Structure                                  | 80 |

| 5.2.1 Structure                                             | 81 |

| 5.2.2 Behavior                                              | 82 |

| 5.3 Functional Formalism                                    | 84 |

| 5.4 Overview of the Behavioral Verification System (BEAVER) | 86 |

vi

| 5.5 Primitive Language Constructs                          | 89  |

|------------------------------------------------------------|-----|

| 5.5.1 Types                                                | 90  |

| 5.5.2 Cells                                                | 94  |

| 5.5.3 Assignments                                          | 95  |

| 5.5.4 Recursions                                           | 95  |

| 5.6 Primitive Cells                                        | 96  |

| 5.7 Macros                                                 | 98  |

| 5.8 Conclusions                                            | 99  |

| CHAPTER 6: HIERARCHICAL TIMING VERIFICATION                | 100 |

| 6.1 Introduction                                           | 100 |

| 6.2 Timing Constraints of Synchronous Digital Systems      | 102 |

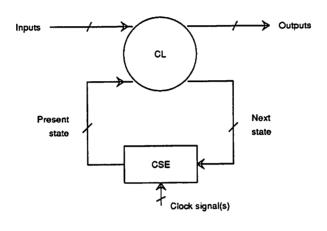

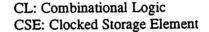

| 6.2.1 Clocked Storage Elements                             | 102 |

| 6.2.2 Timing Constraints with Edge-Triggered Type Elements | 104 |

| 6.2.3 Timing Constraints with Transparent Type Elements    | 107 |

| 6.3 False Path Problem                                     | 111 |

| 6.4 Timing Model                                           | 113 |

| 6.4.1 Two Language Constructs for Timing Behavior          | 114 |

| 6.4.2 Declaration of Synchronizing Signals                 | 115 |

| 6.4.3 A Modeling Example: Clock Skew                       | 115 |

| 6.5 Abstraction of Timing Behavior                         | 118 |

| 6.5.1 Combinational Cells                                  | 118 |

vii

•

| 6.5.2 Synchronous Cells                                    | 123 |

|------------------------------------------------------------|-----|

| 6.5.2.1 Four Kinds of Timing Information                   | 123 |

| 6.5.2.2 Instantiations of Synchronous Cells                | 126 |

| 6.5.3 Compositions of Timing Information                   | 127 |

| 6.5.3.1 Compositions of Output Timing Information          | 128 |

| 6.5.3.2 Compositions of Internal Timing Constraints        | 130 |

| 6.5.3.3 Compositions of Delay and Input Timing Information | 130 |

| 6.6 Examples and Results                                   | 131 |

| 6.7 Conclusions                                            | 135 |

| CHAPTER 7: FORMAL FUNCTIONAL VERIFICATION                  | 136 |

| 7.1 Introduction                                           | 136 |

| 7.2 Equivalence Checking Problem                           | 138 |

| 7.3 Theorem Prover                                         | 140 |

| 7.3.1 Value Domain                                         | 143 |

| 7.3.2 Derived Cells and Axioms                             | 143 |

| 7.3.3 Major Proof Steps                                    | 145 |

| 7.4 Examples and Results                                   | 148 |

| 7.5 Conclusions                                            | 154 |

| CHAPTER 8: CONCLUSIONS                                     | 155 |

| REFERENCES                                                 | 158 |

.

•

.

viii

####

•

en de la desta La desta de la d La desta de la d

n de la companya de Antes de la companya d Antes de la companya d

n de la companya de la comp

ix

### **CHAPTER 1**

### INTRODUCTION

#### **1.1.** Motivation

The ultimate goal of computer-aided design (CAD) of integrated circuits(IC's) is to build systems which can generate automatically designs of entire circuits from the usersupplied requirements. However, the achievement of this goal is not foreseeable in the near future. Current approaches involve human intervention, and design verification continues to be an important problem.

Traditionally, simulation at various levels of description has been used for the verification of hardware design. In order to achieve a complete verification using this approach, exhaustive simulation must be performed. Unfortunately, excluding very simple designs, exhaustive simulation is nearly impossible. To overcome this limitation, formal verification techniques have been proposed. However, in order to apply these techniques to real design problems, more research work is needed.

In this dissertation the practicality of the hardware design verification is addressed in an effort to narrow the gap between the theory and its application to real problems. To achieve the goal of obtaining a more practical verification system, the verification problem is divided into two subproblems: correctness checking of finite-state machines and equivalence checking of multilevel behavioral descriptions.

#### 1.2. Hierarchical Design Methodology

To address the complexity of a very-large-scale-integration (VLSI) design, the concept of hierarchical design has been widely accepted. This idea is similar to the structured programming technique, which has been used by software engineers for many years. A hierarchical methodology allows the designer to specify a design in a modular, multilevel manner, starting from the top level and working to the bottom. In VLSI design, this process involves a decomposition by which a complex entity is partitioned into multiple, less complex subentities. The decomposition of the design into modules is arbitrary, but typically it is organized according to the functional structure of the system under design. The top level of the design is a high-level description of the entire design in terms of modules and the interconnection of those modules. The modules are abstracted to hide unnecessary details from the designer and to allow him to think about only necessary information on a given level.

When a design is performed in a hierarchical environment, the verification of a large system can be split into smaller and simpler problems. This "divide-and-conquer" approach provides a practical approach to solving the complex verification problem. The increasing importance of the logical structure in VLSI design [1,2], demands methodologies and tools to support hierarchical decomposition at high levels.

#### **1.3.** Timing and Functional Verification

In an equivalence checker for multilevel behavior, not only must the functional behavior be verified but it is also necessary to address timing behavior.

Most timing verifiers deal with flattened-down descriptions of a design at a specific level, usually in switch-level or gate-level [3,4,5]. However, with hierarchical descriptions it is more desirable to be able to handle the timing information in a hierarchical manner. The

2

abstraction of timing behavior, as well as functionality, is important. Also, as the timing verification is performed with the known functional relations of signals, the static-insensitizable-path problem, which has been an important problem in timing verification, can be eliminated.

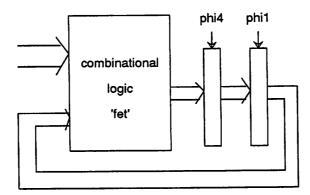

In this work, the functional verification problem is formulated as an equivalence check between two descriptions. The description language and its verifier are presented. The verifier exploits hierarchy and structural regularity, both of which are very important to achieve the goal of practical formal verification.

#### 1.4. Organization of the Dissertation

In Chapter 2, various aspects of design verification are introduced and the relationship between simulation and formal verification is explained. This is followed by a description of the concepts and terms needed in later chapters along with a definition of the verification problem addressed in this work.

Chapter 3 deals with the verification problem of finite-state machines. In this case, the problem is to check whether the implementation satisfies the given specification. The finite-state machine verification problem is defined and an efficient algorithm is presented. Experimental results are also presented.

Previous and related work is reviewed in Chapter 4. Because the study of formal approaches began earlier in the software domain than in hardware design, the most common techniques used in program specification and verification are described first, then existing formal hardware verification techniques are described. Finally, the problems and issues of these existing methods are addressed.

The behavioral description language used in this research is introduced in Chapter 5. The semantics of the language is based on a functional formalism. The primitive constructs are introduced with their semantics. In the language for data abstraction, three kinds of type constructing mechanisms are provided and parameterized designs may be defined as recursive cells. Also, some macro facilities are provided for the convenience of describing hardware.

The timing verification part of the behavioral verifier is presented in Chapter 6. After the timing constraints of synchronous digital systems are reviewed, the static-insensitizablepath problem is addressed. The timing model and the mechanism used for abstracting timing information are described. To illustrate the elimination of the static-insensitizable-path problem, some experimental results are provided.

Chapter 7 deals with the functional verification aspect of the behavioral verifier. Theorem provers utilized in existing hardware verification systems are reviewed and the theorem prover employed in the verification system implemented as part of this work is explained. Also, to illustrate the performance of the verification system, several verification examples are provided.

Conclusions and future research work in the formal verification field are included in Chapter 8.

### CHAPTER 2

## THE HARDWARE DESIGN VERIFICATION PROBLEM

#### 2.1. Introduction

When a hardware or software system is designed there is always the problem of determining whether the design behaves as the designer intended. In a software system design, the final product is a program or a package of programs and the reproduction of the final result is usually very easy and inexpensive. However, in hardware design, the final product is not as easy to implement and in general it is very expensive to build the first version. Therefore it is necessary to check the correctness of the design prior to fabrication so as to prevent costly errors and corrections at a later prototype debugging phase. This activity is called design verification, design test or design correctness checking and should be distinguished from product test. In a product test, the goal is to see if there has been any physical failure during the fabrication process (which should not occur if the fabrication process is perfect). However, since the manufacturing cycle is not perfect, each of the products should be tested before being brought to market. The number of manufactured devices is generally very large and the evaluation cost of each device is critical for the total cost of the product. Hence it is important to devise a set of test inputs which detect most of the probable errors incurred during fabrication, yet is small enough so that manufacturing costs are within a reasonable limit. On the other hand, the goal of a design test is to check the correctness of the design so that if the manufacturing process was perfect, the final product would be fault free; that is, it is also what the designer intended. The focus of this dissertation is the design test problem.

Early integrated circuit design was performed manually. Since the circuits involved were relatively small and simple, this approach was quite satisfactory. The first digital integrated circuits (IC's) were available commercially in the early 1960's; it was a number of years before computer-aids were applied to the design and verification of these circuits. In retrospect, it is surprising how little the computer has been used in the design of IC's. Early circuits were small enough that mask patterns could be drawn by hand, and then photographically reduced to generate the IC masks directly. For the verification of the function of the circuit, however, simulators proved very useful. Initial work in the mid-1960's thus focussed on the development of device analysis [6,7] and circuit analysis [8,9] techniques. The circuit simulators were originally developed for the analysis of nonlinear and radiation effects in discrete circuits. It was not until the early 1970's that circuit simulators suitable for IC analysis became generally available [10, 11, 12, 13, 14, 15]. As the digital hardware continued to become integrated into monolithic form and with increasing complexity, industry turned to the computer to store IC layout data and produce the masks required for manufacture. Systems for layout digitization and interactive correction found extensive use by the early 1970's. However, it was not until the mid-1970's that programs for the physical layout rule checking of the circuit began to find widespread use [16, 17]. By 1975 it had become clear that computer-aids were a necessity in the design of complex IC's, both for physical and for functional design and verification. Until then, the layout of an IC and its transistor-level schematic diagram had been quite separate. In the late 1970's, computer programs became available for tasks such as connectivity verification [18], extraction of transistor-level schematics from IC artwork data [19, 20, 21] and even extraction of gate-level schematics from the transistor list [22]. These programs are loosely coupled in general and are often incompatible with one another. It was not until the mid-1980's that much effort was invested in making the computer-aided design (CAD) systems integrated.

In this chapter, various aspects of design verification are introduced, and the relation between simulation and formal verification is explained. Finally, the concepts and terms needed in the sequel of the dissertation are described, along with a definition of the verification problem.

#### 2.2. Various Aspects of Design Verification

Throughout the process of designing VLSI circuits, a variety of different representations or *views* of the design are used. These representations may reflect a particular level of abstraction, such as a functional specification or mask layout, or they may reflect the view required for a certain application, such as the information required for simulation or formal verification. The choice of appropriate representations for each level of the design process is a key factor in determining the effectiveness of computer aids since it is through these representations that both the structure of the design and specific information relating to a particular design level are expressed. The design process involves transformations between these representations, both for design and verification. In this section, a classification of representations is presented. This classification is used in the later part of this section to relate various aspects of design verification.

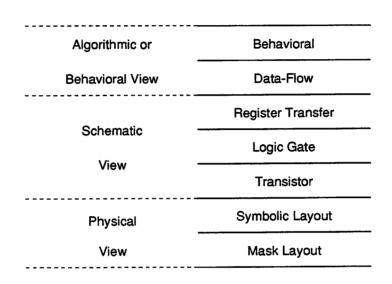

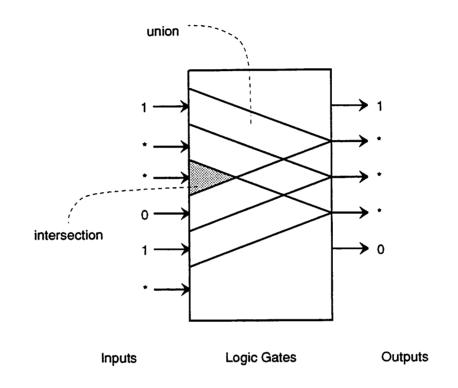

The major categories of design representations are shown in Figure 2.1 [23]. These representations fall into one of three major categories: behavioral, schematic, and physical. At the behavioral or algorithmic level, the functional intent of a design is described independent of a particular implementation. In some cases, programming languages such as concurrent Pascal [24] have been used to represent the design at this level, as well as to provide simulation capability. Languages specifically designed for this task, called *hardware description languages* (HDL's), have also been developed [25, 26, 27, 28].

Figure 2.1 Categories of design representation

Once a functional implementation strategy has been determined, a schematic view may be generated. At its most abstract level, this schematic view consists of a *chip plan*, illustrating the loose physical placement of the major components and busses, or a register transfer level (RTL) description, defining the functional relationships between the major components of the design. As the implementation is further refined, logic gate level and finally transistor level schematics may be generated. With each new level of refinement more information concerned with the detailed physical and functional implementation of the circuit is included in the description. The final transformation consists of the generation of detailed, mask-level geometries, from a transistor-level schematic view. The transition between high-level functional schematic descriptions and lower-level schematic and mask layout may involve the use of additional views. At the higher level, a data-flow description of the circuit may serve this purpose. At the behavioral level, this description may be viewed as the parse tree generated by a compiler operating on the algorithmic description of the intended function. At the RTL level, nodes in the data-flow graph represent an initial configuration of circuit building blocks used to implement the function, while branches indicate data paths between these functions. At the physical level, the symbolic layout forms a bridge between a schematic view of the circuit and its mask-level layout. A symbolic layout contains both explicit connectivity information and the relative placement of circuit components, such as transistors, cells, and building blocks.

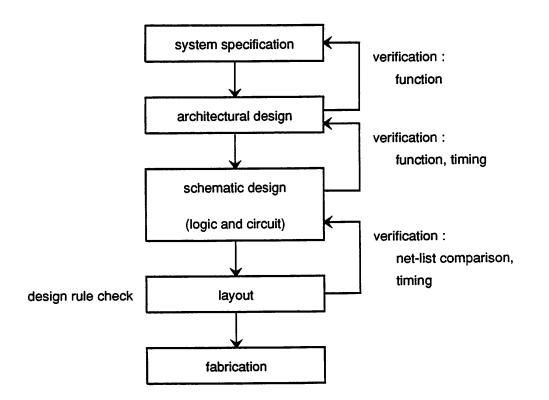

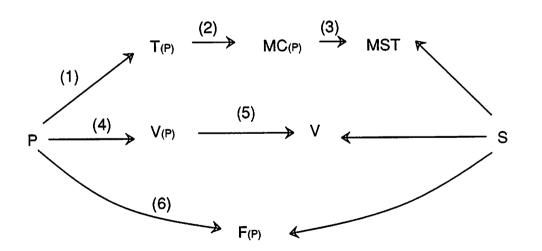

A typical, top-down design flow of a contemporary design system is illustrated in Figure 2.2. First, from the system specification the designer chooses an architecture. The architectural design is then refined to the logic and circuit level. Finally, a layout is generated from the schematics of logic and transistors. An ideal approach is to develop the design from the specification by a methodology that ensures that it cannot be incorrect. This approach serves the ultimate goal of CAD researchers, but requires codification of a great deal of knowledge about the design domain, from the most abstract levels of system description down to the most detailed levels of implementation. It potentially faces a astronomically large search space of design alternatives. In software design, the attempt to achieve *correctness-by-construction* is exemplified in the principles of a structured programming methodology [29] and in research into automatic or semi-automatic programming [30]. In hardware design, research has focussed on pieces of the problem that are the most tedious for a human designer and therefore prone to human error, such as wire routing or programmable logic array generation. There have been attempts at automatic design of entire integrated cir-

Figure 2.2 A typical VLSI design flow

cuits, including microprocessors that have met with varying degrees of success [32, 33]. However, these attempts are still in their infancy and truly general-purpose design synthesis systems will take many years to perfect. Until all the design processes are performed by automatic and error-free procedures, the verification of design work created by humans will continue to be an important problem. Different aspects of verification are required at different levels during the VLSI design process. The functionality is checked at the architectural level; functional and timing behavior are checked at the logic and circuit level; and

10

physical design rules and detailed timing behavior are checked at the layout level. Finally, as a functionality check, a net-list comparison can be performed.

The problems associated with "verification" can be classified into three categories: functional verification, timing verification, and physical verification. In functional verification, the goal is to show that a design correctly implements the specified function. The goal of timing verification is to show that a proposed design will not malfunction due to hazards, races, excessive delays, or other timing problems. Timing verification may not prove the functional correctness of a design, but it can show whether the design will operate within the timing specifications imposed on it. The problem in physical level verification is in showing that a proposed design conforms to a set of rules or restrictions. These rules may reflect physical limitations of the technology being used, or they may be intended to improve product reliability and maintainability.

#### 2.3. Simulation and Formal Verification

Simulation at various levels has been the most common verification method. The various levels of simulation used for integrated circuit simulation, their use, and examples of simulators for particular levels [34, 35] are listed in Table 2.1. The designer can select a simulator at the proper level depending on the stage of the design process, or may choose a *mixed-level* simulator that combines capabilities at two or more levels.

Circuit simulators, such as SPICE2 [15] and ASTAP [14], have been used successfully for the design and the performance evaluation of integrated circuits, and provide very accurate output waveforms. However, due to long computer run times, it is almost prohibitive to use these simulators for the analysis of large integrated circuits. An extensive effort has been made to reduce the required CPU-time for large circuits, while maintaining the same

| Level      | Use                                          | Simulator Examples        |

|------------|----------------------------------------------|---------------------------|

| Behavioral | Algorithmic Verification                     | GASP, SIMULA, ISPS, ADLIB |

| RTL        | Logic Verification                           | ISPS, ADLIB, SPLICE2      |

| Logic      | Logic Verification                           | LOGIS, ILOGS, SPLICE2     |

| Switch     | Logic Verification                           | MOSSIM, RSIM              |

| Circuit    | Performance Evaluation<br>Logic Verification | SPICE2, ASTAP, SPLICE2    |

| Device     | Device Model Development                     | GEMINI, PISCES            |

| Process    | Process Development                          | SUPREM, SAMPLE            |

Table 2.1 Hierarchy of large integrated circuit simulation

waveform accuracy. Techniques include the use of relaxation methods, such as Iterated Timing Analysis (ITA) [35, 36, 37] and Waveform Relaxation (WR) [38, 39, 40]. Relaxation methods provide significant speed improvement with the same waveform accuracy as SPICE2 (assuming identical device models) and have guaranteed convergence and stability properties. However, relaxation-based electrical simulation is still much slower than logic simulation and the actual CPU-time required depends on the characteristics of the circuit under analysis.

Logic simulation is an area which has evolved over the last two decades. Since the logic circuits of interest were already large and computers were less powerful, even the early work was concerned with efficiency improvement techniques (e.g. [41,42]). Since then, continuous progress has been made towards the simulation of very large circuits [43,44,45,46,47]. Both temporal and structural sparsity is exploited in these techniques. Due to the occurrence of new complex MOS transistor designs, which cannot easily be cast into standard logic gates, transistor level simulation [48,49] has emerged as an alternative. Also, a new form of simulation technique has been developed which solves for the amount of time required for a network variable to make a particular change, rather than solving for the network variables at the given time point (as in conventional circuit simulation) [50].

Recently, to simulate the behavior of a system across several abstraction levels in one simulator, so-called *mixed-level* simulation techniques have been developed [51,52,53,24,54,55,56,57]. In a mixed system, models of more than one abstraction level are used, such as circuit analysis, simplified macromodels, and logic simulation. Numerous mixed-mode and/or multilevel systems include several simulation analysis levels, combining many of the techniques developed for each level.

Simulation has been used for hardware design verification for so long that for many people verification means simulation. It remains true that simulation is still the best known way of answering the question "is my high-level description actually what I want?" However, simulation has several limitations for verifying the correctness of a design process. As a system increases in size and complexity, simulating the system is very costly in both space and time. The second limitation is that selecting a sufficient set of test inputs to "cover" a sequential description is almost impossible. In all but the simplest systems, the space of possible inputs can be vast. For example, a simple multiplier that multiplies two 16-bit integers can require over four billion different inputs to be sure it simulates correctly, and a system that contains a single 32-bit register can potentially have over four billion different responses to each input, depending on previous input sequences. Clearly, we cannot hope to test a system on every possible input with every possible system state. Rather, a subset of these tests must be selected, from which we can extrapolate or otherwise conclude the correctness of the design. Fortunately, the number of test inputs needed grows linearly with the number of components in the system. Unfortunately, the task of finding them is known to be NPcomplete [58]. Therefore, simulation alone cannot guarantee that complete verification has been achieved unless exhaustive simulation has been performed. Here the meaning of the term "complete verification" is that when a verification result is positive, it is guaranteed that a design operates correctly with all possible tests in the input domain. Finally, even if exhaustive simulation were feasible, the interpretation of the simulation output is not easy. Because of these difficulties, there is a need for new verification techniques to supplement the traditional simulation-based approach to design verification.

An important new approach that has emerged in the last decade is formal verification [59, 60, 61, 62, 63, 64, 65, 66, 67, 68, 69, 70, 71, 72, 73, 74, 75, 76, 77, 78, 79, 80, 81, 82, 83, 84]. In formal verification, both a design and its specification are described by a language in which semantics are based on mathematical rigor, and the verification is then performed using symbolic manipulations. This guarantees complete verification when the verification result is positive. When a formal description is used during the complete design process, numerous advantages can be seen. For example the description of the actual behavior of an existing VLSI circuit or specification of the intended behavior of a circuit to be designed is generally performed informally, usually by means of natural language sentences or timing diagrams. By formally specifying the required behavior of a design, it becomes possible to communicate these requirements unambiguously to the people who will implement the specification, while providing a precise statement of design requirements. The ability to describe behavior formally in a design language allows the correspondence between specified behavior and the behavior of the constructed design to be established. As the primary aim in any design exercise is to produce an implementation that satisfies the behavioral specification, the importance of behavioral description is evident.

The use of behavior in a design language has not been fully explored to date. The advent of hierarchical designs requires the rigorous description of both the structure and the behavior of design components at the various intermediate stages in the evolution of a complete design. The manipulation of the large amounts of descriptive data requires that some of the well-established techniques found in programming languages be used to aid the design process. The use of behavioral description "languages" (whether they be graphical, textual, a combination of the two forms, or a data structure) as the medium in which a designer will work will increase steadily in the future, due to the ever-increasing complexity of VLSI designs.

Large designs are usually produced in segments, with some parts of the design being produced by hand and others being produced using design automation tools. An interface between the components must be specified; this can most naturally be done using a design language which supports the description of structural, geometrical and behavioral attributes. Input to design automation systems will require behavioral information if designers are to work at a higher and more abstract level of design than that of pure structure or geometry. Most design automation systems, such as automatic placement and routing programs, work in the structural or geometrical domains. However, abstract behavioral descriptions are being used as input by an emerging number of true silicon compilers [85, 86, 87].

Finally, the most significant reason for including behavioral description capabilities in a language is for automatic design verification. Verification techniques using simulation do not generally make use of behavioral description languages, as they restrict themselves to describing circuits at a single level of representation such as the circuit level of SPICE2 [84], or the switch level of MOSSIM [48] and RSIM [88]. Simulation then occurs monolithically over the complete device description after the design is complete, with the inherent problems of descriptive complexity and redesign effort when flaws are discovered. An integrated design and verification process allowing increasingly detailed descriptions of an evolving top-down design to be verified by simulation or verified by mathematical proof techniques, breaks both the design and verification tasks into manageable sub-tasks. This approach

requires a behavioral description language in which behavior is described at different levels of abstraction, from the interaction among functional blocks down to the behavior of primitive cells. This approach is explained in more detail in the following section.

#### 2.4. Hierarchy and Three Classes of Hardware Modules

Hierarchical techniques are frequently applied in managing complex technical and organizational problems. It is the purpose of such hierarchical techniques to master complexity by decomposing a complex system into a hierarchy of sub-modules. For a proper appreciation of the merits of hierarchical techniques, it is essential to have an understanding of the nature of complexity. Hierarchy applied to VLSI design will not generally lead to a reduction of the number of components in the chip -- on the contrary, there are several reasons to expect the number of components to increase. It can, however, affect the number of interactions between components which must be taken into account (by abstracting the interfaces between components), as well as the number of configurations to be considered during design. These latter aspects are also a measure of system complexity and are known to be dominant in the design of large systems [89, 90]. Hierarchy is designed to reduce the magnitude of these contributions to complexity by using appropriate decomposition techniques. The intuitive notion is straightforward. One decomposes a large problem into a number of smaller parts and while each of the parts can be expected to exhibit only limited complexity, it is the expectation that the integration of the parts will not lead to a significant increase in overall complexity. Hierarchical decomposition techniques have long been in use for IC design supported by CAD tools. Many of these were devised for obtaining a reduction of the amount of design data; they did not intend to provide nor did they achieve a reduction of design complexity as measured by CAD program run times. Apparently, hierarchical decomposition alone is not sufficient for reducing system complexity. Upon developing an understanding of the nature of complexity, it follows that abstraction methods form an essential ingredient.

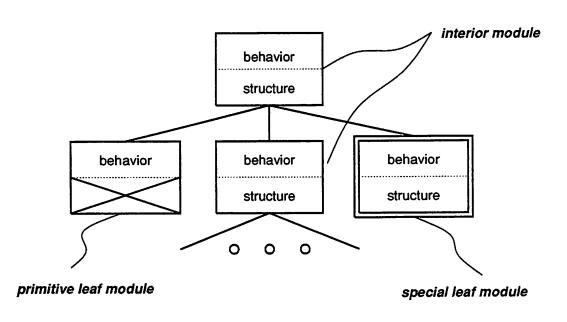

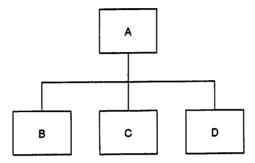

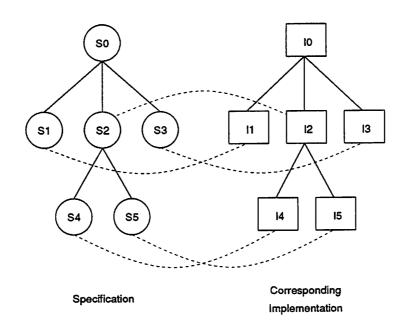

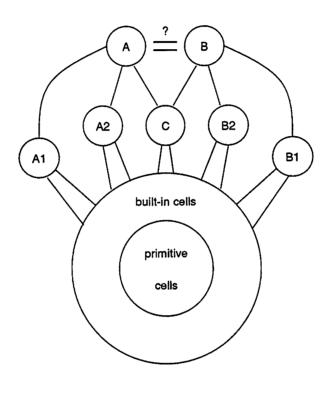

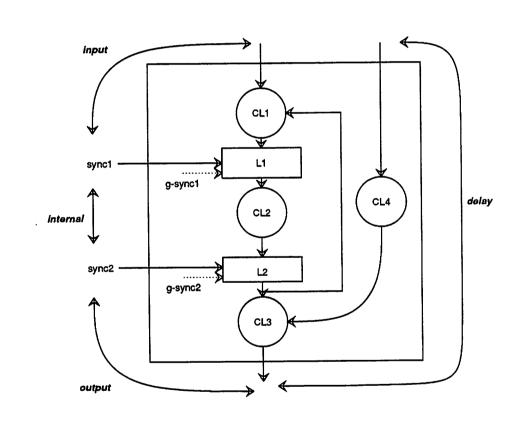

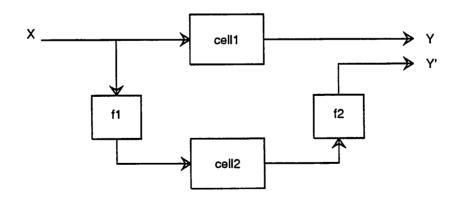

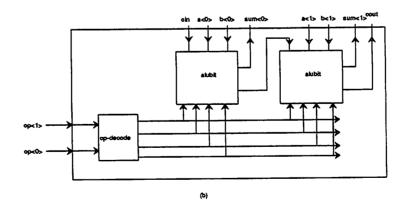

In a hierarchical approach, a hardware module consists of a behavioral specification part and a structural implementation part. A behavioral specification describes how a particular design responds to a given input, and a structural representation describes how components are interconnected. According to how a hardware module is composed, modules can be classified as interior modules and leaf modules. The leaf modules can be further classified into primitive leaf modules and special leaf modules. These modules are illustrated in Figure 2.3. In a primitive leaf module, the structural part does not exist, and therefore does not need to be verified. The special leaf module consists of a behavioral part and a structural part, but its structure does not use any other module and is given as a set of net-lists of elementary parts. The net-lists are obtained using an extraction program, or are given as the results of several stages of the synthesis process. In an interior module, the structural part uses some number of submodules, each of which is either a primitive leaf module or a special leaf module or another interior module. For example, when a full-adder is given as a top level module, the Boolean gates may become primitive leaf modules. Or when a microprocessor is given as a top level module, the control path of the module can be a special leaf module and the logic blocks for data path can be interior modules. For the verification of a partially designed system, a designer may declare proper modules as primitive leaf modules. Later, when the design is implemented by refining the specification of the primitive leaf module, the module can be verified as a top level interior module.

From the verification point of view, a special leaf module can be treated as an interior module whose structural part consists of primitive gates and latches. However, the

Figure 2.3 Three classes of hardware modules

verification approach for interior modules may be impractical for some leaf modules.

#### 2.5. Verification Problem

In general, design verification problems can be classified into two categories. One category is correctness checking [65,91], the other equivalence checking [74,82]. In correctness checking, the verifier checks to see if the structural implementation implies the behavioral specification. Usually there is more than one way to implement a given behavioral specification and the implemented result may have more detail than the specification. Hence even if there were no errors involved during the design process, the

implementation may not be equivalent to the specification; however, the implementation may satisfy all the requirements of the specification. Thus a correctness checker verifies that the implementation implies the specification, i.e., the sufficiency is checked. On the other hand, an equivalence checker verifies that the two descriptions are functionally equivalent. In equivalence checking, two implementations are usually checked to see if they are equivalent. However, if the description language allows that specifications and implementations are described by the same language, the equivalence check between a specification and an implementation can also be performed. (Note that each of the correctness and equivalence checkers may verify functionality only or may verify the combined behavior of function and timing).

In this research, the objective is to develop a verification system with two verifiers: one is a practical correctness checker for special leaf modules of finite state machines and the other is an equivalence checker for interior modules. The correctness checker has been implemented using an implicit enumeration method while the equivalence checker has been implemented using formal verification techniques with the combined behavior of function and timing checked. In functional verification, the target level still uses a discrete Boolean form for signal values -- continuous circuit-level variables are not supported. In timing verification, synchronous digital design is assumed here.

### **CHAPTER 3**

### FINITE-STATE MACHINE VERIFICATION

#### 3.1. Introduction

In hierarchical design, consistency between representations of a design at different levels of abstraction must be maintained throughout the design process if the designer is to be sure of a correct implementation. In this chapter, the correctness checking problem of a finite-state machine is considered. The verification problem of finite-state machines has been dealt with in a few different contexts [91,92,93,94,95]. In the temporal logic approach [91,92], the specification is described by temporal logic formulae and the implementation is represented as a state transition graph. The verification problem is determining if the state transition graph is a model of the temporal logic formula. In the symbolic approach [93], the verification problem involves deciding whether two logic-level sequential circuits with differing numbers of latches are functionally equivalent by using a symbolic comparison. However, due to the intractability of the problem, the formal approaches taken thus far have been restricted to medium-sized circuits with few memory elements (4 - 6 latches). In [94], a finite-state circuit model based on coordinating finite-state machines is proposed. In this approach, the circuit analysis task consists of determining whether or not the circuit model performs a given task by proving that a smaller derived finite-state system performs a derived task. Recently, an algorithm for verifying the equivalence of two sequential machines was presented [95]. In [95], a specification state transition graph is extracted from a registertransfer level description and an implementation state transition graph is extracted from netlists of gates and latches. Then a graph multiplication method is used to check the equivalence. From a practical point of view the approach in [95] is one of the most promising among the finite-state machine verifiers in terms of speed, and it will be used for comparison in the experimental section of this chapter. In [95], some practical-sized circuits could be verified with reasonable cpu-times. However, the verifier of [95] requires every Mealy machine to be converted to a Moore machine (which will usually have a much larger number of states and transition edges than the original Mealy machine). The verifier presented in this chapter outperforms the aforementioned approach by an order of magnitude in speed for Moore machines, and even better performance improvements are obtained for Mealy machines.

In the study of machine identification and fault detection experiments [96,97], it is necessary that a machine described by a state transition table must be strongly connected (i.e., for every pair of states, an input sequence must exist which transfers from one state to the other), must be minimal (i.e., contains no redundant states), and must have a *distinguishing sequence* (i.e., for every distinct state pair, an input sequence must exist which produces different output) [97]. However, the specification machine generally does not have all those properties and thus it is not always possible to devise a test sequence to verify the correctness of an implementation machine.

In this chapter, an efficient algorithm for the verification of finite-state machines is presented based on the concept of machine cover [96,97]. Definitions of terms and notation are given in Section 3.2, and the verification problem dealt with in this chapter is given in Section 3.3. In Section 3.4, the algorithms used to check the correctness of finite-state machines are described along with implementation details. In Section 3.5, the verifier is evaluated with some examples and the experimental results are discussed, conclusions are

given in the last section.

#### 3.2. Definitions and Notation

In this chapter, standard terms and notation are used (e.g. [96, 97, 98]). However, a number of definitions are included here for completeness.

#### Definition 1 (cube and minterm) :

In an n-dimensional Boolean space, any set of vertices can be represented in sum-ofproduct form. Each product terms is called a *cube*. In a cube notation, each variable takes one of three values: 0, 1, or \*. The *don't-care* (DC) value "\*" means that a variable can take either of the values 0 (OFF) or 1 (ON). When a cube represents only one input combination of 1's and 0's, this special cube is called a *minterm*. In general, the number of minterms in a cube is given by  $2^x$ , where x is the number of variables whose value is \*.

Definition 2 (ON-set, OFF-set, DC-set, ON-set cover, and OFF-set cover) :

The ON-set (OFF-set) of a single-output logic function is defined as a set of minterms which evaluate the logic function to ON (OFF), and the DC-set is defined as a set of minterms for which the logic function can take either value of ON or OFF. The ON-set cover (OFF-set cover) of a logic function is a set of cubes that cover all the minterms of the ON-set (OFF-set). In general, the number of cube elements used in a ON-set cover (OFF-set cover) is not unique.

#### Definition 3 (completely specified and incompletely specified function) :

When the DC-set of a logic function is empty, the logic function is called *completely specified*, otherwise, the function is said to be *incompletely specified*. Note that when the logic is given by a net-list of primitive gates, as is the case in this chapter, each of the min-

terms evaluates to 1 or 0. That is, when the logic function is given by an implemented circuit, the logic function is completely specified.

Definition 4 (finite-state machine) :

A finite-state machine is a system that can be characterized by a quintuple

$$M = (\Sigma, S, Z, NSF, OF)$$

(2.1)

| where | Σ   | = | finite nonempty set of input symbols                            |

|-------|-----|---|-----------------------------------------------------------------|

|       | S   | = | finite nonempty set of states                                   |

|       | Ζ   | = | finite nonempty set of output symbols                           |

|       | NSF | = | next-state function, which maps $S \times \Sigma \rightarrow S$ |

|       | OF  | = | output function, which maps $S \times \Sigma \rightarrow Z$     |

The above definition of finite-state machine is referred to as a Mealy machine [97]. The other type of finite-state machine is a Moore machine [97]. In a Moore machine the output function OF depends only on the state space S. Note that a Mealy machine is more general in the sense that any Moore machine can be converted into a Mealy machine without increasing the number of states and transition edges.

## Definition 5 (incompletely specified machine) :

In equivalence checking, two machines are usually specified by structural descriptions, such as net-lists of gates and latches. In this case, the next-state function NSF is defined for all the states in the domain of S of Eqn. (1.1), and NSF is a completely specified function. However, in a hierarchical verification paradigm, the specification is given by a behavioral description -- in case of finite-state machine, the description is usually an equivalent form of a state transition table. And if a designer does not specify a next-state or output entry when it normally would be specified, it is usually because the machine is not expected to enter that next-state condition. Since the designer does not care what the next-state or output is, it could be specified as any valid next-state or output. In fact, it could be specified differently under

different machine conditions. Thus, it is reasonable to let an unspecified state transition table entry assume as many different values as desired. Such a machine is called an *incompletely specified machine*.

### Definition 6 (applicable input sequence) :

Whenever a state transition is unspecified, the behavior of the machine may become unpredictable. In order to avoid such a situation it is assumed that the input sequences applied to the machine, when in any of its possible states, are such that no unspecified next state is encountered. Such an input sequence is said to be *applicable* to the state s of a machine.

### Definition 7 (state cover and machine cover) :

A state q of a machine  $M_Q$  is said to *cover* a state s of another machine  $M_S$  if, and only if, every input sequence applicable to s is also applicable to q, and its application to both  $M_Q$ and  $M_S$  when they are initially in q and s, respectively, results in identical output sequences whenever the outputs of  $M_S$  are specified. The covering concept can be extended to machines as follows : a machine  $M_Q$  is said to cover a machine  $M_S$  if, and only if, for every state s in  $M_S$ , there is a corresponding state q in  $M_Q$  such that q covers s. Thus when a machine  $M_Q$ covers a machine  $M_S$ , for any state in  $M_S$ , there is a state in  $M_Q$  which can not be distinguished by input-output behavior.

### 3.3. Problem Formulation of Finite-State Machine Verification

The meaning of verification in this chapter is as follows: Given a specification and its implementation, the verifier checks the correctness of the design with respect to the specification. If the implementation satisfies the specification, the design is correct. Otherwise, the design is incorrect.

In this chapter, it is assumed that the specification is described by a state transition table and the implementation is given as a net-list of gates and latches. The specification machine will be denoted by  $M_S$ , and the implementation machine by  $M_Q$ . Also, a state of a specification machine will be denoted by s and a state of an implementation machine by q. The design verification problem is defined as a checking if implemented machine  $M_Q$  covers the specification machine  $M_S$ .

## 3.4. Verification Algorithm

The number of states of a finite-state machine grows exponentially with the number of latches in the implementation machine. However, for large machines the number of states actually visited, given the input sequences, is typically a small fraction of the total number of possible states. This is especially true if a state assignment program such as KISS [99] has been used in the synthesis process, where a minimum amount of combinational logic is the target and this may or may not produce a minimum bit encoding of the states. Since the encoding information is generally not available for verification purposes, to deal with general problems it must be assumed that the state encoding information is not available.

As previously mentioned, the number of latches is not minimal and the number of states that the implementation machine can take is much greater than that of the specification machine. There are  $2^{l}$  possible states in a machine with l latches. From these states, a set of candidate states is selected. The procedure involved in selecting these candidates will be explained shortly. From the set of candidates, a state  $q_0$  is arbitrarily chosen. A check is performed to see if the chosen state covers the initial state of the specification machine. This process is repeated until the correct initial state is found. If all the candidates fail to cover the initial state of the specification machine, it is concluded that the implementation is not correct. This checking procedure is referred to in this chapter as state generation and output checking and it is described later in this section. The high-level pseudo-code of the main procedure is shown below. Of course, in the worst-case, this process has complexity of  $O(2^l \times 2^m)$ , where *l* is the number of latches and *m* is the maximum among the numbers of don't-care variables in the primary input segments of state transition edges of  $M_S$ . However, the selection and search procedures described later in this chapter result in much better performance. This is illustrated by the results obtained for real examples, as shown in Section 3.5.

```

main()

ł

/* read in specification machine M_S */

read_spec_machine( );

/* read in implementation machine M_Q */

read_impl_ckt( );

/* levelize the circuit of M_Q and find transitive fan-ins

for each output variable */

levelize_ckt( );

conify_ckt();

/* find all the candidate initial states of M_Q */

Q_0 = \text{enumerate}_q 0();

/* main loop */

foreach (q_0 \text{ in the set } Q_0) {

/* initialize */

add s_0 to the set to be covered by q_0;

if (generate(s_0, q_0) fails ) {

design is incorrect;

/* prepare for the next candidate q_0 */

re-initialize;

}

else

design is correct, exit the main loop;

}

```

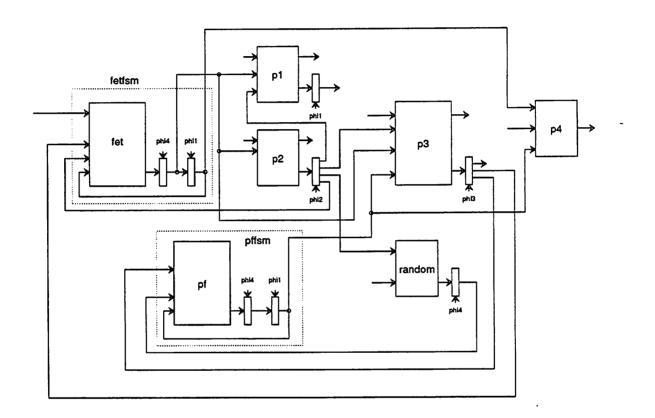

In procedure read\_spec\_machine(), the verifier builds up the state transition graph. The input format is shown in Figure 3.1. In the input format, the first field is an input segment of a transition edge, the second is a present state name, the third is the next state name, and the fourth is the output segment associated with the given inputs for the transition edge. The procedure read\_impl\_ckt() reads in the net-list of logic elements. The current implementation can deal with the primitive gates listed in Table 3.1. After reading in the implementation circuit, the verifier levelizes the circuit in topological order for the fast event-driven simulation used in

name traffic

}

# Highway and Farm road Traffic Light Controller

# (ref. Introduction to VLSI Systems, Mead and Conway, p.87)

| #input | p-state | n-state | output |

|--------|---------|---------|--------|

| 0**    | HG      | HG      | 00010  |

| *0*    | HG      | HG      | 00010  |

| 11*    | HG      | HY      | 10010  |

| **0    | HY      | HY      | 00110  |

| **1    | HY      | FG      | 10110  |

| 10*    | FG      | FG      | 01000  |

| 0**    | FG      | FY      | 11000  |

| *1*    | FG      | FY      | 11000  |

| **0    | FY      | FY      | 01001  |

| **1    | FY      | HG      | 11001  |

#end

Figure 3.1 Input format of a specification machine

| gate name  | description                           |  |  |

|------------|---------------------------------------|--|--|

| AND        | logical and                           |  |  |

| NAND       | negation of and                       |  |  |

| OR         | logical or                            |  |  |

| NOR        | negation of or                        |  |  |

| INVERTER   | logical not                           |  |  |

| XOR        | logical exclusive or                  |  |  |

| XNOR (EQV) | logical equivalence (negation of xor) |  |  |

| Table | 3.1 | Primitive | gates |

|-------|-----|-----------|-------|

|-------|-----|-----------|-------|

later stages of the verification. Also, for each of the output variables, a set of input variables is found which affects the value of the output variable. The input variables thus obtained are called the transitive fan-ins of each of the output variables. The procedures of enumerate\_q0() and generate() are explained in the following subsections.

# 3.4.1. Enumeration of Candidate Initial States

The goal of the enumeration process is to determine all the candidate initial states in the state space of the implementation machine. The procedure of the enumeration of candidate initial states begins with finding a set of output variables which have the same values for all the transitions from the starting state  $s_0$  of the specification machine  $M_s$ . In the next step, for each of these output variables, enumerate from the input space the ON-set cover when the logic value of the output variable is 1 and OFF-set cover when the logic value is 0. The covering set is denoted as  $cube - set_j$ , j = 1, ..., k, where k is the number of output variables which produce the same known output values. In the final step, take the intersection of the latch part of the cube-sets as follows:

```

cube-set_1 \cap cube-set_2 \cdots \cap cube-set_k

```

Then the initial state of the implementation machine should be a member of this set. Note that if none of these candidate initial states covers the initial state of the specification machine, it is concluded that the implementation is incorrect. The algorithm for enumeration of candidate initial states is as follows:

enumerate\_q0(s<sub>0</sub>)

{

/\* initialize the result \*/

set of candidates = UNIVERSE;

}

/\* find output variables which produce the same value for all the

transitions from the starting state of the specification machine M<sub>S</sub> \*/

O = find\_output\_vars( s<sub>0</sub> );

```

/* enumerate the ON-set or OFF-set from the implementation

machine M<sub>Q</sub> and take their intersection */

foreach (output_variable in O) {

```

```

if (output_value = 0) {

/* find OFF-set cover */

S = podem(output_variable, 0);

set_of_candidates = set_of_candidates \cap (latch part of S);

}

else {

/* find ON-set cover */

S = podem(output_variable, 1);

set_of_candidates = set_of_candidates \bigcap (latch part of S);

}

}

/* when there is no candidate state in the implementation

machine, don't waste time */

if (set_of_candidate = \phi) {

the implementation is inconsistent;

exit();

}

else

return( set_of_candidates );

```

The worst case complexity of the above algorithm is  $O(N_{PO} \times COMPLEXITY_{PODEM})$ , where  $N_{PO}$  is the number of primary outputs and  $COMPLEXITY_{PODEM}$  is the complexity of PODEM (path-oriented decision making) method [100]. The PODEM method is used to enumerate the set of cubes in the input space. In PODEM, given an objective, a signal and the desired value on the signal, a procedure called *back trace* traces a path from the signal backwards to a primary input to obtain a primary input assignment. The primary input assignment is then propagated to see if the desired value at the objective signal has been set up. If the objective signal has been properly set up, the procedure terminates. If an opposite value is set up, the procedure backtracks; that is, the previous primary input assignment is ripped up and the opposite value is assigned to that primary input. If the signal remains unspecified, the whole process is repeated. The above procedure continues until either a successful primary input assignment is found or all the primary input assignments have been exhausted. The-process is an implicit enumeration algorithm in that all possible primary input patterns are implicitly, but exhaustively, examined.

To show the enumeration process, a simple example is given as follows:

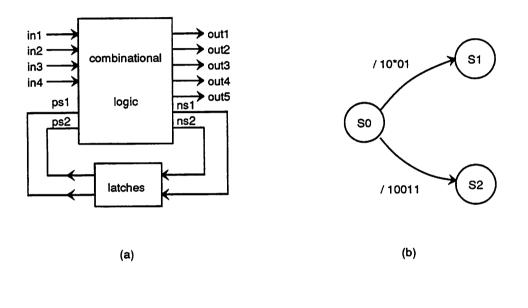

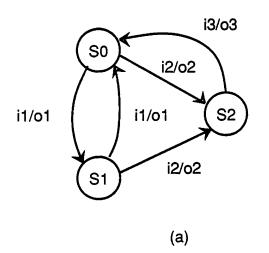

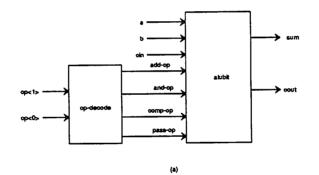

*Example* : Consider the sequential circuit shown in Figure 3.2(a). It consists of four primary inputs, five primary outputs, and two latches. The partial state transition diagram is also shown in Figure 3.2(b). There are two outgoing edges from the initial state  $s_0$ . In the diagram only the output parts are shown for each transition edge. The output variables out1, out2, and out5 are consistent in their values for the two edges. Assume that the ON-set cover of out1, the OFF-set cover of out2, and the ON-set cover of out5 are given as follows :

$$cube -set_1 = (1 1 * 0 1 *)$$

$$cube -set_2 = (1 1 0 0 1 *)$$

$$cube -set_5 = (* 1 0 0 1 0)$$

Figure 3.2 (a) a sequential circuit example (b) state transition diagram

The intersection of the latch part is  $(1 \ 0)$ , and there is only one possible candidate initial state in this particular case. Generally, however, each of the cube-sets may consist of many cubes and the intersection of the latch part would consist of many cubes. For example, if  $(* \ 1 \ 0 \ 0 \ 1^*)$  was obtained instead of  $(* \ 1 \ 0 \ 0 \ 1 \ 0)$  in *cube-set*<sub>5</sub>, then the intersection would be  $(1 \ *)$ , and there would be two candidate initial states,  $(1 \ 0)$  and  $(1 \ 1)$ .

Note that if any don't-care values are among the variables of the latch part, all the possible minterms should be included in the set of candidate initial states. As will be demonstrated in the experimental results section, when an incorrect initial state is tried the verifier notices the error so early in its checking process that the total cpu-time spent for wrong initial states is only a small fraction of total run time for most examples.

### 3.4.2. State Generation and Output Checking

In this subsection the algorithm of checking if a given state q of the implementation machine covers a state s of the specification machine is described.

Since the implementation machine is given by a logic circuit, it is completely specified thus every input sequence is applicable to a state q. Thus to check if a state q in the implementation machine covers a state s of the specification machine, it is sufficient to check if every input sequence applicable to s when applied to both machines results in identical output sequences whenever the outputs of the specification machine are specified. The basic strategy employed in this work is as follows : for each applicable input at the given state s of  $M_S$ , obtain the next state and the output by simulation on the machine  $M_Q$ . Check if the output of  $M_Q$  implies the corresponding output of  $M_S$ . When the value of the output variable of the specification machine is don't-care, the value of the output of  $M_Q$  can have any value. This checking is referred to as output checking. If the output checking fails, the input becomes a component of the sequence of a counter-example. It is then concluded that the given state q does not cover the specification state s. If the output checking succeeds, see if the next state  $q_n$  has already been generated. If it is a newly-generated state, call the same procedure with the state pair  $(s_n, q_n)$  recursively, where  $s_n$  is the next state of s in  $M_S$ . If  $q_n$ was generated earlier, then check if  $q_n$  covers  $s_n$  by referring to the covering set of the state  $q_n$ . If  $s_n$  is in the covering set of  $q_n$ , there is no more work to do. If  $s_n$  is not in the list, repeat the above procedure with the state pair  $(s_n, q_n)$ .

### 3.4.2.1. Example

Before the explanation of the detailed algorithm, a simple example is used to illustrate the state generation process.

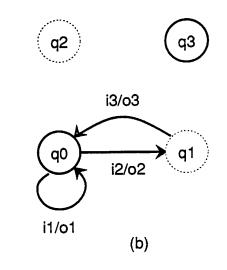

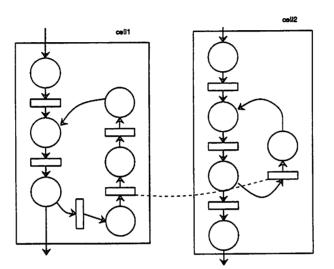

In Figure 3.3, the specification machine is given as an unoptimized machine and the implementation machine as an optimized one. The specification machine consists of three states with five edges. Assume that the implementation has two latches and among the four possible states, two states  $q_0$  and  $q_3$  are enumerated as candidate initial states as illustrated in Figure 3.3(b). The state  $q_0$  is chosen arbitrarily, and a check is performed to see if state  $q_0$ covers the state  $s_0$ . Figure 3.3(c) shows the recursive execution tree with each of the arguments, and Figure 3.3(d) shows the evolution of the covering list. First, the state  $s_0$  is added to the covering list of  $q_0$  (the stage of the evolution of the covering list is at (1) in Figure 3.3(d)). The outgoing edge with input i 1 is simulated on the implementation machine. The next state of implementation is  $q_0$ , which has already been generated. The next state of the specification machine,  $s_1$ , is not in the covering list and is therefore added to the covering list of  $q_0$  (at (2) in Figure 3.3(d)). Now a check is performed to see if state  $s_1$  is covered by state  $q_0$ . When the edge with input i 1 is tried, the next state pair  $(s_0, q_0)$  is obtained. Since the state  $s_0$  is in the covering list of the state  $q_0$ , the check finishes with success (the dotted line means that the check is performed by referring to the covering list). The next edge with input i 2 is tried. A new state  $q_1$  is generated and the state  $s_2$  is added to the covering list of the state  $q_1$  (at (3) in Figure 3.3(d)). The only remaining edge from  $s_0$  with input i 3 leads to state pair  $(s_0, q_0)$  which is checked by examining the covering list. Finally, the only remaining edge from  $s_0$  with input i 2 is checked. Note that the total number of simulations used for this check is five, which is the same as the number of edges in the specification machine.

(C)

(d)

Figure 3.3 Unoptimized specification vs. optimized implementation example

(a) specification machine

(b) implementation machine

(c) execution tree

(d) evolution of covering list

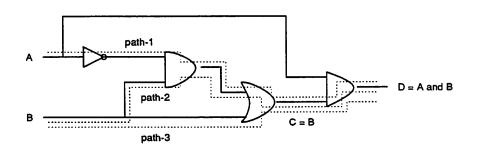

# 3.4.2.2. Cube Simulation and Cube Splitting

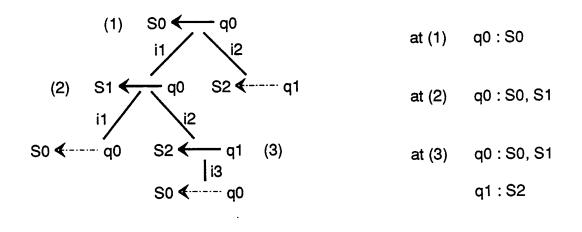

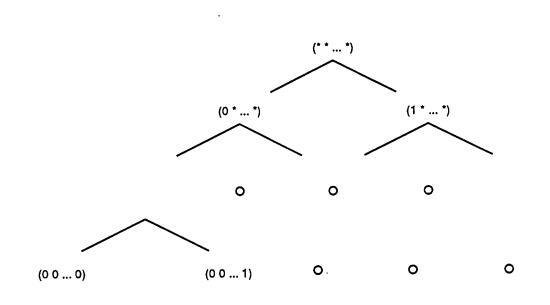

Since the input can take on one of the three values (0, 1, and \*), the term simulation here means three-valued logic simulation [101]. A simulation pass refers to simulation with one input vector. A simulation pass is said to be complete if the outputs of the simulated circuit (after simulation), are known (i.e. 0 or 1). Otherwise, it is incomplete. When the input vector is a minterm, the simulation pass is called minterm simulation, otherwise, it is called cube simulation. Minterm simulation is always complete because all the inputs are specified as 1's or 0's. Cube simulation may be either complete or incomplete; in the latter case, to make the simulation complete, unknowns in the input vector shall be assigned known values, 0 and 1 at different times. This assignment can be performed for one unknown at a time until the simulation becomes complete. Finding out if the simulation has become complete also requires a simulation pass and many passes may be required before the simulation eventually becomes complete. Because the input vector is a cube, the assignment process can be considered cube splitting -- every time an unknown is assigned certain values, the cube is split into two smaller cubes. So, instead of value assignment, cube splitting is considered to make the simulation complete. The cube splitting process can be depicted by a tree structure as shown in Figure 3.4. At the first level, the first unknown variable is split and this procedure is repeated similarly. Which unknown to select at each level is important because a good split order may prevent the tree from growing into its full magnitude ( $O(2^m)$  complexity, where m is the number of unknowns). At each node, the next unknown to be split is selected using the heuristics explained in the next section. The deeper the eventual cube-split, the more simulation passes that are needed.

Figure 3.4 Tree structure of cube splitting

### 3.4.2.3. Cube Splitting Heuristics

Rather than choosing the unknown variables from the inputs in an arbitrary order (leftto-right in the example of Figure 3.4), input variables which have a high probability of resolving the unknown outputs are selected. Figure 3.5 illustrates the heuristics. First, for each of the unknown simulation output variables, find the set of primary input variables which may affect the output, then obtain the intersection and union of these sets. As mentioned in the algorithm of the main procedure, the implementation circuit is segmented as a cone circuit for each output variable [101]. The unknown input variables are then chosen from the intersection first, and from the union second, to split the cube. This process is

Figure 3.5 Ordering heuristics of split variables

repeated until all the output variables become known. This heuristic may avoid some useless cube splitting. For example, the last input variable in Figure 3.5 does not need to be considered in this case.

# 3.4.2.4. Output Checking

When the implementation circuit is simulated with a primary input vector and the present state vector, the present state vector contains no unknowns while the primary input

vector may have many unknowns. As explained in Section 4.2.2, both the next state outputs and primary outputs may have unknown values. In the case of next state variables, all the unknowns must be resolved by input space cube-splitting. However, in the case of primary output variables, the unknowns need only be resolved when the corresponding specification output variables are known. For example, with the specification output  $(1 \ 0 \ * \ 0 \ 1)$ , and simulated output  $(1 \ 0 \ 1 \ * \ 1)$ , only the fifth output variable must be resolved.

## 3.4.2.5. Detailed Algorithms

The procedure generate() and procedure check\_state() return *success* if the given state of the implementation machine covers the state of the specification machine, otherwise they return *fail*. The only difference between the procedure generate() and check\_state() is that when state q has been generated already, to check the covering, the procedure check\_state() refers to the covering list first then checks each of the outgoing edges. If the state s is in the list, the state s is assumed to be covered by the state q. The actual covering check will be performed when all the previous calls of generate() and check\_state() procedures return to the point where the state q was first generated. The procedure simulate() returns the information about completeness of cube simulations. The procedure performs the three-valued logic simulation using an event-driven technique [42] with topological-ordered [102] level information. If there are any unknown values in the next-state variables, procedure split\_simulate() is called, this splits the cube by assigning values to unknown input variables using the heuristics explained above. The procedure split\_simulate() calls itself recursively until all the next-state variables are resolved. The detailed algorithm of the state generation process is as follows:

```

{

foreach (applicable input at s) {

/* get the next-state q_n of q and primary output by simulation */

if (simulate() is not complete)

Q_n = \text{split}_{\text{simulate}};

else

Q_n = \{ q_n \};

foreach (q_n \text{ in the set } Q_n) {

if ( check_output( ) fails )

return(fail);

if (q_n \text{ is newly generated}) {

add s_n (the next-state of s) to the set

to be covered by q_n;

if (generate(s_n, q_n) fails)

return(fail);

} else if (check_state(s_n, q_n) fails)

return(fail);

}

}

}

check_state(s,q)

{

if (s is an element of the set to be covered by q)

return(success);

else

add s to the set to be covered by q;

foreach (applicable input at s) {

/* get the next-state q_n of q and primary output by simulation */

if (simulate() is not complete)

Q_n = \text{split}_{\text{simulate}};

else

Q_n = \{ q_n \};

foreach (q_n \text{ in the set } Q_n) {

if ( check_output( ) fails )

return(fail);

if (q_n \text{ is newly generated}) {

add s_n (the next-state of s) to the set

to be covered by q_n;

if (generate(s_n,q_n) fails)

return(fail);

} else if (check_state(s_n, q_n) fails)

return(fail);

}

}

```

}

39

# 3.4.2.6. Remarks

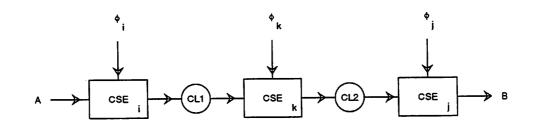

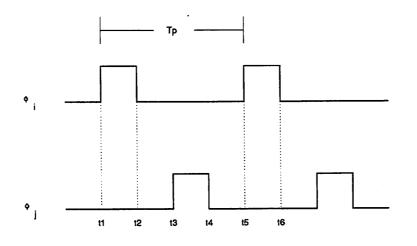

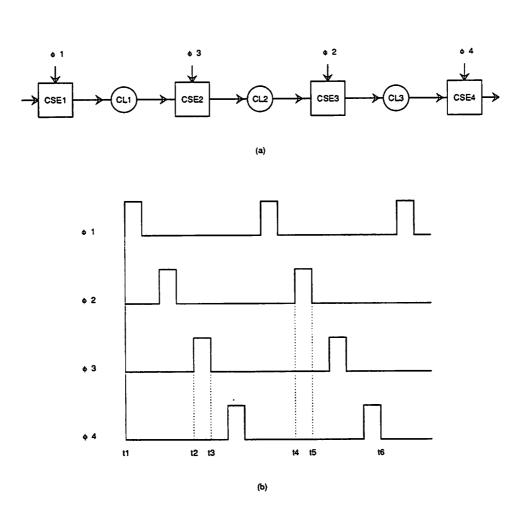

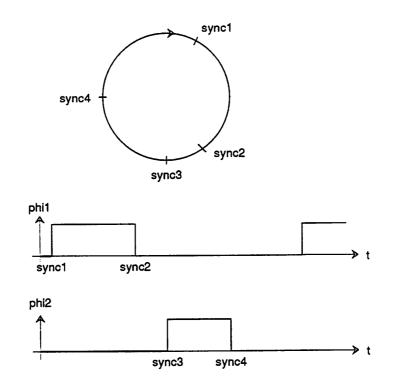

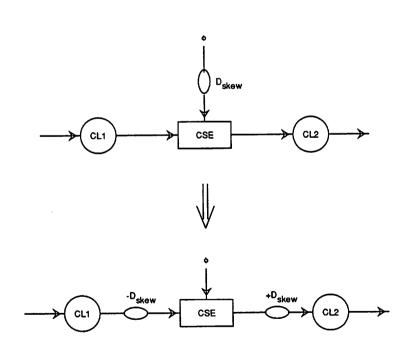

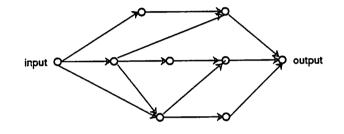

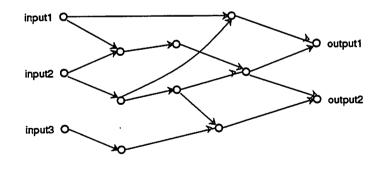

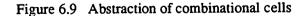

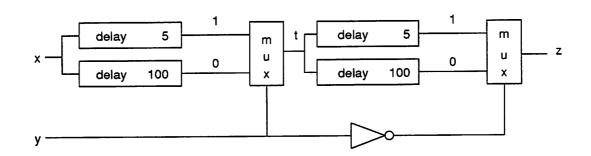

When the generate() procedure succeeds with a  $(s_0,q_0)$  pair, the algorithm guarantees that for each reachable state s from  $s_0$  in  $M_S$ , there exists a state q in  $M_Q$  which covers s. For every meaningful machine  $M_S$ , every state of  $M_S$  should be reachable from the initial state of  $M_S$ . When the specification state transition graph of the machine  $M_S$  is strongly connected, any state can be used as an initial state for verification purpose.