Copyright © 1990, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## A RECONFIGURABLE MULTIPROCESSOR SYSTEM FOR DSP BEHAVIORAL SIMULATION

by

Wook Koh

Memorandum No. UCB/ERL M90/53

our services

13 June 1990

## A RECONFIGURABLE MULTIPROCESSOR SYSTEM FOR DSP BEHAVIORAL SIMULATION

by

Wook Koh

Memorandum No. UCB/ERL M90/53

13 June 1990

# TITLE PAGE

## ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

## A RECONFIGURABLE MULTIPROCESSOR SYSTEM FOR DSP BEHAVIORAL SIMULATION

by

Wook Koh

Memorandum No. UCB/ERL M90/53

13 June 1990

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

1

# A RECONFIGURABLE MULTIPROCESSOR SYSTEM FOR DSP BEHAVIORAL SIMULATION

FOR DSP BEHAVIORAL SIMULATIC

:

Ph.D.

ł

Wook Koh Department of EECS

#### ABSTRACT

A major part of the design effort for DSP systems is devoted to the algorithmic verification and specification process. The behavioral simulation of DSP algorithms on a programmable computer will provide the flexibility to develop the algorithms and enable the short design cycle. However, the simulation often requires high computational throughput and the simulation of large amounts of data. It takes too long or is too costly to simulate on a general purpose computer.

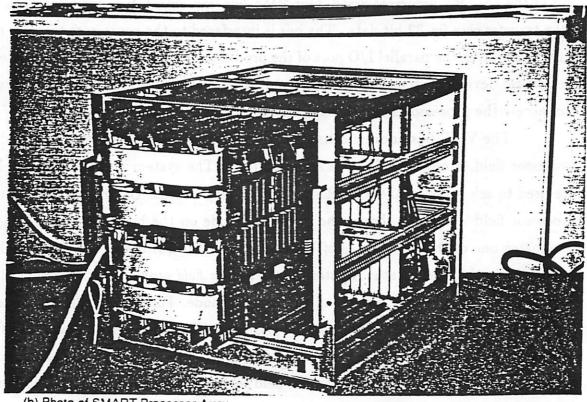

Therefore a dedicated simulation engine called SMART has been developed and presented in this report. It is a multiprocessor architecture optimized for realtime behavioral simulation of Digital Signal Processing (DSP) systems. The first prototype, containing 10 processors, is currently operational with a peak performance of 120 MFLOPS.

The SMART system features a *Configurable Bus* and a *Bypass Unit* to trade off overall communication bandwidth and latency by taking advantage of the local communication between processors. The system performance is further improved by a *Distributed Shared Memory* system which lets the communication latency overlap with the computation time of the processors. *Barriers, locks and events* are supported by hardware to minimize the synchronization overhead. The benchmarks have demonstrated that the SMART architecture actually achieves the targeted low communication and synchronization overhead.

In a SMART simulation environment, the designer can describe the algorithms using a high level language: C and Silage. The C programming environment, which requires the partitioning information in the program, is currently available. A high level software system, based on Silage, is under development to auto-schedule the algorithmic description onto the SMART processor array with a balanced loading and an efficient usage of the communication system. Performance of the actual SMART system was measured for typical DSP programs using floating-point operations. The measurement shows an average speedup of 76 times over SUN 3/60 and a speedup of 29 times over SUN SPARC Station 1. With extensive uses of library routines in programming, the speedup can be easily doubled over the above results. The performance is expected to increase even further when the system is upgraded from 120 MFLOPS to 200 MFLOPS.

# Acknowledgement

A large number of people have contributed in many different ways towards the successful completion of the project described in this thesis. My greatest indebtedness is to my advisor, Professor Jan Rabaey, who always had a great faith in me, and gave invaluable guidance, support and inspiration throughout the course of this project.

I am also indebted to Professor Robert W. Brodersen. Technical discussions with him always seem to provide new insights into the problems. Professor David Hodges, Professor Randy Katz and Professor David Patterson have guided me through my Master Project and taught me valuable lessons to survive and excel in graduate schools.

A project of this scope and nature would not have been possible without the collaborative efforts of Alfred Yeung and Phu Hoang. I am really grateful to have the opportunity to work with them for the last two and half years. For the CAD support, which was indespensible for this project, I am thankful to Brian Richards, Rajeev Jain and Mani Srivastava for maintaining LAGER IV. Thanks are due to Phil Schrupp for maintaining PCB software, Jonathan Min for providing an interface to the Visula program, Robert Yu for helping me to program PLDs, and Kirk Thege and Kevin Zimmerman for maintaining the computers.

This research was sponsored in part by DARPA and the AT&T Company. AT&T was always helpful for giving necessary informations and components to build our system. The MOSIS group deserves a great deal of credit for providing a high quality of VLSI and PCB foundaries. They were also very helpful and cordial in trying to resolve any problem that occurred.

I must thank to my close friends, relatives and parents – Dr. Pum J. Koh and Mrs. Hye S. R. Koh – without whose support this endeavour would not have been possible.

Finally, I dedicate this dissertation to my dearest friend, S. Rim, who gave me the courage to overcome the adversity when I was going through a very difficult time in my life.

# Contents

.

.

.

| Li | st of | Figures                                                      | vii |

|----|-------|--------------------------------------------------------------|-----|

| Li | st of | Tables                                                       | ix  |

| 1  | INT   | TRODUCTION                                                   | 1   |

| 2  | SM    | ART ARCHITECTURE                                             | 4   |

|    | 2.1   | Introduction to the SMART Architecture                       | 4   |

|    |       | 2.1.1 Multiprocessor Review                                  | 4   |

|    |       | 2.1.2 Pipelining and Parallelism - A Pitch Extractor Example | 9   |

|    | 2.2   | Memory Structure                                             | 14  |

|    |       | 2.2.1 Cache Coherence Scheme Review                          | 14  |

|    |       | 2.2.2 Implementation of the Distributed Shared Memory        | 21  |

|    | 2.3   | Reconfigurable Bus                                           | 24  |

|    |       | 2.3.1 Previous Work in Reconfigurable Bus Architectures      | 24  |

|    |       | 2.3.2 Our Reconfigurable Bus                                 | 28  |

|    |       | 2.3.3 Interprocessor Communication                           | 30  |

|    |       | 2.3.4 Self-Reconfigurable Bus                                | 33  |

|    | 2.4   | Synchronization                                              | 36  |

|    |       | 2.4.1 Barriers                                               | 37  |

|    |       | 2.4.2 Locks                                                  | 39  |

|    |       | 2.4.3 Events                                                 | 39  |

|    | 2.5   | Benchmark                                                    | 41  |

| 3  | SM.   | ART ARCHITECTURE IMPLEMENTATION                              | 46  |

|    | 3.1   | SMART System                                                 | 46  |

|    | 3.2   | SMART Processor Array                                        | 50  |

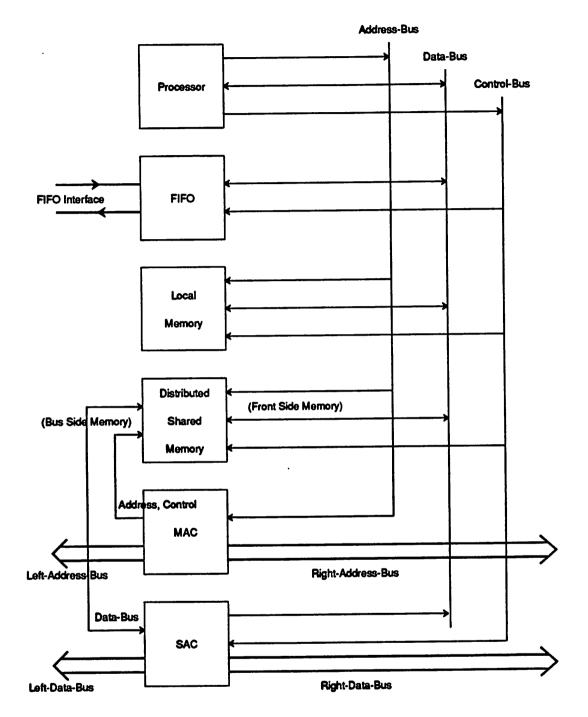

|    | 3.3   | Processing Unit                                              | 52  |

|    | 3.4   | Master Access Controller and Slave Access Controller         | 59  |

|    |       | 3.4.1 Access Controllers Instructions                        | 60  |

|    |       | 3.4.2 Functional Blocks in the MAC Chip                      | 62  |

|    |       | 3.4.3 Functional Blocks in the SAC Chip                      | 67  |

**4** DISCUSSIONS ON DESIGN AND IMPLEMENTATION 68 69 4.1 4.2 Functional Description and Simulation **69** 4.3 74 4.4 76 4.5 Testing and System Integration ..... 77 5 PROGRAMMING SMART 81 Overview of Programming Environment 5.1 81 5.2 Programming in C ..... 84 5.2.1 85 5.2.2Macros for Synchronization ..... 86 5.2.3 Macros for System Configuration 87 5.2.4 A FFT Example ..... 89 5.3 92 5.4 95 5.598 6 CONCLUSIONS 101 Bibliography 104 **A MAC Instructions** 111 **B** MACRO Definitions 118 C IMAGE.C Program 121 D How to Run the SMART System 140

vi

# List of Figures

٠.

| <b>2.1</b>                                                                | Pitch Extractor                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11                                                       |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| 2.2                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                       |

| 2.3                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 13                                                       |

| 2.4                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16                                                       |

| 2.5                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 18                                                       |

| 2.6                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20                                                       |

| 2.7                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22                                                       |

| 2.8                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 25                                                       |

| 2.9                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                                       |

| 2.10                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                       |

| 2.11                                                                      | =                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                                       |

| 2.12                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                       |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38                                                       |

| 2.14                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                                                       |

| 2.15                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 12                                                       |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| •••                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                          |

| 3.1                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 17                                                       |

| 3.2                                                                       | SMART Processor Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19                                                       |

| 3.2<br>3.3                                                                | SMART Processor Array.       4         SMART Processor Board.       5                                                                                                                                                                                                                                                                                                                                                                                                                    | 19<br>51                                                 |

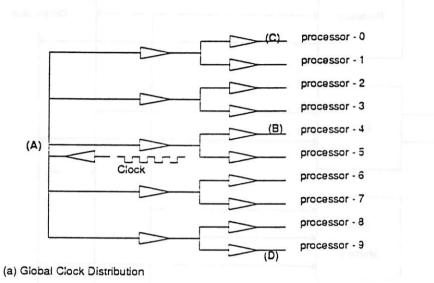

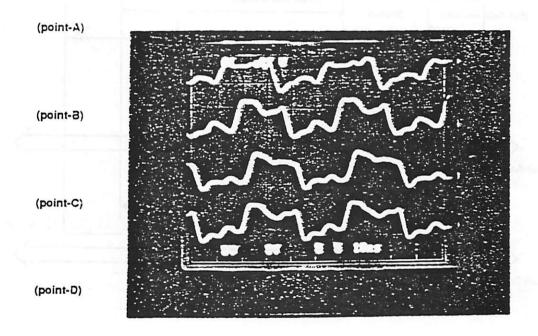

| 3.2<br>3.3<br>3.4                                                         | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5                                                                                                                                                                                                                                                                                                                                                                                      | 19<br>51<br>53                                           |

| 3.2<br>3.3<br>3.4<br>3.5                                                  | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5                                                                                                                                                                                                                                                                                                                          | 19<br>51<br>53<br>54                                     |

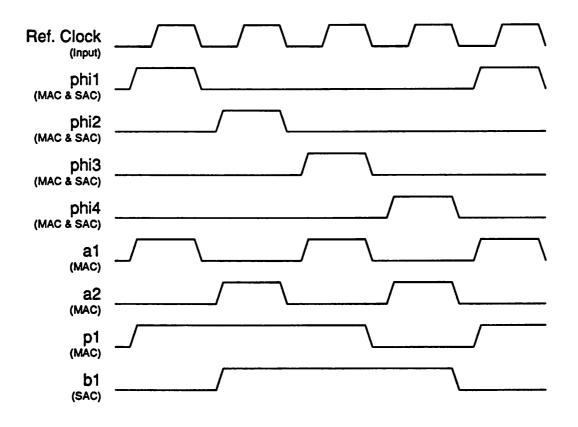

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6                                           | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5                                                                                                                                                                                                                                                                                  | 19<br>51<br>53<br>54<br>58                               |

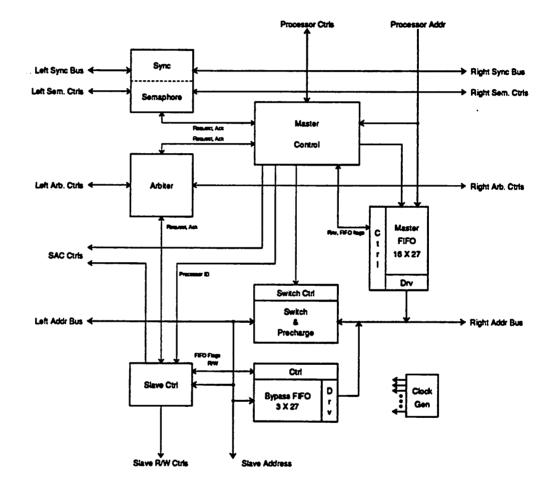

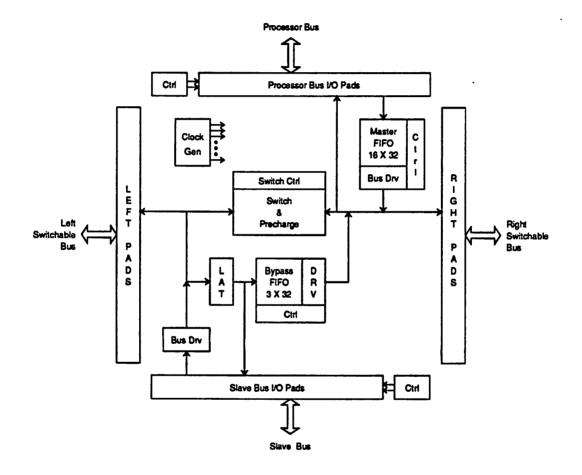

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                    | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6                                                                                                                                                                                                                                            | 19<br>51<br>53<br>54<br>58<br>53                         |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                             | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6                                                                                                                                                                                                      | 19<br>51<br>53<br>54<br>58<br>53<br>54<br>53             |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                    | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6                                                                                                                                                                                                      | 19<br>51<br>53<br>54<br>58<br>53                         |

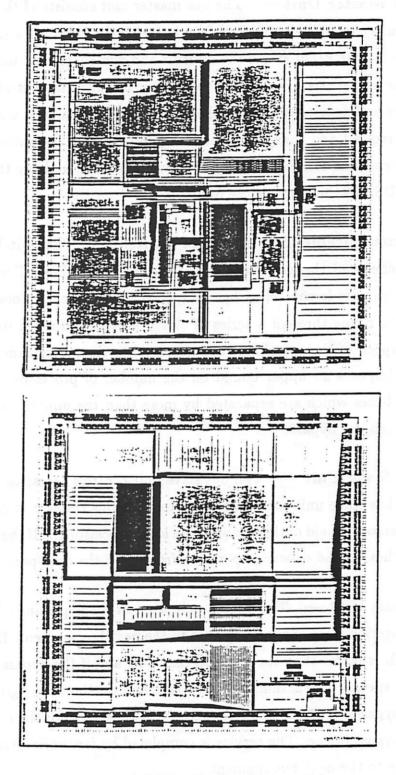

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                             | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6         Pictures of MAC and SAC - die size 1.1cm x 1.1cm       6                                                                                                                                     | 19<br>51<br>53<br>54<br>53<br>54<br>55<br>55             |

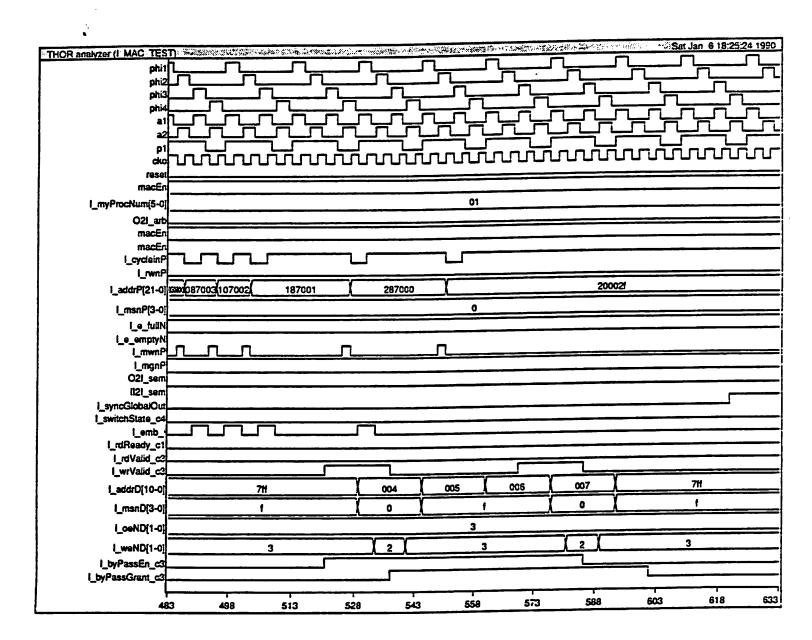

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9                      | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6         Pictures of MAC and SAC - die size 1.1cm x 1.1cm       6         Thor Modeling Example - Arb.c.       7                                                                                      | 19<br>51<br>53<br>54<br>58<br>53<br>54<br>53             |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1               | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6         Pictures of MAC and SAC - die size 1.1cm x 1.1cm       6         Thor Modeling Example - Arb.c.       7         Simulation Example.       7                                                  | 19<br>51<br>53<br>54<br>53<br>54<br>53<br>54<br>55<br>71 |

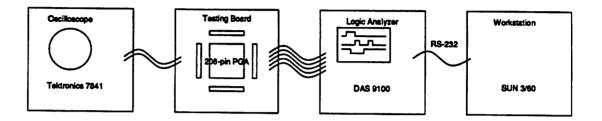

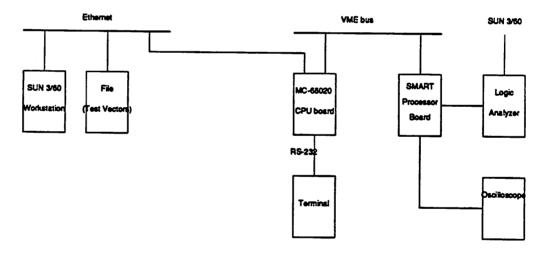

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1<br>4.2<br>4.3 | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Internal Clock Signals.       5         Block Diagram of MAC.       6         Block Diagram of SAC.       6         Pictures of MAC and SAC - die size 1.1cm x 1.1cm       6         Thor Modeling Example - Arb.c.       7         Simulation Example.       7         Test Configuration.       7              | 19<br>51<br>53<br>54<br>53<br>54<br>55<br>71<br>73<br>79 |

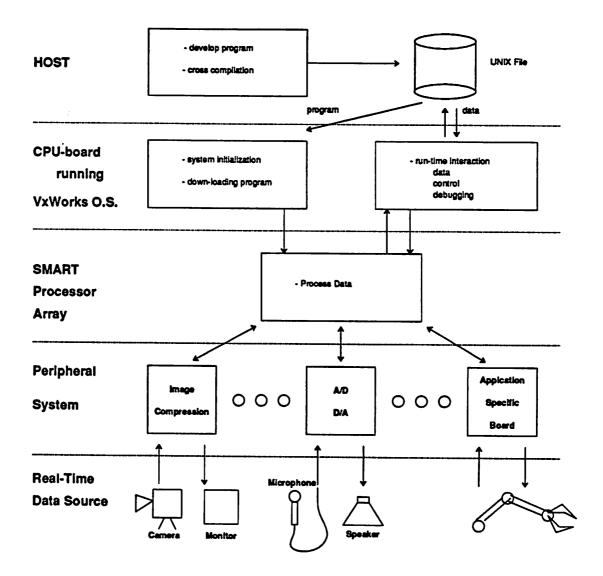

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>4.1<br>4.2        | SMART Processor Array.       4         SMART Processor Board.       5         System Clock.       5         Block Diagram of the SMART Processing Unit.       5         Block Diagram of MAC.       6         Block Diagram of MAC.       6         Block Diagram of SAC.       6         Pictures of MAC and SAC - die size 1.1cm x 1.1cm       6         Thor Modeling Example - Arb.c.       7         Simulation Example.       7         Programming Environment for SMART.       8 | 19<br>51<br>53<br>54<br>53<br>54<br>55<br>71<br>73       |

| 5.3 | Real-Time Data Interface. | 93 |

|-----|---------------------------|----|

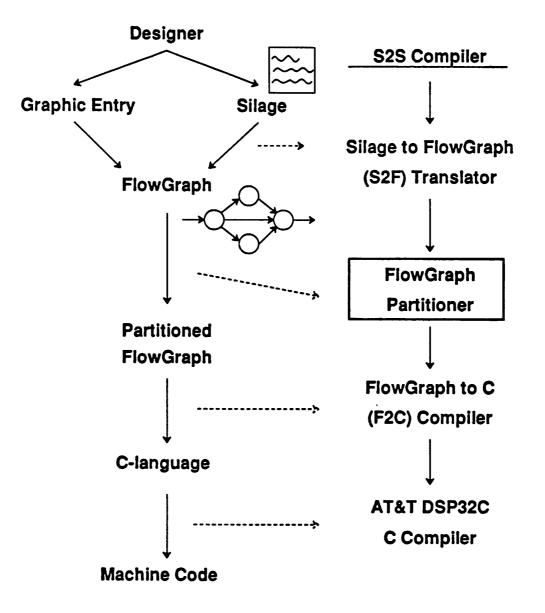

| 5.4 | Silage to SMART Compiler  | 99 |

•

# List of Tables

•

| 2.1 | Benchmark Results for 16 Processors                         | 43 |

|-----|-------------------------------------------------------------|----|

| 2.2 | Benchmark Results for 64 Processors                         | 43 |

| 5.1 | Performance Results for 10 Processors                       | 95 |

| A.1 | DSP32C Memory Configuration, Mode 7 (ROM-less version) 11   | 12 |

| A.2 | Address Mapping for Memory Bank 0 (Group 1 Instructions) 11 | 13 |

| A.3 | Address Mapping for Memory Bank 0 (Group 2 Instructions) 11 | 14 |

| A.4 | Address Mapping for Memory Bank 1 (Internal Access Only) 11 | 15 |

•

•

# Chapter 1

# INTRODUCTION

The woods are lovely, dark and deep. But I have promises to keep, And miles to go before I sleep, And miles to go before I sleep. - Robert Frost

DSP applications have become an important component in the rapidly expanding field of Application Specific Integrated Circuits (ASIC). Examples of applications in this field include digital audio, speech synthesis and recognition, telecommunication, image and video processing and robotics. Due to the high throughput and special input/output requirements, it is often necessary to design special purpose chips, which are optimized for only that particular application. Recently, a great deal of attention has been focused on the development of computer aided design environments, which may help to shorten the design time of those dedicated devices [36].

It has been noted that a major part of the design effort for DSP systems is devoted to the algorithmic verification and specification process. This process often requires high computational throughput and the the simulation of large amounts of data [45] [61]. For example a computation rate of 1 GOPS (Giga Operations Per Second) or more is typical for High Definition Television (HDTV) algorithms [27]. Furthermore, to verify the behavior of the algorithms, many frames of data have to be simulated. These requirements dictate a hardware solution.

The process also includes the simulation of the noise and distortion behavior

taking into account the effect of quantization, rounding and truncation. It is only after a careful checking of all those parasitic effects that Application Specific Integrated Circuits (ASIC) can be implemented.

While techniques such as bread-boarding and fast-prototyping can fulfill the requirements, they typically exhibit long development time and offer very little programmability which is essential in optimizing the parameters of some algorithms.

The behavioral simulation of DSP algorithms on a programmable computer will provide the flexibility to develop the algorithms and enable the short design cycle. Some commercial multiprocessor computers are capable of providing high computation power but the high overhead in inter-processor communication, difficulty in mapping the algorithms to the architecture, lack of instructions for supporting DSP applications and the high cost of the machines often limit the effectiveness of these machines.

In this report, a dedicated compute-engine called SMART (an acronym for Switchable Multiprocessor Architecture supporting Real Time applications) is presented. <sup>1</sup> The machine attempts to speedup simulation of DSP algorithms by at least an order of magnitude as compared to general purpose computer architectures.

The speedup is achieved by using the following two methods. First, in order to handle the number crunching bottleneck, a high performance DSP processor with both floating point and fixed point instructions is used as the core processing unit (DSP32C from AT&T Bell Labs [23] [8]). The processor executes up to 10 million floating point (single precision IEEE) multiplications and additions per second. In addition, it provides special instruction sets to support DSP applications. This results in serveral times of speedup as compared to general purpose processors [67].

Second, another level of simulation speedup can be obtained by exploiting the high degree of concurrency present in most signal processing algorithms [32]. The SMART system should be able to simulate a large variety of DSP algorithms with various degrees and grains of concurrency. Pipelining and Parallelism are two methods used to achieve concurrency.

<sup>&</sup>lt;sup>1</sup>Early studies on the architecture can be found in [38] and [39].

#### CHAPTER 1. INTRODUCTION

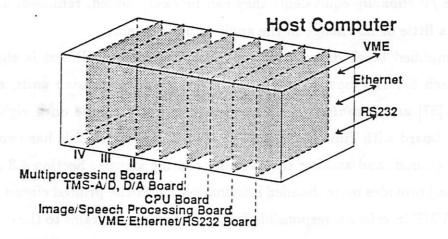

This report describes the architecture and implementation of the SMART machine, and justifies and evaluates some of the architectural features with the aid of system, software and application considerations. Chapter 2 provides an introductory section, which reviews other multiprocessor systems, suggests architecture requirements, and discusses pipelining and parallelism in a typical DSP algorithm. Then the three major aspects of architecture – the memory structure, the reconfigurable bus and the synchronization - are described. The set of software benchmarks are presented to demonstrate the effectiveness of the architecture. In chapter 3, the physical implementation of the SMART architecture is presented in a top-down manner. We first present an overview of the the SMART prototype system. We next provide the detail of implementation of the SMART processor array: the printed circuit board, the processor, the memory structure and the custom VLSI chip sets. Chapter 4 briefly discusses our experiences regarding design and implementation issues. Chapter 5 discusses the supporting software environment of the system. A table which shows the performance of the system is also presented. The last chapter includes some general discussions of the system and the project. Concluding remarks and future developments on SMART are also outlined.

# Chapter 2

# SMART ARCHITECTURE

To see a world in a grain of sand And a heaven in a wild flower, Hold infinity in the palm of your hand And eternity in an hour - William Blake

## 2.1 Introduction to the SMART Architecture

This section reviews contemporary multiprocessor systems, suggests architecture requirements, and discusses pipelining and parallelism in a typical DSP algorithm – a pitch extractor example.

## 2.1.1 Multiprocessor Review

The last decade has witnessed the introduction of a wide variety of new computer architectures for parallel processing that complement and extend the major approaches to parallel computing developed in the early years [17]. The recent proliferation of parallel processing technologies has included new parallel hardware architectures such as systolic and hypercube, interconnection technologies such as multistage switching topologies, and programming paradigms such as applicative languages. The sheer diversity of the field makes it difficult for a designer to find out which architecture is right for his target applications.

#### CHAPTER 2. SMART ARCHITECTURE

Our SMART project is motivated by the demand in the signal processing area to build a simulation engine for simulating the behavior of DSP algorithms. The scope of this target system is real-time operation [42] for medium speed DSP applications (speech, telecom, audio and robotics) and a simulation speedup for high performance DSP applications (video and image processing).

In order to find out which architecture is right for our application, we first reviewed the commercially available systems. From programming experiences and studies on well-known machines such as Connection Machine [77] [75], WARP [22] [21], Sequent Balance [71], Intel iPSC [34] and NCube [55]. we have learned the following lessons and adopted them as the basic architecture requirements for the SMART system.

Number of Processors — According to the Amdahl's law [6], as the number of processors in a parallel computer increases, it becomes more and more difficult to use those processors efficiently.

For instance, Connection Machine has 65,536 processing elements with a peak performance of 2500 MFLOPS/2500 MIPS. The applications of the machine include simulation of VLSI circuits, picture processing and language processing [76], all of which contain large amounts of parallelism. However when the target algorithms do not have enough parallelism to make use of all those processing elements, most of the processing power is wasted. It is extremely difficult to partition typical medium speed DSP algorithms to thousands or millions of processors.

Therefore, in order to build a system with a low cost/performance design we are interested in a system with a relatively small number (10 - 100) of extremely powerful processors.

Overhead of Interprocessor Communication — A general purpose multiprocessor system often provides a flexible programming environment at the cost of a substantial amount of performance degradation in interprocessor communication and synchronization.

For example, the Intel iPSC and the NCube are two message-passing mul-

#### **CHAPTER 2. SMART ARCHITECTURE**

tiprocessors. Both machines are based on the hypercube architecture originally developed at Caltech [70]. The hypercube topology provides a network that is easily scalable to a large number of processors. The network is dense enough to assume each processor is connected to every other processor, while sparse enough to allow a simple implementation.

However performance measurements on the above machines show that it takes about 1msec to send one byte of data from one processor to a nearest neighbor processor. <sup>1</sup> The large communication latency is a result of interprocessor communication protocols implemented in software.

Real-time DSP applications cannot accept such run-time overhead in the interprocessor communication and synchronization. Therefore, the design of the SMART architecture places its highest priority on achieving low interprocessor communication and synchronization overhead.

SIMD vs. MIMD — The simulation system should be able to simulate a large variety of DSP algorithms with various degrees and grains of concurrency. The simulation system should efficiently support both pipelining and parallelism.

A SIMD machine cannot exploit pipelining and parallelism simultaneously because this requires execution of different instructions among processors. Therefore our SMART system has a MIMD (Multiple-Instruction stream, Multiple-Data stream) architecture.

Local vs. Global Communication — A system should support both local and global communications efficiently. For instance, the communication pattern of a FFT algorithm, when partitioned in a pipelined fashion, mainly consists of local communications [38]. An architecture such as WARP [22] [21] can support those local communications quite well.<sup>2</sup> On the other hand, the communication pattern of a Matrix Multiplication algorithm, when partitioned in a parallel fashion, mostly consists of global communications [38]. According to a benchmark result [38], a system

<sup>&</sup>lt;sup>1</sup>The latency for one byte is quite large due to the initial cost to begin message transmission.

<sup>&</sup>lt;sup>2</sup>WARP is a systolic array machine [44] [12] designed at Carnegie Mellon.

¥.

with a high speed shared bus which provides a direct path between distant processors performed better than a system with only local connections such as WARP. Therefore, we developed a system which can reconfigure the processor interconnections to support both local and global communications [Section 2.4].

DSP Processor — On certain DSP-related benchmarks, the performance of programmable DSP processors has consistently exceeded that of general purpose processors (with arithmetic co-processors) by several times throughout their ten year history [48] [50] [52].

Recently, there have been a lot of efforts to develop real-time simulation systems based on powerful DSP processors [46]. In order to handle the number crunching bottleneck, the SMART system uses a high performance DSP processor with both floating point and fixed point instructions as the core processing unit (DSP32C from AT&T Bell Labs [23] [8] ).

The SMART architecture can be applied to far more powerful, new DSP processors such as Texas Instruments TMS320C30 [63], Motorola DSP96002 [41], and Intel i860 [68] [56]. <sup>3</sup>

I/O Interface — The general purpose systems usually do not provide good environment to interface to real-time data. A real-time system should have I/O interfaces which are easy to intergate with the peripheral devices and fast enough to keep up with the incoming sample rate.

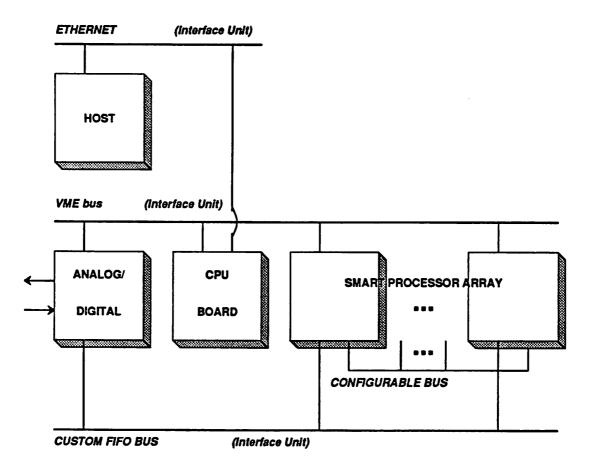

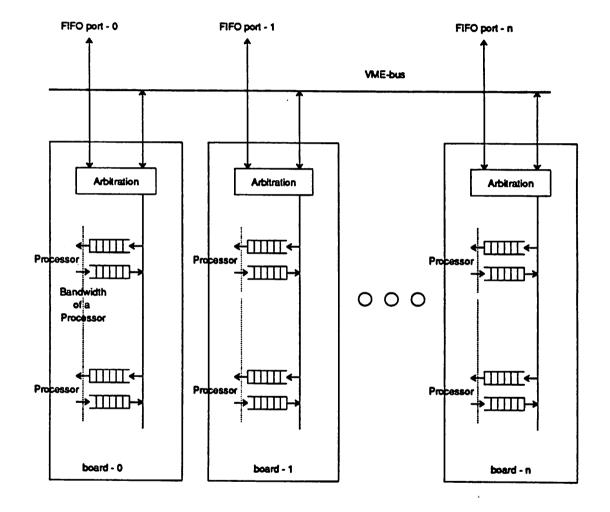

For instance, the DSP32C processor provides a fast hardware conversion feature to convert typical 8-bit real-time data representation, which is used in audio-A/D and D/A converters, to and from the 32-bit floating-point representation, which is used for numeric processing. The SMART system also provides a standard VME bus interface and a custom FIFO interface which allow easy intergration to other peripheral systems. Especially, since a custom FIFO is directly interfaced to the core processor, it is possible to build a high speed interface to the real-time data.

<sup>&</sup>lt;sup>3</sup>The Intel i860 processor is more general than other DSP processors.

Multiprocessor System using DSP Processors — There are many other realtime simulation systems using multiple DSP processors [28].

For instance, the Dolby architecture [49] is a shared memory multiprocessor system. It consists of four Motorola DSP56000's. A transaction to access the shared memory requires first requesting the bus, then reading the memory, checking a semaphore, and resetting the semaphore. Each memory transaction requires about 30 instruction cycles [49]. This relatively high cost implies that only large-grain parallelism can be supported efficiently.

D. Schwartz has developed a multiprocessor system using AT&T DSP32 processors [15]. The system has been specifically designed to support cyclo-static scheduling [74]. The goal of the scheduling is to yield an optimal solution for the following three parameters: the number of processors required, the minimum latency between iterations of the algorithm, and the minimum time between the availability of an input and the availability of the corresponding output. However, the search for an optimal solution requires an exponential run time. Furthermore, the scheduling algorithm does not allow data dependent execution in its fully specified flow graphs [13]. Therefore the system can handle only sub-set of the DSP algorithms.

The ASPEN parallel computer using the DSP32 has been developed by AT&T [62]. <sup>4</sup> The system is designed for a large-vocabulary speech recognition system, and is also applicable to other signal processing problems. The processing elements are interconnected to form a complete binary tree [11]. The system is suitable for pattern recognition, and for calculation of means and variances, which is well suited for binary tree connection. However, the architecture is not suitable for other typical applications. For instance, it is quite difficult to map the FFT (Fast Fourier Transform) to the tree architecture. Furthermore, the system does not provide sufficient interprocessor communication bandwidth for the FFT algorithm.

SMART architecture — Based on the above observations and architecture requirements, we developed a SMART architecture. It utilizes a *reconfigurable bus* [Section 2.3] to adapt the interconnection to the irregular communication pattern of

<sup>&</sup>lt;sup>4</sup>The computer using the DSP32C is described in [2].

. .

an algorithm, a *distributed shared memory* [Section 2.2] to provide a shared memory system with low interprocessor communication overhead, and hardware support for three types of commonly used *synchronizations* [Section 2.4]. The following section discusses pipelining and parallelism in a typical DSP algorithm and gives the background on how the architecture was initially developed.

## 2.1.2 Pipelining and Parallelism - A Pitch Extractor Example

The simulation system is targeted to simulate a large variety of DSP algorithms with various degrees and grains of concurrency. Pipelining and Parallelism are two methods used to achieve concurrency [58] [61] [26]. Pipelining increases concurrency by dividing a computation into a number of steps and allowing a number of tasks to be in various stages of execution at the same time. For our target DSP applications, it is assumed that the program operates on an essentially infinite stream of input data, executing once per input sample. Therefore we can overlap execution of successive iterations to obtain our speedup. Pipelining is a common form of this general technique. On the other hand, parallel processing emphasizes the concurrent manipulation of data to solve a single problem. The SMART architecture is geared towards exploiting block level pipelining and sub-block parallelism simultaneously to obtain a speedup in simulation time.

The bus reconfiguration is used to achieve efficient communication pattern when both pipelining and parallelism are present. A DSP system usually consists of sequentially data-dependent sub-system blocks. The pipelining of sub-system blocks can increase the throughput of the system and further pipelining within a sub-system block may increase the throughput even more. But some sub-system blocks such as iterative singular value decomposition (SVD) [25] or adaptive filters have constraints such that pipelining within the block is not possible. This is the case when, for instance, the output of the current sample has to be produced before the next sample can be processed. Pipelining within the block is not possible without changing the algorithm. However, the iterative SVD has a large amount of parallelism in the

#### CHAPTER 2. SMART ARCHITECTURE

algorithm. For this case, pipelining will be pursued at the system level and parallelism will be exploited within the iterative SVD block. The following example shows how important it is to exploit both pipelining and parallelism for load balancing.

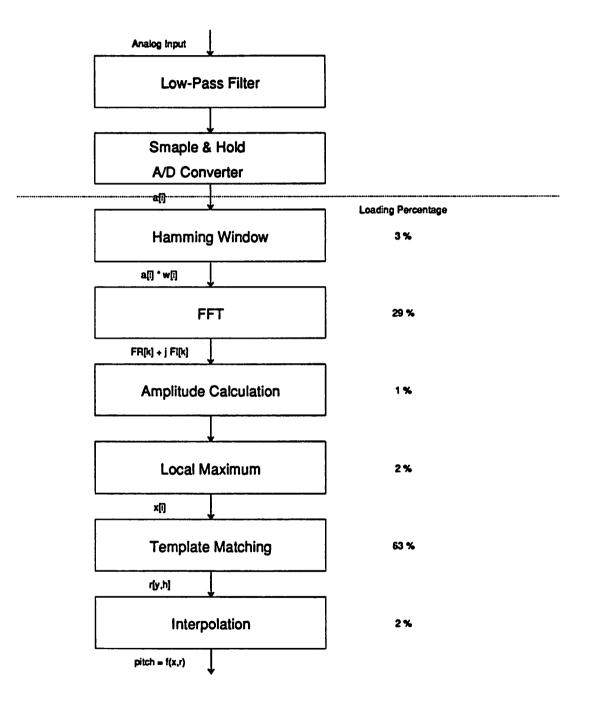

Figure 2.1 shows an implementation of a high quality pitch extraction algorithm for speech analysis and synthesis [24]. The algorithm shows the combination of pipelining and parallelism typical in DSP applications. Sub-system blocks like the hamming window operation, the FFT, the amplitude calculation operate sequentially on streams of data to extract a pitch from voice samples. The numbers beside the blocks in the figure state the percentage of the computation load for each block. If each block is mapped into a pipelined processor, the *template matching* block will be the throughput bottleneck and we will only get a throughput improvement 1.6 times over the single processor system. However the template matching block can be partitioned naturally over 8 parallel processors [Figure 2.2 (a)], which reduces the load of the bottleneck processor to one eighth. By load balancing sub-system blocks and by mapping into pipelined processors, we get a speedup of 12.1 times over a single processor using 15 processors.

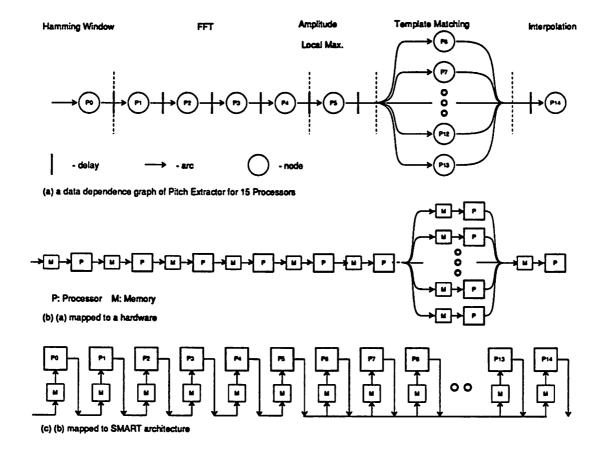

Figure 2.2 (a) shows the data dependence graph for the pitch extraction after partitioning and load balancing process. A data dependence graph consists of nodes, arcs, and delay elements. A node represents operations on data. A directed arc shows the data dependence or the relation between the producer and the consumer. A delay element is a property of the arc connecting two nodes. If there is a unit delay on the arc connecting node A and B, then the n-th data consumed by node B will be the (n-1)st data produced by A. Delays can be placed on any *feed-forward cut-set* to increase the degree of pipelining without altering the computation, as long as the latency of the system is not a consideration.

A one to one mapping of this load balanced data dependence graph on a multiprocessor architecture with a customized communication pattern would result in the architecture of Figure 2.2 (b). The dedicated architecture can now be mapped onto the one dimensional SMART architecture as shown in Figure 2.2 (c). Processors P0 to P5 and P14 are working in a pipelined fashion. Processors P6 to P13 are working in parallel to each other and working in pipelined fashion with other processors.

.

Figure 2.1: Pitch Extractor.

Figure 2.2: Bus Reconfiguration of the Pitch Extractor Algorithm.

.

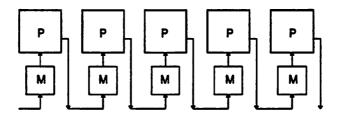

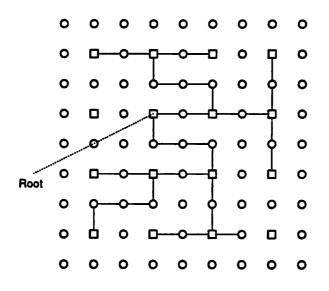

(a) SMART array

(b) an irregularly configured bus

(c) one-dimensional systolic array

(d) a single shared bus

۱

P: Processor, M: Memory, S: Switch

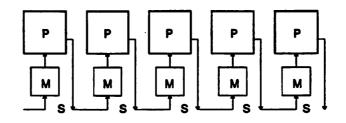

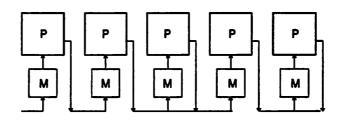

Figure 2.3: Examples of Bus Reconfiguration.

-

--

#### CHAPTER 2. SMART ARCHITECTURE

Figure 2.3 shows examples of a reconfigurable bus in simplified diagrams. The SMART architecture can be statically reconfigured under software control to match irregular communication patterns. This results in a flexible architecture and increased bus bandwidth at the cost of hardware switches. The one dimensional systolic array can be realized by opening all the switches [Figure 2.3 (c)] or and the shared-bus multiprocessor system by closing all the switches [Figure 2.3 (d)]. In terms of interconnection, the one dimensional systolic array and the shared-bus multiprocessor system are special cases of SMART architecture.

The following sections deal with the three main aspects of the SMART architecture – the memory structure, the reconfigurable bus and the synchronization – which are formulated from the analysis of DSP examples. These features are implemented in a special semi-custom VLSI chip set [Chapter 3].

## 2.2 Memory Structure

The design objective of memory architecture in a multiprocessor system is to balance the processor speed with the bandwidth of the memory at a reasonable cost. In real-time system applications, a major concern in memory design is the reduction of the communication overhead between processors.

First, cache coherence schemes are discussed in terms of reducing the communication overhead. Then, an implementation of a *distributed shared memory* with a new cache coherence scheme is presented.

## 2.2.1 Cache Coherence Scheme Review

Multiprocessors can be grouped into two different sets of architectural models: a tightly coupled multiprocessor and a loosely coupled multiprocessor [14]. Tightly coupled multiprocessors communicate through a shared memory. Hence the rate at which data can communicate from one processor to another is on the order of the bandwidth of the shared memory. Complete connectivity is provided between the processors and memory. Loosely coupled multiprocessors communicate by exchanging messages. They do not generally encounter the degree of memory conflicts experienced by tightly coupled systems. Loosely coupled systems are efficient when the interactions between processes are minimal. On the other hand tightly coupled systems can tolerate a higher degree of interactions between processes. Because of the large amount of interaction between processes in our target applications, the throughput of the hierarchical loosely coupled multiprocessor may be too low for applications that require fast response times [26]. Therefore, a tightly coupled structure is chosen for the SMART system.

The presence of caches in a tightly coupled system introduces problems of *cache coherence*. A system of caches is *coherent* if and only if a *read* performed by any processor on any data in main memory always delivers the most recent value. Since the producer and consumer processors of the data communicate through the shared data in cache or main memory, the way to solve cache coherence is closely related to interprocessor communication overhead. The overhead is the sum of the time spent by the producer in writing a shared data word plus the time spent by the consumer in reading the data. In the following paragraphs, the interprocessor communication overhead for *static coherence scheme* and *dynamic coherence scheme* is discussed. After that we present our cache design, where the main goal is to achieve the low communication overhead.

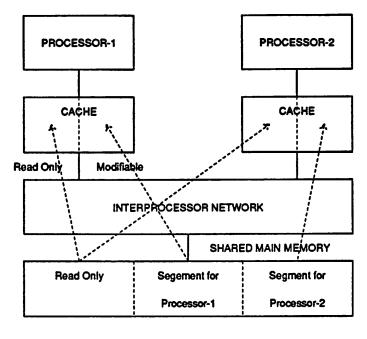

Static Coherence Scheme — Solutions to the cache coherence problem can be generally grouped into two methods. The first method, called *static coherence*, does not allow multiple copies of the *shared writable* data to exist in different caches at any given time.

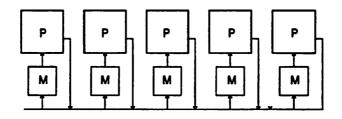

One of the possible implementations is shown in Figure 2.4 (a). Shared data structures which are modifiable remain in shared main memory – called non-cacheable data. References to these shared data are made directly to main memory. On the other hand, *Read-only* segments of data need not be non-cacheable. Read-only segments of data which are shared by several processors may be copied into the cache – called cacheable data. The cacheability of read-only data reduces conflicts in main memory. However, when processors communicate to each other, both a producer and

Figure 2.4: Static Coherence Scheme.

a consumer have to access the main memory, not the cache. The overhead to access the main memory is too large for a high degree of communication between processes.

The other type of implementation is to provide *shared cache* for the shared writable data as well as *private cache* for the private data. The shared cache is connected to the processors and the main memory through switching networks. Figure 2.4 (b) illustrates this shared cache concept. The shared data is accessed through a shared cache while instruction fetches and private data references are made in private caches. Data references by producers and consumers proceed at the cache speed except when conflicts occur at the shared cache or a miss occurs. The communication overhead of the this scheme depends on how well the switching networks are designed. The communication overhead is small for a rather small number of processors. However, as the number of processors increases to tens and hundreds, the potential gain in speed will be limited by the transmission delays through the switch to access the shared cache and by the number of conflicts at the cache. Therefore this cache scheme is not appropriate for our application.

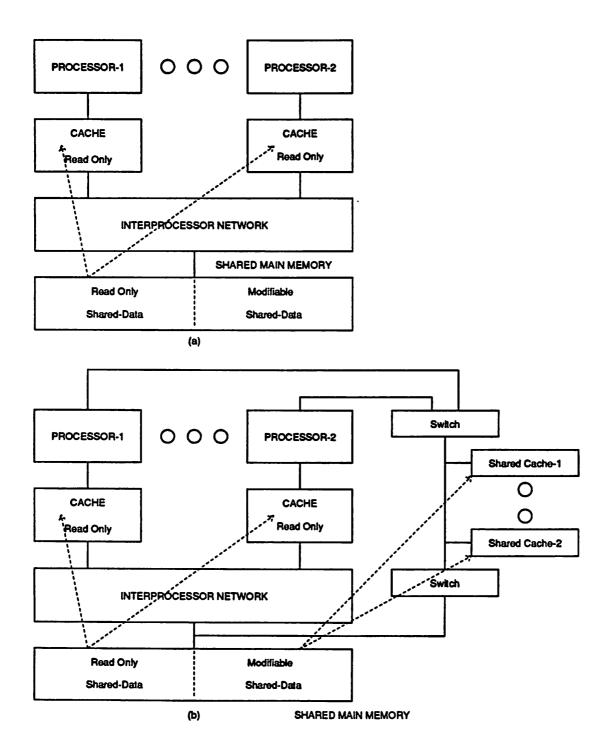

**Dynamic Coherence Scheme** — The second method for solving cache coherence, called *dynamic coherence*, allows multiple copies of the same data to exist in caches, provided that all the copies are identical.

To enforce the cache consistency rule in hardware, a tag is associated with each cache block. It indicates the state of the shard data: read-only state, exclusively read-write state, exclusively read-only state and invalid state.

If the processor associated with each of the caches has not modified its copy since the data was loaded in its cache, the copy is in *read-only* state (RO). In order to modify the copy in the cache, a processor has to own the copy with *exclusive readwrite* (RW) or *exclusive read-only* (EX) states. A RW state means the cache is the only one with the copy and it has been modified. Similarly, an EX state means the cache is the only one with the copy and it has *not* been modified. Therefore at any time, in order to keep cache coherence, only one processor can own a RW or an EX state of a copy. On the other hand, an *invalid* (INV) state means the copy is not valid. For instance, when a processor owns an RW state, all the other copies in other

Figure 2.5: Dynamic Coherence Scheme.

1

processors will be in INV states. <sup>5</sup>

Figure 2.5 shows a simple example of how a producer and a consumer change states of copies during interprocessor communication. In order to modify a block copy, a producer has to wait until it owns the block copy with RW state and invalidates other copies. Then in order to read the modified copy, a consumer has to regain its RO state and wait for the missed data. Therefore both a producer and a consumer have to pay communication overhead.

This dynamic coherence scheme is more flexible than the static coherence method, but also more complex and possibly more costly. When a producer and a consumer alternately writes and reads data the communication overhead is far worse than a simple static coherence scheme.

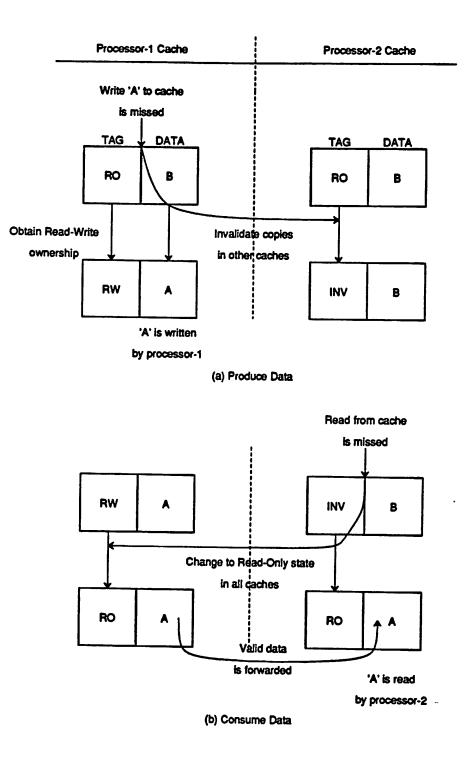

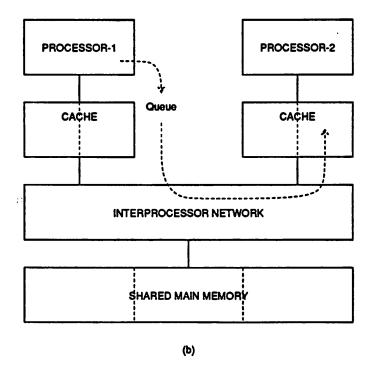

Our Scheme — Our cache design is based on a variation of a static coherence scheme. Figure 2.6 shows our shared cache implementation. It illustrates how to achieve cache coherence and low interprocessor communication overhead simultaneously. A read-only segment of data which is shared by several processors is cacheable by all processors. In other words, multiple copies of shared read-only data are allowed to exist in different caches at any time.

On the other hand, a shared data structure which can be modified is cacheable by only one processor. As shown in Figure 2.6 (a), shared data words in address segment-1 can be cacheable by only processor-1, and shared data words in address segment-2 can be cacheable by only processor-2. The caches are directly connected to the associated processors to reduce the access time to the cache. When a processor accesses a shared data in its own address segment, it can access the copy in its own cache – unless there is a cache miss. However, when a processor accesses a data word in other address segment, it will have to access the data in another processor's cache through the interprocessor network.

The other processor's caches, even though they are not directly connected, are still accessible by the processor through the interconnection network. The access

<sup>&</sup>lt;sup>5</sup>The cache coherence scheme is a rather complicated process. There are several variations of this scheme. More detailed information on cache coherence is discussed in [40] [35] [37].

(a)

Figure 2.6: Communication Scheme in SMART Architecture.

times of *write* operations to those caches are as small as accessing its own cache, since the processor does not have to wait for the data to reach the destination; the data will be pushed into the interprocessor communication queue and will be automatically forwarded to its destination as shown in Figure 2.6 (b), regardless of hit or miss on the other side. In the case of a *read* operation to another processor's cache, however, the processor has to wait until the read data comes back; that is, it has to pay communication overhead.

Therefore in order to keep communication overhead small, the producer has to write a shared data word to the consumer's cache and the consumer has to read the data from its own cache without spending time on accessing the interconnection network. Hence both a producer and a consumer pay no communication overhead unless there is a cache miss. When there is more than one consumer, the producer may broadcast the data to all the consumers at once.

### 2.2.2 Implementation of the Distributed Shared Memory

A communication scheme in which the producer *writes* explicitly the shared data word to the consumer's cache memory was proposed in the previous section. This section describes how it is implemented in our system.

Since the SMART system is designed to support real-time applications, it is efficient to schedule processes at compile time and to use the physical address to access the memory. Hence the producer and the consumer know statically where – what physical address – to write the data to and where to read the data from.

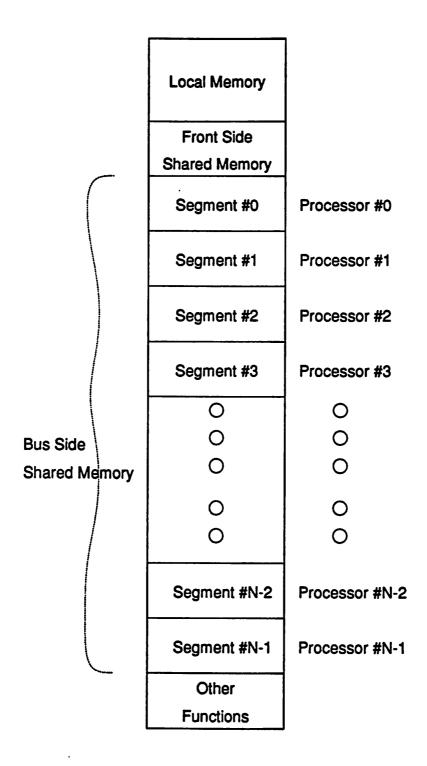

Furthermore, after the address space of AT&T DSP32C processor (24-bit byte address) was partitioned into various functions for 64 processors as in Figure 2.7, the whole memory segment size for each processor (32KB) was small enough to be implemented by cache memory. Therefore, it was not necessary for the main memory to back up the cache miss nor to implement the extra hardware to deal with the miss. However the major ideas of the memory structure remain the same. The prototype system can be regarded as a special case of the proposed cache coherence scheme without any cache miss. In the next generation of the SMART system, since the

Figure 2.7: Memory Address Segmentation.

processor is expected to have 32-bit address space, it will be necessary to implement the main memory to cover the large segment address space.

In order to implement the above interprocessor communication scheme, the following address map – which is same for every processor – is provided as shown in Figure 2.7. The map consists of address spaces of *local memory*, front side shared memory, bus side shared memory and address mapped functions. <sup>6</sup>

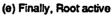

Figure 2.10 (a) shows the configuration of those memories. <sup>7</sup> Each processor has its own *local memory* to store the private data and program which are not shared among processors. The *front side* address space is used for accessing the shared data from the front side of the cache. The *bus side* shared address space, which is assigned for the communication through the interconnection network, is partitioned at the high address bits into equal memory segments and distributed among processors in proper order [Figure 2.7]. The physical memory of each segment corresponds to the physical memory of the associated processor's front side address space. In other words data, which is written to segment *i*, can be read from the front side of the processor *i*, thereby achieving the interprocessor communication. The name *shared distributed memory* is used for this memory scheme to emphasize the feature that shared memory is segmented and distributed to enable the low interprocessor communication overhead.

Figure 2.10 (a) also shows a *bus master* unit and a *bus slave* unit. Those units enable access to the cache memories of other processors. The bus master unit provides the interface between the processor and the network. It consists of an interprocessor communication queue, a network arbitration block, and extra circuitry. The queue stores the address and the data for interprocessor read and write operations. The network arbitration block decides when to send a data word from the queue to the

<sup>&</sup>lt;sup>6</sup>The address mapped functions are specific to the system. A function is invoked by accessing a predefined memory location. In the SMART system, for instance, an input and an output FIFO memory can be accessed with an address of 0zf40000. A far more detailed address map is shown in Appendix-A. Chapter 3 shows more detailed informations on the implementation of the actual memory structure.

<sup>&</sup>lt;sup>7</sup>Figure 2.10 (b) shows the distributed shared memory system which is integrated with a reconfigurable bus. The distributed shared memory system can be interfaced with other networks as well.

#### CHAPTER 2. SMART ARCHITECTURE

network. The extra circuitry is responsible for generating appropriate control signals which are specific to a particular network. The bus slave unit controls access to the bus side of the distributed shared memory. The bus slave unit constantly monitors network traffic and compares the destination processor ID field of the network with the local processor ID. If the result of the comparison matches, a read or write operation to the distributed shared memory is performed.

The distributed shared memory may have a main memory structure for a system with a large address space. In the case of a cache miss, due to the access through the shared address space or the front address space, the miss can be handled the same way as for the case of a single processor cache based system.

## 2.3 Reconfigurable Bus

### 2.3.1 Previous Work in Reconfigurable Bus Architectures

The matching of the multiprocessor structure to an algorithm has a fundamental influence on performance and cost effectiveness [26]. For instance, the hexagonally connected mesh is used for L-U decomposition. The binary tree is used for sorting. The double rooted tree is used for searching. Furthermore when an algorithm with an irregular communication pattern is mapped onto a multiprocessor system with a regular and fixed interconnection network, it is very difficult to schedule the algorithm to achieve efficient communications.

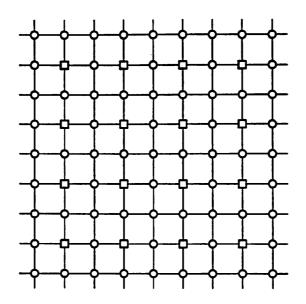

To alleviate this problem, reconfigurable interconnection schemes were proposed by several people. Synder has examined this problem in the CHiP architecture [72] [47]. The CHiP computer consists of three components: a collection of homogeneous processing elements (PE), a switch lattice, and a controller. As shown in Figure 2.8 (a) The switch lattice is a regular structure formed from programmable switches connected by data paths. The PEs are not directly connected to each other, but rather are connected at regular intervals to the switch lattice. A configuration setting enables the switch to establish a static, circuit switching connection between two or more of its incident data paths. In Figure 2.8, for instance, a mesh intercon-

(a) The switch lattice

(b) The switch lattice configured into a binary tree

,

Figure 2.8: The CHiP Architecture.

nection pattern of the PEs are reconfigured to a binary tree connection. In order to host a large number of switch lattice, the CHiP architecture requires wafer-scale integration (WSI).

Like the SMART architecture, the interconnection network is reconfigured to enable more efficient use of the hardware. The CHiP architecture is geared to the fine grain parallelism with thousands and millions of processing units. Hence the PEs, the switch lattice, and the controller have to be very simple to host a larger region of the switch lattice in a single chip. On the other hand, the reconfigurable bus of the SMART architecture is developed for the medium and coarse grain parallelism. It has the shared memory architecture and consists of extremely powerful processors (up to one hundred processor range).

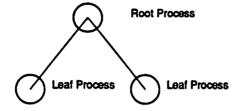

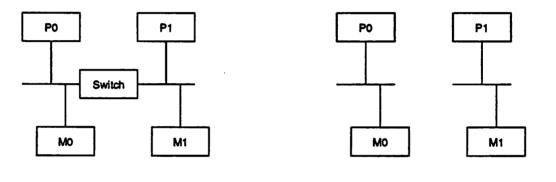

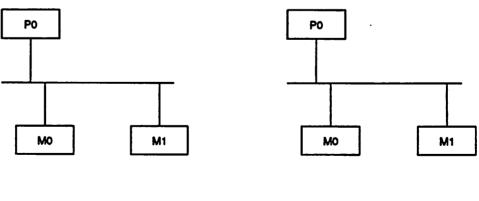

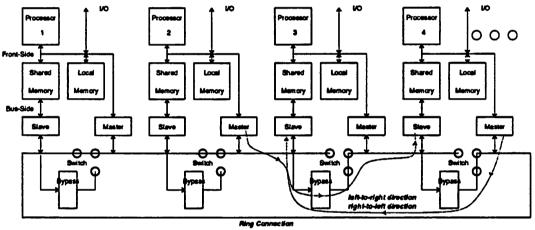

The reconfigurable bus for the coarse grain parallelism has been used in the MP/C system [59]. It has the shared memory aspect of the tightly coupled multiprocessor systems and the connection simplicity associated with the looselycoupled multicomputer systems. A large address space is partitioned into contiguous segments of memory that can be accessed by a single processor. The partitioning is accomplished by switching the buses. To demonstrate the operation of the MP/C, consider the 3-node tree structured multicomputer in Figure 2.9 (a). A typical tree algorithm will first run on the root node, then concurrently on the two leaves, and finally on the root again. Initially, P0 is active, playing the role of the root node, and it can access M0 and M1, as in Figure 2.9 (c). Then P1 is activated and each processor does the computation at a leaf, as in Figure 2.9 (d). Finally, P1 deactivates itself, P0 resumes the root's role and regains control over the whole address space, as in Figure 2.9 (e).

The MP/C architecture has some similarities with the SMART system, since it uses the memory segmentation and the bus switching. However, unlike the SMART system, in order to access shared data, the MP/C architecture must use the interconnection network, making the cost of accessing the shared data quite expensive. Furthermore, when the switch is open, the processors cannot access the shared memory on other buses at all. Therefore the applications are limited, and the programming effort is larger than the SMART system which has the *bypass* ability to bridge the .

(a) Three-node binary tree

(b) MP/C implementation

(d) Leaves active

(c) Root active

Figure 2.9: The MP/C Architecture.

gap between the separate buses.

# 2.3.2 Our Reconfigurable Bus

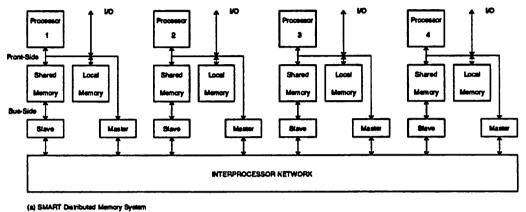

A high-speed reconfigurable bus for shared memory architecture was proposed to provide high performance and bandwidth at low cost for up to a 100 processor range. It alleviates the problems of the bus saturation typical for a single shared bus shared memory system. The basic function of the reconfigurable bus is to divide the single shared bus into several independent sections to increase usage of of the bus. A ring connection is formed by connecting one end of the bus to the other end of the bus to reduce the maximal distance between any two processors in the array.

Figure 2.10 (b) shows an example of a reconfigurable bus. Processor-1 and processor-2 have switches closed and processor-3 and processor-4 have switches opened. Switches can be opened and closeed dynamically under software control. When the buses are separated by open switches, they can be accessed simultaneously. For instance, the bus master unit of processor-1 may send a data word to the bus slave unit of processor-2. At the same time, the bus master unit of processor-3 can send a data word to the bus slave unit of processor-4.

When a group of processors is actively communicating with each other, we reduce the delay of communication between them by closing the bus switches in between. When they are not frequently communicating with each other, we increase the system throughput by opening the bus switches between the processors. Thus, we can obtain the efficient bus reconfiguration by trading the delay of global communication for the bus bandwidth. It is possible to dynamically reconfigure the bus under *hardware control*. It is called the self-reconfiguration bus, which is explained in Section 2.3.4.

A bypass unit which forwards the interprocessor communication from one bus to another is an important function of the system. As shown in Figure 2.10 (b), when the buses are disconnected, they are automatically linked by the bypass unit to support global communication. Through bypass units, the data may be sent through several buses automatically to reach the memory in other bus groups. Hence it is

(b) SMART Reconfigurable Bus

Figure 2.10: SMART Memory and Reconfigurable Bus.

possible to program independently of the bus reconfiguration. The program results can be logically the same, although the performance will be affected. Therefore the reconfigurable bus provides a simple programming environment to a programmer.

The bi-directional bypass and the self-reconfigurable bus features are important features for a large number of processors. The bi-directional bypass (both *left-to-right* and *right-to-left* directions) has the shorter average distance for the communication across the buses than the one-directional bypass (left to right direction) as shown in Figure 2.10 (b). On the other hand, the self-reconfigurable bus has switches dynamically reconfigured at every bus cycle. This allows the dynamic behavior of the bus which is hard to be achieved under *software control*. However, for a small number of processors, the performance gain is too small compared to the complexity of implementation. Those features were not implemented for the first prototype SMART system with 10 processors. Instead, the one-directional bypass and the software controlled reconfigurable bus were implemented.

# 2.3.3 Interprocessor Communication

Section 2.2, *Memory Structure*, has presented the shared distributed memory to achieve small interprocessor communication overhead. The previous section has described how the reconfigurable bus improves the performance of the single shared bus through reconfiguration, bypass and ring connection. This section shows a combined view of the shared distributed memory and the reconfigurable bus using a simple interprocessor communication example.

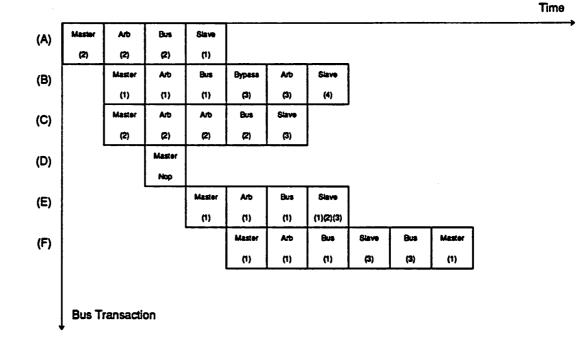

The Figure 2.11 shows how interprocessor communications (A-F) between the processor-1,2,3,4 are handled by the hardware in a pipelined fashion when the bus is configured as in Figure 2.10 (b). Recall that each processor has a distributed shared memory, a bus master unit, a bus slave unit and a bypass unit. Each box in Figure 2.11 represents a pipeline stage with horizontal axis showing the time unit (100ns) and the vertical axis representing the bus transactions. For example Master-2 represents a master cycle by processor-2 and Arb-3 represents an arbitration cycle by processor-3. . .

t

Figure 2.11: Bus Transaction for Interprocessor Communication.

#### CHAPTER 2. SMART ARCHITECTURE

Bus transaction-(A) is the write operation from processor-2 to processor-1's distributed shared memory. The communication will be later accomplished by the read operation by processor-1 from the Front Side Memory port. The first pipeline stage of the bus transaction-(A) is the master cycle, where the bus master unit of processor-2 receives the write request from the processor-2. At the second pipeline stage (arbitration cycle), the arbitration cycle selects the bus master unit or the bypass unit within the bus domain which has an access to the bus in the following cycle. A simple statically prioritized arbitration algorithm is implemented in hardware: a bypass unit has the higher priority then a master unit, and processors with a low identification number(ID) have higher priority than processors with a high ID. During the following bus cycle, data, address and control are placed on the reconfigurable bus by either the bus master unit or the bypass unit of processor-2. Then the bus slave unit of processor-1, which is always snooping the bus, finds out that the current bus transaction belongs to its own distributed shared memory and writes data to the distributed shared memory during the slave cycle. Sometime later when processor-1 needs the data sent by processor-2, it simply reads the data from the front side memory port without accessing the shared bus.

Bus transaction-(B) is another write operation from processor-1 to processor-4. However, since the switch of processor-3 is open, there is no direct path from processor-1 to processor-4. During the bus cycle, the processor-3's bypass unit, which is activated as a result of an opened switch, detects that the current transaction to processor-4 should be forwarded to the adjacent bus. Therefore the bypass unit latches the contents of the bus into the *bypass queue*, generates an arbitration request, and place the copy on the adjacent bus. The slave unit of processor-4 will update the distributed memory accordingly. If there are more than one bypass unit involved in the transaction, each bypass unit will take two extra cycles to forward the data to the next bus.

When the bus transaction-(B) was generated by processor-1, bus transaction-(C) was simultaneously initiated by processor-2. Since the bus couldn't accommodate two data at the same time, the transaction-(B) was granted the first arbitration, and the transaction-(C) was suspended for one pipeline stage. Then it tried for another

#### CHAPTER 2. SMART ARCHITECTURE

bus arbitration and won the following arbitration. After the arbitration cycle, the bus cycle and the slave cycle executes the same pipeline stages as transaction-(A).

Bus transaction-(D) is a NOP (No OPeration), which means no bus mater or bypass unit wants to use the bus at that time.

Bus transaction-(E) represents bus read operation from processor-1 to processor-3's distributed shared memory. The bus master cycle and arbitration cycle operates the same way as in the case of write operation. However the bus cycle consists of the following three sub-pipeline stages: At the first stage, the address and control signals are placed on the bus, which will be latched by the slave unit-3. During the following stage, it will read the data from its bus side memory port. At the last stage the data will be placed on the bus by slave unit-3 and latched by bus master unit-1. Then the data will be forwarded to processor-1, which has been waiting for the arrival of the data.

The bus transaction-(F) is a broadcast from processor-1 to processor-1, 2, 3. Since it's a broadcast, all the bus slave unit will update its memory. The broadcast can be bypassed through switches as the same way as the bypass write operation.

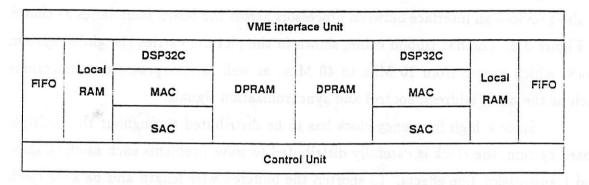

All the functional blocks of reconfigurable bus such as the bus master unit, the bus slave unit, the bypass unit, the switch, the arbitration and other functions are implemented as 2 VLSI chips: Master Access Controller (MAC) and Slave Access Controller (SAC). The details of those chips are described in Section 3.4.

# 2.3.4 Self-Reconfigurable Bus

The reconfigurable bus presented in previous sections was reconfigured under software control. Changes in the switch configuration had to be specified in the program. Sometimes it is not clear what the optimal bus reconfiguration is for a given algorithm. The optimal reconfiguration may be hard to estimate or even change frequently during the different phases of the algorithm. Therefore the architecture of the self-reconfigurable bus is developed to dynamically and automatically reconfigure the bus under hardware control.

The self-reconfigurable bus has a couple of major advantages over the soft-

ware reconfigurable bus. First of all, the programmer or the automatic scheduler does not have to know anything about the bus switches and their reconfigurations. Therefore it reduces some of the programming effort. Second, switches are dynamically reconfigured at every bus cycle. Therefore the network can be reconfigured to maximally utilize the bus resources.

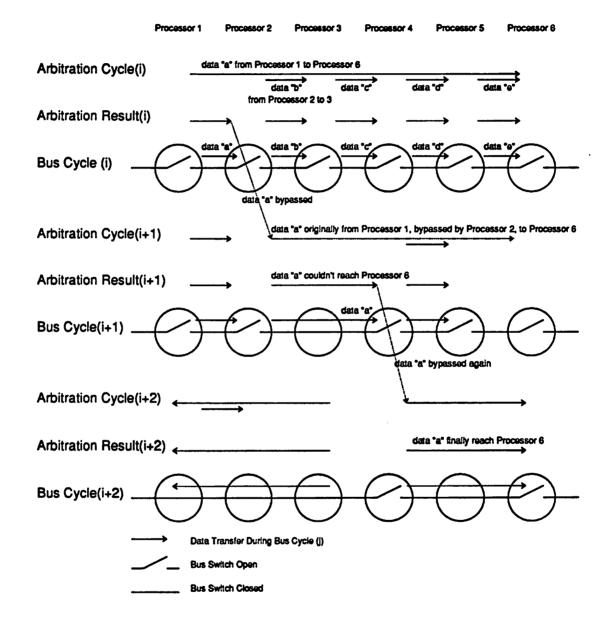

The bus transaction consists of four cycles, as in the reconfigurable bus: a master cycle, an arbitration cycle, a bus cycle, and a slave cycle. The arbitration cycle is the main source of the difference. The arbitration is not used to decide which processor will be granted access to the bus as in the reconfigurable bus, but rather is used to find out which processor will be given which portion of the bus in the following cycle. In other words, switch reconfiguration is determined simultaneously with the arbitration. When a data word needs to be transferred through the bus switch in one bus cycle the switch will be closed, otherwise the switch will be opened.

Figure 2.12 shows three examples of self-reconfigured bus at bus cycle-(i),(i+1),(i+2). For example, at bus cycle (i+2), processor-3 transfers data to processor-1 and processor-4 transfers data to processor-6, and switches are reconfigured accordingly.