### KLAUS ERIK SCHAUSER

### Department of Electrical Engineering and Computer Science Computer Science Division University of California, Berkeley

### Compiling Dataflow into Threads

Efficient Compiler-Controlled Multithreading for Lenient Parallel Languages

July 2, 1991

### **RESEARCH PROJECT**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California, Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II.

Approval for the Report and Comprehensive Examination:

| Committee: | Prof. David E. Culler | Research Advisor |

|------------|-----------------------|------------------|

|            | 7/3/91                | Date             |

|            | Prof. D. A. Patterson | Second Reader    |

|            | 7/9/91                | Date             |

### Compiling Dataflow into Threads

Efficient Compiler-Controlled Multithreading for Lenient Parallel Languages

Klaus Erik Schauser

Department of Electrical Engineering and Computer Science Computer Science Division University of California, Berkeley

July, 1991

This work was supported by National Science Foundation PYI Award (CCR-9058342) with matching funds from Motorola Inc. and the TRW Foundation. Support was also received from the International Computer Science Institute, and computational resources were provided, in part, under NSF Infrastructure Grant CDA-8722788.

### Compiling Dataflow into Threads

Efficient Compiler-Controlled Multithreading for Lenient Parallel Languages

Klaus Erik Schauser

### Abstract

Powerful non-strict parallel languages require fast dynamic scheduling. This thesis explores how the need for multithreaded execution can be addressed as a compilation problem, to achieve switching rates approaching what hardware mechanisms might provide. Compiler-controlled multithreading is examined through compilation of a lenient parallel language, ID90, for a threaded abstract machine, TAM. A key feature of TAM is that synchronization is explicit and occurs only at the start of a thread, so that a simple cost model can be applied. A scheduling hierarchy allows the compiler to schedule logically related threads closely together in time and to use registers across threads. Remote communication is via message sends and split-phase memory accesses. Messages and memory replies are received by compiler-generated message handlers which rapidly integrate these events with thread scheduling.

To compile ID90 for TAM, we employ a new parallel intermediate form, dualgraphs, with distinct control and data arcs. This provides a clean framework for partitioning the program into threads, scheduling threads, and managing registers under asynchronous execution. The compilation process is described and preliminary measurements of the effectiveness of the approach are discussed.

Previous to this work, execution of Id90 programs was limited to specialized architectures or dataflow graph interpreters. By compiling via TAM, we have achieved more than two orders of magnitude performance improvement over graph interpreters on conventional machines, making this Id90 implementation competitive with machines supporting dynamic instruction scheduling in hardware. Timing measurements show that our Id90 implementation on a standard RISC can achieve a performance close to Id90 on one processor of the recent dataflow machine Monsoon. It can be seen that the TAM partitioning presented in this thesis reduces the control overhead substantially and that more aggressive partitioning would yield modest additional benefit. There is, however, considerable room for improvement in scheduling and register management.

# Acknowledgements

There is nothing more exciting than working in a small group of motivated people who want to revolutionize the world. The work described in this thesis is the result of fruitful collaboration within the Berkeley TAM group. I would like to thank all its members, Professor David Culler, Professor John Wawrzynek, Thorsten von Eicken, Seth C. Goldstein, Mike Flaster, Meltin Bell, and Anurag Sah.

I am especially thankful to my advisor, Professor David Culler, for his support. He provided me with more ideas than I could implement, asked more questions than I could answer, and helped me write the thesis. Together we developed dual graphs and explored what really is behind dataflow.

I am grateful to Professor David Patterson, my second reader, for teaching me a quantitative approach to computer architecture. He carefully read my thesis and gave many helpful comments.

This work would not have been possible without the various implementations of our threaded abstract machine. I want to thank Thorsten von Eicken, our Unix wizard and my office mate, for producing a stable nCUBE backend, Seth C. Goldstein for his user friendly C backend, Mike Flaster and Ethan Bernstein for their fast native MIPS backend, as well as Anurag Sah for his shared memory Sequent implementation.

I would also like to thank all the members of Professor Arvind's Computation Structures Group of MIT for providing us with their Id compiler, answering all our questions about it, and for making changes to it at our request.

Finally, I want to thank Krste Asanović for being a perfectionist. I learned my lesson: working with you takes twice as long.

My deepest appreciation goes to Martina, my wife, for her patience, love, and support, and to my little daughter, Natalie, for her impatience, love, and need for support. I know, the world is terrible when Daddy has to work. Für Martina und Natalie

# Contents

| 1 | Con | npilation Challenge             | 6               |

|---|-----|---------------------------------|-----------------|

|   | 1.1 | Overview                        | 7               |

|   | 1.2 | Language Issues                 | 8               |

|   | 1.3 | ТАМ                             | 9               |

|   | 1.4 | Id90-to-TAM Compilation Stages  | 11              |

| 2 | Dua | l Graphs                        | 14              |

|   | 2.1 | Dual Graph Definition           | 14              |

|   | 2.2 | Generation of dual graphs       | 17              |

|   |     | 2.2.1 Basic Operators           | 18              |

|   |     | 2.2.2 Literals                  | 20              |

|   |     |                                 | 20              |

|   |     |                                 | 20              |

|   |     | 2.2.5 I-Structure Operations    | 23              |

|   |     |                                 | 24              |

|   |     | -                               | 25              |

|   |     |                                 | 27              |

|   | 2.3 | Combining Dual Graph Expansions | $\overline{29}$ |

|   | 2.4 |                                 | 30              |

| 3 | Par | titioning                       | 33              |

|   | 3.1 | 0                               | 34              |

|   | 3.2 |                                 | 37              |

|   |     |                                 | 37              |

|   |     | 1 0                             | 37              |

|   |     |                                 | 37              |

|   |     | · ·                             | 38              |

|   | 3.3 |                                 | 39              |

|   |     |                                 | 39              |

|   |     |                                 | 40              |

|   | 3.4 |                                 | 42              |

|   | 3.5 |                                 | 46              |

|   | 3.6 |                                 | 46              |

|   | 3.7 |                                 | 47              |

| 4              | $\mathbf{T}\mathbf{hr}$ | ead Generation                          | 50 |

|----------------|-------------------------|-----------------------------------------|----|

|                | 4.1                     | Lifetime analysis                       | 50 |

|                | 4.2                     | Determining Types                       | 51 |

|                | 4.3                     | Instruction Scheduling                  | 52 |

|                | 4.4                     | Frame slot and register assignment      | 52 |

|                | 4.5                     | Move insertion: Name unifying at merges | 52 |

|                | 4.6                     | Entry counts                            | 54 |

|                | 4.7                     | Fork insertion                          | 55 |

|                | 4.8                     | Thread ordering                         | 56 |

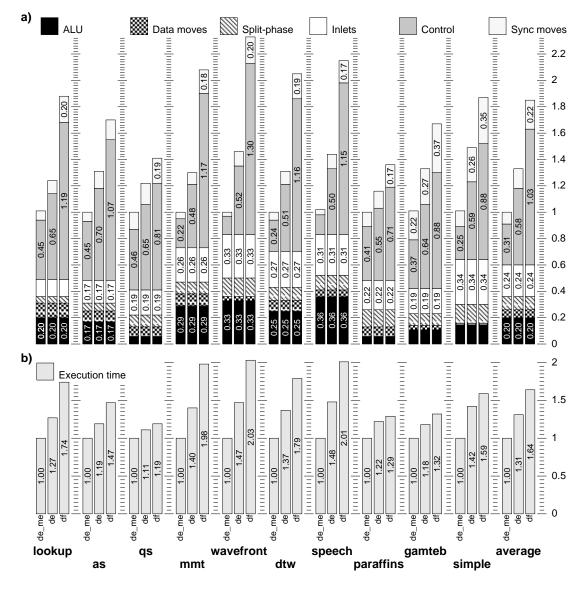

| 5 Code Quality |                         | e Quality                               | 59 |

|                | 5.1                     | Benchmarks                              | 59 |

|                | 5.2                     | Timings                                 | 60 |

|                | 5.3                     | TAM vs Dataflow                         | 62 |

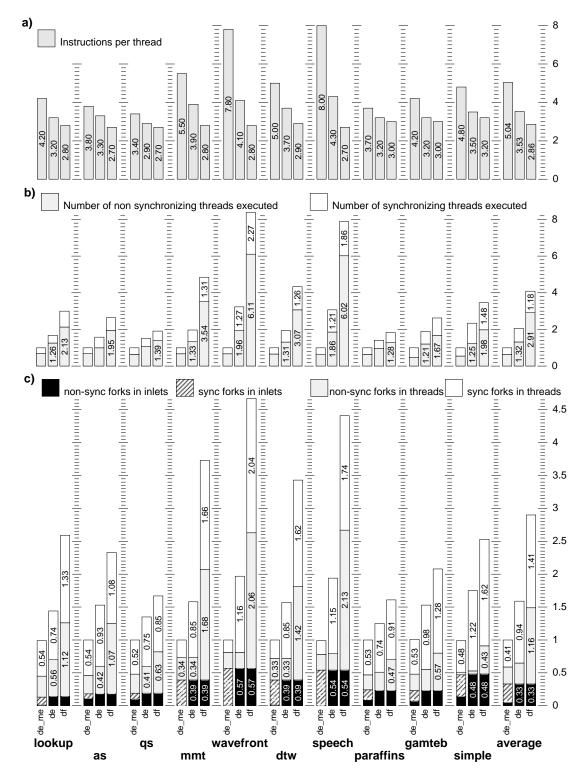

|                | 5.4                     | Thread Characteristics                  | 64 |

|                | 5.5                     | Dynamic Scheduling                      | 66 |

| 6              | Con                     | clusion and future work                 | 68 |

# List of Figures

| 1.1  | Compilation Paths                                                            | 7  |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Small Id90 programs                                                          | 9  |

| 1.3  | Overview of Id90 to TAM compiler. Shown in gray are other compilation        |    |

|      | approaches                                                                   | 12 |

| 2.1  | Dual Graph Arcs                                                              | 15 |

| 2.2  | Dual Graph Nodes. (Arcs: dash = data, solid = control, curly = dependence)   | 15 |

| 2.3  | I 1                                                                          | 17 |

| 2.4  | Example with redundant control arc                                           | 18 |

| 2.5  | Dual graph expansion for unary instructions.                                 | 19 |

| 2.6  |                                                                              | 19 |

| 2.7  |                                                                              | 20 |

| 2.8  | Dual graph expansion for conditionals                                        | 21 |

| 2.9  |                                                                              | 22 |

| 2.10 | Dual graph expansion for I-structure fetch.                                  | 23 |

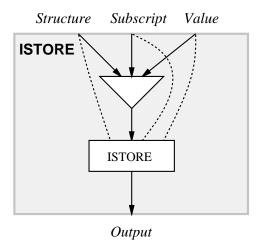

| 2.11 | Dual graph expansion for I-structure store.                                  | 24 |

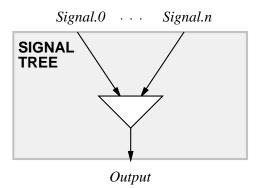

| 2.12 | Dual graph expansion for signal trees.                                       | 24 |

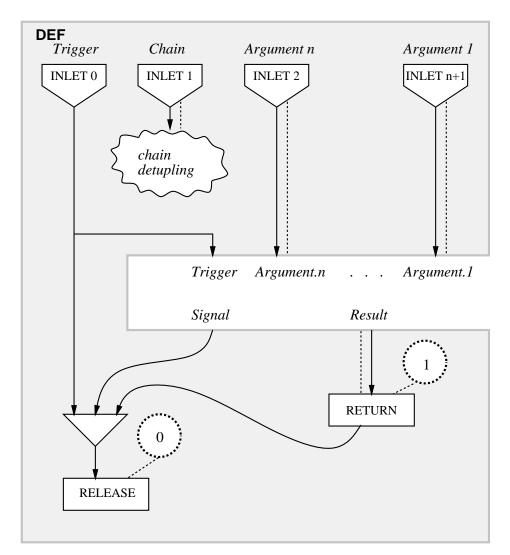

| 2.13 | Dual graph expansion for function definitions                                | 25 |

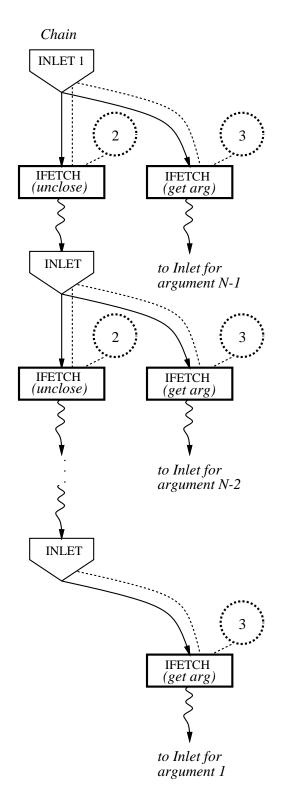

| 2.14 | Dual graph expansion for chain detupling                                     | 26 |

| 2.15 | Closure Structure.                                                           | 27 |

| 2.16 | Dual graph expansion for function application.                               | 28 |

| 2.17 | Dual graph expansion for direct apply                                        | 29 |

| 2.18 | Combining dual graph expansions                                              | 30 |

| 2.19 | Program graph for lookup example                                             | 31 |

| 2.20 | Dual graph for lookup example                                                | 32 |

|      |                                                                              |    |

| 3.1  | 1                                                                            | 34 |

| 3.2  | 1                                                                            | 35 |

| 3.3  |                                                                              | 36 |

| 3.4  | Merge Up: A partition with a single control predecessor can be merged up if  |    |

|      | 1                                                                            | 39 |

| 3.5  | Merge Down: The results of a partition feed strictly into a successor, so it |    |

|      | 0                                                                            | 40 |

| 3.6  | Configurations where merging could occur.                                    | 41 |

| 3.7  |                                                                              | 41 |

| 3.8  | Example where dependence sets partitioning works better than dominance       |    |

|      | sets partitioning.                                                           | 43 |

| 3.9                                       | Example where dominance sets partitioning works better than dependence                                                                                  |                |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                           | sets partitioning.                                                                                                                                      | 44             |

| 3.10                                      | Dependence sets and dominance sets partitioning.                                                                                                        | 45             |

| 3.11                                      | Redundant Arc Elimination Rule                                                                                                                          | 46             |

| 3.12                                      | Switch and Merge Combining                                                                                                                              | 47             |

|                                           | Control Graph for lookup after merging                                                                                                                  | 48             |

|                                           | Final Dual Graph for lookup after merging, redundant arc elimination and                                                                                |                |

|                                           | combining                                                                                                                                               | 49             |

|                                           |                                                                                                                                                         |                |

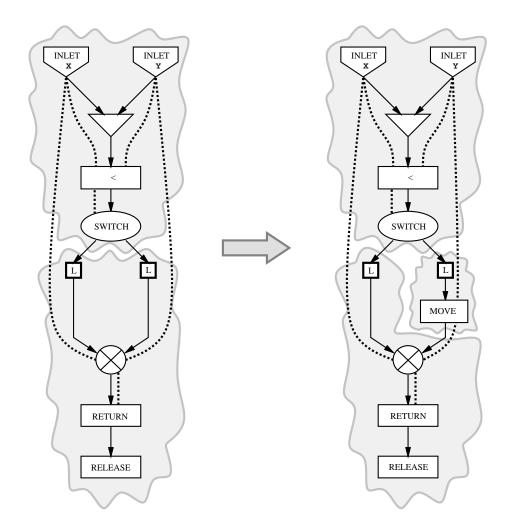

| 4.1                                       | Partitioned dual graph before and after move insertion for function max                                                                                 | 54             |

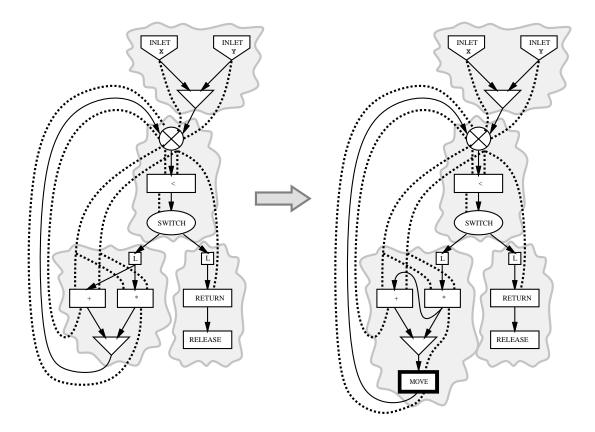

| $4.1 \\ 4.2$                              | Partitioned dual graph before and after move insertion for function max<br>Partitioned dual graph before and after move insertion for function loop_ex. | $54 \\ 55$     |

|                                           |                                                                                                                                                         | -              |

| 4.2                                       | Partitioned dual graph before and after move insertion for function loop_ex.                                                                            | 55             |

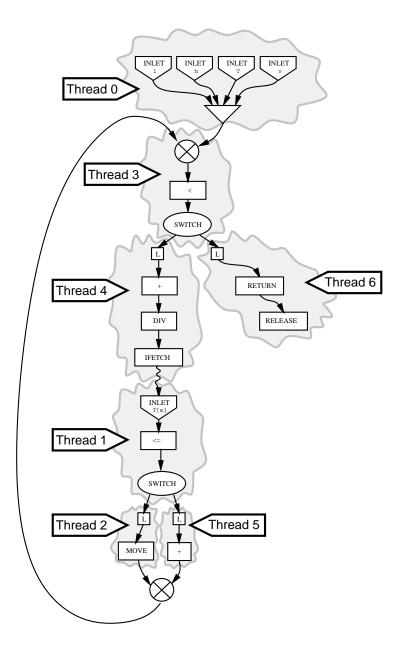

| $\begin{array}{c} 4.2 \\ 4.3 \end{array}$ | Partitioned dual graph before and after move insertion for function loop_ex.<br>Final dual graph for lookup example after thread generation.            | 55<br>57       |

| 4.2<br>4.3<br>4.4                         | Partitioned dual graph before and after move insertion for function loop_ex.<br>Final dual graph for lookup example after thread generation             | 55<br>57<br>58 |

# List of Tables

| 5.1 | Benchmark programs                                     | 60 |

|-----|--------------------------------------------------------|----|

| 5.2 | Run-time in seconds                                    | 60 |

| 5.3 | Run-time in seconds on Monsoon and TAM (on Mips R3000) | 61 |

| 5.4 | Dynamic Scheduling Behaviour                           | 66 |

### Chapter 1

# **Compilation Challenge**

Multithreaded execution appears to be a key ingredient in general purpose parallel computing systems. Many researchers suggest that processors should support multiple instruction streams and switch very rapidly between them in response to remote memory reference latencies or synchronization [AI87, Smi90, HF88, ALKK90, ACC<sup>+</sup>90]. However, the proposed architectural solutions make thread scheduling invisible to the compiler, preventing it from applying optimizations that might reduce the cost of thread switching or improve scheduling based on analysis of the program. Inherently parallel languages, such as Id90[Nik90] and Multilisp[Hal85], require that small execution threads be scheduled dynamically, even if executed on a single processor [Tra88]. Traub's theoretical work demonstrates how to minimize thread switching for these languages on sequential machines. However, in compiling this class of languages for parallel machines, the goal is not simply to minimize the number of thread switches, but to minimize the total cost of synchronization while tolerating latency on remote references and making effective use of critical processor resources, such as registers and cache bandwidth. This thesis addresses this three-fold goal in compiling Id90 for execution on a threaded abstract machine, TAM, that exposes these costs to the compiler through explicit scheduling and storage hierarchies. TAM can be efficiently implemented on standard sequential and parallel machines,

Both the compilation of sequential languages for standard architectures [AU77] as well as the compilation of non-strict parallel languages for dataflow machines [Tra86] is well understood. The storage model of conventional machines is directly reflected in most sequential languages. The control structures provided by those languages can be easily mapped to standard processors which follow only one path of execution.

Non-strict parallel languages, such as Id90, allow functions to execute and possibly return results before all arguments have been provided. This requires dynamic scheduling. Non-strict languages can be implemented efficiently on dataflow and multithreaded architectures, because those machine provide hardware support for fast dynamic synchronization and scheduling of threads of computation. Execution of these languages on standard machines was long viewed as inefficient, and special architectural support was thought to be essential.

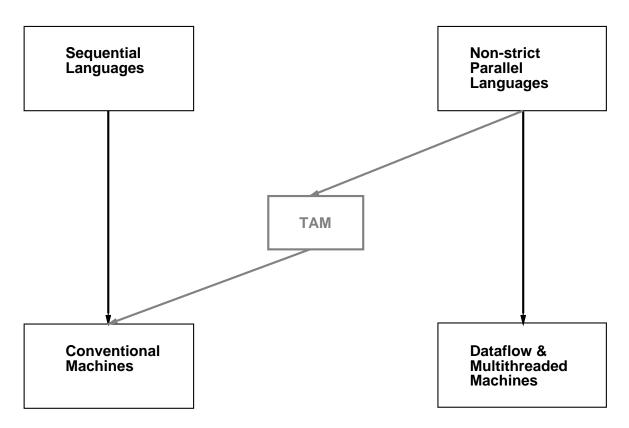

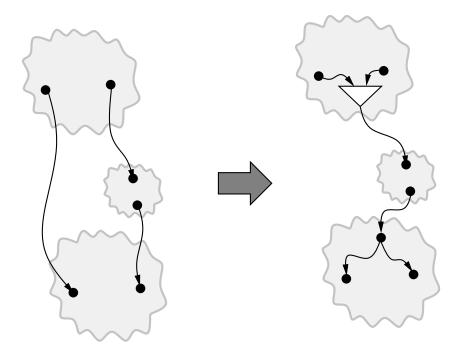

Our approach shows how multithreaded execution can be addressed as a compilation problem, rather than one that needs special architectural solutions. We have designed an abstract threaded machine, which we use as an intermediate form in the compilation of Id90 to standard machines (see Figure 1.1). TAM provides simple primitives to the compiler for scheduling, synchronization and fast message transmission. Although it would be possible

Figure 1.1: Compilation Paths.

to build TAM directly in hardware, it can be translated efficiently to standard parallel and sequential machines. The advantage of TAM over other multithreaded approaches is that it allows the compiler to exploit locality among threads and integrate thread scheduling, processor register assignment and message handling in code generation. Using TAM, compiling Id90 to standard machines, although still challenging, is doable and results in efficient code as our implementation demonstrates.

### 1.1 Overview

This thesis aims to demonstrate how to compile non-strict parallel languages for a multithreaded execution model. In this chapter we first analyze why non-strict parallel languages offer so much parallelism and discuss why they are difficult to implement on standard machines. We present the extended functional language Id90, which is taken as a starting point. We then discuss the main features of TAM, the threaded abstract machine into which we compile. In Chapter 2, we introduce a new intermediate form, called dual graphs, which provides a vehicle for integrated treatment of thread scheduling and register usage. In dual graphs, control and data dependences are separate, but stand on an equal footing. We show how dual graphs are produced for the basic constructs of the language. Chapter 3 then presents partitioning, the fundamental step in compiling a lenient language for a machine that executes instruction sequences. The task of the various partitioning algorithms is to identify portions of the graph that can safely be mapped into threads. The actual thread generation, which includes frame slot and register assignment, instruction scheduling and thread scheduling, is discussed in Chapter 4. Finally, preliminary results are presented in Chapter 5.

### 1.2 Language Issues

We are using the parallel functional language Id90[Nik90] as a starting point. Id90 is a nonstrict but eager language. Traub uses the term *lenient* for this class of languages[Tra88]. A language is called *non-strict*, if it may be necessary to start computation of a function body before all (or even any) arguments have been provided. Conversely, it is called *strict* if all arguments can be evaluated before calling a function. Non-strictness gives the programmer much more expressive power, but at the expense of implementation and execution cost: nonstrict languages require dynamic scheduling of computations, they cannot be completely scheduled statically, as examples given below will show. A language is called *lazy* if it starts computations only when it needs their result, *e.g.* a function would start evaluation of its arguments only by demand. The language is *eager* if all evaluations are started as soon as possible. It is the responsibility of the programmer to avoid divergent computations.

Functional languages are a good basis for a parallel computing, since they offer ample opportunities for implicit parallelism. In pure (side-effect free) functional languages, arguments to a function call can be evaluated in parallel. Non-strictness can substantially enhance the parallelism by allowing functions and arbitrary expressions (even conditionals) to execute and possibly return results before all arguments have been provided. This results in an overlap of computation between the function body and the argument evaluation. Non-strict, but eager, parallel functional languages, such as Id90, exhibit a large amount of parallelism on all levels[ACM88, Cul90, AE88]. Id90 would would exhibit less parallelism if the language were lazy, because then evaluation of arguments could only be started when functions need the corresponding value. This tends to lengthen substantially the critical path, *i.e.*, the time from the start of the computation to when the result is produced.

We begin with several examples in Id90 to indicate the subtlety of compiling such a language and the need for multithreading. These are not intended to be indicative of important applications, but serve to demonstrate the compilation principles. The function lookup\_array, as shown in Figure 1.2, takes as arguments an array A of values and an ordered table T and returns an array of the table indexes corresponding to the values in A. There is very little parallelism in the lookup function, however, all the lookups can be performed in parallel. Each access to T[m] in the lookup may require a remote access or may even suspend, if the table T is still being produced by some other part of the program. Thus, we want to execute several lookups on each processor and be able to suspend and resume them cheaply upon remote or deferred access. Flat produces a list of the leaves of a binary tree using accumulation lists which are constructed with the build-in function cons. If cons and flat were strict, this code would exhibit no parallelism. Under lenient execution, the entire list is constructed in parallel[Nik91]. Simulations showed that with non-strictness the critical path on an example of a full binary tree of depth 10 constists of 250 time steps; with a maximum parallelism of 1776 and an average parallelism of 266 instructions (assuming the resources were available). If executed strictly, the critical path would grow to 26.650 time steps, with a maximum parallelism of 4 instructions. The contrived function two\_things returns a pair containing the square of its first argument and the product of its two arguments. It can compute and return  $\mathbf{x} \star \mathbf{x}$  before  $\mathbf{y}$  has been evaluated, which enhances parallelism. In fact, it must be able to do so, since the first result could be used as the second

```

def lookup_array A T = {(al,ah) = bounds A;

(tl,th) = bounds T;

in {array (al,ah) of

[i] = (lookup tl th T A[i]) || i <- al to ah}};</pre>

def lookup l h T v = {while l < h do</pre>

m = div (1 + h) 2;

next l, next h = if (v <= T[m]) then (l,m)

else (m+1,h)

finally 1};

def flat tree acc = if (leaf tree) then (cons tree acc)

else flat (left tree) (flat (right tree) acc);

def two_things x y = (x*x, x*y);

def cube x = {a,b = two_things x,a;

in b};

def strange x p = {a,b,c = if p then bb, x, aa else x, aa, bb;

aa = 3*a;

bb = 4*b;

in c};

```

Figure 1.2: Small Id90 programs

argument, as in the unusual function cube. The final example, due to Traub[Tra88], shows a cyclic dependence through a conditional that must be resolved dynamically. Because of the three mutually recursive bindings, no top to bottom static ordering of the statements yields a correct execution.

None of these examples present problems for a machine with dynamic instruction scheduling, such as Monsoon[PC90]. At the same time, none require dynamic scheduling throughout. Thus, it makes sense to investigate hybrid execution modes[Ian88a], where statically ordered *threads* are scheduled dynamically. Our TAM model takes this idea one step further by exposing the scheduling of threads to the compiler as well, so even the dynamic scheduling is done without hardware support. This allows register management to be closely tied to thread scheduling in order to minimize the overhead where dynamic scheduling is required. In the following, we use the lookup function to illustrate the compilation techniques.

### 1.3 TAM

To investigate compiler-controlled multithreading, a simple threaded abstract machine (TAM) has been developed. Synchronization, thread scheduling and storage management are explicit in the machine language and, thus, exposed to the compiler. TAM is presented elsewhere[CSS<sup>+</sup>91, vESC91]; in this section we describe the salient features of TAM as a compilation target. The primary design goal in TAM is to provide a means of exploiting locality, even under asynchronous execution, to minimize the overhead of multithreading.

TAM also provides a separation of concerns, since to execute programs compiled to TAM we expand the TAM instructions into machine code for a particular target architecture in a separate compilation step.

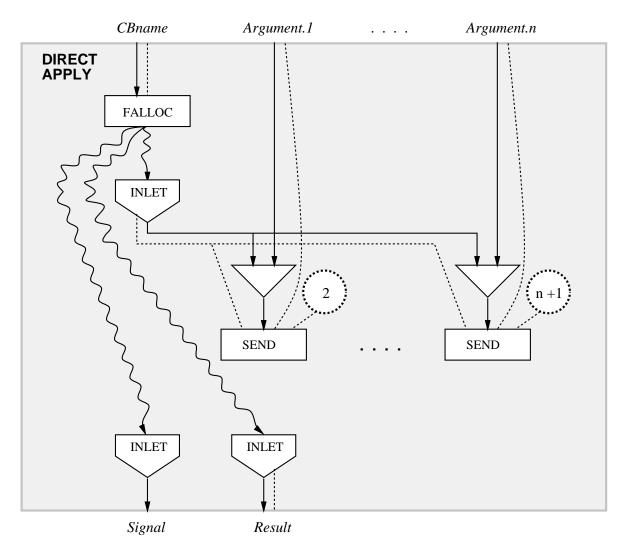

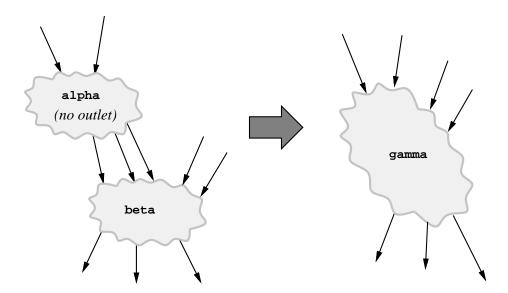

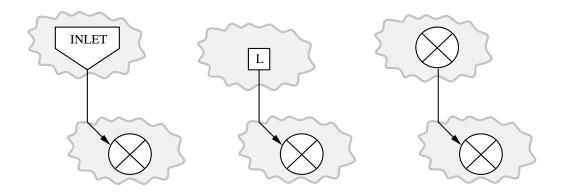

A TAM program is a collection of *code-blocks*, typically representing functions in the program text. Each code-block comprises several *threads* and *inlets* described below. Invoking a code-block involves allocating an *activation frame* to hold its local variables, depositing argument values into the (possibly remote) frame and enabling threads within the codeblock for execution in the context of the frame. Since an activation does not suspend when it invokes a subordinate, the dynamic call structure is represented by a tree of activation frames, rather than a stack. Instructions in a thread may refer to slots in the current frame or processor registers. A frame is said to be *resident* when a processor is executing threads relative to the frame. Once a frame is made resident, it remains resident as long as it has enabled threads. A *quantum* is the set of threads executed during a single residency.

A thread is simply a sequence of instructions; it contains no jumps or suspension points; synchronization occurs only at the top of a thread. TAM control primitives initiate or terminate threads. *Fork* attempts to enable a thread in the current activation. The *stop* instruction terminates its thread and causes some other enabled thread to begin execution. Conditional execution is supported by a *cfork* operation, which forks one of two threads, based on a boolean operand. Merging of conditionally executed threads is implicit, since the arms of a conditional can both contain a fork to a common thread.

In essence, each thread begins with a multiway join. A thread may have associated with it a frame slot containing its *entry count*. The entry count is initialized prior to any fork of the thread with the number of control paths joining. Each time the thread is forked, its entry count is decremented. The thread is enabled when the entry count reaches zero. Threads with a single entry need no associated entry count slot.

This Fork-based control paradigm is somewhat unusual and merits discussion. Fork generalizes branch, since a branch can be simulated by a fork followed by a stop. When fork and stop are separated by a sequence of instructions, it serves as a generalized delayed branch. On a machine that executes multiple threads concurrently, fork generates parallel activity; otherwise, it builds up a queue of threads that can be run while waiting for long latency requests and synchronization events to complete. Architecturally, providing fork, rather than branch, is interesting because it allows instruction fetch and execution to be decoupled without branch prediction. From a compiling viewpoint, mixing forks and branches presents very tricky code-generation issues[Tra88], especially in handling "nonstrict" conditionals where computations must started even if not all inputs to the conditional are available. It should be noted, however, that when mapping TAM to native code for existing machines fork and stop are removed whenever possible to produce a branch or fall-through.

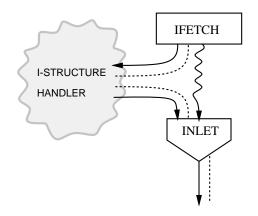

TAM assumes that an activation will execute on a single processor; so work is distributed over processors at the activation level. Thus, passing arguments and results between frames represents (possible) interprocessor communication. The *send* operation delivers a sequence of data values to an *inlet* relative to the target frame. An inlet is a restricted thread that primarily serves to extract data from a message, deposit it into specific slots in the designated frame, and fork threads for the corresponding activation. Inlets are compiler generated message handlers that avoid message parsing. An inlet may interrupt a thread, but it does not disturb the current quantum. Threads enabled by executing the inlet will run when its frame becomes resident.

TAM provides a specialized form of send to support split-phase access to data structures.

The heap is assumed to be distributed over processors, so access to a data element may require interprocessor communication. In addition, accesses may be synchronizing, as with I-structures[ANP87] where a read of an empty element is deferred until the corresponding store takes place. The I-Read, I-Fetch, and I-Take operations generate a request for a particular heap location and the response is received by an inlet. Meanwhile, the processor may continue with other enabled threads or, if none remain, will start working on another activation frame.

Scheduling in TAM is primarily under compiler control and is tied closely to the storage hierarchy. The first level of scheduling is reflected by the static partitioning of instructions into threads and ordering within threads. Values defined and used within a thread can be retained in processor registers. The next level of scheduling is dynamic — a quantum. Threads enabled by *fork* or *cfork* operations execute within the same quantum as the fork. However, the order of execution of the threads is not determined. Values can be transmitted in registers between threads in a quantum. When no enabled threads remain, another activation with enabled threads must be made resident. This is also under compiler control. The scheduling queue is contained within the frames, and the last thread executed in a quantum, called the *leave thread*, includes code to locate the next activation and fork to a designated *enter thread* within that activation. Registers can be used to carry values between threads within a quantum. Empirical studies show that quanta are often large, crossing many points of possible suspension[CSS<sup>+</sup>91]. Thus, it is advantageous for the compiler to be able to keep values in registers between threads that it cannot prove will execute in a single quantum. The leave and enter threads can save and restore specific registers if the guess proves incorrect.

The task of compiling for TAM has two aspects. First, a program must be partitioned into valid threads. This aspect is constrained partly by the language and partly by the execution model. The language dictates which portions of the program can be scheduled statically and which require dynamic synchronization. An elegant theoretical framework for addressing the language requirements is provided by Traub's work[Tra88]. The execution model places further constraints on partitioning, since synchronization only occurs at the entry to a thread and conditional execution occurs only between threads.

The second aspect is management of processor and storage resources in the context of dynamic scheduling to gain maximum performance. This involves analysis of expected quantum boundaries, frame and register assignment under asynchronous thread scheduling, and generation of inlets.

### 1.4 Id90-to-TAM Compilation Stages

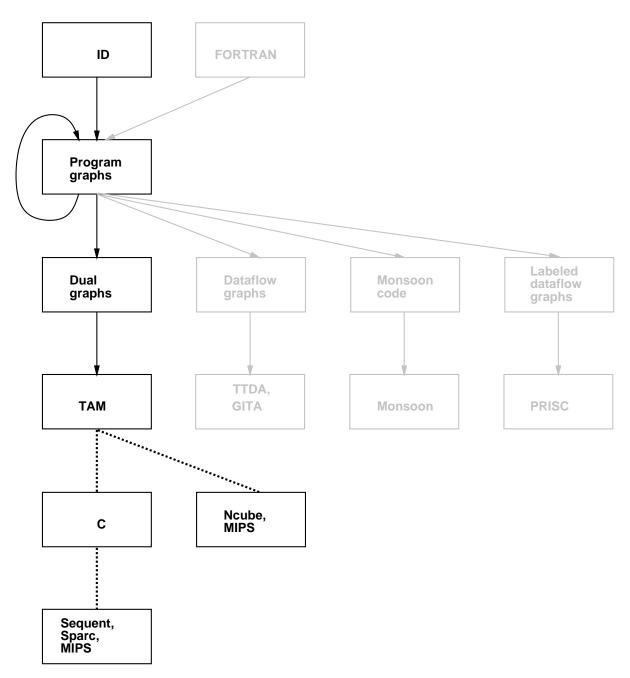

Figure 1.3 gives an overview of the structure of the Id90 to TAM compiler. Id90 programs are first translated into program graphs by an Id90 front-end from MIT[Tra86]. Program graphs are a hierarchical graphical intermediate form with only one kind of arc. Program graphs allow a representation of the various basic operations as well as conditionals, function definition and application. This facilitates powerful high-level optimizations, such as motion of arbitrarily large program constructs across loops or conditionals. The meaning of program graphs is given in terms of a dataflow firing rule, so control flow is implicitly prescribed by the dynamic propagation of values. In our threaded execution model, control is explicit and the flow of data is implicit in the use of registers and frame slots. In order to bridge this gap, we introduce a new graphical intermediate form, *dual graphs*, in which control and

data flow are both explicit.

Figure 1.3: Overview of Id90 to TAM compiler. Shown in gray are other compilation approaches.

Dual graphs are generated by expanding dataflow program graph nodes into equivalent dual graphs. This is a local transformation and can be achieved by following expansion rules for the individual program graph nodes. Compilation to TAM then involves a series of transformations on the dual graph, including partitioning, lifetime analysis, scheduling and linearization, register and frame-slot allocation and fork insertion. Finally TAM code is produced. All these steps, together with dual graphs, will be described in more detail in the next chapters.

TAM is left intentionally abstract, so that it could be implemented on sequential machines, shared-memory machines as well as on message passing machines. TAM is concrete enough though that it can be translated with ease in a second translation step to actual machines. One translation path has chosen C as a portable "intermediate form" and is producing code for parallel machines like the Sequent Symetry[Sah91] and Motorola Delta, as well as for various standard sequential machines. Other backends translate TAM directly into machine code. Currently there exists backends for the MIPS processor and for the parallel Ncube/2.

The figure also shows in gray other compilation approaches that chose program graphs as their intermediate form. The original MIT compiler translated program graphs into dataflow graphs which then could be executed on the Tagged Token Dataflow Architecture (TTDA)[ACI+83] or be interpreted by a graph interpreter (GITA). Other backends translate program graphs for the Monsoon dataflow machine [PC90] and for the P-RISC machine[NA89]. Some other very interesting approaches compile FORTRAN programs into representations similar to program graphs[BP89, FOW87].

### Chapter 2

# **Dual Graphs**

Compilation of Id90 to TAM begins after generation of dataflow program graphs. The meaning of program graphs is given in terms of a dataflow firing rule, so control flow is implicitly prescribed by the dynamic propagation of values. In our threaded execution model, control is explicit and the flow of data is implicit in the use of registers and frame slots. In order to bridge this gap, we introduce a new graphical intermediate form, *dual graphs*, in which control and data flow are both explicit. The dual graph thus tries to capture both the contents of a conventional control flow graph as well as those of a pure dataflow graph. Dual graphs are similar in form to the data structures used in most optimizing compilers; the key differences are that they describe parallel control flow and are in static single assignment form[CFR<sup>+</sup>89].

Compilation to TAM involves a series of transformations on the dual graph, including partitioning, fork and join insertion, lifetime analysis, register and frame-slot allocation, scheduling and linearization.

In this chapter, we will first present dual graphs and then explain how program graphs can be expanded into dual graphs. The expansion is described by presenting expansion rules for the individual program graph nodes. This description is quite long and is intended only for the interested reader. Other readers can skip that section and continue directly with the final section which presents the dual graph expansion for our little lookup example.

### 2.1 Dual Graph Definition

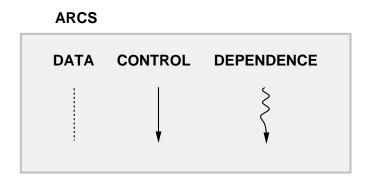

A dual graph is a graphical intermediate form in which both control flow and dataflow are explicit. It is a directed graph with three types of arcs: data, control and dependence. Dependence arcs capture indirect control and data. Each node has some number of ordered inputs and outputs, that are also divided into the three classes: data, control and dependence. An arc must always be of the same kind as the input and the output it connects. There is no restriction on the number of arcs emanating from an output, but each input can have at most one arc feeding it.

The dual graph arcs, shown in Figure 2.1, have the following meanings.

Data Arcs: A data arc (u, o) - - → (v, i) specifies that the value produced by output o of node u is used as operand i by node v. A node may have several data output ports; each port represents a name (i.e. a memory location) to which a value can be bound and read. There can be multiple consumers, but at most one producer

Figure 2.1: Dual Graph Arcs.

- Control Arcs: A control arc  $u \to v$  specifies that instruction u will execute before instruction v, and instruction u has direct responsibility for scheduling v. A node may have one or more control output ports, each with a bundle of control arcs.

- **Dependence Arcs** (split-phase long-latency arcs): A dependence arc  $u \rightsquigarrow v$  specifies that instruction u will execute before instruction v but that v will be scheduled as an indirect consequence of executing u. Being long latency arcs, they also indicate that the two nodes cannot be in the same thread.

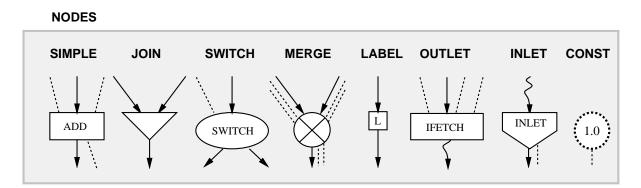

Dual-graphs have well-defined operational semantics and can be executed directly. Control can be represented by tokens traveling along the control arcs. A node fires when control tokens are present on all its control inputs.<sup>1</sup> Upon firing, a node computes a result based on data values bound to its data inputs, binds the result to its data outputs, and propagates control tokens to its control outputs. In correct dual graphs, control will only appear on control inputs if corresponding data inputs have been produced. It is the task of the compiler to ensure this. As shown in Figure 2.2, there are eight types of node: simple, join, switch, label, merge, outlet, inlet and constant nodes.

Figure 2.2: Dual Graph Nodes. (Arcs: dash = data, solid = control, curly = dependence)

• Simple nodes: All the arithmetic and logic operations are described by *simple nodes*. A simple node has a single control input and a data input for each operand. It has a single control output port (the *successors*) and typically a single data output port

<sup>&</sup>lt;sup>1</sup>The merge nodes are the only exception to this rule

(the *result*). When control passes to a simple node, it reads the value bound to its data inputs, performs its operation, binds the result to the data outputs and produces a new token on the control output arcs.

- Joins: A *join* synchronizes control paths; it has multiple control inputs and a single control output port. This node will pass a control token to its control output once every control input has received a token.

- Switches: A *switch* has a control input and a data input called the *predicate*. A switch will pass control on to one of its control outputs depending on the value of the predicate.

- Merges: The *merge* has multiple matching input sets, each with a control input and zero or more data inputs. The output ports have the same topology. Merge complements the switch by steering control from any one of the control inputs to a single control output. Thus it has a special firing rule and is the only node which is not strict in all of its control inputs. Additionally, the merge unifies the corresponding data inputs to its data outputs, *i.e.* data is bound to the output name. In the final code generation this may require moves.

- Labels: A *label* has one control input port and one control output port. It is used to indicate that the adjacent nodes must be in distinct threads *i.e.*, it represents a *separation constraint*. (In generating dual graphs, a label is placed on each output of a switch, reflecting the fork-based control primitives in TAM.)

- **Outlet nodes:** Operations that send messages or initiate requests are described by *outlet* nodes. These have an effect external to their code block. An outlet has a single control input, a data input for each operand, and a dependence output connecting it to inlet nodes.

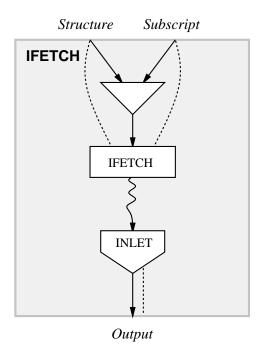

- Inlet: Inlet nodes receive messages, including arguments, values returned from a call, and responses to split-phase I-structure operations. An inlet may have a dependence input; it has a control output and zero or more data outputs. An inlet has no control inputs. It generates control and data as a result of some external message. An inlet represents a compiler generated message handler. It receives values corresponding to the data outputs and passes control to the operations connected to its control outputs. Usually its dependency input is connected to the dependency output of a node that sends the request (e.g. an IFETCH). The inlet then represents the answer coming back.

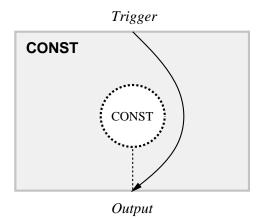

- **Constants:** Constant nodes represent constants. They have only a data output and neither a control input nor a control output, since their value is known at compile time.

Each node can have associated properties. Besides the opcode, the most important is whether a node is 'side-effecting' or not. Sends and I-Stores are examples of side-effecting nodes; the effects are not represented directly in the graph.

We now discuss in more detail what dependence arcs represent. They are used to associate a requester (*e.g.* an I-Fetch) with all of its local receivers (Inlets). This relationship between requester and receiver is shown in Figure 2.3, using the example of an I-fetch

connected to an Inlet. When issuing the request, the I-fetch specifies what I-structure element to fetch, where the result should be placed and what subsequent computation should be started. This is achieved by naming the receiving inlet which is the message handler that knows where to store the data and what computation to start. The I-structure handler will send the data value back to the inlet. Therefore, dependence arcs represent both a special form of control and data arc. It represents the data send over the network and also specifies indirect control: the receiver will execute (but not necessarily immediately) as a consequence of sending of request. The partitioning stage of the compiler makes use of the control information in dependence arcs to eliminate redundant control arcs. Code generation needs the data information, the name of the receiving inlet is one of the requester's operands.

Figure 2.3: Dependence arcs connect requesters to receivers.

### 2.2 Generation of dual graphs

Dual graphs are generated by expanding dataflow program graph instructions into equivalent dual graphs. This is a local transformation and can be described by giving the expansion rules for the individual program graph nodes. Program graphs are a hierarchical graphical intermediate form and described in [Tra86]. The lowest level is represented by basic operations. Larger programs can be built up using program graph encapsulators, including conditionals, loops, function definition, and application. The meaning of program graphs is given in terms of a dataflow firing rule, so control flow is implicitly prescribed by the dynamic propagation of values.

Program graph arcs carry tokens which always represent both a data value and control. Sometimes, as in the case of signals and triggers, we are only interested in the control component. Often, the control information carried by a token is redundant, as the example in Figure 2.4 shows.

Here the control information between **b** and **d** is redundant since we know that **b** is also needed to compute **c**. With the expansion of program graphs into dual graphs, program graph arcs will be represented by two separate arcs: a data arc and a control arc. This allows us to to eliminate them separately if one of them is not necessary. In the previous example, we could have identified and eliminated the redundant control arc from **b** and only retained the corresponding data arc, without having changed the semantics of the original program. Note that, program graph arcs are never transformed into dependence arcs, since those only appear inside a program graph node.

Figure 2.4: Example with redundant control arc.

After presenting the expansion of the basic program graph nodes, we will show the expansion of more complicated encapsulators: conditional and loop encapsulators, function definitions and applications. Finally, we will show how the program graph node expansions are combined to get a single dual graph.

The description of the expansion rules is quite long and can be skipped. The casual reader can continue with the final section which presents the dual graph expansion for our little lookup example.

#### 2.2.1 Basic Operators

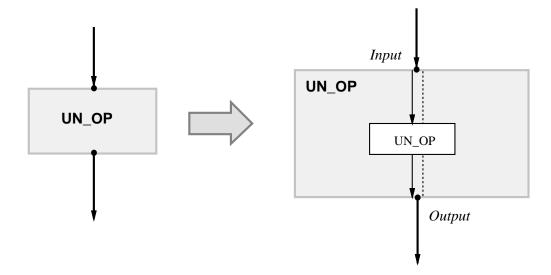

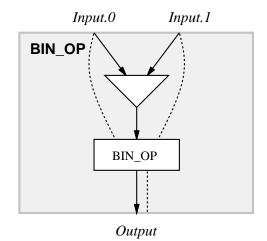

The expansion of basic unary and binary operators is straightforward as shown in Figures 2.5 and 2.6. The program graph instructions are represented by the grey area; the nodes and arcs inside are the dual graph equivalent. The inputs and outputs of the program graph nodes are shown with their names. Basic program graph nodes are strict in all their inputs. They fire when a token arrives on all inputs.

As can be seen in the case of the unary operation, an arc at the program graph level will usually be represented by two arcs at the dual graph level. In the case of the binary instruction, a control arc will be connected from each of the program graph inputs to a join node which will be connected to the control input port of the dual graph operator. This instruction will be executed once control has arrived on both control inputs, thus ensuring that the operands bound to the two data arcs are valid. Then the result is computed, bound to the data output port and control is passed to the control output port.

Figure 2.5: Dual graph expansion for unary instructions.

Figure 2.6: Dual graph expansion for binary instructions.

### 2.2.2 Literals

A literal program graph node, as can be seen in Figure 2.7 has only a single trigger input and an output for the value. When token arrives at the trigger input, the program graph node will produce a token containing the constant at its output. In the dual graph representation the input will be directly connected to the output by a control arc. The literal will be represented by a constant node which has only a data arc going to the program graph output.

Figure 2.7: Dual graph expansion for literals.

### 2.2.3 Conditional

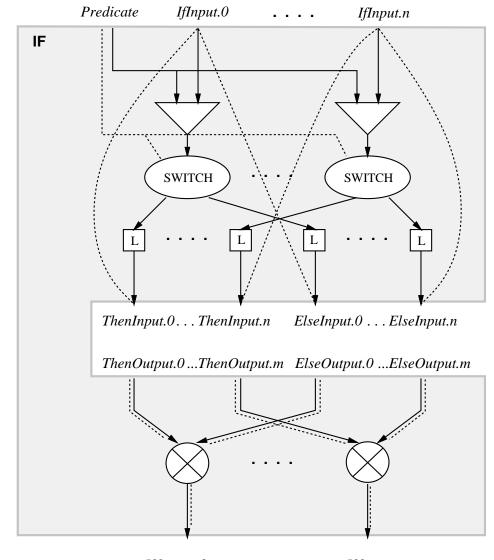

The translation for the conditional encapsulator is shown in Figure 2.8. Depending on the value of the token received at the predicate, the program graph conditional steers the tokens received at the data inputs either to the "then" side or to the "else" side. It also merges the results from the two sides into the output. The program graph conditional is only strict in the predicate, so it must be possible for one input to propagate through the conditional before other inputs have arrived. Therefore a switch node is needed for each input and a merge for each output. A join is placed in front of each switch to synchronize the corresponding input with the predicate. Since data and control flow are separated, the data will not be steered by the switch, as it is the case in the similar dataflow operation. The data arcs will go directly around the switch to the corresponding uses. Separating the control flow from the data flow, shows for all uses of values where they were produced. The task of the merge nodes is to pass control on from one of its inputs to the output of the conditional. It will also bind the values of the corresponding data inputs to the data outputs.

### 2.2.4 Loop

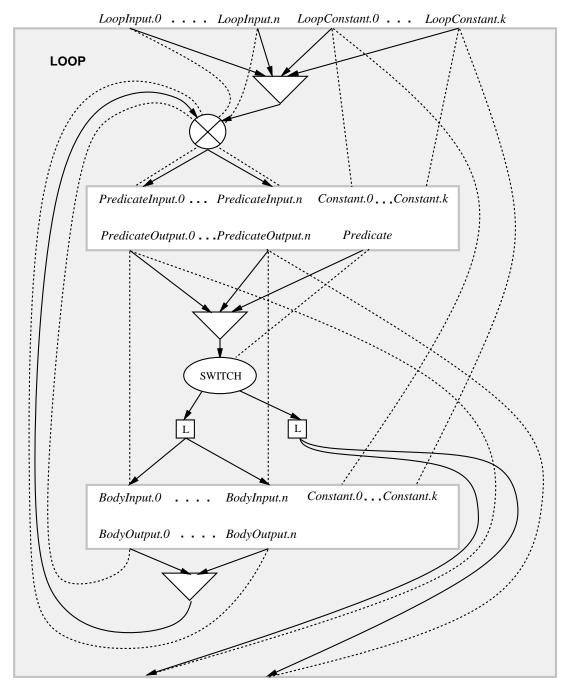

Figure 2.9 shows the expansion of a loop program graph encapsulator into a 1-bounded loop. The loop is a program graph schema for the while loop and encapsulates a predicate and a body. The predicate determines when the loop terminates, while the body will be executed for every iteration that the predicate evaluates to true. The loop has n circulating loop tokens. They enter at the beginning the loop inputs and go to the loop predicate.

IfOutput.0 .... IfOutput.m

Figure 2.8: Dual graph expansion for conditionals.

LoopOutput.0 . . . LoopOutput.n

Figure 2.9: Dual graph expansion for the loop encapsulator.

Depending on the value of the predicate they will either be routed to the loop outputs (if the predicate evaluates to false), or to the loop body. Here the token for the next iteration will be computed. External variables used inside the predicate or the loop body, but which are not changed, are called loop constants. They enter through the loop constant inputs and go to the corresponding predicate and body inputs.

A loop is strict in all its inputs, *i.e.* an implementation is allowed to wait until all the loop inputs as well as all loop constants have arrived before starting it. A join synchronizes all these inputs. Control is then passed on to a merge, that will start the evaluation of the predicate. Data arcs connect the loop inputs to one side of the arcs, while the loop constant inputs are directly connected by data arcs to the predicate and body. The result of the predicate is connected to a switch, which decides whether to pass control on to the the loop body or whether to end the loop. All outputs of the loop body will be synchronized by another join which feeds the other control input of the merge. The merge also serves to unify the names of the inputs to the loop with the corresponding outputs of the loop body. This is being represented by the data arcs connected to each side.

#### 2.2.5 I-Structure Operations

Figures 2.10 and 2.11 show the expansion for I-structure operations. I-fetch is used to fetch an element from a I-structure, while the I-store stores a value into an I-structure element. It might take a long time before the result from an I-fetch is available. The element might be fetched from some distant processor, or the fetch may be deferred waiting for the value to be stored. An I-fetch first needs to synchronize on both the structure pointer and the offset before initiating the request. The result of an ifetch returns into an inlet. Since the ifetch is a long latency operation, the inlet must be in a different thread. This is indicated by the dependence arc connecting these instructions.

Figure 2.10: Dual graph expansion for I-structure fetch.

Figure 2.11: Dual graph expansion for I-structure store.

For the I-store operation, the join first synchronizes on the structure pointer, the offset, and the value to be stored. In our execution model, we do not expect the receiver to signal the store, therefore the control output of the istore is directly connected to the the signal output of the program graph node. For machines that allow messages to get out of order, it might be necessary to acknowledge the store. In this case the expansion of the I-store would look similar to the I-fetch; the istore would be connected by a dependence arc to an inlet which would receive the acknowledgement signal.

### 2.2.6 Signal tree

Our expansion to dual graphs starts with program graphs that have already been enhanced with triggers and signals. Triggers are necessary to start pieces of computation that do not receive some input. That is, for example, why program graph constants have a data input. Signals are used to detect when all computation in a region of code has terminated. Usually many individual signals will be connected to a signal tree. A signal tree serves to synchronize all inputs and produce a signal on the output. Since the program graph arcs feeding this instruction carry only control and no data information, our expansion will connect all inputs to a join using only control arcs (see Figure 2.12). The control output of the join is connected to the output of the signal tree.

Figure 2.12: Dual graph expansion for signal trees.

### 2.2.7 Function Definition

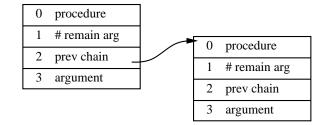

Id90 allows functions to be non-strict in their arguments. Therefore it must be possible to receive each argument independently and start the computation dependent on the argument. A function may also need to be started without receiving any argument, therefore the program graph node has a special trigger output. Id90 provides higher order functions and allows the programmer to build closures by applying a function to some, but not all, of its arguments. A closure representation consists of the name of the procedure to be invoked, an integer indicating how many arguments must still be provided before the arity is satisfied, and a field containing all the arguments collected so far. The last field is also called the *chain*. In Id90 a function can return only a single result.

Figure 2.13: Dual graph expansion for function definitions.

The dual graph expansion for function definition program graph encapsulators is shown in Figure 2.13. For a function with n arguments, n + 2 inlet nodes are needed for the dual graph representation; n are used for the arguments, the other two for the trigger and for the chain. A separate trigger inlet is needed because the function might have to be started

Figure 2.14: Dual graph expansion for chain detupling.

#### closure representation

Figure 2.15: Closure Structure.

before any argument is provided. The chain that collects all arguments except the last will be sent to a special chain inlet, while the last argument will be directly sent to its inlet. There the chain will be "detupled" to get all the other arguments. Detupling the chain, which is shown in Figure 2.14, involves fetching both the argument and the next chain pointer until all arguments are available. Figure 2.15 shows our convention for building closures.

In our calling and argument passing convention the trigger for a function will be received by inlet 0, the chain by inlet 1, and the last argument by inlet 2. All the other arguments from n-1 down to the first will be received by inlet 3 through inlet n+2. So the argument *i* is received by inlet n + 2 - i. Each of the argument inlets defines a data value; it also has to start the computation dependent upon this value. Therefore both a data and a control arc will be connected to the corresponding argument port of the program graph.

The **return** instruction will send the result back to the caller. After synchronizing on the return value as well as on the signal, the function can release its frame and send a completion signal back to its caller.

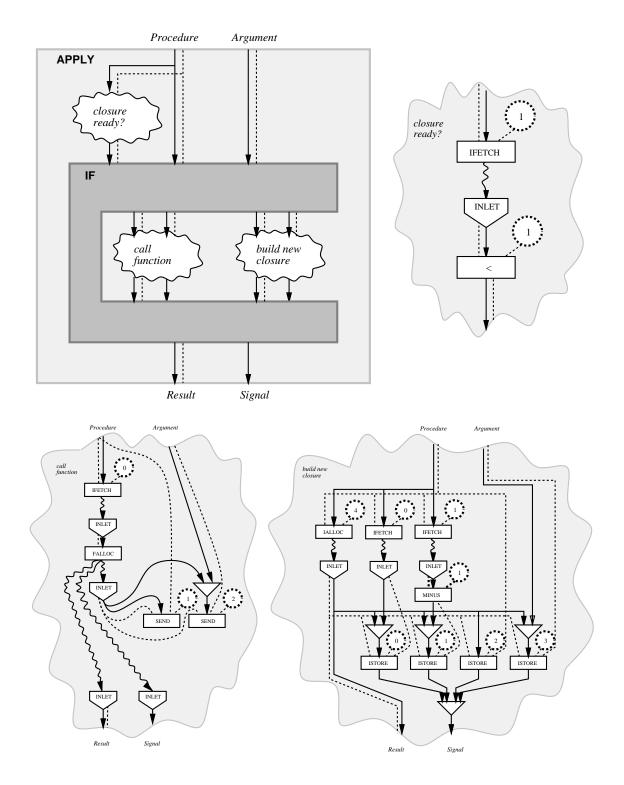

#### 2.2.8 Function Application

Figure 2.16 shows how a caller invokes a function. The inputs to the program graph node *apply* are the function (which could be any closure) as well as an argument. The outputs are the result and the signal. The apply first needs to test whether the arity of the function is already satisfied. Depending on the test it would either need to build up a new closure or, when the arity is satisfied, allocate a frame for the function. The *if* is a program graph conditional and will be expanded by the rule presented earlier. Allocating a frame, possibly on a different processor, is a split phase operation. The frame pointer will be received by an inlet and then the caller will send both the chain as well as the last argument to the corresponding inlets. The called function will return its result and the signal into the two inlets. Allocating the frame will automatically cause a trigger to be sent to the function trigger inlet. Since the return of the values are only known to be a result of the frame allocation, a dependence arc connects the frame allocation node to the result and signal inlet.

In the case where the compiler knows what function is to be invoked and the producers of its arguments a special program graph encapsulator called *direct apply* will be produced. As can be seen in Figure 2.17 the caller first needs to allocate a frame and then send all the arguments directly into the corresponding inlet of the function. The function may still be non-strict in these arguments, therefore it is necessary to separately synchronize each

Figure 2.16: Dual graph expansion for function application.

argument with the reception of the frame pointer. As in the previous case, result and signal will be received by an inlet and a dependence arc connects the frame allocation node to these inlets.

Figure 2.17: Dual graph expansion for direct apply.

With strictness analysis it might be possible to prove that some arguments are strict with respect to each other — they could be grouped together, making sending as well as receiving them cheaper. In general, this might require that we generate specialized function code blocks; we did not implement this optimization in our compiler.

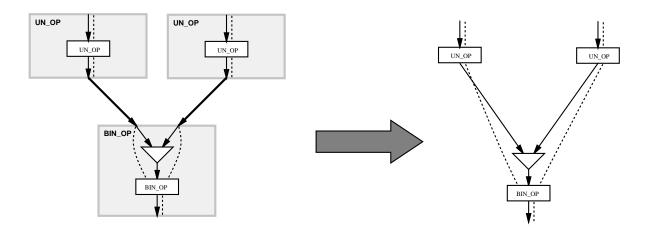

### 2.3 Combining Dual Graph Expansions

Combining dual graph expansions, as in Figure 2.18, produces the complete dual graph equivalent to the original program graph. First, all program graph nodes are individually expanded into the dual graph equivalent, following the rules presented in the previous section. After this step, each program graph output port can have at most one control arc and one data arc feeding it. Now dual graph arcs emanating from program graph

Figure 2.18: Combining dual graph expansions.

inputs are re-connected so that they directly emanate from the corresponding dual graph node (following backwards the corresponding program graph and dual graph arcs). All dual graph arcs still feeding program graph outputs are then eliminated, the previous reconnection step has made them unnecessary.

### 2.4 Example

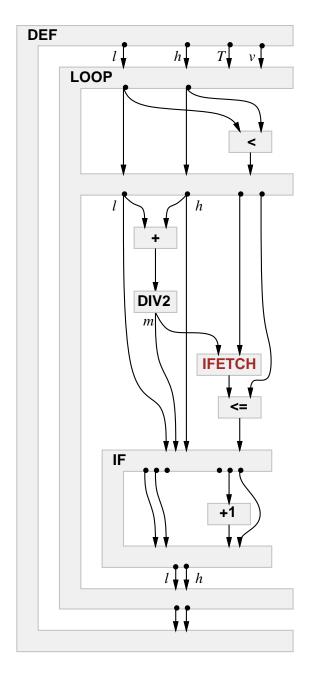

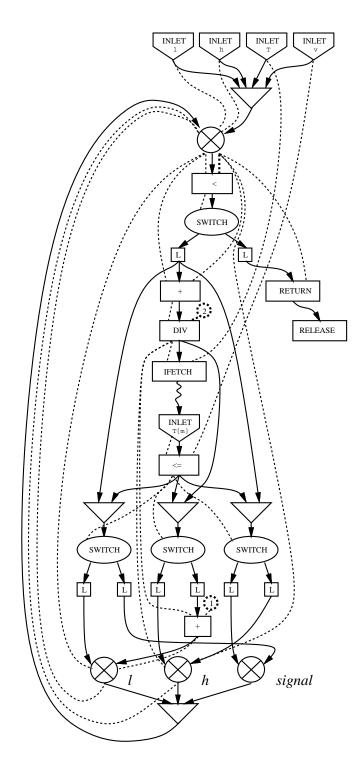

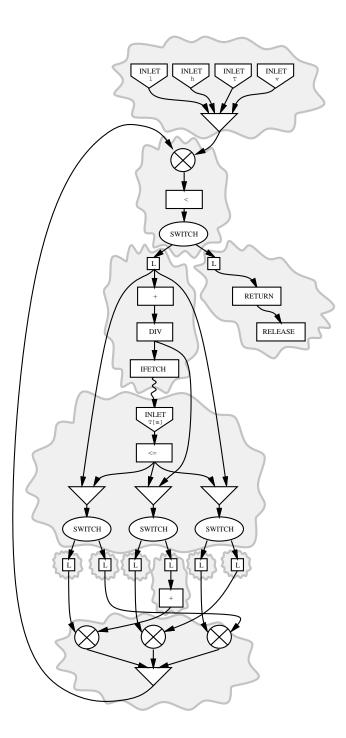

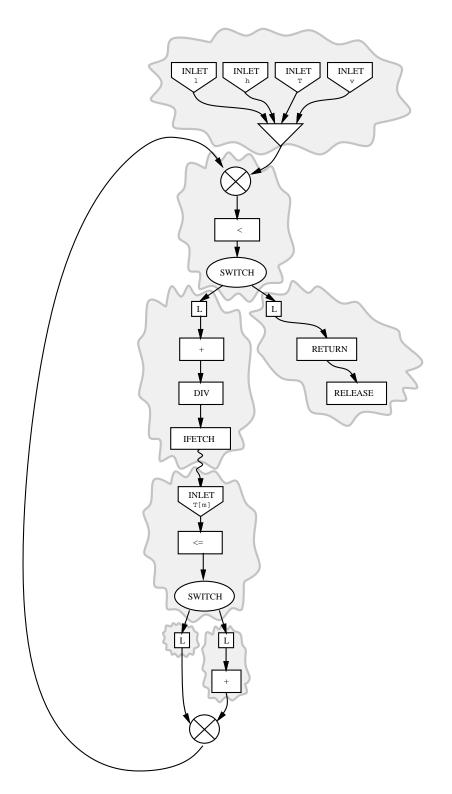

The program graph for the lookup example from Figure 1.2 (page 9) includes a function DEF node, enclosing a LOOP node, enclosing an IF node, as shown in Figure 2.19. Figure 2.20 shows the corresponding dual graph representation, using a 1-bounded loop form, *i.e.* where only one iteration is active at once[Cul90]. The compiler actually produces a slightly more complicated dual graph; we have omitted the trigger inlet and its arcs. The four arguments enter at the inlet nodes at the top of the graph. The control outputs are joined before arriving at the merge. The function is strict in all its arguments. The data arcs for 1 and h connect to the merge nodes at the top of the loop. The other inlets are connected directly to their uses within the loop and the enclosed conditional, as are the data outputs of the loop merge. By separating the control and data arcs, the flow of information is not obscured by control constructs. In each iteration, control is directed to the loop body or exit based on the loop predicate. Within the body of the loop, the value of **m** is calculated and used in an I-fetch operation. The result of the I-fetch will eventually arrive at the inlet indicated by the dependence arc. This inlet feeds the conditional predicate, which controls three separate switches, one for each data value used in the conditional. The three switches cause the correct values to be routed to the merges to produce the next iteration values of 1 and h. The third merge has only control inputs and serves to indicate that all the switches have executed. Control is joined once again at the bottom of the loop and directed to the loop merge.

The dual-graph for an Id90 program could be executed directly, but the number of dynamic synchronizations per useful operation is very high. The compilation goal is to minimize this cost by employing the cheapest form of synchronization available in the synchronization hierarchy provided by TAM. The cheapest form of synchronization is the sequencing of instructions in a thread; here synchronization is implicit in the static ordering. Identifying portions of the dual graph that can be executed as a thread is called *partitioning*.

Figure 2.19: Program graph for lookup example.

Figure 2.20: Dual graph for lookup example.

# Chapter 3

# Partitioning

The fundamental step in compiling a lenient language for a machine that executes instruction sequences is partitioning the program into statically schedulable entities[Tra88]. Limits on partitioning are imposed by dependence cycles that can only be resolved dynamically. In Id90 these arise due to conditionals, function calls, and accesses to I-structures. Partitioning for TAM involves identifying portions of the dual graph that can be executed as a TAM thread, *i.e.*, a partition must be linearizable with synchronization and control entry occurring only at the top. The number of entries to a thread must be statically determined. In the context of the dual graph representation, partitioning can be accomplished using only the control and dependence arcs, ignoring data arcs and the constant nodes which carry only data information. Assignment of storage to output ports is deferred until after partitioning, the critical information is retained in the data arcs.

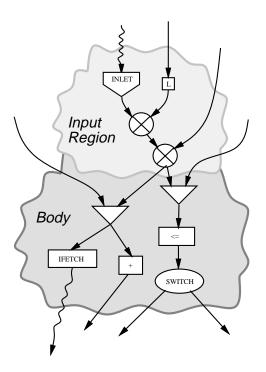

**Definition 1 (TAM Partition)** A *TAM partition* is a subset of dual graph nodes and their incident control and dependence edges. In a valid partitioning, partitions are nodedisjoint and cover the graph. A partition consists of an *input region* containing only inlet, merge, and label nodes and a *body* containing simple nodes, outlets, switches and joins. The *outputs* of a partition are its outlet nodes and all leaving control arcs. Control edges that connect two partitions belong to both partitions.

Figure 3.1 shows a partition with four nodes in the input region and six nodes in the body.

#### Definition 2 (Safe Partition) We call a TAM partition safe if

- 1. no output of the partition need be produced before all inputs to the body are available,

- 2. when the inputs to the body are available, all nodes in the body are executed, and

- 3. no arc connects a body node to an input node of the same partition.

The first property says that body of the partition can be treated as strict, *i.e.* it is safe to wait for all inputs to arrive before executing any instruction of the partition. The second says that there is no conditional execution within a partition; conditional execution occurs only between partitions. The third implies that a partition is acyclic and can be linearized in a manner consistent with the control arcs, since all cycles include a switch and a merge. Also, all dependence arcs must cross partitions. Finally, the entry count for any valid execution of the partition is constant. This implies the following.

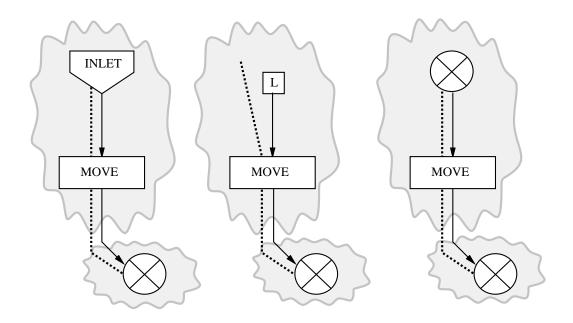

Figure 3.1: Partition example.

#### **Lemma 1** A safe partition can be mapped into a TAM thread.

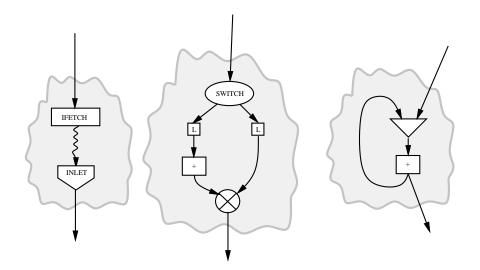

Figure 3.2 gives three examples with unsafe partitions. In the first example an I-fetch and the receiving inlet were placed in the same partition; this violates the third property of a safe partition. The second example has conditional execution within a single partition, thus violating the second property. The last example has a cyclic dependence and violates the first property of a safe partition. While the first two examples could have been partitioned correctly, it is impossible to do so for the third example. This last example would correspond to the code a = a + b; which would deadlock in Id90. Throughout the rest of this chapter, we will assume that we only need to find safe partitions if the programs can be partitioned safely in the first place.

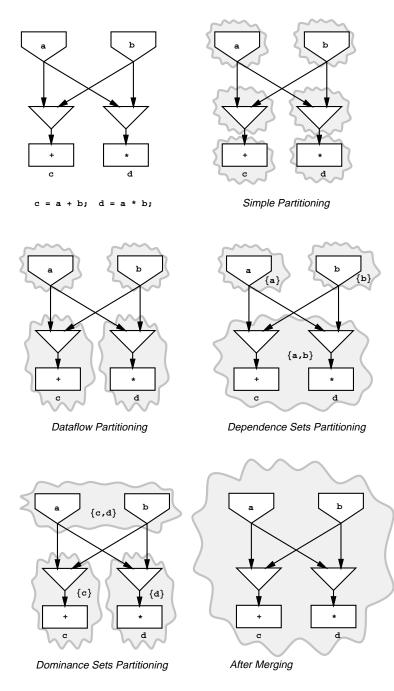

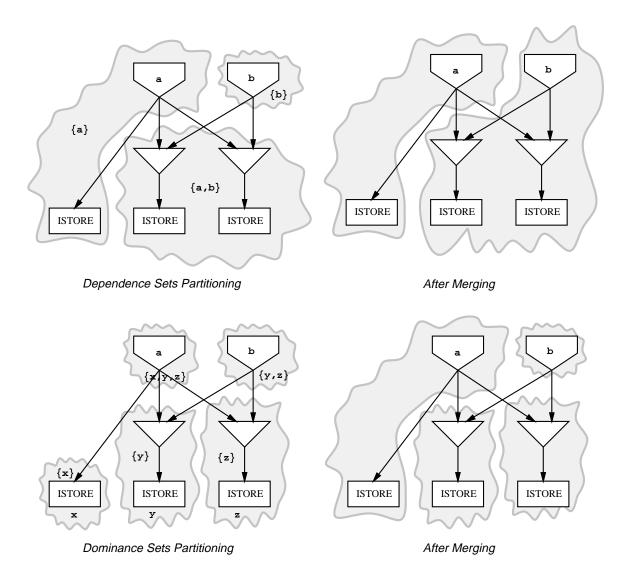

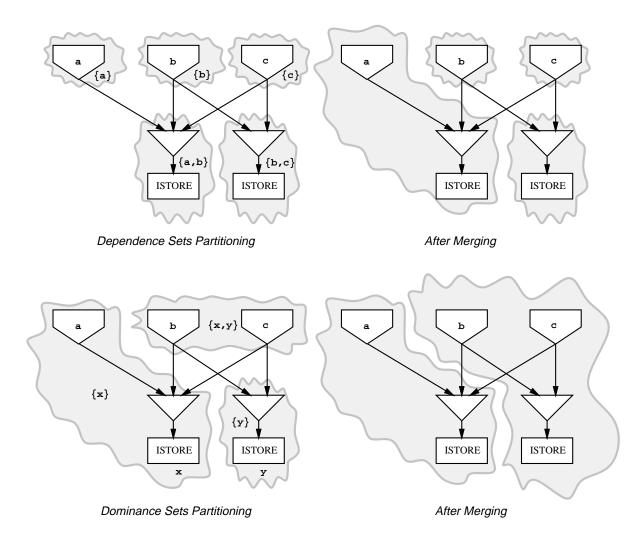

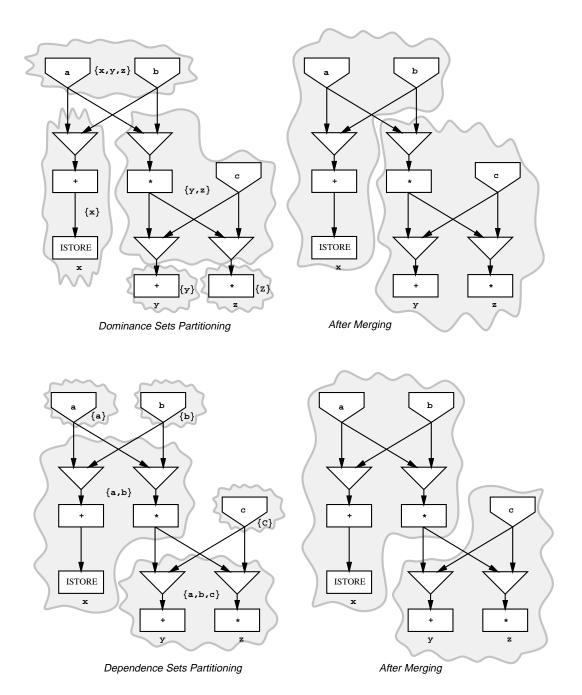

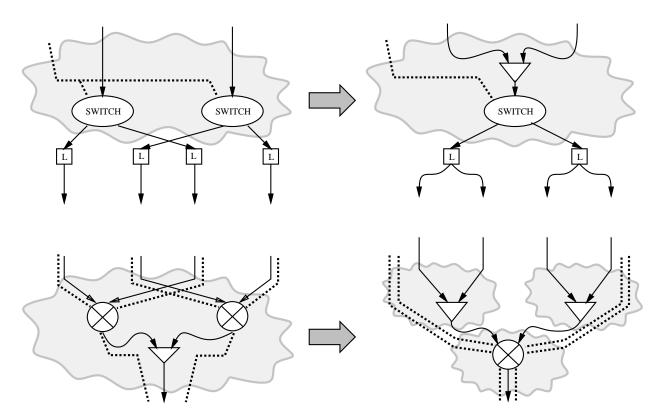

Our partitioning algorithm starts by finding small safe partitions. We have four different ways of creating these basic partitions: simple partitioning, dataflow partitioning, dependence sets partitioning and dominance sets partitioning. These basic partitions are then iteratively merged into larger partitions by applying simple merge rules. The merge rules will ensure that the newly formed partitions are also safe. We first present a small example to illustrate the partitionings schemes, before introducing them in a formal way.

# 3.1 Partitioning a small example

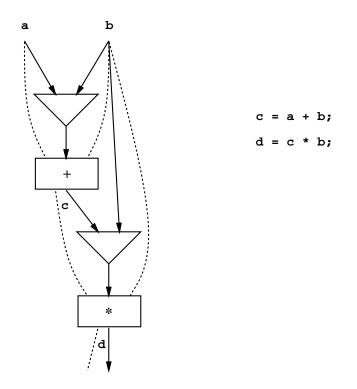

The small program

c = a + b; d = a \* b;

is used to illustrate the different partitioning schemes. Figure 3.3 shows the dual graph (only the control arcs are shown) for this piece of code together with the various partitioning possibilities.

Figure 3.2: Unsafe partitions.

Simple partitioning is the most trivial form of partitioning, here each node is placed into its own partition, resulting in a total of six partitions. This directly yields a safe TAM partitioning, but its dynamic synchronization overhead is large.

Dataflow partitioning recognizes the fact that unary operations never need dynamic synchronization. In this scheme the inlet and sync nodes start a new partition. The add and the multiply nodes are placed into the partition of their control predecessor, we thus get four basic partitions.

Far more powerful is *dependence sets partitioning*, which finds safe partitions by grouping together nodes that depend on the same set of input nodes (inlets, merges and labels). A node u depends on an input node v if there exist a direct control path from v to u. For our example, dependence sets partitioning produces three basic partitions. We have annotated each partition with its dependence set. The four bottom nodes depend on exactly the same inputs, they are therefore placed into the same partition. By only placing nodes with the same dependence sets into the same partition, no node can produce a side-effect on another (because it would then also produce a side-effect on itself).

Dominance sets partitioning finds safe partitions by grouping together nodes which dominate the same set of output nodes. A node u dominates an output node v if there exist a direct control path from u to v. This partitioning scheme also ensures that there are no cyclic dependencies within a partition. Since all nodes of a basic partition dominate the same outputs, under no circumstances can one node have a side-effect on another. We have indicated the dominance sets in our example. With dominance sets partitioning, the top two nodes can go into the same partition since they dominate the same set of outputs: c and d.

After basic partitioning we can apply merge rules which ensure that the merged partition is also safe. A partition with a single control predecessor can be *merged up* if no separation constraints are violated. A partition can be *merged down*, if it feeds strictly a single successor partition. We will present the merge rules in more detail later.

In our example, starting with simple partitioning, we can merge up the add and multiply node into the partition of the corresponding control predecessor. This results in the same safe partitioning as with dataflow partitioning. At this stage no further merge rule can

Figure 3.3: Partitioning c = a + b; d = a \* b;

be applied. Starting with dependence sets partitioning, we can apply the "merge down" rule and finally obtain a single safe partition containing the six nodes. Similarly, starting with dominance sets partitioning, we can apply the "merge up" rule. This will also produce a single partition. As this example shows, the quality of partitioning after merging depends strongly on basic partitioning. The power of dependence sets and dominance sets partitioning lies in the fact that they can work across different fan-out or fan-in trees.

## 3.2 **Basic Partitioning**

We now present the basic partitioning schemes and partition merging formally.

### 3.2.1 Simple Partitioning

Simple partitioning is the most trivial form of partitioning, here each node is placed into its own partition. This directly yields a safe TAM partitioning, but dynamic synchronization overhead is large.

### 3.2.2 Dataflow Partitioning

*Dataflow partitioning* recognizes the fact that unary operations never need dynamic synchronization. In this scheme joins, inlets, merges and labels start a new partition. Simple, switch and outlet nodes are placed into the partition of their control predecessor. Dataflow partitioning also yields safe TAM partitions.

### 3.2.3 Dependence Sets Partitioning

Far more powerful is *dependence sets partitioning*, which is based on a variant of Iannucci's method of dependence sets [Ian88a].

**Definition 3 (Dependence Set)** The *dependence set* for a dual graph node u is the set of input nodes i (inlets, merges and labels) on which it depends, *i.e.* there exists a control path of length zero or greater from i to u that does not go through any other input node.

The algorithm for computing the dependence sets first assigns each input node the dependence set containing only itself; for all other nodes the dependence set is the union of the dependence sets of the control predecessors. Our definition will not allow dependence to cross switches, since every control output of a switch is connected to a label, thus indicating that they must be in a different partition. Stronger notions of dependence could be employed that would capture dependence across conditionals.

Having computed the dependence sets for all nodes, we can then find safe partitions by grouping together nodes that depend on the same set of input nodes. This guarantees that there are no cyclic dependences within a partition. For example, all nodes that depend only on a particular inlet will be grouped with the inlet, and similarly for merges and labels.

#### Algorithm 1 (Basic Partitioning using Dependence Sets)

- Compute the dependence sets for all nodes

- Put all nodes with the same dependence set into the same basic partition.

**Lemma 2** All basic partitions produced by dependence sets partitioning are safe TAM partitions.

**Proof:** We have to show that each basic partition satisfies the three properties of a safe partition. Assume that an output of the partition needs to be produced before all inputs are available. All nodes in the the partition depend on all of the inputs (since they all have the same dependence set). This implies that the node that produces this output also depends on the input. Thus the node depends on itself and no safe partition can be found. We disallowed this case, the basic partition thus satisfies the first property of safe partitions. It also satisfies the second property since all arms of conditional execution are marked with a label. Dependence cannot propagate across inlets, labels, and merges. Also, since we have only structured dual graphs where a circular dependence must go through a merge and a switch we satisfy the third property.  $\Box$

#### 3.2.4 Dominance Sets Partitioning

Analogous to dependence sets partitioning, we can find safe partitions by grouping together nodes which dominate the same set of output nodes.

**Definition 4 (Dominance Set)** The *dominance set* for a dual graph node u is the set of output nodes o (outlet nodes and nodes directly feeding a merge or label) it dominates, *i.e.* there exists a control path of length zero or greater from u to o that does not go through any input node except itself.

The algorithm for computing the dominance sets first assigns each node that is a direct control predecessor to a merge or label node the dominance set containing only itself. For all other nodes the dominance set is the union of the dominance sets of the control successors plus itself if it is an outlet node.

Grouping all nodes that dominate the same set of output nodes into the same partition also ensures that there are no cyclic dependencies within a partition. Since all nodes of a basic partition dominate the same outputs, under no circumstances can one node have a side-effect on another.

#### Algorithm 2 (Basic Partitioning using Dominance Sets)

- Compute the dominance sets for all nodes

- Put all nodes with the same dominance set into the same basic partition.

**Lemma 3** All basic partitions produced by dominance sets partitioning are safe TAM partitions.

**Proof:** Assume again that an output of the partition needs to be produced before all inputs are available. All nodes in the partition dominate the same set of outputs. This implies that the node that need this input also dominates it, which was disallowed. The basic partition thus satisfies the first property of safe partitions. It also satisfies the second property since all arms of conditional execution are marked with a label. All partitions satisfy the third property due to the fact that dominance sets cannot propagate across merge and labels and we only have structured dual graphs.  $\Box$

Other possible basic partitioning schemes could identify regions of the graph that depend solely on a single node (or dominate a single node.) These tree like regions will also create safe partitions. Dependence sets partitioning (or dominance sets partitioning) will create much large basic partitions, since they allow nodes that depend on (dominate) several nodes to be grouped. Downward and upward trees will always be found by partition merging discussed next.

## 3.3 Merging partitions

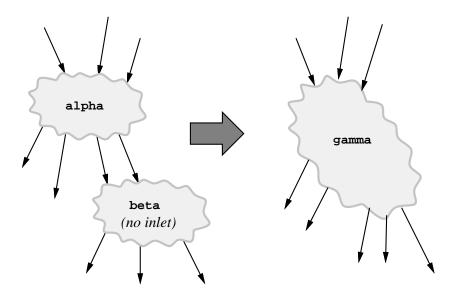

After basic partitioning, partitions will be merged into larger, but still safe, partitions by iteratively applying one of the following two merge rules.

### 3.3.1 Merging up

"Merge up" rule: Two partitions  $\alpha$  and  $\beta$  can be merged into a larger partition  $\gamma$  if

- all input arcs to  $\beta$  come from  $\alpha$ ,

- $\beta$  contains no inlet instructions, and

- no output arc from the body of  $\alpha$  goes to an input node of  $\beta$ .

Figure 3.4 shows this case graphically. The arcs connecting  $\alpha$  to  $\beta$  indicate that it is necessary for  $\alpha$  to execute before  $\beta$ . The first two points of the merge up rule imply that this is also sufficient. The two partitions cannot be merged if  $\beta$  has an arc coming from some other partition besides  $\alpha$  or if it contains an inlet. In both cases it could be that  $\alpha$ or some output from  $\alpha$  will cause a side-effect on this input or inlet. The last point of this merge rule ensures that no separation constraint is violated.

Figure 3.4: Merge Up: A partition with a single control predecessor can be merged up if no "separation constraints" are violated.

The astute reader will notice that this rule cannot be applied after basic partitioning, since then all nodes in  $\beta$  would have the same dependence set as the nodes in  $\alpha$  and the

two partitions would already have been merged. Opportunities for this rule arise as a result of merging down, discussed below.

**Lemma 4 ("Merge Up")** If  $\alpha$  and  $\beta$  are safe partitions then the "merge up" rule will produce a safe partition.

**Proof:** Assume that both  $\alpha$  and  $\beta$  are safe partitions and that the merge rule conditions apply. All inputs from  $\beta$  come from  $\alpha$ , it is therefore valid for the merged partition to produce no output until all inputs to  $\alpha$  are available.  $\beta$  will always be executed if  $\alpha$  is. Otherwise  $\beta$  must be one side of a conditional, but then  $\alpha$  would have contained a switch with an output to a label in  $\beta$  and the "merge up" would not be applicable.  $\Box$

### 3.3.2 Merging down

"Merge down" rule: Two partitions  $\alpha$  and  $\beta$  can be merged into a bigger partition  $\gamma$  if

- all output arcs from  $\alpha$  go to  $\beta$ ,