## Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# PERFORMANCE AND TESTABILITY INTERACTIONS IN LOGIC SYNTHESIS

by

Alexander Saldanha

Memorandum No. UCB/ERL M91/100

28 October 1991

# PERFORMANCE AND TESTABILITY INTERACTIONS IN LOGIC SYNTHESIS

by

Alexander Saldanha

Memorandum No. UCB/ERL M91/100 28 October 1991

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Performance and Testability Interactions in Logic Synthesis

#### Alexander Saldanha

University of California Berkeley, California Department of Electrical Engineering and Computer Sciences Computer Science Division

#### Abstract

Three primary parameters that are optimized at all levels of synthesis and design of very large scale integrated circuits are area, performance, and testability. While techniques for individually optimizing each of these parameters are well formulated, not much is known of the interactions between the parameters. There are two important reasons why this interaction is interesting. First, it is unknown whether circuits may be fully optimized simultaneously for area, performance and testability, or whether a tradeoff between the criteria necessarily exists, i.e. is the optimality of one parameter sacrificed when the others are optimized? Second, the impact of the tradeoff between the area, performance or testability on the resulting quality of the optimized integrated circuit is not well understood. This thesis studies the interaction between the performance, testability, and area of combinational logic circuits. The results apply to sequential circuits as well. There are three contributions; these are motivated by the example of a well-known circuit design, where testability and reliability are apparently sacrificed for performance. The first result proves that there exists a fully testable implementation for every high-performance and untestable circuit. An algorithm that transforms an untestable circuit to a fully testable circuit with no loss in performance is provided. A consequence of this result is the question of whether the testability of a circuit can be retained during performance optimization. The second part of this thesis explores several synthesis situations and provides a comprehensive summary of the testability effects of performance optimization techniques. The synthesis techniques discussed in the first two parts require the analysis of two critical problems that have emerged recently, timing analysis and delay-fault test generation. The final contribution of this thesis is the development of a novel and efficient general framework to solve the class of problems, that includes both timing analysis and delay-fault test generation, involving functional analysis on paths in a circuit.

Prof. Robert K. Brayton

Thesis Committee Chairman

## Performance and Testability Interactions in Logic Synthesis

Copyright © 1991

Alexander Saldanha

### Acknowledgements

What in the dark

I had taken to be a stump of a little tree

appearing above the snow,

to which I had tied my horse,

proved to have been the weathercock of the church steeple.

Rudolf Raspe in "Travels of Baron Munchausen"

The area of performance and testability interactions in logic synthesis seemed like a little stump when I first started research work in the CAD group at Berkeley. There are several people to be acknowledged for their support, encouragement, and friendship in being a part of my "adventure".

Bob Brayton has been my research advisor for over three years. He has been a constant source of guidance, support, and enthusiasm for me. The many stimulating discussions, directions, and ideas he has always provided are directly reflected in much of the work reported in this thesis. I am especially grateful for his meticulous reading of several drafts of each paper that we have written. From him I have learned the importance of mathematically sound and precise presentation.

Alberto Sangiovanni-Vincentelli has been more than just a second member of my thesis committee. I am indebted to him for his initial support during my early years at Berkeley. I thank him for guiding and directing me into the area of testing and its relationship to logic synthesis. From him I have strived to learn the ability to relate solutions for particular problems to more general situations in creating a coherent "big picture". I am grateful for the opportunity provided by Alberto and the experience gained in teaching the two logic synthesis courses at DEC - Hudson in 1990 and 1991.

Dorit Hochbaum has been a member of both my qualifying examination and thesis committees. I am thankful to her for the time spent in serving both roles, as well as the discussions and suggestions she has made on my work.

Thanks to Randy Katz for the support during the year I spent with him completing my master's project. He also served on my qualifying examination committee.

A lot of the work reported here has been done with the assistance of others. Bob Brayton and Alberto Sangiovanni-Vincentelli have supervised or been part of all the work. The summer of 1989 was spent at AT&T Bell Laboratories with Sharad Malik and Kurt Keutzer, where the initial results on the interaction between redundancy and delay were

developed. The testability invariance results were done together with Tim Cheng. The path-recursive paradigm was developed with Rick McGeer. Paul Stephan helped develop the SAT package used in many of the results reported here. Tiziano Villa worked with me on the encoding problem that is not reported here.

I have several people to thank for assisting in the process of completing my thesis. Tiziano Villa has constantly followed my work and personal life. I am grateful to him for his friendship and assistance, especially during the start of my stay in Berkeley. His wide interests have always provided a welcome break from dreary moments. Luciano Lavagno has patiently listened to many of my ideas and made helpful suggestions on drafts of papers and this thesis. Thanks to K.J. Singh, Narendra Shenoy, and Ellen Sentovich for making our office a nice place to be and for spending many times together at the coffee shop. Rick McGeer has been a constant source of ideas and I continue to enjoy our lively discussions and collaboration. The members of the CAD group at Berkeley are thanked for their interaction and companionship over the past few years. They are: Pranav Ashar, Wendell Baker, Mark Beardslee, Andrea Casotto, Srinivas Devadas, Abhijit Ghosh, Chuck Kring, Luciano Lavagno, Tony Ma, Sharad Malik, Rick McGeer, Cho Moon, Rajeev Murgai, Hamid Savoj, Ellen Sentovich, Narendra Shenoy, Kanwar Jit Singh, Rick Spickelmier, Paul Stephan, Hervé Touati, Tiziano Villa, Albert Wang, Yosinori Watanabe, and Greg Whitcomb. Many thanks to Flora Oviedo, Kathryn Crabtree, Irena Stanczyk-Ng, and Elise Mills for the all administrative assistance provided. Brad Krebs helped with many hardware and software problems over the years.

The research support for my work has been primarily from the Semiconductor Research Corporation under contract 90-DC-008. I am grateful for the support provided by Al Dunlop at AT&T Bell Laboratories - Murray Hill, during my stay in 1989. Tushar Gheewala and Susheel Chandra are acknowledged for my stay at CrossCheck Inc., San Jose, during 1990.

My life at Berkeley would not have been as happy and memorable as it has been without my friends from Communion and Liberation. In particular, words cannot express my gratitude to Roberto and Elena, Paul, Damian, Chris, Martin, Tiziano and Maria, Bruno and Kristi, Marco and Antonella, Fr. Mark, Mark and Margaret, Alessandra, Lucia, and many others. I thank them for showing me what is most important in life and for their constant and complete human friendship.

My wife Avril has patiently watched as my work has evolved over the past four years. I thank her above all for her constant love and support over these years, but especially in the past six months.

This thesis is dedicated to my parents, Eric and Doreen Saldanha. Together with my brothers and sisters, Val, Pete and Maria, Ritchie and Roopa, Joan and Ajit, Linda and Trevor, Maria, and their kids, and my "new" family of Alex and Jeannette Lobo, Nisha and Elga, they are constantly in my memory.

## Contents

| 1.1 CAD of IC's       1         1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                               | Ac  | knov  | wledgements                             | j        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------------------------------|----------|

| List of Tables       x         1 Introduction       1         1.1 CAD of IC's       1         1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23 | Ta  | ble o | of Contents                             | v        |

| 1 Introduction       1         1.1 CAD of IC's       1         1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                | Lis | t of  | Figures                                 | ix       |

| 1.1 CAD of IC's       1         1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                               | Lis | t of  | Tables                                  | x        |

| 1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                               | 1   | Intr  | oduction                                | 1        |

| 1.2 Combinational logic synthesis       3         1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                               |     | 1.1   | CAD of IC's                             | 1        |

| 1.2.1 Area optimization       4         1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                 |     | 1.2   |                                         |          |

| 1.2.2 Performance optimization       4         1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                         |     |       | • •                                     |          |

| 1.2.3 Testability optimization       5         1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                        |     |       |                                         | _        |

| 1.3 Relations between optimization criteria       6         1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                       |     |       | -                                       | -        |

| 1.3.1 Area and testability       6         1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                   |     | 13    | · -                                     | _        |

| 1.3.2 Area and delay       7         1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                              |     | 1.0   | <del>-</del>                            | _        |

| 1.3.3 Other relationships       7         1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |       | ▼ · · · · · · · · · · · · · · · · · · · |          |

| 1.4 Thesis contributions and overview       7         2 Redundancy and Delay       11         2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |       | ·                                       | -        |

| 2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     | 1.4   | •                                       | •        |

| 2.1 Boolean networks       11         2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2   | Red   | undancy and Delay                       | 11       |

| 2.2 Redundancy in a network       13         2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _   |       |                                         |          |

| 2.3 Delay of a network       14         2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     | 2.2   |                                         |          |

| 2.3.1 Delay computation using viability analysis       17         2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |       | · · · · · · · · · · · · · · · · · · ·   |          |

| 2.4 Disadvantages of redundancy       21         2.5 Redundancy in high-speed circuits       23         2.5.1 The carry-skip adder       23         2.5.2 Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |       |                                         |          |

| 2.5       Redundancy in high-speed circuits       23         2.5.1       The carry-skip adder       23         2.5.2       Redundancy problems       23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | 24    |                                         |          |

| 2.5.1 The carry-skip adder                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |       |                                         |          |

| 2.5.2 Redundancy problems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 2.0   |                                         |          |

| • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |       |                                         |          |

| 26 Related work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 2.6   | • •                                     | 25<br>25 |

| 2.0 Redundancy and delay questions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |       |                                         |          |

vi *CONTENTS*

| 3 | Is F        | Redundancy Necessary to Reduce Delay?         | 31       |

|---|-------------|-----------------------------------------------|----------|

|   | 3.1         | _ · · · · ·                                   | 32       |

|   | 3.2         |                                               | 33       |

|   |             |                                               | 33       |

|   |             | · · · · · · · · · · · · · · · · · · ·         | 39       |

|   | 3.3         |                                               | 39       |

|   | 3.4         |                                               | 49       |

|   |             |                                               | 49       |

|   |             |                                               | 49       |

|   |             |                                               | 49       |

|   |             |                                               | 51       |

|   | 3.5         |                                               | 53       |

|   |             |                                               | 53       |

|   |             |                                               | 56       |

|   | 3.6         |                                               | 58       |

|   | 0.0         |                                               | 69       |

|   |             |                                               | 03<br>73 |

|   | 3.7         |                                               | 13<br>74 |

|   | 0.1         |                                               | 14<br>74 |

|   |             |                                               | 75       |

|   |             |                                               | 75       |

|   |             |                                               | 76       |

|   | 3.8         |                                               | 76       |

|   | <b>3.</b> 0 | Conclusions                                   | 10       |

| 4 | Tes         | tability Effects of Performance Optimizations | 78       |

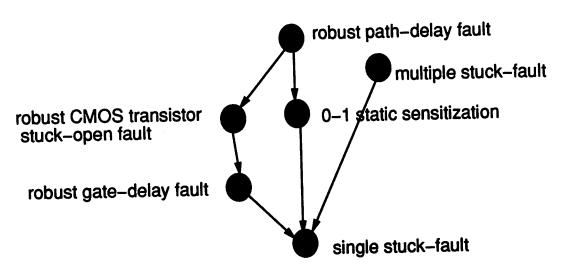

|   | 4.1         | Fault models                                  | 80       |

|   |             | 4.1.1 Stuck-faults                            | 80       |

|   |             |                                               | 81       |

|   |             |                                               | 83       |

|   | 4.2         |                                               | 87       |

|   | 4.3         |                                               | 88       |

|   | 4.4         |                                               | 93       |

|   |             |                                               | 97       |

|   |             |                                               | 01       |

|   |             |                                               | 03       |

|   |             |                                               | 03       |

|   | 4.5         |                                               | 04       |

|   | 4.6         |                                               | 06       |

|   | 4.7         |                                               | 08       |

|   |             |                                               | 08       |

|   |             | <u>-</u>                                      | 09       |

|   |             |                                               | 09       |

|   |             |                                               | 10       |

|   |             | <u> </u>                                      | 12       |

|   | 1 0         |                                               | 19       |

CONTENTS

|    |            | 4.8.1   | Synthesis of 0-1 statically sensitizable circuits    | 114 |

|----|------------|---------|------------------------------------------------------|-----|

|    |            | 4.8.2   | Node duplication and merging of identical nodes      | 115 |

|    |            | 4.8.3   | Resynthesis of a collapsed node                      | 115 |

|    |            | 4.8.4   | Collapsing of critical sub-network                   | 116 |

|    | 4.9        | Other   | performance optimizations                            | 116 |

|    | 4.10       | Conclu  | usions                                               | 119 |

| 5  | Patl       | h-Recu  | rsive Functions and Applications                     | 121 |

|    | 5.1        |         | onal path analysis problems                          | 121 |

|    | 5.2        | Path-r  | ecursive functions                                   | 123 |

|    |            | 5.2.1   | Linearizing Boolean functions                        | 127 |

|    | 5.3        | Viabili | ty analysis                                          |     |

|    |            | 5.3.1   | Viability equations                                  | 130 |

|    |            | 5.3.2   | Dynamic programming algorithm for viability analysis | 131 |

|    |            | 5.3.3   | Linearizing the viability equations                  | 132 |

|    |            | 5.3.4   | Complex gates                                        | 134 |

|    |            | 5.3.5   | Timing analysis results with path-tracing            | 138 |

|    |            | 5.3.6   | Performance optimization and false paths             | 140 |

|    | 5.4        |         | g analysis without path-tracing                      | 143 |

|    |            | 5.4.1   | Timing analysis algorithm without path-tracing       | 148 |

|    |            | 5.4.2   | Timing analysis results without path-tracing         | 152 |

|    | 5.5        |         | fault test generation                                | 153 |

|    |            | 5.5.1   | Hazard-free robust delay-fault testability           | 153 |

|    |            | 5.5.2   | Previous work                                        | 155 |

|    |            | 5.5.3   | Delay-fault test generation equations                | 157 |

|    |            | 5.5.4   | Delay-fault test generation results                  | 160 |

|    | 5.6        |         | sions of the path-recursive paradigm :               | 161 |

|    | 0.0        | 5.6.1   | General robust delay-fault models                    | 161 |

|    | 5.7        |         | isions                                               | 164 |

|    |            |         |                                                      |     |

| 6  | Con        | clusio  | ns                                                   | 167 |

| A  |            |         | letwork Satisfiability                               | 171 |

|    |            |         | tisfiability problem                                 | 171 |

|    |            |         | 3                                                    | 173 |

|    | <b>A.3</b> | The S.  | AT package                                           | 173 |

|    |            | A.3.1   | Forming clauses                                      | 174 |

|    |            | A.3.2   | The search problem                                   | 174 |

|    |            | A.3.3   | Network structure and satisfiability                 | 177 |

| Bi | bliog      | raphy   |                                                      | 179 |

| In | dex o      | of Defi | nitions                                              | 191 |

viii

antigate (1919). Le la companya de Companya de la compa

Additional Control of the Control of

ကျသည်။ သည် သည်သည်။ သည် သည်သည် သည်သည် သည်သည် သည်<mark>မေးမိုးအိုအများမှု မြေ</mark>းများသည်။

The first of the control of the cont

and the second of the second o

and the contraction of the contr

on ng ana a separah kan seregai sebebah berebahkan Afrika seregi kebah milih keban salah kebah salah berbah sa Banan anggaran kebahasan sebesah seberah kebah bersah bersah bersah bersah bersah bersah bersah salah sebagai

and the control of th

on the second of the second and the second of the second o

and the second

£ 11.

18

14-1

.

and a second control of production and section of the control of t

of the control of the conjugate of the first problem of the control of the contro

and the second section of the second

lina kopula rakoja di kijak kombodarijah ili lina (f. 1996).

and the line additionary or become and the particular

on the control of the frequency field straining file of the con-

and the proceeding of the section

TOTAL THE WALLES

The said for the Control of the Cont

o nama elikak kun melitak keralaga erapak olah 1911 - 2011 k

seld of cold to recify to deliver where the

CONTENTS

# List of Figures

| 1.1  | Area versus delay tradeoff on a 32-bit adder                             |

|------|--------------------------------------------------------------------------|

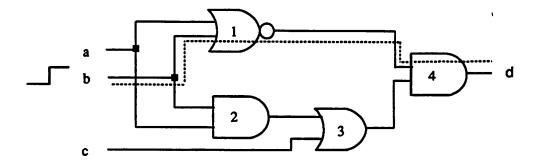

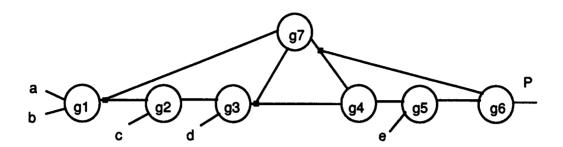

| 2.1  | Example of definitions                                                   |

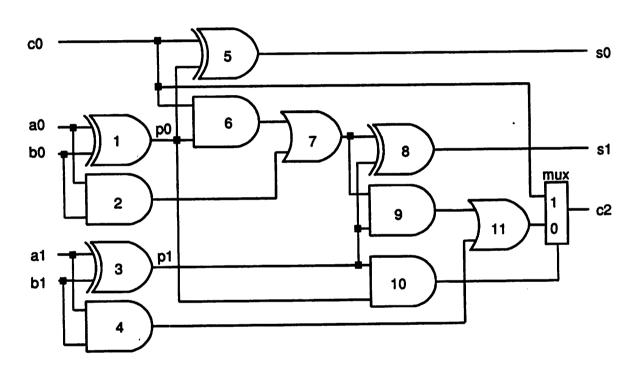

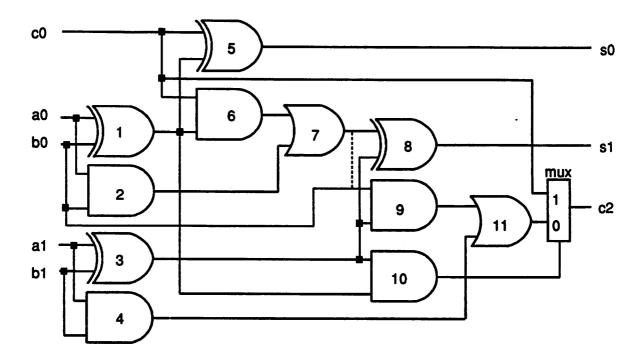

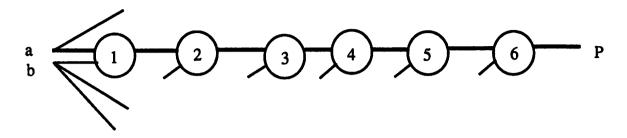

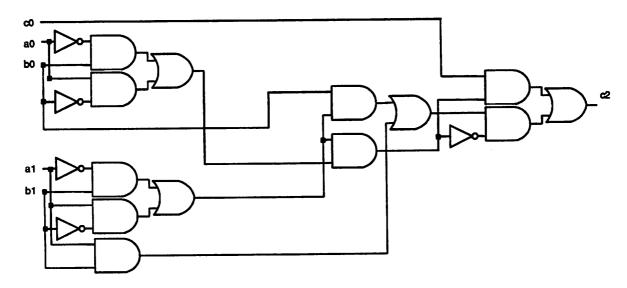

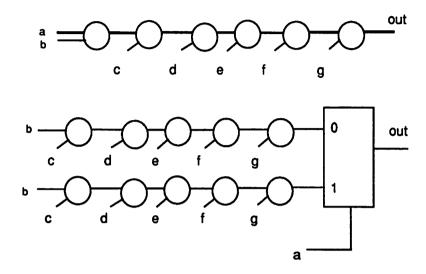

| 2.2  | 2-bit carry-skip adder 24                                                |

| 3.1  | Irredundant 2-bit carry-skip adder                                       |

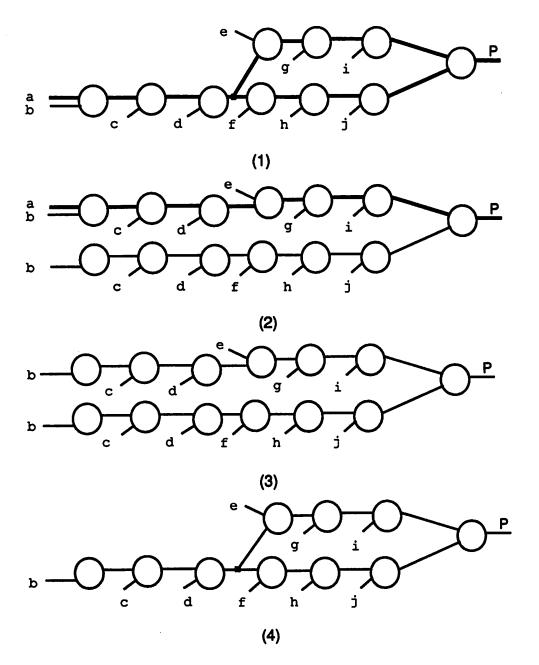

| 3.2  | Example: Fanout-free unsensitizable longest path                         |

| 3.3  | Example: Duplication to avoid fanout on longest path                     |

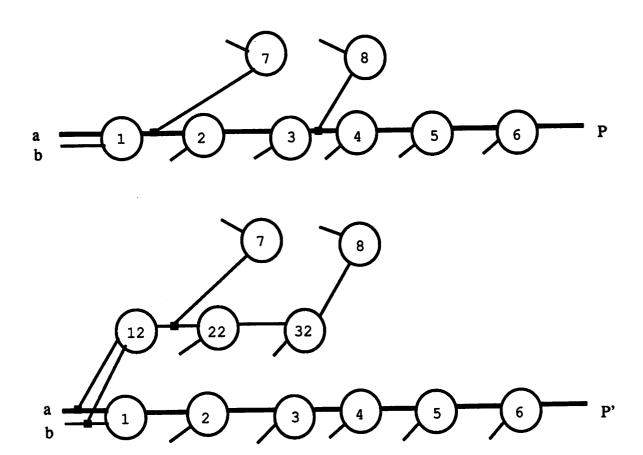

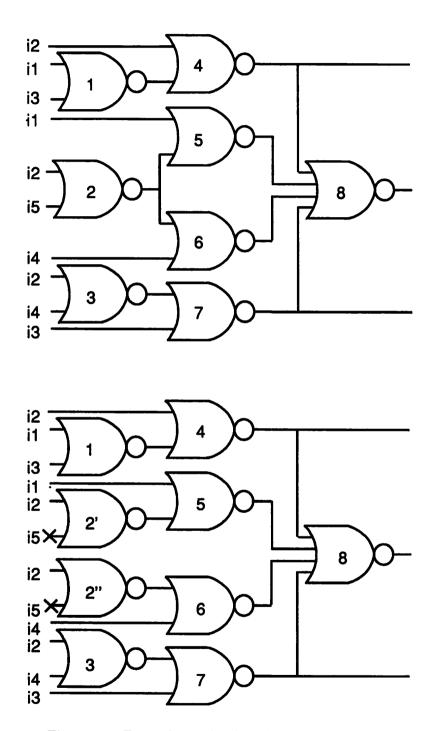

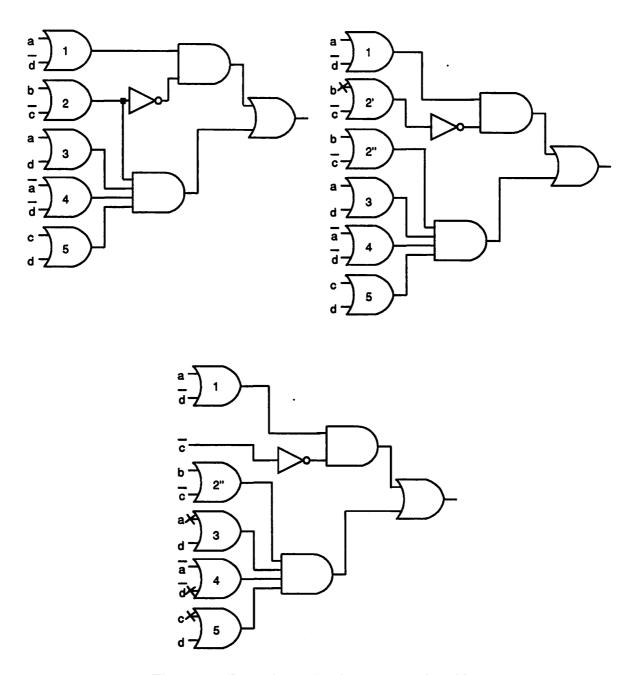

| 3.4  | KMS algorithm for redundancy removal with no increase in delay 3         |

| 3.5  | First intermediate 2-bit carry-skip circuit                              |

| 3.6  | Second intermediate 2-bit carry-skip circuit                             |

| 3.7  | Final 2-bit carry-skip circuit                                           |

| 3.8  | Base case for proof of KMS algorithm                                     |

| 3.9  | Induction case 1 for proof of KMS algorithm                              |

| 3.10 | Induction case 2 for proof of KMS algorithm                              |

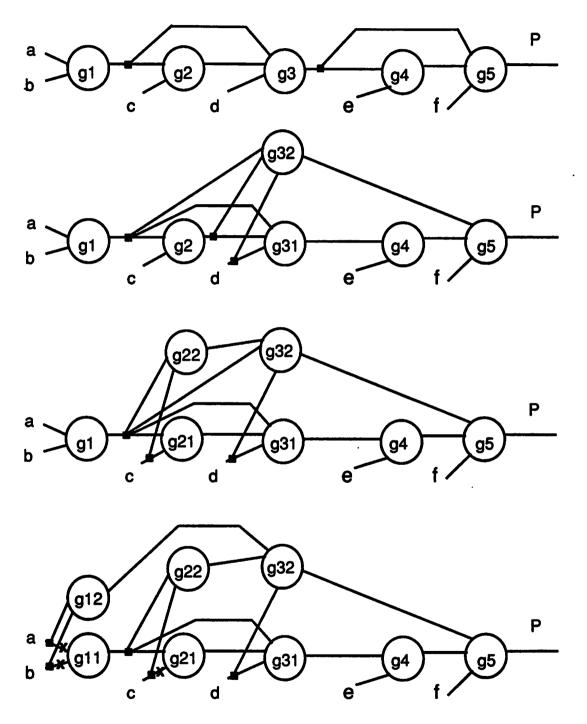

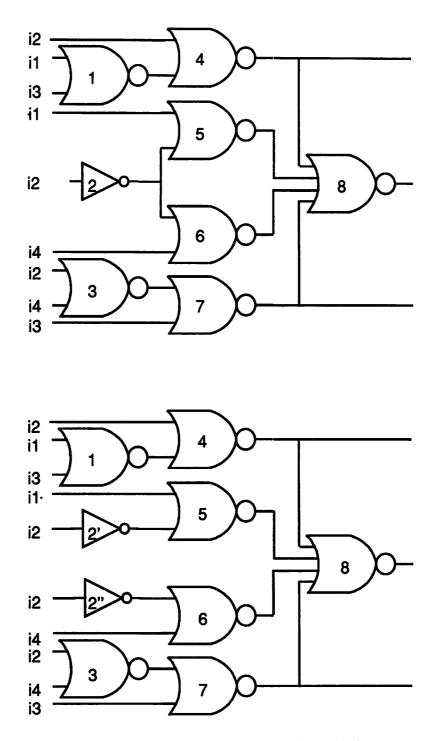

|      | Algorithm for selecting a longest path for duplication                   |

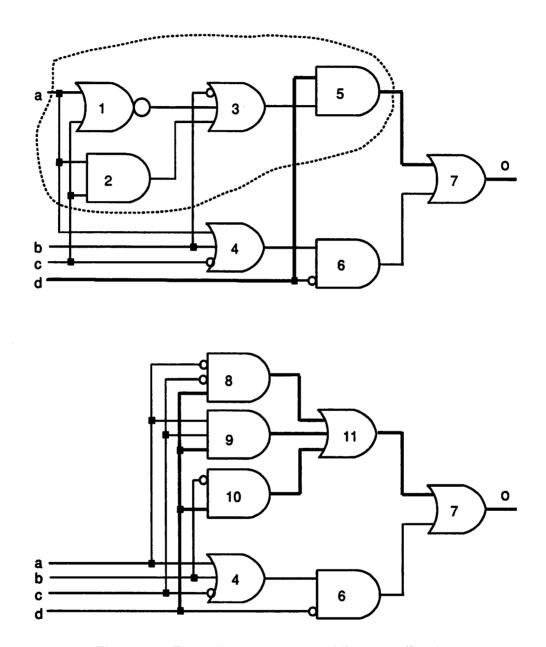

|      | Example: Merging of gates following KMS algorithm                        |

|      | Single-pass algorithm for redundancy removal with no increase in delay 6 |

|      | Path length calculations in the single-pass algorithm                    |

|      | Gate duplication in the single-pass algorithm                            |

|      | Setting constants on false paths in the single-pass algorithm 6          |

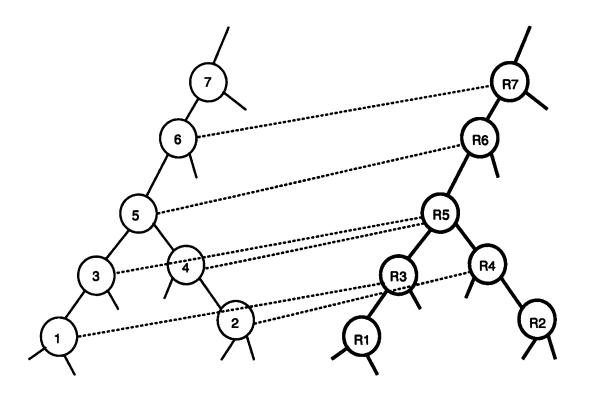

|      | Example: Construction of an L-path-disjoint network                      |

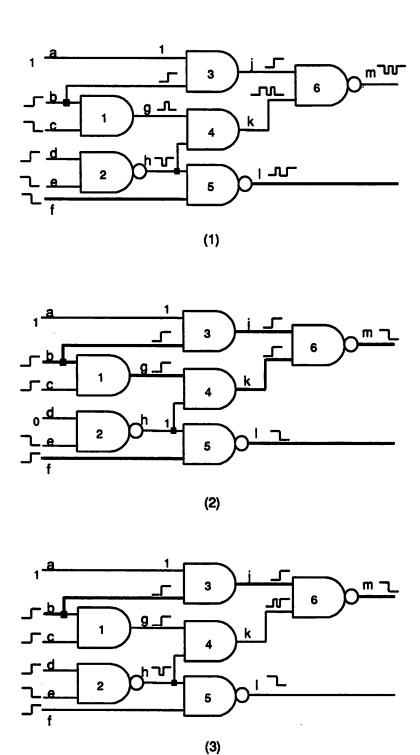

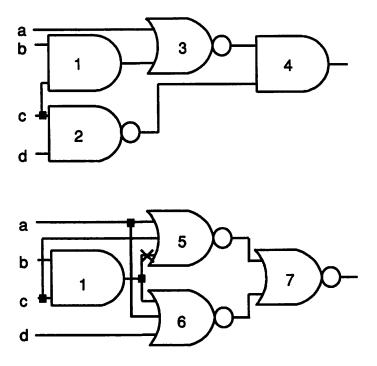

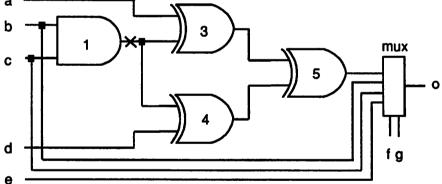

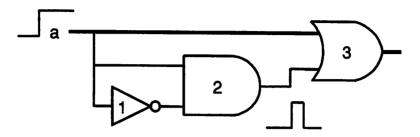

| 4.1  | Examples: Delay-fault testing                                            |

| 4.2  | Outline of the timing optimization process                               |

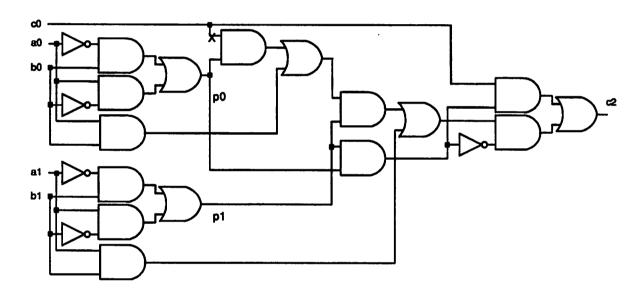

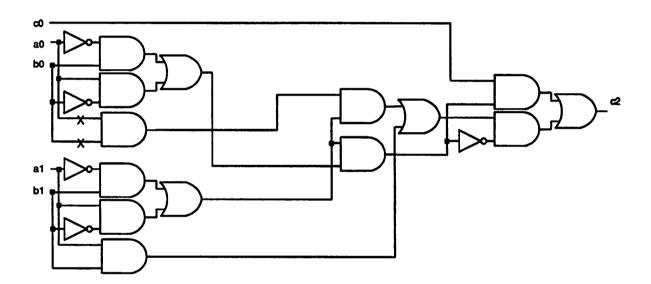

| 4.3  | Example: Timing optimization process                                     |

| 4.4  | Example: Redundant fault on duplication                                  |

| 4.5  | Example: No redundant fault on duplication                               |

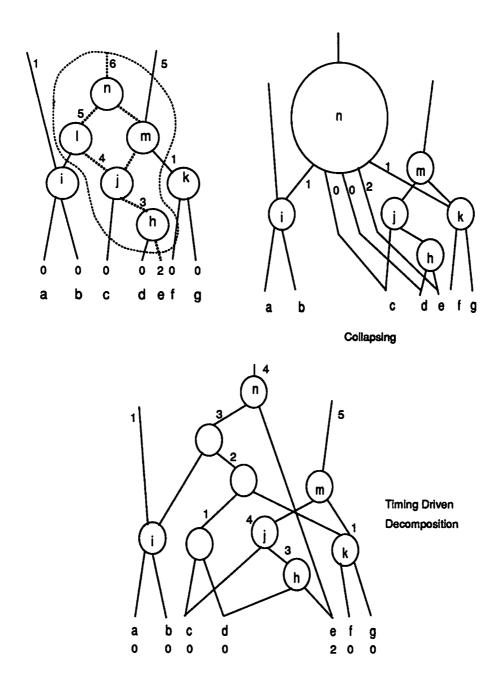

| 4.6  | Example: Redundant fault on collapsing                                   |

| 4.7  | Example: Redundant fault on merging                                      |

| 4.8  | Example: Redundancy removal problem                                      |

| 4.9  | Example: RPDFT untestability on collapsing                               |

| 4.10 |                                                                          |

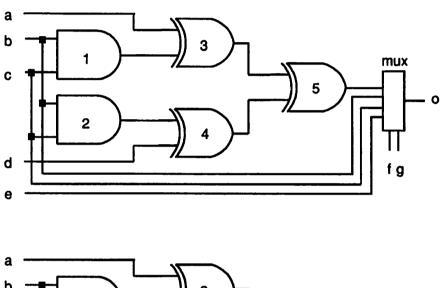

|      | Generalized select transform                                             |

X LIST OF FIGURES

| 4.12       | Generalized bypass transform                                             | 118 |

|------------|--------------------------------------------------------------------------|-----|

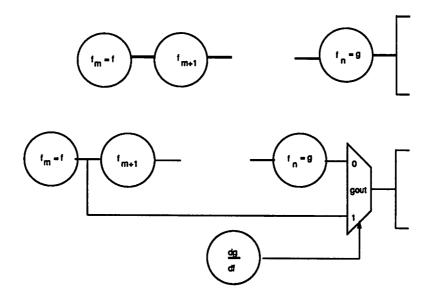

| 5.1        | Example: Representing path-recursive functions by multilevel network     | 126 |

| <b>5.2</b> | Dynamic programming procedure to find longest viable path                | 135 |

| 5.3        | Computation of the viability function                                    | 136 |

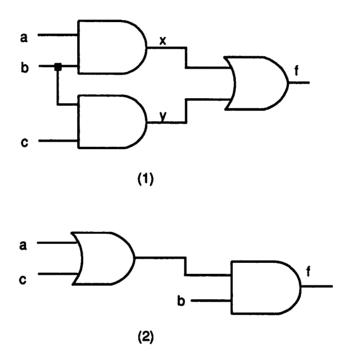

|            | Macro-expansion operation for the function $f = b(a + c) \dots \dots$    |     |

| 5.5        | Example: Multiple function computations at a node during timing analysis | 148 |

| 5.6        | Delay estimation using viability analysis without path-tracing           | 149 |

| 5.7        | Path length calculations for timing analysis without path-tracing        | 150 |

| 5.8        | Computation of $\chi^{f,t}$                                              | 151 |

|            | Example: Hazard problem in robust delay-fault test generation            |     |

## List of Tables

| 3.1        | KMS algorithm versus redundancy removal on adders 54                |

|------------|---------------------------------------------------------------------|

| 3.2        | KMS algorithm versus redundancy removal on MCNC circuits 57         |

| 3.3        | Single-pass algorithm versus redundancy removal on adders           |

| 3.4        | Single-pass algorithm versus redundancy removal on MCNC circuits 71 |

| 3.5        | Single-pass algorithm versus redundancy removal on ISCAS circuits   |

| 4.1        | Example: Impact of redundancy on timing optimization                |

| 4.2        | Redundancy in timing optimization                                   |

| 5.1        | BDD based path-tracing timing analysis on ISCAS circuits            |

| <b>5.2</b> | SAT based path-tracing timing analysis on ISCAS circuits            |

| 5.3        | BDD based path-tracing timing analysis on MCNC circuits 141         |

| 5.4        | SAT based path-tracing timing analysis on MCNC circuits             |

| 5.5        | Timing analysis without path-tracing on ISCAS circuits              |

| 5.6        | Timing analysis without path-tracing on MCNC circuits               |

| 5.7        | Hazard-free RPDFT test generation on MCNC circuits 162              |

| 5.8        | Hazard-free RPDFT test generation on ISCAS circuits                 |

ිදු කරන කරන කරන කරන සහ ප්රතිය සහ සුනා සහ ප්රතිය කරන සම්බන්ධ විශ්ය විශ්ය සහ සම්බන්ධ වෙන සම්බන්ධ වෙනවන් කරන සිට සුදු කරන සහ සහ සහ සම්බන්ධ සහ සිත්තේ සිට සුනා සම්බන්ධ සහ සම්බන්ධ සිට සම්බන්ධ සිට සම්බන්ධ සහ සම්බන්ධ සිට සිට සිට සහ සිට සහ සිට සහ සිත්තේ සහ සම්බන්ධ සම්බන්ධ සම්බන්ධ සම්බන්ධ සම්බන්ධ සිට සිට සිට සම්බන්ධ සම්බන්ධ සම්බන්ධ සිට සිට

and and a sign a section of the real Education of the action of the action of the education of the section of t The action of the education of the section of the education of t

្ត្រាស់ បានប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប សមានប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពល សមានប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប សមានប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រាជិតប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រសាធិតិចិត្តប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពលប្រជាពិចិត្តប្រជាពិចិតប្រជាពិចិត្តប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិតប្រជាពិចិ

and a large for the contraction of the contraction

ាន នៅមានមានទៅក្នុង ២០ សម្រេចសម្រាប់ មួនបង្ហាញ ។ មើនអ្នក ហើយមកស៊ីនិ

## Chapter 1

## Introduction

This thesis explores the interaction between the three primary optimization criteria of logic synthesis during the design of very large scale integration (VLSI) digital circuits, namely performance, testability, and area. The interactions between these criteria are studied primarily in combinational logic circuits, yet also apply to sequential logic. This chapter is organized as follows. In Section 1.1 the role and goals of logic synthesis in the design of VLSI circuits are described. The problems that arise in combinational logic synthesis are briefly reviewed in Section 1.2, with an overview of previous work on these problems. A brief introduction to the interactions between the various optimization criteria is provided in Section 1.3. Section 1.4 describes the scope and organization of this thesis.

#### 1.1 CAD of IC's

Computer-aided design (CAD) of digital integrated circuits (IC's) has proven to be extremely successful for a number of reasons. The most significant of these are the ability to automatically design highly complex IC's, low turnaround times, automatic verification, and better chip quality. While significant improvements have been made individually in each of these aspects of CAD of IC's over the past few years, most of the focus presently is on the quality of a chip design. The principal goals of a high quality IC are the area of the layout, the speed of the circuit and the reliability of the manufactured chip. Good chip quality almost always results in the ability to create a more complex design, with better verification capabilities and lower turnaround times. Chip quality depends to a large extent on the level of sophistication and optimization that is provided by the algorithms

in the different stages of synthesis. In this thesis, the quality of a circuit is focused upon by studying the interactions between the three optimality criteria of area, performance and testability. The design flow in the complete synthesis process of an IC is briefly described below, focusing on the how each of these optimization criteria are addressed at each level.

High-level Synthesis: The initial step in the synthesis of a digital system involves the translation of an abstract specification of the system (referred to as a behavioral specification) to a structural description. The resulting structural description is typically specified as an interconnection of combinational logic blocks and memory elements, termed a register transfer-level description. The function of each combinational block may be specified as a set of logic equations or as well-known functional blocks, e.g. a 32-bit adder. [73] provides a tutorial of the most significant behavioral synthesis algorithms and results. The first step of translating a specification to an intermediate register transfer-level description involves optimizations akin to compiler optimizations. The target optimization criterion may be either the area or performance of the resulting description. The two core transformations used in high-level synthesis are classified as resource scheduling and allocation. Scheduling is performed to assign operations to control steps so as to minimize the delay, subject to some constraints on the amount of available hardware resources. Allocation is the problem of minimizing the amount of hardware needed. While most early synthesis systems performed these two optimization steps independently, all current systems address the area-performance tradeoff that arises at the behavioral synthesis level by relating the optimizations across the two steps. The impact on testability of design choices at this level of synthesis is still emerging as an issue.

Sequential Synthesis: The input description at this level of synthesis is typically a register transfer (or symbolic) description. Often this description is expressed as a finite state machine. Sequential synthesis techniques are used to create a logic level implementation by performing a binary assignment (or encoding) of the states of the symbolic description. There are several techniques that target the optimization of the area of the resulting implementation. These include the minimization of the number of symbolic states in the register transfer description (state minimization) [52], the encoding of symbolic states (state assignment) [34], and the decomposition and factorization of a large state machine into smaller interacting state machines (state decomposition) [52]. A technique for improving the testability of the resulting sequential circuit has also been proposed [39]. While each of the techniques listed above have some impact on the performance of the resulting

circuit, sequential synthesis for performance optimization is not well understood as yet.

Logic Synthesis: Logic synthesis is the process of converting a logical description of a circuit to a technology specific interconnection of gates that realize an equivalent function. In this step of IC synthesis, the optimization goals of minimum area, minimum delay, and complete testability are most directly targeted. The design optimization performed at this level profoundly affects the quality of the final chip with respect to the three optimization goals. The interaction played out between these three axes of optimization at this level is the focus of this thesis.

Layout Synthesis: The final step of synthesis of an integrated circuit prior to manufacture is the process of arranging the network of gates onto actual silicon. This physical synthesis consists in mapping the gates into actual transistors and interconnections among them. The steps in this process include module and gate placement, and global and local routing. [62] provides a complete review of this area. A lot of the problems in this stage of synthesis have mature and widely used solutions. However, an important problem that is emerging at this level is the ability to provide the logic and behavioral level synthesis tools fast and accurate estimates of the area and delay corresponding to various choices of structures during optimization. Recent work includes algorithms for timing driven placement [54], and proposals for fast and accurate estimates of area and performance at the layout level to direct performance oriented logic synthesis operations [86]. This stage of synthesis has an impact on the testability of the IC related to defects arising due to the physical proximity of transistors and wires (e.g. bridging faults); however, results relating the effects of layout synthesis on testability are lacking.

A more complete description of performance-directed synthesis at all levels of the design of VLSI systems is provided in [2].

### 1.2 Combinational logic synthesis

Given a functional description of a system that includes memory constructs, combinational logic synthesis extracts only the combinational portion of the logic for optimization. The memory elements are connected back into the final optimized circuit at the end of the process. [16] is a complete description of the algorithms and approaches used in this level of synthesis. In this section, the three most common goals of any logic optimization problem are considered; the focus is on techniques and results relevant to the subject of this thesis.

#### 1.2.1 Area optimization

By far the best understood aspect of combinational logic synthesis is the manipulation of logic equations to yield an implementation of minimal area. When the target technology is a two-level implementation both exact and heuristic algorithms are well established [30, 15]. In two-level implementations, the area of an implementation is proportional to the number of terms. A secondary function is the number of occurrences of the variables (referred to as the number of literals). In multilevel logic, exact minimization algorithms are much harder to achieve than for two-level logic, since the solution space is considerably larger due to increased degrees of freedom compared to two-level logic [16]. However, several techniques exist that yield sufficiently high-quality area-minimal solutions. In a multilevel implementation, area is most often estimated by the number of literals in the implementation. For multilevel implementations there are two basic approaches that are adopted. The first is a rule-based approach consisting of the application of selected transformations from a given collection of rules developed by experienced circuit designers [32, 7]. The second is algorithmic based [18, 5]. Synthesis systems based on this approach have proved substantially superior to those based on the former [16]. Many industrial synthesis systems employ the second technique followed by the first.

A successful strategy employed in the latter approach is to decompose the process into two steps: technology independent optimization and technology dependent optimization. This often simplifies the design and optimization problem to be solved, while still yielding an efficient solution. Technology independent operations, which apply to generic gates independent of technology specific information, may be further classified as algebraic and Boolean. While algebraic operations restrict the set of operations that are used to optimize circuit structure, they are popular due to the time-efficiency of the process. They can be performed in polynomial time in the number of variables of a function [111]. Boolean operations are more time-consuming, yet are essential in obtaining minimal circuits [97]. The technology dependent optimizations consist of mapping the generic gates to a specific library of cells, corresponding to a target technology [35].

#### 1.2.2 Performance optimization

Performance optimization is almost always the primary optimization criteria in logic designs [2, 16] (subject to some area constraints). A typical problem is to improve the

delay of an existing circuit structure. At the technology independent level this is done by incremental modifications to the structure of the network to yield a faster circuit. Three transformations [105, 78, 11], that have recently matured into efficient and feasible algorithms to reduce the delay of circuits are studied in detail in this thesis. At the technology dependent level, delay may be minimized instead of area during the mapping phase [108]. An alternate technique, that is often used in conjunction with mapping, is the insertion of buffer cells with high capacitative-drive properties to further improve delays through gates propagating signals to several different parts of the circuit [10].

While a reasonable first-order approximation of the delay of a circuit is the number of levels of gates that a signal passes through, it is known that capacitative loading effects, functional considerations, and other operating factors (e.g. transistor gate sizes) must also be taken into account [76]. In this thesis, performance estimates are made after the incorporation of all these factors. In fact, the core problems addressed in subsequent chapters result from the interactions of these factors during delay estimation of high-performance circuits. In particular, the interaction between the logical and timing behavior is related to the impact on the testability and area of a circuit.

#### 1.2.3 Testability optimization

Testability refers to the ability to determine whether an IC is behaving in accordance with the given specifications. Most approaches to digital IC testing before the middle of the last decade attempted to improve the testability of the design by ad-hoc post-synthesis modifications. However, with persistently increasing VLSI densities, the increasing need for reliability in manufactured circuits has led to the evolution of testability as an important logic optimization criterion.

In order to refer to the ability to test a chip a fault model is required. Several fault models are in use today. The most common is the stuck-fault model that detects static (or DC) defects [19]. However, since the delay of a chip is often as critical as its logical behavior, circuits also have to be tested for dynamic (or AC) defects [106]. This has led to the definition of two delay fault models. Even more comprehensive detection of manufacturing defects may be achieved by checking for faults that model open and shorted connections within transistors. One goal when optimizing combinational circuits for testability is to ensure that 100% of all faults being modeled can be tested by applying a suitable test vector

sequence at the primary inputs of the circuits. A defect is detected as a logical difference at some primary output. Other important considerations are the number of test vectors required to detect all the faults, the computation effort required in generating the tests, and the time required to apply them.

There are well developed synthesis techniques for all of the fault models listed above. Most are best understood for two-level circuits [6, 51, 36]. However, several multilevel optimization operations are known that may be used to retain testability in circuits [51, 36, 94, 20].

#### 1.3 Relations between optimization criteria

The goal of logic optimization is to obtain a design that is fully optimized with respect to all three criteria; yet, all the optimization techniques mentioned in the previous section target only one of the three criteria. However, when optimizing for one of the goals, sometimes the effects on the remaining criteria are known or may be predicted. A brief description of some of these known results is presented below.

#### 1.3.1 Area and testability

The area of a circuit is directly related to its testability. Here testability means the percentage of faults for which there exists a test vector which tests for the fault. The reason for this is as follows. Consider a connection which can be set to a constant value without affecting the functionality. In such a case, this connection may as well be replaced by the constant value, thus resulting in a smaller circuit. If the connection is retained in the circuit then a manufacturing defect that appears on the connection cannot be tested; this leads to an untestable circuit. Untestable circuits are undesirable for several reasons which are explored in detail in the next chapter. Besides a non area-minimal implementation, untestability impedes the test generation process and degrades the reliability of a chip. The circuit resulting from the replacement of the connection by a constant is more testable than the original circuit. There are several optimality criteria that can be used to relate area to testability. The first order optimality criterion for area is related to 100% single stuck-fault testability [6]. In such a circuit, no single connection can be removed without changing the function of the circuit. A second order form of optimality is related to the more stringent testability criterion of 100% multiple stuck-fault testability [51]. In such a circuit no set of

connections can be simultaneously removed from a circuit without changing the function of the circuit.

#### 1.3.2 Area and delay

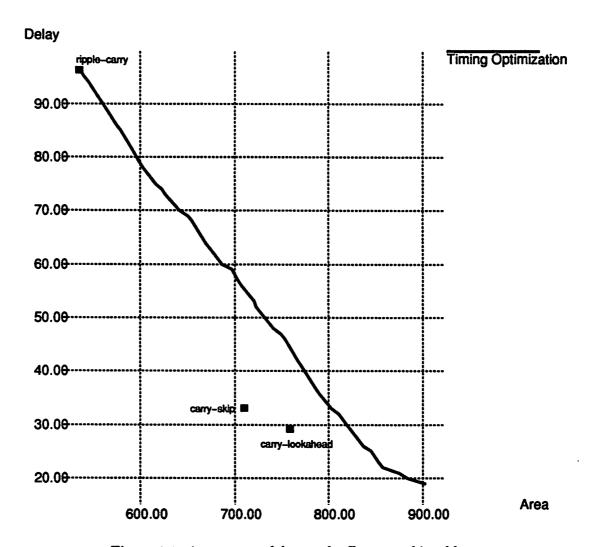

Any of the approaches described in Section 1.2.2 can be used to achieve an improvement in the delay characteristic of a circuit, albeit with some penalty in area of the resulting implementation [105]. An example of this phenomenon is the several different implementations of an adder circuit. A ripple-carry adder has the least area among all adders, but it is also the slowest. A carry-skip adder [66] is faster and is derived using an additional AND gate and MUX. A carry-select adder [112], is similarly derived from a ripple-carry adder with some duplication of logic to achieve a reduction in speed. A circuit with even better delay uses a carry-lookahead structure, [112], but at substantially higher cost in area.

Synthesis techniques also show the same phenomenon. An example of the areadelay tradeoff is shown in Figure 1.1, where a 32-bit ripple carry adder is optimized for delay using path reduction techniques [105]. The experiment is performed using a parameter to control the strength of the optimizations used in restructuring the logic. Details of this procedure are discussed in the sequel. It is instructive to note that during the course of the area-delay tradeoff, each of the manual adder designs mentioned above is achieved by the automatic synthesis procedure.

#### 1.3.3 Other relationships

Little is known of the remaining relationships that exist between the three criteria. The purpose of this thesis is to explore the interactions between area, testability and delay more completely. In particular, the focus is on the relationship between the delay and testability in area minimal circuits. This relationship is shown to be critical in the design of reliable high-performance circuits. An interesting aspect of this exploration is that it leads to similar approaches to efficiently solving problems that involve timing analysis and test generation for all types of fault models.

#### 1.4 Thesis contributions and overview

A general question that captures the focus of this thesis is:

Figure 1.1: Area versus delay tradeoff on a 32-bit adder

• What is the relationship between the performance, testability, and area of an optimized logic circuit?

While the principal focus will be on the interaction between the performance and testability of circuits, the area of the synthesized design is always an important consideration in the results stated in this thesis.

Chapter 2 explores the impact of redundancy in high-performance circuits. Most high-speed circuits have redundancy introduced when delay optimization is performed on a circuit. At first, it appears that this redundancy is necessary to reduce the delay of the circuit since a straightforward technique for removing redundancy slows down the circuit. The redundancy also has a profound effect on the reliability of the manufactured circuits. The illustration of a high-performance and redundant circuit that exhibits unreliable behavior motivates three problems that are addressed in the remaining chapters of this thesis.

Chapter 3 addresses the question of whether redundancy is necessary to reduce delay. An algorithm is provided that converts any high-speed redundant circuit into an irredundant one guaranteed to be no slower. A proof of the invariance of the delay estimate in the original and final circuits using the most accurate functional timing analysis technique is provided.

Even though redundancy is unnecessary to reduce delay, performance optimization transformations may reduce testability, and this is studied in Chapter 4. Different fault models are considered to examine their invariance under common delay optimization transformations. In particular, delay-fault testing of IC's, which has found increased interest in recent years, is considered.

In the area of performance optimization, delay estimation of a circuit has lacked efficient algorithms. In the area of testability, efficient algorithms for delay-fault testing have not existed until recently. Both timing analysis and delay-fault testing are the focus in Chapter 5, where a uniform and novel approach to solving general path analysis problems is presented [80].

Chapter 6 provides a synopsis of the theoretical and practical results obtained in this research.

The solutions to several problems in this thesis are obtained by formulating them as Boolean satisfiability problems. An overview of the heuristics used in solving a general Boolean satisfiability problem is provided in Appendix A.

oninate on autoriogram, deprindinta de la secolo de la contrate de la sego de sinai en internacionale. Especialista de la companya de la confesiona de la sego de sinatorio, de la confesiona de la confesiona de la La confesiona de la confe

o provincia de la completa de la com La completa de la co La completa de la comp

entitus para la la la compania de l La compania de la co

and the contract of the contra

Application of the control of the excitation to be a significant expension of the control of the contro

Lesses provinces de la final de la final de la companya de la final de la fina

The same of the control of the sites of the same of the same of the same of the control of the c

under konstantigen in die geschellte der Steuerschaftliche der der steuerschaftliche in der Ausbergerichte der Lieder von der werten der Antonier der Steuerschaftliche der Landerschaftliche der Steuerschaftliche der Antonier der Steuerschaftliche der Steuerschaftliche der Steuerschaftliche der Steuerschaftliche der Steuerschaftliche der Antonier der Steuerschaftliche der

## Chapter 2

## Redundancy and Delay

This chapter serves two purposes. The first part provides definitions of the two circuit properties that are of most concern in this thesis, namely redundancy and delay. Following a few basic definitions relating to combinational circuits in Section 2.1, the terms and techniques used in the testability and delay analysis of Boolean networks are discussed in Sections 2.2 and 2.3, respectively. The second part of this chapter explores the interaction between redundancy and delay. Besides the well known disadvantages of redundancy, briefly reviewed in Section 2.4, a significant reliability problem due to redundancy is discussed in Section 2.5 using the example of a well known adder circuit. This example motivates three problems, enumerated in Section 2.7, and addressed in the remainder of this thesis. Related work is reviewed in Section 2.6 to place the contributions of this thesis in context.

#### 2.1 Boolean networks

During the process of logic synthesis, combinational logic is represented by an abstraction known as Boolean network. A few definitions related to Boolean networks required in subsequent discussions are provided below. Further details may be found in [16].

Definition 2.1.1 A combinational circuit (or Boolean network) is a directed acyclic graph composed of gates (or nodes) and connections (or edges) between gates.

Definition 2.1.2 A path in a combinational circuit is an alternating sequence of connections and gates,  $\{c_0, f_0, c_1, ..., c_m, f_m, c_{m+1}\}$ , where connection  $c_i$ ,  $1 \le i \le n$ , connects the output of gate  $f_{i-1}$  to an input of gate  $f_i$ . The  $f_i$ 's are referred to as gates along the path.

Defining a path as a sequence of connections and gates, rather than simply as a sequence of gates, gives greater flexibility in modeling delay and allows the unambiguous description of circuits with more than one connection from one gate to another.

Definition 2.1.3 A path that includes a primary input and a primary output is termed an IO-path.

Definition 2.1.4 The depth of a circuit is the maximum number of gates along any path in the circuit.

Definition 2.1.5 If the output of a gate  $f_1$ , is connected to an input of gate  $f_2$ ,  $f_1$  is a fanin of  $f_2$ . Gate  $f_2$  is a fanout of gate  $f_1$ . If there is a path from  $f_i$  to  $f_j$ , then  $f_i$  is a transitive fanin of  $f_j$ , and  $f_j$  is a transitive fanout of  $f_i$ .

Definition 2.1.6 A literal refers to a Boolean variable that appears either in its complemented or uncomplemented form, e.g. x' or x.

Definition 2.1.7 A cube is a product of literals: e.g. xy'z. A minterm is a cube in which every variable appears.

Minterms may be used to represent the values of a set of input variables: e.g. xy'z is shorthand for x = 1, y = 0, and z = 1. In this way there is a natural correspondence between an input vector or input stimulus and a minterm. This correspondence may be extended to cubes where unspecified values in the function are assumed to be arbitrary or unknown values. Thus if a circuit C has inputs v, w, x, y, and z, then applying the cube xy'z to C is shorthand for applying u = X, v = X, x = 1, y = 0, and z = 1. Here X denotes an unknown value.

In this thesis, the terms logical behavior and temporal behavior of a combinational circuit are used to make an important distinction. Logical behavior refers to the final value on each primary output of the circuit when a stable value is asserted on the primary inputs. Two circuits are logically equivalent under an input cube if they have the same stable values on the primary outputs. Temporal behavior refers to the dynamic behavior of the circuit, which considers the logical values on the primary outputs at a particular instant of time. Thus, two circuits may exhibit the same logical behavior under an input cube, yet the final values on the primary outputs of one circuit may be available at different times than the other circuit. In this case, the circuits exhibit different temporal behavior.

#### 2.2 Redundancy in a network

Most manufactured IC's must be tested. The goal of testing is to determine whether a manufactured circuit behaves correctly. This is done by applying test vectors (at the primary inputs) that distinguish between the functional behavior of the correct and faulty circuits. Defects that may occur are abstracted using fault models which define their impact on circuit behavior. For example, a fault may change only the logical value on some gate in a circuit. Another modeled fault may impact only the timing behavior of a gate, but not its logical behavior. Although several fault models have been proposed [19], in this thesis only the two major classes of fault models are considered. The first, and most common, are static faults that model only the impact of defects on the logical behavior of gates or connections in circuits. This class is briefly reviewed later in this section. The second, introduced and discussed in detail in Chapter 4, are delay-faults, which represent changes only in the temporal behavior of gates or connections.

Having chosen a fault model, the term testability of a circuit refers to the ability to generate a test for each fault that may exist in the network. The term testability has many connotations in testing and synthesis [4, 27]. It often includes the time required for test pattern generation and the time required for actual application of the tests to each manufactured circuit. These two criteria are particularly significant in some methods of testing sequential circuits [47]. Since the focus here is on combinational circuits, our only concern with respect to testability is the existence of a test for each fault.