Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# SYNTHESIS OF VLSI DESIGNS WITH SYMBOLIC TECHNIQUES

by

Bill Lin

Memorandum No. UCB/ERL M91/105

27 November 1991

# SYNTHESIS OF VLSI DESIGNS WITH SYMBOLIC TECHNIQUES

by

Bill Lin

Memorandum No. UCB/ERL M91/105

27 November 1991

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Synthesis of VLSI Designs with Symbolic Techniques

Bill Lin

Ph.D. University of California, Berkeley

Department of Electrical Engineering and Computer Sciences

#### Abstract

Very large-scale integrated circuits are essential in modern digital electronic systems. Integrated circuits with over a million transistors are possible with current technology. The design of these circuits is an extremely difficult and time consuming process, virtually impossible without the use of design-aids to assist in some aspects of design. In this dissertation, a variety of techniques are presented for automating this design process starting from a register-transfer level hardware description of the desired functionality down to an optimized circuit implementation for fabrication. This automation is referred to as synthesis. Specifically, the synthesis of sequential designs is considered. To model real life situations, the hardware description may contain variables that carry symbolic values. This form of specification is referred to as a symbolic specification. The first contribution of this work is to present the concept of symbolic relation for specifying multiple choices of output mappings. This is useful for capturing the next-state behavior of a finite state machine in the presence of equivalent states. The optimization problem requires both the selection of output mappings and binary code assignments. A unified framework for solving this problem exactly for two-level implementations has been developed. The second contribution of this research is a set of encoding algorithms for multi-level logic implementations. These algorithms have the merit of being very fast and can be used to encode large hardware descriptions compiled from hardware description languages. Techniques for optimizing sequential circuits, once they have been encoded, have also been developed in this research. These techniques are based on the use of global state-space information with well-developed combinational logic optimization algorithms. A key problem that arises is the need for efficient algorithms to derive state-space information for large sequential circuits. Efficient algorithms based on binary decision diagrams have been developed for this purpose. An associated problem is the state minimization of large sequential circuits. New concepts and machinery for representing and manipulating equivalence classes efficiently are presented for solving this and related problems.

## Synthesis of VLSI Designs with Symbolic Techniques

Copyright © 1991

Bill Lin

### Acknowledgments

I would first like to thank my advisor, Prof. Richard Newton, for his guidance, inspiration, encouragement, and support during my graduate years at Berkeley. This work would not have been possible without his help and trust in me. I am also grateful to Prof. Bob Brayton for taking the burden of being on both my qualifying examination and thesis committees. He read my dissertation meticulously and offered many constructive criticisms. He has also influenced me to be more rigorous and precise in my thinking. I have also to thank Prof. Jan Rabaey for being on my qualifying examination committee. Although I have not had the opportunity to work with him directly, I have enjoyed all our stimulating conversations on a broad range of topics. Prof. Sarah Beckman has been a member of both my qualifying examination and thesis committees. I am thankful for her time and suggestions. My research was sponsored in part by National Science Foundation and Defense Advanced Research Project Agency. I am grateful for their financial support.

Part of the work reported here has been done in collaboration with others. The symbolic relations work was done together with Fabio Somenzi of University of Colorado, Boulder. The sequential optimization work using implicit enumeration was done together with Hervé Touati.

Being a part of the Berkeley CAD-group has really been an enriching experience. I have Richard Newton, Bob Brayton, Don Pederson, and Alberto Sangiovanni-Vincentelli to thank for creating such an extraordinary research environment and for recruiting a truly remarkable team of people. This might well be the "best" place in the world for research. I have been extremely fortunate and privileged to be a part of this talented group. I have also to thank the many interesting and brilliant people in the group for making the CAD-group an exciting place. Thanks go to Wendell Baker, Brian O'Krafka, and Masahiro Fukui for being great office-mates. I would like to thank Pranav Ashar, Wendell Baker, Mark Beardslee, Srinivas Devadas, Abhijit Ghosh, Tim Kam, Sharad Malik, Rajeev Murgai, Alex Saldanha, Hamid Savoj, Ellen Sentovich, Narandra Shenoy, Kanwar Jit Singh, Hervé Touati, Yosinori Watanabe, and Greg Whitcomb for many interesting discussions on a wide variety of topics. Thanks also to Andrea Casotto, Gary Jones, Chuck Kring, Luciano Lavagno, Brian Lee, Chris Lennard, Rick McGeer, Cho Moon, Jaijeet Roychowdhury, Henry Sheng, Paul Stephan, and Tiziano Villa for making 550-Cory a more lively place. Special thanks to Gary Jones, Henry Sheng, and Dan Preslar for "being there" in the last few months. I

don't think I would have gotten through without them.

Many thanks to Kia Cooper, Elise Mills, and Flora Oviedo for all the friendly assistance provided over the years. Brad Krebs and Mike Kiernan were always helpful in hardware and software problems.

During my graduate years at Berkeley, I have also had the fortune to interact with many people from other places. I have certainly enjoyed my interactions with Fabio Somenzi, Gary Hachtel, and Xuejun Du from University of Colorado, Boulder. I have also had the pleasure to interact with Olivier Coudert and Jean-Christophe Madre from the Bull Research Center in France, and Takayasu Sakurai from Toshiba Corporation in Japan. Apart from many stimulating discussions on research issues, David Ku from Stanford has also been a very good friend. I hope our friendship continues for many years to come.

Above all, I would like to thank Joyce Fung for her constant love and support, especially this past year. Words cannot express my feelings. We have been through a great deal together. I don't think I could have made it through without her. I would like to thank my family, especially my parents, Michael and Kitty Lin, for their support, encouragement, and enthusiasm in my life. I thank them for everything that I am today.

## Contents

| A  | ckno                                      | wledgements                                               | i   |  |  |  |  |  |

|----|-------------------------------------------|-----------------------------------------------------------|-----|--|--|--|--|--|

| Тŧ | able o                                    | of Contents                                               | iii |  |  |  |  |  |

| Li | st of                                     | Figures                                                   | vi  |  |  |  |  |  |

| Li | st of                                     | Tables                                                    | vii |  |  |  |  |  |

| 1  | Intr                                      | roduction                                                 | 1   |  |  |  |  |  |

|    | 1.1                                       | A Design Trajectory                                       | 1   |  |  |  |  |  |

|    | 1.2                                       | Previous Work                                             | 5   |  |  |  |  |  |

|    |                                           | 1.2.1 Symbolic Encoding Techniques                        | 5   |  |  |  |  |  |

|    |                                           | 1.2.2 Sequential Optimization Techniques                  | 7   |  |  |  |  |  |

|    |                                           | 1.2.3 Symbolic Representations and Computation            | 9   |  |  |  |  |  |

|    | 1.3                                       | Overview of Dissertation                                  | 10  |  |  |  |  |  |

| 2  | Symbolic Relations and Two-Level Encoding |                                                           |     |  |  |  |  |  |

|    | 2.1                                       | Introduction                                              | 13  |  |  |  |  |  |

|    | 2.2                                       | Background and Terminology                                | 17  |  |  |  |  |  |

|    |                                           | 2.2.1 Boolean Functions and Relations                     | 17  |  |  |  |  |  |

|    |                                           | 2.2.2 Symbolic Functions                                  | 18  |  |  |  |  |  |

|    |                                           | 2.2.3 Symbolic Relations                                  | 20  |  |  |  |  |  |

|    |                                           | 2.2.4 Finite State Machines                               | 21  |  |  |  |  |  |

|    |                                           | 2.2.5 Binary Decision Diagrams                            | 23  |  |  |  |  |  |

|    | 2.3                                       | Minimization of Symbolic Relations                        | 24  |  |  |  |  |  |

|    |                                           | 2.3.1 Definitions of Symbolic Relations Problems          | 24  |  |  |  |  |  |

|    |                                           | 2.3.2 FSM Synthesis: Restructuring and State Assignment   | 26  |  |  |  |  |  |

|    | 2.4                                       | A Unified Framework                                       | 30  |  |  |  |  |  |

|    | 2.5                                       | Prime Generation                                          | 31  |  |  |  |  |  |

|    |                                           | 2.5.1 Candidate Primes for Boolean Relations              | 31  |  |  |  |  |  |

|    |                                           | 2.5.2 Generalized Candidate Primes for Symbolic Relations | 32  |  |  |  |  |  |

|    |                                           | 2.5.3 Reduced Prime Implicant Table                       | 35  |  |  |  |  |  |

|    | 2.6                                       | Exact Symbolic Relation Constraints                       | 35  |  |  |  |  |  |

|    |                                           | 2.6.1 Output Encoding                                     | 35  |  |  |  |  |  |

iv CONTENTS

|   |            | 2.6.2                | State Encoding                                     | 38        |  |  |

|---|------------|----------------------|----------------------------------------------------|-----------|--|--|

|   |            | 2.6.3                | State Minimization and State Encoding              | 39        |  |  |

|   | 2.7        |                      |                                                    | 40        |  |  |

|   |            | _                    |                                                    | 40        |  |  |

|   |            | 2.7.2                | Branch-and-Bound Techniques                        | 41        |  |  |

|   |            |                      | BDD-Based Formulation of Binate Covering           | 43        |  |  |

|   |            |                      | <del>_</del>                                       | 45        |  |  |

|   | 2.8        |                      |                                                    | 48        |  |  |

|   |            |                      |                                                    | 48        |  |  |

|   |            |                      | <del>_</del>                                       | 50        |  |  |

|   | 2.9        |                      | <del>-</del>                                       | <b>52</b> |  |  |

| • | 3.6        | M. T                 | l Comballa Branchia                                |           |  |  |

| 3 |            |                      | l Symbolic Encoding                                | 53        |  |  |

|   | 3.1<br>3.2 |                      |                                                    | 53        |  |  |

|   |            |                      |                                                    | 55        |  |  |

|   | 3.3        |                      |                                                    | 55        |  |  |

|   | 3.4        |                      |                                                    | 57        |  |  |

|   | 3.5        |                      | trum of Graph Embedding Algorithms                 | 59        |  |  |

|   |            |                      | 3 . 3                                              | 60        |  |  |

|   |            |                      |                                                    | 62        |  |  |

|   |            |                      | Exact Binate Covering Formulation                  | 62        |  |  |

|   | 3.6        |                      | nental Results                                     | 66        |  |  |

|   |            |                      | Comparing Encoding Programs                        | 68        |  |  |

|   |            |                      | Comparing Post Encoding Optimization Procedures    | 69        |  |  |

|   |            |                      | Comparing Graph Embedding Algorithms               | 72        |  |  |

|   | 3.7        | Conclus              | sions                                              | 74        |  |  |

| 4 | Opt        | imizati              | on of Sequential Circuits                          | 78        |  |  |

|   | 4.1        | Introdu              | ction                                              | 78        |  |  |

|   | 4.2        | State S <sub>1</sub> | pace Analysis for Sequential Optimization          | 80        |  |  |

|   | 4.3        | Efficien             | t State Enumeration                                | 84        |  |  |

|   |            | 4.3.1                | Set Computation and BDD Operators                  | 84        |  |  |

|   |            | 4.3.2                | Representation of States and State Relations       | 85        |  |  |

|   |            | 4.3.3                | Implicit Enumeration and Fixed Point Computation   | 87        |  |  |

|   | 4.4        | Comput               | ting the Equivalent States                         | 88        |  |  |

|   |            | 4.4.1                | Equivalence-Based Analysis                         | 90        |  |  |

|   |            |                      | Differentiation-Based Analysis                     | 90        |  |  |

|   |            |                      | Computing Single Cycle State Equivalence           | 93        |  |  |

|   |            |                      | Computing State Equivalence in the Valid Component | 94        |  |  |

|   | 4.5        |                      | · =                                                | 95        |  |  |

|   | 16         | A. 6. Complesions    |                                                    |           |  |  |

CONTENTS

| 5  | Imp          | plicit Manipulation of Equivalence Classes      | 100 |

|----|--------------|-------------------------------------------------|-----|

|    | 5.1          | Introduction                                    | 100 |

|    | <b>5.2</b> . | Definitions and Notation                        | 102 |

|    | <b>5.3</b>   | Efficient Representation of Equivalence Classes | 104 |

|    | 5.4          | The Compatible Projection Operator              | 105 |

|    |              | 5.4.1 Definition and Properties                 | 105 |

|    |              | 5.4.2 An Efficient Algorithm using BDD's        | 107 |

|    | 5.5          | <del>_</del>                                    | 108 |

|    |              | 5.5.1 Communication Complexity                  | 108 |

|    |              | 5.5.2 Reduction of Finite Automata              | 110 |

|    | 5.6          | Experimental Results                            | 112 |

|    | 5.7          | Conclusions                                     | 116 |

| 6  | Mir          | nimization of State Latches                     | 118 |

|    | 6.1          | Introduction                                    | 118 |

|    | 6.2          | Redundant Encoding Variable Removal             | 120 |

|    | 6.3          | BDD-Based Branch-and-Bound Algorithm            | 122 |

|    | 6.4          | Experimental Results                            | 124 |

|    | 6.5          | Conclusions                                     | 128 |

| 7  | Cor          | nclusions                                       | 129 |

| Bi | bliog        | zraphy                                          | 133 |

# List of Figures

| 1.1 | A Symbolic Specification Fragment written in VHDL                        | 3   |

|-----|--------------------------------------------------------------------------|-----|

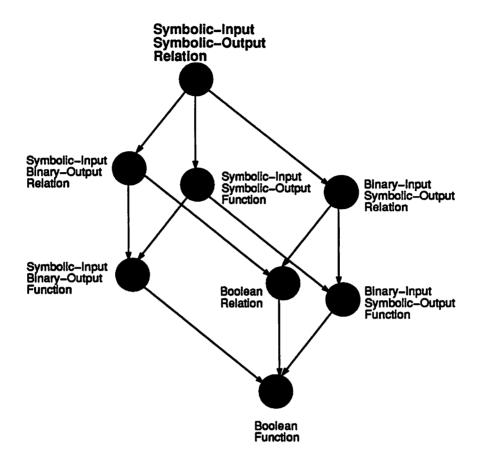

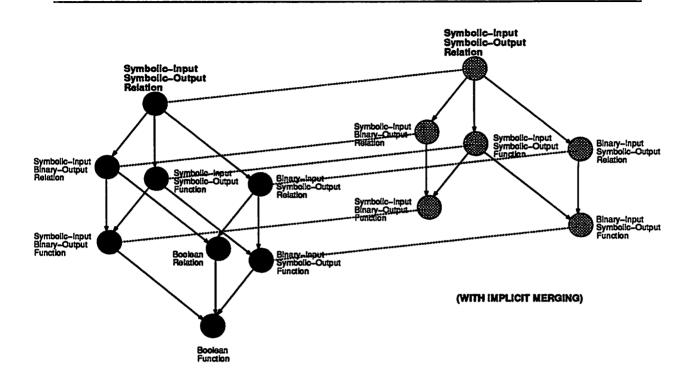

| 2.1 | Lattice of Symbolic Minimization Problems                                | 25  |

| 2.2 | Symbolic Minimization Problems with Implicit Merging                     | 26  |

| 2.3 | Limitation of State Assignment                                           | 27  |

| 2.4 | Splitting and Merging of States                                          | 28  |

| 2.5 | Limitation of State Minimization                                         | 29  |

| 2.6 | Prime Generation Procedure for c-primes of Boolean Relations             | 33  |

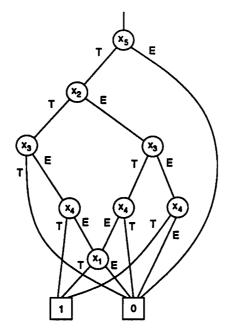

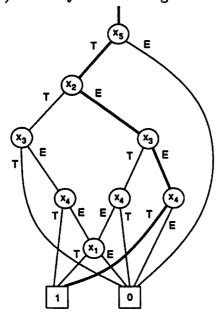

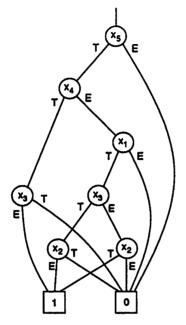

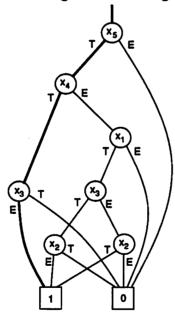

| 2.7 | Binary Decision Diagram and Shortest Path Solution                       | 44  |

| 2.8 | Binary Decision Diagram and Shortest Path Solution using a Different Or- |     |

|     | dering                                                                   | 46  |

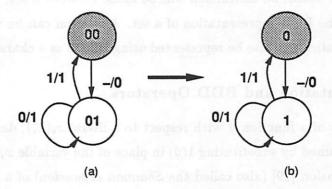

| 2.9 | (a) Example FSM and (b) Minimized FSM with Two Possible Choices for      |     |

|     | One Next State Entry                                                     | 48  |

| 3.1 | The Algorithm cluster_encode for the Minimum Cost Graph Embedding        |     |

|     | Problem                                                                  | 61  |

| 3.2 | The Algorithm anneal_encode for the Minimum Cost Graph Embedding         |     |

|     | Problem                                                                  | 63  |

| 3.3 | The Algorithm new_configuration for Annealing Based Embedding            | 64  |

| 3.4 | The E Post Encoding Optimization Script                                  | 71  |

| 3.5 | The ES Post Encoding Optimization Script                                 | 71  |

| 3.6 | The ESO Post Encoding Optimization Script                                | 72  |

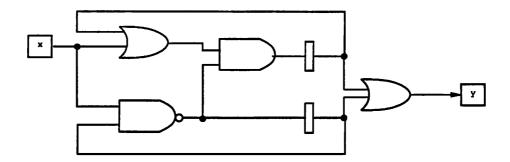

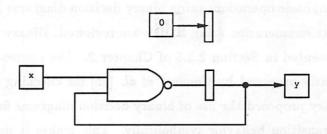

| 4.1 | The Original Circuit                                                     | 81  |

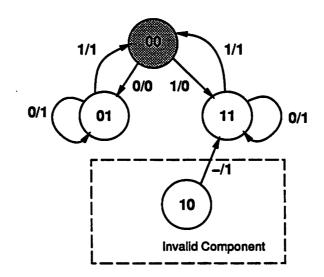

| 4.2 | The State Diagram Corresponding to the Above Example                     | 81  |

| 4.3 | The Simplified Circuit under Invalid and Equivalent States               | 83  |

| 4.4 | The Corresponding State Diagrams.                                        | 83  |

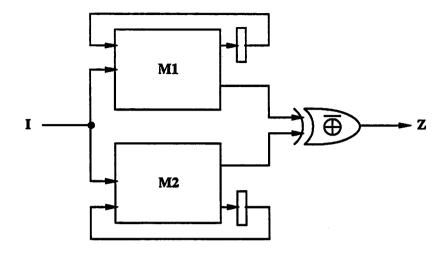

| 4.5 | Product Machine                                                          | 87  |

| 5.1 | A Recursive Algorithm for the Compatible Projection Operator             | 109 |

| 5.2 | Calculating Communication Complexity                                     | 110 |

## List of Tables

| 2.1        | Experimental Results                                                      | 51  |  |  |  |  |  |

|------------|---------------------------------------------------------------------------|-----|--|--|--|--|--|

| 3.1        | Statistics for IWLS'89 FSM Benchmarks                                     | 67  |  |  |  |  |  |

| 3.2        | Experimental Results for IWLS'89 FSM Benchmarks                           | 70  |  |  |  |  |  |

| 3.3        | Comparisons of JEDI and MUSE with Different Post Optimization Procedures. |     |  |  |  |  |  |

| 3.4        | Comparing the Effectiveness of Different Graph Embedding Algorithms       | 75  |  |  |  |  |  |

| 3.5        | CPU Expenditures of cluster_encode vs. anneal_encode                      | 76  |  |  |  |  |  |

| 3.6        | Comparisons with Exact Graph Embedding                                    | 77  |  |  |  |  |  |

| 4.1        | Computation of Invalid States                                             | 96  |  |  |  |  |  |

| 4.2        | Computation of Equivalent States                                          | 97  |  |  |  |  |  |

| 4.3        | Results on Sequential Optimization                                        | 98  |  |  |  |  |  |

| 4.4        | Computation of Single-Cycle Equivalent States                             | 99  |  |  |  |  |  |

| 5.1        | Computing and Representing Equivalent Pairs                               | 113 |  |  |  |  |  |

| <b>5.2</b> | Computing the Communication Complexity                                    | 114 |  |  |  |  |  |

| 5.3        |                                                                           | 115 |  |  |  |  |  |

| 5.4        | State Minimization Results                                                | 115 |  |  |  |  |  |

| 6.1        | Exact Redundant State Register Removal Results                            | 124 |  |  |  |  |  |

| 6.2        | Comparisons of Transition Relation Sizes                                  | 125 |  |  |  |  |  |

| 6.3        | Comparisons of Gate-Level Implementations                                 | 126 |  |  |  |  |  |

| 6.4        | Comparisons of State-Bit Removal with script.rugged                       | 127 |  |  |  |  |  |

| ::                         |                  |                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    | and the state of the                                                |                                                                          | :  |

|----------------------------|------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------|----|

|                            | magari<br>Nga it | e e e e e e e e e e e e e e e e e e e | er zemeler<br>ero-skrieß forgr<br>drugsfadd ugrefa<br>Samunifatea                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | i kadisi senali<br>Sengan sengan<br>Senalis sekal<br>Senalis sekal | ki pa silabih<br>da hua - 11 i i<br>eepusite iii i<br>seriu a eeusi | o portugações<br>escorbistações (1)<br>organistações<br>de organistações |    |

| 80<br>30<br>50<br>80<br>80 |                  | •                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . Lineausid<br>Til a eliganid                                      | t desidenting Person<br>och gjar teden sava                         | Ales <b>ape a d</b> ipa<br>Martina da Ba                                 |    |

| 5 []<br>                   |                  | • • • • •                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | gradus († 1905)<br>1944 – Francis                                  | กละหวางการกลัง<br>ประจัดได้เหตุก็เรื่อ                              | ing population (files).<br>The first of the second                       |    |

| 1812<br>Add<br>181<br>181  |                  |                                       | The family of the second of th | क्षानुही असी कार्य<br>१९५० - १८ असी का                             | Named a state                                                       | on Briga                                                                 | 3. |

## Chapter 1

## Introduction

Very Large Scale Integrated (VLSI) circuits are widely used in modern digital electronic systems. The development of a new system usually requires the design of several custom application-specific integrated circuits (ASIC's). Using current VLSI technology, it is possible to manufacture integrated circuits (IC's) with over a million transistors. This level of integration is still increasing at a rapid rate.

With the availability of commercial ASIC vendors, very complex VLSI designs can be readily implemented in silicon by using such ASIC design-styles as standard cells, gate arrays, or sea-of-gates (also known as channel-less gate arrays) [55]. Despite the ease of fabricating ASIC's today, their design time remains one of the most crucial bottlenecks in the overall product development cycle for most new systems. In a highly competitive global market, with many strong domestic as well as international contenders, time-to-market is a key strategic factor. Therefore, effective computer-aided design (CAD) tools are urgently needed for helping designers to reduce the time required to design new ASIC's. Techniques for automating VLSI design steps can greatly help in this direction. This automation is referred to as synthesis.

### 1.1 A Design Trajectory

The design of a custom ASIC involves a series of design steps. A typical design process begins with a specification of circuit behavior in the form of a hardware description language (HDL). ELLA [71], VHDL [50], ISPS [6], are examples of hardware description languages. In this dissertation, a hardware description where the specified cycle-to-cycle

behavior cannot be changed is referred to as a register-transfer level (RTL) model. This means that final implementation must produce the same output at every clock cycle when the same input sequence is applied, i.e., the cycle-to-cycle behavior must be preserved. A hardware specification where the cycle-to-cycle behavior can be modified is referred to as a behavioral model. Behavioral synthesis transformations like scheduling allocation, and pipelining can be applied to a behavioral model to obtain an optimized register-transfer level model. The topic of behavioral synthesis is beyond the scope of this research. The reader is instead referred to the following literature for detailed expositions on some representative work in behavioral synthesis [84, 30, 22]. At this time, behavioral synthesis is still an active area of research and many open issues remain unresolved.

If the hardware is only specified in terms of Boolean values, i.e., in terms of 0's and 1's, then software compilation-like techniques [1, 83] can be used to map the RTL model into an interconnection of combinational logic blocks and synchronous memory elements directly. Many RTL synthesis systems assume this type of description [83]. However, to model real life situations more naturally, the hardware specification may include symbolic (also referred to as multi-valued) variables, that can assume finite sets of values, in addition to Boolean variables, which can only assume values from the set {0,1}. This form of specification is referred to as a symbolic specification. For example, symbolic specification is widely used in describing finite state machines (FSM's) where the internal states are initially specified symbolically rather than with Boolean vectors. This is, however, a highly restricted form of symbolic specification. In general, the concept can be used for describing complete hardware designs with potentially many symbolic variables. A number of hardware description languages, including VHDL [50] and ELLA[71], provide abstract data typing mechanisms for specifying the variables and functional behavior symbolically. As an example, a partial hardware description written in VHDL for a process control interface module is shown in Figure 1.1. Here, the variables representing process instructions may take on four possible values from the symbol set {ADD, SUB, MUL, CMP}, and the variables representing the control stages may assume the values {WAIT, RESET, FETCH}. This example is shown to illustrate the use of symbolic variables and the description of symbolic functions.

Since symbolic descriptions cannot be implemented in digital logic directly with conventional logic families <sup>1</sup>, a binary representation must be derived. This can be obtained

<sup>&</sup>lt;sup>1</sup>Some multi-valued logic circuit families do exist, but they are not yet practical for commercial use.

```

-- declaration of symbolic data types

package data_type is

type stages is (PAUSE, RESET, FETCH);

type instructions is (ADD, SUB, MUL, CMP);

end data_type;

-- interface specification

use work.data_type.all;

entity process_control is

port (clk, c, flag1, flag2: in bit;

mode: out bit; opcode1, opcode2: out instructions);

end process_control;

-- model specification

architecture behavior of process_control is

component latch port

(clk: in bit; d: in bit; q: out bit);

end component;

signal pfork, pjoin: stages;

process (c, flag1, flag2, pfork)

begin

if (pfork = PAUSE) and (flag1 = '0') then

mode <= '0'; opcode1 <= SUB; opcode2 <= MUL; pjoin <= PAUSE;</pre>

elsif (pfork = FETCH) and (flag1 = '0') then

mode <= '0'; opcode1 <= CMP; opcode2 <= SUB; pjoin <= FETCH;</pre>

end if;

end process;

state: latch port map (clk, pjoin, pfork);

end behavior;

```

Figure 1.1: A Symbolic Specification Fragment written in VHDL.

by encoding the symbolic variables with binary-valued variables. This process is referred to as symbolic encoding. During symbolic encoding, a binary pattern must be determined to represent uniquely each symbolic value in the symbol-set. Each symbolic variable is then replaced by a set of binary-valued variables, known as encoding variables, to represent the binary encoding patterns. For example, in the case of the symbol set representing the process instructions in Figure 1.1, the four admissible values {ADD, SUB, MUL, CMP} might be represented with the binary codes 00, 01, 11, 10, respectively, using two binary-valued encoding variables per symbolic value. Depending on the choice of encoding, the resulting Boolean logic may differ substantially. Therefore, it is crucial to develop effective encoding algorithms that can optimize for the eventual logic implementation under some criteria, e.g., area, performance, or testability.

After symbolic encoding, an interconnection of combinational logic blocks and memory elements is generated. Each combinational logic block is made up of logic gates interconnected in a prescribed way to implement a particular Boolean logic function. The memory elements are used to store data between successive evaluations of the logic blocks. The memory elements are also referred to as latches or registers. This block-level description is referred to as a sequential logic network. The next step in the design process is to optimize the sequential logic network under some criteria. This process is referred to as sequential logic synthesis or sequential logic optimization. This step is extremely crucial in the overall synthesis process since the initially translated description may contain a significant amount of unnecessary (redundant) logic. Again, the optimization criteria may be in terms of area, performance, testability, or some combination. In this research, a restricted class of sequential circuits called synchronous circuits is assumed. These circuits have the property that a common global clock is used to determine when the memory elements latch in new data. A large percentage of circuits designed fall into this category. This is especially the case for semi-custom designs that target gate array or standard cell technologies.

The result of sequential logic synthesis is an optimized gate-level description of the circuit. The next step in the synthesis process is to produce a mask-level description for fabrication. There are many approaches to performing this transformation. One widely used approach is to map the logic gates and memory elements from an optimized gate-level description on to a set of pre-designed library cells. This mapping step is referred to as technology mapping [52, 31, 87]. Since the actual physical layouts for the library cells are available, accurate area and load information for each cell can be obtained easily. The final

TEM Serve

step in the synthesis process is to place and route the mapped library cells. A detailed exposition on various placement and routing techniques can be found in [55]. The placed and routed mask-level description can be used to manufacture the final product.

#### 1.2 Previous Work

#### 1.2.1 Symbolic Encoding Techniques

The encoding problem is perhaps one of the oldest problems in switching and automata theory [46]. In general, a symbolic specification of hardware may have either symbolic input variables, symbolic output variables, or both. Input encoding refers to the version of the problem where only symbolic input variables are considered, and output encoding refers to the version where only symbolic outputs are considered. In the case of state assignment for finite state machine synthesis, the two symbolic variables representing the present-state input and the next-state output are in fact used to represent the same set of symbolic values. Additional constraints must be imposed such that the same encoding is selected for both variables. This instance of the encoding problem is referred to as the input-output encoding or the state assignment problem. For optimization, the target implementation can be either two-level or multi-level logic. Depending on the target implementation, the goal for the encoding step, be it input, output, or input-output encoding, varies. Encoding problems are difficult because they typically have to model a complicated optimization step that follows.

Two-Level Encoding: In the case where the target implementation is two-level logic, many approaches have been proposed. The encoding problem has been studied since the 1960's [38, 46], but these earlier approaches do not have a strong correlation with the logic minimization step that follows. De Micheli et al. [70] introduced a new paradigm where the two-level encoding problem was divided into two stages: an encoding independent optimization phase called symbolic minimization, and a constraint satisfaction step. In the symbolic minimization step, two-level logic minimization techniques [78, 74, 67] were extended to perform minimization with symbolic variables. The minimized symbolic result can then be mapped to a binary implementation by satisfying a set of encoding constraints. This paradigm was originally introduced for the input encoding problem as an approximation to state assignment. It was later generalized to solve the output encoding and input-output

encoding problems [68]. Similar approaches were followed in [92, 95]. These approaches are heuristic in nature. In [35], Devadas et al. presented exact symbolic minimization algorithms that can solve the problems of input, output, and input-output encoding for the two-level case.

In all of these approaches, symbolic functions were assumed. That is, for every possible input condition, either the output is left unspecified or there is exactly one mapping. For example, in the classical state assignment problem, the next-state function is a symbolic function since every primary input and present-state combination is deterministically mapped to a unique next-state. Thus, the techniques described above are applicable, and the problem can be regarded as well-solved. However, in many important applications in synthesis, the need for capturing multiple output choices arises [60, 63, 61]. Symbolic relations (one-to-many mapping) rather than functions must be considered, meaning that the possible output response for a given input condition may be one of several symbolic values rather than just one. For example, when synthesizing a finite state machine, either in isolation or in the context of an interacting network, there may be a number of equivalent states. Equivalent states may be exploited by permitting the next-state to be any one of the equivalent states [60]. Previous encoding methods did not consider the selection of output mapping (viz. symbolic relation). However, the cost of the final implementation depends heavily on this mapping. A careful selection is therefore extremely crucial. Unfortunately, the choice of output mapping interacts in complex ways with the encoding process. Ideally, both problems should be solved simultaneously. The problem of minimizing symbolic relations with both degrees of freedom considered has not be been addressed so far. Also, equivalent states may be assigned the same binary code, provided that appropriate constraints are satisfied. This additional degree of freedom has also not been explored in previous work.

Multi-Level Encoding: The problem of encoding an arbitrary symbolic specification as to minimize the area of the eventual multi-level logic implementation is an extremely difficult problem in general. This is partly due to the inherent difficulties of multi-level logic optimization. Current encoding techniques that target multi-level logic implementation can be classified into two classes: symbolic-minimization-based and estimation-based. In the work of Malik et al. [56], a symbolic minimization procedure was proposed for encoding specifications with symbolic input variables. Analogous to two-level symbolic

minimization, multi-level logic transformations like algebraic decomposition were extended to minimize under symbolic inputs. These multi-level symbolic minimization techniques can be used to solve the input encoding problem. Although the proposed approach has been shown to produce good results for the input encoding problem, the current implementation relies on an expensive simulated annealing based encoding step that uses two-level logic minimization [12] in the the inner loop of the annealing procedure to determine the size of the algebraic factors [65]. Multi-level symbolic minimization for output encoding remains an open problem.

An alternative approach is to estimate the outcome of multi-level logic optimization. Devadas et al. [33] proposed an approach for state assignment based on enhancing the likelihood of finding common subexpressions in the encoded logic prior to logic optimization. In this approach, weights were statically computed between pairs of states based on the observation that encoding states close together in the Boolean space may result in many common subexpressions. Following the weight computation phase, a graph embedding step is solved to encode heuristically state pairs with large weights closer together in the Boolean space. Recently, new encoding procedures based on this encoding paradigm have been presented in [59] and [39]. These new procedures make use of improved estimation models and new graph embedding algorithms that have been shown to produce consistently better results.

In contrast with the symbolic minimization approach, the choice of code assignments in estimation-based approaches are determined by modeling the effects of encoding on the multi-level logic optimization process. The main drawback is the weak correlation that these approaches have with the actual logic transformations that are typically used in multi-level logic synthesis. However, they have been shown to consistently yield good results, and have the merit of being extremely fast.

#### 1.2.2 Sequential Optimization Techniques

Combinational logic optimization has reached significant maturity in the past decade. This is partially reflected by the number of successful combinational logic optimization systems that have been developed in universities as well as the industry [78, 13, 10, 29, 45]. A detailed review of the state-of-the-art in combinational logic optimization techniques can be found in [12, 15]. While combinational logic optimization techniques

ξ

are relatively well-developed, research in sequential optimization is still in its earlier stages. Techniques for sequential optimization can be classified into two categories: those that work on a state transition graph (STG) model of the finite state machine, and those that work directly at the structure of the sequential circuit.

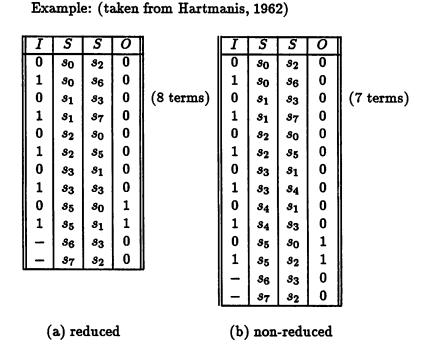

STG-Based Optimization: Sequential optimization techniques that work at the state transition graph level have been studied since the 60's [46, 54]. Traditionally, a state transition graph model is converted to a sequential logic network viz. the process of state assignment. While effective state assignment techniques are available, they do not explore possible state assignments from other equivalent state transition graph structures. Therefore, the solutions achieved using even exact state assignment may be suboptimal. One heuristic is to apply a state minimization procedure [44, 54] to reduce the number of internal states prior to state encoding. The primary objective of classical state minimization is to minimize the number of states. It is well known, however, that non-reduced state machines may actually lead to superior logic implementations [47]. Techniques for relating state minimization and state assignment have not been developed to date.

Algorithms for decomposing a finite state machine into a set of interacting FSM's have been proposed. Earlier work on FSM decomposition was based on a theory of partition [46, 54]. Researchers have recently developed more sophisticated methods that attempt to relate FSM decomposition with state assignment and two-level logic minimization [36, 5]. Methods for synthesizing interacting FSM's have also been actively pursued [32, 4].

Structural-Based Optimization: Transformations that attempt to optimize the sequential logic at the circuit-level have been proposed. Leiserson and Saxe [57] developed a transformation called retiming for improving the performance of a synchronous digital system by re-positioning the registers. This technique was further developed in [69] in the context of sequential logic optimization. In [66], retiming was used to temporarily reposition the registers such that combinational logic optimization can be applied to a larger portion of the network. Although these retiming-based techniques have been found to be useful for clock cycle minimization, they have had only limited success for area optimization.

Another important source of sequential optimization is the use of don't-care information. Don't-care conditions represent the degrees of freedom that the circuit can be modified without affecting its intended behavior. In [7, 15], various don't-care sets for

combinational logic circuits have been identified. Recently, efficient procedures have been developed for computing them [81]. For hierarchically-defined logic networks, Brayton and Somenzi [16] proposed the use of Boolean relations to capture the possible degrees of freedom. This is related to the work of Cerny and Marin [23] of observability relations for hierarchical combinational network specification and synthesis.

Combinational don't-care conditions are not sufficient when sequential machines are considered. For finite state machines, Devadas et al. [34] described a don't-care based optimization procedure for two-level logic implementations that can produce a fully-testable sequential machine, under the single-stuck-at fault model in testing [18], without access to the memory elements. In their work, invalid and equivalent state information was extracted from a state transition graph representation of the FSM. This information was then used by a two-level Boolean minimizer [12, 14] as don't-care conditions to obtain an optimized implementation. This procedure was limited to those sequential circuits whose state-space can be enumerated explicitly. Multi-level logic optimization was not considered.

In [28], the notion of synchronous don't-cares was proposed to capture sequential don't-care conditions at the circuit-level. New synchronous don't-care sets were proposed along with computation algorithms. Sequential don't-care sets that correspond to an acyclic portion of the sequential circuit can be captured using their techniques. Larger sets of don't-cares may be derived by considering different acyclic portions of the feedback network. It is not currently known if all degrees of freedom can be captured this way.

#### 1.2.3 Symbolic Representations and Computation

Recently, it has become apparent that many tasks in logic synthesis are intimately related in that they are often fundamentally dependent on the same set of basic logic manipulations. Therefore, it is important to improve existing and develop new logic manipulation methods. The binary decision diagram (BDD) [20, 11, 2] is an efficient data structure for representing logic. Bryant proposed a restricted version of BDD that requires an ordering on the variables. It was shown that the resulting reduced decision graph is canonical with respect to a given variable ordering. It also has the important advantage that Boolean operations (e.g., Boolean and and Boolean or) can be performed directly on the data structure. Another important idea is the concept of characteristic functions proposed by Cerny and Marin [23]. Their original idea was to capture the input-output behavior of a combina-

tional circuit as a single Boolean function. This form of specification can naturally express multiple output mappings, as in Boolean relations. The concept of characteristic function can be applied in general to represent and manipulate finite sets of elements. Recently, Coudert et al. developed the concept of implicit enumeration for efficiently traversing large state-spaces [26, 27]. This method is based on the use of BDD's and characteristic functions for implicitly representing the state space. While BDD's, characteristic functions, and implicit enumeration provide the basic machinery and concepts to manipulate logic functions, sets, and state-spaces efficiently, efficient representations and manipulation algorithms have not been developed for handling equivalence classes. The ability to represent and manipulate equivalence classes efficiently is important in a number of problems in sequential logic synthesis, e.g., manipulation of equivalent states in finite state machines.

#### 1.3 Overview of Dissertation

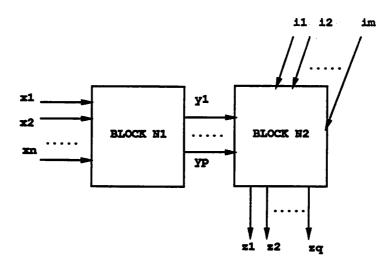

The goal of this research has been to develop new synthesis techniques for automating the design process for transforming a symbolic specification of hardware into an optimized VLSI circuit. The designs considered are synchronous sequential circuits that are composed of combinational logic blocks and synchronously-clocked memory elements. The first part of the dissertation is focussed on the optimization problem of encoding a symbolic specification into a binary representation. This is necessary since conventional digital circuits can only implement Boolean logic.

In Chapter 2, the encoding problem for two-level logic implementations is considered. Although this problem has been well-investigated in the past, techniques developed thus far have not considered the interactions between the encoding process and sequential optimization. In the case of finite state machine (FSM) synthesis, optimizations at the FSM-level can be implicitly captured in the encoding process if multiple output choices are considered. This gives rise to the symbolic relations problem where each input condition may be mapped to one of many output choices. The optimization problem requires both the selection of output mappings and code assignments. A unified framework is presented for finding exact solutions, in terms of area, to the symbolic relation minimization problem. The formulation is based on prime generation and minimum-cost covering. Various versions of the minimization problem can be uniformly treated by incorporating problem-specific constraints to the covering problem. The problem of FSM synthesis using a symbolic

relations formulation is also described. Extensions to symbolic relations are presented to consider implicitly the merging of equivalent states in the synthesis process. Based on these extensions, the traditionally separate problems of state minimization and state assignment are formulated as a single unified optimization problem.

In Chapter 3, new algorithms are described for solving the encoding problem for multi-level logic implementations. For encoding large symbolic specifications, such as those translated from hardware description languages (e.g., VHDL [50] or ELLA [71]), fast, but effective, algorithms are required. The techniques in this chapter build on the work of Devadas et al. [33]. The new techniques presented include modified estimation models for general symbolic specifications rather than state machines, and new optimization algorithms for solving the graph embedding problem.

The second part of this dissertation is concerned with the problem of optimizing an already encoded circuit description. Specifically, the optimization of synchronous sequential circuits is considered. In Chapter 4, an approach based on combining global state-space information with logic-level transformations is presented. In particular, efficient algorithms are presented for computing invalid and equivalent state information from a structural-level description. The extracted information can then be used as sequential don't-care conditions in logic optimization. These don't-care conditions provide more degrees of freedom for combinational logic optimization algorithms to optimize the circuit, both for area and performance improvement. Although synthesis for testability is not directly addressed in this research, it has been shown that the use of these sequential don't-cares in optimization can greatly enhance the testability of the resulting circuit, if not making it fully testable [34]. The main bottleneck in previous methods for extracting similar don't-care information has been the size of the problems that they can handled. Many circuits considered in practice typically contain a large number of latches. Hence, the size of the corresponding state-spaces are usually quite vast, rendering existing methods, based on state diagrams or cube enumeration, impractical. New algorithms based on binary decision diagrams (BDD's [20]) are presented in Chapter 4 that can greatly extend current capabilities in computing these don't-care conditions for large circuits. These algorithms build on the implicit state enumeration techniques recently introduced by Coudert et al. [25].

The work presented in Chapter 5 is concerned with efficient techniques for representing and manipulating equivalence classes. The main motivation for investigating this problem in this research is in the application of sequential optimization. Specifically, equiv-

alent states information can also be used in synthesis to reduce the size of the state-space by merging them together, *i.e.*, state minimization. To perform this transformation for large sequential circuits, efficient techniques for representing and manipulating equivalent classes are required. These problems are addressed in Chapter 5 by introducing a new representation for equivalence classes and a new Boolean operator for manipulating them that can be applied to very large problem instances.

The work presented in Chapter 6 is concerned with optimizing sequential circuits by means of removing redundant state latches. Unoptimized sequential circuits may contain latches and next-state functions that can be re-derived from information contained in the other latches in the circuits. These latches and next-state functions can be deleted from the circuit if appropriate re-encoding logic is added. A simple algorithm is presented for performing this transformation that has been shown to heuristically reduce the size of the circuits for verification purposes and physical implementations.

Finally, in Chapter 7, conclusions from this work are summarized.

## Chapter 2

# Symbolic Relations and Two-Level Encoding

#### 2.1 Introduction

Many problems in synthesis can be posed as encoding problems and so effective encoding methods are fundamental to high-quality results from synthesis. As mentioned already in Chapter 1, different encoding techniques must be developed depending on whether the eventual logic implementation is two-level or multi-level. This is, in part, because state-of-the-art logic optimization techniques for both styles of implementations are different, and the cost functions for physical realizations are different. In this chapter, techniques targeting two-level implementations are considered.

For two-level encoding, the eventual physical realization is in most cases a programmable logic array (PLA). Since a PLA is typically implemented as a two-dimensional transistor array, the area complexity is roughly proportional to the number of rows times the number of columns. The number of rows corresponds to the number of product terms (i.e., implicants), and the number of columns is determined by the code lengths used to encode the symbolic variables, as well as the number of primary inputs and outputs of the finite state machine in the most general case. Hence, a widely accepted first-order measure of area complexity of a PLA is simply the number of product terms (which is a first-order approximation). Therefore, the goal of two-level encoding has been to produce a realizable binary implementation with as few product terms as possible. Based on this cost measure,

a significant amount of work has been published since the 1960's, as reviewed briefly in Chapter 1. The most successful approaches for two-level encoding to date have been based on the paradigm of symbolic minimization. Symbolic minimization is the process of minimizing directly the logic specification with symbolic variables such that the minimized result can be translated into a binary representation by satisfying some prescribed encoding constraints. Such an approach was used in [70] to minimize functions with only symbolic inputs. The basic approach was later generalized to minimize functions with both symbolic inputs and outputs [68, 92] (e.g., the state assignment problem). Recently, Devadas et al. [35] proposed an exact symbolic minimization procedure for minimizing symbolic functions with both symbolic input and output variables.

In all of the previous work on symbolic encoding, symbolic functions were assumed. That is, for every possible input condition, either the output is left entirely unspecified or there is exactly one mapping. However, in many interesting applications, relations rather than functions have to be considered, meaning that several output choices of symbolic values may be possible for each input condition rather than just one.

Symbolic relations arise in many contexts in synthesis [60, 63, 61]. Many optimization problems can in fact be naturally formulated as a symbolic relation minimization problem. For example, when synthesizing a finite state machine, there may be a number of equivalent states in the original specification. Equivalent states may be exploited by permitting the next-state to be any one of the equivalent states. Let the behavior of a completely specified finite state machine be given by the function  $T: I \times \Sigma \to \Sigma \times \mathcal{O}$ . In the classical state machine synthesis problem, T is treated as a symbolic function with  $I \times \Sigma$  as the domain (i.e., the machine inputs and present-states) and  $\Sigma \times \mathcal{O}$  as the co-domain (i.e., the next-states and machine outputs). For every combination of input and present-state, exactly one next-state and one output pattern is produced. However, if a set of equivalent states  $E \subseteq \Sigma \times \Sigma$  is known, where  $(y, y') \in E$  means the state y and the state y' are equivalent, then the behavior of the finite state machine, under the degrees of freedom of equivalent states, can in fact be formulated as a symbolic relation  $T'\subseteq I imes \Sigma imes \Sigma imes \mathcal{O}$  as follows: for every  $(i,x) \in I \times \Sigma$ , (y,o) is a possible output mapping for T' if and only if either (y,o) was the mapping for the original function T(i,x), or there exists a state y' such that y and y' are equivalent states and (y', o) was the original mapping for T(i, x).

In this way, it may be possible to implement a more efficient machine using the equivalent states. In essence, T' is a symbolic relation that captures a complete family of

2.1. INTRODUCTION 15

equivalent FSM's that can be obtained by re-directing state transitions to equivalent states in a state transition graph. The idea of using equivalent states to formulate a symbolic relation was first introduced in [58, 60]. Another FSM synthesis problem is the state minimization of incompletely specified finite state machines. In this problem, a set of prime classes are selected to represent the minimized machine. However, a state in the original machine may be covered by a number of prime classes. There is an optimization problem that must be solved in choosing which prime class implements a next-state. This is referred to as the mapping problem [75] and can be naturally formulated as a symbolic relation minimization problem.

Other problems that can be formulated with symbolic relations include any applications for Boolean relations with the added degree of re-encoding the binary outputs. For example, consider the problem of minimizing a pair of cascaded PLA's. The signals passing from the first PLA to the second may be re-encoded to simplify the two combinational blocks. A symbolic relation may arise if some output vectors of the first PLA are not differentiable by the second PLA. This is the same phenomenon that gave rise to Boolean relations. However, these intermediate signals can be re-encoded. Straightforward re-encoding without considering relations does not exploit all degrees of freedom.

The goal of two-level symbolic relation minimization is to find the minimum (or a minimal) two-level binary implementation to realize the symbolic relation. The problem of minimizing symbolic relations is fundamentally more difficult than the problem of minimizing symbolic functions. In addition to the degrees of freedom of choosing different encodings for the symbolic variables (both symbolic inputs and outputs), the choice of output mapping for each input condition must also be decided. The choice of output mapping can, and often do, affect tremendously the optimality of the final result. In fact, the choice of output mapping and the choice of encoding have complex interactions with each other. Hence, it is important that they be considered together during the optimization process.

In this chapter, a unified framework is presented for solving various two-level symbolic relation minimization problems exactly. The overall framework is based on the classical paradigm of prime implicant generation and covering, but generalized to minimize symbolic relations. The notion of generalized prime implicants (GPI's) proposed by Devadas et al. [35] for symbolic function minimization is extended to the concept of generalized candidate primes (or simply generalized c-primes). This is similar to the notion of candidate primes in the Boolean relation problem [14]. After the generalized c-primes have

been generated, a covering problem must be solved whereby a subset of the generalized cprimes is selected to implement the symbolic relation. In [35], the problem was formulated as a minimum unate covering problem with encodeability check. The branch-and-bound strategies are similar to those used in classical two-level minimization [78], but encodeability must be checked before a solution is declared valid. The encodeability check was performed using a separate graph resolution algorithm.

Here, a binate covering formulation of the problem is proposed whereby the covering step, the encodeability check, and the all-zero code problem<sup>1</sup> are solved simultaneously. A succinct set of covering constraint equations is given that considers the complete covering process. When formulated as a binate covering problem (BCP), a number of developed bounding strategies (e.g., implications) can be exploited to prune the search space. Also, the formulation into one unified framework permits a deeper understanding of the underlying problem. Most importantly, a variety of symbolic relation minimization problems can be solved uniformly by modifying the covering constraints without the need to change the core mechanisms for solving the binate covering problem.

The framework for symbolic relation minimization is further generalized for solving the FSM synthesis problem. As already mentioned, knowledge of equivalent states can be exploited in FSM synthesis by permitting the next-state transition to be any one of the equivalent states. Formulating the symbolic relation problem this way accounts for all the degrees of freedom of state encoding and re-direction of state transitions in a state transition graph. However, this is not the most general case since equivalent states can be merged to reduce the number of states. Merging of equivalent states can be considered implicitly in the minimization process by permitting them to assume an identical code<sup>2</sup>. This is in contrast with the classical statement of the encoding problem where the assignment of distinct codes to each symbolic value is required. Relaxing this requirement adds yet another dimension in the optimization space, but doing so captures implicitly the state minimization process as one of state encoding. The key difference is the use of actual logic area as the cost function rather than the number of states. However, new constraints must be imposed such that resulting solution is realizable. In particular, the implicit merging of some equivalent states may necessitate the merging of other equivalent states (cf. Section

<sup>&</sup>lt;sup>1</sup>In a PLA implementation, if the outputs of a product term are all 0's, then the product term can be discarded. This condition must be accounted for during the minimization process.

<sup>&</sup>lt;sup>2</sup>The idea of assigning identical codes to equivalent states as a means for considering state merging implicitly was first proposed in [58, 60].

2.3.2 and Section 2.6.3). These additional constraints can be treated uniformly using the unified framework described in this chapter.

The remainder of the chapter is organized as follows. In the next section, definitions and notation used throughout the chapter are given. In Section 2.3, different symbolic relation minimization problems are classified along with a global view of the unified framework, namely prime generation, constraints generation, and minimum covering. The problem of generating generalized candidate primes is examined in Section 2.5. Then in Section 2.6, succinct sets of covering constraints are given for various symbolic relation minimization problems. Specifically, in Section 2.6.3, the complete set of constraints for capturing the degrees of freedom of state encoding, re-direction of state transitions, and implicit merging is succinctly stated. This set of constraints essentially captures a complete family of equivalent FSM's under state minimization and state assignment. In Section 2.7, the binate covering problem, which is also known as the minimum-cost satisfiability problem, is addressed. Specifically, a novel approach based on the use of binary decision diagrams (BDD's) is presented that can handle constraints specified in multi-level form directly. It is shown that the minimum cost solution can be found in linear time if the corresponding BDD can be built. Experimental results for the algorithms described in this chapter are given in Section 2.8. A complete example is worked out to illustrate the overall minimization process.

### 2.2 Background and Terminology

#### 2.2.1 Boolean Functions and Relations

Let  $B = \{0,1\}$  be the set of Boolean<sup>3</sup> values. A Boolean variable, or binary variable, is a variable that can accept values from the set B. A Boolean function f (also called a binary function) with r binary input variables and n binary output variables is a mapping function from an r-dimensional Boolean space to a n-dimensional Boolean space, denoted as

$$f:B^r\to B^n$$

.

$B^r$  is called the **domain** and  $B^n$  is called the **co-domain** of the function f. Each element in the domain of the function is called a **minterm** of the function. Given a subset of the domain

<sup>&</sup>lt;sup>3</sup>Throughout the dissertation, the term "Boolean" will be used to refer to the two-valued set {0, 1}.

$X \subseteq B^r$ , the image of X with respect to f is the set  $f(X) = \{y \in B^n \mid \exists x \in X : y = f(x)\}$  that the minterms in X can map to. The range of a function is the image of the entire domain. A single-output function is a special case where m = 1. A multi-output function  $f: B^r \to B^n$  is in fact a collection of single output functions  $[f_1, f_2, \ldots, f_n]$ .

A Boolean function  $f: B^r \to B^n$  is said to be incompletely specified if there exists some minterms in the domain,  $X^{DC} \subseteq B^r$ , where an output  $f_i$  of f is not specified (i.e., the output can take on either value in  $B = \{0,1\}$ ). This set of minterms  $X^{DC}$  is called a don't-care set of  $f_i$ . A more general form of incomplete specification is a Boolean relation defined as follows:

Definition 2.1 A Boolean relation is a one-to-many multi-output Boolean mapping  $\mathcal{R} \subseteq B^r \times B^n$ . For each minterm  $\mathbf{x} \in B^r$ ,  $\mathcal{R}(\mathbf{x}) = \{y \in B^n \mid (\mathbf{x}, y) \in \mathcal{R}\}$  is the set of possible mappings for  $\mathbf{x}$ , also called the image of  $\mathbf{x}$ .

The image for a set of points in the domain is similarly defined. Given a subset of the domain  $X \subseteq B^r$ , the image of X with respect to  $\mathcal{R}$  is the set  $\mathcal{R}(X) = \{y \in B^n \mid \exists x \in X : (x,y) \in \mathcal{R}\}$ . A Boolean relation, in essence, captures a set of completely specified functions over the domain  $B^r$  and the co-domain  $B^n$ . In the following definitions, the relationship between a Boolean function and a Boolean relation is established.

**Definition 2.2** A Boolean relation  $\mathcal{R} \subseteq B^r \times B^n$  is said to be well-defined if  $\forall \mathbf{x} \in B^r$ ,  $\mathcal{R}(\mathbf{x})$  is not empty.

Definition 2.3 A multi-output Boolean function f is a mapping compatible with  $\mathcal{R}$  if  $\forall \mathbf{x} \in B^r$ ,  $f(\mathbf{x}) \in \mathcal{R}(\mathbf{x})$ . This is denoted by  $f \prec \mathcal{R}$ .

#### 2.2.2 Symbolic Functions

Definition 2.4 Let  $D_1 = \{d_0, d_1, \ldots, d_{|D_1|-1}\}$ ,  $D_2 = \{d_0, d_1, \ldots, d_{|D_2|-1}\}$ , ..., and  $D_r = \{d_0, d_1, \ldots, d_{|D_r|-1}\}$ , and  $\Sigma_1 = \{\sigma_0, \sigma_1, \ldots, \sigma_{|\Sigma_1|-1}\}$ ,  $\Sigma_2 = \{\sigma_0, \sigma_1, \ldots, \sigma_{|\Sigma_2|-1}\}$ , ..., and  $\Sigma_n = \{\sigma_0, \sigma_1, \ldots, \sigma_{|\Sigma_n|-1}\}$  be finite sets of elements. Each  $D_i$  and  $\Sigma_i$  represents a finite set of symbolic values. A symbolic function with r input variables and n output variables is a mapping

$$f: D_1 \times D_2 \times \cdots \times D_r \to \Sigma_1 \times \Sigma_2 \times \cdots \times \Sigma_n$$