## Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A REAL TIME LARGE VOCABULARY SPEECH RECOGNITION SYSTEM

by

Anton Manfred Stölzle

Memorandum No. UCB/ERL M91/109

6 December 1991

To my family,

Christine, Alexander, Sebastian, and Michaela Stölzle

and to my parents,

Helene and Franz Stölzle

# A REAL TIME LARGE VOCABULARY SPEECH RECOGNITION SYSTEM

by

Anton Manfred Stölzle

Memorandum No. UCB/ERL M91/109

6 December 1991

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720 S. C.

To my family,

Christine, Alexander, Sebastian, and Michaela Stölzle

and to my parents,

Helene and Franz Stölzle

## A Real Time Large Vocabulary Speech Recognition System

by

Ph.D.

**Anton Manfred Stölzle**

**Department of EECS**

#### **Abstract**

This thesis describes hardware for connected speech recognition based on Hidden Markov Models. It can perform real time speech recognition for vocabularies of up to 60,000 words using the Viterbi dynamic programming algorithm. It is not customized to a particular HMM topology, thus supporting multiple recognition systems. To minimize hardware implementation, the recognition algorithm was modified to a pruned frame synchronous beam search, a fixed point number representation using the logarithm of the probability parameters, and a hierarchical HMM representation which allows the Viterbi algorithm to be processed in parallel on two hierarchy levels, the phone level and the grammar level. The specific properties of HMMs on the two hierarchy levels (left-to-right vs. ergodic) motivated different implementations of the Viterbi algorithm (predecessor processing and successor processing). The system configuration is based on the VME bus, and uses 3 custom triple-height boards that include a combination of general purpose hardware and full custom VLSI hardware (2 sets of 6 custom VLSI processors).

**Chairman of Committee**

To my family,

Christine, Alexander, Sebastian, and Michaela Stölzle

and to my parents,

Helene and Franz Stölzle

## **Table of Contents**

| Introd | luction                                                            | 1  |

|--------|--------------------------------------------------------------------|----|

| 1.1.   | Advantages of Speech Recognition                                   | 1  |

| 1.2.   | Algorithms in Speech Recognition                                   | 2  |

|        | 1. 2. 1. Template Based Speech Recognition [Wai90a]                | 3  |

|        | 1. 2. 2. Knowledge Based Speech Recognition [Wai90b]               | 3  |

|        | 1. 2. 3. Stochastic Speech Recognition Systems [Wai90d]            |    |

|        | 1. 2. 4. Connectionist Speech Recognition Systems [Wai90c]         |    |

| 1.3.   | Language Processing                                                | 6  |

| 1.4.   | Performance and Limitations of Speech Recognition                  | 7  |

| 1.5.   | VLSI for Real Time Speech Recognition                              | 8  |

|        | 1. 5. 1. General vs. Special Purpose Implementation                |    |

| Algor  | ithm                                                               | 13 |

| 2.1.   | Front End Processing                                               |    |

|        | _                                                                  |    |

| 2.2.   | Hidden Markov Model                                                | 19 |

| 2.3.   | Recognition                                                        | 21 |

|        | 2. 3. 1. State probabilities, Viterbi algorithm                    |    |

|        | 2. 3. 2. Backtracking                                              |    |

|        | 2. 3. 3. Multiple output probabilities                             | 25 |

| Previ  | ous Work                                                           | 26 |

| 3.1.   | Hardware Based on General Purpose Processors                       | 27 |

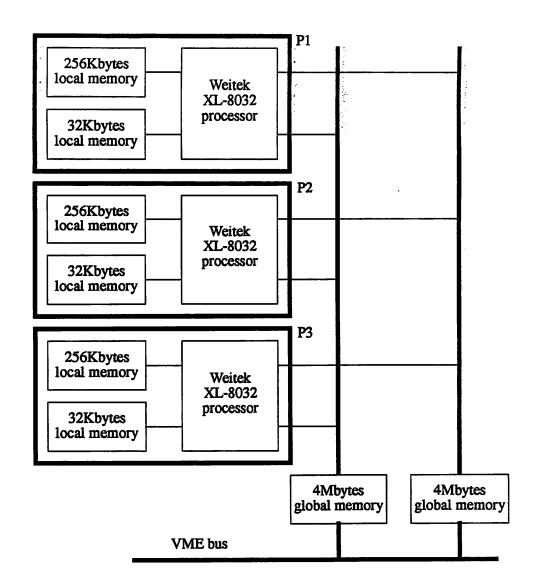

|        | 3. 1. 1. The BEAM Hardware Accelerator                             |    |

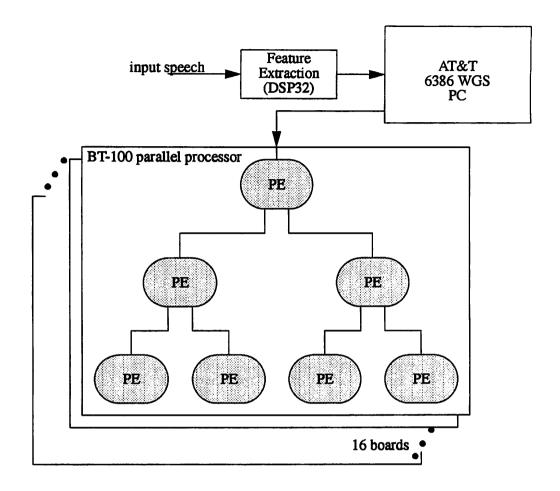

|        | 3. 1. 2. The AT&T BT-100 ASPEN Parallel Computer                   | 29 |

|        | 3. 1. 3. The MARS Multiprocessor Pipeline                          |    |

|        | 3. 1. 4. The Dragon Real Time Continuous Speech Recognition System | 31 |

| 3.2.   | General Purpose Speech Recognition Hardware.                       |    |

|        | 3. 2. 1. The AT&T Graph Search Machine                             | 33 |

| 3.3.   | Comparison to other Dynamic Programming Applications               | 35 |

|        | 3. 3. 1. Viterbi in Communication Systems                          | 35 |

|        | 3. 3. 2. Dynamic Time Warp Algorithm                               | 36 |

| 2.4    | 3. 3. 2. a The LIMSI-CNRS Dynamic Programming (DP) Processor       |    |

| 3.4.   | Advantages of a System with Full Custom VLSI Processors            | 44 |

| Algor  | ithmic Modifications for Hardware Implementation                   | 46 |

| 4.1.   | "Brute Force" Requirements for a 60,000 Word System                | 46 |

| 4.2.   | Changes that Affect the Performance of the Algorithm               |    |

|        | 4. 2. 1. Number Representation, Normalization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                         |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

|        | 4. 2. 2. Pruning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| 4.3.   | Changes that do not Affect the Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 51                         |

|        | 4. 3. 1. Hierarchical HMM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|        | 4. 3. 2. Grammar Processing and Phone Processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |

|        | 4. 3. 3. Predecessors Processing vs. Successor Processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                            |

|        | 4. 3. 3. a Predecessor Implementation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

|        | 4. 3. 3. b Successor Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 60                         |

|        | 4. 3. 3. c Trade Offs between Successor and Predecessor Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                            |

|        | 4. 3. 4. Backtrack Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            |

| G4     | A 11.94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | (5                         |

| Syster | n Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            |

| 5.1.   | Functional Partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 67                         |

|        | 5. 1. 1. Phone Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 68                         |

|        | 5. 1. 2. Grammar Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

|        | 5. 1. 3. Backtracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

| 5.2.   | Hardware Partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                            |

| J.4.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

|        | 5. 2. 1. Front End Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            |

|        | 5. 2. 2. Phone Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                            |

|        | 5. 2. 3. Grammar Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |

|        | 5. 2. 4. Backtracking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                            |

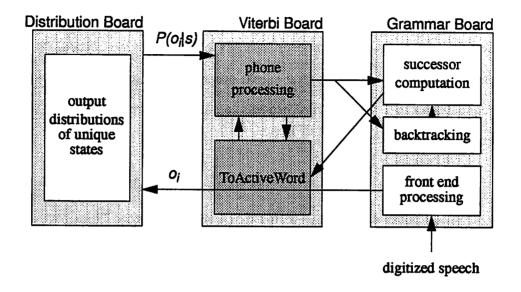

|        | 5. 2. 5. Final Hardware Partition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78                         |

| The V  | <sup>7</sup> iterbi Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 92                         |

|        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |

| 6.1.   | Uhona Urocassing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| 0.1.   | Phone Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83                         |

| 0.1.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 83                         |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83<br>85                   |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83<br>85<br>87             |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83<br>85<br>87<br>87       |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83<br>85<br>87<br>87<br>87 |

| 0.1.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83<br>85<br>87<br>87<br>87 |

| 6.2.   | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83858787878788             |

|        | 6. 1. 1. Data Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 83858787878890             |

|        | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process                                                                                                                                                                                                                                                                                             | 83858787889092             |

|        | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process                                                                                                                                                                                                                         | 8385878788909293           |

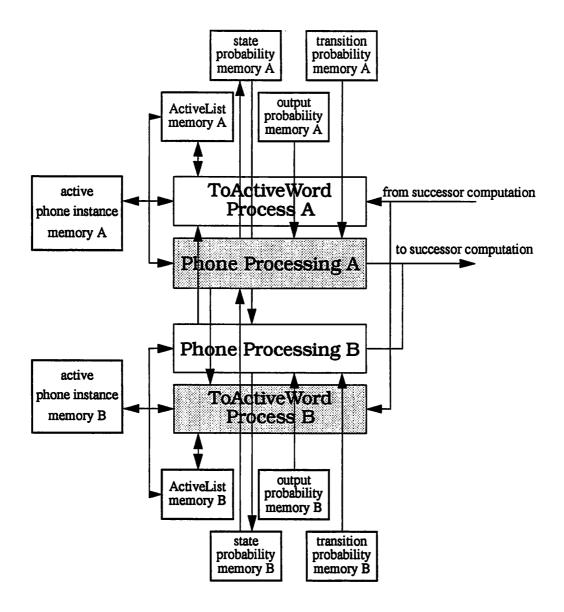

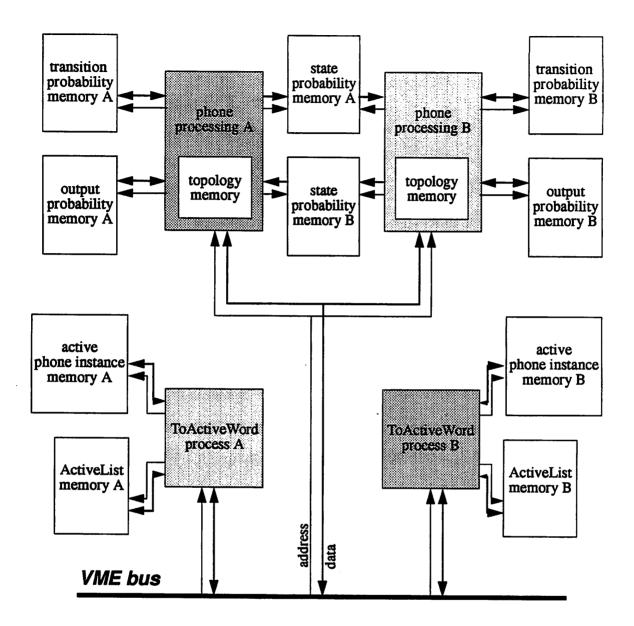

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture                                                                                                                                                                                                     | 838587878890929395         |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. d Output Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture                                                                                                                                                          |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories                                                                                                                           |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories 6. 3. 3. The VLSI Phone Processing System                                                                                 |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. d Output Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories 6. 3. 3. The VLSI Phone Processing System 6. 3. 3. a Processor Partition                                                  |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories 6. 3. 3. The VLSI Phone Processing System                                                                                 |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. d Output Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories 6. 3. 3. The VLSI Phone Processing System 6. 3. 3. a Processor Partition 6. 3. 3. b Chip Architecture 6. 3. 3. c Control |                            |

| 6.2.   | 6. 1. 1. Data Access 6. 1. 2. Parallel Processing of Active States 6. 1. 3. Serial Processing of Active States 6. 1. 3. a Transition Probabilities A(p,s) 6. 1. 3. b Topology Memory 6. 1. 3. c State Probability Memories 6. 1. 3. dOutput Probability Memory  ToActiveWord Process 6. 2. 1. Active Phone Instance Memory 6. 2. 2. ToActiveWord Process  Board Architecture 6. 3. 1. Switching Processor Architecture 6. 3. 2. VME Access to Memories 6. 3. 3. The VLSI Phone Processing System 6. 3. 3. a Processor Partition 6. 3. 3. b Chip Architecture                     |                            |

|        | 6. 3. 4. c Control Structure                                                   | 125 |

|--------|--------------------------------------------------------------------------------|-----|

| The D  | vistribution Board                                                             | 130 |

| 7.1.   | Board Operation                                                                | 130 |

| 7.2.   | Architecture                                                                   | 133 |

|        | 7. 2. 1. Memory Organization                                                   |     |

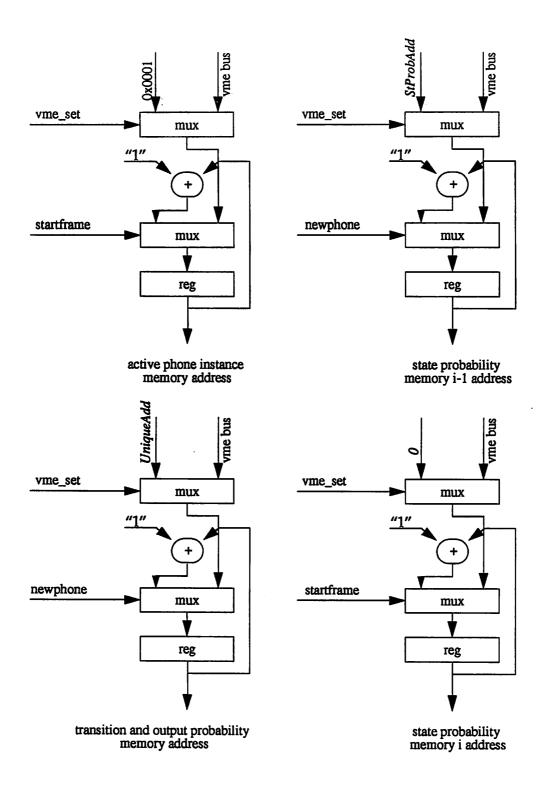

|        | 7. 2. 2. Address Generation                                                    | 134 |

| The D  | SP Board                                                                       | 139 |

| 8.1.   | The Board Architecture                                                         | 139 |

|        | 8. 1. 1. Parallel Processing of Successors                                     |     |

|        | 8. 1. 2. Bitsliced Successor Processing                                        | 143 |

| 8.2.   | Full Custom Interface                                                          | 145 |

|        | 8. 2. 1. Input Interface                                                       |     |

|        | 8. 2. 2. Output Interface                                                      |     |

|        | 8. 2. 3. Interface Implementation                                              |     |

| 8.3.   | Processor Synchronization                                                      | 150 |

| 8.4.   | Multi Board Operation                                                          | 152 |

| Syster | n Software and Recognition Results                                             | 156 |

| 9.1.   | System Startup                                                                 | 156 |

|        | 9. 1. 1. Format of the HMM Parameter File                                      | 156 |

|        | 9. 1. 2. HMM Representation in the Memories of the Speech Recognition Hardware |     |

|        | 9. 1. 3. Representation of the Digit Recognition Model                         | 160 |

| 9.2.   | System Control During Recognition                                              | 161 |

| 9.3.   | Recognition Results                                                            | 163 |

| Concl  | usions                                                                         | 164 |

| Annei  | ndiv                                                                           | 150 |

## **List of Figures**

| Figure 1  | Recognition Accuracies for the Resource Management Task [Way91]     |     |  |

|-----------|---------------------------------------------------------------------|-----|--|

| Figure 2  | Block Diagram of the Front End Algorithm                            | 15  |  |

| Figure 3  | Mel Bandpass Filters                                                |     |  |

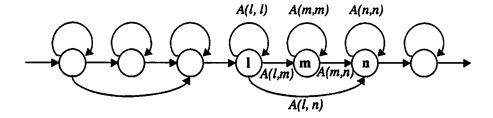

| Figure 4  | Graph of a HMM                                                      | 20  |  |

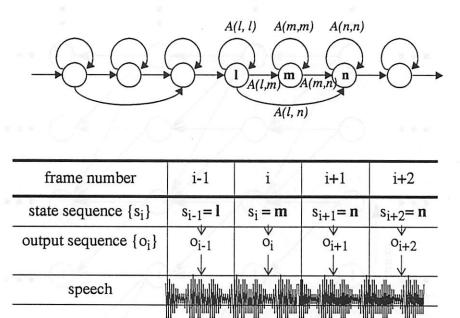

| Figure 5  | Hidden Markov Model for Speech Production                           | 21  |  |

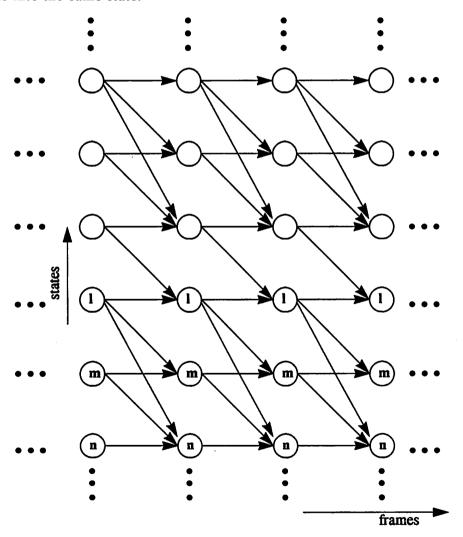

| Figure 6  | Trellis Structure for the Model in Figure 4                         | 22  |  |

| Figure 7  | The Architecture of BEAM                                            |     |  |

| Figure 8  | Architecture of the AT&T ASPEN Processor                            | 30  |  |

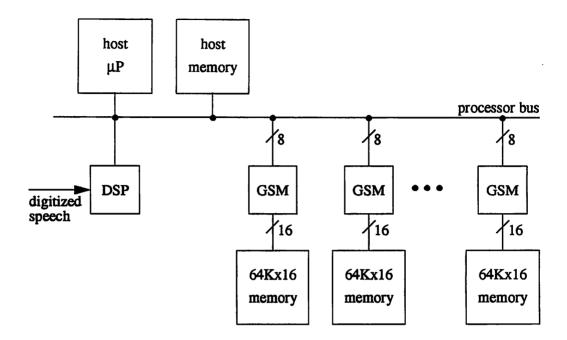

| Figure 9  | System Architecture for the GSM                                     | 34  |  |

| Figure 10 | Alignment of Two Utterances of /six/                                | 37  |  |

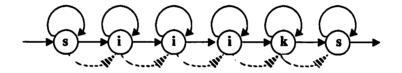

| Figure 11 | State Transition Model of the Template Word /siiiks/                | 39  |  |

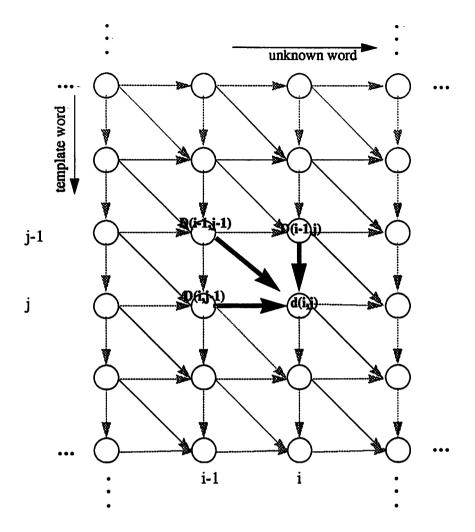

| Figure 12 | Trellis Structure for the Dynamic Time Warp Algorithm               | 40  |  |

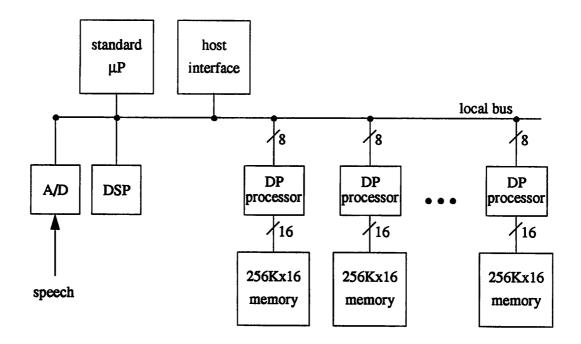

| Figure 13 | System Architecture for the Dynamic Programming Processor           |     |  |

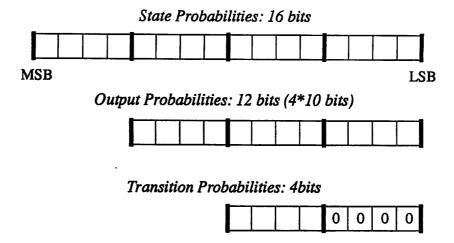

| Figure 14 | Wordlength Representations for Probabilities                        | 50  |  |

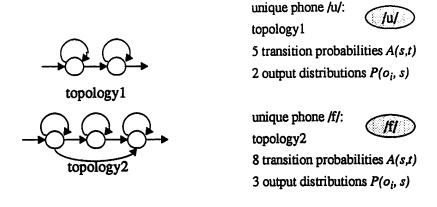

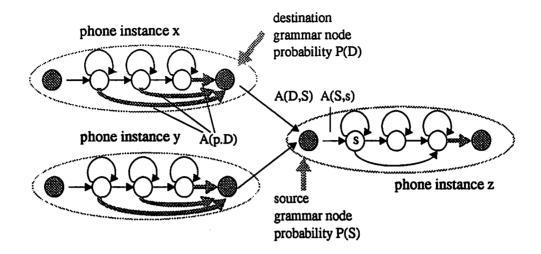

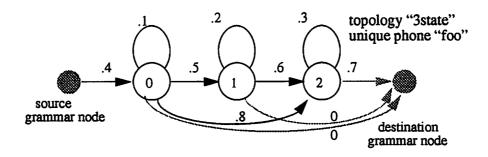

| Figure 15 | hierarchical HMM                                                    | 53  |  |

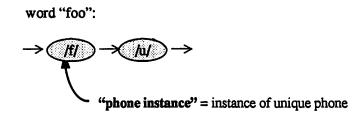

| Figure 16 | Concatenation of Unique Phones in Grammar Processing                | 55  |  |

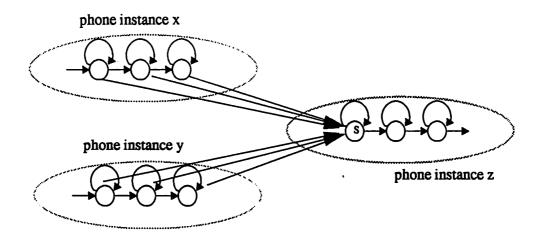

| Figure 17 | Concatenation of Unique Phones (inside dashed ellipses) using Gramm | nar |  |

|           | Nodes                                                               | 57  |  |

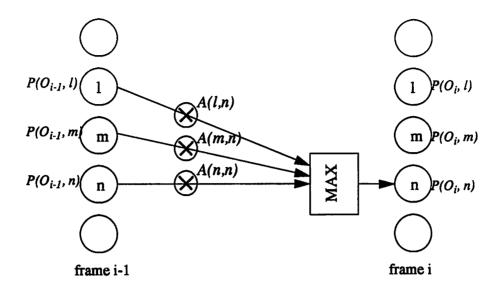

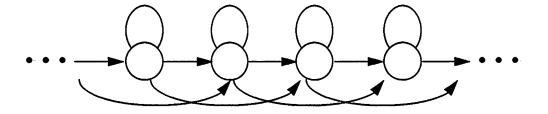

| Figure 18 | Lattice Structure for the Predecessor Implementation                | 60  |  |

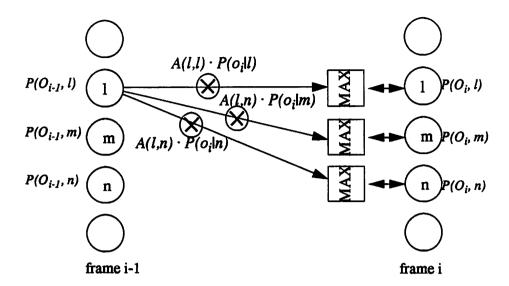

| Figure 19 | Lattice Structure for the Successor Implementation                  | 61  |  |

| Figure 20 | Implementation of the Linked List in the Backtrack Memory           | 66  |  |

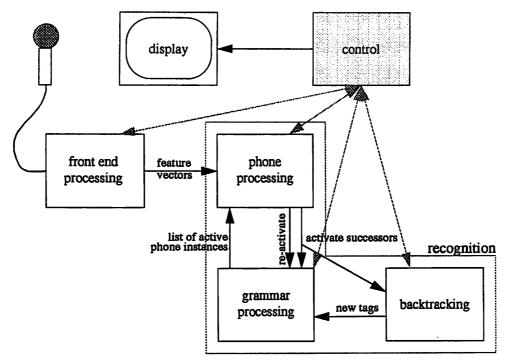

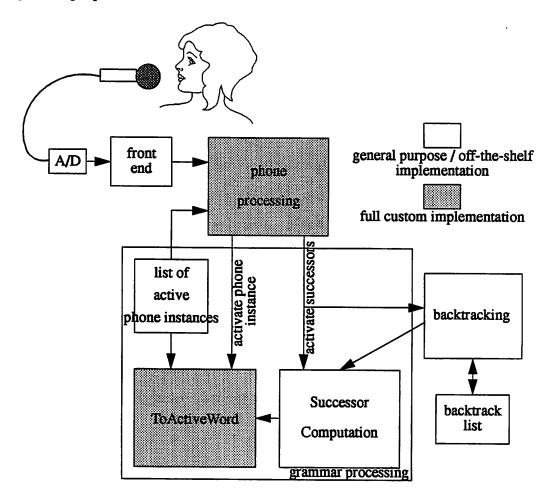

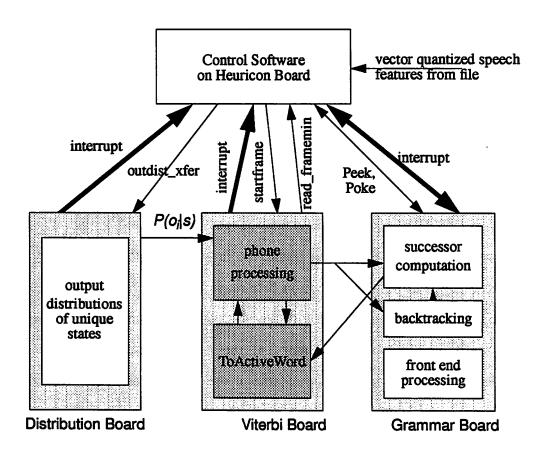

| Figure 21 | Functional System Partition                                         | 68  |  |

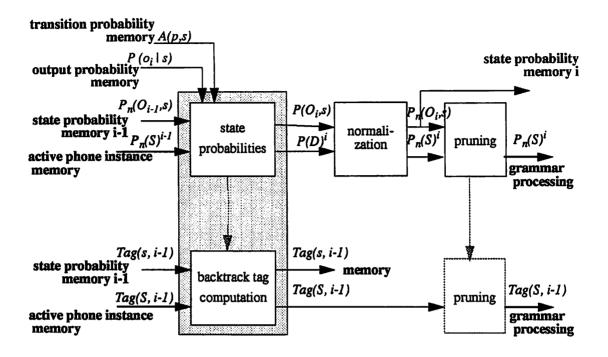

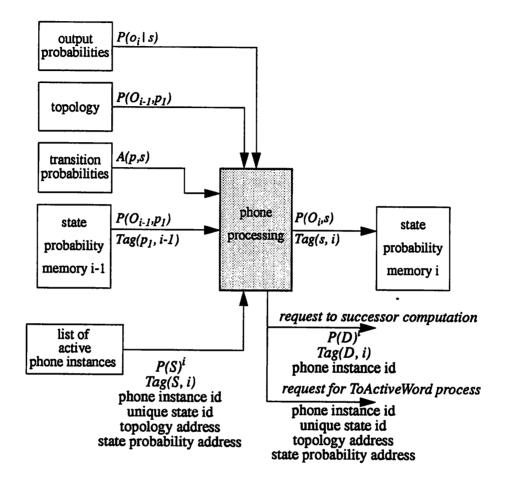

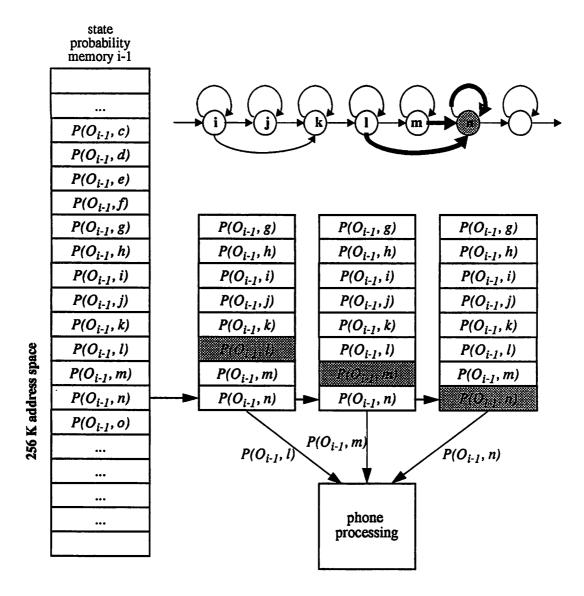

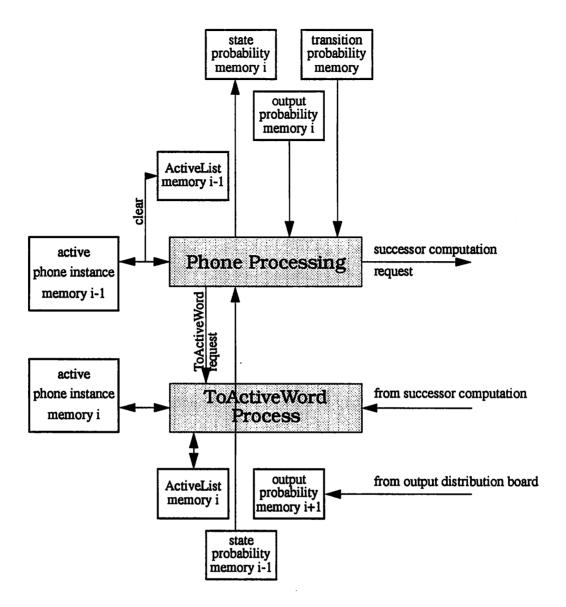

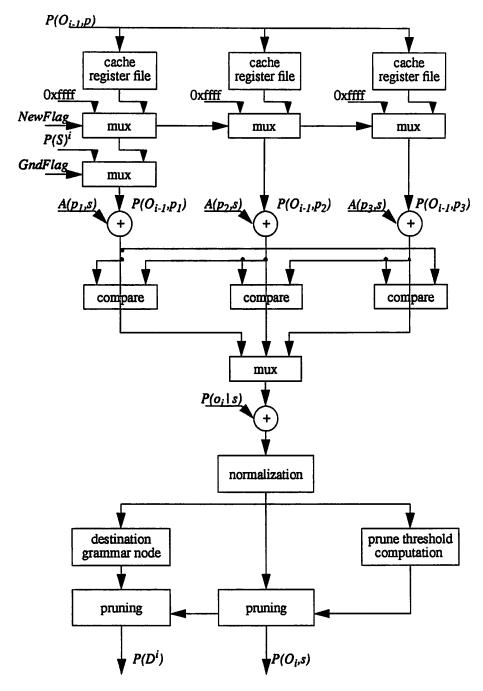

| Figure 22 | Functional Diagram of the Phone Processing System                   | 69  |  |

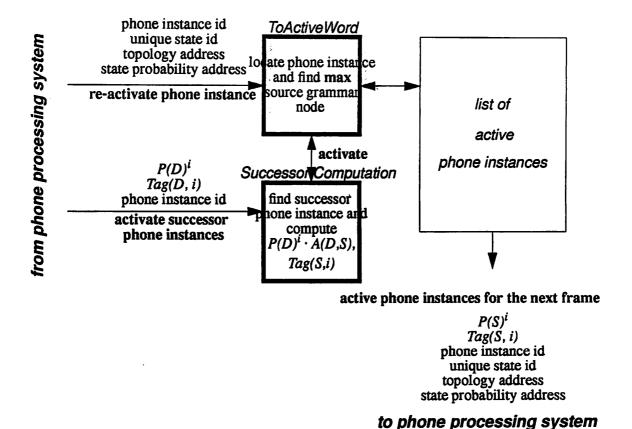

| Figure 23 | Block Diagram of the Grammar Processing System                      | 72  |  |

| Figure 24 | Hardware Partition                                                  | 78  |  |

| Figure 25 | Hardware Partition of the Recognition System                        | 79  |  |

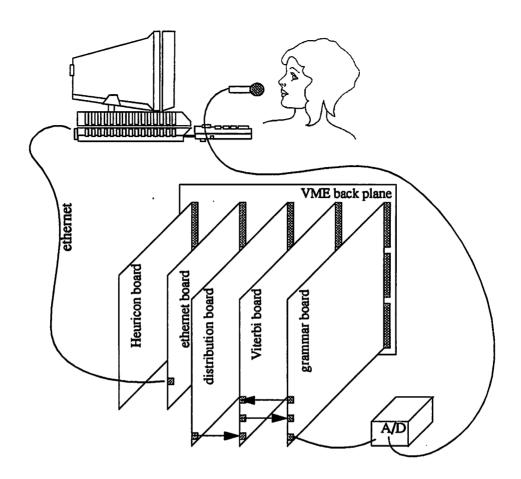

| Figure 26 | The Complete Speech Recognition Hardware                            | 81  |  |

| Figure 27 | Data Flow Diagram of the Viterbi Process on the Phone Level         | 83  |  |

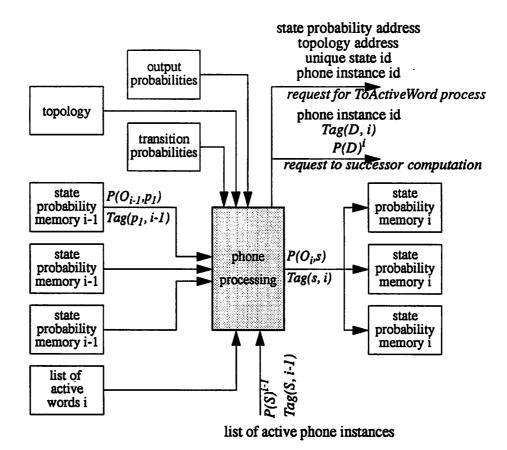

| Figure 28 | Viterbi Process on the Phone Level using Multiple State Probability |     |  |

|           | Memories                                                            | 89  |  |

| Figure 29 | Replication of a Local Subset of the State Probability Memory i-1   |     |  |

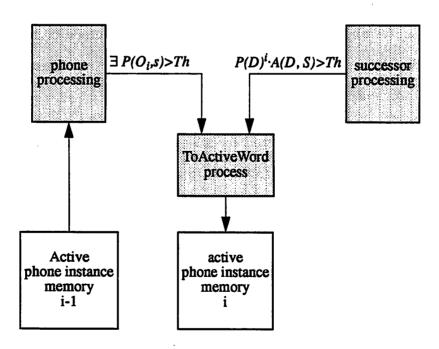

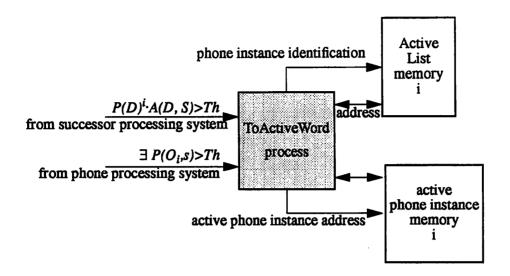

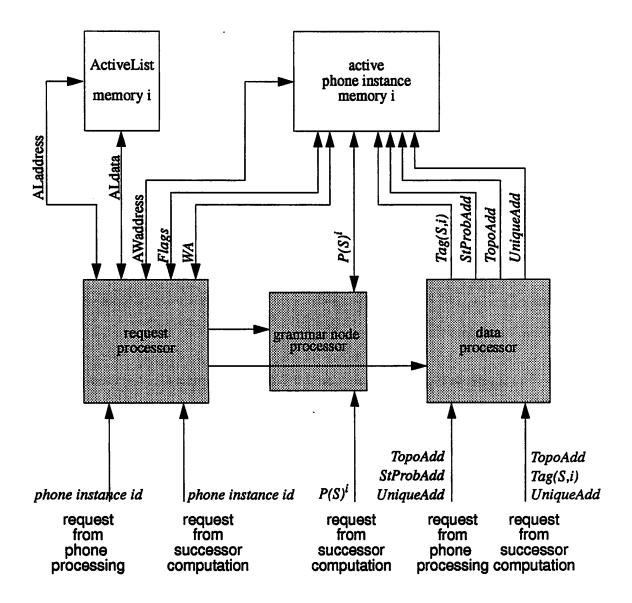

| Figure 30 | Sources for Requests to the ToActiveWord Process                    |     |  |

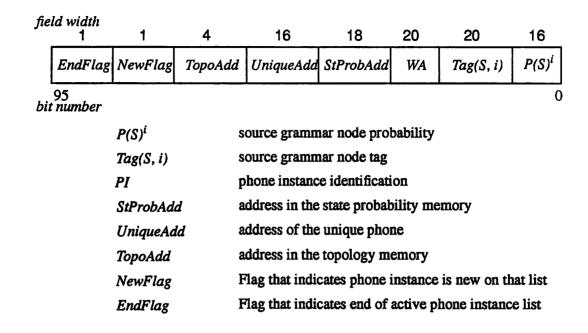

| Figure 31 | Content of the Active Word Memory                                   | 95  |  |

| Figure 32 | Actions of the ToActiveWord System if Phone Instance was Already    |     |  |

| <b>T</b>  | Activated                                                           |     |  |

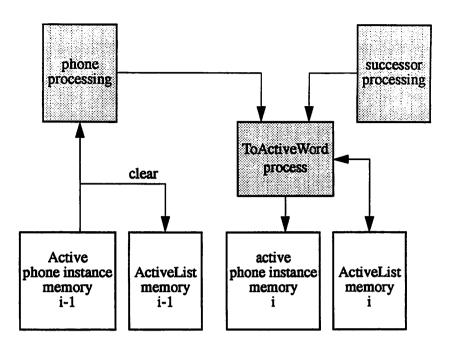

| Figure 33 | Generation of the Active Word List                                  | 99  |  |

| Figure 34 | Clearing the ActiveList Memory                                    | 100 |

|-----------|-------------------------------------------------------------------|-----|

| Figure 35 | Processes and Memories that were implemented on the Viterbi Board |     |

| Figure 36 | Switching Processor Architecture                                  |     |

| Figure 37 | VME Host Access to the Viterbi Board Memories                     | 106 |

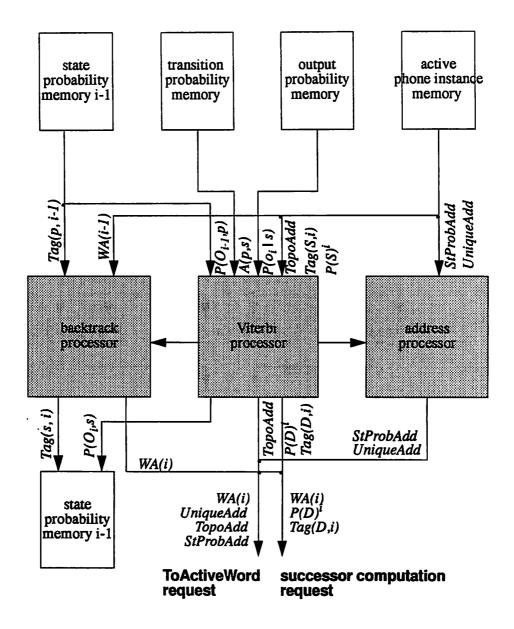

| Figure 38 | Viterbi Process Chip Partition                                    | 109 |

| Figure 39 | Architecture of the Viterbi Processor                             |     |

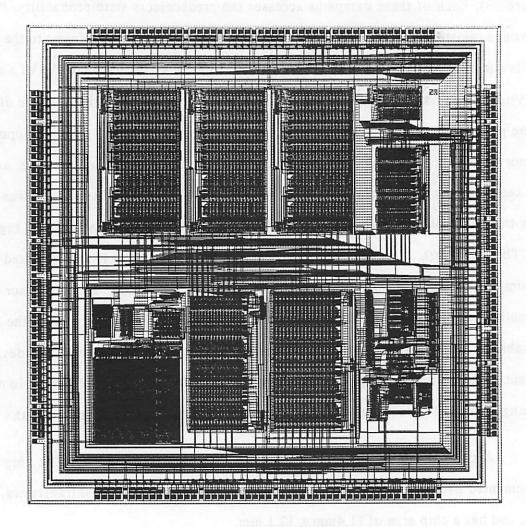

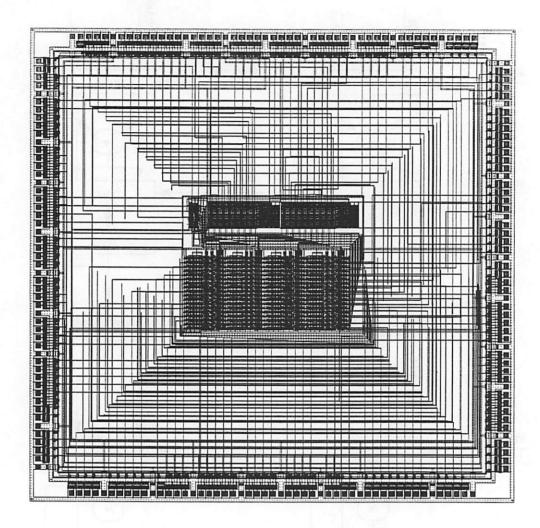

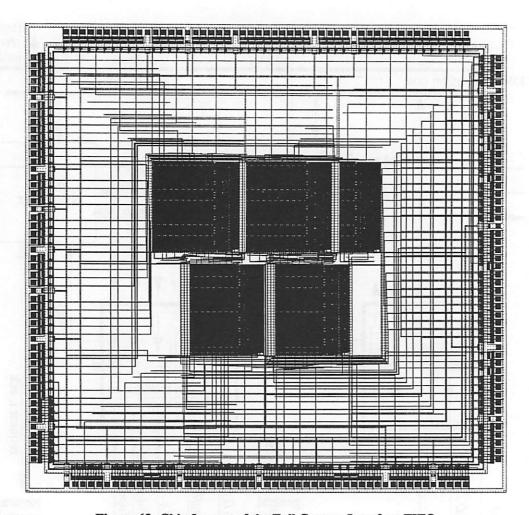

| Figure 40 | Layout of the Viterbi Processor                                   | 112 |

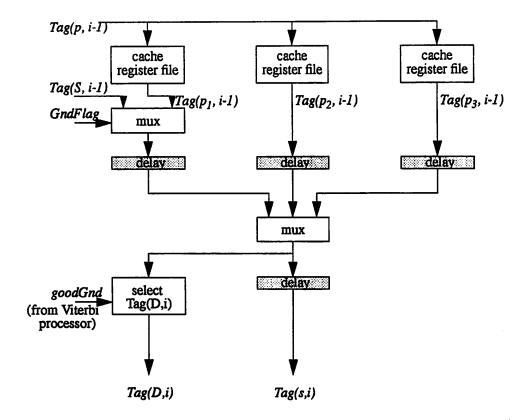

| Figure 41 | Architecture of the Backtrack Processor                           | 113 |

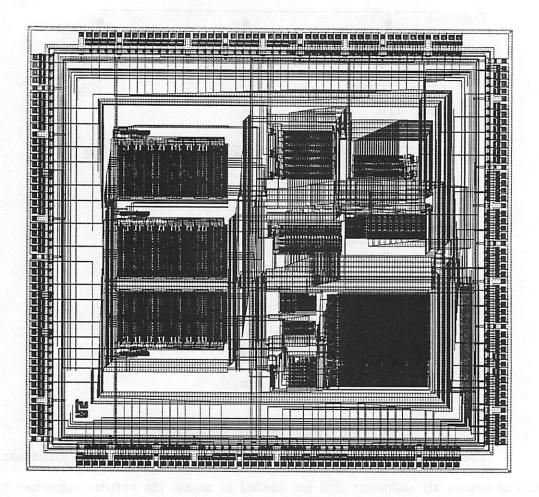

| Figure 42 | Layout of the Backtrack Processor                                 | 114 |

| Figure 43 | Datapaths of the Address Processor                                | 115 |

| Figure 44 | Layout of the Address Processor                                   | 116 |

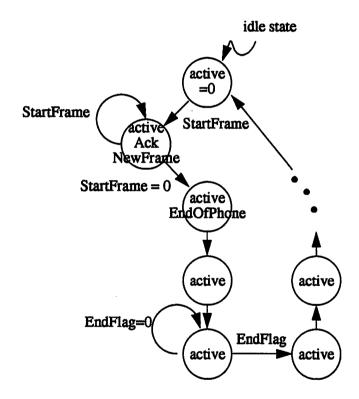

| Figure 45 | State Transition Diagram of the Main Controller                   | 118 |

| Figure 46 | Partition of the ToActiveWord System                              | 122 |

| Figure 47 | Hardware Allocation Table for the ToActiveWord system             | 124 |

| Figure 48 | Layout of the Request Processors                                  | 126 |

| Figure 49 | Layout of the Data Processors                                     | 127 |

| Figure 50 | Layout of the Grammar Node Processors                             | 128 |

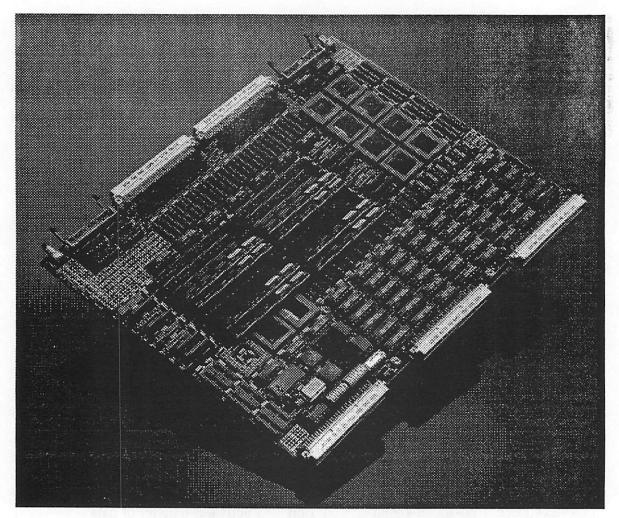

| Figure 51 | The Viterbi Board                                                 | 129 |

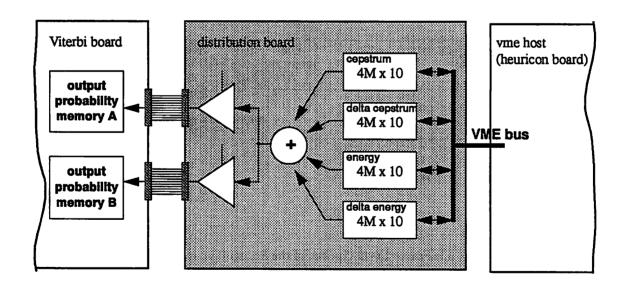

| Figure 52 | Basic Function of the Distribution Board                          | 131 |

| Figure 53 | Frame Level Pipeline of the Recognition Hardware                  | 132 |

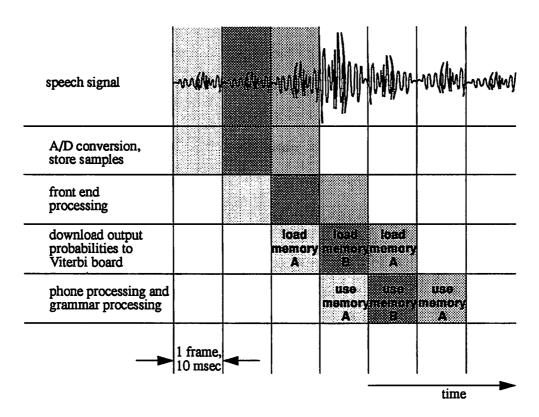

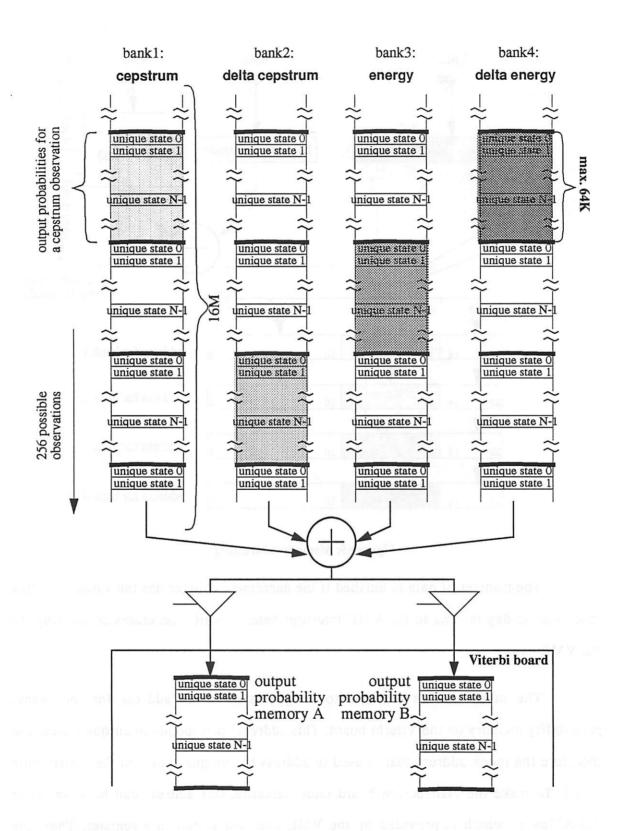

| Figure 54 | Memory Architecture                                               | 135 |

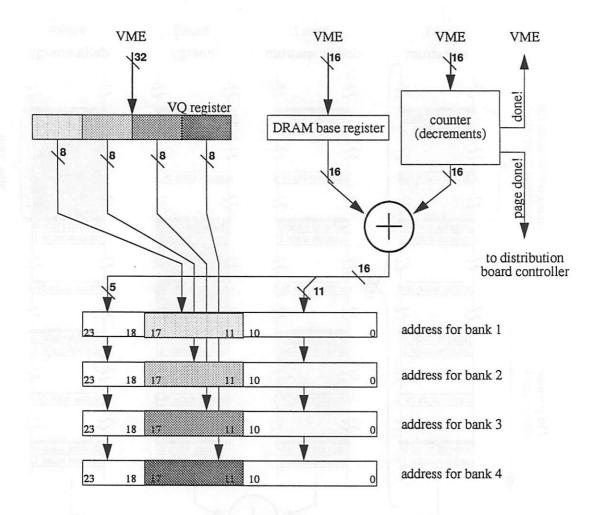

| Figure 55 | Memory Addressing                                                 | 136 |

| Figure 56 | The Distribution Board                                            | 138 |

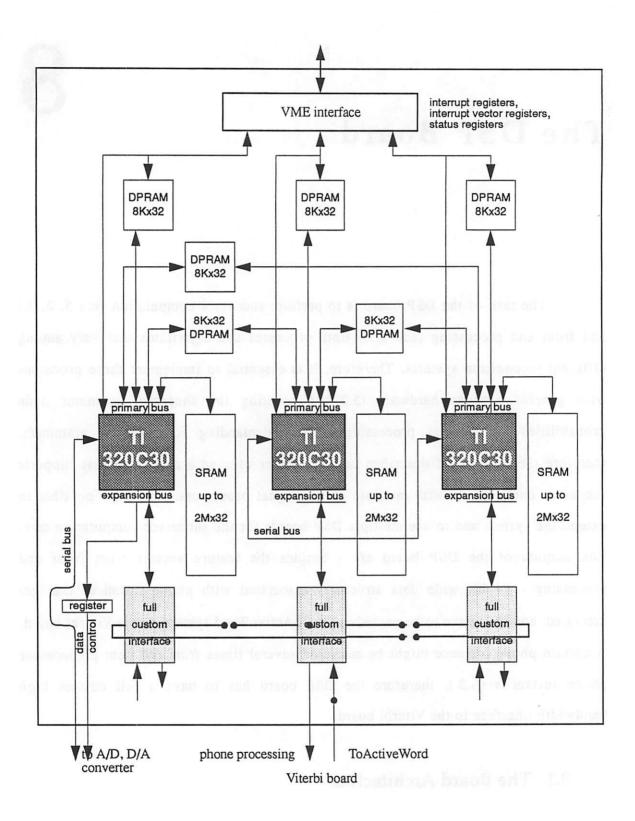

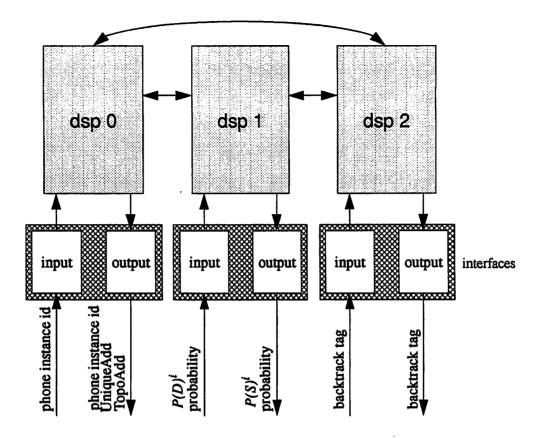

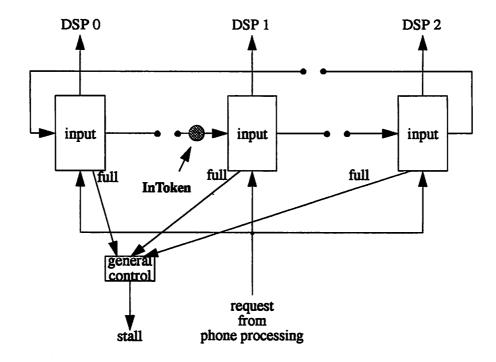

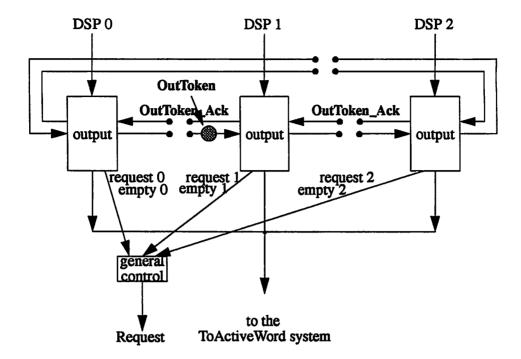

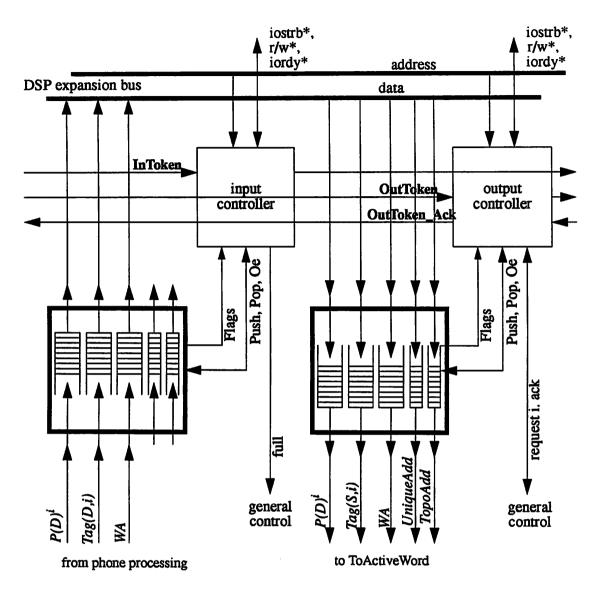

| Figure 57 | DSP Board Architecture                                            | 140 |

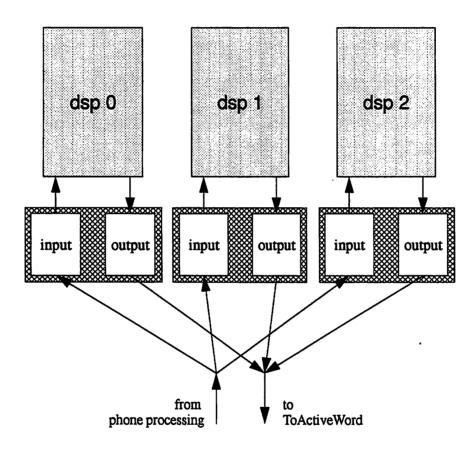

| Figure 58 | Parallel Processing of Successors                                 | 142 |

| Figure 59 | Bitsliced Successor Computation System                            | 144 |

| Figure 60 | Structure of the Input Interface                                  |     |

| Figure 61 | Structure of the Output Interface                                 | 148 |

| Figure 62 | Full Custom Interface                                             |     |

| Figure 63 | Chip Layout of the Full Custom Interface FIFO                     | 150 |

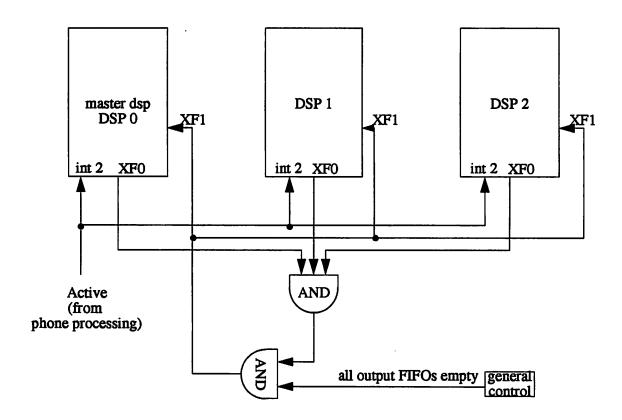

| Figure 64 | Processor Synchronization at the End of a Frame                   | 151 |

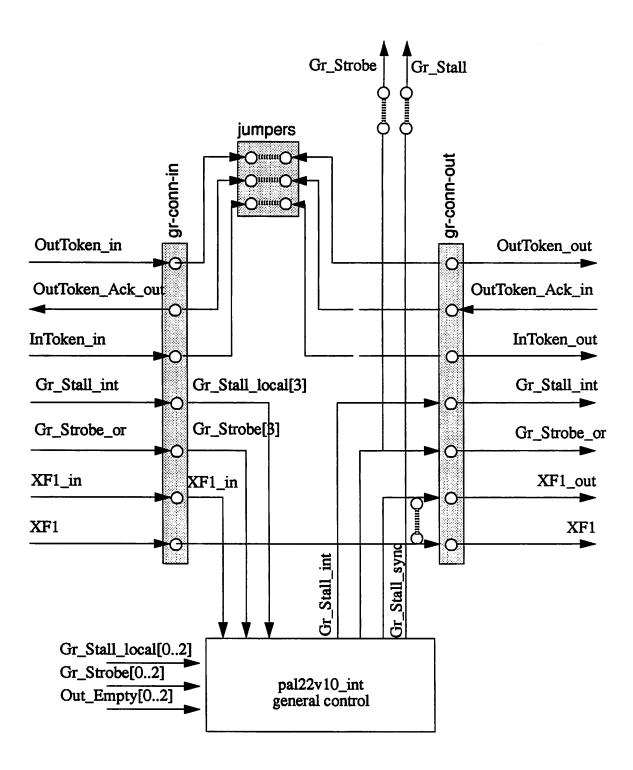

| Figure 65 | Connectors and Jumpers for Multi Board Operation                  | 154 |

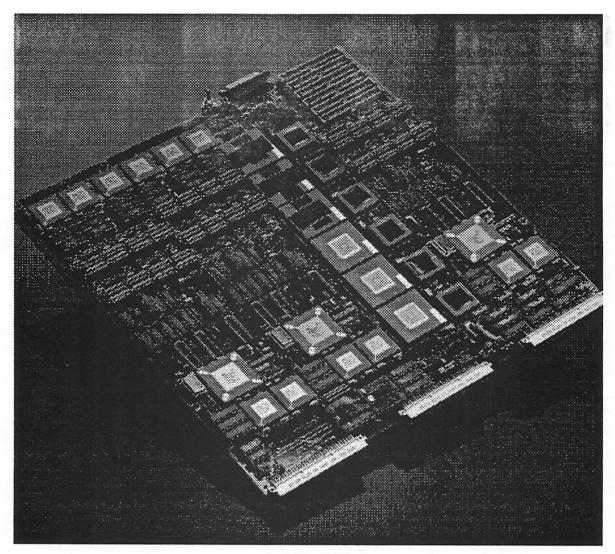

| Figure 66 | The DSP Board                                                     |     |

| Figure 67 | Example Phone Topology                                            | 157 |

| Figure 68 | Topology for the Digit Recognition Task                           |     |

| Figure 69 | System Control During Recognition                                 |     |

## Acknowledgments

A large number of people have contributed towards the successful completion of this project. Above all, I want to thank my advisor, Professor Robert W. Brodersen. He is a great teacher who inspired, guided, and supported me in the past 4 years in so many ways.

In the early phases of the project, I benefitted immensely from numerous discussions I had with Professor Jan Rabaey, Professor Brodersen, and Dr. Hy Murveit. This project contains a large amount of design work, and without the support of many great people it would have been impossible to finish in such a short time. Many thanks to Shankar Narajanaswamy, who designed the ToActiveWord chip set, Robert Yu, who designed the distribution board, and Phil Schrupp, who's knowledge in PCB design was invaluable and who did the physical design of the Viterbi board. Also many thanks to Mani Srivastava, who gave me his parametrized DSP models for the DSP board design, and Brian Richards, who designed the address computation chip, debugged the output distribution board, and who was always available and gave great advice whenever there were problems. This project was a collaboration with the Stanford Research Institute (SRI) in Menlo Park. My thanks to Hy Murveit, Mitch Weintraub, George Chen, and Psi Mankoski. Hy and Mitch made that collaboration possible, and George and Psi spent countless days and nights and weekends to get the hardware working. Also many thanks to the Siemens Research Laboratories in Munich. They made it possible for me to spend these years in Berkeley.

Finally, special thanks to my friends and family. My biggest debt of gratitude goes to my wife, Christine, who gave me so much love and support. She had the strength to take care of our three kids and a stressed graduate student.

## Introduction

Speech is a natural way of transmitting messages between humans, which is more efficient than handwriting or typewriting. It is therefore desirable to provide a speech recognizing man-machine interface that has the ability to listen to a human voice and to recognize the words spoken.

### 1.1. Advantages of Speech Recognition

A speech recognition system offers a number of advantages for entering data into a computer. The average word duration for a continuous speech recognition database that contains 1,529 sentences was computed, and the result shows that, in this database, a word has an average length of 0.352 seconds [Lee89], corresponding to a rate of 170 words per minute. If a speech recognition system were available to keep up with this rate, speech input would be clearly faster than keyboard entry. Another advantage is, that controlling equipment or entering data with speech allows hands free of eyes free operation. For example, a driver would not be distracted if he controlled a car radio by voice: he does not have to push buttons, nor look at the radio to locate these buttons. The hands free feature also is desirable for physically handicapped people to work with a computer or to control equipment.

Speech recognition can also be used to make future portable products feasible by reducing their volume and weight. A normal sized keyboard considerably adds to the bulk of a portable product and could be eliminated if a recognizer were used as the entry mechanism.

Speech recognition systems can be classified in the following way:

- isolated words or connected words. Isolated speech recognition is less difficult than connected speech recognition, but, since the user has to pause between each word, it is not user friendly, and the speech rate is by a factor of 2.5 slower than connected speech recognition [Lee89].

- speaker dependent or speaker independent. Speaker dependent systems have a

higher recognition accuracy than speaker independent systems, but the

recognition accuracy significantly degrades for other users.

- small vocabulary and large vocabulary. As the vocabulary size of a system increases, the number of confusable words grows substantially. Also, in large vocabulary systems each word cannot be modelled individually, and this degrades the recognition accuracy. Large vocabulary typically means a vocabulary of 1,000 words or more [Lee89].

### 1.2. Algorithms in Speech Recognition

Speech recognition has been an active area of research over the last 40 years, and it yielded speech recognition algorithms that roughly can be classified in four groups: template based systems [Wai90a], knowledge-based systems [Wai90b], connectionist systems [Wai90c], and stochastic systems [Wai90d]. The most successful and most widely used speech recognition approach is stochastic modelling, in particular, stochastic modelling using hidden Markov models (HMM) in conjunction with the Viterbi algorithm (2. 3. 1.) for recognition [Wai90d]. The hardware described

in this thesis is used to perform the Viterbi algorithm for HMM based speech recognition systems.

#### 1. 2. 1. Template Based Speech Recognition [Wai90a]

Template based speech recognition systems have a database of prototype speech patterns (templates) that define the vocabulary. The generation of this database is performed during the training mode. During recognition, the incoming speech is compared to the templates in the database, and the template that represents the best match is selected. Since the rate of human speech production varies considerably, it is necessary to stretch or compress the time axes between the incoming speech and the reference template. This can be done efficiently using a dynamic programming based strategy called dynamic time warping (DTW). Template based systems usually are speaker dependent, so each person who wants to use the system has to generate a personal template database by uttering each vocabulary word several times. Usually, each vocabulary word has its own template, and therefore this method becomes impractical as the vocabulary size is increased (>1,000 words). Template based systems have been most successful for speaker dependent, isolated word recognition, however, there are methods to extend these systems to connected speech [Sak79], or towards speaker independence [Rab79].

#### 1. 2. 2. Knowledge Based Speech Recognition [Wai90b]

Knowledge based speech recognition systems incorporate expert speech knowledge that is, for example, derived from spectograms, linguistics, or phonetics. The "existence proof" that speech recognition can be performed using a multitude of knowledge sources comes from experiments with expert spectogram<sup>1</sup> readers. An expert was able to segment spectograms of discrete and continuous speech into phonetic units

<sup>1.</sup> In a spectrogram, the energy of the speech signal in different frequency bands is graphed against time. The intensity of the image at a certain frequency-time point indicates the energy of the speech signal corresponding to that point.

(100% correct for isolated speech, 97% correct for connected speech), and label these units with an error rate of 7% to 19% [Zue85]. The goal of a knowledge based speech recognition system is to incorporate this knowledge using rules or procedures. The drawback of these systems is the difficulty of quantifying expert knowledge and to integrate the multitude of knowledge sources [Wai90b]. This gets increasingly difficult if the speech is continuous, and the vocabulary size is increased. The knowledge based speech recognition system, HEARSAY, developed at CMU, is a speaker-dependent continuous recognition system with a vocabulary of 1011 words. Using a very restrictive syntax (perplexity<sup>2</sup> 4.5), it achieved a recognition accuracy of 87% [Les75].

#### 1. 2. 3. Stochastic Speech Recognition Systems [Wai90d]

The most widely used and most successful speech recognition approach is stochastic modelling. Here, probabilistic models of speech are used to deal with incomplete information or uncertainty. The most widely used model is the hidden Markov model (HMM). It uses states that model generic speech sounds and transitions between the states with associated transition probabilities to model the temporal behavior of speech. This model assumes that speech was produced by a hidden Markov process. At any given time the process occupies one state in the HMM, and this state outputs a small segment of speech (observation) based on a probability distribution that gives the likelihood that a certain speech sound could have been produced by that state (output probability). Then, the speech process makes a state transition based on the transition probabilities between the states.

To derive these HMM parameters (output and transition probabilities), an efficient estimate-maximize algorithm, the forward-backward algorithm, is often used [Wai90d]. Because of it's efficiency, it is possible to derive these parameters from a

<sup>2.</sup> The perplexity Q is an information theoretic measure of a tasks difficulty. It is defined as Q=2<sup>H</sup>, where H is the entropy, or the number of bits necessary to specify the next word using an optimal encoding scheme [Lee89].

large body of speech data (for example, several thousand words for any vocabulary word). Thus, compared to knowledge-based approaches, it is easy to compile knowledge sources into a compiled architecture [Wai90]. For speech recognition, it is necessary to find the most likely state transition given the incoming speech. This state transition can be found using the dynamic programming Viterbi algorithm (see 2. 3. 1.).

A short coming of HMMs is, that speech observations generated by the HMM are only conditionally independent given the underlying state sequence [Ost90]. Another stochastic modelling approach that attempts to overcome this problem are stochastic segment models (SSM) [Rou87]. In this approach, there are templates that model the distributions of entire speech segments consisting of a sequence of observations, and the incoming speech has to be aligned to these template segments (resampling transformation). In [Rou87], it was shown that SSMs achieve - for a 350 connected word, speaker-dependent task - an average word recognition accuracy of 83%, while in the same task, a HMM based recognizer achieved 76%. The drawback of SSMs is, however, that recognition requires significantly more computation than HMM based speech recognition [Ost90].

#### 1. 2. 4. Connectionist Speech Recognition Systems [Wai90c]

Connectionist speech recognition is based on artificial neural networks that use learning strategies to organize and optimize a network of processing elements (neurons). These networks are used as classifiers or mapping functions to recognize the incoming speech. Thus, speech knowledge or constraints used for speech recognition are distributed among many, but simple processing elements [Wai90c]. This approach to speech recognition is the youngest, and researchers are investigating a number of approaches. For example, new physiological-based front end processing, and combined recognizers, that implement neural net and conventional recognition approaches are being investigated. Preliminary results look promising, a Time-Delay Neural Network recognizer was compared to a HMM recognizer in the task to recognize the phones "B",

"D", and "G" out of a database of 5,240 Japanese words. For different speakers, the HMM had a recognition accuracy of 90.9% to 97.2%, while the neural net achieved accuracies of 97.5%-99.1% [Wai88].

### 1.3. Language Processing

The speech recognition described above concentrated on the problem of recognizing speech given an acoustic representation of the speech patterns. However, a human uses many other sources of knowledge that are non-acoustic: for example, knowing the person talking and what he is talking about makes it possible to understand the person, even if there is noise and not every individual word can be understood. These non-acoustic sources of information are collectively called language processing, and modeling these non-acoustical sources is called language modelling [Wai90e].

As an example how language constraints can improve recognition accuracy, let us consider a car radio control application. After a person said the word "turn", it is possible to constrain the recognition vocabulary to the words "on" or "off". This increases recognition accuracy, since this constraint eliminates words that might be acoustically similar and thus hard to distinguish. On the other hand, this grammar constrains the recognition system just to car radio control application, other applications might use a different grammar and the user is constrained to use the appropriate one. This is termed finite state grammar, since there is only a set of allowable sentences which are modelled using fixed networks.

Another language modelling technique is to use statistical methods. One approach is to assume, that the probability of a word depends on the previous N words, and that the probabilities of different words are independent. The most common grammars use N=1 (bigram grammar) or N=2 (trigram grammar). Using such a statistical grammar reduces the perplexity, which is a measure of a task's difficulty. It is

roughly the number of words that can follow a word<sup>3</sup>. Reducing the perplexity, however, does not contribute to speech understanding. For that, models for syntax (which sentences are acceptable), prosody (pitch, loudness, rhythm, stress), and semantics (the meaning of a sentence) have to be integrated to the acoustic recognizer. These methods are powerful to increase the usability for speech recognition systems.

For example, SRI has an experimental airline travel information system (ATIS) that can be used to query a database of flight schedules [Murv91]. The user can ask questions to the system, and the words of these questions are recognized by an HMM recognition system. Then, the semantics of the question is extracted, and a database query generated. The user can speak in a natural way, not constrained to any grammar or vocabulary. The word recognition accuracy of the speech recognition system is 86.4%, which corresponds to a sentence error rate of 60%. Despite this large sentence recognition error, the ATIS system generates a valid database query for 66.2% of the input sentences, for 7.5% of the sentences it generates a false query, and with 26% it generates no query [Pal91].

### 1.4. Performance and Limitations of Speech Recognition

Ideally, a speech recognition system should be usable by several people, and not just dedicated to a certain person. It should have a high recognition accuracy, a very large vocabulary, have the ability to recognize connected words, be task independent, and operate in real time. Given state-of-the-art speech technology, however, it is necessary to make some compromises to achieve acceptable recognition accuracies (>90%). The task of speech recognition gets more complicated as the system moves from speaker dependence to speaker independence, from discrete words to connected

<sup>3.</sup> The perplexity Q is an information theoretic measure of a tasks difficulty. It is defined as  $Q=2^{H}$ , where H is the entropy, or the number of bits necessary to specify the next word using an optimal encoding scheme [Lee89].

words, from small vocabulary to large vocabulary, and from task dependence to natural tasks. For example, IBM's Tangora system [Jel85] has a large vocabulary (20,000 words), the grammar is not restricted to a certain task, the recognition accuracy averages 94.3%, and it operates in real time. However, the system is speaker dependent and can only recognize discrete words, so the user is confined to speak in an unnatural way. Another example is SRI's DECYPHER system: It has a 1,000 word vocabulary, is speaker independent, accepts natural, connected speech and has a recognition accuracy of 95.6% [Pal90]. However, in order to achieve high recognition accuracy, the vocabulary and the grammar are restricted to a certain task (resource management, [Pri88]). In this task, a statistical bigram grammar is used that reduces the perplexity to 60 (without grammar, any word can follow a given word). Using this grammar, the recognition accuracy for DECIPHER improves from 75.7% (no grammar) to 95.6% [Pal90]. Since DECIPHER is a connected speech recognition system, the recognition algorithm involves more computation than a discrete recognition system (by a factor of 3 [Lee90], [Bah81]), and real time performance is more difficult to achieve.

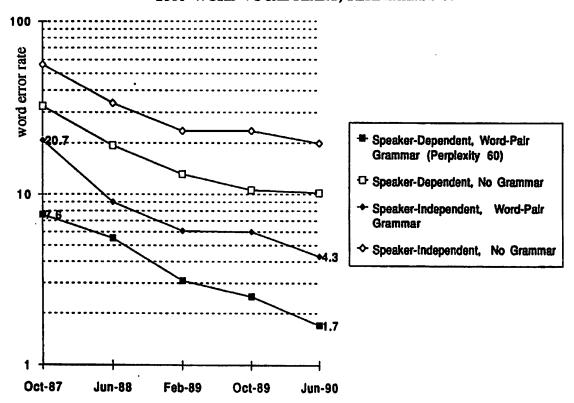

Figure 1 shows the influences that speaker independence and grammar has on recognition accuracy, and it summarizes the progress that has been made in speech recognition over the last years. In this graph, the word error rates for a specific task (resource management, [Pri89]) is shown over time. It demonstrates, that speaker dependent speech recognition that uses a grammar yields the best recognition accuracy, while speaker independent recognition without grammatical constraints performs worst.

### 1.5. VLSI for Real Time Speech Recognition

To fully realize the advantage of speech recognition, it is critical that the recognition system operates in real time. This means, it must continuously process the speech input so the user does not have to pause in order for the recognition system to catch up with the computation.

## RESOURCE MANAGEMENT CORPUS, READ SPEECH 1000-WORD VOCABULARY, PERPLEXITY 60

Figure 1: Recognition Accuracies for the Resource Management Task [Way91]

Speech recognition based on HMMs is computational demanding, particularly for continuous speech and large vocabulary. A signal processor, the TMS320C30, can process in real time about 100,000 states of a HMM per second using the Viterbi recognition algorithm, however, at least 400,000 states per second are required for a 1,000 word continuous speech recognition system [Bis89]. Since real time performance is an important issue, commercial and experimental real time recognition systems have been developed, but no system has been reported that can recognize connected speech in real time for a vocabulary that has significantly more than 1,000 words. A few real time systems are described in 3.1. and 3.2.

#### 1. 5. 1. General vs. Special Purpose Implementation

The question is, should a real time speech recognition system be implemented using full custom processors that are tailored to the recognition algorithm, or should systems be used that consist of general purpose processors. The conventional view is, that general purpose systems can be developed much faster and thus cheaper than custom VLSI systems, also it is believed that general purpose systems can be programmed using a high level language which makes them more versatile, since a new recognition algorithm can be supported just by re-writing the software for the general purpose processors. Since speech recognition algorithms are still evolving, this feature is desirable.

However, one of the goals of this thesis is to demonstrate that there is no reason why VLSI systems cannot be developed as fast as general purpose systems. Furthermore, the HMM algorithms have stabilized so that an appropriate custom architecture is able to adapt to new algorithms.

The approach to reduce the time for development of VLSI systems is based on advances that were made in computer aided design (CAD) tools. In particular, the LAGER silicon compilation system can be used to compile VLSI chips using either a hierarchical structural description, or an architectural template in conjunction with microcode [Shu91]. The LAGER system evolved into the SIERA design environment for rapid VLSI system prototyping. In SIERA, it is possible to specify an algorithm in a variety of ways including a high level flowgraph and structural description. Within the environment are a number of generation and a synthesis tools which produce a complete structural description using scheduling and re-timing. This structure is then used to compile the individual VLSI processors and to generate PCB layouts or multichip modules. The VLSI systems thus obtained effectively have the algorithm coded in the structure of the datapaths, or in microcode of programmable processors [Rab91].

General purpose systems, on the other hand, often make use of programmable hardware. Thus, the task of scheduling or re-timing is moved to the software level. For the BEAM general purpose real time speech recognition system, 80% of the development time was spent for software development [Bis89]. This time was almost equally divided between support software development, algorithm restructuring, and algorithm coding. 20% of the time was spent for designing and building a custom board that contains three commercial processors. Designing and building a board, however, has to be done for both approaches, and there is no fundamental difference in the time required for the board design. In the system described in the thesis, it took about 5 months to design and simulate the most complex board (Viterbi board), but it took only 2 months to design the full custom processors that already implement the algorithm. If the time is also considered that it took to structure and modify the algorithm, and to design the system architecture, the "time to market" for this full custom system is comparable to the time it takes to design a general purpose system.

Of course, in the same way CAD tools for VLSI systems advanced, there are synthesis tools for software development, for example [Rab91]. Thus, with the advent of these design tools, a high level description of the algorithm can either be synthesized into VLSI, or into code, and the choice between one implementation over the other can be independent of the "time to market" issue, and only depend on issues like cost, performance, or quantity.

The advantage of VLSI systems over systems that use general purpose components is, however, that they can be much more powerful while being small (see 3.2.). The reason for that is, that the architecture of the system and the VLSI chips can be tailored to the specific needs of the algorithm that is implemented. For example, if there is a memory bottleneck, it can be eliminated just by implementing parallel interconnect. Also, VLSI systems only contain the essential hardware needed to perform a particular algorithm, while general purpose systems include a number of

unused features. These are advantages that are decisive for competitiveness, be it production cost or performance.

This thesis describes the algorithm, architecture and implementation of a VLSI-based connected speech recognition system capable of recognizing words using a vocabulary of up to 60,000 words. Thus, it can be used for applications such as word processing where most of the English language is in the recognition vocabulary (Merriam Webster's Seventh New Collegiate Dictionary has 60,000 words). In this system, it is necessary to achieve a high performance: in section 4. 2. 2., we will derive that such a system has to process 20 million states per second (a factor of 50 over what has been previously reported [Bis89]). Thus, it was implemented in an architecture based on 6 full custom VLSI processors that directly map the recognition algorithm into hardware.

2

## Algorithm

It is generally accepted that Hidden Markov Models (HMM) are currently the most accurate technique for modelling speech for use in automatic speech recognition [Rab86], [Lee88], [Schw87]. For large vocabulary speaker independent connected speech recognition systems it has better recognition accuracies than the preciously popular dynamic time warp algorithm (DTW) [Kav86, Stö87]. The DTW algorithm was implemented by a number of researchers in custom hardware, and the basic search mechanism is similar to the HMM approach. So, it is worthwhile to compare the two methods [Kav86, Stö87].

For both techniques, the task is to recognize a sequence of speech utterances by comparing it to a model that describes speech segments such as phones or words. To do that efficiently, the incoming speech is first processed to reduce its data rate. This will be called *front end processing* in which speech is segmented into *frames*, which are time intervals of typically 10-20 msec, and the characteristics of frame i is described with a vector of features,  $o_i = \{o_i^{\ l} \dots o_i^{\ l}\}$ . One feature vector,  $o_i^{\ l}$ , could be the energy of the speech signal in different frequency bands, or if this vector is vector quantized [Gra84], the address of the codebook vector that has the best match to these energies.

The difference between DTW and HMM based speech recognition is the way in which a speech segment is modelled. In DTW based systems, the speech representation

is a template, which is the sequence of trained features that describe a certain word. Thus, to find the unknown word or phrase, it is necessary to find the template that is most similar to the unknown word. This is done by computing a distance between the features of the template and the unknown word: the smaller the distance between these two representations, the more similar the words. To take into account a possible time distortion between the two representations, the time axis are warped to minimize the distance using the recursive dynamic time warp algorithm.

In HMM based systems, the speech model is statistical and based on a Hidden Markov model. The assumption is that the unknown speech was produced by an HMM speech process that produces speech features based on state transitions. The task in speech recognition is to recover the state transitions that most likely produced the input speech features. When the most probable state sequence is determined, it is straightforward to reconstruct the sequence of words that was spoken. A very efficient search algorithm for the most likely state sequence is the Viterbi algorithm.

### 2.1. Front End Processing

Front end processing takes the speech waveform that has to be recognized and converts it into sets of features. The set of features at time i is an observation,  $o_i$ , and a whole sentence can be described by a sequence of observations,  $O_N = o_1 \dots o_N$ . This observation sequence is then used to find the most probable state sequence in the HMM.

In general, there are two major classes of front end processing algorithms, parametric and non-parametric. Parametric algorithms extract speech parameters such as LPC<sup>1</sup> coefficients. Thus, the observations are the parameters of the autoregressive

<sup>1.</sup> Here, the generation of the speech waveform is modeled with an all-pole filter (autoregressive model) that has two inputs: a stream of pulses to generate voiced speech, and white noise to generate non-voiced speech. Thus, to describe a segment of speech it is only necessary to specify the filter coefficients and the input. These parameters are estimated using linear predictive coding (LPC, [Rab78]).

speech model itself or some features that were derived from these parameters (for example, LPC-based cepstral coefficients). Non-parametric algorithms, on the other hand, analyze speech data to directly measure certain features such as zero crossings or the energy of the signal in certain frequency bands.

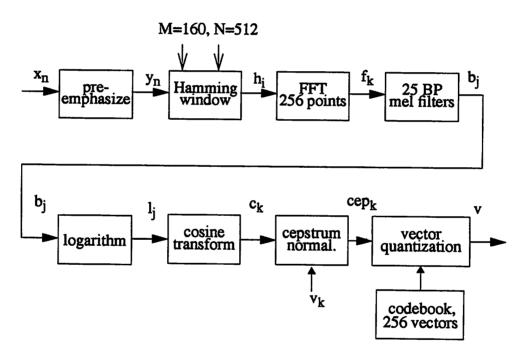

Both classes are widely used in speech recognition, with active proponents of both approaches [Lee89, Murv89]. This system uses a general purpose signal processor for front end processing, so either method (or both) can be implemented. We chose to implement a non-parametric feature extraction algorithm that is used in DECIPHER [Murv89]. A block diagram of this algorithm is shown in Figure 2.

Figure 2: Block Diagram of the Front End Algorithm

The incoming speech,  $x_n$ , is sampled at 16KHz and linearly quantized to 16 bits. It then is pre-emphasized using the following equation

$$y_n = x_n - A \cdot x_{n-1}$$

$$A = 0.95$$

(EQ 1)

The pre-emphasized speech is then blocked into frames of N=512 samples (32 msec) which are spaced M=160 samples (10ms) apart. Thus, consecutive frames overlap by 352 samples (22ms). Each frame is smoothed by a Hamming window, (EQ 2) shows the corresponding equation for the kth frame:

$$h_i = m_i \cdot y_{kM-i}$$

$m_i = 0.54 - 0.46\cos\left(\frac{2\pi i}{N-1}\right)$

$i = 0...N-1$

(EQ 2)

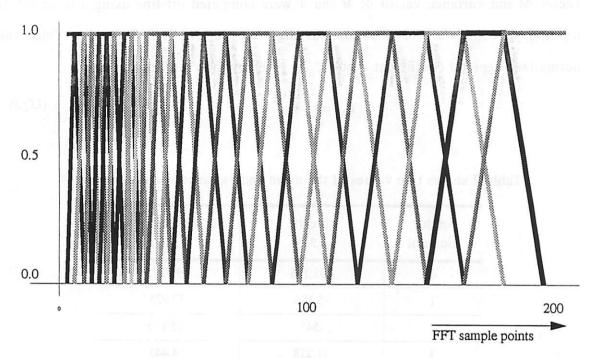

This resulting windowed frame is then used to compute a 256 point Fast Fourier Transform (FFT). The FFT spectrum is then integrated into L=25 mel-bandpass filters<sup>2</sup>. These filters are shown in Figure 3, and a table of the band edges is shown in Table 1.

| 1 FFT point = 31.25 Hz | lower stopband edge, in FFT points | lower passband edge, in FFT points | upper passband<br>edge, in FFT points | upper stopband edge, in FFT points |

|------------------------|------------------------------------|------------------------------------|---------------------------------------|------------------------------------|

| filter 0               | 0                                  | 0                                  | 6                                     | 11                                 |

| filter 1               | 3                                  | 6                                  | 10                                    | 14                                 |

| filter 2               | 6                                  | 10                                 | 13                                    | 17                                 |

| filter 3               | 10                                 | 13                                 | 16                                    | 20                                 |

| filter 4               | 13                                 | 16                                 | 19                                    | 23                                 |

| filter 5               | 16                                 | 19                                 | 22                                    | 27                                 |

| filter 6               | 19                                 | 22                                 | 26                                    | 30                                 |

| filter 7               | 22                                 | 26                                 | 29                                    | 33                                 |

| filter 8               | 26                                 | 29                                 | 32                                    | 36                                 |

| filter 9               | 29                                 | 32                                 | 35                                    | 41                                 |

Table 1: Band Edges of the Mel BP Filter

<sup>2.</sup> The mel frequency scale is a physiological scale that takes into account the performance of the human auditory system to differentiate between frequencies. The differences in frequencies below 1 KHz can be very well distinguished, while frequencies above 1KHz are more difficult. This behavior roughly translates into a frequency scale which is linear to the physical frequency below 1 KHz, but the logarithm of the frequency above. The mel bandpass filters are equally spaced in the mel frequency scale, and they are used to copy human performance in the perception of frequencies in the hope that information relevant for speech recognition is extracted from the speech signal.

Figure 3: Mel Bandpass Filters

| 1 FFT point = 31.25 Hz | lower stopband edge, in FFT points | lower passband edge, in FFT points | upper passband edge, in FFT points | upper stopband edge, in FFT points |

|------------------------|------------------------------------|------------------------------------|------------------------------------|------------------------------------|

| filter 10              | 32                                 | 35                                 | 40                                 | 46                                 |

| filter 11              | 35                                 | 40                                 | 45                                 | 52                                 |

| filter 12              | 40                                 | 45                                 | 51                                 | 59                                 |

| filter 13              | 45                                 | 51                                 | 58                                 | 68                                 |

| filter 14              | 51                                 | 58                                 | 67                                 | 77                                 |

| filter 15              | 58                                 | 67                                 | 76                                 | 87                                 |

| filter 16              | 67                                 | 76                                 | 86                                 | 98                                 |

| filter 17              | 76                                 | 86                                 | 97                                 | 110                                |

| filter 18              | 86                                 | 97                                 | 109                                | 122                                |

| filter 19              | 97                                 | 109                                | 121                                | 136                                |

| filter 20              | 109                                | 121                                | 135                                | 150                                |

| filter 21              | 121                                | 135                                | 149                                | 165                                |

| filter 22              | 135                                | 149                                | 164                                | 181                                |

| filter 23              | 149                                | 164                                | 180                                | 197                                |

| filter 24              | 164                                | 180                                | 255                                | 255                                |

Table 1: Band Edges of the Mel BP Filter

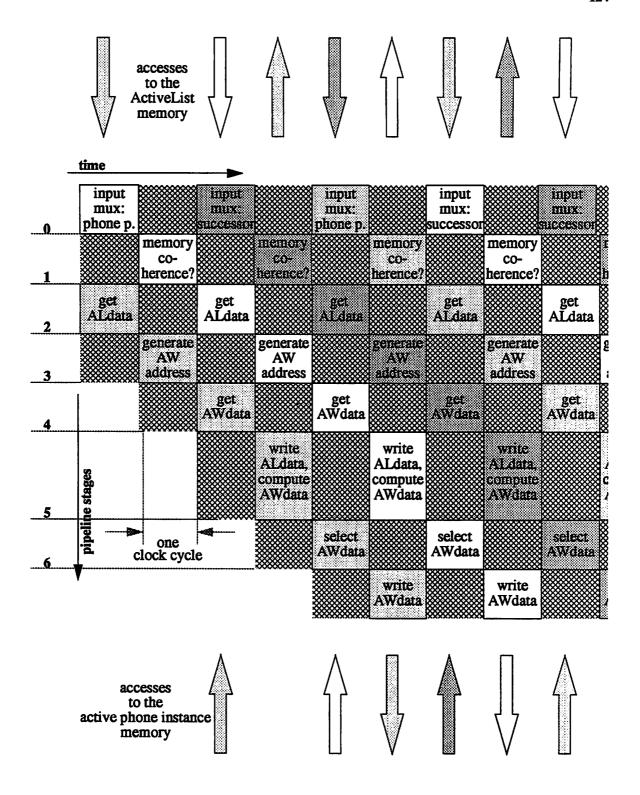

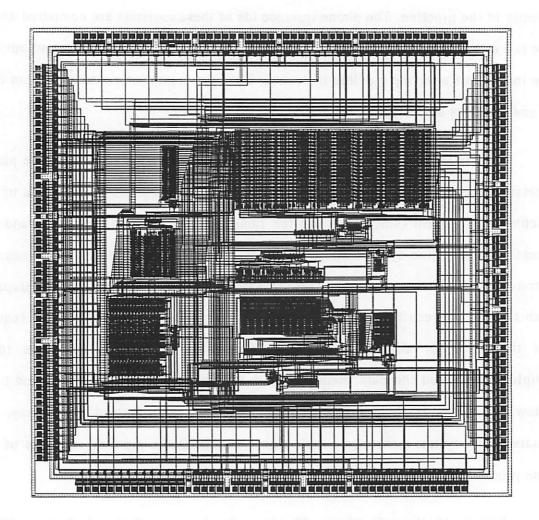

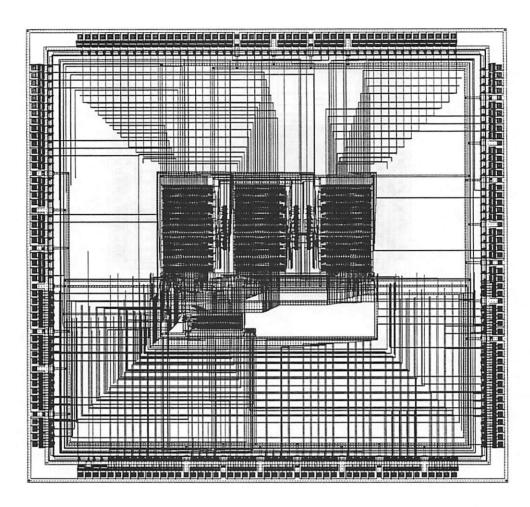

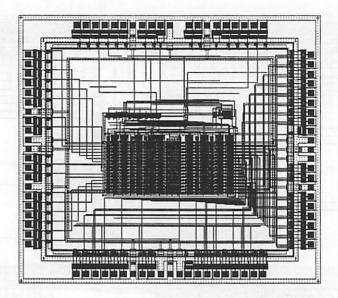

After that, the energy of each bandpass filter gets converted to the logarithm of the energy,  $l_j$ , j=0..L-1. These energy values are then used to get the cepstral coefficient<sup>3</sup> vector  $C = [c_0, ..., c_{12}]$  using the cosine transform, which is described in the following equation (EQ 3):