Copyright © 1991, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### HIGH QUALITY, LOW BIT-RATE SPEECH CODING FOR LOW-POWER VLSI IMPLEMENTATION

by

Paul Landman

Memorandum No. UCB/ERL M91/41

20 May 1991

# HIGH QUALITY, LOW BIT-RATE SPEECH CODING FOR LOW-POWER VLSI IMPLEMENTATION

by

Paul Landman

Memorandum No. UCB/ERL M91/41

20 May 1991

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Acknowledgements

This report was made possible by the support and guidance of several individuals. Foremost, I would like to recognize my research advisor, Professor Jan Rabaey, for his invaluable contributions during all phases of this project. Furthermore, I thank all of the members of his research group for their assistance and patience in answering my questions. Likewise, I am grateful to Professor Robert Brodersen and his students for their equally kind support and assistance.

In addition, I would like to acknowledge my parents, Art and Fran Landman, who were an endless source of comfort throughout my academic career.

Finally, I would like to dedicate this report to Karen Lugenbehl, the guardian of my sanity for the last five years.

This research was sponsored by a fellowship from the National Science Foundation as well as DARPA grants N00039-88-C-0292 and J-FBI 90-073.

# Contents

| Li | st of | Figur            | res                            |   |   |   | iv |  |  |  |  |  |

|----|-------|------------------|--------------------------------|---|---|---|----|--|--|--|--|--|

| Li | st of | Table            | <b>es</b>                      |   |   |   | vi |  |  |  |  |  |

| 1  | Ove   | erview           |                                |   |   |   | 1  |  |  |  |  |  |

|    | 1.1   | Introd           | duction                        |   |   |   | 1  |  |  |  |  |  |

|    | 1.2   |                  | aization                       |   |   |   | 2  |  |  |  |  |  |

| 2  | Low   | -Powe            | er VLSI Systems                |   |   |   | 3  |  |  |  |  |  |

|    | 2.1   | Power            | r Consumption in CMOS Circuits |   | _ |   | 3  |  |  |  |  |  |

|    | 2.2   | Strate           | egies for Low-Power VLSI       |   |   |   | 5  |  |  |  |  |  |

|    |       | 2.2.1            | Packaging                      |   |   |   | 5  |  |  |  |  |  |

|    |       | 2.2.2            | Design Styles                  |   |   |   | 6  |  |  |  |  |  |

|    |       | 2.2.3            | Circuit Techniques             |   |   |   | 9  |  |  |  |  |  |

|    |       | 2.2.4            | Technology Scaling             |   |   |   | 10 |  |  |  |  |  |

|    |       | 2.2.5            | Supply Voltage Scaling         |   |   |   | 12 |  |  |  |  |  |

|    |       | 2.2.6            | Architectures                  |   |   |   | 13 |  |  |  |  |  |

|    |       | 2.2.7            | Algorithms                     |   |   |   | 17 |  |  |  |  |  |

|    |       | 2.2.8            | Power Management               | _ |   |   | 18 |  |  |  |  |  |

|    | 2.3   | Summ             | nary of Low-Power Methodology  |   |   |   | 19 |  |  |  |  |  |

| 3  | Spe   | Speech Coding 20 |                                |   |   |   |    |  |  |  |  |  |

|    | 3.1   | Speech           | h Processing Background        |   |   |   | 20 |  |  |  |  |  |

|    |       | 3.1.1            | Human Speech Generation        | • | • | • | 20 |  |  |  |  |  |

|    |       | 3.1.2            | The Speech Waveform            | • | • | • | 22 |  |  |  |  |  |

|    |       | 3.1.3            | A Model for Speech Generation  | • | · | • | 24 |  |  |  |  |  |

|    | 3.2   | Speech           | h Coding Methods               | • | • | • | 28 |  |  |  |  |  |

|    | 3.3   | Criteri          | ia for Candidate Algorithms    |   |   |   | 30 |  |  |  |  |  |

|    | 3.4   | Selecti          | ion of Candidate Coding Class  |   |   |   | 32 |  |  |  |  |  |

|    | 3.5   | Overvi           | new of LPC and CELP            |   |   |   | 33 |  |  |  |  |  |

|    |       | 3.5.1            | Linear Predictive Coding       |   |   |   | 33 |  |  |  |  |  |

|    |       | 3.5.2            | Code-Excited Linear Prediction |   | - |   | 37 |  |  |  |  |  |

| 4  | Low   | -Powe   | r Speech Coding                                     | 40 |

|----|-------|---------|-----------------------------------------------------|----|

|    | 4.1   | Propos  | sed Architectural and Algorithmic Approach          | 40 |

|    |       | 4.1.1   | Proposed Architecture                               | 40 |

|    |       | 4.1.2   | Analysis of Architectural and Algorithmic Issues    | 43 |

|    |       | 4.1.3   | Summary of Architectural and Algorithmic Techniques | 55 |

|    | 4.2   | VSELI   | P Case Study                                        | 56 |

|    |       | 4.2.1   | Overview of Algorithm                               | 57 |

|    |       | 4.2.2   | Computational Complexity                            | 63 |

|    |       | 4.2.3   | Suitability for Low-Power Implementation            | 65 |

|    |       | 4.2.4   | Parallelization of Algorithm                        | 67 |

|    | 4.3   | Compa   | arative Analysis of LD-CELP Algorithm               | 73 |

|    |       | 4.3.1   | Overview of Algorithm                               | 73 |

|    |       | 4.3.2   | Computational Complexity                            | 76 |

|    |       | 4.3.3   | Suitability for Low-Power Implementation            | 78 |

|    |       | 4.3.4   | Parallelization of Algorithm                        | 79 |

|    | 4.4   | Compa   | arative Analysis of DoD CELP Algorithm              | 80 |

|    |       | 4.4.1   | Overview of Algorithm                               | 80 |

|    |       | 4.4.2   | Computational Complexity                            | 82 |

|    |       | 4.4.3   | Suitability for Low-Power Implementation            | 83 |

|    |       | 4.4.4   | Parallelization of Algorithm                        | 84 |

|    | 4.5   | Conclu  | sions Regarding Low-Power Speech Coding             | 84 |

| 5  | Dire  | ections | for Future Work                                     | 85 |

| 6  | Con   | clusior | ns                                                  | 87 |

| Bi | bliog | raphy   |                                                     | 89 |

# List of Figures

| 2.1  | CMOS Inverter for Power Analysis                                  |

|------|-------------------------------------------------------------------|

| 2.2  | Waveforms for Power Analysis                                      |

| 2.3  | Static versus Dynamic Design Styles                               |

| 2.4  | Dynamic CPL NAND Gate                                             |

| 2.5  | Static CPL NAND Gate                                              |

| 2.6  | CPL NAND Gate with PMOS Level Restorer                            |

| 2.7  | Generic Sequential Processor                                      |

| 2.8  | Generic Parallel Processor                                        |

| 2.9  | Generic Pipelined Processor                                       |

| 3.1  | Human Speech Generation                                           |

| 3.2  | Pitch Signal in Time-Domain                                       |

| 3.3  | Pitch Signal in Frequency-Domain                                  |

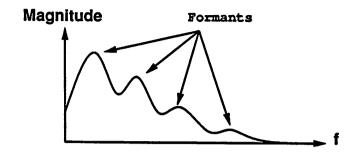

| 3.4  | Spectral Envelope of Speech Signal                                |

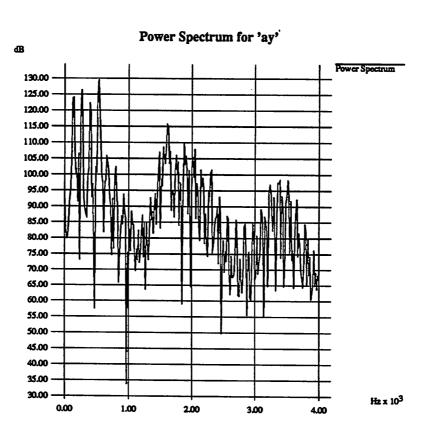

| 3.5  | Power Spectrum of Phoneme $\bar{a}$                               |

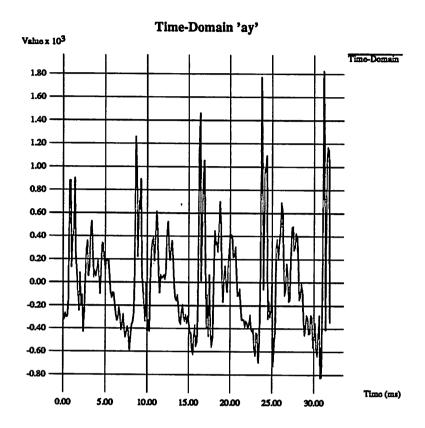

| 3.6  | Time-Domain $\bar{a}$                                             |

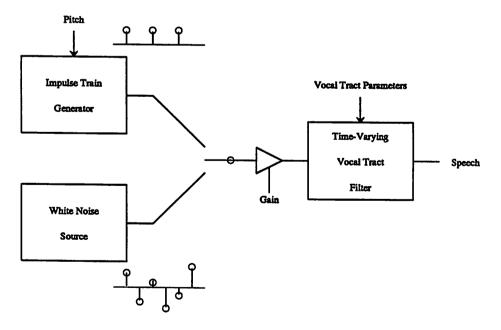

| 3.7  | Simplified Model for Human Speech Generation                      |

| 3.8  | Acoustical Tube Model of Vocal Tract Filter                       |

| 3.9  | Pole-Zero Plot for Vocal Tract Filter                             |

| 3.10 | Coder Complexity versus Quality                                   |

| 3.11 | LPC Analysis Filter                                               |

| 3.12 | LPC Synthesis Filter                                              |

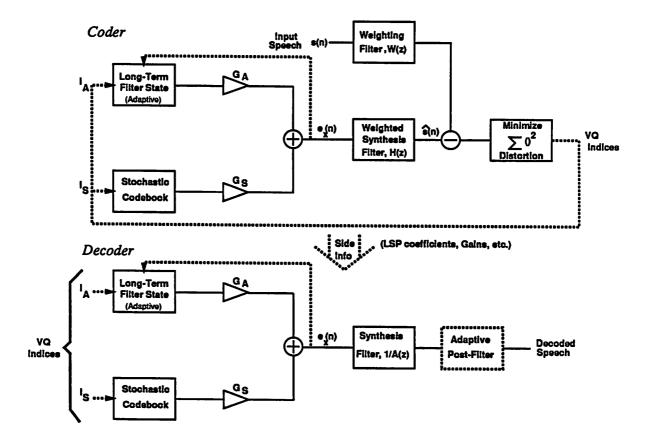

| 3.13 | Simplified CELP Speech Coder/Decoder                              |

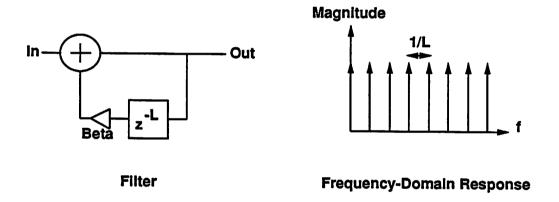

| 3.14 | Long-Term Pitch Filter                                            |

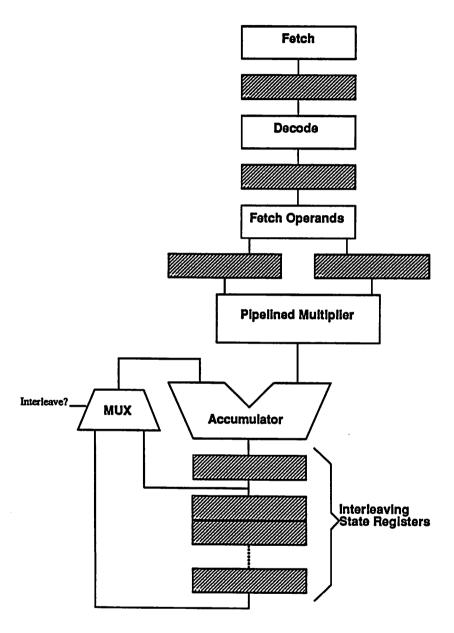

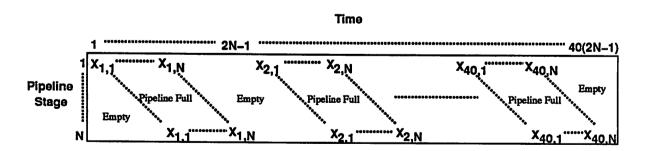

| 4.1  | Pipelined-Interleaved Architecture                                |

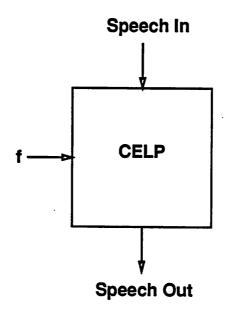

| 4.2  | Sequential CELP Processor                                         |

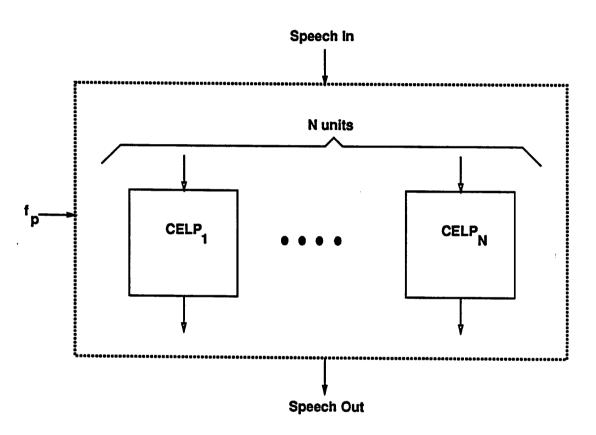

| 4.3  | Parallel CELP Processor                                           |

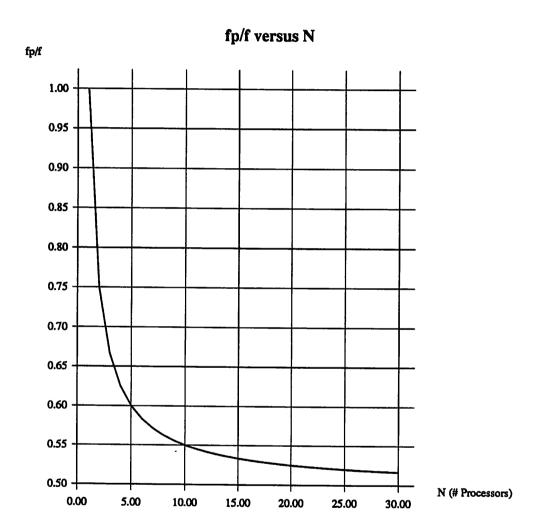

| 4.4  | Effect of Number of Parallel Processors on Operating Frequency 48 |

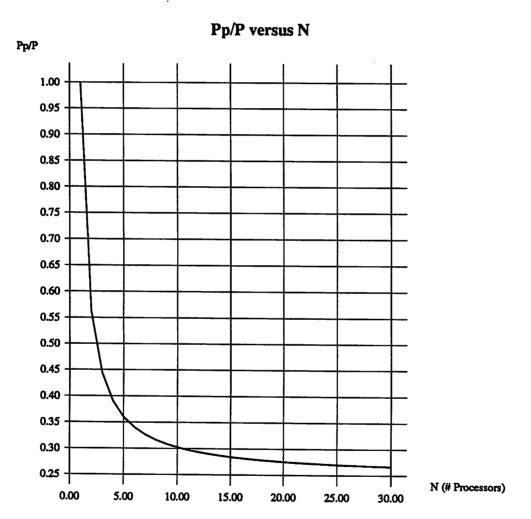

| 4.5  | Effect of Number of Parallel Processors on Power Savings          |

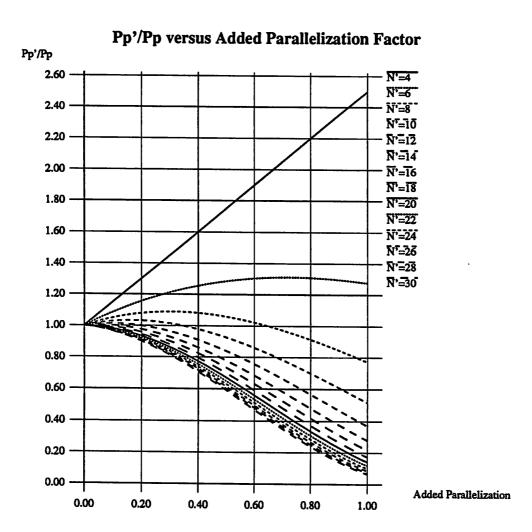

| 4.6  | Effect of Parallelization on Power Savings                        |

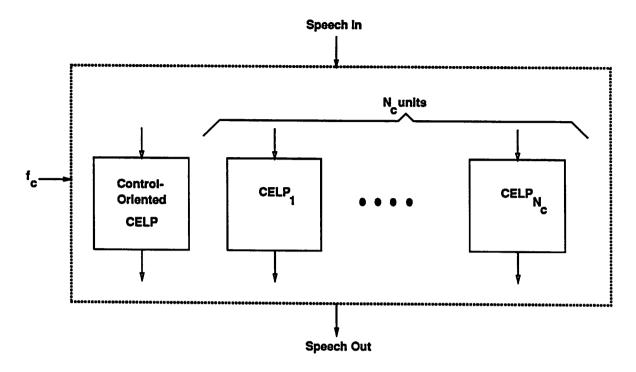

| 4.7  | Co-Processor CELP Architecture                                    |

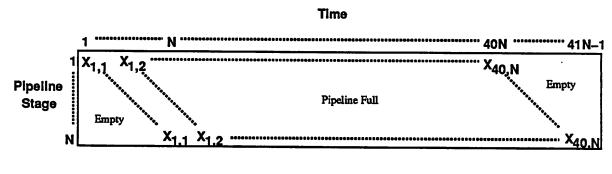

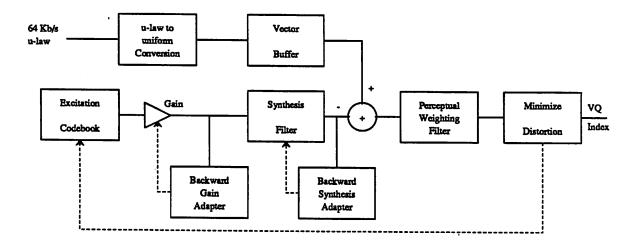

| 4.8  | VSELP Block Diagram                                               |

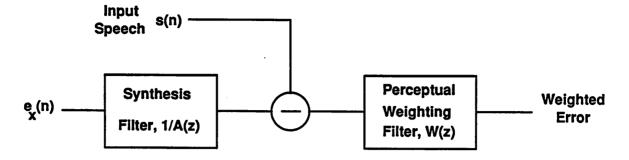

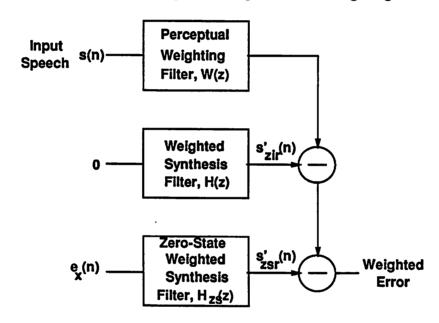

| 4.9  | Perceptual Noise-Weighting                   | 60 |

|------|----------------------------------------------|----|

| 4.10 | Removal of Synthesis Filter Memory Component | 60 |

| 4.11 | Direct-Form Synthesis Filter                 | 70 |

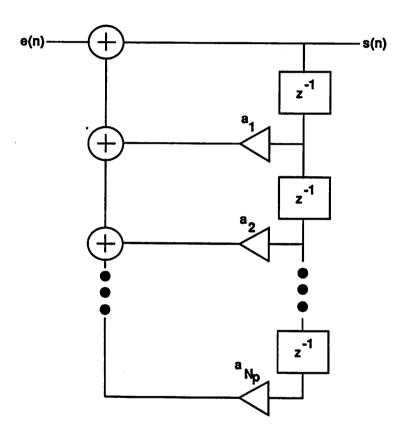

| 4.12 | Synthesis Filter After First Retiming Step   | 71 |

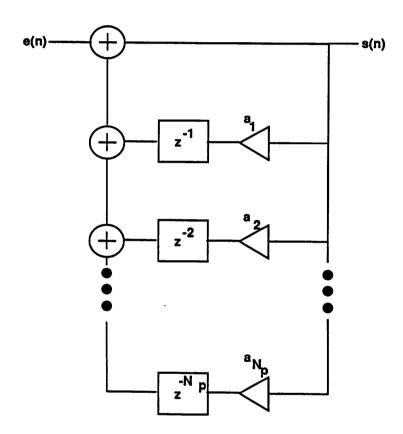

| 4.13 | Synthesis Filter After Second Retiming Step  | 72 |

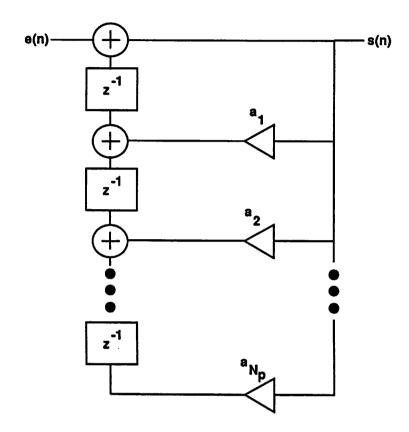

| 4.14 | Direct-Form Pipeline Allocation Schedule     | 72 |

| 4.15 | Restructured Pipeline Allocation Schedule    | 73 |

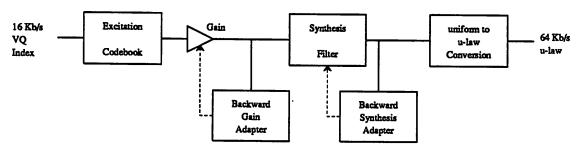

| 4.16 | LD-CELP Speech Coder/Decoder                 | 74 |

| 4.17 | DoD CELP Speech Coder/Decoder                | 80 |

•

# List of Tables

| 4.1  | Complexity of VSELP Coder                      |

|------|------------------------------------------------|

| 4.2  | gprof Breakdown of Dominant VSELP Coder Tasks  |

| 4.3  | Manual Breakdown of Dominant VSELP Coder Tasks |

| 4.4  | Complexity of VSELP Decoder                    |

| 4.5  | Complexity of LD-CELP Coder                    |

| 4.6  | Breakdown of Dominant LD-CELP Coder Tasks      |

| 4.7  | Complexity of LD-CELP Decoder                  |

| 4.8  | Complexity of DoD Coder                        |

| 4.9  | Breakdown of Dominant DoD Coder Tasks          |

| 4.10 | Complexity of DoD Decoder                      |

# Chapter 1

## Overview

#### 1.1 Introduction

Over the past several decades, the topic of speech analysis and processing has been the focus of much research and study. Considering the importance of the spoken word in communications, this is not surprising. Indeed, the progress made in the development of the digital signal processing field has largely been driven by its applications to the speech signal. These applications are wide ranging and include speech recognition, synthesis, encryption, and compression among others. Of course, speech and audio signals are but one form of communication – video is an equally important medium. Recently, the possibility of combining these two capabilities into a single portable, personal communications system (PCS) has stirred a great deal of interest.

The portability requirement, however, raises several important issues. First, this form of personal, wireless communications suggests a cellular environment. In such an environment, communication bandwidth becomes a severe constraint. This has been the case for existing cellular telephone networks, and the situation will only be exacerbated by the addition of full-motion video. Thus, compression of both audio and video channel information will be a key issue.

Furthermore, as with all portable, battery-operated systems, power dissipation will be a critical concern. By minimizing the power consumed by each component of the system, the operating time between recharging sessions can be maximized. One could argue that this could also be accomplished by increasing the storage capacity of the batteries; however, batteries add both mass and volume to a portable system. The weight of the batteries required to power a 25 Watt system for 8 hours is approximately 40 pounds, assuming modern battery technologies. Therefore, it is clear that power conservation is not a trivial concern.

In summary, data compression and low-power operation are two important issues in the development of a portable multi-media terminal. This report will address these issues through a case study of low-power speech coding. Of course, the ideas presented here are not limited to a single application. The speech coding techniques could, for example, be equally well applied to mobile telephony, secure communications, or voice mail. Moreover, the low-power techniques developed in this paper are applicable not only to speech processing, but to virtually any digital signal processing (DSP) application constrained to low-power operation.

#### 1.2 Organization

The contents of this report can be decomposed into several sections. Chapter 2 describes the mechanism of power consumption in CMOS circuits and proposes several strategies for low-power VLSI. Chapter 3 then provides the reader with a brief background on speech processing – coding, in particular. Moreover, it describes the concepts of linear predictive coding (LPC) and code-excited linear prediction (CELP). Chapter 4 relies heavily on the backgrounds built up in the previous chapters. Basically, this chapter combines the notions of low-power VLSI and of speech coding to develop architectural and algorithmic techniques for low-power speech coders. Finally, chapter 5 discusses several possible directions for future work, and chapter 6 summarizes the results of the research.

# Chapter 2

# Low-Power VLSI Systems

### 2.1 Power Consumption in CMOS Circuits

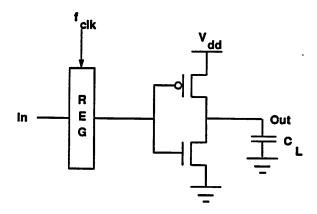

One of the objectives of this report is to develop a methodology for achieving low-power VLSI implementations of digital signal processing algorithms. Therefore, it would be judicious at this point to discuss the mechanics of power consumption in CMOS circuits. Consider the CMOS inverter of figure 2.1. The power consumed when this inverter is in use can be decomposed into three basic components: static power, dynamic power, and short-circuit  $(V_{dd} - V_{ss})$  power. Each of these components will now be analyzed individually.

Ideally, CMOS circuits dissipate no static (DC) power since in the steady state there is no direct path from  $V_{dd}$  to ground. Of course, this scenario can never be realized in practice since in reality the MOS transistor is not a perfect switch. Thus, there will

Figure 2.1: CMOS Inverter for Power Analysis

always be leakage currents and substrate injection currents, which will give rise to a static component of CMOS power dissipation. For a submicron NMOS device with an effective  $\frac{W}{L} = \frac{10\mu m}{0.5\mu m}$ , the substrate injection current is on the order of 1-100  $\mu A$  for a  $V_{dd}$  of 5 V [1]. Since the substrate current reaches its maximum for gate voltages near  $0.4V_{dd}$  and since gate voltages are only transiently in this range as devices switch, the actual power contribution of the substrate injection current is several orders of magnitude below other contributors. Likewise, reverse-bias junction leakage currents are on the order of nanoamps and will have little effect on overall power consumption.

Another component of power dissipation arises from the transient switching behavior of the CMOS device. At some point during the switching transient, both the NMOS and PMOS devices will be turned on. This occurs for gates voltages between  $V_{tn}$  and  $V_{dd} - |V_{tp}|$ . During this time, a short-circuit exists between  $V_{dd}$  and ground and currents are allowed to flow. A detailed analysis of this phenomenon by Veendrick reveals that for traditional CMOS circuits this component is approximately 10% of the dynamic power dissipation of the circuit [2]. Thus, although it can not be neglected, it is certainly not the dominant component of power dissipation in CMOS circuits.

Instead, dynamic power dissipation consumes most of the power used by CMOS circuits. Dynamic power dissipation is the result of charging and discharging parasitic capacitances in the circuit. The situation is modeled in figure 2.1 where the parasitic capacitances are lumped at the output in the load capacitor,  $C_L$ . Assume the inverter has as input and output the waveforms of figure 2.2. The frequency, f, of the input signal corresponds to a clock frequency in figure 2.1 of  $f_{clk} = 2f$ . The total power dissipation of the circuit, then, is given by:

$$P_{dyn} = \frac{1}{T} \int_0^{\frac{T}{2}} I_{dn}(t) V_o(t) dt + \frac{1}{T} \int_{\frac{T}{2}}^T I_{dp}(t) (V_{dd} - V_o(t)) dt$$

(2.1)

Using the fact that  $I_{dn}(t) = C_L \frac{dV_o}{dt}$  and  $I_{dp}(t) = C_L \frac{d(V_{dd} - V_o(t))}{dt}$  we can solve for the power,  $P_{dyn} = C_L V_{dd}^2 f = \frac{1}{2} C_L V_{dd}^2 f_{clk}$ . This is the classical result for dynamic CMOS power consumption. It illustrates that, assuming continual switching, the dynamic power is proportional to the frequency, the capacitive loading, and the square of the supply voltage. In CMOS circuits, this component of power dissipation is by far the most important (accounting for over 90% of the total power dissipation), as illustrated by the previous discussion.

Having derived the expressions for CMOS power consumption, it is interesting to analyze how power consumption is distributed on a VLSI chip. It is important to realize

Figure 2.2: Waveforms for Power Analysis (after Weste)

that not only does the core circuitry consume power, but also the I/O drivers consume a significant amount of power. This is not surprising since I/O capacitances are on the order of tens of picofarads while on-chip capacitances are in the tens of femtofarads. More specifically, for conventional packaging technologies, Bakoglu suggests that pins contribute approximately 13-14 pF of capacitance each (10 pF for the pad and 3-4 pF for the printed circuit board traces) [3]. Since dynamic power is proportional to capacitance, I/O power is clearly a significant portion of overall chip power consumption.

#### 2.2 Strategies for Low-Power VLSI

#### 2.2.1 Packaging

The preceding analysis of power consumption in CMOS circuits can be exploited to yield several techniques for reducing power dissipation. The realization that I/O capacitance at the chip-level can account for as much as 1/4 to 1/2 of the overall system power dissipation suggests that reduction of I/O power is a necessity in multi-chip systems such as the portable communications terminal. For I/O power, the issue, as stated before, is mainly one of packaging technology. If the large capacitances associated with inter-chip I/O were drastically reduced, the I/O component of system power consumption

would be reduced proportionally. One currently evolving method of achieving this goal is the multi-chip module or MCM.

In an MCM, all of the chips comprising a given system are mounted on a single substrate, and the entire module is placed in a single package. Utilizing this technology, inter-chip I/O capacitances are reduced to the same order as on-chip capacitances. This is due not only to the elimination of the highly capacitive PCB trace interconnect, but also to the reduction of on-chip pad driver capacitances due to the minimized off-chip load driving requirements. Thus, utilizing MCM technology, the I/O component of system power consumption can be kept at a minimum, shifting the focus of power optimization from I/O considerations to chip core considerations.

Actually, low-power operation is but one of the advantages of MCM technology. In addition, MCM's with their reduced chip level interconnect lengths and capacitances can significantly reduce system delays resulting in possibly higher clock speeds and correspondingly higher performance levels. Furthermore, this packaging technique raises the effective system integration level several orders of magnitude over existing packaging technologies. For projected submicron technologies, an 8"×10" MCM can be expected to house close to a billion transistors [4]. This will relax current silicon area constraints and allow much needed flexibility in designing low-power architectures such as those discussed in this report.

#### 2.2.2 Design Styles

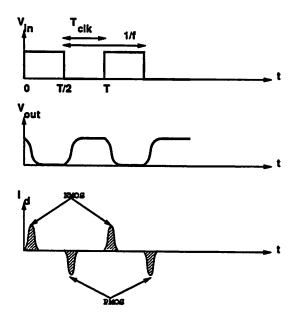

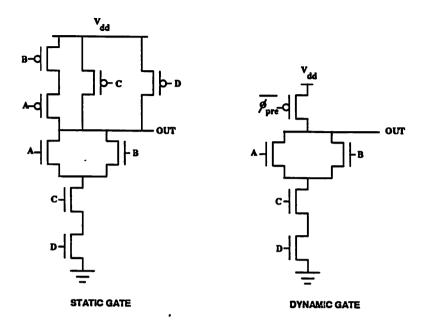

Logic design styles can also influence power consumption in CMOS circuits. At the highest level, the choice of logic styles is between static and dynamic. Historically, dynamic design styles have been touted for their inherent low-power properties. For example, dynamic design styles often have significantly reduced device counts. Figure 2.3 shows an implementation of a complex boolean expression in both static and dynamic design styles. For the dynamic design, the logic evaluation function is fulfilled by the NMOS tree alone, while in the static design both an NMOS and PMOS tree are required for this operation. Since dynamic device counts are drastically reduced, corresponding capacitive loading is also reduced; this, in turn, can lead to power savings.

In addition, dynamic gates don't experience short-circuit current power dissipation. In contrast, whenever static circuits switch, a brief pulse of transient current flows from  $V_{dd}$  to ground, consuming power. Furthermore, dynamic logic nodes are guaranteed to

Figure 2.3: Static and Dynamic Implementations of a Complex Logic Function

have a maximum of one transition per clock cycle. Static gates, unfortunately, do not follow this pattern and can experience a glitching phenomenon whereby output nodes undergo spurious transitions before settling at their final value. This causes excess power dissipation in static gates.

In practice, however, situations can arise that result in significantly increased power dissipation in dynamic circuits. Consider a dynamic gate whose output is low over a large number of clock cycles. During the precharge phase, the output node is charged to the  $V_{dd}$  supply rail. When the gate is evaluated, however, the node is pulled down to ground. This pattern repeats over many clock cycles as long as the output of the gate remains low. Thus, power is consumed during each clock cycle. If this were a static implementation, however, only power due to leakage currents would be consumed since no switching would take place. For certain data patterns, then, static logic can actually result in lower power consumption overall.

Dynamic logic styles have additional drawbacks. For example, although reduced device counts tend to lower circuit capacitances, dynamic gates often require large precharging transistors to meet timing constraints. This, coupled with the fact that every dynamic gate must have at least one precharge transistor, can lead to huge clock line capacitances, which, aside from making reliable clocking difficult, also consume a great deal of power.

Figure 2.4: Dynamic CPL NAND Gate

Also, there is the related issue of clock distribution and skew. As clock rates and die sizes increase, these issues become increasingly important and can significantly limit the utility of dynamic circuits. Of course, similar clocking issues arise in static logic; however, the problem is not nearly as severe as in the dynamic case.

Furthermore, dynamic circuits are more difficult to design. For example, avoiding charge sharing and its associated difficulties requires careful consideration by the designer. As issues such as this arise, design times for dynamic circuits increase and dynamic logic styles become less attractive.

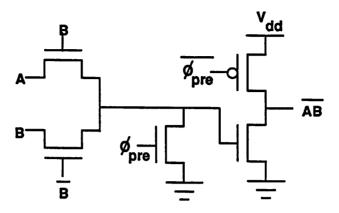

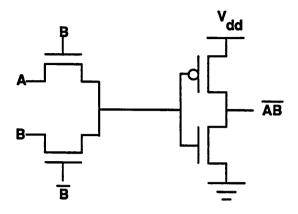

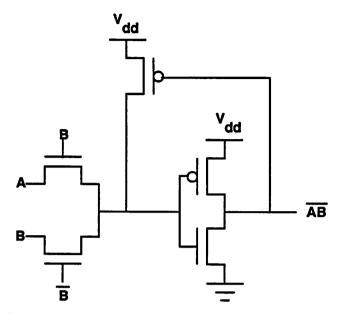

Clearly, dynamic design styles do, however, merit serious consideration in the development of a low-power circuit library. Indeed, adder simulations by Chandrakasan, et. al., [4] demonstrate the low-power possibilities of dynamic circuits. In particular, their findings suggest dynamic complementary pass-gate logic (CPL) [5] as a possible candidate for a low-power design style. A dynamic CPL NAND gate is depicted in figure 2.4. The NMOS pass-transistor network performs the logic evaluation while the succeeding buffer stage drives the fan-out of the gate. An additional clocked NMOS transistor is provided to ensure that the final, inverting NMOS is off during the precharge phase. Note that this "N" stage would be preceded and followed by "P" stages based on PMOS transistors. Thus, the A and B inputs would be precharged low, disabling the pass transistors and allowing evaluation to proceed in a "domino"-like fashion. Clearly, for complex pass-transistor networks, the buffer and precharge transistor overhead becomes less significant; moreover, even if it were not required, a buffer would probably be advisable to ensure adequate load driving capabilities.

Figure 2.5: Static CPL NAND Gate

It is interesting to note, however, that the advantages of dynamic CPL are more a function of the logic style rather than the dynamic circuit style. Figure 2.5 illustrates that the static and dynamic versions differ only in the connection of the PMOS in the buffering inverter and the presence or absence of the clocked NMOS transistor. Therefore, the capacitance of the static circuit is actually less than the dynamic configuration. In fact, since clock routing and loading are now reduced, additional power savings are possible. Of course, this consideration must be balanced with the possibility of glitching and short-circuit power dissipation. Indeed, since the NMOS pass-transistors exhibit a  $V_t$  drop in the transmission of high logic levels, the PMOS buffer devices could remain slightly conducting even for a "high" logic level input. This situation can be remedied with a zero- $V_t$  NMOS pass-transistor or a PMOS level-restorer as illustrated in figure 2.6. Overall, CPL has proven to be a fast, low-power circuit style and deserves consideration in the construction of a low-power CMOS cell library.

#### 2.2.3 Circuit Techniques

In addition to judicious selection of design style, circuit-level techniques can also allow designers to reduce power consumption. One example where custom circuits can provide large gains in power reduction is in clock distribution. Switching power consumed in charging clock lines and transistor gates often dominates chip power consumption. This is especially true for dynamic logic in which each logic gate has at least one clocked transistor, requiring extensive clock distribution. In order to reduce clock line charging power (which is proportional to  $V^2$ ), one can attempt to reduce the voltage swing on large interblock

Figure 2.6: CPL NAND Gate with PMOS Level Restorer

portions of the clock line. This would, of course, require sense amps of some kind at the boundaries of each block to restore full logic levels; however, significant power gains might be possible with such a technique. Similarly, in a multi-chip, low-power system these reduced logic swing techniques could be used at chip boundaries to reduce inter-chip I/O power.

#### 2.2.4 Technology Scaling

Scaling of physical dimensions is another consideration for low-power circuits. Analysis of device scaling is commonly coupled with a treatment of supply voltage scaling. In this report, however, they are treated separately to emphasize the effect of each technique independently on the parameters of interest. Moreover, in attempting full scaling (dimensions and supply), subthreshold conduction limitations prevent supply scaling from proceeding to the same extent as dimensional scaling. The independent scaling analyses account for this situation.

Basically, scaling involves reducing all vertical and horizontal dimensions by a factor, S, greater than one. Thus, transistor widths and lengths are reduced, oxide thicknesses are reduced, depletion region widths are reduced, interconnect widths and thicknesses are reduced, etc. From classical analysis [6], the first order effects of such a scaling on important parameters can be derived. Device loading capacitances, for example, are of the

form,  $C = C_{ox}WL$ . But  $C_{ox} \propto \frac{1}{t_{ox}} \propto S$  and  $W \propto \frac{1}{S}$  as is L. The result is that gate capacitances scale down by the factor S. This bodes well for reduced power consumption since  $P \propto CV_{dd}^2 f$ . So if f and  $V_{dd}$  remain constant, power also sees a reduction of S. The effect of scaling on delays is equally promising. First, notice that current drive increases:  $I \propto C_{ox} \frac{W}{L} \propto S$ . Thus, propagation delays, which are proportional to  $\frac{CV_{dd}}{I}$ , scale down by a factor of  $S^2$ . The power-delay product, then, shrinks by a factor of  $S^3$ .

This discussion, however, ignores many important second order effects. For example, as dimensions scale down, more functionality tends to be placed on a single chip leaving die sizes relatively constant. As a result interconnect lengths don't scale down by the full scaling factor S. In fact, they tend to remain constant. As a result, interconnect capacitance now remains constant rather than scaling down by S. Thus, it begins to dominate gate capacitance terms, which scale down by S. As this occurs, power consumption is no longer reduced by S; instead, it too remains constant. Furthermore, delays are now reduced only linearly, rather than quadratically, with S. Finally, combining these results, the power-delay product sees only a factor of S improvement overall.

Another second order effect is that of velocity saturation. As dimensional scaling continues to submicron dimensions without commensurate scaling of supply voltage, high electric fields develop in device channels. Eventually, carrier mobility is heavily degraded due to increased carrier collisions with the crystal lattice; this, in turn, brings on velocity saturation. The net effect is the reduction of the current drive voltage dependence from a square law to a linear relation. As would be expected, this significant reduction of current drive has an adverse effect on circuit delays. Nevertheless, technology scaling does offer significant advantages for low-power CMOS circuits.

Unfortunately, scaling is not always a viable option. Aside from the drawbacks of interconnect non-scalability and submicron effects, chip designers often don't have complete freedom to arbitrarily scale their fabrication technology. Instead, the capabilities of their fabrication facilities impose limits on minimum lithographic dimensions. For this reason, in order to achieve widespread acceptance, an ideal low-power methodology should not rely solely on technology scaling or specialized processing techniques. Indeed, the methodology should be applicable not only to different technologies, but also to different circuit and logic styles. Of course, whenever possible scaling and circuit techniques should be combined with the high-level methodology to further reduce power consumption; however, the general low-power strategy should not require these tricks. Again, the advantages of scaling and

low-level techniques cannot be overemphasized, but they should not be the sole arena from which the designer can extract power gains.

#### 2.2.5 Supply Voltage Scaling

Having treated dimensional technology scaling, the effects of voltage scaling will now be considered independently. Specifically, consider reducing the supply voltage by a factor,  $S_v$ , greater than one. Since dynamic power consumption is proportional to the square of the supply voltage, power dissipation is reduced in a quadratic fashion with  $S_v$ . This square-law reduction offers a direct and dramatic means of minimizing energy consumption. Without requiring any special circuits or technologies, a factor of two reduction in supply voltage yields a factor of four decrease in power. Furthermore, this power reduction is experienced not only in the chip core, but also for chip I/O (assuming the chip is communicating with other low-voltage components).

This savings does not, however, come without a cost. For as supply voltage is lowered, circuit delays increase. To the first order,  $I_{dd} \propto V_{dd}^2 \propto \frac{1}{S_v^2}$ . Thus, propagation delays, which go as  $\frac{CV_{dd}}{I}$ , will increase linearly with  $S_v$ . In order for the circuit to remain functional, these delay increases cannot go unchecked. Some techniques must be applied, either technological or architectural, in order to compensate for this effect. This is the topic of the next section. First, however, a short discussion of second order effects in supply scaling is in order.

Several important refinements can be added to the classical voltage scaling model. First, the quadratic dependence of current drive on supply voltage is an approximation valid only for supply voltages much larger than the device threshold voltage,  $V_t$ . In reality,  $I \propto (V_{dd} - V_t)^2$  and, unfortunately,  $V_t$  cannot be scaled down indefinitely with supply voltage. Instead, it is limited to approximately 0.6 V, by subthreshold conduction and noise margin considerations. As the supply voltage decreases, the significance of this factor is manifested as an undesirable loss of current drive.

Another, previously mentioned, second order effect is velocity saturation. Since voltage scaling cannot track dimensional scaling beyond  $V_t^{min}$ , it will not prevent high channel fields from eventually developing, causing velocity saturation. Consequently, even under voltage scaling conditions, saturated device currents will begin to drop and propagation delays will increase. This further limits the amount that the voltage supply can be reduced

without incurring unacceptable delay penalties.

#### 2.2.6 Architectures

#### **Parallelism**

In addition to the several low-level strategies presented, certain architectural issues deserve consideration. As stated in the previous section, supply voltage scaling causes linear increases in propagation delays which must be dealt with in order to maintain constant system throughput. Parallel computing techniques are ideal for this objective [4]. In this context, architectural parallelism refers not only to systems with physical hardware duplication, but also to pipelined systems. In general, any technique that increases computational concurrency can be used to compensate for the negative effects of voltage scaling.

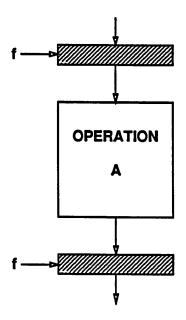

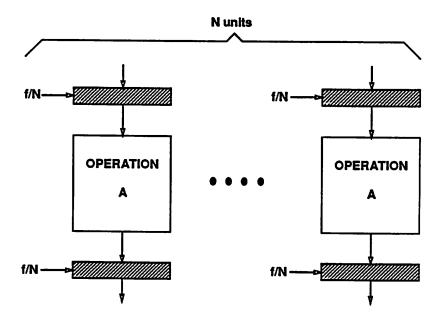

As an example, consider a functional block that performs some complex operation, A, as illustrated in figure 2.7. The registers supplying operands and storing results for A are clocked at a frequency, f. Further assume that algorithmic and data dependency constraints do not prevent concurrency in the calculations performed by A. When the computation of A is parallelized, figure 2.8 results. Basically, the hardware comprising block A has been duplicated N times resulting in N identical processors. Since there are now N processors, a throughput equal to that of sequential processor, A, can be maintained with a clocking frequency N times lower than that of A. That is, although each block will produce a result only 1/Nth as frequently as processor A, there are N such processors producing results. Consequently, identical throughput is maintained.

The key to this architecture's utility as a power saving configuration lies in this factor of N reduction in clocking frequency. In particular, with a clocking frequency of f/N, each individual processor can run N times slower. Since delays vary approximately linearly with voltage supply, this corresponds to a possible factor of N reduction in supply voltage. Examining the dynamic power consumption relative to the single processor configuration, we see that capacitances have increased by a factor of N (due to hardware duplication), while frequency and supply voltage have been reduced by the same factor. Thus, since  $P_{dyn} \propto CV_{dd}^2 f$ , dynamic power consumption is reduced by the square of the concurrency factor, N (i.e.  $P_{dyn} \propto \frac{1}{N^2}$ ).

Parallelism is not, however, the only form of concurrent computation that can be exploited for power reduction - pipelining can be equally interesting. The pipelined case

Figure 2.7: Sequential Processor for Operation A

Figure 2.8: N-way Parallel Processor for Operation A

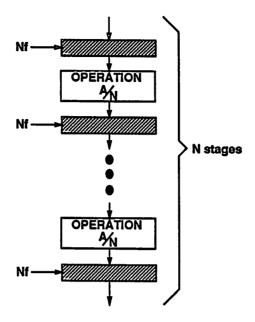

Figure 2.9: N-stage Pipelined Processor for Operation A

is shown in figure 2.9. In this situation, rather than duplicating hardware, concurrency is achieved by inserting pipeline registers, arriving at an N-stage pipelined version of processor A (assuming processor A can be pipelined to this extent). In this implementation, maintaining throughput requires that we maintain clocking frequency, f; however, ignoring the overhead of the pipeline registers, the capacitance, C, also remains constant. The advantage of this configuration is derived from the greatly reduced computational requirements between pipeline registers. Rather than performing the entire computation, A, within one clock cycle, only 1/Nth of A need be calculated per clock cycle. Again, this allows a factor N reduction in supply voltage and, considering the constant C and f terms, the dynamic power consumption is reduced by  $N^2$ . Thus, both concurrency techniques – pipelining and parallelism – result in a first-order quadratic reduction in power consumption.

Bit-serial processing was another architectural style given consideration in this study. Bit-serial processors do, in some sense, exhibit concurrency. Rather than time-domain concurrency, however, they display what can be called spatial concurrency. There is an important distinction to be made between time-domain concurrency and spatial-domain concurrency. Pipelining and parallelism are examples of time-concurrent techniques. In other words, at a given time, computations are occurring concurrently across a large number of spatially distinct processing units. In the case of pipelining, these units are the N stages

of the pipeline, while in the parallel scenario they are the N identical processors. In contrast, spatial concurrency refers to architectures that perform computations using the same piece of hardware (i.e. spatial concurrency) over a large number of clock cycles. This is commonly referred to as time-shared hardware, and bit-serial processing is a prime example.

Unfortunately, this form of processing has no advantages for low-power circuits. Consider, for example, a function, B, that operates on a word of N bits. In bit-serial form, this function would be implemented by a single-bit processor, which would clearly possess 1/Nth the capacitance of the bit-parallel case. Unfortunately, in order to maintain throughput, the bit-serial processor must be clocked at a frequency N times higher than the bit-parallel case. As in the pipelined and parallel scenarios, then, the effects of the capacitive and frequency components in the dynamic power equation cancel out. Unlike, those cases, however, the bit-serial processor cannot operate at a reduced voltage supply. That is, due to the increased clocking frequency, the time allotted for the calculation of a single result bit has not increased over the bit-parallel case; therefore, no  $V_{dd}$  reduction and, subsequently, no power reduction are possible. Clearly then, it is time-concurrent rather than time-sharing architectures that are attractive for low-power systems.

The preceding analysis has considered only the first order effects of parallelism on power consumption. There are second order effects that detract from the power savings achieved by using concurrent hardware. In a pipelined processor, for example, the pipeline registers represent an overhead in both power and area that cannot be ignored. As the pipeline depth increases, the hardware (capacitance) associated with the pipeline registers approaches that of the actual processor stages. At that point, further pipelining becomes unattractive.

Hardware parallelism also has its disadvantages. For instance, complete hardware duplication entails a severe area penalty. In addition, associated with these distributed processors is hardware and interconnect overhead related to signal distribution at the processor inputs and signal merging at the outputs. As in the pipelined case, these contribute to increased power consumption and tend to limit the utility of excessive parallelism. Even before considering this overhead, the area requirements of full parallelism can be a limiting factor; however, the advent of MCM's should help to minimize this concern.

#### **Arithmetic Format**

Another architectural consideration is arithmetic format. High quality, low bit-rate speech coding places severe computational requirements on the datapath of its hardware platform. In particular, squaring and multiply-accumulate (MAC) instructions are quite common (as in many DSP applications). Thus, dynamic range in the datapath becomes an important issue. Among the several arithmetic formats available are fixed-point, floating-point, and block floating-point. Each of these has different implications for low-power performance.

Fixed-point offers the minimum hardware requirements and power consumption, among the three options. Unfortunately, it also suffers the most from dynamic range difficulties. Algorithmic scaling offers some relief from this problem, however, it must be incorporated into the processor  $\mu$ -code and thus has some runtime overhead. Floating-point, in contrast, alleviates the dynamic range issue at the expense of extensive hardware additions. This increased hardware leads to correspondingly higher capacitances and, as a result, higher power consumption. Block floating-point may offer the best compromise between the two techniques. At the expense of a small amount of additional hardware (and power), it accomplishes the scaling process (for the most part) automatically. Thus, it achieves some compromise between dynamic range and hardware overhead.

#### 2.2.7 Algorithms

These architectural considerations suggest several algorithmic criteria for low-power. Although further developed in section 3.3, the key issues are presented now in an introductory fashion.

The technique of scaling supply voltage is bounded not only by threshold voltage considerations, but also by real-time requirements. Specifically, as voltage levels are scaled down, propagation delays increase proportionally. At some point, the requirement for real-time operation sets a limit on supply scaling. In other words, the maximum number of sequential operations that can be executed in one coding cycle relates directly to the operating voltage.

As this relationship suggests, reducing the required number of sequential operations per coding cycle translates directly to a lower supply voltage and, ultimately, to reduced power consumption. Significantly, the number of "sequential" operations and not

the total number of operations per cycle limits power supply reduction. Independent operations may be performed concurrently and, thus, do not serve to increase the time required to complete a given coding cycle. Of course, this assumes that the hardware to efficiently handle this concurrency is in place and, indeed, that was the focus of the previous section.

Parallelizability is but one algorithmic consideration. As suggested previously, suitability for fixed-point or block floating-point implementation can also be important. Again, this is intimately related to the dynamic range issue that can be so troublesome in DSP applications such as speech coding. The issue is not purely one of hardware. Certain algorithms and filter structures are more suitable for fixed-point implementations than others. For example, the auto-regressive lattice synthesis filters associated with many speech coding techniques are highly advantageous for fixed-point implementations. This stems from the property that the tap coefficients (reflection coefficients) for these stable filters are less than one in magnitude. This allows greatly simplified quantization schemes and minimizes fixed-point implementation difficulties. Although not always the structure of choice for various other reasons, the lattice example illustrates that algorithmic considerations can affect power-related issues.

#### 2.2.8 Power Management

At a slightly higher level, well-known power-management techniques can be applied to reduce energy consumption. Specifically, processing blocks need only be clocked and powered when they are performing some computation. During idle periods these processors may be powered down (assuming state information is properly preserved). In this way, large power savings are possible (depending on the utilization level of the particular processing unit).

For speech coding applications, in particular, power-down techniques can provide significant power savings. In most speech coding environments, long periods of relative silence are observed. A speech coder that monitors input energy levels can take advantage of this fact by shutting down during periods of inactivity. Moreover, for a full-duplex (transmitting and receiving) coder, only one of the processes, either the coder or the decoder will be active at a time. This can provide an additional measure of power reduction.

### 2.3 Summary of Low-Power Methodology

To summarize, the proposed low-power methodology involves techniques ranging from the circuit to the architectural level of design. At the highest level, the supply voltage is scaled down from 5 V to some optimum technology-dependent voltage (roughly 1.5 V for the 2  $\mu m$  MOSIS CMOS process)[4]. In order to compensate for linearly increasing circuit delays, some form of concurrent computational technique, such as parallelism or pipelining is employed. The result is a power reduction, which to the first order goes as the square of the supply reduction.

Beyond this, circuit techniques such as reduced clock line and I/O pad voltage swings, with accompanying sense amp circuitry, can be applied to further reduce power consumption. In addition, judicious choice of logic style can allow additional power reduction, as can technology scaling and advanced packaging techniques. Finally, proper selection and optimization of candidate algorithms to achieve maximum concurrency offers equally significant gains in power conservation. Combinations of these schemes, coordinated through an intelligent power management methodology, can help to achieve maximum overall power savings.

Of course, if some of these techniques are unavailable or undesirable for a particular design effort, the voltage scaling alone will provide large power savings. As stated previously, this is one of the advantages of the parallelism technique: no additional circuit or technology tricks are required. They are, however, extremely desirable and should be employed when possible.

For the most part, this methodology is not specific to speech coding. This was one of the key objectives of this research. As a result, the strategies discussed in this report can be applied equally well to a wide range of DSP applications and algorithms.

# Chapter 3

# Speech Coding

The previous chapter presented techniques for achieving low-power VLSI implementations of DSP algorithms. Furthermore, it contained important background material on topics that are of critical concern to low-power circuits. The current chapter provides additional background information, this time on speech processing, that will be central to understanding the detailed analyses of the coding algorithms to be presented in chapter 4.

### 3.1 Speech Processing Background

#### 3.1.1 Human Speech Generation

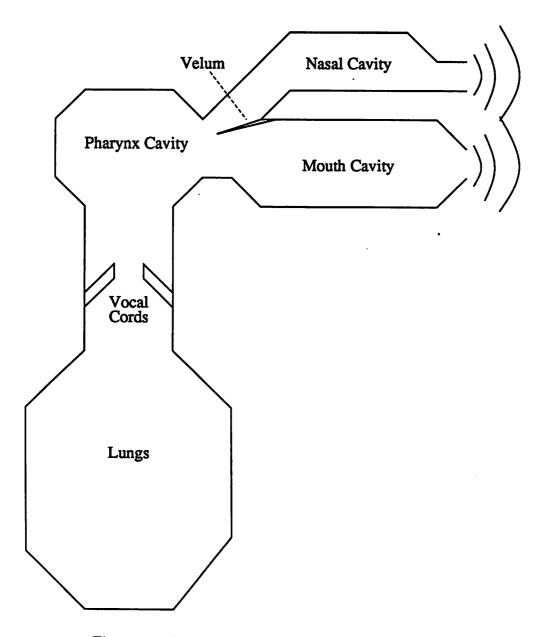

In order to facilitate an understanding of modern speech coding methods, an understanding of the speech signal and the mechanism by which it is generated is essential. Figure 3.1 shows a model of the human speech generation system. During speech production, the diaphragm forces air out of the lungs and into the trachea. This flow of air passes by the vocal cords resulting in one of two possible scenarios. In the first, the vocal cords are tense, and the rush of air from the lungs causes them to vibrate at some pitch frequency, thereby, modulating the flow of air into a series of discrete bursts. This corresponds to a voiced sound such as a vowel. In the second scenario, the vocal cords are relaxed and the air passes by relatively unaffected. This unvoiced mode of speech corresponds to consonants such as s, f, and p.

Continuing through figure 3.1, the stream of air proceeds past the larynx and passes through a series of resonant cavities - the pharynx cavity, the mouth cavity, and the

Figure 3.1: Human Speech Generation (after Flanagan)

nasal cavity, in particular. The flow of air, either modulated or unimpeded, excites these cavities and causes them to resonate. The frequencies of these resonations is determined by the size and shape of the cavities. This, in turn, depends upon the positions of various vocal tract components including the jaw, the velum, the tongue, and the lips. As an example, consider the production of the so-called *nasal* phonemes such as n. During a nasal utterance, the velum allows the unimpeded flow of air into the nasal cavity as well as the mouth. Thus, both cavities respond to the air flow and sound is radiated not only from the lips, but also from the nostrils.

As a further example illustrating the importance of the vocal articulators, consider the generation of the unvoiced consonants s and p. In the production of an s, the velum is closed and the steady flow of air from the lungs directly enters the mouth. Were the lips and tongue positioned so as to open the mouth cavity, the air would pass through and radiate from the lips forming a sound similar to that of an h; however, the formation of an s requires that the tongue be pressed to the roof of the mouth. Thus, the flow of air is impeded and it passes by the tongue and lips as a turbulent stream. This is recognized as the "hissing" quality of the s phoneme. When forming the phoneme p, the lips rather than the tongue impede the air flow. Specifically, the lips cause a brief, but total, closure of the vocal tract allowing a buildup of pressure, which is released as a transient burst as the lips are opened. The result if the "popping" sound characteristic of this phoneme.

The shape of the vocal cavities determines the resonances of the vocal tract filter. These resonant frequencies are called formants and are largely responsible for the character of the speech generated. In other words, for voiced speech, altering the formant frequencies can change the generated phoneme from, say,  $\bar{a}$  to some other voiced phoneme such as  $\bar{e}$ . Thus, the information contained in the formant frequencies is closely related to the particular phoneme uttered. Indeed, extraction of these formants can be (and has been) used for rudimentary speech recognition.

#### 3.1.2 The Speech Waveform

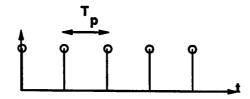

The previous discussion suggests several attributes of the speech waveform. For example, realizing that (voiced) speech generation is excited by the modulated puffs of air passing the vocal cords, a speech signal containing a periodic component at the frequency of the vocal cord vibrations would be expected. In the time-domain, this signal component

Figure 3.2: Pitch Signal in Time-Domain

Figure 3.3: Pitch Signal in Frequency-Domain

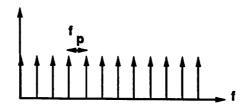

could be thought of as a discrete, periodic series of pulses recurring at an interval referred to as the pitch period,  $T_p$  (see figure 3.2). In the frequency-domain, this corresponds to a power spectrum with components at the pitch frequency,  $f_p$ , and all of its harmonics (see figure 3.3). This pitch-periodic signal is, however, but one component of the overall speech signal.

In addition to the pitch excitation, the response of the vocal tract filter must be considered. This component lends itself most directly to analysis in the frequency-domain. Remember, the effect of the resonant vocal cavities is to introduce formant frequencies into the speech signal. These resonances appear as peaks in the speech power spectrum. In general, three to five formant frequencies can adequately describe the vocal tract frequency response. This number corresponds roughly to the number of resonant cavities present in the human vocal tract. Thus, the cavities of the vocal tract filter contribute a frequency-domain envelope of the form shown in figure 3.4.

Combining excitation and envelope, an actual frequency-domain power spectrum of the voiced phoneme  $\bar{a}$  is shown in figure 3.5. Notice the overall spectral envelope with roughly three formant frequencies representing the response of the vocal tract filter. Furthermore, the periodic fine-structure at the 125 Hz fundamental and its harmonics is the direct contribution of the pitch periodicity of the voiced vowel. In the time-domain (figure 3.6), the periodic pitch excitation is again noticeable at approximately 8 ms (=1/125 Hz) intervals. Each impulse-like pitch excitation is followed by an oscillating response corresponding

Figure 3.4: Spectral Envelope of Speech Signal Due to Vocal Tract Filter

directly to the impulse-response of the vocal tract filter. As this response begins to die out, it is excited anew by the arrival of the next pitch impulse.

Of particular interest to many communications applications is the bandwidth required to adequately represent the speech waveform. As seen in figure 3.5, the power spectrum of the speech signal is largely band-limited to frequencies below 4 Khz. Indeed, the sampling rate for contemporary digital telephone communications networks is 8 Khz, resulting in a maximum representable frequency component of 4 Khz. Telephone network anti-aliasing sending filters, however, further reduce this maximum to approximately 3.6 Khz (-3 dB point). As a matter of common experience, the resulting speech quality is quite satisfactory for most verbal communication purposes. Indeed, the input to the majority of existing speech coders is 8 Khz "toll-quality" speech and, thus, for these coders it represents the ultimate achievable quality for the compressed and decoded speech signal.

#### 3.1.3 A Model for Speech Generation

The characteristics of the speech signal and its production suggest a straight-forward model for human speech generation. The model consists of two components: an excitation source and a vocal tract filter as illustrated in figure 3.7[8]. The excitation source is selected from two possible generators. The first is simply a periodic impulse train which models the voiced speech excitation signal. The unvoiced speech excitation, in contrast, is modeled by a "white"-noise source, which corresponds physically to the turbulent air stream that is characteristic of unvoiced speech.

As suggested in section 3.1.2, the effect of the vocal tract can be simulated by a filter capable of modeling three to five resonant frequencies. Since the shape and size of the vocal cavities vary with time in the production of continuous speech, the vocal tract

Figure 3.5: Power Spectrum of Phoneme  $\bar{a}$

Figure 3.6: Time-Domain  $\bar{a}$

Figure 3.7: Simplified Model for Human Speech Generation (after Rabiner)

Figure 3.8: Acoustical Tube Model of Vocal Tract Filter

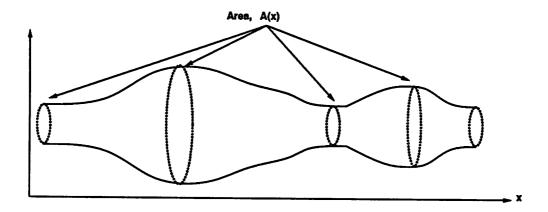

filter model must, of necessity, be time-varying. The detailed nature of this filter can be derived by comparing the vocal tract to a cylindrical acoustical tube of non-uniform cross-sectional area (see figure 3.8). The behavior of such a system has been examined extensively [7, 8]. Using the mass conservation and momentum equations we can derive the theoretical response of the system:

$$-\frac{\partial P}{\partial T} = \frac{\rho v^2}{A(x)} \frac{\partial U}{\partial x}$$

(3.1)

$$-\frac{\partial U}{\partial T} = \frac{A(x)}{\rho} \frac{\partial P}{\partial x}$$

(3.2)

In these equations, x is the distance along the vocal tract, U is the volume-velocity, P is the sound pressure, A(x) is the cross-sectional area at x,  $\rho$  is the density of air, and v is the velocity of sound. These equations can be solved for the approximate form of the vocal tract transfer function, H(z) [8]:

$$|H(z)| \approx \frac{G}{1 - \sum_{k=1}^{N} a_k z^{-i}}$$

(3.3)

where the relationship becomes exact as N goes to infinity.

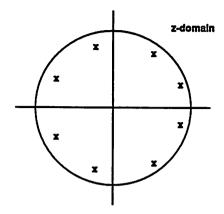

This transfer function has the form of an all-pole filter. Thus, the vocal tract filter can be modeled as a time-varying all-pole filter of order N. The determination of the order, N, relates to the number of formant frequencies to be modeled. Two complex-conjugate poles are required to model a single formant frequency. Therefore, it is not surprising that a ten-pole filter quite effectively models the response of the vocal tract (which is primarily influenced by its first five formants). A pole-zero plot of a vocal tract filter model is shown

Figure 3.9: Pole-Zero Plot for Vocal Tract Filter

in figure 3.9. The spectral envelope produced by this model would be quite similar to that of figure 3.4.

The applicability of the model is, of course, not universal. For example, the model assumes the separability and independence of the excitation source and vocal tract filter. This assumption does not strictly hold, especially in the case of the plosives (p, for example). For most phonemes, however, the condition is sufficiently satisfied and it need not be a point of concern. Another restriction stems from the all-pole nature of the vocal tract model. The all-pole filter models vocal tract resonances well, however, the anti-resonances introduced by the nasal cavity are best modeled by zeros. Very high quality can still be achieved, however, with the classical all-pole vocal tract filter. Furthermore, its relative simplicity with respect to a full pole-zero representation makes the all-pole filter far more useful than the pole-zero model.

## 3.2 Speech Coding Methods

Previous sections have dealt at length with the background information required to understand the speech signal and how it can be modeled. This section now delves further into the issue of speech processing and, specifically, into methods and algorithms for speech coding. Speech coding refers to techniques that, taking the speech signal as input, reduce the amount of information required to describe the waveform.

Consider, for example, a "toll-quality" digital speech waveform. As discussed in section 3.1.2, this corresponds to an analog speech waveform sampled at 8 Khz. Further

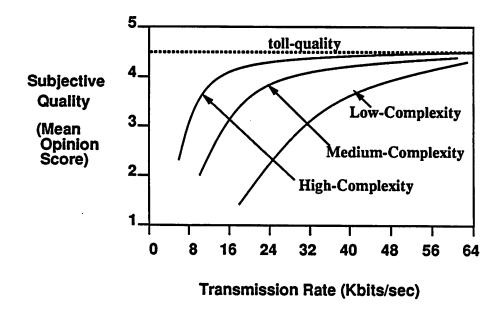

Figure 3.10: Coder Complexity versus Subjective Quality (after Noll)

assume that the speech samples require 8-bits of storage each (corresponding to the American telephony standard 8-bit  $\mu$ -law). For this case, the data bandwidth required to store or transmit the speech signal is 64 Kbits/sec. The purpose of a speech codec (coder/decoder) is to reduce this bandwidth requirement. Taking advantage of redundant information in the speech signal, the coder produces a reduced bandwidth data stream that represents the input speech signal. This channel information is then stored for later decoding or is transmitted directly to the decoder, which reverses the process to retrieve the original speech waveform (or an approximation).

The compression ratios available from contemporary coding techniques vary widely as does the quality of the decoded speech signal. Figure 3.10 shows a plot of subjective speech quality versus transmission rate for coders of varying complexity [9]. In this graph, complexity is defined by a criterion such as the number of multiply-accumulate operations required per input sample. As a point of reference, toll-quality telephony achieves a Mean Opinion Score (MOS) of 4.5 at 64 Kbits/sec.

Basically, coders can be subdivided into two categories: waveform coders and parametric coders. Waveform coders perform time-domain sample-by-sample coding of the speech signal. That is, these coders do not use prior knowledge of the nature of speech in order to reduce the information bandwidth requirements. Pulse Code Modulation (PCM)

is the most common example of this type of coding. PCM is among the simplest coding methods and, as such, it is also among the most prevalent. Quite simply, PCM coding corresponds to sampling the analog waveform and quantizing sample amplitudes. Digital telephony networks employ PCM with logarithmic ( $\mu$ -law) quantizing schemes to achieve their 64 Kbit/sec transmission rates.

A slightly more complicated scheme known as differential pulse code modulation (DPCM) can be employed to reduce the transmission rate for toll-quality speech. In DPCM, differences between successive sample amplitudes, rather than their absolute values, are encoded. Another member of this family, adaptive differential pulse code modulation (ADPCM) performs the identical function with the addition of adaptive quantization. These coders achieve subjective qualities approaching 64 Kbit/sec PCM at bit-rates of 32 Kbits/sec.

Waveform coders are, however, only one class of coders; the second class, parametric coders, are equally important. Parametric speech coders utilize a priori information about the properties of the speech signal to reduce transmission bandwidth. Most parametric speech coders rely on linear predictive coding (LPC) in one form or another to achieve this data reduction. Basically, these coding methods take into consideration the fact that speech is a highly redundant signal. That is to say, speech samples in close proximity are highly correlated. By modeling this correlation, LPC coders can extract a small number of parameters that describe the speech waveform. These then, rather than the quantized signal itself, are transmitted and used to synthesize decoded speech at the receiver. Included in this important class of coders are residual-excited linear predictive coders (RELP), self-excited linear predictive coders (SELP), and code-excited linear predictive coders (CELP). The latter has proven extremely useful for low bit-rate coding and will be discussed later in much more detail.

## 3.3 Criteria for Candidate Algorithms

Clearly then, there is a wide variety of algorithms available for the implementation of speech codecs. Selection of a particular coding style depends on the unique criteria of a particular application. For example, several factors were considered in selecting candidate algorithms for the PCS speech coder. Most importantly, the search was constrained to high subjective-quality coders (approaching toll-quality). Subjective quality, unfortunately,

is difficult to define and to measure. Several different measures exist and they include the Mean Opinion Score (MOS), the Diagnostic Rhyme Test (DRT), and the Diagnostic Acceptability Measure (DAM).

A second requirement – antagonistic to the first – was a compression ratio of 4:1 or more. Beginning with a 64 Kbit/sec toll-quality input stream, this requirement corresponds to a channel stream of 16 Kbits/sec or less. Furthermore, channel streams of 9.6 Kbits/sec or less were even more desirable if high quality could be maintained. Unfortunately, as figure 3.10 demonstrates, the combination of high quality and low bit-rates dictates the use of high-complexity coders. Though unfortunate from an implementation standpoint, the high-complexity of the candidate coding algorithms does provide a forum for thoroughly testing the proposed low-power strategies.

Related to coder complexity is the concept of encoding delay. Encoding delay describes the length of the waveform segment that must be analyzed in order to utilize waveform redundancies to achieve compression. Thus, encoding delay is directly related to memory storage requirements, which is one measure of implementation complexity.

Another issue related to encoding delay is that of real-time operation. Long coder-decoder delays can be quite a hindrance to real-time communication. Assuming appropriate echo control, however, total end-to-end delays on the order of 100-200 ms are acceptable. Implied in this discussion is the requirement that the codec hardware operate in real-time. For some systems, such as voice-mail, where speech is stored rather than decoded immediately, a real-time codec is not a necessity; however, the main application for this speech coder is a real-time communication system. This places some restrictions on coder complexity since there is a limit to the number of operations per sample that can be implemented in real-time.

An additional criterion for the candidate algorithms was suitability for low-power implementation. As shown in the preceding sections, this corresponds, in some sense, to suitability for parallel implementation. The highly parallel nature of the proposed architecture is most suited to an algorithm with a good deal of inherent concurrency. Remember, for a parallel architecture, it is not the total number of operations per sample that dictates the real-time requirements, but rather the total number of sequential operations per sample.

Another condition related to low-power operation is the suitability of the algorithm for fixed-point or block floating-point implementation. As stated in section 2.2.6, full-scale floating-point arithmetic is extremely costly in terms of power. It is, therefore, desirable

to implement the codec on a fixed-point or block floating-point processor, if possible. Unfortunately, fixed-point quantization and dynamic range issues can be extremely important in determining overall coding quality. Moreover, algorithm designers rarely delve into such analyses when defining their algorithm; instead, they assume floating point platforms such as commercially available DSP chips (i.e. AT&T DSP32c).

A final desirable property for the candidate algorithms is compatibility with existing coding standards. Of course, this is by far the least critical concern; however, in order to promote maximum utility of the speech coder, compatibility with some well-accepted standard is a desirable situation.

## 3.4 Selection of Candidate Coding Class

The prerequisites for the candidate coding algorithms are numerous. In general, the CELP class of coders, however, meets these requirements admirably. Actually, the high quality at low bit-rates criterion in itself narrows the field quite significantly. At bit-rates at and below 16 Kbits/sec, waveform coders are severely disadvantaged and yield very low quality speech. In this realm, parametric LPC-based coders begin to demonstrate their coding capabilities. Straight LPC coding, however, although intelligible at low bit-rates, can not be considered "high quality." The decoded speech has an unmistakable "synthesized" character that we are trying to avoid. Unlike straight LPC, however, CELP performs very well at bit-rates down to 4.8 Kbits/sec. Thus, the high quality, low bit-rate requirements alone were enough to suggest a CELP coding scheme.

The third criterion, minimization of the encoding delay, is a difficult problem for high quality, low bit-rate speech. Inherently, achieving high quality at low bit-rates requires that the coder make use of speech redundancies; however, this requires the coder to build a history of the input speech waveform, which can then be analyzed for correlations. This implies a coding delay of at least a frame (approximately 20 ms). Furthermore, channel delays can themselves be on the order of 100 ms. Fortunately, however, with adequate echo control, CELP encoding delays are not a hindrance to real-time communication.

Real-time considerations have long been another drawback for CELP coders. CELP coders are based upon an analysis-by-synthesis methodology. In other words, several candidate speech waveforms are synthesized, and the parameters corresponding to least distorted synthesized signal are transmitted to the decoder. Such a methodology is, clearly, computa-

tionally intensive. To some extent, however, this is the price that must be paid for very high quality speech coding. Furthermore, the heavy computational requirements will provide an extreme test of the low-power techniques espoused in this report.

Suitability for low-power implementation was an additional prerequisite. For low-power, parallel architectures, this criterion is equivalent to requiring a highly concurrent algorithm. CELP coders meet this requirement admirably. Their analysis-by-synthesis approach requires the synthesis of numerous independent speech waveforms. For the classic CELP coder, these synthesis operations can be performed concurrently. Since this "codebook search" traditionally embodies the majority of the algorithmic complexity, CELP is well-suited for low-power implementation.

Aside from concurrency, similarity to more general DSP algorithms is another desirable quality. Again, the main component of the CELP algorithm is the synthesis of several candidate speech waveforms. This synthesis is performed by a linear, time-varying all-pole filter. This multiply-accumulate intensive operation is present in many, if not all, DSP algorithms. Thus, optimizing a low-power architecture based upon this operation will go a long way towards defining a more general-purpose low-power DSP architecture.

All of these considerations led us to restrict candidate algorithms to the CELP family of coders. From this class, three algorithms were selected as candidates; they were compared on the basis of all the previous criteria. In addition, suitability for fixed-point or block floating-point implementation was evaluated, as was the issue of compatibility with existing systems and standards. The three algorithms are Motorola's 8.0 Kbit/sec VSELP algorithm [10], the Department of Defense's (DoD) 4.8/9.6 Kbit/sec CELP algorithm [11], and AT&T's 16 Kbit/sec LD-CELP algorithm [12]. The three coders are very high quality, all achieving Mean Opinion Scores greater than 4.0 (4.5 corresponds to toll-quality). Since they all meet the high quality coding criterion, it was not considered in final algorithm selection.

## 3.5 Overview of LPC and CELP

## 3.5.1 Linear Predictive Coding

Before delving into an analysis of these three algorithms, an explanation of the concept of linear prediction and, specifically, code-excited linear prediction is desirable.

The use of linear prediction in speech coding dates back to the late 1960's [13] and is based on an extremely simple concept. In traditional LPC, bandwidth compression is achieved by utilizing the inherent correlation present in the speech signal. Basically, a small set of parameters containing information such as the pitch of the input speech and the coefficients of the vocal tract filter are extracted from a frame of input speech. These parameters are then transmitted to the decoder and used to resynthesize a time-domain approximation to the original speech.

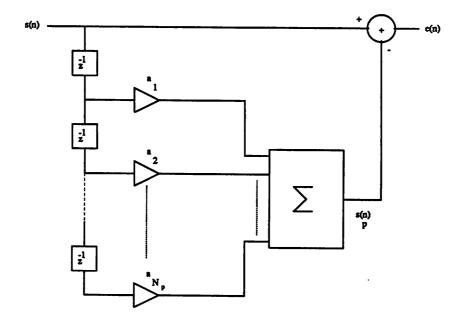

The method is based on the concept of linear prediction. This notion suggests that speech can be modeled as an auto-regressive (AR) process. In other words, it assumes that a sample of speech can be represented as a linear combination of  $N_p$  previous speech samples, where  $N_p$  is the prediction order. Expressed mathematically,

$$s_p(n) = a_1 s(n-1) + a_2 s(n-2) + \dots + a_{N_p} s(n-N_p)$$

(3.4)

where  $s_p(n)$  is the predicted value of the sample s(n). The next step is to define an error signal,

$$e(n) = s(n) - s_p(n) \tag{3.5}$$

By appropriate selection of the LPC coefficients,  $a_i$ , it is, of course, possible to make the error signal identically zero for any particular sample, s(n). If this were done, however, no information reduction would be possible since new LPC coefficients would have to be transmitted for every sample. The goal, then, is to optimize the LPC coefficients over a wide range of, say,  $N_A$  input samples, where  $N_A$  is the analysis interval. This optimization is accomplished by minimizing the energy contained in the error signal over the analysis interval. Defining the energy,

$$E = \sum_{n=0}^{N_A - 1} e^2(n) \tag{3.6}$$

To minimize energy with respect to the LPC coefficients we set its partial derivatives to zero:

$$\frac{\partial E}{\partial a_i} = 0 \qquad \text{for } i = 1, \dots, N_p \tag{3.7}$$

This results in a system of  $N_p$  equations with  $N_p$  unknowns. The equations are known as the autocorrelation normal equations and in matrix form are given by

$$[R(i-k)][a_i] = [R(k)]$$

for  $i, k = 1, ..., N_p$  (3.8)

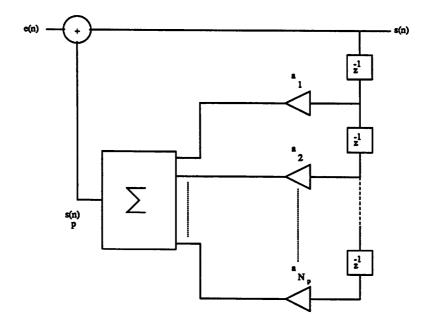

Figure 3.11: LPC Analysis Filter

where R(k) is the short-term autocorrelation function,

$$R(k) = \sum_{n=0}^{N_A - 1} s(n)s(n - k)$$

(3.9)

In general, solving such a system of equations would be a difficult task; however, the autocorrelation matrix, [R(i-k)], has some useful properties. First, it's symmetric; this reduces not only computational requirements, but also storage requirements since the matrix is uniquely determined by its upper triangular component. Furthermore, the matrix is Toeplitz (the elements on each diagonal are equal). For Toeplitz matrices, a particularly nice method known as the Levinson-Durbin recursion exists for solving system 3.8.

Notice that the previous derivation inherently depends on the stationarity of the input speech signal. Although the speech signal is not stationary in general, short segments of speech can be approximated as stationary. This sets an upper bound on the size of the analysis interval and requires that the LPC coefficients be updated regularly.

Using the coefficients defined by the normal equations, we can consider two interesting filter configurations. The first is the LPC analysis filter depicted in figure 3.11. This filter is simply a realization of equations 3.4 and 3.5 and is given in the z-domain by

$$A(z) = 1 - \sum_{i=1}^{N_p} a_i z^{-i}$$

(3.10)

Since the purpose of LPC analysis is to fully describe the correlation in the input signal, the optimal output of the analysis filter would be white noise (i.e. a signal with no correlation between its samples). For such a signal, each new sample gives new information about the stochastic process. For that reason, it is called an innovations process [14]. The innovations process wastes no energy describing redundant (correlated) information. For this ideal scenario, the power spectrum of the input speech waveform is completely described by the LPC coefficients, and these coefficients would be all that was required at the receiver to synthesize the decoded speech.

Actually, Wiener filter theory demonstrates that for large enough prediction orders,  $N_p$ , the residual signal, e(n), will, indeed, be white. Computational as well as stationarity considerations, however, limit the the prediction order. In practice, a prediction order of ten is quite common. Assuming this value for the prediction order, we can study the actual form of the residual signal, e(n). While a tenth order predictor can remove the short-term correlations due to the vocal tract response following a pitch excitation, it cannot predict the long-term pitch correlations present in the input speech. Therefore, for voiced speech, we expect e(n) to closely resemble an impulse train, with period equal to the pitch period, emersed in low-energy white noise. For unvoiced speech, there is no long-term pitch correlation, and we expect e(n) to be nearly white.

Considering the inverse of the analysis filter (the synthesis filter) will give us further insight into the situation. The synthesis filter depicted in figure 3.12 can be derived from equations 3.4 and 3.5 in the z-domain is given by

$$\frac{1}{A(z)} = \frac{S(z)}{E(z)} = \frac{1}{1 - \sum_{i=1}^{N_p} a_i z^{-i}}$$

(3.11)

Notice that the form of  $\frac{1}{A(z)}$  is that of an all-pole filter. In the figure, the residual, e(n), is used to excite the all-pole synthesis filter,  $\frac{1}{A(z)}$ , to produce the original input speech. Ideally, if e(n) as well as the LPC coefficients were available at the decoder, the input speech could be reproduced exactly; however, in order to reduce transmission requirements we can take advantage of a priori knowledge of the form of the residual, e(n). In the voiced case, we can approximate e(n) at the decoder by an impulse train and, thus, only the pitch period need be transmitted to the decoder. For the unvoiced case, e(n) is approximately white, and a white noise generator at the decoder can be used to excite the synthesis filter.

It is of interest that the preceding discussion has provided a justification for the original speech generation model of section 3.1.3. Using that model as a guide, we see that

Figure 3.12: LPC Synthesis Filter

the residual signal, e(n), can be thought of as the excitation source in the model. Moreover, the time-varying all-pole vocal tract filter is implemented by  $\frac{1}{A(z)}$ . This realization also justifies the choice of ten as the prediction order since this value corresponds to two complex-conjugate poles for each of five formants.

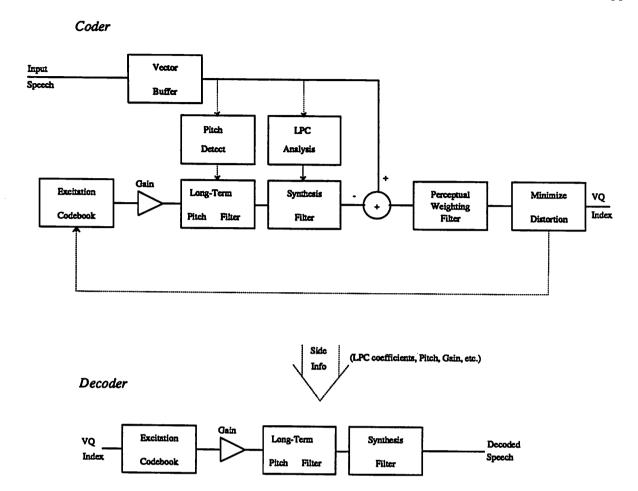

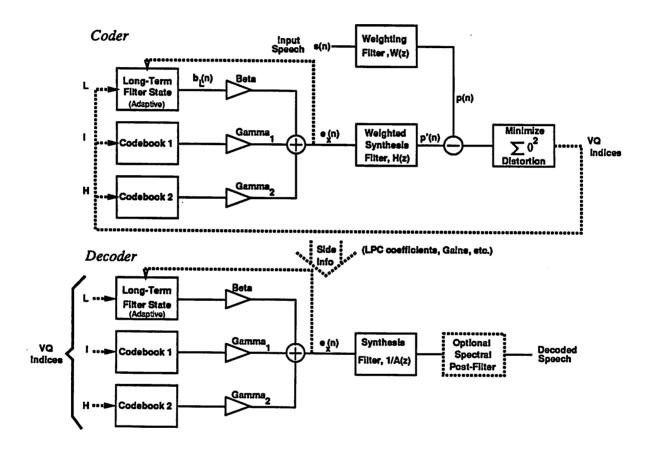

#### 3.5.2 Code-Excited Linear Prediction

Ideally, we would like to excite the synthesis filter in the decoder with the actual residual signal, e(n). Code-Excited Linear Prediction (CELP) is a variation of LPC that attempts to achieve this goal. The CELP concept is similar to LPC with the addition that a vector quantized version of the excitation, e(n), is transmitted to the decoder and is then used to excite the synthesis filter there (see figure 3.13) [15]. The vector quantization process is achieved through an analysis-by-synthesis approach. Specifically, a codebook of vector quantized excitation signals is kept in both the coder and decoder. In the coder, each possible excitation in the codebook is passed through an LPC synthesis filter and the synthesized signal is compared to the input speech. The codevector that produces a synthesized speech segment that is perceptually closest to the input speech is selected, and an index to this vector quantized version of e(n) is transmitted along with the LPC coefficients to the decoder. In the decoder, this excitation is selected out of an identical