#### Vector Processor Caches\*

Jeffrey D. Gee Alan Jay Smith

Computer Science Division University of California Berkeley, CA 94720

#### ABSTRACT

Vector processors have typically used vector registers, interleaved memory, and pipelined access to data to provide sufficient memory system performance. Caches have been used mainly for instructions, while data references are usually uncached, presumably partially because of the belief that there is insufficient data locality in vector workloads. In this study we use memory address traces from Cray X-MP and Ardent Titan machines to examine both reference locality and cache performance in a vector processing environment. Many of the Titan traces in particular are from real vectorized applications which reference large amounts of data. We have found that vector references contain somewhat less temporal locality, but large amounts of spatial locality compared to instruction and scalar references. Cache miss ratios are found to be comparable to those measured and published previously for various non-vectorized workloads. We provide analyses of trace behavior with regard to parameters of interest to cache designers. Calculations based on our measured miss ratios indicate that caches will improve average access times, which in turn can be expected to translate into significant improvements in machine performance.

October 21, 1992

<sup>\*</sup> The material presented here is based on research supported in part by the National Science Foundation under grants MIP-8713274 and MIP-9116578, by NASA under consortium agreement NCA2-128, by the State of California under the MICRO program, and by Philips Laboratories/Signetics, the International Business Machines Corporation, Digital Equipment Corporation, the Intel Corporation, Mitsubishi Electric Company and Sun Microsystems,

## 1. Introduction

Caches are small, high speed memories which improve performance by reducing memory access time from tens of processor cycles to at most a few processor cycles. Caches are effective because of the *principle of locality*, which states that over small periods of time, programs tend to cluster their references to a small subset of the address space. *Temporal locality* implies that data currently in use will likely be used again in the near future (i.e. program loops and local variables). *Spatial locality* implies that data near recently referenced data is also likely to be used (i.e. instructions, array data and stack data).

Most commercial vector processors do not fully utilize caches in their memory hierarchies. Vector processors from Cray, Hitachi, Fujitsu, and NEC use caches only as high speed instruction buffers [Eoya88, Lazo88, Lube85]. The IBM 3090 VF [Tuck86] and Alliant FX-8 [Abu86] are among the few machines which cache vector references. The IBM 3090, however, is a commercial mainframe with cache memory. The add-on Vector Facility simply shares the common memory interface with the general purpose processor. The Alliant FX-8 is a vector multiprocessor which requires caches to support the memory bandwidth requirements of its eight processors.

One reason for the lack of data caches in most vector processors is the (incorrect) assumption that there is little locality in vector workloads. We will show that sufficient locality exists in these workloads to well justify the use of caches. Furthermore, current technology allows the implementation of much larger caches compared to the cache sizes available when current supercomputers were developed. Caches of a megabyte or more may reasonably contain the working sets of real vector applications.

Caches have also been avoided because it has been possible to obtain good performance through careful programming. By overlapping data access with useful computation and using long vectors to minimize the effect of large memory latencies, programs can be coded to run well on supercomputers. Nevertheless, there is the cost in programmer time to tune programs on vector machines, which follows what we believe is the obsolete paradigm of expending human time rather than improving the machine hardware or software. We also point out that coding around memory latencies is becoming increasingly difficult as memory latencies continue to increase [Neve89]. By improving locality in vector applications [McKe69, Triv77] and using vector caches to speed access to data, it may be possible to obtain higher performance levels with less programmer effort.

This research makes extensive use of trace-driven simulation to explore the feasibility of using caches in vector processors. We drive cache models with a large number of vector traces, including many from real production applications running on Ardent Titan machines. Our results indicate that caches can significantly improve the performance of a vector processor. Vector references contain large amounts of spatial locality and significant temporal locality. Miss ratios are in the same range as miss ratios for scalar machines, and are especially low for the large cache sizes possible with current technology. Vector caches reduce average access times by large amounts, which should translate into improved execution rates.

The remainder of this paper is organized as follows. Section 2 provides some background information and summarizes prior research on vector processor caches. Section 3 describes our methodology and examines the address traces used in this study. The bulk of our work is contained in Sections 4 and 5, in which we evaluate the locality present in the traces and analyze cache miss ratios across a wide range of cache parameters. Section 6 uses these miss ratios to estimate the performance effect of a vector cache, and compares these estimates to detailed timing simulations carried out in a separate effort [Gee92]. Section 7 presents our conclusions.

#### 2. Background

### 2.1. Caches and Vector Processors

Very few commercial vector machines cache vector references. One such machine is the IBM 3090 VF [Tuck86], which caches vector references in a 64 Kbyte cache with a 128-byte block size and 4-way associativity. The cache is a write-back cache with LRU replacement and a data bandwidth of one 64-bit word per processor cycle. The single-ported cache is shared between the 3090 general purpose unit and the Vector Facility. The Alliant FX/8 multiprocessor [Abu86] also caches vector references in a shared, 128 Kbyte cache. The FX/8 consists of eight processors, each capable of 12 Mflops peak execution rate, connected to the shared cache via a crossbar switch. The cache is direct-mapped, with four-way interleaving and a peak bandwidth of 47 million words per second.

The fastest supercomputers only cache instructions, or at most scalar data references. Cray machines contain four to eight instruction buffers to store program code fragments currently in use. Cray 1 processors contain four 128-byte buffers; Cray X-MP and Y-MP processors contain four 256-byte buffers; Cray 2 processors contain eight 128-byte buffers. The Cray-2 also has a 128 Kbyte programmable local memory which can hold scalar as well as vector data currently in use. This local memory is not a cache, and its performance hinges on the ability of the compiler or programmer to keep frequently used data resident. The Hitachi S-810/20, Fujitsu VP-200, and NEC SX-2 contain 256 Kbyte, 64 Kbyte, and 64 Kbyte caches for instruction and scalar references respectively [Lazo88]. Successors to those Japanese machines continue to avoid using caches for vector references [Neve89].

Personal supercomputer and minisupercomputers such as the Ardent Titan [Died88], Stardent ST3000, and Convex C-240 [Chas88] use caches to improve integer or scalar operations, but have no cache for vector operations. The Ardent Titan consists of a commercial microprocessor (the MIPS R2000) performing integer operations, with a custom floating-point vector unit capable of delivering 16 Mflops peak performance. A Titan processor has 16 Kbytes of instruction and 16 Kbytes of data cache for MIPS scalar references. The Stardent ST3000, the successor to the Ardent Titan, runs at twice the clock speed of the Titan and contains 32 Kbyte instruction and scalar data caches. The Convex C-240 multiprocessor supports up to four 50-Mflop processors which execute a Cray-like instruction set. Each processor has 8 Kbytes of instruction cache and 4 Kbytes of data cache for scalar data references.

### 2.2. Previous Work

Although caches for vector data are currently not used in many supercomputers, continuing improvements in processor speed relative to memory speed have led to renewed interest. Several studies have recently looked at vector cache performance by measuring cache miss ratios using traces from vectorized applications. A few studies have also looked at the more important issue of processor performance with a vector cache. This section summarizes these earlier efforts, all of which tend to indicate that vector caches perform reasonably well. Results from our research supplement and extend the previous work.

Clark and Wilson [Clar86] measured cache miss ratios for an IBM 3090 VF running both scalar and vectorized versions of a benchmark set. The 3090 has a 64 Kbyte cache, with a 128 byte block size and a set size of four. Clark and Wilson found that vectorized versions of a program have higher cache miss rates, because vectorized programs execute and reference fewer instructions. The absolute number of cache misses was fairly constant.

So and Zecca [So88a,So88b] and Callahan and Porterfield [Call90] measured miss ratios for scientific programs running on IBM vector machines. Both studies started from a baseline cache organization and selectively varied parameters such as cache size, block size, and associativity. So and Zecca simulated cache sizes up to 2 Mbytes, while Callahan and Porterfield simulated cache sizes up to 256 Kbytes. Miss ratios were found to be approximately 5% or less for caches larger than 64 Kbytes using large block sizes (i.e. 64-128 bytes). Callahan and Porterfield estimated processor performance with a 32 Kbyte data cache with a four-byte block size, and found that approximately one-third of total execution time is spent waiting for cache misses. Those authors suggest that compilation techniques can be used to reduce this waiting time, although it is possible that larger caches with larger blocks would be as effective, and potentially more useful given the large size of typical vector applications.

Abu-Sufah and Malony [Abu86] timed kernels of varying vector length on the Alliant FX/8 to evaluate the performance effect of its 64 Kbyte data cache. Caching vectors was found to improve performance significantly, as programs executing on a uniprocessor system ran 1.4 to 2.3 times faster when vector data fits into the cache. In an eight-processor system, observed speedups from caching vectors are even larger, because the cache alleviates to a large extent the bottleneck at shared main memory.

Our research extends earlier work by first providing a detailed evaluation of the spatial and temporal locality within the reference stream of a vector processor. This analysis provides useful insight as to the potential benefit of vector caches. We then measure cache miss ratios over a much wider range of cache parameters, as compared to earlier efforts. These miss ratios are in turn used to estimate the performance effect of a vector cache. Our estimates show that very large caches can improve execution speed by a factor of two when memory is slow (e.g. 50 processor cycles). Studies which have previously looked at machine performance [Abu86, Call90] examined cache sizes (32-64 Kbytes) which are considerably smaller than the cache sizes that can be obtained with current technology. Our performance estimates are also validated against results from an accurate timing simulator of a vector cache machine [Gee92].

### 3. Methodology and Trace Characteristics

This research makes extensive use of *trace-driven simulation*. Trace-driven simulation involves the recording, via either hardware or software means, of the sequence of memory addresses referenced by a program. These addresses are later used as input to a cache simulator.

We have collected two sets of vectorized traces, one from programs running on a Cray X-MP, and another from programs running on an Ardent Titan. Most of the applications traced on the Cray are small programs such as the Livermore Loops and NAS Kernels. These programs are designed more for evaluating processor pipelines rather than large vector caches. We have other Cray traces from scalar UNIX applications, also not typical of large vectorized workloads. The Ardent Titan traces are more representative of true memory reference behavior, as they were gathered from large real production applications. The Titan traces are also quite long (20 million references), enabling us to more thoroughly evaluate the large caches that we simulate.

The Cray X-MP address traces were collected by a modified Cray Research Inc. simulator of Cray machines [Cast87]. In this case, the simulator was configured to simulate the X-MP and was also run on an X-MP. The simulator was modified to record reference addresses into a trace file while simulating X-MP execution. The traces come from both vectorizable and non-vectorizable benchmarks. Traces from vector benchmarks include four of the NAS Kernels [Bail85] and four of the Livermore Loops [McMa86]. The NAS Kernels are specifically designed to evaluate vector processor performance, while the Livermore Loops are Fortran

computations frequently used at the Lawrence Livermore National Laboratory. The remaining traces were collected from the UNIX utilities *diff*, *grep*, and *qsort*, and the *dhrystone*, *linpack*, and *whetstone* benchmarks. None of the Cray benchmarks references very much address space. As mentioned earlier, the vectorized kernels are designed to represent computational rather than memory reference behavior.

The Cray traces include all instruction, scalar data, and vector data references. Data references access eight-byte quantities, although references involving Cray 24-bit address registers use only the low three bytes of an eight-byte word. Instruction fetches reference two-byte instruction parcels, with an instruction being either one or two parcels long. Separate trace records are generated for each parcel of a two-parcel instruction. Each benchmark was traced for up to one million instruction executions.

The Ardent Titan is a graphics supercomputer which combines the scalar performance of a MIPS R2000 processor with a custom floating point unit (FPU) which executes scalar and vector floating-point operations. The FPU has a peak performance of 16 Mflops, and is fully pipelined with chaining support, vector register storage for 8K 64-bit words, and three memory access pipelines. A Titan can be configured with up to four processor boards, where each board contains a 16 MHz R2000 and an 8 MHz FPU.

The Titan traces were collected by using an Ardent *postloader* (similar to the MIPS *pixie* tool) to instrument object code. Calls to tracing routines were inserted in front of each load, store, and branch in the original object code. The tracing routines are implemented in Unix System V shared libraries, which are attached to the code at runtime. When the calls to the tracing routines are inserted, care is taken to ensure that instruction addresses passed to the tracer are the same as in the original, unmodified code. While it is working, the postloader maintains original addresses for each basic block. Calls to tracing routines pass these original addresses as parameters, along with the number of instructions in the basic block. Data reference addresses are unaffected by the postloader. Traces include instruction and scalar references made by the MIPS R2000, as well as scalar and vector references made by the FPU. The FPU can also perform scatter/gather references, which are seen as a sequence of scalar references. MIPS instruction and data references are four bytes wide, while FPU data references are four or eight bytes wide, depending on the floating-point operation precision.

The Ardent benchmarks, all of which are in Fortran, are listed in Table 1. Three (*bmk1*, *bmk11a*, and *bmk21b*) come from the Los Alamos benchmark set [Grif84]. Although these codes are self-contained applications, and not just program kernels, they are smaller and somewhat less "real" than the other programs.

|           | Ardent Benchmarks                               |

|-----------|-------------------------------------------------|

| Benchmark | Description                                     |

| ampac     | molecular orbital package                       |

| arc3d     | 3-D fluid flow using finite difference analysis |

| bmk1      | monte carlo simulation                          |

| bmk11a    | particle in a cell                              |

| bmk21b    | photon transport                                |

| born      | molecular mechanics minimization                |

| flo82     | airfoil flow analysis using Euler equations     |

| lapack    | 1000x1000 linear equation solver (BLAS level 3) |

| mopac     | molecular orbital package                       |

| simple    | hydrodynamic and thermal behavior of fluids     |

| wake      | calculates free wake of rotor                   |

Table 1: Ardent Benchmarks

The other programs are real production applications used for benchmarking at Ardent Computer, and come from areas such as computational chemistry, computational fluid dynamics and linear analysis. While not as large as programs routinely run on Cray machines, the Ardent programs are large enough to stress the memory system of the Titan, and are very similar *qualitatively* to the types of programs run on Crays. Thus, results observed on the Ardent programs should apply directly to Cray applications, provided we scale our results to correspond to the larger problem sizes.

Table 2 lists memory reference and address space characteristics of our traces. The memory reference counts were measured using two techniques:

- (1) Each architectural memory reference is counted as one access, irrespective of whether it references a one, two, four, or eight-byte quantity. These reference counts, being *unnor-malized* to the word size of the machine, are more representative of the machine architecture rather than the machine implementation.

- (2) Certain program references are merged into one or split into two accesses, depending on the nominal word size of the machine. This corresponds more to how data is actually referenced. For the Cray, with a word size of eight bytes, consecutive two-byte instruction parcels in the same basic block are packed into a single eight-byte word reference. For the Ardent Titan, with a word size of four bytes, each double precision data reference is split into two single precision references. These are referred to as *normalized* reference counts.

In Table 2, *unnormalized* instruction fetch percentages are highest for the Cray scalar workload and smallest for the highly vectorized kernels in the Cray vector workload. Cray instruction fetch percentages are reduced significantly once the counts are normalized to word size. Table 2 also lists the fraction of data references that are vectorized, which ranges from a low 10 percent in the Cray scalar workload to over 80 percent in the Cray vector workload. Average basic block size ranges from 17 to 25 instructions, corresponding to branch taken frequencies of 4 to 6 percent. Prior studies have measured branch taken frequencies of 7% and 6% for IBM 370 and CDC 6400 scientific workloads [Lee84] and 10% in a MIPS floating point workload [Perl89]. The fraction of taken branches is much larger in non-scientific workloads, and ranges from 10 to nearly 30 percent [Lee84, Perl89].

Table 2 also shows workload averages from [Smit85], including data from a VAX workload of ten integer C programs, an IBM 370 workload of three FORTRAN scientific applications, and an IBM 360/91 workload consisting of four mixed applications. All results from [Smit85] are normalized to machine word size, and thus are best compared to our normalized statistics. The VAX and IBM 370 workloads assume a constant four-byte reference width, while the 360/91 workload assumes a constant eight-byte reference width.

Normalized averages for the Ardent workload agree quite well with the workloads from [Smit85]. In the Cray vector workload, instruction fetch percentages are much lower because the highly vectorized kernels require fewer instructions to execute the application. In the Cray scalar workload, the ratio of data reads to writes is only one-to-one, much lower than the typical two-to-one ratio. This is possible because Cray machines provide programmer-visible *backup scalar registers* which buffer data between primary scalar registers and main memory. Transfers between these backup registers and main memory are carried out in block mode, thus equalizing the ratio of reads to writes.

Table 2 also shows that the Cray traces are quite small, as none references much more than 128 Kbytes of memory space. In comparison, the Ardent traces average over one megabyte of referenced space, and many of the Ardent programs have not even reached their full size by the end of the trace.

| 4          | Unne     | Unnormalized Ref | 3d Refere | erence Stats |       | ION      | malized  | Normalized Reference Stats | ce Stats |       |        | Addr | Address Space Size | s Size |       | Basic Bl | Basic Block Size |

|------------|----------|------------------|-----------|--------------|-------|----------|----------|----------------------------|----------|-------|--------|------|--------------------|--------|-------|----------|------------------|

| Prog       | Refs     | if%              | rd%       | wt%          | vect% | Refs     | if%      | rd%                        | wt%      | vect% | kbytes | if%  | sclr%              | vect%  | shrd% | Instr    | Bytes            |

|            |          |                  |           |              |       |          | Cray Sc. | Tray Scalar Benchmark      | chmarks  |       |        |      |                    |        |       |          |                  |

| diff       | 1398418  | 88.0             | 5.9       | 6.1          | З     | 524145   | 68.1     | 15.7                       | 16.1     | 2     | 60.9   | 13.1 | 84.6               | 0.9    | 0.0   | 14.01    | 34.50            |

| dry        | 1650467  | 79.1             | 10.8      | 10.1         | 16    | 708229   | 51.2     | 25.2                       | 23.6     | 16    | 15.4   | 39.4 | 48.5               | 7.4    | 4.7   | 21.79    | 58.86            |

| grep       | 1250849  | 91.6             | 4.8       | 3.6          | 0     | 429150   | 75.4     | 13.9                       | 10.6     | 0     | 23.9   | 42.2 | 51.3               | 4.1    | 2.3   | 20.02    | 45.87            |

| lin        | 1299384  | 79.0             | 10.8      | 10.2         | 16    | 559291   | 51.2     | 25.2                       | 23.7     | 15    | 47.4   | 57.4 | 31.1               | 7.4    | 4.1   | 19.16    | 47.10            |

| qsort      | 1351702  | 86.5             | 6.3       | 7.2          | 8     | 498116   | 63.5     | 17.0                       | 19.5     | ×     | 25.6   | 17.3 | 70.3               | 6.3    | 6.1   | 38.11    | 89.16            |

| whets      | 528524   | 84.1             | 8.6       | 7.3          | з     | 209165   | 59.9     | 21.6                       | 18.6     | ю     | 38.5   | 63.6 | 29.3               | 2.7    | 4.4   | 18.01    | 45.93            |

|            |          |                  |           |              |       |          | Cray Ve  | ray Vector Ben             | chmarks  |       |        |      |                    |        |       |          |                  |

| loops14    | 1653620  | 69.7             | 15.0      | 15.4         | 45    | 812275   | 38.2     | 30.6                       | 31.2     | 45    | 117.8  | 18.0 | 25.5               | 15.0   | 41.5  | 18.86    | 52.33            |

| loops16    | 2150136  | 80.1             | 15.4      | 4.5          | 0     | 934442   | 54.1     | 35.6                       | 10.3     | 0     | 44.4   | 47.9 | 31.3               | 12.4   | 8.4   | 12.19    | 37.24            |

| loops21    | 1316361  | 57.8             | 27.1      | 15.2         | 84    | 757861   | 26.7     | 47.0                       | 26.3     | 84    | 64.4   | 33.9 | 20.7               | 6.7    | 38.7  | 62.22    | 148.38           |

| loops8     | 2384954  | 27.3             | 51.5      | 21.2         | 96    | 1902983  | 8.8      | 64.6                       | 26.6     | 96    | 98.0   | 22.8 | 63.7               | 2.0    | 11.4  | 44.83    | 108.44           |

| nas1       | 1356365  | 47.2             | 41.1      | 11.7         | 89    | 884391   | 19.1     | 63.0                       | 17.9     | 89    | 45.2   | 46.5 | 34.5               | 6.7    | 12.3  | 50.39    | 117.18           |

| nas2       | 901095   | 65.1             | 18.1      | 16.7         | 70    | 469120   | 33.1     | 34.8                       | 32.1     | 71    | 46.0   | 51.7 | 36.0               | 4.2    | 8.1   | 41.42    | 102.56           |

| nas5       | 660936   | 68.2             | 20.3      | 11.5         | 71    | 334603   | 37.1     | 40.2                       | 22.8     | 70    | 56.9   | 43.5 | 24.2               | 15.3   | 17.0  | 24.98    | 61.48            |

| nas7       | 2531979  | 30.2             | 50.6      | 19.1         | 96    | 1968210  | 10.2     | 65.2                       | 24.5     | 96    | 139.0  | 16.5 | 8.5                | 29.0   | 46.1  | 78.15    | 190.39           |

|            |          |                  |           |              |       |          | Arder    | ut Bench                   | marks    |       |        |      |                    |        |       |          |                  |

| ampac      | 2000001  | 76.7             | 15.5      | 7.9          | 0     | 21647268 | 70.8     | 19.9                       | 9.3      | 0     | 498.0  | 17.1 | 82.8               | 0.0    | 0.0   | 19.59    | 78.37            |

| arc3d      | 2000001  | 58.6             | 28.9      | 12.6         | 60    | 20110071 | 58.3     | 29.1                       | 12.6     | 60    | 1882.5 | 7.6  | 3.7                | 48.1   | 40.5  | 23.98    | 95.92            |

| bmk1       | 2000005  | 71.1             | 20.3      | 8.6          | 39    | 20000171 | 71.1     | 20.3                       | 8.6      | 39    | 119.5  | 9.2  | 1.5                | 88.4   | 1.0   | 13.19    | 52.77            |

| bmk11a     | 2000005  | 53.7             | 26.2      | 17.0         | 78    | 27191793 | 39.5     | 34.2                       | 21.8     | 80    | 367.5  | 2.9  | 0.3                | 66.7   | 30.2  | 14.02    | 56.10            |

| bmk21b     | 2000002  | 85.7             | 9.1       | 5.2          | 0     | 22033529 | T.T.     | 14.3                       | 7.9      | 0     | 72.2   | 25.7 | 55.2               | 13.2   | 6.0   | 16.69    | 66.76            |

| born       | 2000001  | 76.4             | 9.9       | 13.7         | 0     | 20027535 | 76.3     | 10.1                       | 13.7     | 0     | 4152.9 | 0.7  | 99.3               | 0.0    | 0.0   | 7.41     | 29.63            |

| flo82      | 2000003  | 72.5             | 18.9      | 8.7          | 57    | 20599516 | 70.3     | 21.0                       | 8.6      | 52    | 281.3  | 36.1 | 25.8               | 24.4   | 13.8  | 22.83    | 91.31            |

| lapack     | 2000002  | 75.8             | 15.7      | 8.7          | 35    | 22278263 | 68.0     | 19.2                       | 12.8     | 47    | 4461.8 | 0.1  | 0.1                | 0.2    | 9.66  | 17.34    | 69.34            |

| mopac      | 14907709 | 78.1             | 13.1      | 8.8          | 11    | 16113545 | 72.3     | 13.5                       | 11.2     | 18    | 779.6  | 16.1 | 35.4               | 38.0   | 10.6  | 16.77    | 67.10            |

| simple     | 2000001  | 58.2             | 31.5      | 10.4         | 74    | 27092792 | 42.9     | 43.7                       | 13.4     | 80    | 242.9  | 24.1 | 3.3                | 47.3   | 25.4  | 22.97    | 91.87            |

| wake       | 2000001  | 70.6             | 17.9      | 11.2         | 40    | 20325378 | 69.4     | 18.6                       | 11.6     | 39    | 225.0  | 22.6 | 8.2                | 53.0   | 16.2  | 13.95    | 55.82            |

|            |          |                  |           |              |       |          | Work     | load Ave                   | rages    |       |        |      |                    |        |       |          |                  |

| Cray sclr  | 1246557  | 84.5             | 7.9       | 7.6          | 10    | 488016   | 60.5     | 20.2                       | 19.3     | 10    | 36.3   | 37.3 | 55.3               | 4.1    | 3.0   | 20.22    | 49.32            |

| Cray vect  | 1619430  | 51.9             | 33.2      | 14.8         | 81    | 1007985  | 22.8     | 53.4                       | 23.8     | 81    | 76.5   | 29.3 | 29.0               | 13.6   | 28.1  | 25.46    | 66.60            |

| Ardent     | 19537067 | 68.3             | 19.9      | 11.8         | 50    | 21583623 | 63.8     | 23.4                       | 12.3     | 49    | 1189.4 | 4.9  | 38.4               | 14.3   | 42.4  | 16.98    | 67.92            |

| VAX        | ı        | ī                | ī         | ı            | ı     | 250000   | 57.3     | 26.6                       | 16.1     | 0     | 22.5   | 26.3 | 73.7               | ı      | ,     | NA       | NA               |

| IBM 370    | ı        | ı                | ı         | ı            | ı     | 250000   | 57.8     | 30.2                       | 12.0     | 0     | 66.8   | 32.5 | 67.5               | ı      | ı     | NA       | NA               |

| IBM 360/91 | I        | T                | T         | Т            | 1     | 250000   | 66.4     | 23.2                       | 10.4     | 0     | 27.7   | 37.9 | 62.1               | I      | 1     | NA       | NA               |

|            |          |                  |           |              |       |          |          |                            |          |       |        |      |                    |        |       |          |                  |

Reference percentages are listed for instructions (if%), data reads (rd%), and data writes (wt%). The percentage of data references that are carried out in vector mode is also given (vect%). The total number of kbytes referenced within each trace is listed, as well as the percentage of bytes touched by instructions (if%), by scalar-only data references (sclr%), by vector-only data references (vect%), and by both scalar and vector data references (shrd%). Average basic block size is listed both by instructions and by bytes. Table 2: Unnormalized and normalized breakdown of memory references as well as the amount of referenced address space in the traces.

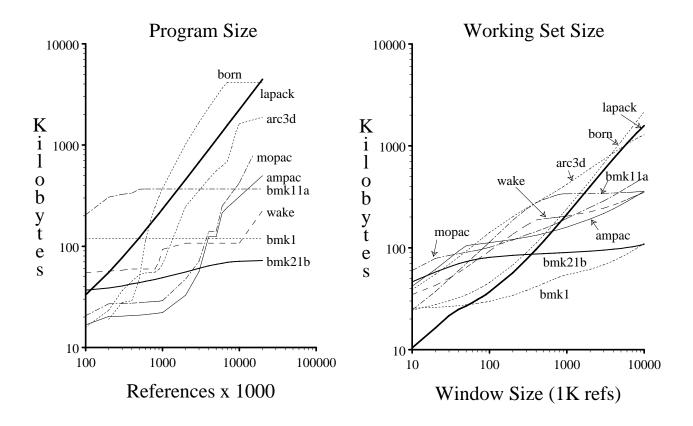

**Figure 1**: Ardent program sizes as a function of time (top) and working set sizes as a function of the window size parameter (bottom).

Figure 1 displays the cumulative address space size referenced as a function of time for various Ardent programs. Programs such as *born*, *bmk1*, *bmk11a*, and *bmk21b* appear to have reached maximum size by the end of the trace, while *arc3d*, *ampac*, *lapack*, *mopac*, and *wake* continue to reference new data. Working set sizes in the same figure increase with window size, but remain for the most part below 500 kilobytes for window sizes as large as 10 million references.

Tables 3 and 4 list the vector lengths and strides observed in all of the the traces containing vector references. Averages and distributions are provided for individual traces and for all traces collected on a given machine. In this context, vector lengths represent the length of individual vector load and store instructions, which is constrained to some maximum number (64 in the Cray X-MP, 32 in the Ardent Titan). Actual vector lengths coded in the applications may even be larger, but such vectors are processed in strips. Vector strides are the distances (in words) between memory addresses of successive vector elements; vectors of unit stride are contiguous. Geometric as well as linear averages are listed for strides, as the presence of only a few large strides can greatly skew linear averages.

|           |         | •       | Vector Len  | gths in the | e Cray T | Traces |      |      |              |

|-----------|---------|---------|-------------|-------------|----------|--------|------|------|--------------|

| 1         | loop14  | loop16  | loop21      | loop8       | nas1     | nas2   | nas5 | nas7 | All Programs |

| length    | %       | %       | %           | %           | %        | %      | %    | %    | %            |

| 3         | 2.1     | 45.3    | -           | -           | -        | -      | 1.8  | -    | 0.2          |

| 5         | -       | 22.1    | -           | -           | -        | -      | 2.3  | -    | 0.1          |

| 7         | -       | 10.5    | -           | -           | -        | -      | 2.0  | -    | 0.1          |

| 8         | -       | -       | -           | -           | -        | 73.6   | 1.8  | -    | 10.8         |

| 16        | -       | -       | -           | -           | -        | 24.9   | 1.5  | -    | 3.7          |

| 19        | -       | -       | -           | -           | -        | -      | 19.6 | -    | 0.8          |

| 20        | -       | -       | -           | -           | -        | -      | 3.4  | -    | 0.1          |

| 25        | -       | -       | 99.2        | -           | -        | -      | 2.3  | -    | 12.5         |

| 32        | -       | -       | -           | -           | 98.2     | -      | 3.5  | 91.6 | 43.9         |

| 35        | -       | -       | -           | 49.3        | -        | -      | 3.3  | -    | 11.3         |

| 41        | 5.6     | -       | -           | -           | -        | -      | -    | -    | 0.1          |

| 64        | 90.1    | 9.3     | -           | 49.8        | -        | -      | -    | 7.7  | 16.1         |

| averages  | 60      | 11      | 25          | 49          | 32       | 10     | 24   | 34   | 33           |

|           |         |         | Vector Stri | ides in the | Cray T   | races  |      |      |              |

| stride    | loops14 | loops16 | loops21     | loops8      | nas1     | nas2   | nas5 | nas7 | All Programs |

| stride    | %       | %       | %           | %           | %        | %      | %    | %    | %            |

| 1         | 99.8    | 90.7    | 0.7         | 15.4        | 99.6     | 17.7   | 18.9 | 8.3  | 24.9         |

| 2         | -       | -       | -           | -           | -        | 61.5   | 5.7  | -    | 8.9          |

| 5         | -       | -       | -           | 84.6        | -        | -      | -    | -    | 18.5         |

| 8         | 0.2     | 9.3     | -           | -           | 0.4      | 0.4    | 1.3  | 0.2  | 0.2          |

| 16        | -       | -       | -           | -           | -        | 20.4   | -    | -    | 2.9          |

| 25        | -       | -       | 99.2        | -           | -        | -      | -    | -    | 12.0         |

| 32        | -       | -       | -           | -           | -        | -      | -    | 91.6 | 29.4         |

| 40        | -       | -       | -           | -           | -        | -      | 74.2 | -    | 3.0          |

| lin. avg. | 1.0     | 1.7     | 24.8        | 4.4         | 1.0      | 4.7    | 30.1 | 29.4 | 15.5         |

| geo. avg. | 1.0     | 1.2     | 24.4        | 3.9         | 1.0      | 2.7    | 16.5 | 24.0 | 7.1          |

Table 3: Vector lengths and strides in the Cray traces.

The Cray benchmarks tend to operate on only a few different vector lengths, with the exception of *nas5*. Cray vector lengths are also short for the most part, averaging less than half the maximum vector length on the X-MP. The average Cray stride is quite large due to large values in *loops21*, *nas5*, and *nas7*, but geometric averages are lower due to short strides in *loops14*, *loops16*, and *nas1*. Geometric and linear averages for *individual* Cray traces are approximately equal, as strides within a Cray kernel are fairly uniform.

Average vector lengths in the Ardent traces are close to the maximum vector length on the Titan. Ardent strides, in comparison to Cray strides, are less uniform. Ardent linear averages are larger than Cray linear averages, but this is due more to the presence of outlying values rather than to poorer locality in the Ardent programs. Since the Ardent programs are real applications, they are presumably more representative of the relevant workload.

|           |       | V     | ector Leng  | ths in the | e Ardent 7 | Traces |      |              |

|-----------|-------|-------|-------------|------------|------------|--------|------|--------------|

| length    | arc3d | bmk1  | bmk11a      | flo82      | lapack     | simple | wake | All Programs |

| _         | %     | %     | %           | %          | %          | %      | %    | %            |

| 2         | -     | -     | -           | 5.7        | -          | -      | -    | 1.1          |

| 4         | -     | -     | -           | 13.7       | -          | -      | -    | 2.7          |

| 8         | -     | -     | -           | 30.3       | 3.1        | -      | -    | 6.1          |

| 9         | -     | -     | -           | 3.7        | -          | 42.4   | -    | 11.5         |

| 10        | -     | -     | -           | 4.5        | -          | -      | -    | 0.9          |

| 15        | -     | -     | -           | -          | -          | -      | 3.8  | 0.3          |

| 20        | -     | 98.6  | -           | 14.1       | -          | -      | -    | 12.6         |

| 21        | -     | -     | -           | 3.2        | -          | -      | -    | 0.6          |

| 26        | 5.5   | -     | -           | -          | -          | -      | -    | 0.9          |

| 28        | 55.0  | -     | -           | -          | -          | -      | -    | 8.7          |

| 29        | 10.1  | -     | -           | -          | -          | -      | -    | 1.6          |

| 30        | 26.1  | -     | -           | -          | -          | -      | -    | 4.1          |

| 31        | -     | -     | -           | -          | -          | 46.2   | 11.9 | 12.6         |

| 32        | -     | -     | 100.0       | 20.6       | 96.9       | 11.2   | 83.9 | 36.3         |

| averages  | 28    | 20    | 32          | 15         | 31         | 22     | 31   | 24           |

| _         |       |       | Vector Stri | des in th  | e Ardent ' | Fraces |      |              |

| stride    | arc3d | bmk1  | bmk11a      | flo82      | lapack     | simple | wake | All Programs |

| suide     | %     | %     | %           | %          | %          | %      | %    | %            |

| 1         | 98.6  | 50.4  | 100.0       | 74.5       | 100.0      | 55.4   | 99.5 | 78.8         |

| 2         | -     | -     | -           | 0.8        | -          | -      | -    | 0.2          |

| 12        | -     | -     | -           | -          | -          | 21.2   | -    | 5.3          |

| 20        | -     | 24.8  | -           | -          | -          | -      | -    | 2.5          |

| 30        | 0.9   | -     | -           | -          | -          | -      | -    | 0.1          |

| 34        | -     | -     | -           | -          | -          | 23.4   | -    | 5.9          |

| 48        | -     | -     | -           | -          | -          | -      | 0.2  | 0.0          |

| 90        | 0.5   | -     | -           | -          | -          | -      | -    | 0.0          |

| 385       | -     | -     | -           | 3.9        | -          | -      | -    | 0.8          |

| 386       | -     | -     | -           | 20.7       | -          | -      | -    | 4.0          |

| 961       | -     | -     | -           | -          | -          | -      | 0.3  | 0.0          |

| 1351      | -     | 24.7  | -           | -          | -          | -      | -    | 2.4          |

| lin. avg. | 1.9   | 339.8 | 1.0         | 95.6       | 1.0        | 11.1   | 4.4  | 55.4         |

| geo. avg. | 1.1   | 12.5  | 1.0         | 4.4        | 1.0        | 3.9    | 1.0  | 2.4          |

**Table 4**: Vector lengths and strides in the Ardent traces.

## 4. Locality in Vectorized Applications

This section directly examines the temporal and spatial locality present in the address traces. We characterize temporal locality by using *reference counts* and *reference intervals*, which respectively represent (a) the number of references to an address, and (b) the times between references to an address. Applications containing temporal locality have high reference counts and short reference intervals, as data is referenced repeatedly within small windows of time. We characterize spatial locality by examining the decrease in cache miss ratio with increasing block size. The greater the degree of spatial locality, the more quickly the miss ratio

will decrease with increasing block size.

Our various analyses have been run on each individual trace; we've condensed those analyses into three workloads from the Cray traces and two from the Ardent traces. The Cray traces are divided into a *Livermore Loops* workload, a *NAS Kernel* workload, and a *scalar* workload consisting of the remaining traces. The first two workloads are heavily vectorized, while the third workload consists mainly of scalar benchmarks plus *linpack*. The Cray linpack trace was generated for a small 10x10 dataset and thus is predominantly scalar. Throughout this and remaining sections of the paper, Cray references are analyzed with consecutive instruction parcels packed into eight-byte quantities, i.e. an instruction parcel fetch does not occur until parcels outside the current eight-byte word are needed. This packing of instructions is consistent with the actual X-MP hardware, which fetches both instructions and data in eight-byte quantities.

The Ardent traces with significant vectorization (arc3d, bmk1, bmk11a, flo82, lapack, simple, and wake) comprise an Ardent vectorized workload, while the remaining Ardent traces (ampac, bmk21b, born, mopac) comprise an Ardent scalar workload. Unlike the Cray traces, we analyze the Ardent traces without normalizing to a single reference width, as the Ardent Titan references both four and eight-byte data items over its eight-byte bus. The Titan fetches instructions four bytes at a time from its instruction cache, which is how we model the instruction stream.

# 4.1. Reference Counts

Reference counts were obtained by measuring the number of individual (1) instruction, (2) scalar, and (3) vector references to each memory location. This separates reference counts for what we call *shared* data (Table 2) into scalar and vector components, allowing us to draw comparisons between scalar and vector reference locality. We later combine counts for all reference types to examine the overall temporal locality in vector applications.

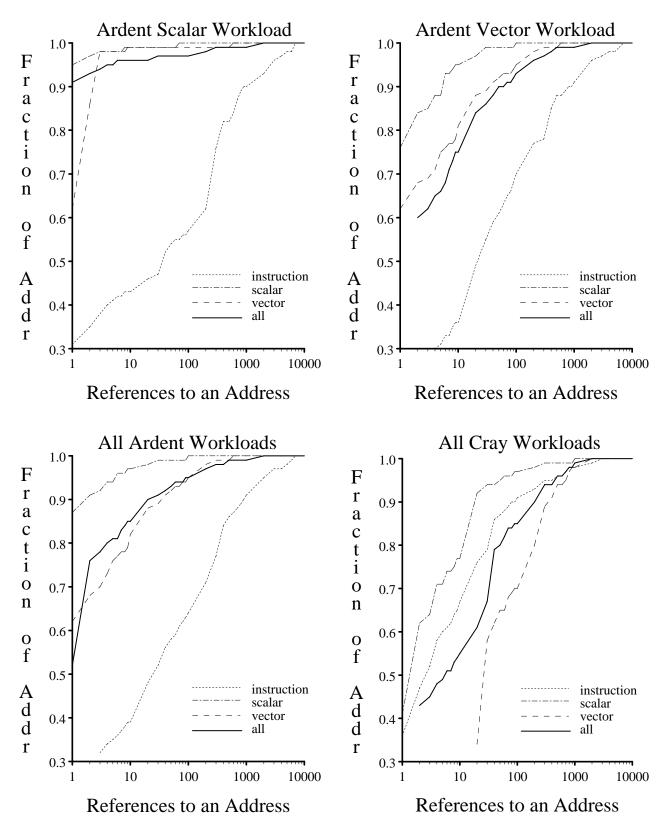

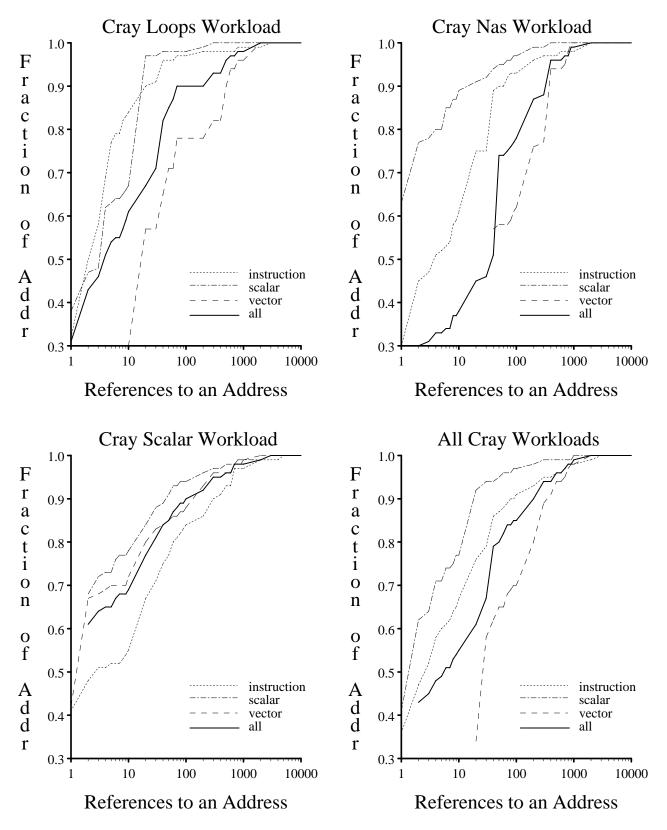

Figure 2 presents reference counts for the individual Ardent workloads, the entire set of Ardent traces, and the entire set of Cray traces. (Results for individual Cray workloads, are left to the Appendix). Each graph in Figure 2 shows reference counts for instruction, scalar, vector, and all references. The point (X,Y) on the graph signifies that a fraction **Y** of all memory locations are referenced up to **X** times during the course of the trace.

Vector reference counts in the Cray benchmarks are very high, but are an artifact of the large loop indices required to benchmark accurately with the Livermore and NAS kernels. Vector reference counts in the Ardent traces, while lower, are more likely to reflect the true amount of data reuse in vectorized workloads. Note that there is reuse of vector data, as vector reference counts in the Ardent vector workload actually exceed scalar reference counts. Mean, median, and 90 percentile reference counts for all workloads are summarized in Table 5.

**Figure 2**: Cumulative reference count distributions for individual Ardent workloads, the combined Ardent workload, and the combined Cray workload.

|               | Referen | ce Count S  | ummary b | oy Workl | oad    |         |

|---------------|---------|-------------|----------|----------|--------|---------|

| Workload      |         | Instruction | ı        |          | Scalar |         |

| w of kioau    | Mean    | Median      | 90 pct.  | Mean     | Median | 90 pct. |

| Cray loops    | 55      | 3           | 23       | 17       | 4      | 20      |

| Cray nas      | 54      | 4           | 55       | 14       | 1      | 16      |

| Cray scalar   | 144     | 3           | 270      | 53       | 2      | 58      |

| Cray (all)    | 99      | 3           | 80       | 26       | 2      | 20      |

| Ardent vector | 352     | 21          | 928      | 8        | 1      | 6       |

| Ardent scalar | 464     | 37          | 920      | 6        | 1      | 1       |

| Ardent (all)  | 397     | 23          | 928      | 7        | 1      | 2       |

| Workload      |         | Vector      |          |          | All    |         |

| Workload      | Mean    | Median      | 90 pct.  | Mean     | Median | 90 pct. |

| Cray loops    | 157     | 20          | 479      | 83       | 4      | 90      |

| Cray nas      | 156     | 40          | 360      | 99       | 40     | 360     |

| Cray scalar   | 59      | 2           | 169      | 89       | 2      | 104     |

| Cray (all)    | 135     | 20          | 400      | 87       | 6      | 208     |

| Ardent vector | 22      | 1           | 32       | 51       | 2      | 60      |

| Ardent scalar | 8       | 1           | 3        | 30       | 1      | 1       |

| Ardent (all)  | 22      | 1           | 32       | 40       | 1      | 20      |

Table 5: Reference Count Summary

Listed are mean, median, and 90 percentile *reference counts* (number of references to each memory location) for the Cray and Ardent workloads. Results are provided for individual workloads and for all traces collected on a given machine. Summaries are presented for instruction references, scalar references, vector references, and all references combined.

### 4.2. Reference Intervals

*Reference intervals* are the number of references between successive accesses to the same memory location. As a measure of temporal locality, reference intervals are more useful than reference counts because references that are closely clustered in time define a different type of locality of reference than the same number of references uniformly spaced over the traced interval. Programs contain large amounts of temporal locality if reference intervals are short, and low amounts if the opposite holds true. Data will remain cached during short reference intervals, but will often be pushed from the cache during longer intervals. One study [Sang84] found that data must be referenced more than 600 times per second to remain cached in the Amdahl 580.

We analyze reference intervals *separately* for instructions, scalar references, and vector references. For data referenced by both scalar and vector instructions, scalar reference intervals are the times between the *current* and *previous scalar* reference to that data. Similarly, vector

reference intervals are the times between the current and previous *vector* reference to that data. For *overall* results, we do not differentiate between data reference types and measure reference intervals between any two references to that data.

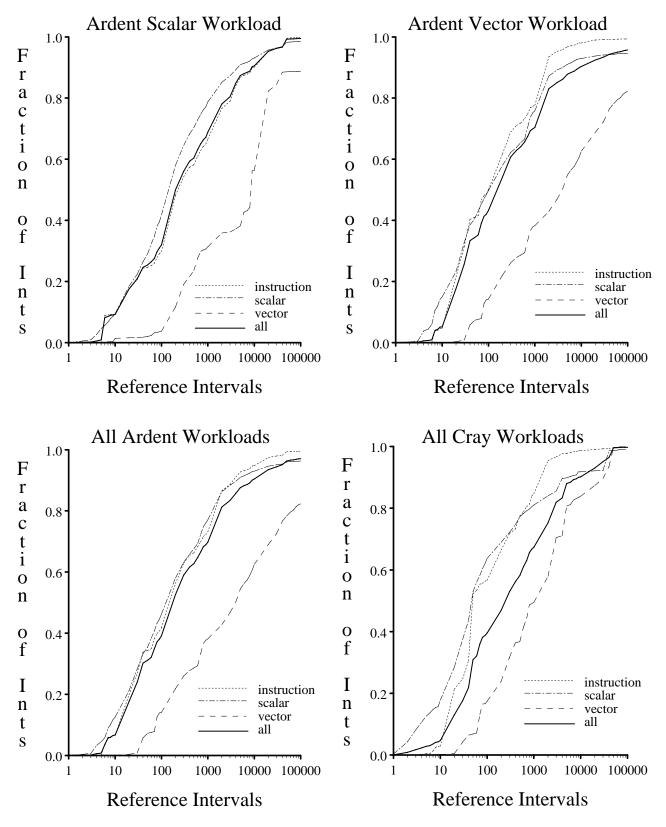

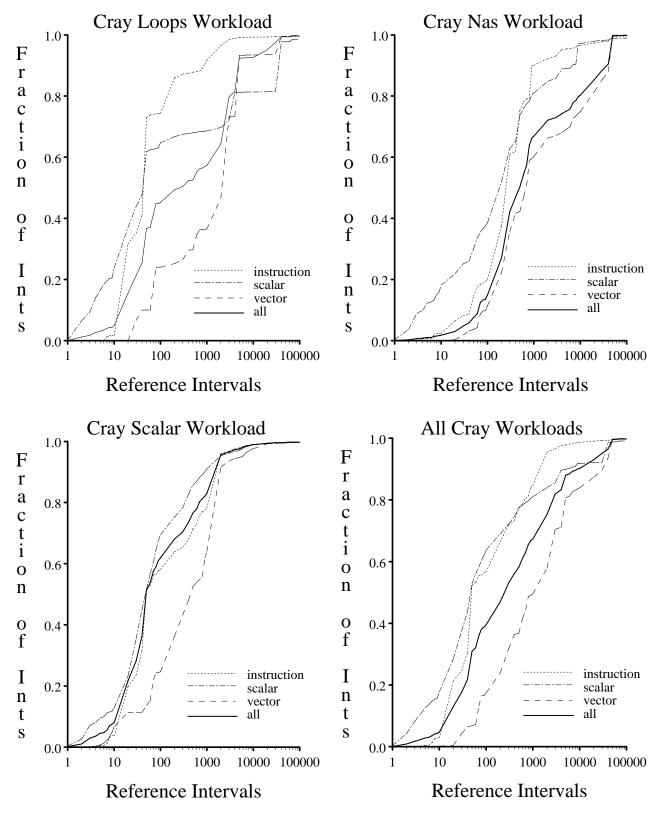

Figure 3 shows cumulative reference interval distributions for the individual Ardent workloads and the complete sets of Ardent and Cray traces (results for the individual Cray workloads are in the Appendix). Each graph contains reference interval distributions for instruction, scalar, vector, and all references. Mean, median, and 90 percentile reference intervals are listed in Table 6.

|               | Reference | e Interval  | Summary | by Workl | oad    |         |

|---------------|-----------|-------------|---------|----------|--------|---------|

| Workload      |           | Instruction | ı       |          | Scalar |         |

| workioau      | Mean      | Median      | 90 pct. | Mean     | Median | 90 pct. |

| Cray loops    | 2034      | 46          | 873     | 13714    | 45     | 38395   |

| Cray nas      | 2478      | 237         | 984     | 3094     | 169    | 6515    |

| Cray scalar   | 1049      | 48          | 1086    | 1267     | 48     | 892     |

| Cray (all)    | 1628      | 49          | 1086    | 6347     | 48     | 5472    |

| Ardent vector | 1992      | 98          | 1713    | 6456     | 103    | 3962    |

| Ardent scalar | 3915      | 234         | 9643    | 3719     | 138    | 4339    |

| Ardent (all)  | 2776      | 156         | 3332    | 5243     | 121    | 4231    |

| Workload      |           | Vector      |         |          | All    |         |

| w orkioad     | Mean      | Median      | 90 pct. | Mean     | Median | 90 pct. |

| Cray loops    | 5058      | 2217        | 4444    | 4181     | 292    | 4444    |

| Cray nas      | 9240      | 699         | 46521   | 7608     | 490    | 37089   |

| Cray scalar   | 1740      | 410         | 1461    | 1109     | 48     | 1086    |

| Cray (all)    | 7165      | 1086        | 32887   | 4502     | 237    | 8996    |

| Ardent vector | 45655     | 3917        | 268165  | 10456    | 150    | 9213    |

| Ardent scalar | 23613     | 8435        | 238069  | 3911     | 201    | 8620    |

| Ardent (all)  | 45294     | 3962        | 265333  | 8072     | 160    | 8759    |

**Table 6**. Mean, median, and 90 percentile reference intervals (number of references between rereferences to data) for the Cray and Ardent workloads.

In the Cray programs, reference intervals for instructions and scalar data are short, while vector reference intervals are roughly an order of magnitude larger. Since vectorized applications operate on large data structures in a serial fashion, the times between successive references to each individual vector data item are consequently high. In processing each vector element however, the same instructions and scalar variables are being reused, which accounts for the higher temporal locality in these reference classes. Note, however, that median vector reference intervals are only a few thousand references, which is sufficiently short that vector data should remain in the cache between loop iterations.

**Figure 3**: Cumulative distribution of time between successive references to the same memory location.

Results for the Ardent workloads are similar to the Cray results. Instruction and scalar reference intervals are both short, while vector reference intervals are roughly an order of magnitude larger than both. Reference intervals in the Ardent traces are also larger relative to the Cray traces, as the Ardent programs are real, long-running codes and not tightly-coded kernels or small benchmarks.

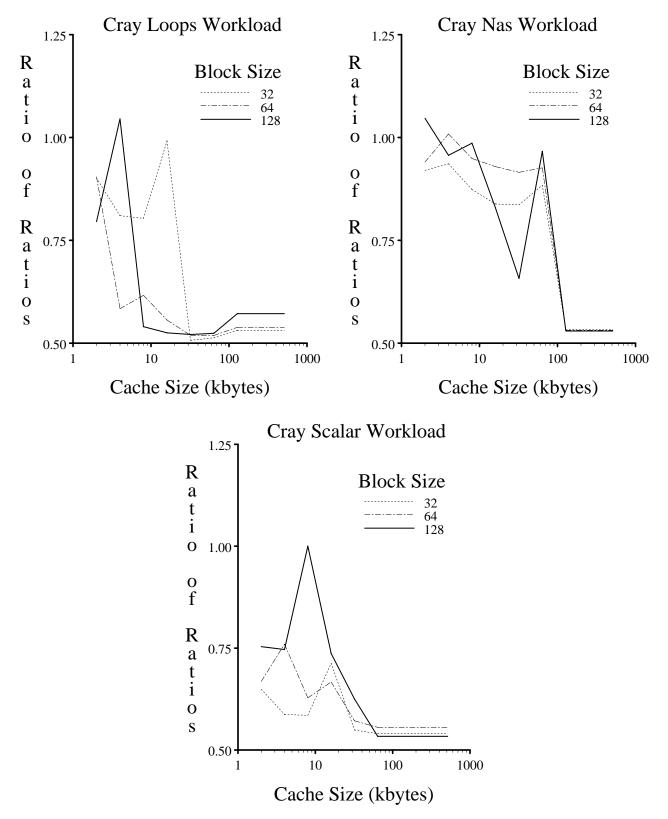

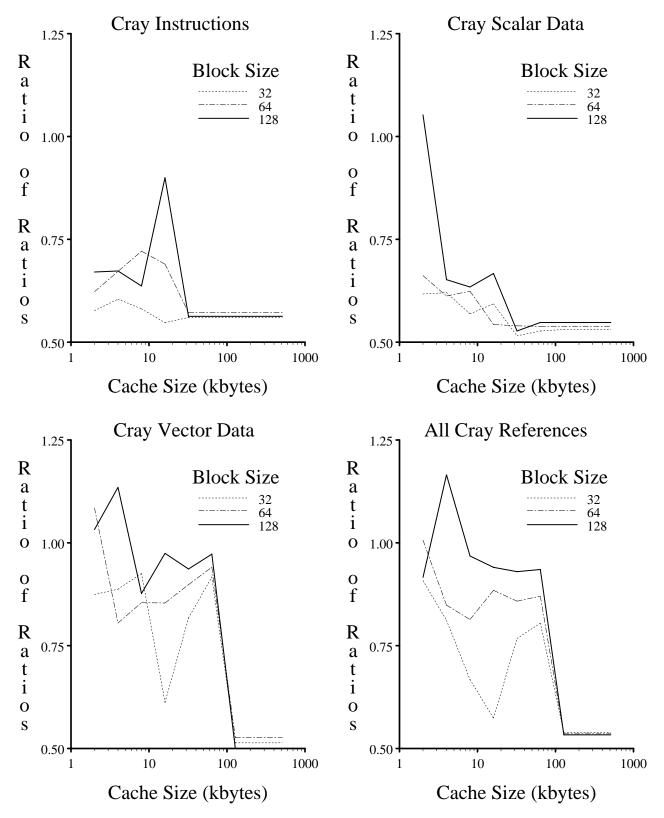

### 4.3. Ratios of Miss Ratios

To quantify spatial locality, we measured *ratios of miss ratios* [Smit87], which, for a particular cache and block size, is the ratio of its miss ratio to the miss ratio for the same-size cache with one-half the block size. Mathematically, the ratios of miss ratios for a cache of size C and block size B is given by  $\frac{mr(C,B)}{mr(C,\frac{B}{2})}$  where mr(C,B) is the miss rate for a cache of size C with

block size B. The ratio of miss ratios can range from a low of 0.5, when the level of spatial locality is very high, to well above 1.0 if there is little spatial locality; the ratio of miss ratios can be above one if the extra data fetched in large blocks is not used and only displaces useful data from the cache. This latter phenomenon, known as *memory pollution*, is most noticeable in smaller caches since increasing block size reduces the number of cache blocks below the number of distinct regions in concurrent use.

To obtain ratios of miss ratios, we measured cache miss ratios using LRU stack techniques. Simulations were run for block sizes from 16 to 128 bytes, covering a wide range of microprocessor and mainframe cache implementations. Fully-associative caches were simulated using fairly deep LRU stacks (500 elements). For still larger caches, set-associative simulations were performed to reduce overhead searching LRU stacks. Each set-associative cache consisted of 64 fully-associative stacks, with each stack containing up to 500 elements. Prior work [Smit82, Hill89] had found that set sizes beyond eight do little to improve cache miss ratios; thus our setassociative results should be virtually identical to results for fully-associative caches.

Figures showing ratios of miss ratios for various reference classes in the individual Cray and Ardent workloads are left to the Appendix. In the Cray workloads, ratios of miss ratios are low for instruction and scalar data references. Vector references, however, contain little spatial locality due to large strides in the Livermore and NAS kernels. We have noted that these kernels are designed for evaluating processor pipelines, and do not necessarily reflect the typical memory reference behavior of vector applications.

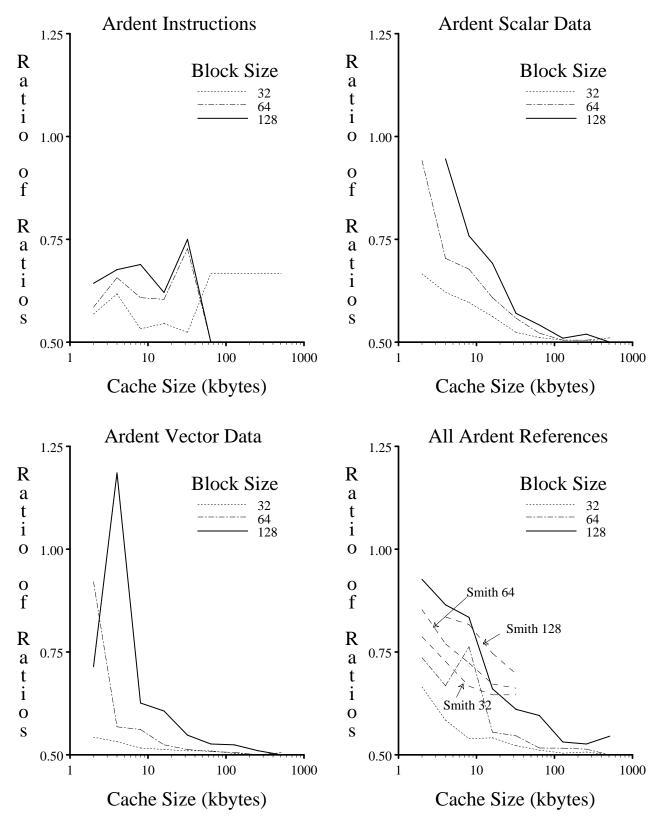

**Figure 4**: Ardent ratios of miss ratios for all workloads plotted on the basis of instructions, scalar data, vector data, and all references. The last graph also contains ratios of miss ratios from [Smit87].

Figure 4 shows the ratios of miss ratios across all Ardent traces, plotted on the basis of instruction, scalar, vector, and all references. The last graph in the figure also contains ratios of miss ratios measured for general-purpose, multiprogrammed workloads [Smit87]. Unlike the Cray results, spatial locality is present in all reference classes, and is particularly strong for vector references. This improved locality is mainly due to the shorter strides in the Ardent programs. Ratios of miss ratios for scalar and vector data become quite low once the cache size exceeds 16 Kbytes. In Figure 4d, measured ratios of miss ratios across all references are actually lower than results from [Smit87]; i.e. we find more locality in our workloads than was found previously for a non-vectorized workload.

In summary, in our analysis of locality we have found large amounts of spatial and temporal locality in instruction and scalar references within the Ardent and Cray traces. Vector references contain lesser amounts of temporal locality, although median vector reference intervals are short enough (several thousand references in the Ardent programs) that the bulk of the vector data should remain cached between periods of use. The Ardent traces show large amounts of spatial locality; there is less spatial locality in the Cray traces. We believe the Cray results to be anomalous due to the artificial memory reference behavior in the small kernels, whereas the Ardent results reflect the considerable spatial locality in real vector applications.

## 5. Cache Miss Ratios

In this section, we examine cache miss ratios over a wide range of cache parameters, to see if the measurements of locality yield the expected low miss ratios. Simulations were conducted using both the Ardent and Cray traces, although as in prior sections we will emphasize the Ardent results over the Cray results. To approximate actual hardware implementations, references to consecutive two-byte Cray instruction parcels are merged into one eight-byte word reference. The Ardent Titan, unlike the Cray X-MP, references both single-precision as well as double-precision data, thus Titan references are not normalized to a constant word size. We do not implement periodic cache flushing in our cache simulator, as uniprogrammed vector machines typically execute for long periods of time between interrupts.

### 5.1. Fully-Associative Caches

Three types of fully-associative caches were simulated: *instruction caches*, *data caches* (containing scalar and vector data), and *unified caches* (containing instructions, scalar data, and vector data). Block sizes range from 16 to 128 bytes, and the maximum cache size simulated is 4 Mbytes. To keep stack distances manageable, we did not simulate some combinations of large cache size and small block size.

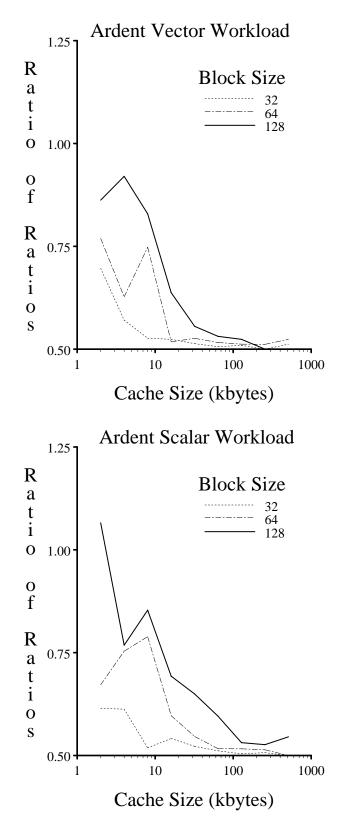

#### 5.1.1. Miss Ratios

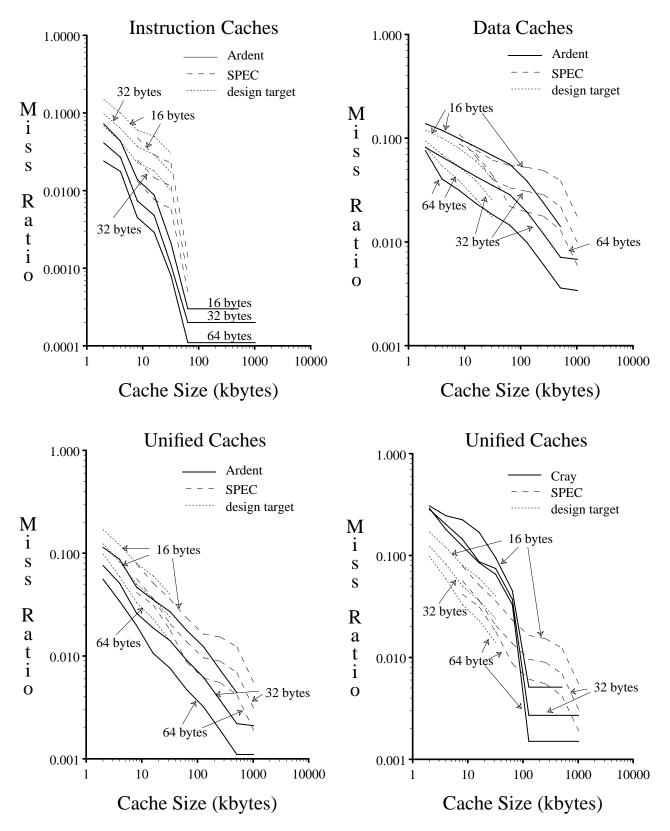

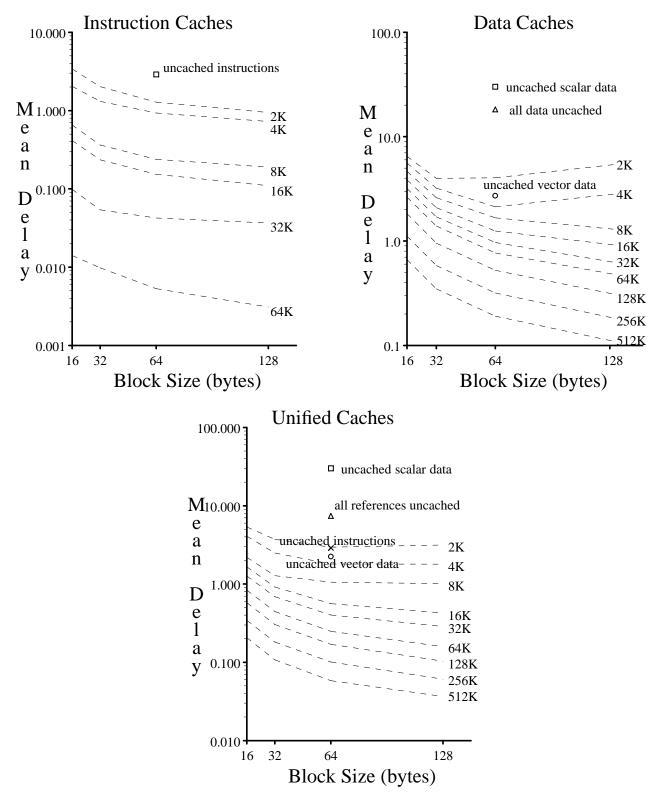

Figure 5 shows miss ratios for fully-associative Ardent instruction, data, and unified caches, as well as for fully-associative Cray unified caches. Figures containing results for Cray instruction and data caches are left to the Appendix.

Figure 5 also shows (a) design target miss ratios [Smit87] and (b) SPEC miss ratios [Gee91] averaged over the SPEC [SPEC89] floating-point application subset. All miss ratios are for fully-associative caches except for the SPEC results, which are plotted for a set size of eight, the maximum measured. The design target miss ratios, measured from address traces for a variety of scalar machines, represent the cache performance in general-purpose, multiprogrammed environments. The SPEC miss ratios were measured in a uniprogrammed environment, and should provide a better basis for comparison against our uniprogrammed vector workloads. We note that the SPEC floating-point miss ratios are significantly higher than miss ratios for the SPEC integer benchmarks [Pnev90].

In the figure, both the Ardent and SPEC instruction cache miss ratios fall more rapidly than design target miss ratios as cache size increases. Unlike the workloads used to measure design target miss rates, the Ardent and SPEC workloads are uniprogrammed, and thus do not contain any multiprogramming cache misses.

Ardent data cache miss ratios agree reasonably well with the design targets, while SPEC data cache miss ratios tend to be larger by as much as a factor of three. The higher SPEC miss rates are likely due to inherent differences between workloads. What is more interesting is that data cache miss ratios for real vector workloads are actually quite low; they compare favorably with miss ratios for general-purpose workloads (the design targets) and with miss ratios for the popular floating-point benchmark suite (SPEC).

For unified caches, design target miss ratios are slightly higher than Ardent miss ratios, again due to multiprogramming effects. SPEC unified cache miss ratios are also higher than Ardent miss ratios, due to a higher data component of the miss rate. For the Cray programs, unified cache miss ratios are larger than SPEC and design target miss rates at small cache sizes, since the Cray kernels contain little spatial locality. We also observe that Cray miss ratios drop dramatically once these kernels completely fit into the cache.

**Figure 5**: Fully-associative cache miss ratios plotted against design target and SPEC floating-point miss rates.

We can make a couple of observations from these results:

- (a) The Ardent traces reference significant amounts of data, as data and unified cache miss ratios continue to decrease until the cache size exceeds 512K. Traces used in previous cache simulation efforts [Hill87, Hill89, Pnev90, Przy88, Smit82, Smit85, Smit87] have referenced much less data. Bypassing the trace storage process completely and simulating references during trace generation [Borg90, Gee92, Gee91, So88a, So88b] can allow even larger problem sizes (e.g. [Borg90]) to be observed. However, the large increase in CPU time to simulate these longer traces limits the design space that can be explored.

- (b) Ardent miss ratios level off beyond caches larger than one half megabyte. This cache size is large enough to capture most, if not all of the locality within these programs. There is even sufficient locality in the Ardent programs to make use of smaller caches. Data cache miss ratios fall below 1 percent for cache sizes as small as 64 or 128 Kbytes.

In generating these results, we have assumed that Ardent data references can be either four or eight-byte quantities. To compare Ardent results more directly with design target and SPEC miss ratios, Ardent Titan simulations were repeated with data references *normalized* to a four-byte reference width, i.e. double precision data references are split into two four-byte halves. Results for Ardent data and unified caches, listed in the Appendix, show that normalizing data references to a four-byte word size reduces data and unified cache miss ratios by some 30 and 10%, respectively. The reduction arises because the second half of each double-precision data reference always hits in the cache. Ardent data cache miss ratios fall to roughly 70% of design target miss ratios and less than 50% of SPEC data cache miss ratios, while unified cache miss ratios fall to less than 50% of design target and SPEC miss rates.

### 5.1.2. Ratios of Miss Ratios

Cache miss ratios are often workload dependent. A more stable measure of cache performance is the *ratio of miss ratios*, which we used in Section 4 to analyze spatial locality. Ratios of miss ratios less than one indicate that doubling the cache block size decreases miss ratios. However, whenever the ratio of ratios exceeds 0.5, any decrease in cache miss ratio is also accompanied by increased fetch traffic.

Ratios of miss ratios for fully-associative unified caches are shown in Table 7 (instruction and unified cache results are in the Appendix). The table also includes ratios of ratios from [Smit87] for comparison. Ardent ratios of miss ratios are consistently 12 to 15 percent *smaller* than ratios of miss ratios from [Smit87], due to the large amount of spatial locality in this

|        |       | U         | nified Ca | iche Rati | os of Mis | s Ratios |       |            |       |

|--------|-------|-----------|-----------|-----------|-----------|----------|-------|------------|-------|

|        |       | Ardent    |           |           | Cray      |          |       | [Smit87]   |       |

| Cache  | I     | Block Siz | e         | I         | Block Siz | e        | I     | Block Size | e     |

| Size   | 32    | 64        | 128       | 32        | 64        | 128      | 32    | 64         | 128   |

| 128    | 0.753 | 0.941     | 1.801     | 0.861     | 0.871     | 1.110    | 0.942 | 1.184      | 2.046 |

| 256    | 0.685 | 0.942     | 1.078     | 0.860     | 0.836     | 0.952    | 0.822 | 1.162      | 1.453 |

| 512    | 0.668 | 0.776     | 0.967     | 0.950     | 0.819     | 0.878    | 0.767 | 0.914      | 1.451 |

| 1024   | 0.732 | 0.729     | 0.886     | 0.955     | 0.856     | 0.876    | 0.831 | 0.880      | 1.023 |

| 2048   | 0.665 | 0.736     | 0.927     | 0.923     | 1.028     | 0.930    | 0.731 | 0.787      | 1.132 |

| 4096   | 0.584 | 0.668     | 0.865     | 0.824     | 0.893     | 1.187    | 0.719 | 0.746      | 0.809 |

| 8192   | 0.558 | 0.763     | 0.834     | 0.646     | 0.857     | 1.028    | 0.645 | 0.661      | 0.753 |

| 16384  | 0.530 | 0.567     | 0.660     | 0.513     | 0.979     | 1.007    | 0.616 | 0.633      | 0.685 |

| 32768  | 0.522 | 0.539     | 0.618     | 0.784     | 0.197     | 2.878    | 0.601 | 0.601      | 0.660 |

| 65536  | 0.511 | 0.517     | 0.553     | 0.825     | 0.887     | 0.160    | -     | -          | -     |

| 131072 | 0.504 | 0.516     | 0.531     | 0.529     | 0.556     | 0.533    | -     | -          | -     |

| 262144 | 0.507 | 0.514     | 0.526     | 0.529     | 0.556     | 0.533    | -     | -          | -     |

| 524288 | 0.500 | 0.500     | 0.546     | 0.529     | 0.556     | 0.533    | -     | -          | -     |

Table 7: Unified Cache Ratios of Miss Ratios

workload. Cray ratios of miss ratios are about 15 percent larger for unified caches, but agree fairly well with [Smit87] for instruction and data caches. These results, in conjunction with the miss ratios presented earlier, indicate that the cache performance of vector workloads is comparable to that of any other workload which normally benefits from data caching.

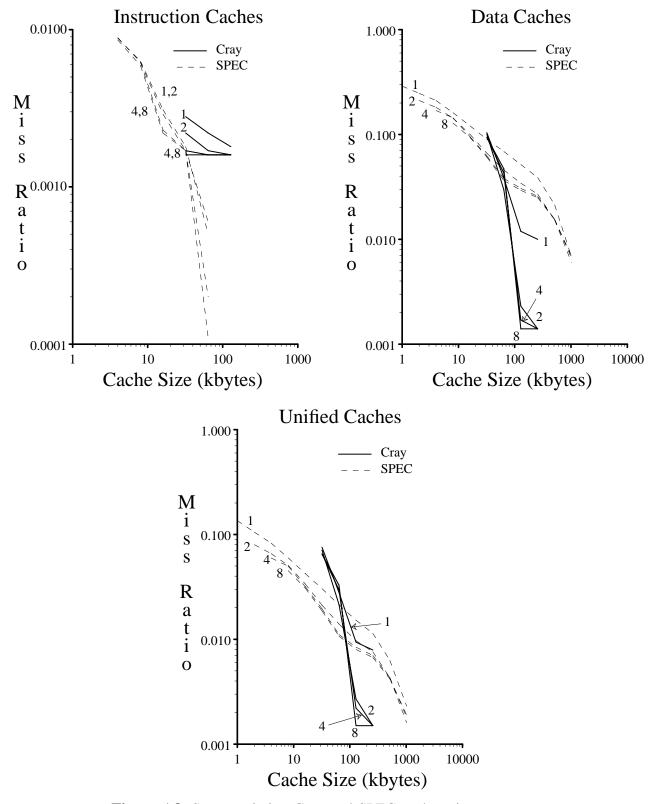

## 5.2. Set-Associative Caches

Set-associative caches have been studied in detail in the literature (see e.g. [Smit82], [Hill89]); it has been observed that caches with moderate levels of associativity (4-way to 8-way) have miss rations nearly as low as for fully-associative caches. In [Hill89], it was found that reducing associativity from eight-way to four-way, four-way to two-way, and from two-way to direct-mapped causes relative increases of 5, 10, and 30 percent in miss ratio respectively. These increases in miss ratio were found to be consistent over a wide range of cache and block sizes. As discussed, the benefits of increasing associativity clearly diminish beyond a size size of eight.

The question is whether these results also apply for vector workloads. Two prior studies using vector applications [So88a, So88b] simulated three programs on a 64 Kbyte cache with set size varying from one to four. On average, their results agree with [Hill89]. As set size varied from four to two, and two to one, miss ratios increased by averages of 10 and 28 percent, respectively. Another study [Call90], however, found that increasing associativity has little effect on vector cache performance, and could even reduce performance in certain cases.

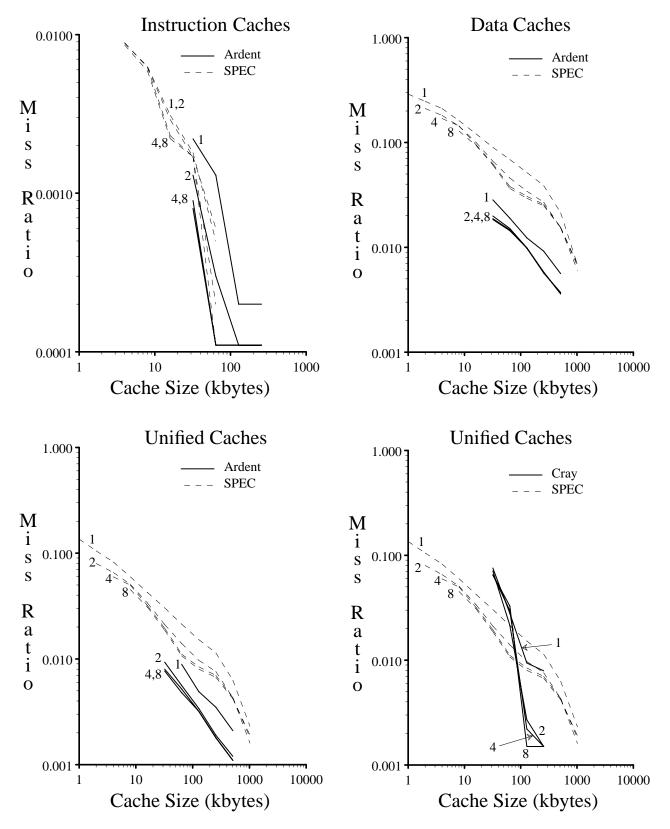

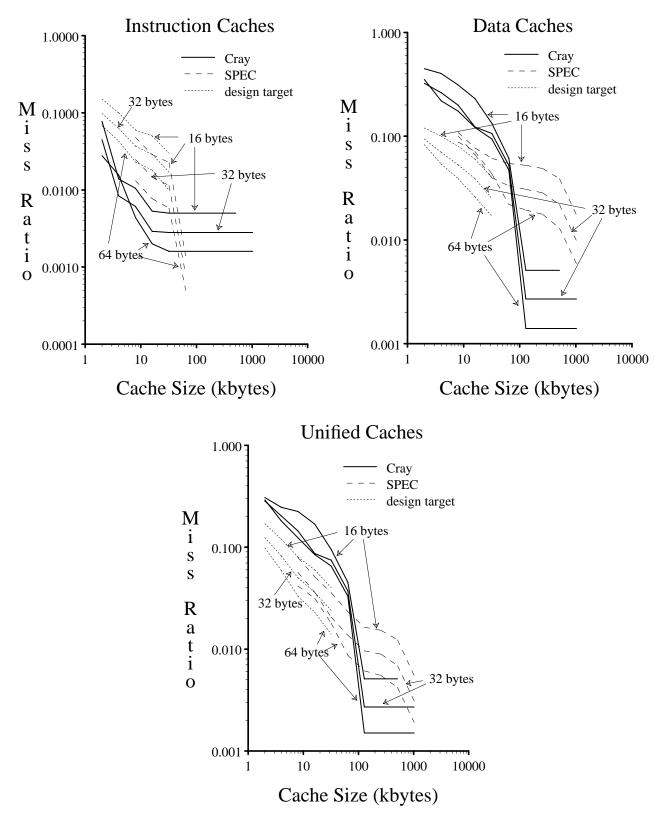

**Figure 6**: Set-associative Ardent and Cray cache miss ratios for a 64 byte block size, plotted against SPEC floating point miss ratios. Curves are labeled by set size.

In this section, we evaluate the effect of set-associativity in vector processor caches over a wide range of cache parameters, covering cache designs not examined in previous studies. Instruction, data, and unified caches up to four megabytes in size were simulated, with set size ranging from one to eight. We also compare LRU replacement to random replacement.

### 5.2.1. Miss Ratios

Figure 6 shows set-associative Ardent and Cray miss ratios vs. set-associative SPEC floating-point miss ratios for a block size of 64 bytes. Full tables of set-associative Ardent and Cray cache miss ratios are available in the Appendix.

Set-associative miss ratios for the Ardent and Cray traces decrease significantly when the set size is increased from one to two. Set sizes beyond two have much less effect, as only instruction cache performance improves noticeably. In contrast, SPEC floating-point miss ratios continue to drop as associativity increases, although most of the improvement is realized with a set size of two.

Ardent and Cray instruction cache miss ratios are roughly equal to SPEC instruction cache miss ratios, For data and unified caches, Ardent and Cray miss ratios are both lower than the SPEC miss ratios. The smaller Cray miss ratios, as we have noted before, are due to the small kernels being completely contained in caches larger than 64 Kbytes. The smaller Ardent miss ratios are likely due to workload differences, as we had observed similar results for fully-associative caches.

One interesting observation is that miss ratios for 128 Kbyte and 256 Kbyte Ardent data caches, as well as for 64 Kbyte Cray data caches, actually *increase* as set size increases beyond two. This same phenomenon was observed in one study [Call90], but not in another [So88a]. We suspect that the LRU replacement algorithm used in the simulations is poorly matched to the reference patterns typical of vector applications. When references are highly sequential (i.e. instruction and vector references) and the set size is not large enough to manage collisions, then LRU replacement will often remove blocks that are most needed in the near future [Smit83]. We compare LRU to random replacement in Section 5.2.3.

## 5.2.2. Miss Ratio Spreads

*Miss ratio spreads* enable us to isolate the relative effect of increasing associativity on cache miss ratios. The miss ratio spread between a 2n-way set associative cache and an n-way set associative cache is defined as m(n)/m(2n) - 1. Here m(2n) is the miss ratio for the 2n-way set associative cache, and m(n) is the miss ratio for the n-way set associative cache. Table 8 list miss ratio spreads for Ardent unified caches as set size varies from eight-to-four, four-to-two, and two-to-one. The data is smoothed with a weighted average of adjacent spreads as recommended

by [Cham83]. If mrs(c) is the miss ratio spread for a cache of size c, then the smoothed spread mrs'(c) is equal to 0.15\*mrs(c/4) + 0.20\*mrs(c/2) + 0.30\*mrs(c) + 0.20\*mrs(2c) + 0.15\*mrs(4c). Spreads for endpoint cache sizes are calculated with weights increased proportionately to sum to 1.0.

In a previous study [Hill89], smoothed miss ratio spreads were found to be fairly constant across cache size, block size, and cache type, averaging 5, 10, and 25 percent for changes in associativity from eight-to-four, four-to-two, and two-to-one, respectively. Our results are not as consistent, as miss ratio spreads for unified caches clearly increase with increasing block size. The spreads going from two-way to one-way associativity (direct mapping) are much larger compared to [Hill89], but spreads from eight-way to four-way and four-way to two-way associativity are much smaller. Ardent instruction caches (see Appendix) do seem to benefit more from increased associativity than Ardent data or unified caches, but instruction miss ratios are so low that any reduction in the number of misses appears insignificant.

Miss ratio spreads for the Cray traces, which are not given, are smaller than Ardent miss ratio spreads for instruction caches but larger for data and unified caches. Like the Ardent spreads, the Cray spreads vary significantly with cache and block size, but also suggest that set sizes beyond two or four are unnecessary in vector applications. This differs from earlier work in both scalar [Smit82, Hill89] and vector [So88a, So88b] environments, where increasing associativity beyond two continued to yield decreases in miss ratio.

| Ardent     | Smoothee | l Miss Ra | tio Sprea | ds for Un | ified Cac | hes    |

|------------|----------|-----------|-----------|-----------|-----------|--------|

| Cache Size | Block    | Size: 16  | Bytes     | Block     | Size: 32  | Bytes  |

|            | 8-to-4   | 4-to-2    | 2-to-1    | 8-to-4    | 4-to-2    | 2-to-1 |

| 32K        | 0.019    | 0.056     | 0.296     | 0.020     | 0.080     | 0.381  |

| 64K        | 0.020    | 0.044     | 0.370     | 0.024     | 0.059     | 0.450  |

| 128K       | 0.010    | 0.040     | 0.414     | 0.014     | 0.050     | 0.488  |

| 256K       | 0.003    | 0.030     | 0.433     | 0.014     | 0.028     | 0.498  |

| 512K       | -0.006   | 0.030     | 0.370     | 0.003     | 0.021     | 0.426  |

| Cache Size | Block    | Size: 64  | Bytes     | Block     | Size: 128 | Bytes  |

|            | 8-to-4   | 4-to-2    | 2-to-1    | 8-to-4    | 4-to-2    | 2-to-1 |

| 32K        | 0.044    | 0.113     | 0.521     | 0.051     | 0.197     | 1.292  |

| 64K        | 0.039    | 0.090     | 0.582     | 0.060     | 0.141     | 1.316  |

| 128K       | 0.023    | 0.083     | 0.609     | 0.046     | 0.104     | 1.295  |

| 256K       | 0.012    | 0.059     | 0.607     | 0.044     | 0.044     | 1.124  |

| 512K       | 0.000    | 0.048     | 0.526     | 0.022     | 0.018     | 0.905  |

Table 8: Smoothed miss ratio spreads for Ardent unified caches

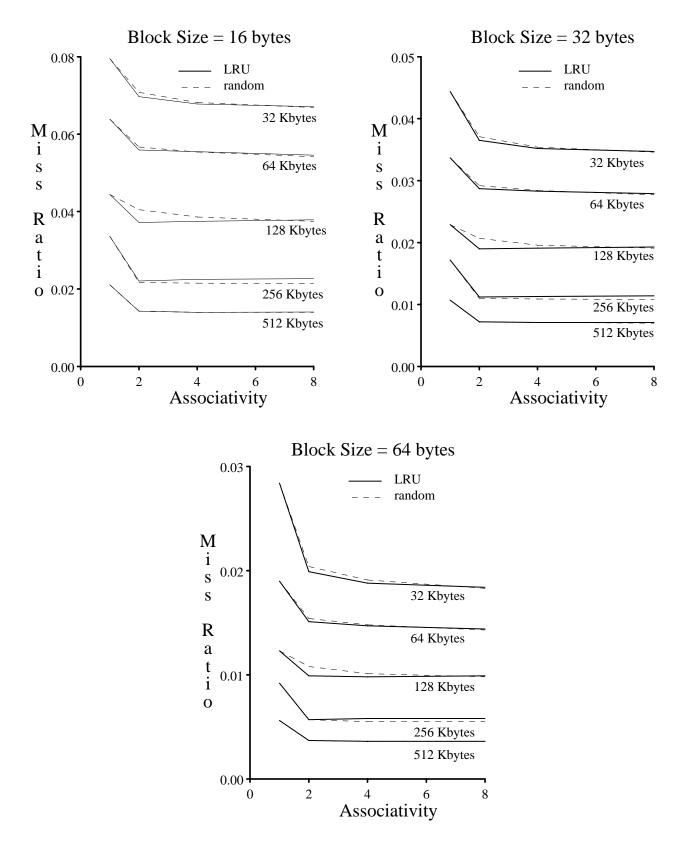

#### 5.2.3. Replacement Algorithms

While studying the effects of set-associativity, we observed that data cache miss rates for certain combinations of cache and block size data caches can actually *increase* with increasing associativity. For the Cray kernels, this increase is as large as 30 percent as the set size increases from two to four to eight. For the Ardent workload, based on real applications rather than small kernels, the increase is slight but apparent.

One paper [Smit83] noted that LRU and FIFO replacement can lead to 100 percent miss ratios in small, fully-associative instruction caches when program loops are larger than the cache size. Under such conditions, random replacement provides superior performance compared to both LRU and FIFO. While the data caches we study are much larger than the small instruction buffers analyzed in that study, we believe that similar effects are occurring within cache sets when the number of blocks which map into a set is larger than the set size.

To test this theory, set-associative data cache simulations were repeated for the Ardent traces using the stack-based implementation of random replacement described in [Matt70]. Figure 7 compares Ardent data cache miss ratios with random replacement vs. data cache miss ratios with LRU replacement. The various curves in the figure are parameterized by cache size. The figure shows that there is effectively *no consistent difference* in performance between random and LRU replacement. With random replacement, miss ratios no longer increase with increasing associativity, but neither is there a significant improvement in performance. LRU replacement performs slightly better than random replacement when the set size is small, while random replacement is slightly better for larger set sizes.

#### 6. Estimated Performance Impact

So far we have provided fairly strong evidence supporting the use of vector caches. This evidence, however, consists mainly of time-independent metrics such as cache miss ratios and ratios of miss ratios. The performance impact of caching vector references on machine performance is the actual issue, and we consider this by using our measured cache miss ratios to estimate average memory access delays. Our results suggest that vector caches can significantly reduce the time needed to gain access to data in memory.

Before proceeding, we should mention that reducing memory access delays may not always translate into large performance gains in a vector machine. Vector machines typically reference long vectors in a pipelined fashion, which reduces the average delay seen per individual reference. Vector processors can also request data well before it is used, although this generally requires significant programming effort. Still, applications can often be coded to perform well in an environment where memory is many cycles away.

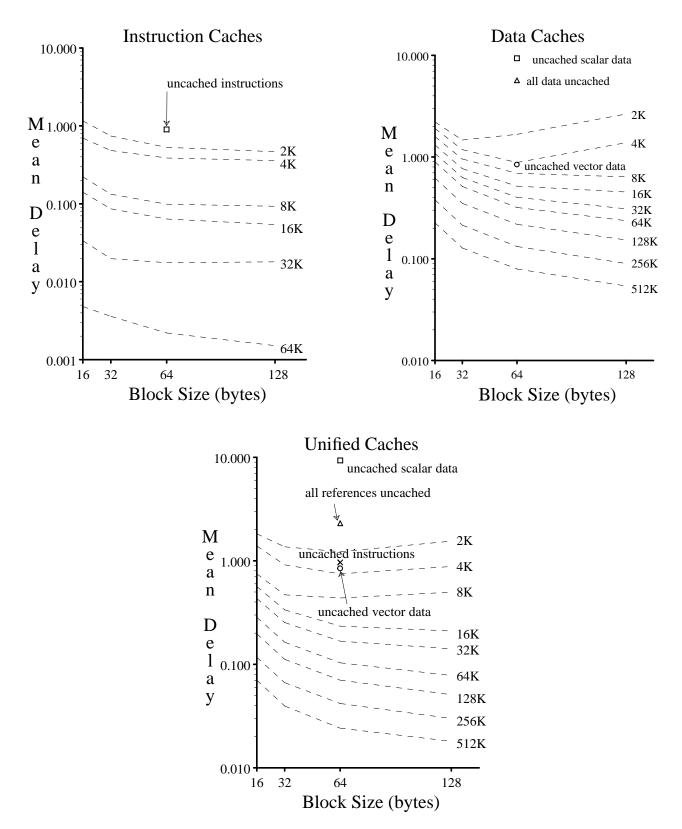

#### 6.1. Mean Delay Per Memory Reference

We can compare the memory system performance of caching vs. non-caching vector processors by estimating the *average delay seen by each memory reference*. In a machine using a cache, the mean delay is approximately the product of the cache miss ratio and the time to service a cache miss. This estimate assumes that copy-back caches with write buffering are employed to minimize the effect of data writes on average delays [Smit79]. The time to service a cache miss is the sum of (a) memory system latency, and (b) cache block size divided by total memory bandwidth. Given a memory latency of *L* cycles, a block size of *B* bytes, a bus width of *W* bytes, and *C* cycles per bus transfer, the miss service time (in cycles) is equal to  $L + C(\frac{B}{W})$ . This calculation assumes no fetch bypass or wrap-around load; instead, the entire line is fetched and then accessed.

A non-caching vector processor encounters main memory delays at: (1) branches in the instruction stream, (2) the first element of a vector load, and (3) scalar loads. Instruction references following a branch and vector loads following the first load cause no additional delay, as these accesses are overlapped in a pipelined memory system. Note that assumption (1) is somewhat unfair by ignoring the use of commonly used instruction buffers. We make this assumption, however, to show that even small instruction caches are extremely effective relative to a machine which does not cache instructions. Similarly, (2) and (3) assume that a vector machine stalls on each pending scalar or vector load, which is clearly a worst-case scenario. We also assume that stores to memory are buffered, and only the occasional store which overflows the store buffers will cause delays. We assume that such stores make up 10 percent of the total [Smit79].

Two sets of parameters were used to compute a range of mean delays per memory reference for the Ardent traces. The first set of parameters assumes a memory latency of 14 cycles, an eight-byte bus, and a transfer rate of eight bytes per cycle. These values correspond closely to Cray X-MP and Ardent Titan memory system parameters. The second set of parameters assumes a memory latency of 45 cycles, an eight-byte bus, and a transfer rate of eight bytes per cycle. The longer memory latency corresponds roughly to the memory system parameters of a Cray 2.

Figures 8 and 9 show mean delays per memory reference for Ardent fully-associative instruction, data, and unified caches. The figures show average delay vs. cache block size, with curves in each figure parameterized by cache size. Each graph also shows mean delays per reference without caches for comparison. For data and unified caches, which support combinations of instruction, scalar, and vector references, mean delays without caches are separately plotted for the different reference classes.

**Figure 7**: Set-associative Ardent data cache miss ratios for block sizes of 16, 32, and 64 bytes. For each cache size (labeled in kbytes), miss ratios are plotted for LRU and random replacement.

**Figure 8**: Mean delay per memory reference (cycles) for Ardent fully-associative instruction, data, and unified caches. Plots are labeled by cache size (Kbytes), and delays without caches are also shown for the different reference types. Memory latency is 14 cycles, and transfer time is 1 cycle per 8-byte word.