# Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# PROGRAMMABLE ARITHMETIC DEVICES FOR HIGH SPEED DIGITAL SIGNAL PROCESSING

by

Devereaux C. Chen

Memorandum No. UCB/ERL M92/49

14 May 1992

# PROGRAMMABLE ARITHMETIC DEVICES FOR HIGH SPEED DIGITAL SIGNAL PROCESSING

Copyright © 1992

by

Devereaux C. Chen

Memorandum No. UCB/ERL M92/49

14 May 1992

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Programmable Arithmetic Devices for High Speed Digital Signal Processing

Devereaux C. Chen

University of California Berkeley, California

Department of Electrical Engineering and Computer Science

### Abstract

The high throughput (computation) requirements of real-time digital signal processing (DSP) systems usually dictate hardware intensive solutions. Often attendant to hardware approaches are problems of high development costs, slow turnaround, susceptibility to errors, and difficulty in testing and debugging, all of which tend to inhibit the rapid implementation of such systems. Research is underway into the synthesis of application specific hardware to aid the system designer by automatically generating hardware that is "correct by construction". The creation of configurable, pre-fabricated hardware that has been designed for high speed computations forms part of this research and is the main topic of this thesis.

This work contains a survey of some typical real-time DSP algorithms drawn from video and speech processing and summarizes the particular computation challenges posed by this class of algorithms. Currently available hardware choices and their trade-offs and limitations are discussed. A multiprocessor architecture consisting of programmable arithmetic devices is presented as a novel platform for supporting high speed digital signal processing. The VLSI realization of the architecture and an accompanying software development environment are presented as a proof of concept. The main conclusion of this work is that software-configurable hardware approaches to high speed digital signal processing problems form viable alternatives to existing approaches, for systems designers interested in rapidly prototyping or implementing their ideas.

5/11/92

rof / Jan M Rabae

An M Rabaey

Dedicated to my loving family, and that wonderful someone who was "on her way to Dibbidi-dop, early in the morning."

## Acknowledgements

No man is an Illand intire of it selfe;

- J. Donne

I wish to thank my advisor Jan Rabaey for his support and guidance of this work. His high standards have left an indelible mark upon this thesis. I would also like to thank Bob Brodersen and Charles Stone for serving on my dissertation committee. Thanks also to Bob Brayton and John Wawrzynek for participating on my qualifying examination committee,

Among the many members of the U.C. Berkeley EECS faculty who have been especially encouraging and supportive are David Hodges, Ping Ko, Edward Lee, Richard Muller, A. Richard Newton, and Aram Thomasian. William Oldham deserves special thanks for encouraging me to apply to the Department.

Tso-Ping Ma of Yale University, Winston Strachan of St. George's College, and Sister Margaret Mary of Holy Childhood Prep. represent the many wonderful teachers from my previous schools who have taught me so much.

Several former colleagues who encouraged and inspired me to continue with graduate studies are Paul Merchant, John Moll, and Chuck Tyler.

Hugo de Man and Francky Catthoor of IMEC gave helpful advice at the beginning of the PADDI project.

Participants on the PADDI project included Cecilia Yu, who helped with the XILINX investigation, David Schultz who assisted with the EXU layout, Simon Li who assisted with the scan-test board, and Eric Ng who wrote the PADDI assembler and simulator. Their assistance is gratefully acknowledged. Thanks also to Andy Burstein and Cormac Conroy for assistance with SPICE, Angela Cheng, Joan Pendelton and Bart Sano for providing the PAD cells, Chuck Cox for advice on XILINX, Paul Landmann for providing the carry-select adder cells, Alex Lee for providing the SRAM cells, and the staff members of the MOSIS organization, especially Sam Reynolds, for chip fabrication support.

The BJ group members included many fellow students who provided generous time, support, and camaraderie when it was needed. Special thanks to Alfred Yeung for being a great office-mate. Staff members including Tom Boot, Carole Frank, Sue Mellers, Brian Richards, Phil Schrupp, Kirk Thege, and Kevin Zimmerman provided the essential infrastructure which was critical to the success of the project.

Among the many friends who have enrichened my life at Berkeley, Pranav Ashar, Behzad Behtash, Chedsada Chinrungrueng, Randy Cieslak, German Ferrer, Paul Freiberg, Bruce Holmer, D.K. Jeong, Ming Lin, Rajeev Murgai, Irena Stanczyk-Ng, Allen Nehorayaff, Todd Strauss, Greg Thomas, and Greg Uviegara deserve special mention. They, among many others, have made the going a whole lot easier and fun than it might have been otherwise.

I am at loss for words to express my gratitude to my parents, Marsden and Viola, my wife, Sharon, and my cousin Pamela for their wonderful love and encouragement through the years. This thesis would not have been possible without them. My daughter Kristin helped make it all a much happier and brighter experience.

To all the people that I should have mentioned but haven't, due to lack of space, many thanks. Please forgive the omission.

I would like to thank the Hewlett-Packard Company for providing financial support during my first year as a graduate student.

This project was sponsored by the Defense Advanced Research Projects Agency (monitored by U.S. Department of Justice, Federal Bureau of Investigation, under contract no. J-FBI-90-073) and Sharp Microelectronics Technology, Inc. Their support is gratefully acknowledged. The views and conclusions in this document are those of the authors and should not be interpreted as representing the official policies, either express ed or implied, of the Defense Advanced Research Projects Agency, the U.S. Government, or Sharp Microelectronics Technology, Inc.

## **Contents**

| A  | ckno  | wledgements                                    | i   |

|----|-------|------------------------------------------------|-----|

| Ta | ble   | of Contents                                    | iii |

| Li | st of | Figures                                        | vii |

| Li | st of | Tables                                         | x   |

| 1  | Int   | roduction                                      | 1   |

|    | 1.1   | A Perspective                                  | 1   |

|    | 1.2   | Goals and Organization                         | 2   |

| 2  | Hig   | h Speed Digital Signal Processing              | 4   |

|    | 2.1   | Introduction                                   | 4   |

|    | 2.2   | Video                                          | 5   |

|    | 2.3   | Image Processing                               | 6   |

|    | 2.4   | Speech Recognition                             | 7   |

|    | 2.5   | Computation Requirements of High Speed DSP     | 10  |

|    | 2.6   | Conclusions                                    | 12  |

| 3  | Arc   | hitectural Classification                      | 13  |

|    | 3.1   | Introduction                                   | 13  |

|    | 3.2   | Architectural Taxonomies                       | 14  |

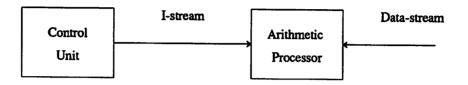

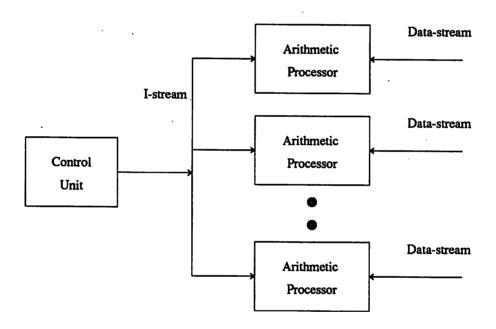

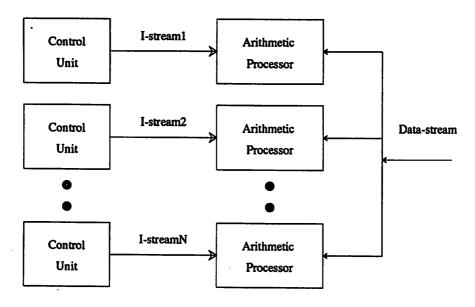

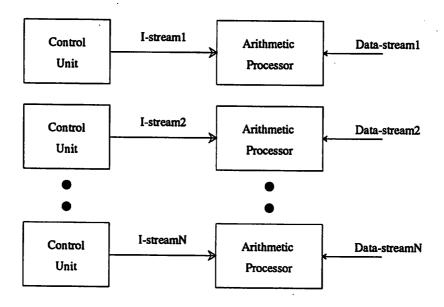

|    |       | 3.2.1 Flynn                                    | 14  |

|    |       | 3.2.2 Extensions to Flynn's Taxonomy           | 14  |

|    |       | 3.2.3 Telecommunications ASICs                 | 21  |

|    |       | 3.2.4 Image and Video Processing Architectures | 22  |

|    |       | 3.2.5 Digital Signal Processors                | 22  |

|    | 3.3   | Architectures for High Speed DSP               | 24  |

|    | 3.4   | Conclusions                                    | 26  |

| 4  | Rap   | oid Prototyping Platforms                      | 27  |

|    | 4.1   | Introduction                                   | 27  |

|    | 4.2   | Implementation Platforms                       | 28  |

CONTENTS

|   |            | 4.2.1  | Programmable DSPs                                         |

|---|------------|--------|-----------------------------------------------------------|

|   |            | 4.2.2  | Generic Components                                        |

|   |            | 4.2.3  | ASICs                                                     |

|   | 4.3        | High 1 | Level Synthesis                                           |

|   |            | 4.3.1  | Microsystems: Chip Level                                  |

|   |            | 4.3.2  | Systems: Board Level                                      |

|   | 4.4        | _      | are-configurable Hardware                                 |

|   |            | 4.4.1  | Purdue CHiP                                               |

|   |            | 4.4.2  | Texas Instrument RIC                                      |

|   |            | 4.4.3  | CMU White Dwarf                                           |

|   |            | 4.4.4  | MIT RAP                                                   |

|   |            | 4.4.5  | Video Signal Processors (VSD's)                           |

|   |            | 7.7.0  | Video Signal Processors (VSP's)                           |

|   |            |        | Philips VSP                                               |

|   |            | 4.4.6  | ITT DataWave                                              |

|   |            |        | NTT VSP                                                   |

|   |            | 4.4.7  | Software Reconfigurable Transceiver                       |

|   |            | 4.4.8  | Field Programmable Gate Arrays                            |

|   |            | 4.4.9  | PADDI: Programmable Arithmetic Devices for High Speed DSP |

|   | 4.5        | Concl  | usions                                                    |

| 5 | DA1        | DDI. A | Anabitantunal Darian                                      |

| J | 5.1        |        | Architectural Design                                      |

|   | 5.2        | Design | luction                                                   |

|   |            | Desigi | a Goals                                                   |

|   | 5.3        | Dynar  | nic/Static and Hardware/Software Interfaces               |

|   |            | 5.3.1  | Design Methodology                                        |

|   |            | 5.3.2  | Functional Design                                         |

|   |            |        | Operator Statistics                                       |

|   |            |        | Interconnect Statistics                                   |

|   |            |        | Control Statistics                                        |

|   |            |        | IO Statistics                                             |

|   |            |        | Computation Rate Statistics                               |

|   | <b>5.4</b> | Techni | iques for High Performance                                |

|   | 5.5        | Proces | ssor Architecture                                         |

|   |            | 5.5.1  | Execution Units                                           |

|   |            |        | Design Considerations                                     |

|   |            |        | Execution Unit Architecture                               |

|   |            | 5.5.2  | Interconnection Network                                   |

|   |            |        | Design Considerations                                     |

|   |            |        | Interconnect Network Architecture                         |

|   |            | 5.5.3  | Control                                                   |

|   |            | J.J.J  | Decign Considerations                                     |

|   |            |        | Design Considerations                                     |

|   |            | E E 4  | Control Architecture                                      |

|   |            | 5.5.4  | 10                                                        |

|   |            | 5.5.5  | Memory                                                    |

|   |            | 5.5.6  | Configuration                                             |

CONTENTS

|   |     | Design Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 82                   |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|   | 5.6 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 83                   |

|   | 5.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                   |

|   | 5.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                   |

|   | 5.9 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 86                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

| 6 |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88                   |

|   | 6.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88                   |

|   | 6.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 89                   |

|   | 6.3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91                   |

|   | 6.4 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00                   |

|   | 6.5 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 04                   |

|   |     | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 04                   |

| • |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 06                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 06                   |

|   | 6.6 | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 09                   |

|   |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 09                   |

|   |     | • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 10                   |

|   | 6.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 12                   |

|   |     | <u>▼</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 12                   |

|   |     | · -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 15                   |

|   | 6.8 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17                   |

|   | 6.9 | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 21                   |

| 7 | ΡΔΊ | DDI: Software Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22                   |

| • | 7.1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22                   |

|   | 7.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22<br>22             |

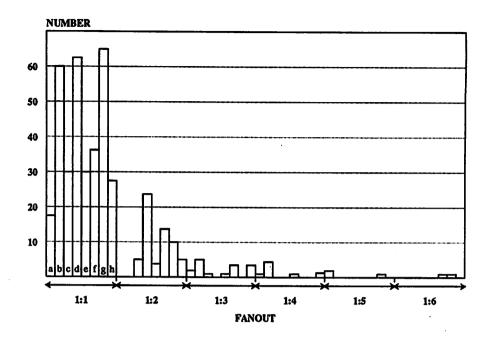

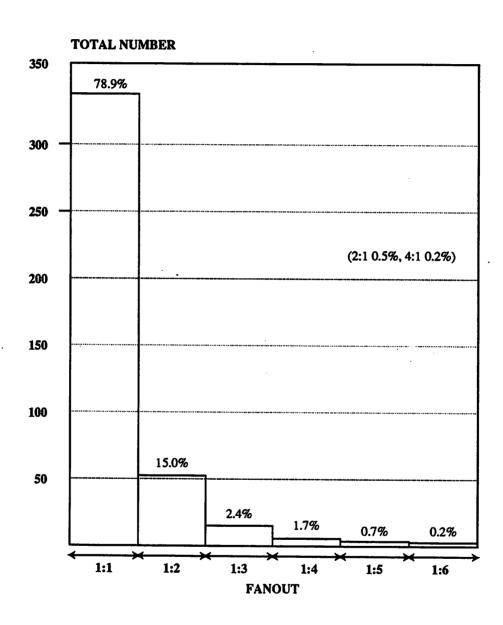

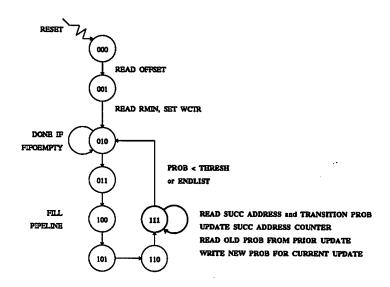

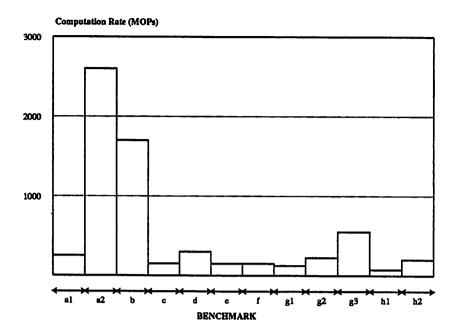

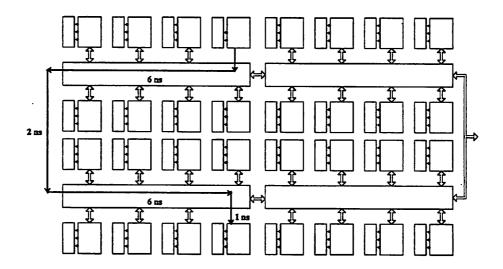

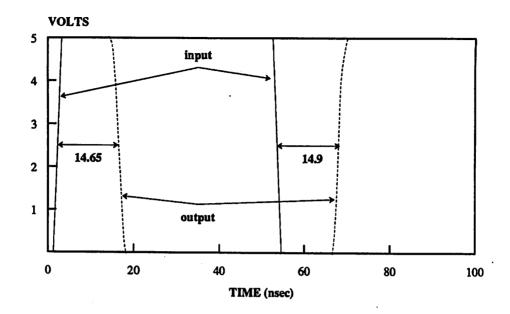

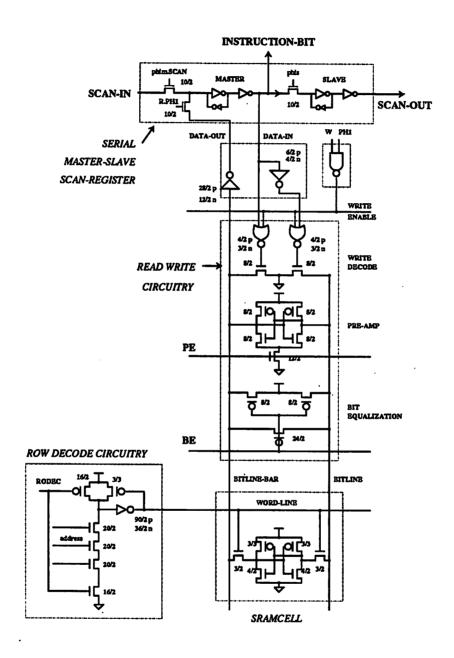

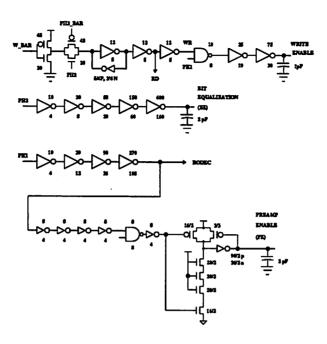

|   | 1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 23                   |