# Copyright © 1992, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

by

Chung-Sheng Li

Memorandum No. UCB/ERL M92/59

2 June 1992

Copyright © 1991

by

Chung-Sheng Li

Memorandum No. UCB/ERL M92/59

2 June 1992

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

Copyright © 1991

by

Chung-Sheng Li

Memorandum No. UCB/ERL M92/59

2 June 1992

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

by

# Chung-Sheng Li

#### **Abstract**

Optical interconnect technology has the potential to provide larger bandwidth and better noise immunity than existing electrical interconnect technology for high-speed digital systems. Both the bandwidth and the noise immunity are limited in the electrical interconnect technology at the backplane, the board, and the multi-chip-module levels by problems such as reflections, ground-loop noise, crosstalk, frequency-dependent signal distortion, and capacitive loading effect. However, an optical interconnect system might still be limited in density and speed due to optical and electrical crosstalk either from neighboring channels or through the shared power supply. This thesis is thus focused on analyzing problems arising from using dense optical interconnects in a high-speed digital system.

Fully Differential Optical Interconnect. A fully differential optical interconnect concept is proposed and analyzed in this thesis to overcome the electrical noise problems. Furthermore, a series of fully differential driver and receiver array chips with maximum array size from 4 to 12 using advanced bipolar, BiCMOS and GaAs technology have been designed and fabricated. Extensive circuit simulations verify the new design of the driver and the receiver, which are fully functional at 2.5 and 1 Gbps, respectively, with the capability of supporting less than 200ps signal rise time. In order to address the electrical packaging issues, models of the laser transmitter array and receiver array are developed to examine the influences of system performance through thermal noise, parasitic capacitance, and coupling through the substrate and power supply. Our study shows that it is possible to drive a large number of differentially configured laser drivers and receivers (≥ 32 if the maximum allowable switching noise is 25%) at 1 Gbps in a monolithic integration environment using a common power supply. Single-ended drivers or receivers are far more sensitive to noise, and are not recommended for this application.

Interconnect Density. Crosstalk models that incorporate detailed device models for each individual optical and optoelectronical component in a system have been developed and used to evaluate the density of the optical channels in a waveguide array environment as well as in a Wavelength-Division-Multiplexed (WDM) environment. The results show that the interference between the waveguides can contribute a significant amount of crosstalk, and the effect depends on the coherence of the signals carried in the adjacent waveguides. Using a 1 dB power penalty criterion, we show that the crosstalk between adjacent waveguides must be smaller than -12 dB and -25 dB for wavelength noncoinciding and coinciding monochromatic light sources, respectively, in order to achieve a bit-error rate smaller than  $10^{-15}$ . These crosstalk requirements limit the spacing between adjacent single-mode waveguides to  $\approx 10 \ \mu m$ . Instead of transmitting different channels through different waveguides, it is also possible to transmit different channels through the same waveguide but at different wavelengths. In contrast to a waveguide-based interconnect system, channel den-

sity of a WDM-based system using OOK is limited by the transient chirp of the laser diode and the crosstalk allowed by the optical filter. The combined effect is significant for high bit-rate channels. Our results indicate that a minimum channel spacing of  $\geq$  30 GHz, with each channel operating at 2 Gbps, is needed with the use of commercially available DFB laser diodes and optical filters.

System Requirements. Analytical models for high-speed synchronous and self-timed interconnect systems have been developed and analyzed to derive system-level requirements (such as rise time, the maximum allowable skew, and the latency) of using optical interconnects for high speed digital systems. Optical clock distribution using single-stage architecture and multi-stage architecture with optical amplifiers has been evaluated using these models. The results show that such a multi-stage distribution network can improve the total number of fanout by several orders of magnitude when compared to that obtained from a single-stage distribution network. Experimental results are consistent with those predicted by the analytical model.

Lavid St Plessendmitt 11/27/9/

Professor David G. Messerschmitt

Chairman, Thesis Committee

To my parents,

An-Min and Kuei-Yueh Li

#### **ACKNOWLEDGEMENTS**

I am grateful to my advisor, Prof. David G. Messerschmitt, for his generous and continuous support, encouragement and guidance throughout my graduate career. My supervisor at IBM, Dr. Harold S. Stone, who also served on my thesis committee, has been a tremendous source of guidance, support, and inspiration during the last two years. I also wish to thank Dr. Paul E. Green Jr. for his technical guidance in my WDM/WDMA work and his generosity in providing lab space during my stay in IBM, and thank Dr. Stephen S. Lavenberg for his unreserved support of my projects during my stay in IBM. Many thanks go to Drs. Karen Liu, Franklin Tong, C. Michael Olsen, Michael M. Choy, Rajiv Ramaswami, Richard Bates, and John D. Crow, who have been of great help in giving me basic understanding of optical devices and systems, and to Drs. Kai-Yap Toh, Young Hoon Kwark, Peter Lim, and Dennis Rogers, who assisted me in understanding circuit design, and to Drs. Y. Kwark, F. Tong, Randall A. Cieslak, Kumar Sivaraj, and Rajesh Pankaj for their careful reviewing of the chapters in this thesis.

I would like to thank Profs. T. K. Gustafson, Paul R. Gray, Michael Klass, for serving on my qualifying examination committee, and Profs. Joseph M. Kahn and Michael Klass for participating in my thesis committee. I would also like to thank numerous discussions with Profs. Kam Lau, Randy Katz, Jean Walrand, Richard Newton, Robert G. Meyer, and Abhiram Ranade during my graduate study.

The work reported here was supported by California MICRO and a grant from IBM. This work is performed at both U.C. Berkeley and IBM Thomas J. Watson Research Center, Yorktown Heights, New York.

The transmission line models in Chapter 2 are characterized by W. P. Smetana and A. Deutsch. Chapters 4 and 6 of this thesis were joint work with F. Tong and K. Liu, Chapter 5 was joint work with C. M. Olsen. Chapter 8 has used simulation models from K. Toh and D. Rogers. Chapter 10 came out of a collaboration with K. Toh and H. Ainspan. Chapter 11 uses a circuit designed by Y. Kwark and also came out of a collaboration with Y. Kwark and K. Wrenner. The

chip photographs in Chapter 11 were taken by K. P. Jackson, digitized by J. C. Lee, and the digitized images were processed using a halftoning program developed by G. R. Thompson.

Finally, a word of thanks to Ming-Kang Liu, Ping-San Tzeng, Bernard Shung, Alex Lee, Ming-Chang Wu, Wen-Lung Chen, Teresa H.-Y. Meng, Horng-dar Lin, Limin Hu, Shih-Fu Chang, Vijay Maddisetti, Meng-Hsiung Kiang and many others of my friends who continuously provide moral and technical support during my graduate study in Berkeley, and to Long-Sheng Fan in particular, for many inspirational days when we live in the same house. I am also grateful to Wei-Yi Li, my nephew, for his help in serving as a great communicator between me and Berkeley while I was in New York.

# Contents

| CHAPTER 1 INTRODUCTION                                   | 1        |

|----------------------------------------------------------|----------|

| 1.1 Motivation                                           | 1        |

| 1.1.1 Reflections                                        | 3        |

| 1.1.2 Ground-loop noise                                  | 4        |

| 1.1.3 Crosstalk among adjacent interconnects             | 4        |

| 1.1.4 Frequency-dependent signal distortion              | 5        |

| 1.2 Optical Interconnects for High-Speed Digital Systems | 5        |

| 1.2.1 Potential advantages                               | <b>6</b> |

| 1.2.2 Potential problems                                 | 7        |

| 1.3 Architecture of Dense Optical Interconnects          | 9        |

| 1.3.1 Interconnect media                                 | 9        |

| 1.3.2 Backplane optical interconnects                    | . 10     |

| 1.3.3 Board and multi-chip-module optical interconnects  | . 11     |

| 1.4 Differential Optical Interconnection                 | . 13     |

| 1.5 Prior Art of Optical Interconnects                   | . 16     |

| 1.6 Contribution of This Thesis                          | . 16     |

| 1.7 Thesis Outline                                       | . 17     |

|                                                          |          |

| CHAPTER 2 MODELING AND PERFORMANCE EVALUATION OF METAL   |          |

| INTERCONNECTS                                            | . 19     |

| 2.1 Introduction                                         | . 19     |

| 2.2 Multi-Chip Module Level Metal Interconnects          | . 21     |

| 2.2.1 Modeling                                           | . 21     |

| 2.2.2 Simulation Results                                 | . 25     |

| 2.3 Board Level Metal Interconnects                      | . 28     |

| 2.3.1 Modeling                                           | 29       |

| 2.3.2 Simulation Results                                          | 30 |

|-------------------------------------------------------------------|----|

| 2.4 Backplane Level Metal Interconnects                           | 32 |

| 2.4.1 Modeling                                                    | 32 |

| 2.4.2 Simulation Results                                          | 34 |

| 2.5 Summary                                                       | 36 |

| •                                                                 |    |

| CHAPTER 3 STATISTICAL ANALYSIS OF TIMING RULES FOR SYNCHRONOUS    |    |

| INTERCONNECTS                                                     | 41 |

| 3.1 Introduction                                                  | 41 |

| 3.2 Sources of Timing Skew                                        | 43 |

| 3.2.1 Static skew                                                 | 46 |

| 3.2.1.1 Variation of propagation length and signal group velocity | 46 |

| 3.2.1.2 Device Variation                                          | 47 |

| 3.2.2 Random skew                                                 | 49 |

| 3.2.2.1 Timing Jitter on the Clock Sources                        | 49 |

| 3.2.2.2 Circuit Noise                                             | 49 |

| 3.3 Timing Rules for Synchronous Bus Systems                      | 50 |

| 3.3.1 Conservative design                                         | 51 |

| 3.3.2 Aggressive design                                           | 56 |

| 3.4 Timing Rules for Finite State Machines                        | 58 |

| 3.5 Throughput Improvement from Pipelined Architecture            | 61 |

| 3.5.1 Pipelined approach                                          | 61 |

| 3.5.2 Nonpipelined approach                                       | 64 |

| 3.6 Numerical Results                                             | 66 |

| 3.7 Summary                                                       | 70 |

|                                                                   |    |

| CHAPTER 4 CLOCK DISTRIBUTION USING OPTICAL AMPLIFIERS             | 71 |

| 4.1 Introduction                                                  |    |

| 4.2 Architecture of Clack Distribution Networks                   | 72 |

| 4.3 Clock Skew Analysis                                         | 74         |

|-----------------------------------------------------------------|------------|

| 4.3.1 Distribution skew                                         | 76         |

| 4.3.2 Receiver static skew                                      | 77         |

| 4.3.3 Receiver random skew                                      | <b>7</b> 9 |

| 4.4 Maximum Fanout of a Single-Stage Clock Distribution Network | 81         |

| 4.5 Maximum Fanout For Multistage Distribution Network          | 88         |

| 4.5.1 Modeling of multi-stage amplifier chain                   | 88         |

| 4.5.2 Maximum fanout calculation                                | 89         |

| 4.6 Experimental Results                                        | 98         |

| 4.7 Summary                                                     | 103        |

|                                                                 |            |

| CHAPTER 5 CROSSTALK MODELING OF DENSE SINGLE-MODE WAVEGUIDE     |            |

| ARRAY                                                           | 109        |

| 5.1 Introduction                                                | 109        |

| 5.2 Waveguide Array Model                                       | 110        |

| 5.3 Formulation of Waveguide Crosstalk                          | 117        |

| 5.3.1 Adjacent channel crosstalk                                | 117        |

| 5.3.2 Total receiver noise                                      | 119        |

| 5.3.3 Calculation of optimal threshold level                    | 120        |

| 5.4 SYSTEM PENALTY DUE TO ADJACENT CHANNEL CROSSTALK            | 121        |

| 5.4.1 Noncoinciding Uncorrelated Light Sources                  | 121        |

| 5.4.2 Coinciding Uncorrelated Light Sources                     | 124        |

| 5.4.3 Coinciding Correlated Light Sources                       | 125        |

| 5.4.4 Discussion                                                | 127        |

| 5.5 SUMMARY                                                     | 132        |

|                                                                 |            |

| CHAPTER 6 DENSE WDM/WDMA SYSTEMS                                | 143        |

| 6.1 Introduction                                                | 143        |

| 6.2 Derivation of System Penalty                                | 145        |

| 6.3 Simulation Models                               | . 148 |

|-----------------------------------------------------|-------|

| 6.4 Simulation                                      | . 155 |

| 6.5 System Optimization                             | . 173 |

| 6.6 Dense WDM/WDMA-FSK Systems                      | . 181 |

| 6.7 Conclusions                                     | . 186 |

| CHAPTER 7 DENSE TRANSMITTER ARRAYS                  | . 187 |

| 7.1 Introduction                                    | . 187 |

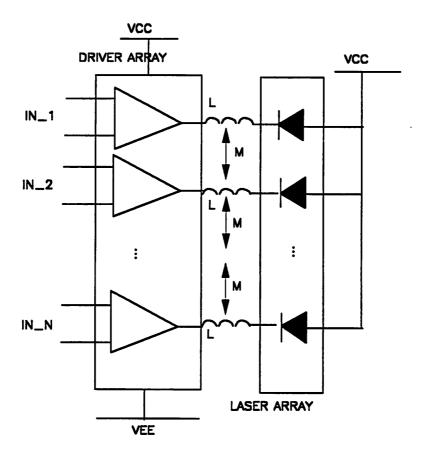

| 7.2 Transmitter Array Modeling                      | . 188 |

| 7.2.1 Laser Modeling                                | . 188 |

| 7.2.2 Single-Ended Driver                           | . 190 |

| 7.2.3 Differential Driver                           | . 190 |

| 7.3 Switching Noise Analysis of Single-Ended Driver | . 191 |

| 7.4 Simulation of Differential Driver               | . 193 |

| 7.4.1 Simulation Methodology                        | . 193 |

| 7.4.2 Simulation Results                            | . 194 |

| 7.5 Summary                                         | . 196 |

| CHAPTER 8 DENSE RECEIVER ARRAYS                     | . 201 |

| 8.1 Introduction                                    | . 201 |

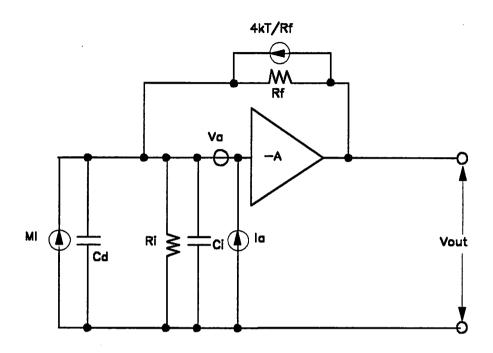

| 8.2 Receiver Array Model                            | . 203 |

| 8.3 Simulation Methodology                          | . 206 |

| 8.4 Single-Ended Receiver                           | . 206 |

| 8.5 Differential Receivers                          | . 213 |

| 8.6 Summary                                         | . 213 |

| CHAPTER 9 DIFFERENTIAL OPTICAL INTERCONNECTS        | 217   |

| 9.1 Introduction                                    | . 217 |

| 9.2 Optical Interconnect Architectures              | 210   |

| 9.2.1 Single-Ended Interconnect                          | 219 |

|----------------------------------------------------------|-----|

| 9.2.1.1 Disadvantages                                    | 219 |

| 9.2.1.2 Advantages                                       | 222 |

| 9.2.2 Differential Interconnect                          | 222 |

| 9.2.2.1 Disadvantages                                    | 222 |

| 9.2.2.2 Advantages                                       | 223 |

| 9.3 Implementation of Differential Optical Interconnects | 225 |

| 9.3.1 External Modulators                                | 225 |

| 9.3.2 Time Division Multiplexing Technique               | 228 |

| 9.3.3 Frequency Division Multiplexing Technique          | 230 |

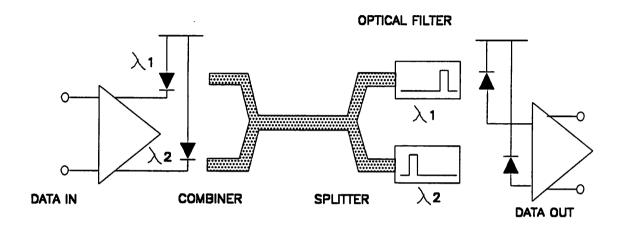

| 9.3.4 Wavelength Division Multiplexing                   | 231 |

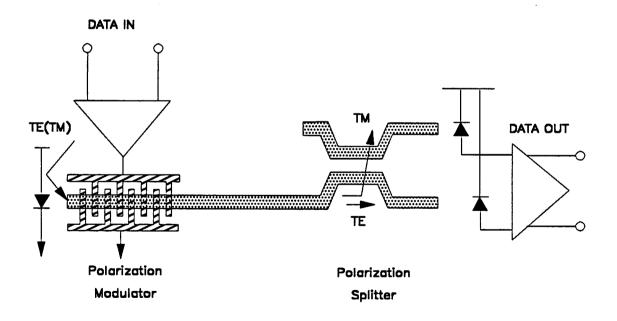

| 9.3.5 Polarization Division Multiplexing Technique       | 233 |

| 9.4 Receiver Sensitivity Analysis                        | 234 |

| 9.4.1 Single-ended optical interconnect                  | 234 |

| 9.4.2 Differential Optical Interconnect                  | 239 |

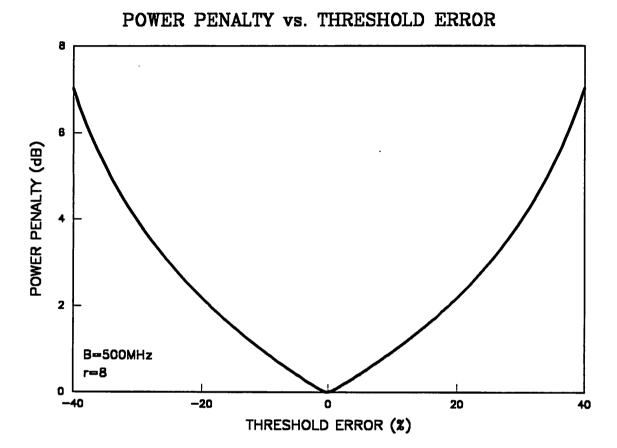

| 9.5 System Degradation Due to Channel Mismatch           | 242 |

| 9.5.1 Threshold Offset                                   | 242 |

| 9.5.2 System Penalty                                     | 246 |

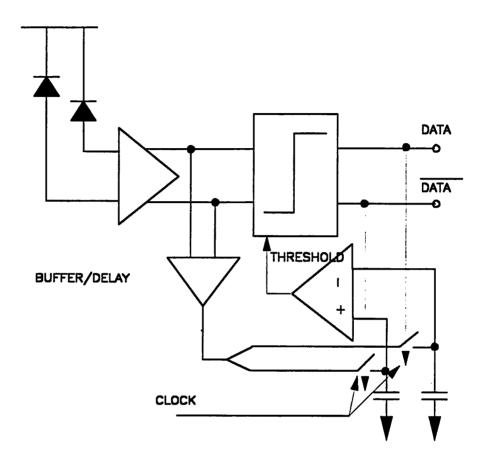

| 9.6 Mismatch Cancellation Techniques                     | 247 |

| 9.6.1 Periodic Null Insertion                            | 247 |

| 9.6.2 Average Computation                                | 248 |

| 9.6.3 Decision Feedback Average Computation              | 248 |

| 9.7 Summary                                              | 248 |

|                                                          |     |

| CHAPTER 10 FULLY DIFFERENTIAL TRANSMITTER ARRAY          | 251 |

| 10.1 Introduction                                        | 251 |

| 10.2 Circuit Design                                      | 252 |

| 10.3 Physical Circuit Layout                             | 255 |

| In 4. Simulation Results                                 | 256 |

| 10.5 Summary                                                    | 261 |

|-----------------------------------------------------------------|-----|

| CHAPTER 11 FULLY DIFFERENTIAL INTEGRATED OPTICAL RECEIVER ARRAY | 267 |

| 11.1 Introduction                                               | 267 |

| 11.2 Circuit Design                                             | 268 |

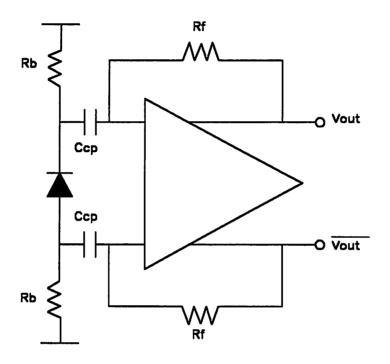

| 11.2.1 Preamplifier Array                                       | 268 |

| 11.2.2 Full Receiver Array                                      | 272 |

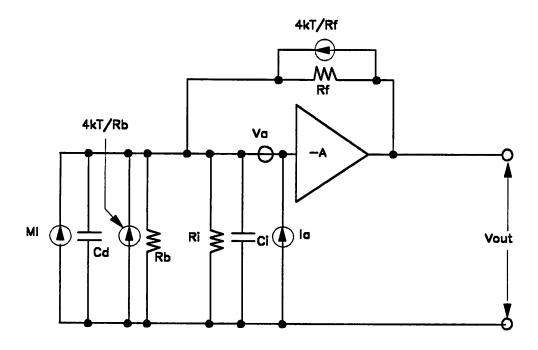

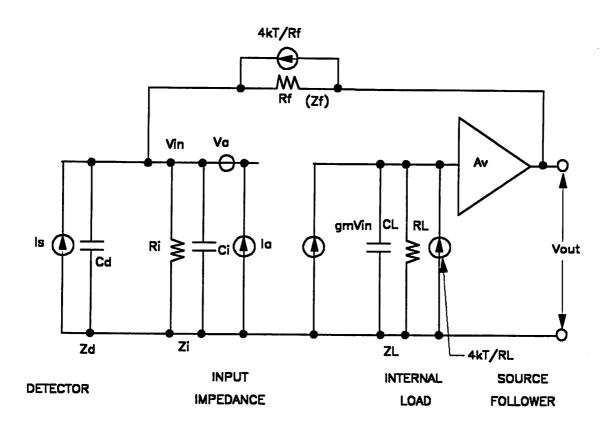

| 11.3 Receiver Sensitivity and Front-End Optimization            | 273 |

| 11.3.1 Receiver Sensitivity                                     | 273 |

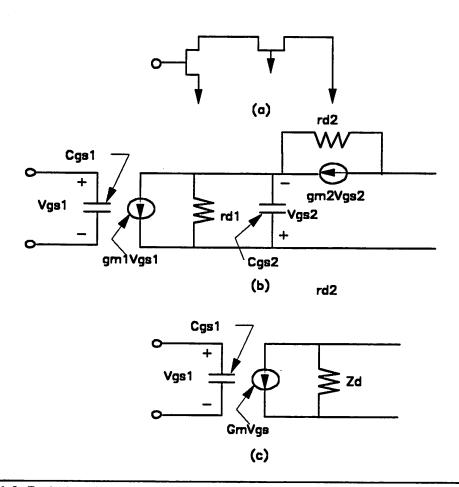

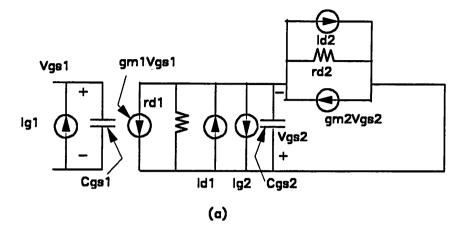

| 11.3.2 Preamp Optimization                                      | 274 |

| 11.3.3 MSM-PD Optimization                                      | 280 |

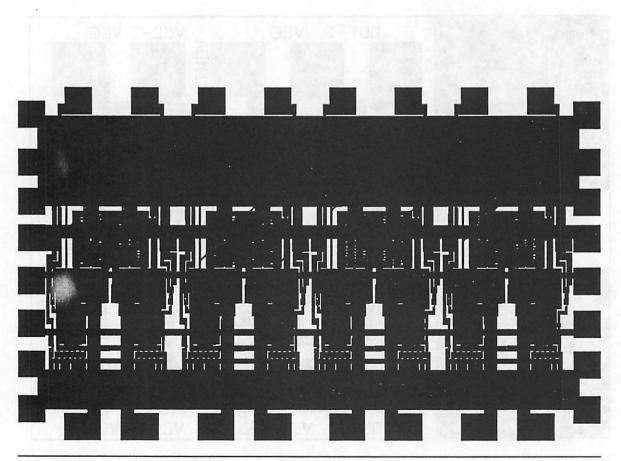

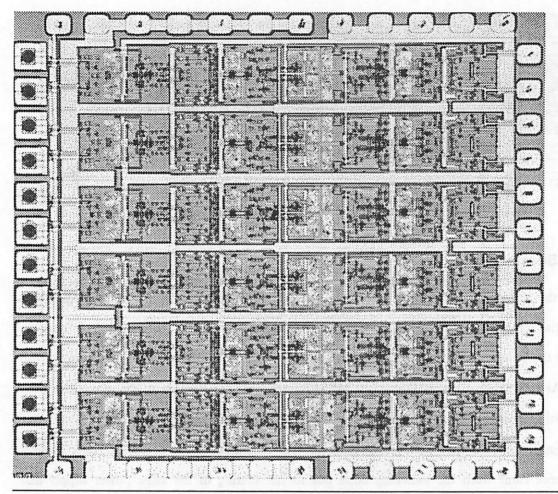

| 11.4 Chip Photographs of the Receiver Array                     | 284 |

| 11.4.1 Receiver Cell                                            | 284 |

| 11.4.2 Integrated Receiver Array                                | 284 |

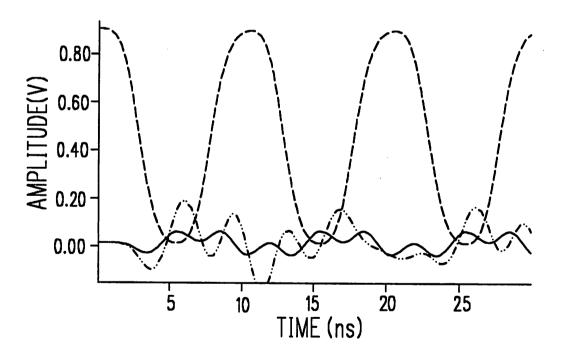

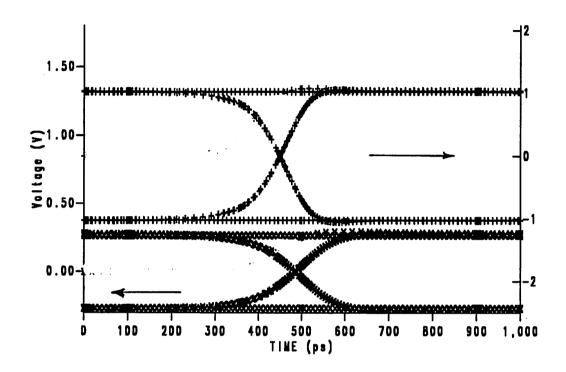

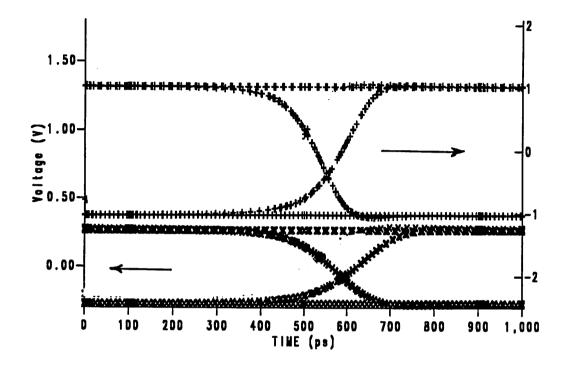

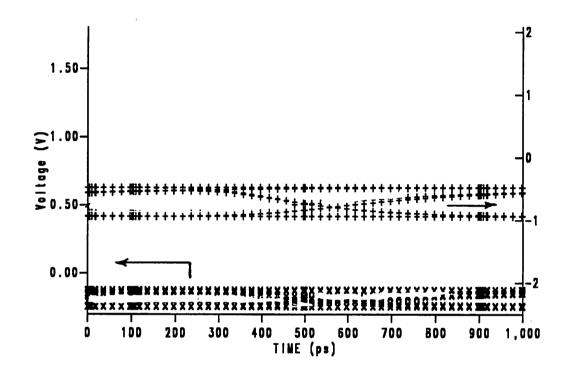

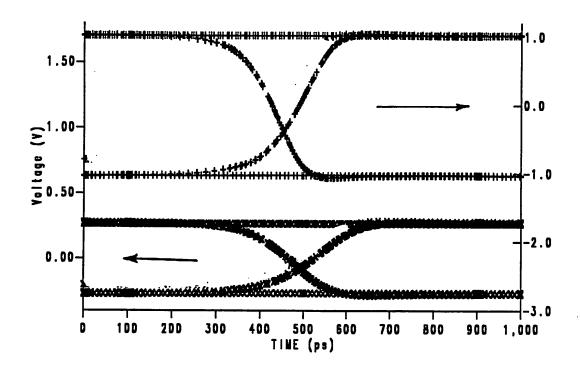

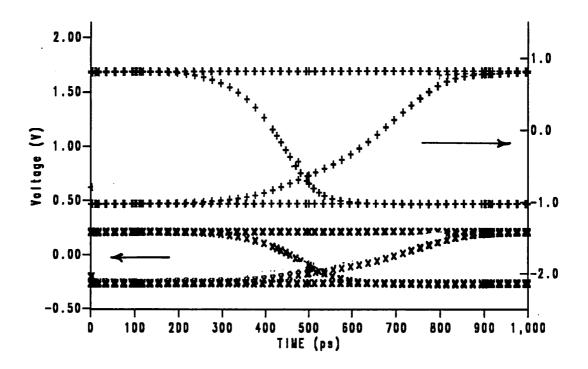

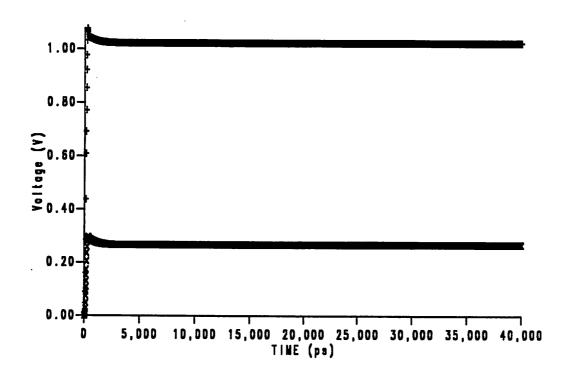

| 11.5 Simulation Results                                         | 284 |

| 11.6 Summary                                                    | 287 |

| CHAPTER 12 SUMMARY AND FUTURE WORK                              | 307 |

| 12.1 Summary                                                    | 307 |

|                                                                 | 309 |

| 12.2.1 Multi-Mode Waveguide                                     | 309 |

| 12.2.2 Fault-Tolerant Interconnect Architecture                 | 310 |

|                                                                 | 310 |

| 1004 7                                                          | 311 |

| Bibliography                                                    | 315 |

# List of Illustrations

| 1-1.  | Packaging hierarchy                                                                    | . 2 |

|-------|----------------------------------------------------------------------------------------|-----|

| 1-2.  | Optical backplane interconnects                                                        | 11  |

| 1-3.  | Optical backplane interconnects                                                        | 12  |

| 1-4.  | E/O and O/E conversion                                                                 | 13  |

| 1-5.  | E/O and O/E conversion                                                                 | 14  |

| 1-6.  | A fully differential optical interconnect architecture                                 | 15  |

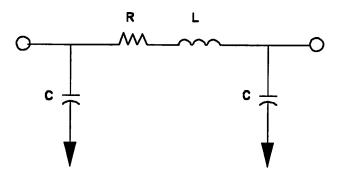

| 2-1.  | Structure of an electrical path for an MCM interconnect                                | 22  |

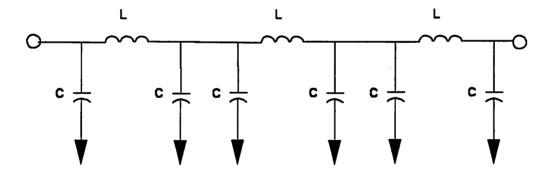

| 2-2.  | Circuit model of a typical multi-chip module interconnect                              | 23  |

| 2-3.  | Equivalent circuit for a electrical discontinuity                                      | 24  |

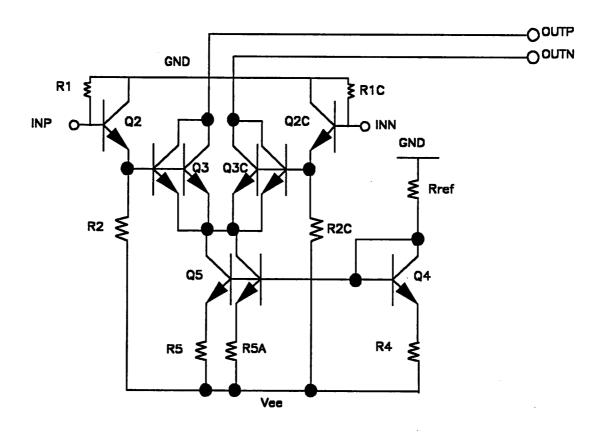

| 2-4.  | ECL driver and receiver circuit used for simulations                                   | 25  |

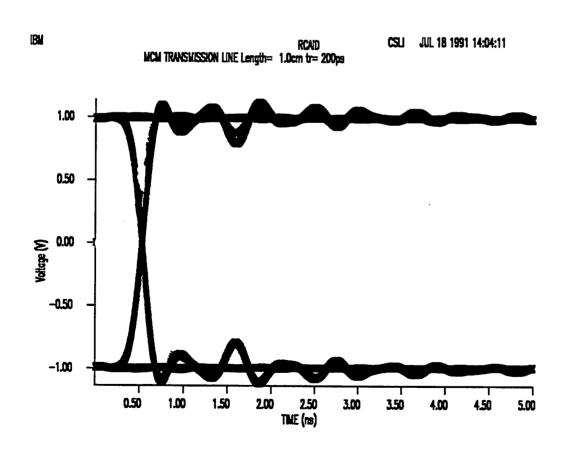

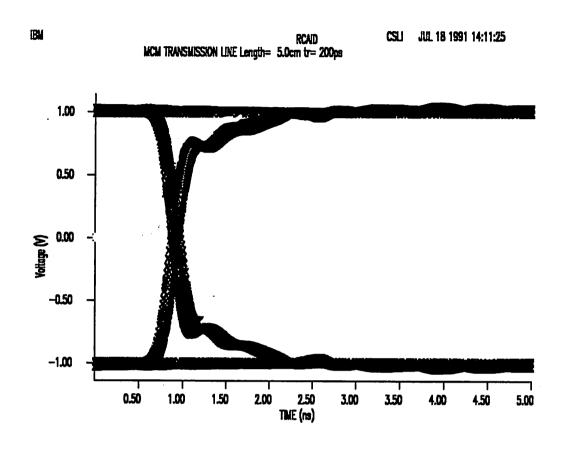

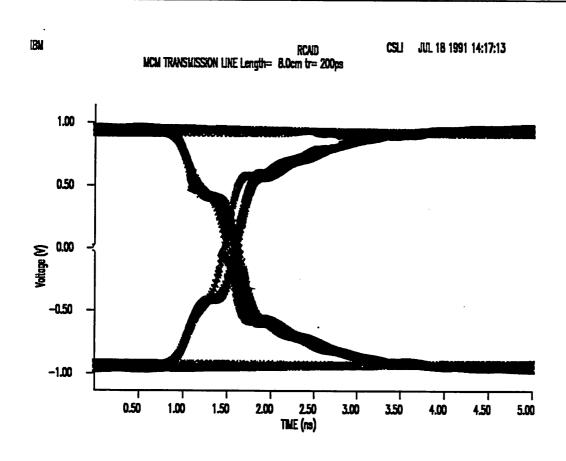

| 2-5.  | Simulated eye pattern of an MCM interconnect                                           | 26  |

| 2-6.  | Simulated eye pattern of an MCM interconnect                                           | 27  |

| 2-7.  | Simulated eye pattern of an MCM interconnect                                           | 28  |

| 2-8.  | Structure of a board level interconnect                                                | 29  |

| 2-9.  | Equivalent circuit of a board level metal interconnect                                 | 30  |

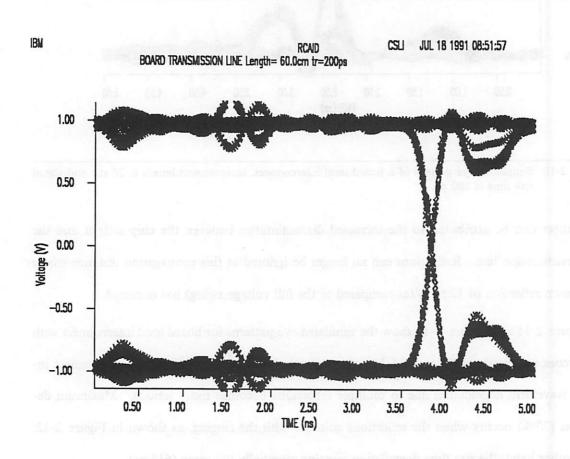

| 2-10. | Simulated eye pattern of a board level interconnect                                    | 31  |

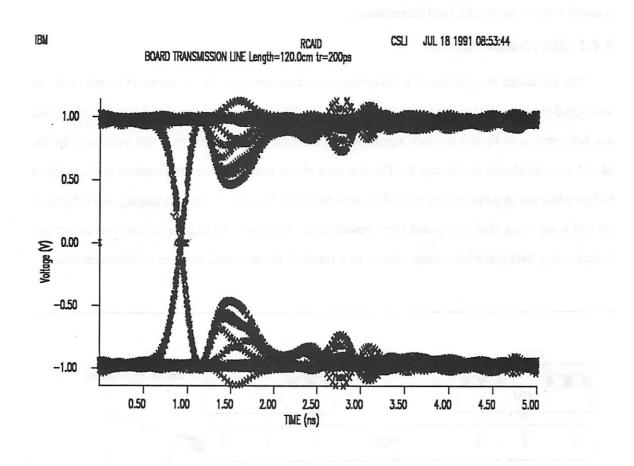

| 2-11. | Simulated eye pattern of a board level interconnect                                    | 32  |

| 2-12. | Simulated eye pattern of a board level interconnect                                    | 33  |

| 2-13. | Structure of a backplane interconnect                                                  | 34  |

| 2-14. | Equivalent circuit of a backplane level interconnect                                   | 35  |

| 2-15. | Equivalent circuit of a cable connector                                                | 36  |

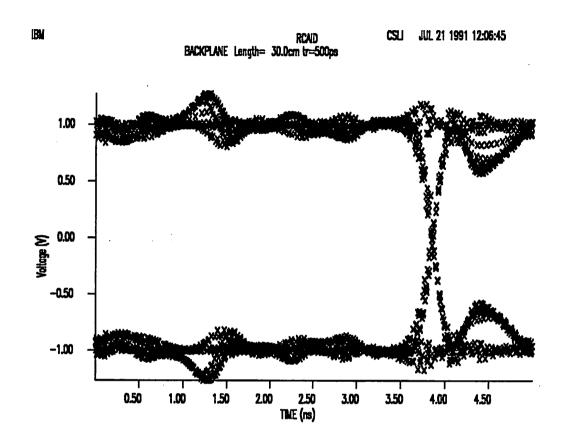

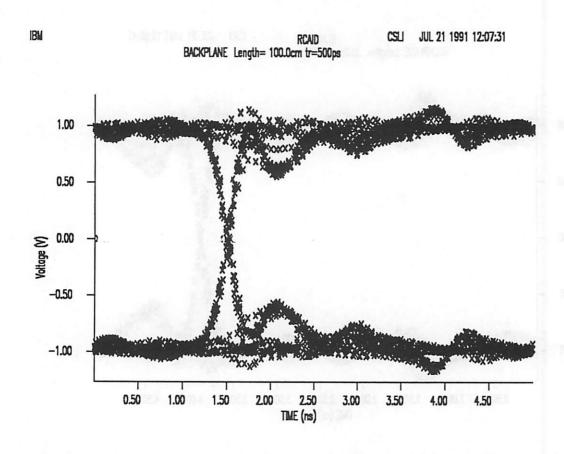

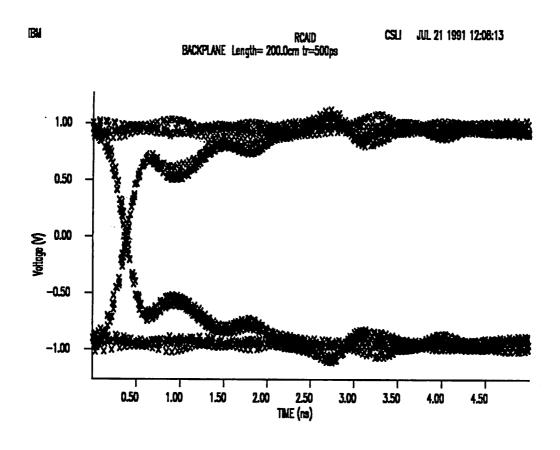

| 2-16. | Simulated eye pattern of a backplane interconnect                                      | 37  |

| 2-17. | Simulated eye pattern of a backplane interconnect                                      | 38  |

| 2-18. | Simulated eye pattern of a backplane interconnect                                      | 39  |

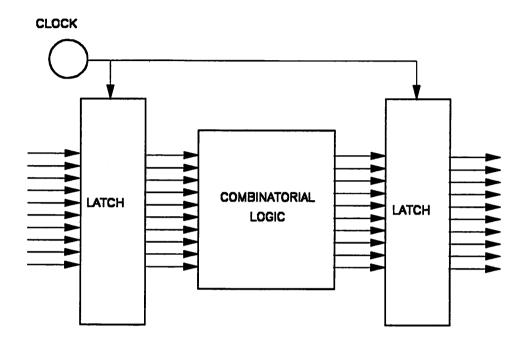

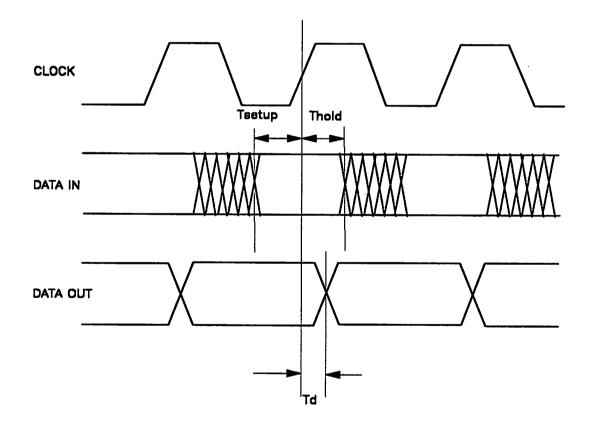

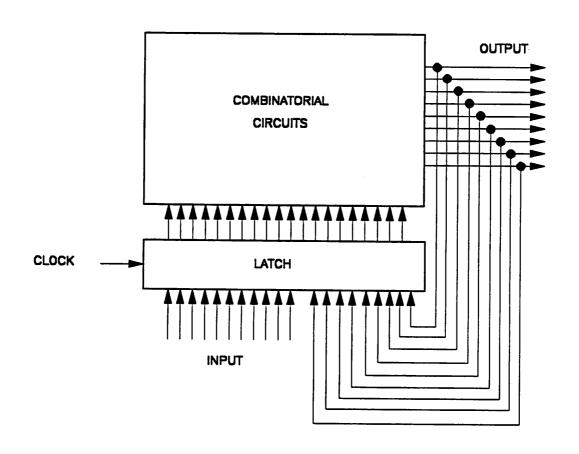

| 3-1.  | Architecture of a synchronous digital system                                           | 44  |

| 3-2.  | Timing relationship between the data input, clock input and the data output of a latch | 45  |

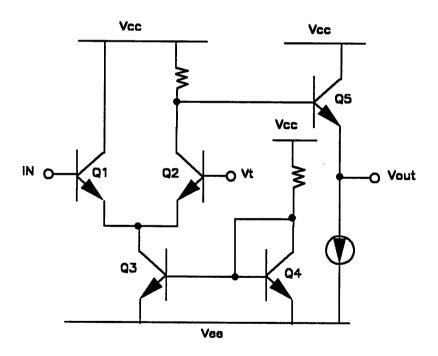

| 3-3.  | Circuitry of a typical ECL gate                                                          | 48 |

|-------|------------------------------------------------------------------------------------------|----|

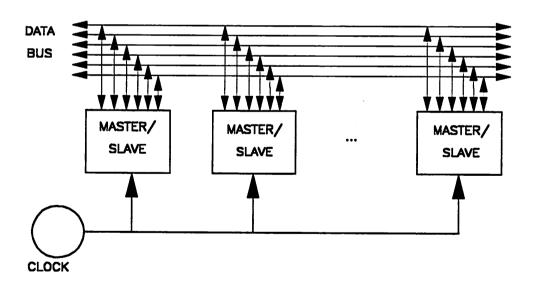

| 3-4.  | Architecture of a synchronous bus                                                        | 51 |

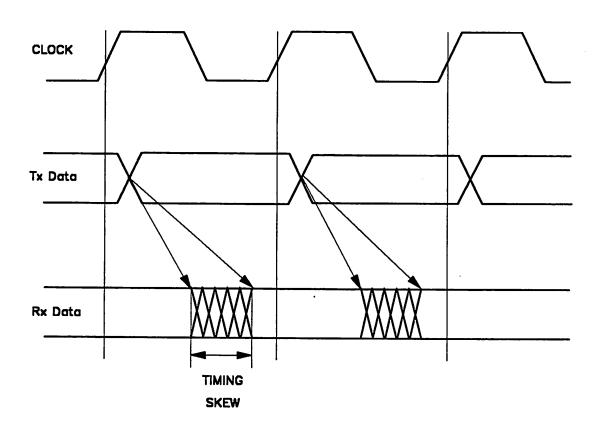

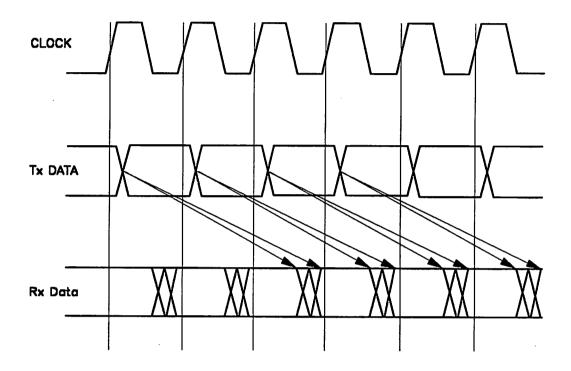

| 3-5.  | Timing relationship between the transmitter and the receiver in a synchronous bus        | 52 |

| 3-6.  | Timing relationship between the transmitter and the receiver in a synchronous bus        | 53 |

| 3-7.  | Architecture of a finite state machine                                                   | 59 |

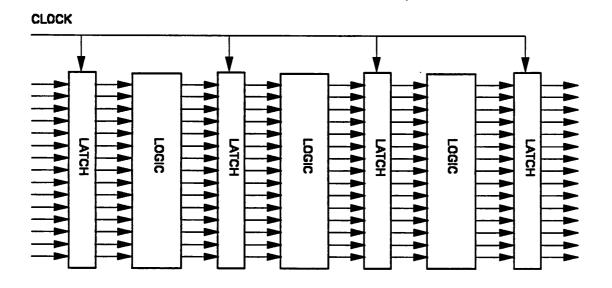

| 3-8.  | Architecture of a pipelined system                                                       | 62 |

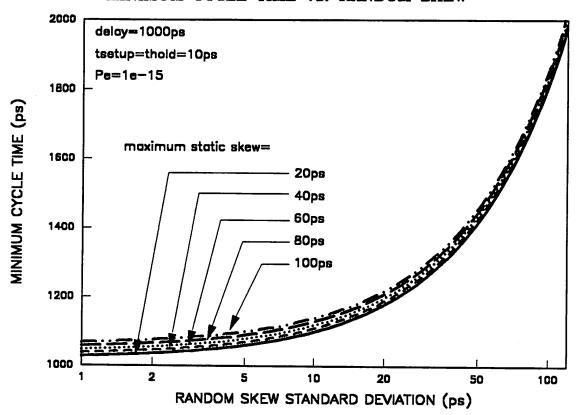

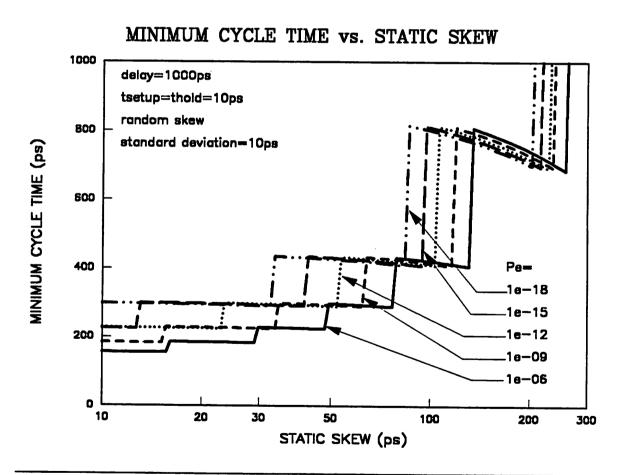

| 3-9.  | Minimum cycle time as a function of the standard deviation of the random skew .          | 65 |

| 3-10. | Minimum cycle time as a function of the standard deviation of the random skew for        |    |

|       | conservative design scheme                                                               | 66 |

| 3-11. | Minimum cycle time as a function of the standard deviation of the random skew for        |    |

|       | the aggressive design scheme                                                             | 67 |

| 3-12. | Minimum cycle time as a function of the standard deviation of the random skew for        |    |

|       | the aggressive design scheme                                                             | 68 |

| 3-13. | Minimum cycle time as a function of the standard deviation of the static skew for the    |    |

|       | aggressive design scheme                                                                 | 69 |

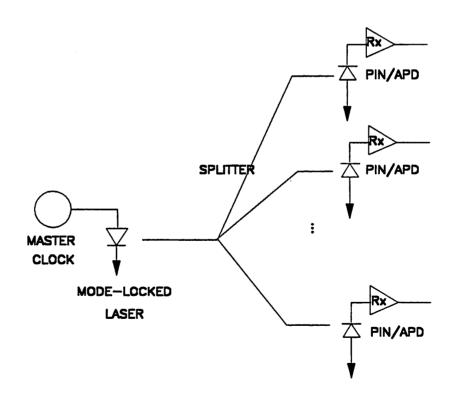

| 4-1.  | Architecture of a single-stage optical clock distribution                                | 74 |

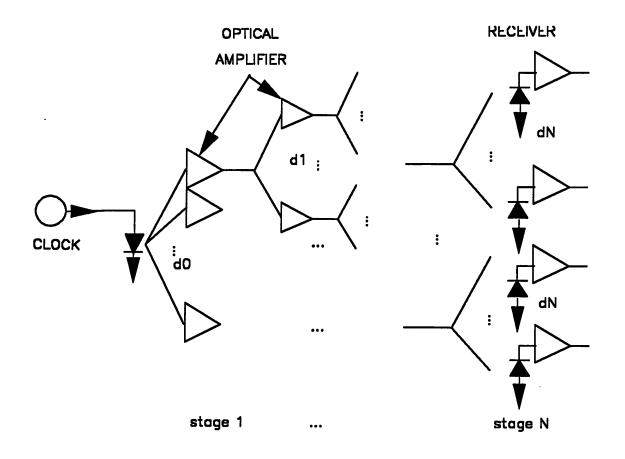

| 4-2.  | Architecture of a multi-stage optical clock distribution                                 | 75 |

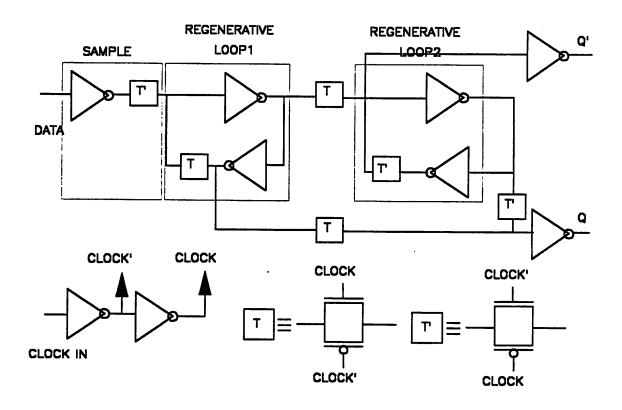

| 4-3.  | Circuit schematic of a typical CMOS flip-flop                                            | 80 |

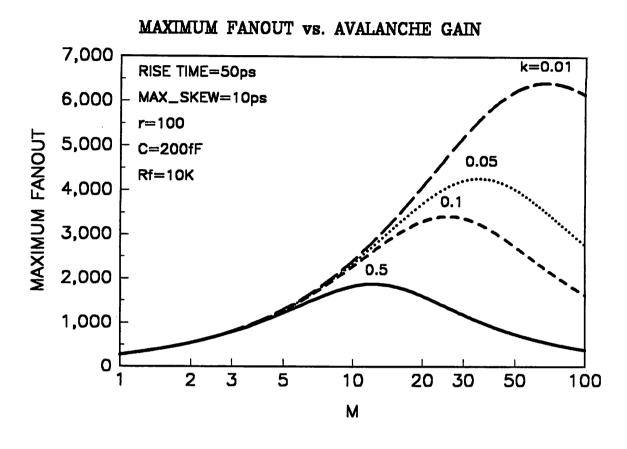

| 4-4.  | Maximum fanout as a function of avalanche gain for various ionization factor             | 81 |

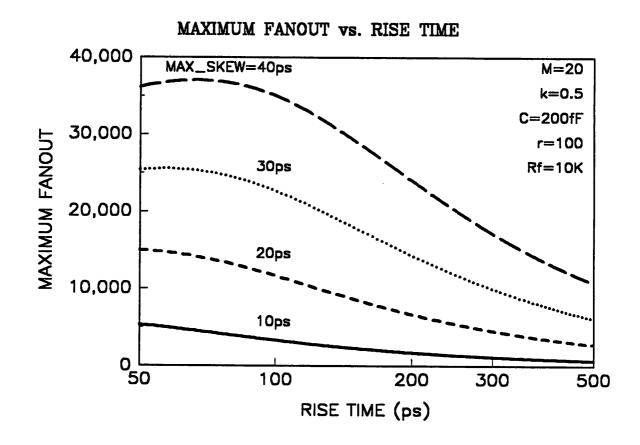

| 4-5.  | Maximum fanout of a single-stage clock distribution network                              | 82 |

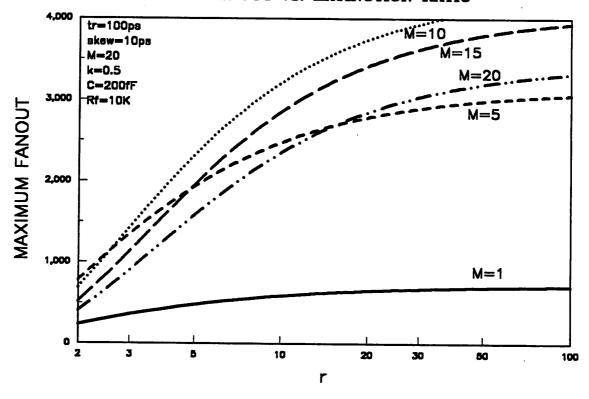

| 4-6.  | Maximum fanout as a function of extinction ratio for various values of avalanche gain    | 83 |

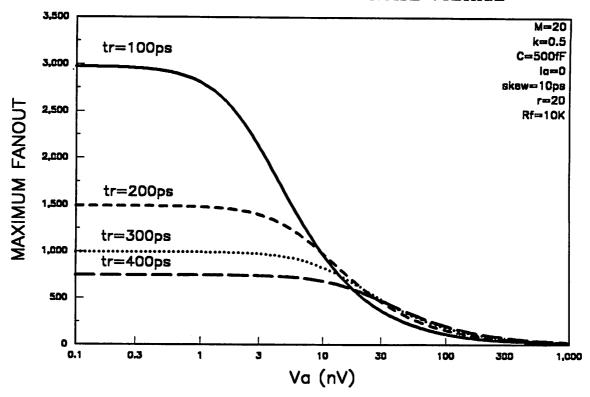

| 4-7.  | Maximum fanout as a function of receiver voltage noise for various values of clock rise  |    |

|       | time                                                                                     | 84 |

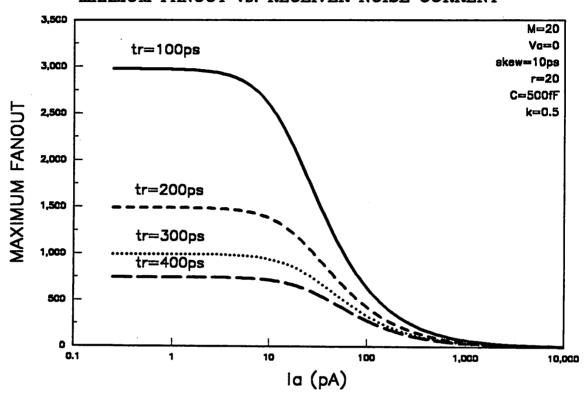

| 4-8.  | Maximum fanout as a function of receiver current noise for various values of clock rise  |    |

|       | time                                                                                     | 85 |

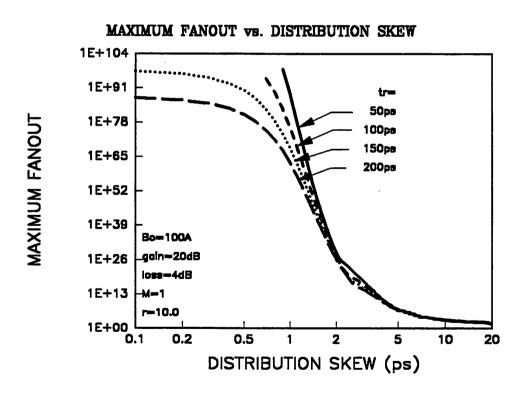

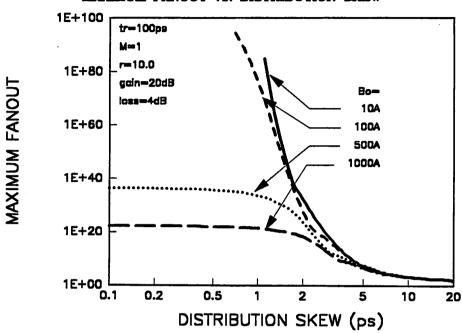

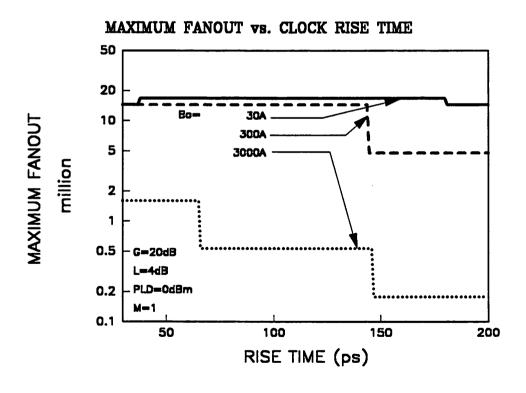

| 4-9.  | Maximum fanout as a function of distribution skew for various clock rise time            | 90 |

| 4-10. | Maximum fanout is plotted against distribution skew for various values of optical filter |    |

|       | bandwidth                                                                                | 91 |

| 4-11. | Maximum famout as a function of clock rise time for various optical filter handwidths    | ດາ |

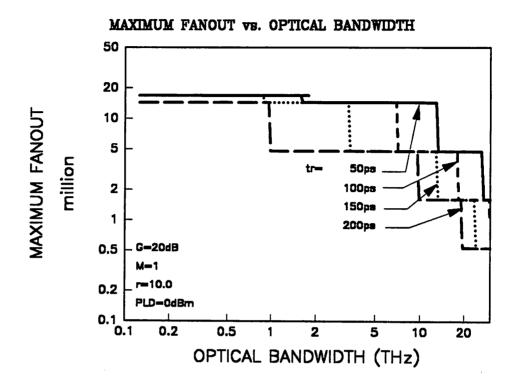

| 4-12.         | Maximum fanout vs. optical filter bandwidth for various clock rise time                | . 93 |

|---------------|----------------------------------------------------------------------------------------|------|

| 4-13.         | Maximum fanout as a function of avalanche gain for various values of ionization        |      |

|               | factor                                                                                 | . 94 |

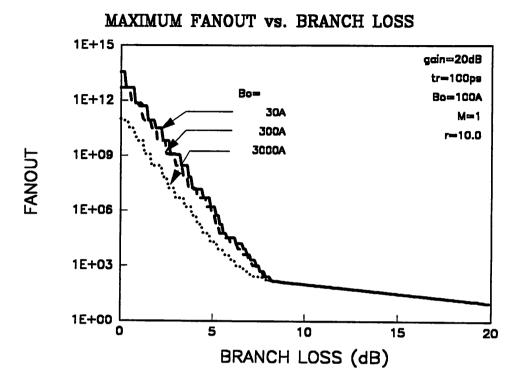

| 4-14.         | Maximum fanout as a function of branch loss for various optical filter bandwidths      | 95   |

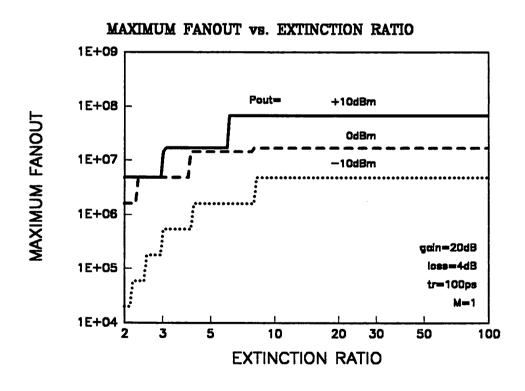

| 4-15.         | Maximum fanout as a function of extinction ratio of the clock signal for various value | S    |

|               | of laser output power                                                                  | . 96 |

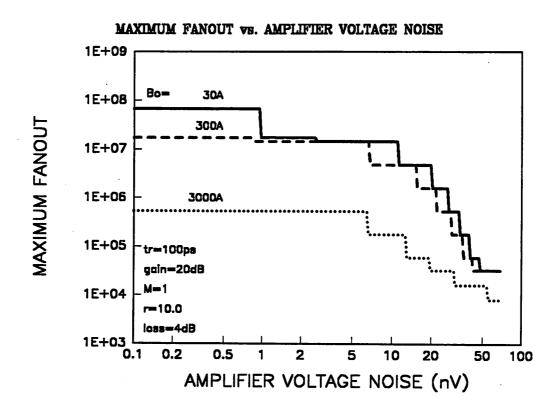

| 4-16.         | Maximum fanout vs. receiver voltage noise for various optical filter bandwidth         | . 97 |

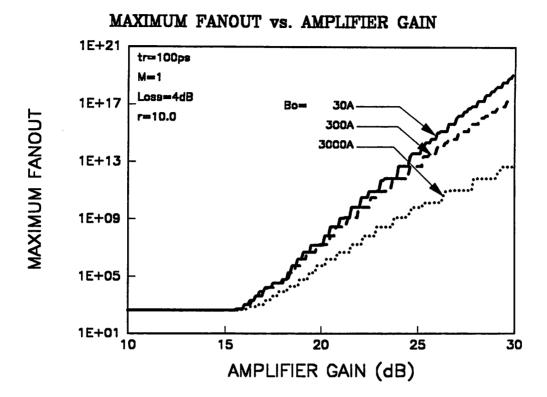

| 4-17.         | Maximum fanout as a function of amplifier gain for various optical filter bandwidth    | s 98 |

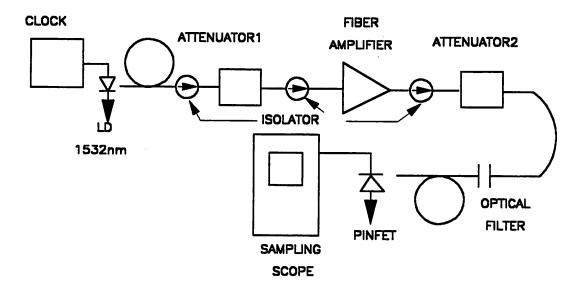

| 4-18.         | Schematic of the clock distribution experiment setup                                   | . 99 |

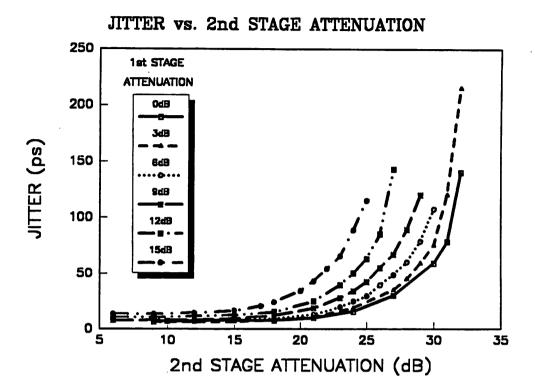

| <b>4-</b> 19. | Jitter as a function of second-stage splitting                                         | 100  |

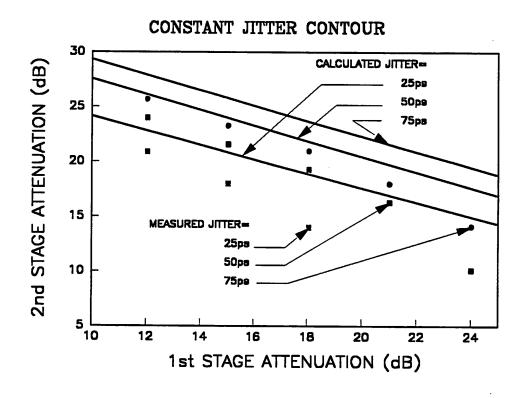

| 4-20.         | Comparison of experimental and calculated constant rms jitter contour                  | 101  |

| 4-21.         | Total attenuation is plotted against the first stage attenuation for various values of |      |

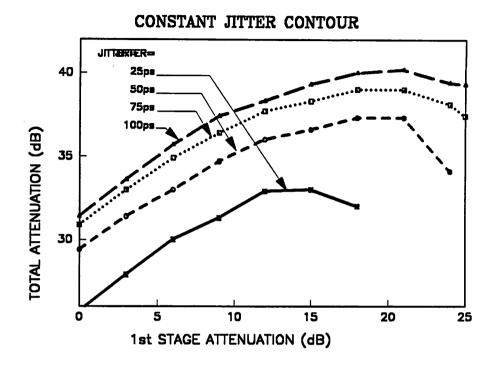

|               | constant rms jitter                                                                    | 102  |

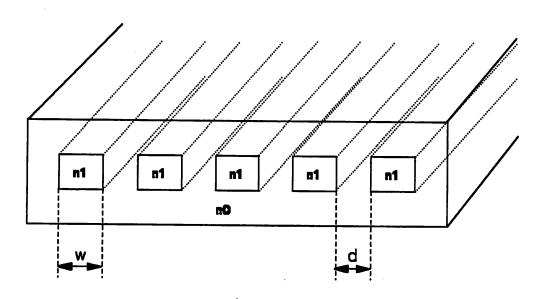

| <b>5-1</b> .  | Structure of a buried-structure single-mode waveguide array                            | 111  |

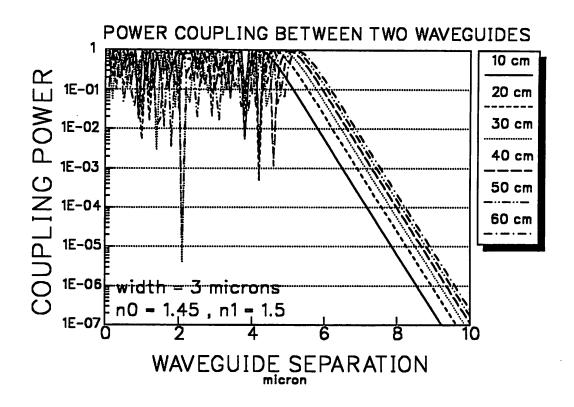

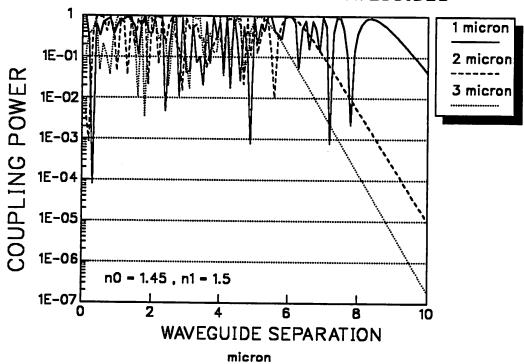

| 5-2.          | Power coupling between two waveguides as a function of waveguide separation .          | 112  |

| 5-3.          | Power coupling between two waveguides as a function of waveguide separation .          | 113  |

| 5-4.          | Power coupling between two waveguides as a function of waveguide separation .          | 114  |

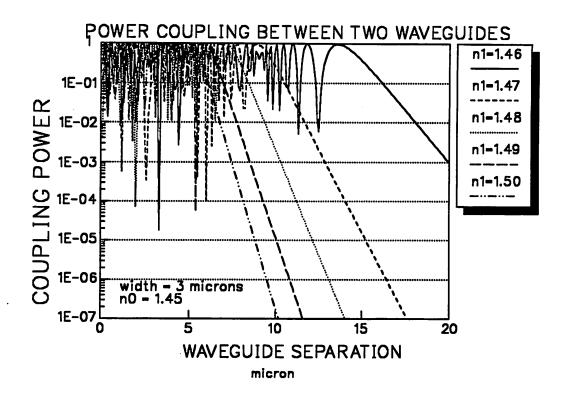

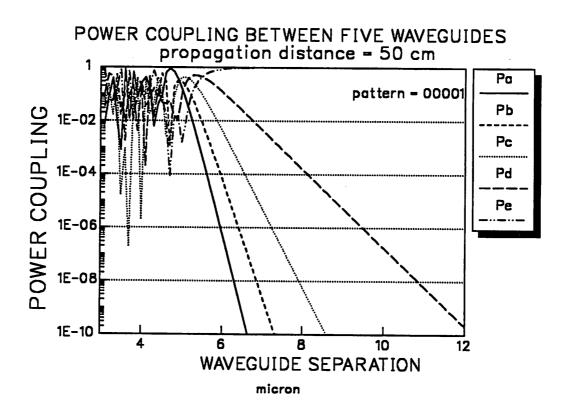

| 5-5.          | Power coupling between five waveguides                                                 | 115  |

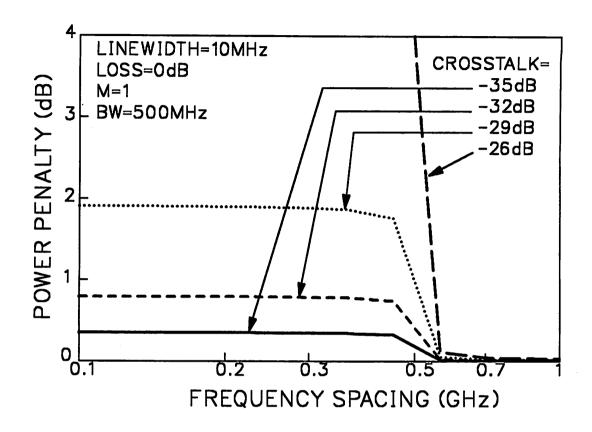

| 5-6.          | Power penalty vs. frequency spacing                                                    | 122  |

| <b>5-7</b> .  | Power penalty vs. crosstalk                                                            | 125  |

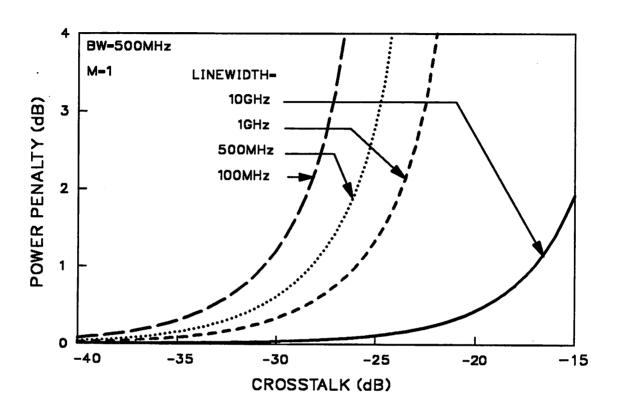

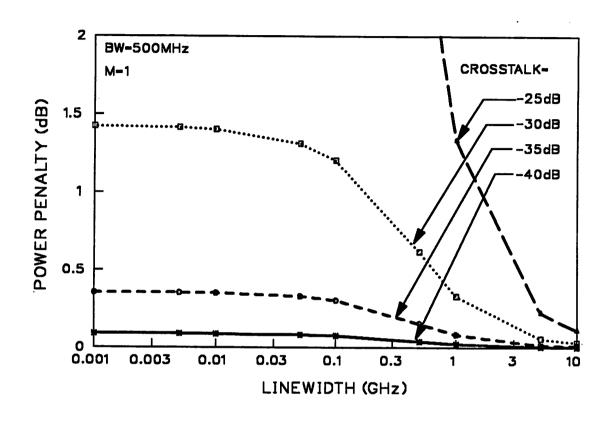

| 5-8.          | Power penalty vs. laser linewidth                                                      | 126  |

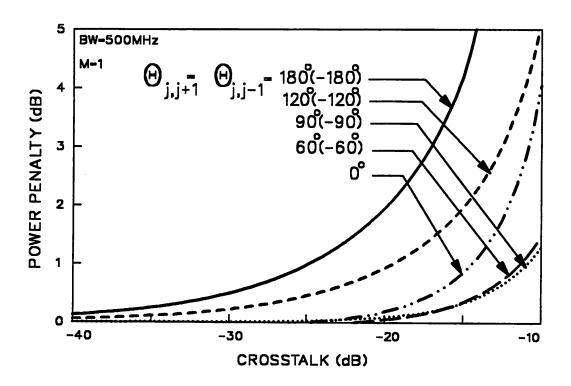

| 5-9.          | Power penalty vs. crosstalk for various phase difference                               | 127  |

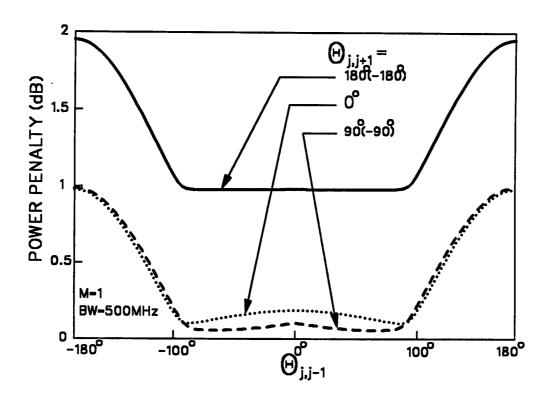

| <b>5-10</b> . | Power penalty vs. phase difference                                                     | 128  |

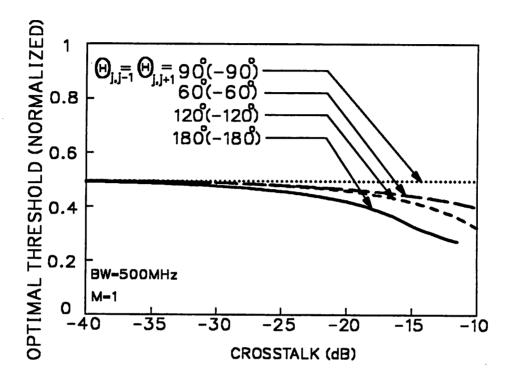

| 5-11.         | Threshold vs. crosstalk for various phase difference                                   | 129  |

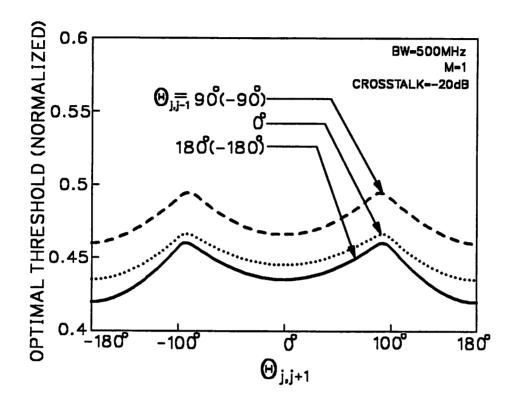

| 5-12.         | Threshold vs. phase difference                                                         | 130  |

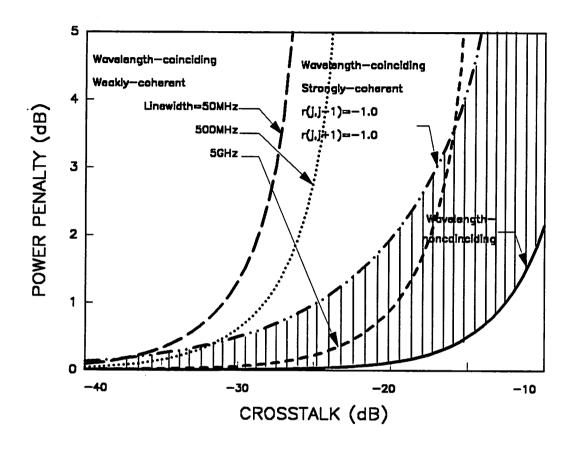

| 5-13.         | Power penalty vs. crosstalk comparison for difference source conditions                | 131  |

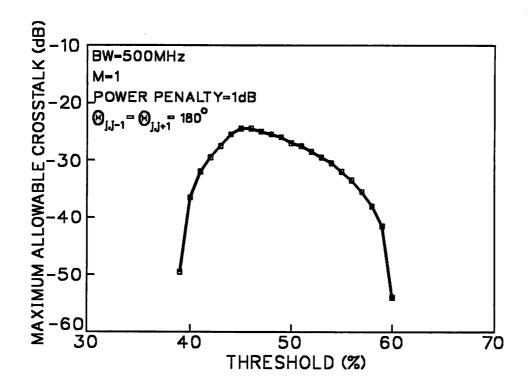

| 5-14.         | Maximum allowable crosstalk vs. position of the threshold                              | 132  |

| 6-1.          | Architecture of a typical N-channel WDM/WDMA backplane                                 | 144  |

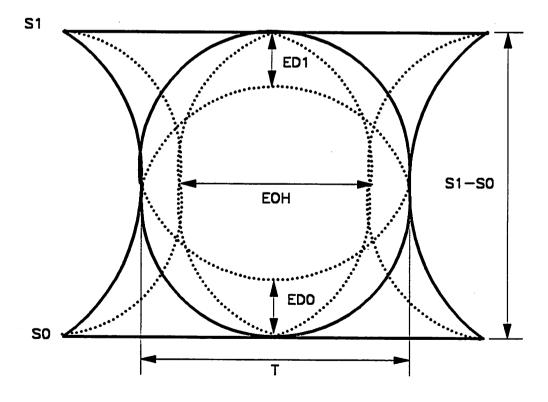

| 6-2.          | A typical eye pattern showing the horizontal and vertical eye opening                  | 147  |

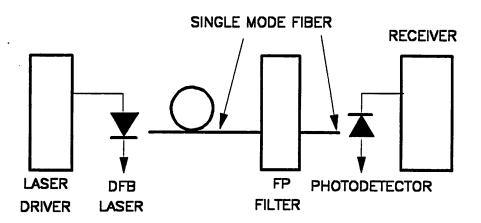

| o-3.  | System configuration for a single channel.                                         | 149 |

|-------|------------------------------------------------------------------------------------|-----|

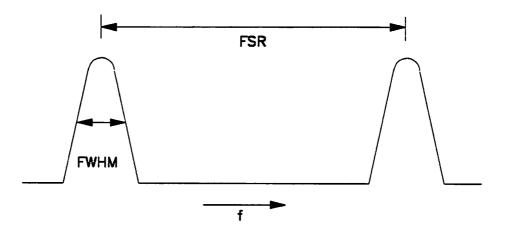

| 6-4.  | Frequency response of a Fabry-Perot filter                                         | 153 |

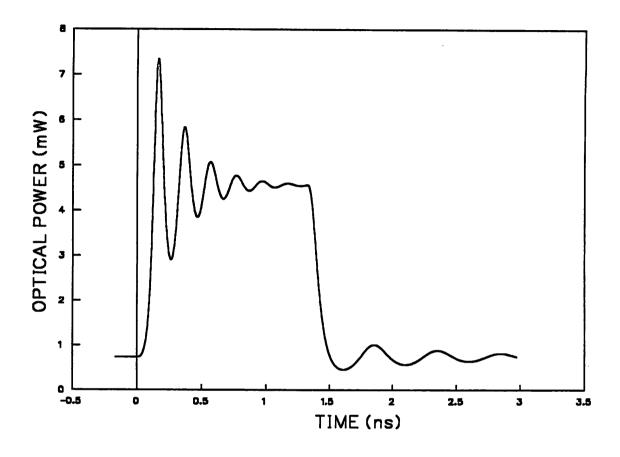

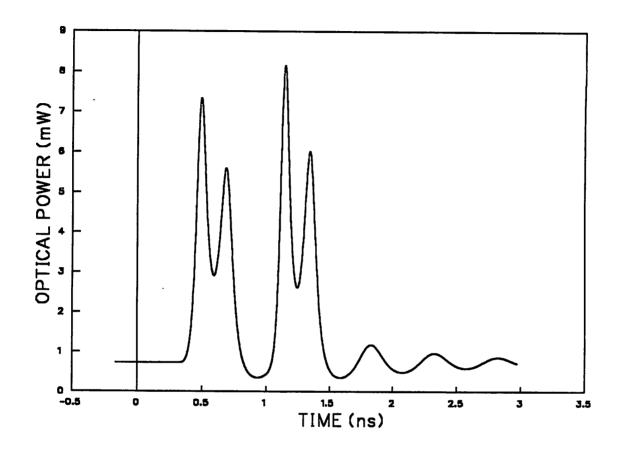

| 6-5.  | Simulated output of instantaneous optical power of a DFB laser using bit pattern   |     |

|       | 0011110000                                                                         | 156 |

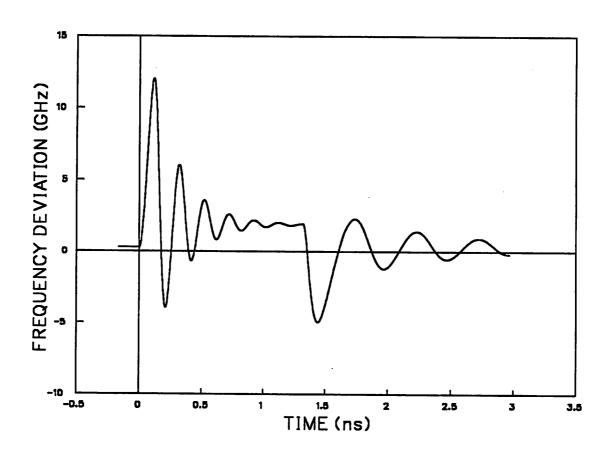

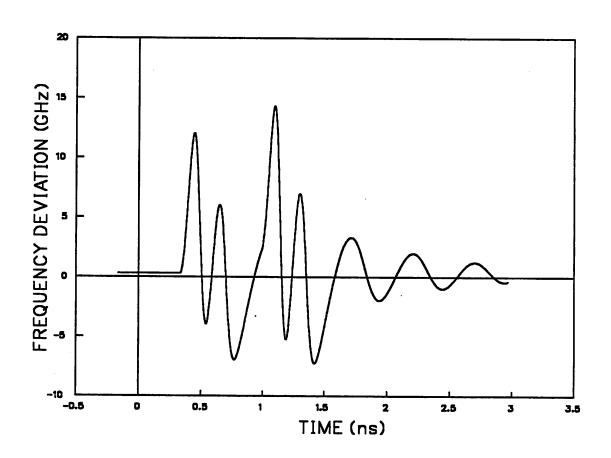

| 6-6.  | Simulated output of instantaneous chirp frequency of a DFB laser using bit pattern |     |

|       | 0011110000                                                                         | 157 |

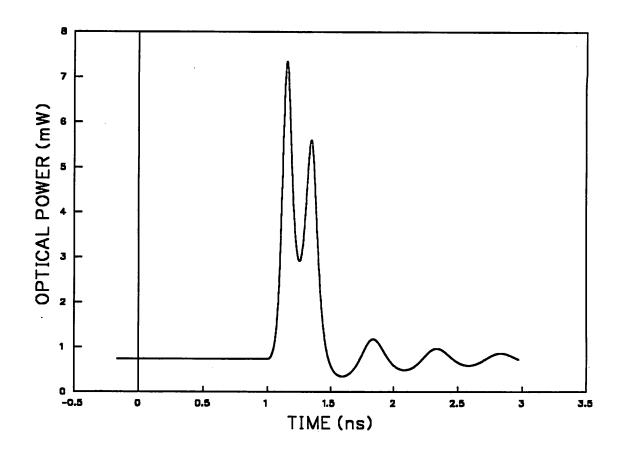

| 6-7.  | Simulated output of instantaneous optical power of a DFB laser using bit pattern   |     |

|       | 0000010000                                                                         | 158 |

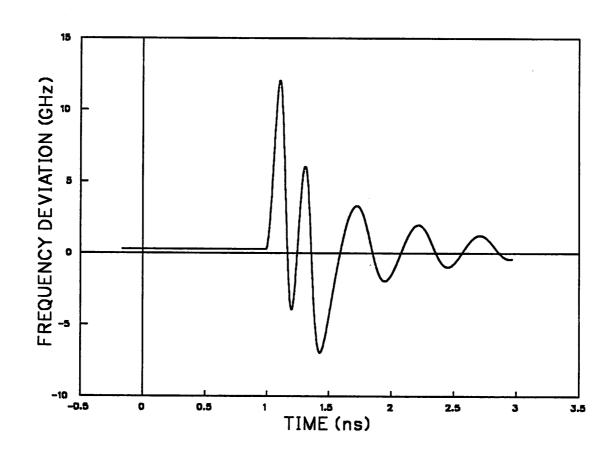

| 6-8.  | Simulated output of instantaneous chirp frequency of a DFB laser using bit pattern |     |

|       | 0000010000                                                                         | 159 |

| 6-9.  | Simulated output of instantaneous optical power of a DFB laser using bit pattern   |     |

|       | 0001010000                                                                         | 160 |

| 6-10. | Simulated output of instantaneous chirp frequency of a DFB laser using bit pattern |     |

|       | 0001010000                                                                         | 161 |

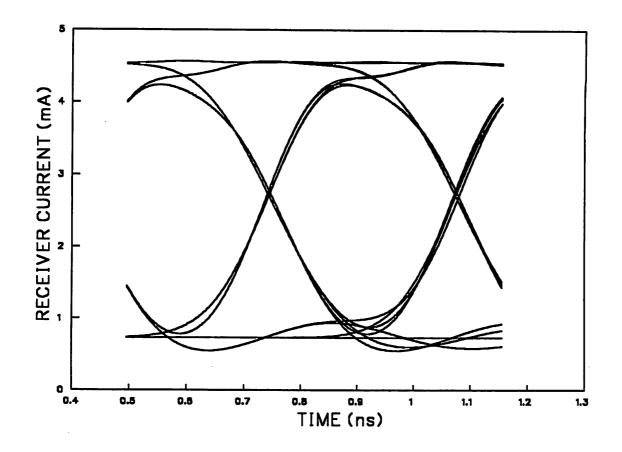

| 6-11. | Simulated eye pattern in the absence of a FP filter                                | 162 |

| 6-12. | Simulated eye pattern in the presence of a FP filter with bandwidth = 20 GHz       | 163 |

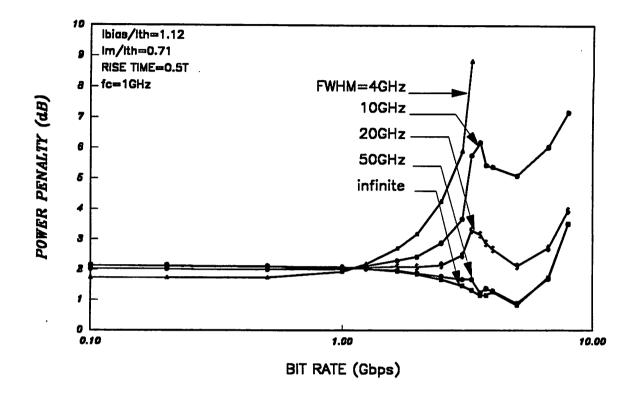

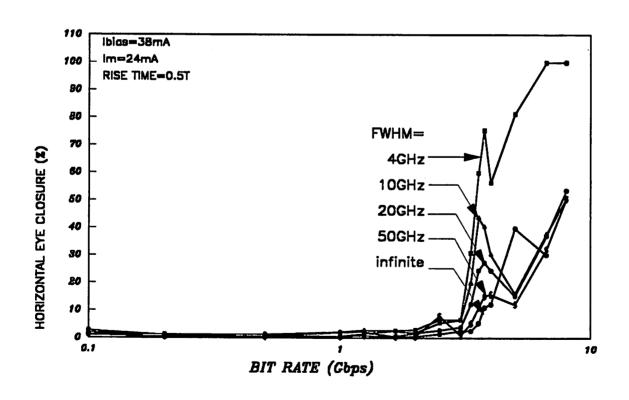

| 6-13. | Power penalty versus bit rate for various filter bandwidth                         | 164 |

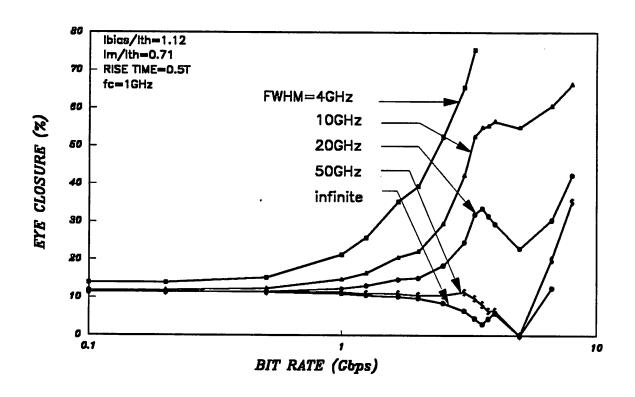

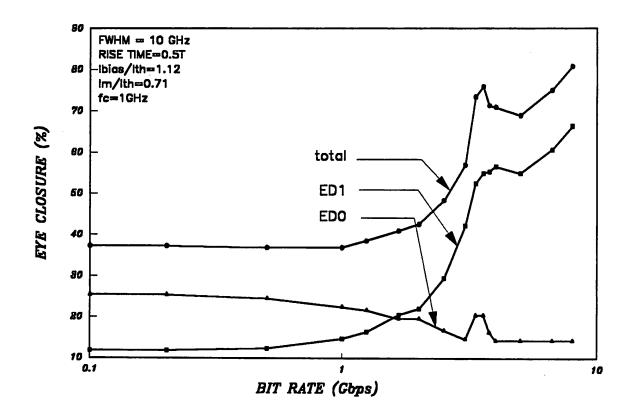

| 6-14. | Eye degradation from the ideal ONE signal level as a function of bit rate          | 165 |

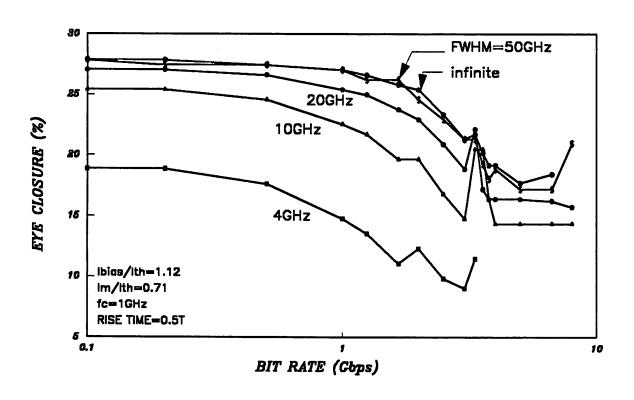

| 6-15. | Eye degradation from the ideal ZERO signal level as a function of bit rate         | 166 |

| 6-16. | Eye-closure as a function of bit rate.                                             | 167 |

| 6-17. | Horizontal eye closure versus bit rate at various filter bandwidth                 | 168 |

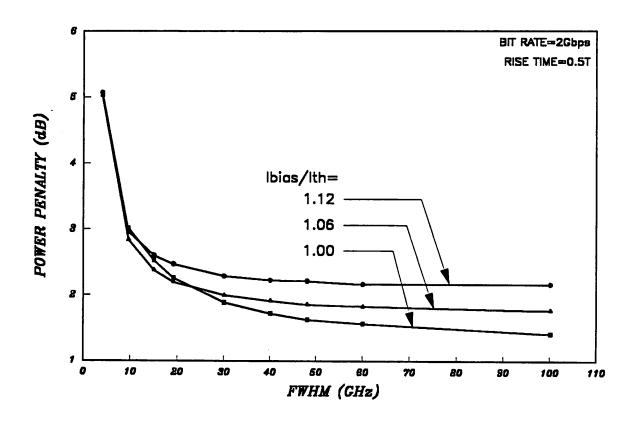

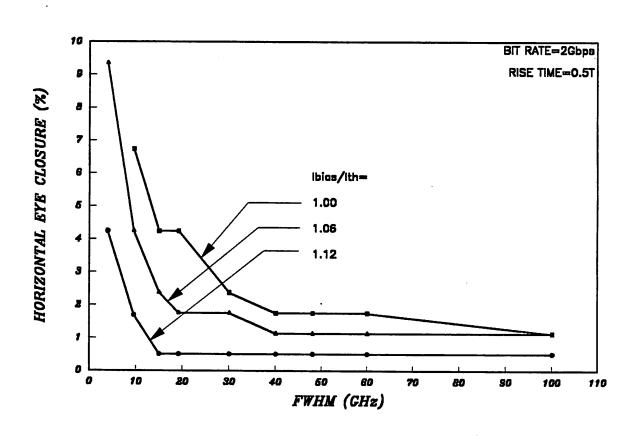

| 6-18. | Power penalty as a function of FWHM                                                | 169 |

| 6-19. | Horizontal eye-closure as a function of FWHM                                       | 170 |

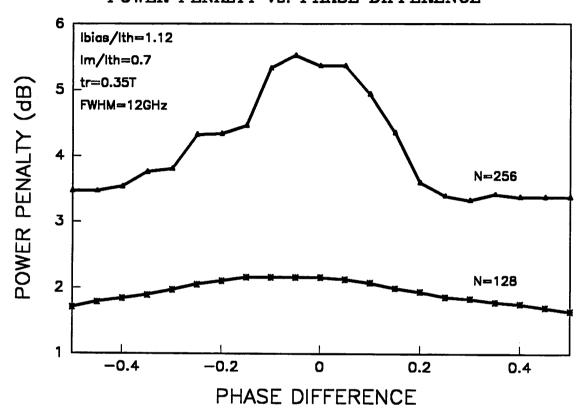

| 6-20. | Power penalty as a function of the skew between the interfering channels and the   |     |

|       | signal channel for N = 128 and 256                                                 | 171 |

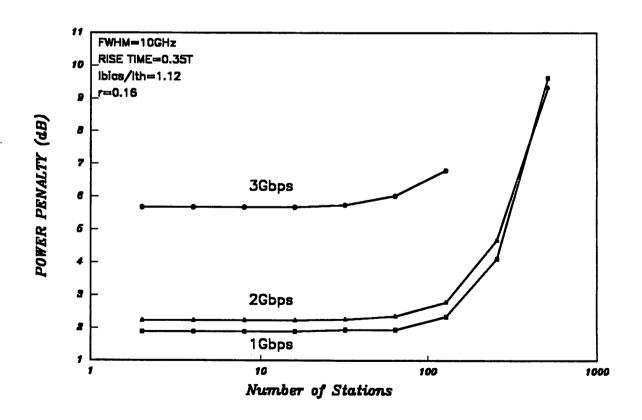

| 6-21. | Power penalty versus number of stations at 1, 2, and 3 Gbps                        | 172 |

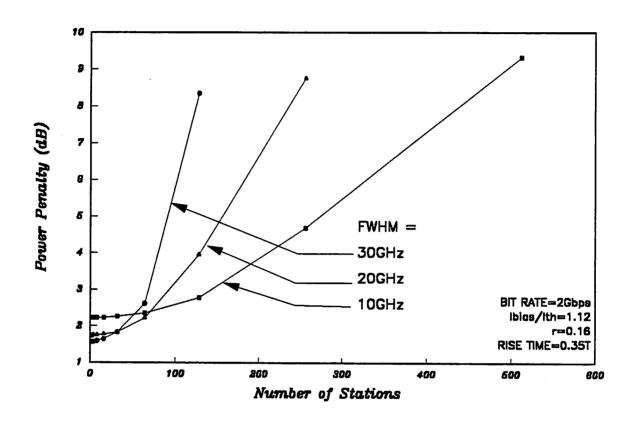

| 6-22. | Power penalty versus number of stations at filter bandwidth of 10, 20, 30 GHz      | 173 |

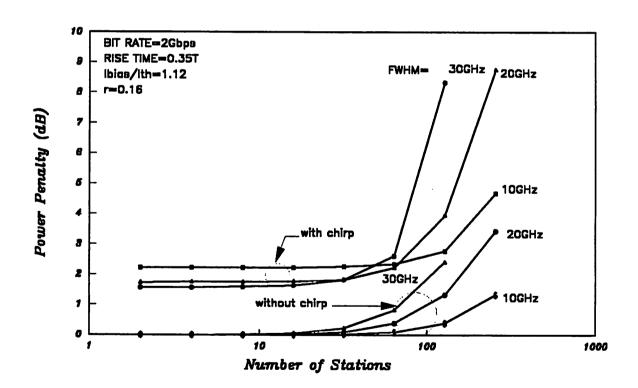

| 6-23. | Comparison of results between with chirp and without chirp for power penalty       |     |

|       | versus number of stations                                                          | 174 |

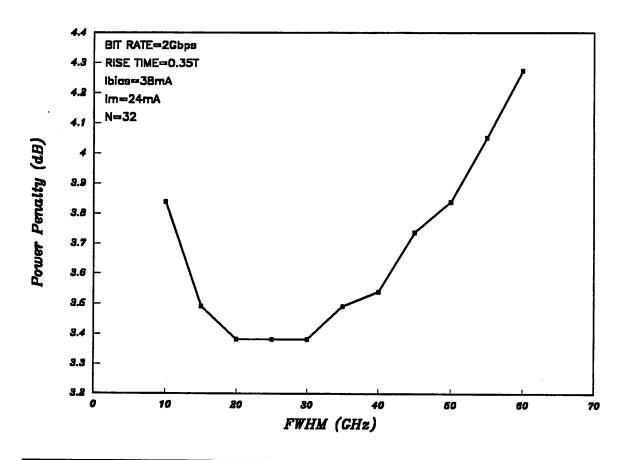

| 6-24.        | Power penalty versus filter bandwidth at various filter bandwidth                    | 175 |

|--------------|--------------------------------------------------------------------------------------|-----|

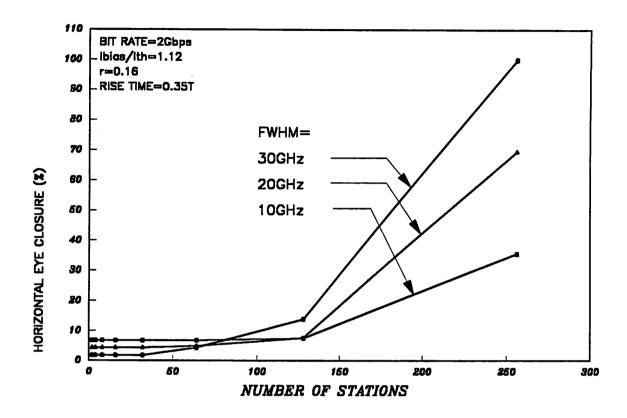

| 6-25.        | Horizontal eye-closure is plotted against the number of stations at filter bandwidth |     |

|              | of 10, 20, and 30 GHz                                                                | 176 |

| 6-26.        | Power penalty is plotted against linewidth enhancement factor                        | 177 |

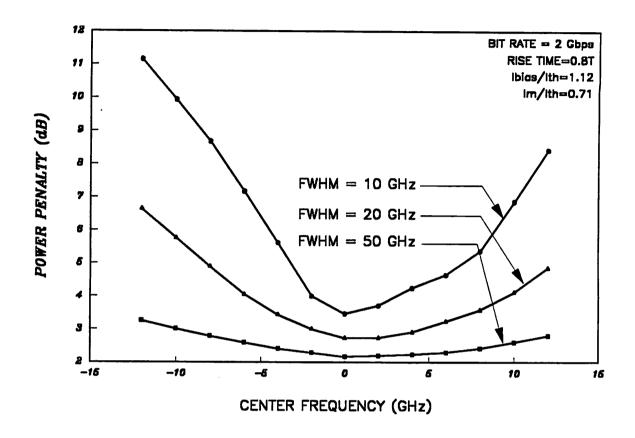

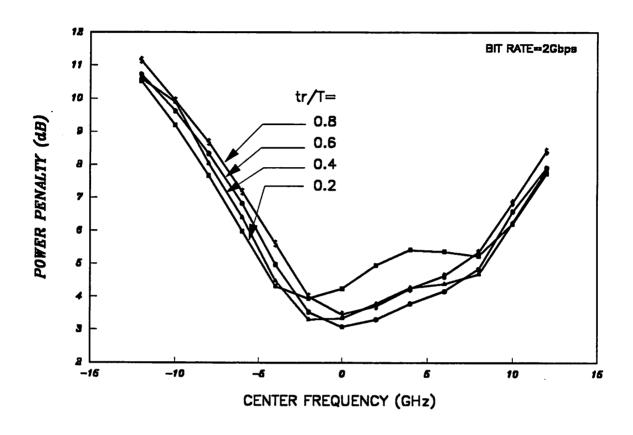

| 6-27.        | Power penalty as a function of the center frequency of the FP filter                 | 178 |

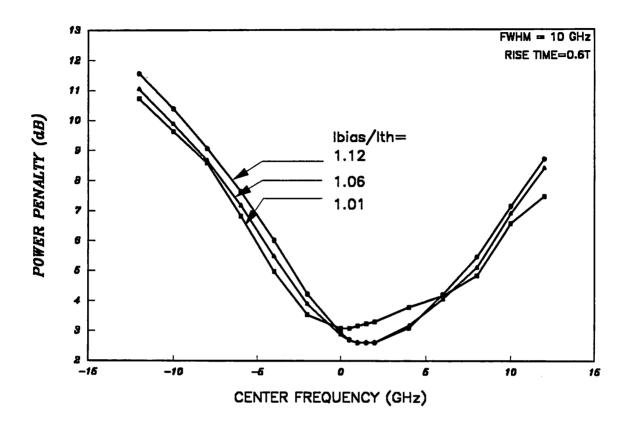

| 6-28.        | Power penalty as a function of filter center frequency                               | 179 |

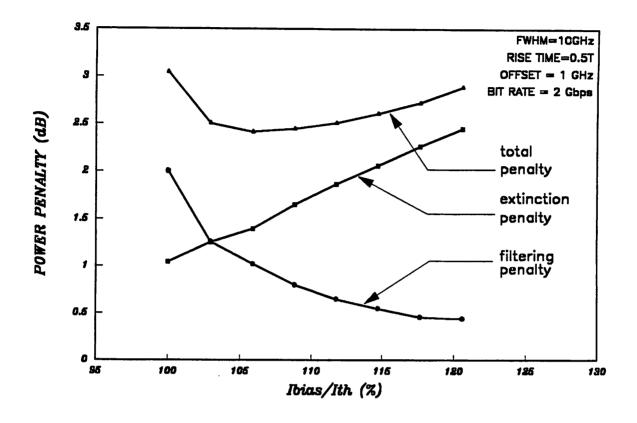

| 6-29.        | Power penalty as a function of laser bias current                                    | 180 |

| 6-30.        | Power penalty as a function of filter center frequency                               | 181 |

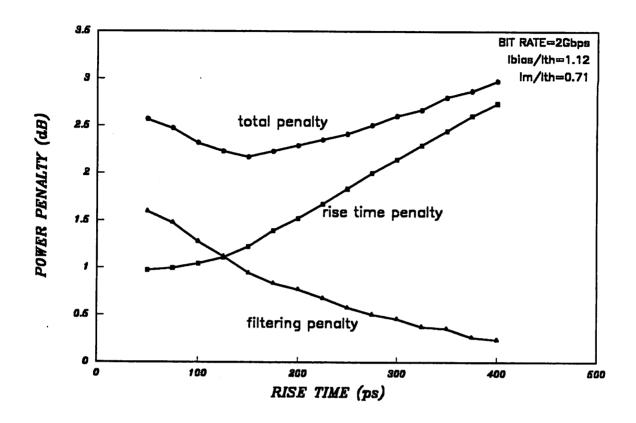

| 6-31.        | Power penalty as a function of rise time                                             | 182 |

| 6-32.        | Single-channel power penalty as a function of filter bandwidth                       | 183 |

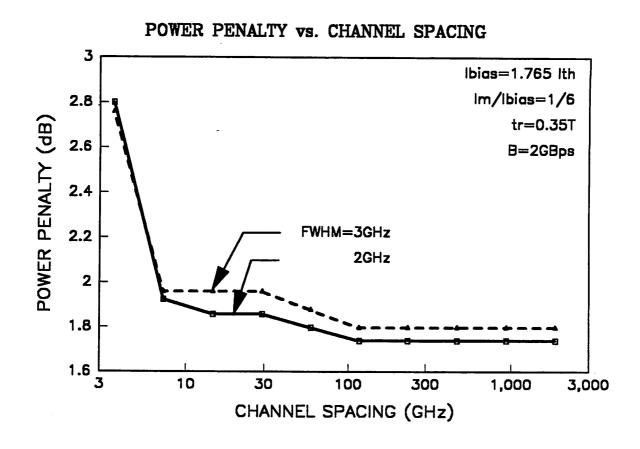

| 6-33.        | Multi-channel power penalty vs. channel spacing for filter bandwidth of 2 and 3 GHz  | 184 |

| 6-34.        | Power penalty vs. linewidth enhancement factor for various                           |     |

|              | nonlinear-gain-suppression ratio                                                     | 185 |

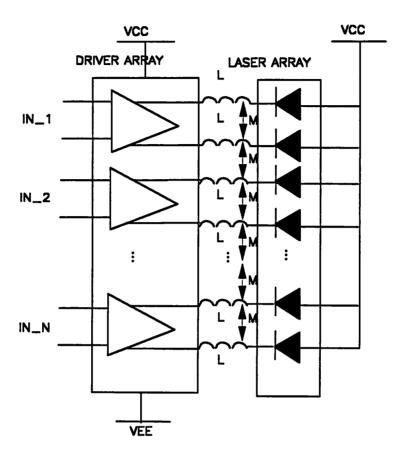

| 7-1.         | Block diagram of a transmitter array                                                 | 189 |

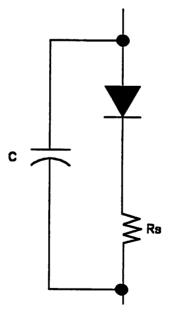

| 7-2.         | Circuit Model of a laser diode                                                       | 190 |

| 7-3.         | Circuit diagram of a single-ended laser driver                                       | 191 |

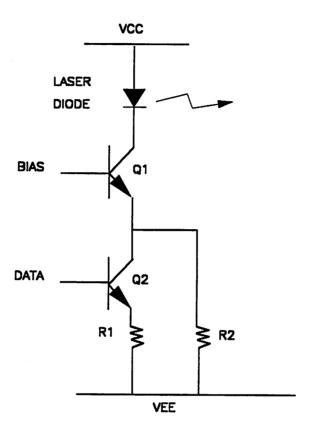

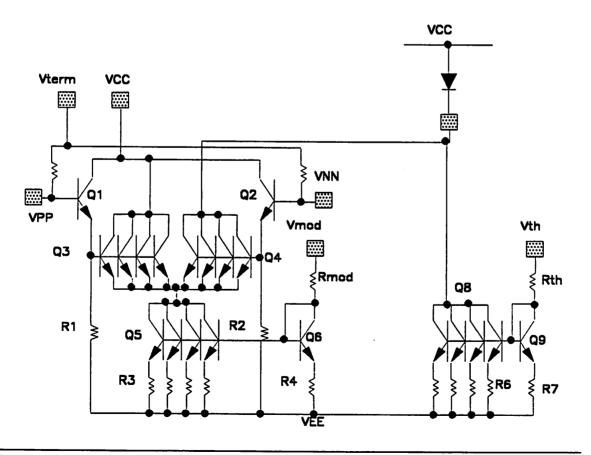

| 7-4.         | Circuit diagram of a differential laser driver                                       | 192 |

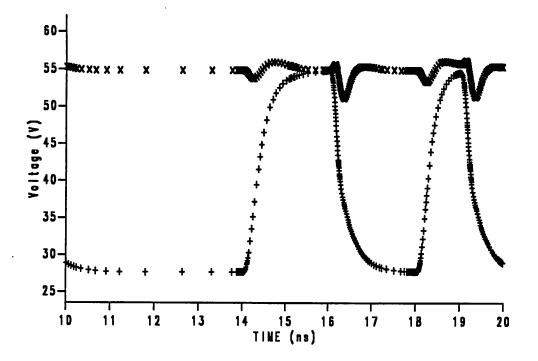

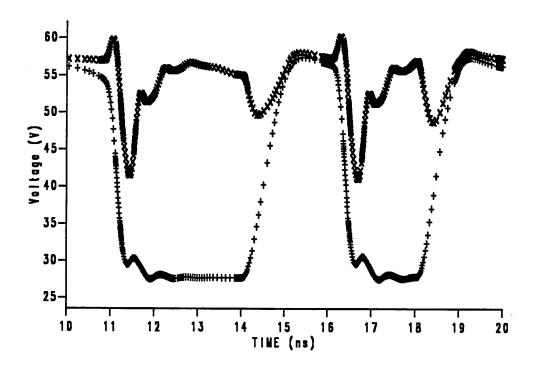

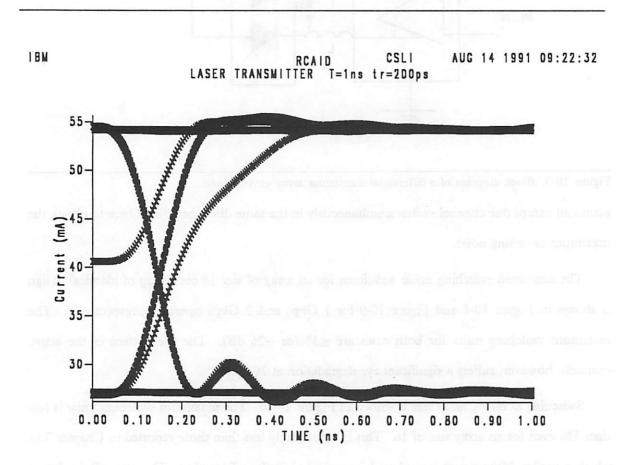

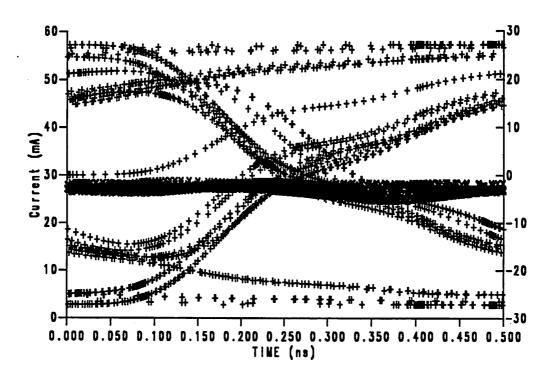

| 7-5.         | Switching noise waveform of the laser driver                                         | 194 |

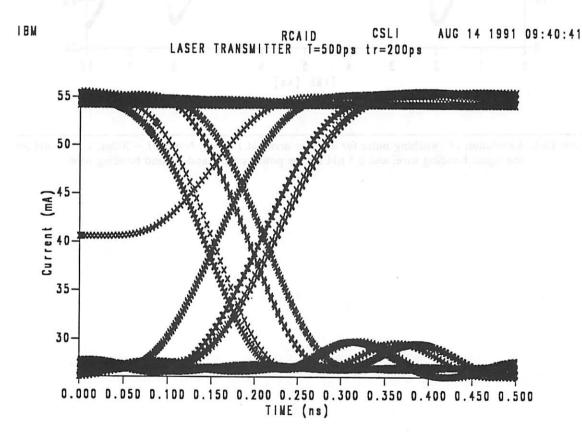

| 7-6.         | Switching noise waveform of the laser driver                                         | 195 |

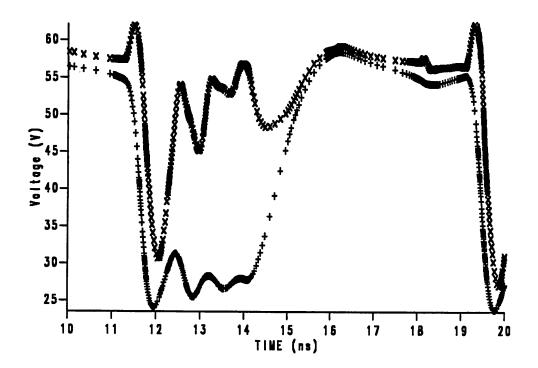

| <b>7-7</b> . | Switching noise waveform of the laser driver                                         | 196 |

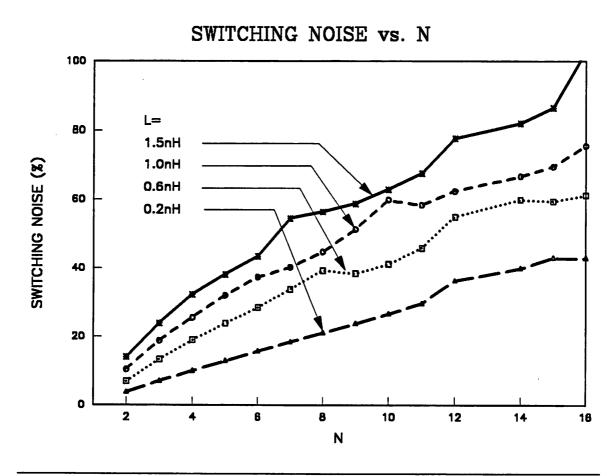

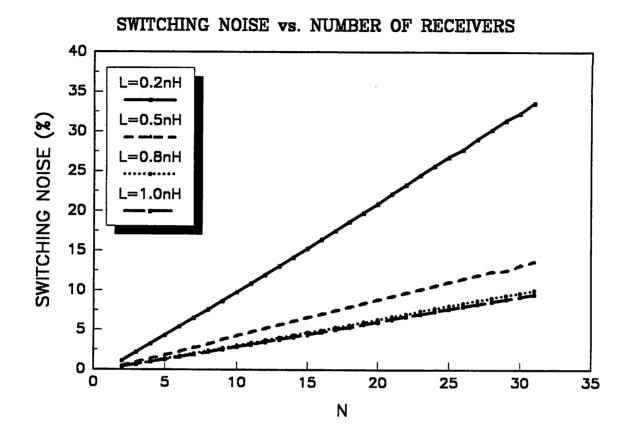

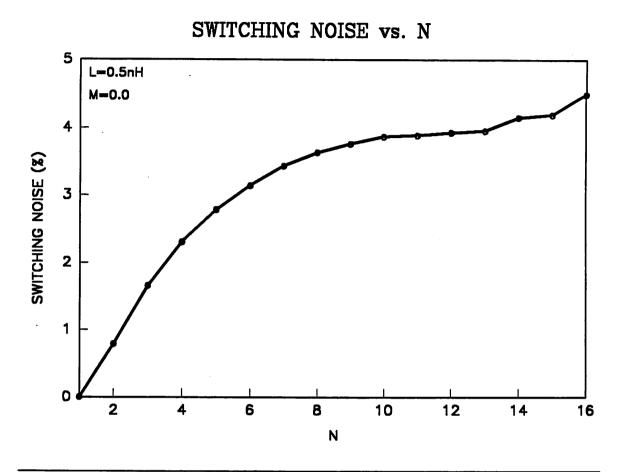

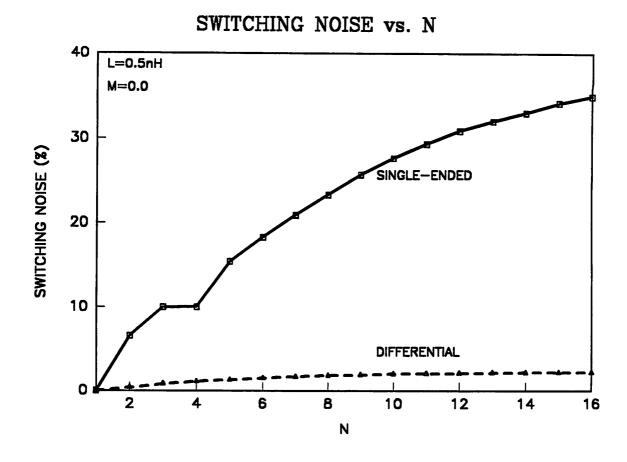

| 7-8.         | Switching noise as a function of the array size                                      | 197 |

| 7-9.         | Switching noise as a function of the lead inductance                                 | 198 |

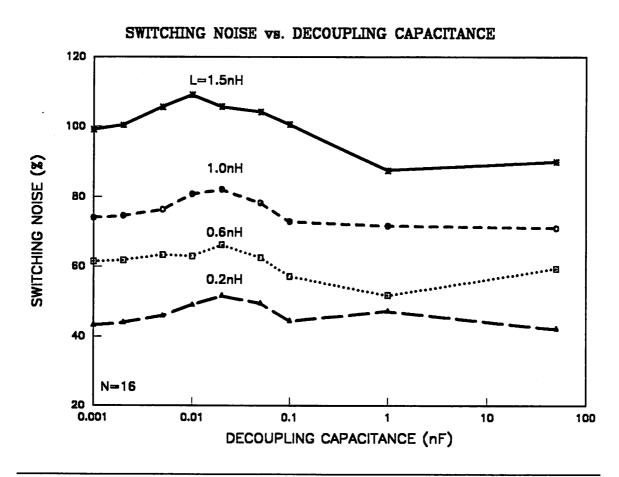

| 7-10.        | Switching noise as a function of decoupling capacitance                              | 199 |

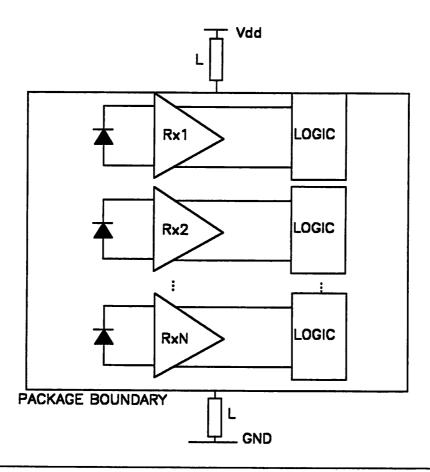

| 8-1.         | Basic configuration of a receiver array with common power supply and ground .        | 204 |

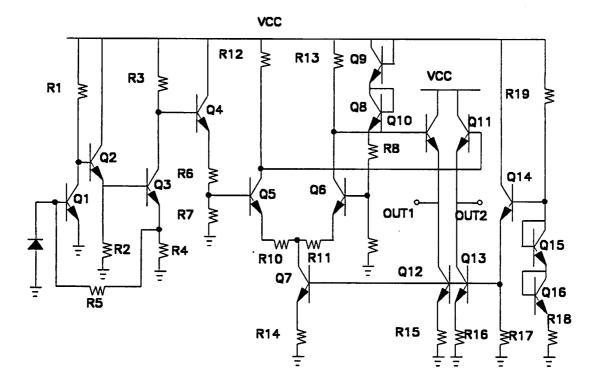

| 8-2.         | Circuit configuration of a single-ended receiver                                     | 205 |

| 8-3.         | Circuit configuration of a differential receiver                                     | 206 |

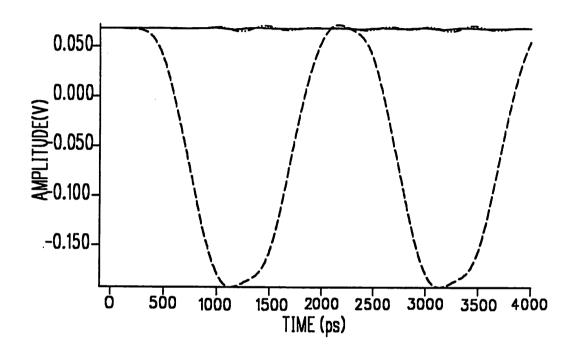

| 8-4.         | Switching noise waveform                                                             | 207 |

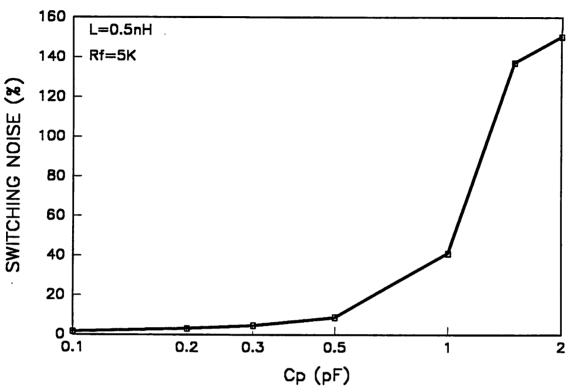

| 8-5.         | Switching noise versus photodetector capacitance                                     | 208 |

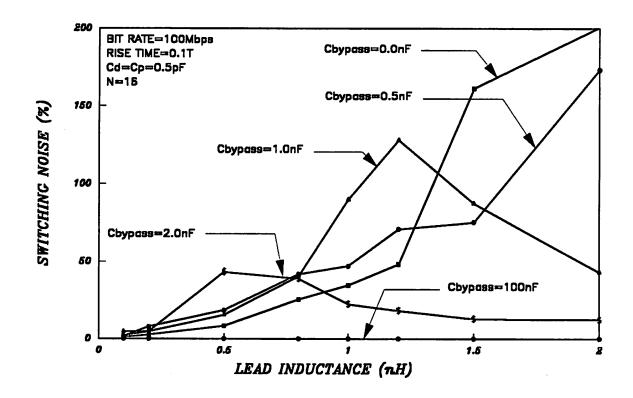

| 8-6.           | Switching noise versus lead inductance for a single-ended configured receiver array    |     |

|----------------|----------------------------------------------------------------------------------------|-----|

|                | with N = 16                                                                            | 209 |

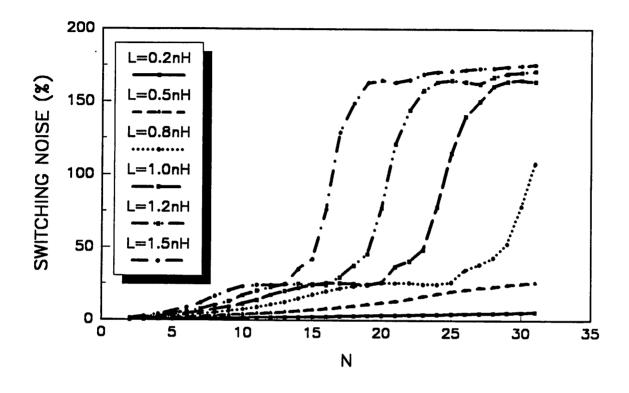

| 8-7.           | Switching noise generated by a single-ended configured receiver as a function of array | 7   |

|                | size                                                                                   | 210 |

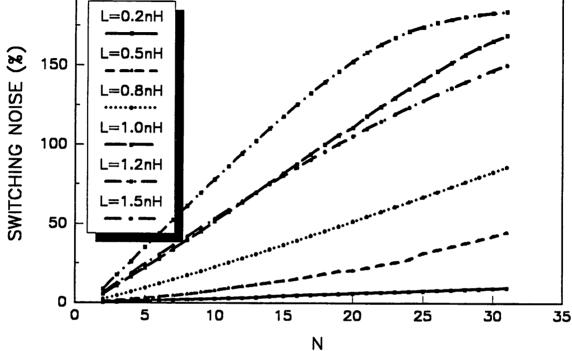

| 8-8.           | Switching noise generated by a single-ended configured receiver as a function of array |     |

|                | size                                                                                   | 211 |

| 8-9.           | Switching noise generated by a single-ended configured receiver as a function of array |     |

|                | size                                                                                   | 212 |

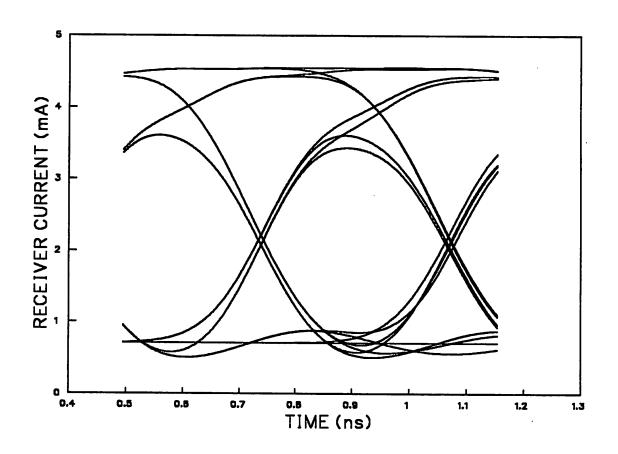

| 8-10.          | Switching noise generated by a differentially configured receiver array                | 214 |

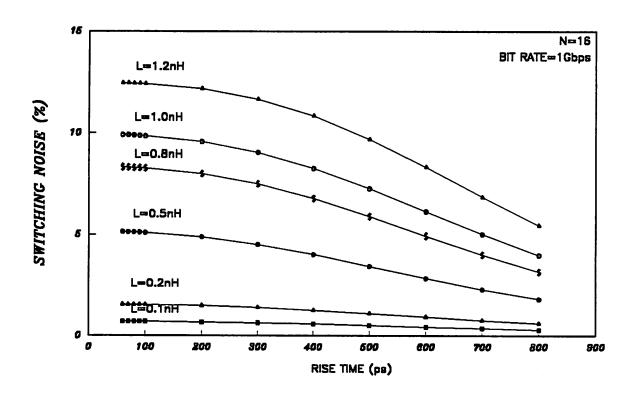

| 8-11.          | Switching noise versus signal rise time for a differential receiver array with N = 16  | 215 |

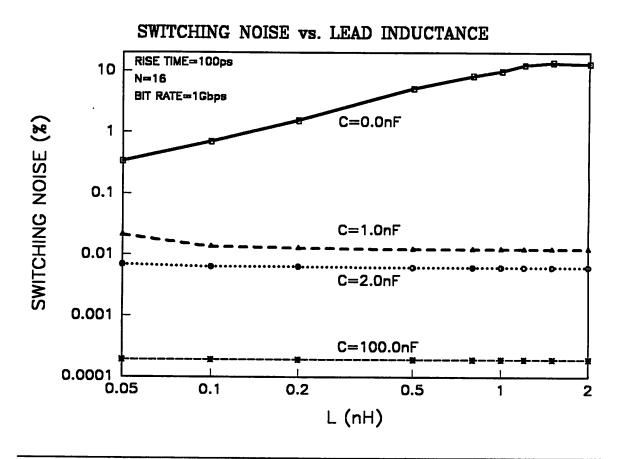

| 8-12.          | Switching noise versus lead inductance for a differentially configured preamp          | 216 |

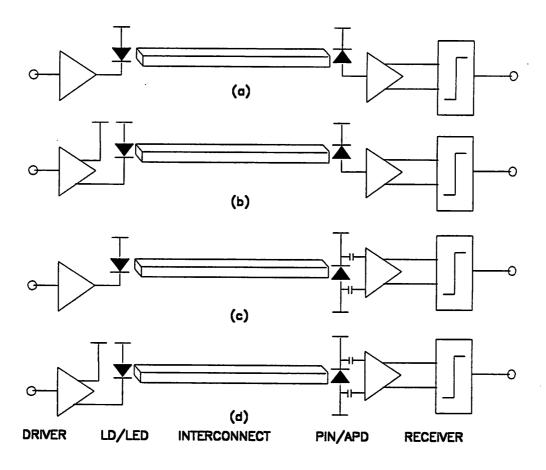

| 9-1.           | Possible structures for a single-ended optical interconnect                            | 220 |

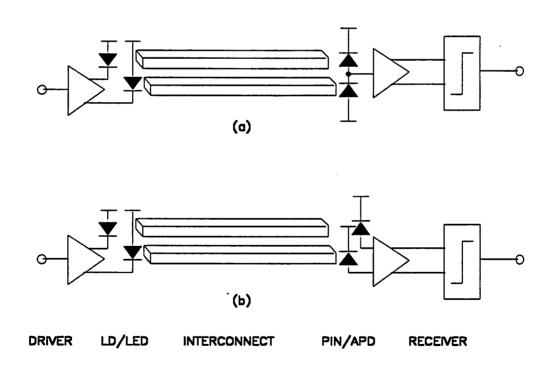

| 9-2.           | Possible structures for a differentially configured optical interconnect               | 223 |

| 9-3.           | Structure of a Mach-Zehnder modulator                                                  | 226 |

| 9-4.           | Structure of a directional coupler modulator                                           | 227 |

| 9-5.           | Structure of a modulator using total internal reflection                               | 228 |

| 9-6.           | Structure of a multiple quantum well modulator                                         | 229 |

| 9-7.           | Structure of a differential optical interconnect using TDM                             | 230 |

| 9-8.           | Structure of a differential optical interconnect using FSK                             | 231 |

| 9-9.           | Structure of a differential optical interconnect using WDM                             | 232 |

| 9-10.          | Structure of a differential optical interconnect using polarization division           |     |

|                | multiplexing                                                                           | 233 |

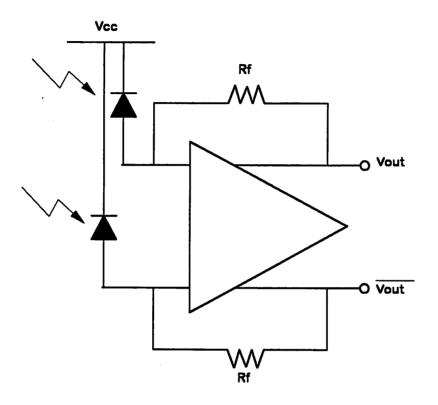

| 9-11.          | Full circuit of a differential receiver using in a single-ended optical interconnect.  | 235 |

| 9-12.          | Half circuit of a differential receiver using in a single-ended optical interconnect.  | 236 |

| 9-13.          | Full circuit of a differential receiver used in a differential optical interconnect    | 240 |

| 9-14.          | Half circuit of a differential receiver used in a differential optical interconnect    | 241 |

| 9-15.          | Power penalty as a function of threshold error                                         | 247 |

| 9-16.          | Structure of decision feedback optimal threshold computation                           | 249 |

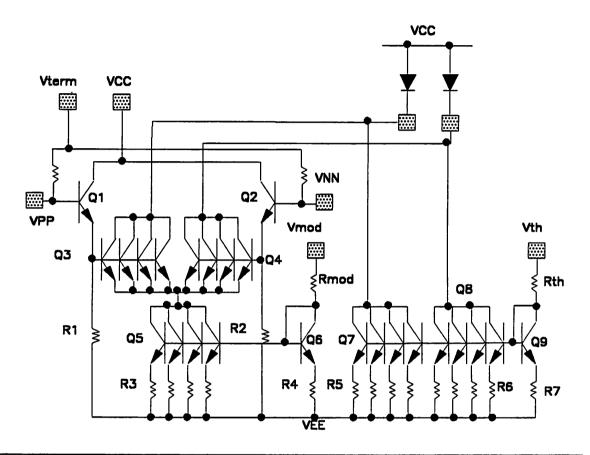

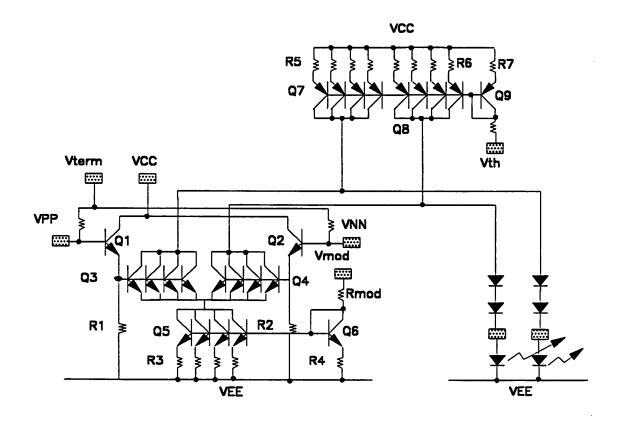

| l <b>0-</b> 1. | Circuit diagram of a fully differential driver                                         | 254 |

| 10-2.  | Circuit diagram of a fully differential transmitter array                        | 256 |

|--------|----------------------------------------------------------------------------------|-----|

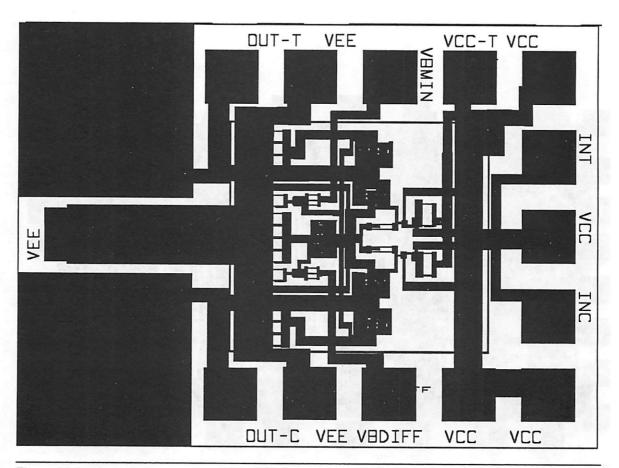

| 10-3.  | Physical layout of a fully differential driver                                   | 257 |

| 10-4.  | Physical layout of a fully differential driver array                             | 258 |

| 10-5.  | Block diagram of a differential transmitter array environment                    | 259 |

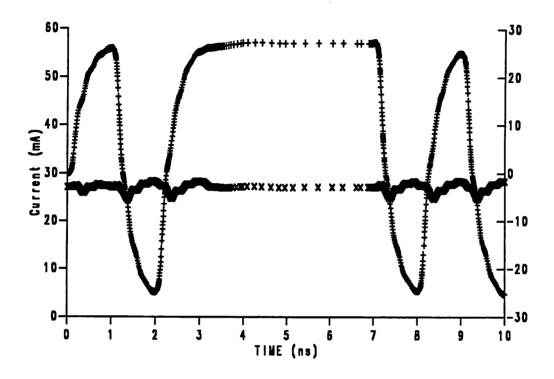

| 10-6.  | Simulated eye pattern of a laser driver at 1Gbps                                 | 260 |

| 10-7.  | Simulated eye pattern of a laser driver at 2Gbps                                 | 261 |

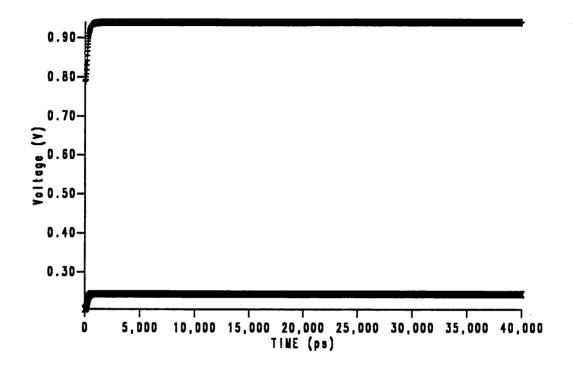

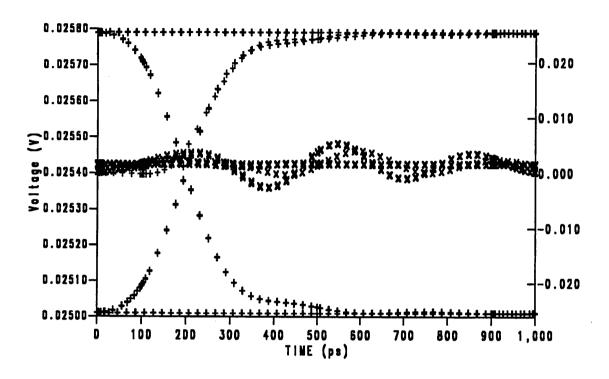

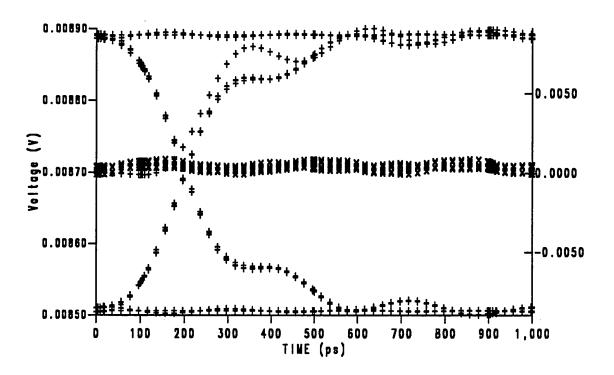

| 10-8.  | Simulation of switching noise for a driver array at 1 Gbps                       | 262 |

| 10-9.  | Simulation of switching noise for a driver array at 2 Gbps                       | 263 |

| 10-10. | Switching noise vs. N for a differential driver array                            | 264 |

| 10-11. | Crosstalk vs. mutual inductance for various driver array configurations          | 265 |

| 10-12. | Comparison of switching noise vs. N between single-ended and differential driver |     |

|        | аттау                                                                            | 266 |

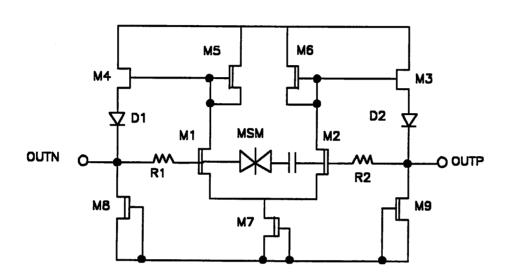

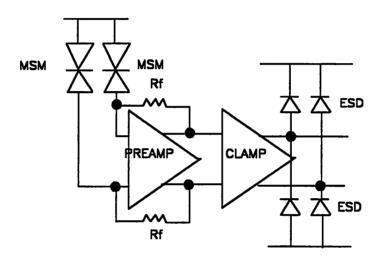

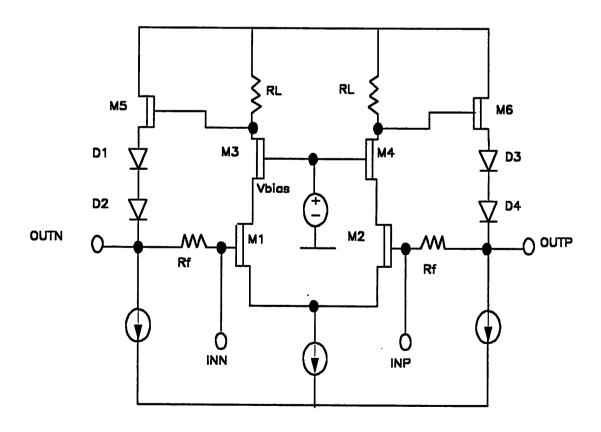

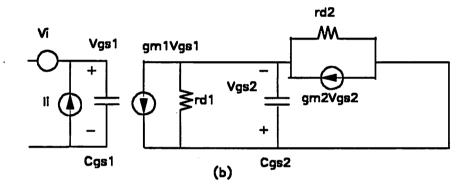

| 11-1.  | Circuit block diagram of a fully differential preamplifier                       | 269 |

| 11-2.  | Simplified circuit diagram of the transimpedance front-end                       | 270 |

| 11-3.  | Circuit block diagram of a complete receiver                                     | 271 |

| 11-4.  | Half circuit of the fully differential receiver                                  | 274 |

| 11-5.  | Equivalent circuit of a cascode configured stage                                 | 275 |

| 11-6.  | Noise equivalent circuit of a cascode configured stage                           | 276 |

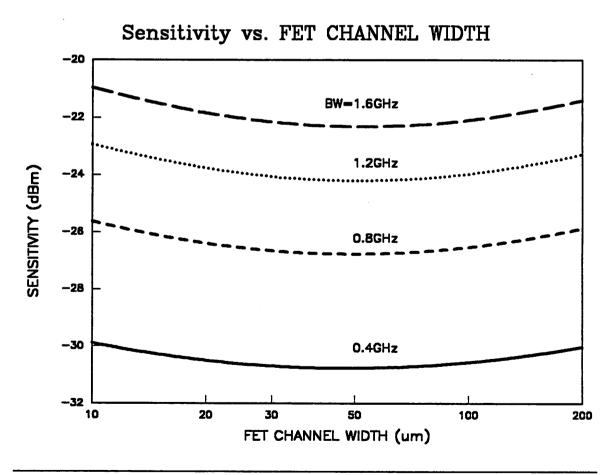

| 11-7.  | Sensitivity vs. channel width of the input MESFET                                | 277 |

| 11-8.  | Sensitivity vs. channel width of the input MESFET                                | 278 |

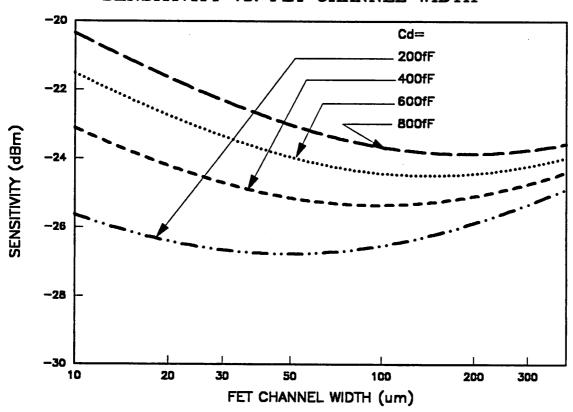

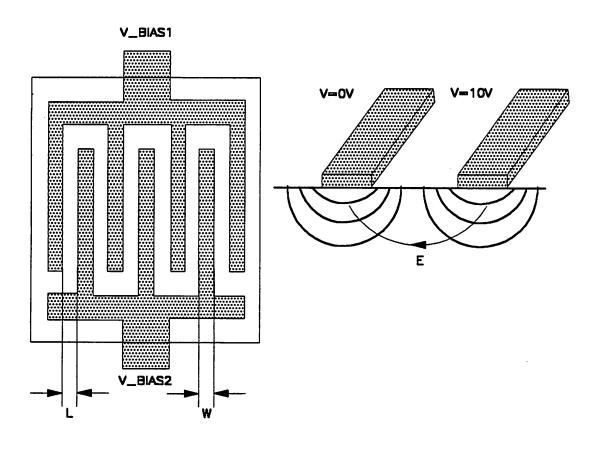

| 11-9.  | Typical Structure of a MSM photodetector                                         | 281 |

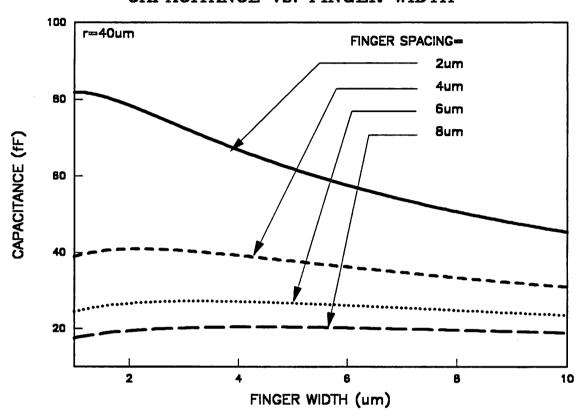

| 11-10. | Total MSM capacitance as a function of the finger spacing                        | 282 |

| 11-11. | Total MSM capacitance as a function of the finger width                          | 283 |

| 11-12. | Chip photograph of a single preamplifier cell                                    | 285 |

| 11-13. | Chip photograph of a full receiver cell                                          | 286 |

| 11-14. | Chip photograph of a 12-receiver array                                           | 287 |

| 11-15. | Chip photograph of a 6-receiver array                                            | 288 |

| 11-16. | Simulated eye pattern of the receiver response                                   | 289 |

| 11-17. | Simulated eye pattern of the receiver response                                   | 290 |

| 11-18. | Simulated eye pattern of the receiver response | 291 |

|--------|------------------------------------------------|-----|

| 11-19. | Simulated eye pattern of the receiver response | 292 |

| 11-20. | Simulated eye pattern of the receiver response | 293 |

| 11-21. | Low frequency response of the receiver         | 294 |

| 11-22. | Low frequency response of the receiver         | 295 |

| 11-23. | Simulated switching noise of a preamp array    | 296 |

| 11-24. | Simulated switching noise of a preamp array    | 297 |

# **CHAPTER 1 INTRODUCTION**

#### 1.1 Motivation

As technology progresses, the demand for high performance digital systems such as high-speed switching systems for broadband integrated service data network (B-ISDN) as well as general-purpose mainframes and workstations for scientific and business applications is unrelenting. Higher performance can be achieved through exploiting concurrent architectures such as parallelization [1] and pipelining of executions [2] or through the use of more advanced and faster technologies. Eventually the more advanced technologies can be applied to the concurrent architectural approaches, achieving increasingly better performance.

Faster devices are announced frequently [3, 4]. These leading devices include

- Super-self-aligned silicon bipolar technology [5].

- GaAs MESFET technology [6],

- high electron mobility transistor (HEMT) [7],

- heterojunction bipolar transistor (HBT) [8],

- Josephson junction technology [9].

These devices routinely demonstrate a gate delay of 30ps or less, and have good prospects in LSI/VLSI applications. Even the speed of CMOS VLSI is improving through either scaling or/and cooling down to liquid nitrogen temperature [10]. Yet speed of devices is not the only criterion that determines the acceptance of a technology. When these devices are used in a complicated system such as a high performance computer, problems of parasitics, circuit design, power consumption and packaging often dominate over sheer speed. Therefore, it is insufficient to improve the performance of a system simply by choosing a faster device technology. Packaging and interconnections also have to be taken into consideration in order to optimize the overall system performance. Currently available packaging and interconnect technology at various packaging levels are [11]:

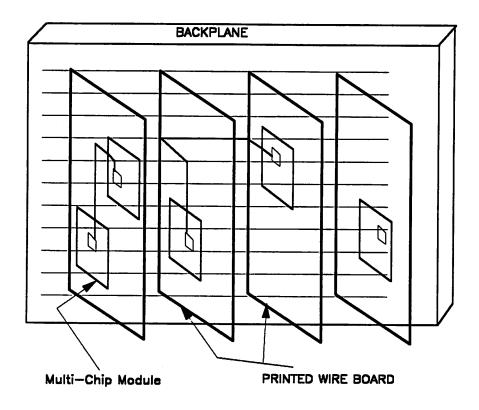

Figure 1-1. Packaging hierarchy. A typical packaging hierarchy, from bottom to top includes chips, multi-chip modules (MCM), cards, boards, and backplanes.

- Chip-to-package interconnections: These technologies include wirebonding, tape automated bonding (TAB), and flip-chip bonding using solder ball.

- Ceramic and plastic chip modules: Each module made of ceramic or plastic encapsulation

contains a single chip (single chip module or SCM) or multiple chips (multichip module or

MCM). The interconnections on these modules can have multiple signal layers using thin-film

or thick-film processing techniques.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup> Thin-film packaging refers to packages in which the conductor and insulators are fabricated using deposition and patterning techniques similar to those used for fabricating integrated-circuit chips.

- Package-to-board interconnections: Existing technologies can be categorized as pin-through-hole (PTH), leadless chip carrier (LLCC), and surface mount technology (SMT). A through-hole on the printed circuit board is provided for each pin of a chip package in PTH. Both mechanical joint and solder joint are feasible for this technology. On the other hand, both LLCC and SMT, which are more area efficient and provide better signal quality, require solder joint between each lead of a package and the pad on a circuit board.

- Printed-circuit board: This technology has been around before 1960. The progress over the past 30 years includes the decrease in the through-hole diameter (from  $\sim$ 840  $\mu$ m to  $\sim$ 350  $\mu$ m), the increase in the through-hole density (from  $\sim$ 9 to  $\sim$  64  $/cm^2$ ), the increase in the number of signal planes (from  $\sim$ 4 to  $\sim$ 50), and the decrease of the interconnect width (from  $\sim$ 250  $\mu$ m to  $\sim$ 50  $\mu$ m).

As the speed of devices increases, existing metallic interconnect technology is no longer adequate due to its performance degradation at high-frequency. Sources of performance degradation include

- Reflections,

- Ground-loop noise,

- · Crosstalk among adjacent interconnects,

- Frequency dependent signal distortion.

We will now describe a few of these impairments.

#### 1.1.1 Reflections

A high performance system requires more than one level of packaging and interconnects to accommodate complicated logic functions. A typical packaging hierarchy, as shown in Figure 1-1, includes chips, single-chip modules (SCM), multi-chip modules (MCM), cards, boards, and backplanes. However, electrical discontinuities exist between any two packaging levels. Discontinuities may be primarily inductive (such as electrical connectors) or capacitive (such as stubs in a multidrop net and 90-degree bends in a microstrip line). Depending upon the nature of the discontinuities and impedance changes, the resulting reflections may be either positive or negative.

Various methods exist to reduce the reflections resulting from impedance mismatch. For example, a termination resistor is usually placed at the receiving end of an interconnect in order to reduce the reflections. However, a perfect matching between the characteristic impedance of the interconnection and the impedance of the load is difficult to achieve because of the parasitic capacitance and inductance. If the round-trip propagation time between the source and the discontinuities is less than the rise time of the signal, these reflections can be absorbed by the interconnect driver with a net effect of an increased signal rise time. On the other hand, the waveform of the signal is severely degraded by the multiple reflections if the round-trip propagation time is longer than the rise time of the signal, resulting in a reduced noise margin or/and false switching.

#### 1.1.2 Ground-loop noise

The ground plane of a packaging system usually cannot achieve zero resistance and inductance. Any local injection of current from the devices changes the electrical potential at that point. For a single-ended interconnection, the receiving side has to rely on the potential of the local ground plane as a reference to determine the amplitude of the incoming signals. Any disturbance of the ground plane is therefore coupled into the received signal.

One way of alleviating this problem is to transmit differential signals so that the signal can be interpreted unambiguously at the receiving end of an interconnect. However, the required interconnect density has to be doubled and thus more signal layers are necessary to accommodate the increased interconnect complexity. Some of the chips that are already pin-count-limited cannot afford this option either.

### 1.1.3 Crosstalk among adjacent interconnects

For a given interconnect density, crosstalk between adjacent interconnects increases as the rise time of the signal decreases. Furthermore, crosstalk of the transmission lines with a TEM or near-TEM structure,<sup>2</sup> such as slotted lines and microstrip lines, usually couple with switching noise and may consume the entire noise margin if they are not carefully controlled [12]. Therefore, either the interconnects have to be spaced farther apart or additional shielding lines have to be inserted

<sup>&</sup>lt;sup>2</sup> TEM mode is the fundamental mode supported by a transmission line such as a coaxial cable. The transmission line structures that can support TEM mode are said to have TEM structures.

between signal lines to reduce crosstalk to an acceptable level. In both cases, the effective interconnect density is reduced.

## 1.1.4 Frequency-dependent signal distortion

Packaging discontinuities introduce frequency-dependent signal distortion as a result of the inductive or capacitive nature of the discontinuities. Additional signal distortion is introduced by the dispersion and the skin effect of metal interconnects.

The microstrip lines on a printed circuit board are inherently dispersive, since they are incapable of supporting a pure TEM mode [13]. The mode's effective dielectric constant is a function of frequency, causing different frequency components of the signal to travel at a different speed. This effect becomes significant when the rise time of the waveform is smaller than 100ps and the signal has to travel more than a few centimeters.

The skin effect also contributes to frequency-dependent signal distortion for metal interconnects when the thickness of the interconnects is large compared to the skin depth. Due to the skin effect, high-frequency components within the signal experience higher attenuation, yielding non-negligible waveform distortion. In order to reduce the skin effect, the thickness of the metal has to be less than the skin depth of the metal.<sup>3</sup> A wider transmission line is thus required to accommodate signals with higher data rate while maintaining an acceptable DC and low-frequency loss, resulting in a net reduction of the interconnect density.

# 1.2 Optical Interconnects for High-Speed Digital Systems

Because of the bandwidth bottleneck associated with the existing interconnect and packaging technology, optical interconnect using free-space, optical waveguides or optical fiber thus becomes a viable and attractive alternative to increase the total system throughput. In this thesis, issues associated with using optical interconnect for high-speed digital systems are investigated. In particular, we will examine the potential problems and solutions of using dense optical interconnects for high-performance digital systems. In such systems, serialization of data cannot be employed to

<sup>&</sup>lt;sup>3</sup> The skin depth of copper is 2  $\mu$ m at 1 GHz, and becomes 0.7  $\mu$ m at 10GHz.

increase the channel density if the data rate of each channel is very high before serialization is introduced. Therefore, an interconnect technology with the capability of providing high density and high bandwidth is necessary for acceptance in digital systems.

## 1.2.1 Potential advantages

Dense optical interconnects have the potential of offering the following advantages:

- More sophisticated interconnection pattern. Light beams from different sources do not interfere with each other upon crossing. Very sophisticated 2-D and 3-D interconnect patterns based on planar optical waveguide and free space interconnect technologies, respectively, can thus be built from this principle, achieving a higher packaging density and shorter average signal propagation distance.

- Electrical reflection reduction. The reflections due to electrical discontinuities of a packaging system does not seriously affect the signal waveform as long as the round-trip propagation delay is less than the rise-time of the signal waveform. Therefore, multiple reflections due to impedance mismatch between different levels of packaging can be reduced or eliminated by replacing metal interconnects on higher packaging levels (such as the boards and the backplanes) with optical interconnects so that the round-trip propagation delay of any metal interconnects is shorter than the signal rise time.

- Higher bandwidth. The bandwidth of the optical interconnects is mainly limited by the interface electronics and has the potential to achieve a multi-gigabit data rate with very little signal distortion.

- Higher spatial density. The potential spatial density of either optical-waveguide or free-space interconnect technology is an order of magnitude higher than what can be achieved by the current metal interconnect technology (line spacing between two thin-film metal interconnects is ≥25 μm with a propagation distance less than 7 cm and increases to ≥100 μm for longer distance in order to avoid large crosstalk between adjacent interconnects [11]).

- Freedom from electro-magnetic interference (EMI). The propagation of light does not generate EMI to interfere with the surrounding circuit, nor can it be affected by the EMI produced

by the environment. As we will show in later chapters, optical crosstalk between adjacent optical interconnects is usually negligible.

Breaking of ground-loops. By using optical interconnects, current is no longer transferred between the transmitters and receivers, and thus the disturbance on the ground plane is reduced.

In addition, optical signals in an optical interconnect can not be disturbed by the noise of the ground plane and therefore the signal quality is improved.

## 1.2.2 Potential problems

On the other hand, we also have to be aware of the potential problems if optical interconnects are used to replace metal interconnects:

- Modal noise [14]. When multimode waveguides or fibers are used in conjunction with highly coherent lasers, the coherent interference of different spatial waveguide or fiber modes give rise to a speckle pattern. Fluctuations of the speckle pattern due, for example, to fluctuations in the spectrum of the optical source, can lead to modal noise if a mode-selective loss (such as a bad connector) is present in the optical link. Modal noise can cause a bit-error-rate (BER) floor which might not be tolerable in applications which require extremely low BER. Modal noise problem can be solved by either using a laser diode with large linewidth or premodulating the laser at a frequency comparable to the relaxation oscillation frequency of the laser diode [15].

- Optical reflections [16]. Index discontinuities are also unavoidable in waveguide or fiber interconnects. Reflections from the laser/waveguide interface might increase the linewidth as well as the relative intensity noise (RIN) of the laser. Other reflections due to the discontinuities along the optical path degrade the signals arriving at the receiver by reducing the eye opening and increasing the RIN.

- Optical crosstalk. Optical crosstalk can occur at the coupling between laser array and optical

waveguide array, between adjacent waveguides, or between the waveguide array and the

photodetector array as a result of the high packaging density required by the system. This

problem will be examined in detail in Chapter 5.

- Threshold uncertainty [17]. The large number of interconnects within a digital system require all of the receivers to be set at the same threshold. In practice, this threshold cannot be individually adjusted according to the characteristics of the source. This means there is no feedback between the driver and the receiver to adjust the laser output, which deteriorates with time. Local feedback might be able to correct for this problem, but the added logic circuitry would compete for chip area with other logic circuitry. This problem will be investigated in Chapter 9.

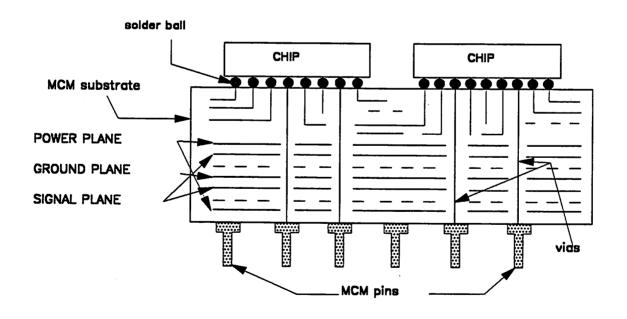

- High density required for optoelectronic components. Each typical single-chip module (SCM) may have over 100 of signal-I/O's, while a multi-chip module (MCM) can have several hundreds to several thousands of signal-I/O's. In order to provide optical interconnect in this environment, we have to be able to fabricate equally dense optoelectronic devices such as LD/LED, PIN/APD arrays, driver arrays and receiver arrays. This problem will be addressed in Chapters 7, 8, 10 and 11.

- Propagation delay [17]. The propagation delay of light in waveguide is unlikely to reduce below the 5.0 ps/mm value currently available. This compares unfavorably with the 3.5-4.0 ps/mm for metal interconnects if suitable fabrication processes are developed to use expanded PTFE type material as an insulator in multi-chip modules and boards. This seems to be a fundamental limitation for waveguide optical interconnects. However, metal interconnects suffer additional delay at each discontinuity as well as require longer settling time due to switching noise, crosstalk, and reflections. Therefore, propagation delay alone can not be used to evaluate the performance of an interconnect technology. System implication of this problem is further exploited in Chapter 3.

- Conversion delay. Signals are useful only in their electrical forms. Therefore, electrical-to-optical (E/O) and optical-to-electrical (O/E) conversions are necessary for every interconnect, which always involve nonnegligible conversion delay. This problem will be examined further in Chapter 4 and 9 in which optical amplifiers are proposed to boost the optical signal power, thus reducing the number of gain stages as well as the O/E conversion time at the receiver.

- Sensitivity to noise during E/O and O/E conversion. Existing optical interconnect technology has more loss than metal interconnection for such distances, due to the insertion loss of the connector and scattering loss of the surface defects of a waveguide. Therefore, more amplification and a higher sensitivity to both power supply noise and electrical crosstalk are experienced by the receiver. This problem is further aggravated by the high density required by a dense optical interconnect environment. In such an environment, there could be significant electrical interference either through the shared common power supply or through the parasitic inductance and capacitance. This problem is analyzed in Chapters 7 and 8 and a solution is proposed in Chapter 9.

- Thermal interactions. Laser characteristics, such as the wavelength, threshold current and differential quantum efficiency, are strongly affected by the operating temperature. Thermal interactions between adjacent lasers in a dense laser array could thus significantly degrade the system performance. A solution to this problem is also proposed in Chapter 9.

Among all these potential problems, optical crosstalks, threshold uncertainty, electrical crosstalk and thermal interactions result from high interconnect density as required by the system and will be addressed in detail in this thesis.

## 1.3 Architecture of Dense Optical Interconnects

In this section, possible architectures for dense optical interconnects are investigated. The constraints for designing the architecture of an optical interconnect systems are:

- Compatibility with existing packaging technology,

- Flexibility in fitting into the architectures of digital systems,

- Fault tolerance,

- Easy engineering change and fault diagnostics.

In the following, we will first examine the available interconnect forms. Possible interconnect architectures at backplane, board, and multi-chip module level will then be investigated. Possible E/O and O/E conversion schemes will also be evaluated.

#### 1.3.1 Interconnect media

Possible media that can be used for optical interconnects include:

- Free-space interconnect. Light travels fastest in free space. In addition, free space interconnects also offer the highest density and the most sophisticated interconnection patterns. Unfortunately, bulk optical elements such as lenses, holograms, beam splitters, etc., are usually unavoidable in free-space optical interconnects and thus make the alignment of optical beams very difficult and unstable with respect to environmental disturbances.

- Optical fiber. Optical fiber has the least loss compared with the other two media, and most of the technologies used in fabrication are already mature. Fiber ribbon cable also has the potential of providing reasonable interconnect density with regular interconnection pattern. However, fibers are incompatible with the existing packaging technology at the board or MCM level and they are not suitable for interconnects with very short distance or complicated patterns due to the possibly excessive volume occupied by the fiber cable.

- Planar optic waveguide. Passive planar optic waveguides are emerging as a viable alternative to optical fiber for very short distance interconnects. It has a higher propagation loss than optical fiber (0.01 ~ 0.5 dB/cm as compared to 0.2 dB/km) but uses technologies that are compatible with existing PCB or MCM technology. Therefore, it is more suitable for short-distance dense interconnect applications. However, coupling of light into and from the waveguides is also difficult and careful alignment cannot be avoided.

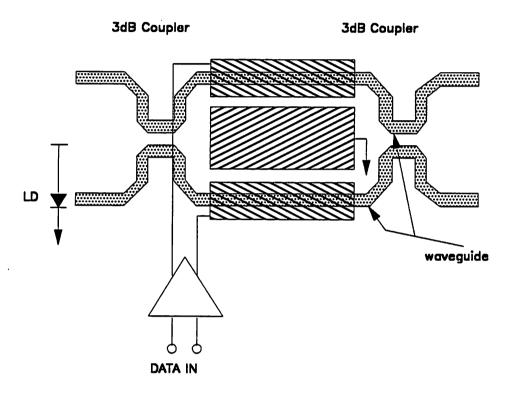

### 1.3.2 Backplane optical interconnects

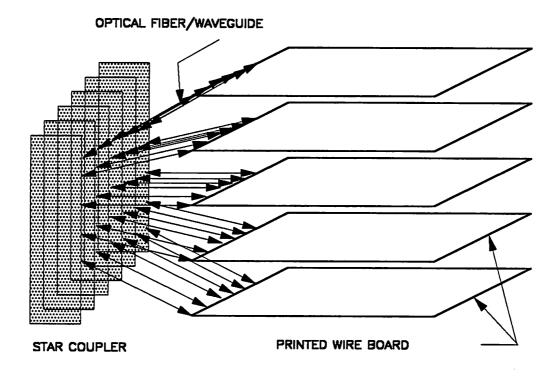

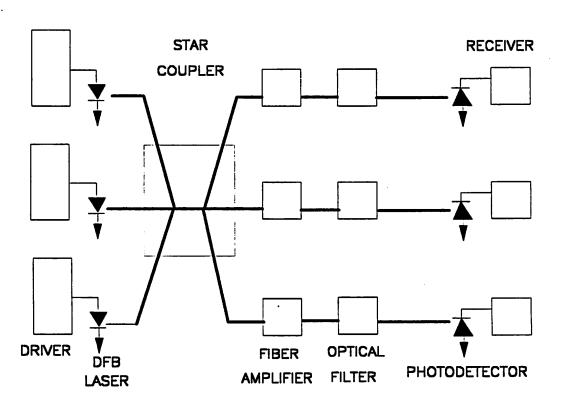

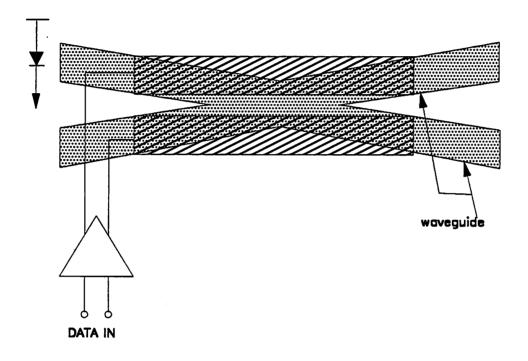

The function of a backplane is to provide a logical bus for all of boards connected to it. Free space, fibers and planar waveguides are all suitable for backplane interconnects. An optical backplane can be achieved through using of star couplers, as shown in Figure 1-2. Each board in the architecture occupies one input port and one output port from each of the star couplers so that signals input to any of the input port will be broadcast to all of the output ports. The total number of star couplers required can be greatly reduced by multiplexing several channels into a single waveguide with each channel using a different wavelength.

Figure 1-2. Optical backplane interconnects. Star couplers are used to combine and redistribute the data signals.

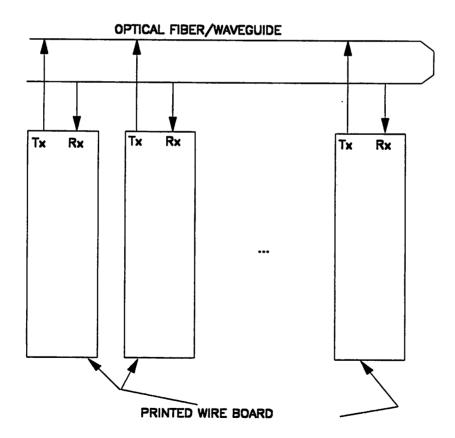

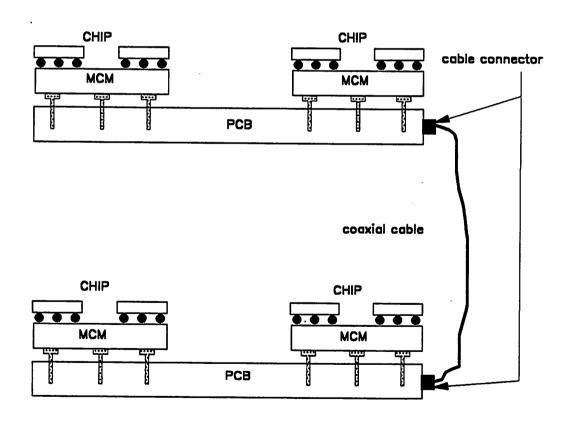

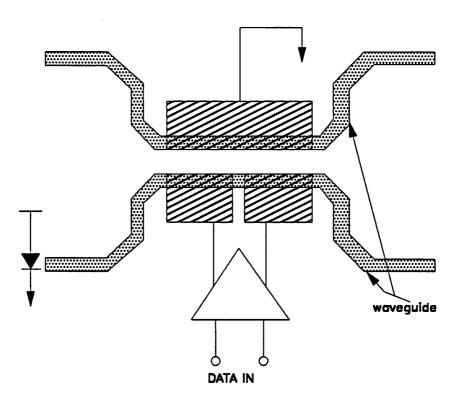

On the other hand, a topological bus can also be used to interconnect from one board to another, as shown in Figure 1-3. The bus is either folded back at the end or two independent buses are used because a unidirectional optical bus structure is usually easier to implement.

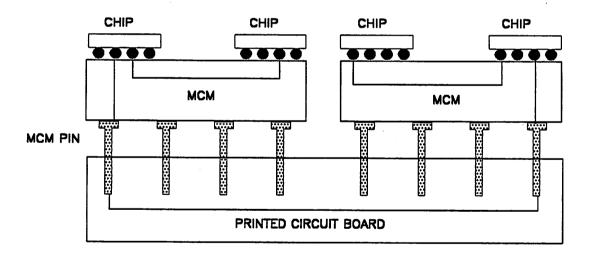

# 1.3.3 Board and multi-chip-module optical interconnects

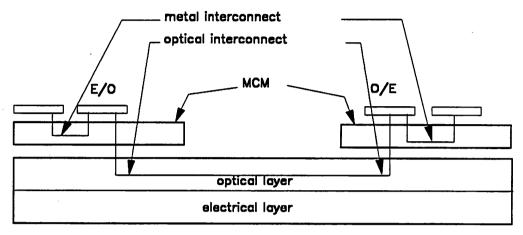

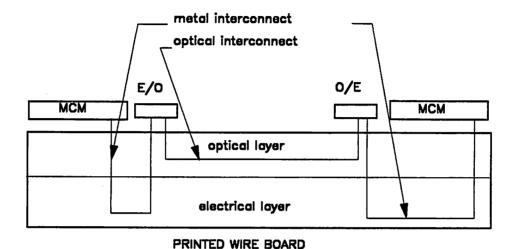

Board-level optical interconnects have to provide interconnects between different SCM's or MCM's while MCM-level optical interconnects have to provide interconnects between unpackaged wire-bonded or solder-ball-bonded flipped chips. At the board level, the E/O and O/E conversion can be performed within an SCM/MCM, or through separate special-purpose E/O and O/E chips.

Similarly, the E/O and O/E conversion at the MCM level can be performed within the chip where the logical signals are generated or via separate special-purpose E/O and O/E chips on an MCM.

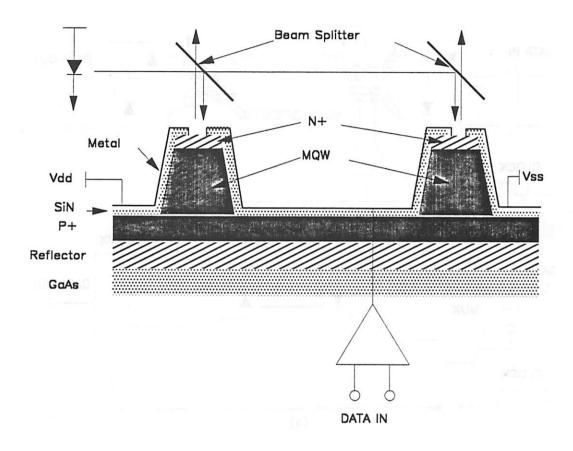

If the E/O and O/E conversion is performed before the package is connected to the next higher level, as shown in Figure 1-4, the electrical discontinuity can be minimized but the optical alignment is more difficult. On the other hand, more electrical discontinuity and thus more signal distortion is introduced if the E/O and O/E conversion is performed after the package is connected to the next level, as shown in Figure 1-5. However, this is acceptable for applications that require only moderate data rates.

Figure 1-3. Optical backplane interconnects. A topological bus is used to provide communication path between any two boards connected to the backplane.

PRINTED WIRE BOARD

Figure 1-4. E/O and O/E conversion. Conversion is performed at the same packaging level as the electrical signal is generated.

In both cases, there already exist multiple layers of metal interconnect to provide signal lines as well as power and ground plane. Optical interconnects can be developed on top of these metal interconnect layers to allow optical signals to propagate from one chip/module to another chip/module. In some cases, more than one optical layer may be necessary in order to provide sufficient interconnect density (such as at the MCM level) just similar to its electrical counterpart.

# 1.4 Differential Optical Interconnection

As discussed in 1.2.2, "Potential problems" on page 7, optical interconnects for a digital system have the following potential problems:

Figure 1-5. E/O and O/E conversion. Conversion is performed at the next higher packaging level.

- · Threshold uncertainty,

- Latency due to serialization/deserialization, encoding/decoding,

- Sensitivity to the switching noise and power supply noise.

- Sensitivity to the thermal interactions.

- Sensitivity to the DC level of the data at the receiver.

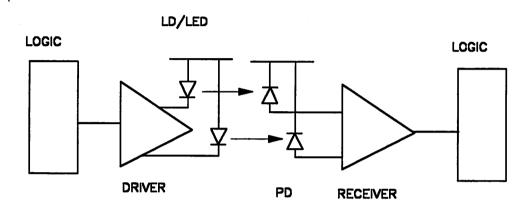

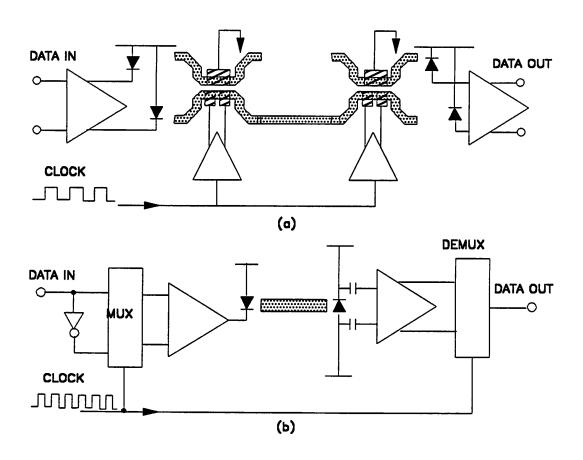

A fully differential optical interconnect architecture, as shown in Figure 1-6, is proposed in this thesis to minimize the detrimental effects arising from these potential problems. In this architecture, complementary optical signals are generated, transmitted, and received along two independent optical channels.

Figure 1-6. A fully differential optical interconnect architecture.

In a fully differential optical interconnect, the threshold voltage at the output of the receiver is always located at differential zero, which is halfway between two signal voltage of approximately equal amplitude but opposite sign, assuming two lasers at the differential transmitter have approximately the same average power and the attenuation along the differential path is similar. The threshold voltage is then independent of the actual power output of the lasers and the attenuation of the channel. Since the laser drivers and receivers are both fully balanced, the fluctuation of the current demands from the power supply is minimized, and thus the switching noise is reduced.<sup>4</sup>

<sup>&</sup>lt;sup>4</sup> An offset voltage is incurred when the laser output power or the attenuation is not balanced along the differential path. We will show in Chapter 9 that a total of 40% mismatch between the lasers, the attenuation of the optical path, and the quantum efficiency of the photodetector cause a 2.2 dB power penalty.

Furthermore, the differential structure for both drivers and receivers increases the common-mode rejection and thus reduces the sensitivity to the power supply noise. Therefore, differential optical interconnect is very attractive in a dense optical environment and has been pursued in detail in this thesis (Chapters 9-11). Fully differential drivers, receivers, and receiver arrays have been designed, fabricated, and characterized to verify this concept.

## 1.5 Prior Art of Optical Interconnects

Using optics for interconnections between VLSI systems was first suggested in [18, 19]. Early systems are mostly based on free space interconnects with the use of holographic optical elements (HOE) and spatial light modulators (SLM) to establish interconnect patterns. More recent systems have begun to use both optical fibers and planar waveguides [20]. An interprocessor optical link has been demonstrated between processor blocks in the Thinking Machines CM-2 at 400 Mbps [21]. The feasibility of board-level optical interconnect using polymer [22, 23] and silica [24] have also been demonstrated recently. Both of these prototypes can demonstrate a bit rate higher than 300 Mbps. However, the problems associated with the high density interconnect are yet to be addressed.

#### 1.6 Contribution of This Thesis

In this thesis, we demonstrate that high-density high-speed optical interconnects can be achieved in a synchronous digital system environment. The density of planar optical waveguides can approach 11µm pitch while the density of a wavelength-division-multiplexed (WDM) system can approach 37 GHz channel spacing for an OOK system with direct detection. We also show that a multi-stage tree-structured optical clock distribution system using optical amplifiers can achieve a very large fanout (≥10<sup>5</sup>) for synchronous digital systems.

The electrical interference between adjacent channels and from the neighboring digital circuitry could be a serious threat to a dense optical interconnect system. A fully differential optical interconnect architecture is therefore proposed, analyzed and implemented in this thesis. We show that a very high density transmitter and receiver array (≥16 channels/chip) can be achieved with minimal adjacent channel interference and switching noise (≤0.2% for the receiver array).

#### 1.7 Thesis Outline

The main theme of this thesis is to investigate potential problems and solutions arising from using dense optical interconnects in a digital system.

Since the metal interconnects cannot be avoided even in systems employing optical interconnects, we thus investigate in Chapter 2 the strength and the weakness of metal interconnects at various packaging level, and quantify when optical interconnects should be used.

The system requirements for dense optical interconnects are investigated in Chapter 3, in which a statistical timing skew model is proposed and used to analyze the timing requirements of various synchronous systems requiring parallel interconnections. We conclude that the rise time in the clocks and data signals must be as small as possible in order to maximize system performance. Therefore an optical clock distribution system using multi-stage optical amplifiers is proposed and evaluated both theoretically and experimentally in Chapter 4. The results show that a very large fanout from the clock distribution can be supported through this architecture with a proper adjustment of the system parameters.

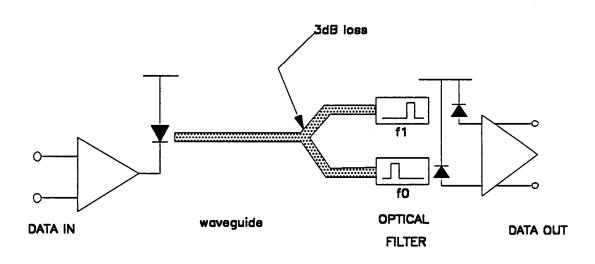

Optical and electrical crosstalk in a dense optical interconnect system are evaluated in Chapters 5-8. In Chapter 5, the mode coupling within a parallel waveguide array is analyzed. A crosstalk model which includes the effect of nonzero linewidth of the light source is used to evaluate the crosstalk penalty. Instead of using multiple parallel waveguides, more than one channel can share the same waveguide with each channel occupying a different wavelength, resulting in a wavelength-division multiplexing (WDM) system. In Chapter 6, a dense WDM system is simulated to determine the maximum channel capacity, taking into account the chirp from the laser and imperfect optical filtering.

Chapter 7 describes the simulation results of the crosstalk and switching noise in an optical transmitter array consisting of a driver array and a laser diode array under various packaging assumptions. Simulation results of the crosstalk and switching noise in an optical receiver array consisting of photodetector array, preamp array, and postamp array are reported in Chapter 8. Both of the single-ended and differential-ended configurations for drivers and receivers are considered in Chapters 7 and 8.

A differential optical interconnect architecture that minimizes the electrical and thermal interference is proposed and analyzed in Chapter 9. A fully differential driver and receiver based on this concept are designed, simulated and fabricated. In Chapters 10 and 11, we report the design and simulation results of these fully differential driver and receiver array.

A summary of this thesis and suggestions for future work are given in Chapter 12.

.

# CHAPTER 2 MODELING AND PERFORMANCE EVALUATION OF METAL INTERCONNECTS

#### 2.1 Introduction

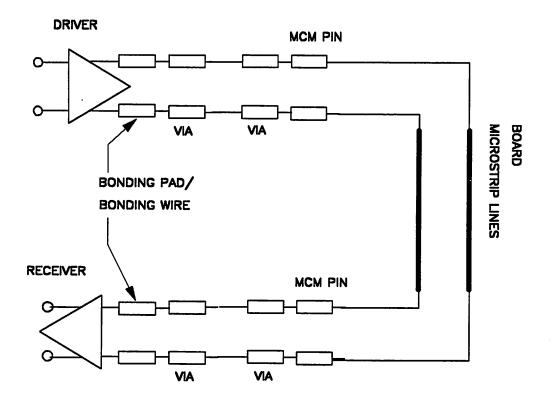

Metal interconnects have been used inside of most of the digital systems for either point-to-point or multi-drop interconnects. Even a system employing optical interconnects still cannot avoid using metal interconnects as part of its transmission paths. Therefore it is important to realize the strength and weakness of metal interconnects at various packaging levels so that optical interconnects can be used to supplement at those places where metal interconnects become the performance bottleneck.

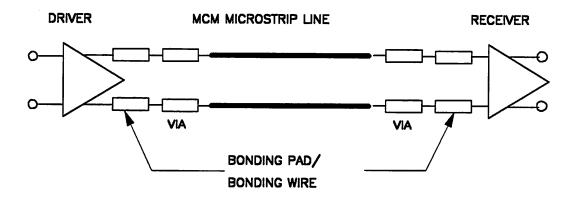

A high speed digital system usually assumes a controlled-impedance environment, in which a constant characteristic impedance is maintained for its metal interconnects in order to minimize signal distortion and reflections. However, electrical discontinuity cannot be completely avoided even in such an environment. Several types of discontinuities usually arise in this environment:

- Connector discontinuities. Due to the lack of a reference (ground) plane, the characteristic impedance of connectors such as bonding wires is very difficult to control.

- Via discontinuities. In general, multichip modules, cards, and boards can have more than one signal plane. Vias are used for signals to pass from one signal plane to another. However, the characteristic impedance of these vias is also difficult to control due to the lack of a reference plane.

- Signal-line bends and T-junctions. For routing purposes, some of the signal paths on a signal plane have to be bent by 45 degrees or 90 degrees. In other cases, signal line splitting is necessary in order to provide fan-out. Both of these cases create electrical discontinuities.

- Other line and vias (OLV) discontinuities. Ideally, a continuous ground or power plane can provide the best shielding and isolation between signal planes. However, due to the vias which are necessary for signals to pass from one signal plane to another, the ground and power plane are usually configured as a mesh plane instead of a continuous plane. Adjacent transmission

lines and vias surrounding a signal transmission line may increase its line capacitance and inductance and modify its local characteristic impedance.

These effects, together with the dispersion, skin effect, crosstalk, and switching noise, introduce intersymbol interference as well as signal distortion and limit the bandwidth of metal interconnects.

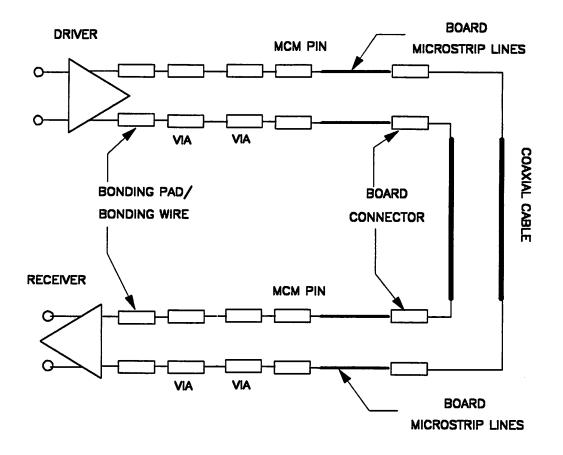

Transmission lines for interconnects in a high-speed LSI/VLSI system have been analyzed in [25-32]. Signal dispersion and distortion in microstrip lines at the multi-chip module (MCM) and printed circuit board (PCB) levels have been analyzed and simulated, for example, in [13, 33]. A linear source and a resistive load are usually used for analysis as well as simulations while the discontinuities of a transmission path are mostly ignored. On the other hand, various types of electrical discontinuities that can be found in a transmission line have been analyzed in [34] while their implications on waveform distortion is reported in [35, 36]. Signal distortion at a system level that includes driver and receiver circuits, transmission lines, and packaging discontinuities is simulated and evaluated in [37]. However, only the discontinuity due to bonding wire at a chip boundary is considered.

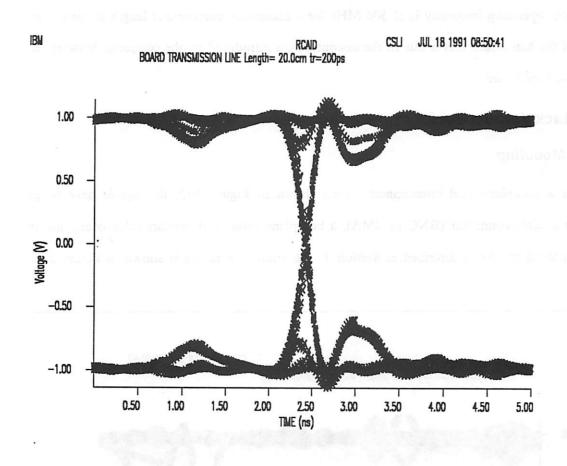

In this chapter, we investigate the signal distortion due to skin effect, DC loss, and electrical discontinuities at various package boundaries.<sup>5</sup> Using a strategy similar to [37], we simulate eye patterns of the following systems

- · From one chip to another chip located on the same multi-chip module (MCM),

- · From one chip to another chip located on a different MCM, and

- From one chip to another chip located on a different board.