## **CNS-1** Architecture Specification

A Connectionist Network Supercomputer

A Collaboration of the University of California, Berkeley and the International Computer Science Institute

TR-93-021 April 1, 1993

Krste Asanović, James Beck, Tim Callahan Jerry Feldman, Bertrand Irissou, Brian Kingsbury Phil Kohn, John Lazzaro, Nelson Morgan, David Stoutamire and John Wawrzynek

R4.989

## Preface

In the past two decades, the fields of VLSI systems design and massively parallel computation have grown into mature disciplines. Both fields began as research topics in industrial and academic laboratories; today, they form the core technologies for several large corporations. This report proposes a massively parallel computer, the Connectionist Network Supercomputer (CNS-1), which leverages off these fields. By targeting the computer to connectionist networks and related applications, we can focus on custom chip design and efficient software to achieve performance goals which challenge the best that industry has to offer.

Why are we building such a project in an academic environment? Three different issues have motivated us to design and construct the CNS-1.

The first issue involves the difficulty in applying neural network techniques to very large problems. Our research in the area of speech recognition has shown that current neural algorithms are helpful in solving problems with up to one million parameters. Performing this work cost-effectively required the construction of a smaller custom neurocomputer. Will the same algorithms work for one billion parameters? To answer this question requires a system that can train very large networks one thousand times faster than our current machines. Commercial machines with this capability do not exist.

The second issue relates to the field of computer architecture. A strong distinction, apparent in the publications of the field, exists between projects that are actually realized and those which are merely paper designs. As faculty, staff and students at a leading school of computer architecture, we believe it is important to be involved in the design and construction of applied software and hardware systems.

The third issue is the application of VLSI chip technology to system design. Dealing with the complexity of competitive VLSI design is a daunting challenge for an academic research group. However, several factors have led us to include custom VLSI design as a key element in the CNS-1 project. Technically, only custom VLSI lets us exploit the simplicity and parallelism of connectionist computation. From an academic standpoint, we believe university VLSI programs must undertake design projects that meet and challenge the industrial state of the art, and that these projects must be pushed to fabrication, test, and use in prototype systems. This approach teaches students relevant perspectives on VLSI design, and results in significant contributions to the engineering literature.

The goal of the CNS-1 project is to produce a system with supercomputer performance and flexible software for connectionist computation at moderate cost and on a time scale of a few years. This report outlines why we have chosen this task, why we believe we can achieve our goals and the current state of our design.

**About the researchers** The computing requirements of several neural network research projects at the International Computer Science Institute motivated our initial work in neurocomputing systems. These projects were directed by Dr. Nelson Morgan, Adjunct Professor of EECS and head of the Realization group at ICSI, and by Dr. Jerry Feldman, Professor of EECS and Director of ICSI. The first neurocomputing projects, which resulted in the Ring Array Processor (RAP) machine, were designed and implemented by ICSI staff professionals James Beck, Phil Kohn, and

Jeff Bilmes, in collaboration with Nelson Morgan. As our neurocomputing goals expanded to incorporate custom VLSI implementations, our research team grew to include other members of the UC Berkeley community.

John Wawrzynek, and graduate students Krste Asanović, Brian Kingsbury, and Bertrand Irissou, have joined James Beck in assuming primary responsibility for the hardware design of T0, a prototype of the CNS-1 neurocomputing node. Nelson Morgan is concerned with the suitability of processor architectures to target applications such as speech recognition. This group, along with postdoctoral researcher John Lazzaro and graduate students Tim Callahan, Stelios Perissakis, and Sven Meier, will also develop the hardware for CNS-1. UCB Professor Carlo Séquin has joined the project in an advisory role, bringing his experience from previous large computing projects at UC Berkeley, including the RISC-I and RISC-II.

The software group has also grown to meet the new demands of the project. Jerry Feldman oversees the design of the system and application software architecture of the machine, in collaboration with Phil Kohn and Dave Johnson. Also involved are graduate students David Bailey, Ben Gomes, Srini Narayaran and David Stoutamire. In addition to the full-time members of the project, many other researchers have played significant roles in the development of RAP, T0 and CNS-1. The RAP user community has provided invaluable feedback and suggestions. ICSI visiting researcher Thomas Schwair has taken on an important role in defining test strategies for T0 and CNS-1. Steve Omohundro of ICSI and visiting researcher Silvia Mueller have made key suggestions about the CNS-1 architecture and software.

**About this document** We have written this document for several reasons. We are now at the point in the project where we have settled the major architectural decisions and we wish to get feedback from other researchers. Unlike an industrial project, we have nothing to lose and everything to gain by sharing our ideas with others. We will also use this document internally as an informal design specification to orient new members of the team. We will continue to add details to it as we proceed. As with many large design projects the *formal* specification will ultimately be embedded in the descriptions written for simulation purposes.

This document is divided into three major parts. Part I provides the technical and motivational background. We briefly introduce the state of the art in neurocomputing and show how our work fits in. Several target applications are discussed and we present a set of performance requirements for our system. Part I closes with an overview of the CNS-1 machine hardware and software. Part II is a technical specification for the CNS-1 hardware architecture represented as a "snapshot" of our current thinking. Since it reflects work in progress, it must not be considered complete. Part III is an initial specification of the CNS-1 software. While this architecture document emphasizes hardware, the software specification is provided as a sanity check and to help readers understand the functionality of CNS-1. The three parts are preceded by an Executive Summary.

Acknowledgments Primary funding for this project since May 1992 has come from the Office of Naval Research, Clifford Lau, program director, URI-N00014-92-J-1672. Major support also comes from ICSI, whose funds are provided by the ministries of research of Germany, Italy, and Switzerland, and cooperating companies. Additional support comes from the National Science Foundation, grants MIP-8922354, MIP-8958568, Graduate Fellowships, and Infrastructure Grant number CDA-8722788.

# **Table of Contents**

| P | Prefacei                                             |    |  |  |  |

|---|------------------------------------------------------|----|--|--|--|

| E | xecutive Summary                                     | 1  |  |  |  |

| 1 | Neurocomputing                                       | 7  |  |  |  |

| 1 | 1.1 Motivations                                      | 7  |  |  |  |

|   |                                                      |    |  |  |  |

|   | 1.2 Connectionist Approaches in Signal Understanding | 10 |  |  |  |

|   | 1.3 Application Targets                              | 10 |  |  |  |

|   | 1.3.1 Speech Processing                              |    |  |  |  |

|   | 1.3.2 Other Concrete Tasks                           |    |  |  |  |

|   | 1.3.3 A Benchmark Problem                            |    |  |  |  |

|   | 1.3.4 CNS-1 Goals                                    |    |  |  |  |

|   | 1.4 Previous Neurocomputers                          |    |  |  |  |

|   | 1.5 The CNS-1 System Overview                        | 15 |  |  |  |

| 2 | Hardware                                             | 21 |  |  |  |

| _ | 2.1 Torrent Processor Node                           |    |  |  |  |

|   | 2.1.1 Torrent Chip Overview                          |    |  |  |  |

|   | 2.1.2 Instruction Execution                          |    |  |  |  |

|   | 2.1.2 Instruction Excertion                          |    |  |  |  |

|   | 2.1.4 Vector Unit                                    |    |  |  |  |

|   | 2.1.5 Vector Memory Pipeline                         |    |  |  |  |

|   | 2.1.6 Floating Point Arithmetic Support              |    |  |  |  |

|   | 2.1.0 Floating Fourt Anumetic Support                | 24 |  |  |  |

|   | 2.1.7 Kanous merrace                                 |    |  |  |  |

|   | 2.1.9 Data Cache (D-cache)                           |    |  |  |  |

|   | 2.1.9 Data Cache (D-cache)<br>2.1.10 Torrent Events  |    |  |  |  |

|   | 2.1.10 Torrent Events                                |    |  |  |  |

|   | 2.1.11 Network Interface                             |    |  |  |  |

|   |                                                      |    |  |  |  |

|   | 2.1.13 Torrent Silicon Technology                    | 21 |  |  |  |

|   | 2.2 Hydrant I/O Chip                                 | 28 |  |  |  |

|   | 2.3 Data Network                                     |    |  |  |  |

|   | 2.3.1 Topology                                       |    |  |  |  |

|   | 2.3.2 Physical Link Interface                        |    |  |  |  |

|   | 2.3.3 Message Format                                 |    |  |  |  |

|   | 2.3.4 Routing                                        |    |  |  |  |

|   | 2.3.5 Buffering and Deadlock Prevention              | 30 |  |  |  |

|   | 2.3.6 Message Priority                               | 32 |  |  |  |

|   | 2.3.7 Performance                                    |    |  |  |  |

|   | 2.4 TSIP Diagnostic Network                          | 32 |  |  |  |

|   | 2.4.1 Diagnostic Strategy                            | 32 |  |  |  |

|   | 2.4.2 Diagnostic Port                                | 33 |  |  |  |

|   | 2.4.3 TSIP-JTAG Comparison                           | 34 |  |  |  |

|   | 2.4.4 Additional TSIP Operations                     | 34 |  |  |  |

|   | 2.5 Physical Design and Implementation               | 35 |  |  |  |

|   | 2.5.1 Packaging Overview                             | 35 |  |  |  |

|   | 2.5.2 Module and Wiring Technologies                 | 36 |  |  |  |

|   | 2.5.3 Clock Distribution                             | 37 |  |  |  |

|   | 2.5.4 Heat Removal                                   |    |  |  |  |

|   |                                                      |    |  |  |  |

| 3 | Software                                | 43 |

|---|-----------------------------------------|----|

|   | 3.1 CNS-1 Software Overview             |    |

|   | 3.2 Machine Diagnostics                 |    |

|   | 3.3 cnsserver                           | 43 |

|   | 3.4 Run-time Resource Management        | 44 |

|   | 3.4.1 CPU Management                    | 44 |

|   | 3.4.2 Memory Management                 |    |

|   | 3.4.3 Network management                |    |

|   | 3.5 Application Software                | 46 |

|   | 3.5.1 Researcher Model                  | 47 |

|   | 3.5.2 Developer Model                   | 47 |

|   | 3.5.3 Wizard Model                      | 47 |

|   | 3.6 Programming Languages               | 47 |

|   | 3.6.1 Assembler and C/C++ Compiler      |    |

|   | 3.6.2 Gang-C/C++                        |    |

|   | 3.6.3 Sather                            |    |

|   | 3.6.4 Parallel Languages                | 48 |

|   | 3.7 Local Object Libraries              |    |

|   | 3.7.1 IEEE Floating Point Support       |    |

|   | 3.7.2 Block Floating Point Support      |    |

|   | 3.7.3 Timer Libraries                   | 49 |

|   | 3.7.4 Profiling                         | 49 |

|   | 3.8 Communication and Control libraries | 49 |

|   | 3.9 Distributed Object Libraries        |    |

|   | 3.10 Input/Output Libraries             | 50 |

|   | 3.11 Simulation Environments            |    |

|   | 3.12 Debugging                          |    |

|   | 3.13 Applications Programming           |    |

|   | 3.13.1 Dense Back-propagation           |    |

|   | 3.13.2 Sparse Connectivity Patterns     |    |

|   | 3.13.3 CNSim                            |    |

| R | eferences                               | 55 |

# **Table of Figures**

| CNS-1 Hardware Overview    | 16 |

|----------------------------|----|

| One Vector Datapath        | 23 |

| Vector Unit Registers      | 23 |

| Torrent Chip Block Diagram |    |

| Network Routing Protocol   |    |

| Data Network Interface     | 31 |

| Torrent Tower              | 36 |

| Quad Torrent Module        | 37 |

|                            |    |

## **Executive Summary**

**The Project** The CNS-1 project is an effort to build a real machine to run real programs which solve real problems. Although the project is based at an academic institution, our emphasis is on producing tangible results within a limited time frame and with a realistic budget. Along the way, we expect to raise and answer important questions in the fields of connectionist networks, VLSI design, computer architecture, system software design, and application frameworks for connectionist computation.

Aside from the CNS-1's role as a research vehicle, it is expected to fill a need in the area of connectionist applications. Recent advances in neural net research are outpacing the limits of the fastest available workstations and special purpose neurocomputing systems are becoming increasingly popular. ICSI has been successful at developing such systems over the past 4 years. Neurocomputers under development at other sites are examined in Section 1.4.

Connectionist applications have been written for general purpose supercomputers, but the match is sub-optimal. Current supercomputers are typically engineered to solve problems requiring high numerical precision and wide dynamic range, while many neural network algorithms allow reduced limits on both. We expect to take advantage of this and other application-specific considerations to produce a machine with supercomputer performance but with a major savings in cost and complexity.

**The Applications** We have explored a number of application targets for the CNS-1, including tasks in speech and language processing, auditory modeling, early and high-level vision, VLSI functional simulation, and knowledge representation. Extensive work in the area of connectionist speech understanding points to the need for a machine two to three orders of magnitude faster than the best machines available today. In condensed form, a statement of the requirements for one abstract problem, representative of potential applications is: *Evaluate the activations in a network with one million units having an average of a thousand connections per unit for a total of a billion connections. This should be done one hundred times per second.*

**The Machine** The CNS-1 is a multiprocessor system designed for the moderate precision fixed point operations used extensively in connectionist network calculations. Custom VLSI digital processors employ an on-chip vector coprocessor unit tailored for neural network calculations and controlled by a RISC scalar CPU. One processor and associated commercial DRAM comprise a node, which is connected in a mesh topology with other nodes to establish a MIMD array. One edge of the communications mesh is reserved for attaching various I/O devices, which connect via a custom network adaptor chip. The CNS-1 operates as a compute server and one I/O port is used for connecting to a host workstation.

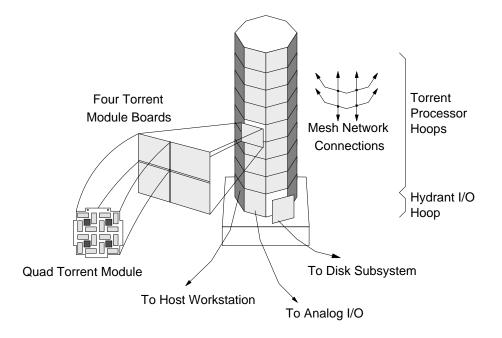

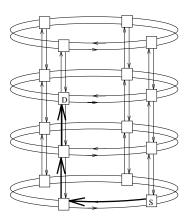

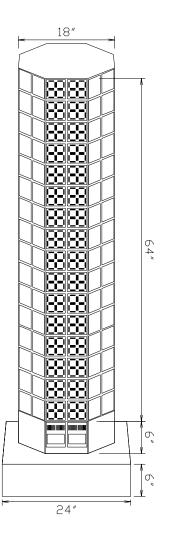

Four of the VLSI processing nodes are connected on a small module circuit board. Sixteen such boards are arranged on the exterior surface of an upright octagonal tower with network connections between boards. The tower provides mechanical support, along with clock, power and cooling resources. One hoop of sixteen boards provides 64 nodes; up to 16 hoops can be stacked on the vertical tower for a total of 1024 nodes. The mesh network connections provide a cylindrical topology, with the bottom edge of the net used for the I/O ports.

**The Node** Each node consists of one VLSI custom processor and 16 DRAM chips. Using 18 Mb devices, this provides 32 MB total of local memory, plus error correction. The DRAM is connected using four independent Rambus<sup>\*</sup> interfaces. The Rambus channel transfers address, data and control information at 500 MB/s using a synchronous, block-oriented protocol.<sup>\*\*</sup> No additional logic is necessary to complete a node, improving reliability and minimizing the board area required per processor.

**The Processor** The CNS-1 custom processor chip, called Torrent, is designed for high performance on connectionist algorithms and other data-parallel codes. The Torrent processor includes a 32b RISC CPU, a pair of vector arithmetic pipelines and a vector memory unit, all able to operate simultaneously. Parallel pipes, along with a 2 GB/s datapath to memory, allow sustained execution of 10<sup>9</sup> multiply-accumulate operations per second at a clock rate of 125 MHz. The RISC scalar unit, based on the industry standard MIPS-I instruction set architecture, is included to provide general computational support as well as address generation and loop control for the vector unit.

To support the large instruction bandwidth, Torrent has an on-chip 4 KB I-cache. A data cache is included on-chip to compensate for the latency in accessing DRAM. To sustain high overall bandwidth, the D-cache is non-blocking, allowing the processors to continue execution from the instruction stream while earlier misses are being serviced. The D-cache also merges multiple scalar accesses into blocks for greater efficiency. An additional feature of the architecture allows the data cache to be bypassed when accessing vector data to avoid cache pollution.

**The Memory** CNS-1 node memory is implemented using four Rambus channels, each with four 18 Mb RDRAMs for a total of 32 MB. With a *peak* channel rate of 500 MB/s, we anticipate *actual* performance in excess of 1 GB/s aggregate (per Torrent) for block transfers of 32B. Although the RDRAM is based on dynamic RAM technology, the design incorporates several on-chip 1 KB caches to improve the effective access time. Other DRAM-based memory technologies are being investigated (cached and synchronous DRAM) as a hedge against technical or availability problems with the RDRAMs.

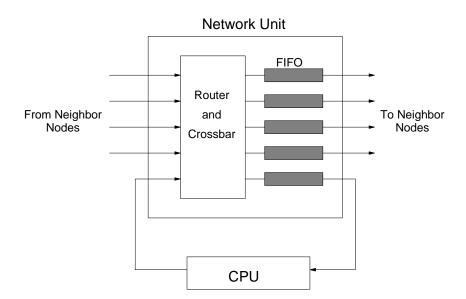

**The Network** Torrent includes an on-chip hardware router to handle message-based communications in the CNS-1 mesh. A fast processor-network interface supports efficient execution of neural networks even when sparse interconnections are mapped across several nodes. To improve efficiency, the message length is relatively short, and low-overhead access directly to the processor registers is provided in Torrent. The active message model is directly supported, where an arriving message triggers execution of a local event handler.

A network link between neighboring nodes consists of an 8b data bus and an acknowledgement wire in each direction. The data network is synchronous with a clock rate of 125 MHz, giving a peak data throughput of 125 MB/s in each direction per link. The largest CNS-1 system with 1024 Torrent nodes has a bisection bandwidth of 8 GB/s, or 8 MB/s per processor.

<sup>\*</sup>Rambus and RDRAM are registered trademarks of Rambus Inc.

<sup>\*\*</sup>An alternate design using synchronous DRAM is also under investigation.

**The I/O** Connection between the CNS-1 and external devices is through custom VLSI I/O nodes attached to an edge of the communications mesh. The I/O node, named Hydrant, includes the same network router as Torrent together with a set of send and receive buffers that can be accessed using a conventional parallel interface. Additional external components can be used to customize an I/O node to provide a wide variety of interfaces, including industry standards such as HIPPI and SCSI. This strategy also allows the construction of custom interfaces for sensors and actuators.

**The Diagnostic Network** A bit-serial diagnostic network is provided for hardware diagnostics, bootstrapping, and run-time monitoring. This diagnostic network is a high-performance extension of the industry standard JTAG and is controlled by the host workstation. The diagnostic network follows the same mesh topology as the data network, thereby giving redundant paths to any node. The two networks share the same connectors, simplifying wiring.

**The Software** Since the CNS-1 operates as an attached coprocessor to a host workstation, it will not use a standard operating system nor will it support multiple users. It will, however, include multiple programming and operating environments, to allow systems and applications programmers to work at several levels of abstraction. At every stage of software design, we expect to take advantage of available tools and systems which are compatible with the MIPS-I instruction set architecture. In particular, open systems compilers and debuggers will be extended to implement the Torrent vector unit instructions. Additionally, commercial computers from MIPS-compatible vendors will be used during code development and as simulation accelerators for the VLSI chip design.

Users with mainstream connectionist applications can use CNSim, an object-oriented, graphical high-level interface to the CNS-1 environment. Those with more complicated applications can use one of several high-level programming languages (C, C++, Sather), and access a complete set of hand-coded assembler subroutine libraries for connectionist applications. Simulation, debugging and profiling tools will be available to aid both types of users.

Additional tools are available for the systems programmer to code at a low level for maximum performance. Access to the low-level processor and network functions will be provided, along with the evaluation tools needed to complement the process.

**Performance** Each Torrent processor, operating at 125 MHz, can perform two billion 32b arithmetic operations per second in the vector unit. This corresponds to one billion connections per second, with a connection consisting of a multiply and an add operation. The memory bandwidth required to support this rate is available from the on-chip instruction and data caches. The off-chip memory access rate of >1 GB/s would typically not limit the raw performance, assuming moderate reuse of operands.

The initial CNS-1 implementation will include 128 processing nodes, giving a maximum computational capacity of 256 billion integer operations per second and a total of 4 GB of storage. The design is scalable to 1024 processing nodes for a total of up to 2 x  $10^{12}$  operations per second and 32 GB of RAM.

Part I

Introduction

## 1 Neurocomputing

Connectionist, or "neural" computation is structured as the interconnection of many simple functional units. Over the last 30 years, algorithms based on this style of computing have been used for a variety of difficult applications. For instance, in the 1960's these approaches were used for problems such as lunar terrain analysis and brainwave sleep state classification [Vig70]. More recently, connectionist algorithms have been applied with success to such problems as Hidden Markov model probability estimation for continuous speech recognition [MB90], zip code recognition [MBLD92], and spoken language identification [MC91].

This section discusses directions for future neurocomputing research and the reasons for building custom connectionist systems.

### **1.1 Motivations**

Much of the recent success of the connectionist approach is due to the explosion in computing power available to researchers. This technological advance has been matched by new theoretical work as well as a substantial body of application-oriented research. The synergy between these developments is encouraging experiments with networks and tasks that were not feasible even a few years ago. However, now that scientists and engineers are aware of the potential of connectionist methods, they typically find workstation power to be insufficient by several orders of magnitude. Conventional supercomputers are prohibitively expensive to purchase and maintain for many applications and lack the appropriate software. For these reasons, a number of researchers around the world are engineering supercomputers targeted for connectionist algorithms.

In a university-based research environment, there are only two justifications for undertaking an ambitious development project: either the result is needed, and cannot be obtained elsewhere, or the effort is necessary to advance science and technology. Both motivations are important for CNS-1. Recent work has shown the practicality of connectionist systems for a range of important problems, but has also revealed the need for computational resources far exceeding those available to investigators in the field. The realization of the RAP system at ICSI [MBK+92] is an example of an application-specific project which has yielded results crucial to our research, easily justifying the development effort. In addition, the RAP has proven beneficial to other groups that have acquired the system.

In the case of the CNS-1 project, there are already<sup>\*</sup> interesting results at several levels of hardware and software architecture. These results originate from our examination of the connectionist model of computation, which differs from more conventional models in several important ways. These differences allow us to design and build systems that are much simpler than conventional supercomputers and yet outperform them on the problems of interest to us. In addition, the design choices that work well for connectionist systems appear to be applicable to a broader class of computations and also yield insights into the general problems of parallel hardware and software development.

<sup>\*</sup>Start date for the project was May 1, 1992.

Why are connectionist algorithms of interest? There are a number of answers to this, and their order of relevance is strongly task-dependent. Viewed as probability estimators, connectionist systems are relatively free of distribution assumptions, an advantage when the distribution is unknown. Viewed as function approximators, such systems can implement arbitrary nonlinear mappings. Viewed as computational systems, connectionist networks provide strong parallelism for the applications that can be represented in this way. This parallelism can then be translated to significant performance advantages with parallel hardware. While it would be irresponsible to say that these approaches are *always* better than alternatives, it is clear as of 1993 that connectionist algorithms are a powerful and useful family of techniques for a variety of problems, and engineers and scientists benefit by having them in their "toolkit."

There are several features of connectionist computation that are exploited in the CNS-1 design. Experiments show that limited precision fixed point arithmetic suffices for almost all algorithms. Many problems are highly regular and are well suited to parallel and pipelined execution. Connectionist networks are "embarrassingly" parallel and map nicely to distributed memory machines. Communication is usually multicast and normally only values are sent, eliminating the read latency that plagues most distributed computing. There appears to be no need for memory coherence since global variables are not used.

Another major source of simplification in the CNS-1 design is that the machine will be used as a single-user, single-task attached processor. This decision does little to compromise our application requirements yet eliminates many of the most complex hardware and software difficulties in parallel computing.

For problems such as speech recognition, complete tasks have so many parameters to optimize that training time is the main impediment to progress, often forcing the researcher to make suboptimal decisions. While such research is computationally intensive, the required power could be provided by one of the many large conventional computers being built. Researchers can often do very well with a conventional vector supercomputer, such as offerings from Cray Research. However, the computations per dollar for these machines is quite low in comparison to what can be achieved with an application-specific architecture. One of the reasons for this is that connectionist computation can be done with moderate precision (commonly 8 bits or less for activations and 16 bits for weights). This not only reduces the size of arithmetic units, but more importantly reduces the amount of memory and memory bandwidth requirements significantly.

Probably the most graphic argument for an application-specific system over a general purpose processor is the RAP. Recent experiments at Berkeley show ICSI's RAP machine to be slightly more effective than a single head Cray X-MP for a variety of connectionist computations at less than 1% of the cost. Both of these machines are orders of magnitude less powerful than the CNS-1.

We estimate that when the CNS-1 becomes functional, it will be 20-100 times more efficient in terms of cost, electrical power requirements, weight, and size, than conventional supercomputers. This is true even for microprocessor-base parallel distributed memory supercomputers such as Intel's Paragon series. Table 1 compares some features of two Paragon models and two sizes of CNS-1 systems. For the CNS-1 price, the estimate is based on a RDRAM parts cost of \$20 and a cost for all other components associated with a node at \$320. The total parts cost is then multiplied by a factor of 4 to suggest a selling price if CNS-1 were produced commercially.

| Table 1: CNS-1 vs. Intel Paragon Comparison                                                               |            |       |                      |              |  |  |  |

|-----------------------------------------------------------------------------------------------------------|------------|-------|----------------------|--------------|--|--|--|

| Machine                                                                                                   | Power (kW) | Nodes | Peak Performance     | Price (est.) |  |  |  |

| Paragon XP/S-20                                                                                           | 19         | 192   | $19.2 \times 10^{9}$ | \$6,700,000  |  |  |  |

| Paragon XP/S-50                                                                                           | 86         | 672   | $50.4 \times 10^{9}$ | \$19,000,000 |  |  |  |

| CNS-1 (small)                                                                                             | 2          | 128   | $250 \times 10^{9}$  | \$330,000    |  |  |  |

| CNS-1 (largest)                                                                                           | 16         | 1024  | $2 \times 10^{12}$   | \$2,600,000  |  |  |  |

| Note: Paragon figures are for double-precision floating point while CNS-1 uses 32-bit integer operations. |            |       |                      |              |  |  |  |

Not indicated in the chart are other advantages that accrue from designing a machine specifically for connectionist applications. One particular emphasis in the CNS-1 design is a simple method for attaching external sensors and actuators operating under a soft real-time constraint. Retrofitting such an interface to a conventional supercomputer may be prohibitively complex. Another advantage of a custom design is that the realized performance is routinely a higher percentage of the peak value than on general purpose supercomputers. Put another way, the general purpose supercomputer designers include some features in their machines that are expensive yet do not improve performance on connectionist networks.

In the near future, the greatest challenge to a custom architecture machine for connectionist research comes not from the general-purpose supercomputers, but low cost, high performance workstations. Performance in uniprocessor workstations is improving by as much as 60% per year, and multiprocessor systems are starting to be introduced. We believe, nevertheless, that workstation vendors will concentrate their efforts in areas that will not yield optimal improvements for the connectionist community. In particular, the most favorable pricing (in terms of dollar per operation) is frequently the workstation model designed for the highest volume of sales. Such low-end systems usually feature limited expandability, making them incompatible with our large task requirements.

Justifying the effort to construct the CNS-1 rests on the expected performance advantage of application-specific computing. Briefly, the CNS-1 attains this advantage with:

- Application-optimized processor design.

- Parallel processing units on each silicon die.

- Multiple computing nodes within one chassis.

- Simplified memory system architecture.

- A low-latency high-bandwidth communication network between nodes.

- Flexible, high-performance I/O channels.

- New programming paradigms customized for the machine.

- The exclusion of features (hardware and software) least likely to improve performance on a real application.

Even when academic projects result in implementations that are not faster than commercial computers, they often teach us much that can affect the entire field of computing. An example here at Berkeley was the RISC development. While the RISC I and II chips were not faster than commercial microprocessors at that time, they showed the strengths of this style of computing quite convincingly.

#### **1.2** Connectionist Approaches in Signal Understanding

The human nervous system is still the best example that we have of a complete system to perform complex problems in signal understanding. For decades this system has served as a conceptual model for such tasks as speech and image understanding. Sensory input systems such as the cochlea (inner ear) are roughly imitated in speech recognition systems by the microphone and some simple form of spectral analysis. Phonetic classification and likelihood estimation, assumed to occur in a number of brain structures, is typically done in artificially engineered systems using some kind of probability estimator such as a Gaussian mixture model or a back-propagation trained multilayer perceptron. Assembling phonetic information into meaning is probably done in association areas all over the brain, but this process is little understood. The corresponding engineering approach is usually very primitive, for example using a list of allowable wordpairs. Typical engineering systems also do not permit much feedback from these higher level processes into the earlier decisions, while anatomical pathways exist in the nervous system for many such interactions.

While connectionist approaches are not the only way to implement these different pieces of the signal understanding problem, they are plausible, and offer at least a set of techniques that have not been fully explored (particularly for the more syntactic and semantic cases). These approaches generally tend to be less bound by restrictive assumptions than previous techniques, and permit higher-order interactions. Additionally, connectionist architectures provide a consistent expressive framework for all of the pieces of the problem, in contrast to the current situation in which various components are designed by scientists and engineers from different disciplines, often with different perspectives and jargon. Incorporating connectionist models in all aspects of signal understanding should permit feedforward and feedback between different parts of the system in a much more flexible way than is currently practical.

Researchers in this area must use fully programmable digital computers, as many of the design issues are completely unresolved. With some specialization, (particularly moderate fixed-point wordlengths), fast neurocomputers can provide significant advantages over general purpose computers for this research, while being much more flexible than specialized analog systems. The latter can be more efficient for the modeling of specialized sensors and feature extractors, however. The most useful complete systems will probably require both forms of implementation, and effective and flexible interfaces between the two are a major concern in our project.

#### **1.3 Application Targets**

It is difficult to design a parallel machine to be equally effective for all applications. Ideally the design team would carefully examine proposed tasks and determine which features were required to optimize performance and cost for the target applications. Unfortunately, for many cases there is a "chicken and egg" problem; that is, the optimal computer cannot be designed until we have experience with the application, but we cannot gain this experience until we have a machine that can run the application efficiently.

A feasible solution to this dilemma is to observe the requirements for smaller tasks that we believe to be similar to our end goals, as well as to analyze those cases which have no good working precedent. A machine is then designed to perform well on both sets of these problems. Iterations on this process should result in better solutions both at the algorithmic and architectural levels.

We have developed a number of application targets for the CNS-1. These range from obvious extensions of tasks we have run on parallel computers at ICSI through bona fide applications that have never been implemented on fast hardware. In addition, we have developed an abstract target application which we believe to be representative of a class of problems which has withstood conventional analysis.

#### 1.3.1 Speech Processing

Over the last few years, we and others have demonstrated that fairly large connectionist networks (more than one million parameters) are effective for the estimation of posterior class probabilities given training data that is a sparse sampling of a highly dimensioned feature space. Specifically, we have been training large multilayer perceptrons to estimate phonetic probabilities for continuous speech recognition. This is of interest because the resulting estimates are provably discriminant (that is, trained to differentiate between different classes) and are also essentially free of distributional assumptions. Recognizers using this mechanism have now been tested on large standard databases, (principally DARPA's Resource Management corpus), and have been found to be at least competitive with more standard approaches while requiring fewer careful optimizations for a particular task or vocabulary [RMCF92].

The Resource Management task incorporates a 109-speaker training set with a total of about 3 hours of speech. This translates to over a million feature vectors of 10 milliseconds each. These features are used to train networks with approximately one million parameters, requiring 5-10 iterations through the training set. The resulting training problem requires on the order of  $10^{14}$  arithmetic operations. Depending on the details of the run, this requires a few days of computing on our current parallel computer, the RAP.

New tasks we are attacking require significantly more computing for a number of reasons:

- The databases we are considering for future research have ten times more training data than the Resource Management corpus.

- We are planning further research in robust front ends, which cannot be evaluated without complete training and recognition iterations. Therefore, a 1-5 day training time is not practical for such an optimization; a one hour turnaround is a more workable goal.

- Network size has increased inexorably over the last few years and the trend will continue. Before the RAP, our nets were typically under 100,000 connections. Our current speech recognition nets range from 300,000 to 1.5 million connections.

When taken together, these increased requirements suggest a computing engine that is 2 to 3 orders of magnitude more powerful than the RAP. This translates to 4 to 5 orders of magnitude faster than a Sparc 2 workstation, or perhaps 3 orders of magnitude more powerful than a 1995-vintage workstation.

In addition to greater raw performance, larger networks and increases in training set size, the CNS-1 includes a more diversified instruction mix to handle the "non-neural" operations. One potentially tricky area is the ability to easily couple dynamic programming steps and the network evaluations without excessive communication overhead. This requires that dynamic programming and pointer bookkeeping must be handled *within* a CNS-1 node.

A final, more speculative point is that as nets grow larger they tend to be more sparsely interconnected. For huge nets, full connectivity is not reasonable, even if the computational power were available, because we lack sufficient data to train the large number of parameters. However, in our experience this sparseness is generally not in the form of random connection vacancies, but rather in the form of fully-connected subnets that are glued together in application-specific ways. Such "chunky" networks must be supported in the CNS-1 for the speech recognition research application.

#### 1.3.2 Other Concrete Tasks

In addition to the speech connectionist applications of CNS-1, we are interested in the potential of CNS-1 as a general purpose connectionist accelerator. The connectionist model of computation differs in many ways from conventional models and we exploit these differences in the design. In some cases, such as speech recognition, we already have clear ideas on how to apply the capabilities of CNS-1. There are other domains, such as early vision and auditory modeling, where the outlines of promising approaches are understood but the details remain to be worked out. Even more intriguing is the prospect that a connectionist supercomputer will encourage explorations on unwieldy problems previously ignored.

We expect many applications will run efficiently on the CNS-1. The following lists some we have considered during the design.

**Language processing** Speech recognition systems such as the one referred to above have largely ignored language processing above the phonetic level. Once syntactic, semantic and pragmatic knowledge is incorporated, the connectionist computation will expand significantly for the speech understanding task. Connectionist language processing models are under development [Sha88].

**Auditory modeling** Auditory models such as the correlogram [Lyo92] are instantiations of known physiological or psychological functions. Full implementations require an enormous amount of computation, and researchers would like to couple modifications of these subsystems with speech training systems so that the effect of model changes could be evaluated. This is of particular interest for speech degraded by noise and reverberation.

**Early vision** An example task is texture recognition [MP89], which requires no learning (the convolution kernels are assumed). For the case of NTSC video and 100 kernels, 100 billion connections per second are required. There is considerable work at UCB being done in this area.

**High-level vision** This task involves recognition and analysis of objects from some earlier low-level image processing. In addition to the large raw computational requirement, high-level vision is believed to require the sparse interconnection (fan-in and fan-out averaging 100-1000) of hundreds of thousands of units. This is a research focus of the ICSI applications group.

**Functional simulation of specialized hardware (VLSI)** The design of extremely fast specialized hardware for connectionist computation requires many simulations at the switch or logical level. For this application, the interconnection is typically extremely sparse, since local connectivity is limited in planar silicon architectures. Functional simulation fits well with a major thrust of the EECS department at UCB.

**Large conceptual knowledge representation studies** Many tasks, including high-level vision and language processing described above, rely on large fully associative memories, like human memory. Simulating such rich conceptual systems was a goal of the original Connection Machine development, and remains a goal of current research.

#### 1.3.3 A Benchmark Problem

In addition to the concrete tasks described above, it is important to consider a more abstract problem that may clarify some of the costs and tradeoffs resulting from design decisions. To that end, we have defined the following problem description:

Evaluate a network with one million units and an average of one thousand connections per unit for a total of one billion connections. This should be done 100 times per second.

This description is deceptively simple, and does not specify the distribution of connections. Without the connection context, it is not possible to relate this benchmark to the previously described concrete tasks. Nevertheless, it does allow us to examine the relationship between the connectivity and performance for alternate design choices. In particular, some extreme connection distribution examples must be examined to ensure that the CNS-1 performance is not unacceptably degraded.

#### 1.3.4 CNS-1 Goals

Given the above target tasks and perspectives, we conclude this section with a summary of CNS-1 performance goals:

- Connectionist compute power. The minimum configuration machine should evaluate 100 billion connections per second, which requires a weight-reading bandwidth of 200 GB/s for 2B weights.

- Learning capability. Back-propagation learning, including weight updates, should be accomplished in at worst 1/5 of the evaluation rate.

- Communication capability. For the large abstract problem, we require a broadcast of 10<sup>6</sup> activations 100 times per second. Each node must then read 10<sup>8</sup> bytes/sec from the network (the inputs from all units), but write out a much smaller amount (only the outputs from the units represented locally).

- Storage. Two GB are needed to hold one billion 2-byte connections. When activation tables and pointers for sparse networks are included, another 2 GB are required. This 4 GB represents a minimum, and larger CNS-1 systems will be in demand for retaining the largest data sets.

- Sparseness. A network with arbitrary sparseness will run on CNS-1, although with reduced efficiency compared to applications with fully connected subnets. The performance degradation with progressively random sparseness should be gradual, so that a fully random interconnection pattern should be evaluated at a speed that is no worse than 1% of peak.

- Shared Weights. Many of the tasks described above incorporate shared or tied weights. While in some cases these weights have been tied to save storage, even in the case of a large available memory shared weights are a useful way to enforce properties such as shift-invariance, as well as to reduce parameters for smooth estimators. Shared weight evaluation and learning must be supported.

- Non-connectionist processing. Many applications require integrating operations that are not fixed point vector operations. The CNS-1 node must be able to perform general scalar processing at a rate only moderately reduced from the peak rates of vector operations.

- Floating point support. During the development stages of fixed point algorithms, it is important to be able to write code with multiple precision and floating point representations. Additionally, the final form of an algorithm may include occasional floating point or double precision fixed point variables. The CNS-1 processing node will contain enhancements to allow handling such variables with a reasonable performance trade-off.

- Coding capabilities. CNS-1 is intended as a fully programmable computer, and is not just a fixed function back-propagation machine. Software must be developed to give CNS-1 the "look and feel" of a more general computer, if it is to be anything beyond an academic curiosity. The use of carefully hand-coded library routines will provide efficient operation for the most common functions. However, another design goal is the graceful performance degradation for the general (non-parallel) operations included in the application code. Provision for clean mechanisms of expression for these programming modes is another key requirement for the system.

- Soft real time capabilities. While hard (deterministic) timing guarantees are probably not required for CNS-1 applications, an important aspect of the machine's intended function is the ability to interface interactively with analog sensors and activators. For instance, real-time streams of speech and video images must be accepted by the machine and processed within the appropriate frame times. These time frames are 33 msec for video, 10 msec for preprocessed speech, and 60 µs for raw speech. There should be a simple high-performance interface mechanism that can be used to connect CNS-1 to a variety of target external devices, such as analog circuits that implement complex auditory models.

## **1.4 Previous Neurocomputers**

A number of parallel computers have been built in the past with connectionist computations as the target task. Many of these have used special-purpose architectures incorporating commercial DSP chips. Examples of this approach are the NeuroTurbo from Nagoya University [IYM+89] and the Ring Array Processor (RAP) machine that has been developed at ICSI in Berkeley. In the latter case, the ring-based machine has been used since 1990 as an essential component in the development of connectionist algorithms for speech recognition. Implementations of this machine consist of 4 to 40 Texas Instruments TMS320C30 floating-point DSP chips connected via a ring of Xilinx programmable gate arrays, each implementing a simple two-register data pipeline.

Several related efforts are underway to construct programmable digital neurocomputers, most notably the CNAPS chip from Adaptive Solutions [Ham90] and the MA-16 chip from Siemens [RBR+91]. Adaptive Solutions provides a SIMD array with 64 processing elements per chip, in a system with four chips on a board controlled by a common microcode sequencer. As with the CNS-1, processing elements are similar to general purpose DSPs with reduced precision multipliers. Unlike the CNS-1 hardware, the Adaptive Solutions chip provides on-chip SRAM sufficient to hold 128K 16b weights but has no support for off-chip memory. Larger networks require additional processor chips to obtain the required weight storage.

Like the CNS-1 hardware, the MA-16 leverages the high density and low cost of commercial memory parts. This chip is a direct realization of three general network formulae that summarize many connectionist computations. The system that is envisioned will consist of a 2D systolic array containing 256 of these chips, and the resulting system provides impressive raw peak throughput. Multiple Motorola 68040s with additional integer ALUs are used as general-purpose processors to complement the systolic processing array.

Important goals in the CNS-1 design are to achieve high performance on large, irregular network structures and to tightly couple the scalar non-connectionist portions of real applications with efficient connectionist computation. Both the CNAPS and the MA-16 are designed to be cascaded into larger SIMD processor arrays with only auxiliary scalar capabilities; the CNS-1 is MIMD with integrated scalar units.

#### 1.5 The CNS-1 System Overview

The CNS-1 is a multiprocessing system designed for connectionist network calculations and other moderate precision integer calculations. The architecture of the CNS-1 system is similar to that of other massively parallel computers; major differences arise in the details of the processing nodes and the communication mechanisms. A custom VLSI digital chip is tailored for neural-network calculations, with integral vector processing units yielding up to two billion integer operations per second. Computing nodes are connected in a mesh topology and operate independently in a MIMD style. Each node contains a private memory space and communicates with others through a simple message passing scheme. The initial CNS-1 implementation will include 128 processing nodes, giving a maximum computational capacity of 256 billion integer operations per second and a total of 4 GB of storage. The design is scalable to 1024 processing nodes for a total of up to  $2 \times 10^{12}$  operations per second and 32 GB of RAM. One edge of the communications mesh is reserved for attaching I/O devices, allowing up to 8 GB/s of I/O bandwidth. The CNS-1 system is attached as a compute server to a host workstation.

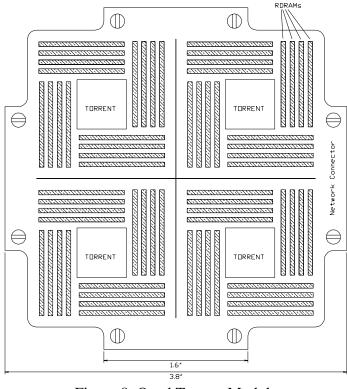

Each processing node comprises a custom single chip processor, called Torrent, and DRAM chips. No external logic is necessary to complete a node, increasing reliability and minimizing the board area required per processor. Four complete Torrent nodes are placed on a circuit board module, which is attached to the outside surface of an octagonal cylinder (Figure 1). Clock, power and cooling resources come from the center of the cylinder, while the communication network connections are made along the cylinder surface. By placing the modules on the cylinder surface, network cabling is kept simple and communication distances are minimized.

The Torrent chip includes a 32b RISC scalar unit compatible with the industry standard MIPS-I instruction set architecture. This RISC CPU provides tightly coupled scalar processing for those applications which have a significant non-neural component. The main compute engine in Torrent is a vector unit with eight parallel 32b datapaths, where each datapath can complete two arithmetic operations per cycle. To provide the high memory bandwidth needed to keep the vector unit busy, the memory interface implements four Rambus channels [Ram92] with an aggregate memory bandwidth of well over 1 GB/s. The Torrent nodes in CNS-1 have four 18Mb RDRAM<sup>\*</sup>

<sup>\*</sup>Rambus Dynamic Random Access Memory.

chips per Rambus channel giving a per node total of 32 MB of RDRAM.<sup>\*</sup> An on-chip data cache is included to reduce average memory access latencies, but may be bypassed when accessing vector data to avoid cache pollution. On-chip instruction cache helps provide the required instruction bandwidth.

Figure 1: CNS-1 Hardware Overview

Torrent includes an on-chip hardware router to handle communications in the CNS-1 network. An important feature of Torrent is a fast processor-network interface tailored for effective execution of connectionist networks with sparse interconnections and activations. To handle communication of continuous external asynchronous sensory data streams, Torrent hardware implements a short message protocol with access directly to processor registers. However, larger block transfers can be programmed in software with minimal CPU burden due to low-overhead event handling. This event handling is based on the active message model [vEC+92], with an arriving message triggering execution of a local event handler routine. This mechanism is similar in spirit to message-driven architectures [DW89], but requires simpler hardware and decouples message handling from computation.

A host computer and other devices connect to the processors of the CNS-1 through custom VLSI I/O nodes attached to an edge of the communications mesh. The I/O node, named Hydrant, includes the same network router as Torrent together with a set of message send and receive buffers that can be accessed over a conventional parallel interface. Additional external components can be used to customize a Hydrant to provide a wide variety of I/O interfaces, including standard peripheral interfaces, such as HIPPI and SCSI. For custom interfaces to sensors and actuators, field

<sup>\*</sup>Alternative memory system designs using wider busses with conventional DRAMs are also being considered.

programmable gate arrays may be used as the peripheral interfaces to Hydrant. In early versions of the machine the host will provide access to disk storage. Later improvements will include direct interfaces to fast mass-storage subsystems without requiring host intervention.

A mesh topology is used for the data network connecting Torrent and Hydrant nodes. A network link between neighboring nodes consists of 8b of data and an acknowledgement wire in each direction. The data network is synchronous with a clock rate of 125 MHz, giving a peak data throughput of 125 MB/s in each direction per link. The largest CNS-1 system with 1024 Torrent nodes has a bisection bandwidth of 8 GB/s, or 8 MB/s per processor.

A separate bit-serial network (TSIP) is provided for hardware diagnostics, bootstrapping, and run-time monitoring. This diagnostic network is a high-performance extension of the industry standard JTAG and is controlled by the host workstation. The network wiring is implemented using the same connectors and cables as the data network mesh.

Much of the software for CNS-1 will be developed with the help of industry standard compilers and debuggers for MIPS-I compatible machines. At the lowest level of software development will be diagnostic routines for detecting hardware failures in the machine. These routines are written for the host system and use the diagnostic network to control the CNS-1 for the duration of the diagnostic tests.

During normal operation, users start their application from the host by invoking the CNS server program (cnsserver) and giving it the name of a CNS-1 executable. Assuming the machine is free, the server process first resets each node and then downloads and starts an executable program. This program will usually be the same for each node (SPMD) but may be different on different nodes (MIMD). Next, cnsserver enters a monitoring loop, repeatedly scanning for error flags and profiling information across the diagnostic network. In the early CNS-1 system, the host is also used for operating system support, so cnsserver may be interrupted with system I/O requests from the array. Finally, the application will send an exit message back to cnsserver which will then clean up on the host and release the machine for the next user.

A number of high-level languages will be supported by CNS-1. The commercially available MIPS languages (C, C++, FORTRAN, Pascal, Ada, etc.) will be supported along with an object oriented language developed at ICSI, Sather [Omo91]. In addition, a Torrent assembler filter will be written to help in the development of the optimized libraries.

Support for parallel languages on distributed memory machines is still very much a research issue. Current efforts to port our parallel version of Sather, called pSather [FLR92], to the CM-5 should provide valuable lessons in this area. The CNS-1 hardware is simple, fast, and flexible, and should prove an interesting vehicle for further research into parallel languages.

CNS-1 is an application-specific system, and an important component of the project is the development of software libraries for the applications we have in mind. These libraries should allow a high percentage of the peak performance of the machine to be made available to connectionist researchers in a straightforward and flexible manner. These connectionist libraries will be based on simulators that have evolved over several generations at ICSI, including parallel versions for the RAP.

Part II

Hardware

# 2 Hardware

This section presents the hardware design of the CNS-1. The two custom VLSI circuits, the Torrent processor and the Hydrant network adaptor are described first. Next follows a description of the two internal networks used in the CNS-1, the data and diagnostic nets. Lastly, the physical design issues are introduced, with emphasis on clocking, power distribution, packaging and cooling details.

## 2.1 Torrent Processor Node

The Torrent processor node provides the computational power of the CNS-1. Each node includes the Torrent processor, DRAM chips and communication channels for the interconnection of several nodes.

## 2.1.1 Torrent Chip Overview

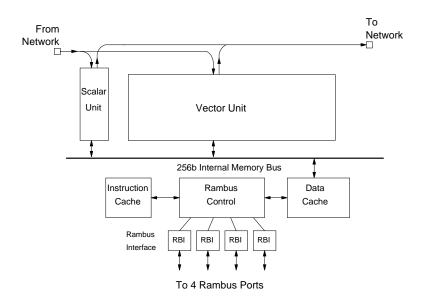

Torrent is a single chip processor designed for high performance on connectionist algorithms and other data parallel codes. The processor is a highly pipelined vector architecture based on the MIPS-I instruction set architecture (ISA) and designed to run at 125 MHz. Torrent integrates a 32b integer scalar unit, two fixed point vector execution pipelines, a vector memory pipeline, on-chip instruction and data caches, a 1 GB/s off-chip memory interface, and a network interface with hardware routing which supports up to 1 GB/s of data I/O. The Torrent chip is designed to form part of a large scale multiprocessor system and requires minimal support circuitry to implement a processor node. Torrent also includes a serial diagnostic network interface used for bootstrapping and debugging.

The Torrent processor for the CNS-1 is an *instance* of a more general design, described in the Torrent Architecture Manual [Asa93a]. Another instance of the same architecture is **T0**, to be fabricated before Torrent [Asa93b]. T0 is designed without a network interface and will use conventional SRAM storage on a compute accelerator board for a workstation.

## 2.1.2 Instruction Execution

Torrent initiates the execution of a 32b instruction every 8 ns (for a 125 MHz clock rate). Each instruction adheres to the MIPS-I ISA specification, with CNS-1 extensions added within the coprocessor framework. The instructions are dispatched to one of four execution pipelines: the scalar unit, vector memory pipelines (VM), or one of the two vector arithmetic pipelines (VP0 and VP1).

The Torrent ISA extensions define approximately 100 new instructions in five categories:

- Vector Control Register. Used for establishing configuration and monitoring vector unit operation.

- Vector Branch. Modifies CPU control flow based on vector comparison.

- Vector Load/Store and Move. Allow moving vectors of data between vector registers and memory or between sets of vector registers.

- Vector Integer Arithmetic. Include arithmetic, shift, logical and conditional operations on vector register contents.

• Vector Fixed-Point Arithmetic. Provide scaled and rounded fixed-point arithmetic operations on vector register contents.

Details of the instruction dispatch and execution are under development. The general model, however, is that Torrent is superpipelined in each of the execution units, with branch and load delay slots where appropriate. The vector units can begin a new instruction every 4 cycles, and when appropriately combined with scalar instructions, sustain the peak performance. Data accesses are non-blocking and can bypass the cache to allow high off-chip memory bandwidths to be maintained.

#### 2.1.3 Scalar Unit

The scalar unit provides general purpose computation and overall control of Torrent, as well as support for the vector unit. Based on the MIPS-I ISA, the scalar unit is binary compatible with computers using MIPS R2000 and R3000 processors. The interface to the vector unit is implemented as a MIPS-standard coprocessor CP2. To simplify synchronizing the scalar unit and vector memory pipelines, Torrent includes the SYNC instruction from the MIPS-II specification.

The scalar unit includes a fully bypassed register file with 31 32b general purpose registers plus r0, which is hardwired to the constant 0. In addition, three special purpose registers are included for MIPS compatibility: the program counter (pc) and two registers to hold the results of integer multiplies and divides, 10 and hi. These special registers are used or modified implicitly by certain instructions.

The CPU functional units include a 32b adder, a 32b logical unit, a 32b shifter, a 32b×32b multiplier-divider, a zero comparator, the program counter datapath and an address adder. Also included in the scalar unit is the standard system control coprocessor CP0 used for memory management and exception handling.

#### 2.1.4 Vector Unit

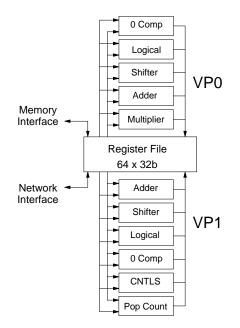

The vector unit consists of eight identical datapaths with two execution pipelines in each datapath. (Figure 2) The execution pipelines, VP0 and VP1 are similar, and share access to a common register file. Each pipeline contains a 32b logical unit, a 32b adder, a 32b shifter, a zero comparator and a clip unit. Additionally, VP0 contains a 16b×16b multiplier, pipelined to produce one result per clock cycle. VP1 also includes a population count unit, and a CNTLS (count leading signs) unit.

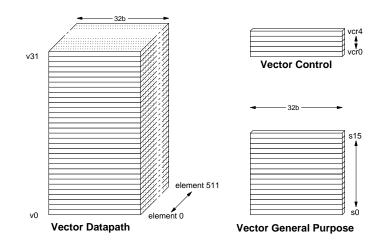

The vector register file in the vector unit, also split among the 8 datapaths, holds 16 or 32 vectors. (Figure 3) Each vector contains at least 32 elements, of 32b each, up to a maximum of 512 elements.<sup>\*</sup> Vector register v0 is defined to hold the constant zero. Note that a minimum register file design, with 16 vectors of 32 elements each, requires 2 KB of storage.

Twenty-one non-datapath registers have been defined in the vector unit, divided into two categories. Five registers are defined for specific control and status functions and are accessed with the CFC2 and CTC2 instructions. The remaining 16 registers in the vector unit are general purpose, and can be loaded and stored from either the CPU register file or directly from memory. These general purpose registers are used primarily for two classes of operations:

<sup>\*</sup>The final vector register file architecture will depend on algorithm requirements and silicon area constraints.

Figure 2: One Vector Datapath

Figure 3: Vector Unit Registers

- Vector datapath configuration. These allow control of the vector datapath's shift, clip and round functions for the most common multiply-add operations. By providing this level of hardware flexibility, the maximum precision in the integer vector units is obtained without sacrificing performance.

- Scalar operand registers. For vector-scalar operations, registers supply the scalar values.

#### 2.1.5 Vector Memory Pipeline

The vector memory pipeline can move vectors between registers and memory as well as perform moves from one vector register to another. Vector loads and stores transfer words, halfwords and bytes (32b, 16b and 8b) between vector register locations and memory. Bytes and halfwords are sign-extended when loaded into the vector elements. Memory address generation for vector loads and stores can use one of three techniques: unit-stride, arbitrary stride, and vector indexed.

The vector move instruction transfers elements between pairs of vector registers. One of the scalar registers in the vector unit provides the index into the source register, and the instruction provides the address of the destination vector register.

#### 2.1.6 Floating Point Arithmetic Support

Although floating point arithmetic on CNS-1 is implemented in software, the vector unit in Torrent contains a small amount of hardware to support floating point calculations. Each datapath contains a "count leading signs" (CNTLS) unit that takes two inputs, X and Y, and returns a count of the number of bits in X (scanning from most significant bit) equal to the sign of Y. This unit accelerates the normalization step required by floating point addition and multiplication routines.

The shifters in the vector datapaths are also customized for floating point support. Each of the shifters can use separate shift amount values, allowing the binary point alignment step of floating point normalization to occur in parallel. A more conventional design, with a single shift amount value, would not provide the parallel performance speedup.

These two modifications are inexpensive, requiring minimal design effort and increasing the size of the vector unit by about 5%. However, by including them in the design, floating point performance is significantly improved. Without this support the vector unit performs 32 floating point adds in 1680 clock cycles; with this support it performs 32 floating point adds in 264 clock cycles.

#### 2.1.7 Rambus Interface

Torrent applications operating on large data sets will require high off-chip memory bandwidth. To supply the bandwidth necessary to feed the vector unit, Torrent parallels 4 Rambus interfaces. The arrangement of the Rambus ports in Torrent is shown in Figure 4.

The Rambus protocol transfers data in blocks, with larger blocks giving greater effective bandwidth. To simplify the protocol, the Torrent Rambus interfaces (RBIs) only transfer naturally aligned blocks of 8B, 16B, or 32B of data. Using a 32B block size gives a data bandwidth on RDRAM cache read hits of over 250 MB/s, with a latency of approximately 110 ns.

The large number of RDRAMs in the CNS-1 system represents a considerable reliability concern. Each RDRAM includes a ninth data bit paralleling every byte, allowing us to implement error detection and correction (EDC). Single bit error correction and double bit error detection will be performed on the 8B blocks over a single port, and will be managed by the port RBI. Correctable errors will be fixed and written back to memory, on the assumption they are transient. Hard (uncorrectable) errors are considered catastrophic and cause Torrent to reset into bootstrap mode.

Figure 4: Torrent Chip Block Diagram

Each RBI has two sticky register bits per RDRAM bank to indicate if any correctable or non-correctable errors have been found in that bank. These sticky bits can be read over the serial interface port as well as by the processor in bootstrap mode, allowing Rambus and RDRAM faults to be located easily by diagnostic software.

An alternative design is also under investigation what would use synchronous DRAM rather than RDRAM. This is a more conventional approach allowing a simpler interface, running at more conservative data rates.<sup>\*</sup> To attain the performance goals, wider off-chip data busses are required.

#### 2.1.8 Instruction Cache (I-cache)

To support the large instruction bandwidth required, Torrent has an on-chip I-cache of 4 KB, or 1024 instructions. The I-cache supports one 32b instruction fetch per cycle (500 MB/s). The I-cache is direct mapped with 32 lines, each holding a 20b tag, a valid bit, and 32 instructions (128B).

On an I-cache miss, the instruction fetch phase of the CPU pipe is stalled while the I-cache is refilled. An instruction read request is sent to the Rambus controller, which, after allowing ongoing Rambus transactions to complete, eventually returns the 128B I-cache line. At best, an I-cache miss takes 20 cycles (160 ns) to service: 1 cycle to transmit the instruction read request, 14 cycles for the fastest Rambus read when the port is free, 4 cycles to return instruction responses from the Rambus controller, and 1 cycle to finish writing the last block to the I-cache. If the Rambus is busy when the I-cache miss occurs, the service time may increase by an additional 11 cycles.

<sup>\*</sup>Synchronous DRAM runs at 10 ns/B versus 2 ns/B for RDRAM.

#### 2.1.9 Data Cache (D-cache)

To help overcome the relatively long DRAM latency (14 clocks for a Rambus read), Torrent includes a fast data cache on chip. The D-cache supports up to one 256b data access per cycle (4 GB/s), while also effectively merging multiple scalar accesses into block accesses. To support applications with poor cache behavior, every Torrent memory operation has an "allocate" flag that indicates if the data should be allocated in the primary cache on a cache miss. This prevents data which is unlikely to be reused from polluting the cache.

Two features help Torrent sustain high memory bandwidth. The first is a decoupled memory system including a non-blocking D-cache. This allows the CPU to continue execution while data is fetched from off-chip memory, so multiple memory requests can be issued. The second is a set of vector load/store operations that transfer aligned 32B blocks of memory treated as 32×8b, 16×16b or 8×32b operands. Although the cache bus can transmit a complete 256b block every cycle, there is only a single memory port on each register file, limiting vector load/stores to transferring 8 operands per cycle. Further instructions can execute while a multicycle vector load/store operations takes place, provided they do not include another memory operation.

#### 2.1.10 Torrent Events

The on-chip network interface and timer use the Torrent asynchronous event model. Torrent is designed to handle these asynchronous events quickly, and typically only a few overhead cycles are required from the CPU to service an event. The overhead cycles are used to write a return instruction pointer to a fixed register in coprocessor CP0, and may also transfer further data into both the scalar and vector register files.

The three kinds of events on Torrent are message arrival (inlet), message departure (outlet), and timeout (timelet). The message arrival event is set *pending* when a new message arrives on the node, and becomes *active* when the inlet handler is started. The outlet handler is similarly invoked when a network output buffer becomes available. The hardware timer generates the timelet event when the counter reaches the value specified in the timeout register.

The active message model [vEC+92] allows event handlers to be executed within the current compute thread without requiring pipeline flushes. By keeping event handlers short and scheduling related computation for background (i.e. non-event) processing, the network can be serviced with acceptable latency without excessive context swapping. Event handlers will execute within reserved registers, allowing compute threads to run until they yield, minimizing register spills and cache misses. The Torrent system coprocessor CP0 also includes control bits to disable event handlers.

#### 2.1.11 Network Interface

The network interface supports a 2-dimensional mesh topology, with 4 bidirectional links to neighboring processors. Each link consists of 2 bytewide unidirectional connections, providing up to 125 MB/s in each direction for an aggregate node I/O bandwidth of 1 GB/s. Deadlock-free, cut-through routing is supported in hardware, with message buffering to allow high link utilization.

The processor-network interface is designed to be general, simple, and fast. Torrent sends and receives messages in registers, with a small amount of network buffering provided at each port. A send instruction specifies up to 5 32b scalar registers as well as a 32b instruction pointer, together with an optional data block obtained from a vector register. The message is then moved from the message buffers into the network under the control of the network router. Similarly, an arriving message is first moved from the network unit into datapath message buffers. The message can then be transferred directly from the buffers into the register file, stealing a few cycles from the CPU to complete the operation.

Active messages are supported in hardware, allowing fast, custom handlers to be directly invoked by arriving messages. If active messages are enabled, the processor will generate an event whose instruction pointer is the head of the message. By software convention, the message arrival frame pointer is generally the next word in the message.

#### 2.1.12 Timer

Torrent has an on-chip timer consisting of a 32b counter cycling at the processor clock frequency. A system timeout register together with a comparator allows a timeout event to be generated when the counter reaches the preset value. The timeout instruction pointer is specified in a system register and a software convention names a scalar unit register to hold the frame pointer. This hardware can be used to implement various timer facilities in software. Since the timers on all Torrents are reset and clocked synchronously, a valid global timestamp is maintained.

#### 2.1.13 Torrent Silicon Technology

Torrent and Hydrant are both full custom integrated circuits, fabricated through the MOSIS<sup>\*</sup> service. It is anticipated the CNS-1 chips will use the MOSIS 0.8µm scaled CMOS design rules, although the 0.5µm process will also be considered. The design uses a combination of full-custom cells for the datapaths and pads, and standard cells for control and other random logic. Supply voltage for the chips will be 3.3 volts, making them compatible with the RDRAM supply.

The silicon tool set used for the CNS-1 project includes a mixture of commercial and public domain software. We are using magic for layout editing, HSPICE and CAzM for circuit level simulation, irsim for switch level simulation, ViewLogic for schematic capture, and the Lager system for logic synthesis.