## Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# LOGIC SYNTHESIS AND MASSIVELY PARALLEL COMPUTERS: TOOLS FOR SPEEDING-UP LOGIC SIMULATION

by

Gary A. Jones

Memorandum No. UCB/ERL M93/16

16 February 1993

# LOGIC SYNTHESIS AND MASSIVELY PARALLEL COMPUTERS: TOOLS FOR SPEEDING-UP LOGIC SIMULATION

by

Gary A. Jones

Memorandum No. UCB/ERL M93/16

16 February 1993

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### Logic Synthesis and Massively Parallel Computers: Tools for Speeding-Up Logic Simulation

Gary A. Jones

University of California Berkeley, CA 94720 Department of Electrical Engineering and Computer Sciences

### **Abstract**

Simulation continues to be a major tool in the design of digital circuits. With increases in design sizes and the relative simulation times, the need for better simulation performance grows. Many studies have been performed on methods to improve simulation performance, covering both software techniques and hardware acceleration methods. This report combines both ideas. On the software side, the concept is presented for using logic synthesis techniques to produce better implementations of a circuit for functional simulation. From a hardware perspective, this concept is investigated using a simulator running on a massively parallel SIMD computer. Synthesis tools are used to modify the functional description of a circuit to increase the parallelism and shorten the expected simulation time while mapping the description for execution on the parallel architecture.

Professor A. Richard Newton Research Advisor

### Acknowledgements

I would like to thank my research advisor, Prof. A. Richard Newton, for his guidance and support during my years at Berkeley. This work would not have been possible without his inspiration and encouragement. I also thank Prof. Alberto Sangiovanni-Vincentelli for his constructive criticism and timely reading of this work. My research was sponsored in part by the Semiconductor Research Corporation under contract numbers 91-DC-008 and 92-DC-008, by the Microelectronics Innovation and Computer Research Opportunities (MICRO) program through the state of California under grant number 91101 and by the National Science Foundation under grant number EMC-8419744. I am grateful for their financial support. It has been a pleasure working with the excellent computer resources provided by the UC Berkeley EECS CAD Group and made possible by grants from Digital Equipment Corporation. I am also grateful to MasPar Computer Corporation for access to their MP-1 massively parallel computer and the excellent software tools available with it.

Special thanks to Chris Lennard, Bill Lin, and Mark Noworolski for their friendship both in and out of school, to Andie Mishoe for the long distance counseling sessions, and to Jenny Ho for some spice and some fun when I needed the sanity check. Kenneth and Lisa Lee Rust could always be counted on for a balanced perspective on life. I owe additional debts to my friends in Berkeley who made their own contributions, but may never read this report: Chris Lennard, Mark Noworolski, Bill Lin, Jenny Ho, Debra Weir, Henry Sheng, Henry Chang, Lisa Guerra, Kia Cooper, Christi Clark and Shane Ahn among many. They may not recognize their contributions, but they certainly made my life more enjoyable and complete.

I can never repay my family for their love and support over the years. Without their constant encouragement and support I would not have come to Berkeley, much less attained the degree. I can not conceive of anyone better to owe this debt. I thank my parents, Opal and Elizabeth Jones and my sisters Karen, Vicki and Patti, for emotional and financial support. I also thank Vicki for more direct help in reading, discussion and revision of this report. I thank each of them and the remainder of my family for everything I am today.

## **Contents**

| Ta              | ble of                                            | Contents                                                  | ii |  |  |  |  |  |  |  |  |  |  |  |

|-----------------|---------------------------------------------------|-----------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|--|--|

| List of Figures |                                                   |                                                           |    |  |  |  |  |  |  |  |  |  |  |  |

| Li              | st of 7                                           | Tables .                                                  | v  |  |  |  |  |  |  |  |  |  |  |  |

| 1               | Intr                                              | oduction                                                  | 1  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.1                                               | Synthesis for Simulation                                  | 2  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 1.2                                               | Report Organization                                       | 3  |  |  |  |  |  |  |  |  |  |  |  |

| 2               | Digi                                              | tal Simulation Background                                 | 5  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.1                                               | Levels of Digital Simulators                              | 5  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.1 Circuit-Level Simulation                            | 6  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.2 Switch-Level Simulation                             | 6  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.3 Gate-Level Simulation                               | 7  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.4 Functional Simulation                               | 7  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.5 Behavioral-Level Simulation                         | 7  |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 2.1.6 Mixed-Level and Mixed-Mode Simulation               | 8  |  |  |  |  |  |  |  |  |  |  |  |

|                 | 2.2                                               | Discrete-Event Simulation Terminology and Classifications | 8  |  |  |  |  |  |  |  |  |  |  |  |

| 3               | Para                                              | allel Simulation                                          | 11 |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.1                                               | Circuit Parallelism Studies                               |    |  |  |  |  |  |  |  |  |  |  |  |

|                 | 3.2                                               | Parallel SIMD Simulators                                  | 12 |  |  |  |  |  |  |  |  |  |  |  |

| 4               | The                                               | Massively-Parallel SIMD Machine Model                     | 14 |  |  |  |  |  |  |  |  |  |  |  |

|                 | 4.1                                               | The Hardware Model                                        | 14 |  |  |  |  |  |  |  |  |  |  |  |

|                 | 4.2                                               | The Instruction Set                                       | 14 |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 4.2.1 Functional Computation Instructions                 | 15 |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 4.2.2 Data Access and Transfer Capability                 | 15 |  |  |  |  |  |  |  |  |  |  |  |

|                 |                                                   | 4.2.3 Specialized SIMD Operations                         | 15 |  |  |  |  |  |  |  |  |  |  |  |

| 5               | Parallel Simulation Algorithm / Implementation 16 |                                                           |    |  |  |  |  |  |  |  |  |  |  |  |

|                 | 5.1                                               | Simulation Algorithm                                      | 17 |  |  |  |  |  |  |  |  |  |  |  |

|                 | 5.2                                               | Gate to Processor Manning                                 | 17 |  |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 5.3    | Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 18       |  |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|--|--|--|

| 6                                                                | Syn    | esis Tools for Improving Simulation Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20       |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 6.1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 6.2    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 6.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22       |  |  |  |  |  |  |  |  |  |  |

| 6.3.1 Conversion to Simulation Model: Mapping vs. Decomposition. |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22<br>25 |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        | The state of the s | 25<br>26 |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        | oss mining regordents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 20       |  |  |  |  |  |  |  |  |  |  |

| 7                                                                | Exp    | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 7.1    | Benchmark Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 29       |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 7.2    | <b></b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29       |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 30       |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 31       |  |  |  |  |  |  |  |  |  |  |

|                                                                  | 7.3    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32       |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 32       |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _        |  |  |  |  |  |  |  |  |  |  |

|                                                                  |        | 7.3.2 Synthesis Improvement to Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 33       |  |  |  |  |  |  |  |  |  |  |

| 8                                                                | Con    | usions and Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42       |  |  |  |  |  |  |  |  |  |  |

| Bi                                                               | bliogr | phy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 43       |  |  |  |  |  |  |  |  |  |  |

## **List of Figures**

| 1.1 | Conventional Approach to Discrete-Event Simulation                            | 3  |

|-----|-------------------------------------------------------------------------------|----|

| 1.2 | Synthesis Techniques Used for Discrete-Event Simulation                       | 4  |

| 2.1 | A Simple Network                                                              | 9  |

| 2.2 | Basic Discrete Event Simulation Algorithm                                     | 10 |

| 2.3 | Flow Chart of Basic Discrete Event Simulation                                 | 10 |

| 5.1 | Simple Compiled-Mode Simulation Algorithm for Massively-Parallel SIMD Machine | 18 |

| 5.2 | Implementation for Massively-Parallel Machine                                 | 19 |

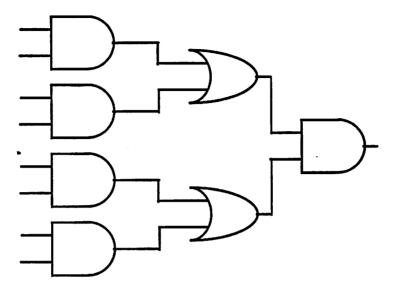

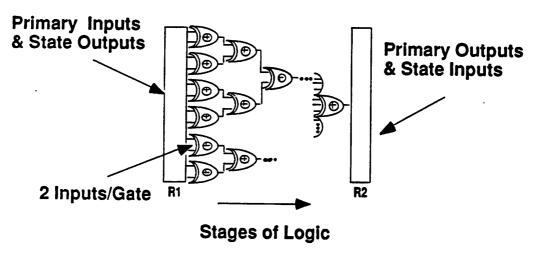

| 6.1 | 100,000-input Parity Network: Two Inputs per Gate                             | 21 |

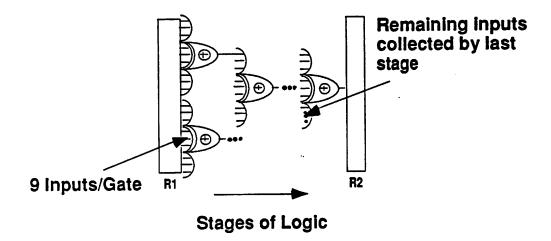

| 6.2 | 100,000-input Parity Network: Nine Inputs per Gate                            | 22 |

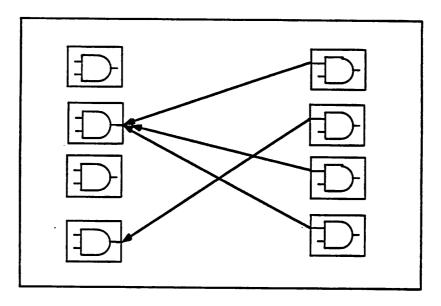

| 7.1 | Contention on a Single Input Fetch                                            | 30 |

| 7.2 | Contention Time Comparison                                                    | 31 |

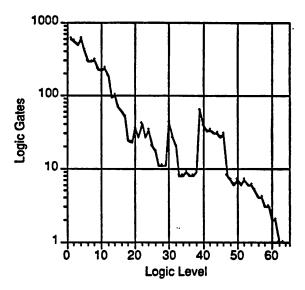

| 7.3 | TRISC Gates vs. Logic Level                                                   | 34 |

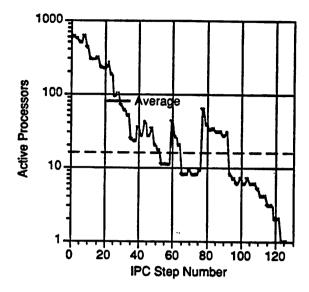

| 7.4 | TRISC Active Processors vs. IPC Step                                          | 35 |

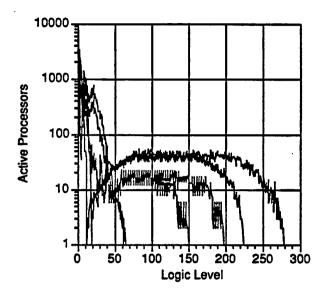

| 7.5 | Benchmark Processor Utilization                                               | 36 |

| 7.6 | Synthesis Optimization for MP Simulation                                      | 37 |

## **List of Tables**

| 6.1 | Comparison of Technology Mapping and Decomposition | 25 |

|-----|----------------------------------------------------|----|

| 7.1 | Performance Results for the MP Simulator           | 33 |

| 7.2 | Results for simplify                               | 38 |

| 7.3 | Results for full_simplify                          | 30 |

| 7.4 | Results for collapse                               | 20 |

| 7.5 | Results for speed_up.                              | 37 |

| 7.6 | Results for reduce_depth                           | 40 |

| 77  | Results for reduce_depth with simplification       | 40 |

| ,., | Acsults for reduce-depth with simplification       | 41 |

## Chapter 1

## Introduction

Computer-Aided Design (CAD) systems aid designers of integrated circuits through the verification of designs at all levels and the automatic synthesis of designs from a behavioral description to silicon. The primary goal of CAD systems is to produce near optimal implementations of a correct design as quickly as possible. Performance of a CAD system is crucial: the rapid growth of the integrated circuit market requires quick, correct designs in order to maintain competitiveness.

Integrated circuits are usually designed with the help of validation tools to guarantee correctness. After design, circuit descriptions are optimized using logic synthesis tools to minimize delay, minimize area, or some combination. The output of the synthesis is a netlist which is used to create the fabrication masks.

Simulation is the primary method for validation used in designing circuits. While other validation methods such as timing verification are useful tools in designing circuits, simulation is the most important method of assuring a design's correctness. Emerging techniques including formal verification and correct-by-construction techniques (silicon compilation) are reducing the need for extensive simulation. However, these techniques are only as valid as the input given. If the input to a formal verification tool or a correct-by-construction program has not been validated, the resulting design may not be what was intended. Formal specification can never fully replace simulation. Many times incorrect systems are specified and built because inadequate simulation was performed.

While simulation is necessary, it is also a hindrance. Simulation consumes much of the designer's effort and even more of the computational effort in designing a digital system. As systems become larger, the simulation costs can only grow. With larger systems, the number of interconnections between components greatly increases the amount of validation needed. Tomorrow's

simulators must be fast and must be able to handle the larger circuits being designed.

In general, circuit designs may be described at a variety of levels - functional, logic, etc. The description of a circuit's behavior is input to the simulator along with a collection of test cases. Most simulations systems consist of two general steps - the mapping of the description (input/output specification of a circuit) to the data structures used by the simulation engine and the simulation itself (that is, executing the simulation with the specified input) run on the simulation engine. During the mapping phase the description is also often optimized to reduce the run time of the simulation. As noted earlier, simulator performance is extremely important since simulation is considered the bottleneck in most integrated circuit designs.

In this report the simulation system attempts to achieve faster simulation through the use of synthesis tools to do the mapping of functional descriptions to the simulation format and a massively-parallel machine as the simulation engine.

### 1.1 Synthesis for Simulation

Conventional discrete-event simulation techniques include gate-level, RTL, behavior, and system-level. Current simulation tools are becoming obsolete as electronic systems rapidly become more complex. Even so-called behavioral simulation, if it is to maintain the precision required by many designs, does not provide sufficient speed-up over logic simulation to do the job.

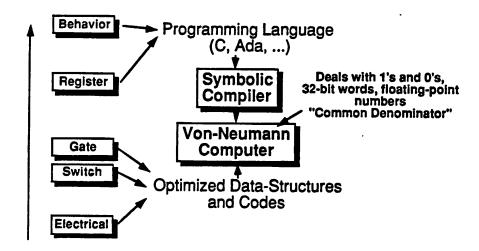

In these conventional systems all design descriptions are ultimately evaluated at the gate-level, so the potential for speed-up is restricted. Since conventional mainframes and workstations are Von Neumann machines and implement only binary data types directly in the hardware, the final binary file produced by the compiler is really a logic-level description. The datapath of the simulation engine (workstation, mainframe) performs simple operations (and, or, etc.) and some special support is provided for the number datatype via the floating point hardware. In reality, the C-compiler (FORTRAN or ADA, in some cases) of the workstation is "synthesizing" a logic-level description of the system behavior which is intended to have the same functional characteristics as a real implementation. This description is intended to simulate quickly on a Von Neumann computer.

This gate-level evaluation is illustrated in Figure 1.1, where the levels of design abstraction are shown on the left. The Von Neumann computer is shown as a gate-level implementation since the dominant abstract data type it directly implements is the binary "bit" on wires in the main processor.

The key idea of using synthesis for simulation is to replace the general-purpose symbolic

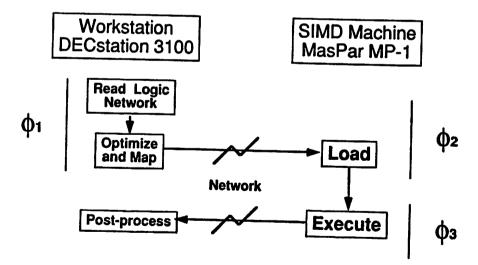

Figure 1.1: Conventional Approach to Discrete-Event Simulation

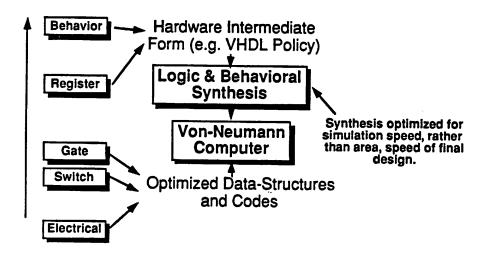

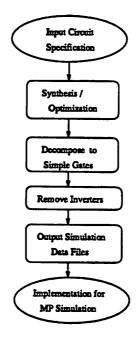

C-compiler (which maps a behavioral description to the format of the simulation engine) with effective synthesis tools which understand the special properties of the behavioral descriptions of digital electronic systems. These tools can manipulate the description from a mathematical and global point of view, while maintaining its external behavior, so that it simulates quickly. In addition to using synthesis to minimize the final area or delay time of the hardware implementation of the design, synthesis tools can be used early in the design cycle to improve the simulation speed (Figure 1.2).

Once synthesis tools are used to compile for simulation, they can also be used to retarget descriptions to other hardware platforms for improved simulation, such as massively-parallel single-instruction multiple-data (SIMD) machines, or even FPGA-based emulation engines, giving designers a wide range of price/performance options. This project targets the massively-parallel SIMD computer as the simulation engine. The two primary goals of the project were to evaluate the usefulness of synthesis tools to map behavioral descriptions to a simulation engine format and to evaluate the performance improvements of the simulation engine using SIMD architectures.

### 1.2 Report Organization

An introduction to digital simulation, including terminology and general types of simulators is presented in Chapter 2. Discrete event simulation algorithms and implementation techniques

Figure 1.2: Synthesis Techniques Used for Discrete-Event Simulation

are described and some example simulators are reviewed. In Chapter 3 the potential parallelism in circuits and some previous work in parallel digital simulation is summarized. Previous work in the application of simulation techniques to various target hardware platforms is presented. A machine model for the massively-parallel SIMD computer in Chapter 4, which is the basis for the study of techniques in the remainder of this report.

A general simulation algorithm and implementation is presented in Chapter 5, which serves as the basis for investigating the use of synthesis tools and techniques as a preprocessor for parallel simulation. The synthesis tools and framework, experimental results, and conclusions are presented in Chapter 6, 7 and 8, respectively.

### Chapter 2

## **Digital Simulation Background**

Before presenting the simulation approach chosen for implementation, an understanding of the basic model of discrete-event simulation and its terminology is necessary. An overview of digital simulation and some necessary background is presented in this chapter. In the first section, the different levels of circuit simulators are defined. The discrete-event model and simulation classifications are defined in the final section.

### 2.1 Levels of Digital Simulators

There are many levels for modeling the behavior of a digital circuit. At the physical level, the silicon, metal, etc. may be treated as simple devices such as transistors with timing behavior derived from the physical components. Transistors may be modeled as simple on-off (digital) switches with special timing parameters to approximate the behavior of the physical elements of the transistors. Above this switch model, the transistors may be grouped into functional blocks implementing Boolean logic functions. These logic blocks, or gates, retain the functionality but are a less accurate model of the underlying physical elements. In the same way, gates can be grouped into behavioral or functional blocks. These blocks model the functions, but not the individual behavior of the underlying transistors. In each case the physical design is modeled at a more abstract and less physically accurate behavioral level. These models are often used to specify a design at a high level of abstraction. The design is then refined to successively lower abstractions, eventually leading to a physical design specification. Simulation tools are available to verify designs at every level of abstraction. These design levels translate to five types of digital simulation: circuit-level, switch-level, gate-level, functional-level and behavioral-level simulation. Techniques for simulation and

example simulators of each type are presented in the following sections.

#### 2.1.1 Circuit-Level Simulation

Circuit-level simulation is the most accurate simulation of a circuit's behavior. The circuit is modeled as transistors, resistors and wires. The behavior of these elements is determined by their physical geometry and the technology in which the circuit is built. From this basis, a set of mathematical equations can be derived to represent this behavior. The state of any node in the circuit can be found by solving these equations. Detailed behavior provided by this level of simulation is essential to verify critical parts of a design. The computational expense of this detailed solution is too high for general simulation of large designs. Circuit-level simulators such as SPICE [Nag75] and CAzM [Erd89] are feasible for simulating up to 10,000 transistor networks. Today designs easily eclipse this size limit. To handle larger designs, simulation accuracy is traded against computational complexity. Investigation in reducing the computational complexity at the circuit level has concentrated on relaxation techniques [NSV83]. A simple model of the circuit elements may be chosen for simulation giving less accurate behavior modeling at a greatly reduced computational cost.

### 2.1.2 Switch-Level Simulation

In digital circuit design a transistor can be modeled as a simple switch with an acceptable loss of accuracy. For better analysis of critical portions of the circuit, circuit-level simulation may still be used for small pieces of the design. Switch-level simulators model the entire circuit as a collection of transistors and wires. The wires are generally modeled as idealized, zero-delay conductors. The transistors are modeled as switches with a simple delay model such as unit-delay in switching. More complex delay information may often be included if it is available. Some example switch-level simulators are *ESIM* [Ter83], *MOSSIM* [Bry84], and *COSMOS* [Bry87]. The circuit simulation involves solving simplified equations based on approximate circuit theory. Many switch-level simulators incorporate more accurate timing at the cost of additional computation time. Some also allow the user to specify increased levels of precision in modeling the element behavior. In spite of the loss of accuracy from circuit-level simulation, the timing information at the switch level may be sufficient to detect timing problems such as hazards, glitches and race conditions.

### 2.1.3 Gate-Level Simulation

Gate-level simulators model circuit elements at the gate rather than transistor level. The representation of a group of transistors as a simple Boolean logic gate greatly reduces the number of models to be evaluated and thus the total computation time for the simulation. Rather than equations for the voltage and current levels at nodes in the circuit, a set of Boolean logic equations represent the circuit behavior. The total simulation is more efficient due to the reduced number of equations and the simplicity of the basic logic computations. The circuit is represented as a collection of logic gates and the connecting wires. Gate-level simulators frequently support only a small set of functions: and, nand, or, nor and dff. A delay value is assigned to each gate, reducing the timing information as compared to switch-level simulation. Some simulators assign fixed or unit delays to each gate while others incorporate additional information about capacitance or fanout into the delay models. HILO [Gen85] and THOR [SB87] provide gate-level modeling for simulation.

#### 2.1.4 Functional Simulation

Functional-level, or register-transfer-level, simulation is abstracted another step from the gate level. The logic gates are grouped into functional blocks of combinational and sequential components. The connections between these components are no longer restricted to wires. Related wires or bits may be grouped into ordered sets of words or buses. The simulation consists of a set of statements describing transfers of data between functional blocks and arithmetic operations on this data. The higher level of abstraction in functional-level simulation allows functional verification of a large design in a reasonable amount of computation time. This functional testing does not include the ability to catch subtle errors such as races, hazards and critical timing constraints. These timing errors can only be detected at the lower levels presented above.

### 2.1.5 Behavioral-Level Simulation

Behavioral-level simulation is very similar to functional-level simulation. Both represent the circuit design by a set of blocks with functions specified directly by the designer. The main difference is the blocks correspond directly to hardware blocks in functional-level simulation. While behavioral-level descriptions duplicate behavior, but not necessarily the structure of the implementation. The behavioral-level units are generally described using a hardware description language such as VHDL. Similar to software programming languages these descriptions can be compiled and executed to emulate the operation of the design specification. Like functional-level

simulation, behavioral-level simulation is very efficient for verifying the high-level operation of the design, but does not include the information to detect low-level timing or design errors.

### 2.1.6 Mixed-Level and Mixed-Mode Simulation

Mixed-level simulation combines two different levels of simulation, such as switch and functional, in a single simulator. These are combined to allow different portions of a design to be tested at different levels. Critical pieces of the design can be simulated for detailed timing behavior at the switch-level, while less critical pieces only have their high-level behavior verified. Computation and precision tradeoffs are made in a single simulation run. LDVSIM [Bri89] and Lsim2 [CE75] are examples of mixed-level simulators.

Where mixed-level simulation blends two different levels of abstraction for a single simulation, mixed-mode simulation mixes computational techniques, such as direct and relaxation methods, in a single simulation. Mixed-mode simulators such as *SPLICE* [New79] and *SAMSON* [SD80] improve simulation performance by their dynamic choice of algorithm.

### 2.2 Discrete-Event Simulation Terminology and Classifications

Figure 2.1 represents a simple circuit comprised of three gates. A change in one of the inputs may cause a change in one of the internal nodes which, in turn, may cause a change at the output. Simulation's role is to determine the effects of changes at the inputs and involves not only determining the values of the internal nodes, but also the time at which changes occur at the nodes.

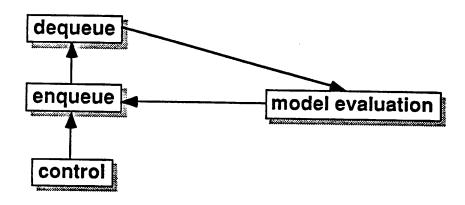

The basic model of discrete-event simulation has a *clock* representing the current time in the system and an *event queue* consisting of events that will happen in the future relative to the clock. When a node changes state because of a change in the output of a simulated gate, the node change cannot be directly applied to the node until the appropriate time. A simulation *event* consists of a new value for a node and the time at which the change will occur. For example, assume an event has been placed on the event queue for the circuit input in Figure 2.1. When the clock reaches the time specified in the event, the event is dequeued and the new gate output value is calculated using the new input value. The new output value with the appropriate time is now an event for each of the gate fanout nodes. Each of these gates must be evaluated, potentially generating more events. The simulation continues until the event queue is empty or some maximum time value is reached. This basic discrete-event simulation algorithm is given in Figure 2.2 and depicted in Figure 2.3.

Figure 2.1: A Simple Network

The designers of HSS [B<sup>+</sup>87] defined several classifications for simulators which are of interest for discrete-event simulation. A simulation algorithm can be event-driven or oblivious. In oblivious simulation every gate is evaluated at every time step. In event-driven simulation only those gates whose input has changed are evaluated. Additionally, a simulation implementation can be compiled or interpretive. In interpretive simulation a data structure representing the circuit network is constructed. A central scheduler iterates over the simulation time, calling procedures to evaluate the network. In compiled simulation a customized program is produced which simulates the network. The simulation iterations of the interpretive scheduler are effectively unrolled to produce a straight line program with direct data addressing. This reduces the overhead of the simulation in traversing the network data structure. HSS4 [B<sup>+</sup>87] is an example of a compiled event-driven logic simulator and SSIM [WHPZ87] is an example of an interpretive oblivious simulation.

```

while ( events remain ) {

take earliest event;

update time;

modify node;

evaluate affected gates;

enqueue any events determinde by evaluation;

}

```

Figure 2.2: Basic Discrete Event Simulation Algorithm

Figure 2.3: Flow Chart of Basic Discrete Event Simulation

### Chapter 3

## **Parallel Simulation**

Previous studies have tried to measure the potential of using parallel approaches for digital simulation. These studies, investigating circuit characteristics for parallel simulation, are reviewed in the next section. Previous work on simulators for massively parallel single-instruction multiple-data (SIMD) machines is reviewed in the final section.

### 3.1 Circuit Parallelism Studies

Many studies have investigated the feasibility of massively parallel simulation, which depends on the existence of large amounts of parallelism in the simulation model. In a study of potential parallelism in logic simulation [Fra86] gave very promising theoretical estimates. Similar studies ([BS88], [SB88] and [Won86]) have indicated small degrees of parallelism and forecast accordingly small speedups from parallel simulation.

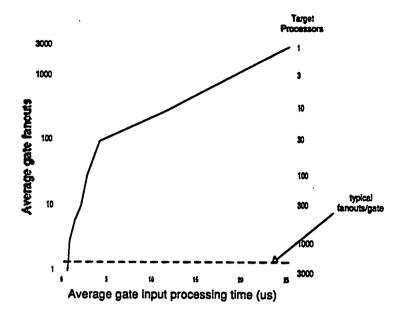

Frank [Fra86] determined the theoretical speedup of simulating digital designs of up to 20,000 transistors. The author proposed a theoretical architecture consisting of unlimited numbers of processors connected with a network for instantaneous interprocessor communication. The instruction of the processors is optimized for switch-level simulation. The multiprocessor organization for switch-level simulation consists of a single simulation instruction per processor allowing unlimited operands per instruction, eg. unlimited inputs and outputs for nodes in the circuit. This proposed multiprocessor architecture was simulated on a uniprocessor machine. The resulting theoretical speedups were as high as 200 times over a simulation for a single processor. A more realistic simulation of the architecture using 64 processors obtained speedups of 28 times with no communication costs considered and 12 times with communication costs included. Frank concluded

that there is parallelism to exploit in switch-level simulation. He also concluded that the parallelism does not generally increase with the circuit size and average parallelism will be relatively limited even for large circuits.

A number of statistics on logic simulation were collected by Wong, et al [Won86] to identify the potential for increased simulation performance. The statistics collected include the number of events associated with each simulation component, the number of events in the event queue, times between events in the queue and queue activity. The main statistic of concern for predicting parallelism is the number of simultaneous events for queue activity. From their simulation of example circuits of less than 8,000 transistors the authors concluded that relatively few events occur in parallel. Further, they concluded that the amount of parallelism scales with the size of the circuit, thus offering opportunities for exploiting parallelism in larger circuits.

Soule and Blank collected statistics similar to Wong, et al's in [SB88]. These statistics were collected on circuit designs specified at four description levels from gate to behavioral level. The circuits were simulated and analyzed for exploitable parallelism. The maximum speedup was measured using an "ideal" parallel environment model with no cost for processor memory contention and synchronization. Analyzing the simulation for up to 1,000 parallel processors they found a maximum speedup of 100 times for most circuits. For most circuits the maximum predicted speedup is only 5 times, with little correlation between speedup and design size.

A study by Bailey and Snyder [BS88] was expressly targeted to measure parallelism in CMOS circuit designs. They also used the event queue activity to measure the parallelism in the designs being simulated. Simulating a small number of circuits of up to 27,000 transistors, they obtained a maximum speedup of 25 times. The percentage of parallel activity in the circuits ranged from 0.04% to only 2.9% of the total design size. For their benchmark circuits, the amount of parallelism often decreased with increased circuit size.

### 3.2 Parallel SIMD Simulators

A parallel simulator implementation should give a more accurate performance measure for exploiting parallelism than a static analysis of serial simulation runs. Following the direction of this research report, a number of simulators implemented on massively parallel SIMD machines are presented below.

A relaxation-based circuit-level simulator was implemented by Webber, et al, [WSV87]. This simulator produced good results but used parallelization of circuit analysis techniques which

do not readily extend to parallel logic simulation.

A data parallel version of the switch-level simulator COSMOS was implemented by Bryant for a massively parallel SIMD machine [Bry88]. The entire switch-level model is replicated onto each processing element with a separate input vector evaluated on each. Using a 32,768 processor machine the simulator runs up to 33,000 times faster than a sequential simulator on a uniprocessor workstation.

The COSMOS switch-level simulator was extended for general parallel simulation on a SIMD machine by Kravitz and Bryant [KBR89]. The COSMOS algorithm decomposes a transistor circuit into a series of Boolean equations. These equations form a set of data independent modules which can be partitioned onto the massively parallel machine for maximum parallelism. From their investigations, they concluded that sufficient parallelism is available for speedup through massively parallel evaluation of the Boolean modules. The parallel implementation of COSMOS took twice as long to simulate one benchmark circuit and half as long to benchmark the second circuit, as the same simulation on the regular COSMOS simulator. The authors concluded that the one limiting factor for massively-parallel simulation was the interprocessor communication times on the SIMD machine.