## Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# AUTOMATED DESIGN OF SIGNAL ACQUISITION MODULES

by

Monte Frank Mar

Memorandum No. UCB/ERL M93/21

3 March 1993

# AUTOMATED DESIGN OF SIGNAL ACQUISITION MODULES

by

Monte Frank Mar

Memorandum No. UCB/ERL M93/21

3 March 1993

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### **Abstract**

### Automated Design of Signal Acquisition Modules

by

#### Monte Frank Mar

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Science

University of California Berkeley

Professor Robert W. Brodersen, Chair

Signal acquisition modules implement the functions of capturing a signal and providing a digitized representation of the signal. They usually include an A/D converter and filters to prevent anti-aliasing after sampling. This dissertation discusses methods for automating the design process from a high-level specification to layout using oversampling A/D converters. Using common levels of abstraction, a design framework was established allowing centralization of design information and development of a unified design methodology for these systems. The method of hierarchical design estimation was developed to guide design development. At the lowest level, hierarchical design estimation relies on the use of architecture templates to capture design information for specific implementations of processors and to increase accuracy of design estimates. In the initial search of the design space, performance estimates are made and propagated in a top down fashion through the various levels of the hierarchy. At a high level, promising design candidates can be identified and pursued. Accurate simulation of the mixed signal system provides verification of the design. Models for 1/f noise were incorporated with existing difference equation methods to provide improved simulation capabilities for the analog oversampling modulators. These models were able to predict the performance of several fabricated modulator variations to within 3 dB of measured results. To verify the functionality of the system, several chip designs were implemented. The chips covered applications including data acquisition, linear phase filtering, and signal acquisition for speech recognition. Analysis using the design framework reduced design time significantly while still providing high performance, fully functional chips.

Chairman of the Committee

## Table of Contents

| CHA            | APTER 1 Introduction                                                                        |    |

|----------------|---------------------------------------------------------------------------------------------|----|

| 1.1            | Previous Approaches to Mixed Signal Design Systems                                          | 2  |

| 1.1.1          | Analog CAD Tools.                                                                           |    |

| 1.1.2          | Digital CAD tools                                                                           | 4  |

| 1.1.3          | System Design: Methodologies and Design Tools                                               | 4  |

| 1.2            | Design System Overview                                                                      | 5  |

| 1.2.1          | Levels of Abstraction                                                                       |    |

| 1.2.2          | Functional Compilers and Estimation                                                         |    |

| 1.3            | Summary                                                                                     | 10 |

| СНА            | APTER 2 Oversampling A/D Conversion                                                         |    |

| 2.1            | Introduction                                                                                | 11 |

| 2.2            | Modulators for Oversampling A/D Conversion                                                  | 11 |

| 2.2.1          | Quantization Noise and Oversampling                                                         |    |

| 2.2.2          | Noise Shaping and the $\Delta$ - $\Sigma$ Modulator Family                                  |    |

| 2.2.3          | Theoretical Analysis Methods for Modulators                                                 |    |

| 2.3            | Higher Order Noise Shaping Modulators                                                       |    |

| 2.3.1<br>2.3.2 | The Multistage Noise-Shaping Modulators                                                     |    |

| 2.3.2<br>2.3.3 | Modulators with Higher Order Loop Filters  Modulators with Multi-Bit A/D and D/A converters |    |

| 2.4            | A/D Converters and Filters                                                                  |    |

| 2.5            | Multirate Filter Design                                                                     | 22 |

| 2.5.1          | A Multirate Filtering Example Using FIR Filters                                             |    |

| 2.5.2          | Other Solutions to Multirate Filtering Problems                                             |    |

| 2.6            | Summary                                                                                     | 28 |

| СНА            | APTER 3 Framework Overview                                                                  |    |

| 3.1            | Hierarchical Design Estimation                                                              |    |

|                | Introduction                                                                                |    |

| 3.1.2          | Estimation Strategies                                                                       |    |

| 3.2            | Design System Overview                                                                      |    |

| 3.2.1          | Objectives for the Design System                                                            |    |

| 3.2.2<br>3.2.3 | CAD Framework  Status of the Design System                                                  |    |

| 3.2.3          | Spreadsheet-Based Design Tools                                                              |    |

|                | •                                                                                           |    |

| 3.4            | Framework for Detailed Design                                                               |    |

| 3.5            | The Detailed Design Database                                                                |    |

| 3.5.1<br>3.5.2 | The OCT Database                                                                            |    |

| 3.3.2          | UK. I COMPONENT VIEW POLICY                                                                 | 41 |

| iv  |

|-----|

| 3.6 |

| 3.6<br>3.6.1<br>3.6.2<br>3.6.3 | Adding Programs to the Design Framework  Consistency in Programming  Database Interfaces for Coefficient Design Programs  Database Interfaces for Coefficient Quantization Programs | 44<br>45<br>46 |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 3.6.4<br>3.7                   | Interfaces for Architecture Mapping Programs  Layout Generation                                                                                                                     |                |

| 3.8                            | Using the Design System                                                                                                                                                             | •              |

| 3.8.1                          | Basic Design Steps                                                                                                                                                                  |                |

| 3.8.2                          | Other Modes For Design System Use                                                                                                                                                   | 49             |

| 3.9                            | Summary                                                                                                                                                                             | 50             |

| CHA                            | PTER 4 Simulation Methods                                                                                                                                                           |                |

| 4.1                            | Simulation Methods                                                                                                                                                                  | 51             |

| 4.1.1                          | Circuit-Level Simulation                                                                                                                                                            |                |

| 4.1.2                          | Difference Equations and Behavioral Simulation                                                                                                                                      |                |

| 4.2                            | Developing Accurate High-Level Simulation Models                                                                                                                                    |                |

| 4.2.1<br>4.2.1.1               | Switched Capacitor Integrator Analysis                                                                                                                                              | 54<br>55       |

| 4.2.1.2                        | Modelling the effects of nonlinearities                                                                                                                                             |                |

| 4.2.1.3                        | Combining Finite Gain and Capacitor Nonlinearity                                                                                                                                    |                |

| 4.2.1.4                        | Parasitic Input Capacitance of the Opamp                                                                                                                                            |                |

| 4.2.1.5<br>4.2.1.6             | Integrator Settling Integrator Clipping                                                                                                                                             |                |

| 4.2.1.7                        | Sampling Jitter                                                                                                                                                                     |                |

| 4.2.1.8                        | Models for Switched-Capacitor $\Delta$ - $\Sigma$ Modulators                                                                                                                        | 60             |

| 4.2.2                          | Modelling Continuous Time Integrators for Oversampling A/D Converters                                                                                                               | 60             |

| 4.2.2.1<br>4.2.2.2             | Digital System Simulation of the Integrator                                                                                                                                         |                |

| 4.2.3                          | Modelling Noise Sources                                                                                                                                                             |                |

| 4.2.3.1                        | Generating White Noise                                                                                                                                                              | 61             |

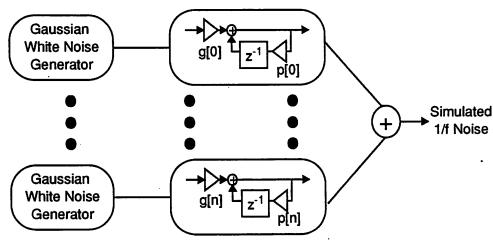

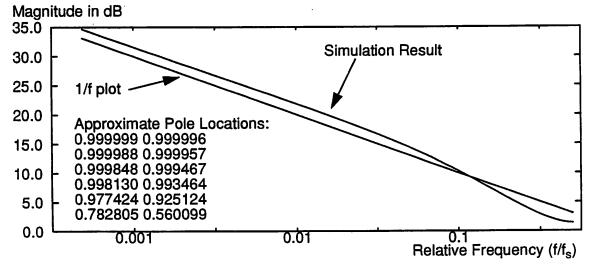

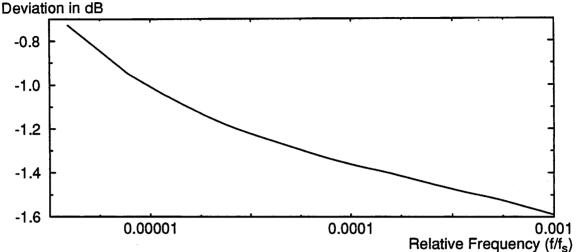

| 4.2.3.2                        | Generating 1/f Noise                                                                                                                                                                | 62             |

| 4.3                            | Simulation and Analysis of Digital Filters                                                                                                                                          | 66             |

| 4.3.1                          | PTOLEMY                                                                                                                                                                             |                |

| 4.3.2                          | Stars for Oversampling A/D Simulation                                                                                                                                               |                |

| 4.3.3<br>4.4                   | Simulation Example  System Simulation Strategy                                                                                                                                      |                |

|                                | •                                                                                                                                                                                   |                |

| 4.5                            | Summary                                                                                                                                                                             | 72             |

| CHA                            | PTER 5 Coefficient Design Techniques                                                                                                                                                |                |

| 5.1                            | Overview                                                                                                                                                                            | 73             |

| 5.2                            | Tools for Filter Design                                                                                                                                                             | 73             |

| 5.2.1                          | Coefficient Design                                                                                                                                                                  |                |

| 5.2.2                          | Classical Design Methods                                                                                                                                                            | 74             |

| 5.2.3<br>5.2.4                 | Remez's Second Algorithm  Least p-th Error Approximation                                                                                                                            |                |

| T                              |                                                                                                                                                                                     |                |

•

.

| 5.2.5          | Nonlinear Programming                                      | 77  |

|----------------|------------------------------------------------------------|-----|

| 5.3            | Coefficient Design                                         | 77  |

| 5.4            | Coefficient Design for Analog Modulators                   | 79  |

| 5.5            | Summary                                                    | 79  |

|                | •                                                          |     |

| CHAI           | PTER 6 Architecture Design                                 |     |

| 6.1            | Architecture Selection                                     | 81  |

| 6.1.1          | Bit-Serial Architectures                                   |     |

| 6.1.2          | High-performance Architectures                             |     |

| 6.2            | Time Multiplexed FIR filter family                         |     |

| 6.2.1          | Background                                                 |     |

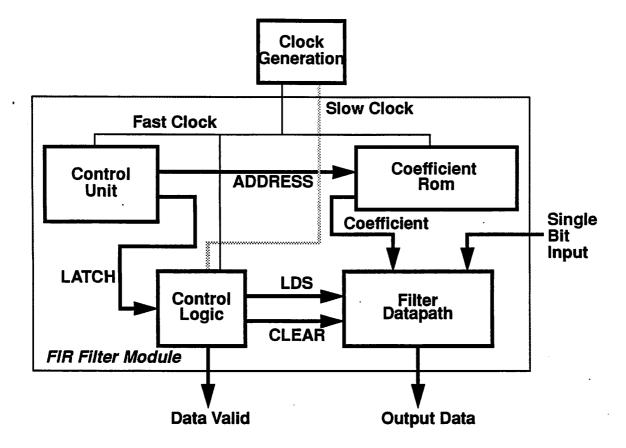

| 6.2.2<br>6.2.3 | Overview and Black-Box view  Details of the implementation |     |

| 6.2.4          | DECFIR                                                     |     |

| 6.3            | CIC Filter family.                                         |     |

| 6.3.1          | Background                                                 |     |

| 6.3.2          | Overview and Black Box View                                |     |

| 6.3.2.1        | Bit-Parallel Integrator version                            |     |

| 6.3.2.2        | Digit-Serial Integrator version                            |     |

| 6.3.3          | Details of the Implementation                              |     |

| 6.4            | Custom Decimate-by-2 FIR filter                            |     |

| 6.4.1          | Overview                                                   |     |

| 6.4.2<br>6.4.3 | Black-box view                                             |     |

|                | Implementation details                                     |     |

| 6.5            | C-to-silicon                                               |     |

| 6.5.1<br>6.5.2 | Overview  Black-box description.                           |     |

| 6.5.3          | Implementation details                                     |     |

| 6.6            | Parallel to Serial Converter                               |     |

| 6.6.1          | Description                                                |     |

| 6.6.2          | Details                                                    |     |

| 6.7            | Clock Generators                                           |     |

| 6.8            | Analog Modulator Architecture Selection                    | 111 |

| 6.8.1          | Overview                                                   | 111 |

| 6.8.2          | Black Box Description                                      | 111 |

| 6.9            | Estimation Techniques                                      | 112 |

| 6.9.1          | Area                                                       |     |

| 6.9.2          | Speed                                                      |     |

| 6.9.3          | Power                                                      |     |

| 6.10           | Adding New Architecture Templates                          |     |

| 6.10.1         | Different Techniques                                       |     |

| 6.10.2         | System Integration Issues                                  |     |

| 6.11           | Summary                                                    | 117 |

•

•

9.2

| **             |                                                           |     |

|----------------|-----------------------------------------------------------|-----|

| CHA            | PTER 7 Design and Implementation of the Analog Circuits   |     |

| 7.1            | Design of the Experimental Circuits                       | 119 |

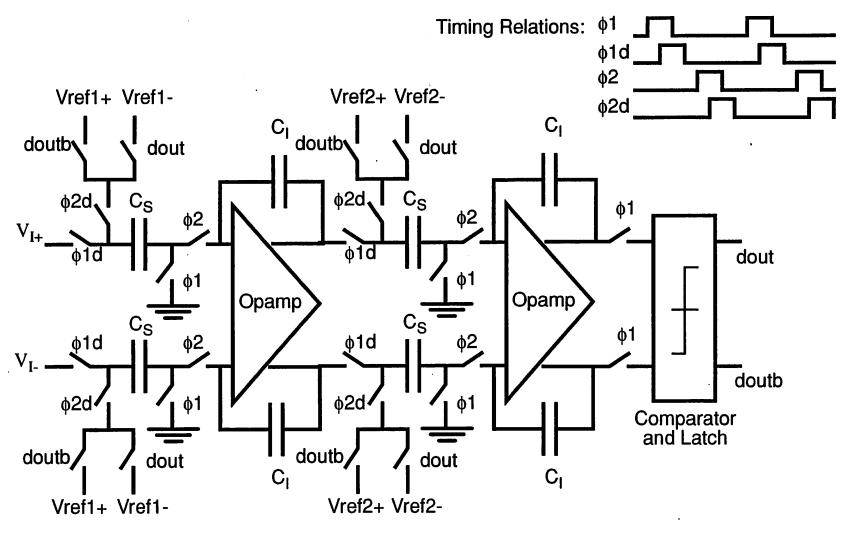

| 7.1.1          | Modulator Overview                                        |     |

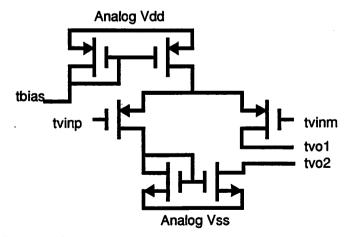

| 7.1.2          | Integrator Design                                         |     |

| 7.1.3<br>7.1.4 | Opamps                                                    |     |

| 7.1.4          | Comparators                                               |     |

| 7.2            | Results from the Test Circuits                            |     |

| 7.3            | Comparing Circuits and Simulation Results                 | 133 |

| 7.4            | Module Generators for Oversampling Modulators             | 137 |

| 7.4.1          | Developing a Module Generator                             | 137 |

| 7.4.2          | Module Generation and Topology Choice                     | 139 |

| 7.5            | Layout Techniques for Oversampling Modulators             |     |

| 7.6            | Summary                                                   | 144 |

|                | APTER 8 Design Examples                                   |     |

| 8.1            | Analysis Principles for Oversampling A/D Converter Design | 145 |

| 8.2            | Example 1: Data Acquisition                               | 146 |

| 8.2.1          | Application                                               |     |

| 8.2.2<br>8.2.3 | Requirements                                              |     |

| 8.2.4          | Implementation  Verification Strategy                     |     |

| 8.2.5          | Results                                                   |     |

| 8.3            | Example 2: Linear Phase A/D converter                     | 151 |

| 8.3.1          | Background                                                | 151 |

| 8.3.2          | Implementation                                            |     |

| 8.3.3<br>8.3.4 | Verification  Results                                     |     |

| 8.4            | Example 3: Speech Coder                                   |     |

| 8.4.1          | Requirements                                              |     |

| 8.4.2          | Design Study                                              |     |

| 8.4.3          | Verification                                              |     |

| 8.4.4          | Results                                                   |     |

| 8.5            | Other Examples                                            |     |

| 8.6            | Summary                                                   | 165 |

| CHA            | APTER 9 Conclusion                                        |     |

| 9.1            | Design System Features                                    | 167 |

| 9.1.1          | Partitioning of the Mixed Signal Design Process           |     |

| 9.1.2          | Improved Modulator Modelling                              |     |

| 9.1.3          | Centralized Design Templates                              | 169 |

Extensions for D/A Conversion......169

| C.6            | Final Design Steps                      | 234 |

|----------------|-----------------------------------------|-----|

| APPI           | ENDIX D Detailed Database Documentation |     |

| D.1            | Overview                                | 235 |

| D.2            | dblib Programming Library               | 235 |

| D.2.1          | Header File                             |     |

| D.2.2          | dblib Function Call Descriptions        |     |

| D.3            | Coefficient Storage                     |     |

| D.4            | MAPPING bag                             | 242 |

| APPI           | ENDIX E Architecture Library Summary    |     |

| E.1            | CIC Filters                             | 245 |

| E.2            | C-to-Silicon                            | 246 |

| E.3            | Clock Generators                        | 246 |

| E.4            | Decimate-by-2 FIR Filter                | 246 |

| E.5            | FIR Filter Family, Time Multiplexed     | 247 |

| E.6            | Parallel to Serial Converter            |     |

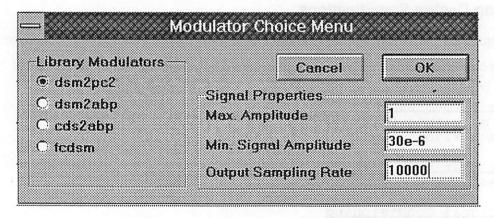

| E.7            | Second Order Modulators                 | 248 |

| E.7.1          | Modulator 1: dsm2pc2                    | 248 |

| E.7.2<br>E.7.3 | Modulator 2: dsm2abp                    |     |

| E.7.3<br>E.7.4 | Modulator 3: dsm2abn                    |     |

| E.7.5          | Modulator 5: dsm2fc2p                   |     |

| APP            | ENDIX F Mixed Signal VLSI Design        |     |

| F.1            | Overview                                | 251 |

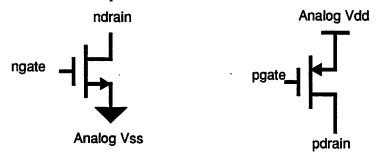

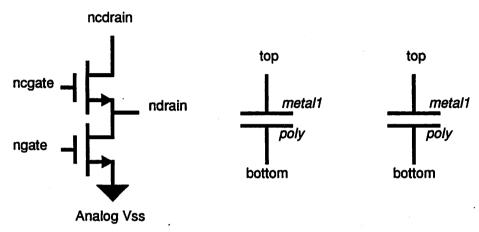

| F.2            | Cell Design                             | 251 |

| F.3            | Global Place and Route                  | 252 |

| F.4            | Pad Ring Design                         | 253 |

| F.5            | Board Level                             | 253 |

| APP            | ENDIX G Modulator Test Setup            |     |

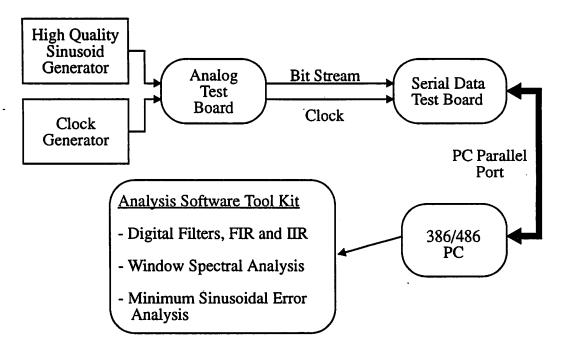

| G.1            | Testing Oversampling A/D converters     | 255 |

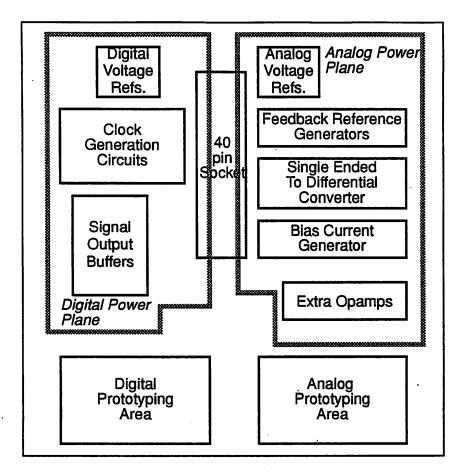

| G.2            | Chip Testing Board                      | 255 |

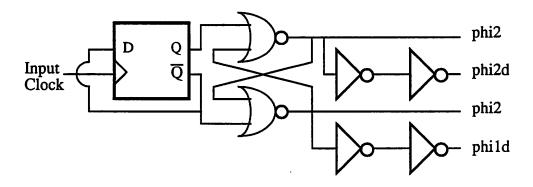

| G.2.1          | Digital Clock Generation Circuitry.     |     |

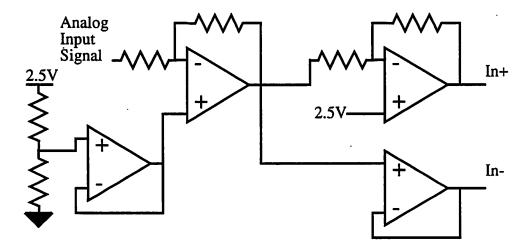

| G.2.2<br>G.2.3 | Single-Ended to Differential Converter  |     |

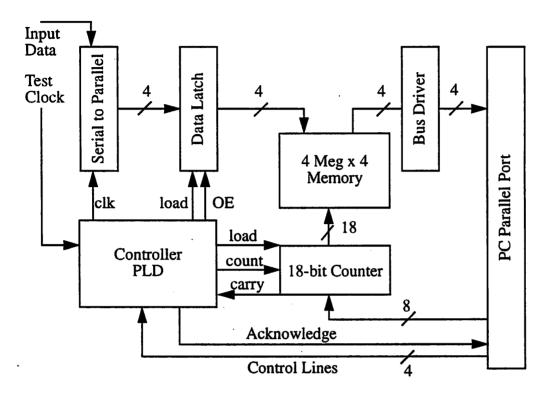

| G.3            | Serial Data Acquisition Board           |     |

| G.3.1 Overview of the Serial Data Acquisition Board |       | ti                                               |

|-----------------------------------------------------|-------|--------------------------------------------------|

| G.3.2 Communication Protocols                       | G.3.1 | Overview of the Serial Data Acquisition Board260 |

| APPENDIX H Chip Descriptions                        | G.3.2 | Communication Protocols260                       |

| • •                                                 | G.3.3 | Parallel to Serial Converters26                  |

| H.1 Overview                                        | APPE  | ENDIX H Chip Descriptions                        |

|                                                     | H.1   | Overview263                                      |

|                                                     |       |                                                  |

|                                                     |       | ·                                                |

| ullet                                               | •     |                                                  |

## List of Figures

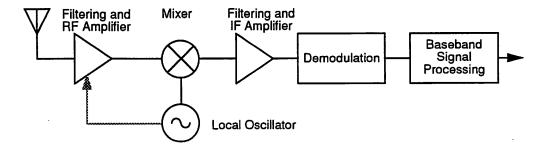

| Figure | 1.1:  | Block diagram of a superheterodyne receiver                                                                          | 5  |

|--------|-------|----------------------------------------------------------------------------------------------------------------------|----|

| Figure | 1.2:  | Block diagram for a typical signal acquisition module.                                                               | 6  |

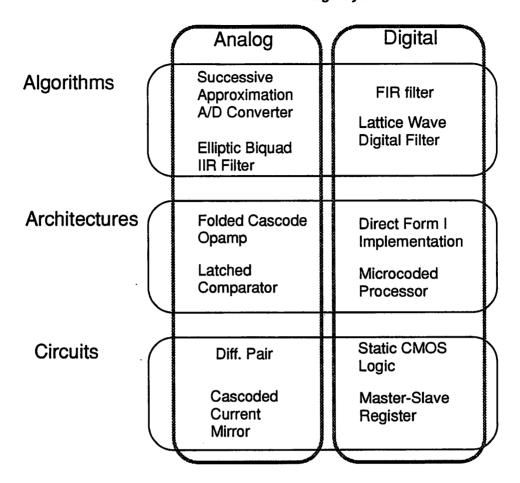

| Figure | 1.3:  | Levels of abstraction for design.                                                                                    | 7  |

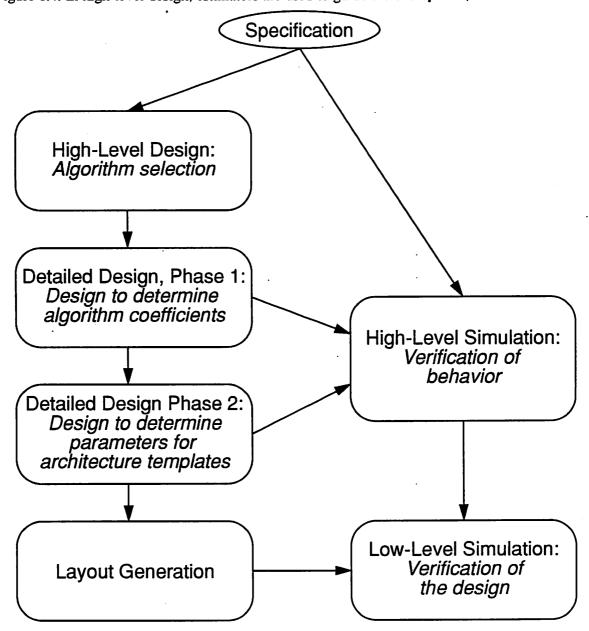

| Figure | 1.4:  | Flow for the design framework                                                                                        | 9  |

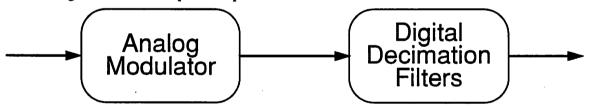

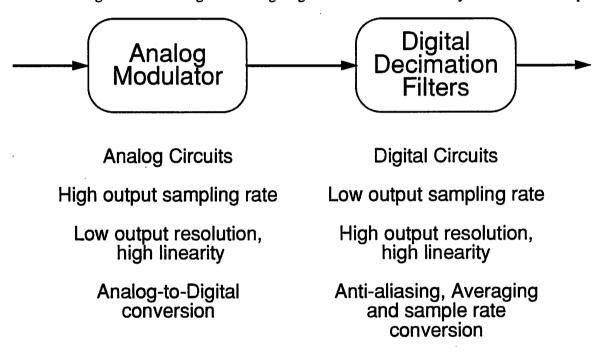

| Figure | 2.1:  | Block diagram and functions of an oversampling A/D Converter                                                         | 11 |

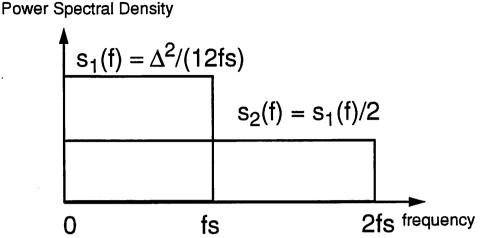

| Figure | 2.2:  | Power spectral density of the quantization noise for a signal sampled at fs and 2fs                                  | 13 |

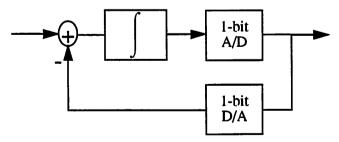

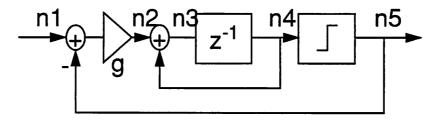

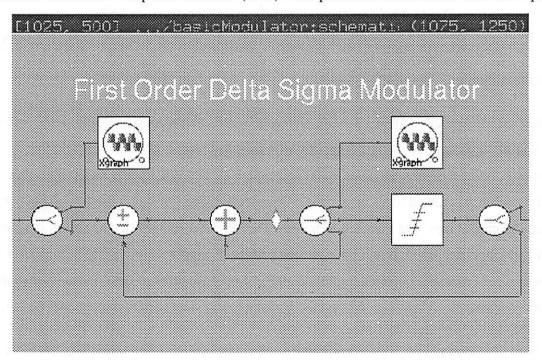

| Figure | 2.3:  | Block diagram of a first order $\Delta$ - $\Sigma$ modulator.                                                        | 13 |

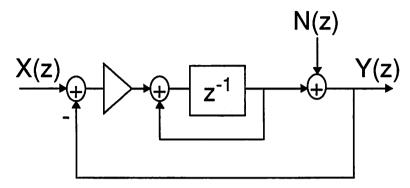

| Figure | 2.4:  | Linearized model of the first order $\Delta$ - $\Sigma$ modulator                                                    | 14 |

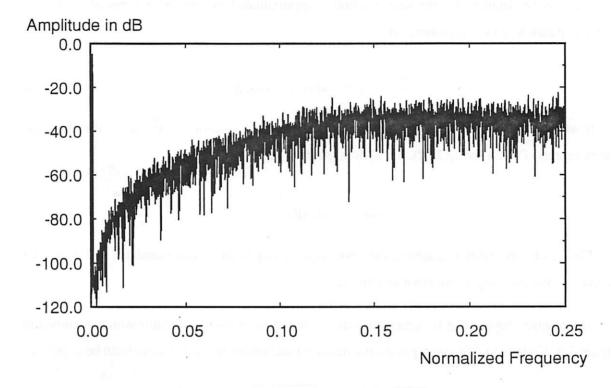

| Figure | 2.5:  | FFT output of a second-order $\Delta$ - $\Sigma$ modulator with a sinusoidal input                                   | 15 |

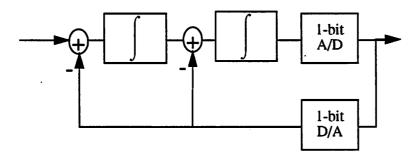

| Figure | 2.6:  | Block diagram of a second order $\Delta$ – $\Sigma$ modulator.                                                       | 16 |

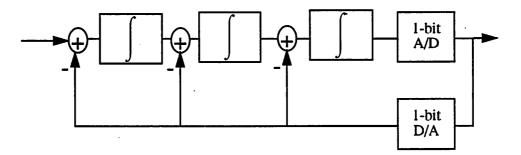

| Figure | 2.7:  | A third order $\Delta$ – $\Sigma$ modulator using triple integration                                                 | 17 |

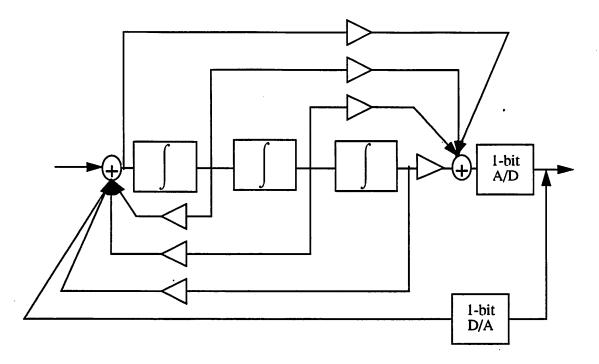

| Figure | 2.8:  | Block diagram of a modulator with a higher order loop filter.                                                        | 20 |

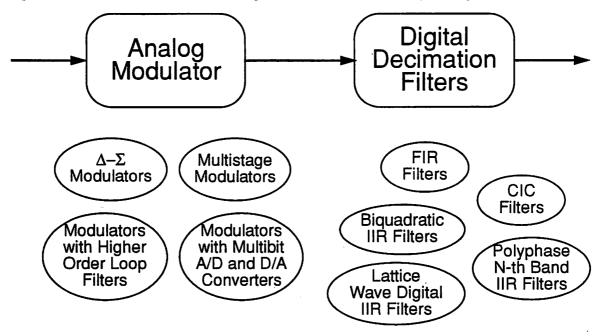

| Figure | 2.9:  | Summary of functions for the modulator and filters                                                                   |    |

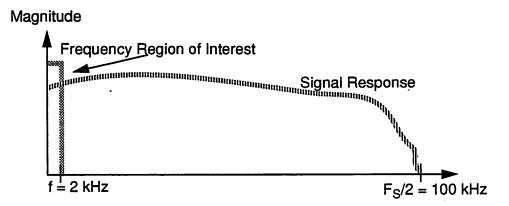

| Figure | 2.10: | Frequency specification for a narrow-band filter.                                                                    | 23 |

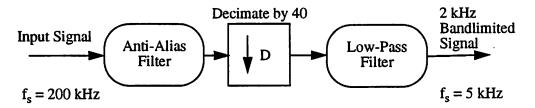

| Figure | 2.11: | Block diagram of a system to recover 200 Hz bandlimited data                                                         | 23 |

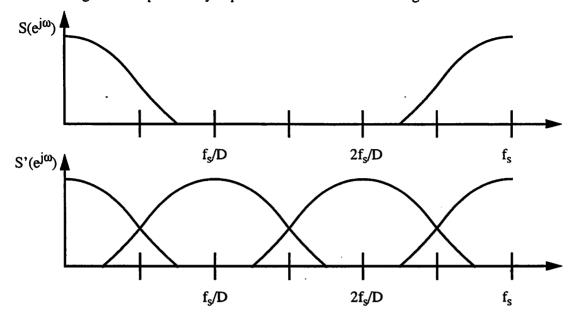

| Figure | 2.12: | Frequency domain interpretation of resampling a signal that isn't band-limited.                                      | 24 |

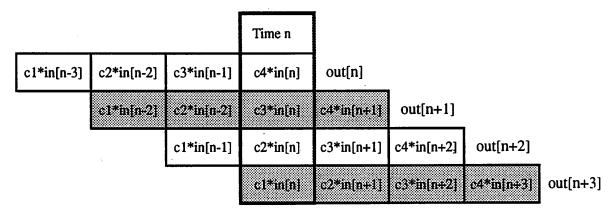

| Figure | 2.13: | Calculations in an FIR filter with L = 4.                                                                            | 25 |

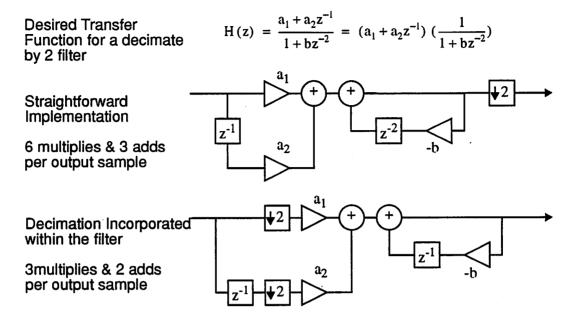

| Figure | 2.14: | Incorporating decimation in an IIR filter structure.                                                                 | 27 |

| Figure | 2.15: | Modules for implementing an oversampling A/D converter.                                                              | 29 |

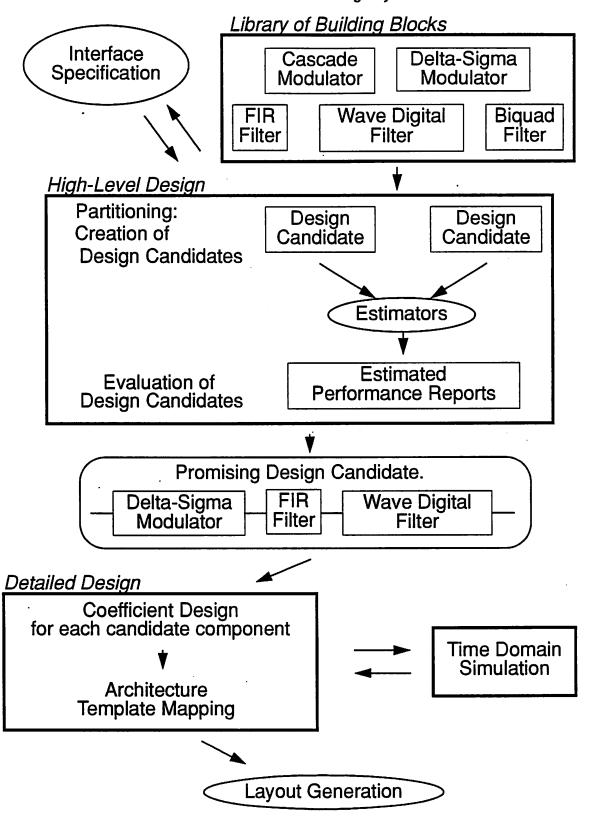

| Figure | 3.1:  | Basic design flow for the design system.                                                                             | 35 |

| Figure | 3.2:  | The custom add filter menu generated in Excel                                                                        | 37 |

| Figure | 3.3:  | Spreadsheet template for studying multirate digital filters.                                                         | 38 |

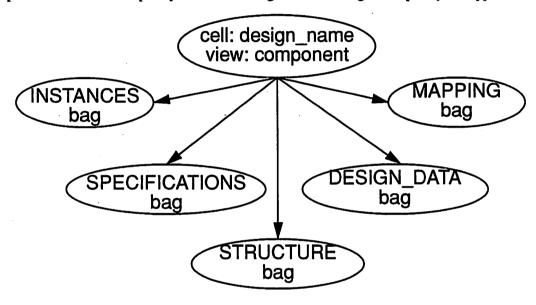

| Figure | 3.4:  | Top level of the policy for the component view.                                                                      | 40 |

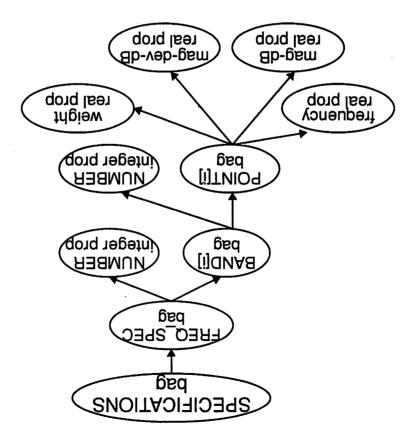

| Figure | 3.5:  | Policy for storing the specification for the frequency response of a component                                       | 41 |

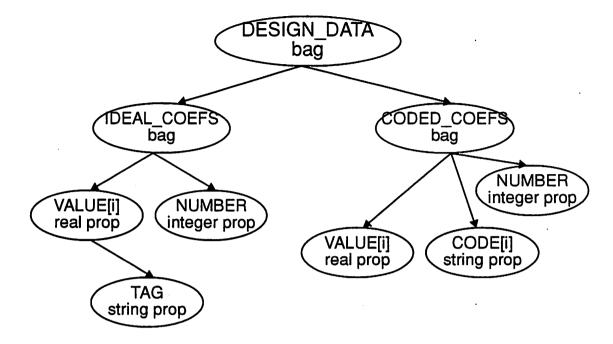

| Figure | 3.6:  | Policy for storage of coefficients in the DESIGN_DATA bag                                                            | 43 |

| Figure | 3.7:  | Modulator estimation tool and results implemented in Microsoft Excel                                                 | 49 |

| Figure | 4.1:  | Block diagram and C code fragment for modelling a first-order $\Delta$ – $\Sigma$ modulator                          | 53 |

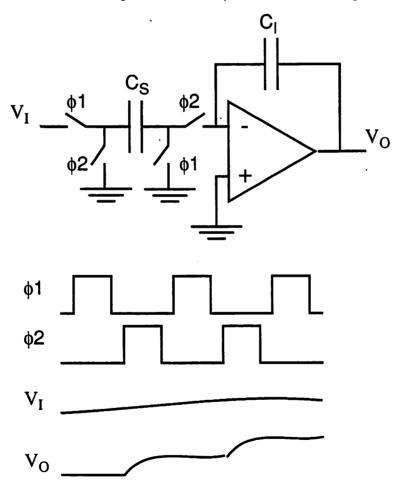

| Figure | 4.2:  | Switched capacitor integrator and waveforms                                                                          | 54 |

| Figure | 4.3:  | Regions of operation for integrator settling                                                                         | 59 |

| Figure | 4.4:  | Summation of approximate Lorentzian spectra to obtain a 1/f noise model.                                             | 64 |

| Figure | 4.5:  | Frequency response of a 1/f noise generator                                                                          | 64 |

| Figure | 4.6:  | Deviation between the true 1/f response and the simulation result                                                    | 65 |

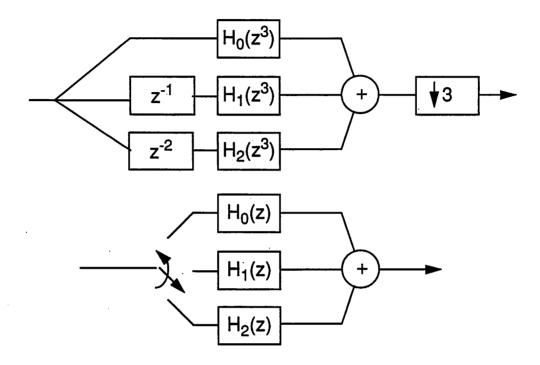

| Figure | 4.7:  | Block diagrams of a polyphase 3rd band filter using external decimation and the counter-clockwise commutation model. | 68 |

| Figure | 4.8:  | Flowgraph of a first order $\Delta$ – $\Sigma$ modulator implemented in PTOLEMY                                                      | 69    |

|--------|-------|--------------------------------------------------------------------------------------------------------------------------------------|-------|

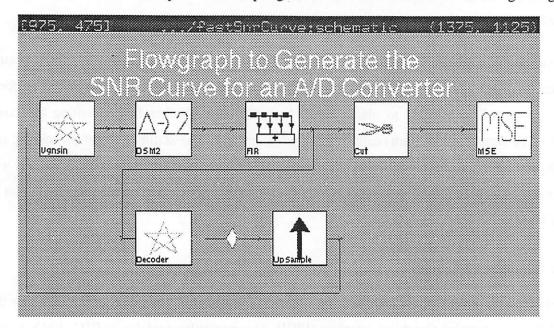

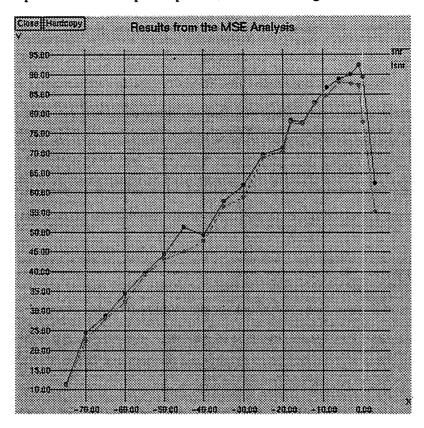

| Figure | 4.9:  | Complete simulation flowgraph for determining SNR.                                                                                   | 70    |

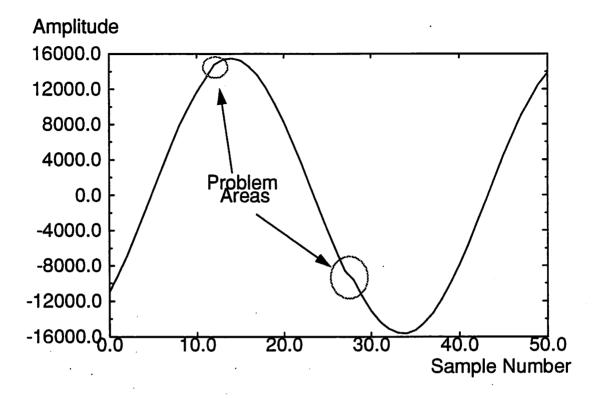

| Figure | 4.10: | Output from the flowgraph shown in Figure 4.9                                                                                        | 71    |

| Figure | 6.1:  | Block diagram of the FIR filter family.                                                                                              | 84    |

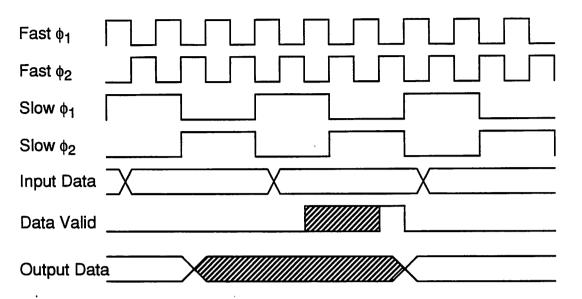

| Figure | 6.2:  | Timing relations for the FIR filter family for the case L/D=3                                                                        | 85    |

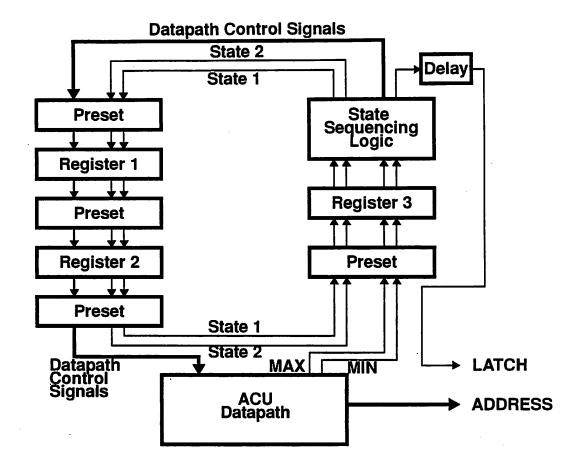

| Figure | 6.3:  | Block diagram of the controller for the case where $L/D = 3$                                                                         | 87    |

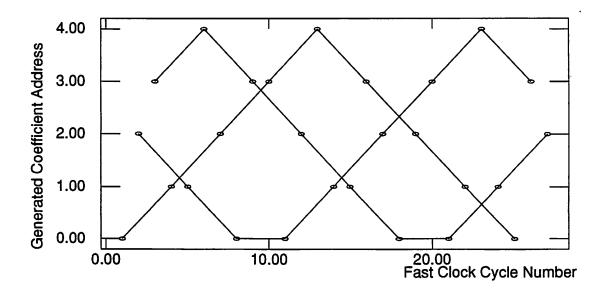

| Figure | 6.4:  | Sequence for generating coefficient addresses for the case $L/D = 3$                                                                 | 87    |

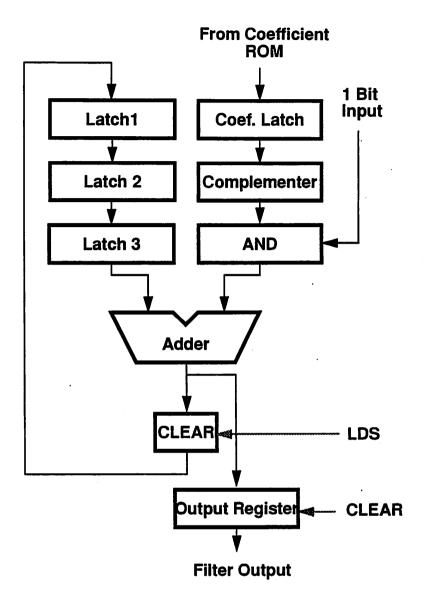

| Figure | 6.5:  | Datapath for the FIR filter family for the case $L/D = 3$                                                                            | 88    |

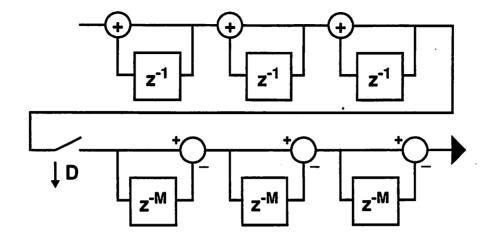

| Figure | 6.6:  | Block diagram of a CIC decimation filter.                                                                                            | 90    |

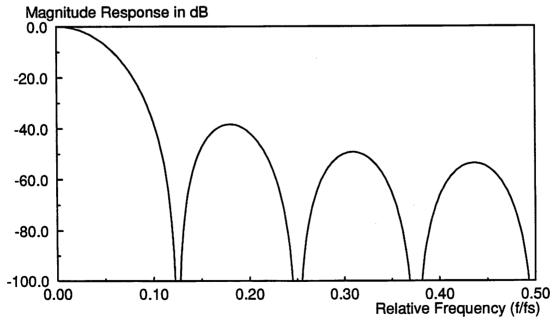

| Figure | 6.7:  | Magnitude response for a decimate-by-8 sinc3 filter.                                                                                 | 90    |

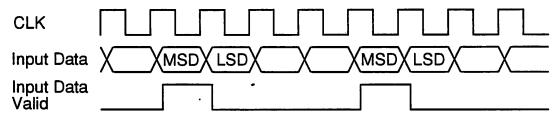

| Figure | 6.8:  | The output timing relations for the input signals for a CIC filter with digit-<br>serial integrators. Digit-size was assumed to be 4 | 92    |

| Figure | 6.9:  | The expected timing relations for the input signals for a CIC filter with digit-serial integrators. Digit-size was assumed to be 4   | 93    |

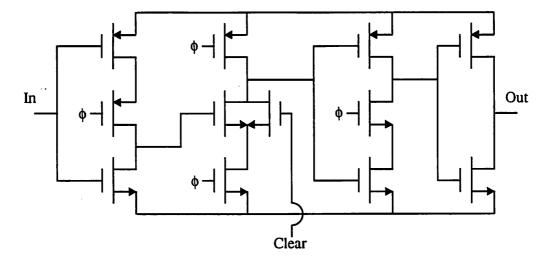

| Figure | 6.10: | Modified TSPC latch with reset.                                                                                                      | 95    |

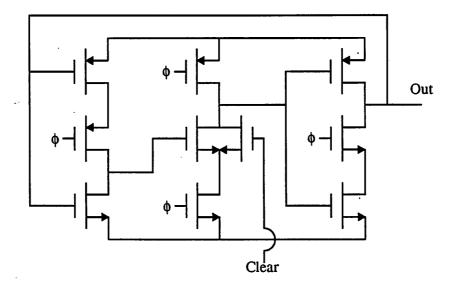

| Figure | 6.11: | Divide by 2 circuit.                                                                                                                 | 95    |

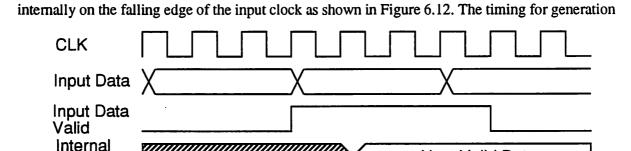

| Figure | 6.12: | Timing diagram for latching of the bit-parallel input                                                                                | 97    |

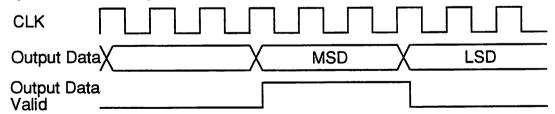

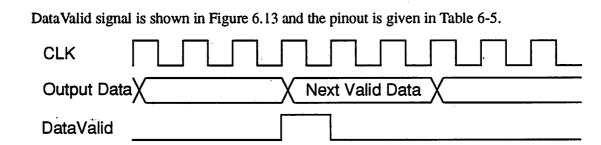

| Figure | 6.13: | Timing relations for the output data for the decimate-by-2 filter                                                                    | 97    |

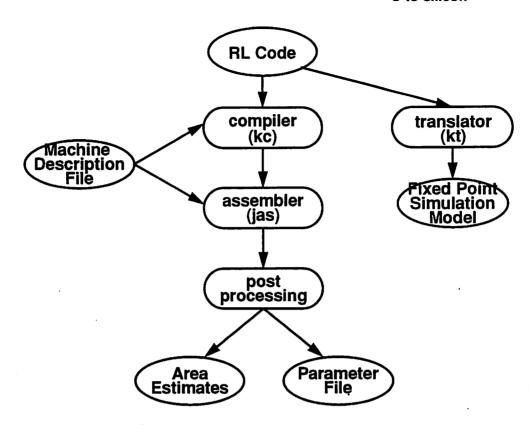

| Figure | 6.14: | Design flow for the C-to-silicon design tools                                                                                        | 99    |

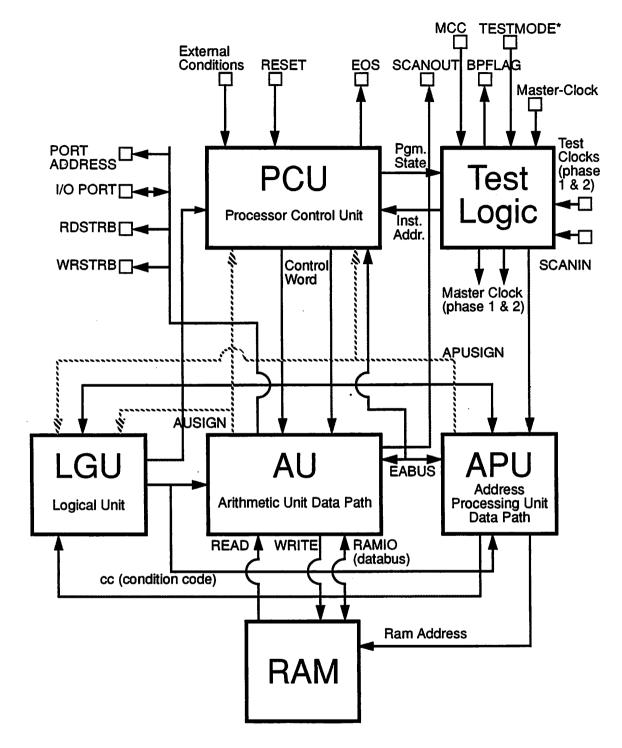

| Figure | 6.15: | Block diagram of the Puma processor                                                                                                  | . 100 |

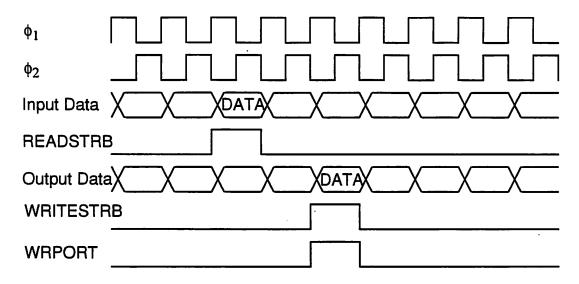

| Figure | 6.16: | Timing relations for the Puma processor.                                                                                             | .102  |

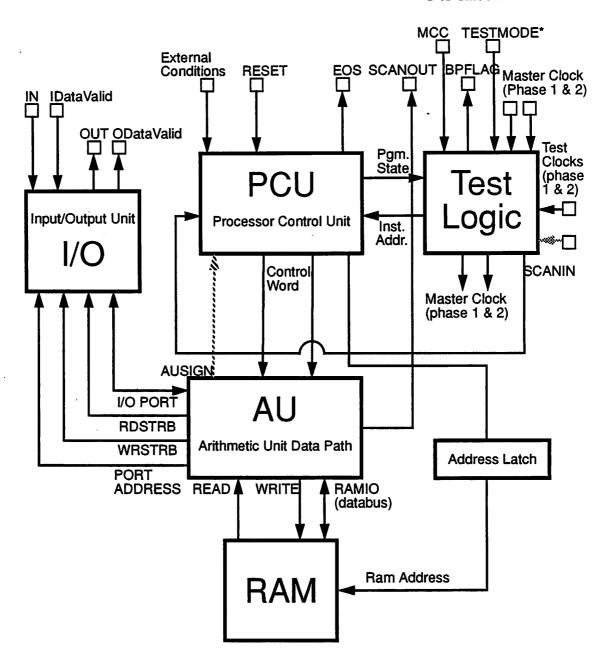

| Figure | 6.17: | Block diagram of the Lambda processor.                                                                                               | . 103 |

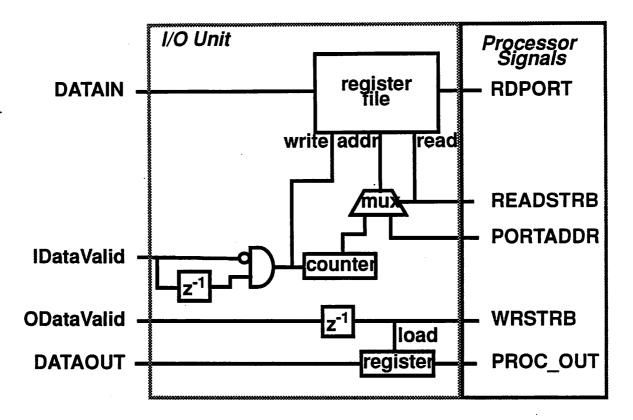

| Figure | 6.18: | Block diagram of the I/O unit in the Lambda Processor                                                                                | . 105 |

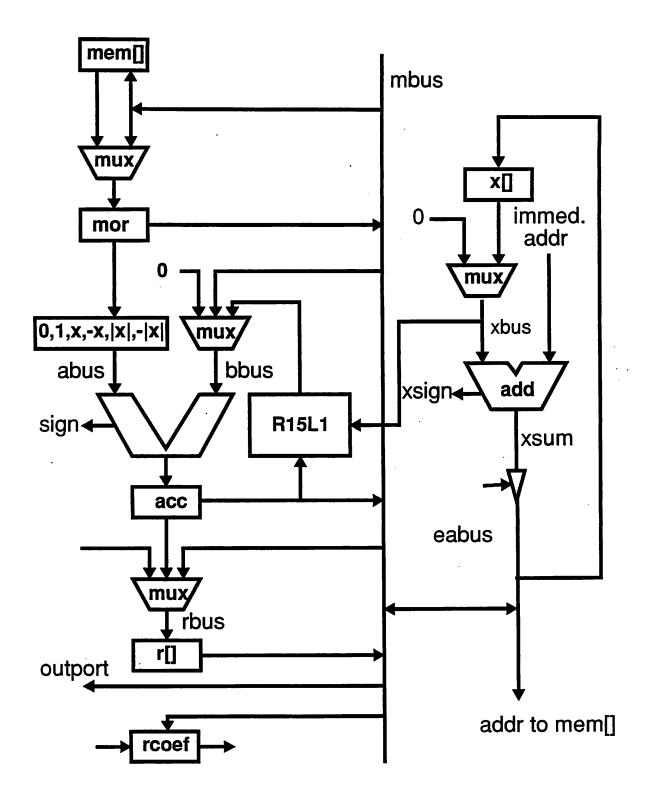

| Figure | 6.19: | Block diagram of the PUMA datapath and Address Calculation Unit.                                                                     | . 106 |

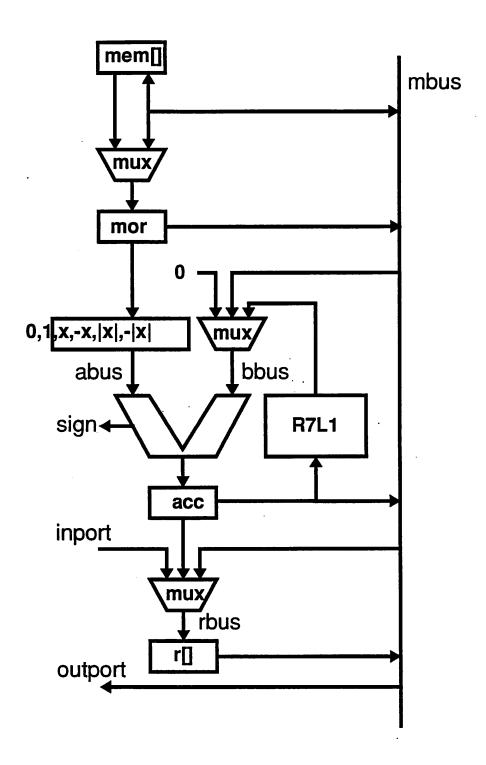

| Figure | 6.20: | Block diagram of the Lambda datapath.                                                                                                | . 107 |

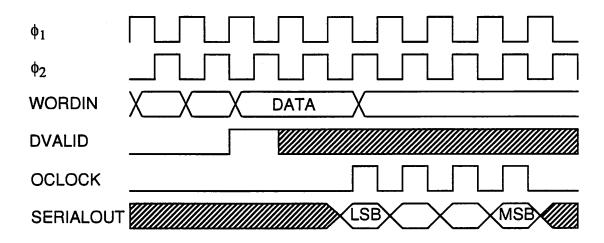

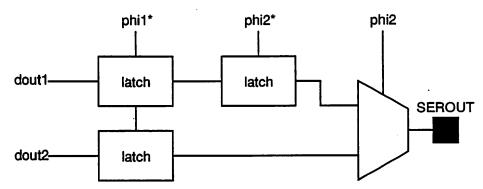

| Figure | 6.21: | Timing diagram for the parallel to serial converter.                                                                                 | . 109 |

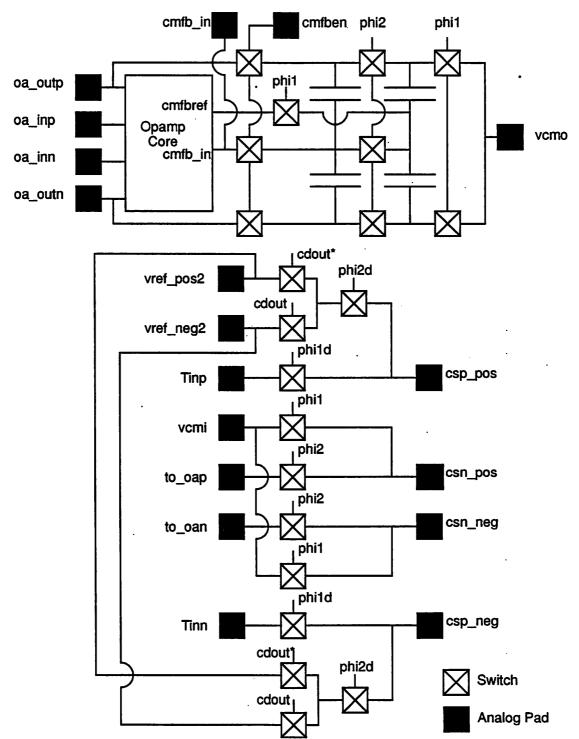

| Figure | 6.22: | Block diagram of the parallel to serial converter.                                                                                   | 109   |

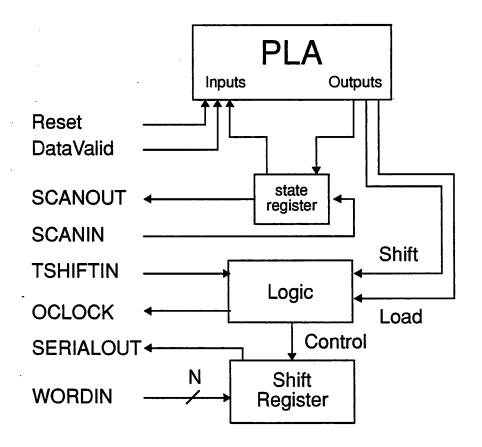

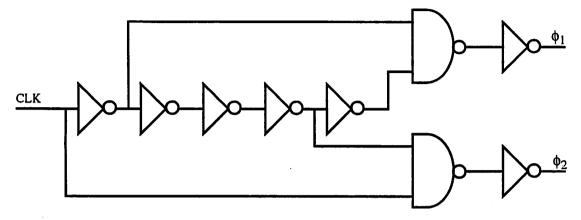

| Figure | 6.23: | Clock generator circuit for generating 2 non-overlapping phases.                                                                     | 110   |

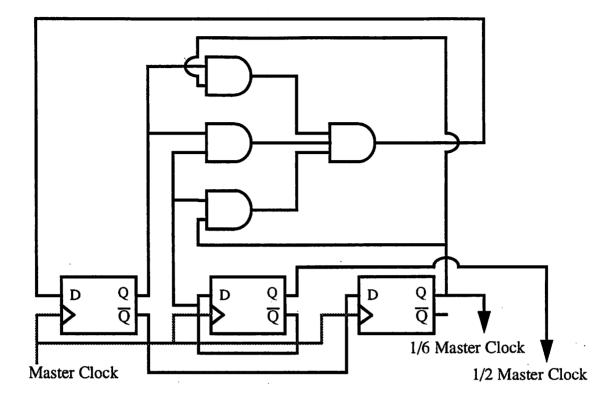

| Figure | 6.24: | Block diagram of circuit used to generate 1/6 and 1/2 clock phases                                                                   | 111   |

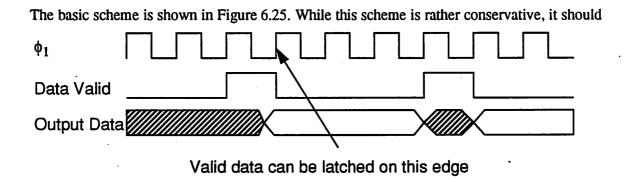

| Figure | 6.25: | Timing relations for system design.                                                                                                  | 116   |

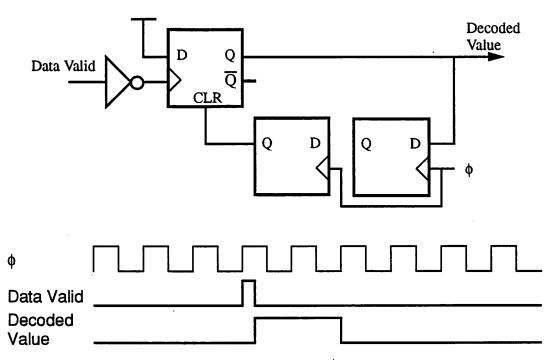

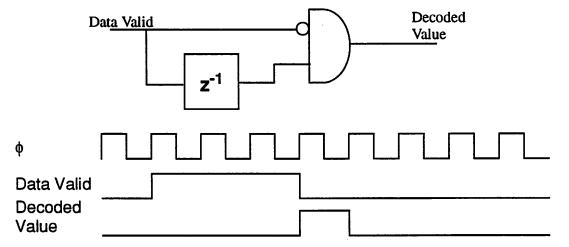

| Figure | 6.26: | Circuit for detecting the falling edge of a data valid signal.                                                                       | 117   |

| Figure | 6.27: | Simpler circuit for detecting a falling edge.                                                                                        | 117   |

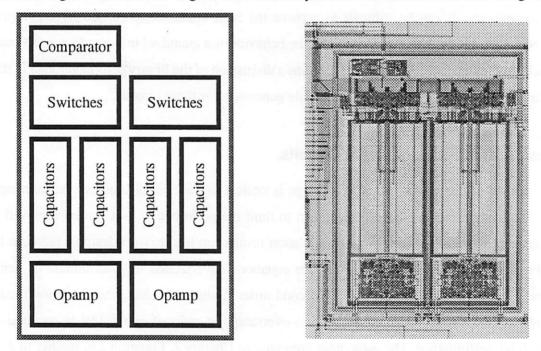

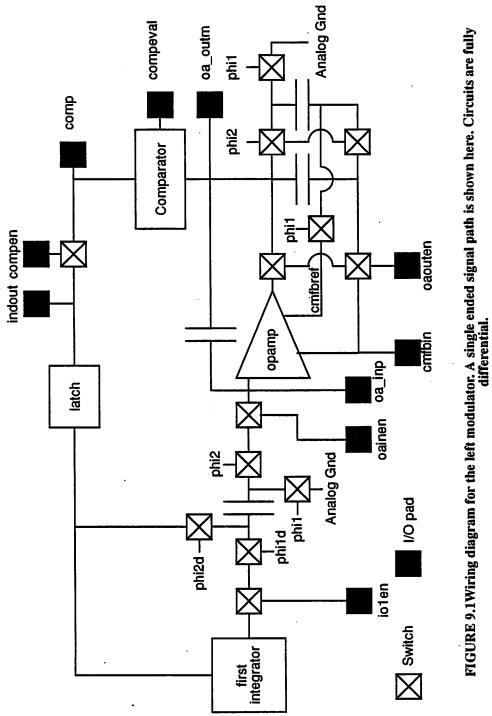

| Figure | 7.2:  | Block diagram of modulator layout and a die photo from a fabricated chip                                                             | 120   |

| Figure | 7.1:  | Basic diagram of a second order $\Delta$ - $\Sigma$ modulator                                                                        | 121   |

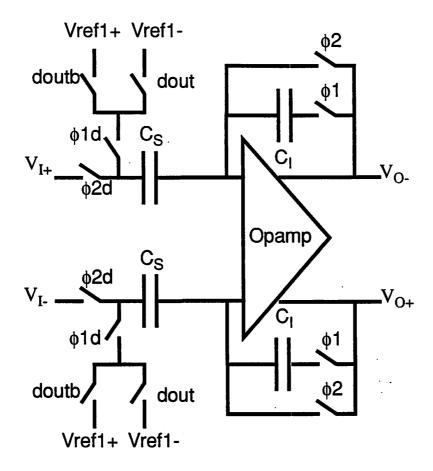

| Figure | 7.3:  | Integrator with correlated double sampling.                                                                                          | 124   |

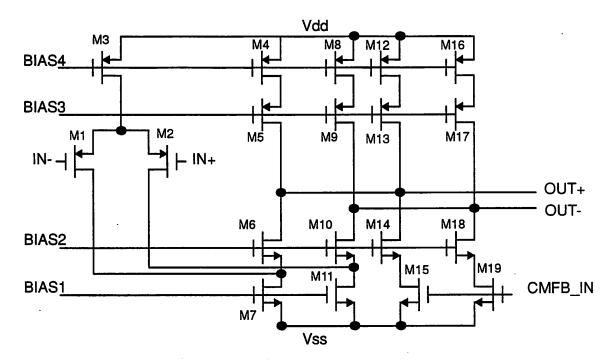

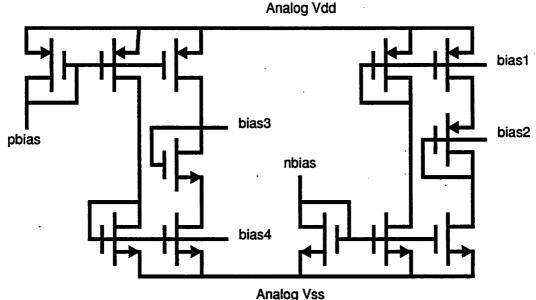

| Figure | 7.4:  | Folded Cascode Opamp.                                                                                                                | 125   |

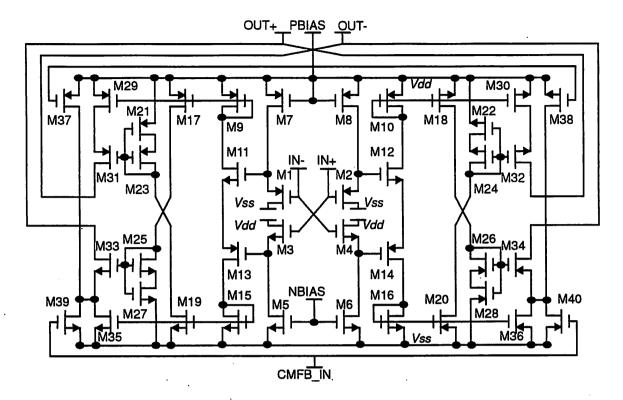

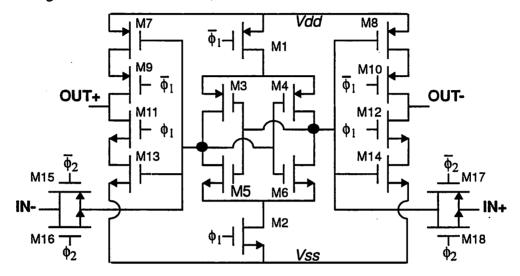

| Figure | 7.5:  | Class AB opamp, variation 1                                                                                                          | 126   |

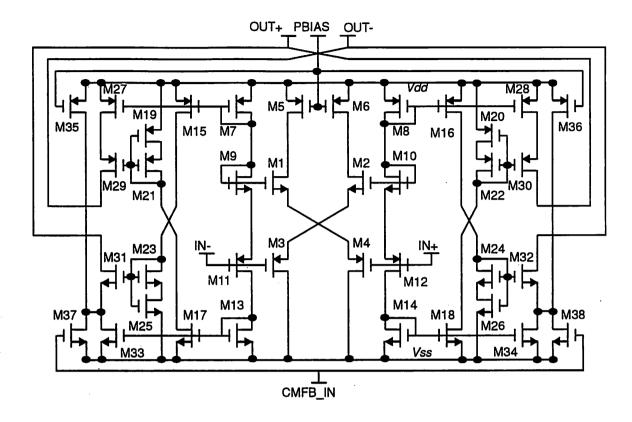

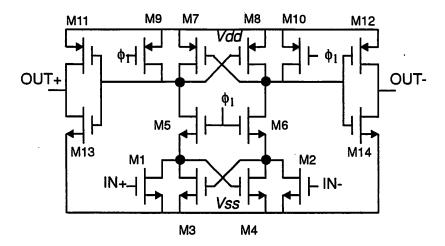

| Figure | 7.6:  | Class AB opamp, variation 2                                                                                                          | 127   |

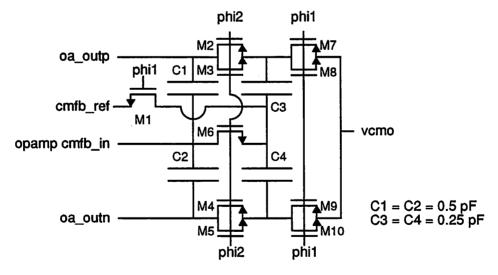

| Figure | 7.7:  | Common mode feedback circuit using capacitive updates.                                                                               | 128   |

| Figure | 7.8:  | Circuit diagram for comparator variation 1                                                                                                                                                                                                                            | 129   |

|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Figure | 7.9:  | Circuit diagram for comparator, version 2.                                                                                                                                                                                                                            | . 130 |

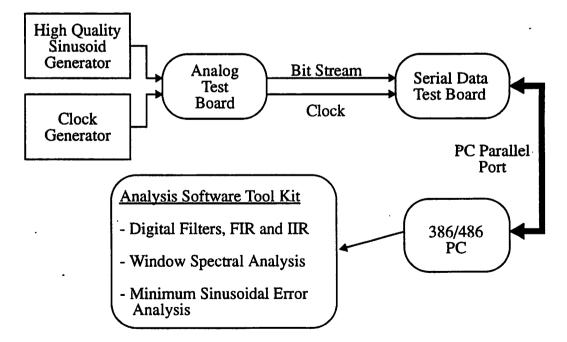

| Figure | 7.10: | Block diagram of the measurement setup.                                                                                                                                                                                                                               | . 131 |

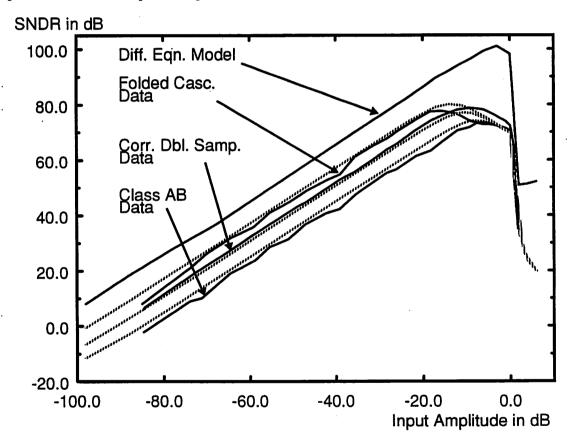

| Figure | 7.11: | Comparison of measured data (solid lines) and results from simulation models (dotted lines)                                                                                                                                                                           | . 133 |

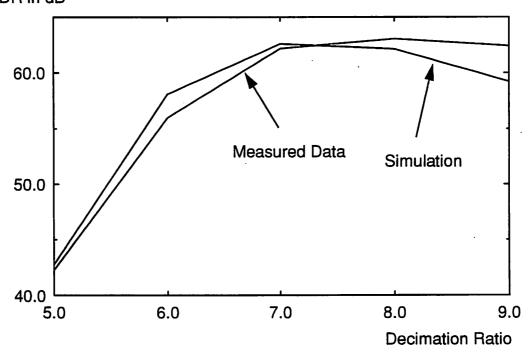

| Figure | 7.12: | Comparison of simulation and measured results for changes in decimation ratio. Input is a sinusoid, 20 dB down from full scale                                                                                                                                        | . 135 |

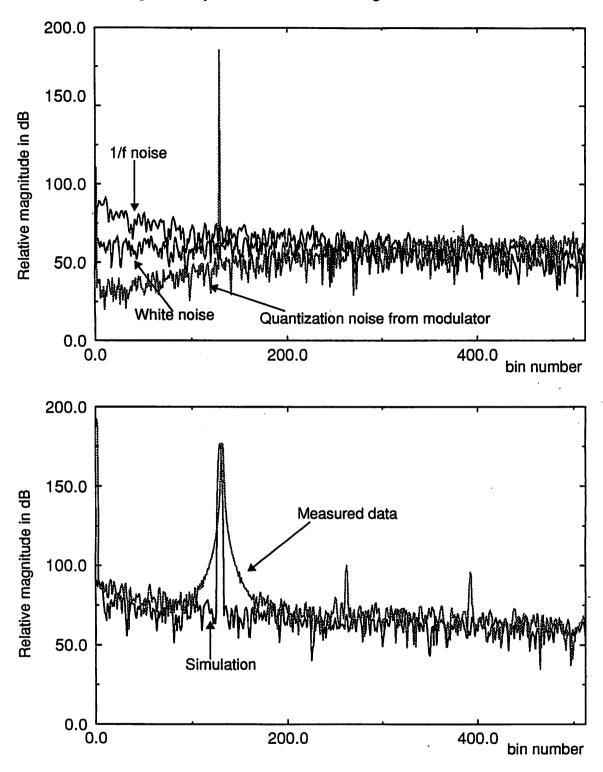

| Figure | 7.13: | FFT plots of simulated and measured data. The top plot shows the ideal response from a modulator, along with white noise and 1/f noise contributions. The bottom plot shows the composite simulation along with an FFT plot from taken from one of the test circuits. | . 136 |

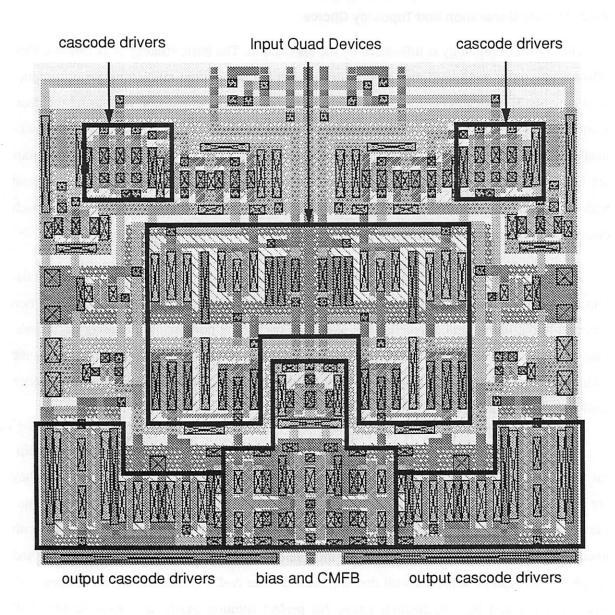

| Figure | 7.14: | Layout of the Class AB 2 opamp.                                                                                                                                                                                                                                       |       |

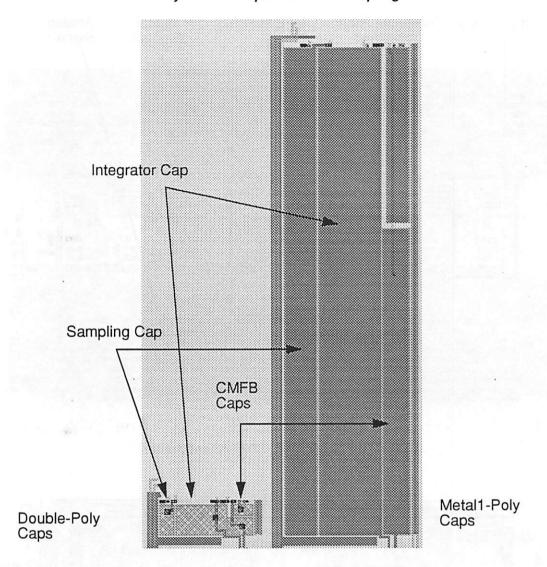

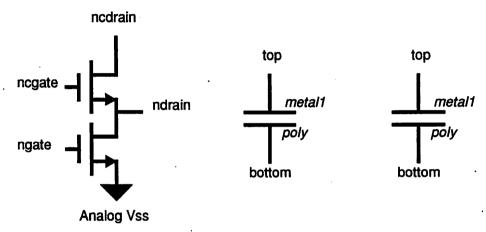

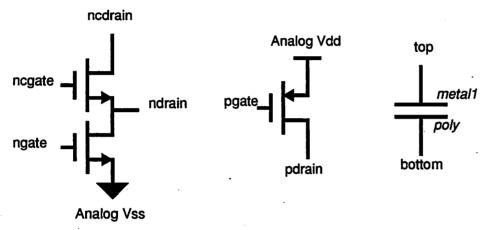

| Figure |       | Layout for double-poly and metal1-poly capacitors                                                                                                                                                                                                                     |       |

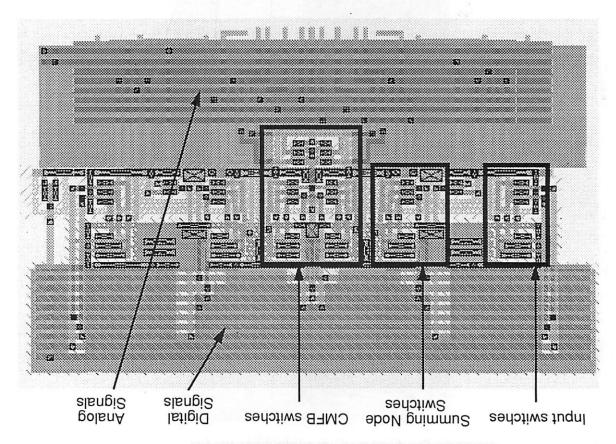

| Figure |       | Layout for the integrator switch array.                                                                                                                                                                                                                               |       |

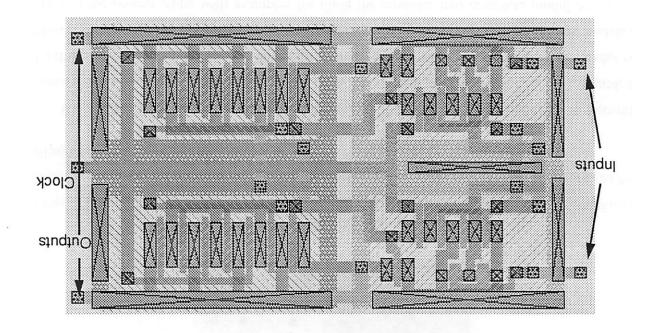

| Figure |       | Layout for the second comparator variation.                                                                                                                                                                                                                           |       |

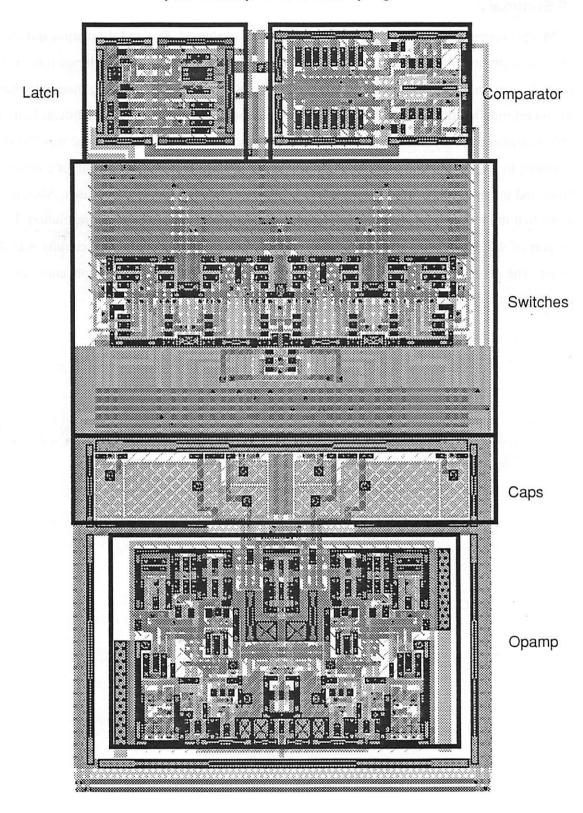

| Figure |       | Layout for a first-order modulator.                                                                                                                                                                                                                                   |       |

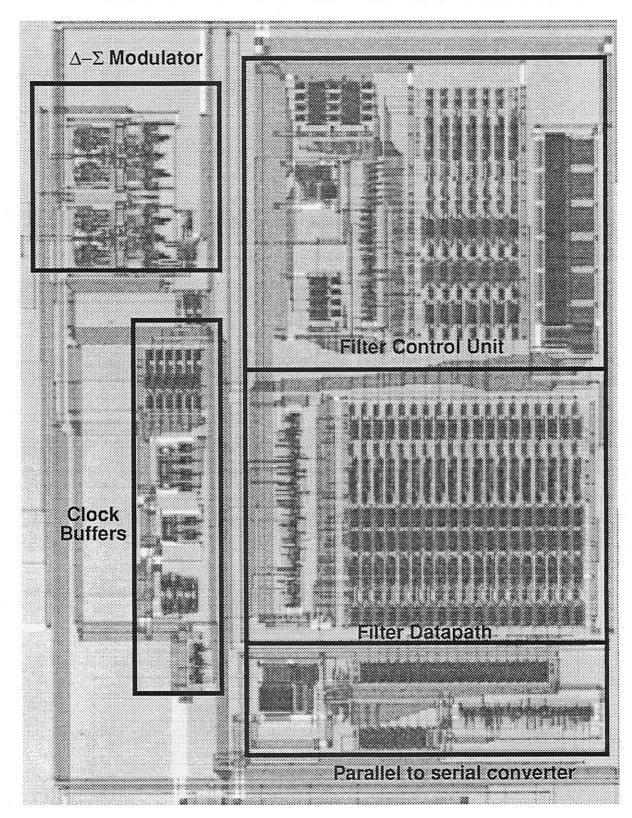

| Figure |       | Die photo of the chip for data acquisition                                                                                                                                                                                                                            |       |

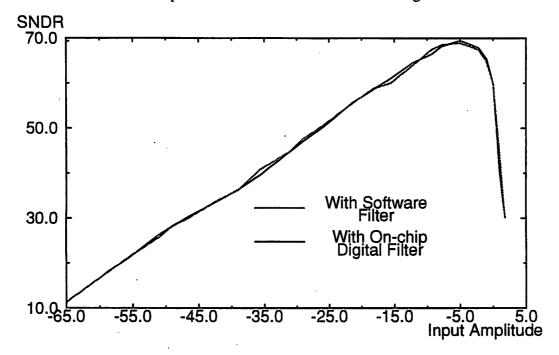

| Figure |       | Comparison of SNR curves when the filtering is performed on-chip and                                                                                                                                                                                                  |       |

| J      |       | off-chip                                                                                                                                                                                                                                                              | 150   |

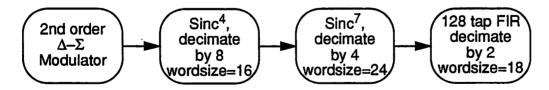

| Figure | 8.3:  | Functional units in the linear phase A/D converter                                                                                                                                                                                                                    | 152   |

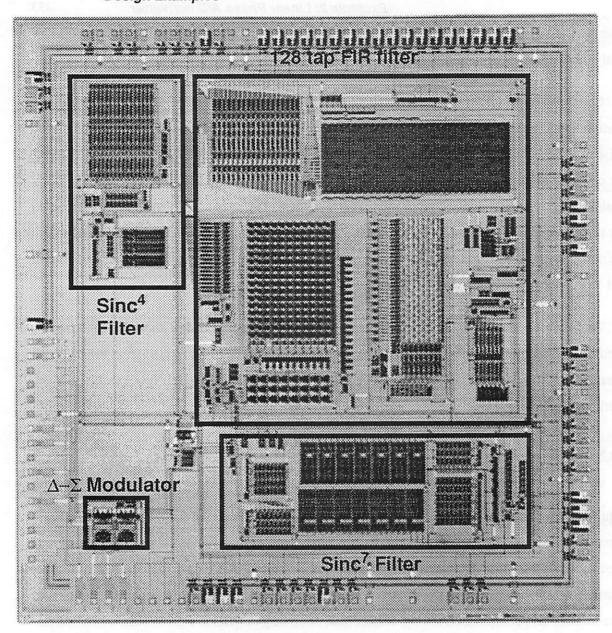

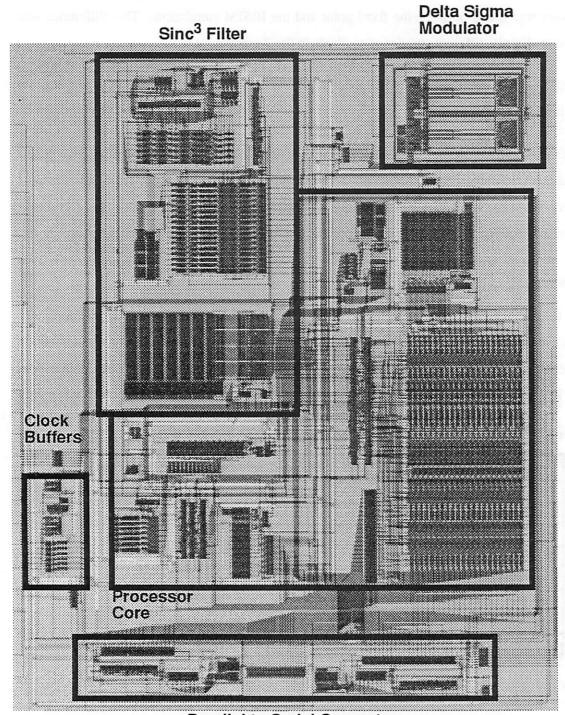

| Figure | 8.4:  | Die photo of the linear phase A/D converter.                                                                                                                                                                                                                          | 154   |

| Figure | 8.5:  | Measured output from the linear phase A/D chip                                                                                                                                                                                                                        | 155   |

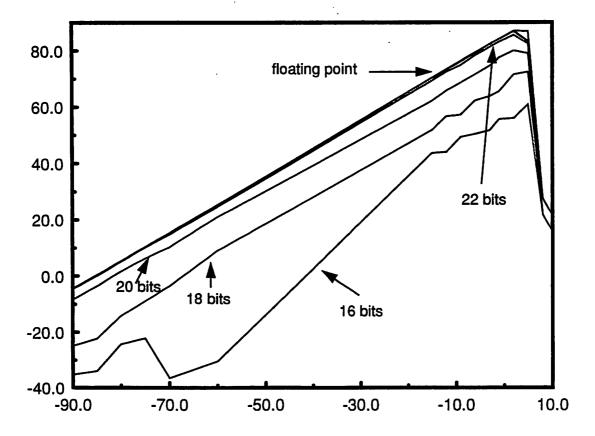

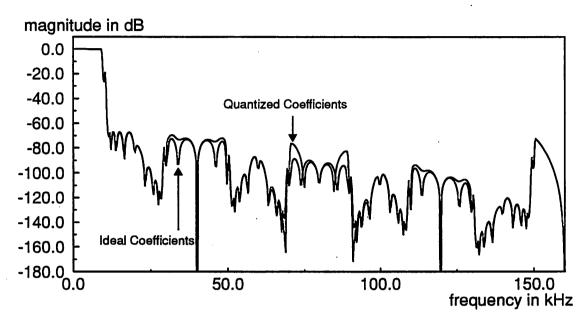

| Figure | 8.6:  | Results from finite wordlength simulations for the overall chip.                                                                                                                                                                                                      | 158   |

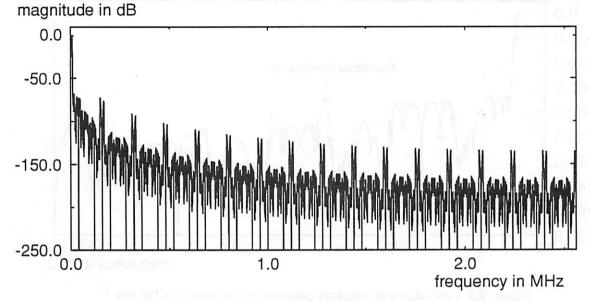

| Figure | 8.7:  | Composite frequency response for the decimate by 256 filter cascade                                                                                                                                                                                                   | 159   |

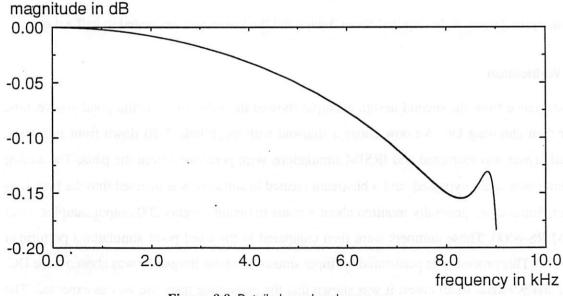

| Figure | 8.8:  | Detailed passband response.                                                                                                                                                                                                                                           | 159   |

| Figure | 8.9:  | Detail of overall frequency response for the region 0 to 160 kHz                                                                                                                                                                                                      | 160   |

| Figure | 8.10: | Die photo for the speech coder A/D interface.                                                                                                                                                                                                                         | 162   |

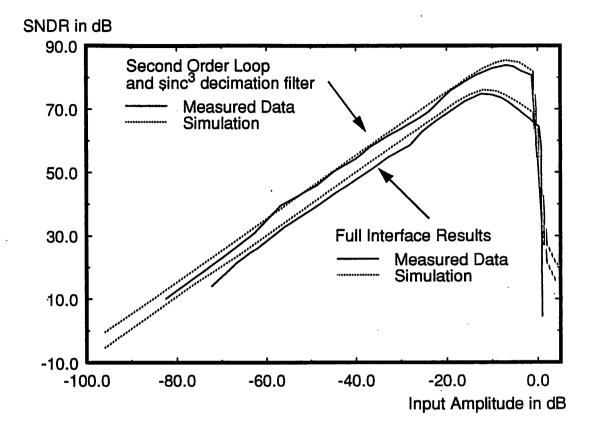

| Figure | 8.11: | Measured results from test chips                                                                                                                                                                                                                                      | 163   |

| Figure | 9.1:  | Block diagram of an oversampling D/A channel                                                                                                                                                                                                                          | 169   |

| Figure | C.1:  | Sample data entry box for estimating modulator parameters.                                                                                                                                                                                                            | 220   |

| Figure | C.2:  | Results from the modulator estimation macro.                                                                                                                                                                                                                          | 221   |

| Figure | C.3:  | The Add Filter menu for filter parameter estimation                                                                                                                                                                                                                   | 221   |

| Figure | C.4:  | Completed worksheet for decimation filter design.                                                                                                                                                                                                                     | 222   |

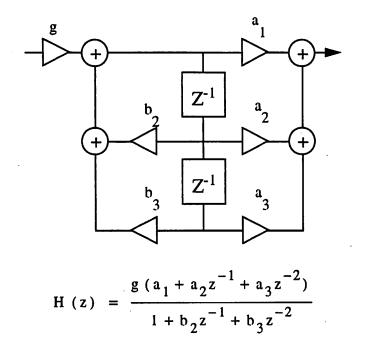

| Figure | D.1:  | Correspondence between a biquad and the system equation                                                                                                                                                                                                               | 240   |

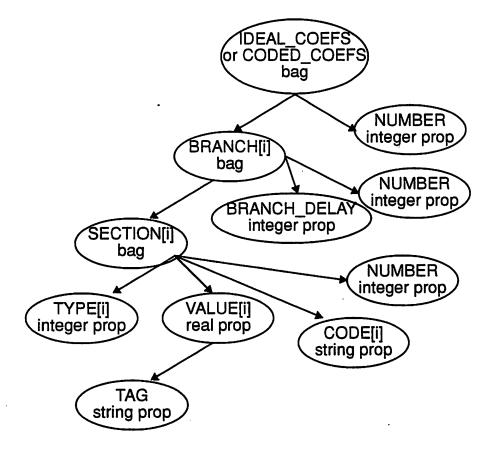

| Figure | D.2:  | OCT policy for storing biquad and LWDF coefficients                                                                                                                                                                                                                   | 242   |

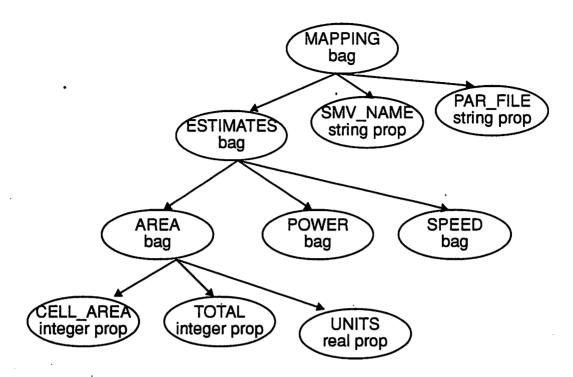

| Figure | D.3:  | Policy for the MAPPING bag and the ESTIMATES bag                                                                                                                                                                                                                      | 243   |

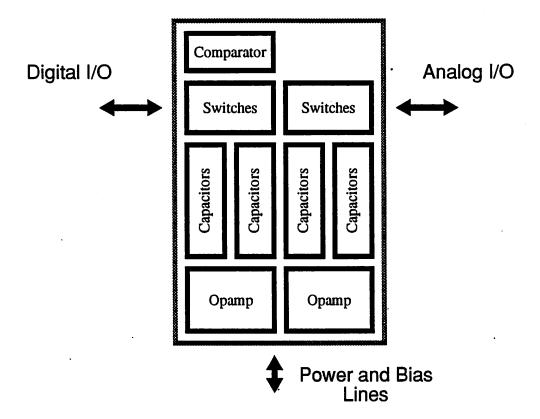

| Figure | F.1:  | Floorplan for the modulator.                                                                                                                                                                                                                                          | 252   |

| Figure | G.1:  | Block diagram of the test system.                                                                                                                                                                                                                                     | 256   |

| Figure | G.2:  | Test board layout                                                                                                                                                                                                                                                     | . 258 |

| Figure | G.3:  | Clock generation circuitry.                                                                                                                                                                                                                                           | 258   |

| Figure | G.4:  | Single-ended to differential converter.                                                                                                                                                                                                                               | 259   |

| Figure G.5: Block diagram of the Serial Data Acquisition Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |