# Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## A PARALLEL ARCHITECTURE FOR HIGH-DATA-RATE DIGITAL RECEIVERS IN SCALED CMOS TECHNOLOGY

by

Timothy Hak-Ting Hu

Memorandum No. UCB/ERL M93/62

26 July 1993

# A PARALLEL ARCHITECTURE FOR HIGH-DATA-RATE DIGITAL RECEIVERS IN SCALED CMOS TECHNOLOGY

Copyright © 1993

by

Timothy Hak-Ting Hu

Memorandum No. UCB/ERL M93/62 26 July 1993

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### **Abstract**

# A Parallel Architecture for High-Data-Rate Digital Receivers in Scaled CMOS Technology

by Timothy Hak-Ting Hu

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Paul R. Gray, Chair

Reduction in cost of terminal electronics is essential in order for fiber optic technology to penetrate LAN and telephony subscriber loop applications extensively. Currently, high-data-rate fiber transceiver electronics are implemented principally with the multichip approach, with bipolar and gallium arsenide technology.

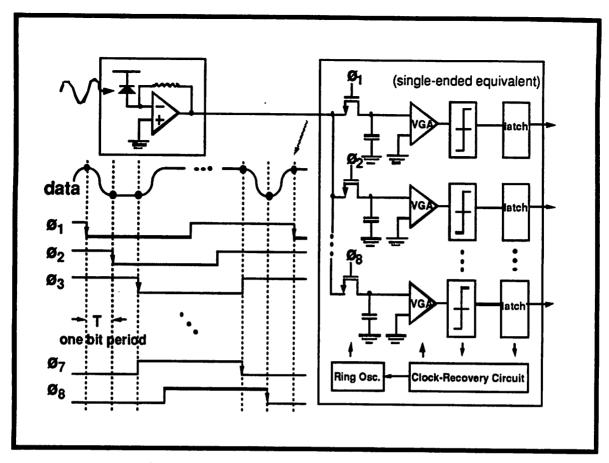

The objective of this researh is to develop a new parallel architecture to use the lower cost and higher integration of scaled CMOS technology to address the cost problem in fiber transceivers. The problem is first attacked by integrating the parallel-to-serial conversion, automatic gain control (AGC), decision, and clock recovery functions in CMOS at rates about 500Mb/s. The inherently slower speed of CMOS compared to bipolar and GaAs is compensated through the use of a high degree of parallel signal processing in the signal path.

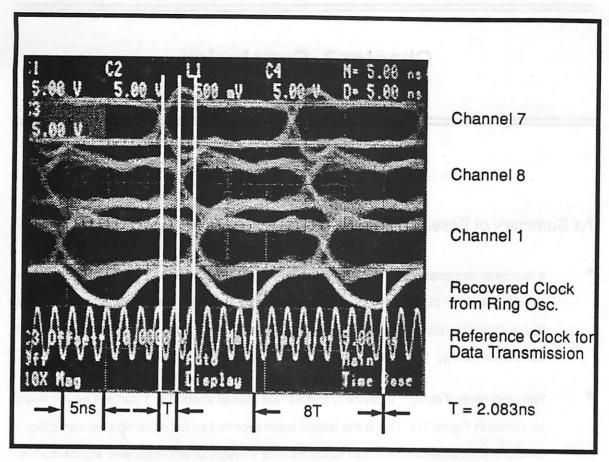

To verify the main idea about the new parallel architecture proposed in this thesis, an experimental prototype with 8 parallel channels was designed and fab-

ricated in a 1.2 $\mu$ m CMOS technology. A bit rate of 480Mb/s is achieved with a minimum peak-to-peak input voltage of  $18mV_{p-p}$ . The area of the chip is 160 mil X 160 mil (4mm X 4mm) and it consumes 900mW of power.

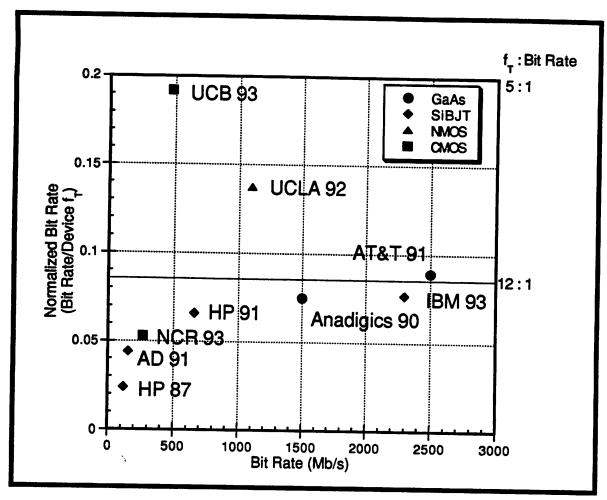

This thesis arrives at three main conclusions. First a minimum device  $f_T$  to data rate ratio of 4:1 can be achieved with the parallel architecture enabling CMOS technology to be used for Gb/s digital optical fiber receivers. Second, clock recovery can be done, through a decision directed scheme with two times oversampling, by inserting one or more timing channels in between the parallel data channels. Finally, the area and power consumption of the parallel architecture are comparable to implementations in bipolar and GaAs.

Chairman of Committee

# Table of Contents

| Chapter 1 Introduction                       |                                                |  |  |  |  |

|----------------------------------------------|------------------------------------------------|--|--|--|--|

| 1.1 Background and Motivation                |                                                |  |  |  |  |

| 1.2 Thesis Organization                      |                                                |  |  |  |  |

| Chapter 2 Optical Fiber Communication System | Chapter 2 Optical Fiber Communication System 3 |  |  |  |  |

| 2.1 Introduction                             | 3                                              |  |  |  |  |

| 2.2 Transmitter                              | 4                                              |  |  |  |  |

| 2.2.1 Light Source                           | 4                                              |  |  |  |  |

| 2.2.1.1 Light Emitting Diode (LED)           | 5                                              |  |  |  |  |

| 2.2.1.2 Semiconductor Junction-Diode Laser   |                                                |  |  |  |  |

| 2.2.1.3 Comparison of LED and Laser          | 8                                              |  |  |  |  |

| 2.2.2 Coder (MUX)                            |                                                |  |  |  |  |

| 2.2.3 Driver                                 | 11                                             |  |  |  |  |

| 2.2.3.1 LED Driver                           | 11                                             |  |  |  |  |

| 2.2.3.2 Semiconductor Laser Driver           |                                                |  |  |  |  |

| 2.3 Optical Fiber                            |                                                |  |  |  |  |

| 2.3.1 Modes of Propagation                   |                                                |  |  |  |  |

| 2.3.2 Attenuation and Dispersion             |                                                |  |  |  |  |

| 2.3.2.1 Attenuation                          | 16                                             |  |  |  |  |

| 2.3.2.2 Dispersion                           |                                                |  |  |  |  |

| 2.3.3 Single-Mode Fibers                     |                                                |  |  |  |  |

| 2.3.3.1 Single-Mode vs Multimode             |                                                |  |  |  |  |

| 2.3.3.2 Dispersion in SM Fibers              |                                                |  |  |  |  |

| 2.3.3.3 Attenuation in SM Fibers             |                                                |  |  |  |  |

| 2.3.4 Erbium-Doped Fiber Amplifiers (EDFAs)  |                                                |  |  |  |  |

| 2.4 Receiver                                 |                                                |  |  |  |  |

| 2.5 Probability of Error and Quantum Limit   | 23                                             |  |  |  |  |

| Chapter 3 Traditional Receiver Architecture  | 25                                             |  |  |  |  |

|      | 3.1 Introduction                            | 25 |

|------|---------------------------------------------|----|

|      | 3.2 Photo-Detectors (PDs)                   | 26 |

|      | 3.2.1 Semiconductor Photodiodes             | 26 |

|      | 3.2.2 Responsivity and Quantum Efficiency   | 26 |

|      | 3.2.3 PIN Photodiode                        | 28 |

|      | 3.2.4 Avalanche Photodiode (APD)            | 30 |

|      | 3.2.5 Photodiode Equivalent Circuit         | 32 |

|      | 3.2.6 PIN Photodiodes vs APDs               | 33 |

|      | 3.3 Low Noise Preamplifier                  | 33 |

|      | 3.3.1 Low-impedance Preamplifier            | 34 |

|      | 3.3.2 High-impedance Preamplifier           | 35 |

|      | 3.3.3 Transimpedance Preamplifier           | 37 |

|      | 3.4 Integrated Optoreceiver                 | 40 |

|      | 3.5 Main amplifier                          | 42 |

|      | 3.5.1 Limiting Amplifiers                   | 42 |

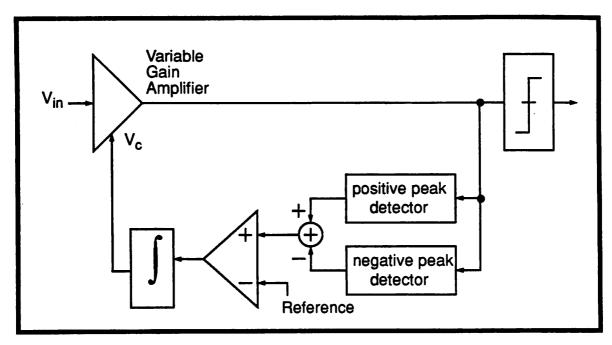

|      | 3.5.2 AGC Amplifiers                        | 43 |

|      | 3.6 Clock Recovery                          | 47 |

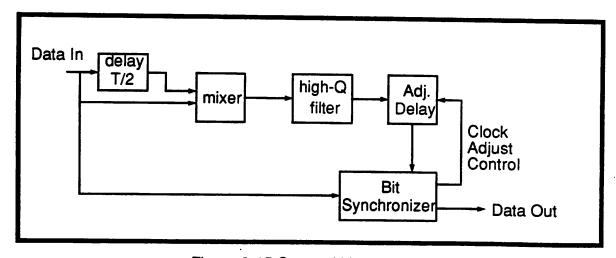

|      | 3.6.1 Spectral-Line Method                  | 49 |

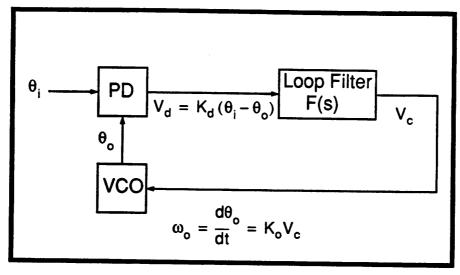

|      | 3.6.2 Phase-Locked Loop (PLL)               | 50 |

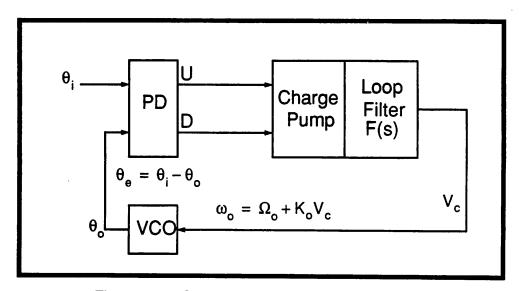

|      | 3.6.3 Charge-Pump Phase-Locked Loop (CPPLL) | 52 |

|      | 3.6.4 Wide-Band Clock Recovery              | 53 |

|      | 3.6.5 Circuit Requirements                  | 53 |

|      | 3.7 Decision Circuit                        | 54 |

|      | 3.8 Demultiplexer (DEMUX)                   | 55 |

|      | 3.9 Limitations of Traditional Architecture | 56 |

| Cha  | pter 4 Parallel Receiver Architecture       | 58 |

|      | 4.1 Introduction                            | 58 |

|      | 4.2 Analog DEMUX                            | 59 |

|      | 4.3 Multi-Phase Clock                       | 60 |

|      | 4.4 Parallel Channel                        |    |

|      | 4.5 Clock Recovery                          |    |

|      | 4.6 Improvement in Performance              |    |

| Chap | pter 5 Parallel Receiver Implementation     |    |

|      | 5.1 Introduction                            | 65 |

|      | 5.1.1 Input Demultiplexing                  |    |

|      |                                             | •  |

| ,                | 5.1.1.1 CMOS Sample-and-Hold                                | 67 |

|------------------|-------------------------------------------------------------|----|

|                  | 5.1.1.2 Bandwidth Related Error                             | 67 |

|                  | 5.1.1.3 Accuracy Related Error                              | 69 |

|                  | 5.1.1.4 Bandwidth vs Accuracy Trade-off                     | 70 |

|                  | 5.1.1.5 Circuit Implementation                              | 71 |

|                  | 5.1.2 Multiple Phase Clock Edges                            | 72 |

|                  | 5.1.3 Channel Amplifier                                     | 73 |

|                  | 5.1.3.1 MOS Variable Gain Amplifier                         | 73 |

|                  | . 5.1.3.2 DC and AC Analysis                                | 74 |

|                  | 5.1.3.3 Channel Amplifier with Input DC Offset Cancellation | 77 |

|                  | 5.1.3.4 Distortion Analysis                                 | 78 |

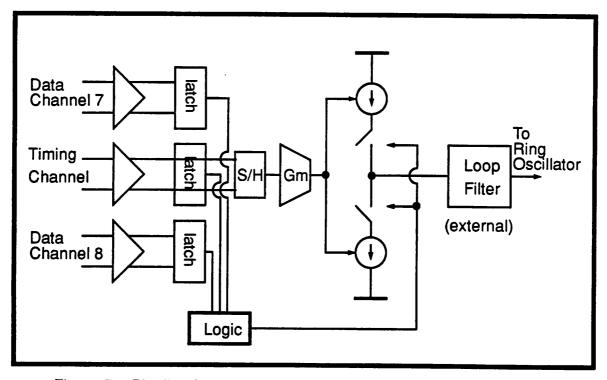

|                  | 5.1.4 Clock Recovery                                        | 82 |

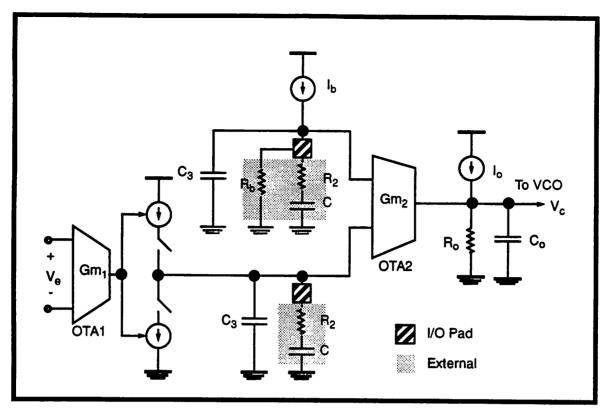

|                  | 5.1.4.1 Designing a Charge-Pump Phase-Lock Loop             | 82 |

|                  | 5.1.4.2 Inductive Clock Recovery                            | 85 |

|                  | 5.1.4.3 Decision Directed Phase Detection                   | 87 |

|                  | 5.1.4.4 Phase Detector Implementation                       | 88 |

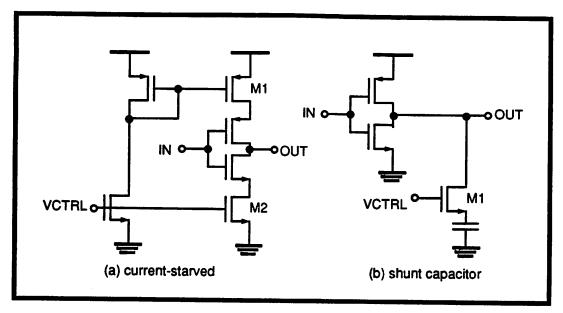

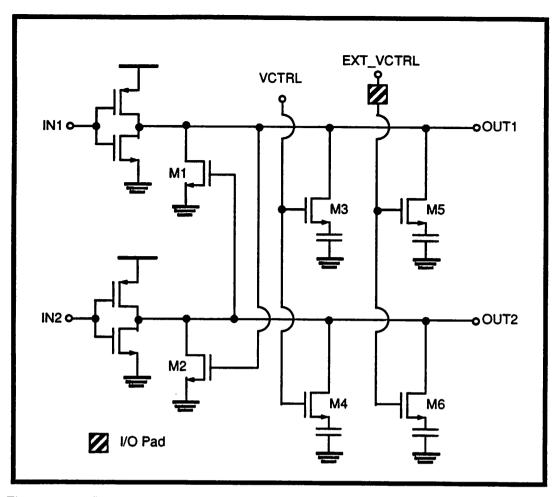

|                  | 5.1.4.5 Ring Oscillator Implementation                      | 89 |

|                  | 5.1.4.6 Charge-Pump PLL Loop Dynamics                       | 91 |

|                  | 5.1.4.7 Initial Acquisition                                 | 94 |

|                  | 5.1.4.8 Effect of DC offset and Pulse Distortion            | 95 |

| Cha <sub>l</sub> | pter 6 Experimental Results                                 | 97 |

|                  | 6.1 Experimental prototype                                  | 97 |

|                  | 6.2 Voltage Control Oscillator                              |    |

|                  | 6.3 AGC Biasing                                             |    |

|                  | 6.4 Bit Error Rate Measurements                             |    |

|                  | 6.4.1 Minimum Input Voltage vs Bit Rate                     |    |

|                  | 6.4.2 BER vs Input Voltage                                  |    |

|                  | 6.4.3 Waveform Dependence of BER                            |    |

|                  | 6.4.4 Channel Dependance of BER                             |    |

|                  | 6.4.5 Supply Dependence of BER                              |    |

|                  | 6.5 Jitter Performance                                      |    |

|                  | 6.6 PLL Performance                                         |    |

|                  | 6.7 Performance Summary                                     |    |

| Chap             | oter 7 Conclusion                                           |    |

| _                | 7.1 Summary of Research Results                             |    |

|                  |                                                             |    |

.

| References                                              | 124 |

|---------------------------------------------------------|-----|

| 7.3 Future Work                                         | 122 |

| 7.2 Projected performance in Scaled Technologies        | 121 |

| 7.1.2 Special Issues in Designing a Parallel Receiver   | 121 |

| 7.1.1 Traditional Architecture vs Parallel Architecture | 118 |

# Acknowledgments

I wish to express my deepest gratitude and appreciation to Professor Paul R. Gray, my research advisor, for his continuous support and encouragement throughout the course of my Ph.D. study. His vast knowledge and insight in the field of analog integrated circuit design have never seized to amaze and enlighten me. It has been my most rewarding experience working under him.

I would also like to thank Professor Robert G. Meyer, and Professor Donald O. Pederson for the helpful discussions and suggestions during these years. The help of Professor Joseph M. Kahn in giving suggestions and loaning the equipments for testing the prototype is also gratefully acknowledged.

The graduate students in the analog integrated circuit group made these years of research a lot more enjoyable and memorable, especially the "inner cubicle gang" - Ken Nishimura, Gregory Uehara, and Weijie Yun. Ken provided numerous technical and CAD supports. Greg gave so much moral support and spent a lot of his time coaching me for my talks. Weijie helped broadening my knowledge in integrated circuit processing and improving my tennis. Discussions with other colleagues - Gani Jusuf, Robert Neff, Cormac Conroy, and David Cline, was always fruitful and enlightening.

Last but not least, I thank my parents, Annie and Hung-Nyie Hu, for their support and patience. Their strong belief in me was an important driving force that

carried me through the tough times.

The research was supported by the National Science Foundation grant MIP-9101525, MICRO, Texas Instruments, and Level One Communications.

# **Chapter 1 Introduction**

#### 1.1 Background and Motivation

The first optical communication system was probably the "photophone", a pattern awarded to Alexander Graham Bell in 1880 [1]. It was a system for transmitting voice over a few hundred meters by modulating reflected sunlight with a vibrating mirror and the receiver was simply a photocell. It was never a commercial success. The breakthrough didn't come until the invention of laser in 1960. With continuous research and development of lasers, photodetectors and materials for optical transmission, the bandwidth for communication is gradually increasing and the attenuation over distance is decreasing. Optical fiber communication is already a major technical and commercial success.

The field of lightwave datacommunication has experienced explosive growth in the past ten years, both in terms of its commercial importance and in terms of the research effort devoted to it in academic and industrial laboratories. High speed integrated circuits (IC) have played a key role in this phenomenal growth because they are essential to interface with the high speed light sources and photodetectors at both ends of a fiber span [2].

A major problem limiting the deployment of optical fiber communication systems in the range of 500Mb/s and above is the cost of the optical components and the terminal electronics attributed to the high cost technology, package and assembly required. Electronic interfaces in general involve complex, low noise linear and nonlinear elements for amplification, threshold detection, and timing extraction. High speed electronic circuits have been among the bottlenecks in the realization of practical high-data-rate systems.

The application of VLSI technology to communication systems has played an important role in reducing the cost of many types of communication systems in use today and will play an increasingly important role in the future. The objective of this research is to develop a new architecture to relax the speed requirement imposed on the technology for implementation, so that the lower cost and higher integration of scaled CMOS technology can be used to address the cost problem in the implementation of high-data-rate terminal electronics.

#### 1.2 Thesis Organization

An examination of the use of demultiplexed sampling and parallel processing in analog signal data path for a CMOS high-data-rate receiver is presented in this thesis. The three basic building blocks of optical fiber communication systems are the transmitter, the fiber, and the receiver. Chapter 2 reviews the transmitter and fiber in detail, and give a brief description of the receiver. The building blocks in the traditional architecture of a fiber optic receiver is described in detail in chapter 3, together with their circuit implementations. The disadvantages and limitations of traditional receiver architecture are pointed out. In Chapter 4, a new parallel receiver architecture is proposed to relax the speed requirement imposed on the technology for implementation. The key building blocks involved in this new parallel receiver architecture is also discussed in the same chapter. In Chapter 5, the design of a prototype implementing the parallel architecture is described in detail with the circuit requirements and circuit solutions. Experimental results from a prototype implemented in a 1.2-µm CMOS technology are presented in chapter 6. Chapter 7 summarizes the research results, and conclusion is drawn with a discussion of further improvement and future work.

# **Chapter 2 Optical Fiber Communication System**

#### 2.1 Introduction

The development of the laser and the optical fiber has brought about a revolution in communication system design. In the 1960s, the laser evolved from a laboratory curiosity to become a versatile and widely applied family of devices and systems. In the 1970s, the optical fiber was developed from an idea with some promise to be a proven communication channel capable of carrying high data rates with low attenuation over distances far exceeding those used in coaxial and microwave systems. In the 1980s, optical fiber communication systems technologies are achieving a broad and still expanding range of successful commercial applications and are expanding the horizons of optical fiber systems capabilities.

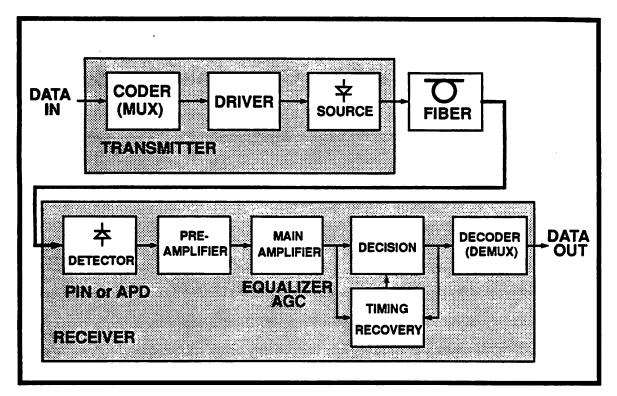

An optical fiber communication system consists of three principle parts: the transmitter, the fiber, and the receiver, as shown in Figure 2-1. When binary information is transmitted, one format may be converted to another; e.g. Non-Return-to-Zero (NRZ) data may be converted to Return-to-Zero (RZ) or M-tary patterns, or the line rate may be raised by transmitting extra bits for framing and coding. These modification facilitate demultiplexing, error detection, and clock recovery. For transmitting analog information, the input signal may be predistorted to compensate for non-linearities in the light source, or digitally encoded to subcarrier frequency modulated to circumvent non-linearities. A good summary of coding and analog modulation techniques can be found in [3] [4]. This chapter will concentrate on direct intensity modulation of the light source for transmission, as it is employed in most practical high-data-rate systems.

The following sections will give a brief description for each of the three main parts, and

Figure 2-1 Block Diagram of a Basic Optical Fiber Communication System the limitations that each part imposes on the total system performance. Receiver Implementation is the main focus in this thesis and will be described in detail in Chapter 3.

#### 2.2 Transmitter

A digital transmitter converts the electrical signals into corresponding light-intensity envelopes. Such direct modulation is intended to affect only the average optical power. Any phase or frequency information incidently imparted to the optical carrier itself is not used at the receiver. This information is however used in another class of systems which employ coherent transmission [5].

The main components in a transmitter are a coder (with multiplexing function), a device driver, and a light source.

#### 2.2.1 Light Source

While optical fiber transmission uses light energy to carry the information, at the present

state of the art, the signals are generated and manipulated electrically. This implies an electrical-to-optical conversion at the input to the fiber medium is needed. Two semiconductor devices, light-emitting diodes (LEDs) and semiconductor lasers, are suitable for use in terms of device dimensions, speed, efficiency, electrical characteristics and reliability.

## 2.2.1.1 Light Emitting Diode (LED)

Optical power of a LED is produced in a forward-biased p-n junction diode by the radiative recombination of holes and electrons. The power is proportional to I, the input current, and hf, the energy of the photon, where h is the Planck constant and f the frequency of light emitted. The constant of proportionality is the quantum efficiency  $\eta$ .

$$P = \eta \frac{I}{q} hf$$

(EQ 2-1)

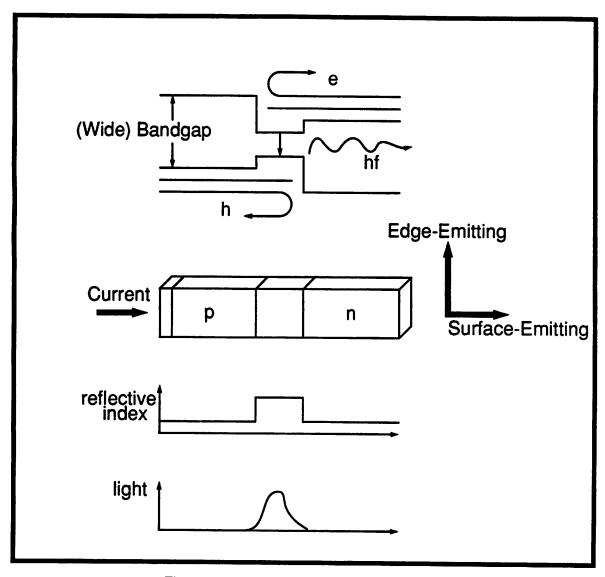

Because the relationship between P and I is linear, the LED can be intensity modulated by modulating the input current. Optical frequency and phase modulation are not feasible when the light source is a LED because the LED output is incoherent; i.e. its spectrum is spread over a range of wavelengths which is large with respect to the bit rate for transmission. The spectrum can be narrowed by using a double-heterostructure instead of a single p-n junction. The double-heterostructure (DH) LED as shown in Figure 2-2, consists of a narrow-bandgap material, constituting the active region, sandwiched between two wide-bandgap materials. The wave-length of the radiation is determined by the narrow-bandgap energy. The DH LED has several advantages over the single p-n junction diode. The recombination region, from which light is emitted, is well defined by the structure of the device. The internal quantum efficiency can be higher than that of the homojunction diode. Because the wide-bandgap material has lower index of refraction, the double heterostructure constitutes a dielectric waveguide that confines the lightwave and results in higher external quantum efficiency. The wide-bandgap material can be made transparent at the wavelength of the lightwave, thus reducing attenuation and further increasing the internal quantum efficiency.

LED devices are available in two basic types, edge-emitting and surface-emitting. The

Figure 2-2 Double Heterostructure LED

edge-emitting LED is usually a stripe-contact device. Light generated in the active region propagates parallel to the stripe and is emitted from one end of the active region. Light propagating in other directions is lost. The surface-emitting LED is usually designed to couple light directly into an optical fiber. The surface through which light is emitted is circular, with a diameter similar to that of the fiber. Because the output is taken from a side of larger area, the external quantum efficiency of the surface-emitter can be larger than that of the edge-emitter.

#### 2.2.1.2 Semiconductor Junction-Diode Laser

The semiconductor junction-diode laser is the dominant laser in optical fiber communica-

tion systems. The laser consists of an optical cavity resonator, and an amplifying mechanism compensating for the losses of the passive resonator. In the semiconductor laser, the optical resonator is normally a Fabry-Perot interferometer with two plane mirrors. Amplification in the laser is provided by the stimulated emission of radiation. Electrons at excited energy levels can be stimulated to decay to a lower-energy state by an incident lightwave, emitting a photon in the process. The energy of the photon and the frequency of the lightwave are related by

$$E = hf = \frac{hc}{\lambda}$$

(EQ 2-2)

where c is the speed of light.

One of the requirement for lasing is to have the gain, as lightwave propagates in an amplifying medium, larger than the losses in the passive resonator which includes absorption, scattering, and transmission through the mirrors. This requires population inversion of the minority carrier concentration in the medium. A population inversion requires some kind of non-equilibrium condition to create and sustain it. Means for sustaining a population inversion are called pumping. With an adequate pump rate, the population inversion will produce enough gain to cause lasing to begin, and the laser field will increase in strength. Saturation ultimately causes the gain to decrease until the gain and total loss are equal; this is the steady-state condition.

The frequency of oscillation is determined by the resonant frequencies for which the gain is greater than the total losses. There can be several modes of oscillation occurred at the same time. However, single mode operation can be achieved by the integration of wavelength selectivity directly into the semiconductor laser structure. As an example, a distributed-feedback (DFB) laser integrated a grating region in the pumped part of the gain region for wavelength selectivity.

In the semiconductor laser, pumping is done by providing a direct current in the forward direction in the junction diode. The steady state photon density can be expressed as [6]

$$\phi_s = (\frac{\tau_{ph}}{qd}) (J - J_{th})$$

(EQ 2-3)

where  $\tau_{\text{ph}}$  is the characteristic lifetime of photon, d is the length of the resonator and  $J_{\text{th}}$  is

the threshold current density for lasing. The power density can then be calculated from the photon density by reconizing that each photon carries energy hf, and are moving with velocity c/n where c is the speed of light and n is the reflective index of the medium.

Modulation of the laser is similar to modulation of the LED. The linear P versus I characteristic provides linear intensity modulation of the laser output powered by modulating the input current. However, even for pulse signals, the biasing current is often set at a value near the threshold current because of the time required for the pulse to reach its peak value can be made shorter if the current and the population of electrons in the conduction band do not have to build up from zero.

#### 2.2.1.3 Comparison of LED and Laser

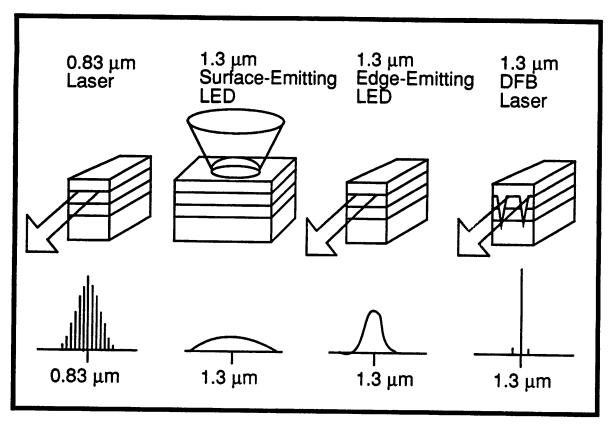

The LED output is incoherent, therefore only intensity modulation is possible. The wide spectral width of the LED also sets a limit on the bit-rate distance product through material dispersion. The laser output is much more coherent, meaning that it has a single frequency with linewidth small compared with the signal bandwidth, making it the only choice if coherent modulation and demodulation is needed. Shown in Figure 2-3 are some typical output spectra of different kinds of LEDs and semiconductor lasers.

The LED emits light spread over a much larger solid angle than a laser. The poor directivity of the LED implies that a smaller proportion of the power is coupled into the fiber, particularly for a single mode fiber which accepts light only at smaller incident angles. Thus, the laser is necessary for single mode fiber except for short distance where the attenuation is low.

A device driver is needed to control the current flowing through the light source in order to modulate the optical power emitted. LED is characterized by a single pole frequency response and can be modulated at frequencies up to 100's MHz. A semiconductor laser source is much more complicated. The maximum modulation frequency depends on the frequency response and turn-on dynamics of the laser. A semiconductor laser can be modulated up to 10 GHz depending on the structure and bias point.

Figure 2-3 Light Sources and Spectra

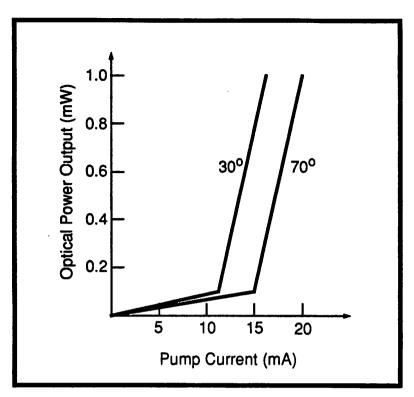

The maximum power emitted by a LED is about 100µW (-10dBm) while the laser can go up to 10mW (10 dBm) with 1mW (0dBm) being typical. However, the light output of the laser is very temperature dependent as shown in Figure 2-4, and hence it is generally necessary to monitor the light output and control the driving current using a feedback circuit.

On the other hand, LED is much cheaper and reliable than semiconductor laser and the driver is much simpler with lower biasing currents.

With modest launched power and speed, and broad spectral width, LED is used for short-distance, medium-bit-rate (50 to 500Mb/s) applications. With high reliability, LED is also used in high-temperature or uncontrolled environments such as for data links within high-speed equipments, in local area networks, or in the telephone subscriber loops.

Laser provides a higher-quality lightwave source than does the light-emitting diode. For many optical communication system applications, the advantages that the laser can offer are valuable. Given the 10-30dB additional launched power levels compared with LED, higher speeds and

Figure 2-4 Effect of Temperature on Laser Threshold Current

narrower spectral widths, lasers are useful over a significantly wider bit-rate · length region. For the long term, the semiconductor laser is the source of choice, especially when single mode fiber is dominating these days. However the laser is considerably more expensive than the LED and also has poorer reliability.

#### 2.2.2 Coder (MUX)

In digital data communications, the optical fiber has bandwidth much greater than most applications required. Most of the time the input to the driver is a time-division-multiplexed (TDM) version of many input bit streams. e.g. Synchronous Optical NETwork (SONET) [7]. SONET has basic transmitting rate of 51.84Mb/s. The communication lines are called OC-n where n is an integer and the lines is transmitting at a rate of n times the basic rate. e.g. OC-9 is a line transmitting at 466.56Mb/s which may be a TDM version of three OC-3 signals, each has a bit rate of 155.52Mb/s. High speed multiplexer, for time division multiplexing, with data rates in the range of 30Gb/s has been realized [8] with a record set at 34Gb/s [9].

For some application, scrambling may be required. There are many reasons for scram-

bling the signal. It can be due to security reasons which one does not want to have unauthorized access to the transmitting data. Another reason may be system requirements. Some transmitting and receiving systems require the transmitted signal to be randomized or having 50% duty cycles (no DC content). Redundant bit(s) may be incooperated into the transmitted bit stream for error detection, or control framing for demultiplexing, or control the line spectrum for clock recovery. As a result, sometimes a coder is required at the transmitter. Coding does not require high speed circuitry because it is done in low data rates before being multiplexed up. However because of the added redundancy, it lowered the effective bit rate of the transmitted data.

#### 2.2.3 Driver

The basic function of the driver for digital transmission is to provide a high current pulse to turn the light source on and off. Since there are two types of light source and they have different characteristics, two types of drivers are needed.

#### **2.2.3.1 LED Driver**

LEDs are frequently operated with a small forward bias in the "off" state to overcome the turn-on delay associated with the space-charge capacitance of the junction. To this bias, the transmitter adds a high-speed drive current of 25 to 200mA to reach the "on" state. With series resistance of a few ohms (series resistance  $r_d$  of a forward biased p-n junction), LED drive current can be provided by simply using a line-driver IC from logic family appropriate for the speed.

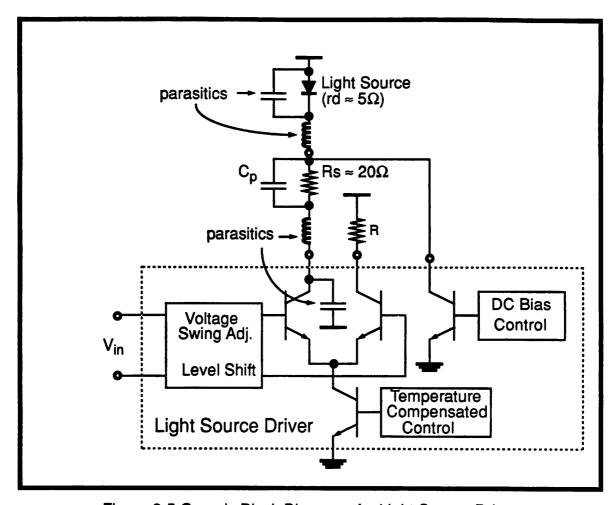

A generic block diagram is shown in Figure 2-5. An important characteristic of LEDs is that their optical outputs decrease with temperature exponentially. Therefore, to stabilize the output power, a temperature compensated control is needed to increase the driving current with rising temperature [10]. An alternative way is to stabilize the temperature of the LED is using a Peltier active-cooling device. Such a thermoelectric cooler (TEC) is usually integral to the LED package.

For high-data-rate operation with bit rate above 100Mb/s, special compensation or speed up networks are required. The problem is that a high current pulse must be generated which drives a series connection of a low-ohmic load and a relatively large parasitic inductance mainly caused

Figure 2-5 Generic Block Diagram of a Light Source Driver

by the bond-wires, which is paralleled by the output capacitance of the laser driver caused by the junction capacitance of the large output transistor. As a consequence of these facts, severe ringing may occur, which also causes large time jitter. Therefore, ringing must be reduced by appropriate circuit and transistor design and by damping the parasitic resonance circuit at the output by using additional resistors. However, these techniques degrade pulse steepness and thus reduce maximum bit rate. Therefore, as an important precondition for achieving high-data-rate operation, the parasitic inductance should be minimized. This can be overcome if the LED can be integrated with the driver on a single chip. High DC bias levels or circuits that actively remove stored charges are also used [11] to speed up the charging process. By using a very-high-speed LED and using GaAsFET as driver, operation up to Gb/s has been reported [12].

#### 2.2.3.2 Semiconductor Laser Driver

The laser driver has the same problems of a LED driver. On top of everything mentioned in Section 2.2.3.1, there is an additional problem of the lasing threshold as explained in Section 2.2.1.2.

The threshold current I<sub>th</sub> is the forward injection current at which optical gain in the laser cavity exceeds losses. Additional injected current is converted efficiently to light through the processes of stimulated emission. Once lasing occur, a lower driving current is needed for the same optical output as for the LEDs.

The turn-on time for the laser is increased dramatically when the DC biasing current used in the off-state is close to this threshold current. A bias at or above threshold also reduces overshoot and ringing associated with laser turn-on. As the DC biasing current is increased beyond the threshold, laser frequency response rises. However, this advantage is offset by reduced extinction ratio, which results in degradated sensitivity at the receiver. Therefore, the design goal is to provide bias near threshold that optimizes the turn-on characteristics for the specific application.

The major design problem is that the threshold current varies with temperature as shown in Figure 2-4. Therefore to stabilize the laser operating point with regard to both temperature and time, feedback regulation of the DC biasing current is needed. Stabilization is accomplished by monitoring the light output of the laser with a photodiode. Bias adjustment using low-frequency circuitry stabilizes the photocurrent of the monitor, hence the laser operating point [13].

As in the LED driver case, for high-data-rate operation, interactions among all circuit elements, interconnections, and packaging have to be considered. Operation up to 3Gb/s with a current swing of 30mA has been reported [14]. In the future, monolithic integration of the laser with the driver should result in highest speed performance as interconnection lead inductance severely limits laser performance.

#### 2.3 Optical Fiber

Optical fibers have become the preferred transmission medium for datacommunication because they are capable of transmitting light for long distances with high bandwidth and low attenuation. Not only this but they offer freedom from external interference, immunity from interception by external means, and inexpensive with abundant raw materials.

#### 2.3.1 Modes of Propagation

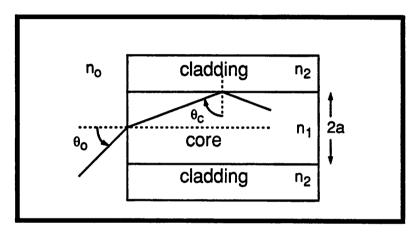

An optical fiber can be considered as a waveguide based on total internal reflection for light propagating inside the fiber. If we assume for the moment that the conditions for total internal

Figure 2-6 Numerical Aperture of a dielectric waveguide

reflection at the boundaries of the waveguide are requirements for propagation, we can consider the manner in which a lightwave must enter the guide in order to satisfy these conditions. The geometric relationships are illustrated in Figure 2-6. By applying Snell's law to the wave incident on the end of waveguide, it can be shown that total internal reflection can take place inside the guide for

$$n_o sin\theta_o \le n_1 cos\theta_c$$

(EQ 2-4)

where  $\theta_c$  is the critical angle for total internal reflection and the maximum value of  $\sin\theta_o$  that can satisfy this equation is called the numerical aperture, NA, of the waveguide. Specifying

the NA is the standard way of specifying the range of angles of incidence over which the waveguide will accept input wave. If the outside medium is air then  $n_0 = 1$  and

$$NA = (n_1^2 - n_2^2)^{\frac{1}{2}}$$

(EQ 2-5)

While the ray model gives some insight into the behavior of light in an optical fiber waveguide, this model is inadequate to give an accurate description since in practice, the radial dimension "a" of the fiber is on the order of wavelength of the light. The ray model predicts that there is a continuum of angles for which the light will bounce back and forth between core-cladding boundaries indefinitely. A more refined model using Maxwell's equations to predict the behavior of light in the waveguide, finds that in fact there are only a discrete and finite number of angles at which light zigzags indefinitely.

A set of eigenvalues can be found to satisfy the Maxwell's equations. Each eigenvalue defines a "mode" that will, if excited, be sustained in the waveguide. Also, there is a cut-off frequency at which there will be no solution. This cut-off frequency can be used to decide how many modes can propagate in the fiber. The normalized cutoff frequency is

$$V = 2\pi \frac{a}{\lambda} (n_1^2 - n_2^2)^{\frac{1}{2}} = 2\pi \frac{a}{\lambda} (NA)$$

(EQ 2-6)

where V is the normalized cutoff frequency, a is the diameter for the core and  $\lambda$  is the wavelength of the propagating light. As the radius of the core is reduced, V is reduced and fewer and fewer modes are accommodated. It can be shown that for V < 2.405, there can only be one single mode for propagation. Based on this, optical fibers can generally be classified as single-mode fiber where only one mode is allowed to propagate, and multi-mode fibers where more than one mode is allowed to propagate.

#### 2.3.2 Attenuation and Dispersion

The bandwidth or bit rate which can be transmitted through an optical fiber for a given length is basically limited by two major factors, the attenuation of the signal inside the fiber and the dispersion of the signal. With high-data-rate in the range of Gb/s, the maximum distance without

repeater is limited by dispersion and for low data rate below Gb/s, the maximum distance is basically limited by attenuation [15].

#### 2.3.2.1 Attenuation

Attenuation in the optical fiber is the loss in signal power that inevitably results as light travels down an optical waveguide. There are four major sources of attenuation - scattering of light by inherent inhomogeneities in the molecular structure of the glass crystal, absorption of the light by impurities in the crystal, losses in connectors, and losses introduced by bending of fiber. Generally these losses are affected by the wavelength of the light, which affects the distribution of power between core and cladding as well as scattering and absorption mechanisms. The effect of these attenuation mechanism is that the signal power loss in dB is proportional to the length of the fiber.

#### 2.3.2.2 Dispersion

Dispersion is the difference in time of arrival of the signal resulting in a form of distortion. It limits the rate at which data can be transmitted through the medium. Dispersion in optical fiber can be related to the frequency dependence of the index of refraction. This implies the velocity of propagation is a function of frequency. Dispersion can arise from three major sources, material dispersion, waveguide dispersion and modal dispersion. Material dispersion results when the dielectric constant, and therefore the index of reflection is a function of frequency. Waveguide dispersion results when the propagation constants for the waveguide are functions of frequency. For multimode fibers, modal dispersion results because each mode will have a characteristic group velocity and corresponding propagation delay. The modal dispersion is the difference between the longest and shortest propagation delay.

#### 2.3.3 Single-Mode Fibers

#### 2.3.3.1 Single-Mode vs Multimode

The first low-loss fibers fabricated by Corning Glass Works in 1970 were single-mode (SM) fibers, since the transmission characteristics of such fibers were expected to be best suited

for datacommunication. However, to get a single mode fiber, the normalized cutoff frequency V must be smaller than 2.405 which implies a small fiber radius a and small difference in the reflective index  $\Delta n = n_1 - n_2$ . This makes the fiber more difficult to manufacture and it also make the numerical aperture NA small and coupling lightwaves into the fiber more difficult. As a result, in the early stage, development efforts were first concentrated on large-core multimode (MM) fibers.

With the development of semiconductor light sources and the growing demand of longer distance, wider bandwidth transmission, SM fibers was reintroduced and have become the most widely used optical transmission medium in datacommunication, their major advantage over MM fibers is the absence of modal dispersion and modal noise, making it the lowest cost, largest bandwidth transmission medium available. MM fibers are only used in short distance applications these days.

Important design considerations for SM fibers are low transmission loss, suitable dispersion characteristics, low splice loss, and low bending loss.

#### 2.3.3.2 Dispersion in SM Fibers

In SM fibers, modal dispersion is eliminated. The two other types of dispersion remains are the material dispersion and waveguide dispersion. The total dispersion can be approximated by [16]

$$D_{T} = \frac{\Delta \tau}{L \times \Delta \lambda} = D_{M} + D_{W}$$

$$D_{M} = \frac{1}{c} \cdot \frac{dN_{2}}{d\lambda}$$

(EQ 2-7)

$$D_{W} = -\frac{N_{1} - N_{2}}{\lambda c} \left[ V \cdot \frac{d^{2}}{dV^{2}} (Vb) \right] = -\frac{1.984 N_{2}}{(2\pi a)^{2} 2 cn_{2}^{2}} \lambda$$

Where  $D_M$  is the material dispersion and  $D_W$  is the waveguide dispersion.  $n_2$  is the reflective index, and  $N_2$  is the group reflective index of the cladding material defined by  $c/V_g$ ; c is the speed of light and Vg is the group velocity of the light pulse;  $\lambda$  is the wavelength used, V is the normalized cutoff velocity, a is the radius of the core and b is the normalized propagation constant.

Multiplying D<sub>T</sub> by the distance travelled and the width of the light pulse, the spread in time can be calculated.

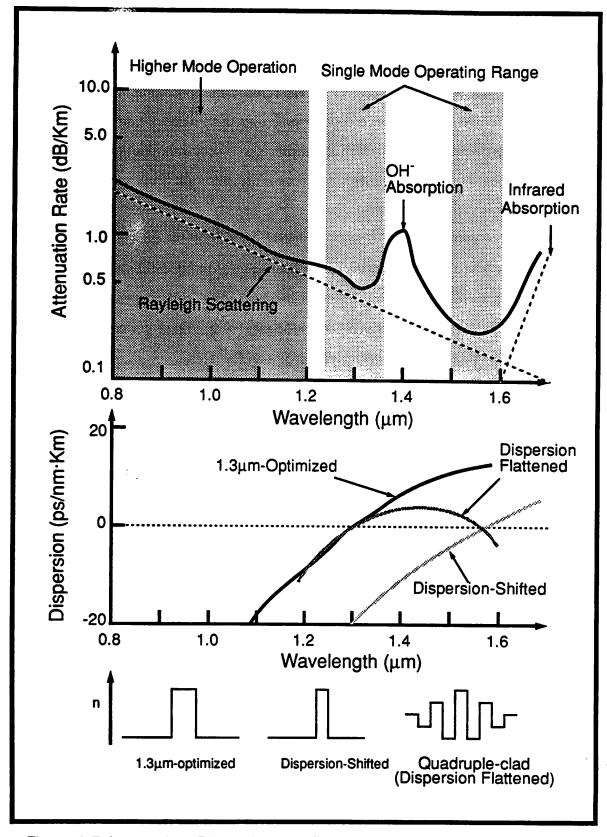

The important result from (EQ 2-7) is that the waveguide dispersion is of opposite sign of the material dispersion. As a result, by adjusting the fiber core radius a, the material dispersion can be controlled to give a null at a desired wavelength. A further refinement in the design of SM fibers is the use of more complex index profiles. One possible design is the quadruple-clad step index profile. By using such profiles, it is possible to achieve relatively low total dispersion over a wide range of wavelengths and there can be two wavelengths of zero total dispersion. The profiles and dispersion characteristics of these SM fibers are shown in Figure 2-7.

#### 2.3.3.3 Attenuation in SM Fibers

Attenuation in state-of-the-art SM fibers is primarily caused by two fundamental physical phenomena that establish a lower limit to the fiber attenuation. In the short wavelength end of the range, the limit is due to the intrinsic Rayleigh scattering of the doped fused silica, which decreases with the inverse of 4th power of wavelength. The lower limit on attenuation at the longer wavelength is determined by atomic absorption. For wavelength longer than 1.6µm, the absorption is due to the intrinsic infrared tail of the Si-O and/or Ge-O vibrations.

Excess loss caused by waveguide imperfections and metallic impurities are negligible even in today's mass-produced fibers made by any of the commonly-used preform fabrication techniques and minimum losses can be obtained at a wavelength of 1.55µm. An additional peak of loss at 1.38µm is due to the Hydroxyl ion (OH¹) absorption and can be practically minimized through suitable dehydration of the preform and limited to below 2dB/Km. The range of spectral losses is shown in Figure 2-7.

In addition to the fundamental limits on scattering and absorption losses, there are other practical factors that can introduce additional losses such as micro-bending losses, splicing losses, and connecting losses. However these can be kept small as evident from Figure 2-7.

Figure 2-7 Attenuation, Dispersion, and Reflective Index Profiles of SM Fibers

#### 2.3.4 Erbium-Doped Fiber Amplifiers (EDFAs)

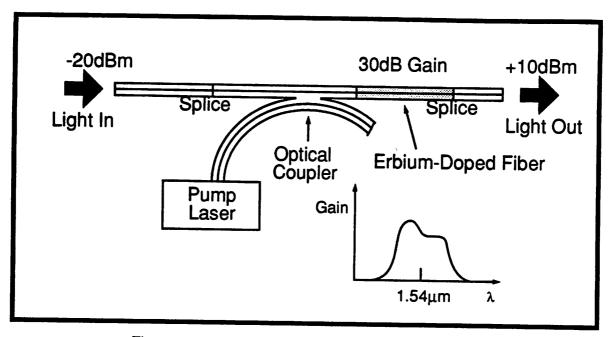

Coherent lightwave techniques can be used to construct long-distance digital transmission systems without regenerative repeaters. Instead of repeaters, optical amplifiers are placed at intervals along the fiber, much as conventional amplifiers are used in analog coaxial-cable systems. The difference between regeneration and amplification is not merely one of nomenclature. A regenerative repeater as currently implemented requires optoelectronic devices for source and detector, as well as substantial circuitry for pulse slicing, retiming and reshaping. The optical amplifier, on the other hand, is in principle much simpler; it is a single component that delivers at its output a linearly amplified replica of the optical input signal. In additional to simplicity, the advantage to this approach is flexibility. The same amplifier can be used for any modulation scheme at any bit rate. Indeed, if the amplifier is sufficiently linear, a single device can simultaneously amplify several signals at different wavelengths and bit rates.

There are two promising approaches to optical amplification: semiconductor amplifiers, which utilize stimulated emission from injected carriers [17] [18], and fiber amplifiers, in which gain is provided by stimulated Raman or Brillouin scattering of fiber dopants [19] [20]. The semiconductor optical amplifiers have the advantages of smaller size and lower power consumption due to direct injection pumping. However, they are sensitive to polarization and have a large connection loss when connected to transmission fibers. As a result, they are mostly suitable for use when combined with optical integrated circuits and optoelectronic integrated circuits. On the other hand, fiber amplifiers are directly connected to the transmission fiber and connection loss is small. Although there are many attractions to using Raman gain mechanism, high pump power is required and the pump and signal polarization have to be aligned for higher efficiency. The Erbium-doped fiber amplifiers (EDFAs), on the other hand, have the extra advantage of polarization insensitive and low power level of the pump power. As a result, EDFAs will be the choice as optical amplifiers for future all-optical networks.

An EDFA mainly consists of an Erbium-doped fiber (EDF), an optical coupler, and a pump light source. There are three basic configurations of EDFA, classified mainly by their pump light propagation direction. Forward pumping gives the best noise performance and is shown in

Figure 2-8. The type of EDFA used depends on the applications.

Figure 2-8 Forward Pumped EDFA Configuration

#### 2.4 Receiver

The purpose of an optical receiver is to convert a modulated optical signal to an electrical signal and to recover from electrical signal whatever information had been impressed on the optical carrier. This information may be digital or analog, and the optical carrier may be modulated in a variety of ways, including amplitude modulation (AM), frequency modulation (FM), and phase modulation(PM). However, because a simple optical detector implemented by either PIN diode or avalanche photodiode (APD) is an ideal AM envelop detector, but is insensitive to phase or to small changes in wavelength, it is amplitude modulation that is used extensively in present optical communication systems. Frequency and phase modulation are being investigated in many laboratories for use in coherent optical transmission [21] but in this thesis, we will concern with the conventional approach of amplitude-modulated optical signals and the design of appropriate direct-detection receivers.

Analog transmission is not commonly used in optical systems because of the non-linear characteristics of optical sources (laser and LEDs). Digital modulation, also known as on-off key-

ing, is easily accomplished with these sources by modulation of bias current as explained in Section 2.2.1. The simplicity of modulation plus the extremely wide bandwidth of optical fibers have made binary digital transmission the method of choice for the majority of optical communications systems. A direct detection digital transmission consists of a steam of light pulses, where the presence of a pulse corresponds to the transmission of a binary "1", and the absence of light corresponds to the transmission of a binary "0".

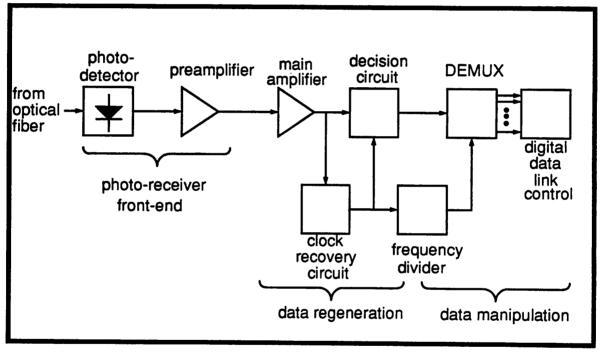

Shown in Figure 2-1 is a block diagram of a basic datacommunication receiver. First, there is a photodetector and a low-noise preamplifier that converts the input photon into photo-current, and subsequently into a low level voltage. These two blocks form the front-end for the receiver and is sometimes called collectively as a photoreceiver. It is then followed by a main amplifier that serves several purposes - equalization of roll-off in the front end (not always necessary), low pass filtering to limit the noise bandwidth to the minimum required, and high gain amplification with limiting amplifier or automatic-gain-control (AGC) amplifier. For optimal performance, it is necessary to extract timing information from the received signal in order to synchronize the process of making decision on the noisy main amplifier output. For this purpose, the output of the main amplifier is also fed to a clock recovery circuit that generates a clock signal at the baud rate synchronized with transitions in the received data. The decision circuit then use this timing information to compare the input with a fixed threshold level set to the center of the received eye pattern to give an equal probability of error for decisions on both 1's and 0's. Once the digital data is regenerated from the analog waveform, the high-data-rate bit stream is then deserialized back to it's parallel form by a demultiplexer, and passed to a digital data link control for high level manipulation of data received.

For most lightwave communication systems, the receiving function limits the maximum data rates for transmission. The optical fiber itself has a wide bandwidth, larger than 40GHz, larger than any electronic components can handle. The transmitters using high speed technology and semiconductor lasers can operate above 10 Gb/s. The digital blocks of the receiver, such as the demultiplexers and decision circuits, can also operate above 10Gb/s, but the analog blocks such as the low noise preamplifier, main amplifier, and clock recovery circuit, todate, still cannot break

through the 10Gb/s barrier even with the fastest technology available.

High-data-rate receiver design is the main topic in this thesis and will be discussed with more detail in Chapter 3.

### 2.5 Probability of Error and Quantum Limit

If one consider an ideal photodetector followed by a noiseless electronic amplifier, it is possible to derive the minimum received optical power required for acceptable bit-error-rate (BER) performance in a digital transmission system. This minimum received power level, known as the quantum limit, is a result of the statistically random nature of light absorption in a material medium. The probability of receiving exactly n photons during a pulse interval T, when the average number of photons received during this interval is N, is given by a Poisson distribution P[n]

$$p[n] = \frac{N^n e^{-N}}{n!}$$

(EQ 2-8)

The probability of making an error can be expressed as

$$p[error] = p[error|1]p[1] + p[error|0]p[0]$$

(EQ 2-9)

When "0" is transmitted, no photon will be received and the decision will be made with probability of error equals to zero. When "1" is transmitted, even though the average number of photon transmitted is N, there is a finite probability that none will be received, causing an error. If we assume there is an equal probability of transmitting a "1" and a "0", then the probability of error is  $p[error] = p[n=0] \cdot 1/2 + 0 \cdot 1/2 = 1/2e^{\cdot N}$ . For a BER of  $10^{-9}$ , N = 20. This implies an average of 10 photons per bit is the quantum limit provided everythings are perfect.

Although the quantum limit is of interest as a basis for evaluating the performance of specific systems, it is not a realistic measure of the sensitivity of such systems. Two assumptions are unrealistic; the first one is that when no signal is transmitted, the output of the detector will be zero, and the second assumption that when a signal is transmitted, the only output is due to signal photons from the transmitter. The major source of violation comes from the fact that there is noise both

with the photodetector and the amplifier following it.

Noise is characterized with a Gaussian probability density function

$$p(x) = \frac{1}{\sigma\sqrt{2\pi}} exp\left[-\frac{1}{2}\left(\frac{x-\mu}{\sigma}\right)^{2}\right]$$

(EQ 2-10)

where  $\boldsymbol{\mu}$  is the mean and  $\boldsymbol{\sigma}$  the rms deviation from the mean value.

For pulse code modulation, a binary "1" would be represented by a signal voltage of mean value  $V_0$  and a binary "0" by zero volt. In each case, noise will cause a rms deviation from the signal voltage of  $\sigma$  volts. If the threshold is placed at  $V_0/2$ , and let

$$Q(x) = P[X > x] = \int_{x}^{\infty} p(x) dx$$

(EQ 2-11)

where X follows a standard normal distribution with  $\mu=0$  and  $\sigma=1$ . Assuming the probability of receiving a "1" is the same as receiving a "0", and the noise mechanism is the same in both cases, the probability of error can be calculated from (EQ 2-9) to be

$$Q\left(\frac{V_o}{2\sigma}\right) = Q\left(\frac{\sqrt{SNR}}{2}\right)$$

(EQ 2-12)

For a BER of  $10^{-9}$ ,  $V_o = 12\sigma$ , or a signal-to-noise (SNR) ratio of 21.6dB; for a BER of  $10^{-11}$ , a SNR of 22.5dB is needed. For high BER or high SNR, Q(x) can be approximated by

$$Q(x) \approx \frac{1}{\sqrt{2\pi}x} e^{-\frac{x^2}{2}}$$

(EQ 2-13)

On a log plot of the BER vs the input Voltage, the input referred SNR can be calculated from the slope of the curve. If two such curves are measured with different  $(x-\mu)$ 's, then the magnitude of the rms deviation, or the rms noise, can also be calculated.

# **Chapter 3 Traditional Receiver Architecture**

#### 3.1 Introduction

The traditional architecture of an optical fiber receiver is shown in Figure 3-1. It can be

Figure 3-1 Traditional Architecture for Digital Fiber Optic Receivers

basically divided into a photoreceiver front-end and a data regeneration and manipulation backend. This chapter will look into each functional block in more detail and identify the performance limits.

### 3.2 Photo-Detectors (PDs)

The function of the photodetector is to convert the normally weak optical signal into a corresponding weak electrical signal. Subsequent stages in the receiver provide amplification and signal processing.

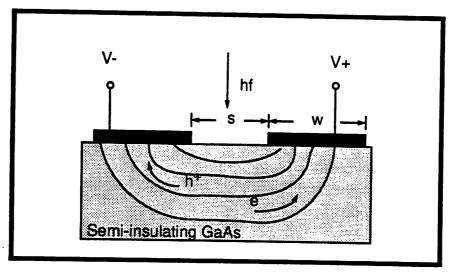

There are quite a variety of photodetectors such as PIN photodiodes, avalanche photodiodes (APDs), Metal-Semiconductor-Metal (MSM) photodiodes, phototransistors, photoconductors. However only PINs and APDs will be described in detail herein, as they have demonstrated the best characteristics over the photoresistors and photoconductors for datacommunication applications, and MSM detectors are only used in integrated optoreceivers.

#### 3.2.1 Semiconductor Photodiodes

Both PINs and APDs are semiconductor photodiodes. As an electromagnetic wave propagate through a semiconductor, the wave may deliver enough energy to a valence electron to free it from the covalent bond that holds it in its place in the crystal structure. When this occurs, an electron-hole pair is created and a photon is removed from the wave. The electron that has been excited into the conduction band and the hole in the valence band are now free to move under the influence of an electric field. If an electric field is present in the region where electron hole pairs have been created, the electron and the hole are accelerated in opposite directions and are swept out of the region. This motion of charges in the semiconductor induces a current that can be detected in the external circuit. The charges released by the incident photons are called photocarriers. The external current due to the motion of these charges is the photocurrent.

### 3.2.2 Responsivity and Quantum Efficiency

The responsivity of a photodiode R is defined as the output photocurrent produced per unit of incident optical power. An incident optical power of P with frequency f is equivalent to P/hf photons per second, where h is the Planck's constant. Let  $\eta$  be the ratio of the average number of electrons excited into the conduction band to the number of incident photons. The average number of electrons per second, or the photocurrent will then be

$$I_{p} = q \eta \frac{P}{hf}$$

(EQ 3-1)

and the responsivity is

$$R = \frac{I_p}{P} = \frac{q\eta}{hf} = \frac{\eta\lambda}{1.24} \qquad (\lambda \text{ in } \mu\text{m})$$

(EQ 3-2)

The term  $\eta$  is the quantum efficiency of the photodiode. Its value is less than unity and is determined by both the properties of the semiconductor material(s) and the physical structure of the device. It can be expressed as

$$\eta = (1 - r) (e^{-\alpha d}) (1 - e^{-\alpha_p W})$$

(EQ 3-3)

The first term is due to the reflection loss from the front surface of the photodiode, the optical power that passes through the front surface and into the photodetector is then (1-r)P. The second term is due to the absorption loss of the input optical power when it gets through the region of length d where no electrical field exists. Charges produced will recombine back without any significant effect on the photocurrent. The wave then enters the high field depletion region of width W where the usual absorption takes place. The attenuation in this region is represented by the third term. The first two terms are due to the physical structure of the device and can be design to make r small for low reflection loss and d small for low absorption loss. The third term is both structure dependent and material dependent. W can be made large but then it takes more time for the carriers to be swept through this region, so there will be a speed vs gain trade-off as usual.  $\alpha$  and  $\alpha_p$  are essentially the same, it is determined by the bandgap energy of the material(s) used.

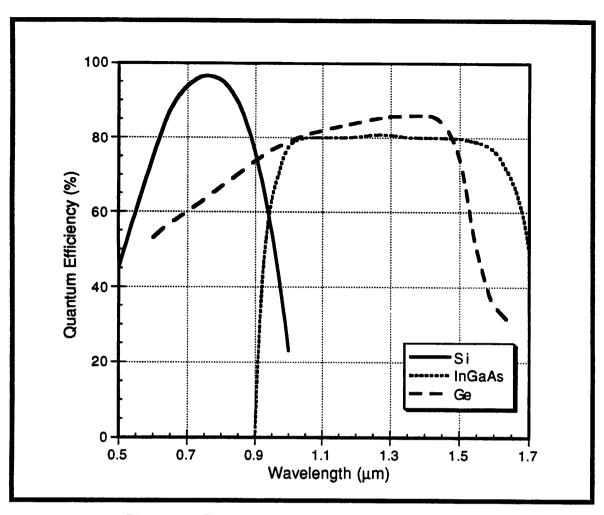

Some typical photodiode spectral response is shown in Figure 3-2. Silicon is the material most commonly used in photodiodes for wavelength shorter than 1µm. It is not used for 1.3µm and 1.55µm wavelengths because the bandgap energy of Silicon is too large for these long wavelength spectral regions. From Figure 3-2, it appears that Germanium and compound semiconductors such as InGaAs should be useful in longer wavelengths.

Figure 3-2 Typical Photodiode Spectral Response

#### 3.2.3 PIN Photodiode

The most commonly used semiconductor photodetector in long wavelength optical communication systems is the PIN photodiode. The P-I-N photodiode is a p-n junction structure with a very lightly doped "intrinsic" region between the normal p and n type regions. The normal mode of operation of the PIN photodiode is by applying a reverse biased voltage, the intrinsic region is completely depleted, thus establishing a high electric field region with no free carrier. This minimizes the dark current flow in the absence of light. The dark current in a PIN photodiode is typically in the range of 10nA. With state-of-the-art design, the lowest dark current reported is below 0.1nA [22].

To maximize the quantum efficiency and hence responsivity, photon absorption in the

depletion region should be maximized, and minimized elsewhere. From (EQ 3-3), this can be done by increasing the width W of the depleted intrinsic region, and by using a material with large absorption coefficient  $\alpha_p$ , However, if  $\alpha$  is approximate the same as  $\alpha_p$ , loss will increase before the optical wave reaches the intrinsic region.  $\alpha$  can be made smaller than  $\alpha_p$  by applying a heterostructure similar to those used in the light sources. If the material through which the optical wave enters the device can be selected to have a bandgap larger than hf, it will not absorb energy from the wave as it passes through this section of the photodiode. Absorption is thus confined to the region where it is effective in producing photocarriers. With such design, quantum efficiency as high as 0.95 can be achieved with InGaAs PIN photodiodes, making it the most frequently used device for long wavelength communication systems.

The rate at which the photodiode can respond to changes in the intensity of the optical input signal is a measure of the maximum information rate or bandwidth of the photodetector. The ultimate bandwidth of the device is limited by the carrier transit time, the carrier diffusion time, and the hole trapping at heterojunction interfaces; with the carrier transit time being the dominating factor. The transit time of the PIN photodiode is limited by the high-field, saturated carrier velocity of the slowest carrier. The bandwidth of efficient InGaAs PIN diodes has been found to be greater than 20GHz [22] with a quantum efficiency of 0.8. If the intrinsic region's width W is allowed to be narrow, frequency responds as high as 67GHz has been reported [23]; although at these width, a significant loss in quantum efficiency is expected.

In practise, because of the wide bandwidth of the PIN photodiode, the detector's bandwidth is limited by the extrinsic RC time constant, where R is the effective resistance of the external bias circuit, and C is the photodiode capacitance. The photodiode capacitance depends on the area of the photodiode, typically in the range of 0.5pF. When the area of the photodiode is small, typically below 40µm in junction diameter, the bandwidth is limited by the transit time, and for larger diameters, it is limited by the extrinsic RC delay. There are several techniques to reduce the parasitics at the interface of the photodetector and the amplifier. One approach is to use microwave design to compensate for the parasitics [24], bandwidth of 16GHz is achievable. Another approach to integrated design is to fabricate the device elements at the closest distance possible

so that the introduction of any parasitic reactances is minimized. Monolithic integration of optoelectronic integrated circuits (OEICs) is an attractive prospect, and recent advances have shown

encouraging receiver sensitivity improvement. It will be discussed later in Section 3.4. While

OEICs will become increasingly important, the fabrication technology of OEICs has not grown

quick enough to bear many practical applications, primarily due to the necessity of integrating

highly different devices on one chip. For near future applications of integrated receivers, a more

practical approach can be found in flip-chip integration, in which two existing elements are joined

directly by bonding. A bandwidth of 21GHz is achievable using this technique [22].

The generation of photocurrent is a sequence of discrete events that includes the creation of electron hold pairs and the motion of these charges under the influence of local electric field. Each electron hole pair will result in a pulse of current. The total current is the sum of many pulses. The total current is not a smooth continuous flow but has variation about an average value. This variation is the "shot" noise of the photodiode. The mean-squared value of the shot noise associated with the photocurrent is

$$\overline{i_n^2} = 2qIB (EQ 3-4)$$

where I is the total photocurrent and B is the equivalent noise bandwidth.

### 3.2.4 Avalanche Photodiode (APD)

The photocurrents produced in the photodiode of optical communication receivers are usually very small. Amplification of these weak electrical signals is necessary before useful signal levels are established. One approach to amplify the signal is the use of an avalanche phenomenon to provide current amplification within the photodiode. The device that provides this current amplification is the avalanche photodiode (APD).

APDs are similar to PIN photodiodes in that they are operated under reverse bias, and therefore in the absence of large background dark currents. Unlike PIN photodiodes, APDs are operated at sufficient high reverse voltage such that photocurrent gain due to impact ionization of carriers with the lattice atoms occurs. Detail studies of the avalanche mechanism can be found

in [25]. The important result is that a current gain factor M, which is a function of the applied reversed voltage, results from the avalanche mechanism, thus, improving the responsivity of an APD by M times over the PIN photodetectors. Most long-distance high-data-rate lightwave transmission systems operating near 1.3µm or 1.55µm have utilized InP/InGaAsP/InGaAs APDs in the front-ends of the receiver because of the excess gain factor M.

The bandwidth of APDs is limited by the carrier transit time, hole trapping at the heterojunction interface, and extrinsic RC time constant just as in the PIN photodiodes. As a result, for

low gain setting, the bandwidth is constant just as a PIN photodiode. At high gain setting, the avalanche build-up time dominates. The bandwidth decreases proportionately with increasing gain M,

resulting in a constant gain-bandwidth (GBW) product. A GBW product as high as 70GHz has

been reported in [26] though the constant bandwidth at low gain setting is only 8GHz due to a

higher carrier transit time because more layers are required than for the PIN photodiodes.

The avalanche current-multiplication process is a random process in that M is only the average, but not absolutely fixed multiplication factor. The number of secondary electrons and holes that results from any individual injected electron or hole may differ from this average value M. The multiplication process has its own fluctuations that are superimposed on any fluctuations inherent in the primary photocurrent. The excess noise is usually represented by an excess noise factor F which in itself a function of M. The mean-squared total noise current is therefore

$$\frac{\overline{i_n^2}}{i_n^2} = 2qI_{ph}FM^2B$$

(EQ 3-5)

where  $I_{ph}$  is the primary photocurrent without multiplying by M. It was shown in [27] that the excess noise factor can be expressed by

$$F = kM + (1 - k) (2 - \frac{1}{M})$$

(EQ 3-6)

where k is the carrier ionization ratio. Note that F increases with increasing k as the randomness increases with higher ionization ratio. As expected, when k=0 and M=1, F=1 and the equation degenerates to be the same as that of the PIN photodiode.

### 3.2.5 Photodiode Equivalent Circuit

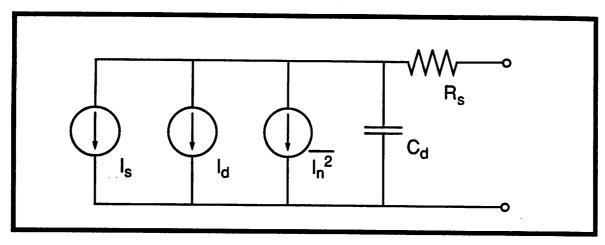

Figure 3-3 shows an AC equivalent circuit for both the PIN photodiodes and APDs. The

Figure 3-3 AC Equivalent Circuit of Photodiode

current source  $I_s$  represents photocurrent resulting from the detection of an optical signal.  $I_d$  is the background dark current that flows with no input signals.  $I_n^2$  is the shot noise current of the photodiode.

$$I_{d} = I_{du} + MI_{dm}$$

(EQ 3-7)

$$I_n^2 = 2q[I_{du} + M^2F(M)I_{dm}]B$$

(EQ 3-8)

The back ground dark noise has two components, one is the unmultiplied dark current  $I_{du}$  and the other one is the multiplied dark current  $I_{dm}$  multiplied by the avalanche gain M. For a PIN diode, M is simply one. The shot noise term also has two components, one is due to the unmultiplied dark current and the other is due to the avalanche gain M. Because of the randomness of the multiplication process for APDs, there's an extra excess noise factor F which is a function of M that has to be multiplied with  $M^2$  to get the variance in the multiplication gain factor M. For a PIN diode, M = 1 and F(M) = 1 indicating that as expected, there is no excess noise.  $C_d$  is the parasitic nonlinear junction capacitance of the p-n junction and  $R_s$  is the series resistance which is usually very small (5-10 $\Omega$ ) and can be neglected in most cases.  $C_d$  depends on the size of the photodiode and

### 3.2.6 PIN Photodiodes vs APDs

A comparison of PIN photodiodes against APDs is listed in Table 3-1. While PIN diodes

| Photo-<br>diodes | Advantages                                                                                          | Disadvantages                                                                                                                                                                                                     |

|------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN              | Simple to Use<br>Low Cost<br>High Speed<br>Reliable                                                 | Low Receiver Sensitivity Low Receiver Dynamic Range                                                                                                                                                               |

| APD              | Higher Sensitivity (5 to 15 dB<br>better than PIN)<br>Wider Dynamic Range<br>through Gain Variation | Gain Characteristic is Temperature Sensitive Requires High Voltage Power Supply Higher Cost Dark Current and Excess Noise of Long Wave- length APDs are still High, Limiting Their Useful- ness at Low Bit Rates. |

Table 3-1 Comparison of PIN Photodiodes Vs APDs

have all the advantages of a low power and low cost solution for a high speed photodetector, the only draw back is that it has a limited dynamic range and most of all, low sensitivity. However, with the advances made in both fiber and semiconductor optical amplifiers as mentioned in Section 2.3.4, there is a trend of replacing APDs with a combination of optical amplifiers and PIN photodiodes because of the lack of excess noise. This approach is even more attractive fueled by the integration of optical detector and amplifiers such as those in OEICs, as it is much more complicated to integrate an APD as compared to integrating a PIN photodiode. As a result, the future solution will be an optical amplifier, such as Erbium-doped fiber, followed by an OEIC with a PIN photodiode.

### 3.3 Low Noise Preamplifier

The preamplifier acts as an interface between the photodetector and conventional electronics. Once the signal is converted from the optical domain into the electrical domain, in the form of a low level photocurrent, a low noise preamplifier is needed to bring the signal and noise amplitudes to a level where the noise produced in subsequent stages has a negligible effect on the overall signal-to-noise ratio. As a result, the preamplifier and photodetector have to be considered together to evaluate the performance and this combination is known as an optical receiver. The primary performance parameters that determines the usefulness of an optical receiver is the sensitivity, bandwidth, dynamic range, and the interface to the remaining electronics.

The preamplifiers can be classified into three broad categories, based on the equivalent resistance seen by the photodetector. They are the low-impedance, high impedance, and transimpedance preamplifier.

### 3.3.1 Low-impedance Preamplifier

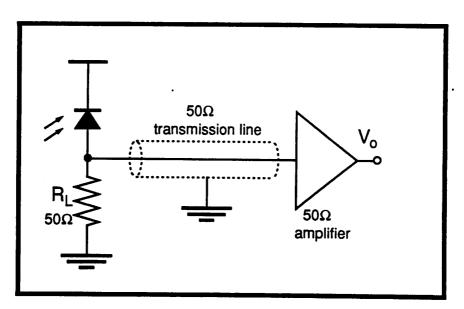

Low-impedance preamplifiers typically consists of a photodiode operating into a low-impedance amplifier, often through a length of coaxial cable or other transmission line. A terminating resister R<sub>L</sub> equal to the transmission line impedance is generally included to suppress standing waves for uniform frequency response. A typical low-impedance preamplifier is shown in Figure 3-4.

Figure 3-4 Low-impedance Preamplifier

The first advantage of the low-impedance preamplifier is that it is simple, commercially available  $50\Omega$  RF amplifier can be used. The second advantage is that it has a wide bandwidth as

the RC time constant is extremely low due to a low load resistance. It also has a wide dynamic range as the signal to the preamplifier input is a a very low level. However, the disadvantage is also due to the low load resistance. The noise of the low-impedance amplifier is dominating by the thermal noise of the low resistance

$$\overline{i_n^2} = \frac{4kTFB}{R_1}$$

(EQ 3-9)

where F is the noise figure of the amplifier and B is the equivalent bandwidth. The sensitivity is degraded heavily because of the low load resistance. As a result, it is only useful in application such as instrumentation where sensitivity is not a major concern.

### 3.3.2 High-impedance Preamplifier

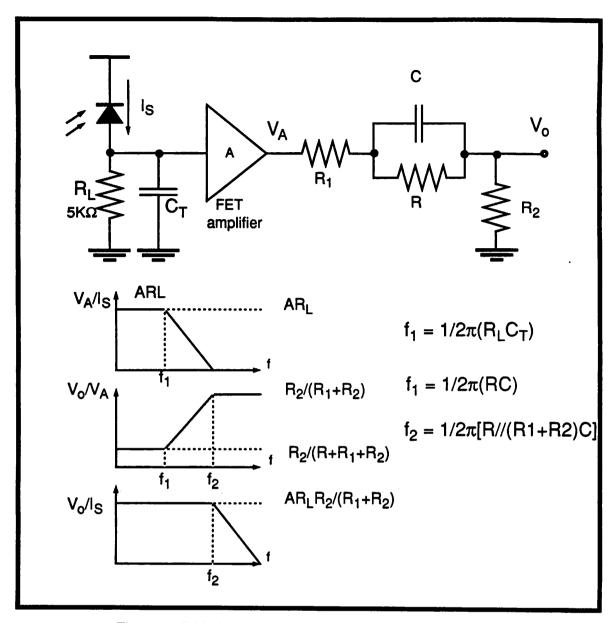

Because of current source nature of photodiodes, it is possible to increase signal voltage for a given photocurrent by operating the photodiode into an amplifier with higher input resistance. The signal voltage is therefore increased prior to the addition of noise from the following preamplifier, resulting in improved sensitivity. In a high-impedance preamplifier, as shown in Figure 3-5, the load resistance  $R_L$  is large ( $\sim$ 5K $\Omega$ ) and a high-impedance field-effect transistor (FET) amplifier is employed. The total input capacitance  $C_T$  is the sum of FET input capacitance, detector capacitance, and stray capacitance. As a result of large input RC time constant, the preamplifier bandwidth is small and acts like an integrator for high frequency input. Such integrating front-ends require equalization to compensate for their lack of bandwidth. Equalization is commonly provided by a simple RC circuit that also shown in Figure 3-5. The transfer function of the equalizer has a zero at  $f_1$  and a pole at  $f_2$ . The value of R and C are chosen such that the zero at  $f_1$  cancels the pole of the high-impedance preamplifier, and the overall receiver bandwidth is extended to  $f_2$ .

The biggest advantage of the high-impedance preamplifier is that it has the highest sensitivity as it has the best power transfer efficiency from the photodiode. Neglecting noise from the preamplifier and shot noise of the photodiode, the SNR can be expressed as

$$SNR = \frac{(I_s R_L)^2}{\frac{4kTB}{R_L} \times R_L^2} = \frac{I_s^2 R_L}{4kTB}$$

(EQ 3-10)

Figure 3-5 High-impedance preamplifier and Equalizer

The SNR increases with increasing  $R_L$ . It is ultimately limited by the input impedance of the preamplifier.

The disadvantages of the high-impedance amplifier are the need of an equalizer that increases the design complexity as it is hard to match the zero of the equalizer to the pole of the front-end; also, because of the front-end enhances the amplitude of low frequency signals at the preamplifier input, early saturation of the preamplifier may occur. As a result, the high-impedance preamplifier only has a limited dynamic range.

For practical implementations, the amplifier used does not have infinite frequency respond and contributes significant amount of noise that has to be taken into consideration. Wide-band amplifiers are generally based on a cascaded amplifier configuration using mismatched interstage resistive load coupling [28]. The interstage load resistances are shunted by the parasitic capacitances of the FETs, giving rise to additional RC integrations which restricts the frequency response of the receiver. In the conventional design, receiver bandwidth can only be extended at the expense of receiver gain and signal-to-noise performance. To overcome this problem, interstage microwave matching networks and series inductive peaking between the photodiode and preamplifier are used [29] [24]. Applying the above technique, a 16GHz optical receiver, operating at 11Gb/s, with -19.8dBm sensitivity results. It was fabricated as a hybrid integrated circuit, with a high speed InGaAs p-i-n photodiode coupled to a three stage GaAs HEMT preamplifier.

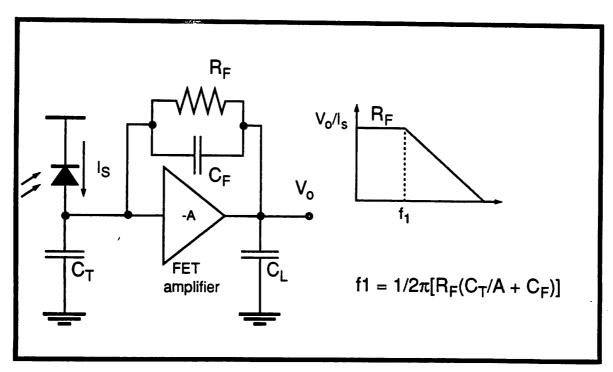

## 3.3.3 Transimpedance Preamplifier

A configuration that provides improved dynamic range is the transimpedance front end as shown in Figure 3-6. The load resister is connected as a feedback resister around an inverting

Figure 3-6 Transimpedance Preamplifier

amplifier with gain A. The bandwidth of the preamplifier is increased roughly by the factor A compared with a high-impedance preamplifier with the same load resistance and input capacitance. As a result, there is no need for equalization in general. The dynamic range is improved because of the flat response with no low frequency signal enhancement.

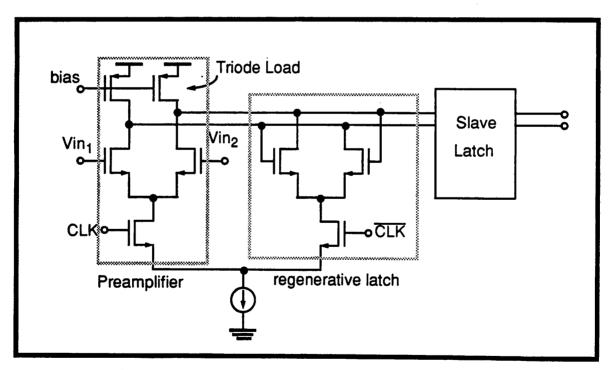

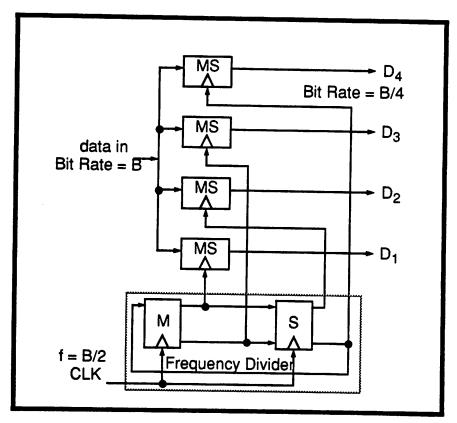

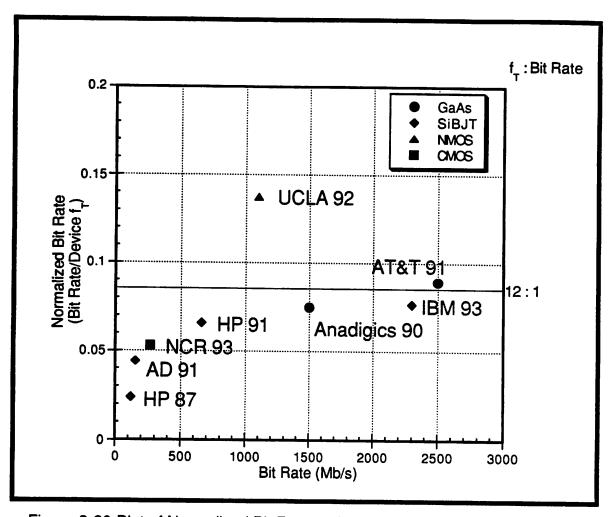

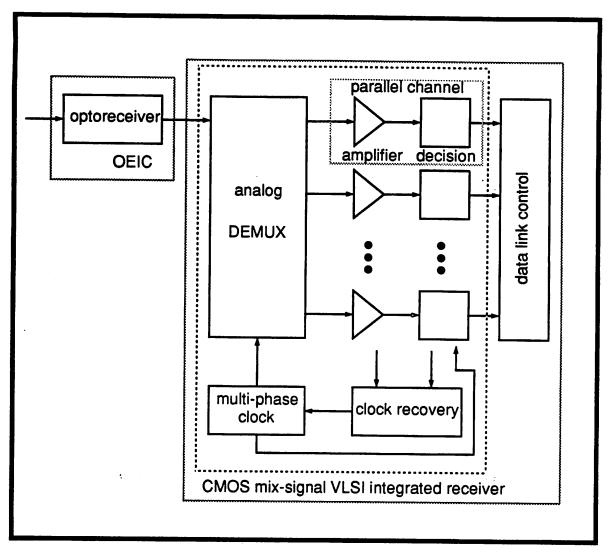

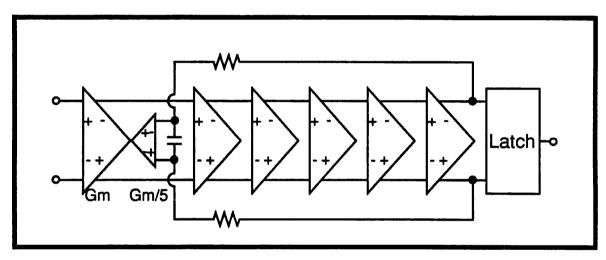

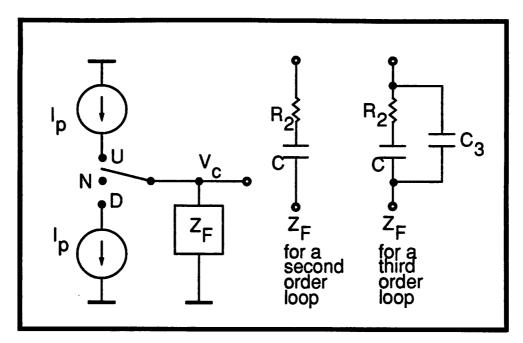

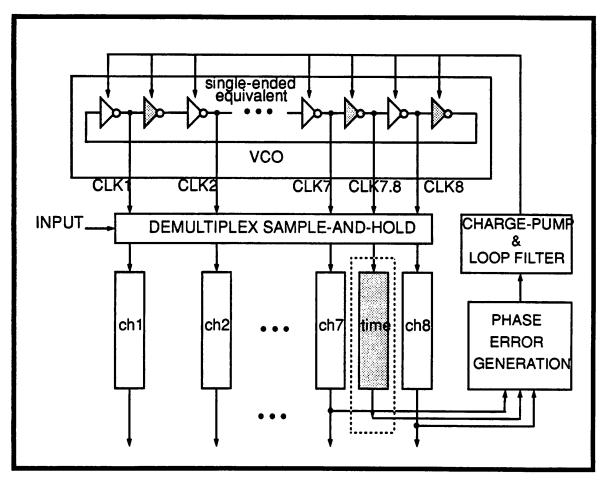

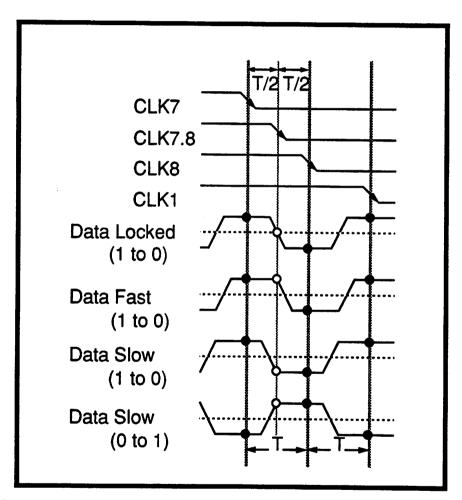

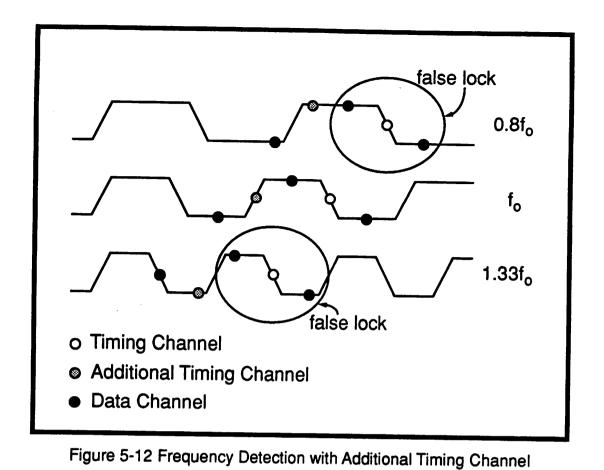

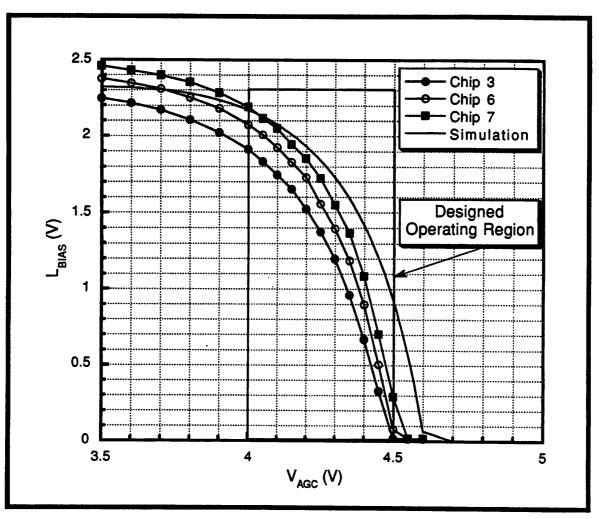

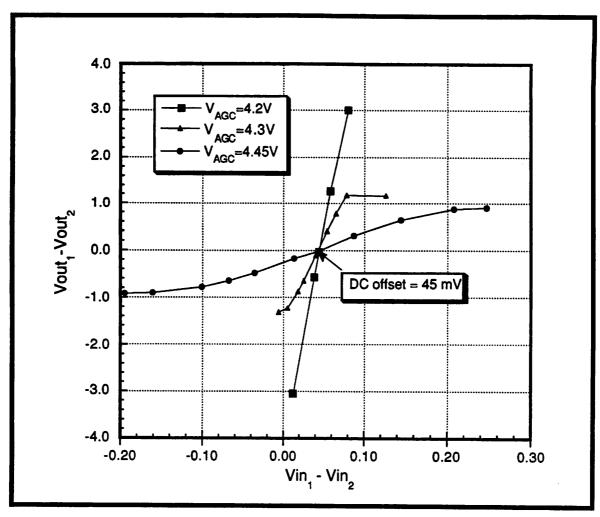

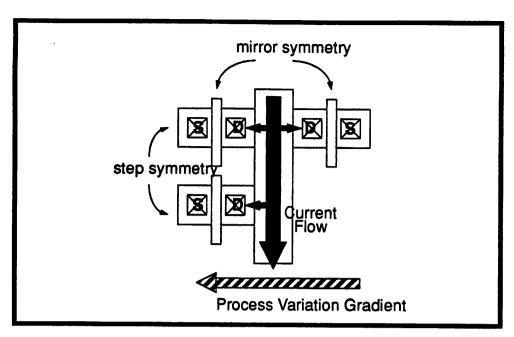

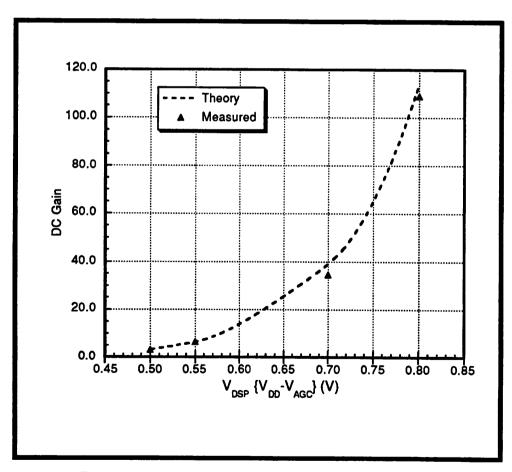

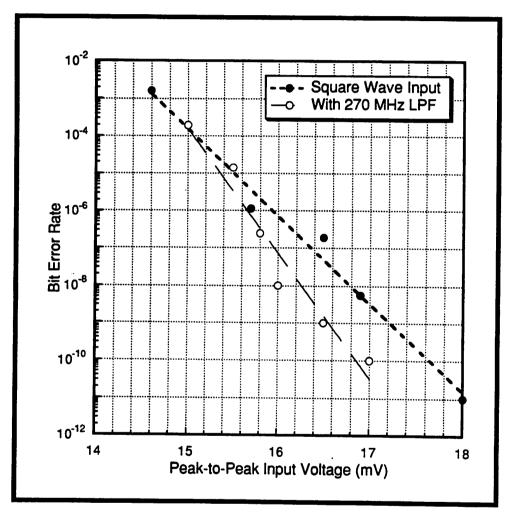

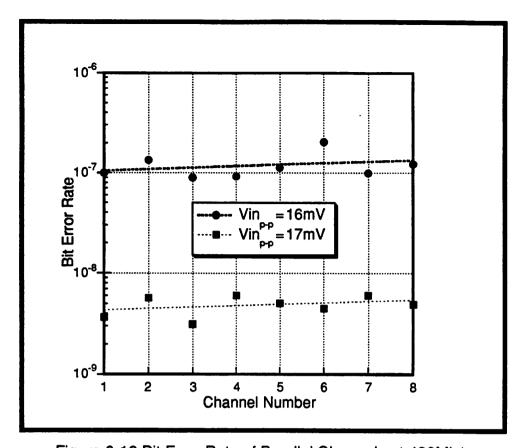

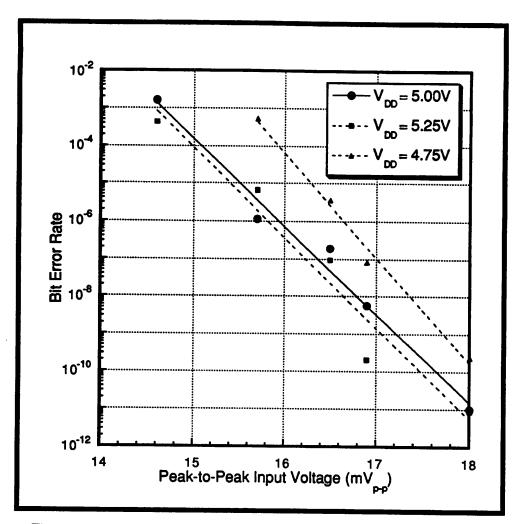

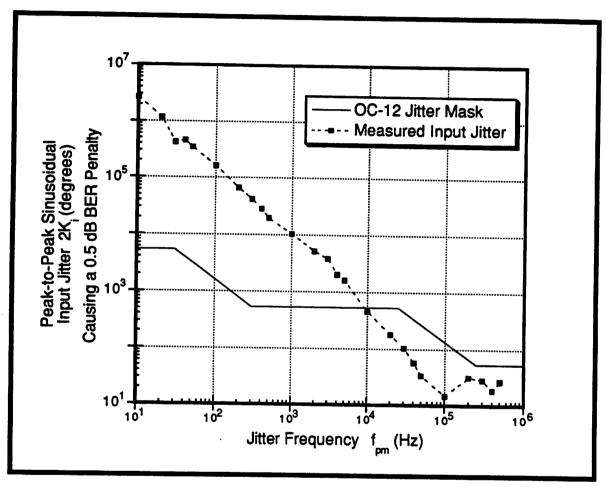

The noise of the preamplifier is a combination of the thermal noise of the feedback resistance and thermal noise of the input transistor. For high transimpedance gain and low input referred current noise, a high value of  $R_f$  is desired just as in the high-impedance preamplifier case. However, the bandwidth is inversely proportional to  $R_f$ . As a result, there is a trade-off between the sensitivity and bandwidth of the preamplifier.