# Copyright © 1993, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# COMBINED HIERARCHICAL APPROACHES TO INTEGRATED CIRCUIT LAYOUT BASED ON A COMMON DATA MODEL

by

Brian Douglas Ngai Lee

Memorandum No. UCB/ERL M93/81

22 November 1993

# COMBINED HIERARCHICAL APPROACHES TO INTEGRATED CIRCUIT LAYOUT BASED ON A COMMON DATA MODEL

Copyright © 1993

by

Brian Douglas Ngai Lee

Memorandum No. UCB/ERL M93/81

22 November 1993

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# COMBINED HIERARCHICAL APPROACHES TO INTEGRATED CIRCUIT LAYOUT BASED ON A COMMON DATA MODEL

Copyright © 1993

by

Brian Douglas Ngai Lee

Memorandum No. UCB/ERL M93/81

22 November 1993

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

To Donna for her love and inspiration

#### Abstract

# Combined Hierarchical Approaches to Integrated Circuit Layout Based on a Common Data Model

by

Brian Douglas Ngai Lee

Doctor of Philosophy in

Electrical Engineering and Computer Science

University of California at Berkeley

Professor A. Richard Newton. Chair

The integrated circuit layout problem is the specification of fabrication patterns that implement a given circuit description subject to manufacturing and performance constraints. The high complexity of integrated circuits has made it necessary to decompose the layout problem into a set of subproblems, and the typical layout process usually solves a sequence of subproblems corresponding to the steps of floor planning, placement, channel definition, global routing, detailed routing, and compaction. Each subproblem depends on the solutions of the previous subproblems and iteration over the sequence of problems may be required to find a feasible layout solution. Unfortunately, iterative improvement of layout solutions is very difficult because a side effect of the partitioning is that feedback between subproblems is hard and not well understood.

A merged hierarchical approach to layout is presented that provides a means of investigating the relationship between placement and routing to improve current layout methods. A common data model is used to integrate layout phases and to simplify and enhance information flow within the layout process. The data model induces a structure to the layout process for experimenting with feedback and information management.

A layout system based on a  $2 \times 2$  grid-graph abstraction that combines placement and global routing has been implemented based on this paradigm. Examples from sea-of-gates designs are used for benchmark comparisons.

Prof. A. Richard Newton Dissertation Committee Chairman

To Donna for her love and inspiration

# List of Tables

| 3.2 Comparison of linear versus nonlinear objective function                                                          | 1.1 | Example characteristics                                                                                               | 13  |

|-----------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 Comparison of linear versus nonlinear objective function                                                          | 3.1 | Relative edge weights by abstract net type and edge                                                                   | 37  |

| 3.3 Statistics on the number of non-integer programs solved during the branch- and-bound solution of integer programs | 3.2 | Comparison of linear versus nonlinear objective function                                                              | 45  |

| 3.4 Effects of applying a simple re-route procedure                                                                   | 3.3 | Statistics on the number of non-integer programs solved during the branch-                                            |     |

| 4.1 Total net length comparisons between the separate phase 2 × 2 algorithms and TimberWolf 6.1                       | 9.4 | Efforts of application of integer programs                                                                            |     |

| and TimberWolf 6.1                                                                                                    | J.4 | Effects of applying a simple re-route procedure                                                                       | 51  |

| 4.2 Area and aspect ratio comparisons between the separate phase 2 × 2 algorithms and TimberWolf 6.1                  | 4.1 | Total net length comparisons between the separate phase $2 \times 2$ algorithms and Timber Wolf 6.1                   | =0  |

| rithms and TimberWolf 6.1                                                                                             | 4.9 | Area and aspect ratio comparisons between the constant phase 2 x 2 alms                                               | -99 |

| ment performed ahead of route assignment                                                                              |     | rithms and TimberWolf 6.1                                                                                             | 60  |

| 5.2 Edge capacity violations and total net length for the immediate and gradual methods of pseudo-pin assignment      | 5.1 | Edge capacity violations as a function of the number of levels of cell assignment performed ahead of route assignment | 69  |

| 6.1 Merged placement and routing versus separate phases                                                               | 5.2 | Edge capacity violations and total net length for the immediate and gradual                                           |     |

| 6.2 Coupled placement and routing versus separate phases                                                              |     | methods of pseudo-pin assignment                                                                                      | 70  |

| 6.2 Coupled placement and routing versus separate phases                                                              | 6.1 | Merged placement and routing versus separate phases                                                                   | 81  |

| on Hilliam polymere burners                                                                                           | 6.2 | Coupled placement and routing versus separate phases                                                                  |     |

| 0.3 Hybrid placement and routing versus separate phases                                                               | 6.3 | Hybrid placement and routing versus separate phases.                                                                  | 92  |

#### Acknowledgements

First, I would like to thank Professor Richard Newton, my research advisor, for his generous and constant support and patience throughout my graduate school years. His vision and ideas maintained my interest, provided encouragement, and spurred my creativity.

I am grateful to Professor Carlo Séquin and Professor Charles Stone for reading this dissertation and for being on my committee.

I also thank Professors Robert Brayton, Richard Newton, Donald Pederson, and Alberto Sangiovanni-Vincentelli for creating the enjoyable and stimulating research environment called the Berkeley CAD group. I especially thank Professor Sangiovanni-Vincentelli for serving as my qualifying exam committee chairman and Professor Pederson for starting me, as a freshman, on the path that eventually led to this degree.

Many other members of the Berkeley CAD group, both past and present, contributed beneficially to my graduate school experience. To mention but a few, I thank Mark Beardslee, Jeff Burns, Andrea Casotto, Wayne Christopher, David Harrison, Chuck Kring, Tom Laidig, Peter Moore, Tom Quarles, Ellen Sentovich, Greg Sorkin, and Rick Spickelmier for all their time and help and for generally making my stay here fun and worthwhile. I am especially grateful to Ellen Sentovich and Mark Beardslee for their support, advice, and friendship these past few years.

This research was sponsored in part by the Defense Advanced Research Projects Agency, the Digital Equipment Corporation, and the Semiconductor Research Corporation. Their support is gratefully acknowledged.

Thanks also go to my friends in the Berkeley Hang Gliding Club for aiding and abetting my much needed escapes from reality to freedom in the air. I wish them all good lift and safe flights.

I am also grateful to the extended "Pajaro Dunes Gang" for their support, encouragement, and gentle nagging.

A special thanks goes to my parents and family for their constant love and faith. They put up with much and never gave up on me.

Finally, and with much love, I thank Donna for being there at the end to help me finish.

# List of Figures

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5                             | Gate array design structure                                                           | 5<br>6<br>7<br>8<br>10                             |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------|

| 2.1                                                         | Classification of chip level integrated placement and routing methods                 | 16                                                 |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9 | Problem hierarchy created by a hierarchical decomposition  Example decomposition step | 26<br>28<br>30<br>35<br>38<br>40<br>43<br>49<br>50 |

| 4.1                                                         | Placement constraints for terminal propagation                                        | 5-1                                                |

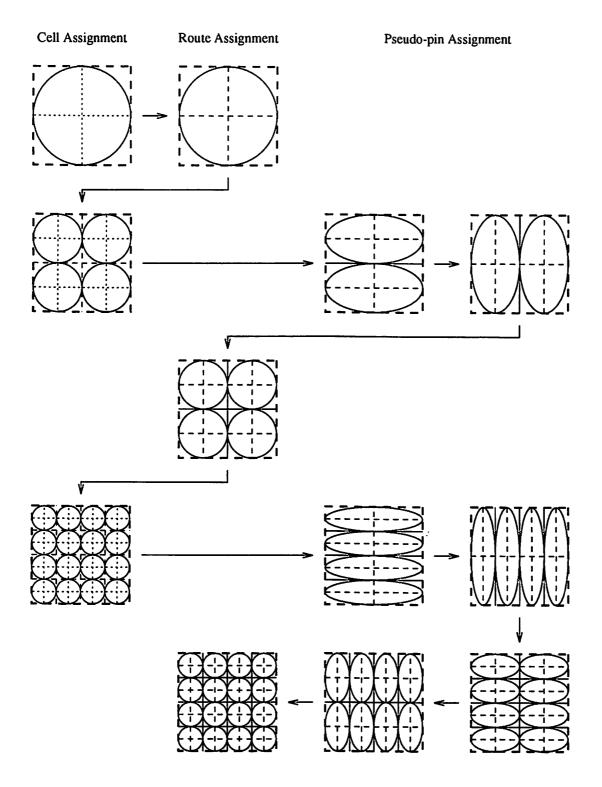

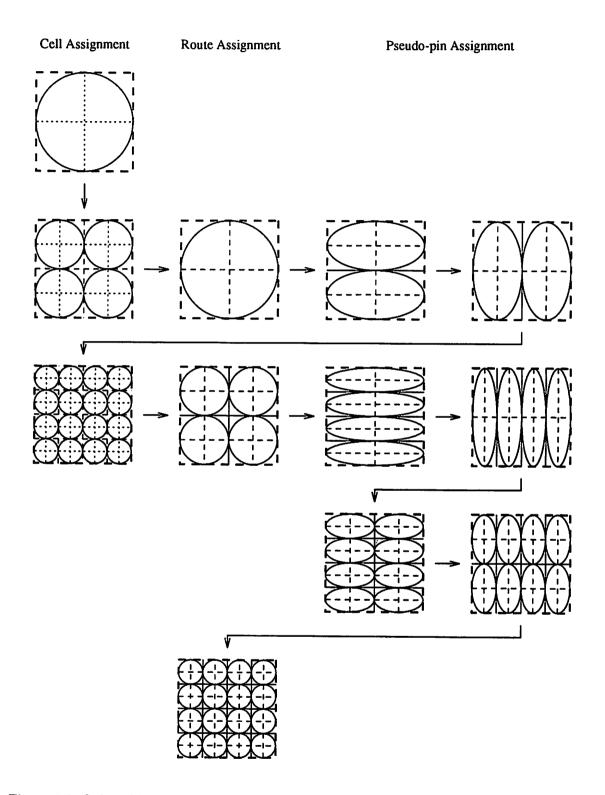

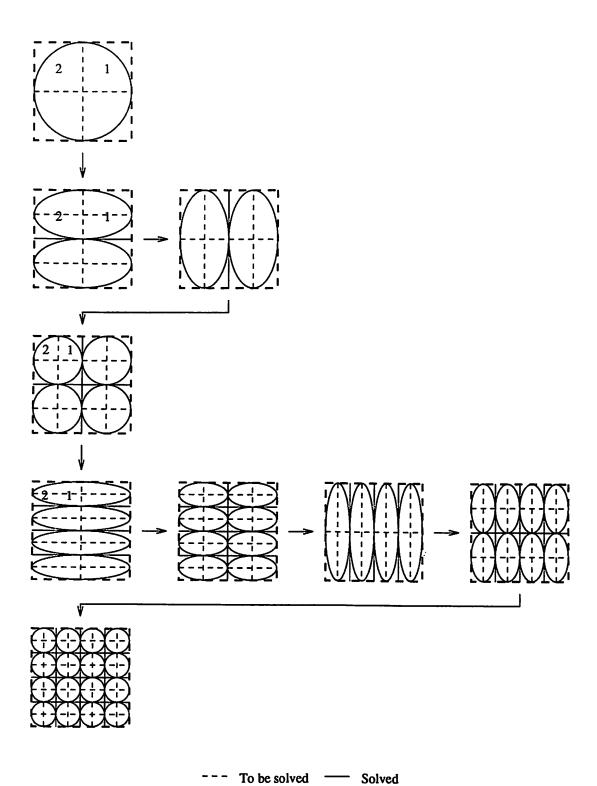

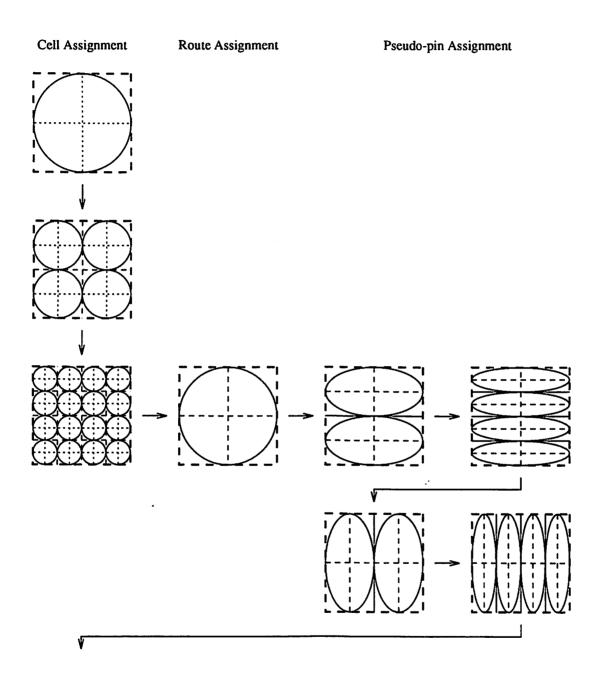

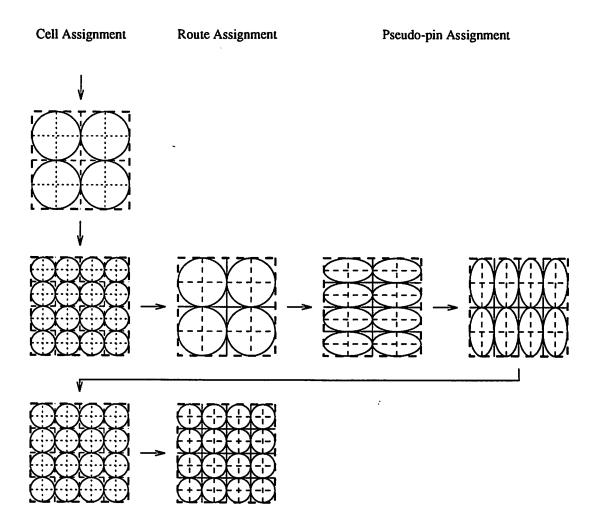

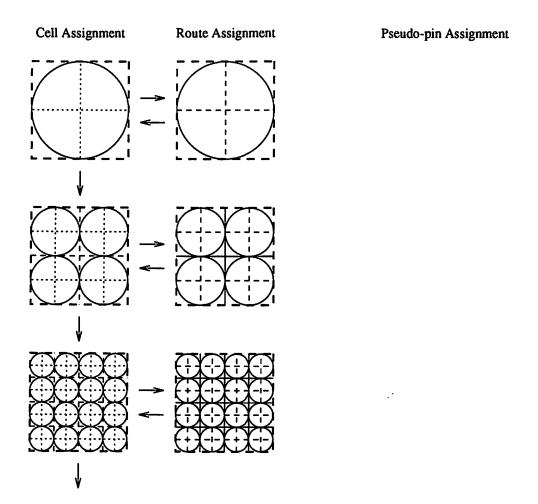

| <ul><li>4.2</li><li>5.1</li><li>5.2</li></ul>               | Subproblem abstraction sequence for solving a routing level immediately after         | 56<br>64                                           |

| 5.3                                                         | before routing                                                                        | 65<br>66                                           |

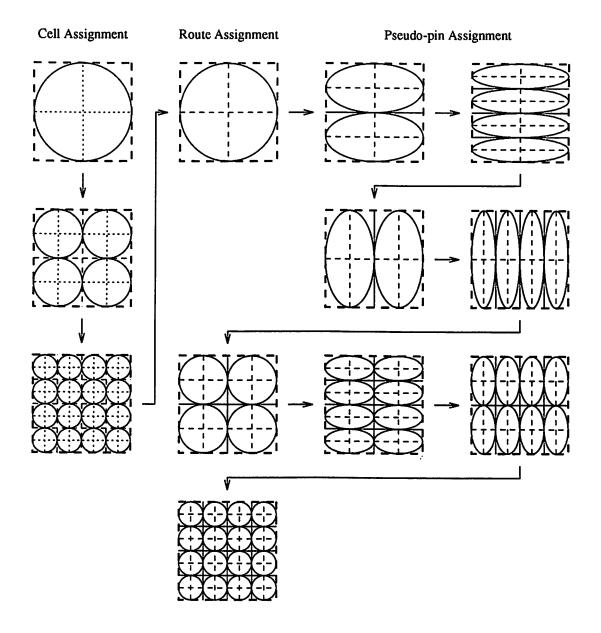

| 6.1<br>6.2<br>6.3<br>6.4                                    | Routing and pseudo-pin assignment influence on placement                              | 78<br>80<br>82<br>84                               |

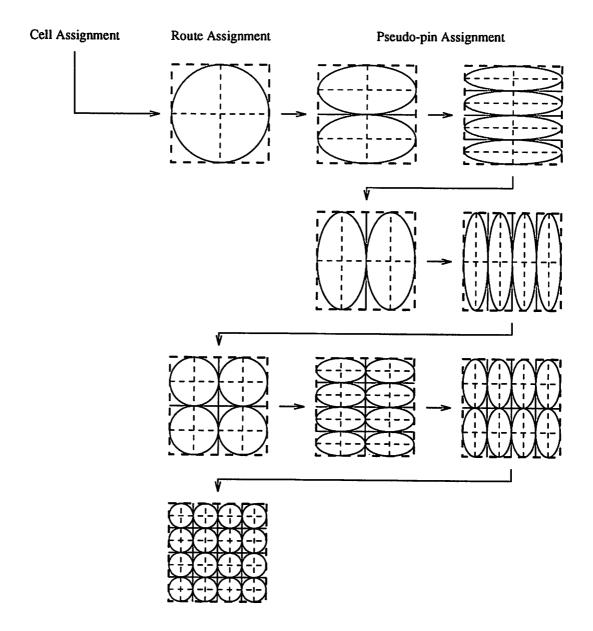

| 6.5<br>6.6                                                  | Remaining coupled approach subproblem abstraction sequence                            | 85<br>88                                           |

| 6.7 | Remaining hybrid approach subproblem abstraction sequence | • |  |  |  | • | • | 89 |

|-----|-----------------------------------------------------------|---|--|--|--|---|---|----|

|-----|-----------------------------------------------------------|---|--|--|--|---|---|----|

## Contents

| Lis | st of | Figures                                      | v    |

|-----|-------|----------------------------------------------|------|

| Lis | st of | Tables                                       | viii |

| 1   | Intr  | oduction                                     | 1    |

|     | 1.1   | Integrated Circuit Layout Problem Definition | 2    |

|     | 1.2   | Design Styles                                | 4    |

|     | 1.3   | Typical Layout Process                       | 9    |

|     | 1.4   | Problems with the Typical Layout Process     | 12   |

|     | 1.5   | Goals                                        | 1:3  |

|     | 1.6   | Benchmark Examples                           | 1:3  |

| 2   | Bacl  | kground                                      | 15   |

|     | 2.1   | Coupled Placement and Routing                | 17   |

|     | 2.2   | Merged Placement and Routing                 | 18   |

|     | 2.3   | Unified Placement and Routing                | 22   |

|     | 2.4   | Summary                                      | 22   |

| 3   | Algo  | prithms                                      | 24   |

|     | 3.1   | Hierarchical Decomposition                   | 25   |

|     |       | 3.1.1 Common Data Model                      | 25   |

|     |       | 3.1.2 Problem Reduction                      | 26   |

|     | 3.2   | Subproblem Solution                          | 32   |

|     |       | 3.2.1 Cell Assignment                        | 33   |

|     |       | 3.2.2 Route Assignment                       | 38   |

|     | 3.3   | Pseudo-pin Assignment                        | 46   |

|     | 3.4   | Rip-up and Re-route                          | 48   |

| 4   | Sepa  | arate Placement and Routing                  | 52   |

|     |       | Placement                                    | 52   |

|     |       | Routing                                      | 55   |

|     | 4.3   | Results                                      | 57   |

| 5 | Placement and Routing Communication | 61   |

|---|-------------------------------------|------|

|   | 5.1 Routing                         | . 61 |

|   | 5.1.1 Placement Resolution          | . 62 |

|   | 5.1.2 Routing Decision Resolution   | . 69 |

|   | 5.2 Placement                       | . 71 |

| 6 | Combining Placement and Routing     | 73   |

| Ü | 6.1 Unified Approach                | . 74 |

|   | 6.2 Merged Approach                 | . 76 |

|   | 6.3 Coupled Approach                | . 83 |

|   | 6.4 Hybrid Approach                 | . 87 |

| 7 | Conclusion                          | 94   |

| В | Bibliography                        | 97   |

### Chapter 1

## Introduction

The physical design of integrated circuits requires the transformation of a circuit description into layout, the set of geometric patterns needed to generate the fabrication masks used in very large scale integration (VLSI) manufacturing processes. This layout generation step is a difficult stage in the design process of an integrated circuit and the effectiveness of layout generation systems affects both the cost and performance of the final product. The research presented in this dissertation is intended to indicate layout paradigm modifications that will produce higher quality layout solutions.

The layout problem is to produce layout that implements a given circuit description subject to manufacturing and performance constraints. Current circuits may contain millions of devices, resulting in complex and difficult layout problems. Today's market pressures make continual improvement in layout solution quality an imperative for current layout systems.

The physical design stage of an integrated circuit has an important impact on the performance and cost of the final product. As the last step in the circuit design process, layout generation is the closest stage to the manufacturing process and its function as the major link between design and production makes it a crucial determinant of ultimate circuit performance relative to the underlying fabrication technology. The effectiveness of the layout solution process directly affects design cycle time and thus total design cost. Layout solution quality directly affects yield and thus manufacturing cost. Both design cost and manufacturing cost are major components of the final product cost.

Unfortunately, the combinatorial nature of the layout problem makes the generation of layout a difficult task. Exact solution methods are prohibitively expensive except

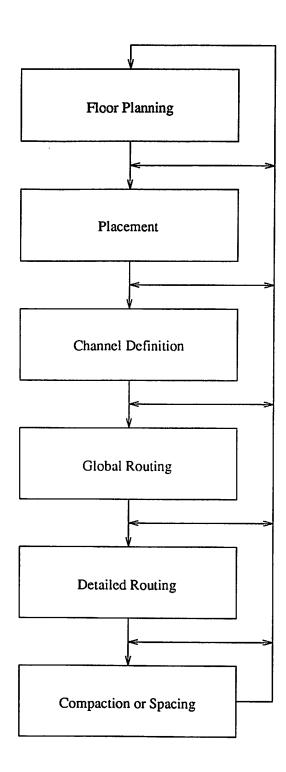

for trivial cases, so layout algorithms tend to rely on heuristics and approximations to find reasonable solutions. The typical layout system solves a layout problem by decomposition into an ordered set of simpler subproblems and then sequential solution of the subproblems. These subproblems are referred to as layout phases and may include stages called floor planning, placement, channel definition, global routing, detailed routing, and compaction. Because of the difficulty and complexity of generating layout, this decomposition is often considered essential and is usually assumed implicitly in any discussion of layout algorithms. Despite the problem reduction, the "simpler" subproblems are actually still difficult combinatorial optimization problems. The phases are easier only in the sense that heuristic and approximate methods have been found which produce acceptable solutions for them.

The difficulty of the individual phases has focused layout research on solutions for each phase. An unfortunate side effect of this emphasis is that the interaction and dependencies between phases have been neglected. Information flow and feedback between phases is often nonexistent or ad hoc. Ideally, a layout algorithm would solve the layout problem as a single problem, but since some form of problem decomposition is required to make the problem tractable, enhancing communication between subproblem solution processes is critical for improving the effectiveness of the whole approach. The goal of this research is to obtain better layout solutions by modifying the standard layout decomposition paradigm to allow more structured and effective information management. In particular, integration of placement and routing phases and mechanisms for feedback are investigated.

In the remainder of this chapter, more introductory material is presented on the layout problem, the characteristics and problems of typical layout processes, and the goals for improving these processes. A discussion of previous work in combining layout phases is given in Chapter 2. The major algorithms used are described in Chapter 3 and reference results are presented in Chapter 4. Placement and routing interaction is discussed and analyzed in Chapter 5 and experiments in integrating placement and routing based on a common  $2 \times 2$  data model are detailed in Chapter 6.

#### 1.1 Integrated Circuit Layout Problem Definition

Current VLSI manufacturing processes create circuits by building layers of different materials. The patterns and combinations of these layers create electrical devices and the interconnections between these devices. Fabrication requires a set of geometric patterns for each layer, and the patterns are used to create the templates or masks for processing each layer. The layout problem is to transform a circuit description into the appropriate geometric patterns for generation of fabrication masks. For the typical layout system, this transformation requires taking a circuit description and determining circuit element positions and wire positions that implement the circuit subject to manufacturing and performance constraints.

The net list is a common form of circuit description. It consists of a set of interconnections between circuit elements. The interconnections specify which elements must be electrically connected to each other. Each interconnection is called a net and represents an electrically equivalent point in the circuit. Hence, circuit descriptions presented as collections of interconnections are called "net lists". Circuit elements may be single devices like transistors or collections of devices such as logic gates or other circuit building blocks. These elements are often referred to as cells or modules. The term "net" is also used to refer to the wire or wire patterns that implement an interconnection. Wires connect to cells at specific locations called pins or terminals, so a net may be associated with a set of cells that require interconnection or with the corresponding set of pins.

Cells or circuit elements are often used multiple times within a design and across designs, so the sets of geometric patterns that implement particular circuit elements are usually predefined. However, the patterns that implement the wiring corresponding to each net are not predefined because in general these interconnections are unique to each circuit. Fortunately, the interconnection patterns can often be derived from specification of simpler, abstract wire positions. Thus, solving the layout problem involves assigning cell positions and determining abstract wire positions. The process of assigning cell positions is called *placement* and the process of assigning wire positions is called *routing*. This information is usually sufficient to generate the set of geometric patterns required for generation of the actual fabrication templates.

The solution of a layout problem requires that the final geometric patterns satisfy certain problem specifications. These specifications may be grouped into manufacturing constraints and performance constraints. Proper fabrication requires that certain requirements be met on the size, shape, and relative positions of the geometric patterns both within layers and between layers. These requirements are referred to as design rules. Typically, these rules are translated into constraints on cell and wire positions such that a feasible set of positions may always be transformed into a set of design-rule correct geometry. Per-

formance constraints are usually specified with respect to the fabricated circuit. The most common example is timing requirements on the circuit inputs and outputs. Unfortunately, it is often difficult to relate constraints of this type to the specification of layer patterns. Often, accurate testing of constraint satisfaction is only possible after complete specification of the layout. This kind of dependence makes finding layout solutions difficult.

Strictly speaking, a feasible layout solution must meet all design constraints. However, because of the simplifications and approximations made by many layout systems, a feasible layout solution often refers only to a solution that may be correctly manufactured. In these cases, the performance constraints have been ignored and the usage is usually clear from context.

#### 1.2 Design Styles

Gate array, standard cell, and macro-cell layout are the most common design styles implemented by automatic layout systems. A brief review of these styles follows to provide context for the subsequent discussion on layout phases. The examples and layout system in this dissertation are based on a specific type of gate array layout called sea-of-gates.

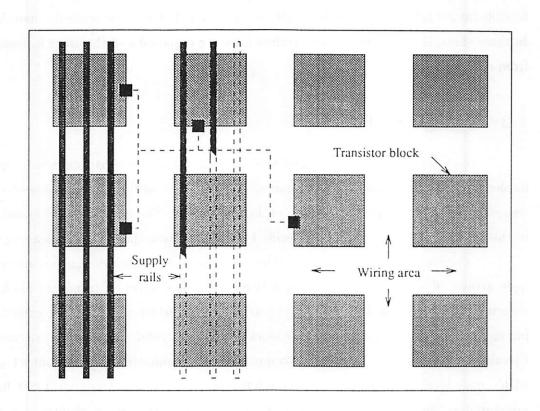

Gate array designs are also referred to as master-slice designs or uncommitted logic arrays. Each design is based on a two dimensional array of transistor blocks. This structure is depicted in Figure 1.1. The array is completely prefabricated except for the interconnection layers. Each transistor block consists of a solid group or array of transistors. Circuit elements or functions are implemented by customization of interconnect patterns within each local transistor group. The interconnect patterns for common circuit functions are stored as templates in cell libraries. Connections between circuit elements are made in the predefined wiring areas or *channels* left open between transistor blocks. Though the use of partially fabricated standard arrays is advantageous for manufacturing, it creates difficult constraints on the layout problem. In particular, because of the predefined and fixed areas for routing, the complete connection of circuit elements may not be possible for a given assignment of elements to transistor blocks.

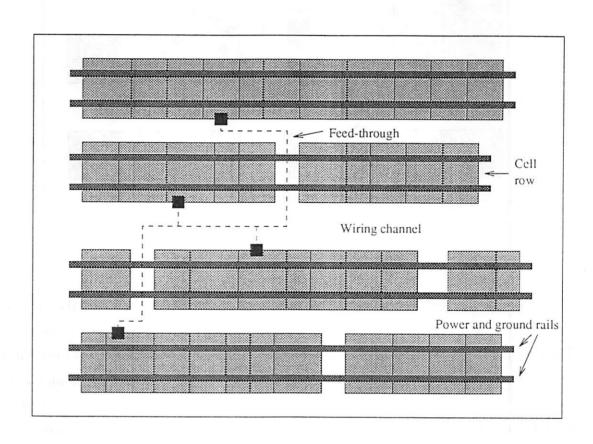

Standard cell designs are characterized by rows of cells separated by wiring or routing channels. This structure is illustrated in Figure 1.2. Cells are custom-designed to implement circuit functions on the level of simple logic gates, flip-flops, and latches, and are often constrained to have uniform height to simplify wiring between rows and power

Figure 1.1: Gate array design structure

Figure 1.2: Standard cell design structure

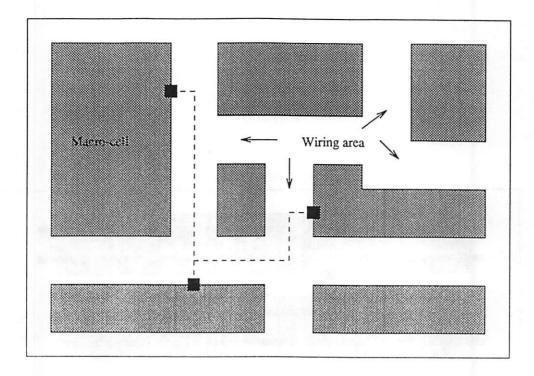

Figure 1.3: Macro-cell design structure

distribution along rows. Typically, all wiring between cells is confined to the channels between rows and any connections that cross rows must use reserved spaces between cells. These spaces are called feed-throughs and are often modeled as a special type of cell. More sophisticated systems are capable of wiring over or through cells to make connections across rows. Unlike gate arrays, standard cell designs specify design-dependent geometry on all mask layers. This characteristic permits the number of feed-throughs and the amount of wiring area between rows to be adjusted as necessary and guarantees that feasible wire assignments for all nets can always be generated.

Macro-cell or building-block designs differ from standard cell designs in that each cell implements a much larger amount of functionality and the cell topology is less constrained. While each standard cell typically implements a simple logic function, each macro-cell usually implements a major circuit function. In fact, the predefined patterns of the macro-cells are occasionally generated using standard cell design. Macro-cells may vary widely in size and shape and may be positioned in any non-overlapping configuration. Figure 1.3 shows an example macro-cell design structure. Similar to standard cells, the

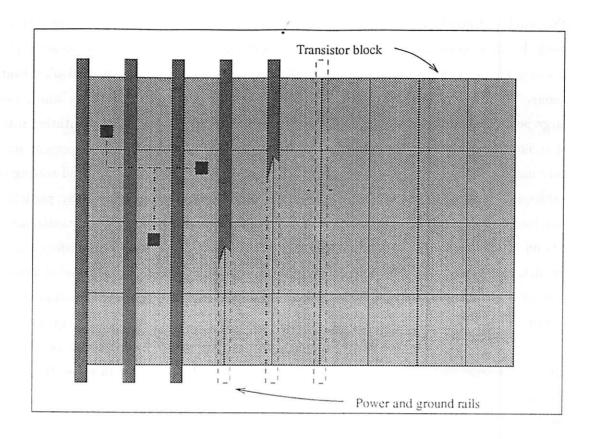

Figure 1.4: Sea-of-gates design structure

patterns for inter-cell wiring connections are specified in the regions between and around cells. These wiring spaces can be adjusted as required to allow complete specification of the layout.

Sea-of-gates or "channel-less" gate-array designs are gate arrays without any reserved wiring area between transistor blocks. This structure is illustrated in Figure 1.4. Connection patterns within cells are usually sparse and inter-cell wiring patterns are specified both through cells and over cells. In the desired interconnection regions, extra area for wiring can be obtained by not utilizing some of the transistor blocks for circuit element implementation. A goal of sea-of-gates design systems is to use as few transistor blocks as possible for this extra interconnection area, resulting in a maximal amount of functionality implemented for a given array size. Relative cell positions are unconstrained except for the grid restrictions which force spacing between cells to occur in multiples of transistor blocks. Of course, simplifying restrictions could be added to force the use of cell rows, but

this would artificially limit the number of cells and thus, the amount of functionality that could be implemented on a sea-of-gates array, invalidating a major reason for attempting sea-of-gates designs. The unconstrained situation is both advantageous and disadvantageous. The freedom in choosing cell positions may allow very good solutions which use a large percentage of the available transistor blocks for circuit element implementation rather than interconnection implementation, but this same lack of enforced cell placement structure makes finding feasible solutions more difficult. Allocating routing area and solving the subsequent routing problems is especially difficult. Unlike a standard gate array, predefined routing areas do not exist and unlike a standard cell design, no simplifying constraint exists on the positioning of cells to make the formation of routing areas straightforward and predictable. Also, moving cells apart may incur a large area penalty because of the grid restrictions and often may require a complete re-placement of the design. Maximizing the use of transistor blocks for circuit cell implementation leads to arbitrarily shaped routing areas and requires heavy use of interconnection area over and through cells, resulting in difficult, general routing problems. As in the standard gate-array design style, there is no guarantee that it will be possible to completely connect a particular assignment of cells to blocks.

#### 1.3 Typical Layout Process

Typical layout systems solve the layout problem in several phases. The phases are sequential and dependent. The common phases and their relationship in a typical layout design flow is shown in Figure 1.5.

Sometimes, circuit cells do not have their corresponding geometric patterns completely specified. This occurs in macro-cell design where a cell is a major circuit function consisting of multiple sub-circuits or devices. The functionality of the cell is known, but not its layout. The floor planning phase handles these kinds of specifications. Given bounds on cell areas, the floor planning phase determines relative cell positions and if necessary shapes for cells. The process allocates routing area both between cells and within cells and determines pin locations on the newly assigned cell shapes. Subsequent phases solve the layout problems delineated by the now defined macro-cell regions. For this phase, the generation of a certain chip aspect ratio is a typical constraint and the minimization of total chip area is a common objective function.

Figure 1.5: Typical layout system design flow

The placement phase specifies cell positions on the chip or within regions specified by the floor planning stage. Cells are not allowed to overlap and constraints on relative cell positions depend on the design style being implemented. For example, gate array styles require cell assignments on specific grid locations while other styles are less constrained. Typical placement goals are minimization of area, total net length, or both while producing a feasible placement. The feasibility condition ultimately refers to the feasibility of the subsequent and resultant routing problem. Unfortunately, this condition is often impossible to check without actually performing the routing step.

The channel definition step defines the wiring regions on the chip. Its name originates in design styles where wires are routed in the "channels" between cell rows. More specifically, the term channel refers to a routing problem with two parallel boundaries. Pins are specified at positions along these boundaries. Nets may be assigned to enter or exit from the open sides of the channel, but neither the position nor relative order of these net crossings are specified. The distance between the parallel boundaries of a channel routing problem is allowed to increase to provide more area to complete the interconnections. In standard cell design, the channel definition occurs implicitly as a result of the routing. In macro-cell layout, this step determines explicitly the sizes and positions of the routing areas between cells. It is possible to constrain macro-cell placements so that the regions between cells can always be partitioned into channels. In systems without this constraint, the channel definition stage may also create switchboxes. The classic switchbox is a rectangular routing region with pins specified on all borders. It can be thought of as a channel routing problem where the distance between channel boundaries is fixed and where pins are specified at fixed positions along the open sides of the channel. In gate-array styles, routing also occurs over and through cells and it is more appropriate to think of the channel definition step as routing area definition.

The routing phases perform the actual assignment of inter-cell wire positions. This is commonly performed in two phases. The first phase, global or loose routing, assigns nets to particular routing channels or routing areas. After this step, the path of each wire is known with respect to the areas defined during the channel definition phase. The second phase, detailed routing, assigns specific positions for the wires within the regions assigned during global routing.

After routing, the circuit layout is basically complete. However, some systems employ a final compaction or spacing step where all layout geometries are squeezed

together or re-spaced to generate a final layout of minimal area that still meets design rule constraints.

#### 1.4 Problems with the Typical Layout Process

The fundamental problem of the typical layout process is that it doesn't directly solve the actual, desired layout problem. Instead of solving a single optimization problem subject to the multitude of possible layout constraints, typical layout systems solve a sequence of simpler optimization problems subject to a subset of the possible constraints. Historically, this decomposition into layout phases and relaxation or omission of constraints has been necessary in order to generate any layout solution. Unfortunately, this strategy only solves an approximation of the desired problem and can not guarantee that a feasible solution to the actual layout problem will be found.

Problems arise in the typical layout process from the manner and method in which the decomposition occurs rather than from the decomposition into layout phases itself. As in any sequential decomposition, the subproblem solved at each phase depends on the solutions of the previous phases and iteration over the sequence of phases may be required to find a feasible layout solution. Unfortunately, iterative improvement of layout solutions obtained in this manner is very difficult because a side effect of the decomposition is that feedback between subproblems is hard and not well understood. Each phase solves only a portion of the whole layout problem. Each of these portions may be thought of as an abstraction or approximation of the desired problem. As a result, each phase has its own data model of the layout problem that is different from the other phases. For successful iterative improvement, each phase needs some global information regarding decisions made in previous phases. Typical layout systems have many barriers to the effective flow of this information. Often, each phase is performed by a separate computer program which only understands its particular data model. Any information from other phases must be translated or interpreted relative to the current problem abstraction. In general, this translation or interpretation is not well understood, and even in specific cases where the interpretation is clear, differences between the data models may lead to information loss. Furthermore, the separate programs tend to have simple interfaces which prohibit the exchange of the desired global information. These factors inhibit and discourage the iterative feedback required to find feasible layout solutions.

| Example | Cell Count | Pad Count | Net Count | Cell Area $(\lambda^2)$ |

|---------|------------|-----------|-----------|-------------------------|

| C880    | 257        | 86        | 317       | 1989951                 |

| C1355   | 292        | 73        | 333       | 2260956                 |

| misex3c | 295        | 28        | 309       | 2284185                 |

| duke2   | 299        | 51        | 321       | 2315157                 |

| C1908   | 326        | 58        | 359       | 2524218                 |

| misex3  | 344        | 28        | 358       | 2663592                 |

| C3540   | 784        | 72        | 834       | 6070512                 |

| C5315   | 1073       | 301       | 1251      | 8308239                 |

| C7552   | 1365       | 315       | 1572      | 10569195                |

| C6288   | 2385       | 6.1       | 2417      | 18467055                |

Table 1.1: Example characteristics

#### 1.5 Goals

The main goal of this research is to find modifications to the standard layout paradigm that will produce better layout solutions. This goal is pursued by examining placement and routing interaction and information exchange requirements to understand the relationship between the two phases better, analyzing different placement and routing integration and feedback approaches, and evaluating the use of a common data model to improve communication and reduce information loss between phases due to translation or interpretation inefficiencies. The investigations into these areas are designed to indicate methods for improving placement and routing through closer coupling or merging of the two phases. The experiments are based on a layout system that hierarchically decomposes the layout problem using a common data model. The resulting hierarchy provides a convenient structure for observing placement and routing interaction and allows comparisons of different levels of placement and routing integration from separate phases to concurrent solution. The common data model provides a common reference frame for observing placement and routing communication and for experimenting with feedback mechanisms.

#### 1.6 Benchmark Examples

The benchmark examples used in this research are characterized briefly in Table 1.1. The examples are derived from the MCNC and ISCAS logic synthesis benchmark circuits [45]. Circuit functions include error correction logic, ALUs and their control logic, a 16-bit multiplier, and generic control logic. Each circuit was processed using sis [33] and mapped into the Mariner sea-of-gates library [23]. Sis is an algorithmic sequential circuit optimization program. It was used both to optimize the examples using its standard set of operations and to map the optimized circuits into the sea-of-gates library. The resulting circuits have their cell, pad, and net counts listed in the table. The cells themselves range in complexity from a simple NAND gate with four transistors to an AND-OR-INVERT gate with eight transistors. There are two interconnection layers; the primary vertical interconnection layer is Metal 1 and the primary horizontal interconnection layer is Metal 2. The library cells used by these examples have from four to six feed-throughs for through-the-cell routing and from two to ten free tracks for over-the-cell routing.

### Chapter 2

## Background

Layout algorithms have been studied extensively for many years. Continued interest in this area emphasizes the importance of layout generation to product design. In addition to handling increased circuit sizes and adjusting to rapidly changing manufacturing technologies and design styles, current layout systems must also produce better layout solutions. The discussion in this chapter is limited to previous work in combining placement and routing at the chip level. More general discussion and surveys on placement and routing algorithms can be found in [5, 37, 34].

A major reason for the interest in combining placement and routing is the promise of finding better layout solutions. In the past, research emphasis was concentrated on the separate phases. This was a manifestation of the complexity of the layout problem and the lack of understanding about the relationship between phases. Concentrating on each phase produced results more effectively than tackling the combined problem. Now, as computer power increases, the complexity of some methods of combining phases is becoming tractable, and as the benefits of continued optimization of individual phases decrease, the potential gain from investigating integrated processes increases.

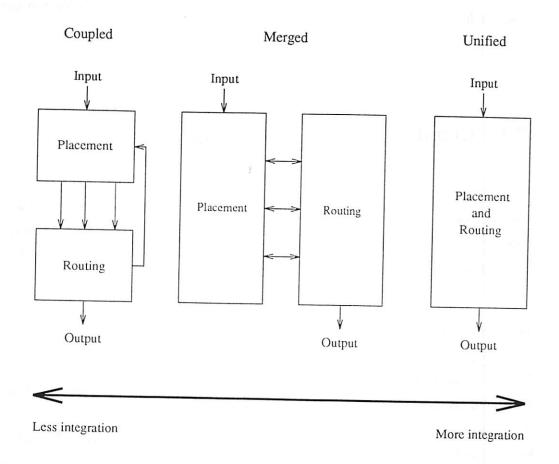

Efforts to combine placement and routing at the chip level can be categorized into three broad classes that span a continuum of algorithm integration possibilities as depicted in Figure 2.1. Coupled approaches execute separate placement and routing phases and then feed back between the two phases. During each phase, a complete solution is found. For these classifications, a complete placement solution is a specification of all cell positions relative to each other and a complete routing solution is an assignment of all nets to global routing configurations. Merged approaches generate complete placement and routing

Figure 2.1: Classification of chip level integrated placement and routing methods

solutions concurrently. These methods are characterized by a more intense exchange of information than in the coupled approaches. The level of feedback information is comparable in magnitude to the forward flow of information. *Unified* approaches determine placement and routing together as a single problem. Coupled methods are the least integrated and unified approaches are the most integrated. Recently, Adams [1] has worked on integrating layout phases for macro-cell design. No attempt is made here to classify his or other cell-level approaches.

### 2.1 Coupled Placement and Routing

Coupled placement and routing methods consist mainly of systems that feed back routing information to re-space placements. Typically, the relative cell topology is maintained in a graph or other global data structure and routing information is fed back to adjust the spacing between cells.

Soupkup and Royle [38] presented a prototype building-block layout system that provides some automatic feedback between routing and placement. This system uses a min-cut placement algorithm based on polar graph representations [21] to generate the basic cell placement topology. The routing regions between cells are represented as possibly zero-sized rectangles and edges for these rectangles are introduced into the polar graphs. Subsequent routing provides size requirements for the routing rectangles. Though the basic layout topology is not changed, size information is fed back to the placement to effect cell re-spacing that accommodates routing requirements.

The Orca sea-of-gates system [17] uses a min-cut placement algorithm [19, 15] to form a cut tree of relative cell topology. Locations and shapes of cell groups within this cut tree are determined by a "shape-adding" approach [39]. A simplified global router is used to determine space requirements in over-congested regions. Spacing information is fed back to the placement by modifying the shape function of the appropriate cell group. The "shape-adding" algorithm and the global routing are iterated until the design can be routed successfully at the detailed level.

#### 2.2 Merged Placement and Routing

Most work on integrating placement and routing can be classified as merged approaches. These are primarily hierarchical methods. Two exceptions are the systems of Shragowitz, Lee, and Sahni [36] and Tzeng [43]. For the merged approaches, the term hierarchical refers to a structuring of the process and data in terms of a hierarchy or tree of decisions or subproblems. Placement and routing can be combined in these methods by solving both placement and routing problems at each step or level of the hierarchy.

Burstein, Hong, and Pelavin [9] presented a merged placement and global routing approach for gate array VLSI layout. The process is structured according to a bi-partitioning hierarchy. Starting with a single super-grid corresponding to the entire layout region, each set of subdivisions creates a new level of super-grids until the final level corresponds to the gate array grid. All grid cells within a level are cut in the same direction, either horizontal or vertical, and directions are alternated between levels. When a super-grid cell is divided, the cells previously assigned to that super-grid must be partitioned into two parts corresponding to the next level grid cells. An initial partition is formed by heuristically selecting one cell at a time to be added to one partition block or the other. Then, the number of nets crossing the partition boundary is compared to the number of available wiring tracks and a pairwise interchange routine may be used to reduce the number of crossing nets. On each level, each net is assigned a global route relative to the current super-grid. The global routing of a net is initially restricted to a region projected from the net's assigned route path on the previous level. A route path is defined by a set of grid cells and when it is projected onto the next level, it covers twice as many cells. This new set of cells can be subdivided into rectangles of width no greater than 2. Each of these rectangles is routed as a  $2 \times n$  grid using Burstein and Pelavin's dynamic programming technique [10]. If a route can not be found within this restricted set of cells, then maze routing is used across all the cells at the current level to find a path.

Szepieniec [42] proposed a method of integrating placement and global routing for slicing structures. The approach begins with a given slicing structure. In this slicing structure, the number of slices, the relative sizes of slices, and the distribution of circuit elements across slices are fixed. Within each slice, the placement of subslices is solved as a linear placement problem. The objective of each linear placement problem is to minimize the geometric span of all nets. Hierarchical global routing is performed top-down along

with the slice placement. The routing problem for each slice is formulated after subslice placement by determining net entry positions along slice boundaries. Each entry position is a range corresponding to the subslice being entered. The positions are chosen to minimize the net's global bounding box. Routes are determined using a pattern router.

Dai and Kuh [12] described a hierarchical method for combining floor planning and global routing for building-block layout. A bottom-up clustering followed by top-down floor plan enumeration is used to determine block positions. The global routing is performed during the top-down portion of the floor planning. At each level of the hierarchy, a particular floor plan template is chosen, and global routing is performed on connected subgraphs of the inner dual graph corresponding to the template's floor plan graph. Each net is routed by finding a minimum Steiner tree on this global routing graph. The edges and vertices of these trees are expanded to obtain the global routing graphs and the input and output pad goals for the next level.

The Mariner sea-of-gates system [11] interleaves placement steps and routing steps to improve layout quality. Though the placement algorithm is based on quadrisection [40] and the routing algorithm is based on  $2 \times 2$  routing [10], both use more complicated data models that account for possible external pin positions. The interleaved global routing steps are used primarily to derive congestion metrics to direct the partitioning process. Final detailed placement is determined using simulated annealing and a maze router is used to obtain final global routes.

Korte, Prömel, and Steger [3] used a graph partitioning paradigm to combine partitioning (global placement) and global routing for sea-of-gates designs. The algorithm combines the tasks of partitioning cells into clusters, assigning these clusters to regions on the chip image, and providing the global routes with respect to these regions. The partitioning is a recursive min-cut bi-partitioning procedure and the global routing is solved as the problem of packing Steiner trees for various terminal sets in a graph with specified edge capacities. The global routing algorithm handles partially routed nets so at each iteration global routes are only updated in correspondence to the local change in the global routing graph. The partitioning cuts are chosen to be the "most critical" for the global routing and the partitioning cost function encodes the global routing information.

Suaris and Kedem [41] built a standard-cell layout system that combines their quadrisection placement algorithm with loose global routing in order to minimize the total layout area. The global routing is divided into two phases. The loose global routing phase

is combined with the placement and determines spanning trees for each net. The detailed global routing phase is performed separately and finds the actual global routes for each net. Finding these actual global routes includes determining the feed-through locations for nets to cross intermediate rows. Placement and loose global routing are performed as sequential operations for each problem abstraction of the quadrisection hierarchy and terminal propagation is used to feed forward loose global routing information to guide placement on subsequent abstractions. They are working on making the detailed global routing hierarchical so that it may be combined with the placement. The new detailed global router will find Steiner trees rather than spanning trees for each global route.

Müller [27] proposed a hierarchical method for combining floor planning and global routing. A min-cut partitioning process will be used to build a cut tree of the circuit. The partitioning will stop when the number of modules in a partition is smaller than a certain threshold. The partitioning structure of the remaining subcircuits is to be determined bottom-up with a clustering technique based on a maximum weighted matching algorithm. Then, the cut tree will be processed bottom-up to determine cut line orientation and to estimate required routing area. The routing area estimation is expected to be a combination of statistical methods and actual global routing computations. A final top-down pass over the cut tree will be performed to determine partition ordering with respect to each cut line, to distribute routing area, and to actually construct the global wiring.

Ohmura, et al. [29] presented a hierarchical floor planning method that also determines global routes. Modules or cells are defined as either hard or soft. Hard modules have a defined shape and size (area). Soft modules have a defined size, but an unknown shape. The approach consists of two phases. First, an initial floor planning phase is performed to determine the basic topology of hard modules and sets of soft modules. It also allocates routing area for critical wires. Second, a detailed floor planning phase is executed to partition the sets of soft modules, to determine positions for the soft modules, and to assign global routes. The partitioning is performed so that the congestion of switchboxes and channels on the next level of hierarchy is reduced. The heuristic used is to partition each rectangular region such that the ratio of subpartition areas is equal to the ratio of nets entering the subpartitions. Only nets that enter a subpartition from outside the rectangular region and cross over an edge of the rectangular region that is parallel to the partition are considered for this metric.

Recently, Bapat [4] presented a method of merging placement and routing based on

a  $3 \times 3$  grid data model. The method computes and stores Steiner trees on the  $3 \times 3$  grid for later table look-up. The solution of the  $3 \times 3$  placement and routing abstraction starts with a random initial partition followed by random assignment of minimal length Steiner trees. Next, a algorithm similar to the Kernighan-Lin-Fiduccia-Mattheyses [19, 15] partitioning method is used to reduce net length through cell movements, to reduce congestion imbalance through selection of alternative minimum length Steiner trees, and to reduce congestion imbalance through cell movements. Problem abstractions within a level of hierarchy are solved independently and then the  $3 \times 3$  algorithm is applied to abstractions formulated across the original decomposition boundaries to combine the partial solutions.

Shragowitz, Lee, and Sahni [36] developed a system to combine placement and global routing for sea-of-gates design styles. A constructive placement is performed one slice at a time from left to right. Slices are connected subareas of the set of unused cell positions and need not be uniform or symmetric in either the horizontal or vertical directions. At each step, nets that connect the new slice and the previously placed portion of the circuit are assigned global routes. A maze router is used for the global routing and the position and size of the new slice may be adjusted to accommodate the routing.

Tzeng [43] implemented a method of combining routing and placement adjustment. Wiring results are stored in a global data structure and cell positions are maintained using a global triangulation graph. An initial constructive placement is derived using standard methods. Next, routing and placement adjustment are iterated. The router is a sophisticated area router based on a hierarchical  $2 \times n$  routing paradigm. The router is able to re-route existing wiring assignments, so its input may contain overlapping wires and partial routes. Placement adjustment is performed by using a one dimensional compaction algorithm on the triangulation graph. Congestion metrics from the routing are translated into spacing constraints on the graph. After placement adjustment, special care is taken to preserve as much of the previous wiring as possible. The resulting routing problem with possible conflicts and broken connections is presented to the router for another iteration. A final compaction step is performed using a more sophisticated compaction algorithm than in the placement adjustment phase.

#### 2.3 Unified Placement and Routing

The unified placement and routing problem remains intractable because of the size and complexity of current circuit designs. However, Burstein reported some attempts at solving the unified problem. His work consists of a basic technique for performing placement and routing in a plane [7] and a partitioning method to handle multiple wiring layers [8].

The basic technique consists of forming a planarized image of the circuit graph, converting this image into an annular embedding, and then finding a geometric realization of the circuit corresponding to the embedding. The last step is formulated as the problem of finding a system of polyominos that corresponds to the annular embedding such that the bounding box of the system is minimized. Channel or river routing must still be performed between the layout rings. The planarization step uses a heuristic  $O(m^2)$  algorithm (where m is the number of edges in the circuit graph) that attempts to minimize the crossing number of the graph. If input and output pins are required to be along chip boundaries, certain embedding choices may be influenced by the distribution of these pins. This method is interesting, but impractical for current circuits. Neither the planarization step nor the reduction to an annular embedding directly address layout constraints or goals and the transformations from planarized image to geometric implementation are overly restrictive.

The basic technique is extended to multiple layers by partitioning the circuit into as many planar parts as there are wiring layers. When possible, nets are routed using a single wiring layer; otherwise, vias are introduced and are treated as circuit cells to determine their placement. Each plane is processed using the basic technique. Consistent placement of cells and vias between planes can be guaranteed only if two wiring layers are used and if the embedding on one of the layers is acyclic.

#### 2.4 Summary

Merged approaches are interesting compromises in the attempt to integrate placement and routing phases. A unified approach would be ideal, but current unified problem formulations are either too simplistic or too complex to be practical. Coupled approaches have utility, but must restrict the possible placement modifications to avoid excessive rerouting. These restrictions place a premium on the performance of the initial placement phase which must execute in the absence of routing information. The placement adjust-

ments primarily re-space cells with out changing the basic cell topology much. Merged approaches are interesting because they can cover a wide range of integration possibilities. This characteristics provides a flexible structure for investigating the relationship between placement and routing and for exploring the possibility of solving a truly unified placement and routing problem. At one extreme, a merged approach can mimic a coupled approach by restricting permissible placement modifications. At the other extreme, a merged approach can solve placement and routing concurrently with the routing solution starting simultaneously with the placement solution. In between, lie many possibilities for placement and routing interaction and communication. Ideally, this interaction and communication should be used to avoid poor layout decisions or at least, to organize and structure the layout process for effective identification of poor decisions. Unfortunately, existing merged methods do not adequately emphasize this communication between phases. They may use routing information to influence subsequent placement decisions, but never use it to change previous decisions. Communication is further inhibited by the differences in data models used by each phase, and routing results are not always easily translated into new placement decisions.

The layout system presented in the following chapters is a merged hierarchical approach based on a common  $2 \times 2$  grid-graph data model. The hierarchical framework is used to analyze the relationship between placement and routing more closely than previous work and to investigate and compare different integration possibilities. The use of a common data model is intended to alleviate the communication problems of previous approaches and to allow the implementation of effective feedback mechanisms.

## Chapter 3

# **Algorithms**

The basic algorithmic approach of this research to solving the layout problem is to reduce or divide the original problem into smaller or simpler subproblems, solve the subproblems, and then combine the partial solutions to form an entire solution to the original problem. This approach is often referred to as a problem reduction or divide-and-conquer method [2] and techniques of this class are often used to deal effectively with large and complex problems. Within this framework, specific algorithms are used to solve the layout subproblems and the constraints between subproblems and to implement a rip-up and re-route capability.

Hierarchical decomposition is the particular form of divide-and-conquer technique implemented. Its distinguishing characteristics are that the original problem is decomposed into a set of subproblems of the same form and that the decomposition process is performed recursively on each subproblem until the subproblems become simple enough to solve immediately. A novel feature is that the hierarchical decomposition for all aspects of the layout problem uses the same  $2 \times 2$  grid-graph data model.

Decomposition of a subproblem into the next set of subproblems requires solving the layout problem for the corresponding  $2 \times 2$  abstraction. A quadrisection [40] style algorithm is used to solve the  $2 \times 2$  placement or partitioning problem and a linearly constrained nonlinear integer program is solved to generate the  $2 \times 2$  routing. This route assignment algorithm is an extension of Burstein's switchbox router [10].

Constraints between subproblems must be enforced in order to guarantee that partial solutions may be combined into a physically possible solution. These constraints are introduced through the use of special pin-pairs along the subproblem boundaries. These terminals are called *pseudo-pins* and the specification of their locations represents the required constraints on the partial solutions. The problem of determining pseudo-pin locations is called the *pseudo-pin assignment* problem.

The hierarchical decomposition is a constructive approach and the rip-up and re-route capability implemented is one example of a structured method for finding and modifying poor heuristic decisions. The procedure is based on the same  $2 \times 2$  abstraction as the other algorithms.

### 3.1 Hierarchical Decomposition

The hierarchical decomposition performs problem reductions of the layout problem based on a  $2 \times 2$  data model. The reduction continues recursively until the grids of the current data model abstraction correspond exactly to the desired final layout grid. Each reduction is based on the solution of the current abstraction.

#### 3.1.1 Common Data Model

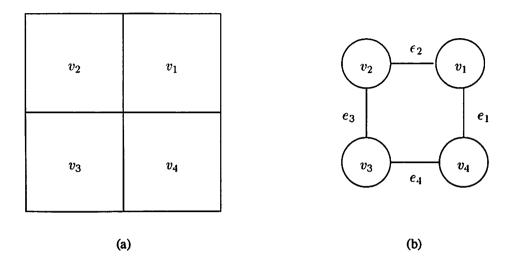

The data model used for the hierarchical decomposition of the layout area is the  $2 \times 2$  grid-graph. This graph was chosen as the simplest useful abstraction for layout subproblems. Using the same model for all aspects of the layout process simplifies management of the interaction between phases and increases the opportunities for combining phases.

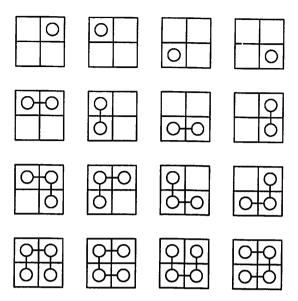

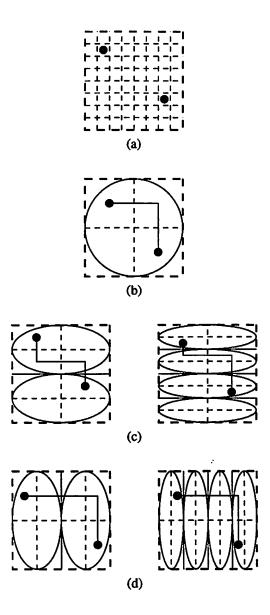

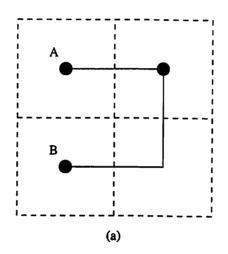

The  $2 \times 2$  data model is depicted in Figure 3.1 as both a set of grid cells and the standard grid-graph representation. The  $2 \times 2$  grid-graph is the graph  $G(\mathcal{V}, \mathcal{E})$ , consisting of vertices

$$\mathcal{V} = \{v_1, v_2, v_3, v_4\}$$

and undirected edges

$$\mathcal{E} = \{e_1, e_2, e_3, e_4\}$$

such that:

$$e_1 = (v_1, v_4),$$

$$e_2 = (v_2, v_1),$$

$$e_3 = (v_2, v_3),$$

$$e_4 = (v_3, v_4).$$

Figure 3.1: The  $2 \times 2$  data model represented as (a) a  $2 \times 2$  grid of cells and (b) the corresponding grid-graph.

This labeling of vertices and edges will be used in all subsequent discussion.

Choosing a data model involves compromising between simple problem formulation and useful progress towards a final solution. The 2×2 grid-graph is the simplest model that captures enough information to make two dimensional layout decisions. The model can be used to perform all aspects of layout from placement through routing, including feedback between phases, rip-up and re-place, rip-up and re-route, and pseudo-pin assignment on subproblem boundaries.

Improved layout quality requires effective communication between layout phases. Better communication is possible with a common data model because it provides a common reference frame for the different layout phases. A common reference frame simplifies and enhances information flow by reducing the amount of translation and interpretation required between phases. Using the same data model for all the layout phases provides opportunities for integrating the different layout phases in that information from each phase can be obtained for each subproblem abstraction concurrently.

#### 3.1.2 Problem Reduction

Problem reduction techniques create a tree or hierarchy of subproblems. Characterizing the relationship between the parts of this problem hierarchy and the original problem is useful for analyzing and describing algorithm features and effects. In these

experiments, the actual reduction is based on formation and solution of  $2 \times 2$  layout abstractions and corresponds to a decomposition of the layout region into subregions. An interesting feature of the problem hierarchy is that each subsequent level of subproblems represents a more detailed view of the original problem.

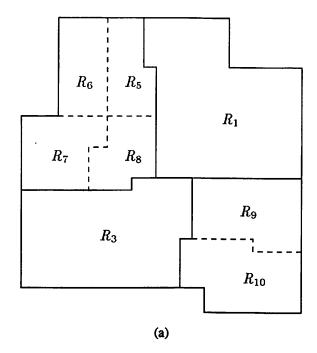

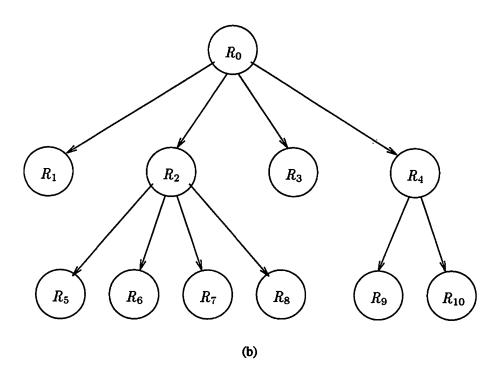

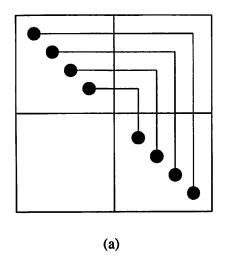

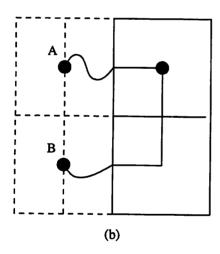

Hierarchy Hierarchical decomposition creates a problem hierarchy where each node represents the data model abstraction of the portion of the original problem corresponding to the subtree rooted at that node. This relationship is illustrated in Figure 3.2. The basic decomposition step physically partitions the region allocated to the original circuit into smaller subregions. The original problem corresponds to the root node,  $R_0$ , of the problem hierarchy. At the first decomposition step or level, the region of the original problem is divided into four subregions, corresponding to the four children subproblems  $R_1$ ,  $R_2$ ,  $R_3$ , and  $R_4$ . At the next level, subproblem  $R_2$  also is divided into four subproblems,  $R_5$  through  $R_8$ , while subproblem  $R_4$  is reduced to two subproblems,  $R_9$  and  $R_{10}$ .

Decomposition The decomposition or reduction of a layout problem into simpler subproblems requires forming an abstraction of the layout problem based on the data model, solving the abstraction, and then using the solution to create the appropriate subproblems. In this research,  $2 \times 2$  abstractions are formed based on a partitioning of the layout region into subregions. The solution of the abstraction depends on the particular application of the hierarchical decomposition method. Separate placement and routing phases can be implemented using this method or because the same data model is used for both phases, a combined placement and routing phase can be implemented. In the case of separate phases, subproblems are generated by solving the relevant aspect of the layout problem. However, in the following example, solutions to both placement and routing are used to illustrate the decomposition of the layout problem in general. Furthermore, in the case of routing, more information is desired for the generation of subproblems than is specified by the  $2 \times 2$  routing solution. Extra constraints on net crossing positions must be added to allow feasible combination of partial routing solutions.

The  $2 \times 2$  grid abstraction of a layout region depends on the determination of subregion shapes and sizes. In general, hierarchical decomposition does not require grid assumptions or straight partition boundaries [24], but in these experiments, for simplicity and efficiency, an underlying grid is assumed and straight line segments are used to divide

Figure 3.2: Hierarchical Decomposition. (a) The decomposition of a layout region and (b) the corresponding problem hierarchy.

regions between grid positions. In general, two line segments are chosen to divide a region into four subregions, corresponding to the four grid cells of the  $2 \times 2$  abstraction. One line segment partitions the region vertically and the other segment partitions the region horizontally. The line segment partitions are chosen to generate subregions of approximately equal area. This leads to a problem hierarchy of shorter height and a smaller total number of subproblems, reducing the amount of required computation. If the horizontal span of a region ranges from grid 0 to grid w-1, then a vertical line segment that lies between grid i-1 and grid i is chosen, where

$$i = \left\lceil \frac{w}{2} \right\rceil$$

.

An analogous calculation is performed to find the position of a horizontal line segment that partitions the region vertically. A value of zero for i indicates a degenerate abstraction. Degenerate  $2 \times 2$  abstractions are problems that are really  $1 \times 2$  or  $2 \times 1$  grids. A degenerate abstraction may be created intentionally depending on the aspect ratio of the problem region. If the height of the region is greater than or equal to twice the width of the region, then only a horizontal line segment will be chosen to partition the region vertically. Similarly, if the width of the region is greater than or equal to twice the height of the region, then only a vertical line segment will be chosen to partition the region horizontally.

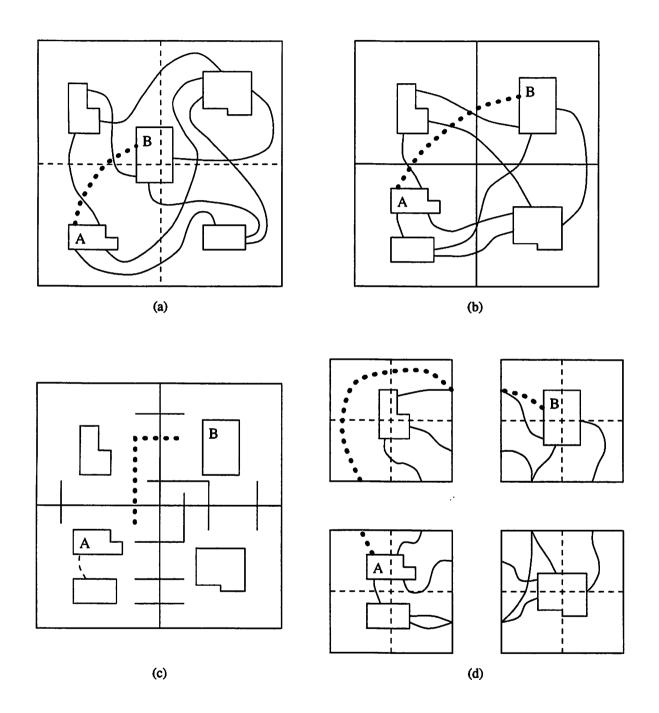

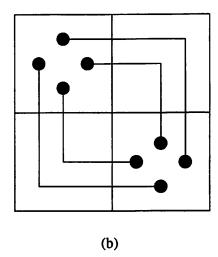

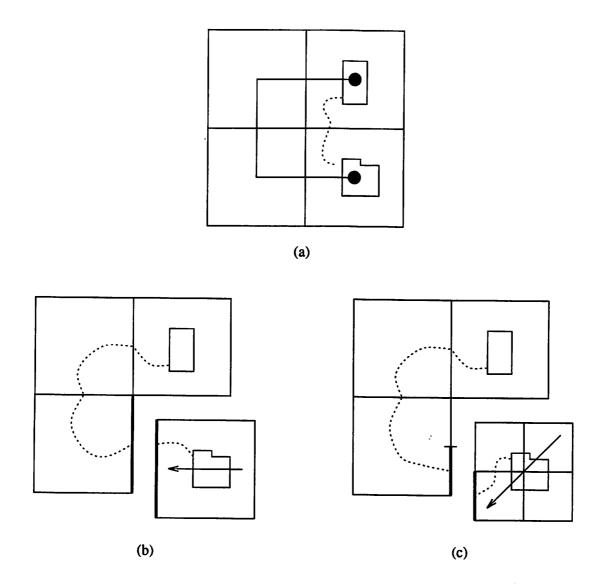

Figure 3.3 illustrates the decomposition of a layout problem into its constituent subproblems. Each decomposition step must reduce a problem to a set of subproblems of the same form. In general, this involves partitioning the layout region into subregions, assigning cells to each subregion, determining subnets for each subregion, and adding boundary consistency constraints so that subproblem solutions can be combined to form the whole solution.

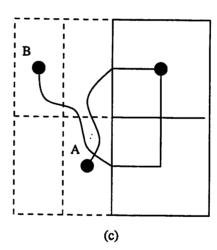

Figure 3.3 (a) shows a small example problem. The problem has five cells and nine nets. The cells are drawn with arbitrary positions for clarity and the curved lines connecting cells represent the unrouted nets. Cells A and B are labeled and the net connecting them is drawn with a different line style to help illustrate the decomposition process.

Figure 3.3 (b) shows the result of performing placement on the problem abstraction. Each cell has been assigned to one of the four grid cells as drawn. For example, cell A is assigned to the lower-left grid cell and cell B is assigned to the upper-left grid cell.

Figure 3.3 (c) shows the result of performing routing on the problem abstraction. The routing problem abstraction is formed by mapping each net of the original problem

Figure 3.3: Example decomposition step

in Figure 3.3 (a) into a corresponding abstract net. Since there are four possible locations on the  $2 \times 2$  grid, abstract nets may have one, two, three, or four terminals. An abstract net has a terminal located in a grid cell if the original net has at least one terminal in the corresponding subregion. Abstract nets with only one terminal are considered degenerate with respect to the current abstraction and are ignored. The net connecting cell A to its companion cell in the lower-left grid cell is an example of a degenerate net. In the figure, route assignments are represented by line segments that are drawn crossing the grid cell boundaries.

Figure 3.3 (d) shows the final reduction into subproblems. Each subproblem is a layout problem for the subregion represented by its corresponding grid cell. The subcircuit description for each subproblem is derived from the placement and routing results of the current abstraction. The cells of a subproblem are those cells assigned to its corresponding grid cell. Nets for each subproblem are derived from the route problem abstraction and the route assignments. Also, extra constraints are added on some of the pins of the subproblem nets so that the final solution may be realized. The reduction results in subproblems that have the same form as the original problem.

Subnets are generated from both the degenerate and nondegenerate nets of a problem. Degenerate nets of the current abstraction are nets of the subproblem corresponding to their terminal's location. For example, the degenerate net connected to cell A is a net of the lower-left subproblem. Whether or not degenerate nets are also degenerate with respect to their new subproblem abstraction depends on the subsequent placement. Other subproblem nets are derived from the current abstraction's route assignments. If the route of a net uses a grid cell, then a subnet corresponding to that portion of the route is present in the corresponding subproblem. For example, in Figure 3.3 (c) the net connecting cell A and cell B is assigned a route that uses the upper-right, upper-left, and lower-left grid cells. In Figure 3.3 (d), this net has been divided into three subnets and each subnet is included in the appropriate subproblem. The pins of subnets are derived from two sources. First, some pins are from the original net specification and are contained in the subproblem as a result of region decomposition or cell placement. Second, some pins are added to represent connection to other subnets. These pins are referred to as pseudo-pins and mark where subnets enter and exit subproblems.

Consistency constraints must be enforced on subnet entry and exit locations in adjacent subproblems to ensure the feasibility of combining partial solutions to form a

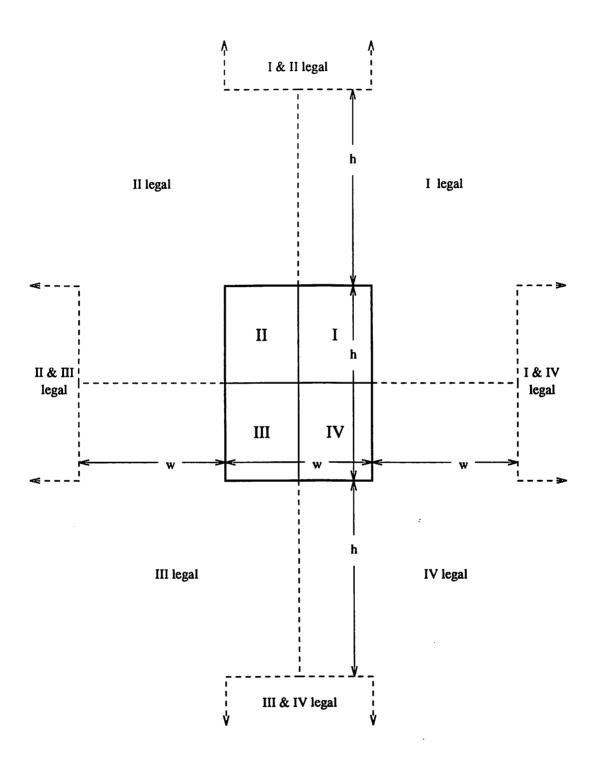

complete solution. Consider the net connecting cell A and cell B in Figure 3.3 (d). In the final solution, the exit location of the net from the lower-left subproblem must be consistent with its entry location into the upper-left subproblem. Similar constraints exist for all net crossings of common subproblem boundaries. These consistency constraints are introduced by assigning pseudo-pins in pairs corresponding to net crossings. Both pins in a pair must always have the same position with respect to the axis of their assigned boundary. Determination of this position is discussed in Section 3.3. Based on the  $2 \times 2$  routing solution, a pseudo-pin's final position may lie anywhere along the extent of its assigned boundary. In the figure, pseudo-pin locations have been refined just enough to determine grid positions on the next level of subproblem abstractions. Pseudo-pins assigned to a particular grid are drawn connected to the midpoint of the appropriate boundary.

Interpretation Hierarchical decomposition can be viewed as a gradual refinement of the layout solution. At higher levels of abstraction, solving the  $2 \times 2$  placement problem can be thought of as solving the partitioning or global placement problem. Similarly, solving  $2 \times 2$  routing problem abstractions solves global routing problems. Subsequent decomposition and abstraction in the hierarchy create more detailed views of the problem. Thus, the solution to each subsequent level of subproblems represents a further refinement of the solution to the original problem.

## 3.2 Subproblem Solution

The problem reduction step of the hierarchical decomposition depends on solving the layout problem for each  $2 \times 2$  abstraction. Solving placement and routing simultaneously on each  $2 \times 2$  abstraction would effect a unified approach to the layout problem. This possibility is discussed further in Section 6.1, but unfortunately, still remains intractable. Alternately,  $2 \times 2$  placement and  $2 \times 2$  routing may be solved separately. The level of placement and routing integration can be managed by using the problem hierarchy to control setup and feedback information for each subproblem abstraction. Solving placement and routing immediately for each subproblem implements a kind of merged placement and routing approach that solves the two phases concurrently, while solving the entire hierarchy of placement subproblems before solving the routing subproblems is equivalent to using separate phases.

#### 3.2.1 Cell Assignment

Placement of a given circuit net list on the  $2 \times 2$  grid-graph,  $G(\mathcal{V}, \mathcal{E})$ , requires that each cell be assigned to one of the four grid-graph vertices subject to admissibility constraints. Given a circuit description, let

$$\mathcal{M} = \{m_1, \ldots, m_M\}$$

be the set of modules (or cells) and let

$$\mathcal{N} = \{n_1, \ldots, n_N\},\,$$

be the set of nets. Placement is equivalent to partitioning  $\mathcal{M}$  into four partition blocks such that each block corresponds to a vertex of G. In this research, the partition is normally generated using a quadrisection algorithm similar to that described by Suaris and Kedem [40]. The exceptions occur for small, detailed abstractions where an exhaustive search is used instead.

Cell-to-vertex assignments are admissible if the set of cells assigned to a particular vertex does not exceed the vertex's limit. Each vertex corresponds to a particular region of the layout and the number of cells that may be placed legally within the region depends on the size and shape of the region and the size and shape of the cells. Cell size and shape are modeled as a single weight value. For a cell  $m_i$ , this value is denoted  $weight(m_i)$ . The area and design rule dependent constraints on legal cell placement are translated into limits on the total cell weight that can be assigned to each vertex. For a vertex  $v_j$ , this constraint is denoted  $limit(v_i)$ .

#### **Partitioning**

The partitioning algorithm assigns cells to vertices of G by dividing  $\mathcal{M}$  into four disjoint sets of cells such that each set corresponds to a vertex of G. If the set of cells assigned to  $v_j$  is denoted as  $\mathcal{M}_{v_j}$ , then a partition of cells can be represented as the vector

$$\vec{P} = (\mathcal{M}_{\nu_1}, \mathcal{M}_{\nu_2}, \mathcal{M}_{\nu_3}, \mathcal{M}_{\nu_4}).$$

Define the area of a partition block  $\mathcal{M}_{v_1}$  as

$$area(\mathcal{M}_{v_j}) = \sum_{m_k \in \mathcal{M}_{v_j}} weight(m_k),$$

and let the area limit for a partition block  $\mathcal{M}_{v_j}$  be the cell weight limit of  $v_j$ ,

$$limit(\mathcal{M}_{v_j}) = limit(v_j).$$

Also, associate with each cell is a set of legal partition block assignments,

$$\mathcal{L}_{m_i} = \{\mathcal{M}_{v_i} | \text{ cell } m_i \text{ may be assigned to } v_i \}.$$

In these experiments, the weight value of a cell is the number of placement grid locations the cell occupies and the weight limit of a vertex is the total number of placement grid locations contained in its corresponding subregion.

For uniform cell sizes, the definitions given above are sufficient to satisfy the placement admissibility constraints, but extra constraints on the distribution of area between partition blocks are often useful. Let

$$target(\mathcal{M}_{v_1})$$

be the desired area of  $\mathcal{M}_{v_j}$ , and let  $\epsilon$  be the maximum error limit between the actual area of a partition block and its target value.

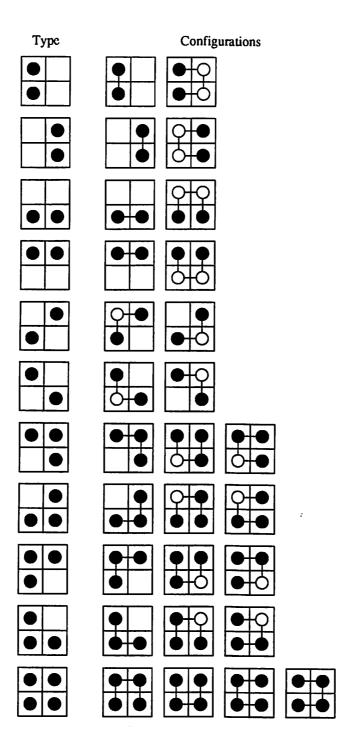

The objective is to minimize the partition cut weight

$$W(\vec{P}) = \sum_{n_i \in \mathcal{N}} w_{n_i}(t^{n_i})$$

where  $w_{n_i}$  is a weight function for the net  $n_i$  that depends only on  $t^{n_i}$ , the abstract net type of  $n_i$ . With respect to  $G(\mathcal{V}, \mathcal{E})$ , an abstract net type is a subset of  $\mathcal{V}$  and the abstract net type for a net  $n_i$  contains vertex  $v_j$  if the subregion corresponding to  $v_j$  contains at least one terminal of  $n_i$ .

Given a net list, the partitioning algorithm returns an optimal partition  $\vec{P}^*$  of minimal cut weight  $W(\vec{P}^*)$  that satisfies:

$$\begin{aligned} area(\mathcal{M}_{v_j}) &\leq limit(\mathcal{M}_{v_j}) \ \forall \ v_j \ , \\ \left| area(\mathcal{M}_{v_j}) - target(\mathcal{M}_{v_j}) \right| &\leq \epsilon & \forall \ v_j \ , \\ \mathcal{M}_{v_j} &\in \mathcal{L}_{m_i} & \forall \ m_i \in \mathcal{M}_{v_j}. \end{aligned}$$

The quadrisection partitioning algorithm is a min-cut [19] class algorithm. The algorithm starts by generating an initial partition of cells. Then, iterative improvement passes are applied to the partition until no further reduction in partition cut weight results.

```

initialize;

while ( a free cell can be moved ) {

remove cell with largest gain from gain tables;

lock cell in new partition block;

update gains of affected cells;

keep track of best partition;

}

use best partition found;

```

Figure 3.4: Basic quadrisection algorithm pass

Each improvement pass can be performed in O(P) time where P is the number of pins in the circuit. In practice, the overall algorithm is quite fast because the number of required improvement passes is usually less than four or five.