### Copyright © 1994, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# SUPERCONDUCTING FLASH-TYPE ANALOG-TO-DIGITAL CONVERTERS WITH MULTI-GIGAHERTZ PERFORMANCE

by

Howard Cam Luong

Memorandum No. UCB/ERL M94/61

29 August 1994

# SUPERCONDUCTING FLASH-TYPE ANALOG-TO-DIGITAL CONVERTERS WITH MULTI-GIGAHERTZ PERFORMANCE

by

Howard Cam Luong

Memorandum No. UCB/ERL M94/61

29 August 1994

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# SUPERCONDUCTING FLASH-TYPE ANALOG-TO-DIGITAL CONVERTERS WITH MULTI-GIGAHERTZ PERFORMANCE

by

Howard Cam Luong

Memorandum No. UCB/ERL M94/61

29 August 1994

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### **Abstract**

## Superconducting Flash-Type Analog-To-Digital Converters With Multi-Gigahertz Performance

by

#### **Howard Cam Luong**

Doctor of Philosophy in Electrical Engineering and Computer Science

University of California at Berkeley

Professor Theodore Van Duzer, Chair

This dissertation presents the design, fabrication, and testing of a fully parallel analog-to-digital converter in Josephson technology that can operate at multi-gigahertz clock and input frequencies with a total power consumption less than 1mW. Compared to the best analog-to-digital converters available in semiconductor technology, this converter performs at least one order of magnitude better in terms of both speed and power consumption.

One-junction SQUIDs (Superconducting Quantum Interference Devices) are used to introduce very sharp, narrow pulses to the comparators to achieve a very small aperture time for the converter. With a junction critical current density of 1 kA/cm<sup>2</sup>, an aperture time as small as 4 ps can be achieved, which makes it feasible to implement a high-performance ADC with 10 GHz clock frequency, 5 GHz input bandwidth, and 4-bit resolution. A completely new ultra-fast logic family, capable of operating at frequencies up to 12.5 GHz, has also been designed based on the comparator building block and has been used to implement the thermometer-to-binary encoder required for the flash ADC.

The comparators and the logic gates have been fully tested, and their correct operations have been verified experimentally at clock frequencies up to 3 GHz, which is limited by our existing test equipment. A three-bit quantizer and a three-bit thermometer-to-binary encoder have been successfully demonstrated. However, due to the process variations in junction critical currents, circuits with larger sizes and more complexity, including a four-bit quantizer, a three-bit ADC, a four-bit ADC, and a pseudo-random bit sequence generator, were only partially functional. All design and testing issues at multigigahertz frequencies are discussed and possible approaches are proposed.

Finally, as an outline for potential future research, the last part of the dissertation discusses our work on another fully parallel ADC originally designed by Petersen and our preliminary study on the feasibility of implementing an ADC with higher resolution using a multi-step subranging architecture.

T. Van Duzer

Chairman of committee

To my parents and my siblings

### TABLE OF CONTENTS

| TABLE OF CONTENTS                                         | iv        |

|-----------------------------------------------------------|-----------|

| LIST OF FIGURES                                           | viii      |

| LIST OF TABLES                                            | xiii      |

| ACKNOWLEDGEMENT                                           | xiv       |

| CHAPTER 1: INTRODUCTION                                   | 1         |

| 1.1 Background and Motivation                             | 1         |

| 1.2 Thesis Organization                                   | 2         |

| CHAPTER 2: OVERVIEW OF ADC ARCHITECTURES                  | 4         |

| 2.1 Serial-Type (Integrating) Analog-To-Digital Converter | 7         |

| 2.2 Parallel (Flash) Analog-To-Digital Converter          | 8         |

| 2.3 Successive-Approximation Analog-To-Digital Converter  | 10        |

| 2.4 Multi-Step Subranging Analog-To-Digital Converter     | 12        |

| 2.5 Pipelined Analog-To-Digital Converter                 | 14        |

| CHAPTER 3: JOSEPHSON FLASH-TYPE ANALOG-TO-DIGITAL CONV    | ERTERS 16 |

| 3.1 Motivation                                            | 16        |

| 3.2 Fundamentals of Josephson Junctions                   | 20        |

| 3.2.1 Circuit Model and IV Characteristic Curve           | 22        |

| 3.2.2 Junction Switching Characteristic                   | 25        |

| 3.2.3 One-Junction SQUID                                  | 29        |

| 3.2.4 Two-Junction SQUID                                  | 31        |

| 3.3 Periodic-Threshold Flash Analog-To-Digital Converters | 33        |

| 3.3.1 Designs Using Two Or Three-Junction SQUIDs          | 35        |

| 3.3.2 Designs Using Quasi-One-Junction SQUIDs             | 38        |

| CHAPTER 4: DESIGN OF FULLY PARALLEL JOSEPHSON ADC42     |

|---------------------------------------------------------|

| 4.1 Fully Parallel ADC Architecture                     |

| 4.2 Comparator Design                                   |

| 4.3 Logic Gates                                         |

| 4.4 Thermometer-To-Binary Encoder 55                    |

| 4.5 Complete Analog-To-Digital Converters               |

| 4.6 Summary                                             |

| CHAPTER 5: PERFORMANCE OF FULLY PARALLEL JOSEPHSON ADC  |

| 5.1 Low -Speed Performance                              |

| 5.1.1 Two-Bit Quantizer and Two-Bit Binary Encoder      |

| 5.1.2 Three-Bit Quantizer and Three-Bit Binary Encoder  |

| 5.1.3 Four-Bit Quantizer                                |

| 5.1.4 Three-Bit Analog-To-Digital Converter             |

| 5.1.5 Four-Bit Analog-To-Digital Converter              |

| 5.2 High-Speed Signal Reconstruction                    |

| 5.3 High-Speed Tests on Comparators                     |

| 5.4 High-Speed Tests on Logic Gates                     |

| 5.5 High-Speed Test Setup                               |

| 5.6 Evaluation of High-Speed ADC Performance            |

| 5.7 Summary                                             |

| CHAPTER 6: ULTRA-FAST JOSEPHSON LOGIC FAMILY104         |

| 6.1 Speed Limitation of Latching Logic Gates            |

| 6.2 New Ultra-Fast Logic Family                         |

| 6.2.1 Modification of Logic Gates for Optimal Speed     |

| 6.2.2 Step-By-Step Design of Circuit Parameters         |

| 6.2.3 Optimization of Circuit Parameters                |

| 6.3 Testing The Ultra-Fast Logic Family                 |

| 6.3.1 Overview of Pseudo-Random Bit Sequence Generator  |

| 6.3.2 Design of a Pseudo-Random Bit Sequence Generator  |

| 6.3.3 Testing of a Pseudo-Random Bit Sequence Generator |

| 6.4 Summary                                             |

| CHAPTER 7: HIGH-SPEED DESIGN AND TESTING ISSUES          | 128 |

|----------------------------------------------------------|-----|

| 7.1 Cross-Talk                                           | 129 |

| 7.1.1 Signal Reflection Due To Impedance Mismatch        |     |

| 7.1.2 Supply Variation Due To Junction Switching         |     |

| 7.1.3 Mutual Inductive and Capacitive Coupling           | 136 |

| 7.1.4 Ground Noise (Ground Bounce)                       |     |

| 7.2 Clock Distribution                                   | 139 |

| 7.3 Testing Issues                                       | 141 |

| 7.3.1 High-Speed Probe                                   | 141 |

| 7.3.2 Flux Trapping                                      | 142 |

| 7.3.3 Magnetic Shielding                                 | 143 |

| 7.4 Summary                                              | 145 |

| CHAPTER 8: BRIDGE-TYPE JOSEPHSON ADC                     | 146 |

| 8.1 Architecture                                         | 146 |

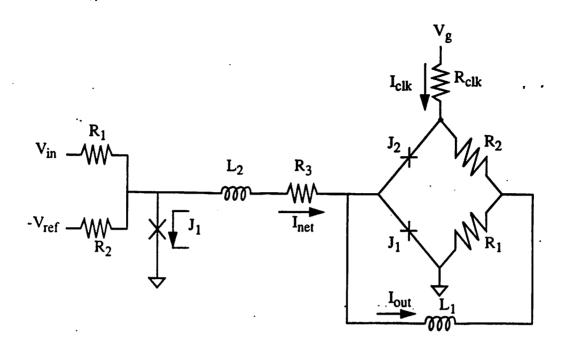

| 8.2 Design Of Bridge-Type Comparators                    |     |

| 8.2.1 Bridge-Type Comparator                             | 147 |

| 8.2.2 Design Of Limiter Circuits                         | 148 |

| 8.2.3 Design Of Sine-Shaped Junctions For Limiters       |     |

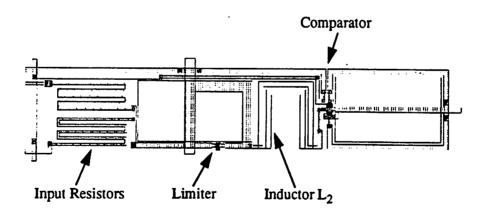

| 8.2.4 Design And Layout Of The Comparator With A Limiter | 153 |

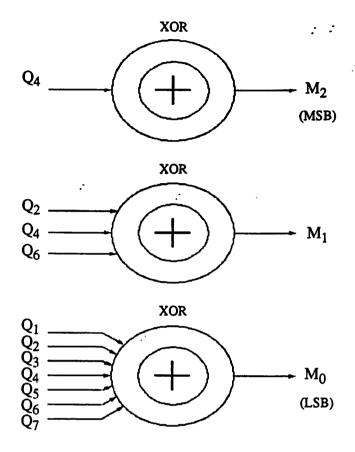

| 8.3 Design Of The Thermometer-To-Binary Encoder          | 153 |

| 8.4 Design And Performance Of The Complete Converter     | 159 |

| 8.5 Summary                                              | 165 |

| CHAPTER 9: PROPOSAL OF MULTI-STEP SUBRANGING ADC         | 167 |

| 9.1 Subranging Architecture                              | 167 |

| 9.2 Digital-To-Analog Converter (DAC)                    |     |

| 9.2.1 DAC Implementation in Superconducting Technology   |     |

| 9.2.2 Calibration of Current Sources for DAC Using CMOS  |     |

| 9.3 Sample-And-Hold Circuit                              | 181 |

| 9.4 Subtractor And Amplifier                             | 183 |

| 9.5 Summary                                              |     |

| CHAPTER 10: CONCLUSION                                   | 185 |

| REFERENCE                                                |     |

|                                                          |     |

| APPENDIX A: SQUID THRESHOLD CURVES                         | 197         |

|------------------------------------------------------------|-------------|

| A.1 One-Junction SQUID                                     | 197         |

| A.2 Two-Junction SQUID                                     | 198         |

| A.3 Lagrange Multiplier Method                             | 199         |

| APPENDIX B: PERFORMANCE EVALUATION OF HIGH-SPEED ADCS      | <b>2</b> 02 |

| B.1 Reconstruction and Fitting.                            | 202         |

| B.2 Code-Density Test                                      | 204         |

| B.3 Signal-To-Noise Ratio Test                             | 205         |

| B.4 ADC's Jitter Effect                                    | 206         |

| APPENDIX C: C PROGRAMS FOR LAYOUT GENERATION & DATA ANALYS | IS208       |

| C.1 Program For Rectangular Junction Layouts               | 208         |

| C.2 Program For Sinusoidal-Shaped Junction Layouts         | 210         |

| C.3 Program For Resistor Layouts                           | 213         |

| C.4 Program For ADC'S Data Reconstruction                  | 214         |

| C.5 Program For Calculation Of The Best Fitting Sine Curve | 216         |

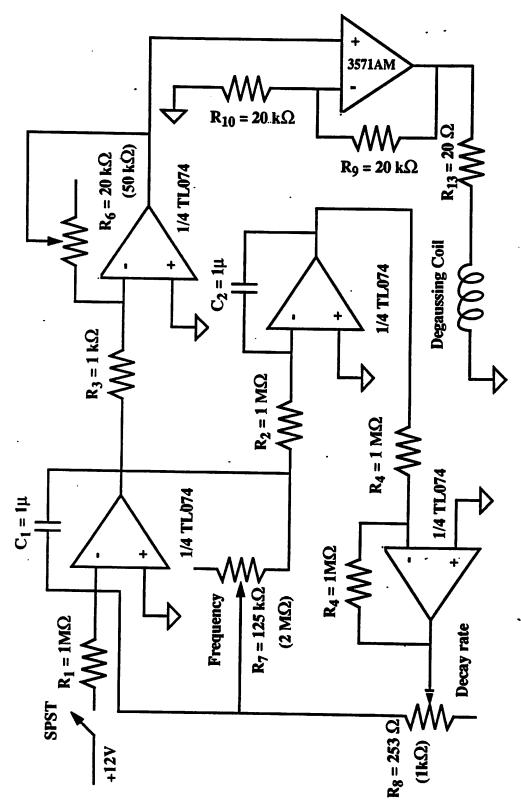

| APPENDIX D: SETUP AND DESIGN FOR THE DEGAUSSER             | 220         |

### **LIST OF FIGURES**

| Fig. 2.1  | Bit resolution vs. speed of various ADC architectures (from [1])                   | •     |

|-----------|------------------------------------------------------------------------------------|-------|

| Fig. 2.2  | Architecture for integrating (serial-type) analog-to-digital converter             |       |

| Fig. 2.3  | Fully parallel (flash) analog-to-digital converter                                 | ••••• |

| Fig. 2.4  | Architecture for successive-approximation analog-to-digital converter              |       |

| Fig. 2.5  | Example of a three-bit successive approximation.                                   |       |

| Fig. 2.6  | Multi-step subranging ADC architecture                                             |       |

| Fig. 2.7  | Illustration of how a three-stage subranging ADC works                             |       |

| Fig. 2.8  | Pipelined analog-to-digital converter architecture                                 |       |

| Fig. 3.1  | Configuration of a sandwich-type Josephson junction.                               |       |

| Fig. 3.2  | Schematic symbol and circuit model for a Josephson junction.                       |       |

| Fig. 3.3  | IV characteristic curve of a typical Josephson junction                            |       |

| Fig. 3.4  | Illustration of a hysteretic IV curve of a junction with $\beta_c = 4$ (from [11]) |       |

| Fig. 3.5  | Supply current (top) and voltage (bottom) across a Josephson junction              |       |

| Fig. 3.6  | Schematic and dc transfer curve of a one-junction SQUID.                           |       |

| Fig. 3.7  | Circuit schematic and threshold curves of a two-junction SQUID.                    |       |

| Fig. 3.8  | Architecture implementation for a four-bit periodic-threshold ADC                  |       |

| Fig. 3.9  | Use of SQUID's periodic threshold curve to implement a comparator                  |       |

| Fig. 3.10 |                                                                                    |       |

| Fig. 3.11 | Periodicity of the junction current of a one-junction SQUID.                       |       |

| Fig. 3.12 | Quasi-one-junction SQUID.                                                          |       |

| Fig. 3.13 | Circuit diagram of comparator using quasi-one-junction SQUID.                      |       |

| Fig, 4.1  | Fully parallel (flash) analog-to-digital converter.                                |       |

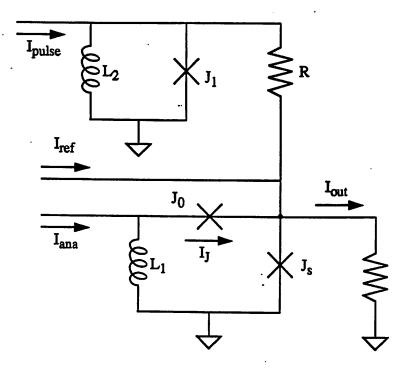

| Fig. 4.2  | Simplified schematic of the current-latched comparator                             |       |

| Fig. 4.3  | Graphical illustration of how the current-latched comparator works.                |       |

| Fig. 4.4  | Complete schematic diagram of the current-latch comparator.                        |       |

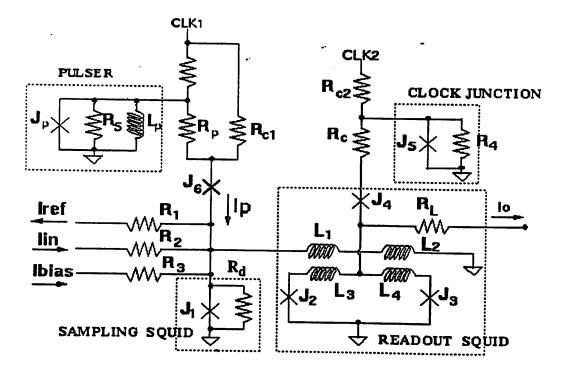

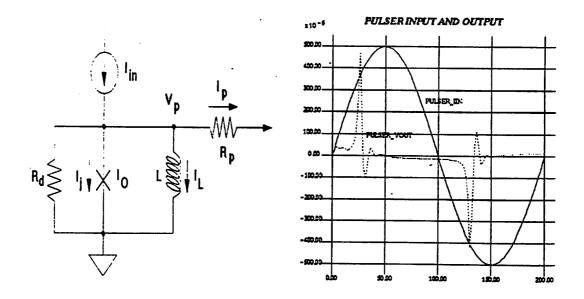

| Fig. 4.5  | One-junction SQUID as a pulser for a minimum aperture time.                        |       |

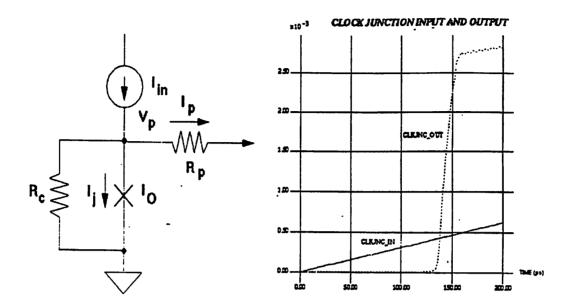

| Fig. 4.6  | Clock-shaping junction to obtain a clock with very sharp rising edge.              |       |

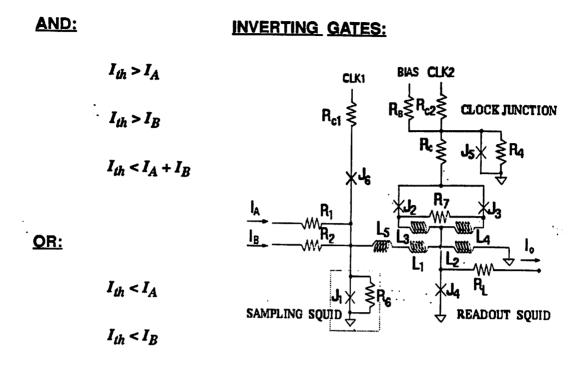

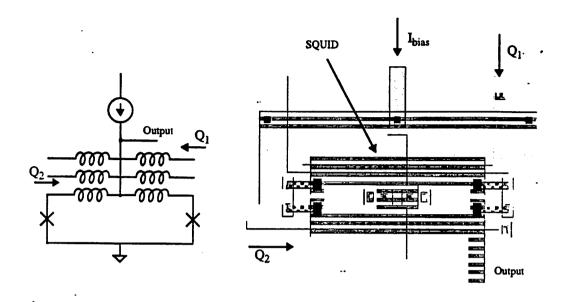

| Fig. 4.7  | Implementation of logic gates from the comparator building block                   |       |

|           | <b>₩</b>                                                                           |       |

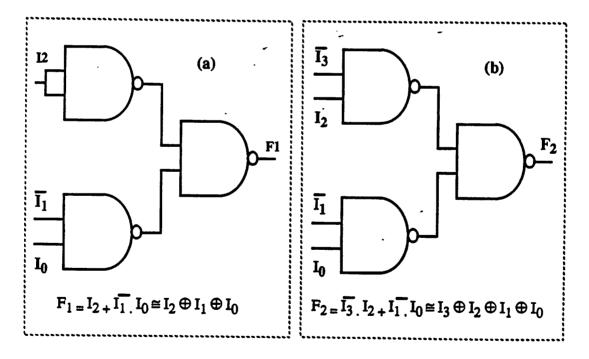

| Fig. 4.9  | Boolean logic functions for the output bits of a four-bit binary encoder         | 56         |

|-----------|----------------------------------------------------------------------------------|------------|

| Fig. 4.10 | Implementation of (a) quasi-three-input XOR and (b) quasi-four-input XOR         | 57         |

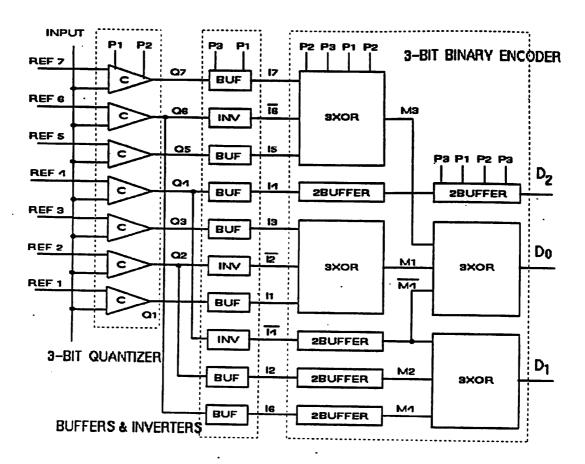

| Fig. 4.11 | Block diagram of a complete three-bit analog-to-digital converter.               | <b>6</b> 0 |

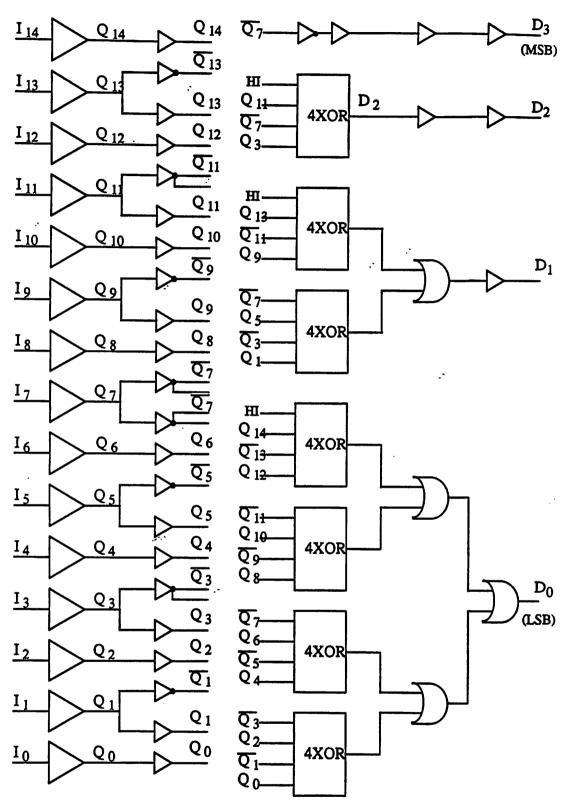

| Fig. 4.12 | Block diagram of a complete 4-bit fully parallel analog-to-digital converter     | 61         |

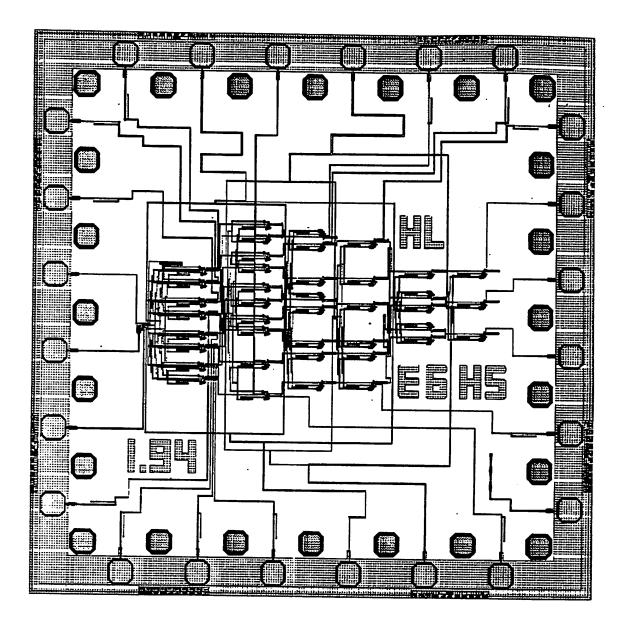

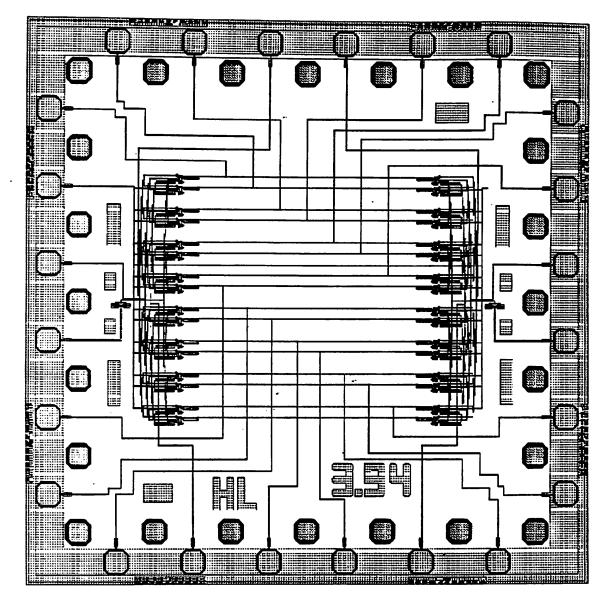

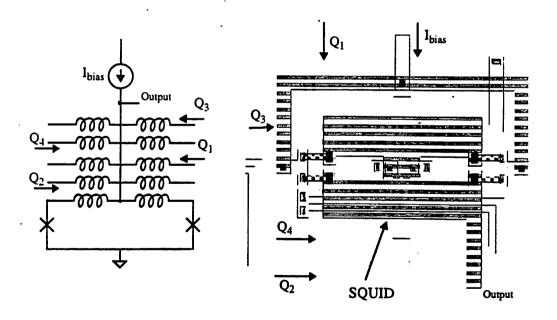

| Fig. 4.13 | Chip layout of the 3-bit analog-to-digital converter for high-speed testing      | 62         |

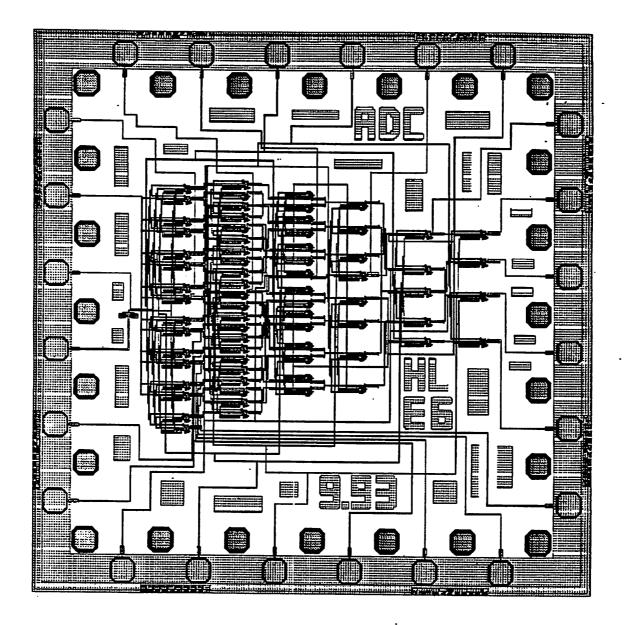

| Fig. 4.14 | Chip layout of the 4-bit analog-to-digital converter for high-speed testing      | 63         |

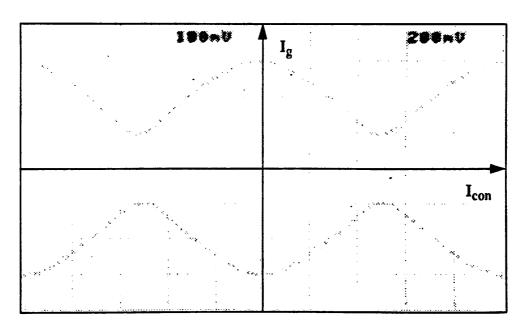

| Fig. 5.1  | Measured threshold curve for the readout two-junction SQUID.                     | <b>6</b> 6 |

| Fig. 5.2  | Measured threshold curve for the readout SQUID with the edge-triggering          |            |

|           | junction.                                                                        | 67         |

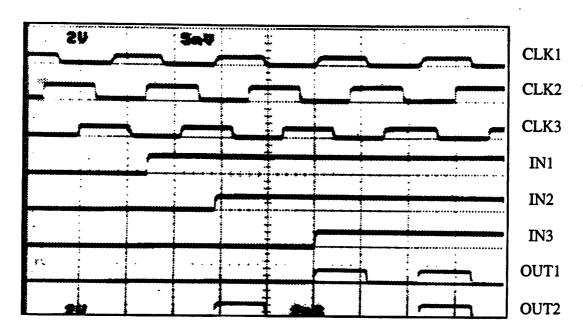

| Fig. 5.3  | Testing results for the three-input quasi-XOR gate shown in Fig. 4.10            | 68         |

| Fig. 5.4  | Test results verifying the correct function of a two-bit quantizer.              | 69         |

| Fig. 5.5  | Measurement of a two-bit thermometer-to-binary encoder                           | 70         |

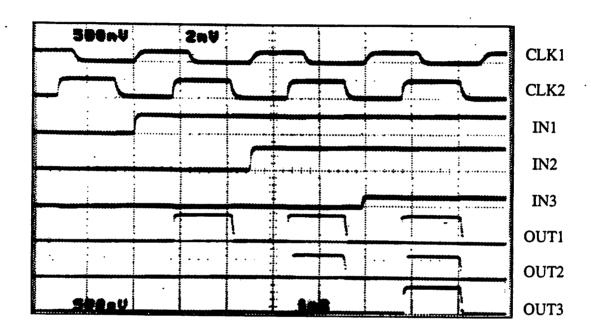

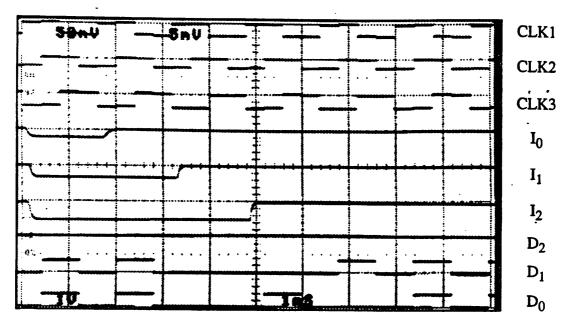

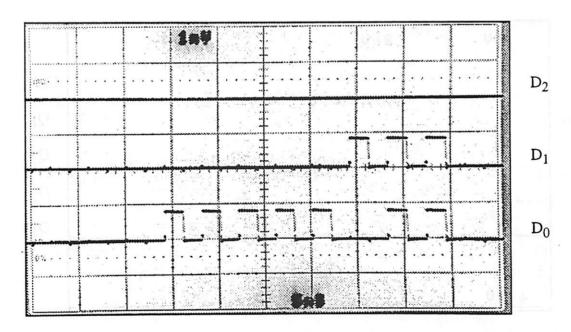

| Fig. 5.6  | Experimental results verifying the correct operation of a three-bit quantizer    | 71         |

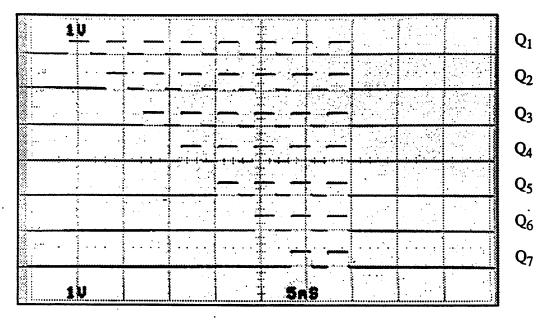

| Fig. 5.7  | Measurement of three-bit thermometer-to-binary encoder for the first four        |            |

|           | patterns shown in Table 5.1. The three middle traces are the three inputs with   |            |

|           | least significant level. All other inputs are low                                | 72         |

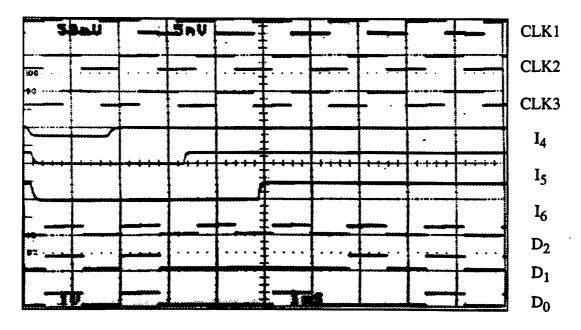

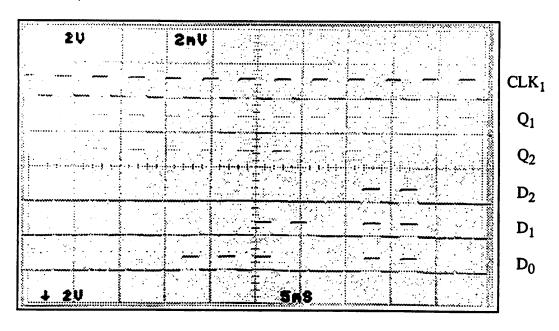

| Fig. 5.8  | Measurement of 3-bit thermometer-to-binary encoder for the last four patterns    |            |

|           | shown in Table 5.1. The three middle traces are the three inputs with most       |            |

|           | significant level. All other inputs are high.                                    | <b>7</b> 2 |

| Fig. 5.9  | Chip layout of two four-bit quantizers connected for a redundant scheme          | 74         |

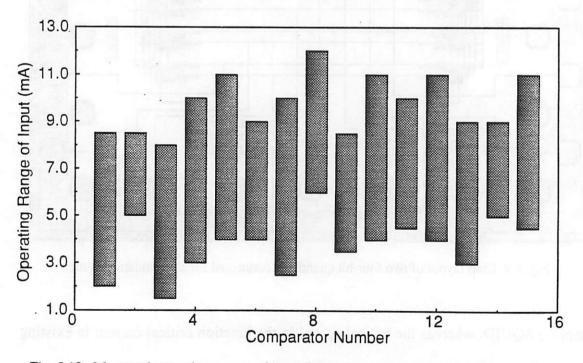

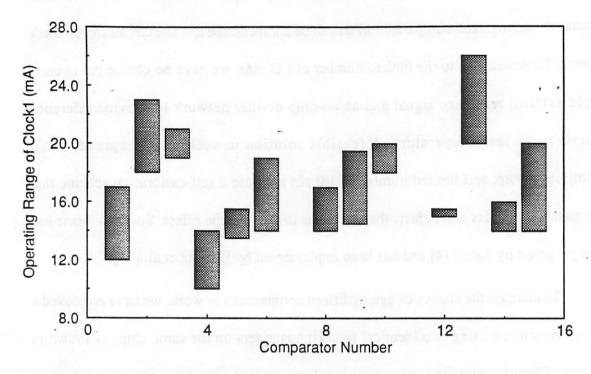

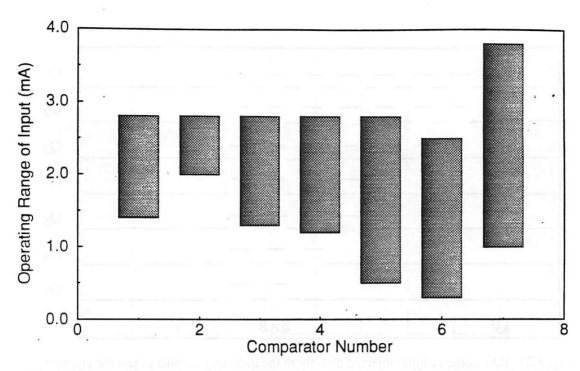

| Fig. 5.10 | Measured operating ranges of input for each comparator in a four-bit quantizer   | 75         |

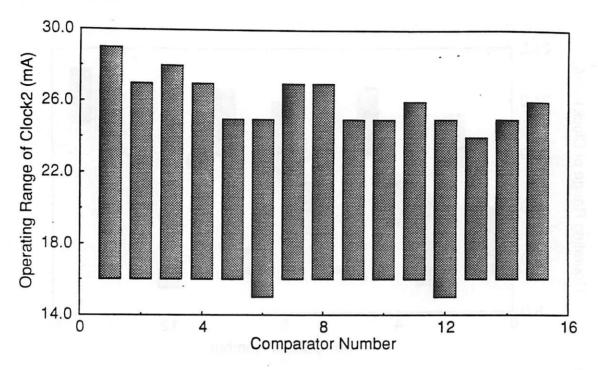

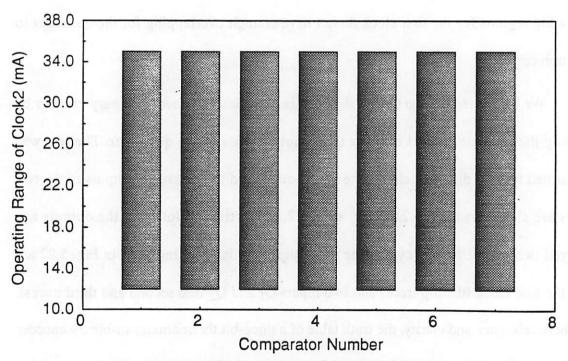

| Fig. 5.11 | Measured operating ranges of Clock 2 for each comparator in a four-bit quantizer | 76         |

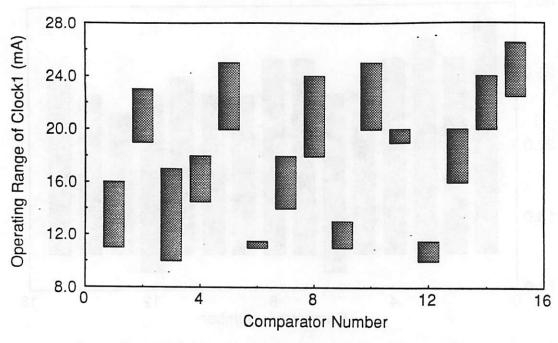

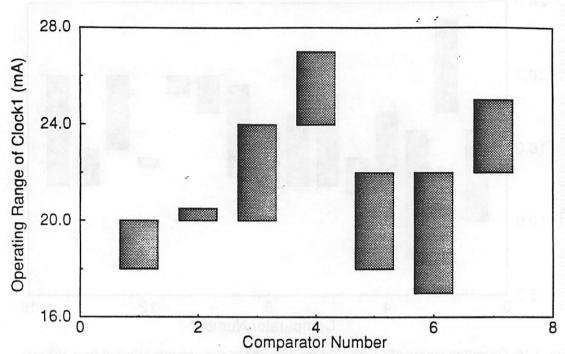

| Fig. 5.12 | Measured operating ranges of Clock 1 for each comparator in a four-bit quantizer | 77         |

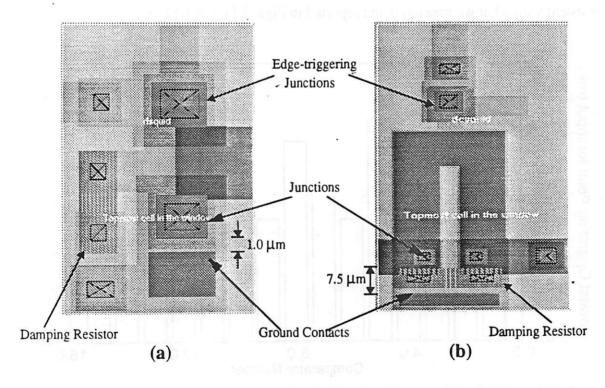

| Fig. 5.13 | Layouts of (a) one-junction SQUID and (b) two-junction SQUID showing the         |            |

|           | spacing between the junctions and the ground contacts                            | 78         |

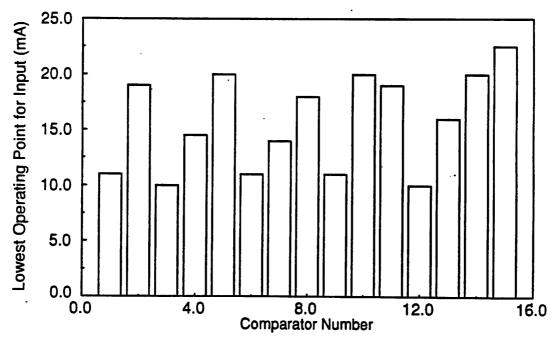

| Fig. 5.14 | Measured lowest operating point for the input for each comparator in a four-bit  |            |

| •         | quantizer.                                                                       | 79         |

| Fig. 5.15 | Measured operating ranges of Clock 1 for the redundant four-bit quantizer        | 81         |

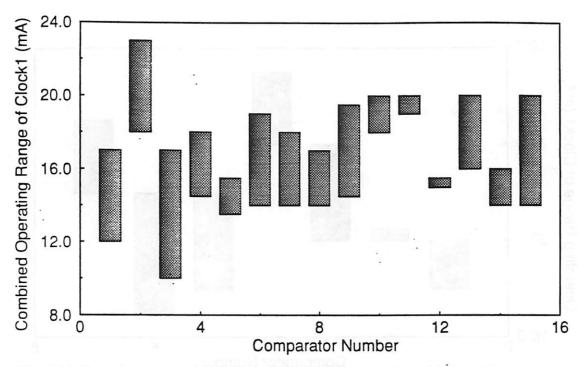

|           | Operating ranges of Clock 1 for the best fifteen comparators selected from the   |            |

|           | two four-bit quantizers                                                          | 82         |

| Fig. 5.17 | Operating ranges of Clock 1 for the seven comparators in the three-bit ADC       |            |

|           | Operating ranges of Clock 2 for the seven comparators in the three-bit ADC       |            |

|           |                                                                                  |            |

| Fig. 5.19 | Operating ranges of the input for the seven comparators in the three-bit ADC 84                           |

|-----------|-----------------------------------------------------------------------------------------------------------|

| Fig. 5.20 | Measured outputs of the ADC (Chip #1) with thermometer input shown in Fig.                                |

|           | 5.21 being injected directly to the quantizer outputs                                                     |

| Fig. 5.21 | Thermometer input injected directly to the quantizer outputs to test the encoder 85                       |

| Fig. 5.22 | Measured outputs of the ADC (Chip #2) with thermometer input shown in Fig.                                |

|           | 5.21 being injected directly to the quantizer outputs                                                     |

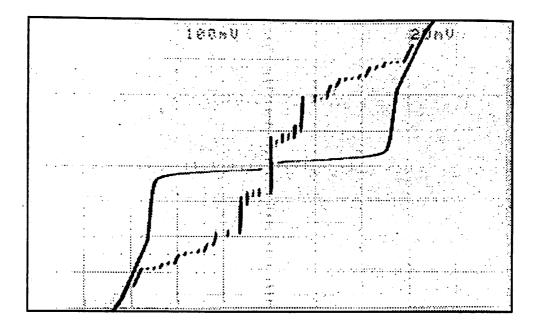

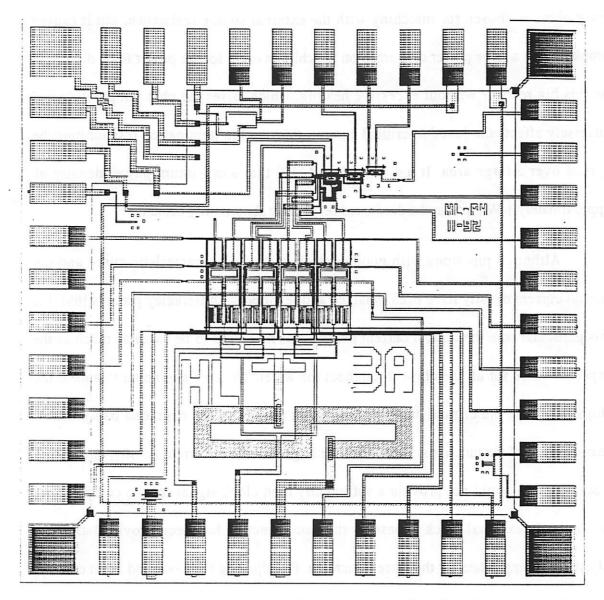

| Fig. 5.23 | Measured IV curve of a series array of Josephson junctions listed in Table 5.3 88                         |

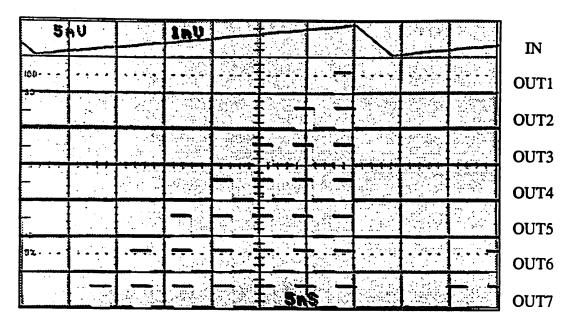

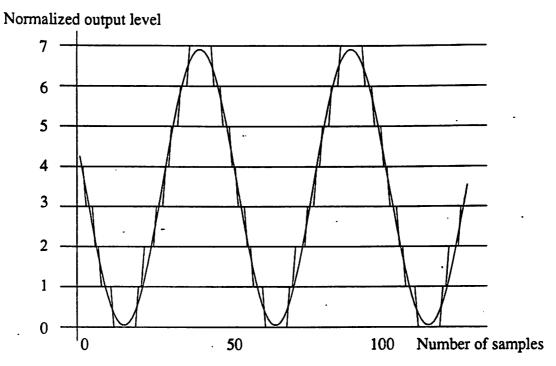

| Fig. 5.24 | Reconstructed and fitted signals for 3-bit ADC, $f_{clk} = 2$ GHz, $f_{in} = 980$ MHz 90                  |

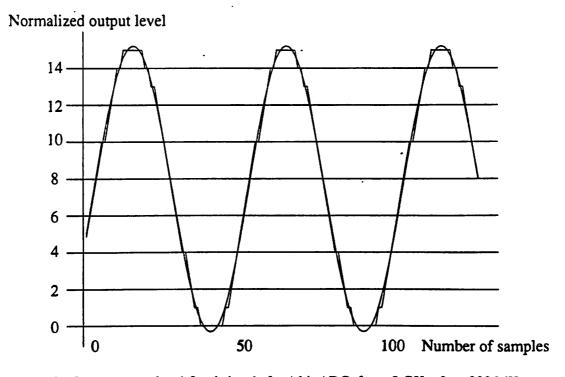

| Fig. 5.25 | Reconstructed and fitted signals for 4-bit ADC, $f_{clk} = 2 \text{ GHz}$ , $f_{in} = 980 \text{ MHz}$ 90 |

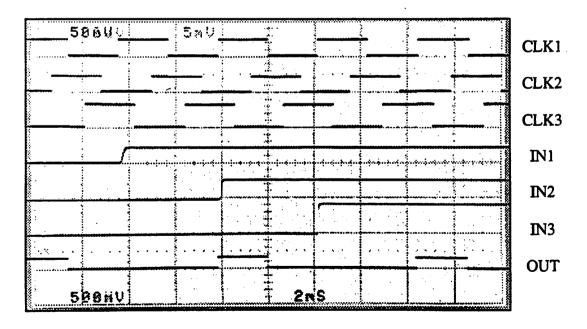

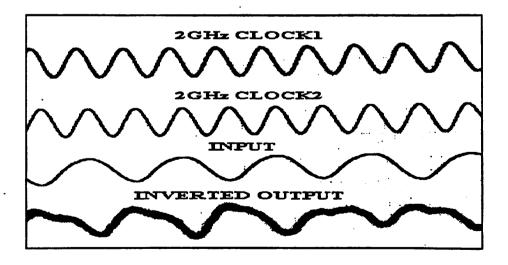

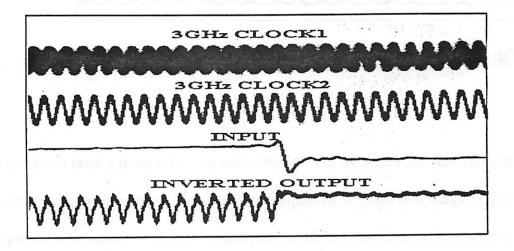

| Fig. 5.26 | Comparator's output tested with 2 GHz clocks and 1 GHz input                                              |

| Fig. 5.27 | Comparator's output tested with 3 GHz clocks and 100 MHz input                                            |

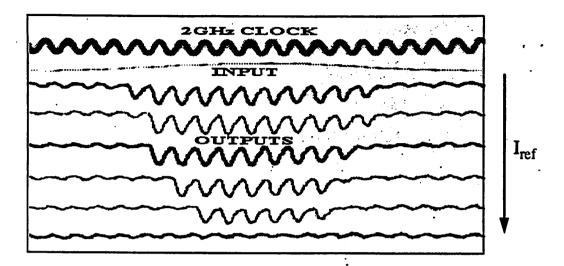

| Fig. 5.28 | Comparator's outputs tested at 2 GHz clocks and 1 GHz input as I <sub>ref</sub> is                        |

|           | increased progressively93                                                                                 |

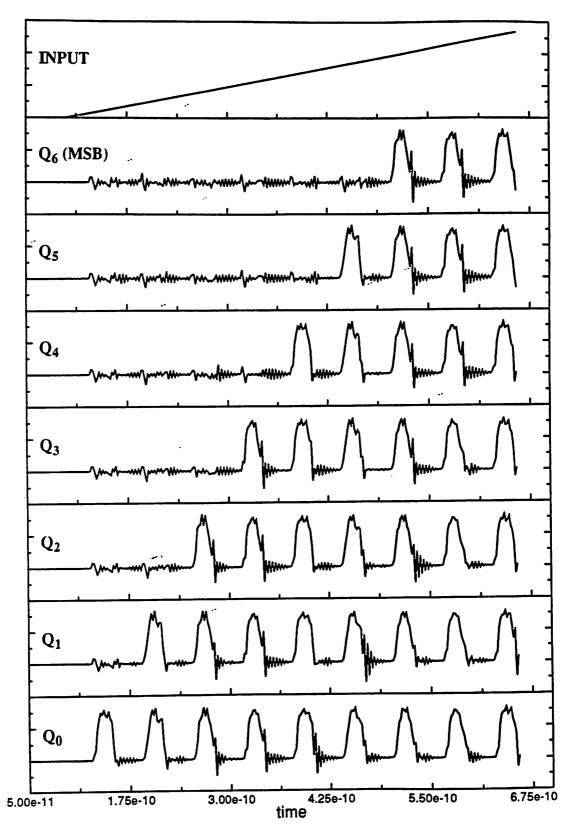

| Fig. 5.29 | Simulation results of a three-bit quantizer at 16 GHz clock frequency                                     |

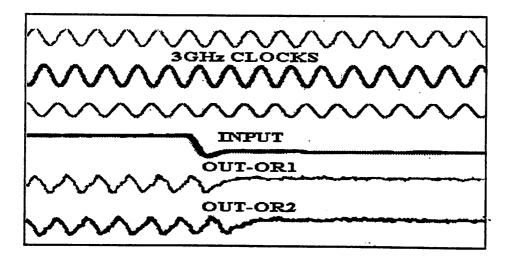

| Fig. 5.30 | Test result for a two-stage buffer at 3 GHz clock and 100 MHz input                                       |

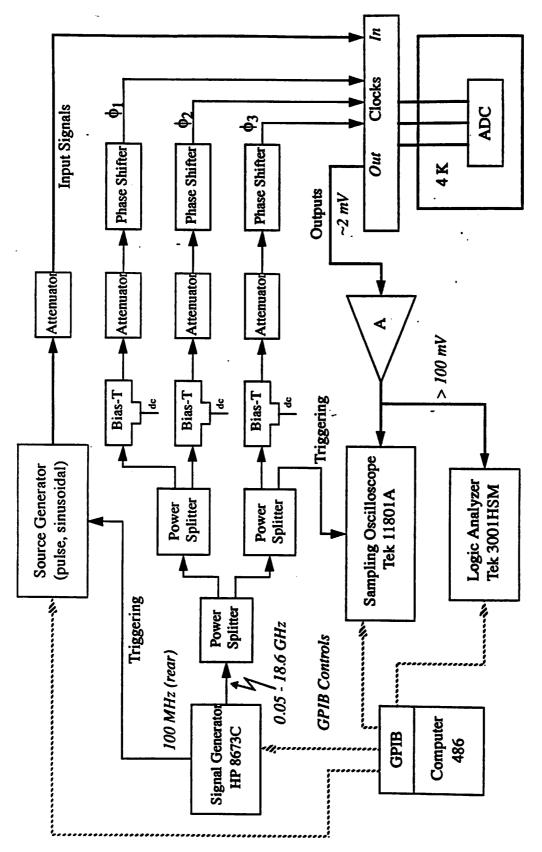

| Fig. 5.31 | Test setup for data acquisition at multi-gigahertz signals 97                                             |

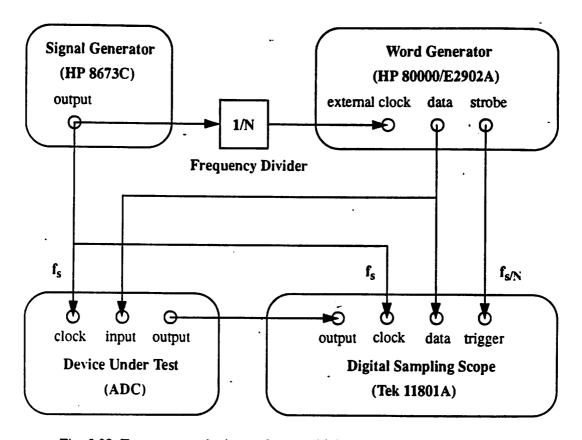

| Fig. 5.32 | Test setup to obtain synchronous high-speed clock and input signals 98                                    |

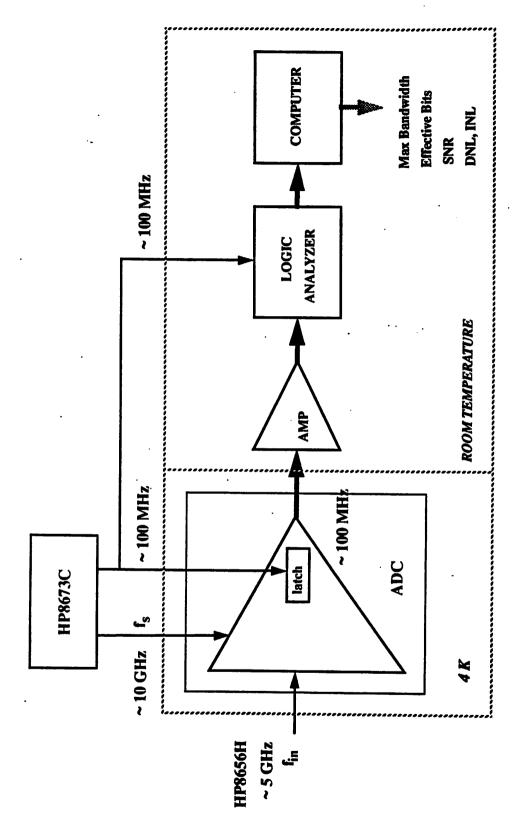

|           | Test setup with latches that are clocked at much slower rate than the converter                           |

|           | itself.                                                                                                   |

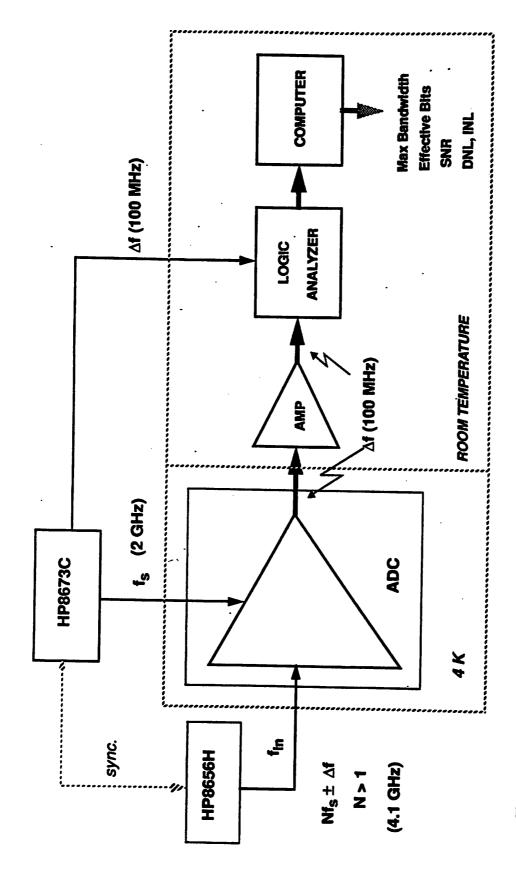

| Fig. 5.34 | Beat-frequency (sub-sampling) test setup, in which the input frequency is                                 |

|           | much higher than the clock frequency. The output is the beat frequency of the                             |

|           | two                                                                                                       |

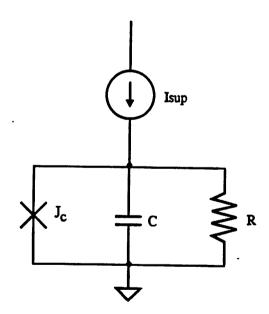

| Fig. 6.1  | Simple Josephson circuit for resetting calculation.                                                       |

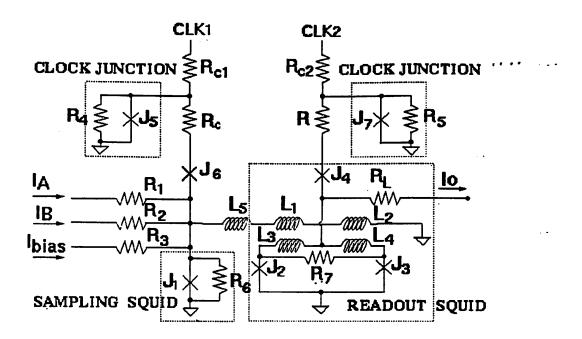

| Fig. 6.2  | Schematic diagram for the new ultra-fast logic gate 108                                                   |

| Fig. 6.3  | Simulated circuit and result for new logic gates at 12.5 GHz clock 110                                    |

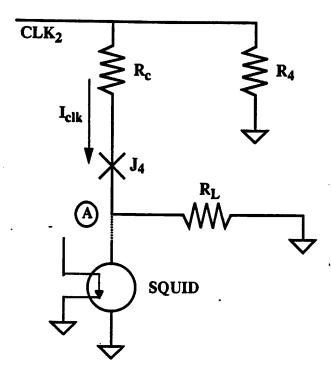

| Fig. 6.4  | Equivalent circuit of the logic gate when the readout SQUID switches 114                                  |

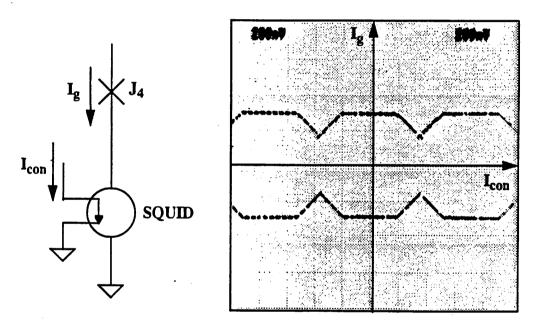

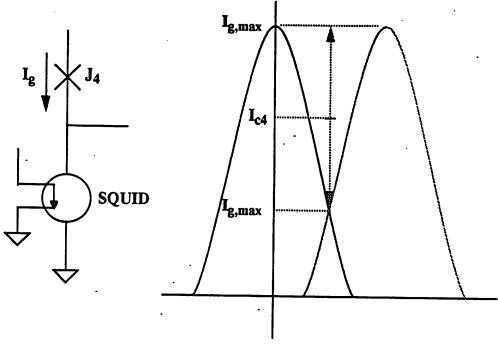

| Fig. 6.5  | Edge-triggering circuit and the ideal choice for critical current of the junction $J_4$ 115               |

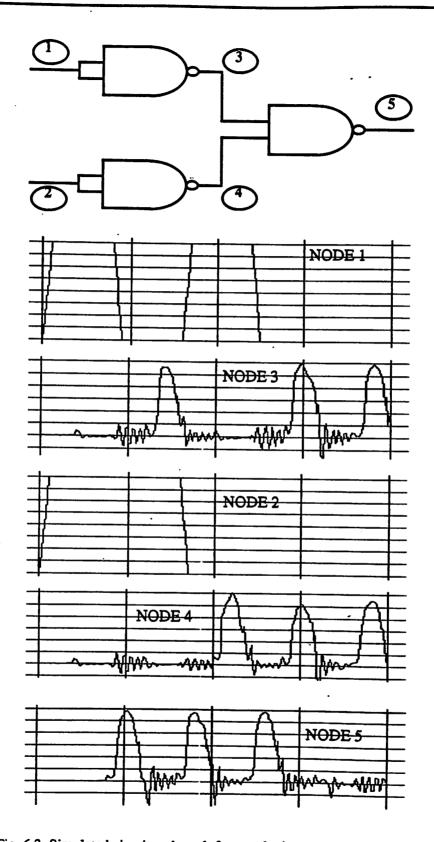

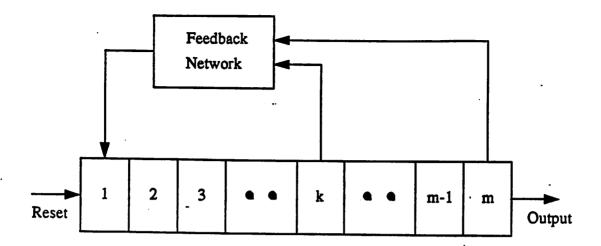

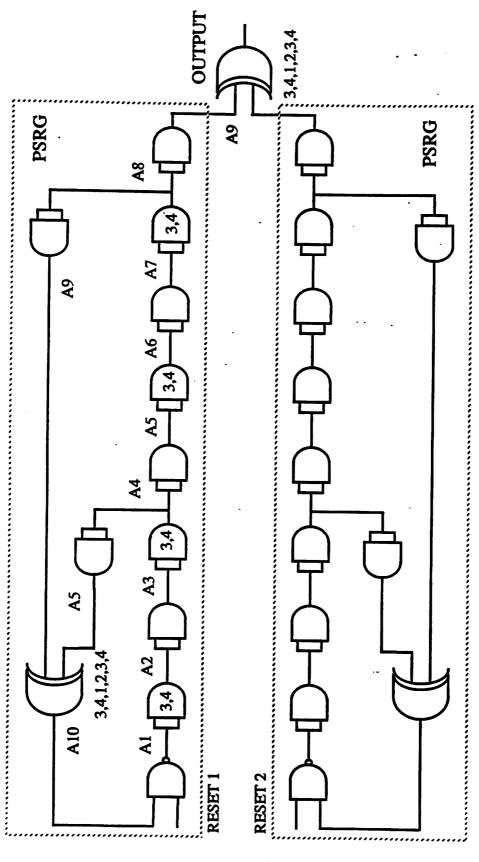

| Fig. 6.6  | Block diagram for a pseudo-random bit sequence generator                                                  |

| Fig. 6.7  | Block diagram of the pseudo-random bit-sequence generator with three-phase                                |

|           | clocks. Shown also is a second PRBSG and an XOR gate used to verify the                                   |

|           | correct operation of the PRBSG                                                                            |

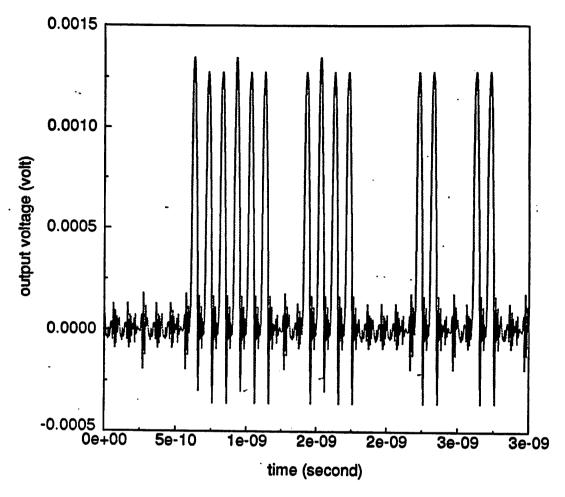

| Fig. 6.8  | Simulation result of the PRBSG at 10 GHz clock frequency showing one            |     |

|-----------|---------------------------------------------------------------------------------|-----|

|           | repeated output sequence.                                                       | 123 |

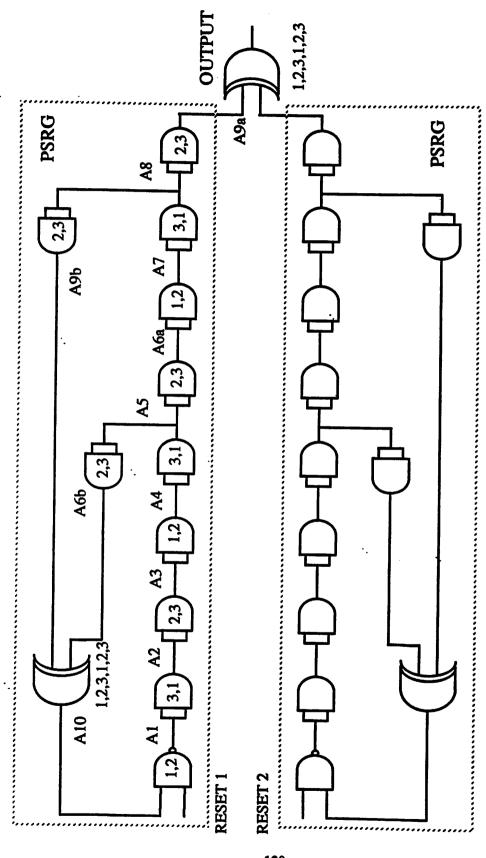

| Fig. 6.9  | Block diagram of the pseudo-random bit-sequence generator with a four-phase     |     |

|           | clock scheme. Shown also is a second PRBSG and an XOR gate used to verify       |     |

|           | the correct operation of the PRBSG.                                             | 124 |

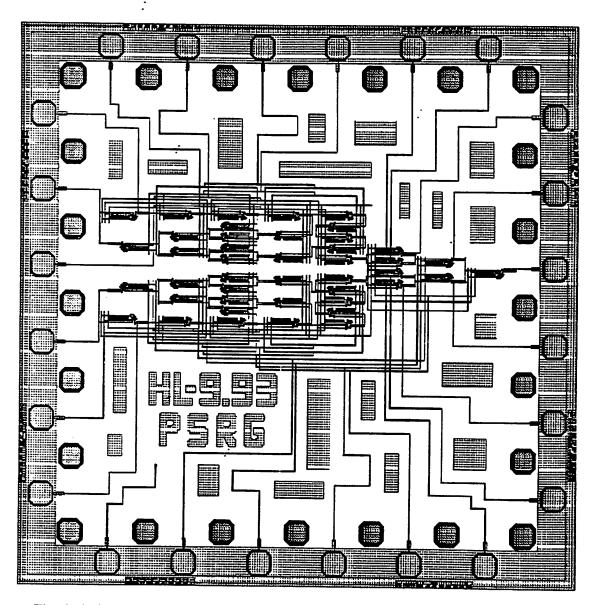

| Fig. 6.10 | Chip layout of two pseudo-random bit-sequence generators and an XOR gate        |     |

|           | as shown in Fig. 6.6.                                                           | 125 |

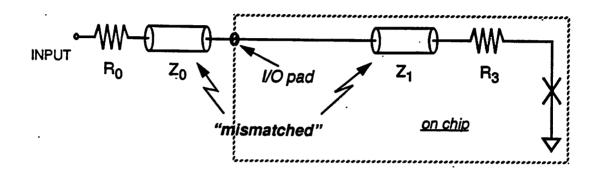

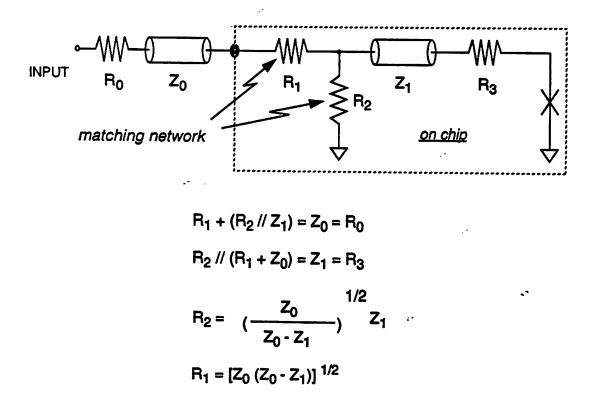

| Fig. 7.1  | A typical superconducting circuit with an impedance mismatch                    |     |

| Fig. 7.2  | Circuit in Fig. 7.1 with addition of a resistive network for perfect matching   |     |

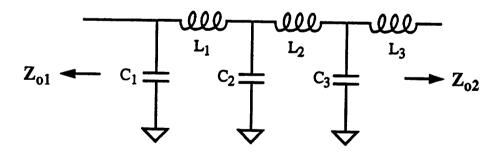

| Fig. 7.3  | Schematic of a 3-stage superconductive filter-type powering device (SFPD)       |     |

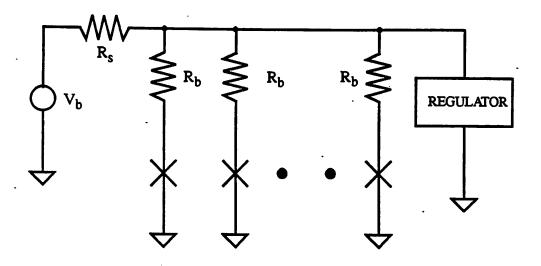

| Fig. 7.4  | Problem and solution for crosstalk due to junction switching.                   |     |

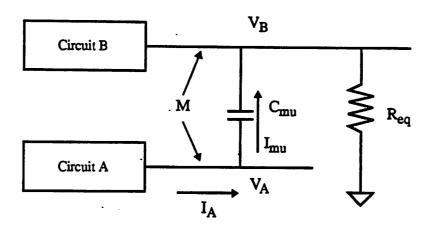

| Fig. 7.5  | Simple model of crosstalk due to mutual inductive and capacitive coupling       | 136 |

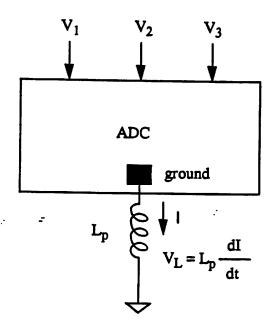

| Fig. 7.6  | Illustration of how high inductive ground line causes ground bounce.            | 138 |

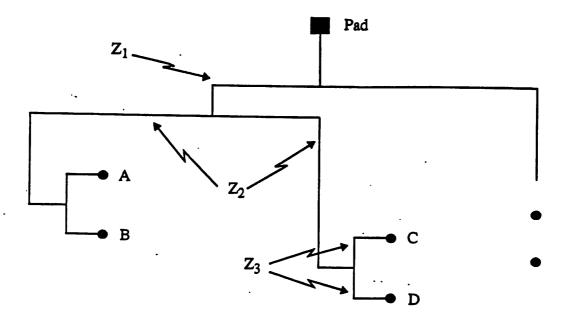

| Fig. 7.7  | A section of an H-tree clock distribution scheme to minimize skew               | 140 |

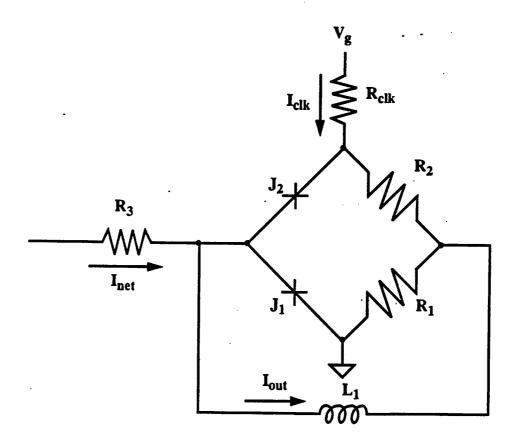

| Fig. 8.1  | Circuit schematic for the current-latched bridge-type comparator                | 148 |

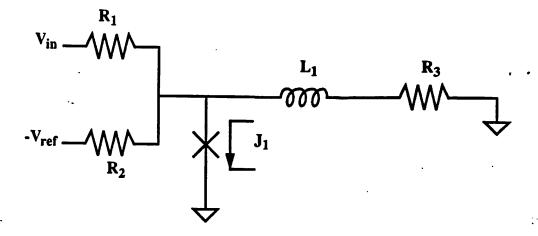

| Fig. 8.2  | Circuit schematic for the limiter using a Josephson junction                    | 150 |

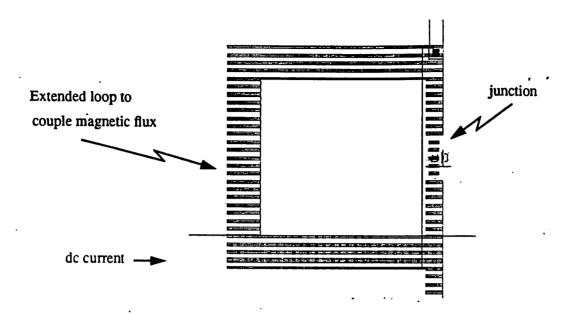

| Fig. 8.3  | Layout of a Josephson junction as a limiter with a loop to couple magnetic flux | 151 |

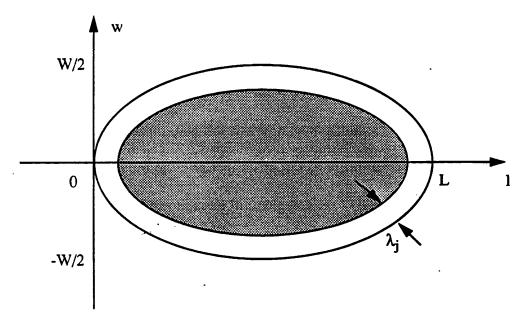

| Fig. 8.4  | A sinusoidal-shaped Josephson junction with large L/λ <sub>j</sub>              | 152 |

| Fig. 8.5  | Complete circuit schematic for the comparator preceded by a limiter             | 154 |

| Fig. 8.6  | Layout of the complete comparator including the limiter and the input resistors | 154 |

| Fig. 8.7  | Logic implementation of the 3-bit binary encoder using XOR gates                | 155 |

| Fig. 8.8  | Schematic and layout of a two-input XOR gate used as a two-bit encoder          | 156 |

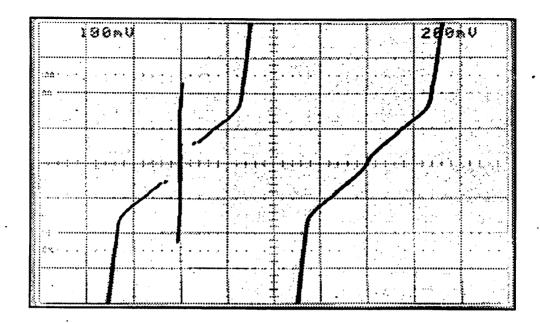

| Fig. 8.9  | Schematic and layout of a four-input XOR gate used as a four-bit encoder        | 156 |

| Fig. 8.10 | Chip layout of the three-bit bridge-type analog-to-digital converter.           | 160 |

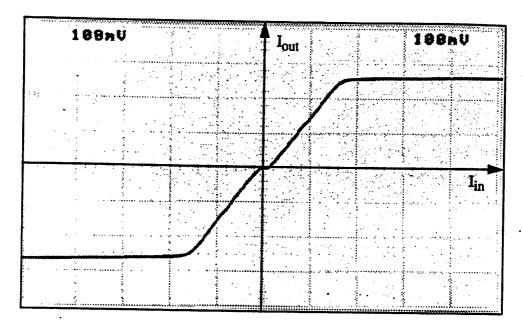

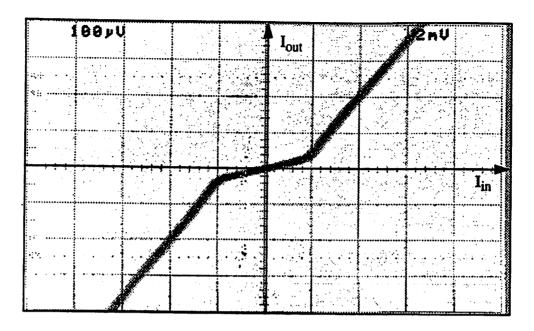

|           | Measured IV curve for the limiter junction without and with suppressing current |     |

|           | Measured dc transfer curve for the limiter with suppression current applied     | 163 |

| Fig. 8.13 | Blown-up version of the "deadband" region around zero input current for Fig.    |     |

|           | 8.12.                                                                           | 164 |

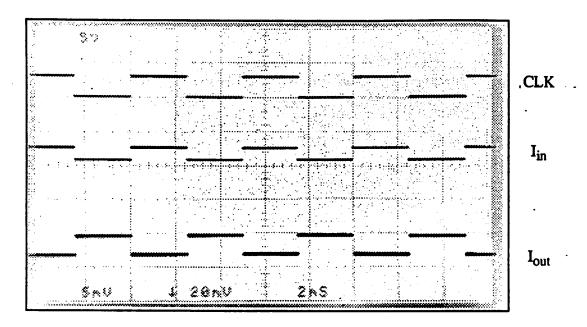

| Fig. 8.14 | Measured outputs of the complete bridge-type comparator.                        | 165 |

| Fig. 9.1  | Multi-step subranging ADC architecture.                                         | 168 |

| Fig. 9.2  | Illustration of how a three-stage subranging ADC works                          | 169 |

| Fig. 9.3  | Basic implementation of a n-bit digital-to-analog converter                     |     |

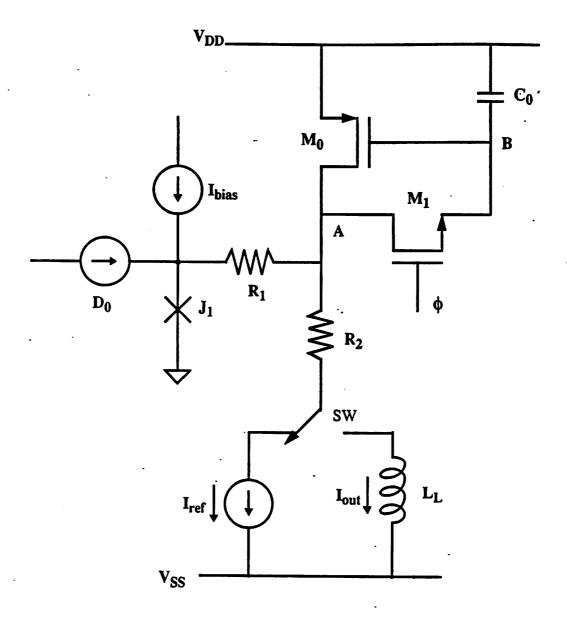

| Fig. 9.4  | Proposed implementation of an DAC using transformer coupling                    | 172 |

| Fig. 9.5  | Proposed implementation of an DAC using SQUIDs as switches                       | 173 |

|-----------|----------------------------------------------------------------------------------|-----|

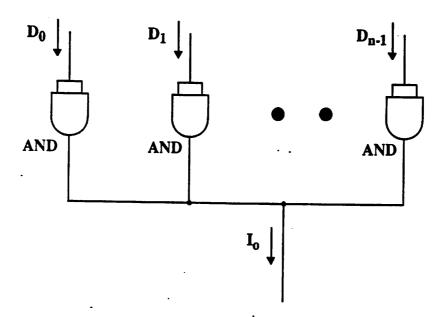

| Fig. 9.6  | Proposed implementation of an DAC using logic AND gates                          | 174 |

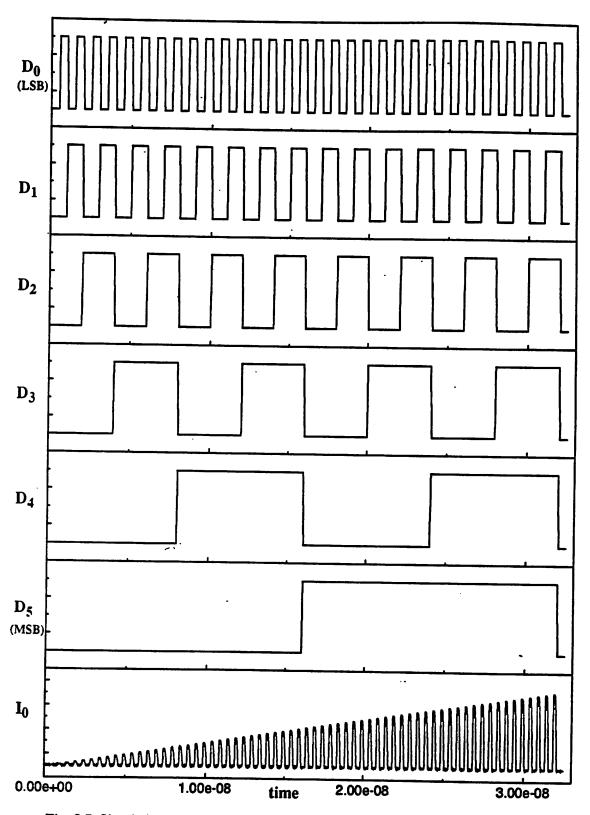

| Fig. 9.7  | Simulation results for a six-bit digital-to-analog converter at 2 GHz clocks     | 175 |

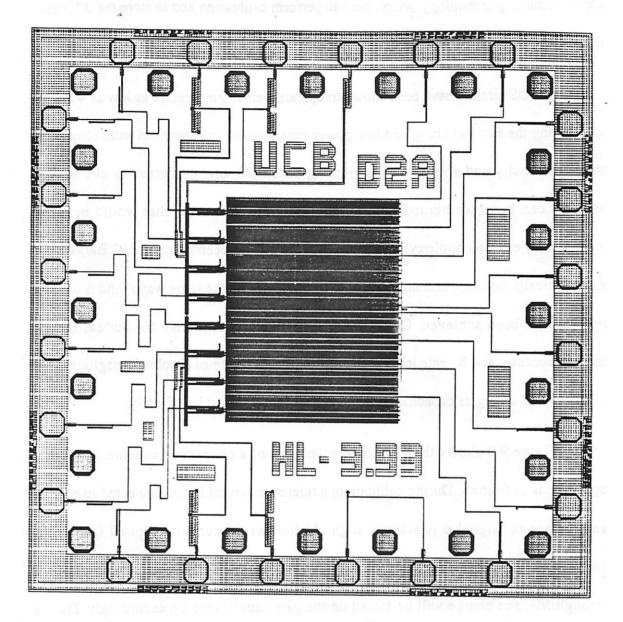

| Fig. 9.8  | Chip layout of the 6-bit digital-to-analog converter (DAC) using AND gates       | 177 |

| Fig. 9.9  | Simplified schematic of a calibration scheme for DAC's current sources           | 179 |

| Fig. 9.10 | Schematic of the sample-and-hold showing sample and hold operation               | 182 |

| Fig. 9.11 | Simulation results of the sample-and-hold at $f_{in} = 1$ GHz, $f_{clk} = 2$ GHz | 183 |

| Fig. A.1  | Circuit schematic for a symmetric two-junction SQUID.                            | 200 |

| Fig. D.1  | Test setup for our degausser to demagnetize the shield prior to testing          | 220 |

| Fig. D.2  | Second-order RLC circuit to generate an exponentially decaying sinusoidal        |     |

| .•        | signal for the degausser                                                         | 223 |

|           |                                                                                  |     |

### LIST OF TABLES

| Table 3.1 | Comparison of performance of the best analog-to-digital converter             | 17         |

|-----------|-------------------------------------------------------------------------------|------------|

| Table 3.2 | Aperture time and figure of merit of the converters listed in Table 3.1       | 20         |

| Table 4.1 | Original and modified design parameters for the comparator                    | <b>5</b> 3 |

| Table 4.2 | Truth table for the LSB bit of a 4-bit thermometer-to-binary encoder          | 59         |

| Table 5.1 | Truth table for a three-bit thermometer-to-binary encoder.                    | 73         |

| Table 5.2 | Truth table for a three-bit binary encoder together with the measured outputs | 86         |

| Table 5.3 | Measurement of the spread in the junction critical currents of a series array | 87         |

| Table 6.1 | Feedback connections to achieve an m-bit maximum-length linear sequence       | 118        |

| Table 6.2 | The output patterns for all stages in the PRBSG shown in Fig. 6.6.            | 122        |

| Table 8.1 | Summary of Petersen's test results on the bridge-type comparator              | 159        |

#### **ACKNOWLEDGEMENT**

First of all, I would like to express my sincere thanks to my research advisor, Professor Theodore Van Duzer, for the opportunity to work on such an interesting project under his supervision. His invaluable support, advice, and encouragement have helped me grow both professionally and personally and have made my long stay at Berkeley both more meaningful and durable. I am especially grateful to him for spending so much time, including his precious vacation time, reviewing this dissertation.

I would like to thank Professors Jan Rabaey, Bernhard Boser, and John Clarke for being in my qualifying examination committee and Professors Rabaey and Paul Richards for reading this dissertation.

I would also like to express my gratitude to members of cryogenic group. My special thanks are to Emerson Fang, David Petersen, and Paul Bradley for their help and suggestions in designing and testing superconducting analog-to-digital converters at high speeds; to Jay Fleischman, Dave Feld, Uttam Ghoshal, Peter Xiao for helpful and stimulating discussion on Josephson devices and circuits; to Kishore Seendripu, Mario Makhalaf, Arnold Feldman, Amit Marathe, Uttam Ghoshal, and Kartika Prihadi for relaxing "coffee" hours and stress-releasing conversation. I would also like to thank Arnold, Peter, and Mario for their expertise and time in administering and maintaining the

computer. I really appreciate Arnold's constant effort to clean up accounts and to get enoughernputer disk space so work can be done.

Totali students remaining in the group, Kishore Seendripu, Amit Marathe, Arnold FeldmanKartika Prihadi, Kenway Tam, Osamu Takahashi, Zhong Deng, Zuoqin Wang, and Jamanan Du, I hope that they will enjoy and appreciate the opportunity and the time spent in the cryogenic group as much as I have, and I wish them all the best in their future endeaves.

Awould like to thank Dave Hebert not only for fabricating the chips and for helpingme learn all the steps and issues in microfabrication but also for giving me valuableadvice about the real life. My sincere appreciation goes to Mike Branch, our equipment kingpin, for his excellent performance and outstanding skills on building test equipment and accessories.

It is my pleasure to acknowledge Hypres Incorporated for fabricating working chips; Dave Petersen for his excellent job in providing and overhauling his high-speed American Cryoprobes; and Air Force, University Research Initiative, and Tektronix for funding and sponsoring my projects.

I would like to thank my mother for all of what she has done for me. If it had not been for her devoted love and constant encouragement, I probably would not have had enough strength and determination to survive all those years. I cannot express enough my gratefulness to my brother Vincent Luong for working so hard to bring us to the United States and for being my role model as a good son and a good brother in the family. Many thanks go to my sisters, Thuc Tran, Buu Tran, My Tran, Nhu Tran; my younger brother,

Cam Toan; my brothers-in-law, Liem Nguyen, Phuong Duong, Hoan Trinh; my sister-in-law, Kim Ong; my niece, Teresa Nguyen; and my nephew, Paul Nguyen; for their constant love and support throughout all these years, even when I was so stressful that I became rude to them. I owe it to them for taking care of most problems in the family so that I had more time to do my own work. I feel very lucky to have such a caring family, whose unreserved love and abundant "weekly food supply" have made my life at Berkeley so much easier and more bearable. Their unselfish love and support in letting me go to Hong Kong to follow my dream is greatly appreciated.

Finally, it was really a privilege for me to have many good friends to share all the good times and the bad times in those years at Berkeley. In particular, I am whole-heartedly indebted to Linda Yip for the wonderful time we shared at Berkeley, which was all too short but always has and always will remain the most meaningful and memorable in my whole life. I am thankful to many of my closest friends - Tran Buu Luong, Cynthia Yip, Mary Trang Nguyen, Phuong Tran, and Cuong Nguyen - for always being there listening to my personal problem and giving me their advice and support. I really enjoyed and appreciated all the time and all the fun activities I shared with these friends and too-many-to-name others.

## Chapter 1

#### INTRODUCTION

#### 1.1 Background and Motivation

Within last ten years or so, the digital world has been advanced continuously and rapidly to an extent that people have started wondering whether the whole world will turn purely digital and whether there will be a place for analog circuit designers in the future. Whether this becomes true or not, it is unquestionable that most of the real signals we are dealing with are analog, and thus there is always a need to build high-performance circuits to interface between analog and digital worlds. To keep up with the fast and steady improvement of technologies and circuit performance in the two worlds, not only in speeds and levels of complexity but also in power consumption, it is clearly indispensable to conceive interfacing circuits with higher and higher performance. This project is to design, fabricate, and test a superconducting analog-to-digital converter that can work up to multi-gigahertz clock frequencies and input bandwidths and at the same time consume only few milliwatts. Compared to the best semiconductor analog-to-digital converters available, this converter performs at least one order of magnitude better in terms of speed and few orders of magnitude less in terms of active power consumption.

#### 1.2 Thesis Organization

This thesis is organized into ten chapters. This chapter introduces the background and the motivation of the project and describes the organization of the thesis. Chapter 2 gives a brief review of existing and widely used architectures for analog-to-digital converters, including their basic designs and their advantages and disadvantages compared to other architectures. Among those available for semiconductor technology are serial-type, successive approximation, flash-type, multi-step subranging, and pipelined architectures. Chapter 3 discusses in full detail why superconducting technology has been chosen for our project over semiconductor technologies, which undoubtedly are much better developed and more mature. Fundamentals of Josephson junctions that are closely related to the specific designs of our converter prototype will be described. For comparison and for completeness, periodic-threshold designs of a flash-type analog-to-digital converter, which is quite unique and available only to optical and superconducting devices, will be presented.

In Chapter 4, we will focus our discussion on the design and fabrication of a prototype for a fully parallel superconducting analog-to-digital converter, in particular the comparators for the quantizer and the logic gates for the thermometer-to-binary encoder. The complete converter's performance and functionalities, both at low speeds and high speeds, are verified and reported in Chapter 5. In Chapter 6, we will describe how the new logic family presented in Chapter 4 has been modified to increase the speed up to 12.5 GHz. We will also present the fabrication and experimental results for a pseudo-random bit sequence generator (PRBSG) we designed to test the logic gates at their highest

possible speeds without strict requirement of synchronous high-speed input and clock signals.

Chapter 7 addresses all issues that need to be considered and treated appropriately in designing and testing circuits at mutli-gigahertz operating frequencies, including problems with crosstalk, clock distribution, and testing at high speeds and at low temperatures. Problems and solutions that are applicable not only to our particular superconducting design but also to semiconductor high-speed circuits will be mentioned in great detail.

Chapter 8 reviews another design of a fully parallel analog-to-digital converter using bridge-type current-latched comparators and reports our progress. In Chapter 9, we study the feasibility of implementing a multi-step subranging analog-to-digital converter in superconducting technology to achieve high resolution without imposing too much restriction on process variations or sacrificing too much hardware. Possible implementations of required components, mainly digital-to-analog converters (DACs), sample-and-hold circuits, subtractors, and amplifiers, will be proposed together with preliminary simulation results.

In Appendix A, we present in detail how SQUID threshold curves can be calculated. Application of the Lagrange multiplier method to derive the threshold curve for a superconducting loop will be illustrated. Appendix B describes how performance of an ADC is evaluated at very high speeds. C programs used for automatic layout generation and for data acquisition and analysis are included in Appendix C. Finally, Appendix D presents our design and test setup to demagnetize the shield before each test.

## Chapter 2

#### **OVERVIEW OF ADC ARCHITECTURES**

In general, analog-to-digital converters (ADCs) are characterized and evaluated by their bit resolution (accuracy) and their sampling rate (conversion speed). Depending on the application, the required converters can have resolution ranging from four to sixteen bits and conversion rate ranging from few hundred samples per second to several hundred mega-samples per second. As examples, applications in telephony and instrumentation require converters with very high resolution and accuracy but with sampling rates in the audio range. On the other hand, video interfaces and radar applications require converters with very high speed performance but with low bit resolution.

As an alternative to the sampling rate, an ADC can be characterized by its maximum input bandwidth. Maximum input bandwidth can be interpreted as a frequency at which signal attenuation and phase shift become significantly large. Ideally, an ADC should be able to achieve a maximum input frequency at the Nyquist rate, which is half of the clock frequency. However, in practice, due to limitations of circuit components and design at high speed, most of existing ADCs have maximum input bandwidths being far below their Nyquist rate.

Assuming that the frequency response of an ADC is dominated by a single pole, the attenuation factor A(f) as a function of frequency is given by:

Assuming that the frequency response of an ADC is dominated by a single pole, the attenuation factor A(f) as a function of frequency is given by:

$$A(f) = \frac{A_0}{\sqrt{1 + (f/f_c)^2}}$$

(1.1)

where  $A_0$  is the dc gain and  $f_c$  is the maximum input bandwidth. The phase shift  $\theta(f)$  is:

$$\theta(f) = \arctan(\frac{f}{f_c})$$

(1.2)

and the time shift error  $\Delta t$  (f) is:

$$\Delta t(f) = \frac{\theta(f)}{360^{\circ}} \frac{1}{f} = \frac{1}{360f} \arctan(\frac{f}{f_c})$$

(1.3)

Overall, given a perfect sinusoidal input signal  $V_{in}(t) = \sin\omega t$ , the output  $V_{out}(t)$  of an ADC with a maximum input bandwidth limited to  $f_c$  becomes:

$$V_{out}(t) = \frac{A_0}{\sqrt{1 + (f/f_C)^2}} \sin\left[\omega t + \arctan\frac{f}{f_C}\right]$$

(1.4)

As an example, to maintain a peak accuracy of 8 bits, that is A(f) < 0.4%, it is necessary from Eq. (1.1) that the maximum input bandwidth  $f_c$  should be at least 10 times larger than the operating frequency f.

According to their performance, analog-to-digital converters can be divided into three different categories: high resolution and low speed, low resolution and high speed, or relatively high resolution and relatively high speed. As far as architectures are concerned, they can be classified according to how the analog signals are sampled and quantized to

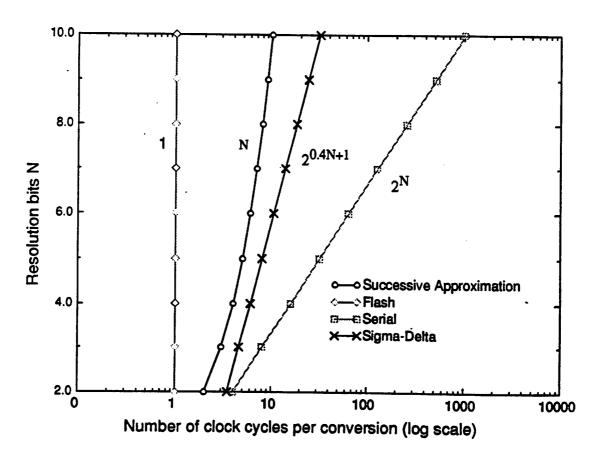

achieve the digital outputs. Figure 2.1 shows a comparison of performance of available architectures, namely the bit resolution and the speed in terms of number of clock cycles per conversion.

At one extreme, serial converters have ultra high resolution but require 2<sup>N</sup> clock cycles per conversion. At the other extreme, flash-type ADCs take only one clock cycle per conversion but have limited resolution. Compromising between these two extremes are converters with multi-step architectures, including successive approximation, which requires N clock cycles, and subranging or pipelined, which requires anywhere between 1 and N cycles, depending on the specific implementation.

Fig. 2.1 Bit resolution vs. speed of various ADC architectures (from [1]).

The rest of this chapter will give brief overview of each architecture, emphasizing basic implementation and fundamental advantages and disadvantages.

#### 2.1 Serial-Type (Integrating) Analog-To-Digital Converter

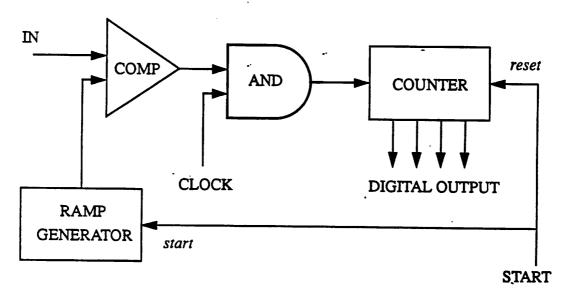

High-resolution and low-speed analog-to-digital conversion can be achieved by the integrating or serial-type architecture, in which the analog input signal is compared to all possible digital representations of the output codes one at a time [2] [3]. Figure 2.2 shows the simplest implementation of the architecture, in which the input signal is compared to a slowly ramping signal. At the beginning of each conversion, the START

Fig. 2.2 Architecture for integrating (serial-type) analog-to-digital converter

signal resets the counter and triggers the ramping generator. As long as the generator output is smaller than the input signal, the output of the comparator is high, the clock is fed through the AND gate, the counter is enabled and the output is counted up. Once the

ramping signal equals or exceeds the input signal, the output of the comparator goes low, which deactivates both the counter and the ramping generator. The output of the counter is the total number of clock cycles required for the ramping signal to reach the input signal and thus reflects the digital representation of the input signal. The exact magnitude of the input can be calculated from the slew rate of the ramp generator, the cycle time, and the number of cycles required for the conversion.

The advantage of this architecture is that it is very simple and requires the least hardware. Since the operation depends on the ramping signal, the converter is inherently monotonic. It requires an implementation of a very linear ramping generator, and as far as the conversion speed is concerned, it takes 2<sup>N</sup> clock cycles for each conversion and is therefore too slow to be practical in most applications.

#### 2.2 Parallel (Flash) Analog-To-Digital Converter

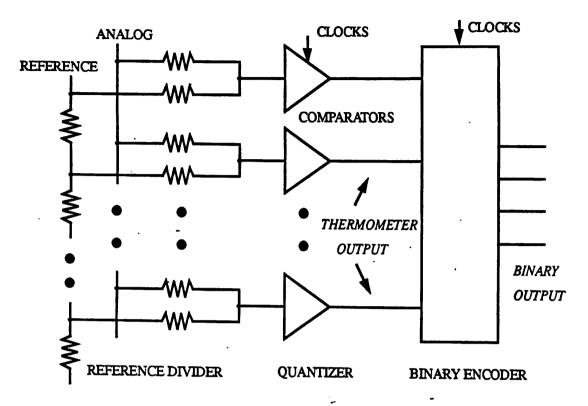

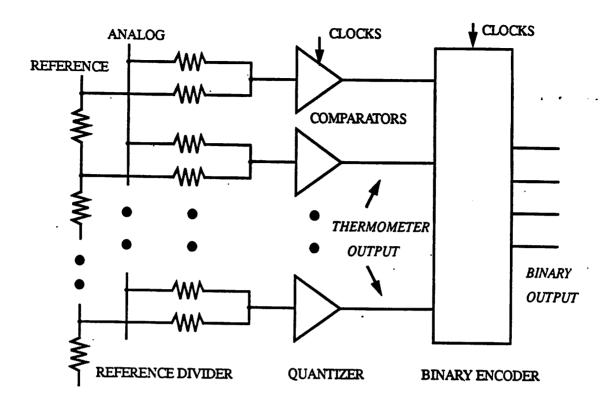

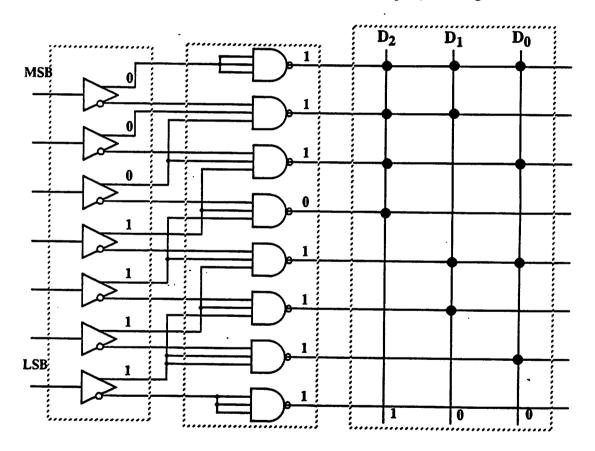

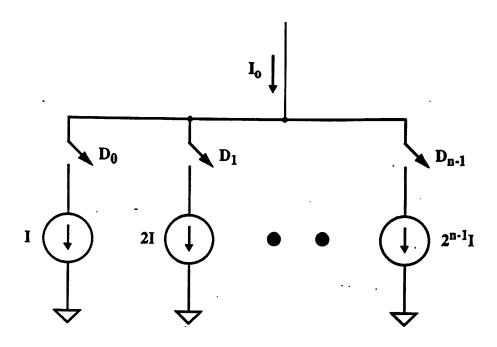

The fastest conversion rate can be achieved by using the flash-type converter, in which the analog signal is compared to all digital output codes simultaneously, as opposed to one at a time as in a serial ADC [2] [3]. As shown in Fig. 2.3, a converter with N-bit resolution consists of  $2^{N}$ -1 comparators to sample the analog input and a binary encoder to convert the thermometer outputs of the comparators into the corresponding binary format. Typically, a resistor string is used to provide  $2^{N}$ -1 linearly graded reference levels to the comparators. The output of each comparator will be high if the input is larger than its reference, and as a result, a thermometer-coded output is achieved.

Fig. 2.3 Fully parallel (flash) analog-to-digital converter

This architecture yields the highest conversion rate, which was mainly the motivation for this work and will be described in full detail in subsequent chapters. However, the converter is relatively complex, and since the number of comparators is exponentially dependent on the resolution bits, it requires very large area, hardware, and power consumption. Another problem with this type of converter is its low resolution due to the large number of comparators, the offsets of the comparators, and the accuracy of the reference ladder network.

#### 2.3 Successive-Approximation Analog-To-Digital Converter

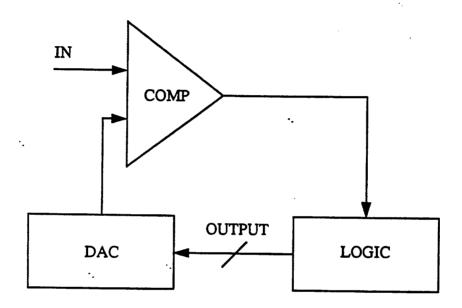

By comparing the input to the output codes in a binary-search algorithm, successive approximation architecture can compromise between the speed and the resolution to achieve faster conversion rate than the serial type and higher resolution than the flash type [2] [3]. Figure 2.4 shows the simplified block diagram of the converter.

Fig. 2.4 Architecture for successive-approximation analog-to-digital converter

The function of the logic block is to select, in a binary-search format, appropriate digital codes for the DAC input, which are also the output of the whole ADC. At the start of a conversion, the logic block selects an input to the DAC such that half of the full-scale reference signal is applied to the comparator and compared to the analog input signal. If this signal is smaller than the input signal, the first digital output is high and the next higher level will be selected. Otherwise, the first digital output is low, and the output of the

DAC will be decreased to the next lower level. By successively increasing or decreasing the DAC output in a binary-search format, one bit is achieved after one comparison, and an N-bit resolution is achieved after N clock cycles.

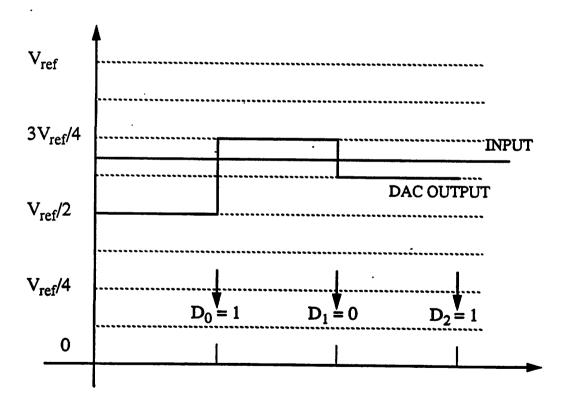

Illustrated in Fig. 2.5 is an example of how a three-bit converter operates. The analog input is chosen to be approximately 11/16 of  $V_{ref}$ . In the first cycle,  $V_{ref}/2$  is asserted at the DAC output. Since it is smaller than the input, the digital output  $D_0$  is set to 1, and the DAC output is increased to 3/4  $V_{ref}$ . Because this signal is larger than the input, the next digital bit  $D_1$  is set to 0, and the DAC output is decreased to 5/8  $V_{ref}$ . The comparator detects that the DAC output is now smaller than the input and sets  $D_2$  to 1.

Fig. 2.5 Example of a three-bit successive approximation.

This architecture is relatively simple and requires very little hardware. The number of clock cycles per conversion is N. The main problem is that a very linear and accurate digital-to-analog converter is necessary.

#### 2.4 Multi-Step Subranging Analog-To-Digital Converter

To alleviate the complexity and to increase the resolution of a flash-type ADC without sacrificing too much speed, multi-step subranging architecture can be used [3] [4].

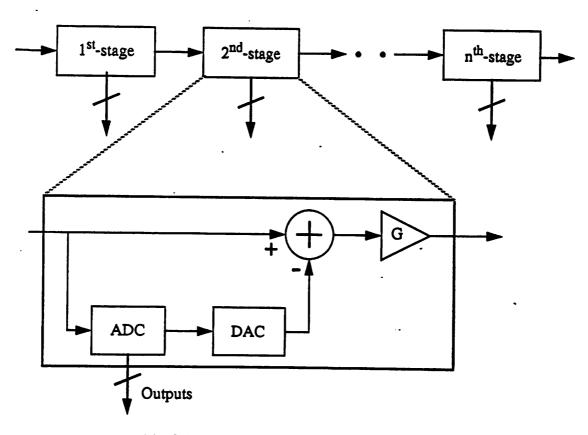

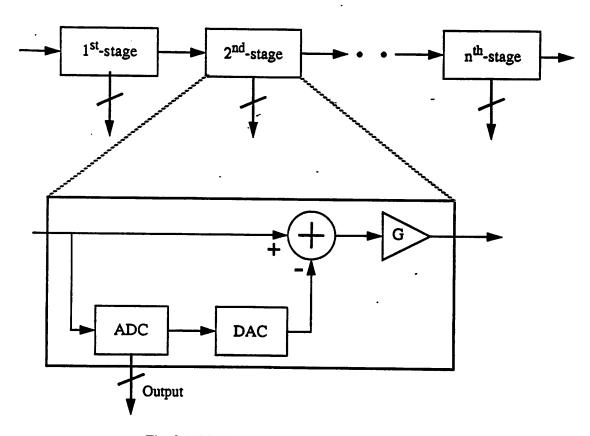

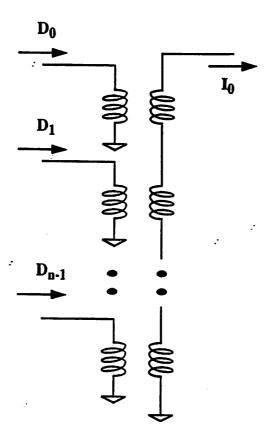

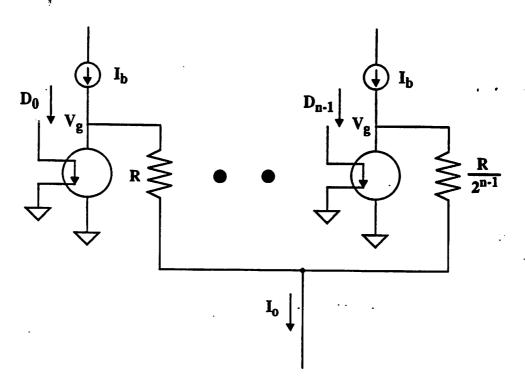

Figure 2.6 shows the implementation of the converter. Basically, this subranging architecture is a combination of the flash and the successive approximation that breaks an

Fig. 2.6 Multi-step subranging ADC architecture

N-bit conversion into M sub-conversions of N/M bits each. The converter consists of several cascaded stages, each of which includes a low-resolution analog-to-digital converter to achieve a coarse estimation of the input, an accurate digital-to-analog converter (DAC) to convert the output of the ADC into an analog version of the estimation, a subtractor to get the residue (the difference between the actual input and its estimation), and a gain block to amplify and to restore the residue to an appropriate level for further estimation by the next stage.

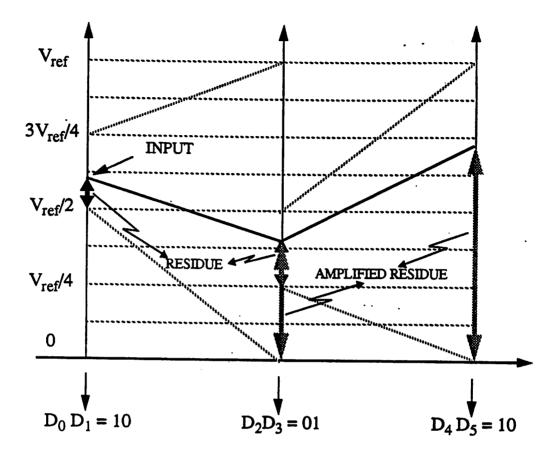

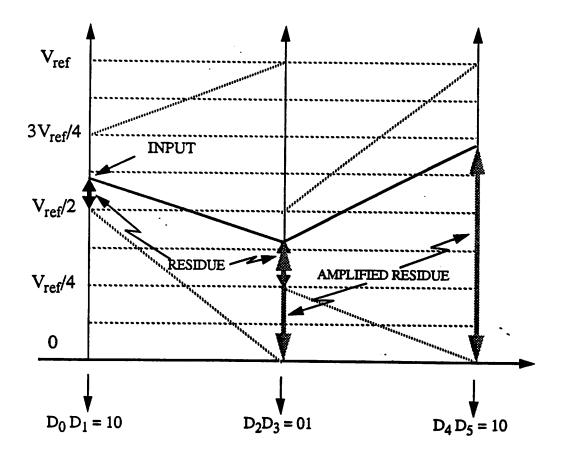

As an illustration, Fig. 2.7 shows the operation of a 6-bit subranging converter that has three cascaded stages, each of which consists of a two-bit ADC, a two-bit DAC, and an amplifier with a gain of 4. The input is chosen to be approximately 77/128  $V_{ref}$ . In the first stage, the two-bit ADC quantizes this input into  $D_0D_1 = 10$ , which is decoded by the DAC as 1/2  $V_{ref}$ , and as a result, the residue becomes 13/128  $V_{ref}$ . This residue is amplified by 4, becomes 13/32  $V_{ref}$  and is passed to the second stage. Similarly, the second stage yields outputs  $D_2D_3$  equal to 01 and a residue of 5/32  $V_{ref}$ , and the third stage receives an input of 5/8  $V_{ref}$  and results in outputs  $D_4D_5 = 10$ . All together, the digital output of the converter is 100110, which corresponds to 38/64  $V_{ref}$ , and the overall error is 1/128  $V_{ref}$ , which is equivalent to an accuracy of 1/2 LSB for 6-bit resolution.

Compared to the flash-type ADC with the same bit resolution, this architecture requires a much smaller number of comparators and thus consumes much less hardware and power. The ADCs can have low bit resolution, but all other components, including the DACs, gain amplifiers, and subtracters, need to be highly accurate. In particular, the amplifiers can limit the overall speed and resolution of the converter.

Fig. 2.7 Illustration of how a three-stage subranging ADC works

Feasibility of implementing a multi-step subranging ADC in a superconducting technology will be presented in Chapter 9. Problems in realizing all required components will be addressed, and possible solutions will be proposed.

#### 2.5 Pipelined Analog-To-Digital Converter

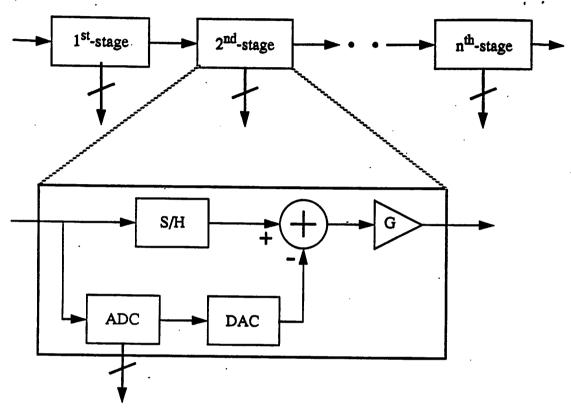

The throughput of a multi-step subranging architecture can be further increased by pipelining the stages. Pipelined architecture is closely related to multi-step subranging except that sample-and-hold (S/H) circuits are added between stages [3] [5] as shown in

Fig. 2.8. With S/H, each stage can work on its input simultaneously and independently from each other. At any instant, while one stage processes the current input sample, the next stage works on the amplified residue of the previous input sample.

Fig. 2.8 Pipelined analog-to-digital converter architecture

Concurrent operation of the stages on many input samples results in a high throughput rate and a conversion speed independent of the number of cascading stages. In addition, like the subranging-type, this architecture requires fewer comparators, smaller area, and lower power consumption. The main disadvantage of the architecture is a limited speed due to a need of very high-performance amplifiers and sample-and-hold circuits.

## Chapter 3

# JOSEPHSON FLASH-TYPE ANALOG-TO-DIGITAL CONVERTERS

#### 3.1 Motivation

Superconducting technology is very attractive for its ultra-high speed and low power. The switching time of a gate is few picoseconds, and the maximum voltage signal level is limited to the junction gap voltage, which is only around 2.6 mV. However, the technology is not as well developed as semiconductor counterparts, and the circuits need to be cooled down to very low temperature to work correctly. For example, niobium technology does not work until it is refrigerated below its critical temperature, which is 9.2 K. For these reasons, it is very hard for superconducting circuits to compete with semiconductor counterparts unless the circuit performance is at least an order of magnitude better. The belief that superconducting flash-type converters can operate at a conversion rate their counterparts in semiconductor can never reach has motivated much research in the field and in the architecture.

For comparison purposes, listed in Table 3.1 are ADCs that have been reported with the best performance. The first column lists the institution that performed the work, the date when the work was done, and the technology that was used. The second column

lists the reported effective bit resolution of the converter, including the effect of noise and distortion of the converter itself. The third, fourth, and fifth list the reported sampling frequency, the maximum measured input frequency, and the power consumption, respectively.

Table 3.1 Comparison of performance of the best analog-to-digital converter

| Institution, Date (Technology)        | Resolution (bits) | Sampling<br>frequency<br>(GHz) | Input<br>frequency<br>(GHz) | Power<br>(W) |

|---------------------------------------|-------------------|--------------------------------|-----------------------------|--------------|

| Fraunhofer, '92<br>(1 μm-GaAs)        | 4.4               | 1.00                           | 0.500                       | 4.30         |

| Ruhr Univ., '87<br>(8 GHz-BJT)        | 3.5               | 1.00                           | 0.500                       | 2.40         |

| NTT LSI, '88<br>(25.7 GHz-BJT)        | 4.7               | 1.00                           | 0.500                       | 2.00         |

| Philips, '92 [6]<br>(13 Ghz-BJT)      | 7.8               | 0.65                           | 0.150                       | 0.85         |

| UCLA, '93 [7]<br>(4 GHz-BJT)          | 9.5               | 0.10                           | 0.050                       | 0.80         |

| Matshushita, '93 [8]<br>(0.8 μm-CMOS) | 10.0              | 0.02                           | . 0.002                     | 0.03         |

| NEC, '93 [9]<br>(0.8 μm-BiCMOS)       | 8.0               | 0.10                           | 0.050                       | 0.95         |

| This work,<br>(Josephson)             | 4                 | 10.00                          | 5.000                       | 0.005        |

Most of the semiconductor ADCs reported in our comparison have high resolution but low speed performance. In particular, those using a CMOS technology have resolution

as high as eight to ten bits and conversion rate as low as 20 MHz. Converters implemented with a bipolar technology can yield higher conversion speed but lower resolution. Those converters with advanced processes in GaAs and BJT can operate at one gigahertz clock frequencies, but their power consumption levels are several watts, which is disadvantageously large! For our superconducting work, the converter is expected to achieve a resolution of 4 bits, a maximum input bandwidth of 5 GHz, a clock frequency of 10 GHz, and at the same time to consume a power of only few milliwatts. Note that the powers listed in the table are the active power and that the power required for refrigeration is not included. Also, although much work has been done on superconducting comparators potentially used in ADCs, there has been no complete superconducting ADC ever reported. For this reason, no other superconducting ADC is included in the comparison

In order to compare the performance of converters with different applications and thus different ranges of resolutions and speeds, the aperture time  $\tau_{ap}$ , defined as the time window in which a sinusoidal input signal applied to the converter can slew at most 1 LSB, has been used. For a sinusoidal input signal of the form  $S_{in} = S_0 \sin{(2\pi f_B t)}$ , the maximum slew rate MSR is  $2\pi f_B S_0$  and is also equal to

$$MSR = 2\pi f_B S_0 = \frac{dS_{in}}{dt} = \frac{1LSB}{\tau_{ap}}$$

(3.1)

Therefore, the minimum time necessary for the input to slew 1 LSB can be derived to be:

$$\tau_{ap} = \frac{1LSB}{2\pi f_B S_0} = \frac{2S_0}{2\pi f_B S_0 2^n} = \frac{1}{\pi f_B 2^n}$$

(3.2)

where n is the bit resolution and  $f_B$  is the maximum input bandwidth. Qualitatively, the aperture time can be interpreted as a measurement of how well a converter can sample its input signal. The smaller the aperture time, the more precisely the converter samples the input, and the higher the performance the converter achieves.

In practice, power consumption of a converter can be and is actually sacrificed in many architectures to trade off for speed. To include the power consumption in the comparison of performance, the figure of merit FOM of a converter, defined as the product of the power consumption of the converter and its aperture time, has been widely used. With the aperture time given in Eq. (3.2), the figure of merit FOM can be simply calculated as

$$FOM = P\tau = \frac{P}{\pi f_B 2^n}$$

(3.3)

where P is the converter's active power consumption.

The corresponding aperture times and figures of merit of the converters mentioned in Table 3.1 are calculated and listed in the first two columns of Table 3.2. For clarification, performance of all semiconductor ADCs are normalized against that of the superconducting converter and listed in the last two columns, from which it can be seen that the potential performance (FOM) of superconducting ADCs is at least a few orders of magnitude better than its semiconductor counterparts.

Table 3.2 Aperture time and figure of merit of the converters listed in Table 3.1

| Institution, Date (Technology)   | Aperture (ps) | FOM<br>(pJ) | Normalized<br>Aperture | Normalized FOM |

|----------------------------------|---------------|-------------|------------------------|----------------|

| Fraunhofer, '92<br>(1µm-GaAs)    | 30.2          | 129.0       | 7.6                    | 6,500          |

| Ruhr Univ., '87<br>(8GHz-BJT)    | 56.3          | 135.0       | 14.1                   | 6,800          |

| NTT LSI, '88<br>(25.7GHz-BJT)    | 24.5          | 49.0        | 6.2                    | 2,500          |

| Philips, '92<br>(13Ghz-BJT)      | 9.5           | 7.6         | 2.4                    | 380            |

| UCLA, '93<br>(4GHz-BJT)          | 8.8           | 7.0         | 2.2                    | 350            |

| Matshushita, '93<br>(0.8µm-CMOS) | 155           | 4.7         | 39.1                   | 230            |

| NEC, '93<br>(0.8μm-BiCMOS)       | 24.9          | 23.6        | 6.3                    | 1,200          |

| This work,<br>(Josephson)        | 4             | 0.02        | 1                      | 1              |

### 3.2 Fundamentals of Josephson Junctions

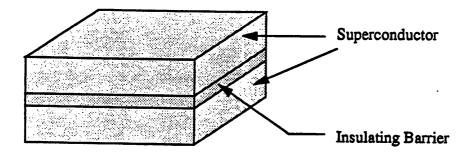

There are many different types of Josephson junctions, including the sandwich, the coplanar, and the point-contact types. However, the most popular and well-developed structure is the sandwich type. As shown in Fig. 3.1,a sandwich-type Josephson junction consists of two superconducting layers separated by a very thin insulating barrier. Today,

Fig. 3.1 Configuration of a sandwich-type Josephson junction.

in a typical Josephson process, the superconducting layers are Nb, and the insulting layer is 2.5 - 5.0 nm of  $Al_2O_3$ .

At low enough temperatures and with a thin enough insulating barrier, the wave functions of the two superconducting layers interact with each other. The so-called Cooper pairs can tunnel through the barrier even without any voltage drop across the junction. As a result, it is possible to have a current flowing through a Josephson junction without a voltage developed across it. This unique feature of the Josephson junction distinguishes it from all other devices and will be used extensively in designing interesting circuits.

Assuming that the wave function of each superconducting layer can be expressed in terms of the pair density  $n_{\text{s}}$  and the phase  $\theta$  as

$$\Psi = n_s^{1/2} e^{i\theta} \tag{3.4}$$

the Josephson relations can be derived to be as follows [10]

$$I = I_c \sin \phi \tag{3.5}$$

and

$$\frac{\partial \phi}{\partial t} = \frac{2e}{h} 2\pi V = \frac{2\pi}{\Phi_0} V \tag{3.6}$$

where  $\phi$  is the phase difference of the two wave functions, defined as  $\phi = \theta_1 - \theta_2$ , I is the current through the junction,  $I_c$  is the maximum zero-voltage current through the junction (normally referred to as the junction critical current), h is Planck's constant,  $\Phi_0$  is the flux quantum (2.07 x  $10^{-15}$  Wb), and V is the voltage drop across the junction.

## 3.2.1 Circuit Model and IV Characteristic Curve

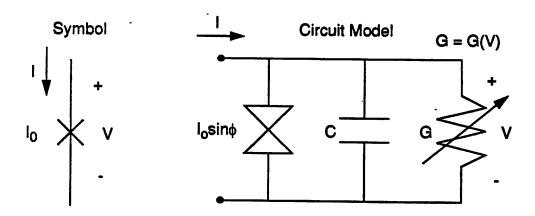

Figure 3.2 shows the schematic symbol of a Josephson junction together with its circuit model. The sinusoidal component represents the current contributed by the Cooper

Fig. 3.2 Schematic symbol and circuit model for a Josephson junction.

pairs as described in Eq. (3.5), the capacitor represents the displacement current due to the parallel structure of the junction, and the voltage-dependent conductance represents both

the leakage current through insulator and the quasi-particle current resulting from the fact that the voltage and the absolute temperature are not zero.

It is clear from Eqs. (3.5) and (3.6) that if the voltage of a junction is not zero, the derivative term  $d\phi/dt$  is not zero. As a consequence, the phase difference  $\phi$  is changing with time, and the current I through the junction is also changing with time. This results in an oscillation of the Josephson junction in its voltage state.

The static IV curve of a Josephson junction can be obtained by applying Kirchoff's current law to the circuit model in Fig. 3.2 as follows:

$$I = I_c \sin\phi + G(V)V + C\frac{dV}{dt}$$

(3.7)

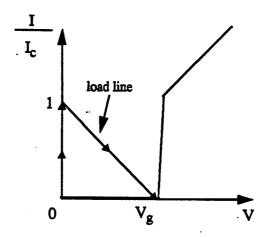

Figure 3.3 shows an IV characteristic curve of a typical Josephson junction. If the current flowing through the junction is smaller than the critical current of the junction I<sub>O</sub>, no voltage is developed across the junction, and the junction is in its superconducting state. As soon as the current exceeds the critical current, the junction switches in a few picoseconds to the voltage state with a voltage of approximately 2.6 mV (for niobium) being developed across the junction. It is important to emphasize that the ultra-short switching time and the ultra-low high voltage level of the junction enable Josephson circuits to achieve very high performance in terms of speed and power consumption.

A junction shunted with a resistive load can be either hysteretic or nonhysteretic; the behavior in the two cases is strikingly different. A very useful and important parameter  $\beta_c$ , so called McCumber parameter, is widely used to define the degree of hysteresis. The parameter is defined as

Fig. 3.3 IV characteristic curve of a typical Josephson junction.

$$\beta_{c} = \frac{2\pi I_{c} CR^{2}}{\Phi_{0}} = \omega_{p}^{2} R^{2} C^{2}$$

(3.8)

where C is the junction capacitance, R is the equivalent impedance load, and  $\omega_p$  is the plasma oscillation frequency, given by:

$$\omega_{\rm p}^2 = \frac{2\pi I_{\rm c}}{\Phi_0 C} \tag{3.9}$$

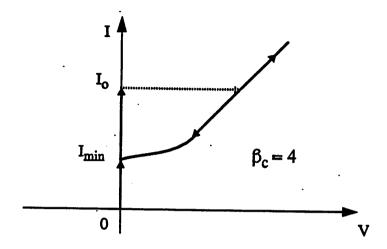

If  $\beta_c$  is less than 1, the junction is nonhysteretic, and the IV curve is single-valued; that is, for every value of current I, there exists a unique corresponding value of voltage V. If  $\beta_c$  is larger than 1, the junction is hysteretic, and the IV curve is more complex. As an illustration, Fig. 3.4 shows a IV curve for  $\beta_c = 4$ , where  $I_{min}$  denotes the maximum current required to reset the junction from the voltage state to the superconducting state. For

current I smaller than  $I_{min}$ , the IV relation is single-valued. However, for current I such that  $I_{min} \le I \le I_0$ , there are two possible operating voltages for each given current value.

Fig. 3.4 Illustration of a hysteretic IV curve of a junction with  $\beta_c = 4$  (from [11]).

## 3.2.2 Junction Switching Characteristic

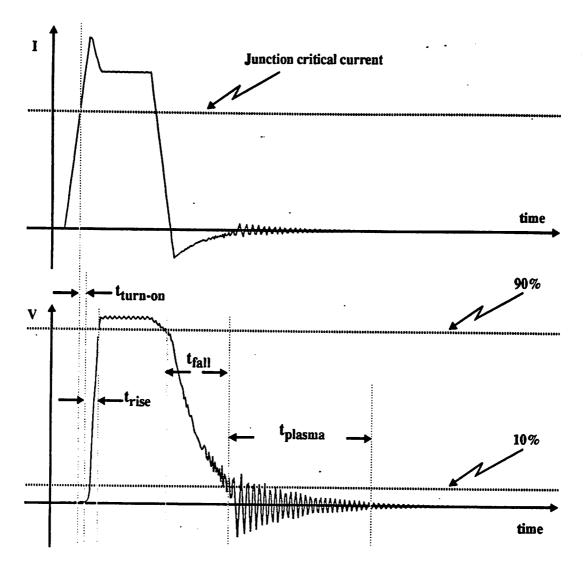

Shown in Fig. 3.5 is a typical transient response of a Josephson junction. The top trace is the supply current and the bottom trace is the voltage developed across the junction.

As the supply current increases from zero to a level above the junction critical current, the junction switches to the voltage state. As the supply current drops back to below the resetting current, the junction returns to its superconducting state with decaying "plasma oscillation". As indicated in the figure, parameters of most interest include the turn-on time, the rise time, the fall time, and the plasma oscillation delay time.

Fig. 3.5 Supply current (top) and voltage (bottom) across a Josephson junction.

#### 3.2.2.1 Junction Turn-On Time

The turn-on switching time of a junction, by definition, is the time it takes for the voltage of the junction to begin to rise after the critical current of the junction is exceeded. This corresponds to the time it takes for the phase of the junction to change from  $\pi/2$  to  $\pi$ .

According to Harris [12] and McDonald et al. [13], the turn-on time can be approximated as follows:

$$t_{turn-on} = \omega_p^{-1} \left\{ \frac{1 + 2\left[\frac{\pi}{2} - \arcsin\left(\frac{I_{bias}}{I_0}\right)\right]}{\frac{(I_{gate} - I_{bias})}{I_{gate}}} \right\}^{0.5}$$

(3.10)

where  $\omega_p$  is the plasma oscillation frequency described in Eq. (3.9),  $I_{bias}$ ,  $I_0$ , and  $I_{gate}$  are the critical current, the initial bias current before switching, and the final bias current right after switching, respectively. For  $I_{bias} \ll I_{gate}$  and  $I_{bias} \ll I_0$ , the turn-on time can be further simplified as:

$$t_{turn-on} = \omega_p^{-1} \left( \frac{1+\pi}{1} \right)^{0.5}$$

(3.11)

#### 3.2.2.2 Junction Rise Time

The rise time is the time it takes for the junction voltage to increase to 90% of its final value, which has been found from simulation to be approximately 2.3 time constants RC, where C is the junction capacitance and R is the equivalent load [14].

#### 3.2.2.3 Junction Fall Time

Analogous to the rise time, the fall time measures how long it takes for the voltage of a junction to drop from 90% to 10% of its high level. The fall time depends on the RC time constant of the junction and the current applied to reset the junction. The lower the

applied current during resetting, the shorter the fall time is. In practice, it can be approximated as somewhere between RC and 4RC [14].

## 3.2.2.4 Junction Plasma Oscillation Decay Time

As can be seen on Fig. 3.5, during the reset, the voltage across the junction decreases exponentially with a time constant RC, where R is the equivalent loading resistance and C is the junction capacitance. Superimposed on this exponentially decaying signal is another component due to the junction's oscillation which occurs at the plasma frequency  $\omega_p$ . The time it takes for this plasma oscillation to decay to an acceptable level is referred to as the plasma oscillation decay time and is the most dominant and limiting factor of a junction's switching time. In most cases, this decay time can be estimated to be around 6 to 7 time constants RC [14].

#### 3.2.2.5 Junction Punchthrough

In the so-called voltage-state logic applications of Josephson junctions, the junction supply current is turned off to reset the junction to the zero-voltage state. It is desired that the junction stays in the zero-voltage state even if the supply current is subsequently raised to a value close to, but less than, the junction critical current  $I_c$ . When the supply current falls below a value  $|I_{min}|$  the junction will fall into the so-called plasma oscillations. If the magnitude of the supply current is raised too quickly and too close to  $|I_c|$ , the junction may again switch to the voltage state. This phenomenon is called punchthrough and occurs because the time allowed for resetting is not long enough. It has been found that the probability P for this type of punchthrough to occur is of the form [15] [16]:

$$P = e^{-\omega_p t_{reset}}$$

(3.12)

where t<sub>reset</sub> is the time for resetting during which the bias is kept below I<sub>min</sub>.

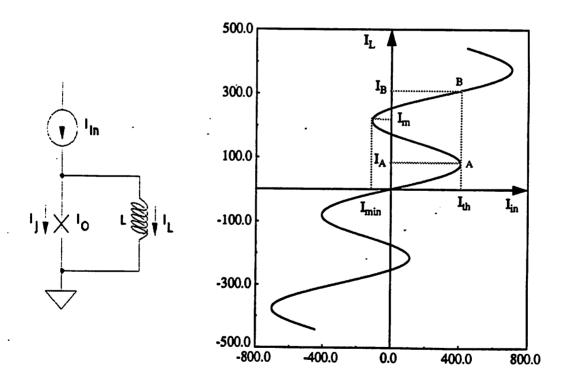

#### 3.2.3 One-Junction SQUID

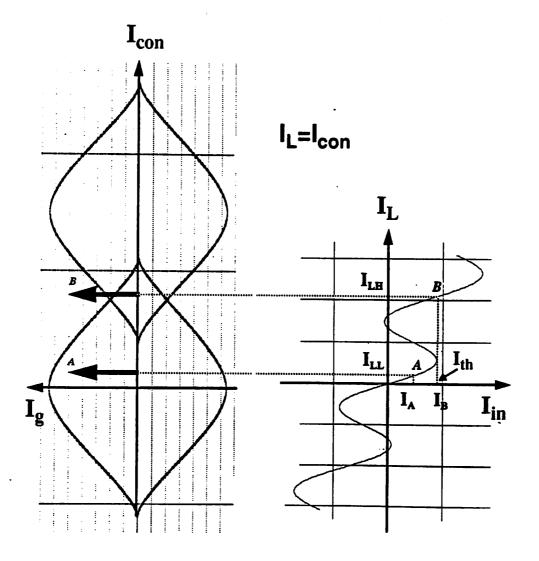

If an inductance is connected in parallel to a junction, one of the most useful devices for superconducting circuits, known as a one-junction SQUID (Superconducting Quantum Interference Device), is obtained. Shown in Fig. 3.6 are both the circuit implementation and the periodic dc transfer curve for a typical one-junction SQUID. Appendix A.1 shows how the transfer curve can be calculated.

Fig. 3.6 Schematic and dc transfer curve of a one-junction SQUID.

In the figure, the horizontal axis is the input current  $I_{in}$ , and the vertical axis is the current through the inductor  $I_L$ . For an input current less than the threshold current  $I_{th}$ , the flux in the superconducting loop (formed by the junction and the inductor) is less than  $\Phi_0/2$ , the SQUID is considered to be the in zero-flux-quantum state, and a very small current  $I_A$  is flowing through the inductor, as indicated by point A. However, as soon as the input current exceeds the threshold current  $I_{th}$ , one flux quantum enters the loop and a much larger current  $I_B$  flows through the inductor (operating point B).

The value of the threshold input current of the SQUID I<sub>th</sub> shown in the dc curve where the SQUID switches from zero-flux-quantum state to one-flux-quantum state can be obtained by differentiating Eq. (A.4) in Appendix A.1 and setting dI<sub>in</sub>/dt to zero to solve for the maximum point. This would give:

$$I_{th} = I_{c} \left\{ \sin \left[ \arccos \frac{-1}{\beta_{L}} \right] + \frac{\arccos (-1/\beta_{L})}{\beta_{L}} \right\}$$

(3.13)

where Ic is the junction critical current and

$$\beta_{\rm L} = \frac{2\pi L I_{\rm L}}{\Phi_0} \tag{3.14}$$

Other useful parameters shown on the curve are the low output current  $I_A$ , the high output current  $I_B$ , the minimum input current to reset the SQUID  $I_{min}$ , and the output current  $I_m$  at the resetting point, which can be derived to be as follows, respectively [14]:

$$I_{A} = I_{C} \frac{\arccos(-1/\beta_{L})}{\beta_{L}}$$

(3.15)

$$I_{B} = I_{m} + \frac{I_{A}}{I_{th}} (I_{th} - I_{min})$$

(3.16)

$$I_{\min} = I_C \frac{2\pi}{\beta_L} - I_{th} \tag{3.17}$$

$$I_{m} = I_{C} \frac{2\pi - \arccos\left(-1/\beta_{L}\right)}{\beta_{L}}$$

(3.18)

It will be shown later that such a device can be used to implement very sensitive comparators by applying a current signal at the input and sensing the output current through the inductor. Analysis and operation of one-junction SQUID will be discussed more extensively and in more detail then.

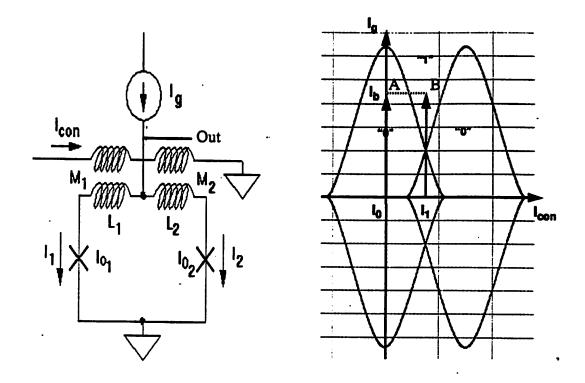

#### 3.2.4 Two-Junction SQUID

Another useful, probably the most important, circuit configuration in superconducting technology is a two-junction SQUID [14] [17]. As shown in Fig. 3.7, a two-junction SQUID consists of two Josephson junctions connected to each other through two inductors  $L_1$  and  $L_2$ , which in turn are magnetically coupled to the two inductors in the control line with mutual inductance  $M_1$  and  $M_2$ . The SQUID is biased by the current  $I_g$  and its critical current is modulated by the control current  $I_{con}$ .

The periodic threshold characteristic curve of the SQUID is plotted in the same figure. The curves show the boundary between the region of the superconducting state (inside the lobes) and the region of the voltage state (outside the lobes). If the operating point of the SQUID lies inside a lobe when the gate bias  $I_g$  is raised, it is in superconducting state and the output voltage is zero. On the other hand, if the operating

Fig. 3.7 Circuit schematic and threshold curves of a two-junction SQUID.

point falls outside a lobe, it is in the voltage state, and the output is high. As a result, for a given bias  $I_b$ , the output of the SQUID is low or high depending on whether the control current  $I_{con}$  is low or high (corresponding to whether the operating point is A or B in the figure), respectively. In the analog-to-digital converter to be discussed in subsequent chapters, this characteristic of a two-junction SQUID is going to be used to implement a device that reads out and determines whether the current through an inductive control line is high or low. Calculation of the threshold curve of a two-junction SQUID is shown in Appendix A.2 and A.3, and detailed analysis can be found in [18].

## 3.3 Periodic-Threshold Flash Analog-To-Digital Converters

There are two different architectures for superconducting flash-type ADCs. The first is the periodic-threshold type, which takes advantages of the periodicity of SQUID threshold characteristic curves to implement an N-bit ADC with only N comparators. The second type is fully parallel architecture, which can potentially achieve faster conversion rate than the periodic-threshold type [19] but requires 2<sup>N</sup>-1 comparators for N-bit resolution. Fully parallel architecture is the main topic of this thesis and will be described in full detail in subsequent chapters. For completeness, various designs and implementations of periodic-threshold ADCs together with their advantages and disadvantages will be described in the rest of the chapter.

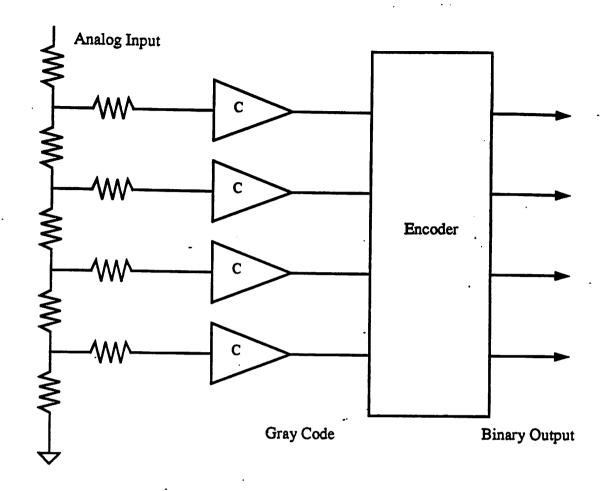

Figure 3.8 shows the architecture implementation for a four-bit periodic-threshold converter. Two- or three-junction SQUIDs are used as comparators and a resistive divider is used to divide the analog current appropriately. Only N comparators are required to implement an N-bit ADC, and the outputs of the comparators are in Gray code. Depending on applications, a Gray-to-binary encoder may or may not be needed. Note that for the Gray-coded numbers, as the output is changed from one level to the next, only one of the output bits changes. This is advantageous since an error in the threshold position can cause at most an output error of 1 LSB.

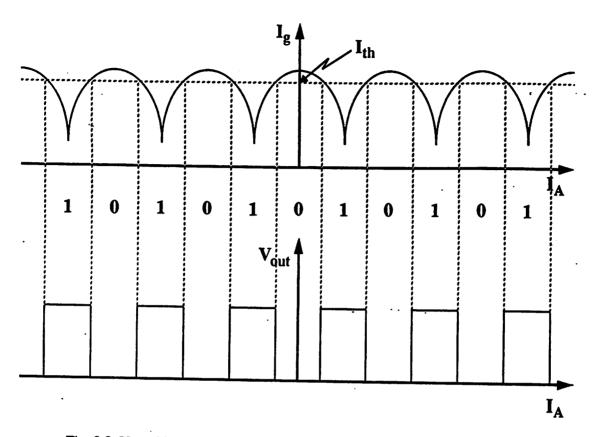

As mentioned earlier in the chapter, the threshold curves of two-junction SQUIDs are periodic. This periodicity of SQUIDs, which is determined by the junction critical current and the loop inductance, can be used to implement comparators with multiple threshold levels, as shown in Fig. 3.9. The periodic threshold curve of a SQUID is shown

Fig. 3.8 Architecture implementation for a four-bit periodic-threshold ADC

again on the top for reference, and the second graph is the output voltage level of the SQUID as a function of the control current  $I_A$ . The input is used as the control for the SQUID and the gate current  $I_g$  is used as the bias. As described earlier, whether the SQUID is in superconducting or voltage state and whether the output is zero or one depend on whether the operating point, determined by the control current  $I_A$  and the bias current  $I_g$ , lies inside or outside a threshold lobe, respectively. As a result, if the SQUID is biased correctly, shown as  $I_{th}$  in the figure, the dependence of the output on the control input is exactly what required for a comparator with multiple threshold levels. As an

Fig. 3.9 Use of SQUID's periodic threshold curve to implement a comparator.

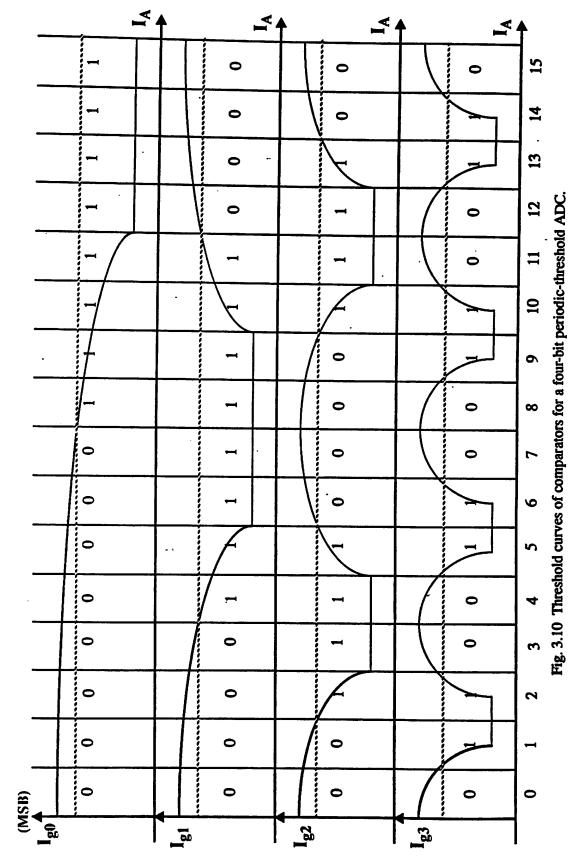

example, Fig. 3.10 shows the threshold curves of comparators for a 4-bit periodic-threshold ADC. The bit patterns of any bit can be generated by expanding the bit patterns of the next less significant bit by a factor of 2. This, in practice, can be done either by successively dividing the input current using a resistive divider or reducing the coupling to the SQUID comparators by a factor of 2.

## 3.3.1 Designs Using Two Or Three-Junction SQUIDs

Periodic threshold characteristic curves of two- or three-junction SQUIDs have been used extensively to design comparators with multiple threshold levels for bit-parallel

analog-to-digital converters [20], [21], and [22]. The mutual coupling of the input signal to the N comparator SQUIDS was designed in the ratio 1,2,4,..., 2<sup>N</sup> by varying the length of the control line. Alternatively, the desired threshold levels for the comparators as described in Fig. 3.10 can be obtained if a resistive divider network is used to divide the input current by a factor of two between successive SQUIDs

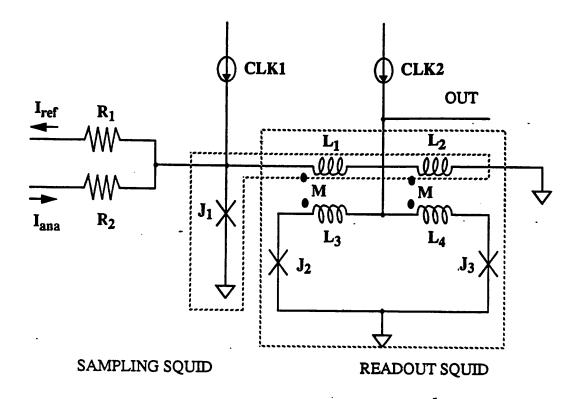

In order to achieve small aperture time and to reduce the circuit sensitivity to the process variation, in particular the variation of the junction critical current density, edge-triggered two- and three-junction SQUIDs have been used in designing comparators for periodic-threshold ADCs.

Since the operation of edge-triggering circuits relies on the rising edge of the bias current and on the relative critical currents of the SQUIDs, the absolute values of the process parameters are not critical [23]. As long as they are tracking well to each other, the circuit will function correctly. In practice, the fast rising edge for the bias current is generated by clock-shaping junctions, which will be discussed further in later chapters. Dhong et al. designed, simulated and tested at low speeds a four-bit ADC using four such edge-triggered comparators [24]. Later on, Petersen was able to demonstrate the operation of the ADC at 1 GHz clock frequency with resolution of three and four bits at 499 MHz and 280 MHz input bandwidth, respectively [25].

Another edge-triggered ADC that was very similar to Dhong's but with much simpler comparators was designed by Hamilton et al. [26]. This design, referred to as Current Latching Analog Microcomparator (CLAM), uses a series stack of two 2-junction SQUIDs to implement each of the comparators and operates in a way similar to the

self-gating AND comparator designed by Dhong. A track-and-hold circuit also was added at the front end of the ADC to increase the maximum bandwidth. The design was simulated successfully for a six-bit version at 300 MHz and for a four-bit version at 1 GHz input bandwidth. Experimentally, the circuits were demonstrated up to 100 MHz input bandwidth and 100 ps conversion time.

## 3.3.2 Designs Using Quasi-One-Junction SQUIDs

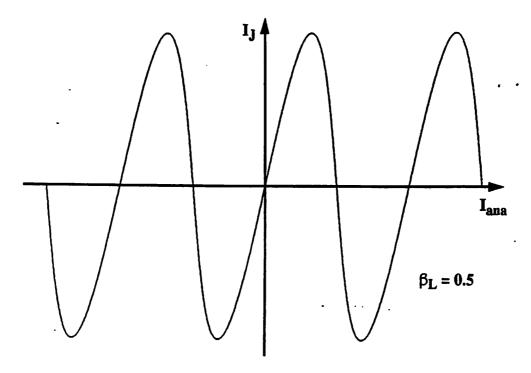

Simulations and experiments have shown that even though ADCs using two- or three-junction SQUIDs can be operated at very high conversion rate, they have very limited maximum input bandwidth. The main reasons include dynamic distortion of the SQUID threshold curve at high frequencies due to the hysteresis in the vortex-to-vortex transition in the SQUIDs [27]. These problems can be reduced by using nonhysteretic one-junction SQUIDs.

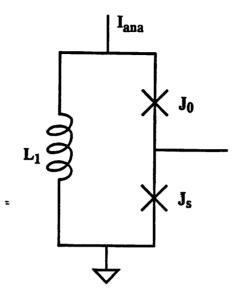

As can be seen from Fig. 3.11, for a one-junction SQUID, the current flowing through the junction itself  $I_J$  is a periodic function of the analog input current  $I_{ana}$ . It is single-valued as long as the parameter  $\beta_L$  is less than 1, where  $\beta_L$  is defined as

$$\beta_{L} = \frac{2\pi L I_0}{\Phi_0} \qquad (3.19)$$

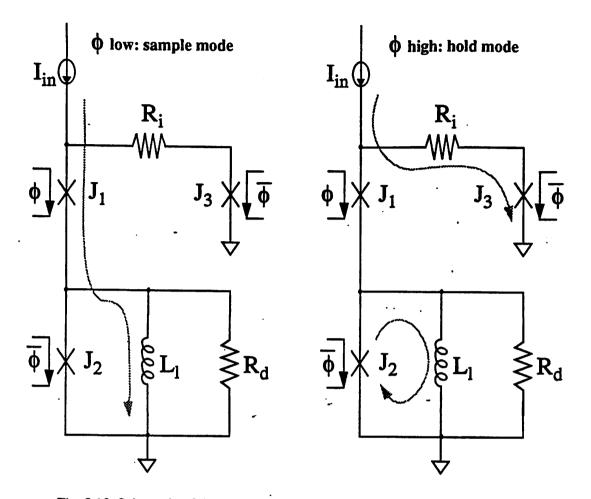

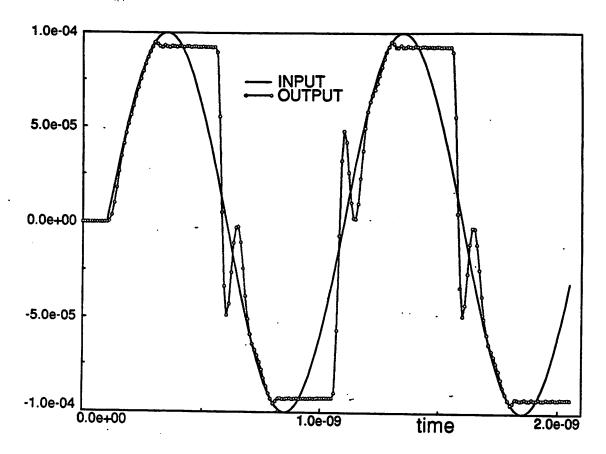

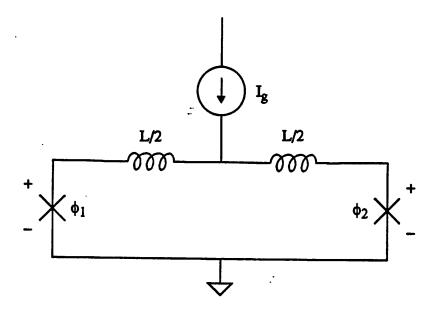

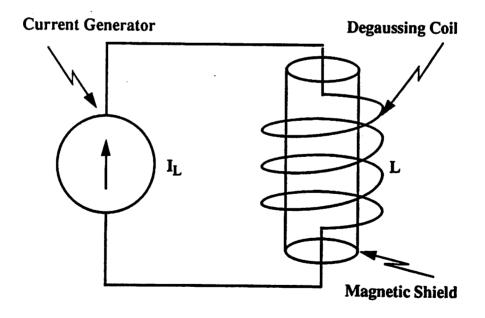

L is the SQUID inductance and Io is the critical current of the junction.