# Copyright © 1994, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### LOW POWER DIGITAL CMOS DESIGN

by

Anantha P. Chandrakasan

Memorandum No. UCB/ERL M94/65

30 August 1994

#### **LOW POWER DIGITAL CMOS DESIGN**

by

Anantha P. Chandrakasan

Memorandum No. UCB/ERL M94/65

30 August 1994

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### **Abstract**

#### Low Power Digital CMOS Design

by

Anantha P. Chandrakasan

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Robert W. Brodersen, Chair

Portable operation is becoming increasingly important for many of the most exciting new electronic products. The strict limitation on power dissipation which this imposes must be met by the designer while still meeting ever higher computational requirements. A system level approach is presented to minimize power consumption which involves optimizing technology, circuit and logic design, architectures, and algorithms. An architecture driven voltage scaling strategy has been developed which trades silicon area for lower power consumption without sacrificing system performance. This strategy enables an order of magnitude reduction in power consumption over current-day "low-voltage" 3.3V standards. Approaches to minimize the switched capacitance are also developed which involve data coding and representation, minimizing resource sharing, minimizing spurious transitions, optimizing transistor sizes, activity based logic level shut down, aggressive predictive shut down for programmable computation, dynamic range optimization, and the utilization of algorithmic transformations. A CAD tool has been developed to automatically find computational structures that have minimal power requirements to implement a given function. The various techniques have been applied to the design of a chipset for a portable multimedia terminal. Six chips provide protocol conversion, synchronization, error correction, packetization, buffering, video decompression, and D/A conversion at a total power consumption of less than 5 mW, while operating from a 1.1V supply.

Robert W. Brodersen

Chairman of Committee

To my dear parents,

Gowri and Nagappa Chandrakasan

my wife Karthiyayani,

and Mrs. Charlotte Coe

## TABLE OF CONTENTS

| Inti | oduction                                                                                                                                                                                                                                                                                                                                                                       | 1                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 1.1  | Overview of Thesis  1.1.1 Low-power Design Methodologies [Chapters 2,3, and 4]                                                                                                                                                                                                                                                                                                 | 4<br>9                     |

| Pov  | ver Consumption in CMOS Circuits                                                                                                                                                                                                                                                                                                                                               | . 12                       |

| 2.1  | Switching Component of Power  2.1.1 Computation of Switching Energy Per Transition  2.1.2 Definition of Switching Activity Factor, α  2.1.3 Components of Physical Load Capacitance  2.1.4 Influence of Logic Level Statistics and Circuit Topologies on Switching Activity, α  2.1.5 Word Level Signal Statistics Influencing Activity, α  2.1.6 Influence of Voltage Scaling | 14<br>19<br>22<br>29<br>44 |

| 2.2  | Short-circuit Component of Power                                                                                                                                                                                                                                                                                                                                               | 52                         |

| 2.3  | Leakage Component of Power                                                                                                                                                                                                                                                                                                                                                     | 58                         |

| 2.4  | Static Power                                                                                                                                                                                                                                                                                                                                                                   | 61                         |

| 2.5  | Summary                                                                                                                                                                                                                                                                                                                                                                        | 62                         |

|      | proaches to Voltage Scaling and Issues for Low Voltage eration                                                                                                                                                                                                                                                                                                                 | . 65                       |

| 3.1  | 3.1.1 Reliability-Driven Voltage Scaling                                                                                                                                                                                                                                                                                                                                       | 66<br>68<br>72<br>73<br>77 |

| 3.2  | Support Circuitry for Low-voltage Operation                                                                                                                                                                                                                                                                                                                                    | .107                       |

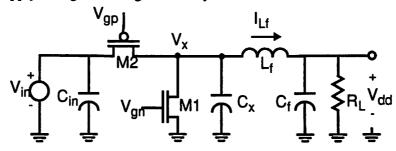

|     | 3.2.1 High Efficiency Power Supply Generation [Stratakos94] | .107<br>.114         |

|-----|-------------------------------------------------------------|----------------------|

| 3.3 | Noise Considerations at Reduced Supply Voltages             | .115                 |

| 3.4 | Summary                                                     | .117                 |

| Apj | proaches to Minimizing Switched Capacitance                 | 119                  |

| 4.1 | Algorithmic Optimization                                    | .122<br>.122         |

|     | Multiplications by Constants                                |                      |

| 4.2 | Architecture Optimization                                   | .144<br>.149<br>.151 |

| 4.3 | Logic Optimization                                          | .156<br>.157         |

| 4.4 | Circuit Optimization                                        | .160<br>.162         |

| 4.5 | Physical Design                                             | .165<br>.166         |

| 4.6 | Summary                                                     | .169                 |

| Coı | mputer Aided Design Tools                                   | .171                 |

| 5.1 | Previous and Concurrent Work                                | .172                 |

| 5.2 | Application of Transformations to Minimize Power            | .181                 |

|            | 5.2.3 Operation Substitution                                           | 183<br>184 |

|------------|------------------------------------------------------------------------|------------|

|            | 5.2.5 Wordlength Reduction                                             |            |

| 5.3        | Cost Function                                                          |            |

|            | 5.3.1 Capacitance estimate                                             | 189        |

| E 1        | 5.3.2 Supply Voltage Estimation                                        |            |

|            | Optimization Algorithm                                                 |            |

| 5.5        | Examples and Results                                                   |            |

|            | 5.5.1 Example #1: Wavelet Filter                                       |            |

|            | 5.5.3 Example #3: Volterra Filter                                      |            |

| 5.6        | Summary                                                                |            |

| A L        | Low-power Chipset for a Portable Multimedia Terminal                   | 216        |

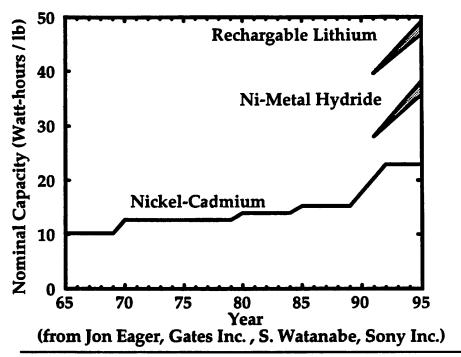

| 6.1        | Technology Trends for Low Power                                        | 220        |

|            | 6.1.1 Battery Technology                                               | 220        |

|            | 6.1.2 Display Technology                                               | 221        |

|            | 6.1.3 Packaging Technology                                             |            |

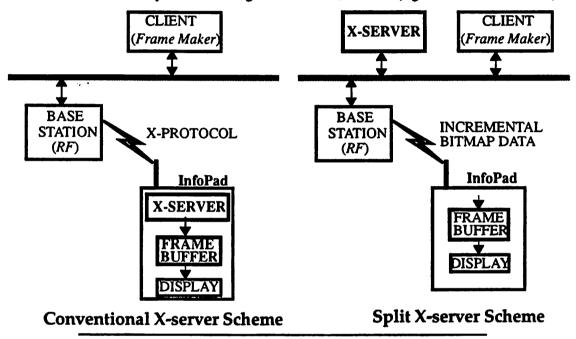

| 6.2        | System Partitioning for Low-power                                      | 223        |

|            | 6.2.1 Impact of the Low-power Partitioning Approach on the Interactive | 227        |

|            | Latency                                                                | 221        |

|            | to High BER                                                            | 228        |

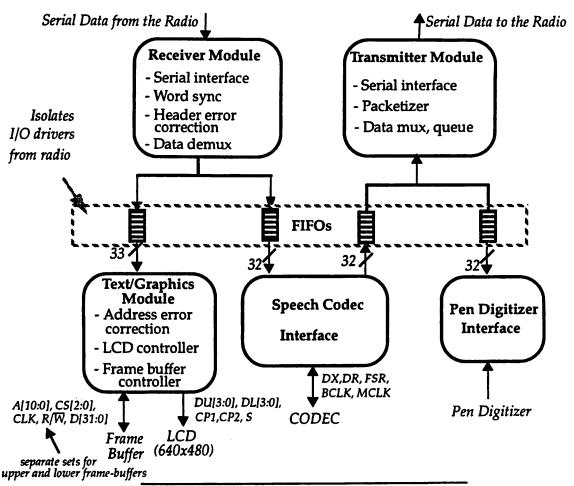

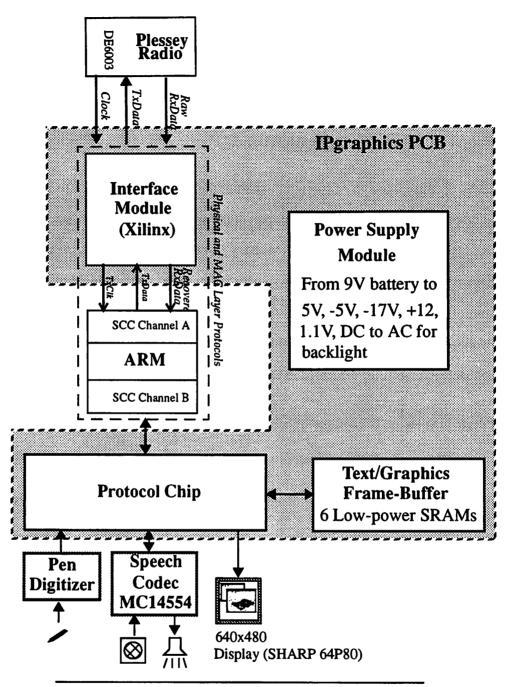

| 6.3        | Architecture of the Portable Multimedia Terminal                       | 229        |

| 6.4        | Protocol Chip                                                          | 231        |

| <b>.</b> . | 6.4.1 Radio Receiver Module [Burd93]                                   | 232        |

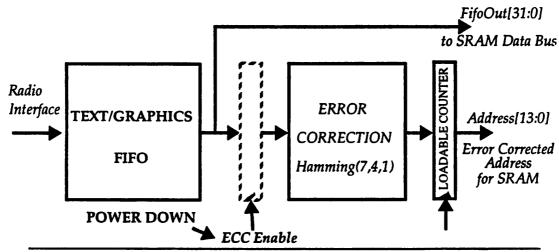

|            | 6.4.2 Text/Graphics Module                                             | 237        |

|            | 6.4.3 Speech I/O Module                                                | 251        |

|            | 6.4.4 Pen Input Module [Narayanaswamy93]                               | 254<br>254 |

|            | 6.4.5 Radio Transmitter Module                                         | 254<br>255 |

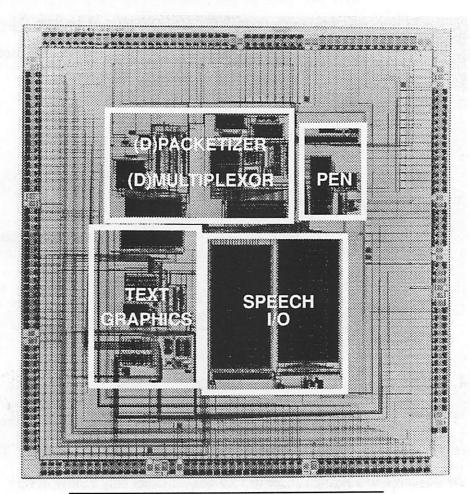

|            | 6.4.7 Chip Layout and Statistics                                       | 259        |

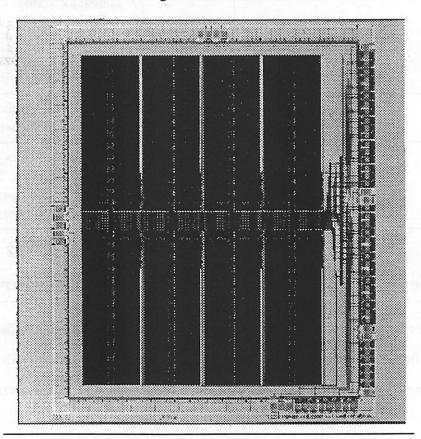

| 6.5        | Text/Graphics Frame-buffer Module [Burstein93]                         | 261        |

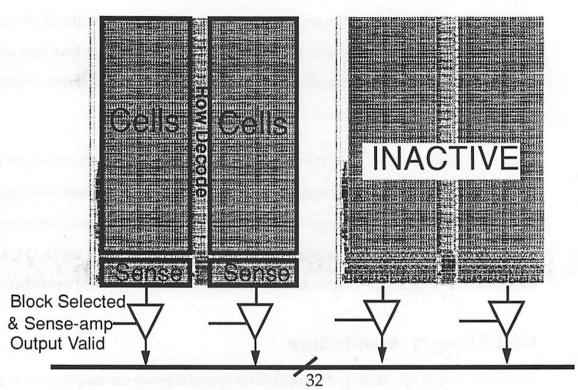

|            | 6.5.1 Memory Architecture                                              | 263        |

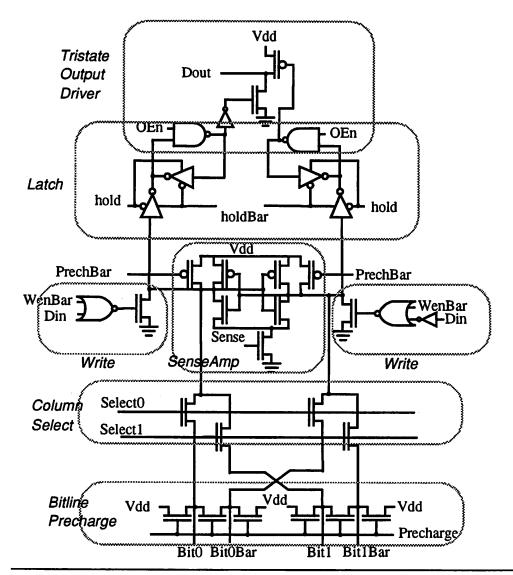

|            | 6.5.2 Circuit Level Optimization                                       | 265        |

|            | 6.5.3 Chip Statistics                                                  |            |

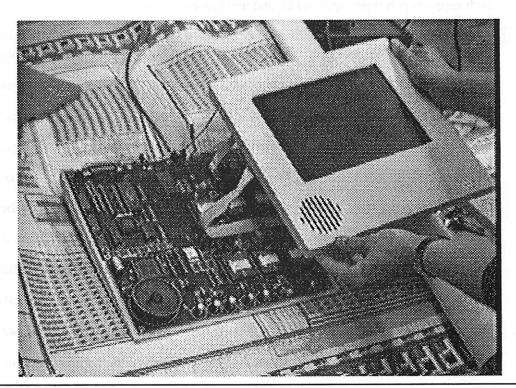

| 6.6        | System Implementation                                                  | 268        |

| 6.7                                    | Summary                                     | 271                      |

|----------------------------------------|---------------------------------------------|--------------------------|

| A L                                    | ow-power Video Decompression Chipset        | 273                      |

| 7.1                                    | Algorithm Selection for Video Decompression | 273<br>274               |

| 7.2                                    | Video Decompression Module Implementation   | 278<br>283<br>285<br>289 |

| 7.3                                    | Summary                                     | 299                      |

|                                        | v-power<br>grammable Computation            | 300                      |

| 8.1                                    | Architectural Approaches to Low-power       | 301                      |

| 8.2                                    | Shutdown Techniques                         | 305                      |

| 8.3                                    | Architecture-Driven Voltage Reduction       | 321<br>323<br>326        |

| 8.4                                    | Summary                                     | 331                      |

| Con                                    | clusions and Future Directions              | 332                      |

| 9.1                                    | Future Directions                           | 337<br>338               |

| Bib                                    | liography                                   | 341                      |

| Appendix A: Proof of NP-Completeness34 |                                             |                          |

## LIST OF FIGURES

| Figure 1-1: | Power consumption of micro-processors reported at ISSCC over the last         |    |

|-------------|-------------------------------------------------------------------------------|----|

|             | 20 years [Rabaey94]                                                           | 2  |

| Figure 1-2: | A system level approach to supply voltage scaling                             | 6  |

| Figure 1-3: | Dependence of activity on statistics: correlated vs. random input             | 7  |

| Figure 1-4: | A system level approach to minimizing the switched capacitance                | 8  |

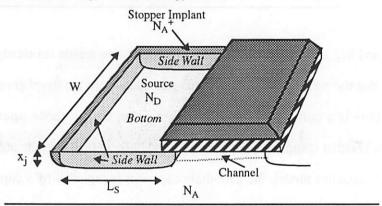

| Figure 2-1: | Circuit model for computing the dynamic power of a CMOS gate                  | 14 |

| Figure 2-2: | Switching power for reduced swing logic.                                      | 16 |

| Figure 2-3: | Charge sharing in dynamic circuits result in "extra" switching power          | 17 |

| Figure 2-4: | Stepwise driver for a capacitive load CL                                      | 18 |

| Figure 2-5: | Switching energy analysis must include internal node switching.               | 21 |

| Figure 2-6: | Circuit model for computing parasitic load capacitance of a CMOS gate         | 22 |

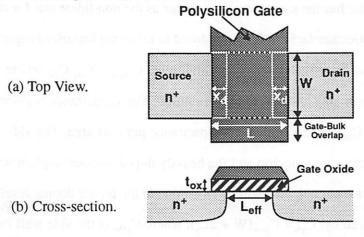

| Figure 2-7: | Overlap capacitance for a MOS device.                                         | 23 |

| Figure 2-8: | Junction capacitance for a MOS device                                         | 24 |

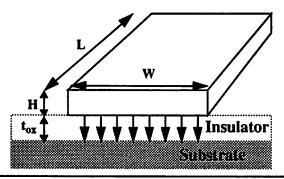

| Figure 2-9: | Parallel plate capacitance model of interconnect capacitance                  | 25 |

| Figure 2-10 | Fringe field contribution to the total interconnect capacitance [Glasser85]   | 26 |

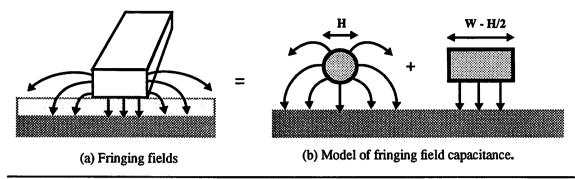

| Figure 2-11 | Interconnect capacitance including fringing effect as a function              |    |

|             | of W/tox [Schaper83]                                                          | 26 |

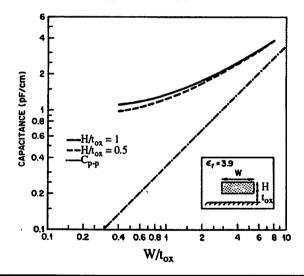

|             | Interconnect capacitance including wire-to-wire capacitance [Schaper83]       |    |

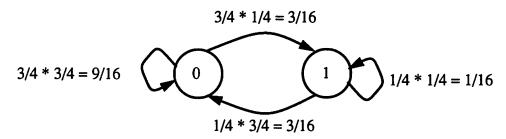

| Figure 2-13 | State transition diagram for a 2 input NOR gate                               | 31 |

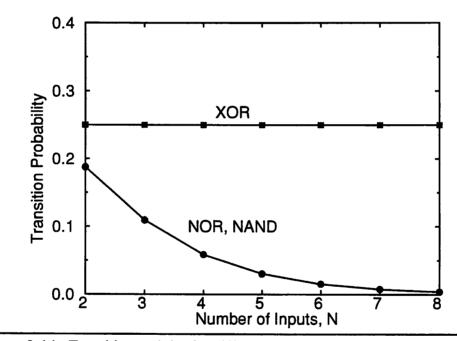

|             | Transition activity for different gates as function of the number of inputs   |    |

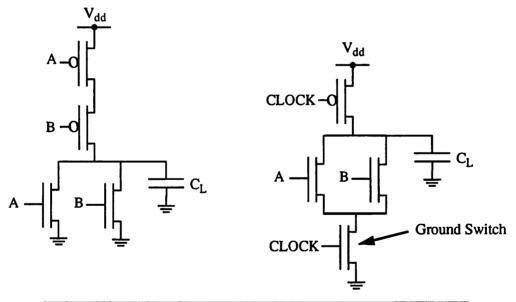

|             | Static NOR vs. N-tree based dynamic NOR                                       |    |

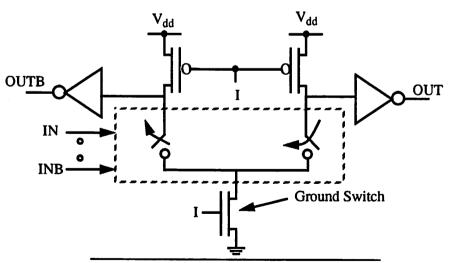

| Figure 2-16 | : A generalized DCVSL gate                                                    | 34 |

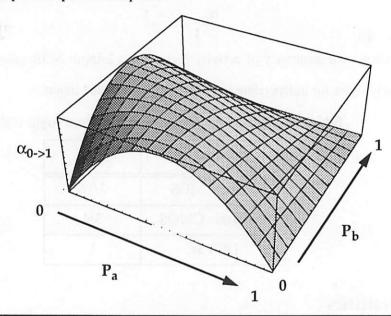

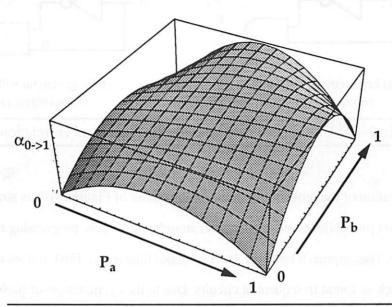

| Figure 2-17 | : Transition probability for a 2 input NOR as a function of input statistics  | 36 |

| -           | : Transition probability for a 2 input XOR gate                               |    |

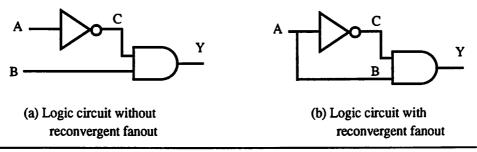

|             | Examples illustrating the effect of signal correlations                       |    |

| Figure 2-20 | : Dynamic component of switching power                                        | 41 |

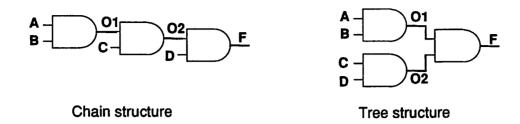

| Figure 2-21 | : Simple example to demonstrate the influence of circuit topology on activity | 42 |

| Figure 2-22 | : Circuit imbalances result in spurious transitions                           | 43 |

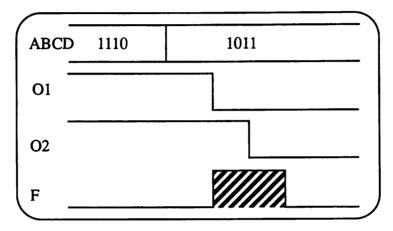

| Figure 2-23 | : Waveforms for a 16-bit adder demonstrating glitching behavior               | 44 |

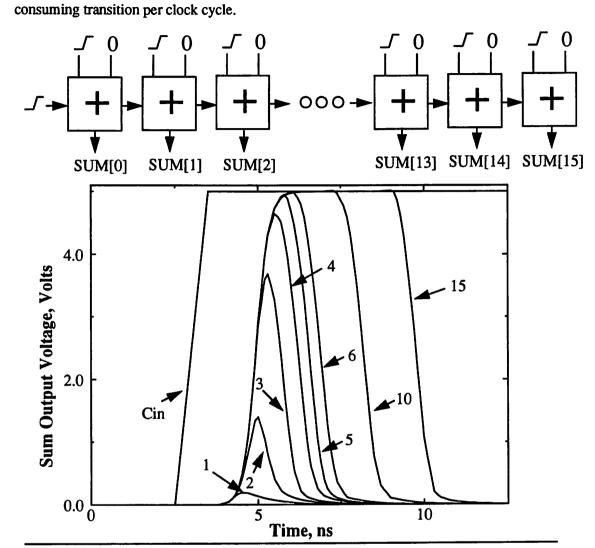

| Figure 2-24 | : Data in signal processing applications is often correlated                  | 45 |

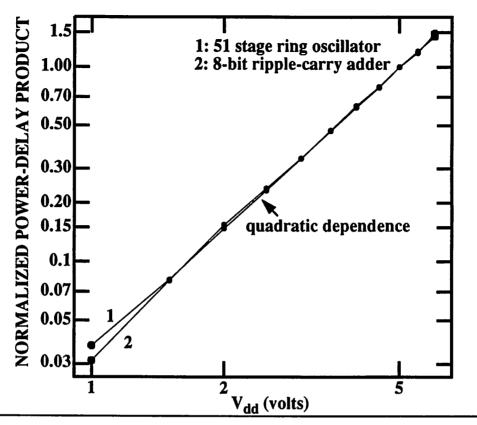

| Figure 2-25 | : Power-delay product exhibiting square law dependence for two different      |    |

|             | circuits                                                                      |    |

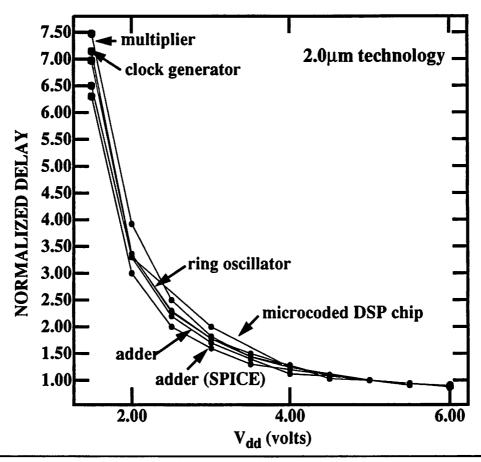

| Figure 2-26 | : Data demonstrating delay characteristics follow simple first order theory   | 49 |

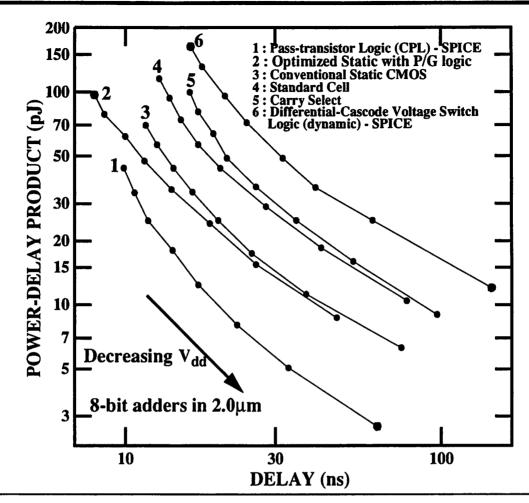

| Figure 2-27 | : Data showing improvement in power-delay product at the cost of speed        |    |

| for various circuit approaches                                                                | 51  |

|-----------------------------------------------------------------------------------------------|-----|

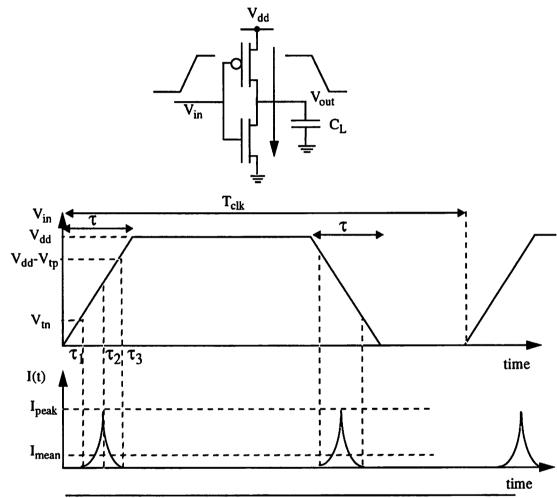

| Figure 2-28 : Current behavior with no output load [Veendrick84]                              |     |

| Figure 2-29: Short-circuit current as a function of load capacitance [Veendrick84]            |     |

| Figure 2-30 : Short-circuit component of power                                                |     |

| Figure 2-31 : Reverse bias diode leakage currents                                             |     |

| Figure 2-32 : Sub-threshold leakage component of power                                        |     |

| Figure 2-33: Degenerated voltage level feeding a CMOS gate resulting in static power          |     |

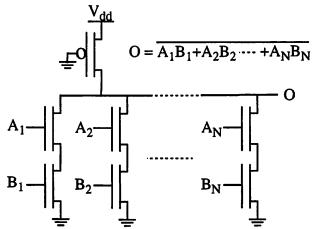

| Figure 2-34: Implementing complex logic using pseudo-NMOS                                     |     |

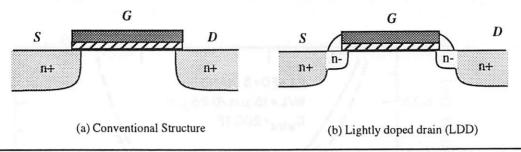

| Figure 3-1: Drain doping profile for a conventional profile and an LDD device                 |     |

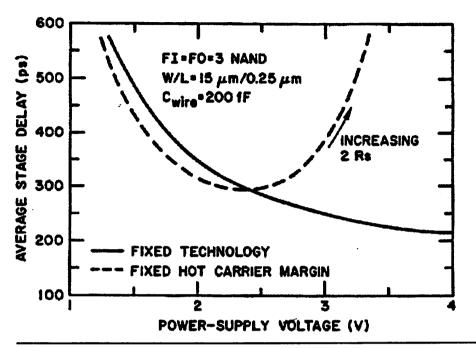

| Figure 3-2: Reliability driven supply voltage selection [Davari88]                            |     |

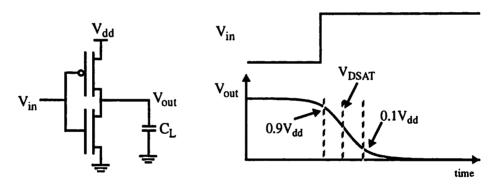

| Figure 3-3: Model for computing delay and critical voltage                                    |     |

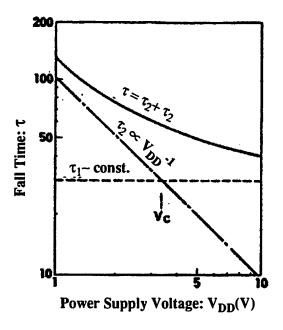

| Figure 3-4: Two components of delay and critical voltage [Kakamu90]                           |     |

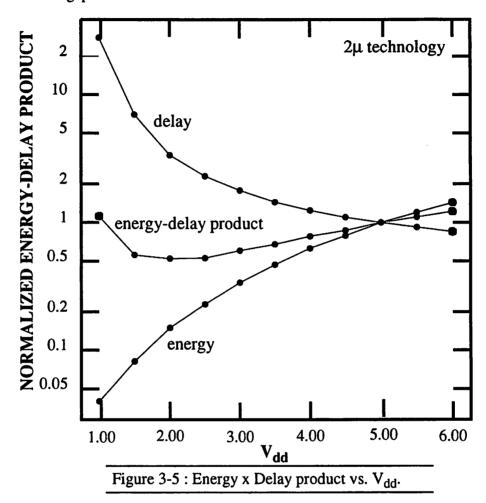

| Figure 3-5: Energy x Delay product vs. V <sub>dd</sub>                                        |     |

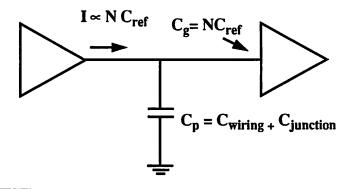

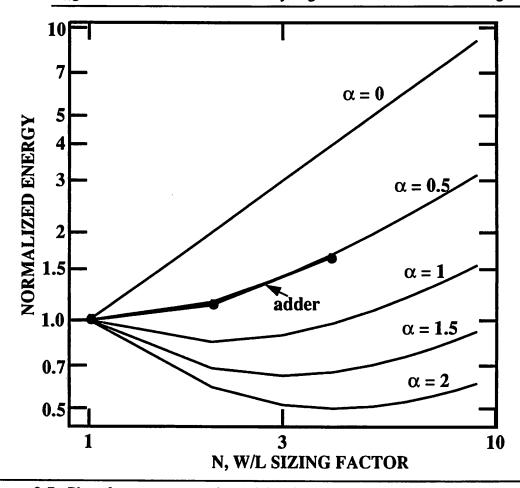

| Figure 3-6: Circuit model for analyzing the effect of transistor sizing                       | 76  |

| Figure 3-7: Plot of energy vs. transistor sizing factor for various parasitic contributions   | 76  |

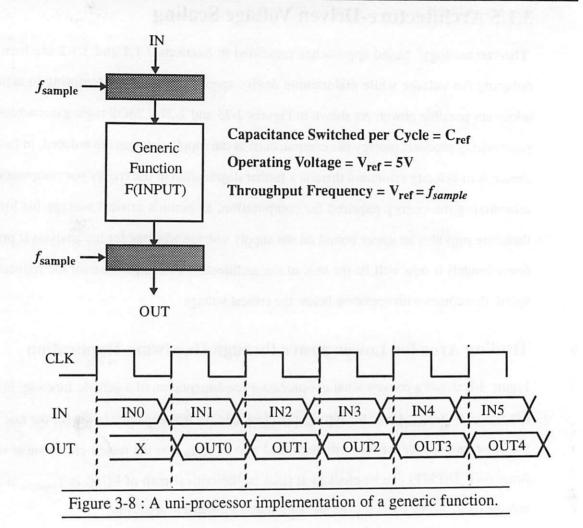

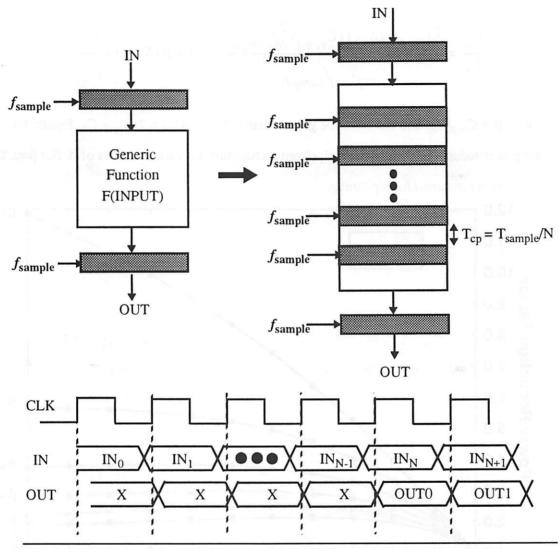

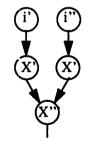

| Figure 3-8: A uni-processor implementation of a generic function.                             | 78  |

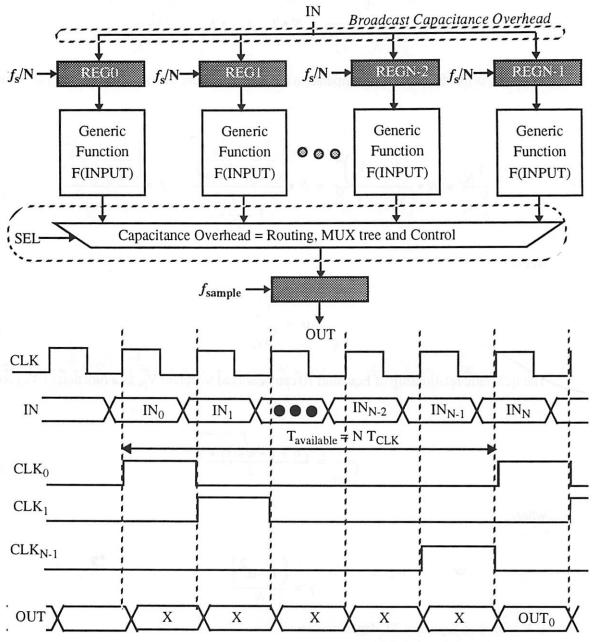

| Figure 3-9: A multi-processor implementation of a generic function                            | 79  |

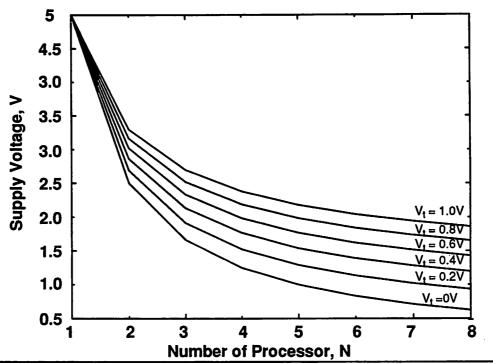

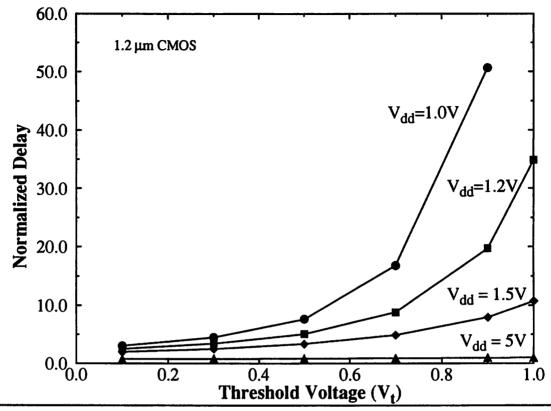

| Figure 3-10: Voltage reduction vs. number of processors as a function of V <sub>t</sub>       | 81  |

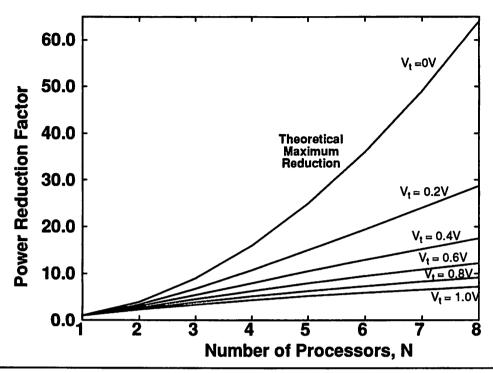

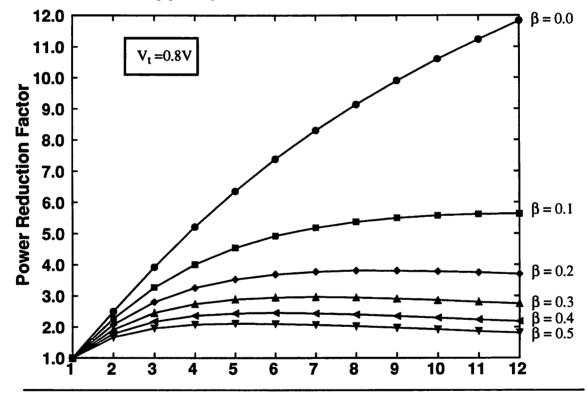

| Figure 3-11: Power reduction (P1/PN) vs. number of processors as a function of V <sub>t</sub> | 84  |

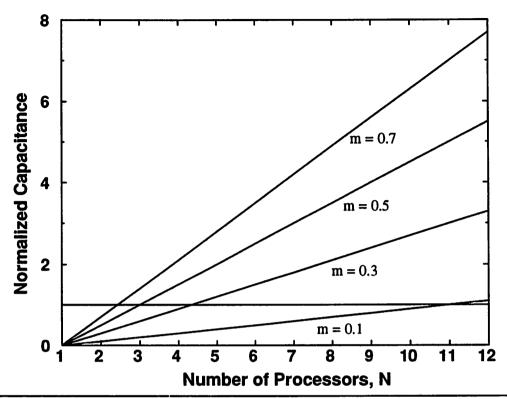

| Figure 3-12: Capacitance function for the processing and input routing overhead               | 87  |

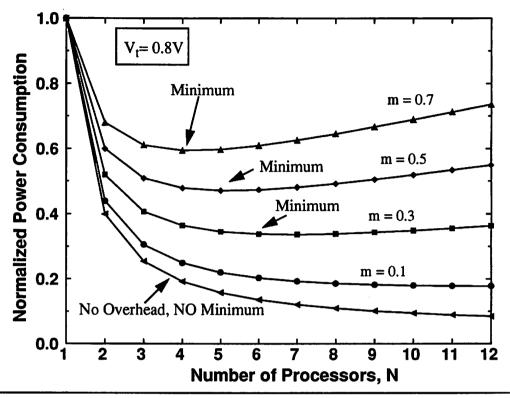

| Figure 3-13: Power vs. N for various levels of overhead capacitance                           | 88  |

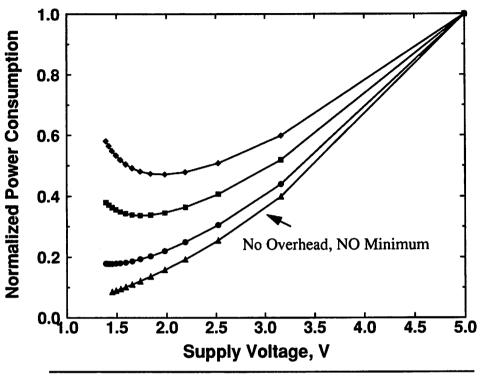

| Figure 3-14 : Architecture Driven Optimum Supply Voltage                                      | 89  |

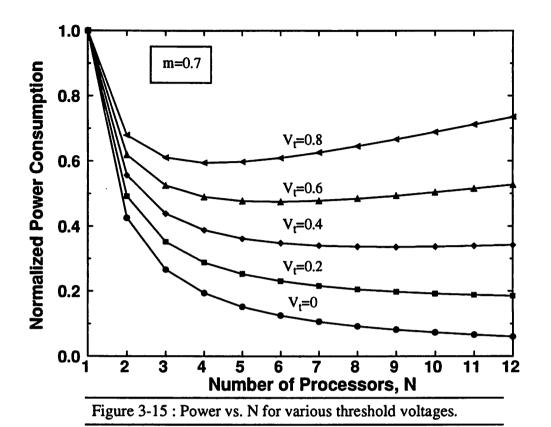

| Figure 3-15: Power vs. N for various threshold voltages                                       | 90  |

| Figure 3-16: N stage pipelining allows reduction of critical path and voltage                 | 91  |

| Figure 3-17: Power reduction for N-stage pipelining for various overhead factors              | 92  |

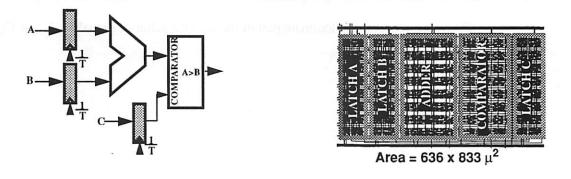

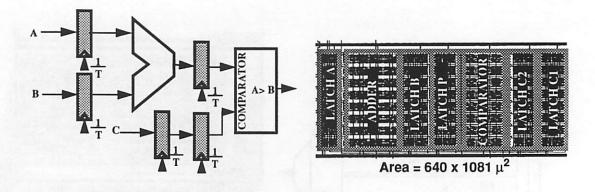

| Figure 3-18: A simple datapath with corresponding layout                                      | 93  |

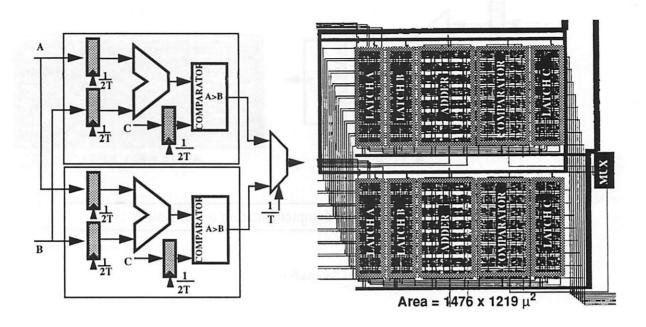

| Figure 3-19 : Parallel implementation of the simple datapath                                  | 95  |

| Figure 3-20: Pipelined implementation of the simple datapath                                  | 96  |

| Figure 3-21: Optimum voltage of operation for the add/compare computation                     | 98  |

| Figure 3-22: Using speedup transformations to reduce power                                    | 102 |

| Figure 3-23: Speed optimizing is different than power optimization                            | 103 |

| Figure 3-24: Effect of threshold reduction on the delay for various supply voltages           | 106 |

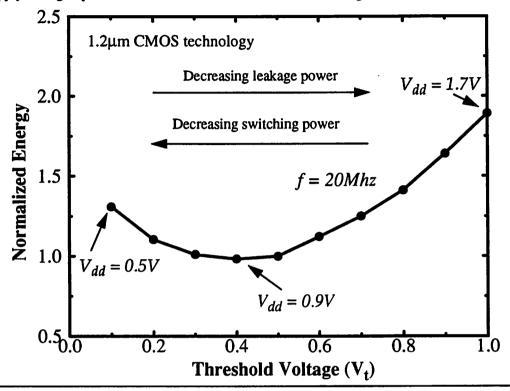

| Figure 3-25: Compromise between dynamic and leakage power dissipation through                 |     |

| V <sub>t</sub> variation                                                                      | 107 |

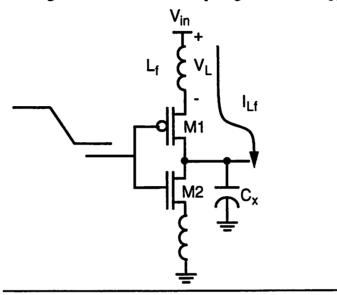

| Figure 3-26: A Buck regulator that be used to generate arbitrary voltages                     | 108 |

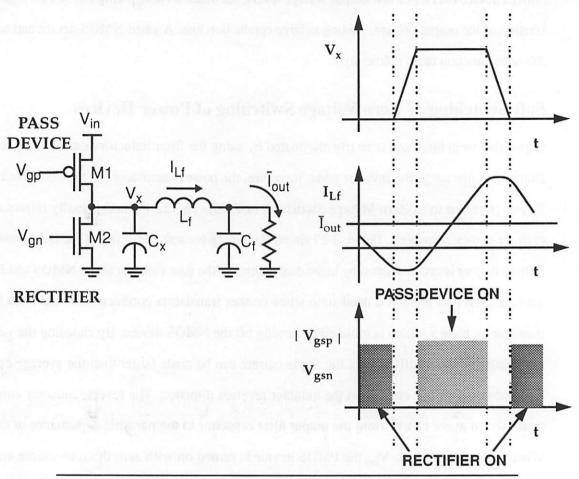

| Figure 3-27: Timing for soft-switching of the Buck converter                                  | 110 |

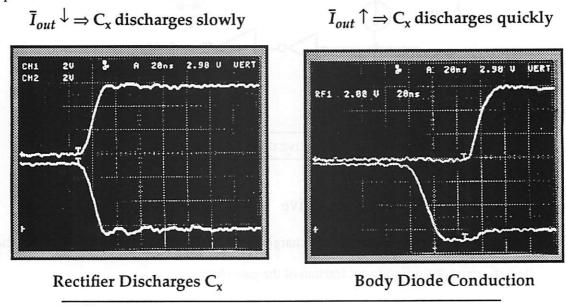

| Figure 3-28: Effects of varying load conditions on waveforms                                  | 111 |

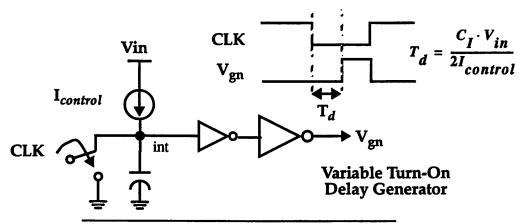

| Figure 3-29 : Adaptive dead-time control                                                      | 112 |

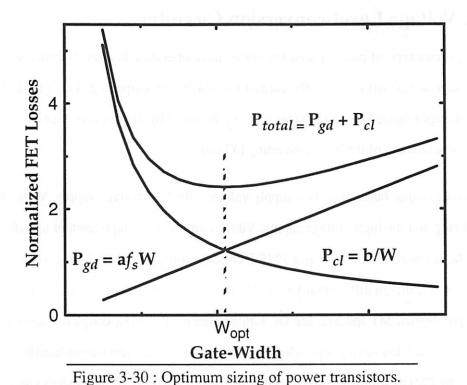

| Figure 3-30: Optimum sizing of power transistors                                        | 113 |

|-----------------------------------------------------------------------------------------|-----|

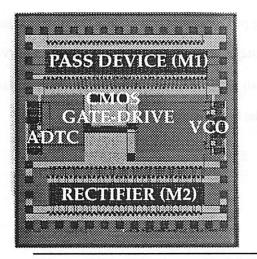

| Figure 3-31: Die photo of a 1.5V Buck regulator                                         | 113 |

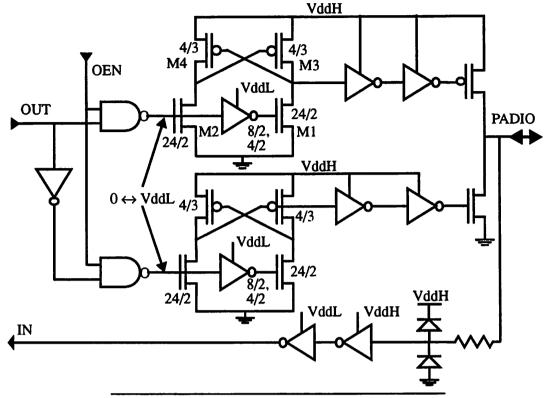

| Figure 3-32 : Level-conversion I/O pad buffer                                           | 115 |

| Figure 3-33: Inductive noise on the power supplies                                      | 116 |

| Figure 4-1: Data in signal processing applications is often correlated                  | 120 |

| Figure 4-2: Dependence of activity on statistics: correlated vs. random input           | 121 |

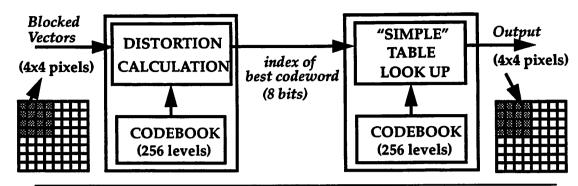

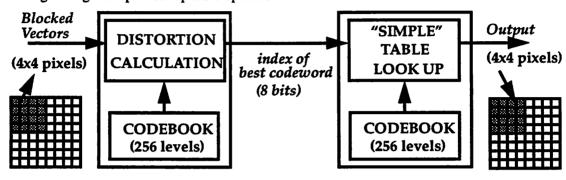

| Figure 4-3: Video compression/decompression using Vector Quantization                   | 123 |

| Figure 4-4: Codebook organization for Full-search Vector Quantization                   | 124 |

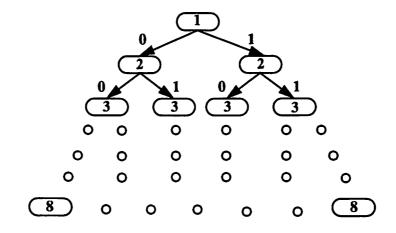

| Figure 4-5: Tree structured Vector Quantization                                         | 125 |

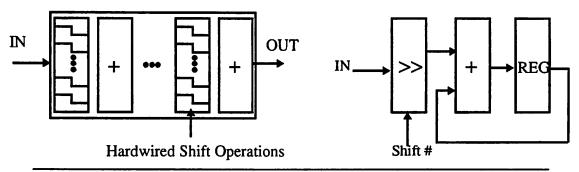

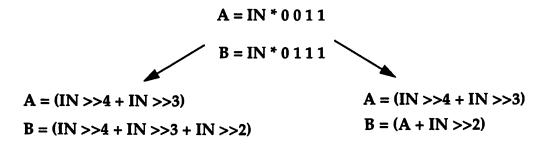

| Figure 4-6: Hardwired shift-add and time-muxed shift-add implementations                | 127 |

| Figure 4-7: Example of common sub-expression elimination                                | 128 |

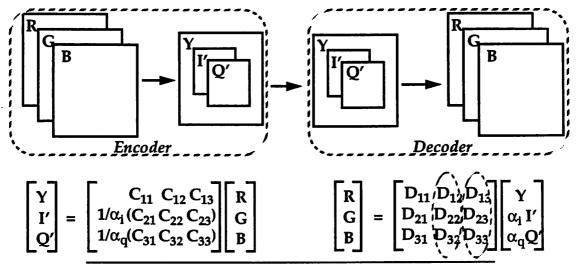

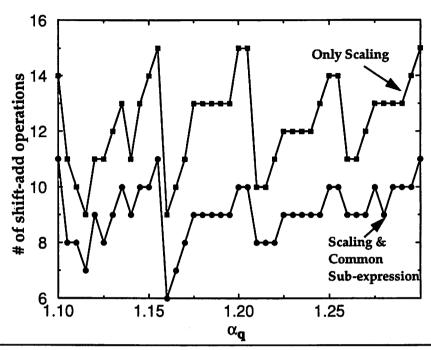

| Figure 4-8: Color conversion matrix for video applications                              | 129 |

| Figure 4-9: Exploiting common sub-expression to minimize number of operations           | 130 |

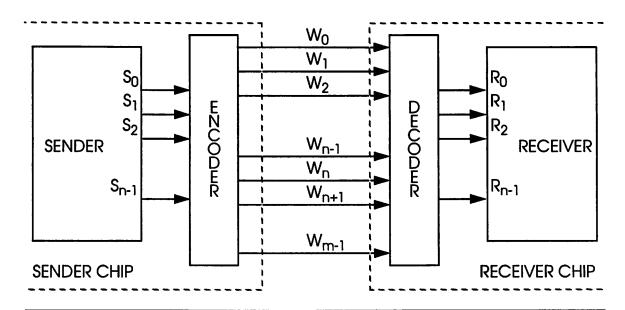

| Figure 4-10: Data coding approach to reduction of switching activity on highly          |     |

| capacitive inter-chip I/O Lines. Note that m >= n                                       | 131 |

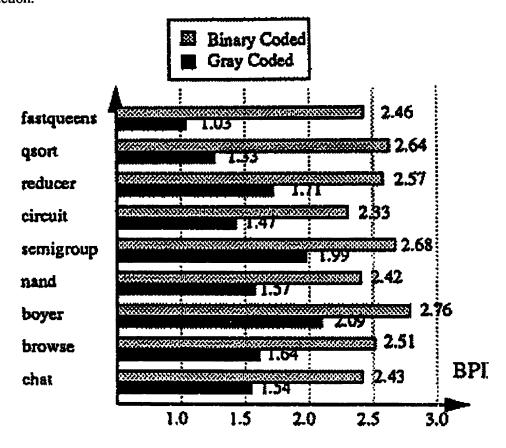

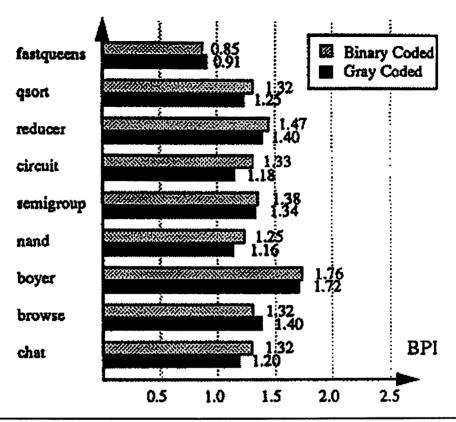

| Figure 4-11: Temporal transition activity comparison for instruction addresses [Su94]   | 135 |

| Figure 4-12: Temporal transition activity comparison for data addresses [Su94]          | 136 |

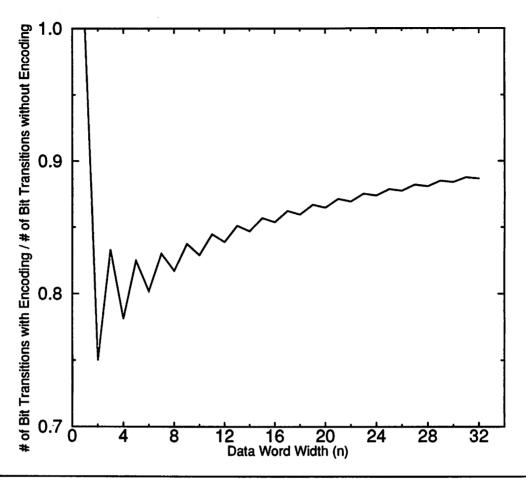

| Figure 4-13: Theoretically predicted reduction in switching activity for a stream of    |     |

| uniformly distributed data words [Srivastava94]                                         | 138 |

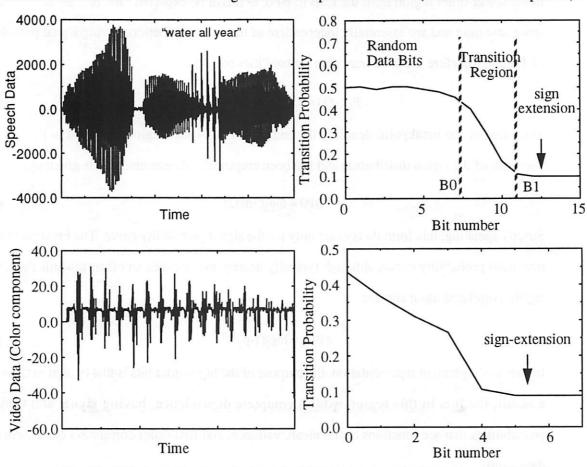

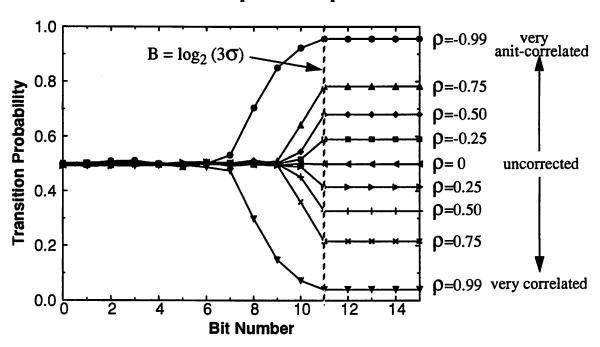

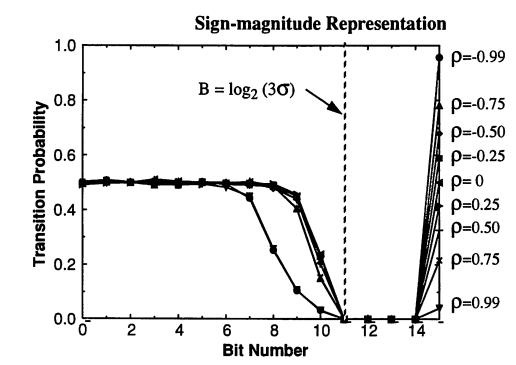

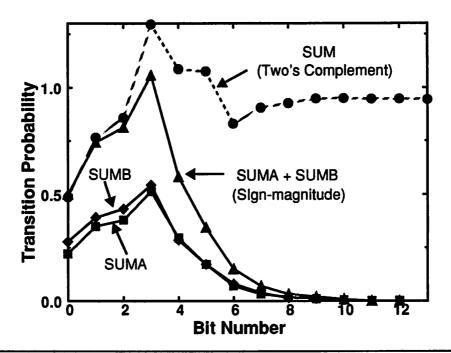

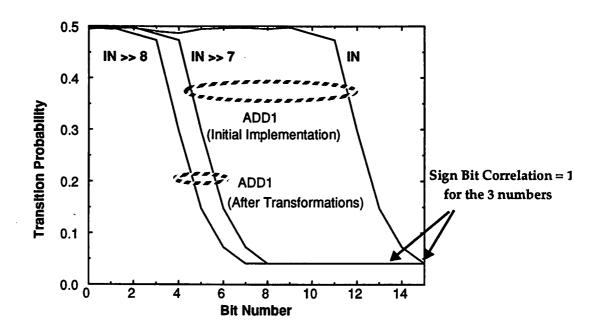

| Figure 4-14: Transition activity for different number representations                   | 142 |

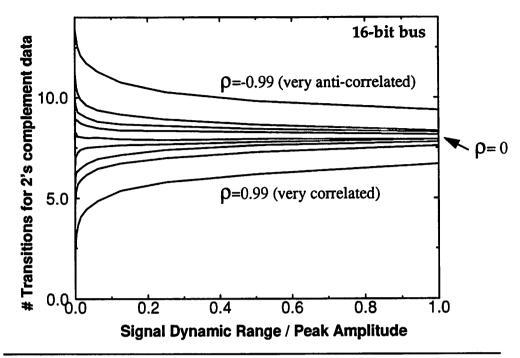

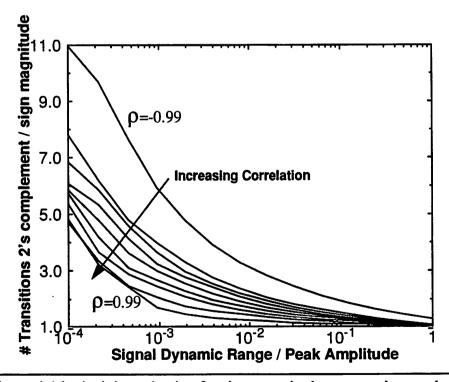

| Figure 4-15: Transition activity for two's complement representation                    | 143 |

| Figure 4-16: Activity reduction for sign-magnitude over two's complement                | 143 |

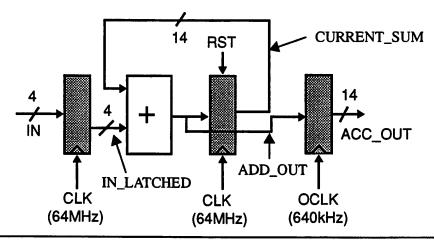

| Figure 4-17: Two's complement implementation of an accumulator                          | 144 |

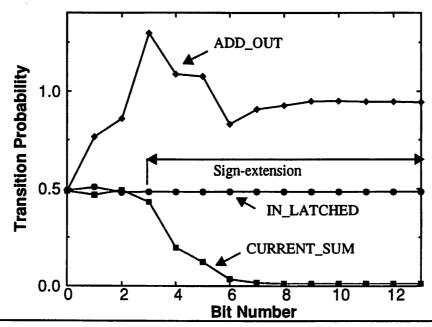

| Figure 4-18: Signal statistics for two's complement implementation of the accumulator   |     |

| datapath assuming random inputs                                                         | 146 |

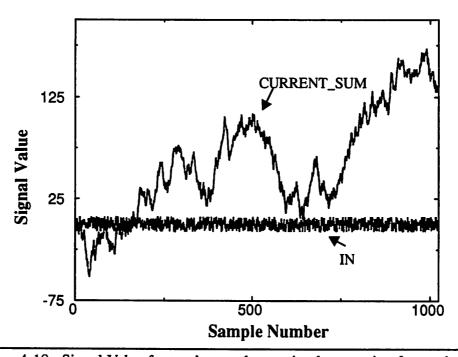

| Figure 4-19: Signal Value for two's complement implementation for random inputs         | 146 |

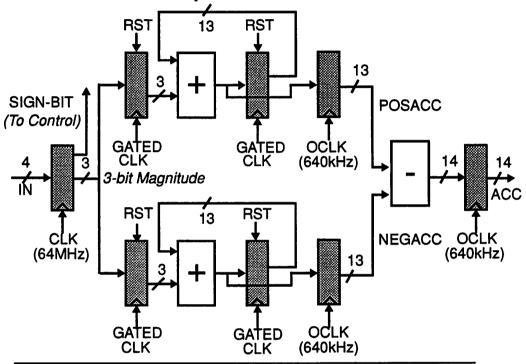

| Figure 4-20: Sign magnitude implementation of an accumulator                            | 147 |

| Figure 4-21: Signal statistics for Sign Magnitude implementation of the accumulator     |     |

| datapath assuming random inputs                                                         | 148 |

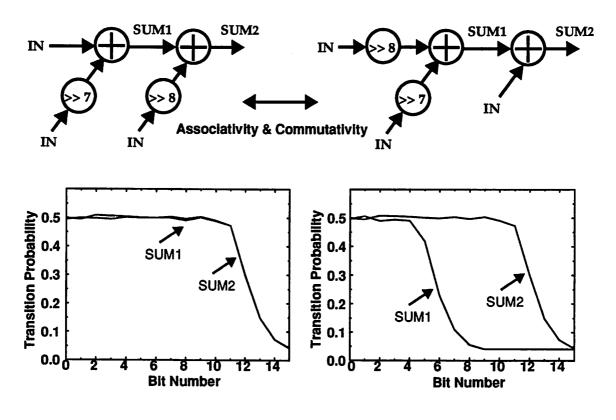

| Figure 4-22: Reducing activity by re-ordering inputs                                    | 150 |

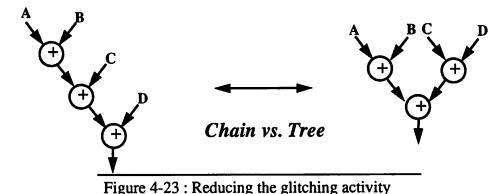

| Figure 4-23: Reducing the glitching activity                                            | 151 |

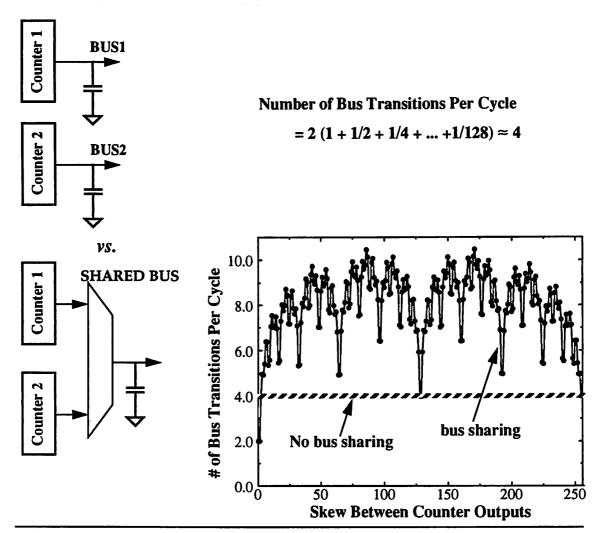

| Figure 4-24: Activity trade-off for time-multiplexed hardware: bus-sharing example      | 154 |

| Figure 4-25: Activity trade-off for time-multiplexed hardware: adder example            | 156 |

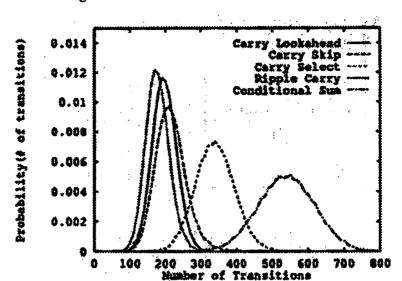

| Figure 4-26: Histogram of transition activity for various adder topologies [Callaway92] | 158 |

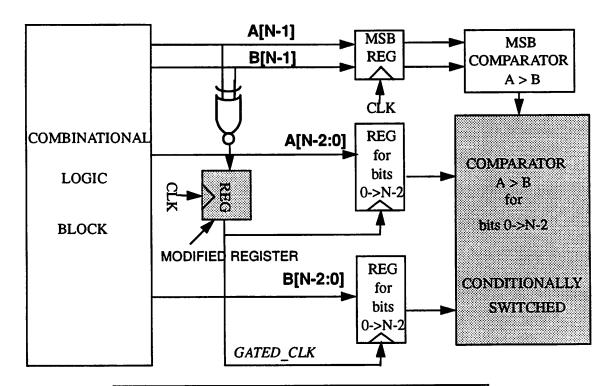

| Figure 4-27: Data dependent logic level shutdown                                        |     |

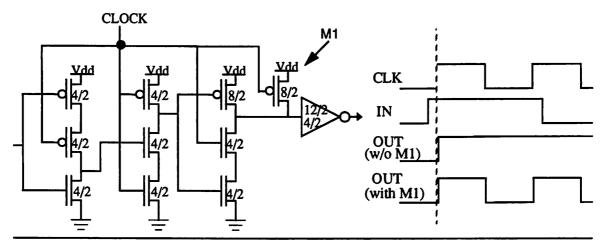

| Figure 4-28: Schematic of a modified TSPC latch that is used to generate gated clocks   | 160 |

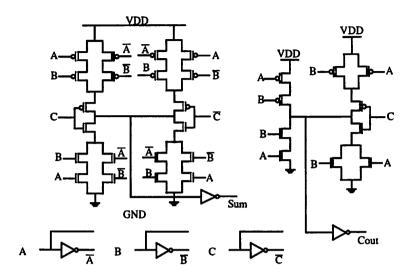

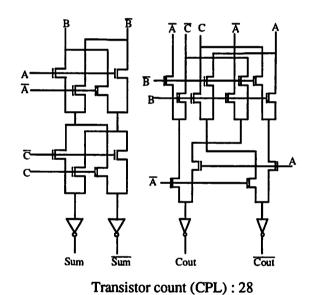

| Figure 4-29 : CMOS vs. Pass Gate Logic: adder example                                   | 164 |

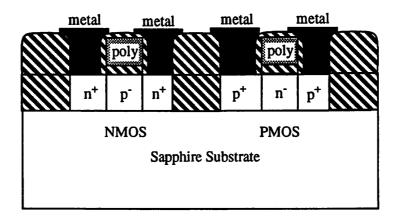

| Figure 4-30 : Silicon-on-Sapphire CMOS                                                  | 166 |

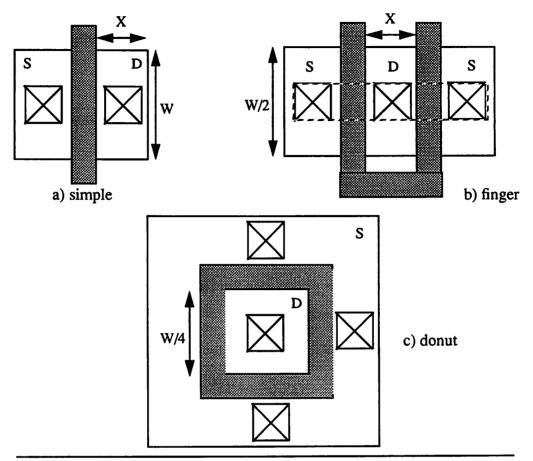

| Figure 4-31: Three layout approaches for a large W/L transistor                                | 167  |

|------------------------------------------------------------------------------------------------|------|

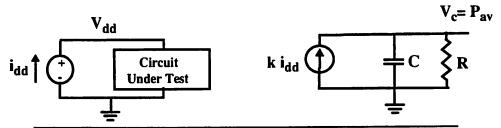

| Figure 5-1: Circuit for measuring the power-delay product                                      |      |

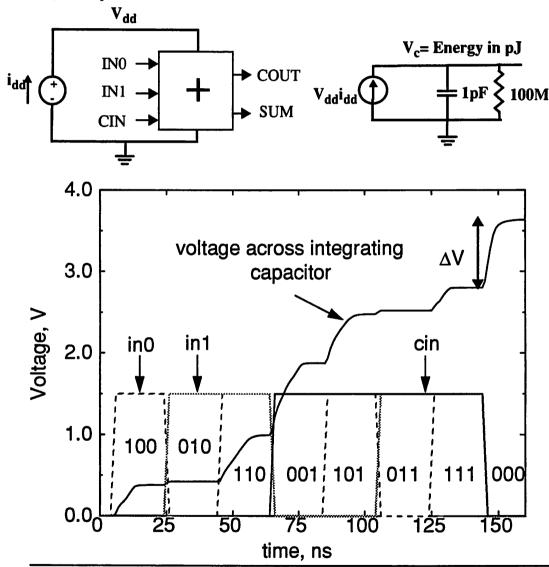

| Figure 5-2: Measuring capacitance switched for a 1-bit full-adder example                      |      |

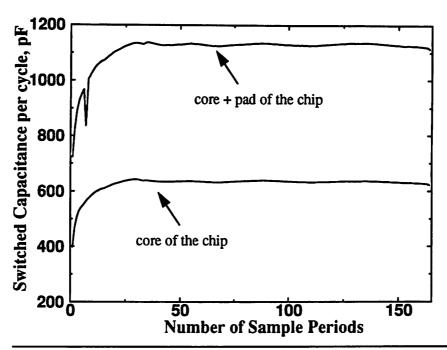

| Figure 5-3: Switched capacitance vs. number of simulated periods                               |      |

| Figure 5-4: Statistical parameter propagation [Landman93]                                      |      |

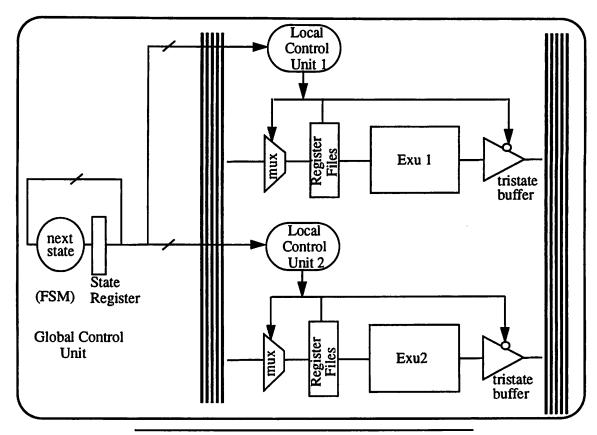

| Figure 5-5: Hardware model used in HYPER                                                       |      |

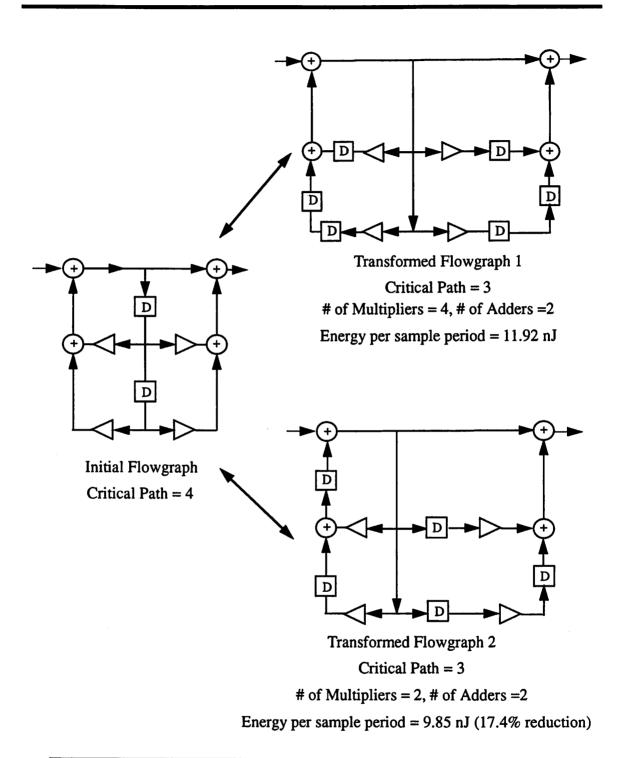

| Figure 5-6: Reducing capacitance while maintaining throughput                                  | 182  |

| Figure 5-7: Reducing capacitance at the expense of a higher supply voltage                     |      |

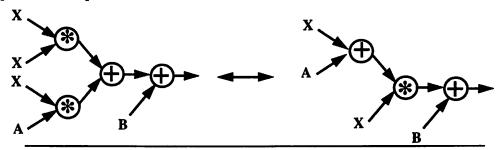

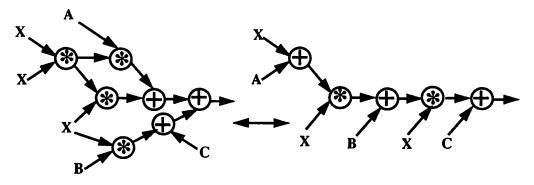

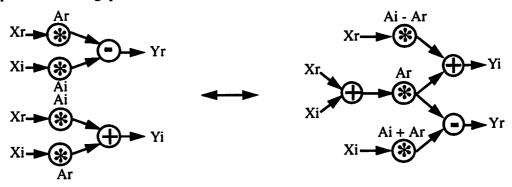

| Figure 5-8: Trading multiplication for an addition                                             |      |

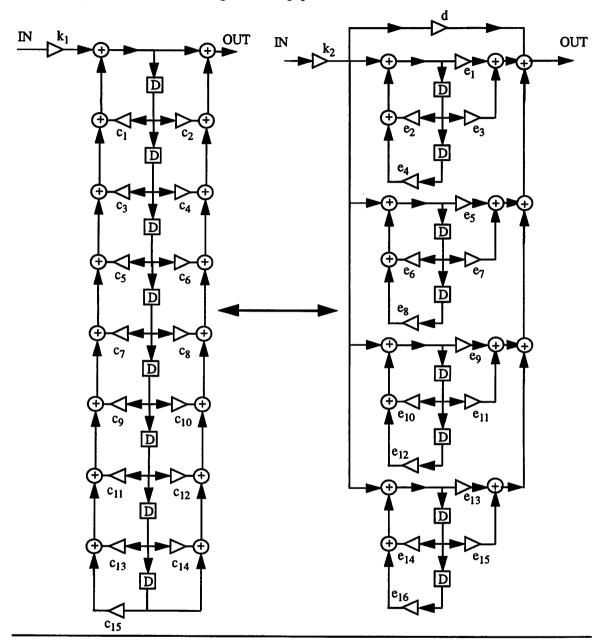

| Figure 5-9: Retiming for improving resource utilization: 2nd order IIR filter                  | 186  |

| Figure 5-10: Direct form structure vs. Parallel form structure: 8th order Avenhous filter      |      |

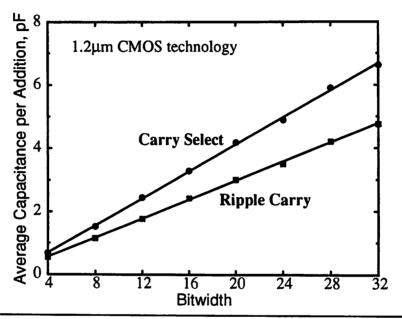

| Figure 5-11: Average capacitance per addition for two different modules                        | 191  |

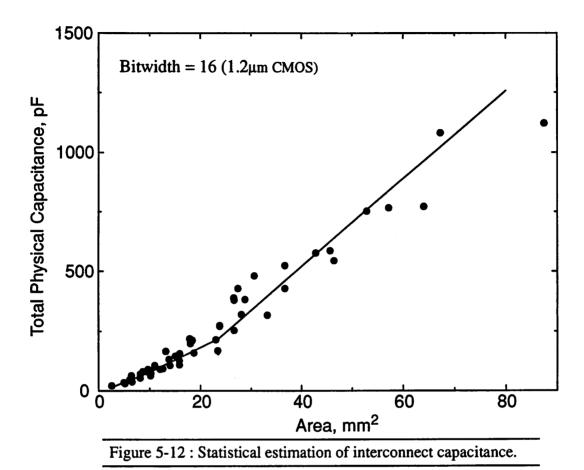

| Figure 5-12: Statistical estimation of interconnect capacitance                                | 195  |

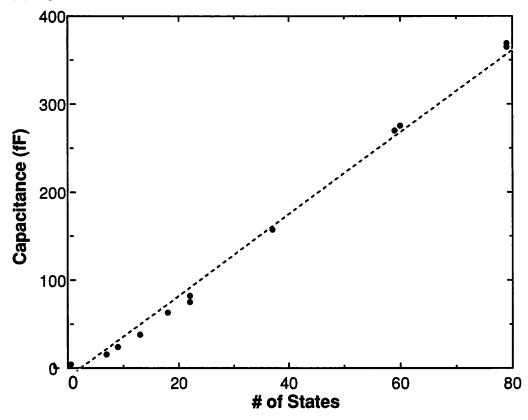

| Figure 5-13: Total capacitance switched vs. number of states for the global controller         | 197  |

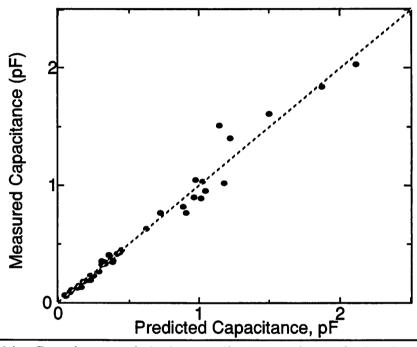

| Figure 5-14: Capacitance switched vs. predicted capacitance for local controllers              | 200  |

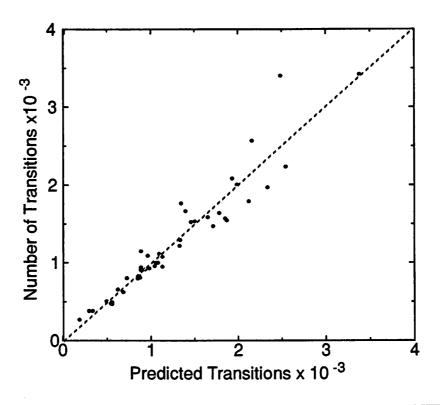

| Figure 5-15: Actual number of transitions vs. predicted transitions for local controllers      | 202  |

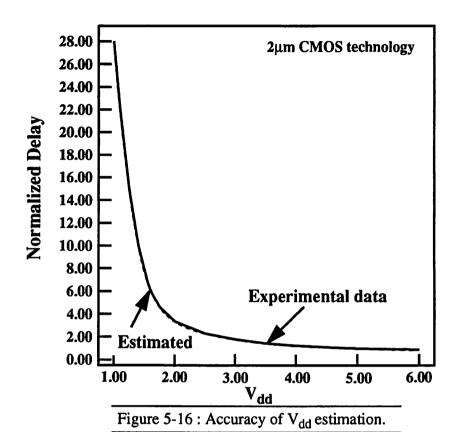

| Figure 5-16 : Accuracy of V <sub>dd</sub> estimation                                           | 204  |

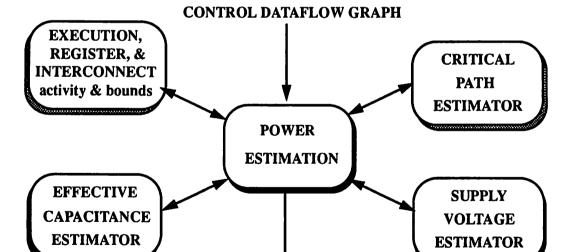

| Figure 5-17: Overview of power estimation                                                      | 204  |

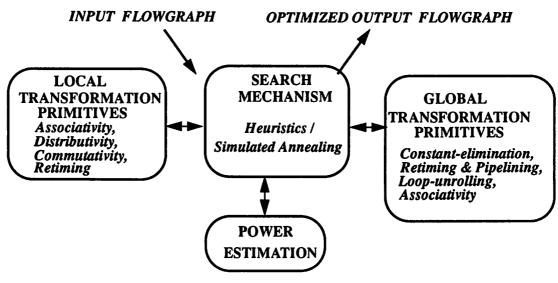

| Figure 5-18: Overview of the HYPER-LP system                                                   | 208  |

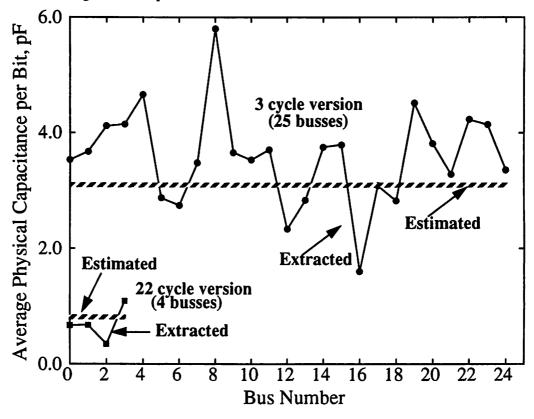

| Figure 5-19: Bus capacitance for the wavelet filter (estimated and extracted)                  | 210  |

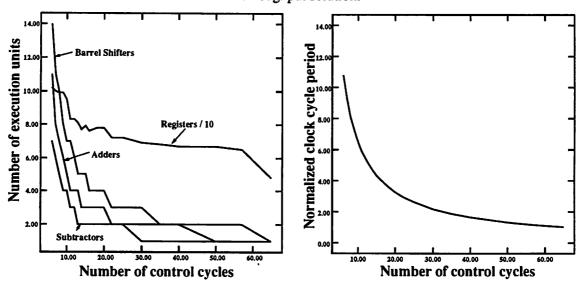

| Figure 5-20: Plot of # of units (a) and clock cycle period (b) vs. # of control cycles for the |      |

| IIR example                                                                                    | 212  |

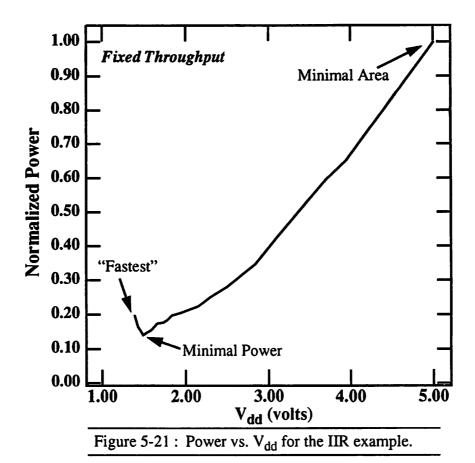

| Figure 5-21: Power vs. V <sub>dd</sub> for the IIR example                                     | 213  |

| Figure 5-22 : Optimizing the volterra filter                                                   | 214  |

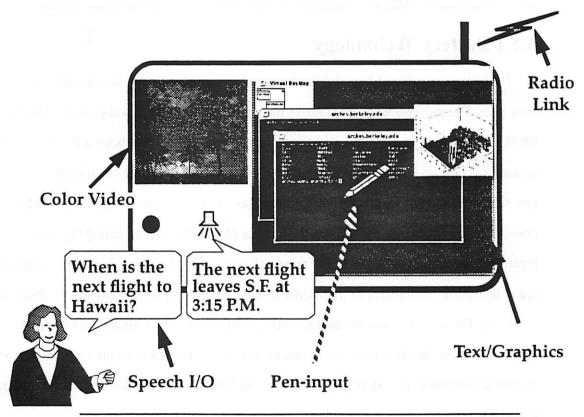

| Figure 6-1: Overview of a future personal communications system                                | 217  |

| Figure 6-2: Desired features of a Portable Multimedia Terminal                                 | 219  |

| Figure 6-3: Trends in battery technology for the last 20 years                                 | 221  |

| Figure 6-4: Low-power color TFT display (courtesy of SHARP)                                    | 222  |

| Figure 6-5: Partitioning of computation: X-server example                                      | 224  |

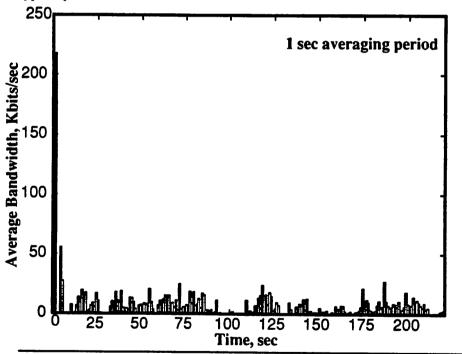

| Figure 6-6: Bandwidth requirement for a Frame-maker session                                    | 225  |

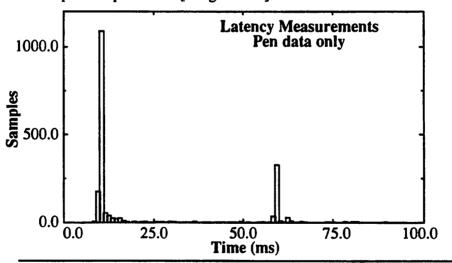

| Figure 6-7: Latency measurement for pen data [Burghardt94]                                     | 227  |

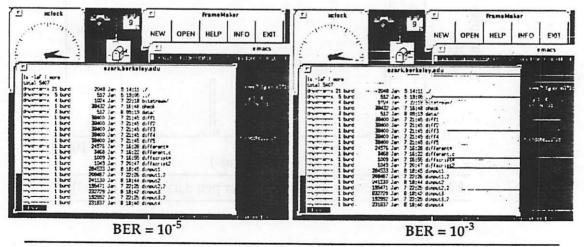

| Figure 6-8: Approach to high BER; transmit more "data" and minimal "control"                   | 228  |

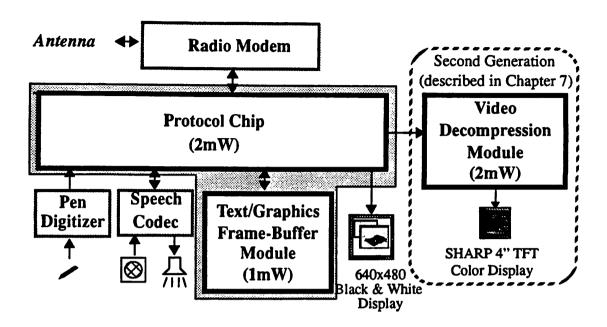

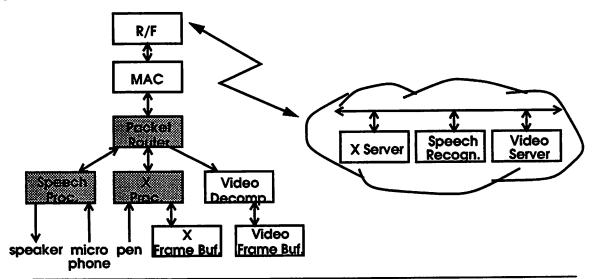

| Figure 6-9: Block Diagram of the InfoPad Terminal                                              | 230  |

| Figure 6-10: Block diagram of the protocol chip                                                | 232  |

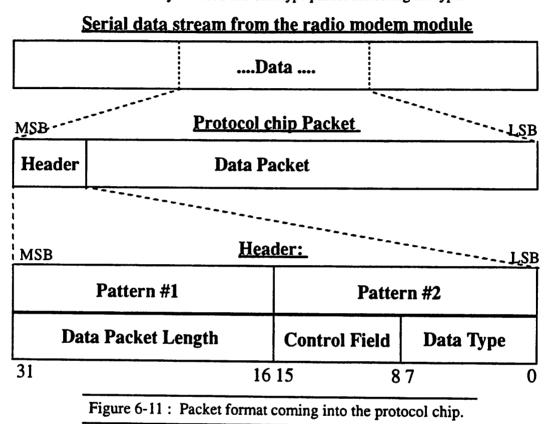

| Figure 6-11: Packet format coming into the protocol chip                                       |      |

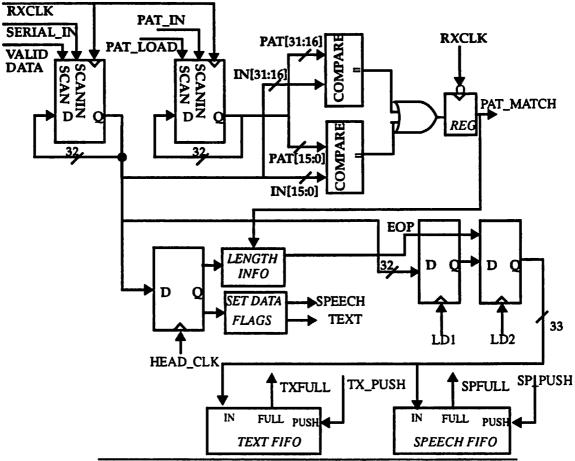

| Figure 6-12: Datapath for depacketization and demultiplexing.                                  | .235 |

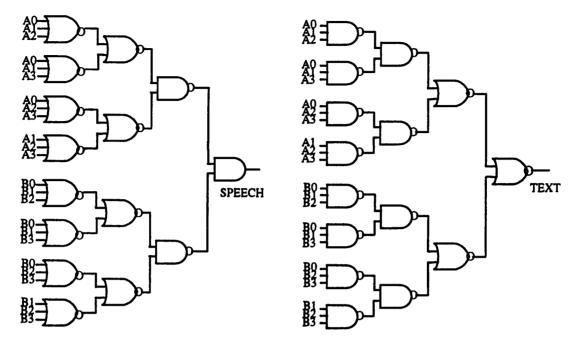

| Figure 6-13: Decoding of data types                                                            |      |

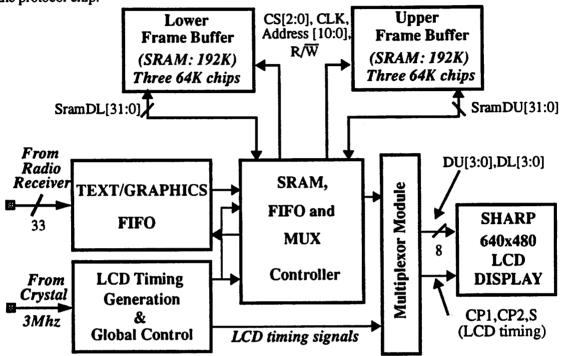

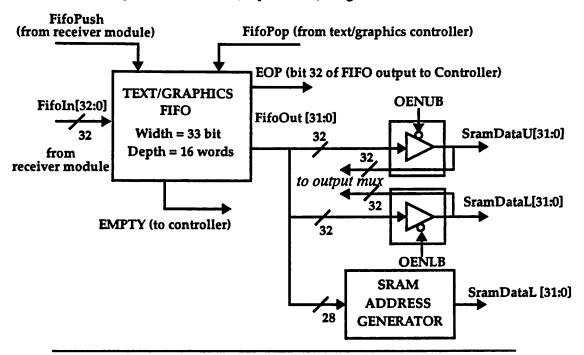

| Figure 6-14: Block diagram of the text/graphics module                                         |      |

| $\cdot$                                                                            |     |

|------------------------------------------------------------------------------------|-----|

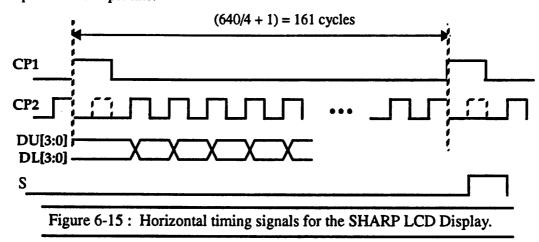

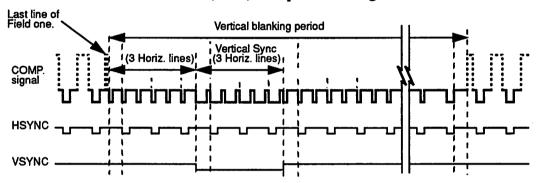

| Figure 6-15: Horizontal timing signals for the SHARP LCD Display                   | 238 |

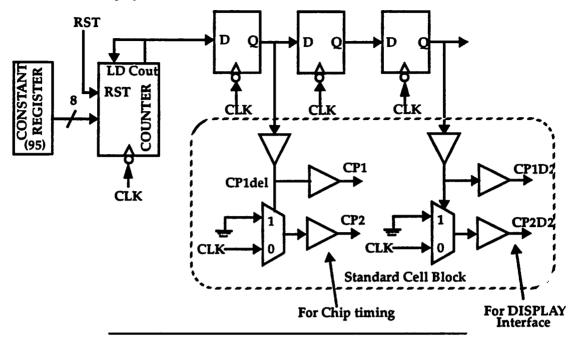

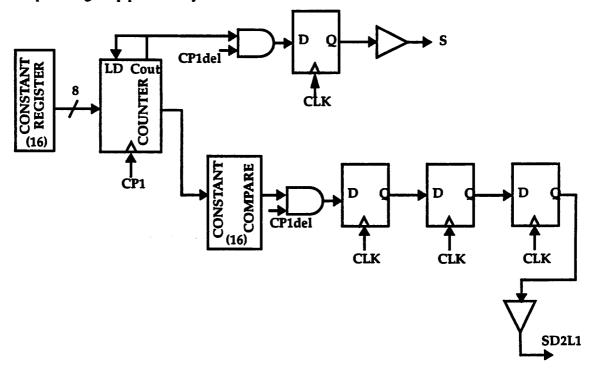

| Figure 6-16: Line synchronization clock generation                                 | 239 |

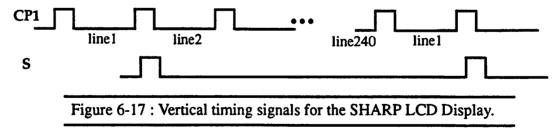

| Figure 6-17: Vertical timing signals for the SHARP LCD Display                     | 239 |

| Figure 6-18: Field synchronization clock generation                                | 240 |

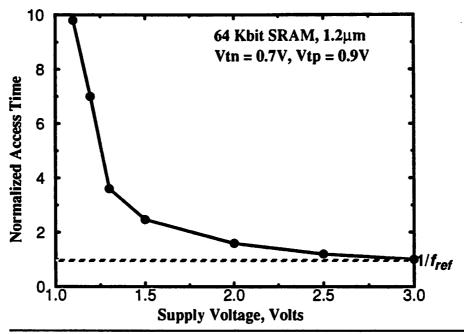

| Figure 6-19: Normalized access time vs. V <sub>dd</sub> for a 64Kbit SRAM          | 241 |

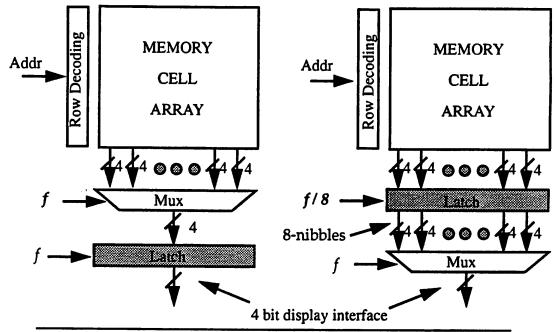

| Figure 6-20: Parallel memory access enables low-voltage operation                  | 242 |

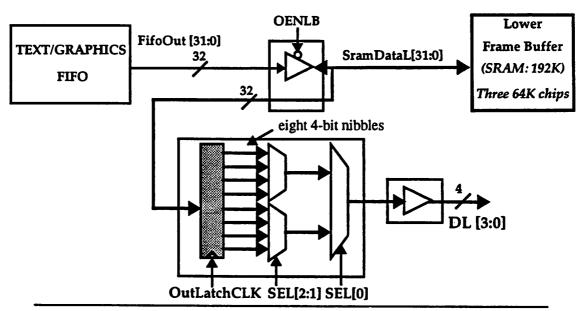

| Figure 6-21: Data and address busses for the text/graphics module                  | 244 |

| Figure 6-22 : Conversion from 32-bit frame-buffer data to 4-bit LCD data           | 245 |

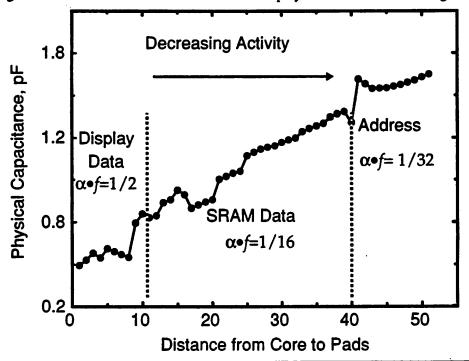

| Figure 6-23: Optimizing placement for low-power: routing large data/control busses | 246 |

| Figure 6-24 : Application specific protocol: text/graphics information             | 247 |

| Figure 6-25: Gated clocks are used to shut down modules when not used              | 248 |

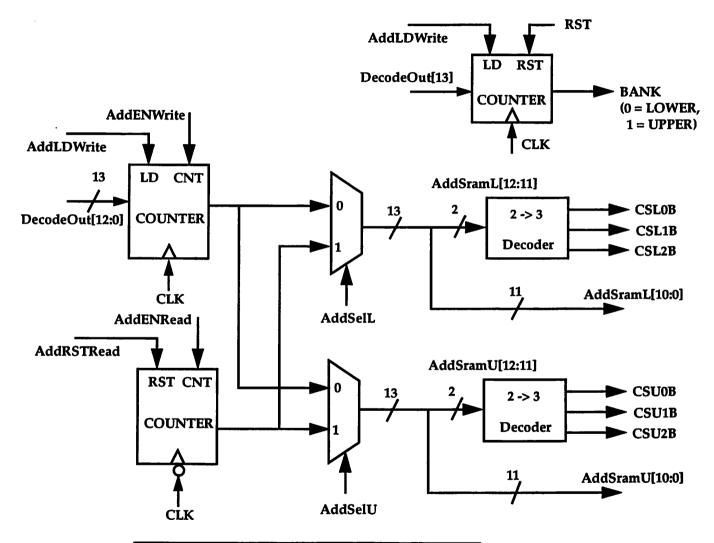

| Figure 6-26 : Address generation for the SRAM                                      | 249 |

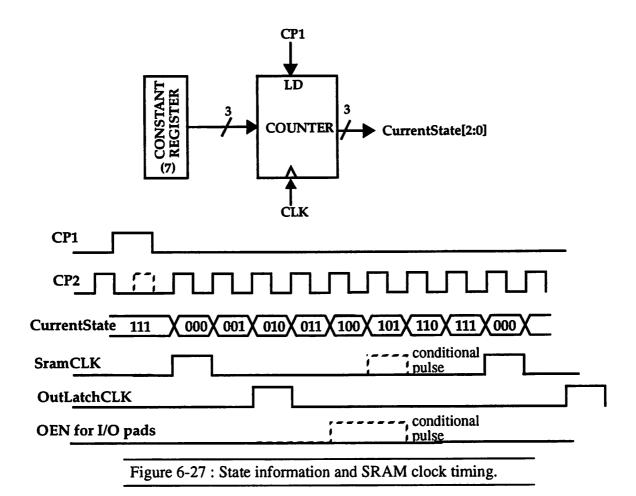

| Figure 6-27: State information and SRAM clock timing                               | 251 |

| Figure 6-28: Interface signals between the speech module and the commercial codec  | 252 |

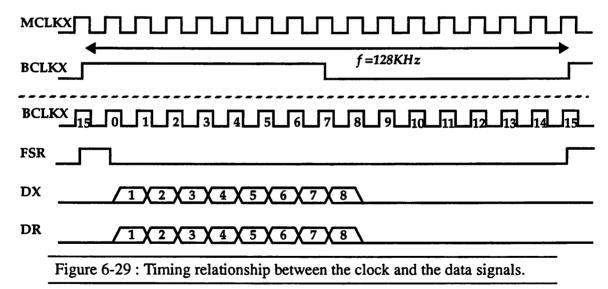

| Figure 6-29: Timing relationship between the clock and the data signals            | 252 |

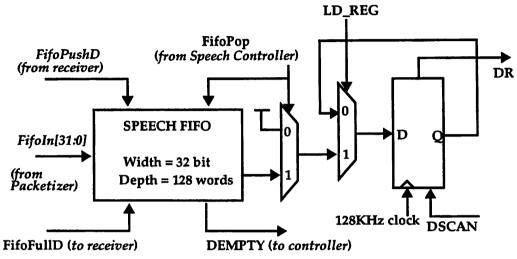

| Figure 6-30 : Speech downlink datapath                                             | 253 |

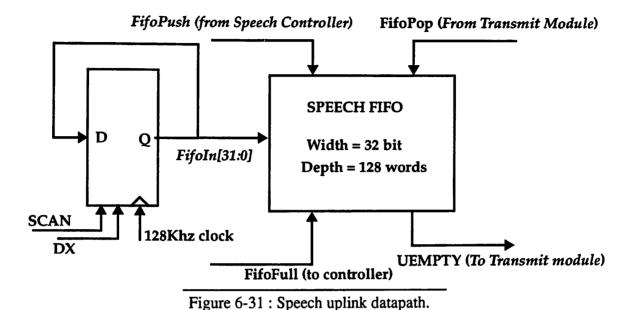

| Figure 6-31 : Speech uplink datapath                                               | 254 |

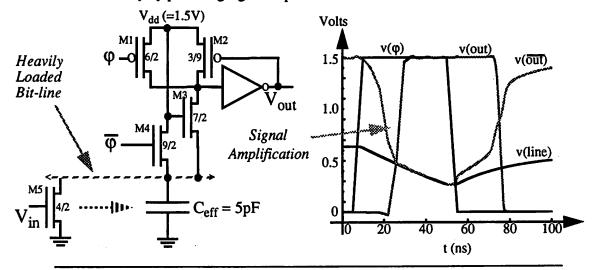

| Figure 6-32: Signal swing reduction for memory circuits: FIFO example              | 256 |

| Figure 6-33 : True single phase clock pipeline register                            | 259 |

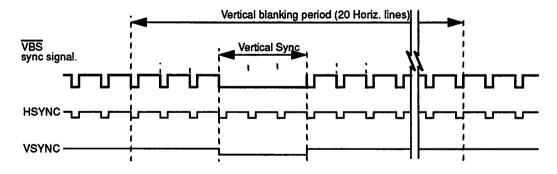

| Figure 6-34 : Die photo of the protocol chip                                       | 260 |

| Figure 6-35: Die photo of the text/graphics frame-buffer.                          | 262 |

| Figure 6-36: SRAM block organization                                               | 264 |

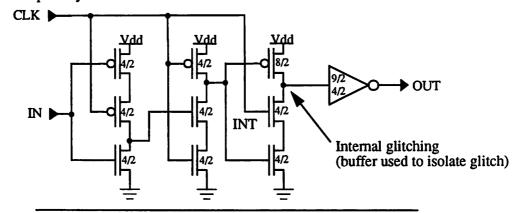

| Figure 6-37: Precharge, sense-amp and "Glitch" free tri-state buffer               | 266 |

| Figure 6-38 : Block Diagram of IPGraphics terminal                                 | 269 |

| Figure 6-39: Overview of IPGraphics (Pen, Speech I/O and Text/graphics) Terminal   | 271 |

| Figure 7-1: Video compression/decompression using vector quantization              | 275 |

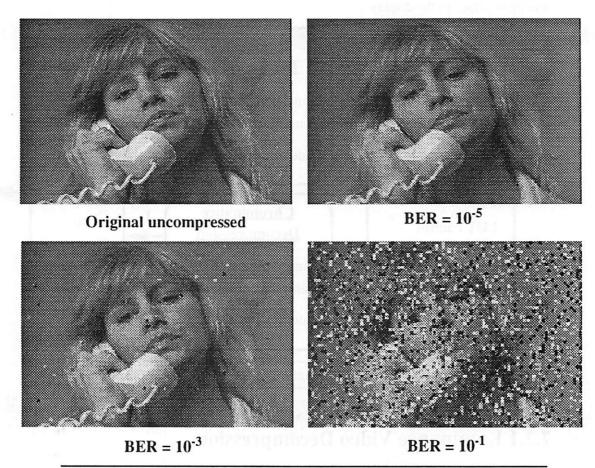

| Figure 7-2: Effect of channel errors on vector quantized images (16:1)             | 277 |

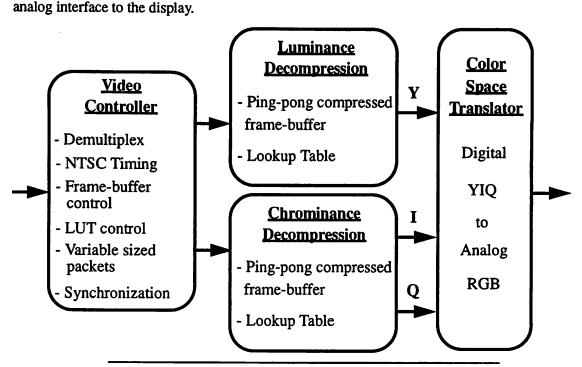

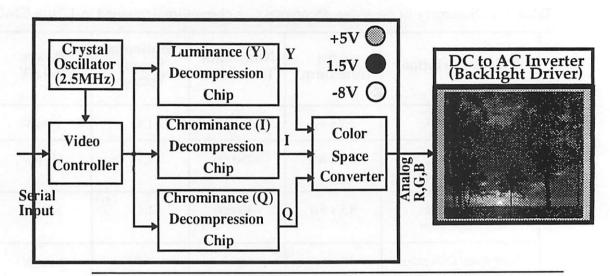

| Figure 7-3: Block diagram of the video decompression                               | 278 |

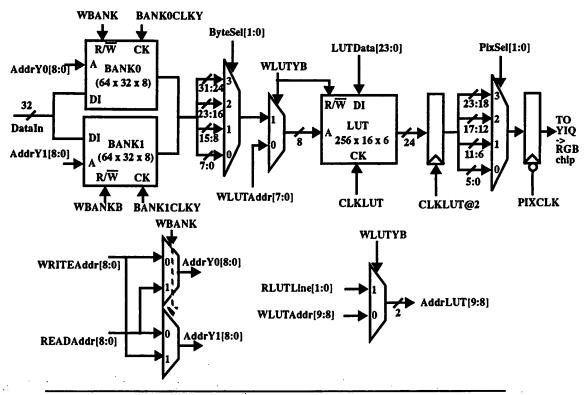

| Figure 7-4: Block diagram of the luminance decompression chip                      | 280 |

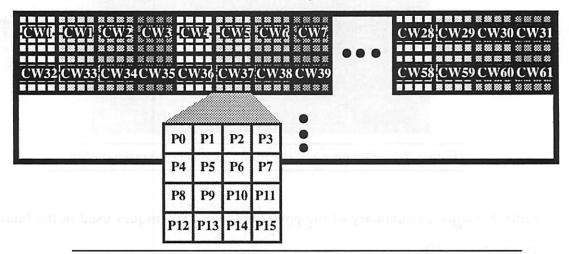

| Figure 7-5: Addressing of the frame-buffers and lookup table                       |     |

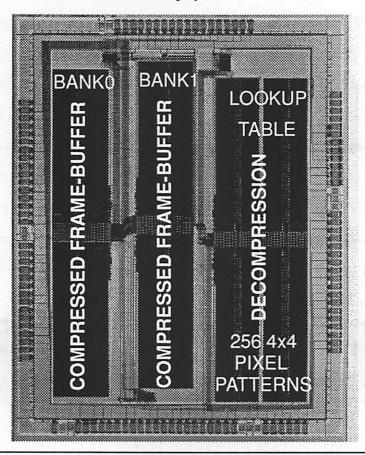

| Figure 7-6: Die photo of the luminance decompression chip                          |     |

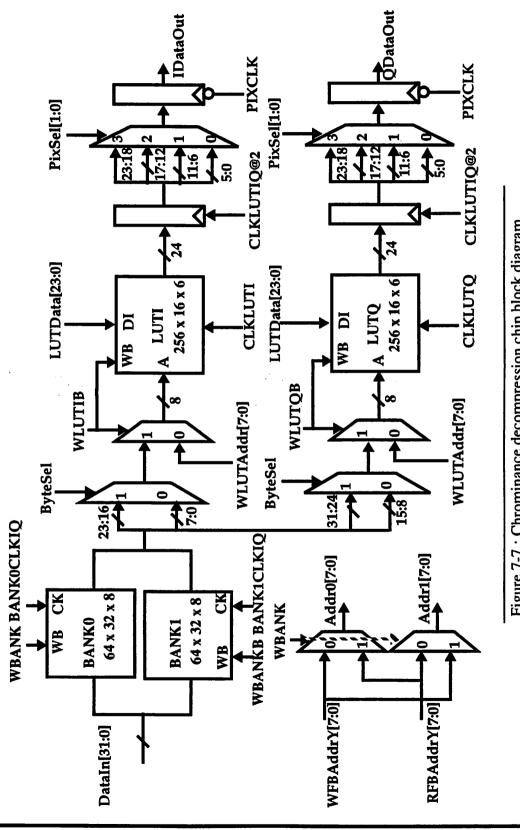

| Figure 7-7: Chrominance decompression chip block diagram                           |     |

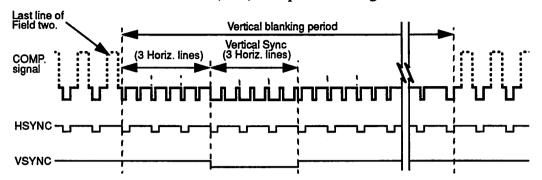

| Figure 7-8: Simplification of the NTSC system timing                               |     |

| Figure 7-9: Protocol for the lookup table and Frame-buffer FIFOs                   |     |

| Figure 7-10: Die photograph of the video controller chip                           |     |

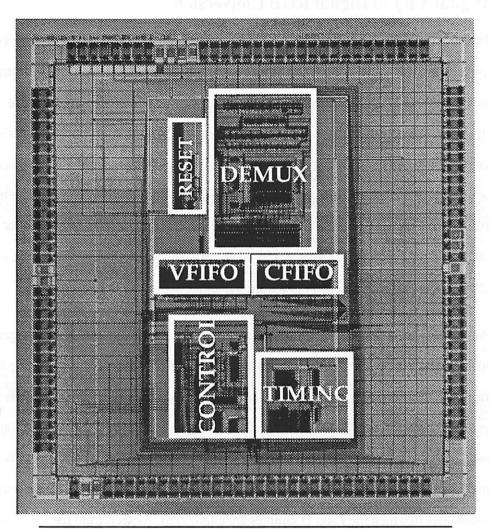

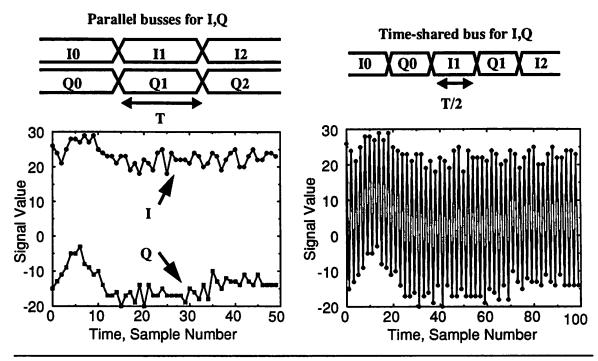

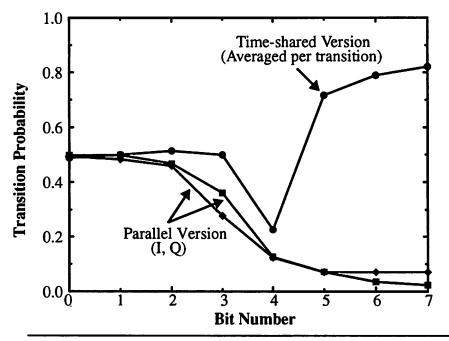

| Figure 7-11: Time-multiplexing can destroy signal correlation increasing activity  |     |

| Figure 7-12: Transition activity for time-multiplexing activity                    |     |

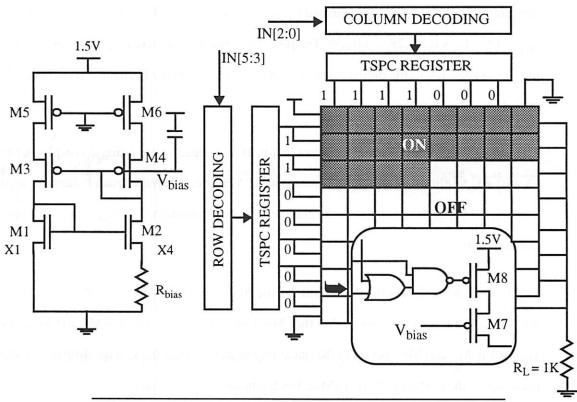

| Figure 7-13: Low-voltage 6-bit Digital to Analog converter                         | 293 |

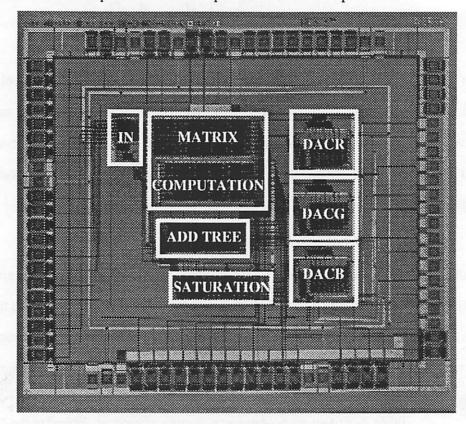

| Figure 7-14: Die photo of the color space converter and digital to analog converter  | 296 |

|--------------------------------------------------------------------------------------|-----|

| Figure 7-15: Block diagram of the video decompression test board                     | 298 |

| Figure 7-16: Output of video decompression chips running at a supply voltage of 1.3V | 298 |

| Figure 8-1: Energy efficient programmable computation required in portables          | 300 |

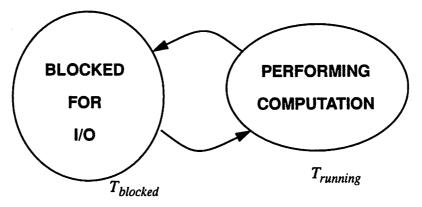

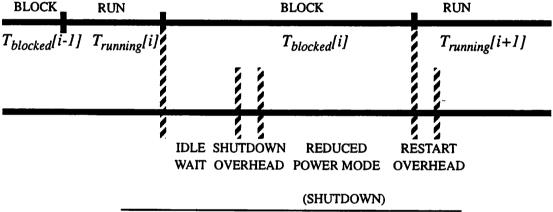

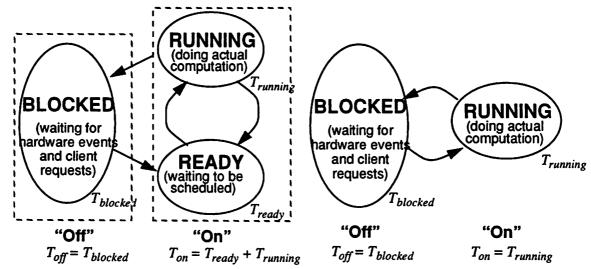

| Figure 8-2: Event-driven applications alternate between blocked and running states   |     |

| Figure 8-3: Conventional shutdown approaches                                         |     |

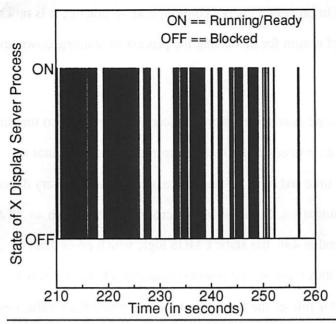

| Figure 8-4: States of X Display Server Process                                       |     |

| Figure 8-5: Sample trace of X server state under UNIX                                | 311 |

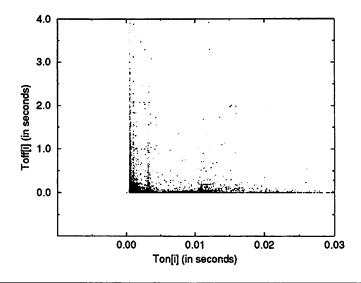

| Figure 8-6: L-shaped T <sub>off</sub> [i] versus T <sub>on</sub> [i] Scatter Plot    | 315 |

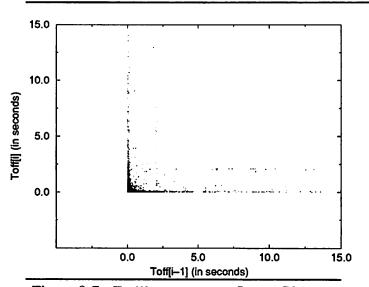

| Figure 8-7: T <sub>off</sub> [i] versus T <sub>off</sub> [i-1] Scatter Plot          | 315 |

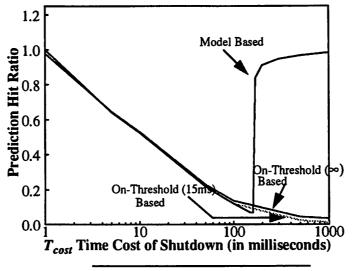

| Figure 8-8: Hit ratio curves                                                         |     |

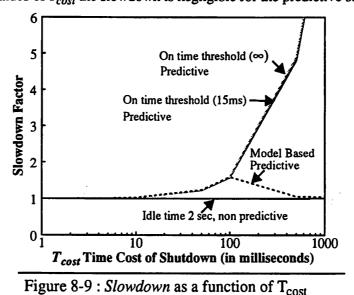

| Figure 8-9: Slowdown as a function of T <sub>cost</sub>                              | 318 |

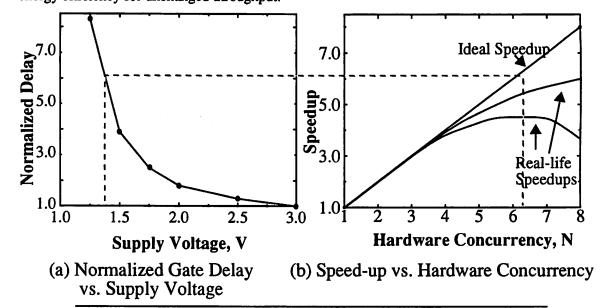

| Figure 8-10: Trade-off between voltage and hardware-concurrency                      | 320 |

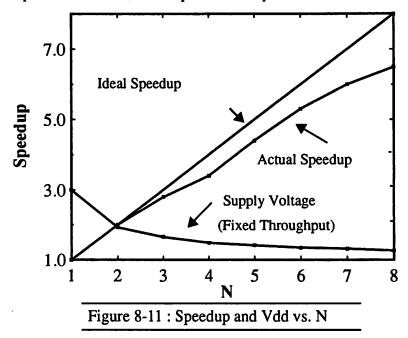

| Figure 8-11: Speedup and V <sub>dd</sub> vs. N                                       | 329 |

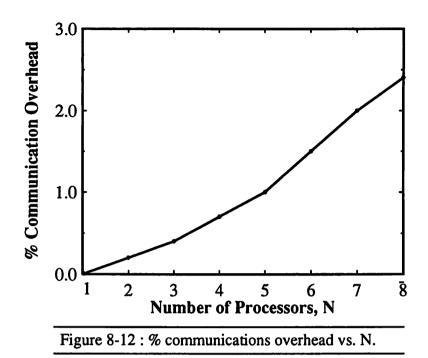

| Figure 8-12: % communications overhead vs. N.                                        | 330 |

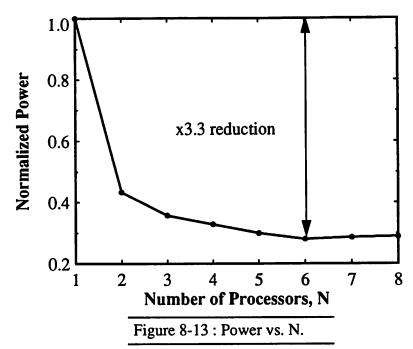

| Figure 8-13 : Power vs. N                                                            |     |

| Figure 11-1: Retiming for power minimization.                                        |     |

## LIST OF TABLES

| Table 2-1:  | Area and perimeter capacitances for a 1.2mm CMOS technology                           | 27   |

|-------------|---------------------------------------------------------------------------------------|------|

| Table 2-2:  | Area and perimeter capacitances for Metal 1 wire of length $100\lambda$ by $3\lambda$ |      |

|             | for two different feature sizes.                                                      | 28   |

| Table 2-3:  | Capacitance breakdown at the module level                                             | 29   |

| Table 2-4:  | Capacitance breakdown at the datapath level                                           | 29   |

| Table 2-5:  | Truth Table of 2 input NOR gate                                                       | 30   |

| Table 2-6:  | Truth Table of 2 input XOR gate                                                       | 31   |

| Table 2-7:  | Activity comparison of different logic styles                                         | 35   |

| Table 2-8 : | Output transition probabilities for various static logic gates                        | 36   |

| Table 2-9:  | Probabilities for tree and chain topologies                                           | 42   |

| Table 2-10: | Details of components used for the study in Figure 2-26                               | 50   |

| Table 2-11: | Description of circuits used for study in Figure 2-27.                                | 51   |

| Table 3-1:  | Results of architecture based voltage scaling                                         | 97   |

| Table 3-2:  | Normalized Area/Power for various supply voltages for Plots 2,3 in                    |      |

|             | Figure 3-21                                                                           | 98   |

| Table 4-1:  | Computational complexity of VQ encoding algorithms                                    | .126 |

| Table 4-2:  | Binary and Gray-code representation.                                                  | .133 |

| Table 4-3:  | Number representation trade-off for arithmetic                                        | 148  |

| Table 4-4:  | Average number of gate transitions per addition [Callaway92]                          | 157  |

| Table 4-5 : | The influence of layout optimization on physical capacitance                          |      |

| Table 5-1:  | Breakdown of power consumed for a 11 tap FIR filter before                            |      |

|             | constant multiplications.                                                             | 184  |

| Table 5-2:  | Breakdown of power consumed for a 11 tap FIR filter after                             |      |

|             | constant multiplications.                                                             | 184  |

| Table 5-3:  | Capacitance models for some of the library hardware units                             |      |

|             | for a 1.2µm CMOS technology                                                           | 190  |

| Table 5-4:  | Results from various local controller units of the selected sample set                | 198  |

| Table 5-5:  | Results for the Wavelet Chip (1.2µm CMOS technology)                                  | 211  |

| Table 5-6:  | Summary of results.                                                                   | 214  |

| Table 6-1:  | Bandwidth requirement for various data types.                                         |      |

| Table 6-2:  |                                                                                       |      |

| Table 6-3:  | Summary of power reduction techniques applied to the protocol chip                    |      |

| Table 6-4:  | Statistics for the text/graphics frame-buffer chip              | 267 |

|-------------|-----------------------------------------------------------------|-----|

| Table 6-5 : | Summary of power reduction techniques applied to the            |     |

|             | frame-buffer chip                                               | 268 |

| Table 7-1 : | Computational complexity of the Discrete Cosine Transform       | 274 |

| Table 7-2 : | Asymmetrical algorithm required for low-power implementation    | 276 |

| Table 7-3 : | Summary of power reduction techniques applied to the luminance  |     |

|             | decompression chip                                              | 282 |

| Table 7-4:  | Summary of power reduction techniques applied to the YIQ -> RGB |     |

|             | conversion                                                      | 292 |

| Table 7-5:  | Summary of power reduction techniques applied to the DAC        | 295 |

| Table 7-6:  | Summary of the video decompression chipset implemented in       |     |

|             | 1.2μm CMOS                                                      | 297 |

| Table 8-1:  | •                                                               | 311 |

| Table 8-2:  | Summary of Energy Reduction                                     | 319 |

|             |                                                                 |     |

#### **A**CKNOWLEDGMENTS

My advisor, Bob Brodersen, provided great guidance during all phases of my project and was the most important person in making this project a success. He defined the low-power research area and spent a lot time helping me define my project. I was spoiled with incredible computational resources, research facilities and support staff which made research a lot more fun. I am very grateful for the exposure he provided and he always encouraged me to look beyond my project to get the "big picture". I am also grateful for his encouragement to publish and I really appreciate all his support. Of course, he did not succeed in getting me to lose weight!

Many students, faculty members and staff made significant technical contributions to this thesis. I would like to thank Prof. David Brillinger and Prof. John Wawrzynek for being on my thesis committee and providing invaluable feedback. I would also like to thank Prof. Larry Rowe for being on my qualifying committee and providing many very useful suggestions.

Phil Schrupp, Susan Mellers, and Ken Lutz setup and supported the infrastructure for designing and testing boards. Brian Richards was always around to answer questions about Lager and provided valuable suggestions concerning the design of the InfoPad chipset. I would like to thank Tom Boot, Peggy Brown, Carole Frank, Elise Mills, and Corey Schaffer for helping me with administrative issues. Heather Brown was also always very helpful with administrative matters. I would like to thank Kevin Zimmerman for doing a wonderful job supporting the computer system.

My venture into the CAD world would not have been possible without the help of Miodrag Potkonjak (Mr. Transformations) and Prof. Jan Rabaey. I appreciate all the invaluable feedback from Prof. Jan Rabaey on low-power design methodologies. I would like to thank Sean Huang for coding the local transforms used in the HYPER-LP system (Chapter 5), Paul Landman for providing software to generate data with different statistics, Renu Mehra for generating the various controllers and building the controller model, and the rest of the HYPER team for software support. The CAD tool, HYPER-LP, was started as a EE244 course project (CAD for IC's) and I

appreciate all the inputs from Dr. Lou Scheffer who was teaching the course. I especially thank Ingrid Verbauwhede for overall feedback on the project and I appreciate all the times she sat through my practice talks for conferences.

The design and demonstration of the InfoPad chipset and terminal would not have been possible without the help of several people. The first generation radio and protocol group consisting of Bill Barringer, Kathy Lu, Trevor Pering, and Tom Truman was responsible for designing the radio module that interfaced with the chipset described in Chapters 6 and 7. Tom Burd (who designed the radio receiver module), Andy Burstein (who designed the SRAM), and Shankar Narayanaswamy (responsible for the pen interface) contributed to the design of the chipset. Tom Burd spent several sleepless nights in Cory debugging the first generation IPGraphics terminal (not just because he had to, but because he has no life! - seriously, thanks Tom). I want to thank the students (especially Tom Burd and Andy Burstein) who developed the low-power cell-library and provided the infrastructure to design the chipset for the InfoPad terminal. Roger Doering and Chuck Smith were responsible for the packaging aspects of the InfoPad. Fred Burghardt, Brian Richards, and Shankar Narayanaswamy designed the basestation software and applications. It was just amazing how so many different pieces fit together in a short period of time before the InfoPad demo in October 1993.

For the video chipset, Ian O'Donnell prototyped the logic to verify the modified NTSC timing suggested by Ken Nishimura (the NTSC God) on a Xilinx. Ian was also an incredible help during the testing phase of the video chips - with all the skills he has picked up, he is going to be a permanent resident of Cory! I also want to thank Cormac Conroy and Robert Neff for their valuable suggestions on the DAC design. I also want to thank Dr. Tom Lookabaugh and Prof. Eve Riskin for providing me source code for VQ which I used as a base for the InfoPad video.

I want to thank Mani Srivastava for all the great technical discussions. He always has great solutions to every and any technical problem. I really enjoyed working with him on energy efficient programmable computation (Chapter 8). He was responsible for the modifications to the X-server and the analysis of the shutdown approaches.

I would like to thank my "other" family in 550 Cory Hall who made my life more enjoyable. My cubicle mates (old and new) included Kevin Kornegay who made sure that I was eating enough so

he can call me Fats, Mani Srivastava and Jane Sun who always entertained me with "lively" discussions, Ian O'Donnell who is responsible for the best arch ever built in 550I using straws leftover from lunch meetings (he works on this when he is not breaking monitors), Kevin Stone (along with Lapoe Lynn) broke my ribs during a once in a life-time game of soccer, and Shankar Narayanaswamy who showed me the dangers of typing too much.

The other students residents of 550 who made my life more enjoyable included Andy Burstein who sits on big rubber ball; Tom Burd who stole money from me on 49er bets; Craig Teuscher, David Lidsky and Anthony Stratakos who played 2 on 2 tackle football with me in 550 cory; Monte Mar the "chip hacker" who had answers to all chip problems; Scarlett Wu who always had food on her desk; Alfred K. Yeung the other major food supplier; Sam "Tools" Sheng considered as God by many - I would like to thank him for his contributions on the low-power design methodology development and for providing me with the correlator example; Lisa Guerra who gave me those precious 14-day parking permits and who was always fun to talk with; Sekhar Narayanaswami who helped me practice my Tamil; Rajiv Murgai who was always around in the middle of the night to talk to; Renu Mehra who has collected leftover chips from group meetings for several years and has a big stock in her lower drawer; Arthur Abnous who hates being called Archer, Winston Sun who taught me that the answer to all problems is 10 and has always been a great friend; My Le who is always bothering me when she is not vacationing in London; Charmine Tung who introduced me to the Latte and was always there when I was bored or depressed; Weiling Chu who is always very supportive; Randy "Scumbag" Allmon who hated going to the Korean restaurant with me and always ended up choosing where we ate; Greg Uehara who brings us chocolates from Hawaii every time he visits; and Cormac Conroy who was very supportive and always fun to talk with.

I would also like to thank IBM for providing me with a fellowship for the academic year 1993-1994. I would also lile to thank ARPA who funded this project.

Finally, I would like to acknowledge my family members. This thesis could not have been possible without the continued support of my parents. I am very grateful for their constant encouragement for me to strive for my best. They have been the greatest source of inspiration to me. I would like to thank Mrs. Charlotte Coe who provide great emotional and financial support

throughout my college years. She is a great inspiration to me. My wife Karthiyayani was very patient and accommodating to my weird schedules, especially during chip deadlines when we spent "quality" time from 2-3A.M! I would also like to thank my brother Nagarajan and sister-in-law Suchitra for their continued support.

#### **CHAPTER 1**

## Introduction

With much of research efforts of the past ten years directed toward increasing the speed of digital systems, present-day technologies possess computing capabilities which make possible powerful personal workstations, sophisticated computer graphics, and multi-media capabilities such as real-time speech recognition and real-time video. High-speed computation has thus become the expected norm from the average user, instead of being the province of the few with access to a powerful mainframe. Likewise, another significant change in the attitude of users is the desire to have access to this computation at any location, without the need to be physically tethered to a wired network. A major factor in the weight and size of portable devices is the amount of batteries which is directly impacted by the power dissipated by the electronic circuits.

Even when power is available in non-portable applications, the issue of low power design is becoming critical. Up until now, this power consumption has not been of great concern, since large packages, cooling fins and fans have been capable of dissipating the generated heat. However, as the density and size of the chips and systems continues to increase, the difficulty in providing adequate cooling might either add significant cost to the system or provide a limit on the amount of

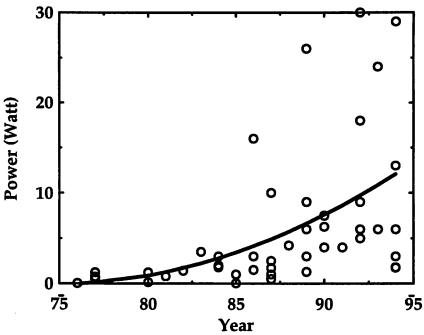

functionality that can be provided. Figure 1-1 shows a plot of the power consumption for various micro-processors that have been reported at the International Solid-state Circuits Conference (ISSCC) for the last 20 years. The obsession of increasing the clock rate has resulted in single chip power levels in excess of 30W.

Figure 1-1: Power consumption of micro-processors reported at ISSCC over the last 20 years [Rabaey94].

In addition to heat removal, there are also economic/environmental incentives for low-power general purpose computation. Studies have shown that personal computers in U.S.A waste \$2 billion dollars of electricity, indirectly produce as much CO<sub>2</sub> as 5 million cars, and account for 5% of commercial electricity consumption (10% by the year 2000) [Nadel93]. These compelling economic and environmental reasons alone have resulted in the concept of "green computers".

Although the traditional mainstay of portable digital applications has been in low-power, low-throughput uses such as wristwatches and pocket calculators, there are an ever-increasing number of portable applications requiring low-power and high-throughput. For example, notebook and laptop computers, representing the fastest growing segment of the computer industry, are

demanding the same computation capabilities as found in desktop machines. Equally demanding are developments in personal communications services (PCS), such as the current generation of digital cellular telephony networks which employ complex speech compression algorithms and sophisticated radio modems in a pocket sized device. Even more dramatic are the proposed PCS applications, with universal, portable multimedia access supporting full-motion digital video and control via speech recognition. In these applications, not only will voice be transmitted via wireless links, but data and video as well. Indeed, it is apparent that portability can no longer be associated with low-throughput; instead, vastly increased capabilities, actually in excess of that demanded of fixed workstations, must be placed in a low-power, portable environment.

In spite of these concerns, until recently, there has not been a major focus on a design methodology of digital circuits which directly addresses power reduction, with the focus rather on ever faster clock rates and logic speeds. The approach which will be presented here, takes another viewpoint, in which all possible aspects of a system design are investigated with the goal of reducing the power consumption. These considerations range from the technology being used for the implementation, the circuit and logic topologies, the digital architectures and even the algorithms being implemented. What is assumed is that the application, which is desired to be implemented with low power is known, and trade-offs can be made as long as the functionality required of this application is met within a given time constraint.

Maintaining a given level of computation or throughput is a common concept in signal processing and other dedicated applications, in which there is no advantage in performing the computation faster than some given rate, since the processor will simply have to wait until further processing is required. This is in contrast to general purpose computing, where the goal is often to provide the fastest possible computation without bound. One of the most important ramifications of only maintaining throughput is that it enables an architecture driven voltage scaling strategy, in which aggressive voltage reduction is used to reduce power, and the resulting reduction in logic speed is compensated through parallel architectures to maintain throughput. However, the techniques

presented are also applicable to the general purpose environment, if the figure of merit is the amount of processing per unit of power dissipation (e.g. MIPS/Watt). Since in this case the efficiency in implementing the computation is considered and voltage scaling decreases the energy expended per evaluation.

The optimization to minimize area, has only been secondary to the fixation on increasing circuit speed and again this should be examined with respect to its effect on power consumption. Some of the techniques that will be presented will come at the expense of increased silicon area and thus the cost of the implementation will be increased. The desirability of this trade-off can only be determined with respect to a given market situation, but in many cases a moderate increase in area can have substantial impact on the power requirements. It is clear that if power reduction is more important than increasing circuit clock rate, that the area consumed by large clock buffers, power distribution busses and predictive circuit architectures would be better spent to reduce the power dissipation.

#### 1.1 Overview of Thesis

#### 1.1.1 Low-power Design Methodologies [Chapters 2,3, and 4]

Chapter 2 reviews the sources of power consumption in CMOS circuits. Four components of power consumption will be described: switching power, short-circuit power, leakage power and static power. For a properly designed CMOS circuit, it is usually the switching component of power which dominates, contributing to more than 90% of the total power. The concept of switching activity (the number of capacitive transitions per clock cycle) will be introduced and the various factors affecting switching activity will be described. The effect of voltage scaling on the circuit performance will be described. This chapter will provide the fundamentals of power consumption in CMOS circuits and will provide the background to understand the various power minimization techniques presented in Chapters 3 and 4.

#### **Approaches to Power Supply Voltage Scaling**

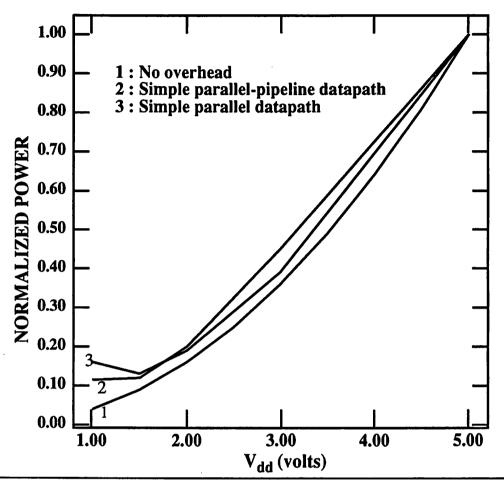

It is evident that methodologies for the design of high-throughput, low-power digital systems are needed. Since power is proportional to the square of the supply voltage, it is clear that lowering the power supply voltage,  $V_{dd}$ , is the key to power reduction. Lowering  $V_{dd}$  however comes at the cost of increased circuit delays and therefore lower functional throughput. Chapter 3 will present various approaches to scaling the power supply voltage without loss in throughput.

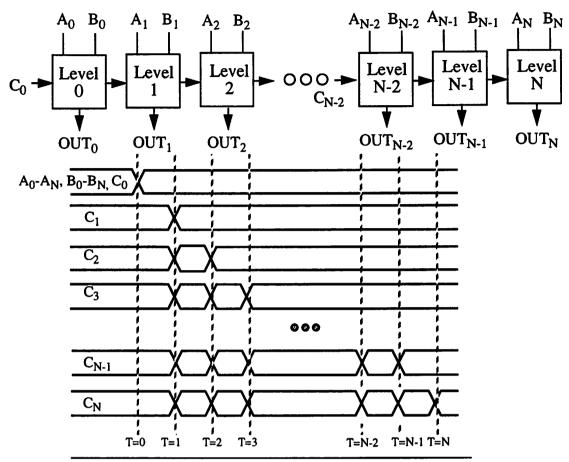

Fortunately, there are clear technological trends that give us a new degree of freedom, so that it is possible to satisfy contradictory requirements of low-power and high throughput. Scaling of device feature sizes, along with the development of high density, low-parasitic packaging, such as multi-chip modules, will alleviate the overriding concern with the numbers of transistors being used. When MOS technology has scaled to 0.2µm minimum feature size it will be possible to place from 1-10x10<sup>9</sup> transistors in an area of 8" by 10" if a high-density packaging technology is used. The question then becomes how can this increased capability be used to meet a goal of low power operation. Previous analyses on the question of how to best utilize increased transistor density at the chip level, concluded that for high-performance microprocessors the best use is to provide increasing amounts of on-chip memory [Patterson80]. It will be shown here that for computationally intensive functions that the best use is to provide additional circuitry to parallelize the computation - our architecture driven voltage scaling strategy.

Another important consideration, particularly in portable applications, is that many computation tasks are likely to be real-time; the radio modem, speech and video compression, and speech recognition all require computation that is always at near-peak rates. Conventional schemes for conserving power in laptops, which are generally based on power-down schemes, are not appropriate for these continually active computations. On the other hand, there is a degree of freedom in design that is available in implementing these functions, in that once the real-time requirements of these applications are met, there is no advantage in increasing the computational

throughput. This fact, along with the availability of increasing numbers of transistors in scaled technology, allows a strategy to be developed for architecture design, which if it can be followed, will be shown to provide significant power savings.

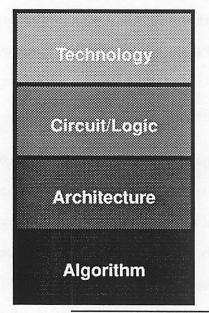

Figure 1-2 shows an overview of various approaches to power supply voltage scaling which range from optimizing the technology and circuits used to the architectures and algorithms. The various techniques currently used to scale the supply voltage will be reviewed which include optimizing the technology and the device reliability. These techniques dictate a limited amount of voltage scaling, typically going from 5V down to 3V. Our architecture driven voltage scaling strategy will be presented which trades area for lower power and allows for voltage scaling down to 1V without loss in system performance. Combining architecture optimization with threshold voltage reduction can result in scaling of the supply voltage to the sub-1V range. The key to architecture driven voltage scaling is the exploitation of concurrency. For this, algorithmic transformations will be used. Chapter 3 will also describe the various support circuitry required for low voltage operation, which includes high-efficiency DC/DC converters and level converting.

Feature Size Scaling, LDD Structures Threshold Voltage Reduction

Transistor Sizing, Fast Logic Structures

Parallelism and Pipelining

Transformations to exploit concurrency

Figure 1-2: A system level approach to supply voltage scaling.

#### **Minimizing Switched Capacitance**

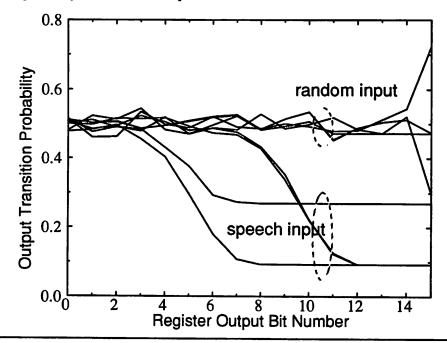

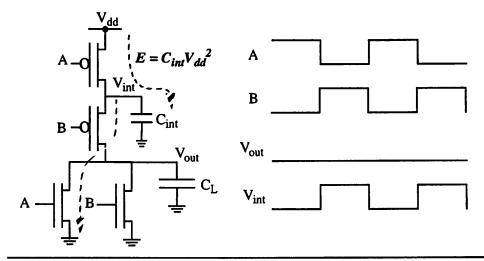

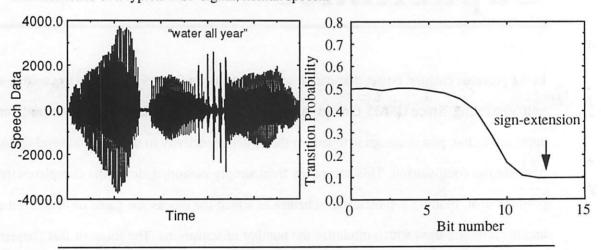

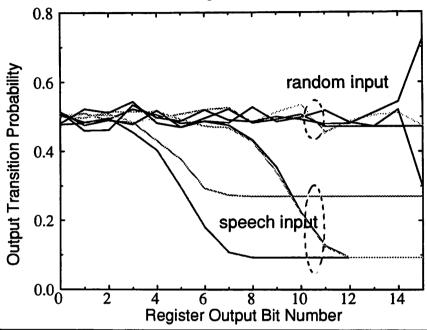

Since CMOS circuits do not dissipate power if they are not switching, a major focus of low power design is to reduce the switching activity to the minimal level required to perform the computation. This can range from simply powering down the complete circuit or portions of it, to more sophisticated schemes in which the clocks are gated or optimized circuit architectures are used which minimize the number of transitions. An important attribute which can be used in circuit and architectural optimization, is the correlation which can exist between values of a temporal sequence of data, since switching should decrease if the data is slowly changing (highly positively correlated). An example of the difference in the number of transitions which can be obtained for a highly correlated data stream (human speech) versus random data is shown in Figure 1-3 - the transition activity for a few registers in an FIR filter design. For an architecture which does not destroy the data correlation, the speech data switches 80% less capacitance than the random input. In addition, the sequencing of operations can result in large variations of the switching activity due to these temporal correlations.

Figure 1-3: Dependence of activity on statistics: correlated vs. random input.

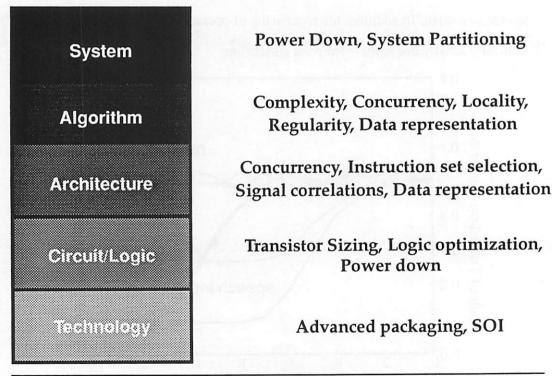

Figure 1-4 shows an overview of the techniques described in Chapter 4 for reducing the effective switched capacitance. The knowledge about signal statistics can be exploited to reduce the number of transitions. Various techniques are described which once again span all levels of the system design ranging from the technology and circuits used to the architectures and algorithms. At the technology level, packaging and SOI can be used to minimize the physical capacitance. Logic minimization and logic level power down is a key technique to keeping the transition activity to a minimum. Data dependent power down will be introduced which is a dynamic technique to reduce switched capacitance. At the architecture level, the trade-offs between time-multiplexed vs. parallel architectures, sign-magnitude vs. two's complement datapaths, ordering of operations, etc. will be studied for their influence on the switched capacitance. At the algorithmic level, the computational complexity (minimizing the number of operations) and data representation will be optimized for minimizing the switched capacitance.

Figure 1-4: A system level approach to minimizing the switched capacitance.

#### 1.1.2 CAD Tools for Low-power Design [Chapter 5]

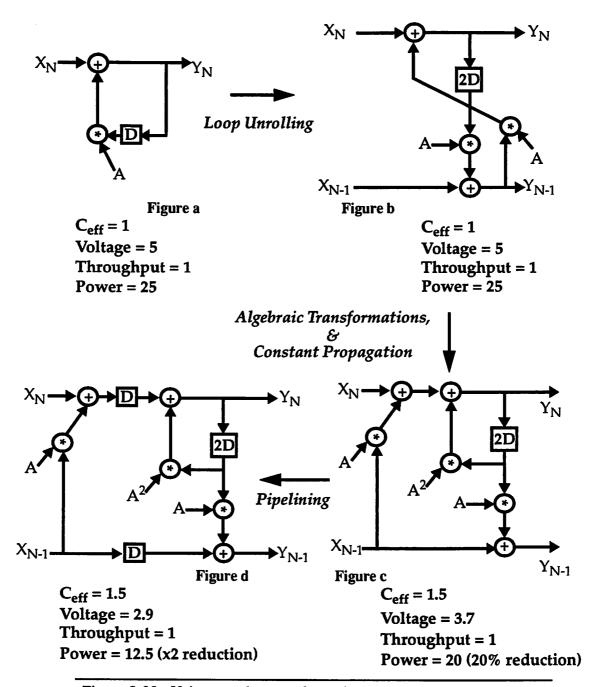

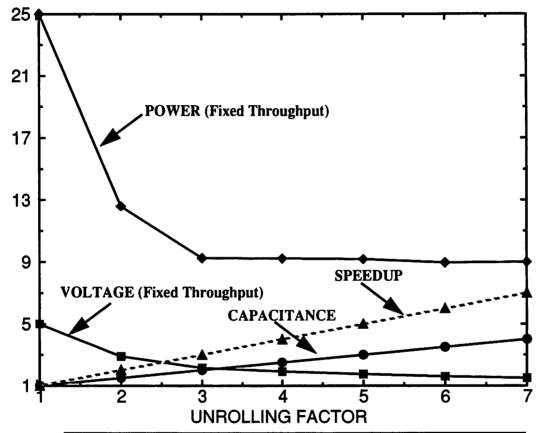

The focus of Chapter 5 is on automatically finding computational structures that result in the lowest power consumption for DSP applications that have a specific throughput constraint given a high-level algorithmic specification. The basic approach is to scan the design space utilizing various algorithmic flowgraph transformations, high-level power estimation, and efficient heuristic/probabilistic search mechanisms. While algorithmic transformations have been successfully applied in high-level synthesis with the goal of optimizing speed and/or area, they have not addressed the problem of minimizing power.

There are two approaches taken to explore the algorithmic design space to minimize power consumption. First, is the exploitation of concurrency which enables circuits to operate at the lowest possible voltage without loss in functional throughput. Second, computational structures are used that minimize the effective capacitance that is switched at a fixed voltage: through reductions in the number of operations, the interconnect capacitance, the glitching activity, and internal bit widths and using operations that require less energy per computation.

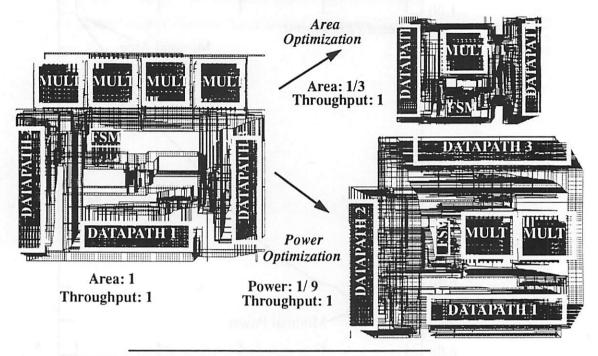

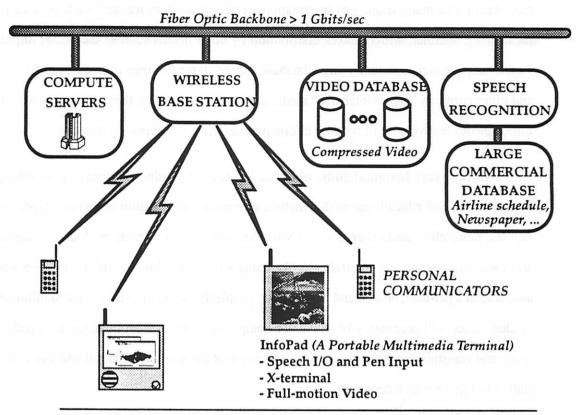

# 1.1.3 System Design Example: A Portable Multimedia Terminal [Chapters 6 and 7]

Future terminals will allow users to have untethered access to multimedia information servers that are interconnected through high bandwidth network backbones. Chapters 6 and 7 describe a low-power chipset for such a terminal, which is designed to transmit audio and pen input from the user to the network on a wireless uplink and will receive audio, text/graphics and compressed video from the backbone on the down link. The portability requirement resulted in the primary design focus to be on power reduction. Six chips provide the interface between a high speed digital radio modem and a commercial speech codec, pen input circuitry, and LCD panels for text/graphics and full-motion video display. This chipset demonstrates the various low-power techniques that are developed in Chapters 3 and 4.

A system approach to power reduction will be described which involves optimizing the physical design, the circuitry, the logic design, the architectures and system partitioning. This includes minimizing the number of operations at the algorithmic level, using the architecture driven voltage scaling strategy described in Chapter 3 to operate at supply voltages as low as 1.1V, using gated clocks to minimize the effective clock load and the switched capacitance in logic circuits, optimizing circuits to minimize the voltage swings and switched capacitance, using self-timed memory circuits to eliminate glitching on the data busses, utilizing a low-power cell-library that features minimum sized devices, optimized layout, and single-phase clocking, and using an activity driven place and route. The chips provide protocol conversion, synchronization, error correction, packetization, buffering, video decompression, and D/A conversion at a total power consumption of less than 5 mW - orders of magnitude lower than existing commercial solutions.

#### 1.1.4 Energy Efficient Programmable Computation [Chapter 8]

Chapter 8 describes approaches for energy efficient programmable computation. Two key architectural approaches for energy efficient programmable computation are described: predictive shutdown and concurrency driven supply voltage reduction. Many computations are "event-driven" in nature with intermittent computation activity triggered by external events and separated by periods of inactivity - examples include X server, communication interfaces etc. An obvious way to reduce average power consumption in such computations would be to shut the system down during periods of inactivity. Shutting the system down - which would make power consumption zero or negligible - can be accomplished either by shutting off the clock (f=0) or in certain cases by shutting off the power supply ( $V_{dd}$ =0). However the shutdown mechanism has to be such that there is no or little degradation in speed - both latency and throughput are usually important in event-driven computations. There are two main problems in shutdown that are addressed- how to shutdown, and when to shutdown. An aggressive shut down strategy based on a predictive technique will be presented which can reduce the power consumption by a large factor compared to the straightforward conventional schemes where the power down decision in based

solely on a predetermined idle time threshold.

Not all computation implemented as software is "event-driven" in nature - data-flow functions such as DSP are "continuous" in nature. Obviously, shutdown is not an effective mechanism for these systems. An alternative strategy is to operate at the lowest possible supply voltage, which, unfortunately, comes at the expense of reduced circuit speed. However, if only throughput and not latency is the metric of speed - as is true for many "continuous" applications such as speech coding - the reduction in circuit speed can be compensated for by architectural techniques like pipelining and parallelism. Compiler techniques for effective parallelization and pipelining play an important role in the success of this strategy to energy efficiency.

#### **CHAPTER 2**

# Power Consumption in CMOS Circuits

In order to minimize the power consumption of a design, the various power components and their relative importance with respect to the overall power consumption must be examined. The two important types of power consumption relevant to circuit design are peak power consumption and average power consumption. Peak power affects both the circuit lifetime and performance. Excessive instantaneous current drawn from the power supply results in large voltage drops across power/ground lines due to the resistance of power wires and results in large instantaneous power dissipation. Voltage drops in the power supply voltage result in power supply glitches which in turn cause erroneous evaluation of logic circuits and results in soft errors. Large instantaneous power dissipation causes overheating of the devices which ultimately causes degradation in circuit performance.

The design of portable devices certainly requires consideration of the peak power consumption for reliability and proper circuit operation, but a much more important consideration is the time averaged power consumption which is directly proportional to the battery weight required to operate circuits for a given amount of time. In fact, the approaches which will be presented to

minimize the average power consumption will also reduce the peak power consumption and improve reliability.

There are four sources of power dissipation in digital CMOS circuits which are summarized in the following equation:

$$\begin{aligned} P_{avg} &= P_{switching} + P_{short-circuit} + P_{leakage} + P_{static} = \\ \alpha_{0->1} C_L &\bullet V \bullet V_{dd} \bullet f_{clk} + I_{sc} \bullet V_{dd} + I_{leakage} \bullet V_{dd} + I_{static} \bullet V_{dd} \end{aligned} \tag{EQ 1}$$

The first term represents the switching component of power, where  $C_L$  is the loading capacitance,  $f_{clk}$  is the clock frequency and  $\alpha_{0 \to 1}$  is the probability that a power consuming transition occurs (the activity factor). In most cases, the voltage swing, V, is the same as the supply voltage,  $V_{dd}$ ; however, some logic circuits, such as in single-transistor pass-transistor implementations, the voltage swing on some internal nodes may be slightly less. The second term is due to the direct-path short circuit current,  $I_{sc}$ , which arises when both the NMOS and PMOS transistors are simultaneously active, conducting current directly from supply to ground. The third term is due to the leakage current,  $I_{leakage}$ , which can arise from substrate injection and sub-threshold effects, is primarily determined by fabrication technology considerations. Finally, static currents,  $I_{static}$ , arise from circuits that have a constant source of current between the power supplies (such as bias circuitry, pseudo-NMOS logic families, etc.). The four components of power consumption are described in detail below.

#### 2.1 Switching Component of Power

The switching component of power arises when energy is drawn from the power supply to charge parasitic capacitors (made up of gate, diffusion, and interconnect). Every parasitic capacitor in a circuit does not consume switching power every single clock cycle, but rather typically at a lower rate called the switching activity. The components of switching activity are described in this section and opportunities for power reduction are explored.

#### 2.1.1 Computation of Switching Energy Per Transition

The energy drawn from the supply for each power consuming transition is derived for various types of circuits implemented in CMOS technology.

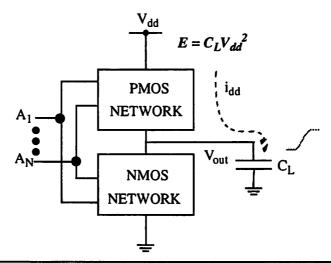

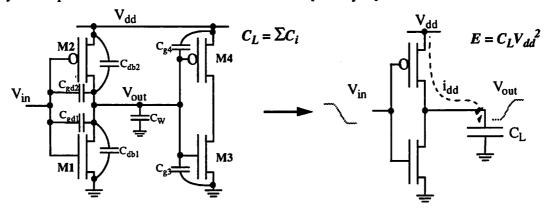

#### Conventional CMOS Circuits with Rail-to-Rail Swing

The switching or dynamic component of power consumption arises when the output of a CMOS circuit is charged through the power supply or is discharged to ground. The switching component of energy drawn from the power supply for a  $0 \rightarrow V_{dd}$  transition at the output of a CMOS gate is given by  $C_L \ V_{dd}^2$ , where  $C_L$  is the physical load capacitance at the output node and  $V_{dd}$  is the supply voltage. Figure 2-6 shows an equivalent circuit model for computing the switching component of power. The switching component of energy is relatively independent of the function being performed (i.e the interconnection network of the NMOS and PMOS transistors) and the slope or rise times for the input signals of the CMOS gate (i.e. the short-circuit currents are ignored) and is only dependent on the output load capacitance and the power supply voltage.

Figure 2-1: Circuit model for computing the dynamic power of a CMOS gate.

To compute the average energy consumed per switching event for the generic CMOS gate shown in Figure 2-6, consider any input transition which causes a  $0->V_{\rm dd}$  transition at the output of the

CMOS gate. For this particular transition (ignoring short-circuit currents) the instantaneous power and energy drawn can be computed as follows:

$$P(t) = \frac{dE}{dt} = i_{supply} \bullet V_{dd}$$

(EQ 2)

where  $i_{supply}$  is the instantaneous current being drawn from the supply voltage  $V_{dd}$ . Therefore, the average energy drawn from the power supply is given by:

$$E_{av} = \int_{0}^{T} p(t) dt = \int_{0}^{T} \frac{dE}{dt} dt = V_{dd} \int_{0}^{t} i_{supply}(t) dt = V_{dd} \int_{0}^{t} C_{L} dV = C_{L} \cdot V_{dd}^{2}$$

(EQ3)

From Equation 3, it is clear that the energy drawn from the power supply for a 0-> $V_{dd}$  transition at the output is  $C_L V_{dd}^2$  regardless of the function being performed by the CMOS gate. For this transition, the energy stored in the output load capacitor is given by:

$$E_{cap} = \int_{0}^{T} p_{cap}(t) dt = \int_{0}^{T} V_{cap} i_{cap}(t) dt = \int_{0}^{V} C_{L} V_{cap} dV = \frac{1}{2} C_{L} \cdot V_{dd}^{2}$$

(EQ 4)

Therefore, half of the energy drawn from the power supply is stored in the output capacitor and half of the energy is dissipated in the PMOS network. For the  $V_{dd} \rightarrow 0$  transition at the output, no charge is drawn from the supply and the energy stored in the capacitor (1/2  $C_L V_{dd}^2$ ) is dissipated in the pull-down NMOS network.

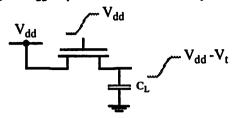

#### **Circuits Employing Voltage Clamping**

The energy drawn from the power supply per switching event for a standard CMOS gate which has rail to rail output swing was calculated in Equation 3. This equation requires slight modification to account for logic that does not have rail to rail swing. This situation is typical for circuit topologies that use single transistor NMOS pass gates which do not have rail to rail swing. Figure 2-2 shows one example in which an NMOS transistor is used to charge an output load capacitor. For this

transition, the output rises only to  $V_{dd}$  - $V_t$ , rather than all the way to the rail voltage.

Figure 2-2: Switching power for reduced swing logic.

The energy drawn from the supply for a  $0 \rightarrow V_{dd} - V_t$  transition at the output is given by:

$$E_{av} = \int_{0}^{T} \frac{T}{dt} dt = V_{dd} \int_{0}^{t} i_{supply}(t) dt = V_{dd} \int_{0}^{t} C_{L} dV = C_{L} \cdot V_{dd} \cdot \left(V_{dd} - V_{t}\right)^{(EQ 5)}$$

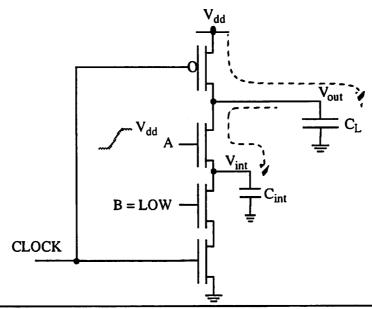

#### **Dynamic Charge Sharing Circuits**

Dynamic logic circuits suffer from charge sharing problems which result in extra parasitic switching power. For N-tree dynamic logic (with PMOS precharge transistor), the precharge operation forces the output to  $V_{dd}$ . During the evaluation operation, depending on the number of NMOS switches turn on, the output voltage is reduced to

$$V_{out} = \frac{C_L}{C_I + C_{int}} \bullet V_{dd}$$

(EQ 6)

where  $C_{int}$  the sum of the internal node capacitances and  $C_L$  is the output load capacitance. Figure 2-3 shows a simple NAND gate example. Here input A goes high during the evaluate period while node B remains LOW. Therefore, the charge on  $C_L$  is redistributed between  $C_L$  and  $C_{int}$  during the evaluate period.

Therefore, during the next precharge period, the output has to be precharged back to  $V_{dd}$ . Therefore, the power consumed for this operation is obtained similar to the analysis of the previous section and is given by:

$$V_{out} = C_L \bullet V_{dd} \bullet \Delta V = C_L \bullet V_{dd} \bullet \left( V_{dd} - \left( \frac{C_L}{C_L + C_{int}} \cdot V_{dd} \right) \right) = C_L \bullet V_{dd}^2 \bullet \frac{C_{int}}{C_L + C_{int}}$$

(EQ 7)

This is significant if the internal node capacitance is comparable to the load capacitance. Charge sharing is a very important consideration for evaluating both functionality and power consumption. If the output drops more than the threshold voltage of the PFET transistor of the next stage (for a NORA implementation), this can result in incorrect evaluation. The effect is less for Domino logic gates since properly designed inverter gates following the logic prevent propagation of low logic levels.

Figure 2-3: Charge sharing in dynamic circuits result in "extra" switching power.

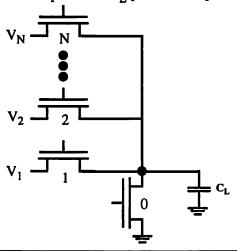

#### **Adiabatic Circuits**

In the conventional CMOS circuits described earlier, the output load capacitance is charged to the power supply voltage through MOSFET switches which have a certain ON resistance. If the load has physical capacitance  $C_L$ , then a charge of  $C_L V_{dd}$  passes through the resistance. The voltage drop across the resistance varies from  $V_{dd}$  initially to a final value of zero. Therefore, the energy dissipated in the resistance for the 0 to 1 transition at the output is  $Q\overline{V} = C_L V_{dd} V_{dd}/2$ , where  $\overline{V}$  is the average voltage drop across the resistance. Adiabatic switching circuits reduce the dissipation

in the resistances by reducing the average voltage drop,  $\overline{V}$  (the charge that has to be transferred from the supply is set by the output capacitance and the voltage). Figure 2-4 shows such a circuit, which is a stepwise driver for a capacitance  $C_L$  [Svensson94].

Figure 2-4: Stepwise driver for a capacitive load C<sub>L</sub>.

Here a bank of N voltage supplies with evenly distributed voltage is used:  $V_i = (i/N)V_{dd}$ . To charge the load,  $V_1$  through  $V_N$  are connected to the load in succession (by closing switch 1, opening switch 1, closing switch 2, etc.). To discharge the load,  $V_{N-1}$  through  $V_1$  are switched and then switch 0 is closed, shorting the output to ground. For each step, the dissipation is equal to the charge transferred and the average voltage drop across the switch resistance:

$$E_{step} = Q \cdot V_{avg} = C_L \cdot \frac{V_{dd}}{N} \cdot \frac{V_{dd}}{2N} = \frac{\frac{1}{2} \cdot C_L \cdot V_{dd}^2}{N^2}$$

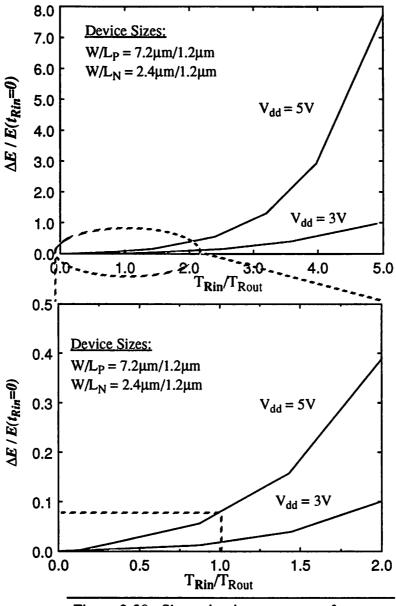

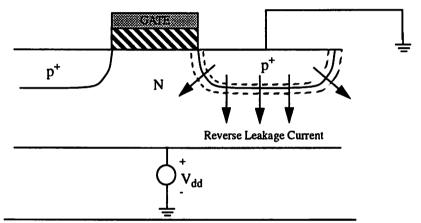

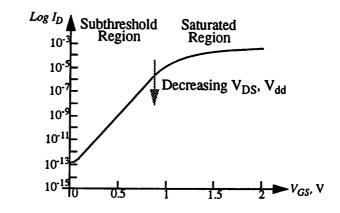

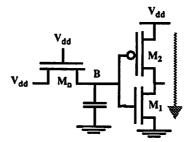

(EQ 8)