# Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# OPTIMIZING SYNCHRONIZATION IN MULTIPROCESSOR IMPLEMENTATIONS OF ITERATIVE DATAFLOW PROGRAMS

by

Shuvra S. Bhattacharyya, Sundararajan Sriram, and Edward A. Lee

Memorandum No. UCB/ERL M95/2

5 January 1995

# OPTIMIZING SYNCHRONIZATION IN MULTIPROCESSOR IMPLEMENTATIONS OF ITERATIVE DATAFLOW PROGRAMS

by

Shuvra S. Bhattacharyya, Sundararajan Sriram, and Edward A. Lee

Memorandum No. UCB/ERL M95/2

5 January 1995

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

# OPTIMIZING SYNCHRONIZATION IN MULTIPROCESSOR IMPLEMENTATIONS OF ITERATIVE DATAFLOW PROGRAMS

by

Shuvra S. Bhattacharyya, Sundararajan Sriram, and Edward A. Lee

Memorandum No. UCB/ERL M95/2

5 January 1995

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

# OPTIMIZING SYNCHRONIZATION IN MULTIPROCESSOR IMPLEMENTATIONS OF ITERATIVE DATAFLOW PROGRAMS

Shuvra S. Bhattacharyya, Sundararajan Sriram, and Edward A. Lee

January 5, 1995

#### **ABSTRACT**

This paper is concerned with multiprocessor implementations of embedded applications specified as iterative dataflow programs, in which synchronization overhead tends to be significant. We develop techniques to alleviate this overhead by determining a minimal set of processor synchronizations that are essential for correct execution. Our study is based in the context of self-timed execution of iterative dataflow programs. An iterative dataflow program consists of a dataflow representation of the body of a loop that is to be iterated an indefinite number of times; dataflow programming in this form has been studied and applied extensively, particularly in the context of signal processing software. Self-timed execution refers to a combined compile-time/run-time scheduling strategy in which processors synchronize with one another only based on inter-processor communication requirements, and thus, synchronization of processors at the end of each loop iteration does not generally occur.

We introduce a new graph-theoretic framework for analyzing and optimizing synchronization overhead in self-timed, iterative dataflow programs. This framework is based on a data structure, which we call the *inter-processor communication* (IPC) graph, that was first proposed in [32] for analyzing the throughput of self-timed systems. We show that the comprehensive techniques that have been developed for removing redundant synchronizations in non-iterative programs can be extended in this framework to optimally remove redundant synchronizations in our context. We also introduce two new optimizations for reducing synchronization overhead in self-timed, iterative dataflow programs — resynchronization and the conversion of the synchronization graph into a strongly connected graph.

This research was partially funded as part of the Ptolemy project, which is supported by the Advanced Research Projects Agency and the U. S. Air Force (under the RASSP program, contract F33615-93-C-1317), Semiconductor Research Corporation (project 94-DC-008), National Science Foundation (MIP-9201605), Office of Naval Technology (via Naval Research Laboratories), the State of California MICRO program, and the following companies: Bell Northern Research, Cadence, Dolby, Hitachi, Mentor Graphics, Mitsubishi, NEC, Pacific Bell, Philips, Rockwell, Sony, and Synopsys.

- S. S. Bhattacharyya is with the Semiconductor Research Laboratory, Hitachi America, Ltd., 179 East Tasman Drive., San Jose, California 95134, USA.

- S. Sriram and E. A. Lee are with the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, California 94720, USA.

#### 1. Introduction

In this paper, we address the problem of minimizing the overhead of inter-processor synchronization for an *iterative synchronous dataflow program* that is implemented on a shared-memory multiprocessor system. This study is motivated by the widespread popularity of the synchronous dataflow (SDF) model in DSP design environments; the suitability of this model for exploiting parallelism; and the high overhead of run-time synchronization, which can severely limit the speedup obtained by moving an implementation of an SDF program from a uniprocessor implementation to a multiprocessor implementation. Our work is particularly relevant when estimates are available for the task execution times, and actual execution times are usually close to the corresponding estimates, but deviations from the estimates of (effectively) arbitrary magnitude can occasionally occur due to phenomena such as cache misses or error handling.

SDF and closely related models have been used widely as foundations for numerous graphical DSP design environments, in which signal processing applications are represented as hierarchies of block diagrams. Some examples are described in [16, 22, 25, 26, 29]. In SDF, as in other forms of dataflow, a program is represented as a directed graph in which the vertices, called actors, represent computations, and the edges specify FIFO channels for communication between actors. The term *synchronous* refers to the requirement that the number of data values produced (consumed) by each actor onto (from) each of its output (input) edges is a fixed value that is known at compile time [18] and should not be confused with the use of "synchronous" in synchronous languages [2]. The techniques developed in this paper assume that the input SDF graph is *homogeneous*, which means that the numbers of data values produced or consumed are identically unity. However, since efficient techniques have been developed to convert general SDF graphs into equivalent (for our purposes) homogeneous SDF graphs [18], our techniques apply equally to general SDF graphs. In the remainder of this paper, when we refer to a dataflow graph (DFG) we imply a homogeneous SDF graph.

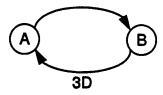

It is sometimes necessary to insert *delays* on the edges of a dataflow graph, to represent initial tokens on the edges. These delays (which can also be interpreted as registers) specify dependencies between iterations of the actors in iteratively executed dataflow graphs. For exam-

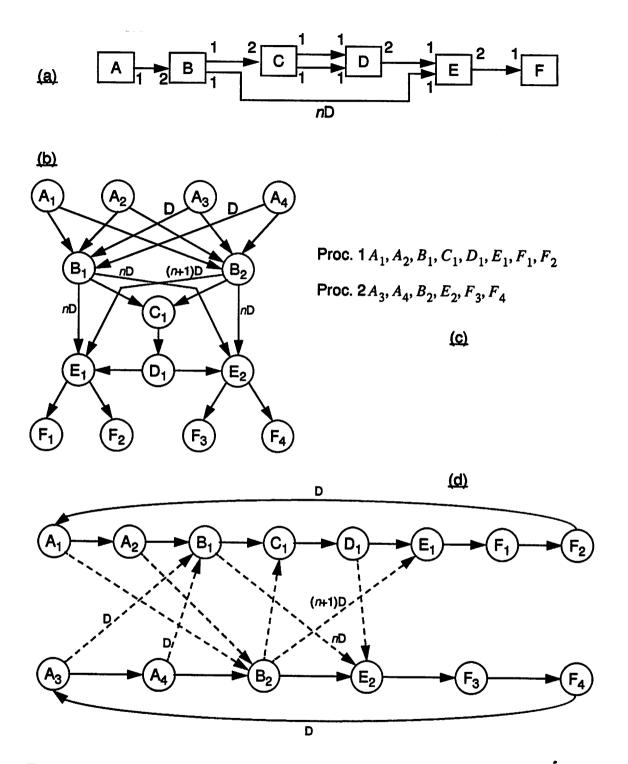

ple, if tokens produced by the k th execution of actor A are consumed by the (k+2) th execution of actor B, then the edge from A to B will contain two initial tokens, or delays. We will represent an edge with n delays by annotating it with the symbol "nD" in the dataflow graph representation (see Figure 1).

Multiprocessor implementation of an algorithm specified as a DFG involves scheduling computations in the algorithm. By "scheduling" we collectively refer to the task of assigning actors in the DFG to processors, ordering execution of these actors on each processor, and determining when each actor fires (begins execution) such that all data precedence constraints are met. Each of these three tasks may be performed either at run time (a dynamic strategy) or at compile time (a static strategy). In [19] and [20] the authors propose a scheduling taxonomy based on which of these tasks are performed at compile time and which at run time; in this paper we will use the same terminology that was introduced there. To reduce run time computation costs it is advantageous to perform as many of the three scheduling tasks as possible at compile time. Which of these can be effectively performed at compile time depends on the information available about the execution time of each actor — that is, on the amount of time it takes for each actor to complete execution once it fires.

The performance metric that is of interest for evaluating schedules is the average iteration period T, which is the average time that it takes for all the actors in the graph to be executed once. Equivalently, we could use the throughput  $T^{-1}$  (that is, the number of iterations of the graph executed per unit time) as a performance metric. Thus an optimal schedule is one that minimizes T.

In the fully-static scheduling strategy of [4], all the three scheduling tasks — assigning actors to processors, ordering their execution on each processor, as well as determining exactly when an actor fires — are performed at compile time. This strategy involves the least possible amount of runtime overhead. All the processors run in lock step and no explicit synchronization is required when they exchange data. However, this strategy assumes that exact execution times of actors are known. Such an assumption is in general not practical. A more realistic assumption for DSP algorithms is that good estimates for the execution times of actors can be obtained. These estimates may not be accurate down to the clock cycle, because the object code for the processors

might be compiled from a high-level language, which makes estimation of exact execution time difficult, or the processor itself might take a non-deterministic number of cycles to complete an instruction, if it employs a cache for instance. These estimates may not even have guaranteed worst case bounds, if, for example, at run time a processor has to respond to events that require error handling or has to process user inputs, which are infrequent (rare) compared to the sample rate at which the DFG executes.

Under such an assumption on timing, it is best to discard the exact timing information from the fully static schedule, but still retain the processor assignment and actor ordering specified by the fully static schedule. This results in the self-timed scheduling strategy of [19]. Each processor executes the actors assigned to it in the order specified at compile time. Before firing an actor, a processor waits for the data needed by that actor to become available. Thus in self-timed scheduling processors are required to perform run-time synchronization when they communicate data. Such synchronization is not necessary in the fully-static case because exact (or guaranteed worst case) times could be used to determine firing times of actors such that processor synchronization was ensured. As a result, the self-timed strategy incurs greater run-time cost than the fully-static case because of the synchronization overhead.

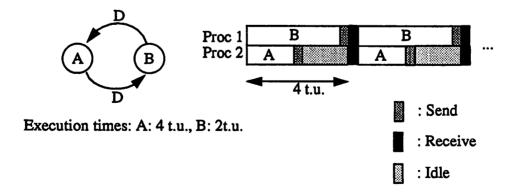

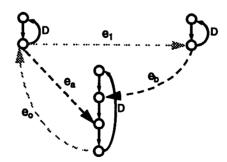

An example of a DFG and a corresponding self-timed schedule are shown in Figure 1. Note that inter-processor communication primitives (*send* and *receive* actors) need to be inserted when data cross processor boundaries. As a result, a multiprocessor schedule for a DFG falls naturally into a message passing inter-processor communication model. The execution times for the

Figure 1. An example of a self-timed schedule.

actors A and B are estimates that are used to determine the processor assignment and ordering for the schedule. However, the processors need to explicitly synchronize at each communication point since the estimated execution times may not be exact or may vary from one iteration of the DFG to the next. Clearly, if these times were known precisely, we could eliminate the need for explicit synchronization by determining precisely when each actor fires and when the send and the receive primitives are executed. If we ignore communication costs, that is, we assume sends and receives take zero time, then the estimated iteration period (T) for this example is 4 time units.

A straightforward implementation of a self-timed schedule would require that for each inter-processor communication (IPC) the sending processor ascertains that the buffer it is writing to is not full, and the receiver ascertains that the buffer it is reading from is not empty. The processors block (suspend execution) when the appropriate condition is not met. Such sender-receiver synchronization can be implemented in many ways depending on the particular hardware platform under consideration: in shared memory machines, such synchronization involves testing and setting semaphores in shared memory; in machines that support synchronization in hardware (such as barriers), special synchronization instructions are used; and in the case of systems that consist of a mix of programmable processors and custom hardware elements, synchronization is achieved by employing interfaces that support blocking reads and writes.

In each kind of platform, every IPC that requires a synchronization check costs performance, and sometimes extra hardware complexity: semaphore checks cost execution time on the processors, synchronization instructions that make use of synchronization hardware also cost execution time, and blocking interfaces in hardware/software implementations require more hardware than non-blocking interfaces [12].

The main goal of this paper is to present algorithms and techniques that reduce the rate at which processors must access shared memory for the purpose of synchronization in embedded, shared-memory multiprocessor implementations of iterative dataflow programs. Thus the optimization procedure that we propose can be used as a post-processing step in any static scheduling technique for reducing synchronization costs in the final implementation. In this paper we assume that "good" estimates are available for the execution times of actors and that these execution

times rarely display large variations so that self-timed scheduling is viable for the applications under consideration. If additional timing information is available, such as guaranteed upper and lower bounds on the execution times of actors, it is possible to use this information to further optimize synchronizations in the schedule. However, use of such timing bounds is beyond the scope of this paper.

Our paper is organized as follows. In Section 2 we review some of the related work in synchronization optimization, and in Section 3 we list some of the notation and terminology used in this paper. Sections 4, 5 and 6 present our graph-theoretic framework for analyzing and optimizing synchronization. In Section 7, we formally define the optimization problem addressed in this paper in terms of the model and results developed in Sections 4-6. Sections 8, 9 and 10 present the algorithms used for our proposed synchronization optimization scheme. Finally, in Section 11 we present the complete synchronization algorithm, and then end with conclusions in Section 12, and discuss directions for future work in Section 13. For reference, some of the terminology and notation used in this paper is summarized in a glossary at the end of the paper.

#### 2. Related Work

Numerous research efforts have focused on constructing efficient parallel schedules for DFGs. Parhi and Messerschmitt [23], and Chao and Sha [6] have developed systematic techniques for exploiting overlapped execution to generate schedules that have optimal throughput, assuming zero cost for IPC. Other work has focused on taking IPC costs into account during scheduling, such as that described in [1, 21, 27, 31]; these efforts have not attempted to exploit overlapped execution of dataflow graph iterations. Similarly, in [10], Govindarajan and Gao develop techniques to simultaneously maximize throughput, possibly using overlapped execution, and minimize buffer memory requirements under the assumption of zero IPC cost. Our work can be used as a post-processing step to improve the performance of implementations that use any of these scheduling techniques when the goal is a self-timed implementation.

Among the prior work that is most relevant to this paper is the barrier-MIMD principle of Dietz, Zaafrani, and O'keefe, which is a combined hardware and software solution to reducing

run-time synchronization overhead [8]. In this approach, a shared-memory MIMD computer is augmented with hardware support that allows arbitrary subsets of processors to synchronize precisely with respect to one another by executing a synchronization operation called a *barrier*. If a subset of processors is involved in a barrier operation, then each processor in this subset will wait at the barrier until all other processors in the subset have reached the barrier. After all processors in the subset have reached the barrier, the corresponding processes resume execution in *exact synchrony*.

In [8], the barrier mechanism is applied to minimize synchronization overhead in a self-timed schedule with hard lower and upper bounds on the task execution times. The execution time ranges are used to detect situations where the earliest possible execution time of a task that requires data from another processor is guaranteed to be later than the latest possible time at which the required data is produced. When such an inference cannot be made, a barrier is instantiated between the sending and receiving processors. In addition to performing the required data synchronization, the barrier resets (to zero) the uncertainty between the relative execution times for the processors that are involved in the barrier, and thus enhances the potential for subsequent timing analysis to eliminate the need for explicit synchronizations.

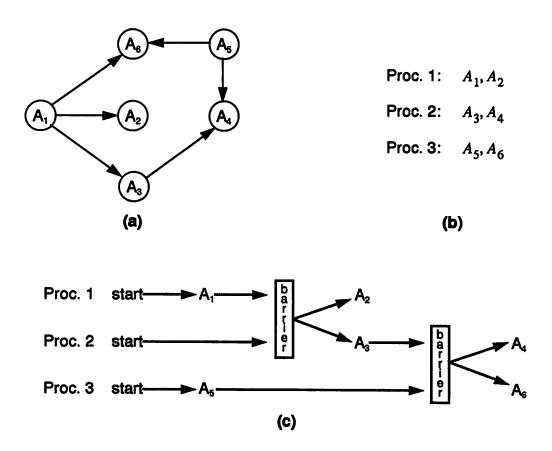

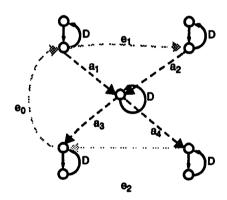

The techniques of barrier MIMD do not apply to the problem that we address because they assume that a hardware barrier mechanism exists; they assume that tight bounds on task execution times are available; they do not address iterative, self-timed execution, in which the execution of successive iterations of the dataflow graph can overlap; and even for non-iterative execution, there is no obvious correspondence between an optimal solution that uses barrier synchronizations and an optimal solution that employs decoupled synchronization checks at the sender and receiver end (directed synchronization). This last point is illustrated in Figure 2. Here, in the absence of execution time bounds, an optimal application of barrier synchronizations can be obtained by inserting two barriers — one barrier across  $A_1$  and  $A_3$ , and the other barrier across  $A_4$  and  $A_5$ . This is illustrated in Figure 2(c). However, the corresponding collection of directed synchronizations ( $A_1$  to  $A_3$ , and  $A_5$  to  $A_4$ ) is not sufficient since it does not guarantee that the data required by  $A_6$  from  $A_1$  is available before  $A_6$  begins execution.

In [30], Shaffer presents an algorithm that minimizes the number of directed synchronizations in the self-timed execution of a dataflow graph. However, this work, like that of Dietz et al., does not allow the execution of successive iterations of the dataflow graph to overlap. It also avoids having to consider dataflow edges that have delay. The technique that we present for removing redundant synchronizations can be viewed as a generalization of Shaffer's algorithm to handle delays and overlapped, iterative execution, and we will discuss this further in Section 8. The other major techniques that we present for optimizing synchronization — handling the feedforward edges of the synchronization graph (to be defined in Section 6), discussed in Section 10,

Figure 2. (a). A DFG.

- (b). A three-processor self-timed schedule for (a).

- (c). An illustration of execution under the placement of barriers.

and "resynchronization", defined and addressed in Sections 9 and the appendix — are fundamentally different from Shaffer's technique since they address issues that are specific to our more general context of overlapped, iterative execution.

#### 3. Background Terminology and Notation

We frequently represent a DFG by an ordered pair (V, E), where V is the set of vertices and E is the set of edges. We refer to the source and sink vertices of a graph edge e by src(e) and snk(e), and we denote the delay on e by delay(e). We say that e is an **output edge** of src(e), and that e is an **input edge** of snk(e).

Given  $x, y \in V$ , we say that x is a predecessor of y if there exists  $e \in E$  such that src(e) = x and snk(e) = y; we say that x is a successor of y if y is a predecessor of x. A path in (V, E) is a finite, nonempty sequence  $(e_1, e_2, ..., e_n)$ , where each  $e_i$  is a member of E, and  $snk(e_1) = src(e_2)$ ,  $snk(e_2) = src(e_3)$ , ...,  $snk(e_{n-1}) = src(e_n)$ . We say that the path  $p = (e_1, e_2, ..., e_n)$  contains each  $e_i$  and each subsequence of  $(e_1, e_2, ..., e_n)$ ; p is directed from  $src(e_1)$  to  $snk(e_n)$ ; and each member of

$\{src(e_1), src(e_2), ..., src(e_n), snk(e_n)\}\$  is on p. A path that is directed from some vertex to itself is called a cycle, and a fundamental cycle is a cycle of which no proper subsequence is a cycle.

If  $p = (e_1, e_2, ..., e_n)$  is a path in a DFG, then we define the **path delay** of p, denoted Delay(p), by  $Delay(p) = \sum_{i=1}^{n} delay(e_i)$ . Since the delays on all DFG edges are restricted to

be non-negative, it is easily seen that between any two vertices  $x, y \in V$ , either there is no path directed from x to y, or there exists a (not necessarily unique) minimum-delay path between x and y. That is, if there is a path from x to y, then there exists a path p from x to y such that

Delay  $(p') \ge Delay(p)$ , for all paths p' directed from x to y. Given a DFG G, and vertices x, y in G, we define  $\rho_G(x, y)$  to be equal to  $\infty$  if there is no path from x to y, and equal to the path delay of a minimum-delay path from x to y if there exist one or more paths from x to y. If G is understood, then we may drop the subscript and simply write " $\rho$ " in place of " $\rho_G$ ".

By a subgraph of (V, E), we mean the directed graph formed by any  $V' \subseteq V$  together with the set of edges  $\{e \in E | src(e), snk(e) \in V'\}$ . We denote the subgraph associated with the vertex-subset V' by subgraph(V'). We say that (V, E) is strongly connected if for each pair of distinct vertices x, y, there is a path directed from x to y and there is a path directed from y to x. We say that a subset  $V' \subseteq V$  is strongly connected if subgraph(V') is strongly connected. A strongly connected component (SCC) of (V, E) is a strongly connected subset  $V' \subseteq V$  such that no strongly connected subset of V properly contains V'. If V' is an SCC, then when there is no ambiguity, we may also say that subgraph(V') is an SCC. If  $C_1$  and  $C_2$  are distinct SCCs in (V, E), we say that  $C_1$  is a predecessor SCC of  $C_2$  if there is an edge directed from some vertex in  $C_1$  to some vertex in  $C_2$ ;  $C_1$  is a successor SCC of  $C_2$  if  $C_2$  is a predecessor SCC of  $C_1$ . An SCC is a successor SCC if it has no predecessor SCC, and an SCC is a successor SCC if it has no successor SCC. An edge e is a successor section in a successor successor SCC, and successor successor SCC, and successor successor SCC if it is not contained in an SCC, or equivalently, if it is not contained in a cycle; an edge that is contained in at least one cycle is called a successor successor edge.

Given two arbitrary sets  $S_1$  and  $S_2$ , we define the difference of these two sets by  $S_1 - S_2 = \{s \in S_1 | s \notin S_2\}$ , and we denote the number of elements in a finite set S by |S|. Also, if r is a real number, then we denote the smallest integer that is greater than or equal to r by  $\lceil r \rceil$ .

In this paper, we assume that the source and sink vertices uniquely identify an edge in a DFG, and thus we may represent an edge  $e \in E$  by the ordered pair (src(e), snk(e)). It is conceivable, however, that a practical system may have a DFG in which one or more pairs of vertices

have multiple edges connecting them in the same "direction". Such graphs can very easily be preprocessed into a form to which the techniques of this paper can be applied; the details are beyond the scope of this paper. Finally, if x, y are vertices in (V, E), we define  $d_n(x, y)$  to represent an edge (that is not necessarily in E) whose source and sink vertices are x and y, respectively, and whose delay is n (assumed non-negative).

For elaboration on any of the graph-theoretic concepts presented in this section, we refer the reader to [7].

# 4. Model of a Multiprocessor Executing a Self-timed Schedule

We model a multiprocessor executing a self-timed schedule as follows. Each processor is assigned a sequential list of actors, some of which are *send* and *receive* actors, which it executes in an infinite loop. When a processor executes a communication actor, it synchronizes with the processor(s) it communicates with. Thus exactly when a processor executes each actor depends on when, at run time, all input data for that actor is available, unlike the fully-static case where no such run time check is needed. In this paper we use "processor" in slightly general terms: a processor could be a programmable component, in which case the actors mapped to it execute as software entities, or it could be a hardware component, in which case actors assigned to it are implemented and execute in hardware. See [13] for a discussion on combined hardware/software synthesis from a single dataflow specification. Examples of application specific multiprocessors that use programmable processors and some form of static scheduling are described in [4, 14, 33].

Inter-processor communication between processors is assumed to take place via shared memory. Thus the sender writes to a particular shared memory location and the receiver reads from that location. The shared memory itself could be global memory between all processors, or it could be distributed between pairs of processors (as a hardware first-in-first-out (FIFO) queues or dual ported memory for example). Each inter-processor communication edge in our DFG thus translates into a buffer of a certain size (which we will discuss later) in shared memory.

Sender-receiver synchronization is also assumed to take place by setting flags in shared memory. Special hardware for synchronization (barriers, semaphores implemented in hardware,

etc.) would be prohibitive for the embedded multiprocessor machines for applications such as DSP that we are considering.

Interfaces between hardware and software are typically implemented using memory-mapped registers in the address space of the programmable processor (again a kind of shared memory), and synchronization is achieved using flags that can be tested and set by the programmable component, and the same can be done by an interface controller on the hardware side [12].

Under the model above, the benefits that our proposed synchronization optimization techniques offer become abundantly clear. Each synchronization that we eliminate directly results in one less synchronization check, or a shared memory access. For example, where a processor would have to check a flag in shared memory before executing a receive primitive, eliminating that synchronization implies there is no longer need for such a check. This translates to one less shared memory read. Such a benefit is especially significant for simplifying interfaces between a programmable component and a hardware component: a send or a receive without the need for synchronization implies that the interface can be implemented in a non-blocking fashion, greatly simplifying the interface controller. As a result, eliminating a synchronization directly results in simpler hardware in this case.

Thus the metric for the optimizations we present in this paper is the total number of accesses to shared memory that are needed for the purpose of synchronization in the final multi-processor implementation of the self-timed schedule. This metric will be defined precisely in Sections 6 and 7.

#### 5. Analysis of Self-Timed Execution

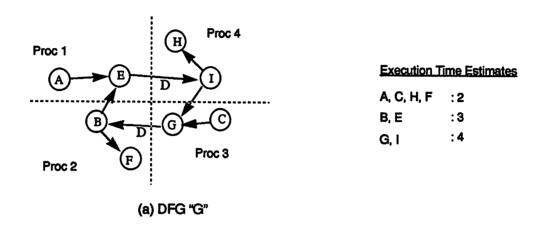

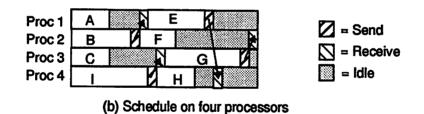

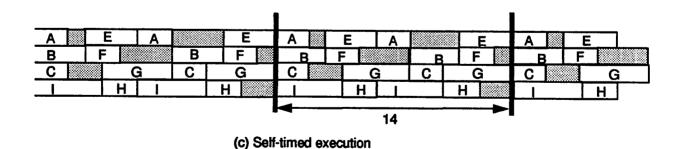

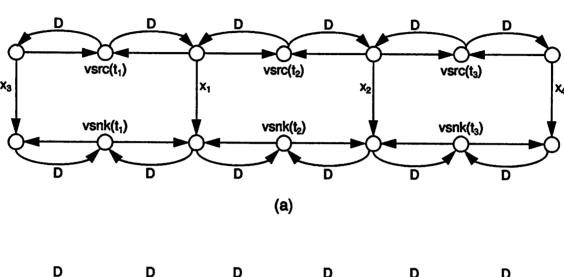

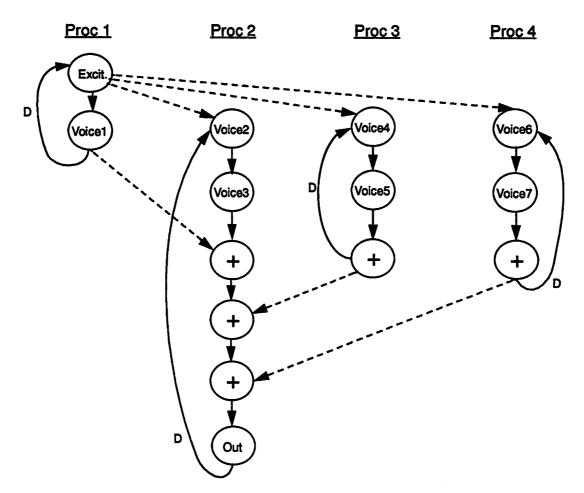

In this section we develop an analytical model to study the execution of a self-timed schedule. To motivate this section, let us consider the execution of the four-processor schedule in Figure 3. Inter-processor communication is ignored in the self-timed execution in Figure 3(c). If the timing estimates are accurate, the schedule execution settles into a repeating pattern spanning two iterations of G, and the average estimated iteration period is 7 time units.

We would like to model such a self-timed execution and determine the average iteration

period, represent the sequential execution of actors assigned to a single processor, and represent dependencies across iterations of the DFG.

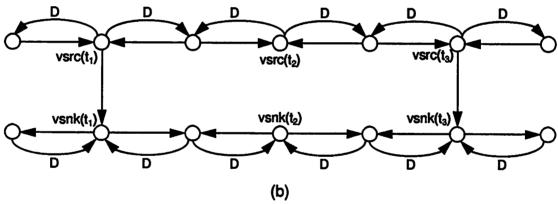

## 5.1 Inter-processor Communication Modelling Graph

Figure 3. Self-timed execution.

$$G_{ipc} = (V, E_{ipc})$$

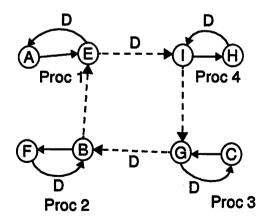

We model a self-timed schedule using a DFG  $G_{ipc} = (V, E_{ipc})$  derived from the original SDF graph G = (V, E) and the given self-timed schedule. The graph  $G_{ipc}$ , which we will refer to as the inter-processor communication modelling graph, or IPC graph for short, models the fact that actors of G assigned to the same processor execute sequentially, and it models constraints due to inter-processor communication. For example, the self-timed schedule in Figure 3 can be modelled by the IPC graph in Figure 4. The IPC edges are shown using dashed arrows. The rest of this subsection describes the construction of the IPC graph in detail.

The IPC graph has the same vertex set V as G, corresponding to the set of actors in G. The self-timed schedule specifies the actors assigned to each processor, and the order in which they execute. For example in Figure 3, processor 1 executes A and then E repeatedly. We model this in  $G_{ipc}$  by drawing a cycle around the vertices corresponding to A and E, and placing a delay on the edge from E to A. The delay-free edge from A to E represents the fact that the kth execution of A precedes the kth execution of E, and the edge from E to A with a delay represents the fact that the kth execution of E can occur only after the E to E the execution of E has

Figure 4. The IPC graph for the schedule in Figure 3.

completed. Thus if actors  $v_1, v_2, ..., v_n$  are assigned to the same processor in that order, then  $G_{ipc}$  would have a cycle  $((v_1, v_2), (v_2, v_3), ..., (v_{n-1}, v_n), (v_n, v_1))$ , with  $delay((v_n, v_1)) = 1$ . If there are P processors in the schedule, then we have P such cycles corresponding to each processor.

As mentioned before, edges in G that cross processor boundaries after scheduling represent inter-processor communication. We will call such edges IPC edges. Instead of explicitly introducing special send and receive primitives at the ends of the IPC edges, we will model these operations as part of the sending and receiving actors themselves. For example, in Figure 3, data produced by actor B is sent from processor 2 to processor 1; instead of inserting explicit communication primitives in the schedule, the send is modelled within actor B while the receive is modelled as part of actor E. This is done so as not to clutter  $G_{ipc}$  with extra communication actors. Even if the actual implementation uses explicit send and receive actors, communication can still be modelled in the above fashion because we are simply clustering the source of an IPC edge with the corresponding send actor and the sink with the receive actor.

For each IPC edge in G we add an IPC edge e in  $G_{ipc}$  between the same actors. We also set the delay on this edge equal to the delay, delay(e), on the corresponding edge in G. Thus, we add an IPC edge from E to I in  $G_{ipc}$  with a single delay on it. The delay corresponds to the fact that execution of E is allowed to lag the execution of E by one iteration. An IPC edge represents a buffer implemented in shared memory, and initial tokens on the IPC edge are used to initialize the shared buffer. In a straightforward self-timed implementation, each such IPC edge would also be a synchronization point between the two communicating processors. Part of our goal is to identify IPC edges that do not require sender synchronization or receiver synchronization.

The IPC graph has the same semantics as a DFG, and its execution models the execution of the corresponding self-timed schedule. The following definitions are useful to formally state the constraints represented by the IPC graph. Time is modelled as an integer that can be viewed as a multiple of a base clock.

**Definition 1:** The function  $start(v, k) \in Z^+$  (non-negative integer) represents the time at which the k th execution of the actor v starts in the self-timed schedule. The function  $end(v, k) \in Z^+$  represents the time at which the k th execution of the actor v ends, and v produces data tokens at its output edges. Since we are interested in the k th execution of each actor for k = 1, 2, 3, ..., we set start(v, k) = 0 and end(v, k) = 0 for  $k \le 0$  as the "initial conditions".

As per the semantics of a DFG, each edge  $(v_j, v_i)$  of  $G_{ipc}$  represents the following data dependency constraint:

$$start(v_i, k) \ge end(v_i, k - delay((v_i, v_i))), \forall (v_i, v_i) \in E_{ipc}, \forall k > delay(v_i, v_i). \tag{1}$$

This is because each actor consumes one token from each of its input edges when it fires. Since there are already delay(e) tokens on each incoming edge e of actor v, another k - delay(e) tokens must be produced on e before the kth execution of v can begin. Thus the actor src(e) must have completed its (k - delay(e)) th execution before v can begin its kth execution. The constraints in (1) are due both to IPC edges (representing synchronization between processors) and to edges that represent serialization of actors assigned to the same processor.

To model execution times of actors we associate execution time t(v) with each vertex of the IPC graph; t(v) assigns a positive integer execution time to each actor v (again, the actual execution time can be interpreted as t(v) cycles of a base clock), and t(v) includes the time taken to execute all IPC operations (sends and receives) that the actor v performs. Thus the IPC graph is  $G_{ipc} = (V, E_{ipc}, t)$ . Now, we can substitute

end

$$(v_i, k) = start(v_i, k) + t(v_i)$$

in (1) to obtain

$$start(v_i, k) \ge start(v_i, k-delay((v_i, v_i))) + t(v_i)$$

for each edge  $(v_i, v_i)$  in  $G_{ipc}$ . (2)

In the self-timed schedule, actors fire as soon as data is available at all their input edges.

Such an "as soon as possible" (ASAP) firing pattern implies:

$$start(v_i, k) = max \left( \left\{ s(v_j, k - delay((v_j, v_i))) + t(v_j) \middle| (v_j, v_i) \in E_{ipc} \right\} \right). \tag{3}$$

The IPC graph can also be looked upon as a Marked graph [24] or Reiter's computation graph [28]. The same properties hold for it, and we state some of the relevant properties here. Some of the proofs are omitted.

Lemma 1: [28] Every cycle C in the IPC graph has a path delay of at least one if and only if the static schedule it is constructed from is free of deadlock. That is, for each cycle C, Delay(C) > 0.

Lemma 2: The number of tokens in any cycle of the IPC graph is always conserved over all possible valid firings of actors in the graph, and is equal to the path delay of that cycle.

*Proof:* For each cycle C in the IPC graph, the number of tokens on C can only change when actors that are on it fire, because actors not on C remove and place tokens only on edges that are not part of C. If  $C = ((v_1, v_2), (v_2, v_3), ..., (v_{n-1}, v_n), (v_n, v_1))$ , and any actor  $v_k$   $(1 \le k \le n)$  fires, then in a valid firing exactly one token is moved from the edge  $(v_{k-1}, v_k)$  to the edge  $(v_k, v_{k+1})$ , where  $v_0 = v_n$  and  $v_{n+1} = v_1$ . This conserves the total number of tokens on C. QED.

Lemma 3: The asymptotic iteration period for a strongly connected IPC graph G when actors execute as soon as data is available at all inputs is given by [28]:

$$T = \max_{\text{cycle } C \text{ in } G} \left\{ \frac{\sum_{v \text{ is on } C} t(v)}{Delay(C)} \right\}. \tag{4}$$

Note that Delay(C) > 0 from Lemma 1.

The quotient in (4) is called the cycle mean of the cycle C. That is, the cycle mean of C is the sum of the execution times of all vertices on C divided by the path delay of C. The entire quantity on the RHS of (4) is called the "maximum cycle mean" of the strongly connected IPC graph G. If the IPC graph contains more than one SCC, then different SCCs may have different asymptotic iteration periods, depending on their individual maximum cycle means. In such a case, the iteration period of the overall graph (and hence the self-timed schedule) is the maximum over the maximum cycle means of all the SCCs of  $G_{ipc}$ . This is because the execution of the schedule is constrained by the slowest component in the system. Henceforth, we will use the following definition for the maximum cycle mean.

Definition 2: The maximum cycle mean of an IPC graph  $G_{ipc}$ , denoted by  $\lambda_{max}$ , is the maximal cycle mean over all strongly connected components of  $G_{ipc}$ : That is,

$$\lambda_{max} = \max_{\text{cycle } C \text{ in } G} \left\{ \frac{\sum_{v \text{ is on } C} t(v)}{Delay(C)} \right\}.$$

A fundamental cycle in  $G_{ipc}$  whose cycle mean is equal to  $\lambda_{max}$  is called a **critical cycle** of  $G_{ipc}$ . Thus the throughput of the system of processors executing a particular self-timed schedule is equal to the corresponding  $\frac{1}{\lambda_{max}}$  value.

For example, in Figure 4,  $G_{ipc}$  has one SCC, and its maximal cycle mean is 7 time units. This corresponds to the critical cycle ((B,E),(E,I),(I,G),(G,B)):t(B)=t(E)=3 time units, t(I)=t(G)=4 time units, so the total time along this cycle is 14 t.u., and there are two delays on this cycle. Thus the average iteration period for this schedule is 7 t.u. We have not included IPC costs in this calculation, but these can be included in a straightforward manner by adding the *send* and *receive* costs to the corresponding actors performing these operations.

The maximum cycle mean can be calculated in time  $O(|V||E_{ipc}|\log_2(|V|+D+T))$  [17]

by repeated applications of the Bellman-Ford shortest-path algorithm. Here, D and T are such that  $delay(e) \le D \ \forall e \in E_{ipc}$  and  $t(v) \le T \ \forall v \in V$ . If D and T are constants, the complexity of determining  $\lambda_{max}$  is simply  $O(|V||E_{ipc}|\log_2(|V|))$ .

#### 5.2 Execution Time Estimates

If we only have execution time estimates available instead of exact values, and we set t(v) in the previous section to be these estimated values, then we obtain the *estimated* iteration period by calculating  $\lambda_{max}$ . Henceforth we will assume that we know the **estimated throughput**  $\frac{1}{\lambda_{max}}$  calculated by setting the t(v) values to the available timing estimates.

In all the transformations that we present in the rest of the paper, we will preserve the estimated throughput by preserving the maximum cycle mean of  $G_{ipc}$ , with each t(v) set to the estimated execution time of v. In the absence of more precise timing information, this is the best we can hope to do.

### 5.3 Strongly Connected Components and Buffer Size Bounds

In dataflow semantics, the edges between actors represent infinite buffers. Accordingly, the edges of the IPC graph are potentially buffers of infinite size. However, from Lemma 2, every feedback edge (an edge that belongs to a strongly connected component, and hence to some cycle) can only have a finite number of tokens at any time during the execution of the IPC graph. We will call this constant the **self-timed buffer bound** of that edge, and for a feedback edge e we will represent this bound by  $B_{fb}\left(e\right)$ . Lemma 2 yields the following self-timed buffer bound:

$$B_{fb}(e) = min(\{Delay(C) | C \text{ is a cycle that contains } e\})$$

(5)

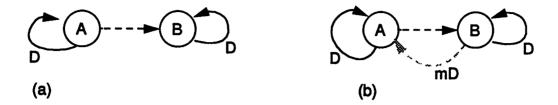

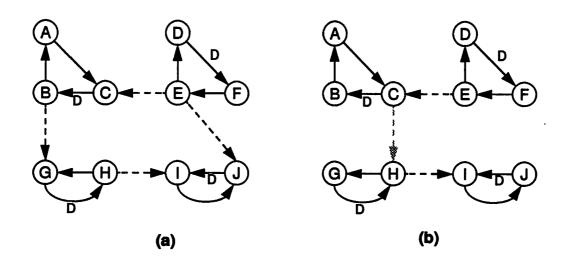

Feedforward edges have no such bound on buffer size; therefore for practical implementations we need to *impose* a bound on the sizes of these edges. For example, Figure 5(a) shows an

IPC graph where the IPC edge (A, B) could be unbounded when the execution time of A is less than that of B, for example. In practice, we need to bound the buffer size of such an edge; we will

Figure 5. An IPC graph with a feedforward edge: (a). original graph (b). imposing bounded buffers.

denote such an "imposed" bound for a feedforward edge e by  $B_{ff}(e)$ . Since the effect of placing such a restriction includes "artificially" constraining src(e) from getting more than  $B_{ff}(e)$  invocations ahead of snk(e), its effect on the estimated throughput can be modelled by adding the reverse edge  $d_m(snk(e), src(e))$ , where  $m = B_{ff}(e) - delay(e)$ , to  $G_{ipc}$  (grey edge in Figure 5(b)). Since the addition of this edge introduces a new cycle in  $G_{ipc}$ , it has the potential to reduce the estimated throughput; to prevent such a reduction,  $B_{ff}(e)$  must be chosen to be large enough so that the maximum cycle mean remains unchanged upon adding  $d_m(snk(e), src(e))$ .

Sizing buffers optimally such that the maximum cycle mean remains unchanged has been studied by Kung, Lewis and Lo in [15], where the authors propose an integer linear programming formulation of the problem, with the number of constraints equal to the number of fundamental cycles in the DFG (potentially an exponential number of constraints).

An efficient albeit suboptimal procedure to determine  $B_{ff}$  is to note that if

$$B_{ff}(e) \ge \left[ \left( \sum_{x \in V} t(x) \right) / \lambda_{max} \right]$$

holds for each feedforward edge e, then the maximum cycle mean of the resulting graph does not exceed  $\lambda_{max}$ .

Then, doing a binary search on  $B_{ff}(e)$  for each feedforward edge, and computing the

maximum cycle mean at each search step and ascertaining that it is less than  $\lambda_{max}$  results in a buffer assignment for the feedforward edges. Although this procedure is efficient, it is greedy (and suboptimal) because the order that the edges e are chosen is arbitrary and may effect the quality of the final solution.

However, as we will see in Section 10, imposing such a bound  $B_{ff}$  is a naive approach for bounding buffer sizes and, in terms of synchronization costs, there is a better technique for bounding buffers. Thus, in our final algorithm, we will not in fact find it necessary to use or compute these bounds  $B_{ff}$ .

#### 6. Synchronization Model

#### 6.1 Synchronization Protocols

We define two basic synchronization protocols for an IPC edge based on whether or not the length of the corresponding buffer is guaranteed to be bounded from the analysis presented in the previous section. Given an IPC graph G, and an IPC edge e in G, if the length of the corresponding buffer is not bounded — that is, if e is a feedforward edge of G — then we apply a synchronization protocol called **unbounded buffer synchronization** (UBS), which guarantees that (a) an invocation of snk(e) never attempts to read data from the buffer unless the buffer contains at least one token; and(b) an invocation of src(e) never attempts to write data into the buffer unless the number of tokens in the buffer is less than some pre-specified limit  $B_{ff}(e)$ , which is the amount of memory allocated to the buffer as discussed in subsection 5.3.

On the other hand, if the topology of the IPC graph guarantees that the buffer length for e is bounded by some value  $B_{fb}(e)$  (the self-timed buffer bound of e), then we use a simpler protocol, called **bounded buffer synchronization (BBS)**, that only explicitly ensures (a) above. Below, we outline the mechanics of the two synchronization protocols that we have defined.

BBS. In this mechanism, a write pointer wr (e) for e is maintained on the processor that

executes src(e); a  $read\ pointer\ rd(e)$  for e is maintained on the processor that executes snk(e); and a copy of wr(e) is maintained in some shared memory location sv(e). The pointers rd(e) and wr(e) are initialized to zero and delay(e), respectively. Just after each execution of src(e), the new data value produced onto e is written into the shared memory buffer for e at offset wr(e); wr(e) is updated by the following operation —  $wr(e) \leftarrow (wr(e) + 1) \mod B_{fb}(e)$ ; and sv(e) is updated to contain the new value of wr(e). Just before each execution of snk(e), the value contained in sv(e) is repeatedly examined until it is found to be  $not\ equal\ to\ rd(e)$ ; then the data value residing at offset rd(e) of the shared memory buffer for e is read; and rd(e) is updated by the operation  $rd(e) \leftarrow (rd(e) + 1) \mod B_{fb}(e)$ .

UBS. This mechanism also uses the read/write pointers rd(e) and wr(e), and these are initialized the same way; however, rather than maintaining a copy of wr(e) in the shared memory location sv(e), we maintain a count (initialized to delay(e)) of the number of unread tokens that currently reside in the buffer. Just after src(e) executes, sv(e) is repeatedly examined until its value is found to be less than  $B_{ff}(e)$ ; then the new data value produced onto e is written into the shared memory buffer for e at offset wr(e); wr(e) is updated as in BBS (except that the new value is not written to shared memory); and the count in sv(e) is incremented. Just before each execution of snk(e), the value contained in sv(e) is repeatedly examined until it is found to be nonzero; then the data value residing at offset rd(e) of the shared memory buffer for e is read; the count in sv(e) is decremented; and rd(e) is updated as in BBS.

Note that we are assuming that there is enough shared memory to hold a separate buffer of size  $B_{ff}(e)$  for each feedforward IPC edge e of  $G_{ipc}$ , and a separate buffer of size  $B_{fb}(e)$  for each feedback IPC edge e. When this assumption does not hold, smaller bounds on some of the buffers must be imposed, possibly for feedback edges as well as for feedforward edges, and in general, this may require some sacrifice in estimated throughput. Note that whenever a buffer

bound smaller than  $B_{fb}(e)$  is imposed on a feedback edge e, then a protocol identical to UBS must be used. The problem of optimally choosing which edges should be subject to stricter buffer bounds when there is a shortage of shared memory, and the selection of these stricter bounds is an interesting area for further investigation.

#### 6.2 The Synchronization Graph $G_s = (V, E_s)$

An IPC edge in  $G_{ipc}$  represents two functions: 1) reading and writing of data values into the buffer represented by that edge; and 2) synchronization between the sender and the receiver, which could be implemented with the UBS protocol or with the BBS protocol. We find it useful to differentiate these two functions by creating another graph called the synchronization graph  $(G_s)$ , in which edges between actors assigned to different processors, called synchronization edges, represent synchronization constraints only. Recall from Subsection 5.1 that an IPC edge  $(v_j, v_i)$  of  $G_{ipc}$  represents the synchronization constraint:

$$start(v_i, k) \ge end(v_j, k - delay((v_j, v_i))) \ \forall k > delay(v_j, v_i).$$

(6)

Thus, before we perform any optimization on synchronizations, the synchronization graph is identical to the IPC graph, because every IPC edge represents a synchronization point. However, we will modify the synchronization graph in certain "valid" ways (which will be defined shortly) by adding some edges and deleting some others. Thus, at the end of our optimizations, the synchronization graph may look very different from the IPC graph: it is of the form  $(V, (E_{ipc} - F + F'))$ , where F is the set of edges deleted from the IPC graph and F' is the set of edges added to it. At this point the IPC edges in  $G_{ipc}$  represent buffer activity, and must be implemented as buffers in shared memory, whereas the synchronization edges represent synchronization constraints, and are implemented using the UBS and BBS protocols introduced in the previous section. If there is an IPC edge as well as a synchronization edge between the same pair of actors, then the synchronization protocol is executed before the buffers corresponding to the IPC edge are accessed so as to ensure sender-receiver synchronization. On the other hand, if there is an IPC edge between two actors in the IPC graph, but there is no synchronization edge between

the two, then no synchronization needs to be done before accessing the shared buffer. If there is a synchronization edge between two actors but no IPC edge, then no shared buffer is allocated between the two actors; only the corresponding synchronization protocol is invoked.

Thus, initially, the synchronization graph  $G_s$  is identical to  $G_{ipc}$ . Then we perform transformations on the synchronization graph in order to reduce synchronization costs. The cost measure and the transformations will be discussed in the following sections of this paper. All of these transformations must respect the synchronization constraints implied by  $G_{ipc}$ . If we ensure this, then we only need to implement the synchronization edges of the optimized synchronization graph. The following theorem is useful to formalize the concept of when the synchronization constraints represented by one synchronization graph  $G_1$  imply the synchronization constraints of another graph  $G_2$ . This theorem provides a useful constraint for synchronization optimization, and it underlies the validity of the main techniques that we will present in this paper.

Theorem 1: The synchronization constraints in a synchronization graph  $G_1 = (V, E_1)$  imply the synchronization constraints of the synchronization graph  $G_2 = (V, E_2)$  if the following condition holds:  $\forall \varepsilon \in E_2, \varepsilon \notin E_1, \rho_{G_1}(src(\varepsilon), snk(\varepsilon)) \leq delay(\varepsilon)$ , that is, if for each edge  $\varepsilon$  that is present in  $G_2$  but not in  $G_1$  there is a minimum delay path from  $src(\varepsilon)$  to  $snk(\varepsilon)$  in  $G_1$  that has total delay of at most  $delay(\varepsilon)$  (number of delays on edge  $\varepsilon$ ).

(Note that since the vertex sets for the two graphs are identical, it is meaningful to refer to src ( $\varepsilon$ ) and snk ( $\varepsilon$ ) as being vertices of  $G_1$  even though  $\varepsilon \in E_2$ ,  $\varepsilon \notin E_1$ .)

First we prove the following lemma.

**Lemma 4:** If there is a path  $p = (e_1, e_2, e_3, ..., e_n)$  in  $G_1$ , then

$$start(snk(e_n), k) \ge end(src(e_1), k - Delay(p))$$

.

Proof of Lemma 4:

The following constraints hold along such a path p (as per (6))

$$start(snk(e_1), k) \ge end(src(e_1), k - delay(e_1)).$$

(7)

Similarly,

$$start(snk(e_2), k) \ge end(src(e_2), k - delay(e_2))$$

.

Noting that  $src(e_2)$  is the same as  $snk(e_1)$ , we get

$$start(snk(e_2), k) \ge end(snk(e_1), k - delay(e_2))$$

.

Causality implies end  $(v, k) \ge start(v, k)$ , so we get

$$start(snk(e_2), k) \ge start(snk(e_1), k - delay(e_2))$$

. (8)

Substituting (7) in (8),

$$start(snk(e_2), k) \ge end(src(e_1), k - delay(e_2) - delay(e_1))$$

.

Continuing along p in this manner, it can easily be verified that

$$start(snk(e_n), k) \ge end(src(e_1), k - delay(e_n) - delay(e_{n-1}) - \dots - delay(e_1));$$

that is,

$$start((snk(e_n), k) \ge end(src(e_1), k - Delay(p))) . QED.$$

Proof of Theorem 1: If  $\varepsilon \in E_2$ ,  $\varepsilon \in E_1$ , then the synchronization constraint due to the edge  $\varepsilon$  holds in both graphs. But for each  $\varepsilon \in E_2$ ,  $\varepsilon \notin E_1$  we need to show that the constraint due to  $\varepsilon$ :

$$start(snk(\epsilon), k) > end(src(\epsilon), k - delay(\epsilon))$$

(9)

holds in  $G_1$  provided  $\rho_{G_1}(src(\epsilon), snk(\epsilon)) \le delay(\epsilon)$ , which implies there is at least one path  $p = (e_1, e_2, e_3, ..., e_n)$  from  $src(\epsilon)$  to  $snk(\epsilon)$  in  $G_1(src(e_1) = src(\epsilon))$  and  $snk(e_n) = snk(\epsilon)$  such that  $Delay(p) \le delay(\epsilon)$ .

From Lemma 4, existence of such a path p implies

$$start((snk(e_n), k) \ge end(src(e_1), k - Delay(p)))$$

.

that is.

$$start((snk(\epsilon), k) \ge end(src(\epsilon), k - Delay(p)))$$

(10)

If  $Delay(p) \le delay(\varepsilon)$ , then  $end(src(\varepsilon), k - Delay(p)) \ge end(src(\varepsilon), k - delay(\varepsilon))$ . Substituting this in (10) we get

$$start((snk(\epsilon), k) \ge end(src(\epsilon), k - delay(\epsilon)))$$

.

The above relation is identical to (9), and this proves the Theorem. QED.

The above theorem motivates the following definition.

**Definition 3:** If  $G_1 = (V, E_1)$  and  $G_2 = (V, E_2)$  are synchronization graphs with the same vertex-set, we say that  $G_1$  preserves  $G_2$  if  $\forall \epsilon \in E_2$ ,  $\epsilon \notin E_1$ , we have  $\rho_{G_1}(src(\epsilon), snk(\epsilon)) \leq delay(\epsilon)$ .

Thus, Theorem 1 states that the synchronization constraints of  $(V, E_1)$  imply the synchronization constraints of  $(V, E_2)$  if  $(V, E_1)$  preserves  $(V, E_2)$ .

Observation 1: Given an IPC graph  $G_{ipc}$ , and a synchronization graph  $G_s$  such that  $G_s$  preserves  $G_{ipc}$ , suppose that we implement the synchronizations corresponding to the synchronization edges of  $G_s$ . Then, the iteration period of the resulting system is determined by the maximum cycle mean of  $G_s$ . This is because the synchronization edges alone determine the interaction between processors; an IPC edge without synchronization does not constrain the execution of the corresponding processors in any way.

#### 6.3 Computing Buffer Bounds from $G_s$ and $G_{ipc}$

After all the optimizations are complete we have a final synchronization graph.  $G_s = (V, (E_{ipc} - F + F'))$  that preserves  $G_{ipc}$ . Since the synchronization edges in  $G_s$  are the ones that are finally implemented, it is advantageous to calculate the self-timed buffer bound  $B_{fb}$

as a final step after all the transformations on  $G_s$  are complete, instead of using  $G_{ipc}$  itself to calculate these bounds. This is because addition of the edges F' may reduce these buffer bounds. It is easily verified that removal of the edges (F) cannot change the buffer bounds in (5) as long as the synchronizations in  $G_{ipc}$  are preserved. Thus, in the interest of obtaining minimum possible shared buffer sizes, we compute the bounds using the optimized synchronization graph. The following theorem tells us how to compute the self-timed buffer bounds from  $G_s$ .

**Theorem 2:** If  $G_s$  preserves  $G_{ipc}$  and the synchronization edges in  $G_s$  are implemented, then for each feedback IPC edge e in  $G_{ipc}$ , the self-timed buffer bound of e ( $B_{fb}(e)$ ) — an upper bound on the number of data tokens that can ever be present on e — is given by:

$$B_{fb}(e) = \rho_{G_s}(snk(e), src(e)) + delay(e)$$

,

Proof: By Lemma 4, if there is a path p from snk(e) to src(e) in  $G_s$ , then  $start(src(e), k) \ge end(snk(e), k - Delay(p))$ .

Taking p to be an arbitrary minimum-delay path from snk(e) to src(e) in  $G_s$ , we get  $start(src(e), k) \ge end(snk(e), k - \rho_{G_s}(snk(e), src(e)))$ .

That is, src(e) cannot be more that  $\rho_{G_s}(snk(e),src(e))$  iterations "ahead" of snk(e). Thus there can never be more that  $\rho_{G_s}(snk(e),src(e))$  tokens more than the initial number of tokens on e - delay(e). Since the initial number of tokens on e was delay(e), the size of the buffer corresponding to e is bounded above by  $B_{fb}(e) = \rho_{G_s}(snk(e),src(e)) + delay(e)$ . QED.

The quantities  $\rho_{G_s}(snk(e), src(e))$  can be computed using Dijkstra's algorithm [7] to solve the all-pairs shortest path problem on the synchronization graph in time  $O(|V|^3)$ . Thus the problem of determining the  $B_{fb}(e)$  values has complexity at most cubic in the size of the number

of actors in the schedule.

#### 7. Problem Statement

We refer to each access of the shared memory "synchronization variable"  $sv\left(e\right)$  by  $src\left(e\right)$  and  $snk\left(e\right)$  as a synchronization access to shared memory. If synchronization for e is implemented using UBS, then we see that on average, 4 synchronization accesses are required for e in each iteration period, while BBS implies 2 synchronization accesses per iteration period. We define the synchronization cost of a synchronization graph  $G_s$  to be the average number of synchronization accesses required per iteration period. Thus, if  $n_{ff}$  denotes the number of synchronization edges in  $G_s$  that are feedforward edges, and  $n_{fb}$  denotes the number of synchronization edges that are feedback edges, then the synchronization cost of  $G_s$  can be expressed as  $(4n_{ff}+2n_{fb})$ . In the remainder of this paper we will develop techniques that apply the results and the analysis framework developed in Sections 4-6 to minimize the synchronization cost of a self-timed implementation of a DFG without sacrificing the integrity of any inter-processor data transfer or reducing the estimated throughput.

We will explore three mechanisms for reducing synchronization accesses. The first is the detection and removal of *redundant* synchronization edges, which are synchronization edges whose respective synchronization functions are subsumed by other synchronization edges, and thus need not be implemented explicitly. The second mechanism is the insertion of new synchronization edges in such a way that the number of original synchronization edges that become redundant exceeds the number of new edges added. This mechanism, which we call *resynchroni*-

<sup>1.</sup> Note that in our measure of the number of shared memory accesses required for synchronization, we neglect the accesses to shared memory that are performed while the sink actor is waiting for the required data to become available, or the source actor is waiting for an "empty slot" in the buffer. The number of accesses required to perform these "busy-wait" or "spin-lock" operations is dependent on the exact relative execution times of the actor invocations. Since in our problem context, this information is not generally available to us, we use the *best case* number of accesses — the number of shared memory accesses required for synchronization assuming that IPC data on an edge is always produced before the corresponding sink invocation attempts to execute — as an approximation.

zation, is explored in sections 9 and in the appendix. Finally, in Section 10, we examine the utility of adding additional synchronization edges to convert a synchronization graph that is not strongly connected into a strongly connected graph. Such a conversion allows us to implement all synchronization edges with BBS. We address optimization criteria in performing such a conversion, and we will show that the extra synchronization accesses required for such a conversion are always (at least) compensated by the number of synchronization accesses that are saved (by the UBSs that get converted to BBSs).

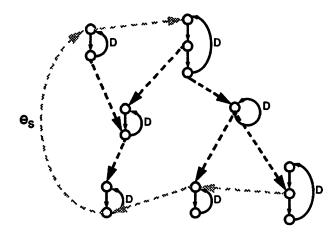

### 8. Removing Redundant Synchronizations

The first technique that we explore for reducing synchronization overhead is the removal of redundant synchronization edges of the synchronization graph. Formally, a synchronization edge is redundant in a synchronization graph G if its removal yields a synchronization graph that preserves G. Equivalently, from definition 3, a synchronization edge e is redundant in the synchronization graph G if there is a path  $p \neq (e)$  in G directed from src(e) to snk(e) such that  $Delay(p) \leq delay(e)$ .

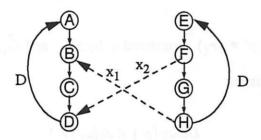

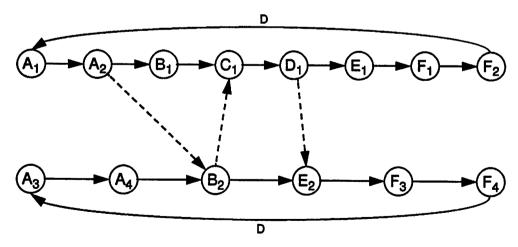

Thus, the synchronization function associated with a redundant synchronization edge "comes for free" as a by product of other synchronizations. Figure 6 shows an example of a redundant synchronization edge. Here, before executing actor D, the processor that executes

Figure 6. An example of a redundant synchronization edge.

$\{A,B,C,D\}$  does not need to synchronize with the processor that executes  $\{E,F,G,H\}$  because due to the synchronization edge  $x_1$ , the corresponding invocation of F is guaranteed to complete before each invocation of D is begun. Thus,  $x_2$  is redundant in Figure 6. It is easily verified that the path  $p=((F,G),(G,H),x_1,(B,C),(C,D))$  is directed from  $src(x_2)$  to  $snk(x_2)$ , and has a path delay (zero) that is equal to the delay on  $x_2$ .

In this section we develop an efficient algorithm to optimally remove redundant synchronization edges from a synchronization graph.

#### 8.1 The Independence of Redundant Synchronizations

The following theorem establishes that the order in which we remove redundant synchronization edges is not important, and thus, we need not implement synchronization for any of the redundant synchronization edges in a synchronization graph.

**Theorem 3:** Suppose that  $G_s = (V, E)$  is a synchronization graph,  $e_1$  and  $e_2$  are distinct redundant synchronization edges in  $G_s$ , and  $\tilde{G}_s = \left(V, E - \{e_1\}\right)$ . Then  $e_2$  is redundant in  $\tilde{G}_s$ .

*Proof:* Since  $e_2$  is redundant in  $G_s$ , there is a path  $p \neq (e_2)$  in  $G_s$  directed from  $src(e_2)$  to  $snk(e_2)$  such that

$$Delay(p) \le delay(e_2). \tag{11}$$

Similarly, there is a path  $p' \neq (e_1)$ , contained in both  $G_s$  and  $\tilde{G}_s$ , that is directed from  $src\ (e_1)$  to  $snk\ (e_1)$ , and that satisfies

$$Delay(p') \le delay(e_1). \tag{12}$$

Now, if p does not contain  $e_1$ , then p exists in  $\tilde{G}_s$ , and we are done. Otherwise, let  $p' = (x_1, x_2, ..., x_n) \text{ ; observe that } p \text{ is of the form}$   $p = (y_1, y_2, ..., y_{k-1}, e_1, y_k, y_{k+1}, ..., y_m) \text{ ; and define}$   $p'' \equiv (y_1, y_2, ..., y_{k-1}, x_1, x_2, ..., x_n, y_k, y_{k+1}, ..., y_m) \text{ .}$   $\text{Clearly, } p'' \text{ is a path from } src(e_2) \text{ to } snk(e_2) \text{ in } \tilde{G}_s \text{. Also,}$   $Delay(p'') = \sum delay(x_i) + \sum delay(y_i)$   $= Delay(p') + (Delay(p) - delay(e_1))$   $\leq Delay(p) \qquad \text{ (from (12))}$   $\leq delay(e_2) \qquad \text{ (from (11)). } QED.$

Theorem 3 tells us that we can avoid implementing synchronization for *all* redundant synchronization edges since the "redundancies" are not interdependent. Thus, an optimal removal of redundant synchronizations can be obtained by applying a straightforward algorithm that successively tests the synchronization edges for redundancy in some arbitrary sequence, and since *shortest path* computation is a tractable problem, we can expect such a solution to be practical.

### 8.2 An Algorithm for Removing Redundant Synchronizations

Figure 7 presents an efficient algorithm, based on the ideas presented in the previous subsection, for optimal removal of redundant synchronization edges. In this algorithm, we first compute the path delay of a minimum-delay path from x to y for each ordered pair of vertices (x, y); here, we assign a path delay of  $\infty$  whenever there is no path from x to y. This computation is equivalent to solving an instance of the well known all points shortest paths problem [7]. Then, we examine each synchronization edge e in some arbitrary sequence — and determine whether or not there is a path from src(e) to snk(e) that does not contain e, and that has a path delay that does not exceed delay(e). Now, at first, it may not be obvious that this check for redun-

dancy is equivalent to the check that is performed by the if statement in RemoveRedundantSynchs: one might ask "What if  $e_0$  satisfies the inequality in the if statement, but all of the minimumdelay paths from  $snk(e_0)$  to snk(e) contain e?" To see that the if statement is indeed equivalent to checking the redundancy of e, observe that if p is a path from src(e) to snk(e) that contains more than one edge and that contains e, then p must contain a cycle c such that c does not contain e; and since all cycles (from Lemma 1) must have positive path delay, the path delay of such a path p must exceed delay(e). Thus, if  $e_0$  satisfies the inequality in the if statement of RemoveRedundantSynchs, and  $p^*$  is a path from  $snk(e_0)$  to snk(e) such that

Delay  $(p^*) = \rho(snk(e_0), snk(e))$ , then  $p^*$  cannot contain e.

```

Function RemoveRedundantSynchs

```

**Input**: A synchronization graph  $G_s = (V, E)$  such that  $I \subseteq E$  is the set of synchronization edges.

Output: The synchronization graph  $G_s^* = (V, (E - E_r))$ , where  $E_r$  is the set of redundant synchronization edges in  $G_{\epsilon}$ .

```

1. Compute \rho(x, y) for each ordered pair of vertices in G_x.

2. Initialize: E_r = \emptyset.

3. For each e \in I

For each output edge e_a of src(e) except for e

If delay(e_0) + \rho(snk(e_0), snk(e)) \le delay(e)

Then

E_r = E_r \cup \{e\}

/* exit the innermost enclosing For loop */

Break

End If

End For

End For

4. Return (V, (E - E_x)).

```

Figure 7. An algorithm that optimally removes redundant synchronization edges.

From the definition of a redundant synchronization edge, it is easily verified that the removal of a redundant synchronization edge does not alter any of the minimum-delay path values (path delays). That is, given a redundant synchronization edge  $e_r$  in  $G_s$ , and two arbitrary vertices  $x, y \in V$ , if we let  $\hat{G}_s = \left(V, \left(E - \{e_r\}\right)\right)$ , then  $\rho_{\hat{G}_s}(x, y) = \rho_{G_s}(x, y)$ . Thus, none of the minimum-delay path values computed in Step 1 need to be recalculated after removing a redundant synchronization edge in Step 3.

Observe that the complexity of Function RemoveRedundantSynchs is dominated by Step 1 and Step 3. Since all edge delays are non-negative, we can repeatedly apply Dijkstra's algorithm (once for each vertex) to carry out Step 1 in  $O(|V|^3)$  time; a modification of Dijkstra's algorithm can be used to reduce the complexity of Step 1 to  $O(|V|^2\log_2(|V|) + |V||E|)$  [7]. In Step 3, |E| is an upper bound for the number of synchronization edges, and in the worst case, each vertex has all members of V in its set of successors. Thus, the time complexity of Step 3 is O(|V||E|), and if we use the modification to Dijkstra's algorithm mentioned above for Step 1, then the time complexity of RemoveRedundantSynchs is

$$O(|V|^2\log_2(|V|) + |V||E| + |V||E|) = O(|V|^2\log_2(|V|) + |V||E|).$$

# 8.3 Comparison with Shaffer's Approach

In [30], Shaffer presents an algorithm that minimizes the number of directed synchronizations in the self-timed execution of a dataflow graph under the (implicit) assumption that the execution of successive iterations of the dataflow graph are not allowed to overlap. In Shaffer's technique, a construction identical to our synchronization graph is used with the exception that there is no feedback edge that connects the last actor executed on a processor to the first actor executed on the same processor. Also, in Shaffer's construction, edges that have delay are ignored since only dependences within the same graph iteration are significant. Thus, Shaffer's synchronization graph can be assumed to be acyclic.

In the context of Shaffer's problem, a synchronization edge is redundant if and only if

there is a path from the source of the edge to the sink — here we only need "reachability" information; no notion of path delay is required. As in the context of our problem, the removal of a redundant synchronization edge in Shaffer's synchronization graph cannot negate the redundancy of another redundant synchronization edge, and consequently, the order in which synchronization edges are tested for redundancy is not significant. Shaffer's algorithm begins by computing a boolean value r(x, y) for each ordered pair of vertices (x, y) that is set to true if and only if there is a path directed from x to y. Then, the algorithm proceeds in a manner equivalent to Step 3 of RemoveRedundantSynchs, with the exception that the predicate of the if statement is changed from  $(delay(e_o) + p(snk(e_o), snk(e)) \le delay(e))$  to  $(r(snk(e_o), snk(e)))$ . Thus, RemoveRedundantSynchs can be viewed as a direct extension of Shaffer's algorithm to handle pure self-timed, iterative execution of a DFG; Shaffer's algorithm accounts for self-timed execution only within a graph iteration, and in general, it can be applied to iterative dataflow programs only if all processors are forced to synchronize between graph iterations.

Shaffer states that the complexity of his algorithm is  $O(|V|^3)$ ; however, the complexity can be improved (at least for sparse graphs) by using a more efficient technique to compute the function r. The function r in Shaffer's method can be computed in O(|V||E|) time [7], and using this method, Shaffer's algorithm achieves a time complexity of O(|V||E|). Thus, in exchange for its dependence on a less flexible execution model, Shaffer's solution, with appropriate choice of r, attains a slightly more favorable asymptotic complexity than our RemoveRedundantSynchs.

# 8.4 An Example

In this subsection, we illustrate the benefits of removing redundant synchronizations through a practical example. Figure 8(a) shows an abstraction of a three channel, multi-resolution quadrature mirror (QMF) filter bank, which has applications in signal compression [34]. This representation is based on the general (not homogeneous) SDF model, and accordingly, each edge is annotated with the number of tokens produced and consumed by its source and sink actors. For

Figure 8. (a). A multi-resolution QMF filter bank used to illustrate the benefits of removing redundant synchronizations. (b). The precedence graph for (a). (c). A self-timed, two-processor, parallel schedule for (a). (d). The initial synchronization graph for (c).

clarity, the actors are drawn as boxes, rather than circles. Actors A and F represent the subsystems that, respectively, supply and consume data to/from the filter bank system; B and C each represents a parallel combination of decimating high and low pass FIR analysis filters; D and E represent the corresponding pairs of interpolating synthesis filters. The amount of delay on the edge directed from B to E is equal to the sum of the filter orders of C and D. For more details on the application represented by Figure 8(a), we refer the reader to [34].

To construct a periodic, parallel schedule we must first determine the number of times  $\mathbf{q}(N)$  that each actor N must be invoked in the periodic schedule. Systematic techniques to compute these values are presented in [18]. Next, we must determine the precedence relationships between the actor invocations. In determining the exact precedence relationships, we must take into account the dependence of a given filter invocation on not only the invocation that produces the token that is "consumed" by the filter, but also on the invocations that produce the n preceding tokens, where n is the order of the filter. Such dependence can easily be evaluated with an additional dataflow parameter on each actor input that specifies the number of past tokens that are accessed  $[27]^1$ . Using this information, together with the invocation counts specified by  $\mathbf{q}$ , we obtain the precedence relationships specified by the graph of Figure 8(b), in which the ith invocation of actor N is labeled  $N_i$ , and each edge e specifies that invocation snk(e) requires data produced by invocation snc(e) snc(e)

A self-timed schedule for Figure 8(b) that can be obtained from Hu's well-known list scheduling method [11] is specified in Figure 8(c), and the synchronization graph that corresponds to the IPC graph of Figure 8(b) and Figure 8(c) is shown in Figure 8(d). All of the dashed edges in Figure 8(d) are synchronization edges. If we apply Shaffer's method, which considers only those synchronization edges that do not have delay, we can eliminate the need for explicit

<sup>1.</sup> It should be noted that some SDF-based design environments choose to forego parallelization across multiple invocations of an actor in favor of simplified code generation and scheduling. For example, in the GRAPE system, this restriction has been justified on the grounds that it simplifies inter-processor data management, reduces code duplication, and allows the derivation of efficient scheduling algorithms that operate directly on general SDF graphs without requiring the use of the acyclic precedence graph (APG) [3].

synchronization along only one of the 8 synchronization edges — edge  $(A_1, B_2)$ . In contrast, if we apply RemoveRedundantSynchs, we can detect the redundancy of  $(A_1, B_2)$  as well as four additional redundant synchronization edges —  $(A_3, B_1)$ ,  $(A_4, B_1)$ ,  $(B_2, E_1)$ , and  $(B_1, E_2)$ . Thus, RemoveRedundantSynchs reduces the number of synchronizations from 8 down to 3 — a reduction of 62%. Figure 9 shows the synchronization graph of Figure 8 (d) after all redundant synchronization edges are removed. It is easily verified that the synchronization edges that remain in this graph are not redundant; explicit synchronizations need only be implemented for these edges.

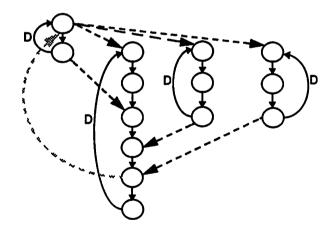

## 9. Resynchronization

It is sometimes possible to reduce the total number of irredundant synchronization edges by adding new synchronization edges to a synchronization graph. We refer to the process of adding one or more new synchronization edges and removing the redundant edges that result as resynchronization (defined more precisely below). Figure 10(a) illustrates this concept. Here, the dashed edges represent synchronization edges. Observe that if we insert the new synchronization

Figure 9. The synchronization graph of Figure 8(d) after all redundant synchronization edges are removed.

edge  $d_0(C, H)$ , then two of the original synchronization edges — (B, G) and (E, J) — become redundant. Since redundant synchronization edges can be removed from the synchronization graph to yield an equivalent synchronization graph, we see that the net effect of adding the synchronization edge  $d_0(C, H)$  is to reduce the number of synchronization edges that need to be implemented by 1. In Figure 10(b), we show the synchronization graph that results from inserting the resynchronization edge  $d_0(C, H)$  into Figure 10(a), and then removing the redundant synchronization edges that result.

Definition 4 gives a formal definition of resynchronization that we will use throughout the remainder of this paper. This considers resynchronization only "across" feedforward edges. Resynchronization that includes inserting edges into the SCCs is also possible; however, for our objectives, it must be verified that each new synchronization edge introduced in an SCC does not decrease the estimated throughput. To avoid this complication, which requires a check of significant complexity  $(O(|V||E|\log_2(|V|)))$ , where (V, E) is the modified synchronization graph—this is using the Bellman Ford algorithm described in [17]) for each candidate resynchronization edge, we focus only on feedforward resynchronization in this paper.

Figure 10. An example of resynchronization.

Definition 4: Given a synchronization graph G = (V, E) consisting of feedforward edges  $F \equiv \{e_1, e_2, ..., e_n\}$ , a resynchronization of G is a finite set  $F' \equiv \{e_1', e_2', ..., e_{m'}\}$  of edges that are not necessarily contained in E, but whose source and sink vertices are in V, such that (a).  $e_1', e_2', ..., e_{m'}$  are feedforward edges in the DFG  $G^* \equiv (V, ((E-F)+F'))$ ; and (b).  $G^*$  preserves G — that is,  $\rho_{G^*}(src(e_i), snk(e_i)) \leq delay(e_i)$  for all  $i \in \{1, 2, ..., n\}$ .

If we let G denote the graph in Figure 10, then the set of feedforward edges is  $F = \{(B, G), (E, J)\}; F' = \{d_0(C, H)\}$  is a resynchronization of G; Figure 10(b) shows the DFG  $G^* = (V, ((E - F) + F'))$ ; and from Figure 10(b), it is easily verified that F, F', and  $G^*$  satisfy conditions (a) and (b) of Definition 4.

We refer to the problem of finding a resynchronization with the fewest number of elements as the **resynchronization problem**. In the appendix, we formally show that the resynchronization problem is NP-hard, and in this section, we explain the intuition behind this result. To establish the NP-hardness of the resynchronization problem, we examine a special case of the problem that occurs when there are exactly two SCCs, which we call the **pairwise resynchronization problem**, and we derive a polynomial-time reduction from the classic set covering problem [7], a well-known NP-hard problem, to the pairwise resynchronization problem. In the set covering problem, one is given a finite set X and a family T of subsets of X, and asked to find a minimal (fewest number of members) subfamily  $T_s \subseteq T$  such that  $\bigcup_{t \in T_s} t = X$ . A subfamily of T is said to cover X if each member of X is contained in some member of the subfamily. Thus, the

Although the correspondence that we establish between the resynchronization problem and set covering shows that the resynchronization problem probably cannot be attacked optimally with a polynomial-time algorithm, we will show that the correspondence allows any heuristic for set covering to be adapted easily into a heuristic for the pairwise resynchronization problem, and

set covering problem is the problem of finding a minimal cover.

applying such a heuristic to each pair of SCCs in a general synchronization graph yields a heuristic for the general (not just pairwise) resynchronization problem. This is fortunate since the set covering problem has been studied in great depth, and efficient heuristic methods have been devised [7].

The following definition facilitates the developments of this section and the appendix.

**Definition 5:** Given a synchronization graph G, let  $(x_1, x_2)$  and  $(y_1, y_2)$  be two ordered pairs of vertices in G. We say that  $(y_1, y_2)$  subsumes  $(x_1, x_2)$  in G if  $\rho(x_1, y_1) = \rho(y_2, x_2) = 0$ . We may omit the qualification "in G" if the graph in question is understood from context.