# Copyright © 1995, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# CIRCUIT SIMULATION FOR VLSI AND ELECTRONIC PACKAGING DESIGN

by

Shen Lin

Memorandum No. UCB/ERL M95/80

13 October 1995

# CIRCUIT SIMULATION FOR VLSI AND ELECTRONIC PACKAGING DESIGN

by

Shen Lin

Memorandum No. UCB/ERL M95/80

13 October 1995

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720 To my parents and Chiang-Chiang.

# Acknowledgments

I am most indebted to my research advisor, Prof. Ernest Kuh, for introducing me to an amazing *CAD* world and for being a consistent source of guidance, support, and encouragement. His guidance and help have made my Ph.D. program a smooth and enjoyable one. I also would like to thank him for cultivating my ability to make clear presentations, both oral and written.

Several other professors have contributed graciously their time on my behalf, and I would like to express my gratitude. I would like to thank Professor Robert Brayton and Professor Kobayashi for their careful reading of this dissertation, and Professor Donald Pederson for serving on my qualifying committee.

I would like to express my appreciation particularly to Prof. M. Marek-Sadowska for her support and encouragement. I have benefited from numerous enlightening discussions with her, which kept my work on track.

I gratefully acknowledge crucial contributions to this project from a special friend of mine Jyh-Shing Jang and from other members in Prof. Kuh's group. They are: Narasimha Bhat, Kamal Chaudhary, Michael Jackson, Massoud Pedram, Arvind Srinivasan, Minshine Shih, Ren-Song Tsay, and Deborah Wang. I also want to thank Jaijeet Roychowdhury for helping me prepare several experimental results and giving me important suggestions.

This work was performed while the author was supported by NSF under Grant 88-03711, and SRC under Grant 91-DC-008, and MICRO. To each of these institutions and to the many others that have provided assistance I am grateful and express my thanks.

# **Contents**

| List of Figures |       |                                                               | v  |

|-----------------|-------|---------------------------------------------------------------|----|

| Li              | st of | Tables                                                        | vi |

| 1               | Intr  | roduction                                                     | 1  |

|                 | 1.1   | The Circuit Simulation Problem                                | 1  |

|                 | 1.2   | Motivation and Goals                                          | 3  |

|                 | 1.3   | Contribution                                                  | 4  |

|                 | 1.4   | Organization                                                  | 6  |

| 2               | Bac   | kground and Review of Previous Work.                          | 8  |

|                 | 2.1   | The Direct Approach of SPICE2                                 | 8  |

|                 |       | 2.1.1 Linear Multistep Numerical Integration                  | 8  |

|                 |       | 2.1.2 Properties of Numerical Integration                     | 10 |

|                 | 2.2   | Work on Improving Efficiency                                  | 15 |

|                 |       | 2.2.1 Simplify the Numerical Algorithms                       | 16 |

|                 |       | 2.2.2 Simplify the Device Models                              | 20 |

|                 | 2.3   | Previous Lossy Interconnect Simulation Work                   | 26 |

| 3               | Ste   | pwise Equivalent Conductance Circuit Simulation.              | 30 |

|                 | 3.1   | Equivalent Linear Time-Varying Circuit Transformation         | 31 |

|                 |       | 3.1.1 Circuit Equations                                       | 31 |

|                 |       | 3.1.2 Exactness of the Transformation                         | 33 |

|                 | 3.2   | The Stepwise Equivalent Conductance Integration Algorithm     | 35 |

|                 | 3.3   | Time Step Selection                                           | 36 |

| 4               | sw    | EC: A Stepwise Equivalent Conductance CMOS Circuit Simulator. | 38 |

|                 | 4.1   | Introduction                                                  | 39 |

|                 | 4.2   | MOS Electrical Models and Time Step Selection of SWEC         | 41 |

|                 | 4.3   | Piecewise Linear Approximation of Waveforms                   | 43 |

|                 | 4.4   | The Event-Driven approach of SWEC                             | 46 |

|                 | 4.5   | Experimental Results for SWEC                                 | 49 |

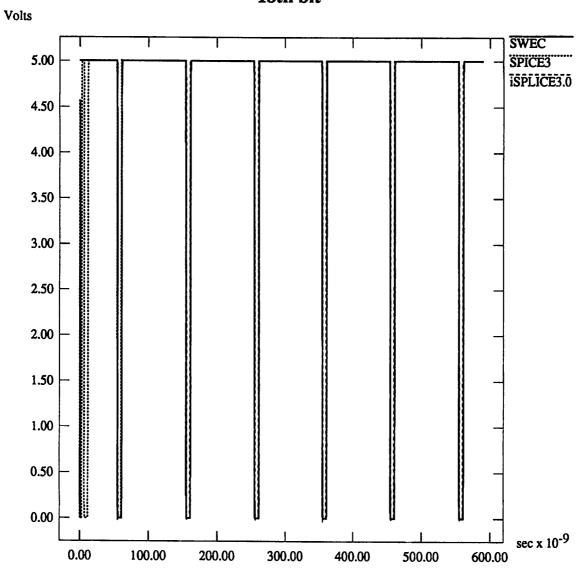

|              |            | 4.5.1 Ring Oscillator with 7 inverters                                | 49       |

|--------------|------------|-----------------------------------------------------------------------|----------|

|              |            | 4.5.2 8-bit Ripple Carry Adder                                        | 50       |

|              |            | 4.5.3 16-bit Multipliers                                              | 50       |

|              |            | 4.5.4 A Stiff Circuit                                                 | 55       |

|              |            | 4.5.5 Micro-Processor                                                 | 57       |

| 5            | Tra        | nsient Simulation of Lossy Interconnects Based on the Recursive Con   | <b>-</b> |

|              |            | ntion Formulation                                                     | 60       |

|              | 5.1        | Background of Convolution Simulation                                  | 62       |

|              |            | 5.1.1 Convolution Simulation of Simple <i>RLGC</i> -lines             | 62       |

|              |            | 5.1.2 Convolution Simulation of Lossy Coupled Lines                   | 65       |

|              | 5.2        | Recursive Convolution Simulation of simple RLGC-lines                 | 70       |

|              |            | 5.2.1 The Pade approximations of $Y_0(s)$ and $e^{-\lambda(s)l}$      | 70       |

|              |            | 5.2.2 Recursive Convolution Formulation                               | 74       |

|              |            | 5.2.3 Frequency Varying Lines                                         | 76       |

|              | 5.3        | Recursive Convolution Simulation of Lossy Coupled Lines               | 76       |

|              |            | 5.3.1 Computing Time-Domain Response Using Pade Approximation and     |          |

|              |            | Polynomial Fit                                                        | 76       |

|              |            | 5.3.2 Recursive Convolution of Multiconductor Lines                   | 80       |

|              |            | 5.3.3 Frequency-Varying Coupled Lines                                 | 81       |

|              | 5.4        | Implementation in a Stepwise Equivalent Conductance Circuit Simulator | 81       |

|              |            | 5.4.1 Circuit Partition                                               | 82       |

|              | 5.5        | Error Analysis of the Pade Approximation                              | 83       |

|              | 5.6        | Experimental Results                                                  | 88       |

|              |            | 5.6.1 Lossy Simple Lines                                              | 88       |

|              |            | 5.6.2 Lossy Coupled Lines                                             | 93       |

| 6            |            | ure Work: Recursive Convolution Simulation of Arbitrary Distributed   | i        |

|              |            | works.                                                                | 97       |

|              | 6.1        | Introduction of the Scattering Parameter Model                        | 99       |

|              | 6.2        | Simulation with Scattering Parameters                                 | 100      |

|              | 6.3        | Recursive Convolution Simulation with Scattering Parameter Models     | 102      |

| 7            | Con        | clusions.                                                             | 104      |

| A            | Circ       | cuits with Inductors, Nonlinear Capacitors and Nonlinear Inductors.   | 106      |

| В            |            | proximation Errors.                                                   | 108      |

|              | <b>B.1</b> | The analysis of $\tau_n^2$                                            | 109      |

|              | <b>B.2</b> | The analysis of $\tau_n^2$                                            | 112      |

| $\mathbf{C}$ | Tim        | e Step Constraints.                                                   | 114      |

| D            | Tim        | e Steps Selection for an Inverter.                                    | 118      |

| $\mathbf{E}$ | Pied       | ewise-Linear Waveform Approximation Algorithm.                        | 125      |

| F            | Remarks on Recursive Convolution Formulation.                     | 130 |  |

|--------------|-------------------------------------------------------------------|-----|--|

| G            | Remarks on Computing Time-Domain Response of Lossy Multiconductor |     |  |

|              | Line System.                                                      | 132 |  |

| Bibliography |                                                                   | 134 |  |

# List of Figures

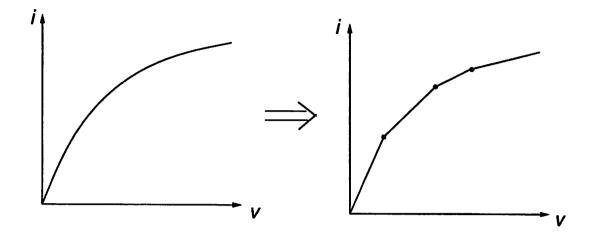

| 2.1        | The Piecewise Linear Approximation of Nonlinear i-v Characteristic 2     | 1  |

|------------|--------------------------------------------------------------------------|----|

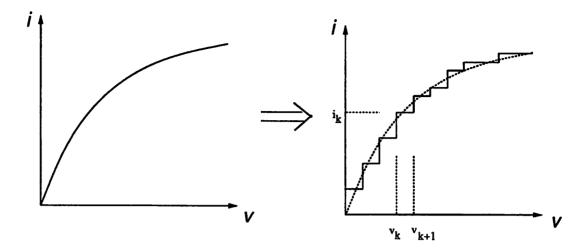

| 2.2        | The Stepwise Constant Approximation of Nonlinear i-v Characteristic 2    | 3  |

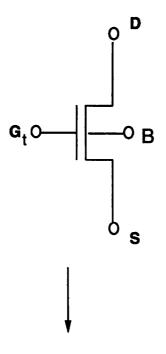

| 4.1        | Electrical Model for a MOS transistor                                    | 0  |

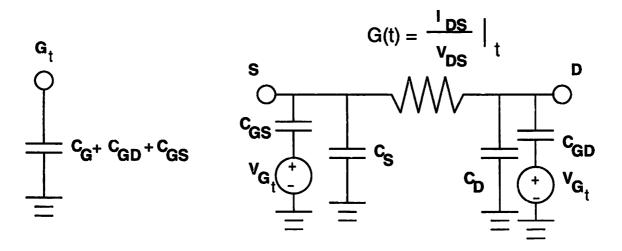

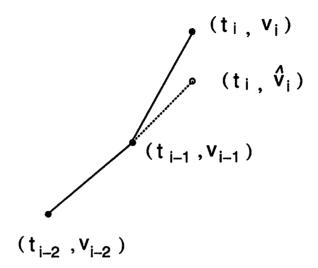

| 4.2        | Piecewise-Linear Waveform Approximation                                  | 5  |

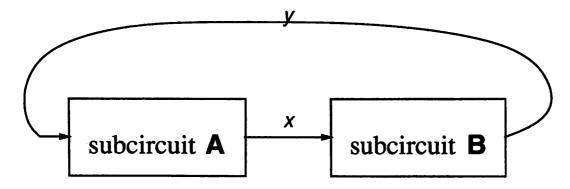

| 4.3        | A circuit with a feedback loop                                           | 8  |

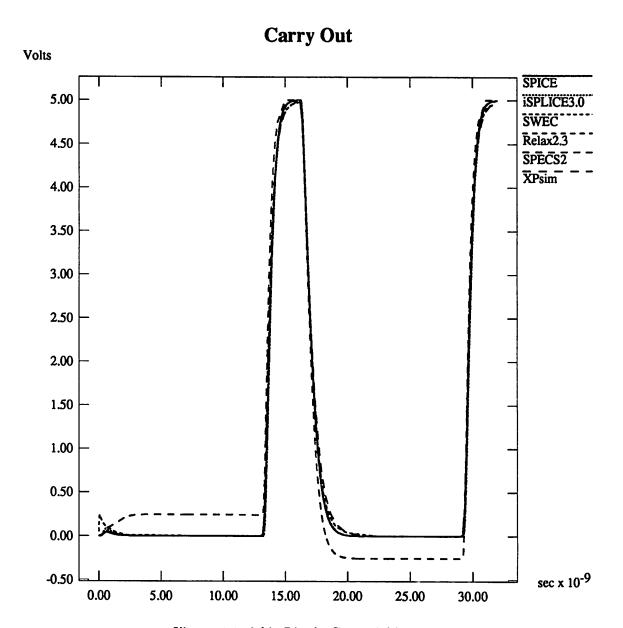

| 4.4        | 8-bit Ripple Carry Adder                                                 | 1  |

| 4.5        | 16-bit Multiplier(MULT7200)                                              | 3  |

| 4.6        | 16-bit Multiplier (MULT6700)                                             | 4  |

| 4.7        | A Stiff Circuit                                                          | 6  |

| 4.8        | Simulation of a Micro-Processor (a)                                      |    |

| 4.9        | Simulation of a Micro-Processor (b)                                      |    |

| 5.1        | A transmission line                                                      | 3  |

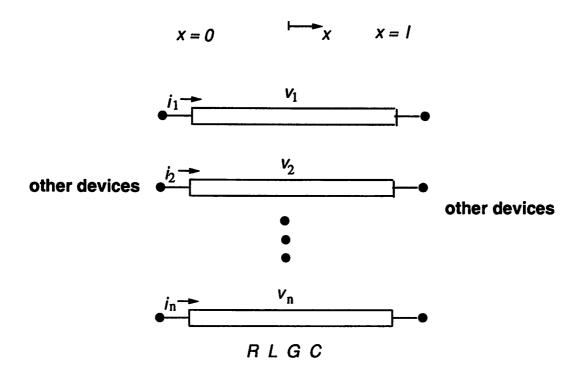

| 5.2        | An <i>n</i> -coupled lossy line system                                   | 6  |

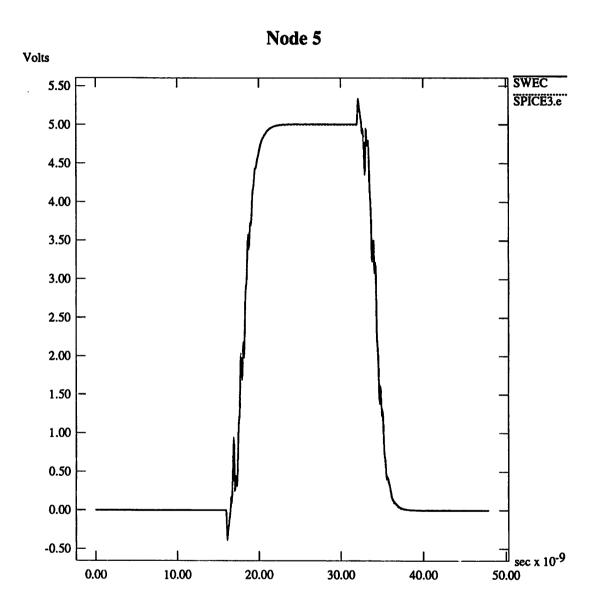

| 5.3        | A line driven by an inverter (3 input vectors) 8                         | 9  |

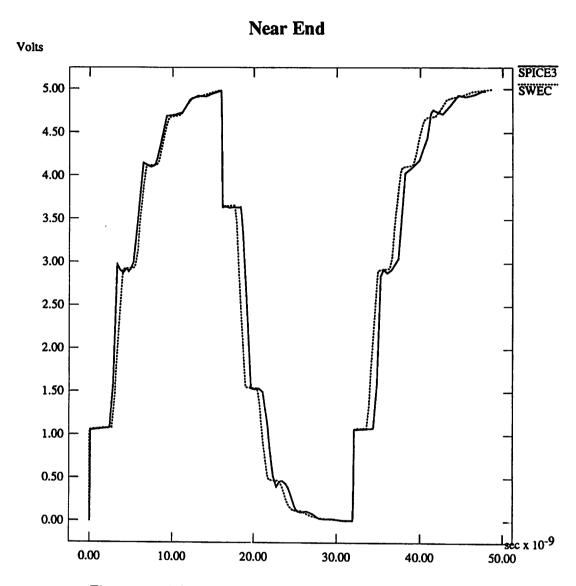

| 5.4        | A line driven by an inverter (24 input vectors)                          | 0  |

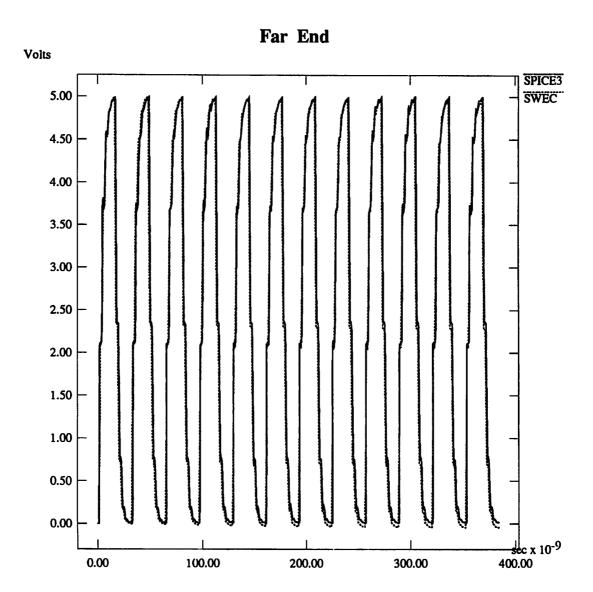

| 5.5        | A line driven by a NAND 9                                                | 1  |

| 5.6        | Expansion in s                                                           | 2  |

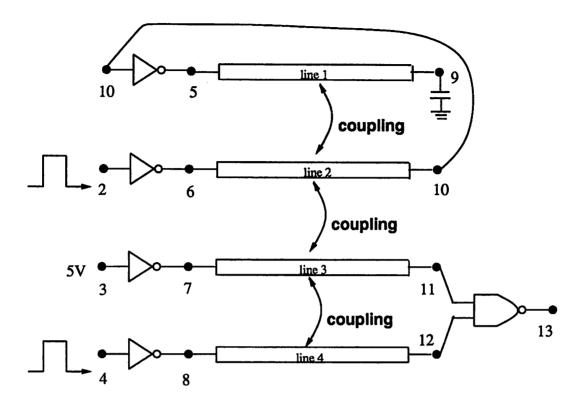

| 5.7        | A test circuit                                                           | 4  |

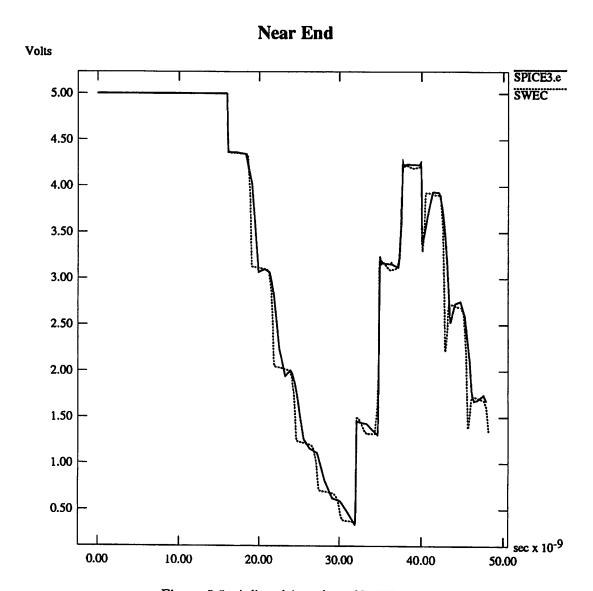

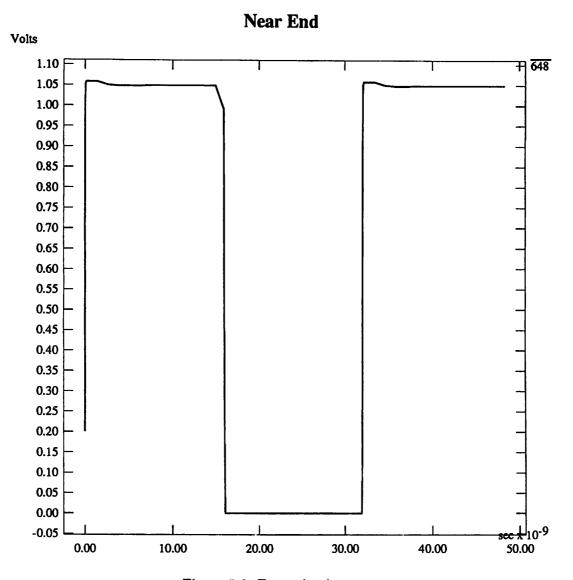

| 5.8        | The Waveform at Node 5                                                   | 5  |

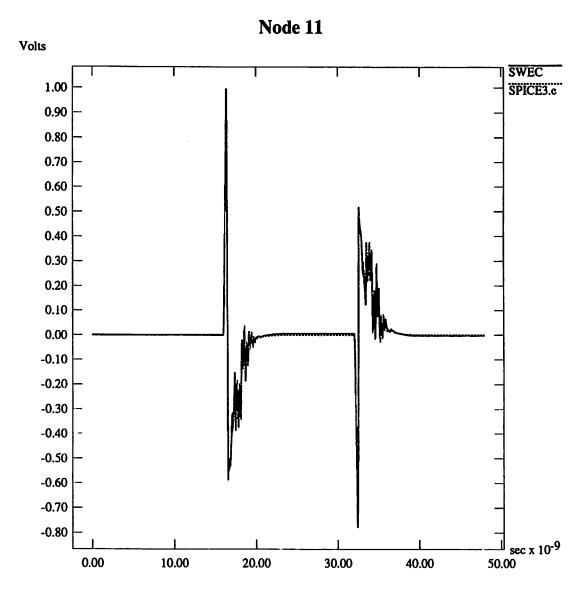

| 5.9        | The Waveform at Node 11                                                  | 6  |

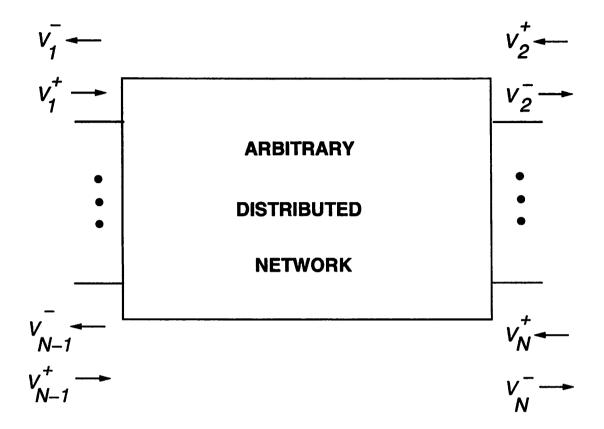

| 6.1        | N-port distributed network                                               | 1  |

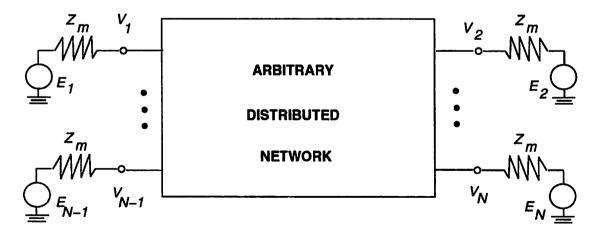

| 6.2        | N-port distributed network with the characteristic impedance termination |    |

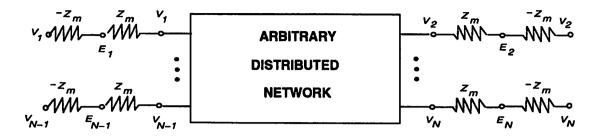

|            | and arbitrary sources                                                    | 1  |

| 6.3        | N-port distributed network with the characteristic impedance removed 10  | 2  |

| D.1        | Equivalent Circuit for the Inverter                                      | :0 |

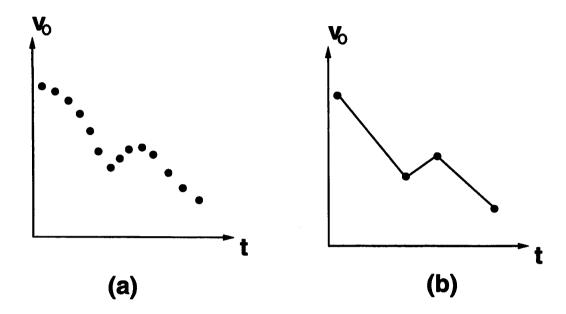

| E.1<br>E.2 | Simulation Waveforms                                                     |    |

# List of Tables

| 4.1 | CPU times for a Ring Oscillator        | 19        |

|-----|----------------------------------------|-----------|

| 4.2 | CPU times for 8-bit Ripple Carry Adder | <b>50</b> |

| 4.3 | CPU times 16-bit Multiplier(MULT7200)  | 52        |

| 4.4 | CPU times 16-bit Multiplier (MULT6700) | 52        |

| 4.5 | CPU times for a Stiff Circuit          | 55        |

|     | CPU times for a Micro-Processor        |           |

| 5.1 | CPU times for Single Line Simulations  | 39        |

|     | CPU times for Coupled Line Simulations |           |

# Chapter 1

# Introduction

## 1.1 The Circuit Simulation Problem.

Computer simulation is used in a variety of different fields to predict the behavior of physical systems whenever it is inappropriate, or too expensive, to build the actual system to observe its behavior. In electrical engineering, circuit simulation is used routinely in the design of integrated circuits (IC) to verify circuit correctness and to obtain detailed timing information before an expensive and time-consuming fabrication process is performed. Moreover, circuit simulation results can be used to guide the circuit optimization process. In fact, circuit simulation is one of the most heavily used computer-aided design (CAD) tools in terms of CPU-time in the IC design cycle. The popularity of this simulation is primarily due to its ability to provide precise electrical waveform information for circuits containing complex devices and all associated parasitics.

Detailed circuit simulation has been used extensively for IC design since the early 1970s. However, the ever-increasing number of devices on a single silicon chip has led to

development of a number of higher-level simulation tools to cope with the complexity of the problem. These tools include behavior simulators, register-transfer-level (RTL) simulators, gate-level logic simulators, and more recently, switch-level simulators [1]. These programs have been used to verify circuit functionality and to obtain first-order timing characteristics. However, there is still a significant gap between a functioning circuit and a circuit which meets all the design specifications - particularly in the case of high-performance custom integrated circuits. In fact, circuit simulation is the only tool which provides enough detailed information to ensure that the simulated circuits will meet specifications over a wide range of operating conditions. Furthermore, the lossy interconnect effects in high-speed Very Large Scale Integrated (VLSI) chips even point out the need for circuit simulation.

At the present time, the most popular circuit simulator tool is the SPICE2 program [2]. There are many thousands of copies of this program in use, as well as a number of versions of "alphabet-SPICE" (e.g. HSPICE, PSPICE, IGSPICE) being marketed commercially. All of these programs offer a wide variety of analyses including DC analysis, time-domain transient analysis, AC analysis, noise analysis and distortion analysis. Of these, the time-domain transient analysis, which solves the time-domain waveforms of each output node voltage and each output branch current, is the most often used and the most computationally expensive in terms of CPU-time. This analysis has always been considered a crucial step in digital VLSI circuit designs. Its results can be used to verify the functionality and the detailed timing performance of simulated circuits and also can be used to guide the circuit optimization process. In this dissertation, we will focus on time-domain transient analysis.

## 1.2 Motivation and Goals.

The SPICE2 program [2] has been the bread and butter of industry and university researchers in circuit design for over two decades. It was originally designed to simulate circuits containing up to hundreds of transistors. However, the continuing improvements of IC technology have made the device feature sizes decreased and the chip sizes increased continuously. With this trend, circuit designers have to design very dense chips. Each chip will have millions of transistors. SPICE2 will be infeasible to simulate circuits of this size. Therefore, the development of fast and accurate simulation methods for VLSI circuits continues to be an important area of research and is one of the goals of this research.

Also, with the trend, it is anticipated that in the near future, the time delay and the speed performance of VLSI systems will be primarily determined by interconnections rather than by device limitations [3]. Therefore, the design of a reliable network for communication and fast computers requires the use of numerical simulation tools that implement models to consider the problems encountered in propagating high-speed signals on lossy interconnects, such as (1) crosstalk, (2) reflections incurred by discontinuity, (3) rise-time slowdown due to dispersion, and (4) dielectric-loss, over a wide frequency range. Fast pulses in excited lines can generate transients via coupling to neighboring lines; these transients can trigger logic gates and other devices, resulting in corrupted data transmission. Circuit designers may also have to ensure that the receiving devices switch on the first incidence of signals. Sometimes it may take the signal voltage several trips back and forth on the transmission lines to turn on the receiving devices, resulting in extra delays, which cannot be estimated by the widely-used first order Elmore delay model.

Improvements in process technology have also made it possible to bond many silicon chips to a common silicon substrate and connect them by thin film interconnects running over the surface of the substrate. With the rapid increase in clock rate and the interconnect lengths of these multi-chip modules (MCMs), electrical length of interconnects can become a significant fraction of the signal wavelength. Consequently, the conventional lumped-impedance interconnect model is no longer adequate. Instead, a distributed transmission line model should be used.

The fundamental difficulty encountered in integrating transmission line simulation into a transient circuit simulator arises because circuits containing nonlinear devices or time-dependent characteristics must be characterized in the time domain while transmission lines with loss, dispersion, or discontinuities are best characterized in the frequency domain. Hence, we need an approach that can handle the two domains at the same time. Currently, there is no generally accepted and efficient approach for the transient simulation of lossy interconnects. This is the second goal of this research.

Therefore, an efficient simulation method for VLSI circuits and an approach for simulating lossy interconnects are the two goals of research in this dissertation.

## 1.3 Contribution.

In order to avoid the Newton-Raphson iterations used in SPICE2's implicit multistep integration of nonlinear circuits, we proposed the Stepwise Equivalent Conductance integration algorithm based on the use of a stepwise equivalent conductance model of a nonlinear resistive device [4, 5]. We proved that a nonlinear circuit can be transformed into

a linear circuit composed of time-varying conductors, and that for the integration of a time-varying circuit within one time step, an effective constant conductance can be determined for each time-varying conductor with a second order of accuracy <sup>1</sup>. The implicit integration of the equivalent linear time-invariant circuit does not require solving any nonlinear equation. This technique, when applicable, is consistent, absolutely stable, and convergent.

When applying the integration algorithm to digital CMOS circuits, we demonstrated that additional speedups in the simulation can be achieved by taking advantage of the fact that voltage waveforms can be modeled to a good approximation as piecewise-linear functions. A specific event-driven approach employing this piecewise-linear waveform property is proposed. The StepWise Equivalent Conductance digital CMOS timing simulator, SWEC, has been implemented based on the above proposed techniques. Comparisons have been made with Relax2.3[6], iSPLICE3.0[7], XPsim[8], and SPECS2[9] on a large number of circuit examples. The results indicate that SWEC, while accurate, exhibits far better efficiency [10].

Moreover, a new approach for transient simulation of lossy interconnects terminated in arbitrary nonlinear elements is also proposed. The approach is based on convolution simulation. By using the Pade approximations of each line's characteristics or of each multiconductor lines' modal functions, we derive a recursive convolution formulation, which greatly reduces the computation used to perform convolutions. The approach can handle frequency-varying effects, such as skin effects, and general coupling situations. A large circuit can be decomposed into subcircuits by making a cut on every line and the integration

<sup>&</sup>lt;sup>1</sup>The local truncation error for integration is of the cubic order of the time step used.

of each subcircuit can be performed independently. Furthermore, we analyzed the errors introduced by Pade approximations and developed a scheme to determine the necessary order for an approximation. We have incorporated the proposed technique in SWEC. The comparisons with SPICE3.e [11] indicate that SWEC can be one to two orders-of-magnitude faster.

In summary, we will present the following three topics in this dissertation:

- 1. the Stepwise Equivalent Conductance implicit integration technique,

- 2. the Piecewise-Linear Waveform event-driven simulation

- 3. the lossy interconnect simulation based on the Recursive Convolution Formulation

# 1.4 Organization

Chapter 2 gives the background of transient circuit simulation. The chapter also reviews the previous work addressing the issues of time efficiency vs. accuracy by simplifying the numerical algorithms or by using simpler device models and the previous work on the lossy interconnect simulation. After indicating the strong and weak points of the approaches, we explain how a simulation approach will benefit from the strong points, which leads to the pursuit of this research.

Chapter 3 presents the Stepwise Equivalent Conductance implicit integration technique. We will give a proof for the correctness of the transformation from a nonlinear circuit to a linear time-varying circuit. We will determine the effective constant conductance of the time-varying conductors for the integration during a time step and then discuss the

choice of time steps for integration. The errors introduced by the transformations will be analyzed.

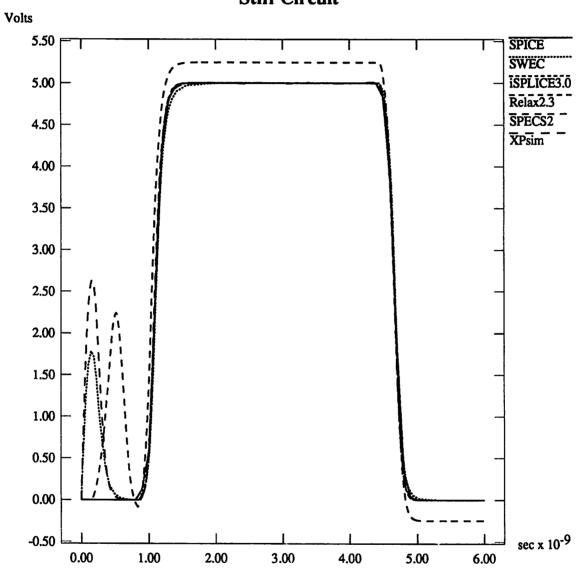

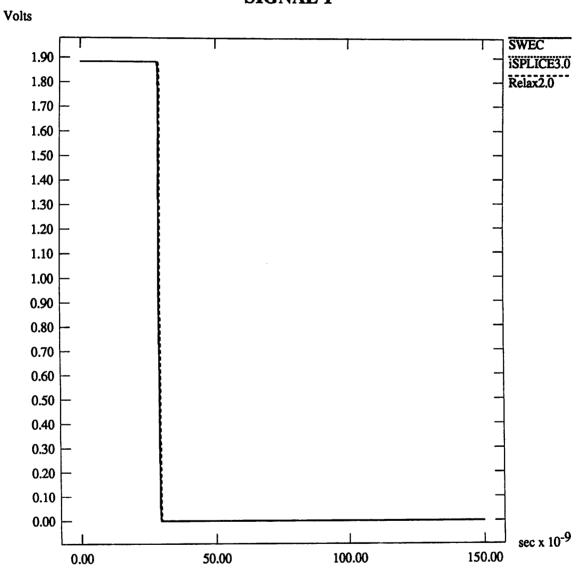

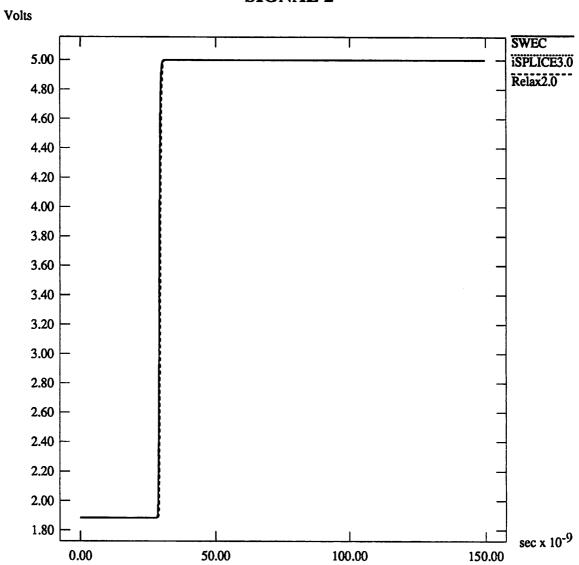

In chapter 4, the StepWise Equivalent Conductance digital CMOS circuit simulator SWEC will be presented. We will introduce SWEC's circuit partition technique, the piecewise-linear waveform approximation, and the event driven approach that employs digital CMOS circuits' piecewise-linear waveform property. Experimental results of SWEC along with comparisons with SPICE, iSPLICE3.0, Relax2.3, XPsim, and SPECS2 programs will be shown.

In chapter 5, we present our lossy interconnect simulation algorithm. The algorithm is based on two techniques: Pade approximation and Recursive Convolution Formulation. These techniques will be introduced. We will analyze the errors introduced by Pade approximations and develop a scheme to determine the necessary order for an approximation. The comparisons of our approach with SPICE3.e [11] will be shown.

Chapter 6 suggests possible future work. The transient simulation of lossy interconnects modeled by scattering parameters will be presented. The scattering parameter model is the key to handle very general coupling geometry and non-uniform lines.

Finally, in chapter 7, conclusions of this research are presented.

# Chapter 2

# Background and Review of

# Previous Work.

# 2.1 The Direct Approach of SPICE2.

# 2.1.1 Linear Multistep Numerical Integration.

The KCL nodal equations for the simulated circuit will be of the form

$$\mathcal{F}(\mathbf{V}(t)) + C\dot{\mathbf{V}}(t) = \mathbf{I_s}(t), \tag{2.1}$$

where V(t) is the node voltage vector,  $\mathcal{F}(\cdot)$  is a vector function of V(t) with its *i*-th entry representing the total current flowing out of node *i* through resistive devices, C is the constant capacitance matrix, and  $I_s(t)$  is the vector for inputs (represented as current sources). Independent voltage sources can be considered by the Norton equivalent models and be represented as current sources. The Modified nodal analysis can be used to consider circuits with linear inductors, nonlinear capacitors, and nonlinear inductors. The circuit

equation will still be a first order differential equation as that of Eq.(2.1). For that case, the variable V(t) will include the inductor branch currents or the charges of nonlinear capacitors, and the matrix C will be a combination of the inductance matrix and the capacitance matrix.

The transient circuit simulation amounts to the numerical integration of the initial-value problem specified by Eq.(2.1). The initial value (or V(0)) is the DC solution of the circuit. SPICE2 uses the linear multi-step (LMS) method to perform the integration step by step. It assumes the following equation will hold

$$V(t_{n+1}) = \sum_{i=0}^{N} \alpha_i V(t_n - ih) + h \sum_{i=-1}^{N} \beta_i \dot{V}(t_n - ih), \qquad (2.2)$$

where h is the time step. If  $\mathbf{V}(t)$  is a k-th degree polynomial of the time t then the  $\alpha$  and the  $\beta$  of Eq.(2.2) can be determined to give the exact solution of  $\mathbf{V}(t_{n+1})$  and we say the method is a k-th order method. The  $\dot{\mathbf{V}}(t)$  of Eq.(2.1) is replaced by Eq.(2.2); therefore, from the values of  $\mathbf{V}(t)$  and  $\dot{\mathbf{V}}(t)$  at previous time points,  $\mathbf{V}(t_{n+1})$  can be solved. The whole simulation is given by a series of these steps.

If the  $\beta_{-1}$  of Eq.(2.2) is not equal to zero, then the integration method is called an implicit integration method because the unknown variable  $V(t_{n+1})$  appears in the function  $\mathcal{F}(\cdot)$  term and  $C\dot{V}(\cdot)$  term. If  $\mathcal{F}$  is nonlinear, then the implicit integration for each time step involves solving a system of nonlinear equations. Computationally expensive Newton Raphson iterations are generally needed to find the solutions. For each Newton iteration, a Jacobian matrix, which involves evaluating device models, needs to be determined and a linear system of equations needs to be solved.

On the other hand, if  $\beta_{-1}$  is zero, it is called the *explicit* integration approach; then

solving  $V(t_{n+1})$  at most takes one inversion of the C matrix because the unknown variable  $V(t_{n+1})$  appears only in the  $C\dot{V}(.)$  term. However, the explicit method has poor stability: the numerical errors will explode if larger time steps are used. Therefore, the explicit method can not handle stiff circuits. Stability and circuit's stiffness will be explained in the next subsection. Because of this stability consideration, SPICE2 employs the computationally expensive implicit integration approach. SPICE2 has been proved to be very reliable and stable; however, it becomes impractical to simulate large circuits.

## 2.1.2 Properties of Numerical Integration.

In this subsection, we are going to introduce the issues to be considered for numerical integration methods. These properties are essential to guarantee the correctness of the integration results and are used as the guide lines to differentiate a better integration method from another. When we present our new integration approach in chapter 3, we will also examine these properties of our approach.

### Existence and Uniqueness of Solutions.

Most numerical methods for solving Eq.(2.1) subject to the initial condition  $V(0) = V_0$  assume the solution to this initial-value problem exists and is well defined for all times  $t \geq 0$ . In the event that the solution does not exist or is pathological, most numerical methods would still produce a set of numbers, which of course is meaningless. Therefore, in order for us to have confidence on the simulation results, it is important to derive some criteria on the simulated circuits to guarantee the existence and the uniqueness of a solution in the general case.

The **Peano existence theorem** shows that the *continuity* of  $\dot{\mathbf{V}}(t)$  (or  $C^{-1}[\mathbf{I_8}(t) - \mathcal{F}(\mathbf{V}(t))]$ ) is a sufficient condition to guarantee the existence of a solution around t=0 [12]. Clearly, if C is singular or  $\mathcal{F}(\cdot)$  is not continuous for some intervals of interest, the solution may not exist.

The Peano's theorem is a local theorem, since it only proves the existence of a solution over some nonzero time interval centered about the initial time. To guarantee the existence of a solution over the whole simulation time, much more severe conditions must be imposed on  $C^{-1}[I_s(t) - \mathcal{F}(V(t))]$ , as shown by Wintner's Global Existence Theorem below

Wintner's Global Existence Theorem: If there exists a piecewise-continuous function L(t) defined for the t over the whole simulation time such that

$$\| C^{-1}(\mathcal{F}(V') - \mathcal{F}(V'')) \| \le L(t) \| V' - V'' \|$$

(2.3)

for all t in the simulation time (this is called a global Lipschitz condition), then Eq. (2.1) has a unique solution. [13].

Wintner's global existence theorem proves both the existence and the uniqueness of a solution. However, the conditions required by the theorem are rather strong. Roughly speaking, these conditions prevent the functions  $\mathcal{F}(V(t))$  and V(t)  $\forall t$  from growing too rapidly. As a result, the simulated circuit cannot have fast switching inputs and all its devices should be modeled by smooth i-v curves. It must be emphasized that the above two theorems provide only sufficient conditions. Hence, even if the circuit does not satisfy Wintner's global existence theorem, the solution may still exist.

#### Local Truncation Errors and Consistence.

The error introduced by one integration step is called the *local truncation error* (LTE). As the time step h gets smaller, the LTE will vary as a degree of h. If the linear multi-step method is of the k-th order, then its LTE will be of  $O(h^{k+1})$ , which means that the method preserves the k-th order of accuracy. Given an error bound on the LTE, the desired time step h can be determined. If the integration method has a larger k, then we are allowed to use a larger time step h to meet the error criterion and get better efficiency.

A numerical integration method is said to be *consistent* if as h approaches zero, the ratio  $\frac{LTE}{h}$  will vanish, where LTE is the method's local truncation errors. For a nonconsistence method, no matter how small the integration time steps are used, nonzero global errors will always exist. Therefore, consistence is a desired property for the integration method.

### Stability and Convergence.

To keep the accuracy requirement, we have to use small time steps. This means for a simulation, many steps of solving the difference equations introduced by numerical integrations will be needed. Thus, as a practical matter, it is important that these solutions should not be too sensitive to small errors in the computations (for example, roundoff errors). This sensitivity to errors is related to what is called the *stability* of the integration method. Numerical errors will be introduced by each integration step. These errors will die out, as simulation proceeds, for a stable integration method. However, for an unstable method, previous errors will magnify later errors; eventually, the global errors will blow up

to infinity.

Basically, the solution of each integration is a linear combination of exponential terms. The exponents of those terms are function of the time step h, the numerical method used, and the poles of the simulated circuit. To obtain stable simulation results, the exponents should be on the left half of the complex plane. We consider the case where the circuit has only left-half-plane poles. A numerical integration method is said to be *stable* if there exists a nonzero interval of time steps around h = 0 such that the exponents can be situated on the left half of the complex plane. To be more specific, to verify the stability of a method, let us consider the test equation

$$\dot{x} = \lambda x, \qquad x(0) = 1, \tag{2.4}$$

where  $\lambda$  is a left-half-plane complex constant and represents the pole of the system modeled by Eq.(2.4). The region of the product  $\lambda h$  that lets the exponents be situated on the left half of the complex plane is called the *region of stability* for the numerical method. If the region of stability includes the origin, then the method is stable.

The stability of a multistep method only guarantees that the local truncation and round-off errors are not amplified and remain bounded for a sufficiently small step size. It is important for us to derive a criterion to guarantee that the global error will tend to zero as  $h \to 0$ , which is defined as the *convergence*. It has been proved that every stable and consistent multistep method is convergent [14]. Conversely, every convergent multistep method is stable.

#### Stiffness and Absolute Stability.

For the sake of efficiency, the time step selection for integration will be based on the activity of the simulated circuit. We want to use large time steps for the situation when the circuit's node voltages do not change considerably. However, the stability property may not hold for some integration methods because the large time steps used cause the  $\lambda h$  values to be outside the method's region of stability.

It is possible that a circuit may have several poles ( $\lambda$ ) and some of them differ in many orders of magnitude. These circuits are called *stiff*. A simple example of stiffness is the case of a fast initial "transient" in the solution, which dies quickly, followed by a slower "steady-state" solution. To handle this type of behavior, it is natural to use small time steps in the transient portion to accurately follow the solution and then to increase the step size for the remainder of the solution. However, the strategy may lead to instability for the integration method, especially for explicit integration methods. For example, let us consider a circuit with two poles  $\lambda_1 = -1.0$  and  $\lambda_2 = -1.0e6$ . The transient associated with  $\lambda_2$  will approach its steady state very fast. After that, the circuit will have only minimum activity because  $\lambda_1$  is small. In this situation, we want to increase the time step h. However, since  $\lambda_2$  is very large, any increase on h will make  $\lambda_2 h$  go beyond an integration method's region of stability. Since the efficiency is one of the major concerns when we choose an integration method, we would like to have its region of stability cover as large the left half of the complex plane as possible. A numerical integration method which has its region of stability cover the whole left half of complex plane is said to have the absolute stability.

It has been proved by Dahlquist [13] that no multistep method that exceeds order 2

has absolute stability. Moreover, no explicit integration method can have absolute stability. Since the absolute stability is rather strong, for practical purpose, we relax the region of stability by a small strip left of the imaginary axis except origin. This kind of stability is called *stiff stability*. Because most circuits do not have poles with large imaginary parts, the stiff stability criterion can be adequate. However, again no explicit method has the stiff stability. Due to the stability consideration, SPICE2 uses stiffly stable and absolutely stable integration methods. Hence, when integrating nonlinear circuits, solving a system of nonlinear equations cannot be avoided.

However, compared with explicit algorithms, the extra computation does not really improve the solution's accuracy. One needs to go through the pain of Newton Raphson iterations in the implicit algorithms mainly to achieve **stability**. This makes one wonder if there is really no easy way of obtaining stability while retaining accuracy, and that is the motivation of our research on developing a new numerical integration approach.

# 2.2 Work on Improving Efficiency.

The overall goal in circuit simulation is to generate the solution as efficiently as possible while providing the desired level of accuracy. To improve the efficiency of circuit simulations, two types of approaches have been proposed previously. One is to simplify the numerical algorithms and the other is to simplify the device models. In this section, we will survey the work in these two categories. The pros and cons of each type of approach will be shown.

## 2.2.1 Simplify the Numerical Algorithms.

Previously, the direct approach of SPICE2 was modified to avoid the large number of Newton iterations, to maximize time steps used, or to exploit circuit's latency and multirate behavior. These approaches include (1) the Relaxation Approach, (2) the Waveform Relaxation Approach, (3) the Semi-Implicit Integration Approach, (4) the Exponential Integration, and (5) the Asymptotic Waveform Evaluation Method. These are described in the following subsubsections.

#### Relaxation Approach:

A large circuit is usually very sparse: every node is only connected to a small number of neighbor nodes. For the direct approach of SPICE2, all the node voltages are solved simultaneously. Even though a sparse linear equation solver is employed, the complexity is still superlinear. Once the number of nodes are large, the approach will become very computation-intensive. The relaxation approach [15] tries to exploit the circuit's sparsity to speed up the solving process. The relaxation approach, instead of solving all the system variables at once, only solves one of them each time by assuming the rest are correct solutions. Then, it iterates on this step over all variables until the solution of each variable converges. The approach can be used to solve the linear system of equations within each Newton Raphson loop or directly applied to solve the system of nonlinear equations.

The efficiency of the relaxation approach is determined by the speed of convergence, which heavily depends on the coupling between nodes. When simulating tightly coupled circuits (e.g. circuits with strong negative feedbacks), it takes a lot of computation

for the solutions to converge. If the circuit simulation program is intended for the simulation of MOS digital circuits, then it is possible to make use of the weak coupling between the gate node of a MOS transistor and the drain node (or the source node) to achieve faster convergence. Examples of relaxation-based simulators are the family of SPLICE [7] [16] [17].

#### Waveform Relaxation Approach:

The circuit simulators employing the direct method use a single common time step to integrate the whole circuit; the step size is, therefore, determined by the activity of the fastest changing part of the circuit. However, for a large circuit at one time point, it is common that only a small portion of the circuit has activity and the rest does not (being latent). As a result, many variables are solved using time steps which are much smaller than necessary to compute their solutions accurately. Waveform relaxation simulators try to improve the efficiency by exploiting the circuit's *latency*, which refers to the situation when most node voltages stay the same from one integration to another.

The waveform relaxation approach [18, 19] solves a node voltage waveform for the whole simulation time by assuming the waveforms of its neighboring nodes are as presolved. Then, it iterates on this process until the waveform of each node converges. When solving the waveform at one node, it can use variable time steps to achieve the maximum efficiency because the waveforms on neighboring nodes are known. The reduction in run time is accomplished by computing fewer solution points for each waveform, thereby reducing the total number of model evaluations, and by avoiding the direct sparse-matrix solution. However, the tradeoff exists only for loosely coupled nodes; otherwise, the approach takes

a long time to converge. Circuit partitions become very important. Strongly connected nodes should be grouped into one solving process. Furthermore, the ordering of the solving processes is also important. Take an inverter chain as an example. The first few iterations will be obsolete if the ordering starts on the last inverter and goes backward. However, there will be no wastage of computation if the ordering starts on the first inverter and goes forward.

The approach is very suitable for simulating digital MOS circuits because of the weak coupling between the gate node of a MOS transistor and the drain node (or the source node). Examples of waveform-relaxation based simulators are Relax2.1 [6] and IDSIM2 [20] (the Partial Waveform Convergence [21]).

### Semi-Implicit Integration Approach:

To avoid being trapped in the lengthy iteration process, the semi-implicit integration method has been proposed and applied in the simulators of MOTIS [22] and Event-EMU [23]. They conjectured that there exists a small enough time step to obtain the solution in exactly one Newton iteration. The nonlinear devices of a circuit are linearized using the node voltages at the previous time point and then the linearized circuit is integrated. However, to maintain the desired accuracy in most cases very small time steps need to be used, and that unfortunately degrades the efficiency.

#### **Exponential Integration Approach:**

The solution of an initial-value linear differential equation is a linear combination of exponential functions. Therefore, if the solution V(t) of Eq.(2.1) between two time

points is approximated by an exponential function of t instead of a polynomial employed by the linear multistep method then it is possible to use larger integration time steps, hence improving the efficiency. Based on this observation, the exponential integration approach was proposed in [8] and implemented in the MOS simulator XPsim. The voltage waveforms produced by the approach are piecewise exponentials. The node voltage at a new time point  $t_{n+1}$  is equal to its previous value  $v(t_n)$  multiplied by  $e^{\lambda h}$ , where  $\lambda$  can be determined by matching the circuit's asymptotic solution at  $t_n$ . The authors of [8] have proved that for a first order exponential integration method, its local truncation error LTE at  $t_n$  is equal to  $v(t_n)\frac{h^2}{2}\frac{d\lambda}{dt}$ . On the other hand, the LTE of a similar first order linear multistep method is equal to  $\ddot{v}(t_n)\frac{h^2}{2}$ . Since  $v(t_n)\frac{d\lambda}{dt}$  will not change as fast as  $\ddot{v}(t_n)$ , larger time steps can be used in the exponential approach.

However, the approach is neither absolutely stable nor stiffly stable. The efficiency will be impaired when simulating stiff circuits.

### Asymptotic Waveform Evaluation Method:

For the SPICE direct approach, when simulating linear RLC networks, even though the waveform at the network's internal nodes are not important, the approach still needs to solve all of them at each time point because the waveforms are the internal states of the RLC network. As the network size increases, there will be too many internal nodes and the computations to perform each integration will be infeasibly large. However, linear system theory tells us that if we treat the whole RLC network as a linear system and the external nodes as the terminals of the system then the convolution of the inputs and the impulse response of the system can be used to determine the waveforms at the system's output

nodes. Then, we don't need to solve the waveforms at the internal nodes and can save a lot of computation. This idea motivates the asymptotic waveform evaluation method of [24].

The timing analyzer AWEsim [25] was implemented based on the asymptotic waveform evaluation method. AWEsim assumes that step inputs are applied at the input nodes of the RLC network. Therefore, the transfer function of the output (or outputs) of the network can be determined. The transfer function is then expanded into a Maclaurin series of s, the Laplace transform variable, around s=0. The first order Elmore delay of the output will be the first moment of the series. An approximated time domain output waveform can also be determined by matching the truncated transfer function. This approach can outperform SPICE by two to three orders of magnitude in speed. However, its efficiency will be impaired if nonlinear terminals exist in the circuit. The authors of [24] suggest using effective linear resistors to represent those nonlinear terminals; however, the accuracy degrades. Also, the approach suffers from the stability problem when the poles of the approximated transfer function are located on the right half of the complex plane. This becomes a phenomenon if the network is not very lossy.

### 2.2.2 Simplify the Device Models.

The approaches of approximating the i-v characteristics of nonlinear devices by piecewise-linear curves or stepwise-constant curves to avoid solving nonlinear equations have been proposed. The increase in efficiency is due to

1. avoiding solving a system of linear equations in each Newton Raphason iteration,

Figure 2.1: The Piecewise Linear Approximation of Nonlinear i-v Characteristic.

avoiding the model evaluation of nonlinear devices, which involves many floating point calculations.

These are described in this subsection.

### Effective Linear Conductance Model:

The effective linear conductance model has been used in the timing analyzers Crystal [26], TV [27], and Rsim [28]. For the whole transition, these timing analyzers replace every MOS transistor by an effective conductor and use the RC-tree [29] approach to estimate first order timing information of the analyzed MOS circuit. Analog waveform information cannot be obtained from this type of analysis, which means that these methods cannot ensure that a circuit meets specifications. Furthermore, there is no mathematically rigorous way of determining the effective conductance. For the simulation that demands high accuracy, this type of approach is not adequate.

#### Piecewise-Linear Device Model:

The application of the Newton-Raphson algorithm to solve the nonlinear equations introduced in each integration step would require the evaluation of a Jacobian matrix at each iteration. This is usually a time-consuming procedure. It is possible to avoid evaluating the Jacobian if we approximate the i-v curve of each nonlinear device by piecewise-linear segments as shown in Fig. 2.1. The Katzenelson algorithm has been proposed to perform this piecewise-linear version of numerical integration [30]. If the i-v curve of each nonlinear device is approximated by only one linear segment, then each integration step of Eq.(2.1) will be brought down to solve just a system of linear equations

$$AV = b, (2.5)$$

where the solution V is the node voltage at the new time point. It is because the approximated circuit is linear. For the situation where the approximation of each nonlinear device has more than one piecewise-linear segment, the space of V can be partitioned into hypercubes such that inside each hypercube every nonlinear characteristic is approximated by one linear segment. The integration step will then require solving a series of linear equations below

$$A^i V^i = b^i i = 0, 1, ..., n.$$

(2.6)

The index i represents the i-th hypercube, which contains the solution  $V^i$ . The matrix  $A^i$  and the column vector  $\mathbf{b}^i$  depend on the linear segment of each device specified in the hypercube i.  $V^0$  is equal to the V at the previous time point and the final  $V^n$  is the solution of V at the new time point. Based on the Katzenelson algorithm, the trajectory

Figure 2.2: The Stepwise Constant Approximation of Nonlinear i-v Characteristic.

from  $V^0$  to  $V^n$  can be determined and the  $A^i$  and the  $b^i$  when crossing the boundary of two hypercubes can be updated. The piecewise-linear simulator PLATO was implemented based on the above approach [31].

This piecewise-linear integration will lose its efficiency if for each integration the trajectory needs to go through many hypercubes. Since the system of linear equations given in Eq.(2.6) needs to be solved for each hypercube, the computation will be comparable with the Newton-Raphson algorithm. Another weakness of this type of approach is that it is no longer consistent because the local truncation error will not vanish even when a very small integration time step is used. Its accuracy has been restricted by the piecewise-linear approximation of the i-v curve.

## Stepwise Constant Device Model:

If the simulated circuit does not not have floating capacitors<sup>1</sup> or inductors then it is possible to perform the simulation without solving any system of equations by approximating the i-v characteristic of each device by a stepwise constant function as shown in Fig. 2.2. In other words, the i-v characteristics are represented by the constant current level  $i_k$  for each voltage range  $v_k \leq v < v_{k+1}$ , for k = 0, 1, ..., n. The approximation can be made with a small number of segments (less accurately but more efficiently) or with a large number of segments (vice versa).

Devices with stepwise constant i-v characteristics have stepwise constant branch currents in time. These currents combine via KCL to force stepwise constant currents flowing into all the grounded capacitors. Therefore, by KVL all the node voltages (or the branch voltages) will be piecewise linear in time. Since the branch voltage of each device is piecewise linear, we can predict the time when the branch current will change from one level to another. The whole simulation is driven by these predicted event times. One event is associated with a device. Events are stored in a priority queue. The event at the top of the queue will be deleted and processed. Each event process has two steps: (1) update the branch current of the device whose branch voltage crosses different segments of its stepwise constant i-v curve, and (2) predict the next event time for the device and insert this event back to the queue.

This approach was proposed in [9] and implemented as a circuit simulator SPECS2. Since no system of linear or nonlinear equations need to be solved, the approach is efficient.

<sup>&</sup>lt;sup>1</sup>A floating capacitor is a capacitor with neither terminal connected to the ground node.

The approach gives the flexibility to vary the tradeoff between accuracy and efficiency on a branch-by-branch basis. However, the approach can only be applied to a very small class of circuits because no floating capacitors and inductors are allowed in the simulated circuits. Furthermore, the accuracy is restricted by the stepwise constant approximation. From our observation, its efficiency degrades very quickly if more voltage segments are used on the device approximation to keep the desired accuracy.

#### **Electrical Logic Model:**

The application of the explicit forward Euler method to integrate Eq.(2.1), say from  $t_n$  to  $t_{n+1}$ , yields

$$\mathcal{F}(\mathbf{V}(t_n)) + C \frac{\mathbf{V}(t_{n+1}) - \mathbf{V}(t_n)}{h_n} = \mathbf{I_s}(t_n), \tag{2.7}$$

or,

$$V(t_{n+1}) = V(t_n) + h_n C^{-1} [I_s(t_n) - \mathcal{F}(V(t_n))],$$

(2.8)

where  $h_n = t_{n+1} - t_n$ .

When there are no floating capacitors in the circuit, the capacitance matrix C and its inverse  $C^{-1}$  are diagonal matrices. Therefore, Eq.(2.8) turns out to be:

$$v_j(t_{n+1}) = v_j(t_n) + h_n C_{j,j}^{-1}[is_j(t_n) - f_j(\mathbf{V}(t_n))], \tag{2.9}$$

where  $v_j(t_n)$  is the voltage at node j at  $t_n$ ,  $C_{j,j}$  is the grounded capacitance at node j,  $f_j(\mathbf{V}(t_n))$  is the current leaving node j at  $t_n$  through devices, and  $is_j(t_n)$  is the current flowing into node j at  $t_n$  from power supplies.

From Eq.(2.9), we can compute the time for node j to make a transition from  $S_{Now}$  to  $S_{Next}$ , as follows:

$$h_n = \frac{C_{j,j}(S_{Next} - S_{Now})}{-(is_j(t_n) - f_j(\mathbf{V}(t_n)))}.$$

(2.10)

It is easy to compute Eq.(2.10) because every term is scalar. The electrical logic model simulation [32] introduced the idea of dividing the voltage range into discrete states, e.g. 0V, 0.5V, 1.0V,... The  $S_{Now}$  and  $S_{Next}$  in Eq.(2.10) are examples for that. The whole simulation is driven by the event times, the time points when a node voltage changes from one state to the next adjacent state. The event process has three steps:

- 1. Update the voltage at node j to the next state.

- 2. Evaluate the  $f_j(\mathbf{V})$  using the new  $v_j$ .

- 3. Compute the transition time for node j using Eq.(2.10) and schedule node j again to the time equal to the current time plus this transition time. Node j will be processed again at that time.

The electrical logic model carries many similarities to the stepwise constant model introduced in the previous subsubsection. Both treat a device as a stepwise current source, both use the event processes to drive the simulation, and both are weak in handling floating capacitors and inductors. One difference is that the events for the stepwise constant model are associated with devices, while the events for the electrical logic model are associated with nodes. Furthermore, for the stepwise constant model, the voltage segment for a device to keep a current level is determined before running the simulation but that for the electrical logic model is determined during the simulation. Because of this difference, the electrical

logic model should preserve better efficiency. Both of them, however, experience problems with accuracy and sometimes stability because of their explicit integration approach.

#### 2.3 Previous Lossy Interconnect Simulation Work.

The fundamental difficulty encountered in integrating transmission line simulation into a transient circuit simulator arises because circuits containing nonlinear devices or timedependent characteristics must be characterized in the time domain while transmission lines with loss, dispersion, or discontinuities are best characterized in the frequency domain. To cope with this difficulty, four types of approaches have been proposed in the literature. One uses a network of lumped elements and segments of ideal transmission line to approximate the frequency response of each lossy transmission line or each lossy multiconductor system [33]. The approximated circuit models are suitable for existing general-purpose circuit simulators. However, the drawback of this type of approach is that the amount of computation increases for the simulation because a large number of extra nodes and elements are introduced [11]. The second type of approach adopts the convolution technique. For each integration, the outputs of linear lossy multiconductor lines are the convolutions of the inputs with the impulse responses (Green's function) of the multiconductor lines. The multiconductor lines are treated as a linear N-Port system. The difficulty of this type of approach lies in how to determine the impulse responses of an arbitrary multiconductor line system. People used the inverse Fast Fourier transformation technique [34], the numerical inverse Laplace transformation technique [35], inverse Fourier transformation of frequencydomain scattering parameters [36] [37], and even the explicit analytical approach[11] to determine the impulse response. However, the convolution simulations suffer from a common drawback: the convolution operation needs to extend over the entire past history. The computation time required at any time point t is then proportional to t; therefore, the convolutions at large time points will be very time-consuming. Furthermore, the inverse Fourier transformations of [34], [36], and [37] will suffer from either the aliasing effects or that too many frequency points are needed for the transformations to avoid aliasing.

To avoid the time-consuming convolution integrations, the state-based approach [38] and the waveform relaxation based approach [33][39] have been proposed. The state-based approach utilizes information about the internal states of a transmission line at a given time to solve the states for the next time point. The voltage and the current at the sample points are kept as the states of the line. The voltages and the currents are assumed to be piecewise-linear between adjacent sample points. Based on this assumption, the state variables can be determined by using integrations on space, hence avoiding convolutions. However, the efficiency of the approach will degrade for the simulation with many sharp edges in the line's waveforms. The samples will be chosen densely in the regions where waveforms are fast-varying. Typically, for the simulation containing a pulse with the rise time of 100 pico seconds and having the voltage resolution of 0.5 Volts, around 20 sample points per inch of the line are required <sup>2</sup>. If the rise time is smaller or the voltage resolution is more accurate than 0.5 Volts, we need even more sample points, which will increase the computation used to perform the simulation. The waveform relaxation based approach

<sup>&</sup>lt;sup>2</sup>The signal travels at the speed of 5e-3 inch per pico-second, or in other words 200 pico seconds per inch. A full ramping-up, from 0 to 5 Volts, takes 100 pico seconds; therefore, with the 0.5 Volt resolution, we need 0.1 samples per pico-second. The number of required samples per inch is equal to 200 pico seconds per inch times 0.1 samples per pico-second, which is 20 samples.

solves the line's equations in the frequency domain and uses the FFT to transform the results back and forth between the two domains for each iteration. Hence, time domain convolutions are avoided by performing multiplications in the frequency domain. Again, this type of approach is not suitable for handling fast-varying signals. For the simulation containing a 100-pico-second-rise-time pulse and having the simulation time of 100 nano seconds, each FFT needs to process around one hundred thousands data points in order to avoid the aliasing effects. In summary, we think in order to solve the simulation involving fast-varying signals we need to focus our efforts on developing fast convolution integration algorithms.

## Chapter 3

# Stepwise Equivalent Conductance

## Circuit Simulation.

In this chapter, we present our Stepwise Equivalent Conductance circuit simulation method, which treats every nonlinear resistance device as a 2-terminal linear time-varying conductor. We show that implicit integration can be efficiently applied to this type of circuit under a given error criterion. No nonlinear equations need to be solved. The technique is proved to be consistent, absolutely stable, and convergent. Furthermore, we demonstrate that a second order of accuracy is achieved by solving a system of linear equations for each integration step.

The Stepwise Equivalent Conductance circuit simulation makes the following two assumptions regarding the simulated circuits:

Every node in the circuit has nonzero capacitance to ground. In fact, this assumption

does not place any restriction on the simulated circuit because practically every node

in a real circuit has nonzero parasitic capacitance to ground.

Every nonlinear device in the circuit has a unique current path. Examples of these kinds of devices are MOS, JFET, and diodes.

The chapter is organized as follows. In section 3.1, we introduce the transformation from a nonlinear circuit to an equivalent circuit composed of 2-terminal linear time-varying conductors and discuss the exactness of the solution of the linear time-varying circuit under the "smooth" i-v characteristic assumption. In section 3.2, an accurate and efficient algorithm to integrate the linear time-varying circuit is introduced. The accuracy and the convergence of the algorithm are analyzed. In section 3.3, we discuss the choice of time steps for integration.

# 3.1 Equivalent Linear Time-Varying Circuit Transformation.

#### 3.1.1 Circuit Equations.

For the sake of simplicity, we start with the assumption that there are no inductors in the simulated circuit and that all the capacitors are constant. We extend the discussion to circuits with linear inductors, nonlinear capacitors, and nonlinear inductors in Appendix A by using modified nodal analysis. The KCL nodal equations for the simulated circuit will be of the form

$$\mathcal{F}(\mathbf{V}(t)) + C\dot{\mathbf{V}}(t) = \mathbf{I}_{\mathbf{s}}(t), \tag{3.1}$$

where V(t) is the node voltage vector,  $\mathcal{F}(\cdot)$  is a vector function of V(t) with its *i*-th entry representing the total current flowing out of node *i* through resistive devices, C is the constant capacitance matrix, and  $I_s(t)$  is the vector of inputs (represented as current sources). Independent voltage sources can be considered by the modified nodal analysis as well. Since every node is assumed to have nonzero grounded capacitance, C is diagonally dominant. If  $\mathcal{F}$  is nonlinear, then the implicit integration of Eq.(3.1) for each time step involves solving a system of nonlinear equations. Computationally expensive Newton Raphson iterations are generally needed to find the solutions.

The unique current path assumption of nonlinear devices implies that the simulated circuit can be treated as an equivalent circuit with 2-terminal resistive elements only. To be more specific, the i-v characteristic of every nonlinear device at each time point can be characterized by its instantaneous equivalent conductance G(t) defined as the ratio of I and V across the two terminals of the current path evaluated at that time instant<sup>1</sup>. Therefore, during the entire simulation process, we are simulating a circuit composed of only linear time-varying conductors and linear time-invariant elements.

Then, Eq.(3.1) can be transformed into the equation below:

$$G(t)\mathbf{V}(t) + C\dot{\mathbf{V}}(t) = \mathbf{I}_{\mathbf{S}}(t). \tag{3.2}$$

Here, G(t) represents the instantaneous equivalent conductance matrix for every branch in the circuit at time t. G(t) will satisfy the following relation

$$G(t)V(t) = \mathcal{F}(V(t))$$

(3.3)

for every time t.

$<sup>{}^{1}</sup>G(t)$  is set to zero if V(t) = 0. The situation where  $I(t) \neq 0$  when V(t) = 0 is practically impossible.

Instead of solving for the V(t) of Eq.(3.1) directly, the Stepwise Equivalent Conductance circuit simulation solves for the V(t) of Eq.(3.2) and uses it as the solution for Eq.(3.1). An efficient implicit integration scheme for Eq.(3.2) is developed, and no nonlinear equations need to be solved. The integration scheme will be introduced in section 3.2.

The question remaining is whether the solution of Eq.(3.2) will be equal to that of Eq.(3.1).

#### 3.1.2 Exactness of the Transformation.

If we know G(t) beforehand, then the uniqueness of the solution of Eq.(3.1)<sup>2</sup> implies that the solution of Eq.(3.2) will be the same as the solution of Eq.(3.1). However, during the process of solving Eq.(3.2), for every time t, we only know the function G up to t and have no idea of G after that. Will we end up with a different solution due to the lack of information on G? To answer this question, we state the following theorem.

Theorem 1 If  $\mathcal{F}(\cdot)$  and  $I_s(\cdot)$  of Eq.(3.1) are continuously differentiable

then the solution of Eq.(3.2) will be exactly the same as that of Eq.(3.1).

**Proof**: We prove this by contradiction. Denote the solution of Eq.(3.1) by  $V_1(t)$  and the solution of Eq.(3.2) by  $V_2(t)$ . If they are not the same then there exists a time  $t_0$  such that  $V_1$  and  $V_2$  coincide at  $t_0$  but depart from each other afterwards, i.e. there exists a positive integer k such that  $V_1^{(i)}(t_0) = V_2^{(i)}(t_0) \ \forall \ i < k \text{ and } V_1^{(k)}(t_0) \neq V_2^{(k)}(t_0)$ , where  $V_1^{(i)}(t_0)$  denotes the i-th derivative of  $V_1(t)$  evaluated at  $t_0$ .

<sup>&</sup>lt;sup>2</sup>The sufficient condition of the uniqueness of the solution of Eq.(3.1) is that  $\dot{V}$  is Lipschitz continuous at every time t.

We know, from Eq.(3.1),

$$\dot{\mathbf{V}}_1(t) = \mathbf{C}^{-1}(-\mathcal{F}(\mathbf{V}_1(t)) + \mathbf{I}_{\mathbf{s}}(t)) \tag{3.4}$$

and from Eq.(3.2) and Eq.(3.3)

$$\dot{\mathbf{V}}_{2}(t) = C^{-1}(-G(t)\mathbf{V}_{2}(t) + \mathbf{I}_{8}(t))$$

$$= C^{-1}(-\mathcal{F}(\mathbf{V}_{2}(t)) + \mathbf{I}_{8}(t)). \tag{3.5}$$

Note, the inverse of C exists because C is diagonally dominant as mentioned before. From successive differentiations of  $\dot{\mathbf{V}}_1(t)$  we have that  $\mathbf{V}_1^{(k)}(t_0)$  is a function of  $\mathbf{V}_1^{(i)}(t_0)$  and  $\mathbf{I}_{\mathbf{S}}^{(i)}(t_0)$  for i < k. Similarly,  $\mathbf{V}_2^{(k)}(t_0)$  is the same function of  $\mathbf{V}_2^{(i)}(t_0)$  and  $\mathbf{I}_{\mathbf{S}}^{(i)}(t_0)$  for i < k. Since  $\mathbf{V}_1^{(i)}(t_0) = \mathbf{V}_2^{(i)}(t_0) \ \forall \ i < k$ , we find that  $\mathbf{V}_1^{(k)}(t_0)$  is equal to  $\mathbf{V}_2^{(k)}(t_0)$ , which contradicts that  $t_0$  is a departing point for  $\mathbf{V}_1(t)$  and  $\mathbf{V}_2(t)$ .

Theorem 1 tells us that for the numerical integration of Eq.(3.2) although we do not know the function G after the current time t, we do know the time derivatives of G at t up to the infinite order and thus can uniquely determine G for a small time interval beyond t. This can in turn be used to determine V for that small interval T. The sufficient condition of theorem 1 is that F of Eq.(3.1) be continuously differentiable, which seems rather restrictive because it excludes piecewise continuous i-V characteristics. To relax this restriction for the purpose of numerical integration we

use small time steps only when any piecewise characteristic in the circuit undergoes

two different operating regions, and

<sup>&</sup>lt;sup>3</sup> For the integration from  $t_n$  to  $t_{n+1}$ , we only know  $\mathcal{F}(V(t))$  is equal to G(t)V(t) up to  $t_n$ . The above proves that  $\mathcal{F}(V(t))$  will be equal to G(t)V(t) from  $t_n$  to  $t_{n+1}$  once they coincide with each other up to  $t_n$ .

• use an absolutely stable integration scheme.

Then, even though the sufficient condition is not satisfied strictly, the numerical solution of Eq.(3.2) can still yield very good accuracy <sup>4</sup>.

# 3.2 The Stepwise Equivalent Conductance Integration Algorithm.

For the integration of each time step, we assume that the equivalent conductances of the time-varying conductors remain constant during the time step. Therefore, for the calculation purpose, we are dealing only with linear constant circuit elements. The constant value assumed for each time-varying conductor can be determined to yield the necessary accuracy<sup>5</sup>.

Using Taylor's series expansion of G(t) at  $t = t_n$ , we obtain from Eq.(3.2)

$$[G(t_n) + \dot{G}(t_n)(t - t_n) + \frac{1}{2}\ddot{G}(t_n)(t - t_n)^2 + \cdots]V(t) + C\dot{V}(t) = I_s(t).$$

(3.6)

Let

$$h_n = t_{n+1} - t_n. (3.7)$$

We show that for  $t \in [t_n, t_{n+1}]$  Eq.(3.6) can be approximated by

$$\mathcal{G}\mathbf{V}(t) + \mathbf{C}\dot{\mathbf{V}}(t) = \mathbf{I}_{\mathbf{S}}(t), \tag{3.8}$$

<sup>&</sup>lt;sup>4</sup>It must be emphasized that the above theorem provides only sufficient conditions. Hence, even if the circuit does not satisfy the continuous differentiability condition, the exactness of the transformation may still hold.

<sup>&</sup>lt;sup>5</sup>At first glance, our approach may seem similar to Crystal [26] since both exploit the idea of using effective conductances. For the whole transition, Crystal replaces every MOS transistor by an effective conductor to estimate the timing information. There is no integration in Crystal. Whereas, our approach is trying to determine the effective conductances which can summarize the total electrical effects during a time step. Furthermore, the goal of our approach is to determine the complete transient characteristics.

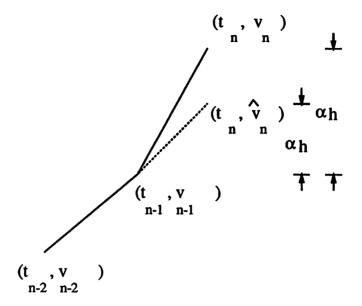

with  $G = G(t_n) + \frac{h_n}{2}\dot{G}(t_n)$ . To solve  $V(t_{n+1})$  from a given  $V(t_n)$  an error is introduced which is proven in Appendix B to be

$$-C^{-1}\ddot{G}(t_n)V(t_n)(\frac{h_n^3}{6})-C^{-1}\dot{G}(t_n)(C^{-1}G(t_n)V(t_n)+\dot{V}(t_n))(\frac{h_n^3}{12}).$$

(3.9)

By using the trapezoidal rule of integration, we obtain

$$\mathbf{V}_{n+1} = [\mathcal{G} + \frac{2}{h_n}C]^{-1}(\frac{2}{h_n}C\mathbf{V}_n + C\dot{\mathbf{V}}_n + \mathbf{I}_{s_{n+1}}).$$

(3.10)

This leads to the total local truncation error for the integration from  $t_n$  to  $t_{n+1}$  of the order  $O(h^3)$ . The method is therefore consistent with respect to the local truncation error, and since we know that the integration scheme, the trapezoidal rule, is absolutely stable, we have demonstrated the convergence of the algorithm.

#### 3.3 Time Step Selection.

The local truncation error for each integration will be equal to the error given in Eq.(3.9) plus the error introduced from the trapezoidal rule approximation of  $\dot{\mathbf{V}}(t_{n+1})$ . Therefore, given the error criterion on the local truncation error at  $t_n$ , we can solve for the necessary time step  $h_n$  exactly. A variable time step integration scheme can be implemented. However, Eq.(3.9) is very complicated. Determining  $h_n$  involves several matrix operations. It would be impractical to perform the matrix operations at every time point. Therefore, we introduce a simpler scheme of choosing  $h_n$ . By using two parameters, a voltage error  $\Delta V$  and a relative error  $\epsilon$ , we can derive the following: For each conductance  $G_i$  and for each node voltage  $V_j$ , if  $h_n$  meets the constraints imposed on Eq.(3.11), then the norm of

the error introduced in Eq.(3.9) will be less than  $\frac{\epsilon}{3}\Delta V$ , which is derived in Appendix C.

$$(|\frac{\ddot{G}_i(t_n)h_n^2}{G_i(t_n)}|) \le \epsilon \quad \forall i, \tag{a}$$

$$(|\frac{\dot{G}_i(t_n)h_n}{G_i(t_n)}|) \le \epsilon \quad \forall i,$$

(b)

and,

$$h_n \dot{V}_j(t_n) \le \Delta V \quad \forall j.$$

(3.11)

The advantage of this is that the computation of determining a time step meeting all the constraints in Eq.(3.11) is linear in terms of nodes or devices in the circuit, while the computation needed to solve Eq.(3.9) is of the cubic order.

This concludes the introduction of our Stepwise Equivalent Conductance circuit simulation technique. As the first application of the technique, a digital CMOS circuit simulator SWEC was implemented, which will be discussed in the next chapter.

## Chapter 4

SWEC: A Stepwise Equivalent

Conductance CMOS Circuit

Simulator.

When applying the Stepwise Equivalent Conductance Circuit Simulation Technique to digital CMOS circuits, we demonstrate that additional speedups can be achieved by the use of a specific event-driven approach to take advantage of the piecewise linear waveforms. Most of the time the voltage waveforms of the outputs from CMOS gates behave like straight line segments. We will show how to make use of this property in the timing simulation in this chapter. The program, called SWEC, has been implemented, and has proven to be accurate and efficient on a large number of circuit examples. The comparisons of results with Relax2.3[6], iSPLICE3.0[7, 17], XPsim[8], and SPECS2[9] will be given in this chapter.

The chapter is organized as follows. Section 4.1 gives an introduction to SWEC. In section 4.2, we discuss SWEC's MOS Electrical models and the time step selection for it. Section 4.3 presents our piecewise linear waveform approximation. In section 4.4, we discuss SWEC's event-driven mechanism, which exploits the piecewise linear voltage waveform property, in detail. In section 4.5, we present experimental results of SWEC along with comparisons with SPICE, iSPLICE3.0, Relax2.3, XPsim, and SPECS2 programs.

#### 4.1 Introduction.

As an application, a timing simulator for digital CMOS VLSI circuits, SWEC, has been implemented based on the concepts introduced in chapter 3 and [4, 10]. To further speed up the simulation, SWEC first decomposes the circuit into weakly coupled subcircuits and applies the Stepwise Equivalent Conductance technique to each of the subcircuits. In addition, SWEC exploits another special property of CMOS circuits, that is, the voltage waveform can be modeled with piecewise-linear segments connected between regions with smooth curves. Thus, the voltage waveforms of the outputs from CMOS gates behave like straight line segments most of the time. Because of this property, larger time steps can be used. To handle feedback inside the circuits and to further exploit the latency and multirate behavior of MOS circuits, a special event driven mechanism based on the piecewise linearity of waveforms has also been developed and built into SWEC. We have developed an algorithm to determine the break points of the piecewise-linear voltage waveforms under the desired accuracy requirements.

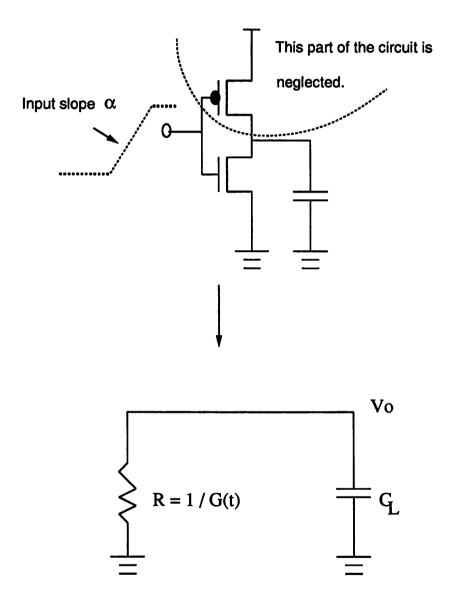

Figure 4.1: Electrical Model for a MOS transistor

#### 4.2 MOS Electrical Models and Time Step Selection of SWEC.

The analytical expression for the G(t) of a MOS transistor is given by the conventional formula:

$$G(t) = \beta * (2 * (V_{GS} - V_{th}) - V_{DS})|_{t} \quad if \quad V_{GS} - V_{th} \ge V_{DS} \ge 0,$$

$$G(t) = \beta * \frac{(V_{GS} - V_{th})^{2}}{V_{DS}}|_{t} \quad if \quad V_{DS} > V_{GS} - V_{th} \ge 0,$$

$$G(t) = 0.0, \quad if \quad V_{GS} < V_{th}, \tag{4.1}$$

where  $V_{th}$ , the threshold voltage, is a function of  $V_{SB}$ . Fig. 4.1 shows the electrical model of a MOS transistor. Between the drain node and the source node there is a time varying conductor with the conductance G(t). The voltage at the gate node is represented by the voltage sources  $V_{G_t}$ . The grounded capacitors,  $C_D$  and  $C_S$ , represent the side-wall and bottom junction grounded capacitances at the drain and the source nodes, respectively.  $C_G$  is the gate oxide capacitance and wiring capacitance.  $C_{GD}$  and  $C_{GS}$  represent the gate-to-drain and gate-to-source overlap capacitances, respectively. Note that they are lumped with  $C_G$  at the gate node  $G_t$  as an approximate total capacitance looking at that node. Since in general  $C_G$  is much larger than  $C_{GS}$  or  $C_{GD}$ , turning  $C_{GS}$  or  $C_{GD}$  into grounded capacitors is a reasonable simplification when looking at the gate node. However, this is not true when looking at the source or drain node because  $C_D$  is comparable with  $C_{GD}$ , and  $C_S$  is comparable with  $C_{GS}$ . We account for this by introducing the two voltage sources  $V_{G_t}$  representing the effects coming from the gate node.

In this way, the determination of the gate voltage does not depend on the voltage at the source node or the voltage at the drain node as long as there is no other charge transfer path (resistor, capacitor, transistor channel) connected between them. Furthermore, if the gate voltage is evaluated prior to the evaluation of the voltages of the source node and the drain node then  $V_{G_t}$  can be treated as a constant voltage source in determining the voltages of the source node and the drain node. If we can keep this ordering correct during the simulation, then solving the voltage at the gate node can be separated from solving them at the source and the drain nodes, and no iterations are needed between the two solving processes. Our event-driven approach is based on this idea and will be discussed in section 4.4.

Since there is no direct charge transfer path between the gate node and the conducting channel of the transistor (one-way circuits), we are able to perform circuit partitioning [40]. Prior to simulation, the circuit is partioned into subcircuits. They are tightly coupled groups of nodes connected by a charge transfer path. Each subcircuit is integrated with its own time step to take advantage of the time latency existing in the circuit. The integration of each subcircuit employs the stepwise equivalent conductance technique. For a subcircuit, the time steps are determined according to the slopes at inputs and the value of the equivalent conductance of each transistor before integration.

The conductance of each transistor used for the integration from  $t_n$  to  $t_n + h_n$  is  $\mathcal{G}_n$ , which is equal to  $G(t_n) + \frac{h_n}{2} \dot{G}(t_n)$ . The expressions are as follows:

$$\mathcal{G}_{n} = G(t_{n}) + \frac{h_{n}}{2}\beta * (2\dot{V}_{GS} - \dot{V}_{DS})|_{t_{n}} \quad if \quad V_{GS} - V_{th} \ge V_{DS} \ge 0,$$

$$\mathcal{G}_{n} = G(t_{n}) + \frac{h_{n}}{2}\beta * (2\frac{V_{GS} - V_{th}}{V_{DS}}\dot{V}_{GS})|_{t_{n}} \quad if \quad V_{DS} > V_{GS} - V_{th} \ge 0,$$

$$\mathcal{G}_{n} = 0.0 \quad if \quad V_{GS} < V_{th}.$$

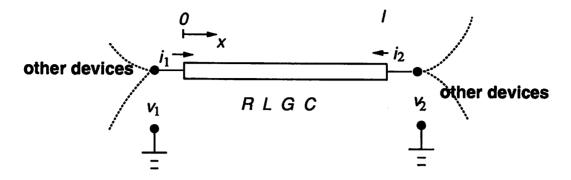

(4.2)