# High-Performance Image Processing Using Special-Purpose CPU Instructions: The UltraSPARC Visual Instruction Set

Copyright © 1996

by Daniel S. Rice

Master's Report under the direction of Carlo Séquin

Computer Science Division Department of Electrical Engineering and Computer Science University of California, Berkeley

March 19, 1996

#### Abstract

The UltraSPARC-I processor implements, in addition to the SPARC v9 instruction set, a set of new instructions that accelerate image and video processing – the visual instruction set, or VIS. These instructions address a number of areas in which traditional instructions perform poorly for these highly parallel tasks. Although these instructions support a wide variety of functions, they represent far less implementation effort than that needed to design dedicated imaging hardware because they leverage the design efforts of the CPU and memory system, and will continue to provide performance improvements as the processor speed is increased.

Unlike traditional CPU features, the performance benefits of such instructions have not been quantified. We attempt to demonstrate the performance effects of the VIS instructions in the context of typical image processing loops.

For the greatest benefit, these instructions must be used with an eye to maximizing various forms of parallelism, including superscalar instruction issue, loop vectorization, and pipelining in both hardware and software. Currently much of this work must be done by hand. We propose some ways to automate portions of this process and describe some of the existing tools.

# Contents

|          | Intr                                                                       | oduction                                                                                                                                                                           | 1                                                        |

|----------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| <b>2</b> | Acc                                                                        | elerated Image Processing                                                                                                                                                          | 2                                                        |

|          | 2.1                                                                        | Dedicated Imaging Hardware                                                                                                                                                         | 2                                                        |

|          | 2.2                                                                        | Imaging In The Graphics Accelerator                                                                                                                                                | 3                                                        |

|          | 2.3                                                                        | Interfacing With The Cache                                                                                                                                                         | 3                                                        |

|          | 2.4                                                                        | The Intel i860                                                                                                                                                                     | 5                                                        |

|          | 2.5                                                                        | The Hewlett-Packard PA-7100LC                                                                                                                                                      | 5                                                        |

|          | 2.6                                                                        | The Intel MMX Enhancements                                                                                                                                                         | 6                                                        |

|          | 2.7                                                                        | The UltraSPARC-I                                                                                                                                                                   | 6                                                        |

|          |                                                                            | 2.7.1 Superscalar Instruction Issue                                                                                                                                                | 7                                                        |

|          |                                                                            | 2.7.2 Branch Prediction and Following                                                                                                                                              | 7                                                        |

|          |                                                                            |                                                                                                                                                                                    | 8                                                        |

|          |                                                                            |                                                                                                                                                                                    | 9                                                        |

|          |                                                                            |                                                                                                                                                                                    | 9                                                        |

|          |                                                                            |                                                                                                                                                                                    | 10                                                       |

|          | 2.8                                                                        |                                                                                                                                                                                    | 10                                                       |

|          | $2.8 \\ 2.9$                                                               |                                                                                                                                                                                    | 12                                                       |

|          |                                                                            |                                                                                                                                                                                    | 13                                                       |

|          |                                                                            | 3                                                                                                                                                                                  | L3<br>[3                                                 |

|          | 2.11                                                                       |                                                                                                                                                                                    | IJ                                                       |

| 3        | Cha                                                                        | racterization of Imaging Tasks 1                                                                                                                                                   | 4                                                        |

|          | 3.1                                                                        |                                                                                                                                                                                    | 14                                                       |

|          | 3.2                                                                        |                                                                                                                                                                                    | 17                                                       |

|          | 3.3                                                                        | 1 0 0                                                                                                                                                                              | 22                                                       |

|          |                                                                            |                                                                                                                                                                                    |                                                          |

| 4        | The                                                                        |                                                                                                                                                                                    | <b>22</b>                                                |

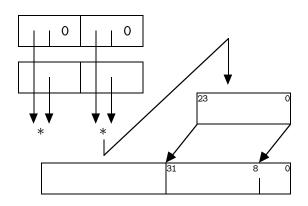

|          | 4.1                                                                        | Data Formats and Conversions                                                                                                                                                       | 23                                                       |

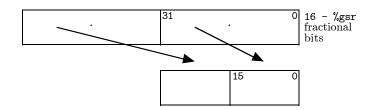

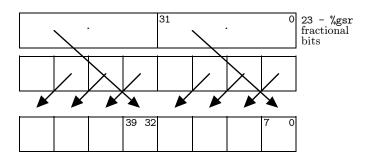

|          |                                                                            | 4.1.1 The Graphics Status Register                                                                                                                                                 | $\underline{23}$                                         |

|          |                                                                            | 4.1.2 Expansion                                                                                                                                                                    | 24                                                       |

|          |                                                                            | 4.1.3 Packing                                                                                                                                                                      | 24                                                       |

|          | 4.2                                                                        | Arithmetic Operators                                                                                                                                                               | 25                                                       |

|          |                                                                            | 4.2.1 Addition and Subtraction                                                                                                                                                     | 27                                                       |

|          |                                                                            |                                                                                                                                                                                    |                                                          |

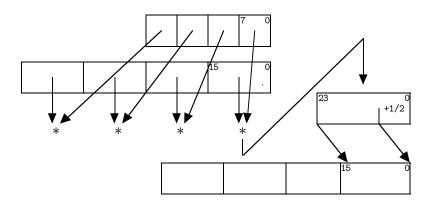

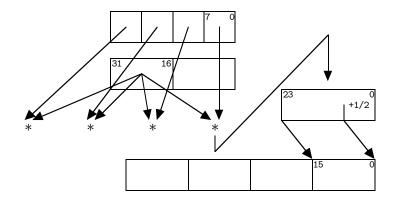

|          |                                                                            | 4.2.2 Multiplication                                                                                                                                                               | 27                                                       |

|          | 4.3                                                                        | 1                                                                                                                                                                                  |                                                          |

|          | 4.3<br>4.4                                                                 | Logical Operators                                                                                                                                                                  | 27                                                       |

|          |                                                                            | Logical Operators3Merging3                                                                                                                                                         | 27<br>31                                                 |

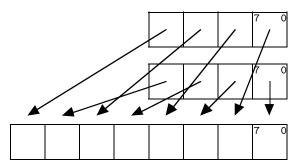

|          | $\begin{array}{c} 4.4 \\ 4.5 \end{array}$                                  | Logical Operators       3         Merging       3         Alignment Operators       3                                                                                              | 27<br>31<br>31<br>32                                     |

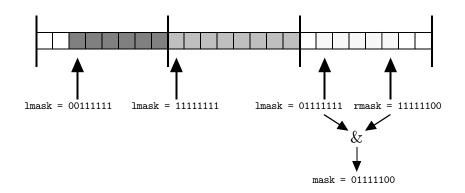

|          | 4.4                                                                        | Logical Operators       3         Merging       3         Alignment Operators       3         Edge Masking and Comparison       3                                                  | 27<br>31<br>31<br>32<br>33                               |

|          | $\begin{array}{c} 4.4 \\ 4.5 \end{array}$                                  | Logical Operators3Merging3Alignment Operators3Edge Masking and Comparison34.6.1Edge MaskingEdge Masking3                                                                           | 27<br>31<br>31<br>32<br>33<br>33                         |

|          | $4.4 \\ 4.5 \\ 4.6$                                                        | Logical Operators3Merging3Alignment Operators3Edge Masking and Comparison34.6.1Edge Masking4.6.2Partitioned Comparison                                                             | 27<br>31<br>32<br>33<br>33<br>34                         |

|          | 4.4<br>4.5<br>4.6<br>4.7                                                   | Logical Operators3Merging3Alignment Operators3Edge Masking and Comparison34.6.1Edge Masking4.6.2Partitioned Comparison9Partial Stores3                                             | 27<br>31<br>32<br>33<br>33<br>33<br>34<br>35             |

|          | $ \begin{array}{r} 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ \end{array} $        | Logical Operators3Merging3Alignment Operators3Edge Masking and Comparison34.6.1Edge Masking4.6.2Partitioned Comparison9Partial Stores3Short and Block Loads and Stores3            | 27<br>31<br>31<br>32<br>33<br>33<br>33<br>34<br>35<br>35 |

|          | $ \begin{array}{r} 4.4 \\ 4.5 \\ 4.6 \\ 4.7 \\ 4.8 \\ 4.9 \\ \end{array} $ | Logical Operators3Merging3Alignment Operators3Edge Masking and Comparison34.6.1Edge Masking4.6.2Partitioned Comparison9Partial Stores3Short and Block Loads and Stores3Miscellany3 | 27<br>31<br>32<br>33<br>33<br>33<br>34<br>35             |

| <b>5</b> | Sou                 | rces of Speedups                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>40</b>  |

|----------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|          | 5.1                 | Superscalarity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 41         |

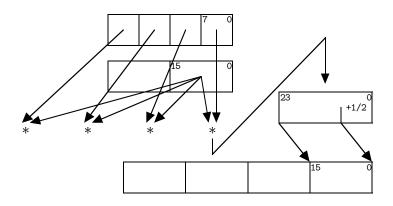

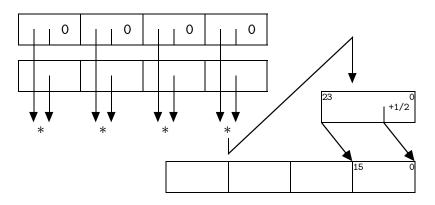

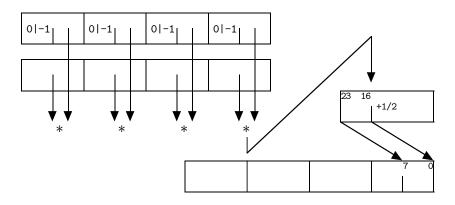

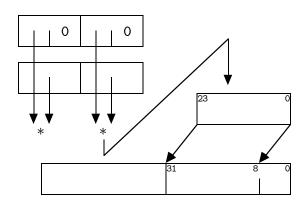

|          | 5.2                 | Alignment and Partitioned Arithmetic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41         |

|          | 5.3                 | Unconditional Clamping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 42         |

|          | 5.4                 | Use of Floating Point Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 42         |

| 6        | Con                 | npilation Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 42         |

| Ŭ        | 6.1                 | Inline Templates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 42         |

|          | 0.1                 | 6.1.1 Prototypes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 44         |

|          | 6.2                 | Simulating VIS Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 44         |

|          | 6.3                 | Instruction Grouping Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 46         |

|          | 6.4                 | Superscalar Code Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 46         |

|          | 0.1                 | 6.4.1 Basic Block Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46         |

|          |                     | 6.4.2 Loop Unrolling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48         |

|          |                     | 6.4.3 Software Pipelining                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 49         |

|          |                     | 6.4.4 Modulo Scheduling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49         |

|          | 6.5                 | Register Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 52         |

|          | 0.0                 | 6.5.1 Register Coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $52 \\ 52$ |

|          |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 01         |

| 7        | VIS                 | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 53         |

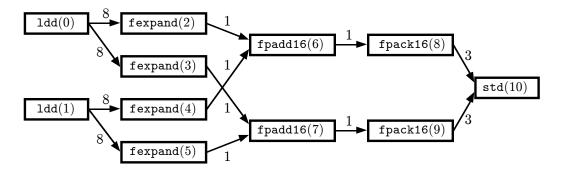

|          | 7.1                 | Addition With Clamping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 54         |

|          | 7.2                 | Blending Using a Mask Image                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58         |

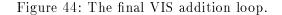

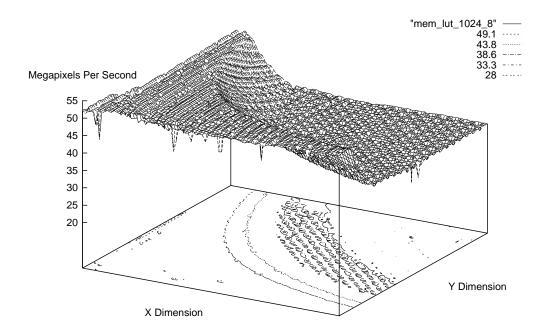

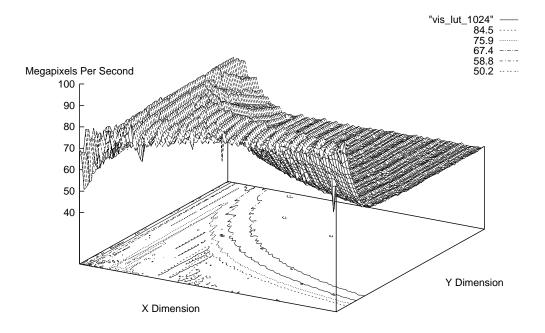

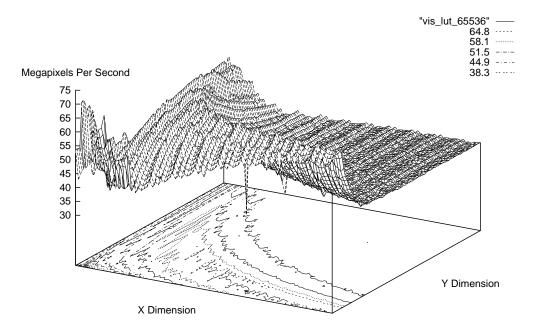

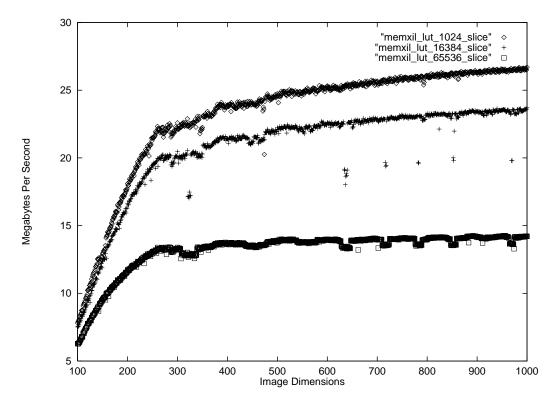

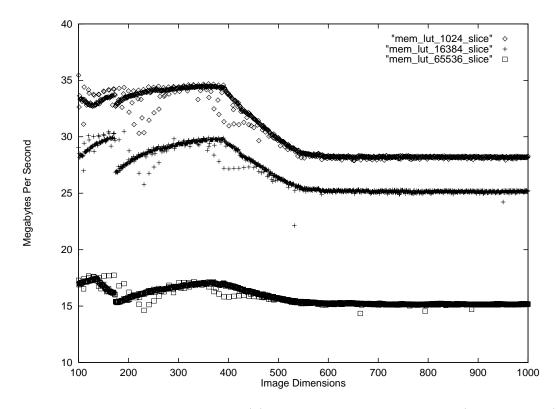

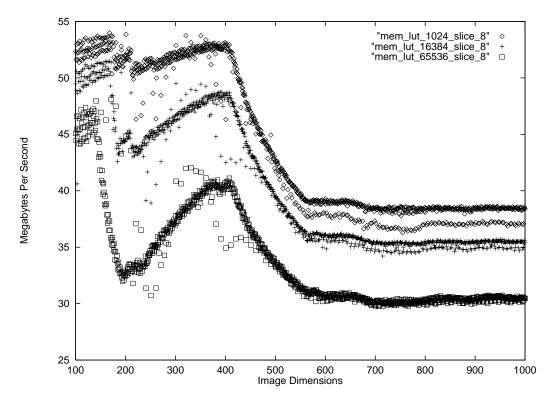

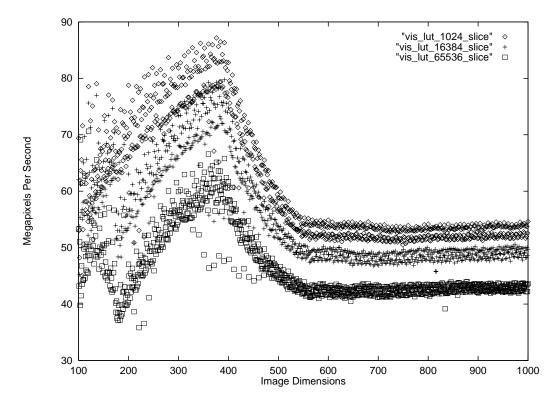

|          | 7.3                 | 16- to 8-Bit Table Lookup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60         |

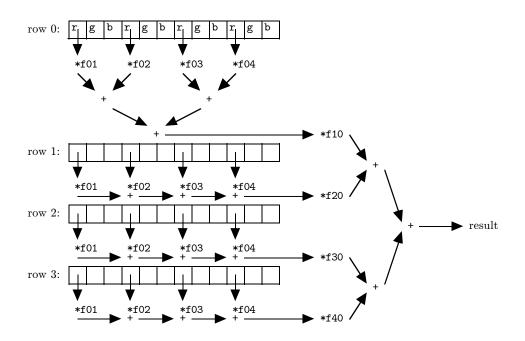

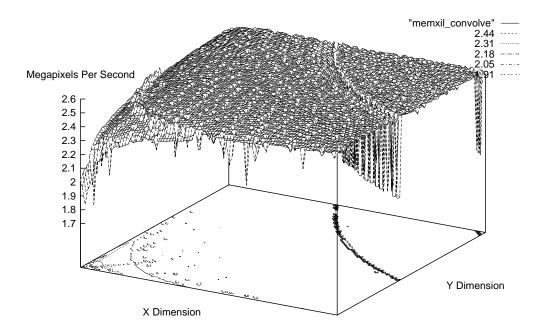

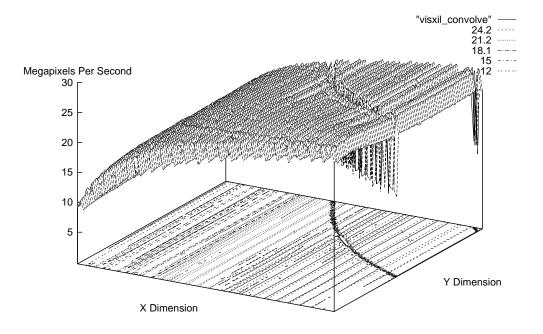

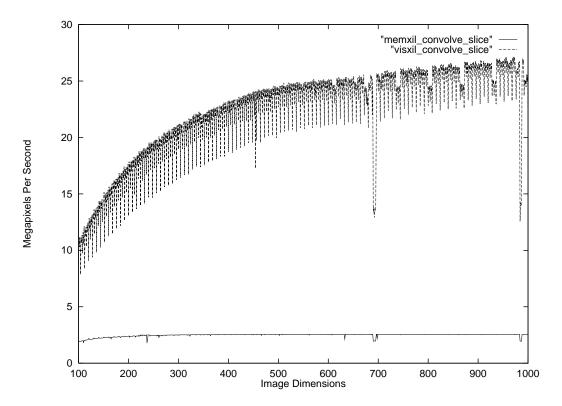

|          | 7.4                 | Convolution With Small Kernels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 62         |

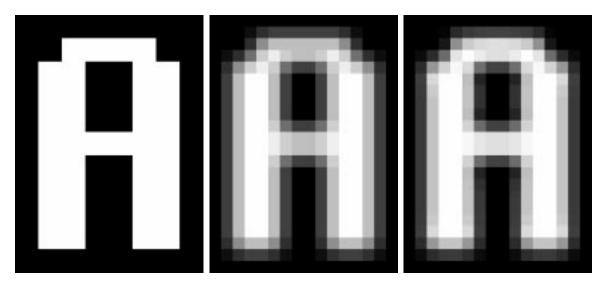

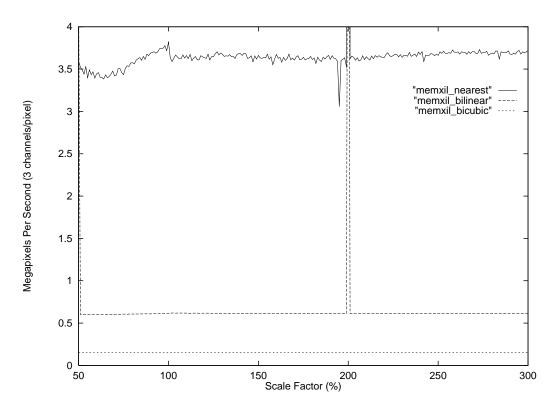

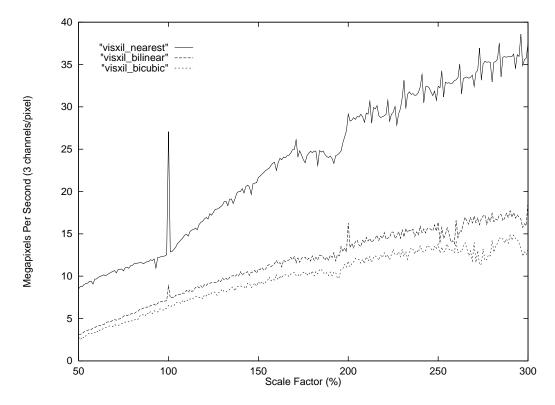

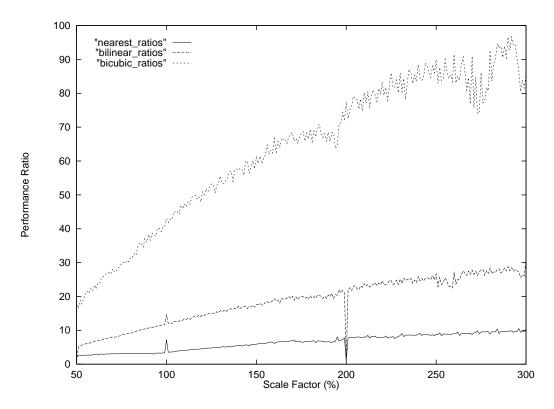

|          | 7.5                 | Resizing Using Bicubic Interpolation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 65         |

|          | 7.6                 | Bilinear Scaling by Two                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76         |

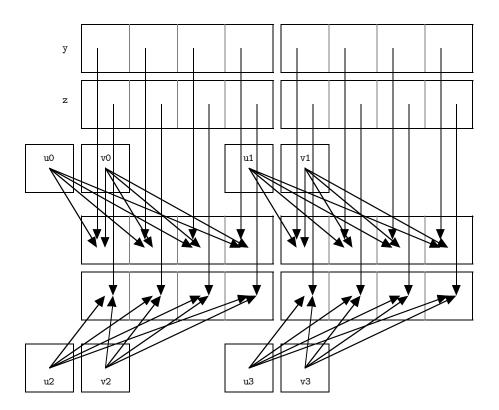

|          | 7.7                 | Conversion From YUV to RGB Color Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 77         |

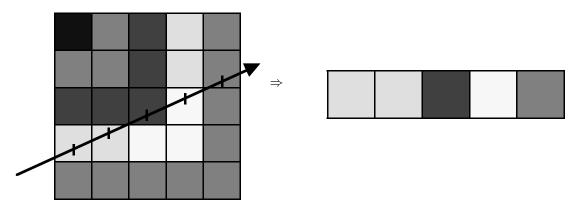

|          | 7.8                 | Gouraud Shading and Texture Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80         |

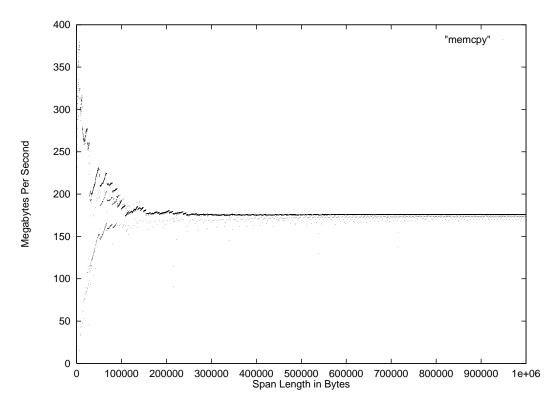

| 8        | $\mathbf{Tim}$      | ning Comparisons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 83         |

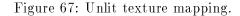

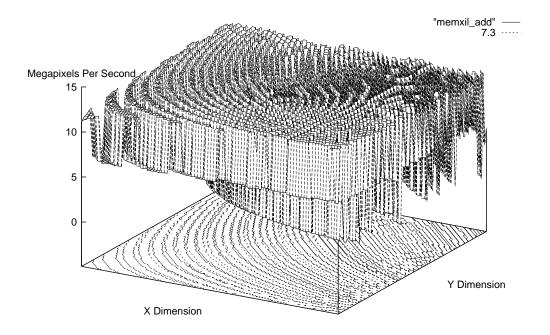

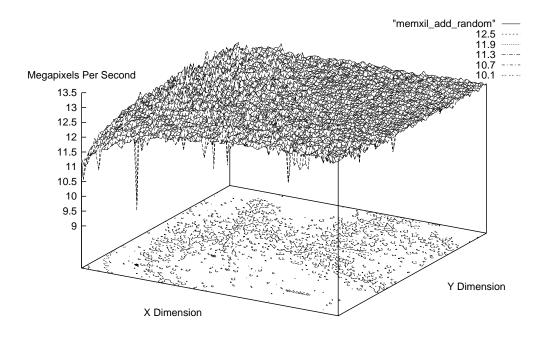

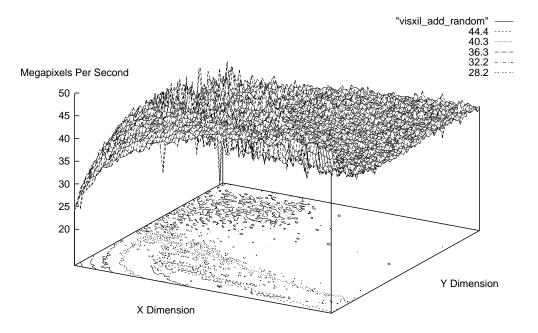

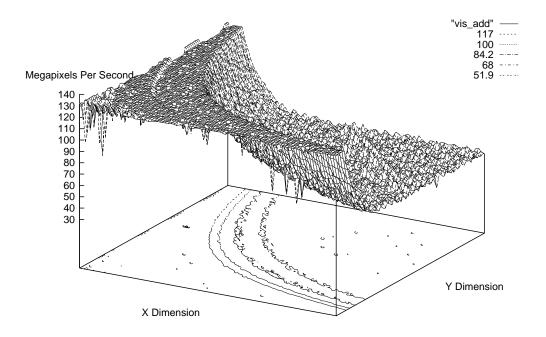

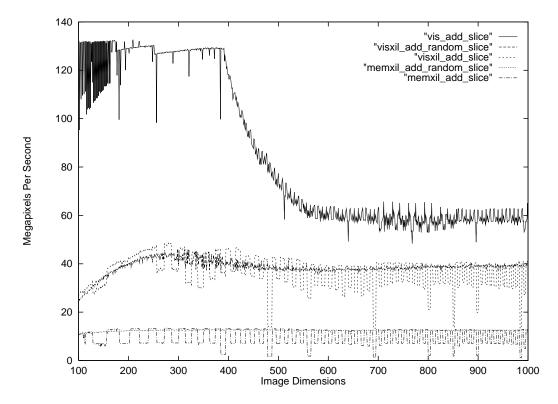

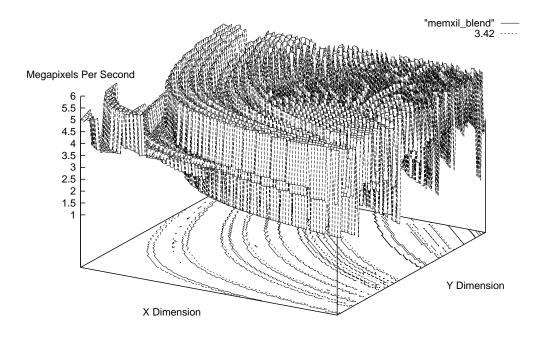

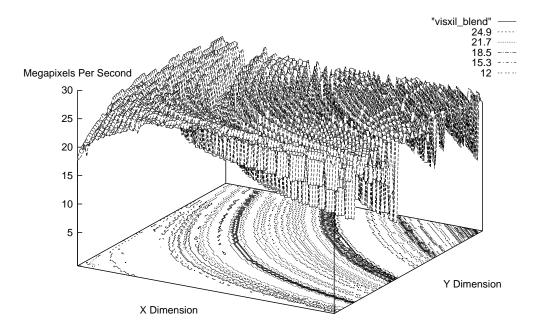

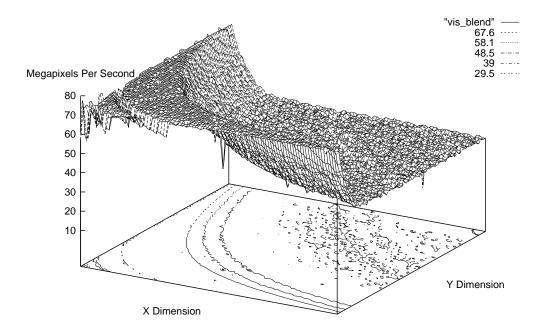

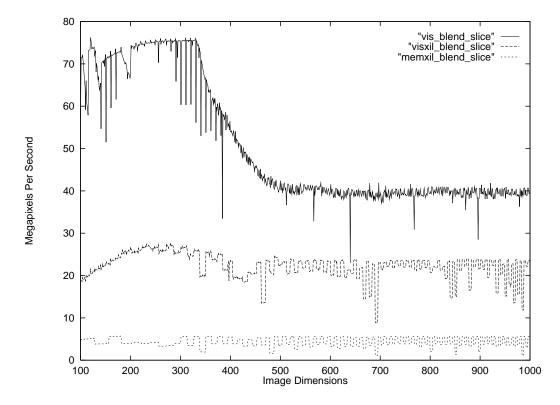

|          | 8.1                 | Addition and Alpha Blending                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84         |