### Efficient Resource Scheduling in Multiprocessors

by

Soumen Chakrabarti

Master of Science, University of California, Berkeley, 1992 Bachelor of Technology, Indian Institute of Technology, Kharagpur, 1991

> A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

> > in

Computer Science

in the

### GRADUATE DIVISION of the UNIVERSITY of CALIFORNIA at BERKELEY

Committee in charge:

Professor Katherine Yelick, Computer Science, Chair Professor James Demmel, Computer Science and Mathematics Professor Dorit Hochbaum, Industrial Engineering and Operations Research

1996

The dissertation of Soumen Chakrabarti is approved:

Chair

Date

Date

Date

University of California at BERKELEY

1996

### Efficient Resource Scheduling in Multiprocessors

Copyright 1996 by Soumen Chakrabarti

### Abstract

Efficient Resource Scheduling in Multiprocessors

by

Soumen Chakrabarti Doctor of Philosophy in Computer Science

University of California at BERKELEY

Professor Katherine Yelick, Computer Science, Chair

As multiprocessing becomes increasingly successful in scientific and commercial computing, parallel systems will be subjected to increasingly complex and challenging workloads. To ensure good job response and high resource utilization, algorithms are needed to allocate resources to jobs and to schedule the jobs. This problem is of central importance, and pervades systems research at diverse places such as compilers, runtime, applications, and operating systems. Despite the attention this area has received, scheduling problems in practical parallel computing still lack satisfactory solutions. The focus of system builders is to provide functionality and features; the resulting systems get so complex that many models and theoretical results lack applicability.

The focus of this thesis is in between the theory and practice of scheduling: it includes modeling, performance analysis and practical algorithmics. We present a variety of new techniques for scheduling problems relevant to parallel scientific computing. The thesis progresses from new compile-time algorithms for message scheduling through new runtime algorithms for processor scheduling to a unified framework for allocating multiprocessor resources to competing jobs while optimizing both individual application performance and system throughput.

The compiler algorithm schedules network communication for parallel programs accessing distributed arrays. By analyzing and optimizing communication patterns globally, rather than at the single statement level, we often reduce communication costs by factors of two to three in an implementation based on IBM's High-Performance Fortran compiler.

The best parallelizing compilers at present support regular, static, array-based

parallelism. But parallel programmers are out-growing this model. Many scientific and commercial applications have a two-level structure: the outer level is a potentially irregular and dynamic task graph, and the inner level comprises relatively regular parallelism within each task. We give new runtime algorithms for allocating processors to such tasks. The result can be a twofold increase in effective megaflops, as seen from an implementation based on ScaLAPACK, a library of scientific software for scalable parallel machines.

Compilers and runtime systems target single programs. Other system software must do resource scheduling across multiple programs. For example, a database scheduler or a multiprocessor batch queuing system must allocate many kinds of resources between multiple programs. Some resources like processors may be traded for time, others, like memory, may not. Also, the goal is not to finish a fixed set of programs as fast as possible but to minimize the average response time of the programs, perhaps weighted by a priority. We present new algorithms for such problems.

Most of the above results assume a central scheduler with global knowledge. When the setting is distributed, decentralized techniques are needed. We study how decentralization and consequent local knowledge by per-processor schedulers affects load balance in fine-grained task-parallel applications. In particular, we give new protocols for distributed load balancing and bounds on the trade-off between locality and load balance. The analysis has been supported by experience with implementing task queues in Multipol, a library for coding dynamic, irregular parallel applications.

> Professor Katherine Yelick, Computer Science Dissertation Committee Chair

রবীন্দ্রনাথ ঠাকুর

না গো, এই যে ধূলা আমার না এ। ডোমার ধূলার ধরার °পরে উড়িয়ে যাব সন্ধ্র্যাবায়ে॥ দিয়ে মাটি আগুন জ্বলি রচলে দেহ পূজ্যার থালি— শেষ আরতি সারা করে ভেঙ্গে যোব তোমার পায়ে॥ ফুল যা ছিল পূজ্যার তরে যেতে পথে ডালি হতে অনেক যে তার গেছে পড়ে। কত প্রদীপ এই থালাতে সাজিয়েছিলে আপন হাতে— কত যে তার নিবল হাওয়ায়, পৌঁছলনা চর+ছায়ে॥

### Acknowledgements

I am grateful to Kathy for her support and encouragement throughout my stay at Berkeley, and Jim, for getting me started on scheduling problems for mixed parallel applications in scientific computing. I am greatly indebted to Professor Dorit Hochbaum for reading my thesis at an incredibly short notice. I am grateful to Professors Richard Karp and Ron Wolff for being on my quals committee and asking questions which led to further studies. Thanks to Joel Wein for introducing me to the area of minsum scheduling. Thanks to Abhiram for helping me analyze some random task allocation algorithms. It was a pleasure working with Mike Mitzenmacher, Micah Adler and Lars Rasmussen on more random allocation problems. I owe the work on compile-time message scheduling to Manish Gupta, Jong-Deok Choi, Edith Schonberg and Harini Srinivasan at IBM T. J. Watson Research Center. I thank Muthu for patient hearing while I clear jumbled thoughts.

I am grateful to many other people for helping me through graduate school in many ways. In particular, I wish to thank Savitha and Sudha Balakrishnan, David Bacon, Prith Banerjee, Janajiban Banik, John Byers, Satish Chandra, Avijit and Amit Chatterjee, Domenico Ferrari, Bhaskar Ghosh, Seth Goldstein, Mor Harchol, Steve Lumetta, P. Pal Chaudhuri, Pradyot and Keya Sen, David Shmoys, Cliff Stein, and Randy Wang for their technical and social support. I thank Kathryn Crabtree, Gail Gran, Gwen Lindsey and Bob Untiedt for keeping "the management" out of my way. I owe this work to my wife, Sunita Sarawagi, who also shared the life of a graduate student, and my parents, Sunil and Arati Chakrabarti, for their continual reassurance.

This work was supported in part by the Advanced Research Projects Agency of the Department of Defense monitored by the Office of Naval Research under contract DABT63-92-C-0026, AT&T, NSF grants (numbers CDA-8722788 and CDA-9401156), a Research Initiation Award (number CCR-9210260), Lawrence Livermore National Laboratory, and DOE (number DE-FG03-94ER25206). The support is gratefully acknowledged. The information presented here does not necessarily reflect the position or the policy of the Government and no official endorsement should be inferred.

## Contents

| Li | st of                                         | Figures                                                                                                    | 3                                                                                                                                                                                                                                    | viii                                                              |

|----|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Li | st of                                         | Tables                                                                                                     |                                                                                                                                                                                                                                      | ix                                                                |

| 1  | <b>Intr</b><br>1.1<br>1.2<br>1.3<br>1.4       | Schedul<br>Schedul                                                                                         | on<br>e scheduling via compiler analysis                                                                                                                                                                                             |                                                                   |

| 2  | Mes<br>2.1<br>2.2                             | Introdu<br>Motivat<br>2.2.1<br>2.2.2                                                                       | heduling via compiler analysisctionctiog codesting codesBeyond redundancy eliminationEarliest placement may hurtSyntax sensitivity                                                                                                   | <b>9</b><br>9<br>11<br>13<br>13<br>14                             |

|    | 2.3<br>2.4                                    | Compile<br>2.4.1 2<br>2.4.2 2<br>2.4.3 2<br>2.4.4 2<br>2.4.5 2<br>2.4.6 2<br>2.4.6 2<br>2.4.7 2<br>2.4.8 4 | k performanceer algorithmsRepresentation and notationIdentifying the latest positionIdentifying the latest positionGenerating candidate positionsSubset eliminationRedundancy eliminationChoosing from the candidatesCode generation | 15     16     18     20     20     24     26     26     28     29 |

|    | <ul><li>2.5</li><li>2.6</li><li>2.7</li></ul> | Extensi<br>2.6.1                                                                                           | General models                                                                                                                                                                                                                       | 30<br>32<br>33<br>35<br>35                                        |

vi

| 3        | $\mathbf{Sch}$ | eduling hybrid parallelism                        | 37              |

|----------|----------------|---------------------------------------------------|-----------------|

|          | 3.1            | Introduction                                      | 37              |

|          | 3.2            | Notation                                          | 39              |

|          | 3.3            | Switched parallel execution                       | 40              |

|          | 0.0            | 3.3.1 Switching a batch                           | 42              |

|          |                | 3.3.2 Precedence graphs                           | 44              |

|          | 3.4            | Modeling and analysis                             | 45              |

|          | 0.1            | 3.4.1 Efficiency of data parallelism              | 46              |

|          |                | 3.4.2 Regular task trees                          | 48              |

|          |                | 3.4.3 Analysis                                    | 51              |

|          |                | 3.4.4 Unbalanced batch problems                   | $51 \\ 52$      |

|          |                | 3.4.5 Simulations                                 | 54              |

|          | 3.5            | Experiments                                       | 58              |

|          | 0.0            | 3.5.1 Software structure                          | 58 - 58         |

|          |                |                                                   | $\frac{58}{59}$ |

|          | 9.0            | 3.5.2 Results                                     |                 |

|          | 3.6            | Related work                                      | 61              |

|          | 3.7            | Discussion                                        | 62              |

| 4        | $\mathbf{Sch}$ | eduling resource constrained jobs                 | 64              |

|          | 4.1            | Introduction                                      | 64              |

|          |                | 4.1.1 Model and problem statement                 | 66              |

|          |                | 4.1.2 Discussion of results                       | 68              |

|          | 4.2            | Motivation                                        | 71              |

|          |                | 4.2.1 Databases                                   | 71              |

|          |                | 4.2.2 Scientific applications                     | 72              |

|          |                | 4.2.3 Fidelity                                    | 72              |

|          | 4.3            | Makespan lower bound                              | $73^{-12}$      |

|          | 4.4            | Makespan upper bound                              | 75              |

|          | 4.5            | Weighted average completion time                  | 78              |

|          | 4.0            | 4.5.1 The bicriteria framework                    | 78              |

|          |                | 4.5.2 DualPack and applications                   | 81              |

|          | 4.6            | Extensions                                        | 84              |

|          | 4.0            |                                                   | 04              |

| <b>5</b> | Dyi            | namic scheduling using parallel random allocation | 86              |

|          | 5.1            | Introduction                                      | 86              |

|          | 5.2            | Random allocation for dynamic task graphs         | 87              |

|          |                | 5.2.1 Models and notation                         | 88              |

|          |                | 5.2.2 Discussion of results                       | 90              |

|          |                | 5.2.3 Weighted occupancy                          | 90              |

|          |                | 5.2.4 Delay sequence                              | 91              |

|          |                | 5.2.5 Empirical evaluation                        | 94              |

|          |                | 5.2.6 Discussions                                 | 96              |

|          | 5.3            | Multi-round load balancing protocols              | 96              |

|          | 0.0            | 5.3.1 The model                                   | 90<br>97        |

|          |                | 5.3.1       The model                             | 97<br>98        |

|          |                | 9.9.2 Dummary Of toburb                           | 00              |

|    |       | 5.3.3  | Threshold protocol     | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 98  |

|----|-------|--------|------------------------|------|---|-------|---|---|---|-------|---|---|-------|---|---|---|---|---|-------|-----|

|    |       | 5.3.4  | Other protocols        | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 106 |

|    |       | 5.3.5  | Concluding remarks     | <br> | • | <br>• | • | • | • | <br>• | • | • | <br>· | • | • | • | • | • | <br>• | 107 |

| 6  | Sur   | vey of | related work           |      |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 108 |

|    | 6.1   | Comm   | unication scheduling   | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 108 |

|    | 6.2   | Multip | rocessor scheduling .  | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 109 |

|    | 6.3   | Minsu  | m metrics              | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 109 |

|    | 6.4   | Resour | ce scheduling          | <br> |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 110 |

|    |       |        | outed load balancing . |      |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       |     |

|    |       |        | ends                   |      |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       |     |

| 7  | Con   | clusio | 1                      |      |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 113 |

| Bi | bliog | graphy |                        |      |   |       |   |   |   |       |   |   |       |   |   |   |   |   |       | 115 |

# List of Figures

| 2.1          | The need for combining communication.                                                                                                                   | 12  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2          | Earliest placement may lose valuable opportunity for message combining.                                                                                 | 12  |

| 2.3          | Syntax sensitivity of earliest placement.                                                                                                               | 12  |

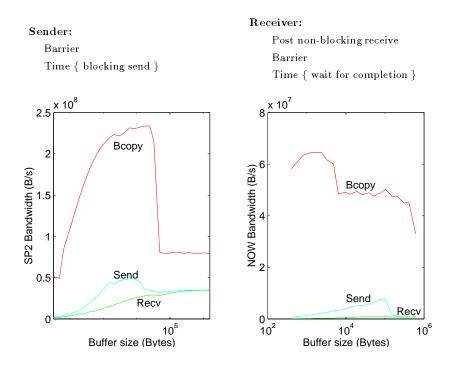

| 2.4          | Buffer copying and network bandwidth studies on the IBM SP2 and the                                                                                     |     |

|              | Berkeley NOW                                                                                                                                            | 16  |

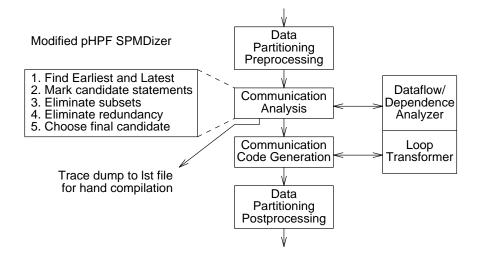

| 2.5          | Prototype modifications to the IBM pHPF SPMDizer                                                                                                        | 17  |

| 2.6          | Running example for analysis and optimization steps.                                                                                                    | 18  |

| 2.7          | Augmented single static assignment representation                                                                                                       | 19  |

| 2.8          | Pseudocode for locating Earliest and Latest.                                                                                                            | 21  |

| 2.9          | Pseudocode for choosing from the candidate positions to place communication.                                                                            | 25  |

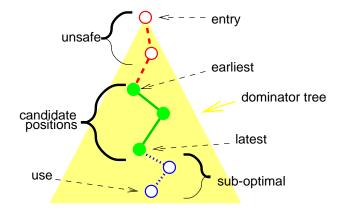

| 2.10         | The candidate communication positions on the dominator tree                                                                                             | 26  |

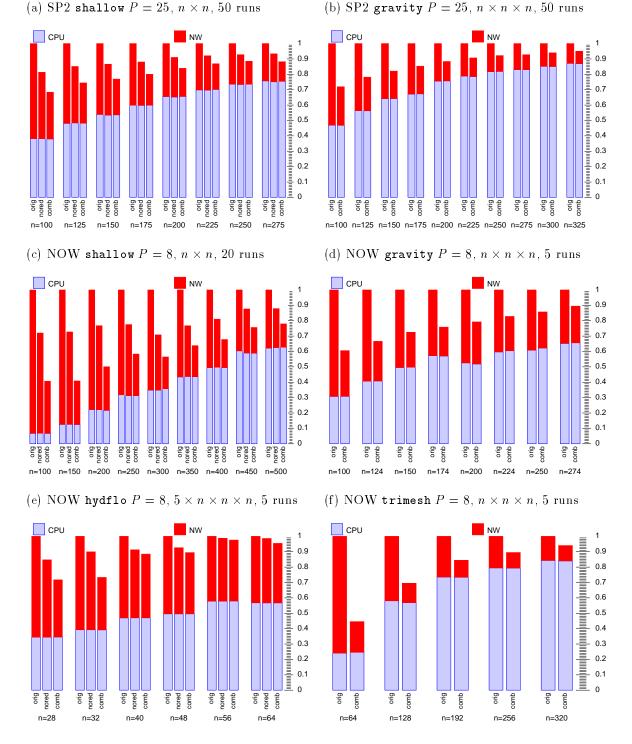

| 2.11         | Performance benefits of the new algorithm: normalized running times                                                                                     | 31  |

| 3.1          | An example application with dynamic irregular mixed parallelism                                                                                         | 40  |

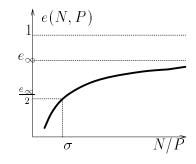

| 3.2          | The proposed efficiency model for data parallelism within a single task. $\therefore$                                                                   | 47  |

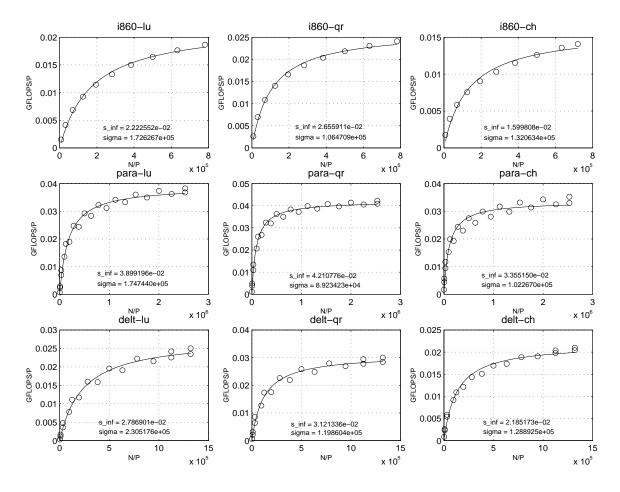

| 3.3          | Validation of the asymptotic model using data from ScaLAPACK                                                                                            | 49  |

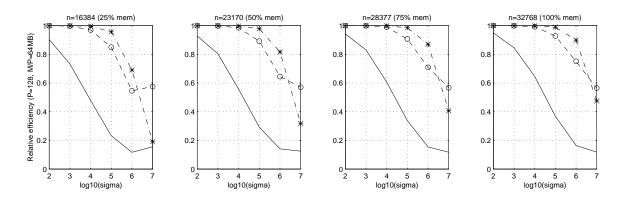

| 3.4          | Variation of efficiency with $\sigma$ in sparse Cholesky                                                                                                | 56  |

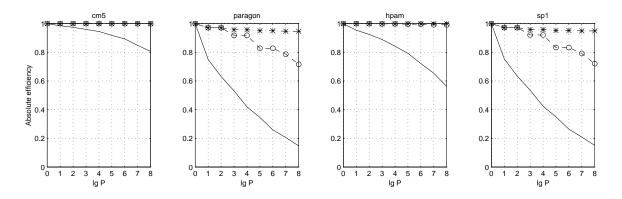

| 3.5          | Scalability of sparse Cholesky on four machines using mixed, switched, and                                                                              |     |

|              | data parallelism.                                                                                                                                       | 56  |

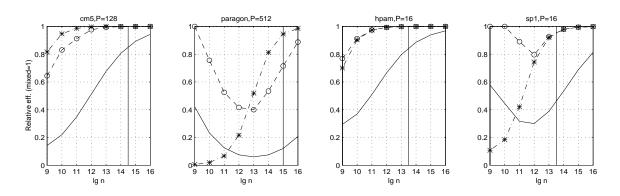

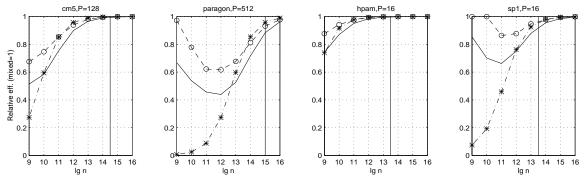

| 3.6          | Plot of efficiency against problem size for a fixed number of processors                                                                                | 57  |

| 3.7          | More efficiency estimates.                                                                                                                              | 57  |

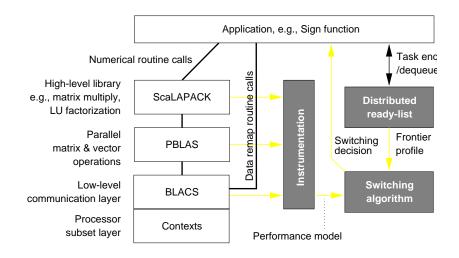

| 3.8          | The software architecture of the dynamic scheduling module in ScaLAPACK.                                                                                | 59  |

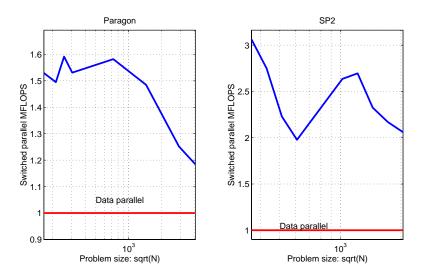

| 3.9          | Performance improvements of switched parallelism over data parallelism on                                                                               |     |

|              | the Paragon and the SP2                                                                                                                                 | 60  |

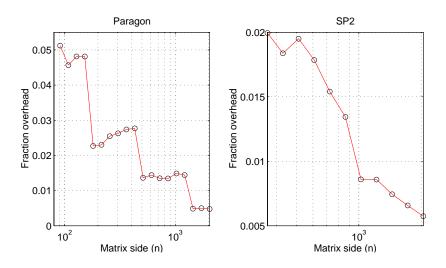

| 3.10         | Switching and data remapping overheads                                                                                                                  | 61  |

| 4.1          | Illustration of the makespan lower bound.                                                                                                               | 74  |

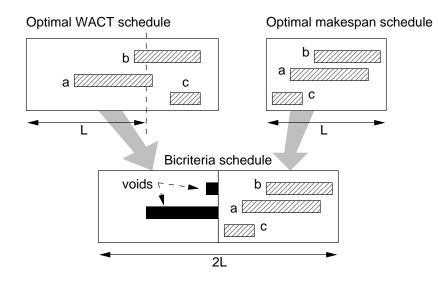

| 4.2          | Existence of bicriteria schedules.                                                                                                                      | 79  |

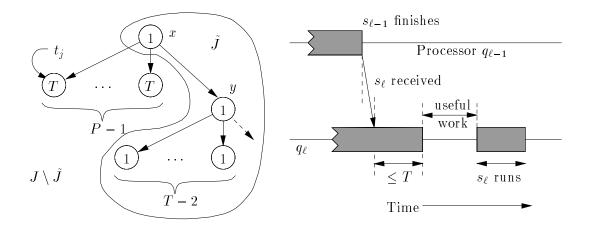

| 5.1          | Parallel branch and bound: lower and upper bounds                                                                                                       | 92  |

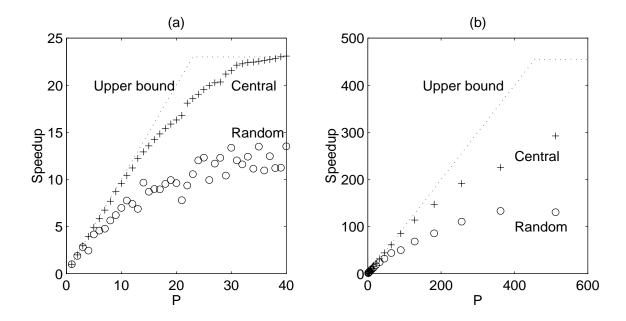

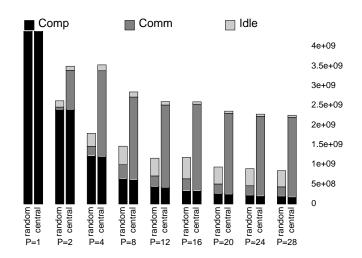

| $5.2 \\ 5.3$ | Comparison of speedup between Graham's list schedule and random allocation.<br>Time break-up of Graham's list schedule and random allocation on the CM5 | 95  |

| 0.0          | for the symmetric eigenvalue problem.                                                                                                                   | 95  |

| 5.4          |                                                                                                                                                         | 104 |

| J• 1         |                                                                                                                                                         | ±01 |

## List of Tables

| 2.1 | Estimates of message startup overhead $\alpha$ and transfer time per double word $\beta$ measured in units of the peak floating point operation time for different |     |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | machines.                                                                                                                                                          |     |

| 3.1 | Fitting the asymptotic model to various parallel machines                                                                                                          | 48  |

| 4.1 | Comparison of results in resource constrained scheduling                                                                                                           | 69  |

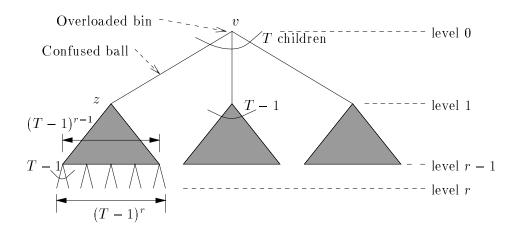

| 5.1 | Simulation results. $d$ is the number of bins that a ball sends initial request to; this is set to two. $r$ is the number of rounds                                | 107 |

### Chapter 1

## Introduction

Parallelism exists in most forms of computation, and exploiting it is a promising means to boost the performance of many important scientific and commercial applications beyond peak uniprocessor performance. However, exploiting parallelism is not trivial; it often requires complete algorithm redesign and implementation for different parallel machines. It has taken almost a decade to identify a few cost-effective parallel architecture configurations, and as a result, system software is only starting to mature and reach a level of portability and standardization that can motivate application writers to invest in parallel programming.

This point in time is unique in the development of parallel computing, since some basic design issues have been resolved, so that one need not chase moving targets any more, but there is a large scope for algorithm design in systems software. The surviving architectural choices are clear for the foreseeable future: cost-effective parallel machines will be built from shared memory "symmetric" multiprocessors (SMP's). These will scale up to a few dozen processors at most. For applications that demand more resources, these SMP's will be interconnected by a network. Processes on different processors will communicate by passing messages to each other, either explicitly by subroutine calls, or implicitly, by accessing remote data and triggering a software abstraction of global memory to issue messages. In units of CPU cycles, communication overhead is expected to be large. Each message has some fixed startup overhead time and then some proportional time per byte of data transfered. It will be the interconnect that will define the character and the price-tag of the machine; the processors will be commodity.

Apart from interface and portability issues, the challenge for system software, such

as compilers, runtime systems, and application libraries, is to export a clean performance model to the client while adjusting to diverse communication cost parameters and diverse application behavior in terms of both locality and load balance.

The work in this dissertation is based on the following premises.

- *Performance engineering* is of paramount importance in parallel computing, because, "Parallelism is not cheaper or easier, it is *faster*" [66].

- Scheduling the resources of the multiprocessor (mainly, processors, network, memory, and IO activity) judiciously between the units of work is essential for achieving high utilization of the resources. Very few compilers or runtime systems take such a global view of the scheduling problem yet, and we shall show the benefits of doing so throughout the thesis.

- These resource scheduling algorithms must use simple models of the machine and the workload, so that the resulting system is performance-portable across diverse platforms without need for ad-hoc tuning.

The contribution of this thesis is a resource scheduling framework for scientific and commercial applications on scalable multiprocessors, comprising techniques at the compiler, runtime, and application level.

Despite the attention that the area of resource allocation and job scheduling has received, many problems in parallel system scheduling lack satisfactory solutions. First, simple application of existing results to new domains is rarely possible, because the setting often has crucial details not addressed by classical scheduling literature. Second, the practical situation is usually complex, and it is hard to abstract a model that is both simple and faithful to reality. Third, most of the problems are computationally intractable, and knowledge of complexity and approximations is needed to design algorithms and analyze them. Finally, practical algorithmics, reflecting both the constraints and simplifications offered by practical scenarios, are more important than exploiting powerful but impractical primitives from theory.

The rest of this chapter summarizes the problems and new solutions described in the thesis.

### 1.1 Message scheduling via compiler analysis

Parallelism expressed through arrays and loops is very common in scientific numerical applications. Many languages have been designed for expressing array parallelism, commonly called "data parallelism." The success of data parallelism has reached the stage where a language standard called High Performance Fortran (HPF) has been defined. HPF extends Fortran with two features: one can refer to regular array sections rather than individual elements (this extension is also part of Fortran 90 [49]), and give directives to the compiler to distribute and align arrays on parallel machines. The compiler partitions computation to match the data distribution and generates communication for remote arrays. However, compiling HPF code to get performance close to hand-coded message-passing programs is still a major challenge. On scalable multiprocessors such as the IBM SP2 or Intel Paragon, a single extra communication step can cost tens of thousands of CPU cycles.

There is a large body of literature on compiler analysis and optimization of communication generated by loops involving distributed arrays. Initial progress was mostly restricted to local optimizations at the single loop-nest level; these could not detect and eliminate communication that is redundant between different loop nests or subroutines. As a simple example, a single value of a distributed array could be used in several loops after its definition throughout a subroutine; if the array value is unchanged, communication for the uses should be done once after the definition of the value, but without global analysis it would be done before each loop enclosing an use.

Several factors complicate the situation. The main existing technique to detect redundancy has been to trace uses of values back to the definition and cancel all communication that is rendered redundant by other communication placed at that point. This is called *earliest placement*, and is also good for overlapping communication with computation. However, this technique places communication for a remote array access at a place depending only on that access and not others, which may prevent some highly profitable optimizations like combining messages from multiple arrays into one. While message combining amortizes communication overhead, it requires memory copies for packing and unpacking data. This has to be done carefully so that the communication buffers are smaller than the cache, or the benefits of amortizing the fixed overhead of a message may be canceled by cache miss penalty.

In Chapter 2 we will describe a new compiler algorithm for communication analysis

and optimization that achieves redundancy elimination while maximizing network and cache performance across loops and statements in a global manner [27]. This significantly improves on the recently proposed array dataflow analyses which use the "earliest placement" policy: our algorithm takes into account all legal positions for all remote accesses before deciding on the final placement of any access. One implication of this is that our algorithm may *avoid* early communication placement if it can lead to larger message overhead. We implemented the algorithm in IBM's production compiler, called pHPF. Although pHPF already generated highly optimized code, the new technique cut down communication time by another factor of two, which meant a 20-40% overall savings for many well-known scientific benchmarks.

### 1.2 Scheduling jobs with mixed parallelism

The underlying execution model of HPF and similar compilers is called *bulk synchronous*: there are alternating phases of computation and communication. Commodity networks perform well if the latter are few and far between; the compiler algorithm outlined in the previous section enhances this effect. However, loop-level parallelism still has limited scalability because many processors have to communicate frequently and cooperatively on a data-parallel problem.

Some applications have a natural two-level structure: at the outer level there is a directed acyclic task graph, where each vertex is a task that can run only after all its predecessors have completed. Tasks not ordered with respect to each other can be executed in parallel. At the inner level, each task is parallelizable; it can run on some set of processors provided they work on it simultaneously. (The inner level parallelism is the data parallelism mentioned earlier.) There is a growing body of such applications, including eigensolvers, adaptive mesh codes, circuit simulation, and parallel database query trees. We shall call applications with these two forms of parallelism *mixed* parallel. Recent versions of the HPF language proposal includes support for such applications, and some parallelizing compilers have been extended to express such applications.

Given the importance of mixed parallel applications, it is not surprising that there has been significant research on scheduling them. Most of the work has been in the area of compile-time scheduling. Array parallelism is expressed as in HPF, and task parallelism is typically expressed using annotations. The compiler uses estimates or profiles of computation and communication in the data parallel modules and uses expensive off-line optimization algorithms to allocate processors to modules.

Unfortunately, the amount of static task parallelism in such problems is so small (typically 4–8) that except for the smallest problems, the gains over pure data parallelism are small. Problems where the task parallelism grows with problem size, such as in divide and conquer, are therefore much more promising from the perspective of exploiting mixed parallelism. On the other hand, these applications have to be scheduled dynamically, and therefore cannot use the expensive optimization algorithms, such as linear-programming, that are used in compile-time scheduling.

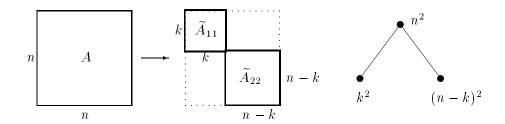

In Chapter 3 we will describe a simple and effective heuristic for scheduling divide and conquer applications with mixed parallelism [26]. The algorithm classifies the tasks into two types. The large problems near the root are allocated all the processors in turn, while small problems close to the leaves are packed in a task-parallel fashion, each task being assigned exactly one processor. There is some internal frontier at which the execution model *switches* from data to task parallelism. Some previous implementations have used switching based on an ad-hoc switch point tuned to a given problem and machine. In contrast, our switching algorithms are parameterized on machine and problem parameters and are provably close to optimal. Control on the switching frontier also gives a simple means for adjusting to diverse network cost parameters, while also trading communication cost with the load imbalance inherent in the task graph.

We have implemented the switching algorithms as an extension of the ScaLAPACK runtime system and used it to run a non-symmetric eigensolver. A significant performance improvement is seen over a purely data-parallel implementation.

We have also analyzed the performance gap between the switched mode execution (which is simple to program) and the general setting of allocating arbitrary processor subsets to jobs (for which many algorithms exist in theory) for a large class of applications. Our analysis shows that the gap is often small. From a language or runtime design perspective, these results indicate that this limited form of mixed parallelism will produce most of the benefits with a much simpler implementation.

### 1.3 Scheduling resource constrained jobs

Chapters 2 and 3 focus on the performance of a single application on a dedicated machine. In realistic installations many users submit jobs that contend for system resources. Since these jobs arrive over time, it makes little sense to measure the performance of a scheduler by giving it a batch of jobs off-line and measuring the finish time of only the last job (this is called the *makespan* of the set of jobs). A better measure to minimize is the average response time, which is the average time from arrival to completion of a job. For reasons elaborated later, this problem is very hard. A useful step in that direction is to solve the special case of minimizing the prioritized (also called *weighted*) average completion time, WACT, over a fixed batch of jobs.

The situation is complicated by the jobs having diverse running times and resource requirements. In real life, jobs need not only processors (which is the predominant case dealt with in scheduling theory) but also other resources, such as memory and network and disk bandwidth. While some known algorithms can deal with general resources, they assume the jobs are independent, while in many situations, there are precedence constraints between them.

Until recently, few machines allowed multiple jobs to execute concurrently. As most machines are going towards a multiprogrammed full-UNIX node model, resource scheduling is becoming more crucial at the system level. Vendors like IBM, SGI and Convex place significant emphasis on load management software, as do academic communities [50]. It is also becoming apparent that applications should dynamically allocate and deallocate resources to avoid under-utilization and long job response times [48]. While significant software infrastructure is being built, the algorithms at the heart of these systems are often variants of list-based greedy schedulers, which perform poorly under heavy load.

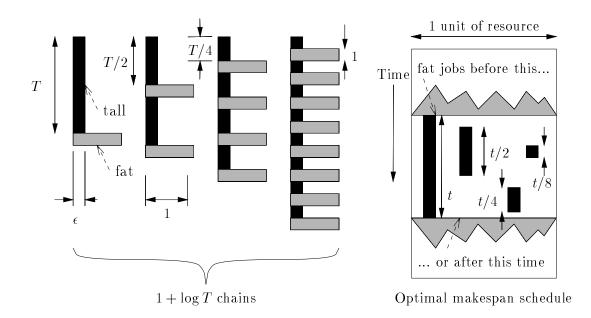

In Chapter 4 we give several simple and near-optimal algorithms for variations of this scenario. They depend on a framework for extending makespan algorithms into WACT algorithms. By applying the framework, we first give new algorithms for processor scheduling under the WACT metric. There appear to be qualitative differences between different types of resources. Some resources, like processors, are *malleable*, i.e., they can be traded for time relatively gracefully, while others, like memory are *non-malleable*, i.e., admitting little or no such flexibility. For jobs with both precedence and non-malleable resource constraints, the problem appears to be very different from most precedence-constrained scheduling results that are based on basic lower bounds like average work per processor or the critical path length in the precedence graph. We obtain an  $O(\log T)$  approximation for both WACT and makespan [28], where T is the longest to shortest job time ratio. Our algorithm uses a technique that deliberately introduces delays to improve on a greedy schedule. We also show that the log T blowup is unavoidable for certain instances. Since our models were carefully abstracted from real-life scheduling problems in parallel databases and operating systems, we expect that these results will prove useful in practice.

### 1.4 Dynamic scheduling using parallel random allocation

The results summarized thus far work well in problem domains where the resource requirements of jobs can be estimated with reasonable accuracy at the time the job is submitted to the scheduler. Sparse, irregular, and dynamic problems do not always have this benign feature. In Chapter 5 we explore randomization as an effective means for dealing with such dynamic and unpredictable problems.

In the first part we consider applications where the tasks each run on only one processor, but may have a precedence relation (the task DAG) unfolding dynamically. The running time of a task may be unknown before completion, and the scheduler has to be *non-clairvoyant*, i.e., it cannot know and use the running time of a job to schedule it. It is not necessary for a centralized scheduler (e.g. Graham's list algorithm [64]) to be clairvoyant, when evaluated using the finish time metric, also called "makespan." But this solution has a communication bottleneck. We analyze the running time using the following decentralized strategy: each processor has a local task pool, new tasks are sent to a random pool, and each processor removes and executes tasks from its local pool. Although used in practice, the effect of random allocation on dynamic, irregular task graphs was unresolved before this work; the closest known analysis was for unit-time tasks [78]. The resulting bounds are supported by practical experience with irregular applications [30, 25], which show that randomization is an effective tool for load balancing a certain class of applications.

It is well-known from the literature on occupancy problems that one round of random allocation leads to roughly a logarithmic smoothing of load. In more concrete terms, if n tasks are randomly assigned to n processors, each processor has  $O(\log n / \log \log n)$  tasks with probability at least 1 - O(1/n). In the second part of Chapter 5 we study an extended

model of random allocation, where assignment of tasks to processors are made in multiple rounds so as to further smooth down the load imbalance to sub-logarithmic amounts. In addition to the task scheduling application, this setting can be motivated by the problem of allocating file blocks in distributed "serverless" file systems like xFS [6]. In this setting there are n client workstations whose local disks comprise the file system, which can be abstracted as n servers. As clients write files, new disk blocks must be allocated in a decentralized way without overloading any particular server. There is a trade-off between the cost of communication to obtain more global information and the cost of load imbalance owing to imperfect knowledge. At one extreme, one can send each new block to a random server; at the other, one can get optimal load balance by maintaining exact global load information. We give a precise characterization of this trade-off [1]. Initial simulation results agree with theoretical predictions.

Extensive work has been done on all the problems studied. In Chapter 6 we will present a survey and classification of known results based on job and machine models. Finally, in Chapter 7 we will summarize the thesis and suggest directions for future work.

### Chapter 2

# Message scheduling via compiler analysis

### 2.1 Introduction

Distributed memory architectures provide a cost-effective method for building scalable parallel computers. However, the absence of a global address space and the resulting need for explicit message passing makes these machines difficult to program. This has motivated the design of languages like High Performance Fortran (HPF) [55], which allow the programmer to write sequential or shared-memory parallel programs that are annotated with directives specifying data decomposition. The compilers for these languages are responsible for partitioning the computation and generating the communication necessary to fetch values of non-local data referenced by a processor [72, 123, 20, 5, 21, 68].

Accessing remote data is usually orders of magnitude slower than accessing local data, for the following reasons. It is getting increasingly cost-effective to build multiprocessors from commodity hardware components and system software. Most current generation CPU's are well beyond the 100 MFLOPS mark, and are consistently out-pacing network performance. Most vendors support UNIX-like environments on each processor, in particular with multiprogramming and virtual memory. This means that low-overhead message passing implementations like Active Messages [115], which work best with gang-scheduled time slicing, user-level access to the network interface, and register-based data transfer, are not the best choice. As a result, communication startup overheads tend

| Machine  | NW software | $\alpha$         | $\beta$ |

|----------|-------------|------------------|---------|

| Paragon  | NX          | $7.8 	imes 10^3$ | 9       |

| Cray T3D | BLT         | $2.7	imes10^4$   | 9       |

| CM5+VU   | CMMD        | $1.4 	imes 10^4$ | 103     |

| IBM SP1  | MPL         | $2.8 	imes 10^4$ | 50      |

| IBM SP2  | MPL         | $1.2 	imes 10^4$ | 60      |

Table 2.1: Estimates of message startup overhead  $\alpha$  and transfer time per double  $\beta$  scaled to the peak floating point operation time for different machines. Estimates are in part from [107, 117, 88, 7]; the network software are described in these references.

to be very large on most distributed memory machines, although reasonable bandwidth can be supported for sufficiently large messages [109, 106]. See Table 2.1 for some idea of the CPU and communication speeds of current multiprocessors.

Therefore, parallelizing compilers have to be extremely careful about generating communication code. A single suboptimal choice may waste time equivalent to several thousand CPU operations. Unfortunately, communication optimization is a very difficult problem, with many potentially conflicting considerations. Consider a parallel program where a data value is produced by some statement, after which it is sent out of the owner processor, received by other processors, and finally used in some other statement. There is usually some flexibility about the placement of the send and receive subroutine calls between the definition and the use. An early placement favors potential overlap between CPU and network activity, but may consume more temporary communication buffers and cache problems if the main CPU is involved in packing and unpacking data, e.g., for strided accesses. A late placement may break up communication of a large array section into smaller sections or individual elements, suffering increased overhead. Furthermore, placing one communication at some point in the code also affects the choice of the best place for other communication.

There is a clear need for global *scheduling* of communication. "Scheduling," in this chapter, means judicious placement of message-passing subroutine calls in the compiled code by the compiler. In this chapter we present a novel compiler algorithm that recognizes the global nature of the communication placement problem. Our algorithm derives from static single assignment analysis, array dependence analysis, and data availability analysis [69], which is extended to detect compatibility of communication patterns in addition to redundancy. We differ significantly from previous research, in which the position of communication code for each remote access is decided independent of other remote accesses; instead, we determine the positions in an interdependent and global manner. The algorithm achieves both redundancy elimination and message combining globally, and is able to reduce the number of messages to an extent that is not achievable with any previous approach.

Our algorithm has been implemented in the IBM pHPF prototype compiler [68]. We report results from a preliminary study of some well-known HPF programs. The performance gains are impressive. Reduction in static message count can be up to a factor of almost nine. Time spent in communication is reduced in many cases by a factor of two or more. We believe that these are also the first results from any implementation of redundant message elimination across different loop nests, and add significant experimental experience to research on communication optimization.

### 2.2 Motivating codes

We will use a few code fragments to show the importance of recognizing the global nature of the message placement problem. We are interested in the communication patterns and the flexibility in message placement revealed by data dependence analysis, not the particulars of the applications.

In the code fragments that we present, we will elide actual operations and show each right hand side (RHS) as a list of variables accessed. Frequently we deal with Fortran 90 (F90) style shift operations that involve nearest-neighbor communication; we show this pictorially using arrows. For simplicity, the combinable messages in our examples have identical patterns on the processor template; in practice, combining is feasible when one pattern is a subset of another.

Specifically, we demonstrate the following.

- Redundancy elimination is useful, but often not enough to reduce the number of messages. Reducing message count is crucial for our target architectures, especially for synchronous and collective communication.

- The traditional mechanisms of redundancy elimination can sometimes *prevent* the compiler from generating the best communication code.

- The well-known redundancy elimination technique of earliest communication placement is sensitive to minor syntactic differences in the high-level source, and may

```

Timestep loop:

glast(:,:) = g(1,:.:)

for i = 2 to nx - 1

\cdots = g(i,:,:)\uparrow \leftarrow \downarrow \rightarrow

\cdots = sum(g(i,ny,:)), sum(g(i,ny-1,:)), sum(g(i,0,:)), sum(g(i,1,:))

\cdots = glast(:,:)\uparrow \leftarrow \downarrow \rightarrow

\cdots = sum(glast(:,:)\uparrow \leftarrow \downarrow \rightarrow

\cdots = sum(glast(ny,:)), sum(glast(ny-1,:)), sum(glast(0,:)), sum(glast(1,:))

glast(:,:) = g(i,:,:)

g(i,:,:) = \cdots

```

Figure 2.1: A simplified form of the NPAC gravity code illustrating the need for combining communication.

| Source code                                                                                                                   | Earliest placement                                                                                                                            | Combined placement                                                                                                                                                                 |

|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Loop:                                                                                                                         | Loop:                                                                                                                                         | Loop:                                                                                                                                                                              |

|                                                                                                                               | $\underline{\texttt{COMM}} \rightarrow \texttt{p}, \texttt{v}  \uparrow \texttt{p}, \texttt{u}  \leftarrow \texttt{u}  \downarrow \texttt{v}$ | $\underline{\texttt{COMM}} \rightarrow \texttt{p}, \texttt{v}  \uparrow \texttt{p}, \texttt{u}  \leftarrow \texttt{u}  \downarrow \texttt{v}$                                      |

| ${ m cu} = { m p}  ightarrow$                                                                                                 | ${\tt cu} = {\tt p} { ightarrow}$                                                                                                             | $\texttt{cu}  = \texttt{p} {\rightarrow}$                                                                                                                                          |

|                                                                                                                               | <u>COMM ←cu ↑cu</u>                                                                                                                           |                                                                                                                                                                                    |

| $cv = p\uparrow$                                                                                                              | $c \mathbf{v} = \mathbf{p} \uparrow$                                                                                                          | $cv = p\uparrow$                                                                                                                                                                   |

|                                                                                                                               | <u>COMM →cv ↓cv</u>                                                                                                                           |                                                                                                                                                                                    |

| $z = u\uparrow, v \rightarrow, p \rightarrow, p\uparrow, p\nearrow$                                                           | $\mathbf{z} = \mathbf{u} \uparrow,  \mathbf{v}  ightarrow,  \mathbf{p}  ightarrow,  \mathbf{p} \uparrow,  \mathbf{p} \nearrow$                | $z = u\uparrow, v\rightarrow, p\rightarrow, p\uparrow, p\nearrow$                                                                                                                  |

|                                                                                                                               | $\underline{\texttt{COMM}} \downarrow_{\textbf{Z}} \leftarrow \underline{\textbf{z}}$                                                         |                                                                                                                                                                                    |

| h = $\mathbf{u} \leftarrow, \mathbf{v} \downarrow$                                                                            | $\mathbf{h} = \mathbf{u} \leftarrow, \mathbf{v} \downarrow$                                                                                   | $\mathbf{h} = \mathbf{u} \leftarrow, \mathbf{v} \downarrow$                                                                                                                        |

|                                                                                                                               | $\underline{\texttt{COMM}} \rightarrow \underline{\mathbf{h}}  \uparrow \underline{\mathbf{h}}$                                               | $\underline{\texttt{COMM}} \rightarrow \texttt{cv}, \texttt{h}  {\downarrow} \texttt{z}, \texttt{cv}  {\leftarrow} \texttt{z}, \texttt{cu}  {\uparrow} \texttt{cu}, \texttt{h}$    |

| $unew = z \downarrow, h \rightarrow, cv \rightarrow, cv \downarrow, cv \searrow$                                              | $unew = z\downarrow, h \rightarrow, cv \rightarrow, cv\downarrow, cv \searrow$                                                                | $\texttt{unew} = \texttt{z} {\downarrow},  \texttt{h} {\rightarrow},  \texttt{c} \texttt{v} {\rightarrow},  \texttt{c} \texttt{v} {\downarrow},  \texttt{c} \texttt{v} {\searrow}$ |

| $\texttt{vnew} = \texttt{z}\leftarrow, \texttt{h}\uparrow, \texttt{cu}\leftarrow, \texttt{cu}\uparrow, \texttt{cu}\checkmark$ | $\mathtt{vnew} = \mathtt{z} \leftarrow,  \mathtt{h} \uparrow,  \mathtt{cu} \leftarrow,  \mathtt{cu} \uparrow,  \mathtt{cu} \land$             | $\mathtt{vnew} = \mathtt{z} \leftarrow, \mathtt{h} \uparrow, \mathtt{cu} \leftarrow, \mathtt{cu} \uparrow, \mathtt{cu} \checkmark$                                                 |

| $\mathtt{pnew} = \mathtt{cu} \leftarrow,  \mathtt{cv} \downarrow$                                                             | $pnew = cu \leftarrow, cv \downarrow$                                                                                                         | $pnew = cu \leftarrow, cv \downarrow$                                                                                                                                              |

Figure 2.2: The NCAR shallow benchmark illustrating that redundancy elimination via earliest placement may lose valuable opportunity for message combining.

| F90 Source code                                                                   | Scalarized code                                                                                                    | Hand coded F77                                                                                                         |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| distribute $a, b, c ::$ (BLOCK)<br>a = 3<br>b = 4<br>c(2:n) = a(1:n-1) + b(1:n-1) | $do \ i = 1 : n$ $a(i) = 3$ $COMM \ Earliest(a)$ $do \ i = 1 : n$ $b(i) = 4$ $COMM \ Earliest(b)$ $do \ i = 2 : n$ | $do \ i = 1 : n$ $a(i) = 3$ $b(i) = 4$ $COMM \ Earliest(a), Earliest(b)$ $do \ i = 2 : n$ $c(i) = a(i - 1) + b(i - 1)$ |

|                                                                                   | c(i) = a(i-1) + b(i-1)                                                                                             | C(i) = G(i - 1) + O(i - 1)                                                                                             |

Figure 2.3: Syntax sensitivity of earliest placement. The right hand expressions are constants for simplicity only; for this particular code constant propagation will lead to communication-free code.

produce suboptimal code.

### 2.2.1 Beyond redundancy elimination

Redundancy elimination seeks to avoid unnecessary repetitions of communication for the same data. Programs often exhibit similar communication patterns involving different data as well. At least two types of additional communication optimization are possible. To see this, regard each (bulk-synchronization) communication as a  $P \times P$  matrix, where P is the number of physical processors, and element (i, j) denotes the volume of data that processor i sends to processor j.

- If, in two distinct communications, processor 1 sends to processor 2, these messages can be combined, if permitted by data dependency analysis, to amortize the fixed overhead for transferring a message.

- If, in one communication, processor 1 sends to processor 2, and in the other, processor 5 sends to processor 9, and data dependency permits these calls to be made by the respective processor pair at the same point in the code, these transfers can be parallelized.

It is quite amazing that in spite of the intense research in the area of communication optimization, these optimizations are often missed (or not even attempted) by most compilers.

Figure 2.1 shows a simplified form of a code called gravity. In this code, the 2-d arrays are of dimension (ny,nz) distributed (BLOCK, BLOCK)<sup>1</sup> and the 3-d arrays are of dimension (nx,ny,nz) distributed (\*,BLOCK,BLOCK)<sup>2</sup> In this code it is easy to detect that the nearest neighbor communication for g and glast can be combined, as can the sum operations. Thus, we can combine the eight nearest neighbor messages into four and the eight global sums into two parallel sets of four global sums.

#### 2.2.2 Earliest placement may hurt

In the last example, earliest placement did not preclude other optimizations; we merely needed a message combining post-pass. But in general, the situation could be more

<sup>&</sup>lt;sup>1</sup>Assuming for simplicity that P divides n, an array a[n] is block distributed over P processors by assigning  $\{a[in/P], \ldots, a[(i+1)n/P - 1]\}$  to processor  $i, 0 \le i < P$ . This extends naturally to multiple dimensions by treating the processors as a grid of the same number of dimensions.

<sup>&</sup>lt;sup>2</sup>The notation \* means that for all *i*, element a[i, j, k] are on the same processor.

complicated. In particular, redundancy elimination via earliest placement can prevent the combining possibilities from being exploited. To demonstrate this, we study the benchmark called shallow.

A simplified form of the code is shown in Figure 2.2. Notice that each statement in the array syntax expands into a two-deep loop-nest. If no redundant message elimination is done across different loop nests, there would be 18 exchanges generated per processor. (The IBM compiler already optimizes diagonal communication like  $p \nearrow$  by decomposing it into  $p\uparrow$  and  $p\rightarrow$ . This is reflected by the message counts.) Earliest placement will move up a communication as far as possible within the loop, communicating data right after definition. After a combining post-pass this will result in 12 array sections being communicated per processor. In contrast, if minimizing the number of messages is the objective, then we can obtain a schedule with only 8 exchanges per processor, in which placement of communication is not at the earliest point detected by dataflow analysis.

### 2.2.3 Syntax sensitivity

Since earliest placement pushes communication close to the production of the data value, placement is sensitive to the structure of intervals containing the production. As a case in point, consider the semantically equivalent codes in the three columns of Figure 2.3. Suppose arrays a and b have identical layout, say blocked. Using earliest placement, the messages for the two arrays can be combined in the third column whereas they cannot in the second code. Even if the programmer were to write the code in the first column, intermediate passes of compilation may destroy the loop structure by fission. In fact, the IBM HPF scalarizer [68] will translate the F90-style source to the scalarized form in the second column. If loop fusion can be performed before this analysis, as in this case, the problem can be avoided. But this is not always possible [120, § 9.2]. Thus, limited communication analysis at a single loop-nest level or a rigid placement policy may not work well. Our framework, by not relying on any restricted placement (like earliest or latest) but evaluating many choices globally, proves to be a much more robust strategy that is not easily perturbed by minor syntactic differences.

### 2.3 Network performance

By profiling our target networks, we justify the need for global message scheduling and identify simplifying assumptions that can be made about the optimization problem. We pick two platforms: the IBM SP2 with a custom network, and a network of Sparc workstations (NOW) connected by a commodity network (Myrinet). The SP2 uses IBM's message passing library MPL; the NOW uses MPICH, a portable implementation of the MPI standard from Argonne National Labs. Details of the networks can be found in [109, 106, 79]. We want to measure the benefits of large messages, while estimating the local block copy (bcopy) cost to collect many small messages into a large one. Figure 2.4 shows the profiling code and results.

We will be mostly interested in effective bandwidth since the HPF runtime does bulk transfer as the common case. For fine-grained communication, there is a distinction between CPU overhead per message, which cannot be overlapped with computation, and network latency, which can. In the bulk-synchronous execution model that HPF compiles down to, the benefits of overlap are very small. Kennedy *et al* estimate this to be typically 5-9% for 2-d stencil problems of size  $256 \times 256$  on a 16-processor iPSC/860, in the context of the Fortran-D execution model and runtime system [81].

The top curve shows the bandwidth of local block copy (bcopy) as a function of buffer size. The bottom curve plots network bandwidth as a function of message length, based on the time that the receiver waits for completion.

The top curve shows that as long as the message buffers fit in cache, we can ignore the overhead of **bcopy**. Fortunately, for both machines, most of the message startup amortization benefits occur at message sizes much smaller than the cache limit; given typical cache sizes, we believe this is a fairly general feature.

On the other hand, for messages much larger than cache, it may be important to suppress combining communication from non-contiguous array sections. E.g., for the SP2, the bandwidth of copying buffers larger than the cache is barely twice the message-passing bandwidth beyond cache size.

If there is a network co-processor or DMA, it is possible for the sender to quickly inject the message and the receiver to retrieve it more slowly. The middle curve shows bandwidth computed using the time the sender takes to inject the message. While the injection bandwidth is much lower than **bcopy**, it is larger than receive bandwidth for

Figure 2.4: Buffer copying and network bandwidth studies on the IBM SP2 using MPL and the Berkeley NOW using MPICH. The x-axis is to a log scale.

certain message sizes. Injection bandwidth also declines around the cache limit.

Given our execution model and typical machine characteristics, we consider message aggregation and parallelization as the first-order concerns, and overlap as a second-order concern [81]. The latter also depends on the co-processor and network software. E.g., the implementors of MPL minimize co-processor assistance because the i860 coprocessor is much slower than the RS 6000 CPU, and the channel between the CPU and the co-processor is slow [106]. However, our algorithm permits additional techniques like Give-n-Take to be used to overlap latency with computation at the sender [114].

### 2.4 Compiler algorithms

In this section we describe our algorithm for placing communication code. This analysis is done after the compiler has performed transformations like loop distribution and loop interchange to increase opportunities for moving communication outside loops [68]. Wolfe provides an excellent overview of the compiler terminology we use [120]. The steps of our algorithm are described below and shown in Figure 2.5.

Figure 2.5: Prototype modifications to the IBM pHPF SPMDizer.

- 1. For each array expression on the right hand side of a statement that may need communication, identify the earliest (§2.4.3) and latest (§2.4.2) safe position to place that communication. One of our key innovations is to exploit the static single assignment (SSA) information [39, 35] already computed in an earlier phase by pHPF, refined by array dependence-testing [121]. In contrast, previous proposals for such analysis typically use a bidirectional dataflow approach with array section descriptors and/or bit-vectors [69].

- 2. For each non-local reference, identify a set of candidate positions, any one of which can be potentially chosen as the final point to emit a call to a message-passing runtime routine (§2.4.4).

- 3. Perform the "array-section" analog of common subexpression elimination: detect and eliminate subsumed communication (§2.4.6).

- 4. For the remaining communication, choose one from the set of candidate placements. In the prototype implementation we do this in two substeps that will be explained later (§2.4.5 and §2.4.7).

The above algorithms have been added to a prototype version of the pHPF compiler as shown in Figure 2.5. Throughout this section, we will use the code in Figure 2.6 as a

|    |                                           | CommSet(S) after     |                      |                |           |  |  |  |  |  |  |

|----|-------------------------------------------|----------------------|----------------------|----------------|-----------|--|--|--|--|--|--|

| S  | Source code                               | Candidate            | Subset               | Redundancy     | Earliest  |  |  |  |  |  |  |

|    |                                           | marking              | elimination          | elimination    | placement |  |  |  |  |  |  |

|    | distribute a, b, c, d :: (BLOCK,*)        |                      |                      |                |           |  |  |  |  |  |  |

| 1  | b(:, 1:n:2) = 1                           | $b_1$                |                      |                | $b_1$     |  |  |  |  |  |  |

| 2  | b(:, 2: n: 2) = 2                         | $b_{1}, b_{2}$       |                      |                | $b_2$     |  |  |  |  |  |  |

| 3  | if ( cond )                               |                      |                      |                |           |  |  |  |  |  |  |

| 4  | a = 3                                     |                      |                      |                | a 2       |  |  |  |  |  |  |

| 5  | else                                      |                      |                      |                |           |  |  |  |  |  |  |

| 6  | a = 4                                     |                      |                      |                | a 2       |  |  |  |  |  |  |

| 7  | endif                                     | $a_1, a_2, b_1, b_2$ | $a_1, a_2, b_1, b_2$ | $\{a_2, b_2\}$ |           |  |  |  |  |  |  |

| 8  | do $i = 2: n$                             |                      |                      |                |           |  |  |  |  |  |  |

| 9  | do $j = 1 : n : 2$                        |                      |                      |                |           |  |  |  |  |  |  |

| 10 | $c(i, j) = a_1(i - 1, j) + b_1(i - 1, j)$ |                      |                      |                |           |  |  |  |  |  |  |

| 11 | do $j = 1: n$                             |                      |                      |                |           |  |  |  |  |  |  |

| 12 | $d(i,j) = a_2(i-1,j) - b_2(i-1,j)$        |                      |                      |                |           |  |  |  |  |  |  |

Figure 2.6: Running example for analysis and optimization steps. Different uses of a and b are subscripted to distinguish their communication entries. Code for each communication entry is executed *after* executing the statement. The notation  $\{a_2, b_2\}$  means the messages for these accesses can be combined. The results of traditional earliest placement is shown in the last column for comparison.

running example to illustrate the operation of the steps of the algorithm.

#### 2.4.1 Representation and notation

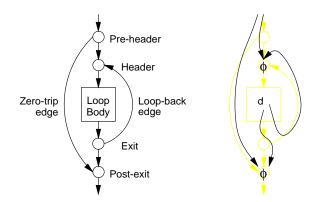

We represent the program using the *augmented* control flow graph (CFG), which makes loop structure more explicit than the standard CFG by placing *preheader* and *postexit* nodes [3, 100] before and after loops. These extra nodes also provide convenient locations for summarizing dataflow information for the loop.

The CFG is a directed graph where each *node* is a basic block, a sequence of statements without jumps. Execution starts at the ENTRY node. A statement S may have a use u or definition d (abbreviated to "def") of an array variable. There are two kinds of defs. A "regular" def is one corresponding to the left hand side variable in a source statement. Conversion to single static assignment (SSA) form also introduces other defs called " $\phi$ -defs." These look like " $v_i = \phi(\ldots, v_j, \ldots)$ ," where each variable<sup>3</sup> v is renamed to  $v_1, v_2$ , etc., and there is only one assignment to a particular renamed version. A  $\phi$ -def  $d = \phi(\ldots, r, \ldots)$  is said to have a set of *parameters*  $\{r\}$ . All regular array defs are considered *preserving*, meaning that (unless proved otherwise) the original value is not assumed to be *killed*. See Cytron *et al* for a detailed treatment of SSA algorithms [39, 35]. We refer interchangeably

<sup>&</sup>lt;sup>3</sup>Arrays are regarded as scalars and the index information is ignored during SSA analysis.

Figure 2.7: The diagram on the left hand side shows an example of a portion of the augmented control flow graph. It is reproduced (faint lines) on the right, and on top of it the SSA structure is super-imposed.

to a use, def, statement, or the node containing them. The node containing S is called CfgNode(S). When we say communication is placed at d we mean immediately after d.

A path  $\pi : v_0 \xrightarrow{+} v_j$  from  $v_0$  to  $v_j$  is a non-empty node sequence  $(v_i)$  with edges  $(v_{i-1}, v_i), 1 \leq i \leq j$ ; we also call  $\pi$  a backward path or backpath from  $v_j$  to  $v_0$ . Possibly empty paths are denoted  $v_0 \xrightarrow{*} v_j$ .  $\pi$  bypasses v if v does not occur on  $\pi$ . Two paths are non-overlapping if they are node-disjoint. Non-empty paths  $\pi_1 : v_0 \xrightarrow{+} v_j, \pi_2 : w_0 \xrightarrow{+} w_k$  are said to converge at z if  $v_0 \neq w_0, v_j = z = w_k$ , and  $(v_p = w_q) \Rightarrow (p = j \lor q = k)$ .

Loops are named L. Every loop has a well-defined *nesting level* called NL(L): this is the number of loops containing it. NL(v) for node v is defined likewise. L or v is *deep* or *shallow* according as NL is large or small. The common nesting level CNL(u,v) of two nodes u and v is the NL of the deepest loop containing them both. Every loop L has a single *preheader* node, PreHdr(L), and there is an edge from PreHdr(L) to Hdr(L), the *header* node. PreHdr(L) dominates all nodes in L. There is a *postexit* node for each distinct loop exit target. Each postexit node of L has an incoming edge, called *zero-trip* edge, from PreHdr(L) (along with the original loop-exiting edges). See Figure 2.7.

L has a  $\phi$ -def at Hdr(L), called  $\phi_{Hdr}$ , for each variable defined in the loop or in a loop transitively nested in L.  $\phi_{Hdr}$  has two parameters,  $r_{pre}$  and  $r_{post}$ , such that there exists a backpath from  $r_{pre}$  to ENTRY that bypasses all nodes in the loop, and there exists a path from any node in the loop to  $r_{post}$  which never takes an exit edge out of the loop.

The postexit node of each loop L has a  $\phi$ -def, called  $\phi_{\mathsf{Exit}}$ , for each variable defined

in the loop or in a loop transitively nested in it. Because of  $\phi_{\mathsf{Exit}}$ , a definition d can reach a use u only through a definition d' at a level  $\mathsf{CNL}(d, u)$ . d' can possibly be d only if  $\mathsf{CNL}(d, u) = \mathsf{NL}(d)$ ; otherwise, d' is a  $\phi$ -def at a level  $\mathsf{CNL}(d, u)$ .

### 2.4.2 Identifying the latest position

We describe how the compiler finds Latest(u), the latest point to place communication for u, which is also placed in as shallow a loop level as possible, so that messages are maximally vectorized. This follows from standard communication analysis: communication is placed just before the outermost loop in which there is no true dependence on u, and is placed just before the statement containing u if no such loop exists [123, 72, 68].

Given a use u, let d range over the reaching regular defs of u. (Reaching defs are defined in Cytron *et al* [39, 35].) Consider some d. Observe that it is never necessary to place communication for u deeper than at CNL(d, u). Given d and u, we can compute all possible direction vectors (each is a CNL(d, u)-dimensional vector) [120]. These vectors are used in the routine lsArrayDep, shown in Figure 2.8(d) on page 21. Let  $DepLevel(d, u) = max\{\ell : lsArrayDep(d, u, \ell)\}$ , the deepest level at which there is a loop-carried dependency between u and d.

Because of the dependency at level  $\mathsf{DepLevel}(d, u)$ , communication for u cannot be moved outside loop level  $\mathsf{DepLevel}(d, u)$ . The overall communication level for use u, denoted  $\mathsf{CommLevel}(u)$ , is set to  $\max_d \{\mathsf{DepLevel}(d, u)\}$ . Finally, to place communication, we check  $\mathsf{CommLevel}(u)$ : if  $\mathsf{CommLevel}(u) = \mathsf{NL}(u)$ , communication is placed immediately before the statement containing  $u^4$ ; if  $\mathsf{CommLevel}(u) < \mathsf{NL}(u)$ , communication is placed in the loop preheader of the loop at level ( $\mathsf{CommLevel}(u) + 1$ ) that contains u. Note that  $\mathsf{CommLevel}(u) > \mathsf{NL}(u)$  is not possible, and that by construction  $\mathsf{Latest}(u)$  dominates u.

### 2.4.3 Identifying the earliest position

We now describe how to compute  $\mathsf{Earliest}(u)$  for use u. Typically, dataflow analysis with array sections marks a set of nodes as "earliest", such that a copy of the communication code has to be placed at *all* these points. This is acceptable if each array section is communicated using a separate call to the communication library, but for our purposes, it greatly complicates code generation. In different control flow paths, communication for u

<sup>&</sup>lt;sup>4</sup>In this case no vectorization has been possible.

```

a. Earliest(u)

For each def d of use u in depth-first preorder traversal:

If \mathsf{Test}(d, u) then return d.

b. \mathsf{Test}(d, u)

If d is a \phi-def, say d = \phi(\ldots, r_i, \ldots)

For each \phi-parameter r_i

\operatorname{visit}[\cdot] = 0, \operatorname{visit}[d] = 1

Let c_i = \mathsf{Rcount}(\mathsf{Reaching}(r_i), u, \mathsf{CNL}(d, u), \text{visit})

If two or more c_i's are positive

Return TRUE

else (d is a regular def)

If lsArrayDep(d, u, CNL(d, u))

Return TRUE.

c. \mathsf{Rcount}(d, u, l, visit)

If d is a \phi-def, say d = \phi(\ldots, r_i, \ldots)

If visit[d] return 0

visit[d] = 1

Return \sum_{i} \mathsf{Rcount}(\mathsf{Reaching}(r_i), u, l, \text{visit})

else (d \text{ is a regular def})

If lsArrayDep(d, u, l)

Return 1

else if d is a preserving def

Return \mathsf{Rcount}(\mathsf{Reaching}(d), u, l, \text{visit})

else return 0.

d. \mathsf{lsArrayDep}(d, u, \ell)

If d is the pseudo-def at ENTRY then return TRUE

If \ell > \mathsf{CNL}(d, u) then return FALSE

If \exists direction vector \vec{v} = (v_1, \dots, v_{\mathsf{CNL}(d,u)}) such that

• v_i = 0, for i \in \{1, ..., \ell - 1\}, and

• v_\ell \ge 0

then return TRUE

else return FALSE

```