# Copyright © 1996, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# VISUALIZING ARCHITECTURE AND ALGORITHM INTERACTION IN EMBEDDED SYSTEMS

by

Farhana Sheikh

Memorandum No. UCB/ERL M96/50

13 September 1996

CONTRACTOR OF THE PARTY OF THE

# VISUALIZING ARCHITECTURE AND ALGORITHM INTERACTION IN EMBEDDED SYSTEMS

by

Farhana Sheikh

Memorandum No. UCB/ERL M96/50

13 September 1996

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## **Abstract**

Embedded systems are increasingly becoming integral parts of almost all technology-oriented applications. The complexity and sophisticated nature of these such systems make it very difficult for engineers to exploit the full potential of the system's underlying resources. More often than not, this results in sub-optimal performance. Tools that allow an engineer to quickly evaluate system behaviour and performance can reduce development costs and time-to-market. Visualization techniques have proven invaluable to the design process in the past as they have greatly simplified tasks faced by engineers. Visual representations of views that depict algorithm and architecture interaction are developed to highlight poor algorithm design. problematic hardware-software interfaces, and other reasons behind poor performance in embedded systems. An objected-oriented framework for visual display of design information has been designed and an implementation of this model is discussed. The framework is then used to develop a prototype that implements architecture-algorithm visualization techniques. The theoretical background and issues relating to effective embedded system design are also discussed.

# Acknowledgements

I am grateful to my advisor Professor Edward A. Lee for his support and guidance. I would also like to thank John Reekie, Alain Girault, Mike Williamson, and Jose Pino for their invaluable comments and advice. This work was supported in part by the National Science and Engineering Research Council of Canada and I am grateful for their financial backing.

# **Table of Contents**

| 1 | Introdu     | ection                                                             | 4  |

|---|-------------|--------------------------------------------------------------------|----|

| 2 | Backgr      | ound and Theory                                                    | 6  |

|   | 2.1         | Embedded Systems and Their Design                                  |    |

|   | 2.2         | Scheduling Concepts                                                |    |

|   | 2.3         | Evaluating Algorithms and Their Performance On Given Architectures |    |

|   |             | 2.3.1 Performance and Performance Models                           |    |

|   | 2.4         | Visual Display of Design Information                               |    |

|   |             | 2.4.1 Visualization Basics                                         |    |

|   |             | 2.4.2 Gantt Charts                                                 | 11 |

|   |             | 2.4.3 Trace Displays                                               | 11 |

|   |             | 2.4.4 Space-Time Diagrams                                          | 12 |

| 3 | The Pto     | olemy and Tycho Frameworks                                         | 13 |

|   | 3.1         | Ptolemy                                                            |    |

|   | 3.2         | Tycho                                                              |    |

|   | 3.3         | Scheduling in Ptolemy                                              |    |

|   |             | 3.3.1 Scheduling Terminology.                                      |    |

|   |             | 3.3.2 Schedule Files                                               |    |

| 4 | Technic     | ues to Visualize Algorithm and Architecture Interaction            |    |

|   | 4.1         | Visual Representation of Hardware Components                       |    |

|   | 4.2         | Visual Representation of Software Components                       |    |

|   | 4.3         | Visual Representation of Schedules                                 |    |

|   |             | 4.3.1 Modifying Schedules.                                         |    |

|   | 4.4         | Visual Representation of Execution Traces                          |    |

|   | 4.5         | Visual Representation of Interprocessor Communication              |    |

|   | 4.6         | Combining Views                                                    |    |

| 5 | An Ohi      | ect-Oriented Model for Visual Display of Design Information        |    |

| 3 | 5.1         | Display Management                                                 |    |

|   | J.1         | 5.1.1 View Management                                              |    |

|   |             | 5.1.2 Menu Management                                              |    |

|   | 5.2         | Views                                                              |    |

|   | 5.3         | Data Filters                                                       |    |

|   | 5.4         | Applications                                                       |    |

| _ | _           |                                                                    |    |

| 6 |             | entation of the Object-Oriented Model For Design Visualization     |    |

|   | 6.1         | Overview                                                           |    |

|   | 6.2         | Displayer                                                          |    |

|   |             | 6.2.1 Displayer Options                                            | 37 |

|   | 6.3         | 6.2.2 Displayer Methods and Variables                              |    |

|   | 0.5         |                                                                    |    |

|   | 6.4         |                                                                    |    |

|   | 0.4         |                                                                    |    |

|   |             | 6.4.1 View Options                                                 | 40 |

|   | 6.5         |                                                                    |    |

|   | <b>U.</b> J |                                                                    |    |

|   |             |                                                                    | 4U |

|   | 6.6         |                                                                    |    |

|   | <b>U.U</b>  | Data Filter  6.6.1 Data Filter Options                             |    |

|   |             | 6.6.2 Data Filter Methods.                                         |    |

|   |             | U.U.L Data Filter Methods                                          | 42 |

| 8 |      | ences                                  |    |

|---|------|----------------------------------------|----|

| 7 | Summ | ary and Future Work                    | 46 |

|   | 6.10 | Communication View                     | 45 |

|   | 6.9  | Trace View                             |    |

|   |      | 6.8.4 Modifying Schedules              |    |

|   |      | 6.8.3 Gantt Data Filter                | 44 |

|   |      | 6.8.2 Gantt View Methods and Variables |    |

|   |      | 6.8.1 Gantt View Options               |    |

|   | 6.8  | Gantt View                             | 43 |

|   | 6.7  | Architecture View                      |    |

# **List of Figures**

| Traditional Design Process Versus Performance-Based Design                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ptolemy Terminology                                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Visual Representation of Hardware Architectures                                | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Visual Representation of An Execution Trace                                    | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

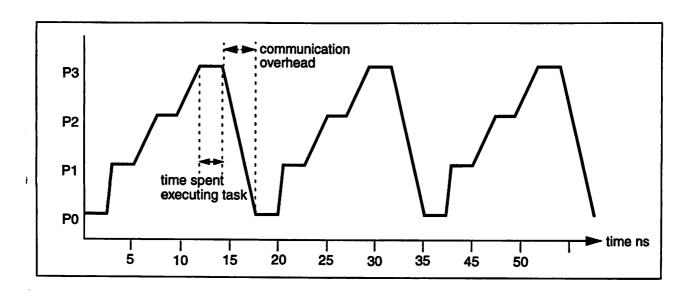

| Visual Representation of Communication Between Interconnected Processors       | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

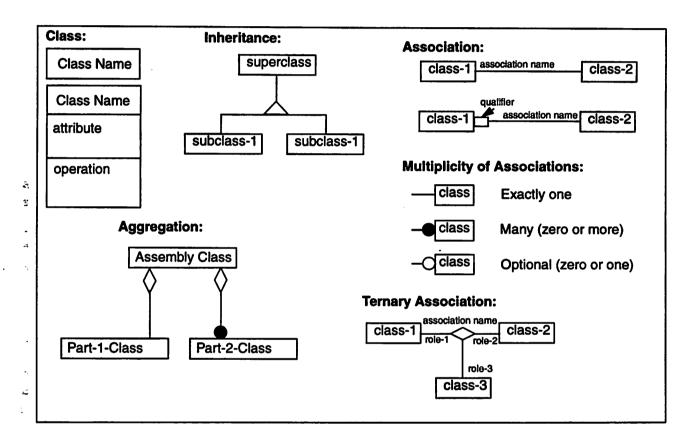

| Summary of Object Model Notation                                               | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

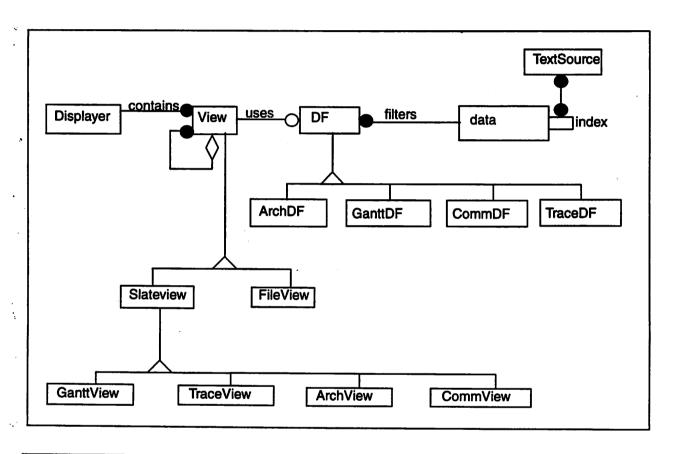

| Overview of the Object-Oriented Model for Visual Display of Design Information | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

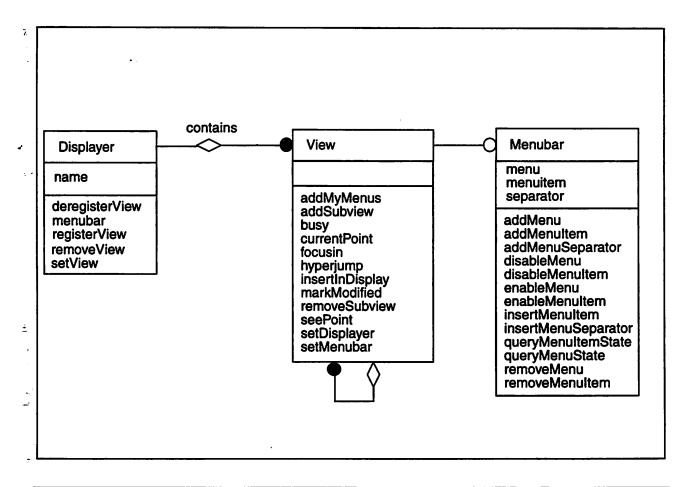

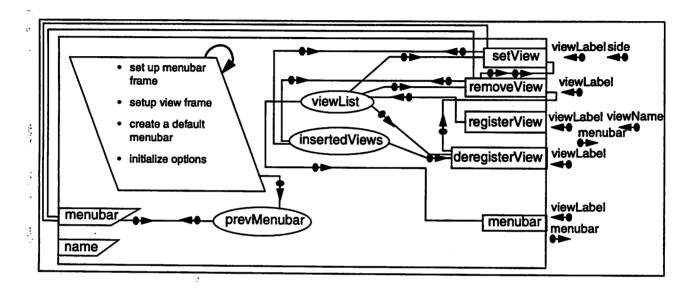

| The Displayer, Menubar and View Objects                                        | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

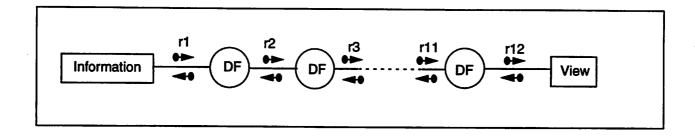

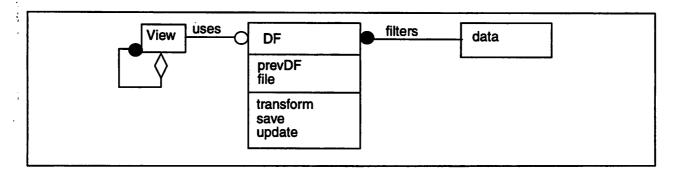

| The Data Filter Concept                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Data Filter                                                                    | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

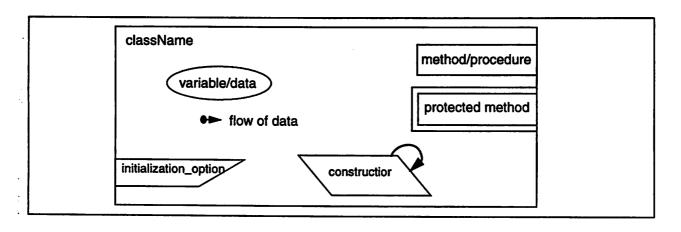

| Summary of Notation Used to Depict Implementation                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

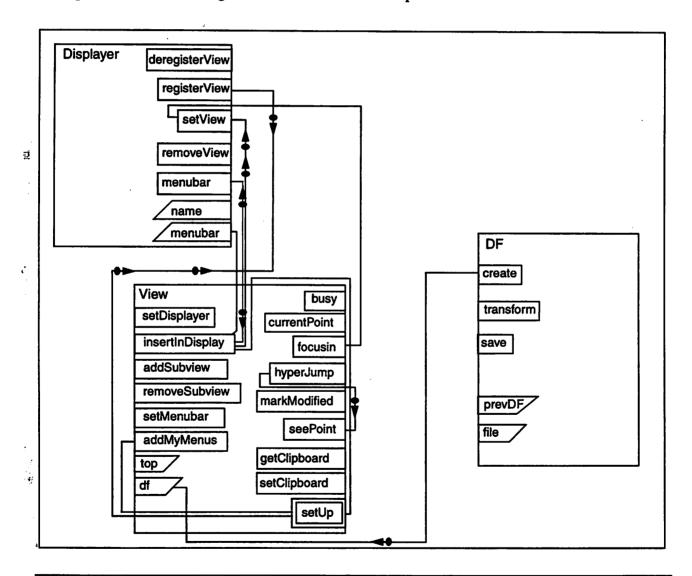

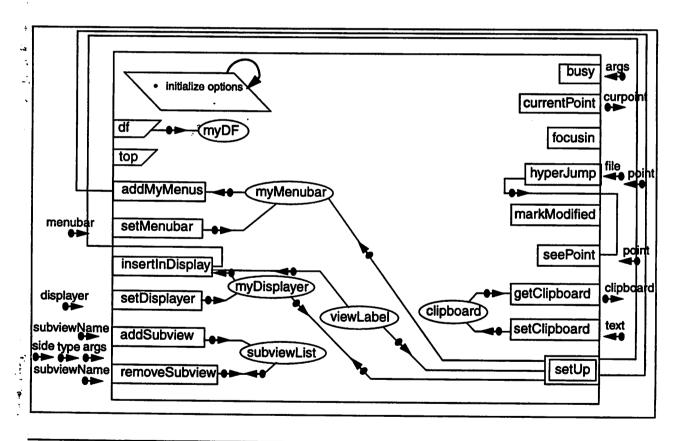

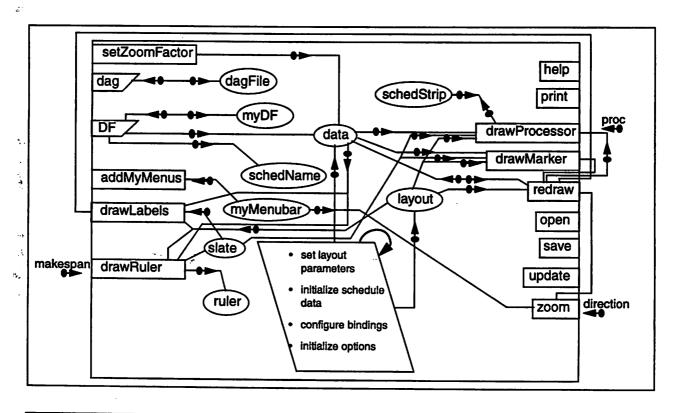

| An Overview of the Implementation of the Model for Design Visualization        | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Implementation of Displayer                                                    | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

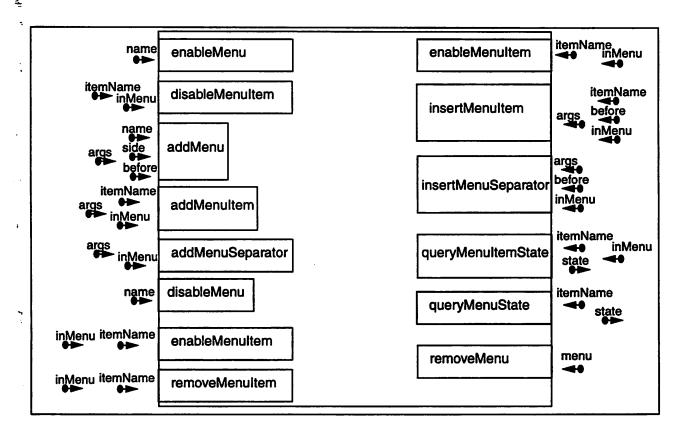

| Implementation of Menubar widget                                               | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Implementation of View                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

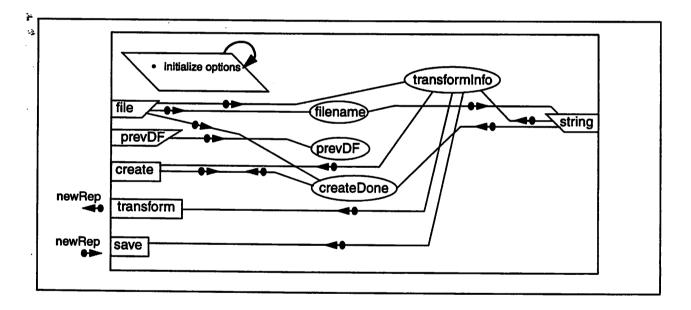

| Implementation of a Data Filter                                                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Implementation of Gantt View                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

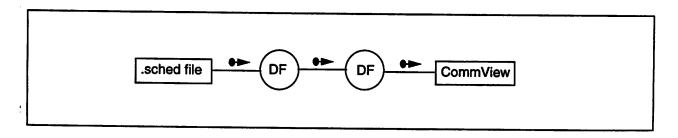

| Generating Communication Pattern View from a Schedule File                     | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                | Ptolemy Terminology  Visual Representation of Hardware Architectures  Visual Representation of An Execution Trace  Visual Representation of Communication Between Interconnected Processors  Summary of Object Model Notation  Overview of the Object-Oriented Model for Visual Display of Design Information  The Displayer, Menubar and View Objects  The Data Filter Concept  Data Filter  Summary of Notation Used to Depict Implementation  An Overview of the Implementation of the Model for Design Visualization.  Implementation of Displayer  Implementation of Menubar widget  Implementation of View  Implementation of Gantt View  Implementation of Gantt View |

# List of Tables

| Table 1. | Some applications that incorporate embedded systems | 4  |

|----------|-----------------------------------------------------|----|

| Table 2. | Types of Design Information                         |    |

| Table 3. | Summary of Domains in Ptolemy                       |    |

| Table 4. | Single Processor Schedulers in Ptolemy              |    |

| Table 5. | Multiple Processor Schedulers in Ptolemy            |    |

| Table 6. | Schedule File Format                                |    |

| Table 7. | Visual Representation of Different Schedules        | 25 |

| Table 8. | Architecture File Format.                           |    |

| Table 9. | Trace File Format                                   |    |

#### Introduction 1

Over the past decade, there has been a steady increase in the number of applications that demand - customized computer systems that offer high performance at low cost. These applications are, more often than not, characterized by the need to process large amounts of data in real time. Examples include consumer electronics, scientific computing, and signal processing systems. A selection of applications is given in Table 1 below.

Constraints on performance, cost and power make software implementations of data processing algorithms for such systems infeasible. Non-programmable hardware, however, does not support modifications of algorithms. The solution to this dilemma has been to develop application-specific hardware that is flexible and programmable – these systems are commonly referred to as embedded systems. They typically include embedded software that is burned into Eraseable Programmable Read Only Memory (EPROM) or resident in memory, special-purpose hardware, and Field Programmable Gate Arrays (FPGAs); often there are stringent requirements on power consumption, performance, and cost. Embedded systems cannot be redesigned or removed easily once the device that incorporates the system has been built.

Embedded systems development thus requires concurrent work on both hardware and software · components. The sophisticated nature of the algorithms that are run on these customized computer systems and the complexity of the hardware architecture make it very difficult for engineers to design algorithms that take full advantage of the underlying resources. This often results in sub-optimal performance and under-utilized hardware. Tuning the algorithm for optimum performance can be a very time-consuming and difficult task, especially if the system architecture is complex.

| Table 1. S        | ome applications that incorporate embedded systems                                                                                                                                     |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Military          | Communications, radar, sonar, image processing, navigation, missile guidance                                                                                                           |

| Automotive        | Engine control, brake control, vibration analysis, cellular telephones, digital radio, air bags, driver navigation systems                                                             |

| Medical           | Hearing aids, patient monitoring, ultrasound equipment, image processing, tomography                                                                                                   |

| Telecommunication | Echo cancellation, facsimile, speaker phones, personal communication systems (PCS), video conferencing, packet switching, data encryption, channel multiplexing, adaptive equalization |

| Consumer          | Radar detectors, power tools, digital TV, music synthesizers, toys, video games, telephones, answering machines, personal digital assistants, paging                                   |

| Industrial        | Robotics, numeric control, security access, visual inspection, lathe control, computer aided manufacturing (CAM), noise cancellation                                                   |

Interfacing software with hardware is a critical issue in embedded system design, since the best performance is achieved when algorithm and architecture interact to reduce communication costs between hardware components, input or output operations, and memory operations. Tools that provide the engineer with the ability to quickly develop, test, and refine algorithms on different hardware architectures are invaluable to the design process. Time to market and development costs are reduced, costly bugs can be eliminated, possible system failures may be avoided, and a wider set of possible solutions may be explored.

In the past, visualization techniques have been applied to various areas in engineering to simplify tasks faced by a design engineer. These techniques vary from drawing free-body diagrams or circuit diagrams to visualizing scientific data. In all cases, the visual techniques have proven to be invaluable to the design process. An early example of how visualization was used to improve worker performance is given in Gantt's 1919 paper, "Organizing for Work", where he shows how charts – visual representations of machine utilization, distribution of tasks across machines, and worker performance – easily disclose possible reasons for poor worker performance [7].

Recently, system engineers have realized that visualization techniques can be very useful to the embedded-system design process. Poor algorithm design, problematic hardware-software interfaces, and other possible reasons for sub-optimal performance are easily discovered by using such techniques. They have also realized that performance-based design can reduce the time to market a product greatly.

Scheduling is an important part of performance-based design. The scheduling process assigns software tasks to available hardware resources and determines the execution order of the tasks. For instance, a schedule that results in high resource utilization and low communication overhead can greatly improve performance. Even though engineers have realized that scheduling is an extremely important part of the design of an embedded system, they lack adequate tools for exploring appropriate scheduling strategies that exploit the full potential of a target architecture to meet timing and other performance constraints.

This report is divided into four parts. Following this introduction, concepts and issues relating to embedded system design are discussed. The next section builds upon the previous section and describes techniques that can be used to visualize the interaction between a given hardware architecture and an algorithm that is to be run on it. The goal is to easily identify whether the design of the algorithm is well-suited to the underlying hardware architecture of the embedded system or vice versa (the architecture is well-suited to the algorithm). This allows the designer to achieve the best performance possible. It may also provide a means to predict performance at an early stage of design. The third part focuses on the development of an object-oriented model for visual display of design information. The final part describes the software implementation of this model in a prototype that is used within the Ptolemy framework. The prototype implements architecture-algorithm interaction visualization techniques.

# Background and Theory

This section presents some of the principles and issues concerning the design of embedded systems that motivated the research presented in this report.

# <sup>2</sup>2.1 Embedded Systems and Their Design

A system can be defined as a group of devices or artificial objects or an organization forming a network especially for distributing something or serving a common purpose [13]. To embed a system into some object means to make that system an integral part of the object. When an engineer talks about an embedded system, he or she is usually referring to a system that satisfies a well-defined need at a specific instant in time. The system is usually dedicated to that need, and its operational limits are clearly defined: lifetime, power consumption, performance, and so on. The system usually has limited capabilities for future development, simply because it is permanently installed in a device that provides a certain service to its user. Examples include DSP processors in hand-held communication devices, programmable controllers installed in robots or cars, and video signal processors in television sets.

Because these systems cannot be redesigned or removed easily once the device that incorporates the embedded system is built, the development procedure must produce a correct system that meets all of its operational requirements. In addition, techniques used to design such systems must reduce development costs and time thereby reducing time to market. This is important since introducing a product to the consumer market early can mean that the producer will be facing fewer competitors and hence earning greater revenues and market share.

As stated in the introduction, some of the characteristics of embedded systems include embedded software that is burned into EPROM or resident in memory, special-purpose hardware, FPGAs, stringent requirements on power consumption, performance, and cost. Clearly, an embedded system consists of both hardware and software components. The performance and cost constraints make it necessary for the design engineer to explore a combination of possible hardware architectures or custom hardware components and software or programmable parts that would best suit the nature of the application. Hence, the division between the programmable and non-programmable components and their interface can become a critical issue in the design.

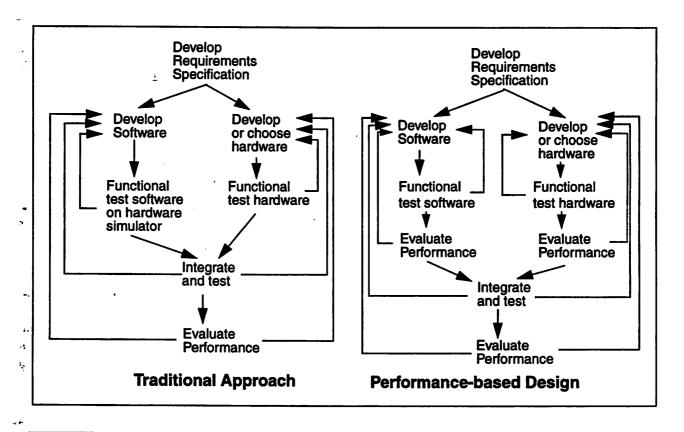

The development process is usually cyclic. The engineer often prototypes an algorithm, tests it on a specific hardware architecture, and then refines the software to make most efficient use of the underlying hardware. If software is to be embedded, this type of development can be very expensive and time-consuming as performance analysis is done after system components have been functionally tested and integrated. This traditional approach to design is shown in Figure 1 and is contrasted to performance-based design. Performance-based design advocates evaluating performance at early stages of design [27] such as after functional testing is complete. It is apparent from the figure that the number of iterations required to refine the design after integration of hardware and software would be much less than if the traditional approach was taken since performance is evaluated at a very early stage in development. Clearly, this strategy reduces implementation cost and time-to-market.

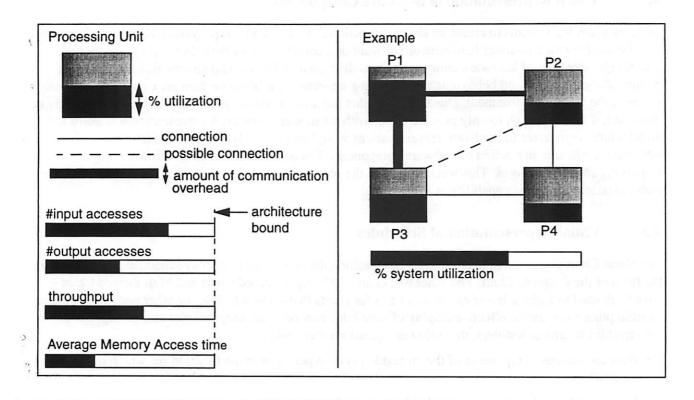

Modeling a system and simulating it before actual implementation can further reduce implementation cost and allow the user to explore the design space in search of an optimal solution. Finding this optimal solution can be a complicated task. The designer needs to be able to measure performance and decide whether other operational constraints will be met. The data that needs to be analyzed – processor

utilization, number of input or output accesses, number of memory accesses, and inter-processor communication overhead – can be large and difficult to sift through. A good visual display of data can lead the designer to quickly determine whether an algorithm and architecture will perform the given task optimally.

There are very few tools available that allow for performance-based design analysis through visualization as well as analytical techniques [28]. There are even fewer tools that allow a designer to explore embedded software solutions for multiple existing "off-the-shelf" hardware architectures. An important part of fitting software to hardware resources is the scheduling process. This is discussed in the next section.

Figure 1. Traditional Design Process Versus Performance-Based Design

# 2.2 Scheduling Concepts

Scheduling is an important part of the synthesis and operation of any system. The scheduling process assigns a subset of all the tasks that the system must perform to its available resources. The performance of a system can be greatly affected if the tasks are allocated to components that cannot efficiently perform those tasks. The sequence in which the tasks are executed can affect performance also.

When designing embedded systems, the engineer tries to ensure that utilization of hardware resources by software is high at all times. Mapping software to hardware components can be a formidable task if there are a large number of possible hardware resources (e.g. processors) and a large number of ways to partition

the software. A number of schedulers, mainly based on heuristics, have been developed to aid the designer map tasks to available processing units and determine their execution order [2][3][23][26].

Scheduling can be performed statically or dynamically. A static scheduler maps tasks to processing units and determines their execution order at compile time, whereas a dynamic scheduler determines this information during run-time. Sometimes choosing one schedule over another may cause a great enhancement in performance. It has not yet been determined whether the reason behind this is that the scheduler is well-suited to the target architecture, or simply because the scheduler does an inadequate job in scheduling the tasks within the given constraints.

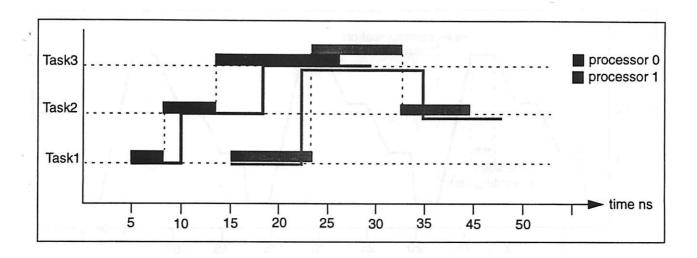

Normally, the engineer needs to quickly determine whether the mapping produced by a scheduler will cause the system to perform its intended function within the performance constraints at the lowest possible cost. Traditionally, Gantt Charts, based on concepts developed by Gantt in [7], have been used to visually represent schedules. These charts show how software components are mapped onto processing units over time. A detailed discussion of Gantt Charts is presented in Section 2.4.2.

Current visual displays of scheduling information, which are based on the linear representation developed by Gantt, are only effective in highlighting resource utilization, processor idle time, and task execution order. This representation is inadequate for revealing possible performance bottlenecks and problematic hardware-software interfaces which can greatly affect overall system performance. In addition, scheduling techniques have evolved and a number of the schedulers that use these techniques generate schedules that cannot be effectively displayed using the traditional Gantt Chart. Section 4.3 discusses ways of modifying this display to effectively visualize schedules generated by these newer schedulers.

# 2.3 Evaluating Algorithms and Their Performance On Given Architectures

It is necessary to gather data about the execution of the algorithm on a target architecture and analyze it in order to evaluate system performance. Evaluating the performance of a system requires gathering, sifting, and displaying many types of information: data from manufacturers, measurements on earlier systems, estimates made during analysis, and availability of logical and physical resources [27]. Scheduling descriptions for logical and physical resources and allocation of processes to hardware or software are emerging to be quite important factors in determining the performance of a system. This section briefly discusses the various types of information that are required to evaluate algorithm performance and current techniques that are used to present the data to design engineers.

## Processor Utilization

Processor utilization is normally determined by finding the time spent computing or doing useful work in relation to the total time required for the task. Traditional Gantt Charts are normally used to display this information.

## Input or Output Accesses

An input or output access occurs when data is either input to the system or output from the system. An input or output operation's performance can be measured in terms of response time or throughput [11]. The response time is measured as the length of time taken for the operation to complete, starting from when the data was placed in a buffer until the time when it is finally output or input. The throughput is the average amount of data that is input or output during a given amount of time.

#### Memory Operations

A memory operation occurs when data is either written to or read from a memory location. The memory access time is measured as the hit time plus the miss rate multiplied by the miss penalty (avg.

mem. access time = hit time + miss rate \* miss penalty) [11]. It is clear that a memory operation that needs to access data residing in local memory on a processor will take less time than an operation that needs to access data residing at a remote location.

### Communication Overhead

Communication overhead is usually considered important in evaluating multiple processor systems. It is the total time spent sending and receiving data between processors in relation to the total execution time. This information has traditionally been displayed in Gantt Charts. Communication overhead can also be described as the time spent sending and receiving messages between concurrent processes in relation to the overall execution time.

#### Critical Paths

A critical path is the longest serial thread, or chain of dependencies, running through an execution of an algorithm [9]. Critical paths are important performance analysis abstractions as the total execution time cannot be reduced without shortening the length of a critical path. Critical paths are potential places for performance bottlenecks.

#### Architecture Bounds

There are physical limits placed on all hardware resources such as processor speeds, memory access times, bus speeds, and so on. This of course limits the performance of any software. Each architecture has different bounds, hence a single piece of software may perform differently on different architectures.

## **2.3.1** Performance and Performance Models

There are number of ways of measuring the performance of a computer system. A system user may evaluate performance by measuring the time that it takes between the start and completion of an event, to therwise known as response time or execution time, or latency. Other people, such as network managers, may use the total amount of work done in a given amount of time which is commonly referred to as throughput as a measure of performance. In all cases, time is the basis for measures of system performance [11]. A system that can perform a given task in the least amount of time is said to be the fastest or has the best performance.

Performance models can be useful as they can be used to abstract system behaviour and can allow engineers to predict and analyze system performance. Performance-based design dictates that performance models should be integrated with functional design and resource scheduling. Models that use early estimates of processing costs of parts of a design can aid in planning software architectures, assessing needs to distribute data and functionality, and hardware planning [27].

In order to obtain adequate and predictable performance, it is important to characterize system behaviour: sequences of events, actions, and delays. In addition, it is important to provision and schedule physical and logical resources: hardware (processors, input or output devices, memory, interconnections) and things such as locks and semaphores. Abstract models such as queuing networks, Petri nets, or other simulation models of available resources have been developed in order to aid in performance analysis which helps in determining contention delays, resource saturation at bottlenecks, load imbalance, and interprocessor or interprocess communication overhead [27]. Simulating a system can generate possible execution paths that may reveal critical paths which can lead to discovery of bottlenecks and other causes of low performance.

## 2.4 Visual Display of Design Information

Design information comes in a multitude of flavours. Whether a system is implemented in hardware or software or both, design information is always present and required at all stages of development. An attempt has been made in Table 2 to categorize the various types in terms of high-level or low-level details whether the design is hardware-based or software-based.

| <b>Table 2.</b> Types of D | Design Information |

|----------------------------|--------------------|

|----------------------------|--------------------|

| High-Level                                                                      | Low-Level                                                                        |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Specification (requirements, architecture descriptions, interface descriptions) | Implementation (software programs, netlists, hardware description language code) |

| Documentation (includes bug reports)                                            | Execution history (traces, execution times, latency measurements)                |

| Design constraints (performance, cost, power, memory)                           | Modification history and version information                                     |

For many years, hardware engineers have relied on visual representations of design information to guide them through the development process. Some of the forms that these visualizations take are circuit diagrams, signal traces, and architecture block diagrams. Comparable visualizations for systems implemented in software are few in number. For purely parallel systems, tools that visualize execution, schedules, and communication patterns exist [9] but are sometimes inadequate for complicated architectures. For uniprocessor and multiprocessor embedded systems, especially those that incorporate both hardware and software modules, very little exists in terms of visualizing architecture, execution, and performance.

Recent interest in visualizing software performance analysis of parallel systems has brought about the advent of some basic visualization concepts and principles. These concepts which are briefly summarized in the following section can be used to create effective visual representations of design information.

#### 2.4.1 Visualization Basics

In [9] and [10] M. T. Heath et. al. outline basic concepts and principles that are necessary to produce effective graphical displays. Good visualization techniques can have dramatic impact in areas where they can lead to a discovery of unexpected phenomena. This is something that must always be kept in mind when designing new visualization techniques. Users are not interested in pretty pictures but something that will lead them to construct an empirical model of behaviour.

Some of the basic principles that must be considered when developing visualization techniques are:

- Users should be able to relate the display of information to a context [9]. The visualization should allow a user to connect the display to an environment from which it is derived.

- Any visualization tool must be able to scale easily to large data sets and there must be a means for a user to give the tool feedback.

- A user should be able to tune the tool to their needs.

- An important but often overlooked concept is generation of multiple views of a body of design information. This is important for yielding insight into the behavioural characteristics of the system and their causes [9].

- Techniques such as using colour or size to highlight useful information from large raw data sets are also necessary.

The visualization of algorithm and architecture interaction developed in this project use the above principles as the basis for their design in combination with the principles underlying Gantt Charts, trace displays, and space-time diagrams which are summarized in the following three sections.

## 2.4.2 Gantt Charts

The Gantt chart was the brainchild of H. L. Gantt, a consulting management engineer who developed methods of planning, production recording, stores-keeping and cost-keeping. He developed three basic charts: Machine Record Chart, Progress Chart, and Man Record Chart. The first displays the amount of time a machine is working, the cumulative working time of an individual machine, the cumulative working time of a group of machines, and reasons for idleness [7]. The Progress Chart gives a distribution of tasks across machines, the rate of work, and the activities on the chart are measured by the amount of time needed to perform them. This chart defines a schedule as it maps tasks to machines and determines their the task execution order. It shows how that schedule is being lived up to by comparing what has been done and what should have been done. If this chart is detailed enough, it can indicate probability of future performance and anticipate needs. The third chart compares what a worker has done with what should have been done: it records a worker's performance. This chart makes it possible to trace the lack of production to its sources.

Gantt created these charts in order to:

- find out how plants are performing the function for which they were created;

- find out reasons why they are not doing as well as they should;

- remove obstacles which hamper them in the performance of their function.

Gantt was trying to solve a planning problem. Designing an embedded system requires similar planning, production recording, stores-keeping, and cost-keeping in order to achieve optimal performance. Hence applying the basic concepts developed by Gantt to embedded system design leads naturally to performance-based design depicted in Figure 1. In addition to using Gantt Charts to discover possible reasons for poor performance, trace displays and space-time diagrams can be useful in empirically modeling system behaviour.

# 2.4.3 Trace Displays

A trace represents an instance of execution of a system. It helps a user model system behaviour and can lead to discovery of unexpected phenomena. Trace files are used to capture performance details by logging operations performed by a system to a file. This raw data then can be analyzed to determine system behaviour. Good visualizations of traces allow the user to look at the traces in a format similar to looking at signals on an oscilloscope which may reveal critical paths.

# 2.4.4 Space-Time Diagrams

A space-time diagram shows message passing and communication between different processing units in a system [10]. Diagrams depicting communication behaviour can bring to light patterns of behaviour that can indicate program loops, or can allow a user to determine reasons for low utilization such as poor message-passing techniques and inadequate pipelining.

# 3 The Ptolemy and Tycho Frameworks

## 3.1 Ptolemy

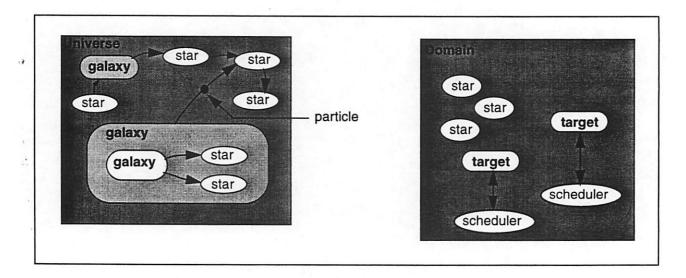

Ptolemy is an environment for specifying, simulating, and synthesizing heterogeneous systems. Many of these systems combine control-flow oriented processes with data-flow oriented processes resulting in subsystems that must be modeled using different models of computation. Ptolemy was designed to allow mixing of different models of computation to specify such systems [18]. A system, application, or algorithm can be specified in Ptolemy by representing it visually in terms of whichever semantics seem feasible for the problem. The system specification may contain homogeneous or heterogeneous semantics and a user may wish to divide the system into subsystems that manage specific tasks in a modular fashion. These functional blocks are known as *stars* in Ptolemy. Data that flows along the arcs connecting the stars are known as *particles*. An interconnection of stars is known as a *galaxy* which may represent the entire system or a part of the system. A complete application is known as a *universe* which is an interconnection of stars and galaxies. Hierarchy is used to manage complexity and mix different models of computation [24].

A target is a modular object in Ptolemy which describes particular features of the target hardware architecture which will implement the design. It manages a simulation or synthesis process. A user can specify target-specific information either at run-time or choose from a standard set of pre-specified options. If no processor-specific information is provided, the target is asked to determine the communication costs and each of the functional blocks are asked to determine execution time and resources required. The target controls operations such as scheduling, compiling, assembling, and downloading code. A scheduler object is associated with each target and it determines how stars will be mapped onto available resources and their execution order. A domain is a collection of stars, schedulers, and targets. It implements a particular model of computation [24] and either performs simulation or code generation. Figure 2 clarifies the aforementioned terms and Table 3 [24] summarizes all the domains available within Ptolemy.

Figure 2. Ptolemy Terminology

Table 3.

Summary of Domains in Ptolemy

| Domain                                        | Description                                                                                                                                       |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                               | <ul> <li>Oldest and most mature domain; it is a sub-domain of<br/>DDF, BDF, and PN.</li> </ul>                                                    |  |

|                                               | <ul> <li>Special case of data flow model of computation<br/>developed by Dennis [5].</li> </ul>                                                   |  |

|                                               | <ul> <li>Flow is completely predictable at compile time thus<br/>allows for efficient scheduling.</li> </ul>                                      |  |

| Synchronous Data Flow (SDF)                   | <ul> <li>Allows for static scheduling.</li> </ul>                                                                                                 |  |

|                                               | <ul> <li>Good match for synchronous signal processing systems<br/>with sample rates that are rational multiples of one<br/>another.</li> </ul>    |  |

|                                               | <ul> <li>Supports multi-rate applications and has a rich star<br/>library.</li> </ul>                                                             |  |

|                                               | Range of applications is limited.                                                                                                                 |  |

|                                               | <ul> <li>Versatile model of computation as it supports<br/>conditionals, data-dependent iteration, and true<br/>recursion.</li> </ul>             |  |

| Dynamic Data Flow (DDF)                       | <ul> <li>More general than SDF.</li> </ul>                                                                                                        |  |

| Dynamic Data Flow (DDF)                       | <ul> <li>Uses dynamic (run-time) scheduling which is more<br/>expensive than static scheduling.</li> </ul>                                        |  |

|                                               | <ul> <li>Good match for signal processing applications with a<br/>limited amount of run-time control.</li> </ul>                                  |  |

|                                               | <ul> <li>Relatively new domain which supports run-time flow of control.</li> </ul>                                                                |  |

| Boolean Data Flow (BDF)                       | <ul> <li>Attempts to construct a compile-time schedule to try<br/>and achieve efficiency of SDF with generality of DDF.</li> </ul>                |  |

|                                               | <ul> <li>More limited than DDF.</li> </ul>                                                                                                        |  |

|                                               | <ul> <li>Constructs an annotated schedule: execution of a task is<br/>annotated with a boolean condition.</li> </ul>                              |  |

|                                               | Very new to Ptolemy and still experimental.                                                                                                       |  |

| Integer and State Controlled Data Flow (STDF) | <ul> <li>Realizes data flow control by integer control data and<br/>port statuses. It is an extension to BDF.</li> </ul>                          |  |

| (CIDI)                                        | <ul> <li>Scheduling is static and conditional like BDF.</li> </ul>                                                                                |  |

|                                               | <ul> <li>It has user-defined evaluation functions.</li> </ul>                                                                                     |  |

|                                               | <ul> <li>Relatively mature domain which uses an event-driven model of computation.</li> </ul>                                                     |  |

| Discrete Event (DE)                           | <ul> <li>Particles carry time-stamps which represent events that<br/>occur at arbitrary points in simulated time.</li> </ul>                      |  |

|                                               | <ul> <li>Events are processed in chronological order.</li> </ul>                                                                                  |  |

|                                               | Very new to Ptolemy and still experimental.                                                                                                       |  |

| Fig. 6. A. M. I. See S.                       | Good match for control-oriented systems like real-time                                                                                            |  |

| Finite State Machine (FSM)                    | <ul> <li>process controllers.</li> <li>Uses a directed node-and-arc graph called a state transition diagram (STD) to describe the FSM.</li> </ul> |  |

Table 3. Summary of Domains in Ptolemy

| Domain                                            | Description                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                   | Implements behaviour of functions that may take a function as an argument and return a function.                                                                                                                                                                                                                            |

| Higher Order Functions (HOF)                      | <ul> <li>HOF collection of stars may be used in all other domains.</li> </ul>                                                                                                                                                                                                                                               |

|                                                   | <ul> <li>Intended to be included only as a sub-domain by other<br/>domains.</li> </ul>                                                                                                                                                                                                                                      |

|                                                   | <ul> <li>Relatively new domain that implements Kahn process<br/>networks which is a generalization of data flow –<br/>processes replace actors.</li> </ul>                                                                                                                                                                  |

| Process Network (PN)                              | • Implements concurrent processes but without a model of time.                                                                                                                                                                                                                                                              |

|                                                   | <ul> <li>Uses POSIX threads.</li> </ul>                                                                                                                                                                                                                                                                                     |

|                                                   | <ul> <li>SDF, BDF, and DDF are sub-domains of PN.</li> </ul>                                                                                                                                                                                                                                                                |

|                                                   | Relatively new and experimental.                                                                                                                                                                                                                                                                                            |

| Multidimensional Synchronous Data                 | <ul> <li>Extends SDF to multidimensional streams.</li> </ul>                                                                                                                                                                                                                                                                |

| Flow (MDSDF)                                      | <ul> <li>Provides ability to express a greater variety of dataflow<br/>schedules in a graphically compact way.</li> </ul>                                                                                                                                                                                                   |

|                                                   | <ul> <li>Currently only implements a two-dimensional stream.</li> </ul>                                                                                                                                                                                                                                                     |

|                                                   | Very new to Ptolemy and still experimental.                                                                                                                                                                                                                                                                                 |

| Synchronous/Reactive (SR)                         | <ul> <li>Implements model of computation based on model of<br/>time used in Esterel.</li> </ul>                                                                                                                                                                                                                             |

|                                                   | <ul> <li>Good match for specifying discrete reactive controllers</li> </ul>                                                                                                                                                                                                                                                 |

|                                                   | <ul> <li>Base domain from which all code generation domains are derived.</li> </ul>                                                                                                                                                                                                                                         |

|                                                   | <ul> <li>Supports a dataflow model that is equivalent to BDF<br/>and SDF semantics.</li> </ul>                                                                                                                                                                                                                              |

|                                                   | <ul> <li>This domain only generates comments, allows viewing<br/>of the generated comments, and displays a Gantt Chart<br/>for parallel schedules.</li> </ul>                                                                                                                                                               |

| Code Generation (CG)                              | <ul> <li>Can only support scalar data types on the input and<br/>output ports.</li> </ul>                                                                                                                                                                                                                                   |

|                                                   | <ul> <li>All derived domains obey SDF semantics.</li> </ul>                                                                                                                                                                                                                                                                 |

|                                                   | <ul> <li>Useful for testing and debugging schedulers.</li> </ul>                                                                                                                                                                                                                                                            |

|                                                   | <ul> <li>Targets include bdf-CGC which supports BDF, default<br/>CGC which supports SDF semantics, TclTk_Target<br/>which supports SDF and must be used when Tcl/Tk<br/>stars are present, and unixMulti_C which supports SDF<br/>semantics and partitions the graph for multiple<br/>workstations on a network.</li> </ul> |

|                                                   | Uses data flow semantics and generates C code.                                                                                                                                                                                                                                                                              |

| Code Generation in C (CGC)                        | <ul> <li>Generated C code is statically scheduled and memory<br/>used to buffer data between stars is statically allocated.</li> </ul>                                                                                                                                                                                      |

| Code Generation for the Motorola DSP 56000 (CG56) | <ul> <li>Synthesizes assembly code for the Motorola DSP56000 family.</li> </ul>                                                                                                                                                                                                                                             |

| Table 3. | Summary of Domains in Ptolemy |  |

|----------|-------------------------------|--|

|          |                               |  |

| Domain                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Code Generation in VHDL (VHDL, VHDLB) | <ul> <li>Relatively new and experimental</li> <li>Generates VHDL code.</li> <li>VHDL domain supports SDF semantics whereas VHDLB supports behavioural models using native VHDL discrete event model of computation.</li> <li>Many targets to choose from.</li> <li>VHDL domain is good for modeling systems at functional block level whereas VHDLB is good for modeling behaviour of components and their interactions at all levels of abstraction.</li> </ul> |

A user may simulate the specified system or generate code for a specific target architecture. Once a user selects a target architecture, code generation can begin. Scheduling is the first stage of code generation in Ptolemy and Section 3.3 discusses it in detail

Developers and users of Ptolemy have found that it has lacked proper facilities to visualize execution traces, schedules for uniprocessor and multiprocessor systems, and performance data. This project aims to fill this need by incorporating appropriate visualization techniques into Ptolemy using Tycho as the basis for the implementation. Tycho is briefly described in the next section.

## 3.2 Tycho

Tycho is a software system designed to complement the Ptolemy framework with a hierarchal syntax manager. Some of the key objectives of the Tycho project are to provide an extensible framework for experimentation with visual syntaxes and to provide a mechanism for system design management. Tycho is based on an object-oriented software architecture which is designed to allow for easy integration of textual and graphical editors and displays. The focus is on allowing users to mix different syntactic models such as allowing combinations of textual and graphical syntaxes. It is a relatively new project and is still in its infancy stages.

## 3.3 Scheduling in Ptolemy

As stated earlier, scheduling is the first stage of code generation in Ptolemy. Currently, code generation facilities exist for Synchronous Data Flow (SDF), Boolean Data Flow (BDF), and Integer and State-controlled Data Flow (STDF) semantics [24]. Since all of the code generation domains support SDF semantics and due to the fact that the SDF domain is the most mature of all the domains, the following description of scheduling will be discussed with respect to SDF semantics. The concepts are easily extended to the other domains.

Code generation begins after the application or algorithm has been specified using a data flow graph and a target hardware architecture description has been selected. The target object contains information specific to the hardware architecture: number of processors, communication costs, interconnection topology, and so on. Several single and multiple processor schedulers use different algorithms for determining partitioning and order of execution of functional blocks. For multiprocessor systems, an acyclic precedence graph (APEG) must be created for every SDF graph before a schedule can be generated. The APEG displays the

precedence relations between the invocations of the SDF functional blocks. All schedulers designed for multiprocessor systems use the generated APEG as input [24].

Several types of schedulers exist within the Ptolemy framework. Some schedulers ignore hierarchy that may be present in the SDF graph in order to maximize concurrency, whereas others use hierarchy to minimize complexity. There are some schedulers that have been designed by Ptolemy researchers that create a new hierarchy by clustering a scheduling graph to take advantage of the natural looping structure of the code. No single scheduler can handle all situations so Ptolemy allows a user to mix and match different schedulers for specific applications [24].

A summary of the types of schedulers available in Ptolemy is given in Table 4 and Table 5 [24]. The terminology used in the tables is described in the following section.

# 3.3.1 Scheduling Terminology

This section briefly describes some of the terms used in Table 4 and Table 5.

#### • APEG

APEG abbreviates acyclic precedence graph. The nodes in this graph represent tasks or computations and the directed arcs represent precedence constraints and data paths. Each arc has a label which specifies the amount of data that the source node passes to the destination node. An APEG can be derived from a SDF representation [26].

### Looped Schedule

A looped schedule is one which may contain any number of schedule loops. A schedule loop consists of m number of actors or functional blocks that are repeated in succession n times. Loops in a looped schedule may be nested [3].

#### Clustering

For each node in a SDF graph, there are q corresponding nodes in an APEG. The number q represents how many times the SDF node must be invoked in order to satisfy data precedences in the SDF graph. This expansion can result in exponential growth of nodes in the APEG. Clustering SDF graph nodes into composite nodes can limit the expansion resulting in a simpler APEG. The clusters may be scheduled much like actors resulting in hierarchical schedules [22].

## • Buffers and Buffering

Each edge in a SDF graph corresponds to first-in-first-out queue that buffers tokens that pass along the edge. The queue is known as the *buffer* for the edge; the process of maintaining the queue of tokens is known as *buffering* [3].

### Single Appearance Schedule

A single appearance schedule is one in which each actor or functional block appears only once in the entire schedule [3].

Table 4. Single Processor Schedulers in Ptolemy

| Scheduler Name                        | Features                                                                                                                                                                                                                                                                                             |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Default SDF Scheduler                 | <ul> <li>Performed at compile time.</li> <li>Many possible schedules but schedule is chosen based on a heuristic that minimizes resource costs and amount of buffering required.</li> <li>No looping employed so if there are large sample rate changes, size of generated code is large.</li> </ul> |

| Joe's Scheduler                       | <ul> <li>Performed at compile time.</li> <li>Sample rates are merged wherever deadlock does not occur.</li> <li>Loops introduced to match the sample rates.</li> <li>Results in hierarchical clustering.</li> <li>Heuristic solution so some looping possibilities are undetected.</li> </ul>        |

| SJS (Shuvra-Joe-Soonhoi)<br>Scheduler | <ul> <li>Performed at compile time.</li> <li>Uses Joe's Scheduler at front end and then uses an algorithm on the remaining graph to find the maximum amount of looping available.</li> </ul>                                                                                                         |

| Acyclic Loop Scheduler                | <ul> <li>Performed at compile time.</li> <li>Constructs a single appearance schedule that minimizes amount of buffering required.</li> <li>Only intended for acyclic dataflow graphs.</li> </ul>                                                                                                     |

Table 5.

Multiple Processor Schedulers in Ptolemy

| Scheduler Name                  | Features                                                                                                                                                                                                                                                |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Hu's Level-based List Scheduler | <ul> <li>Performed at compile time.</li> <li>Most widely used.</li> <li>Tasks assigned priorities and placed in a list in order of decreasing priority.</li> <li>Ignores communication costs when assigning functional blocks to processors.</li> </ul> |  |

| Sih's Dynamic Level Scheduler   | <ul> <li>Performed at compile-time.</li> <li>Assumes that communication and computation can be overlapped.</li> <li>Accounts for interprocessor communication overheads and interconnection topology.</li> </ul>                                        |  |

Table 5. Multiple Processor Schedulers in Ptolemy

| Scheduler Name                | Features                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Sih's Declustering Scheduler  | <ul> <li>Performed at compile-time.</li> <li>Addresses trade-off between exploiting parallelism and interprocessor communication overheads.</li> <li>Analyzes a schedule and finds the most promising placements of APEG nodes.</li> <li>Not single pass but takes an iterative approach.</li> </ul>                      |  |