## Copyright © 1996, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# THE DESIGN AND IMPLEMENTATION OF A SEMI-CUSTOM TRANSMITTER FOR A CDMA DIRECT SEQUENCE SPREAD-SPECTRUM TRANSCEIVER

by

Dennis G. Yee

Memorandum No. UCB/ERL M96/80

17 December 1996

# THE DESIGN AND IMPLEMENTATION OF A SEMI-CUSTOM TRANSMITTER FOR A CDMA DIRECT SEQUENCE SPREAD-SPECTRUM TRANSCEIVER

by

Dennis G. Yee

Memorandum No. UCB/ERL M96/80

17 December 1996

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## The Design and Implementation of a Semi-Custom Transmitter for a CDMA Direct Sequence Spread-Spectrum Transceiver

by

#### Dennis G. Yee

Master of Science in Electrical Engineering and Computer Science

University of California at Berkeley

#### **Abstract**

High-performance wireless communications systems allow access to real-time data located on a high-speed network using portable, low-power terminals. For a pico-cellular network, a basestation within each cell serves as the interface between the backbone network and the various mobile units. A CDMA direct sequence spread-spectrum transmitter is presented which allows the basestation to provide a 1Mbps downlink to each of 15 portable multimedia terminals within the cell. The total transmit bandwidth is 41.6MHz centered at a carrier frequency of 1.056GHz. This design can be easily scaled to support up to 50 users within a single cell.

#### Acknowledgements

As with any endeavor, this research project could not have been completed without the help and support of others. Foremost, I wish to thank my research advisor Professor Robert Brodersen. Your guidance throughout the course of this project is greatly appreciated. I would also like to thank Professor Paul Gray for reviewing this thesis and providing helpful comments.

I am greatly indebted to Sam Sheng for his friendship and his selflessness in teaching me everthing I know about RF design. The success of this project would not have been possible without your guidance. Thanks Sam!

I am grateful to Jim Peroulas for answering all my questions about the baseband modulator chip so promptly and Craig Teuscher for giving me crash courses on communications theory. Both Ian O'Donnell and Tom Burd were very helpful, especially with charge leakage issues. I would also like to thank Mike Kauffman at Hewlett-Packard for providing me with the HPMX-2001 quadrature modulator and Lapoe Lynn for helping me decipher the front-end of the CDMA receiver. For their administrative support, Peggye Brown, Tom Boot and Elise Mills receive my sincere gratitude. I would also like to thank the California MICRO program and the Advanced Research Projects Agency for their generous financial support.

Finally, I would like to thank my family and friends for their support and encouragement.

I am very lucky to have wonderful friends like Richard, Bryant, Albert and Ben.

Yvette, you have made the last six years the richest and most fulfilling of my life. Thanks for your patience and understanding during the many evenings and weekends required for the completion of this project.

Dave, you are always there for me, even when you are over 800 miles away. Thanks big bro!

Mom and Dad, your continual love and encouragment have been a source of strength for the past 24 years. I dedicate this work to you with all my love.

### **Table of Contents**

| CHAPTER 1. | Introduction                                                 | . 1 |

|------------|--------------------------------------------------------------|-----|

| CHAPTER 2. | Transmitter Architecture                                     | . 3 |

| 2.1. Tra   | ansmitter System-Level Overview                              | . 3 |

|            | aseband Modulator                                            |     |

|            | DQPSK Encoding                                               |     |

| 2.1.1.2.   | Walsh Encoding and PN Scrambling                             | . 6 |

|            | Power Control                                                |     |

|            | Raised-Cosine Filtering                                      |     |

|            | IF Modulation                                                |     |

|            | Pata Converter                                               |     |

|            | Data Combining                                               |     |

| 2.1.2.2.   | Digital-to-Analog Conversion and Droop Compensation          | 15  |

| 2.1.2.3.   | Lowpass Filter                                               | 16  |

| CHAPTER 3. | Single-Sideband Upconversion                                 | 17  |

| 3.1. Sin   | ngle-Sideband Upconversion                                   | 19  |

| 3.1.1. F   | ilter Method                                                 | 19  |

|            | hase-Shift Method                                            |     |

| 3.1.2.1.   | Hilbert Transformer: Analog Implementations                  | 23  |

| 3.1.2.1.1  |                                                              | 23  |

| 3.1.2.1.2  | Asymmetric Polyphase Networks                                | 29  |

| 3.1.2.2.   | Hilbert Transformer: Digital Implementations                 | 31  |

| 3.1.2.1.1  | Post-Modulator Double-Sideband to Single-Sideband Converter  | 31  |

| 3.1.2.1.2  | Incorporation of Digital Hilbert Transformer within Baseband |     |

|            | Modulator                                                    | 34  |

| 3.1.3. V   | Veaver Method                                                | 37  |

| 3.1.3.1.   | Double Upconversion Method                                   | 38  |

| 3.1.3.2.   | Down-Up Method                                               | 38  |

|            | rdware Requirements                                          |     |

| CHAPTER 4. | Final Transmitter Design and Implementation                  | 44  |

| 4.1. Im    | plementation Procedure                                       | 46  |

| 4.1.1. S   | Schematic Entry and Component Selection                      | 47  |

| 4.1.1.1.   | System Clocks                                                | 48  |

| 4.1.1.2.   | Digital-to-Analog Converter                                  | 48  |

| 4.1.1.3.   | Lowpass Filter                                               | 51  |

| 4.1.1.4.   | Quadrature Modulator                                         | 51  |

| 4.1.1.5.   | Quadrature Clock Generation                                  | 54  |

| 4.1.1.6                                                                                                  | . Emission Masking                                                                                                                                                                                                                                                       | 54                                                                         |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| 4.1.1.7                                                                                                  | Surface Mount Components                                                                                                                                                                                                                                                 | 56                                                                         |

| 4.1.2.                                                                                                   | Design Simulation and Verification                                                                                                                                                                                                                                       | 56                                                                         |

| 4.1.3.                                                                                                   | Printed Circuit Board Layout                                                                                                                                                                                                                                             | 58                                                                         |

| 4.1.3.1                                                                                                  | . Routing                                                                                                                                                                                                                                                                | 58                                                                         |

| 4.1.3.2                                                                                                  |                                                                                                                                                                                                                                                                          | 59                                                                         |

| СНАРТЕ                                                                                                   | R 5. Testing and Measurements                                                                                                                                                                                                                                            | 61                                                                         |

| 5.1.                                                                                                     | Verification of Correct Functionality                                                                                                                                                                                                                                    | 61                                                                         |

| 5.1.1.                                                                                                   | Eye Diagram                                                                                                                                                                                                                                                              | 61                                                                         |

| 5.1.2.                                                                                                   | Spectral Outputs                                                                                                                                                                                                                                                         | 63                                                                         |

| 5.1.3.                                                                                                   | Autocorrelation Performance                                                                                                                                                                                                                                              |                                                                            |

| 5.1.4.                                                                                                   | Quadrature LO Generator                                                                                                                                                                                                                                                  |                                                                            |

| 5.2.                                                                                                     | Speed and Power Measurements                                                                                                                                                                                                                                             |                                                                            |

| 5.3.                                                                                                     | Bugs                                                                                                                                                                                                                                                                     | 72                                                                         |

| 5.3.1.                                                                                                   | Baseband Modulator Chip                                                                                                                                                                                                                                                  |                                                                            |

| 5.3.2.                                                                                                   | Testboard                                                                                                                                                                                                                                                                | 73                                                                         |

| CHAPTE                                                                                                   | R 6. Conclusion                                                                                                                                                                                                                                                          | 75                                                                         |

| CIMIL ID.                                                                                                |                                                                                                                                                                                                                                                                          |                                                                            |

| 6.1.                                                                                                     | Summary                                                                                                                                                                                                                                                                  | 75                                                                         |

|                                                                                                          |                                                                                                                                                                                                                                                                          | 75                                                                         |

| 6.1.<br>6.2.                                                                                             | Summary                                                                                                                                                                                                                                                                  | 75<br>75                                                                   |

| 6.1.<br>6.2.<br><b>Bibliogra</b> p                                                                       | Summary Future Directions                                                                                                                                                                                                                                                | 75<br>75<br>77                                                             |

| 6.1.<br>6.2.<br><b>Bibliogra</b> p                                                                       | Summary Future Directions                                                                                                                                                                                                                                                | 75<br>75<br>77<br>79                                                       |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix                                                                   | Summary  Future Directions                                                                                                                                                                                                                                               | 75<br>75<br>77<br>79<br>79                                                 |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix<br>A.1.                                                           | Summary                                                                                                                                                                                                                                                                  | 75<br>75<br>77<br>79<br>79<br>79                                           |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix<br>A.1.<br>A.1.1.                                                 | Summary Future Directions                                                                                                                                                                                                                                                | 75<br>75<br>77<br>79<br>79<br>79<br>81                                     |

| 6.1.<br>6.2.<br><b>Bibliograp</b><br><b>Appendix</b><br>A.1.<br>A.1.1.<br>A.1.2.                         | Summary Future Directions                                                                                                                                                                                                                                                | 75<br>75<br>77<br>79<br>79<br>79<br>81                                     |

| 6.1.<br>6.2.<br><b>Bibliograp</b><br><b>Appendix</b><br>A.1.<br>A.1.1.<br>A.1.2.<br>A.1.3.               | Summary                                                                                                                                                                                                                                                                  | 75<br>75<br>77<br>79<br>79<br>79<br>81<br>82<br>82                         |

| 6.1.<br>6.2.<br><b>Bibliograp</b><br><b>Appendix</b><br>A.1.<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>A.1.4.     | Summary Future Directions  A  Description of Transmitter Testboard Input and Output Signals Power Supply Inputs Clock Inputs Baseband Modulator Chip Signals Miscellaneous Inputs and Outputs Description of Files/Directories ViewDraw Files                            | 75<br>75<br>77<br>79<br>79<br>79<br>81<br>82<br>82<br>82                   |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix<br>A.1.<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>A.1.4.<br>A.2.           | Summary Future Directions  A  Description of Transmitter Testboard Input and Output Signals Power Supply Inputs Clock Inputs Baseband Modulator Chip Signals Miscellaneous Inputs and Outputs Description of Files/Directories ViewDraw Files ViewSim Files              | 75<br>75<br>77<br>79<br>79<br>79<br>81<br>82<br>82<br>82<br>82<br>82       |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix<br>A.1.<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>A.1.4.<br>A.2.<br>A.2.   | Summary Future Directions  hy  Description of Transmitter Testboard Input and Output Signals Power Supply Inputs Clock Inputs Baseband Modulator Chip Signals Miscellaneous Inputs and Outputs Description of Files/Directories ViewDraw Files ViewSim Files Racal Files | 75<br>75<br>77<br>79<br>79<br>79<br>81<br>82<br>82<br>82<br>82<br>82<br>82 |

| 6.1.<br>6.2.<br>Bibliograp<br>Appendix<br>A.1.<br>A.1.1.<br>A.1.2.<br>A.1.3.<br>A.1.4.<br>A.2.<br>A.2.1. | Summary Future Directions  A  Description of Transmitter Testboard Input and Output Signals Power Supply Inputs Clock Inputs Baseband Modulator Chip Signals Miscellaneous Inputs and Outputs Description of Files/Directories ViewDraw Files ViewSim Files              | 75<br>75<br>77<br>79<br>79<br>79<br>81<br>82<br>82<br>82<br>82<br>83<br>83 |

## **List of Figures**

| Figure 2-1.  | System Level Architecture of CDMA Transmitter                                                                                                 | 4  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2.  | QPSK Symbol Constellation                                                                                                                     | 5  |

| Figure 2-3.  | Direct Implementation of 256MHz 37-Tap Raised-Cosine Filter                                                                                   | 10 |

| Figure 2-4.  | Implementation of 256Mhz Raised-Cosine Filter using Four Paralle 64MHz Subfilters                                                             |    |

| Figure 2-5.  | Pipelined Implementation of FIR Filter                                                                                                        | 11 |

| Figure 2-6.  | Truncated Raised-Cosine Pulse                                                                                                                 |    |

| Figure 2-7.  | IF Modulation                                                                                                                                 | 13 |

| Figure 2-8.  | RF Modulation                                                                                                                                 | 14 |

| Figure 2-9.  | Lowpass Filter after Digital-to-Analog Converter                                                                                              | 16 |

| Figure 3-1.  | Frequency Response of Multiplexed Baseband Modulator Output.                                                                                  | 17 |

| Figure 3-2.  | Frequency Response of Desired RF Output Signal                                                                                                | 18 |

| Figure 3-3.  | Filter Method                                                                                                                                 | 19 |

| Figure 3-4.  | Phase-Shift Method                                                                                                                            | 20 |

| Figure 3-5.  | Frequency Response at Various Points for Phase-Shift Method                                                                                   | 21 |

| Figure 3-6.  | RLC Phase-Splitter Circuit                                                                                                                    | 24 |

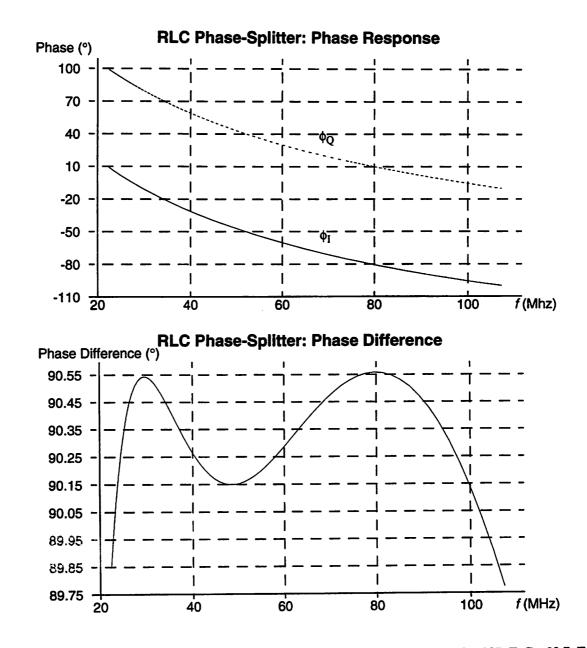

| Figure 3-7.  | RLC Phase-Splitter y Response (f0=48.6MHz, r=2.17, Q=0.242).                                                                                  | 25 |

| Figure 3-8.  | RLC Phase-Splitter y Response (f0=48.6MHz, r=1.9, Q=0.302)                                                                                    | 25 |

| Figure 3-9.  | RLC Phase-Splitter fI and fQ Response (f0=48.6MHz, r=1.9, Q=0.302)                                                                            | 26 |

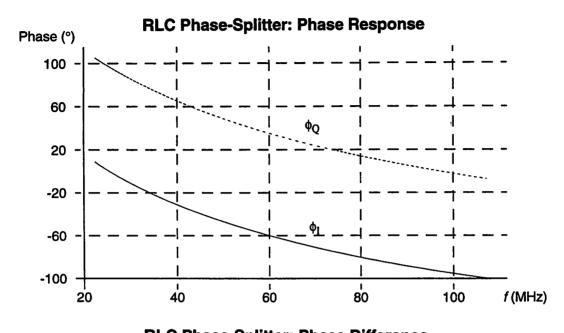

| Figure 3-10. | RLC Phase-Splitter Simulated Response (R1=53.2W, R2=192.1W, C1=387pF, C2=29.7pF, L1=100nH, L2=100nH)                                          | 27 |

| Figure 3-11. | RLC Phase-Splitter Simulated Response with Commercially Available Component Values (R1=53.6W, R2=191W, C1=390pF, C2=27pF, L1=100nH, L2=100nH) | 28 |

| Figure 3-12. | -                                                                                                                                             | 29 |

| Figure 3-13. | SPICE Simulation of Single-Stage Asymmetric Polyphase Filter                                                                                  | 30 |

| Figure 3-14. | N-Stage Asymmetric Polyphase Filter                                                                                                           | 31 |

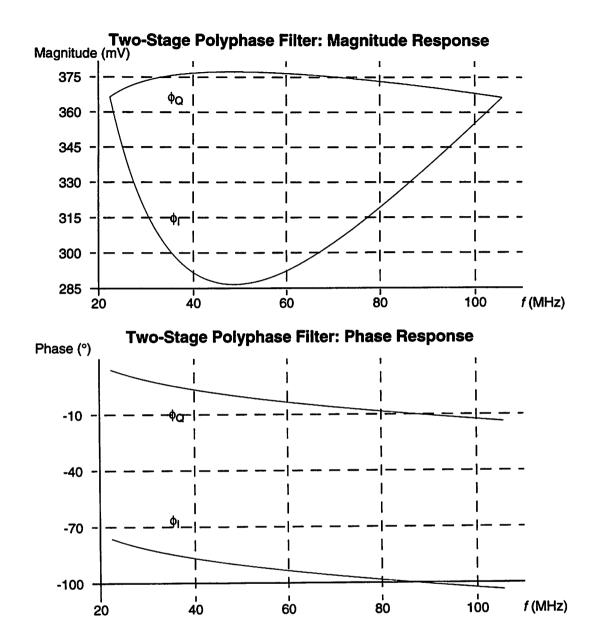

| •            | SPICE Simulation of Two-Stage Asymmetric Polyphase Filter                                                                                     | 32 |

| Figure 3-16. | SPICE Simulation of Two-Stage Asymmetric Polyphase Filter (R1=14.21kW, R2=3.01kW, C1=C2=0.5pF)                                                | 33 |

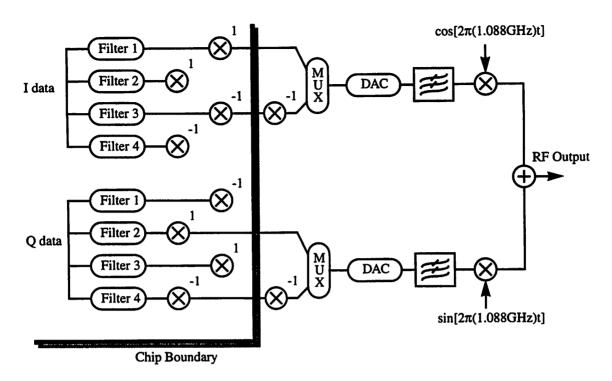

| Figure 3-17. | Architecture of Hilbert Transform Incorporated within Baseband Modulator Chip                                                                 | 35 |

| Figure 3-18. | Weaver Method                                                                                                                                 | 37 |

| Figure 3-19. | Frequency Response at Various Points for Double Upconversion Weaver Method                                                                    | 39 |

| Ti 2 20      | Auchitecture of Down II Wasyer Mathod                         | 40  |

|--------------|---------------------------------------------------------------|-----|

| Figure 3-20. | Architecture of Down-Up Weaver Method                         |     |

| Figure 3-21. | Downsampling Process                                          |     |

| Figure 4-1.  | Final Transmitter Architecture                                |     |

| Figure 4-2.  | ViewDraw Schematic of Transmitter                             |     |

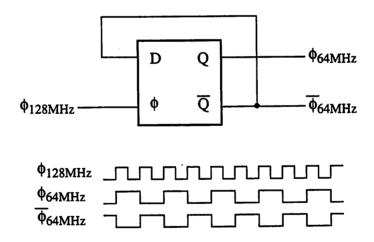

| Figure 4-3.  | Generation of 64MHz Clock                                     |     |

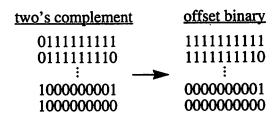

| Figure 4-4.  | Conversion from Two's Complement to Offset Binary             | 49  |

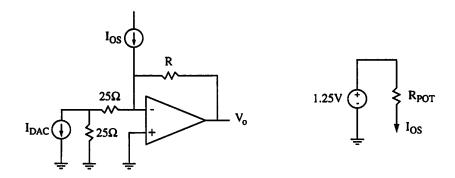

| Figure 4-5.  | Current-to-Voltage Conversion                                 | 49  |

| Figure 4-6.  | Current-to-Voltage Conversion                                 | 53  |

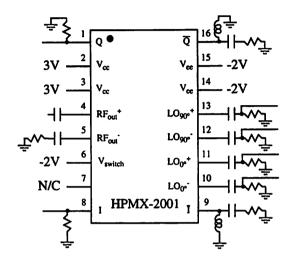

| Figure 4-7.  | Differential Quadrature Clock Generator                       | 55  |

| Figure 4-8.  | Modeling Parasitics in Discrete Components                    | 56  |

| Figure 4-9.  | RLC Bandpass Filter                                           | 56  |

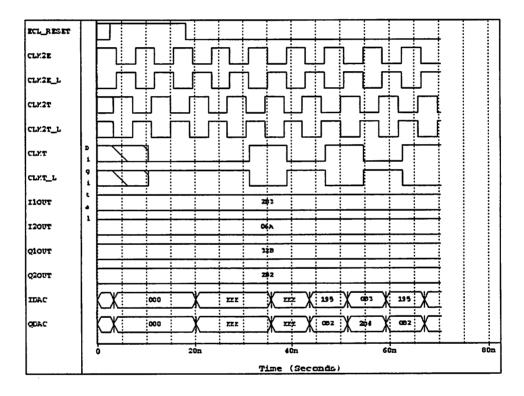

| Figure 4-10. | ViewSim Simulation of Digital Section                         | 57  |

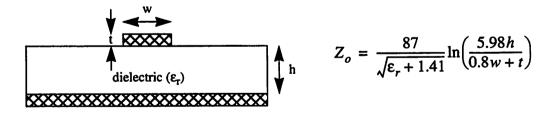

| Figure 4-11. | Characteristic Impedance of a Microstrip Line                 | 58  |

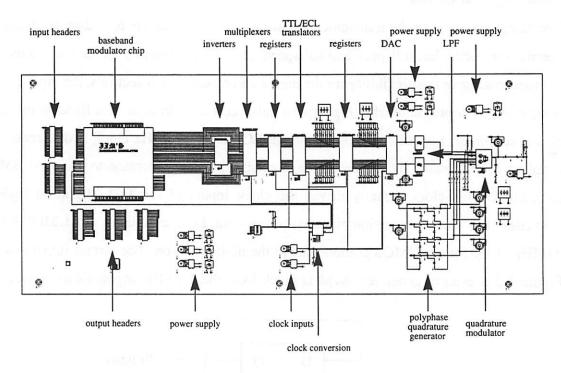

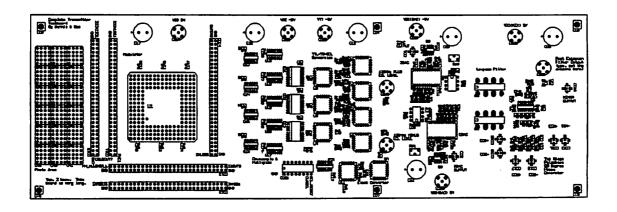

| Figure 4-12. | Transmitter Testboard Layout                                  | 60  |

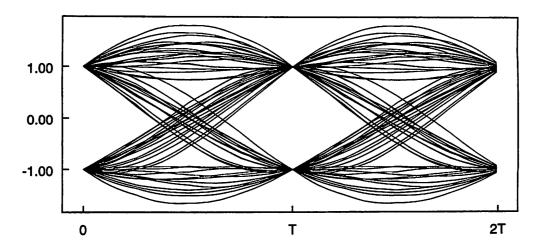

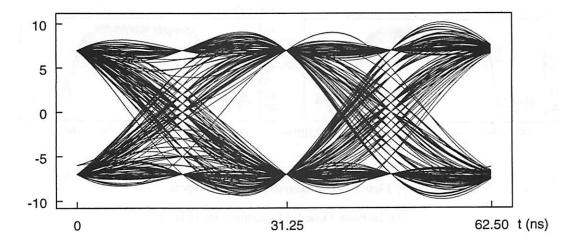

| Figure 5-1.  | Theoretical Eye Diagram for 37-Tap 30% Excess Bandwidth Raise | ed- |

|              | Cosine Filter                                                 | 62  |

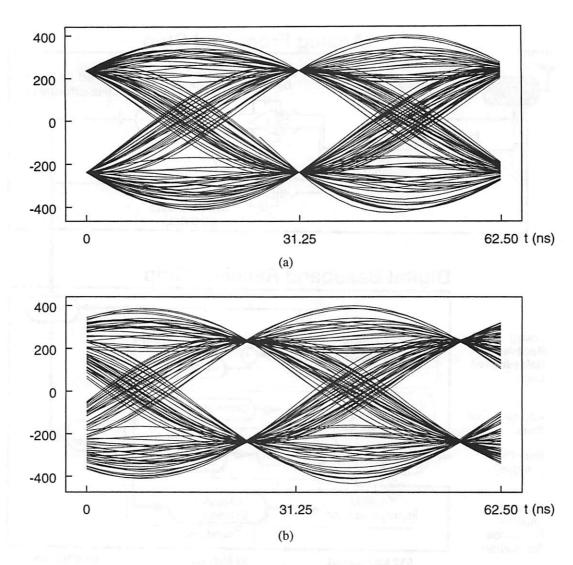

| Figure 5-2.  | Measured Eye Diagrams at the Transmitter                      | 63  |

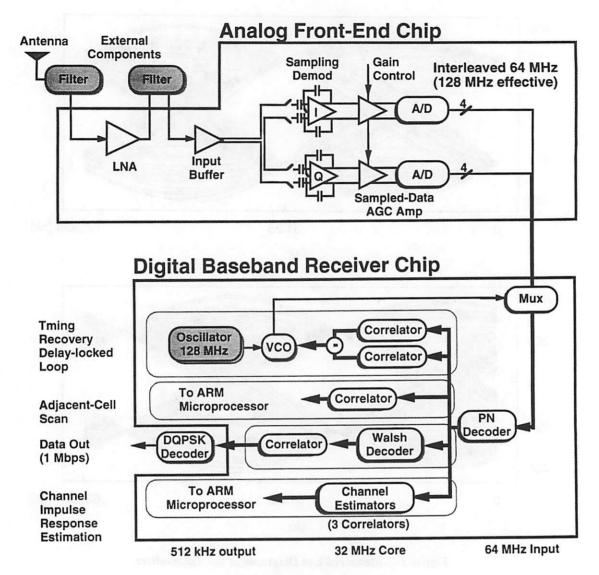

| Figure 5-3.  | Receiver Architecture                                         | 64  |

| Figure 5-4.  | Measured Eye Diagram at the Receiver                          | 65  |

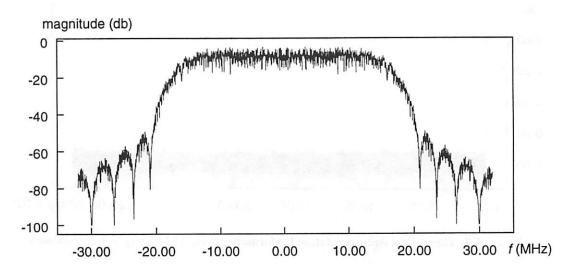

| Figure 5-5.  | Theoretical Frequency Response for 37-Tap 30% Excess Bandwid  |     |

|              | Raised-Cosine Filter without Quantization                     |     |

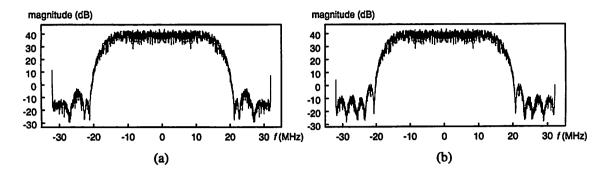

| Figure 5-6.  | Measured Spectral Outputs                                     | 66  |

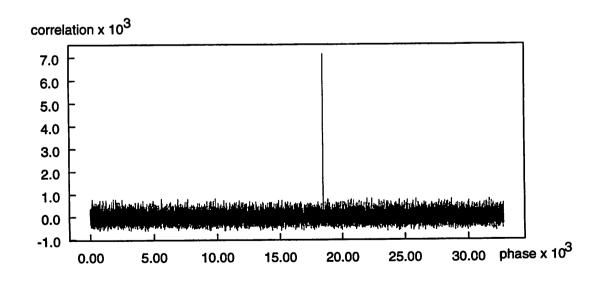

| Figure 5-7.  | Theoretical Autocorrelation Performance using 1024-Long       |     |

|              | Subcorrelations                                               | 66  |

| Figure 5-8.  | Truncated Raised-Cosine Pulse                                 | 67  |

| Figure 5-9.  | Theoretical Autocorrelation Performance using 1024-Long       |     |

|              | Subcorrelations                                               |     |

| Figure 5-10. | Measured Autocorrelation Performance at the Baseband Modulato |     |

|              | Output using 1024-Long Subcorrelations                        | 68  |

| Figure 5-11. | Measured Autocorrelation Performance at the Analog Receiver   |     |

|              | Output using 1024-Long Subcorrelations                        | 68  |

### **List of Tables**

| Table 2-1.  | DQPSK Encoding of Input Data                            | . 6 |

|-------------|---------------------------------------------------------|-----|

| Table 2-2.  | Example of Transmitted Symbols                          | . 6 |

| Table 2-3.  | Digital Representation of fm                            | . 6 |

| Table 3-1.  | Combline Filter Characteristics                         | 19  |

| Table 3-2.  | Quantized Filter Coefficients                           | 36  |

| Table 3-3.  | Comparison of Various Upconversion Methods              | 42  |

| Table 4-1.  | Expected Simulation Results                             | 57  |

| Table 4-2.  | Final Layer Specification                               | 59  |

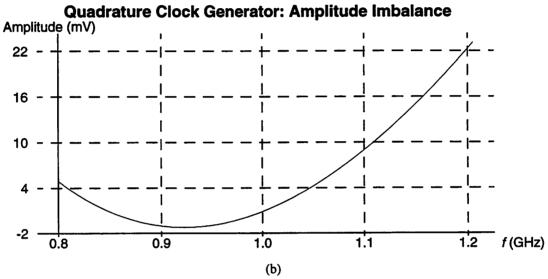

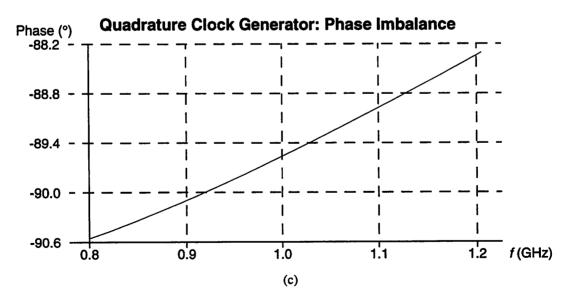

| Table 5-1.  | Performance Summary of Quadrature LO Generator          | 69  |

| Table 5-2.  | Power Consumption Breakdown by Supply Voltages          |     |

| Table 5-3.  | Power Consumption Breakdown by Components               | 71  |

| Table A-1.  | Power Supply Definitions                                | 79  |

| Table A-2.  | Input and Output Clock Definitions                      | 79  |

| Table A-3.  | Clock Control Signals (Connector CO31)                  | 80  |

| Table A-4.  | Baseband Modulator Chip Inputs and Outputs              |     |

| Table A-5.  | Miscellaneous Input and Output Signal Definitions       | 82  |

| Table A-6.  | Description of ViewDraw Files                           |     |

| Table A-7.  | Description of ViewSim Files                            | 82  |

| Table A-8.  | Description of Racal Files                              | 83  |

| Table A-9.  | Description of Quadrature LO Generator Simulation Files | 83  |

| Table A-10. | Description of Miscellaneous Files                      |     |

## Introduction

Society's increasing demands for ubiquitous access to information have stimulated extensive research in the area of high-speed wireless digital communications systems. The InfoPad research project [Sheng92] proposes a solution which allows access to real-time multimedia data on a high-speed network using portable, low-power terminals. A basestation provides the communications interface between the backbone network and the multimedia terminals. In order to provide high-quality, full-motion video to each of the several multimedia terminals, the downlink must provide data rates of up to 2Mbps for each user in the system.

[Sheng96] describes the system-level architecture of a CDMA direct sequence spreadspectrum transceiver which is capable of supporting up to 50 users each with a 2Mbps maximum data rate. The receiver must be low-power and compact since it resides in the portable, battery-operated terminal. In order to achieve these objectives, monolithic integration of the receiver is imperative. These constraints, however, do not apply to the transmitter since it resides in the basestation, and thus, a semi-custom solution is adequate.

This report describes in detail the design and implementation of the CDMA direct sequence spread-spectrum transmitter. The report is organized into six chapters and one appendix. This chapter motivates the work presented in this report and provides an overview of the content. Chapter 2 provides a brief overview of the system-level architecture of the CDMA direct sequence spread-spectrum transmitter. This chapter reviews the architecture of the baseband modulator [Peroulas95] and discusses issues associated with digital-to-analog conversion. Chapter 3 focuses on different methods of single-sideband upconversion and concludes with a discussion of the trade-offs between the various architectures. Chapter 4 presents the final transmitter design and provides a

detailed description of the implementation procedure, including schematic entry, design simulation, and printed circuit board layout. A detailed listing of all relevant design files and directories is tabulated in Appendix A. Chapter 5 concentrates on testing and measurements. Measured results are compared with simulated results in order to evaluate the performance of the transmitter testboard. Power and speed measurements are also presented in this chapter. The chapter concludes with a discussion of the errors discovered in the baseband modulator chip as well as the transmitter testboard. A complete description of all inputs and outputs on the transmitter testboard is tabulated in Appendix A. Finally, concluding comments as well as a discussion of future directions are presented in Chapter 6.

## **2** Transmitter Architecture

The CDMA transmitter must support an aggregate data rate of 100Mbits/s over a wireless link. Consequently, the design of such a system is a nontrivial task. This chapter provides a brief overview of the transmitter architecture and discusses some of the implementation details of the baseband modulator. [Sheng96] provides more detailed discussions of the overall system architecture, whereas [Peroulas95] describes in detail the baseband modulator chip which performs the baseband digital processing and pulse-shaping.

#### 2.1. Transmitter System-Level Overview

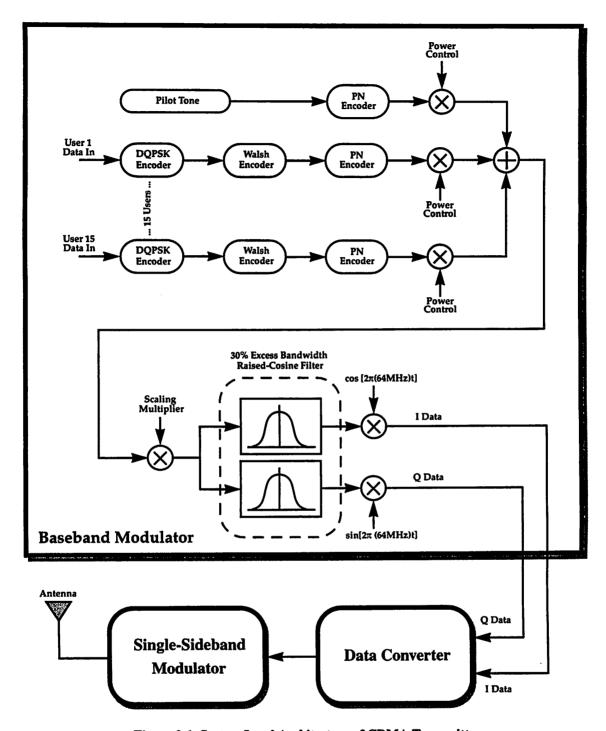

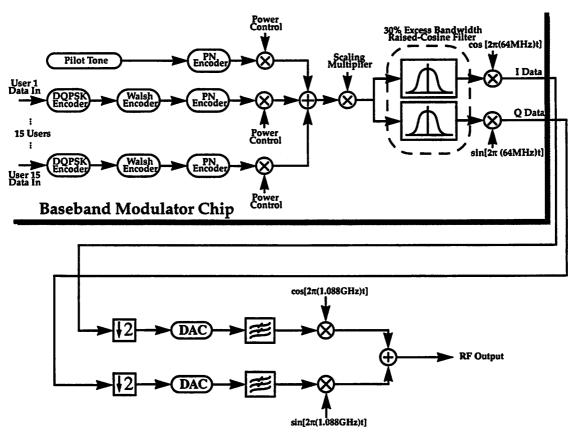

The transmitter architecture is depicted in Figure 2-1. The first major block is the baseband modulator chip which processes the digital data from 15 different users. Multiple chips may be used in parallel to meet the 50 user specification. The data converter block converts the digital output of the baseband modulator to an analog signal and the single-sideband modulator block mixes the IF signal to an RF of 1.088GHz. The design and implementation of the single-sideband upconverter is discussed in detail in the next chapter.

#### 2.1.1. Baseband Modulator

The following functions are performed in the baseband modulator:

- differential quadrature-phase shift keying (DQPSK) encoding

- Walsh encoding

- pseudo-random number (PN) scrambling

- power control

- · raised-cosine filtering

- IF modulation.

Figure 2-1. System Level Architecture of CDMA Transmitter

#### 2.1.1.1. DQPSK Encoding

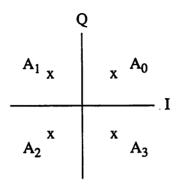

In phase shift keying (PSK) modulation techniques, the information is encoded into the phase of the carrier while the amplitude remains fixed. In QPSK, the signal constellation

consists of four symbols as depicted in Figure 2-2. The phase values of symbols A<sub>0</sub>, A<sub>1</sub>,

Figure 2-2. QPSK Symbol Constellation

$A_2$ , and  $A_3$  are  $\pi/4$ ,  $3\pi/4$ ,  $5\pi/4$ , and  $7\pi/4$ , respectively, while the magnitudes of all symbols are equal. The use of absolute position in PSK encoding schemes may result in incorrect decoding at the receiver due to constellation rotation, e.g., a rotation of  $\pi/2$  in a QPSK signal constellation. Constellation rotation may be caused by rapid phase fluctuations in the channel due to multipath fading as well as frequency offsets between oscillators in the transmitter and the receiver in the absence of carrier recovery.

This problem may be avoided by using a differential encoding scheme for the phase information. In DPSK the symbols may be represented by the equation

$$A_m = ke^{j\phi_m}$$

where k is a constant and  $\phi_m$  is determined by

$$\phi_m = \phi_{m-1} + \Delta_m$$

In this system, DQPSK data modulation is used and  $\Delta_m$  is determined from the input bits based on Table 2-1. The input data of each user is presented to the baseband modulator

**Table 2-1. DQPSK Encoding of Input Data**

| MSB | LSB | $\Delta_{m}$ |

|-----|-----|--------------|

| 0   | 0   | 0            |

| 0   | 1   | π/2          |

| 1   | 0   | 3π/2         |

| 1   | 1   | π            |

chip two bits at a time each at a 1MHz rate. Table 2-2 summarizes the transmitted symbols if the following bit pairs, (MSB,LSB), are input to the baseband modulator chip: (0,0), (1,1), (1,0), (1,0), (0,0), (0,1), (1,0). It is assumed that  $\phi_m=0$  for m<0.

**Table 2-2. Example of Transmitted Symbols**

| m | (MSB,LSB) | $\Delta_{m}$ | φ <sub>m</sub> |

|---|-----------|--------------|----------------|

| 0 | (0,0)     | 0            | 0              |

| 1 | (1,1)     | π            | π              |

| 2 | (1,0)     | $3\pi/2$     | π/2            |

| 3 | (1,0)     | 3π/2         | 0              |

| 4 | (1,1)     | π            | π              |

| 5 | (0,1)     | π/2          | 3π/2           |

| 6 | (1,0)     | 3π/2         | π              |

Finally, the values of  $\phi_m$  need to be encoded digitally. Two bits are required to represent the four values of  $\phi_m$ . Table 2-3 summarizes the digital representation of  $\phi_m$ . A and B are

Table 2-3. Digital Representation of  $\phi_m$

| φ <sub>m</sub> | (A,B) |

|----------------|-------|

| 0              | (0,0) |

| π/2            | (1,0) |

| π              | (1,1) |

| 3π/2           | (0,1) |

called the in-phase and quadrature-phase components, respectively.

#### 2.1.1.2. Walsh Encoding and PN Scrambling

Code-division multiple access (CDMA) is one of several multiple access schemes which may be used to accommodate 50 users. CDMA systems allow multiple users to

simultaneously share the same frequency channel. In a CDMA system each user's data is encoded with a unique user sequence. These user sequences should be mutually orthogonal as well as spectrally white. Typical CDMA systems employ pseudorandom sequences, which operate at a rate much higher than the symbol rate, for data encoding. Thus, modulation by these pseudorandom sequences results in a transmission bandwidth which is much greater than the bandwidth dictated by the symbol rate. The spread-spectrum nature of CDMA results in increased immunity to frequency-selective multipath fading as well as jamming.

Although pseudorandom sequences with good autocorrelation properties may be easily generated, such sequences usually exhibit poor cross-correlation which is necessary in order to distinguish between different users in a CDMA system. One strategy is to first encode each user's data with a user-specific code which is guaranteed to be orthogonal but not necessarily spectrally white. A common pseudorandom sequence is then applied for spectral whitening. One set of orthogonal codes is called the Walsh codes. These codes have a cross-correlation equal to zero and an autocorrelation equal to the length of the Walsh codes. The Walsh sequences in this system are length 64 and clocked at a 64MHz rate. Each user is assigned a unique Walsh sequence which is used to encode both in-phase and quadrature-phase data, both of which are clocked at 1MHz. Walsh code zero, which is simply a DC signal, is reserved for the pilot tone. The pilot tone is used for various functions such as clock recovery and channel estimation.

Finally, although the 1MHz data signal is spectrally spread to a bandwidth of 64MHz, the resulting signal is not pseudorandom. Many advantages of spread-spectrum communications are direct consequences of the pseudorandom nature of the transmitted signal. Thus, Walsh coding must be followed by PN scrambling. The same 64MHz pseudorandom sequence of length 32768 is used to encode the in-phase and quadrature-phase data of all users. Since the same pseudorandom sequence is used for all users, it may seem more efficient to implement the PN scrambling after the data of all users are combined. Since the combiner employs a two's complement number representation, such an implementation of the PN scrambling after the combiner would also require the use of a two's complement number representation. Multiplication with the pseudorandom

sequence, which consists of the values +1 and -1, may be performed much more efficiently by using a sign and magnitude number representation since multiplication by -1 simply requires toggling the sign bit. In contrast, multiplication by -1 in a two's complement number representation requires forming the bitwise complement and then adding one. The increased switching activity associated with negation of a two's complement number results in greater power consumption [Chandrakasan94]. Thus, PN scrambling is performed on the in-phase and quadrature-phase data of all users before the combiner.

#### 2.1.1.3. Power Control

If the basestation transmits the data of all users at the same power level, then receivers which are near the basestation receive a much stronger signal than those which are further away. Power control allows all users to receive the same signal strength by controlling the power level of each user at the basestation. For example, data associated with receivers which are closer to the basestation are transmitted with a lower power level than those associated with receivers which are further away.

Six bits of power control are available for each user as well as for the pilot tone. Both inphase and quadrature-phase data from the PN scrambler are multiplied by the power control value. The data from all 15 users and the pilot tone are then combined into two 10bit data streams: one for in-phase data and one for quadrature-phase data. The combiner is followed by a multiplier which is used to scale the output signal. The 4-bit scaling factor guarantees full-scale inputs to the raised-cosine filters.

#### 2.1.1.4. Raised-Cosine Filtering

A raised-cosine filter is used to avoid intersymbol interference. The raised-cosine pulse is given by

$$x(t) = \frac{\sin\left(\frac{\pi t}{T}\right)}{\frac{\pi t}{T}} \times \frac{\cos\left(\frac{\alpha \pi t}{T}\right)}{1 - \left(\frac{2\alpha t}{T}\right)^2}$$

where  $\alpha$  is called the rolloff parameter and T is the symbol period. For  $\alpha=0$ , x(t) degenerates to a sinc pulse which has a bandwidth of f=1/T. As  $\alpha$  varies from 0 to 1, the excess bandwidth varies from 0% to 100%. Although the tails of the pulses are infinite in extent for all values of  $\alpha$ , as  $\alpha$  increases, the magnitude of the tails becomes increasingly small. Thus, raised-cosine filters may be approximated as FIR filters by truncation of the sequence.

Two identical raised-cosine filters with 30% excess bandwidth are used in this transceiver system: one for the in-phase data and one for the quadrature-phase data. The number of filter taps, tap coefficient quantization as well as internal roundoff noise are optimized to meet a 40dB out-of-band rejection specification. The resulting filters each have 37 taps, all of which are quantized to three bits. Implementation details for these filters may be found in [Peroulas95].

In order to implement the raised-cosine filter with 30% excess bandwidth, an oversampling ratio of at least two is required. A large oversampling ratio is desirable since the rolloff requirement of the subsequent lowpass filter is less stringent. In addition, a large oversampling ratio minimizes the droop distortion introduced by the subsequent digital-to-analog converter, and thus eliminates the need for a droop compensation filter. However, a large oversampling ratio also results in clock rates which may be excessively high to be practically implemented using current process technology. An oversampling ratio of four is used in this transceiver system, resulting in an effective filter output data rate of 256MHz.

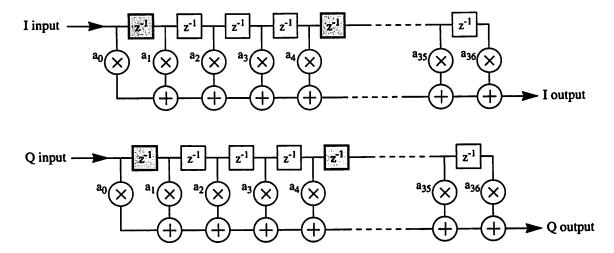

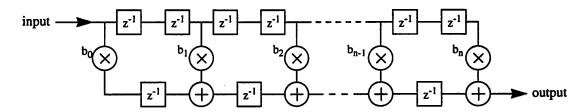

A direct implementation of the 256MHz FIR filters results in the filter structures depicted in Figure 2-3, where a<sub>0</sub>-a<sub>36</sub> are the 37 tap coefficients. The calculation along the critical path of one multiplier and 36 adders must be accomplished under 4ns, which is impossible using current process technology. A practical realization must take advantage of parallelism as well as pipelining [Samueli90]. Parallelization of the filter structure is a direct consequence of oversampling the input data. Upsampling by four is achieved by inserting three zeros between every input sample. Thus, if the inputs to the shaded delay elements in Figure 2-3 have non-zero values, then the inputs to the non-shaded delay

Figure 2-3. Direct Implementation of 256MHz 37-Tap Raised-Cosine Filter

elements are identically equal to zero. Multiplication by zero is trivial and does not need to be computed. The implication is that the 256MHz FIR filter may be divided into four parallel 64MHz subfilters as depicted in Figure 2-4. Since the in-phase and quadrature-

Figure 2-4. Implementation of 256Mhz Raised-Cosine Filter using Four Parallel 64MHz Subfilters

phase filters are identical, only one set of four subfilters is depicted. The output of the four subfilters may be interleaved using a multiplexer to generate the desired 256MHz output stream. The output of each subfilter consists of ten bits, which is determined by the capability of current digital-to-analog converters. Current high performance ECL

compatible digital-to-analog converters which operate in excess of 200MHz are limited to a maximum of ten input bits.

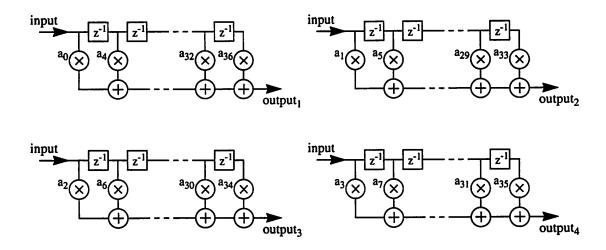

The critical path delay for the four subfilters is still greater than 4ns. For the first subfilter, the critical path consists of one multiplier and nine adders, and for the other three subfilters, the critical path consists of one multiplier and eight adders. A practical realization of the four subfilters must take advantage of pipelining. An example of a pipelined implementation of an FIR filter is illustrated in Figure 2-5. The critical path is now reduced

Figure 2-5. Pipelined Implementation of FIR Filter

to one multiplier and one adder at the expense of increased latency. Also since the tap coefficients are fixed, a general purpose multiplier is not required. Instead each multiplier may be replaced by a series of fixed shifts.

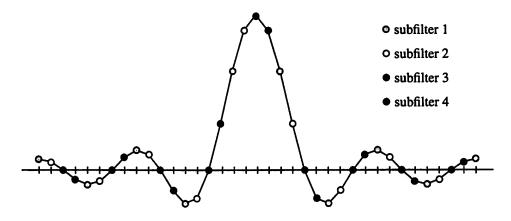

Additional hardware simplifications may be achieved by observing the truncated raised-cosine time-domain response. The assignment of the tap coefficients to the four subfilters is indicated in Figure 2-6. The third subfilter may be simplified to a simple delay since all

Figure 2-6. Truncated Raised-Cosine Pulse

but one coefficient are equal to zero. Also, the tap coefficients of the first filter are symmetric. As a result this ten-tap filter may be implemented using only five physical taps.

#### 2.1.1.5. IF Modulation

Digital modulation of the baseband signal to an intermediate frequency before analog modulation to RF for transmission has two major advantages. First, since the digital data no longer has spectral energy at DC, AC coupling may be used in all subsequent stages in order to minimize data corruption from DC offsets as well as low frequency noise. Second, LO feedthrough in the analog mixers does not appear in the RF signal spectrum due to the IF offset.

Digital modulation may be performed by a direct digital frequency synthesizer (DDFS) [Nicholas91]. The main disadvantage of such an approach is the need for high-speed digital multipliers and adders. However, significant hardware reductions may be achieved by selecting an IF center frequency equal to 1/4 the sampling frequency. In fact, in addition to eliminating the need for a DDFS, the hardware complexity of the raised-cosine filter is also reduced by a factor of two. Instead of requiring eight subfilters for the in-phase and quadrature-phase data, only four subfilters are required.

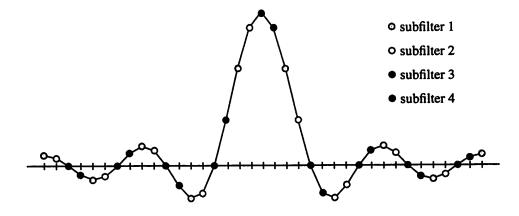

Figure 2-7a illustrates the IF modulation process. The in-phase and quadrature-phase data are multiplied by  $\cos[2\pi n/4]$  and  $\sin[2\pi n/4]$ , respectively. The digital mixers may be moved in front of the multiplexers as illustrated in Figure 2-7b. Since all even samples of  $\cos[2\pi n/4]$  and all odd samples of  $\sin[2\pi n/4]$  are equal to zero, the second and third subfilters for the in-phase data and the first and third subfilters for the quadrature phase data may be eliminated. In addition, multiplication by  $\pm 1$  may be incorporated into the tap coefficients of the remaining subfilters without the need for additional hardware. Finally, since all even samples of the in-phase data output and all odd samples of the quadrature-phase data output are equal to zero, the two data streams may be combined using one multiplexer instead of four adders as illustrated in Figure 2-7c. In addition, since the in-phase and quadrature-phase data streams are combined to form one data stream, only one digital-to-analog converter is required.

Figure 2-7. IF Modulation

(a) Modulation by  $f_s/4$ ; (b) Combining Modulation Process with Raised-Cosine Subfilters; (c) Final Architecture

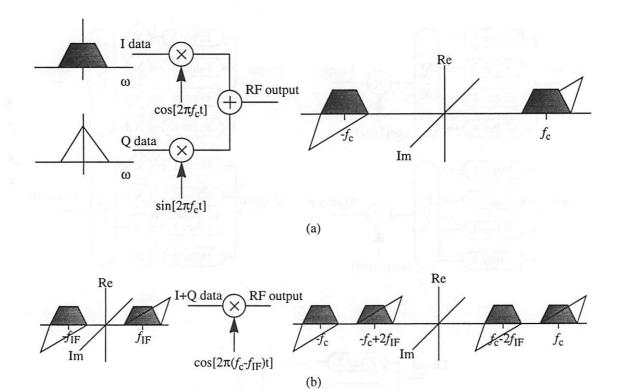

Although IF modulation significantly simplifies the hardware for the raised-cosine filter, it also complicates the architecture required to modulate the signal to RF for transmission. As illustrated in Figure 2-8a, a complex baseband signal may be upconverted to RF simply by multiplying the in-phase and quadrature-phase components by  $\cos[2\pi f_{\rm c}t]$  and  $\sin[2\pi f_{\rm c}t]$ , respectively, where  $f_{\rm c}$  is the carrier frequency. However, multiplication of the IF modulated signal by  $\cos[2\pi (f_{\rm c}-f_{\rm IF})t]$  results in an undesired sideband at  $f_{\rm c}-2f_{\rm IF}$ , where  $f_{\rm IF}$  is the IF center frequency 64MHz. Correct modulation of the IF signal requires single-sideband upconversion techniques which will be discussed in the next chapter.

Figure 2-8. RF Modulation

(a) Direct Quadrature Upconversion of Baseband Signal; (b) Incorrect Modulation of IF Signal

#### 2.1.2. Data Converter

The data converter block is responsible for converting the digital output of the baseband modulator chip to an analog signal for input to the single-sideband upconversion block. The following functions are performed in the data converter block:

- data combining

- digital-to-analog conversion

- droop compensation

- lowpass filter.

The specific implementation of these functions depends on the strategy used for single-sideband upconversion.

#### 2.1.2.1. Data Combining

Except for the output of -Filter 3, each output of the other three subfilters consists of ten bits. The output of -Filter 3 consists of nine bits. As already mentioned, this subfilter may be simplified to a simple delay. The maximum absolute value of the output for this subfilter is less than twice that of the other three subfilters. Since a two's complement number representation is used, only nine bits are required and the tenth bit is determined by sign extension. As indicated in Figure 2-7c, the outputs of the four subfilters must be combined using a multiplexer. This multiplexer is not implemented within the baseband modulator chip in order to increase flexibility in the data combining strategy.

#### 2.1.2.2. Digital-to-Analog Conversion and Droop Compensation

High performance ECL digital-to-analog converters are required in order to meet the 10-bit, 256MHz specification. All digital-to-analog converters introduce droop distortion resulting from zero-order hold reconstruction. The magnitude frequency response of a zero-order hold filter is given by

$$|H(j\omega)| = \frac{\sin\left(\frac{\omega T}{2}\right)}{\frac{\omega}{2}}$$

At  $\omega=\pi/T$ , the amplitude attenuation is 3.92dB. The severity of the amplitude distortion depends on the bandwidth of the desired signal and the sampling period of the analog-to-digital converter. A large oversampling ratio results in less distortion in the frequency band of interest, and as a result, a droop compensation filter may not be necessary.

When the performance degradation due to droop is too severe, a droop compensation filter is required before or after the digital-to-analog converter. The frequency response of the compensation filter is simply the inverse of the zero-order hold filter response. Traditional implementations incorporate the droop compensation filter with the analog lowpass filter which follows the digital-to-analog converter. The main disadvantage of an analog approach is that the compensation filter is fixed-tuned to a specific sampling frequency. The droop compensation filter may also be implemented as a digital FIR filter before the

digital-to-analog converter. This approach allows for droop compensation at any sampling frequency by simply adjusting the clock rate of the digital filter. However, this filter must operate at the sampling frequency of the digital-to-analog converter. Such high-speed filters, although they consume a significant amount of power, are realizable using current submicron CMOS processes [Lin90].

#### 2.1.2.3. Lowpass Filter

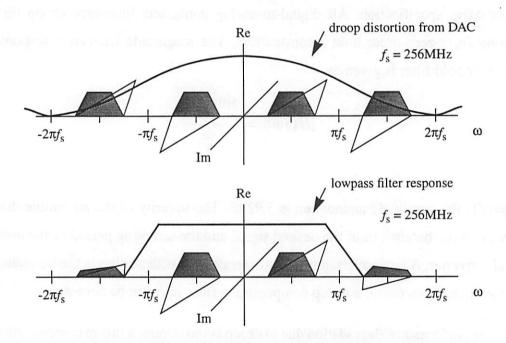

Finally, the spectral output from the digital-to-analog converter contains copies of the baseband spectrum at multiples of the sampling frequency. Although these copies are attenuated by the droop response of the digital-to-analog converter, an additional lowpass filter is necessary to further reject out-of-band components. Figure 2-9 illustrates the frequency spectrum after the digital-to-analog converter. The lowpass filter must have a

Figure 2-9. Lowpass Filter after Digital-to-Analog Converter

single-sided passband of 105.6MHz and at least 40dB of attenuation after 150.4MHz. Lowpass filters with these specifications are commercially available [Mini-Circuits92].

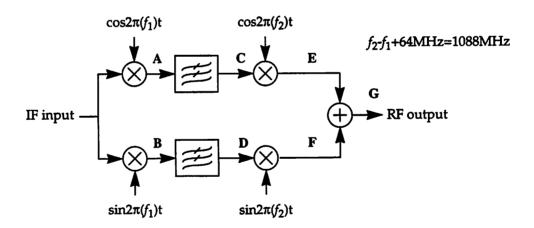

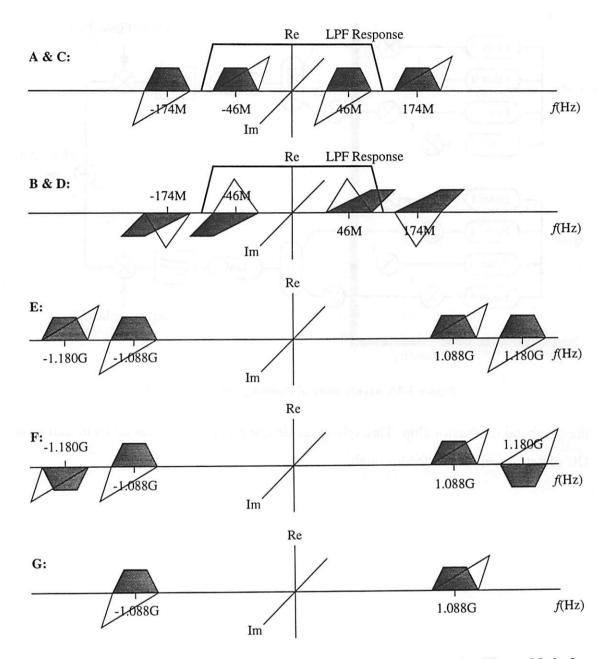

# 3 Single-Sideband Upconversion

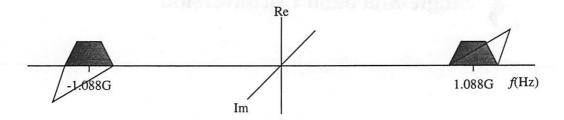

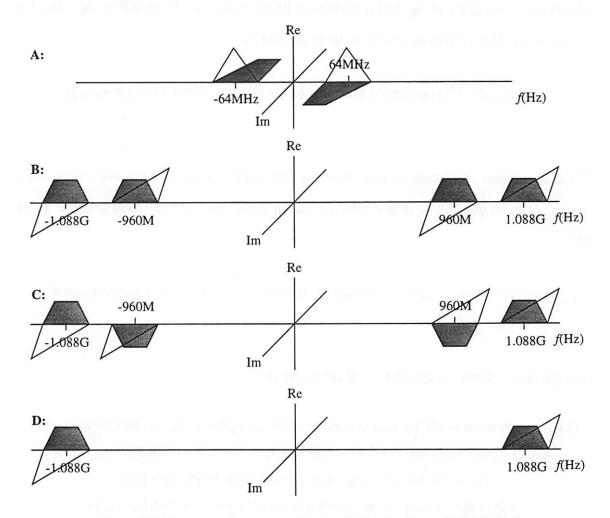

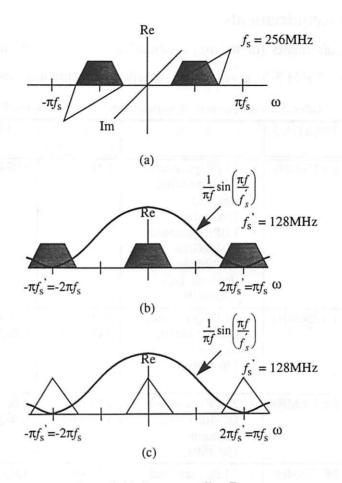

The output of the baseband modulator chip consists of four 64MHz data streams: two for in-phase data and two for quadrature-phase data. A multiplexer combines the four data streams into one 256MHz data stream. The frequency response of the 256MHz data stream is illustrated in Figure 3-1. The in-phase and quadrature-phase data are modulated to a

Figure 3-1. Frequency Response of Multiplexed Baseband Modulator Output

digital IF of 64MHz and may be represented by the following equation:

$$Y_{IF}(t) = I(t)\cos 2\pi (64MHz)t + Q(t)\sin 2\pi (64MHz)t$$

The spectrum of the desired signal for transmission at the RF of 1.088GHz appears in Figure 3-2. Direct upconversion by 1.024GHz of the IF signal results in an incorrect

Figure 3-2. Frequency Response of Desired RF Output Signal

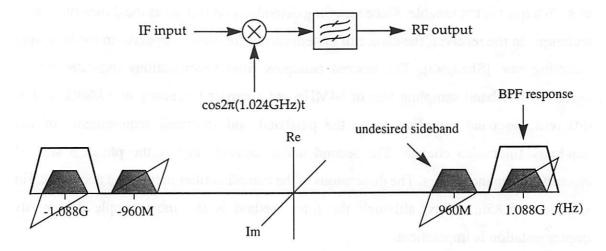

spectrum at RF due to the presence of lower sidebands located at 960MHz and -960MHz:

At least 40dB of sideband rejection is desirable in order to meet typical FCC out-of-band transmission rejection requirements. In order to achieve this sideband rejection, single-sideband upconversion is necessary. Three methods of single-sideband upconversion are listed below:

- · filter method

- · phase-shift method

- · Weaver method.

The advantages and disadvantages of each method are discussed.

#### 3.1. Single-Sideband Upconversion

#### 3.1.1. Filter Method

The filter method is the most simple of the three methods. The block diagram of a possible implementation is illustrated in Figure 3-3. This method requires only one mixer and one

Figure 3-3. Filter Method

bandpass filter. The required bandpass filter has a passband of 83.2MHz centered at 1.088GHz. In addition, 40dB of attenuation is required within a 44.8MHz transition band, which is about 4% of the passband center frequency.

Several different types of bandpass filters exist. Tunable LC filters are attractive since they have center frequencies which may be adjusted for use with different carrier frequencies. However, the stopband attenuation of LC filters with center frequencies in excess of 1GHz falls well short of the desired 40dB rejection requirement. Mechanical resonance filters, such as ceramic resonators and SAW filters, offer high stopband rejection but are restricted to center frequencies under 1GHz. Finally, electrical resonance filters offer the high selectivity of mechanical resonance filters but also operate at center frequencies in excess of 1GHz. The characteristics of a custom eight-pole combline filter which meets the desired bandpass specifications for this application are tabulated in Table 3-1. The use of

Table 3-1. Combline Filter Characteristics

| center frequency                   | 1.088GHz            |

|------------------------------------|---------------------|

| passband (-0.1dB ripple bandwidth) | 1.046GHz - 1.130GHz |

**Table 3-1. Combline Filter Characteristics**

| attenuation at 1.0016GHz | 44dB                   |

|--------------------------|------------------------|

| attenuation at 1.1744GHz | 53dB                   |

| insertion loss           | 0.6dB                  |

| dimensions               | 2.1in x 1.5in x 8.85in |

electrical resonance filters is impractical for two major reasons. First, the center frequency of such a filter is not tunable. Since sampling demodulation is used as the downconversion technique in the receiver, the choice of system carrier frequency depends on the baseband sampling rate [Sheng96]. The desired bandpass filter specifications indicated above assume a baseband sampling rate of 64MHz and a carrier frequency of 1.088GHz. For different baseband sampling rates, the passband and stopband requirements of the bandpass filter also change. The second major disadvantage is the physical size of electrical resonance filters. The dimensions of the combline filter mentioned above is 2.1in x 1.5in x 8.85in. Thus, although the filter method is the most simple design, its implementation is impractical.

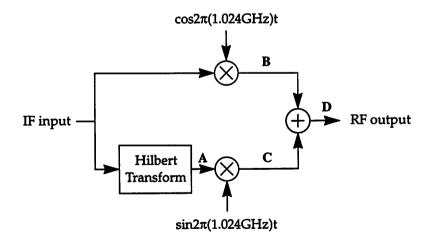

#### 3.1.2. Phase-Shift Method

The phase-shift method is another way to achieve single-sideband upconversion. A block diagram of this method is illustrated in Figure 3-4. This method requires two mixers, an

Figure 3-4. Phase-Shift Method

RF power combiner, and a Hilbert transformer. The Hilbert transformer is a wideband 90° power splitter defined as follows:

$$H(\omega) = \begin{cases} j, & \omega > 0 \\ -j, & \omega < 0 \end{cases}$$

The frequency response at points A, B, C, and D are illustrated in Figure 3-5. This method

Figure 3-5. Frequency Response at Various Points for Phase-Shift Method

of single-sideband upconversion relies on the cancellation of the lower sideband. However, perfect cancellation is impossible in practical implementations due to amplitude and phase

mismatches in the two mixers as well as in the Hilbert transformer. The input signal may be expressed as

$$I(t)\cos[2\pi(64MHz)t] + Q(t)\sin[2\pi(64MHz)t]$$

If a practical implementation of the Hilbert transformer results in a maximum amplitude difference from unity of  $\delta_H$  and a maximum phase difference from 90° of  $\phi_H$ , then the output of the Hilbert transformer may be expressed as

$$(1 + \delta_H)\{-I(t)\sin[2\pi(64MHz)t + \phi_H] + Q(t)\cos[2\pi(64MHz)t + \phi_H]\}$$

If the maximum amplitude mismatch in the two mixers is  $\delta_M$  and the maximum phase mismatch from quadrature is  $\phi_M$ , then the output signal from the in-phase mixer is given by

$$\frac{1}{2}\{I(t)\cos[2\pi(1088MHz)t] + Q(t)\sin[2\pi(1088MHz)t] + I(t)\cos[2\pi(960MHz)t] + Q(t)\sin[2\pi(960MHz)t]\}$$

and the output from the quadrature-phase mixer is

```

\begin{split} (1+\delta_{H})\{-I(t)\sin[2\pi(64MHz)t+\phi_{H}]+Q(t)\cos[2\pi(64MHz)t+\phi_{H}]\}\times (1+\delta_{M})\sin[2\pi(1024MHz)t+\phi_{M}]\\ &=\frac{1}{2}(1+\delta_{H})(1+\delta_{M})\{I(t)\cos[2\pi(1088MHz)t+\phi_{H}+\phi_{M}]+Q(t)\sin[2\pi(1088MHz)t+\phi_{H}+\phi_{M}]-\\ &I(t)\cos[2\pi(960MHz)t+\phi_{H}-\phi_{M}]-Q(t)\sin[2\pi(960MHz)t+\phi_{H}-\phi_{M}]\}\\ &=\frac{1}{2}(1+\delta_{H})(1+\delta_{M})\{\cos[2\pi(1088MHz)t][I(t)\cos(\phi_{H}+\phi_{M})+Q(t)\sin(\phi_{H}+\phi_{M})]+\\ &\sin[2\pi(1088MHz)t][Q(t)\cos(\phi_{H}+\phi_{M})-I(t)\sin(\phi_{H}+\phi_{M})]-\\ &\cos[2\pi(960MHz)t][I(t)\cos(\phi_{H}-\phi_{M})+Q(t)\sin(\phi_{H}-\phi_{M})]-\\ &\sin[2\pi(960MHz)t][Q(t)\cos(\phi_{H}-\phi_{M})-I(t)\sin(\phi_{H}-\phi_{M})]\} \end{split}

```

Thus, after the outputs of the in-phase and quadrature-phase mixers are combined, residual energy in the sidelobe centered at 960MHz remains. In addition, interference from the quadrature-phase component appears in the in-phase sidelobe centered at 1.088GHz and interference from the in-phase component appears in the quadrature-phase sidelobe centered at 1.088GHz. A typical value of amplitude imbalance for a monolithic QPSK modulator is  $\pm 1.0$  dB [Hewlett-Packard93] and a typical value of phase imbalance for a quadrature clock generator is  $\pm 2.0^{\circ}$  [Mini-Circuits92]. A typical 90° power splitter exhibits  $\pm 1.2$  dB of amplitude imbalance and  $\pm 2.0^{\circ}$  of phase imbalance [Mini-Circuits92]. For a voltage swing of 1V,  $|\delta_H|=130$ mV,  $|\phi_H|=2.0^{\circ}$ ,  $|\delta_M|=100$ mV, and  $|\phi_M|=2.0^{\circ}$ , resulting in about 20dB of sideband rejection. It is possible to increase the sideband rejection to about 35dB by adjusting the amplitude of the in-phase and quadrature-phase input signals to the QPSK modulator. Additional sideband rejection may be obtained by using a highpass filter after the RF power combiner.

The most difficult aspect of using the phase-shift method for this application is implementation of a Hilbert transformer which operates between 22.4MHz and 105.6MHz (130% of the center frequency) with a phase imbalance no greater than 2.0°. Commercially available 90° power splitters which meet this specification do not exist. The next two sections discuss custom implementations of the Hilbert transformer. The first section focuses on analog implementations whereas the second section discusses digital implementations.

#### 3.1.2.1. Hilbert Transformer: Analog Implementations

The main advantage of performing the Hilbert transform in the analog domain is that only one digital-to-analog converter is required for the entire transmitter. However, the realization of a Hilbert transformer with constant amplitude and phase outputs from 22.4MHz to 105.6MHz is nontrivial.

#### 3.1.2.1.1. RLC Phase-Splitter Circuit

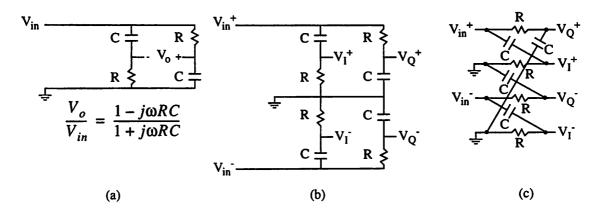

One passive network which produces in-phase and quadrature-phase outputs is depicted in Figure 3-6 [Luck49]. Selecting  $\omega_1=2\pi(22.4\text{MHz})$  and  $\omega_2=2\pi(105.6\text{MHz})$  gives

$$V_{\text{in}}^{+} = \frac{C_{1} + C_{2} + C_{2}}{C_{1} + C_{2} + C_{2}}$$

$$U_{1}^{+} = \frac{C_{1} + C_{2}}{C_{2} + C_{2}}$$

$$U_{2}^{-} = \frac{1}{L_{1}C_{1}}$$

$$\omega_{1}^{2} = \frac{\omega_{0}^{2}}{r^{2}} = \frac{1}{L_{1}C_{1}}$$

$$\omega_{2}^{2} = \omega_{0}^{2}r^{2} = \frac{1}{L_{2}C_{2}}$$

$$Q^{2} = \frac{L_{1}}{C_{1}R_{1}^{2}} = \frac{L_{2}}{C_{2}R_{2}^{2}}$$

Figure 3-6. RLC Phase-Splitter Circuit

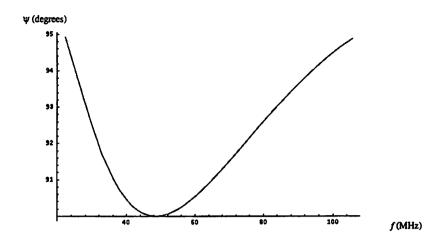

$\omega_0$ =2 $\pi$ (48.6MHz) and r=2.17. The phase difference  $\psi$  between  $V_I$  and  $V_Q$  is related to the frequency  $\omega$  through the following equation:

$$\tan \frac{1}{2} \Psi = \frac{\frac{1}{Q} \left( r - \frac{1}{r} \right) \left( \frac{\omega}{\omega_0} + \frac{\omega_0}{\omega} \right)}{\frac{1}{Q^2} - \left( r - \frac{1}{r} \right)^2 - 4 + \left( \frac{\omega}{\omega_0} + \frac{\omega_0}{\omega} \right)^2}$$

Selecting the phase difference to be 90° at  $\omega = \omega_0$  results in the following expression for Q as a function of r:

$$Q = \frac{\sqrt{2} - 1}{r - \frac{1}{r}}$$

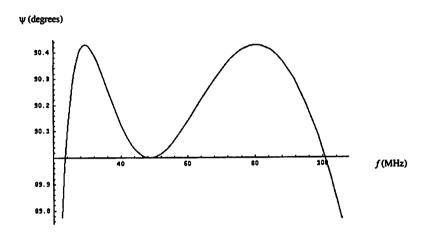

The corresponding value for Q is 0.242. A plot of  $\psi$  as a function of f is given in Figure 3-7. The maximum phase variation from 90° for this case is about 5°, which is too high if the desired sideband rejection of 40dB is to be achieved. The phase variation over the frequency band of interest may be decreased by using a different set of values for  $f_0$ , r, and Q. A plot of  $\psi$  as a function of f for  $f_0$ =48.6MHz, r=1.9, and Q=0.302 appears in Figure 3-8. The maximum phase variation from 90° for this case is only about 1°. Although this implementation of the Hilbert transformer appears very attractive due to the theoretical

Figure 3-7. RLC Phase-Splitter  $\psi$  Response ( $f_0$ =48.6MHz, r=2.17, Q=0.242)

Figure 3-8. RLC Phase-Splitter  $\psi$  Response ( $f_0$ =48.6MHz, r=1.9, Q=0.302)

phase imbalance of only 1°, two major drawbacks exist: non-constant phase relationship of individual outputs; and component value variation and mismatch.

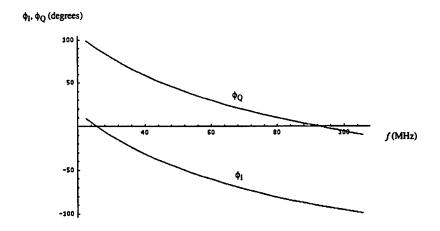

The phase dependence on frequency for both outputs is given below:

$$\tan\frac{1}{2}\phi_I = Q\left(\frac{\omega_0}{r\omega} - \frac{r\omega}{\omega_0}\right)$$

$$\tan\frac{1}{2}\phi_I = Q\left(\frac{\omega_0}{r\omega} - \frac{r\omega}{\omega_0}\right)$$

$\phi_I$  and  $\phi_O$  for  $f_0$ =48.6MHz, r=1.9, and Q=0.302 are plotted in Figure 3-9. Although  $\phi_Q$  is

Figure 3-9. RLC Phase-Splitter  $\varphi_I$  and  $\varphi_Q$  Response (  $\textit{f}_0$  =48.6MHz, r=1.9, Q=0.302)

offset from  $\phi_I$  by 90° across the entire band of interest, the individual phase curves are not constant, resulting in non-constant phase offsets across the entire frequency band. The magnitudes of  $V_I$  and  $V_Q$  are equal to half the input voltage magnitude across the entire frequency band.

The implementation of this method is limited to the use of discrete components since a monolithic approach is not available. If a 100nH surface mount inductor with a 5% tolerance [Digi-Key96] is used for  $L_1$  and  $L_2$ , then the following component values are required for  $f_0$ =48.6MHz, r=1.9, and Q=0.302:  $R_1$ =53.2 $\Omega$ ,  $R_2$ =192.1 $\Omega$ ,  $C_1$ =387pF, and  $C_2$ =29.7pF. SPICE simulation using the above component values results in the plots shown

Figure 3-10. RLC Phase-Splitter Simulated Response (R<sub>1</sub>=53.2 $\Omega$ , R<sub>2</sub>=192.1 $\Omega$ , C<sub>1</sub>=387pF, C<sub>2</sub>=29.7pF, L<sub>1</sub>=100nH, L<sub>2</sub>=100nH)

component values used for this simulation are not commercially available, and in addition, this simulation does not take into account component tolerances. Minimization of parasitic resistance, capacitances and inductances requires the use of surface mount components with very small form factors, such as obtained in a 0603 package. Resistors with 1% tolerance are commercially available with values  $53.6\Omega$  and  $191\Omega$  [Digi-Key96].

Capacitors with 10% tolerance are commercially available with values 390pF and 27pF [Digi-Key96]. SPICE simulation of the RLC phase-splitter circuit using commercially available values results in the plots shown in Figure 3-11. For this case, the maximum

Figure 3-11. RLC Phase-Splitter Simulated Response with Commercially Available Component Values ( $R_1$ =53.6 $\Omega$ ,  $R_2$ =191 $\Omega$ ,  $C_1$ =390pF,  $C_2$ =27pF,  $L_1$ =100nH,  $L_2$ =100nH)

phase variation from quadrature is about 7°. Thus, the RLC phase-splitter network is very

sensitive to component value deviations and is not amenable to discrete component realizations.

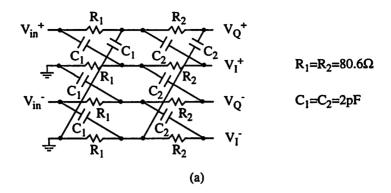

#### 3.1.2.1.1. Asymmetric Polyphase Networks

The most simple asymmetric polyphase network is the RC-CR structure depicted in Figure 3-12a. The voltage gain is unity for all frequencies and the phase of  $V_0$  is offset

Figure 3-12. RC-CR Structure

(a) Single-Ended; (b) Differential; (c) Differential (Redrawn)

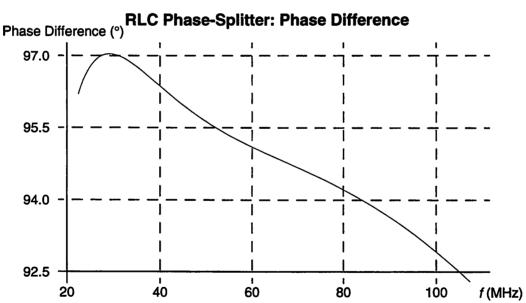

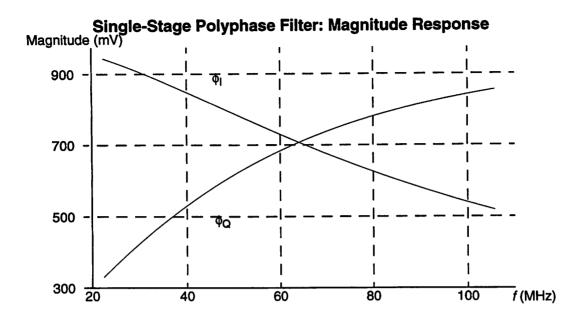

from that of  $V_{in}$  by 90° at  $\omega$ =1/RC. A differential version of the RC-CR structure is depicted in Figure 3-12b. The differential output voltage  $V_Q=V_Q^+-V_Q^-$  is offset from the differential output voltage  $V_I=V_I^+-V_I^-$  by 90° at all frequencies and the amplitude of both output voltages is  $1/\sqrt{2}$  times that of the input voltage at  $\omega$ =1/RC. The results of a SPICE simulation for R=4.97k $\Omega$  and C=0.5pF are depicted in Figure 3-13. As seen in the SPICE results, perfect quadrature is maintained across the entire frequency band. However, the phase response of the individual outputs is not constant. SPICE results also confirm that the gain is equal to  $1/\sqrt{2}$  at  $\omega$ =1/RC and for a 1V input the maximum output amplitude mismatch is about 600mV. Figure 3-12c depicts a redrawn version of the same differential RC-CR network shown in Figure 3-12b.

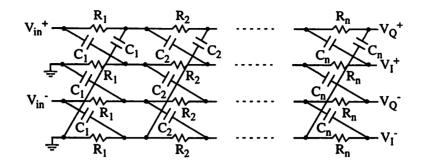

A major disadvantage of the differential RC-CR polyphase network is that output voltage amplitudes are equal at only one frequency. One solution is to cascade multiple stages as

Figure 3-13. SPICE Simulation of Single-Stage Asymmetric Polyphase Filter (R=4.97kΩ, C=0.5pF)

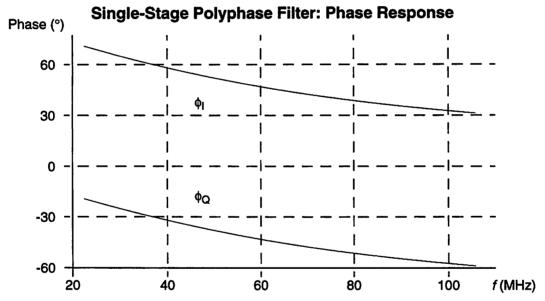

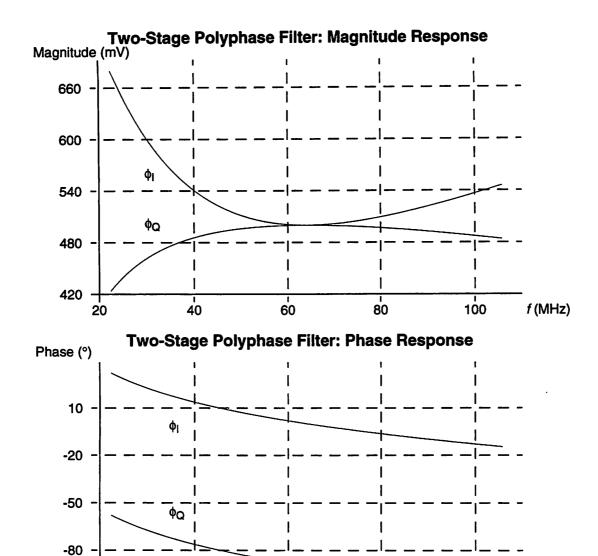

depicted in Figure 3-14 [Gingell73][West91][Crols95]. Each stage contributes a pole at  $s=1/R_xC_x$  and a zero at  $s=-1/R_xC_x$ . SPICE simulation for a two-stage asymmetric polyphase filter with  $R_1=R_2=4.97k\Omega$  and  $C_1=C_2=0.5pF$  results in the plots depicted in Figure 3-15. Again, perfect quadrature is maintained across the entire frequency band. However, for a 1V input voltage, the maximum output amplitude mismatch is now about

Figure 3-14. N-Stage Asymmetric Polyphase Filter

250mV. This mismatch may be decreased further by cascading additional filter stages. However, the insertion loss is directly proportional to the number of cascaded stages, and thus, the output signals may require amplification if many stages are used. Another way to decrease the amplitude mismatch is by selecting different values for  $\omega_1$  and  $\omega_2$ . The results of a SPICE simulation for a two-stage asymmetric polyphase filter with  $R_1$ =14.21k $\Omega$ ,  $R_2$ =3.01k $\Omega$ , and  $C_1$ = $C_2$ =0.5pF are depicted in Figure 3-16. For this case, the maximum amplitude mismatch is about 100mV. The best amplitude mismatch is achieved by using multiple stages and selecting  $\omega_x$ =1/ $R_x$ C $_x$  of each stage to be a different value.

Although perfect quadrature is maintained over the entire frequency band, the individual phase response of each output varies as much as 40° over about 85MHz. Due to the non-constant phase response of these asymmetric polyphase filters, their utility is limited to narrow-band applications, such as generating in-phase and quadrature-phase LO signals.

#### 3.1.2.2. Hilbert Transformer: Digital Implementations

The main disadvantage of implementing the Hilbert transform in the digital domain is that two digital-to-analog converters are required for the complete transmitter circuitry. However, since the transmitter resides in the basestation, the additional power consumption is not critical.

### 3.1.2.2.1. Post-Modulator Double-Sideband to Single-Sideband Converter

Multiplexing the in-phase and quadrature-phase output data streams from the baseband modulator results in a single 256MHz digital data stream, and thus, a 256MHz digital

Figure 3-15. SPICE Simulation of Two-Stage Asymmetric Polyphase Filter (R  $_1$  =R  $_2$  =4.97k  $\Omega$  ,  $C_1$  =C  $_2$  =0.5pF)

80

100

f (MHz)

60

-110

20

40

Hilbert transformer is required. Digital Hilbert transformers have been designed which operate at frequencies as high as 300MHz [Hawley95].

Figure 3-16. SPICE Simulation of Two-Stage Asymmetric Polyphase Filter (R  $_1$  =14.21k  $\Omega$ , R  $_2$  =3.01k  $\Omega$ , C  $_1$  =C  $_2$  =0.5pF)

The frequency response of an ideal Hilbert transformer is given by

$$H(\omega) = e^{-j\left(\frac{\pi}{2}\right)\operatorname{sgn}(\omega)}$$

and the corresponding time domain impulse response is given by

$$h[n] = \begin{cases} 0 & n=0\\ \frac{\sin^2(\pi n/2)}{\pi n/2} & n \neq 0 \end{cases}$$

The ideal transform is not physically realizable since it is noncausal and of infinite duration. A practical realization requires windowing and shifting the sequence, resulting in a finite and causal impulse response. However, such an implementation results in finite stopband energy as well as passband ripple. The number of taps as well as coefficient quantization and internal number representation must be optimized in order to minimize passband ripple and energy in the stopband.

One way of interpreting the output of the Hilbert transformer is that it is a sequence similar to the input but phase shifted by 90°. For example, the in-phase data is multiplied by  $\cos[2\pi n/4]$  in the baseband modulator chip. Since  $\cos[2\pi n/4]$  is equal to zero for all odd values of n, these values of the in-phase data need not be computed and are discarded. The function of the Hilbert transformer is to determine the values at these discarded points. This interpretation of the output of the Hilbert transformer suggests a more efficient way of performing single-sideband upconversion, which will be discussed in the next section.

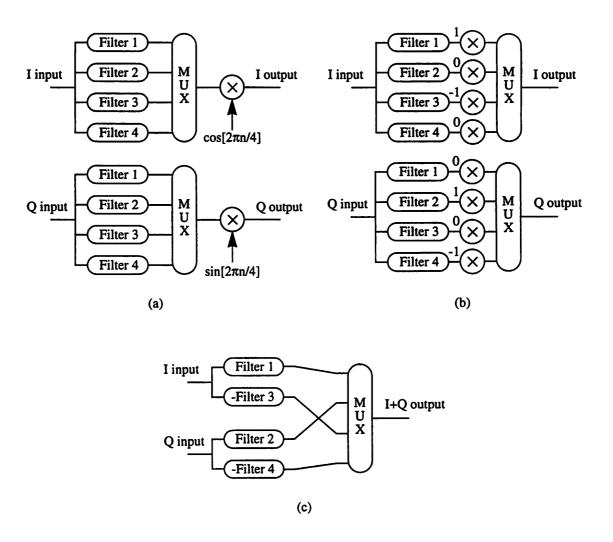

#### 3.1.2.2.2. Incorporation of Digital Hilbert Transformer within Baseband Modulator

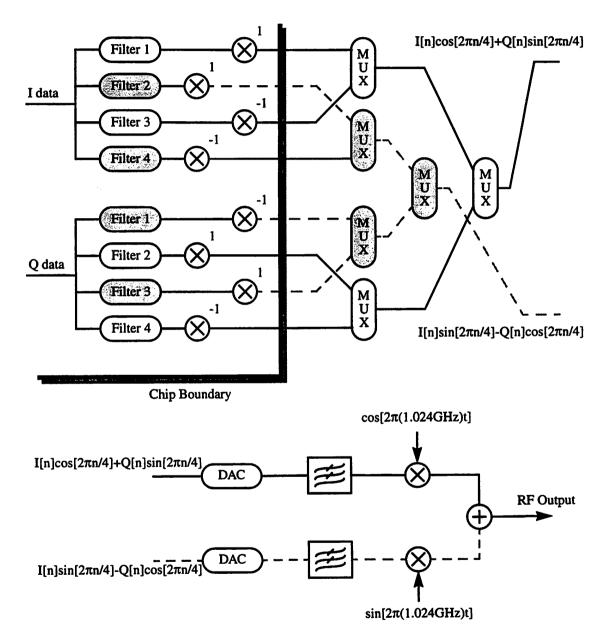

The baseband modulator chip incorporates two important design simplifications. First, since both in-phase and quadrature-phase data sequences are oversampled by a factor of four, each corresponding 256MHz raised-cosine filter may be divided into four parallel subfilters each operating at 64MHz. Second, the in-phase and quadrature-phase data streams are modulated by  $\cos[2\pi n/4]$  and  $\sin[2\pi n/4]$ , respectively. Since all odd samples of  $\cos[2\pi n/4]$  are equal to zero and all even samples of  $\sin[2\pi n/4]$  are equal to zero, the corresponding subfilters may be eliminated, and thus, only two parallel filters each operating at 64MHz are required for each 256MHz raised-cosine filter.

The outputs of the baseband modulator chip are  $I[n]\cos[2\pi n/4]$  and  $Q[n]\sin[2\pi n/4]$ . The Hilbert transforms of these two signal streams are  $I[n]\sin[2\pi n/4]$  and  $-Q[n]\cos[2\pi n/4]$ .

Thus, the function of the post-modulator digital Hilbert transform is to reconstruct the samples of the in-phase and quadrature-phase data which have been discarded. Instead of reconstructing the values of  $I[n]\sin[2\pi n/4]$  and  $-Q[n]\cos[2\pi n/4]$  with a post-modulator Hilbert transformer, these values may be generated directly within the baseband modulator chip. The architecture is depicted in Figure 3-17. The signal  $I[n]\cos[2\pi n/4]+Q[n]\sin[2\pi n/4]$

Figure 3-17. Architecture of Hilbert Transform Incorporated within Baseband Modulator Chip

4] along the signal path denoted by the solid lines is identical the output of the current

baseband modulator chip, which is illustrated in Figure 2-7c. The signal I[n]sin[ $2\pi n/4$ ]-Q[n]cos[ $2\pi n/4$ ] along the signal path denoted by the dashed lines is the corresponding Hilbert transform. The shaded subfilters, Filter 2 and Filter 4, used to generate the Hilbert transform output along the in-phase data path are identical to the unshaded subfilters, Filter 2 and Filter 4, along the quadrature-phase data path. Similarly, the shaded subfilters, Filter 1 and Filter 3, used to generate the Hilbert transform output along the quadrature-phase data path are identical to the unshaded subfilters, Filter 1 and Filter 3, along the in-phase data path. Thus, the procedure used to implement the subfilters in the current baseband modulator chip, which is described in [Peroulas95], may also be used to implement the additional four subfilters required to generate the Hilbert transform output. The filter coefficients of the subfilters are listed in Table 3-2.

**Table 3-2. Quantized Filter Coefficients**

| Filter 1       | Filter 2            | Filter 3 | Filter 4            |

|----------------|---------------------|----------|---------------------|

| 0.005126953125 | 0.00634765625       | 0.0      | -0.0136566162109375 |

| -0.0263671875  | -0.0244140625       | 0.0      | 0.0400390625        |

| 0.072265625    | 0.06353759765625    | 0.0      | -0.09765625         |

| -0.171875      | -0.1572265625       | 0.0      | 0.28515625          |

| 0.623046875    | 0.890625            | 1.0      | 0.890625            |

| 0.623046875    | 0.28515625          | 0.0      | -0.1572265625       |

| -0.171875      | -0.09765625         | 0.0      | 0.06353759765625    |

| 0.072265625    | 0.0400390625        | 0.0      | -0.0244140625       |

| -0.0263671875  | -0.0136566162109375 | 0.0      | 0.00634765625       |

| 0.005126953125 |                     | 0.0      |                     |

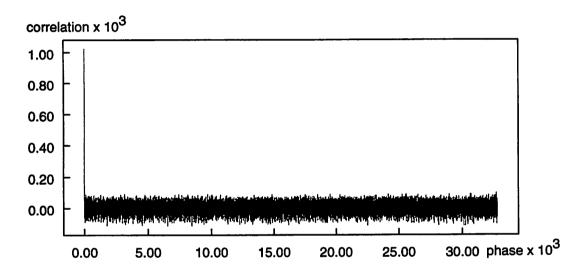

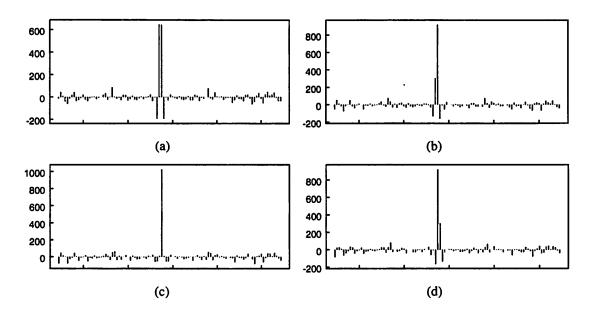

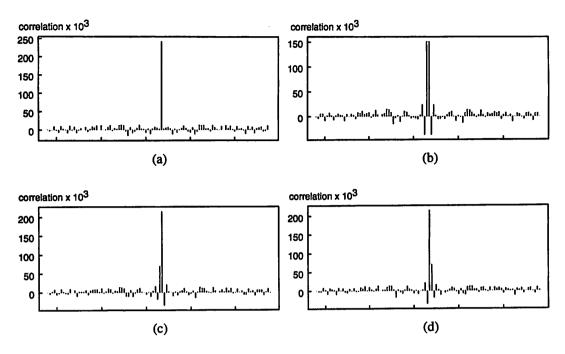

This method of generating the Hilbert transform results in minimum amplitude and phase distortion at the expense of increasing the complexity of the baseband modulator chip. The area of the current baseband modulator chip, which was fabricated in a 0.8µm CMOS process, is  $1 \times 1 \text{cm}^2$ . Since this method requires a total of eight subfilters instead of just four, incorporating the additional four subfilters onto the same chip may be impractical from an area standpoint unless the design is fabricated in a process with a smaller minimum feature size.