Copyright © 1996, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# WIDEBAND SPREAD-SPECTRUM DIGITAL COMMUNICATIONS FOR PORTABLE APPLICATIONS

by

-

,

Samuel Wei Sheng

Memorandum No. UCB/ERL M96/81

19 December 1996

# WIDEBAND SPREAD-SPECTRUM DIGITAL COMMUNICATIONS FOR PORTABLE APPLICATIONS

Copyright © 1996

by

Samuel Wei Sheng

Memorandum No. UCB/ERL M96/81

19 December 1996

### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Abstract

Wideband Spread-Spectrum Digital Communications for Portable Applications

by

Samuel Wei Sheng

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences University of California, Berkeley

Professor Robert W. Brodersen, Chair

Over the past several years, wireless communications have seen dramatic advances in two distinct areas. On one hand, the demand for portable voiceband services has completely inundated the capacity of existing analog cellular communication systems, resulting in intense research efforts to improve performance and increase capacity through digital technologies. Such systems focus on wide-area narrowband communications, providing services to individual users in a portable fashion. On the other hand, the need for more flexible computer networks has led to the advent of wireless LAN's, such as the Motorola Altair. Such systems focus on local-area wideband communications, providing services to computers but usually consuming far too much power to be easily portable. However, the distinction between these two is rapidly blurring – as greater and greater mobile computing resources are placd in the hands of individuals, wireless technologies capable of providing wide-area, wideband services will clearly be needed.

This thesis addresses the design and implementation of an indoor wireless system to support multimedia communication, with emphasis on a broadband downlink capable of supporting digital video. In particular, the development of integrated analog RF front-end and baseband digital interface circuitry, as well as the system simulations driving the design, have been examined. An ultimate per-user data rate 2 Mbps is the target; to achieve the required capacity, a picocellular system architecture will be employed, using cells on the order of 5m in size. In examining multiple access strategies for such an application, direct-sequence spread-spectrum, or code-division multiple access, possesses many advantages. For this system, a symbol rate of 1 Mbaud with a chipping rate of 64 Mchip/sec is used; for the spreading code, a Walsh-PN hybrid loosely based on the existing IS-95 digital cellular standard is chosen. Beyond providing multiple access, the ability to resolve multiple arrivals and detect adjacent channels in the digital baseband circuitry also affords many benefits that other systems, such as time-division or frequency-hop, cannot easily provide. Taking advantage of the broadcast mode transmission of the downlink, each cell is keyed to a pseudorandom pilot tone, which tremendously simplifies timing recovery and detection in the mobile

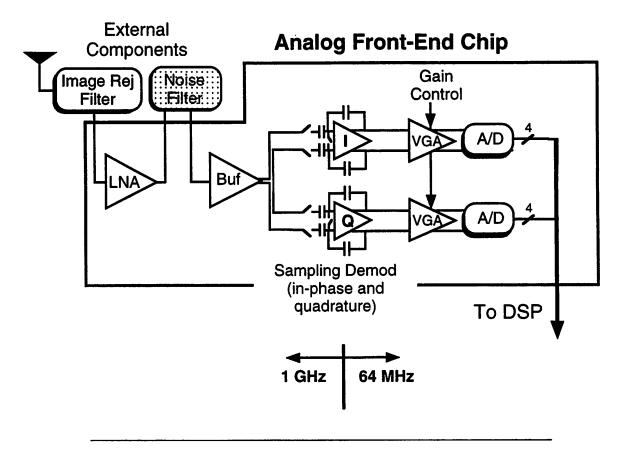

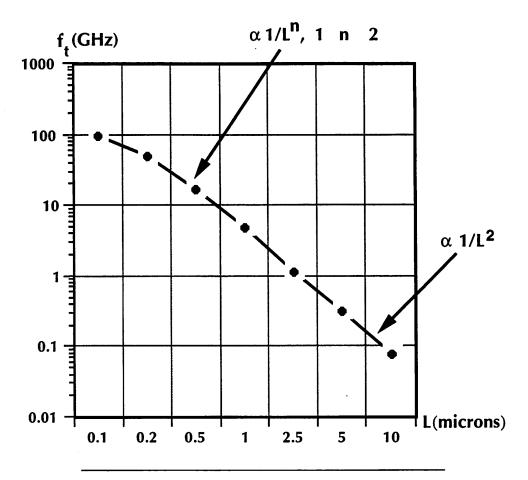

Lastly, the implementation of a high-performance, monolithic RF transceiver has been addressed. It is evident that an all-MOS RF system operating in the 1-2 GHz range is quite feasible, given technologies that are currently available. The benefits of integration are enormous: reduced parasitic effects, greater manufacturability, and minimized power requirements to drive off-chip loads. Likewise, by examining the basic architecture used in the transceiver, the underlying digital nature of the signal can be used to simplify the resulting circuit considerably: homodyne demodulation using passive sampling techniques is one important example of how this can be achieved. By taking advantage of these techniques, factors of 10-20x reduction in the power consumed by the analog RF circuitry in conventional designs can be achieved, at the expense of increased digital process. In some sense, the analog front-end has been reduced to its most basic functionality: amplification, filtering, frequency conversion, and analog-to-digital conversion.

Lastly, by exploiting dedicated parallel and pipelined techniques, a low-power spread-spectrum receiver has been designed in spite of the tremendous chipping rate of the system (64 Mchip/sec). By scaling the supply voltage, and employing multiple supplies into the chip, optimal voltages can be chosen to meet throughput requirements and minimize power consumption in the baseband digital logic. A prototype receiver has been developed; due to technology limitations, data rate is limited to 32 Mchip/sec; total power consumption of the prototype, implemented as a two custom ASIC solution, is 154 mW.

Kola MuBroders

# Table of Contents

• •

| CHAPTER | 1. Introduction                                              | 1  |

|---------|--------------------------------------------------------------|----|

| 1.1.    | Thesis Overview                                              | 4  |

| CHAPTER | 2. Modulation, Multiple Access, and                          |    |

|         | How Radio Waves Behave Indoors                               | 7  |

| 2.1.    | Cellular Reuse and the Indoor Propagation Channel            | 7  |

| 2.1.1.  | Cellular Systems                                             |    |

| 2.1.2.  | The Indoor Picocellular Environment                          |    |

| 2.1.3.  | Statistical Characterization and Multipath Propagation       | 13 |

| 2.1.4.  | Channel Modeling                                             |    |

| 2.2.    | Modulation Techniques                                        |    |

| 2.2.1.  | Quadrature Amplitude Modulation                              | 23 |

| 2.2.2.  | Continuous-Phase Modulation                                  | 25 |

| 2.2.3.  | Modulation Schemes: Comparison and Analysis                  | 27 |

| 2.3.    | Multiple Access Strategies                                   |    |

| 2.3.1.  | Time-Division Multiple Access                                | 30 |

| 2.3.2.  | Frequency-Hopped Spread-Spectrum Multiple Access             | 33 |

| 2.3.3.  | Code-Division Multiple Access                                | 34 |

| 2.4.    | Toward an Indoor Transmission Scheme                         | 40 |

| CHAPTER | 3. System Overview:                                          |    |

|         | The Broadband CDMA Downlink                                  | 41 |

| 3.1.    | Physical Layer Parameters                                    |    |

| 3.1.1.  | Modulation                                                   | 41 |

| 3.1.2.  | Pulse Shaping and System Transmit Bandwidth                  | 43 |

| 3.1.3.  | Transmit Power                                               | 45 |

| 3.1.4.  | Carrier Frequency                                            |    |

| 3.2.    | Multiple-Access Parameters                                   | 49 |

| 3.2.1.  | Processing Gain and Walsh Spreading Codes                    | 49 |

| 3.2.2.  | PN Overlay Code, the Pilot Tone, and Cell-to-Cell Code Reuse | 51 |

| 3.2.3.  | Channel Estimation and RAKE Reception                        |    |

| 3.3.    | An Open-Ended Architecture                                   |    |

| 3.4.    | Appendix: Ptolemy Simulation                                 |    |

| CHAPTER | 4. Transmit Architecture and                                 |    |

|         | The Baseband Modulator Chip                                  | 63 |

| 4.1.    | The Baseband Transmit Modulator                              | 64 |

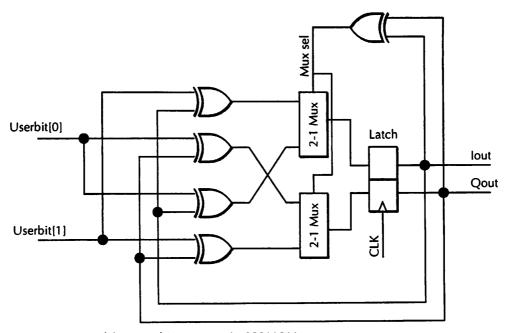

| 4.1.1.  | DQPSK coder                                                    | 64  |

|---------|----------------------------------------------------------------|-----|

| 4.1.2.  | Walsh Modulator                                                |     |

| 4.1.3.  | PN Modulator                                                   |     |

| 4.1.4.  | Per-User Power Control                                         |     |

| 4.1.5.  | The Pulse Shaping Filter                                       | 72  |

| 4.1.6.  | Filter Implementation                                          |     |

| 4.2.    | Results                                                        |     |

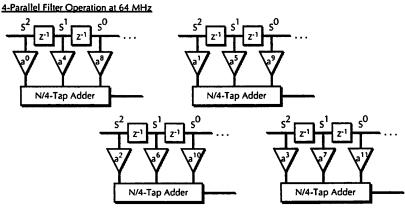

| 4.3.    | Digital-to-Analog Conversion and Frequency Translation         | 85  |

| 4.3.1.  | RF Rejection Method                                            |     |

| 4.3.2.  | Down-Up Method                                                 |     |

| 4.3.3.  | Digital Hilbert Transform                                      | 86  |

| 4.1.    | Epilogue: The Infopad Base Station                             | 88  |

| 4.2.    | Appendix: Modulator Electrical Interface                       | 92  |

| 4.2.1.  | Pinout                                                         | 92  |

| 4.2.2.  | Microprocessor timing                                          | 97  |

| 4.2.3.  | Clock timing 1                                                 | 00  |

| 4.2.4.  | Description of registers 1                                     | 01  |

| CHAPTER | 5. The Receiver:                                               |     |

|         | Analog RF Front-End 1                                          | 109 |

|         | ·                                                              |     |

| 5.1.    | Receiver Architectures                                         |     |

| 5.2.    | Silicon CMOS for RF Analog                                     |     |

| 5.3.    | Low-Noise Amplification                                        |     |

| 5.3.1.  | System Noise Requirements                                      |     |

| 5.3.2.  | RF LNA Design and Matching Filter Networks                     |     |

| 5.3.3.  | Broadband-Matched Topology                                     |     |

| 5.3.4.  | Tuned-Matching Topology                                        |     |

| 5.4.    | Sampling Demodulation.                                         | 132 |

| 5.4.1.  | Quadrature Recovery and the Choice of System Carrier Frequency |     |

| 5.4.2.  | Bandpass Antialiasing                                          |     |

| 5.4.3.  | Frequency Stability and Incoherent Demodulation                |     |

| 5.5.    | MOS Sampling Demodulator Design                                |     |

| 5.5.1.  | The Bottomplate Sampling Demodulator                           |     |

| 5.5.2.  | On-Chip Clock Buffering and Layout Issues                      |     |

| 5.6.    | From RF to Baseband                                            |     |

| 5.7.    | Appendix: RF Chip-on-Board Design                              |     |

| 5.7.1.  | Electromagnetic Effects                                        |     |

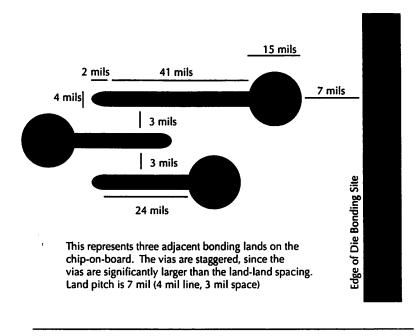

| 5.7.2.  | General Layout Issues                                          | 120 |

| 5.7.3.  | Discrete Inductors and Capacitors                              |     |

| 5.7.4.  | Chip-On-Board Design                                           |     |

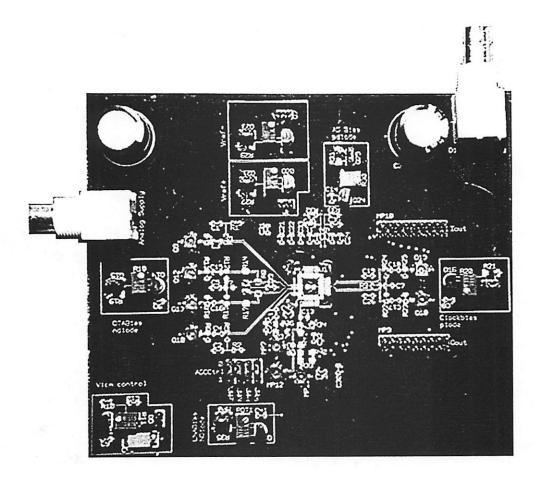

| 5.7.5.  | RF Testboard                                                   | 103 |

. . .

.

| CHAPTER | 6. The Receiver:                                          |     |

|---------|-----------------------------------------------------------|-----|

|         | Baseband Analog Processing                                | 169 |

| 6.1.    | System Dynamic Range and Linearity Requirements           | 170 |

| 6.2.    | Variable-Gain Amplifier Topology                          |     |

| 6.3.    | Operational Amplifier Design                              | 178 |

| 6.3.1.  | Optimizations                                             | 182 |

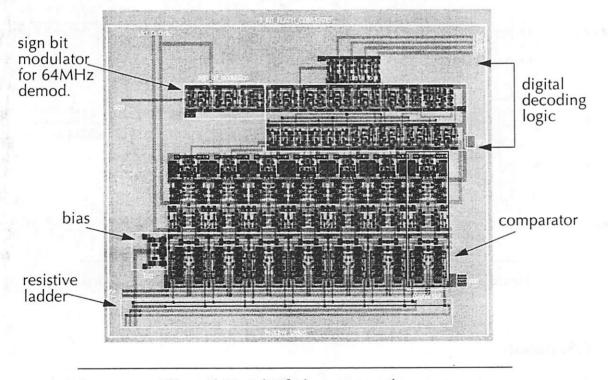

| 6.4.    | The Analog-to-Digital Converter                           | 186 |

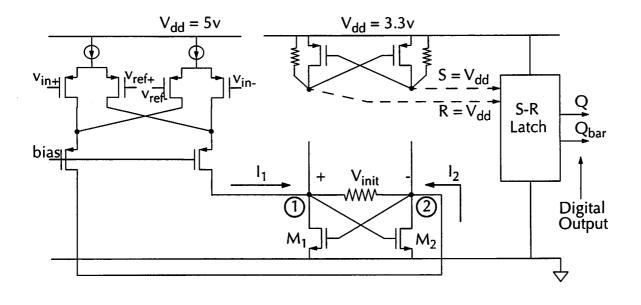

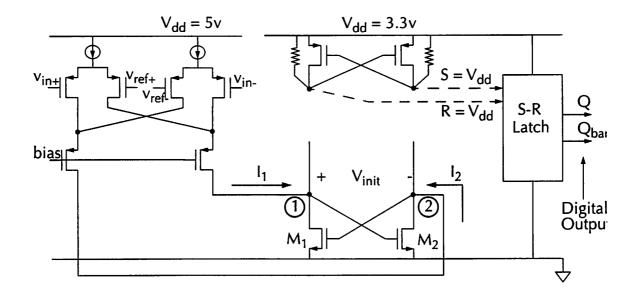

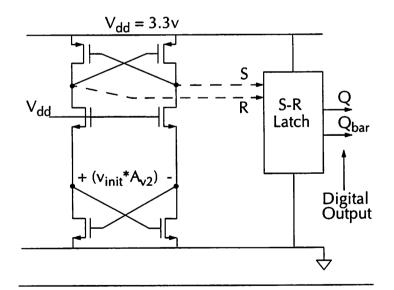

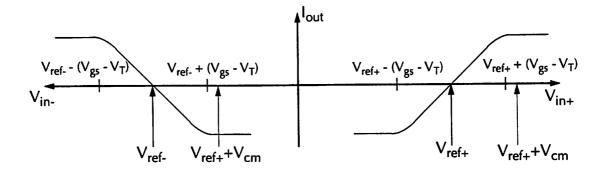

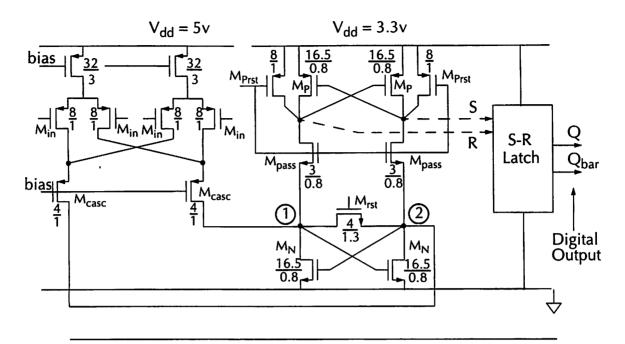

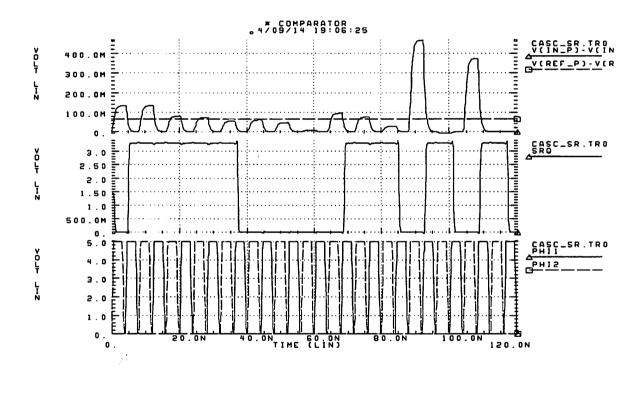

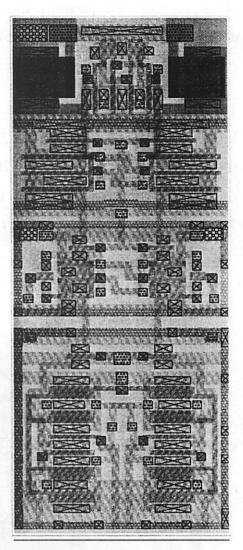

| 6.4.1.  | Comparator Design                                         | 189 |

| 6.4.2.  | A/ D Optimizations                                        | 197 |

| 6.5.    | Results                                                   |     |

| 6.6.    | Appendix: Electrical Interface Specifications             | 212 |

| CHAPTER | 7. The Receiver:                                          |     |

|         | Baseband Spread-Spectrum DSP                              | 221 |

| 7.1.    | Receiver DSP Architecture                                 | 222 |

| 7.2.    | The Matched-Filter Correlator                             | 223 |

| 7.3.    | Timing Recovery and Adjacent-Cell Detection               | 226 |

| 7.3.1.  | Coarse Acquisition                                        |     |

| 7.3.2.  | Fine Timing Acquisition and the Digital Phase-Locked Loop |     |

| 7.3.3.  | Carrier-Offset Compensation                               |     |

| 7.3.4.  | Adjacent-Cell Detection                                   |     |

| 7.4.    | Channel Estimation                                        |     |

| 7.5.    | Data Recovery                                             |     |

| 7.6.    | Results                                                   |     |

| 7.7.    | Appendix: Receiver DSP Electrical Interface               |     |

| 7.7.1.  | Input/Output Description                                  |     |

| 7.7.2.  | Programmable Registers                                    |     |

| 7.7.3.  | Observation Modes                                         |     |

| 7.7.4.  | Test Modes                                                | 256 |

| CHAPTER | 8. Conclusions and Future Work                            | 259 |

v

# List of Figures

| CHAPTER 1                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                          | . 1                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Figure 1.1:                                                                                                                                                                                                                                                                                                            | Infopad System Overview                                                                                                                                                                                                                                                                  | . 2                                                                          |

| CHAPTER 2                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                          | . 7                                                                          |

| Figure 2.1:                                                                                                                                                                                                                                                                                                            | Cellular Transmission System                                                                                                                                                                                                                                                             | . 9                                                                          |

| Figure 2.2:                                                                                                                                                                                                                                                                                                            | Typical Cellular Reuse Patterns                                                                                                                                                                                                                                                          | 10                                                                           |

| Figure 2.3:                                                                                                                                                                                                                                                                                                            | Normalized BW of Cellular System                                                                                                                                                                                                                                                         | 12                                                                           |

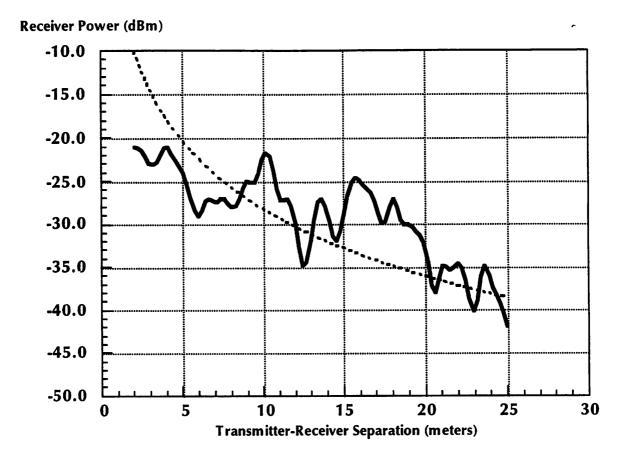

| Figure 2.4:                                                                                                                                                                                                                                                                                                            | Measured Path Loss Characteristic                                                                                                                                                                                                                                                        | 15                                                                           |

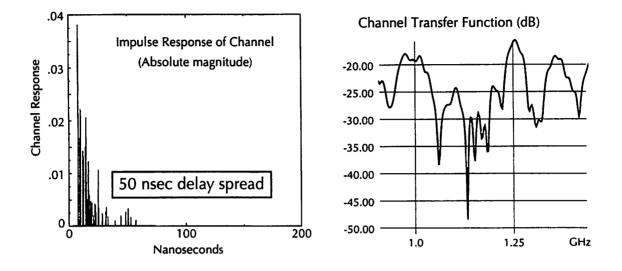

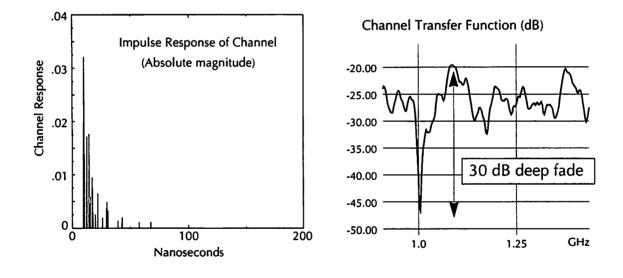

| Figure 2.5:                                                                                                                                                                                                                                                                                                            | Two simulated random sample channels                                                                                                                                                                                                                                                     | 19                                                                           |

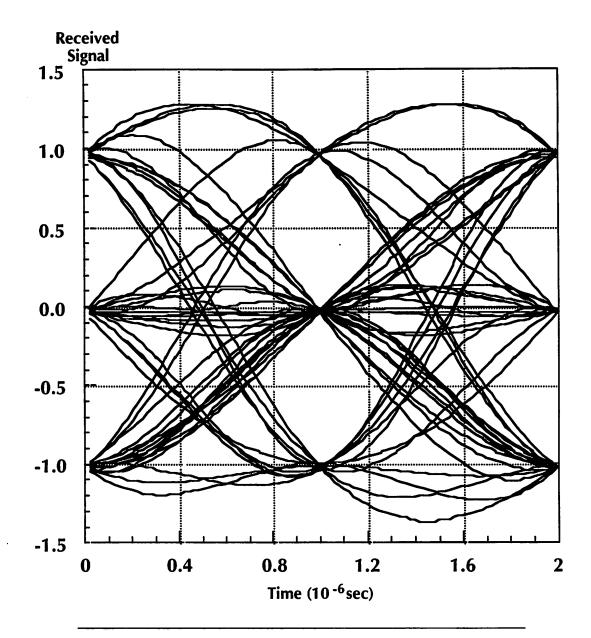

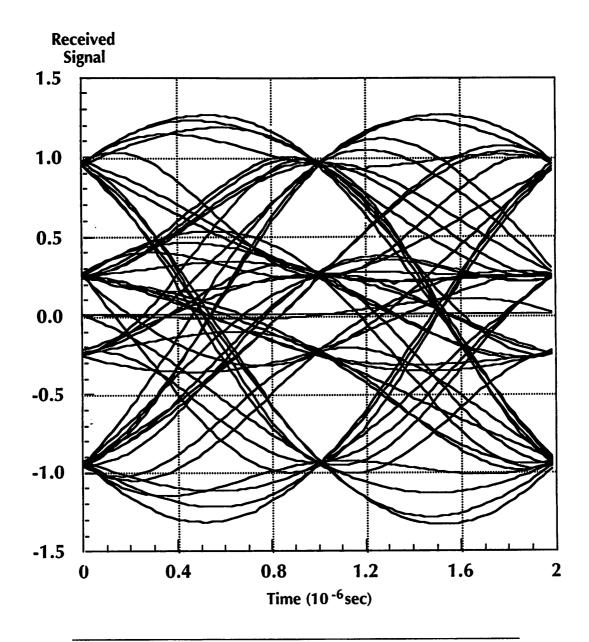

| Figure 2.6:                                                                                                                                                                                                                                                                                                            | Simulated QPSK eye diagram, no channel ISI                                                                                                                                                                                                                                               | 21                                                                           |

| Figure 2.7:                                                                                                                                                                                                                                                                                                            | Simulated QPSK eye diagram, with multipath channel                                                                                                                                                                                                                                       | 22                                                                           |

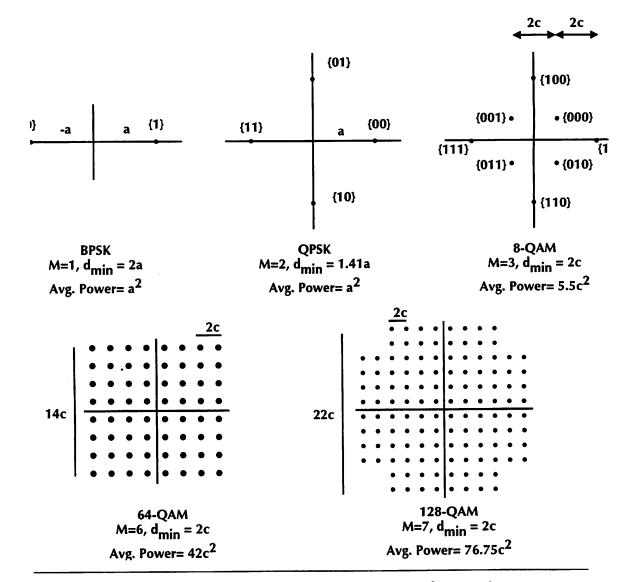

| Figure 2.8:                                                                                                                                                                                                                                                                                                            | QAM Constellations (Cross-configuration)                                                                                                                                                                                                                                                 | 24                                                                           |

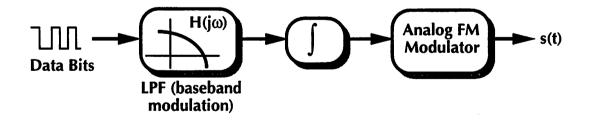

| Figure 2.9:                                                                                                                                                                                                                                                                                                            | General CPM Modulator                                                                                                                                                                                                                                                                    | 26                                                                           |

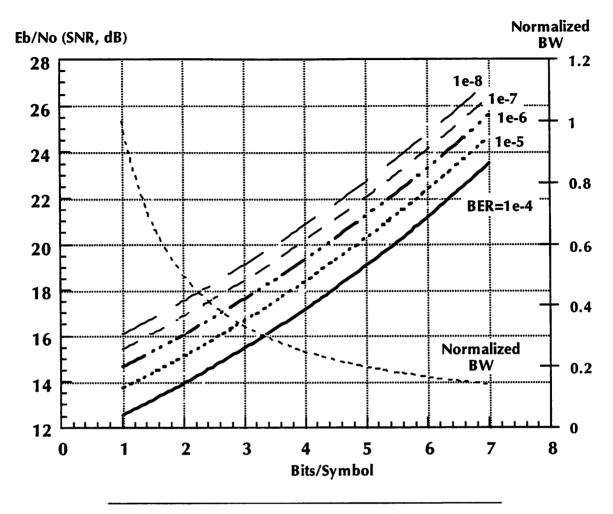

| Figure 2.10:                                                                                                                                                                                                                                                                                                           | Comparison of Modulation Schemes (AWGN only)                                                                                                                                                                                                                                             | 28                                                                           |

| Figure 2.11:                                                                                                                                                                                                                                                                                                           | Required SNR vs. Constellation Size                                                                                                                                                                                                                                                      | 29                                                                           |

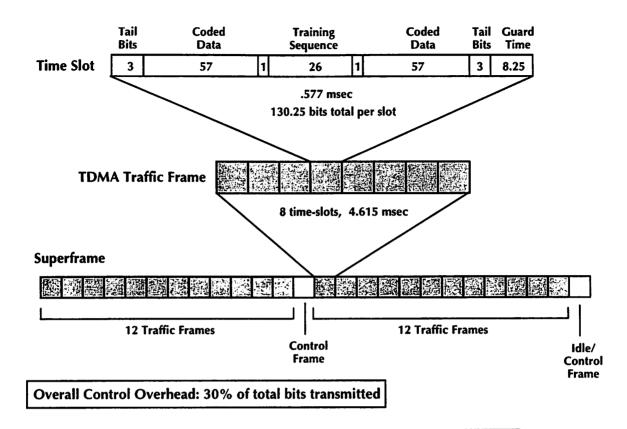

| Figure 2.12:                                                                                                                                                                                                                                                                                                           | TDMA Framing/Control Strategy (GSM)                                                                                                                                                                                                                                                      | 31                                                                           |

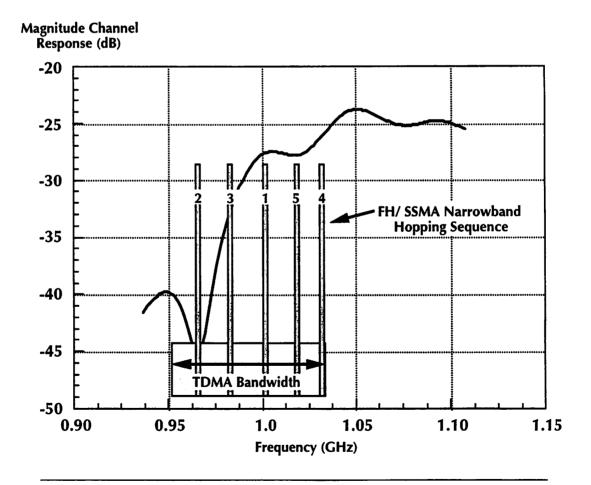

| Figure 2.13:                                                                                                                                                                                                                                                                                                           | Comparison of TDMA and FH/SSMA                                                                                                                                                                                                                                                           | 54                                                                           |

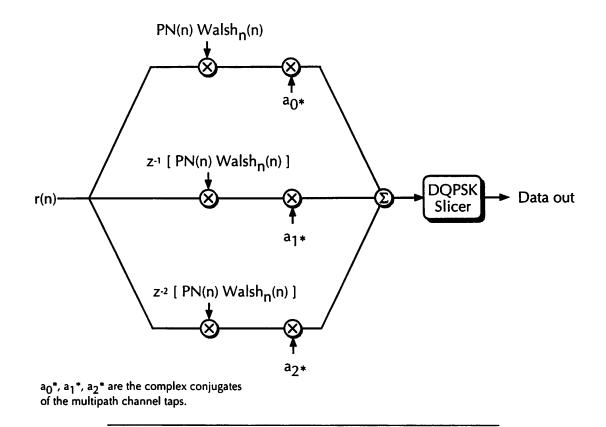

| Figure 2.14:                                                                                                                                                                                                                                                                                                           | RAKE Receiver architecture (3rd order)                                                                                                                                                                                                                                                   | 37                                                                           |

| -                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                          |                                                                              |

| CHAPTER 3                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                          | 41                                                                           |

| CHAPTER 3<br>Table 3.1:                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                          |                                                                              |

|                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                          | . 62                                                                         |

| Table 3.1:                                                                                                                                                                                                                                                                                                             | System link parameters                                                                                                                                                                                                                                                                   | . 62<br>43                                                                   |

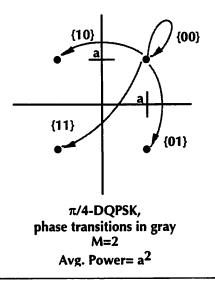

| Table 3.1:<br>Figure 3.1:                                                                                                                                                                                                                                                                                              | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46                                                             |

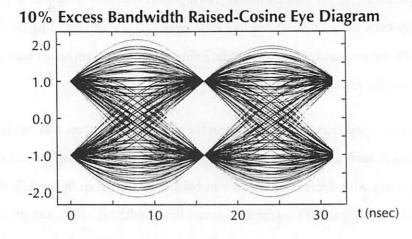

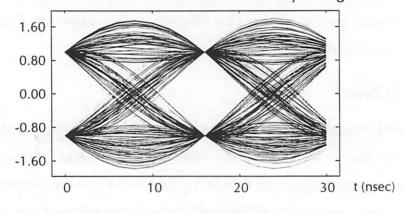

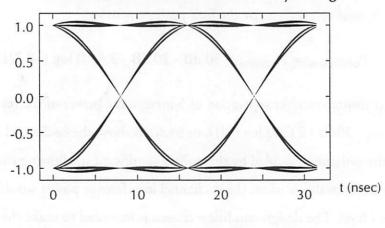

| Table 3.1:<br>Figure 3.1:<br>Figure 3.2:                                                                                                                                                                                                                                                                               | System link parameters<br>DQPSK phase transition diagram<br>Raised-cosine pulse shape eye diagrams                                                                                                                                                                                       | . 62<br>43<br>46<br>47                                                       |

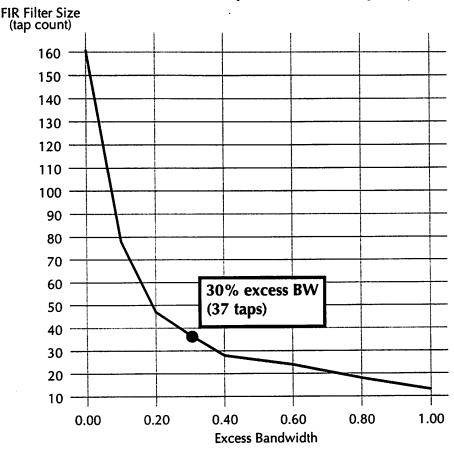

| Table 3.1:<br>Figure 3.1:<br>Figure 3.2:<br>Figure 3.3:                                                                                                                                                                                                                                                                | System link parameters<br>DQPSK phase transition diagram<br>Raised-cosine pulse shape eye diagrams<br>Transmit filter complexity versus excess bandwidth                                                                                                                                 | . 62<br>43<br>46<br>47<br>48                                                 |

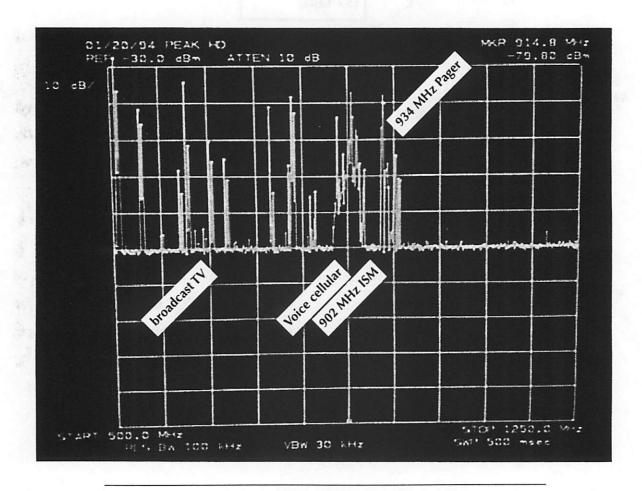

| Table 3.1:<br>Figure 3.1:<br>Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:                                                                                                                                                                                                                                                 | System link parameters<br>DQPSK phase transition diagram<br>Raised-cosine pulse shape eye diagrams<br>Transmit filter complexity versus excess bandwidth.<br>Spectral usage, 500-1250 MHz.                                                                                               | . 62<br>43<br>46<br>47<br>48<br>50                                           |

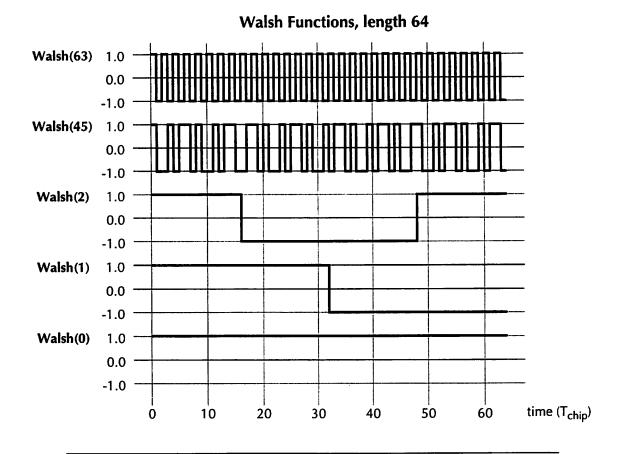

| Table 3.1:<br>Figure 3.1:<br>Figure 3.2:<br>Figure 3.3:<br>Figure 3.4:<br>Figure 3.5:                                                                                                                                                                                                                                  | System link parameters<br>DQPSK phase transition diagram<br>Raised-cosine pulse shape eye diagrams<br>Transmit filter complexity versus excess bandwidth<br>Spectral usage, 500-1250 MHz<br>Sample Length-64 Walsh Functions                                                             | . 62<br>43<br>46<br>47<br>48<br>50<br>51                                     |

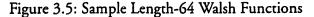

| Table 3.1:Figure 3.1:Figure 3.2:Figure 3.3:Figure 3.3:Figure 3.4:Figure 3.5:Figure 3.5:Figure 3.6:                                                                                                                                                                                                                     | System link parameters<br>DQPSK phase transition diagram<br>Raised-cosine pulse shape eye diagrams<br>Transmit filter complexity versus excess bandwidth<br>Spectral usage, 500-1250 MHz<br>Sample Length-64 Walsh Functions<br>Dataflow diagram of the spread-spectrum signal synthesis | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52                               |

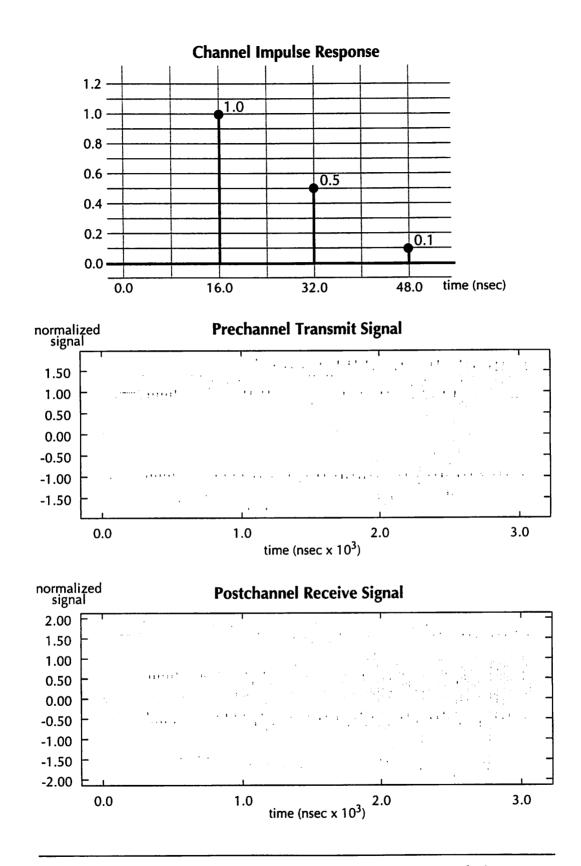

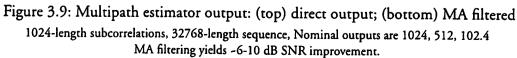

| Table 3.1:         Figure 3.1:         Figure 3.2:         Figure 3.3:         Figure 3.3:         Figure 3.4:         Figure 3.5:         Figure 3.6:         Figure 3.7:         Figure 3.8:         Figure 3.9:                                                                                                     | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52<br>58<br>59                   |

| Table 3.1:         Figure 3.1:         Figure 3.2:         Figure 3.3:         Figure 3.3:         Figure 3.4:         Figure 3.5:         Figure 3.6:         Figure 3.7:         Figure 3.8:         Figure 3.9:                                                                                                     | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52<br>58<br>59                   |

| Table 3.1:         Figure 3.1:         Figure 3.2:         Figure 3.2:         Figure 3.3:         Figure 3.3:         Figure 3.4:         Figure 3.5:         Figure 3.5:         Figure 3.6:         Figure 3.7:         Figure 3.8:         Figure 3.9:         Figure 3.10:                                        | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52<br>58<br>59<br>60             |

| Table 3.1:         Figure 3.1:         Figure 3.2:         Figure 3.2:         Figure 3.3:         Figure 3.3:         Figure 3.4:         Figure 3.5:         Figure 3.5:         Figure 3.6:         Figure 3.7:         Figure 3.8:         Figure 3.9:         Figure 3.10:                                        | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52<br>58<br>59<br>60<br>63       |

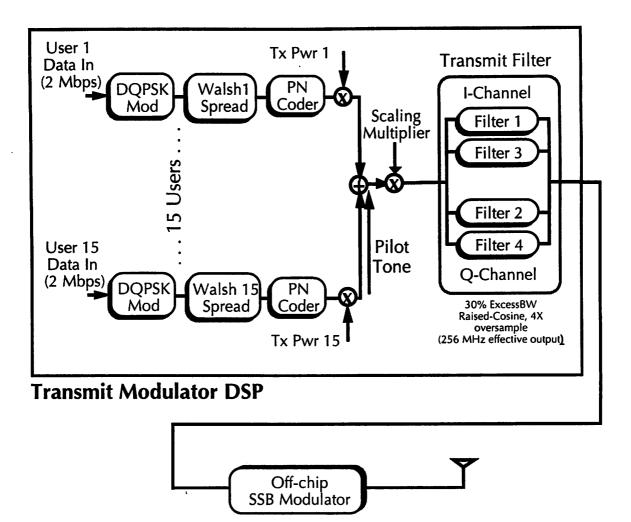

| Table 3.1:         Figure 3.1:         Figure 3.2:         Figure 3.2:         Figure 3.3:         Figure 3.3:         Figure 3.4:         Figure 3.5:         Figure 3.5:         Figure 3.6:         Figure 3.7:         Figure 3.7:         Figure 3.8:         Figure 3.9:         Figure 3.10:         CHAPTER 4. | System link parameters<br>DQPSK phase transition diagram                                                                                                                                                                                                                                 | . 62<br>43<br>46<br>47<br>48<br>50<br>51<br>52<br>58<br>59<br>60<br>63<br>64 |

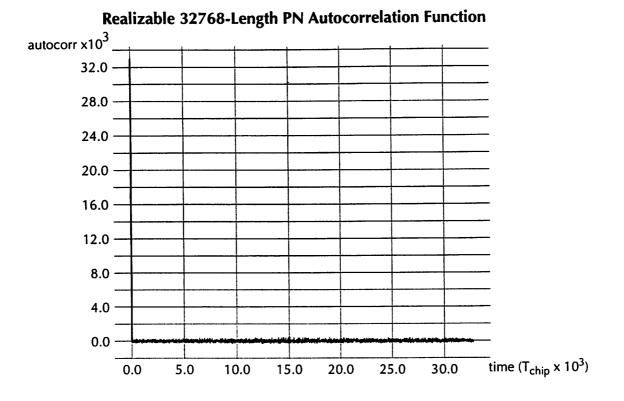

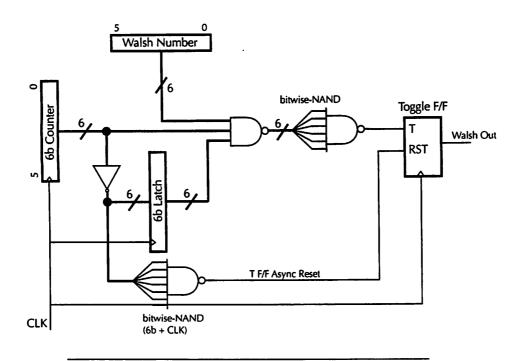

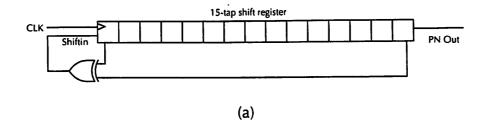

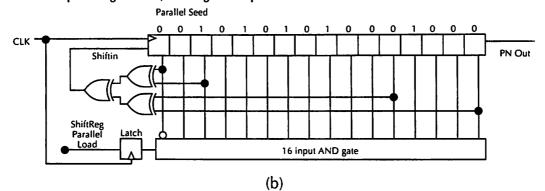

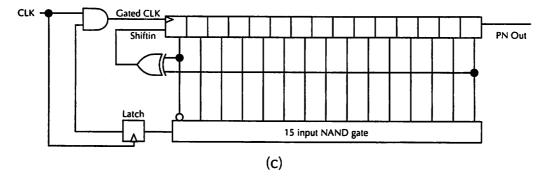

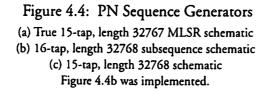

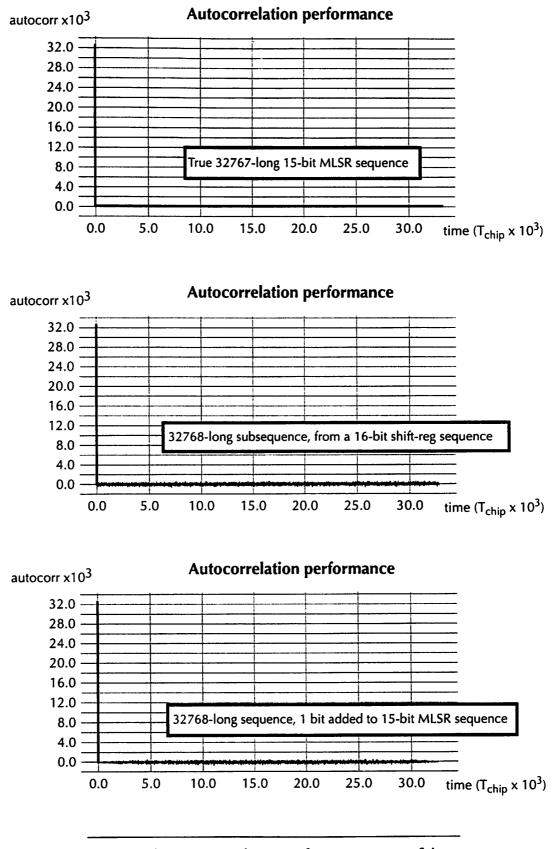

| Figure 4.4:  | PN Sequence Generators                                                                         |

|--------------|------------------------------------------------------------------------------------------------|

|              | (a) True 15-tap, length 32767 MLSR schematic                                                   |

|              | (b) 16-tap, length 32768 subsequence schematic                                                 |

|              | (c) 15-tap, length 32768 schematic                                                             |

| Figure 4.5:  | Autocorrelation performance curves                                                             |

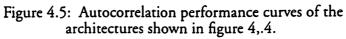

| Figure 4.6:  | Autocorrelation performance under restriction                                                  |

|              | to length 1024 subcorrelations                                                                 |

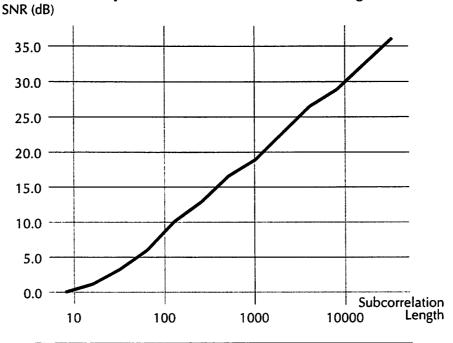

| Figure 4.7:  | Plot of SNR due to off-peak nonzero autocorrelation,<br>as a function of subcorrelation length |

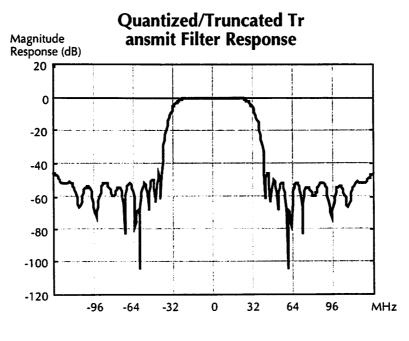

| Figure 4.8:  | Filter response after truncation and tap quantization                                          |

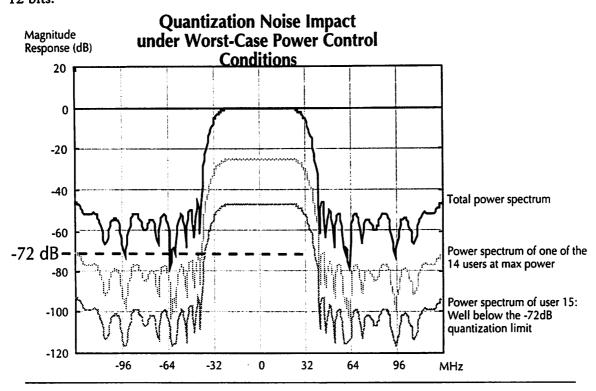

| Figure 4.9:  | Filter quantization noise effects                                                              |

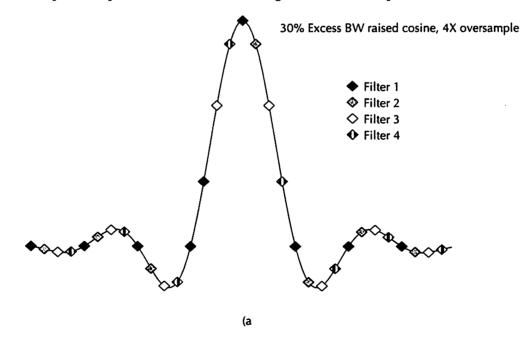

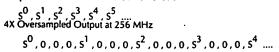

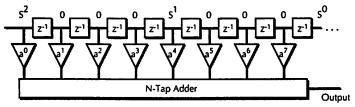

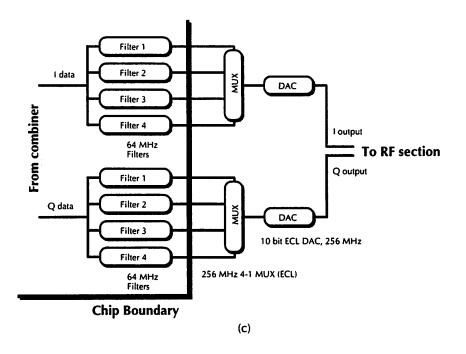

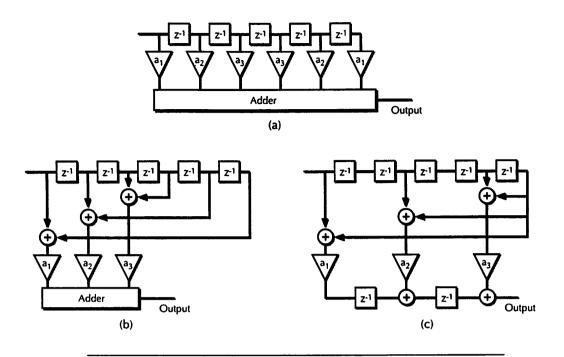

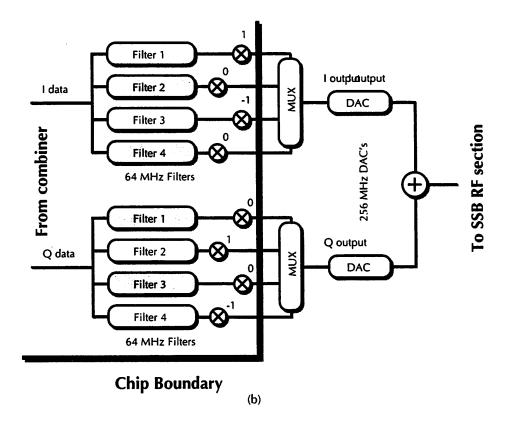

| Figure 4.10: | 4-Parallel Implementation of the Transmit Filter                                               |

| Figure 4.10: | (a) Parallel architecture, (b) System-level schematic of filter                                |

|              | structure, (c) Tap assignments                                                                 |

| Figure 4.11: |                                                                                                |

| 8            | (a) Original transversal structure (b) Shared multipliers                                      |

|              | (c) Pipelined output adder 78                                                                  |

| Figure 4.12: | Pipelined output adder filter structure                                                        |

| Figure 4.14: | Final minimized filter architecture 80                                                         |

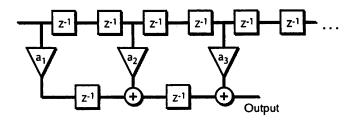

| Figure 4.13: | (a) Premodulation to 64 MHz                                                                    |

| -            | (b) Folding the multiplication into the 4 parallel filters 81                                  |

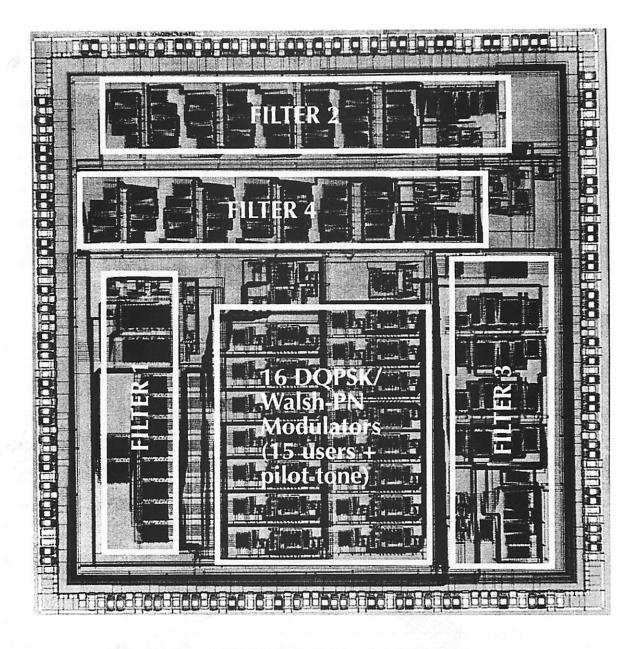

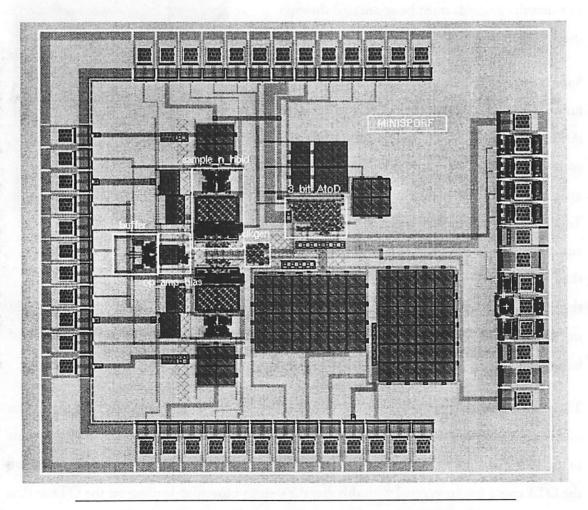

| Figure 4.15: | Modulator Die Photo plus Performance Summary                                                   |

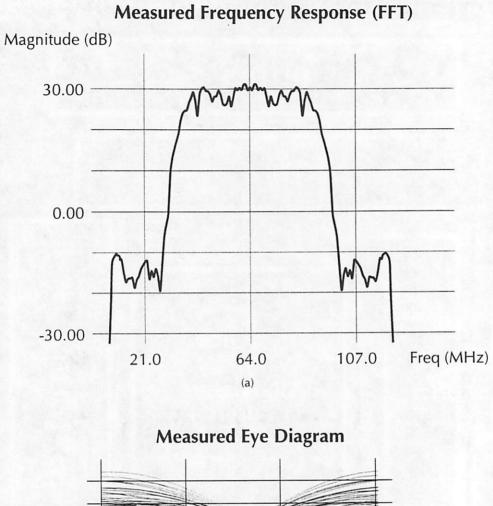

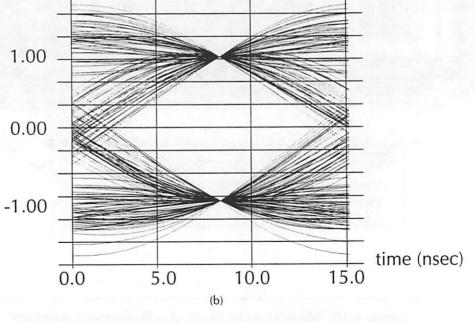

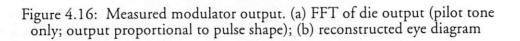

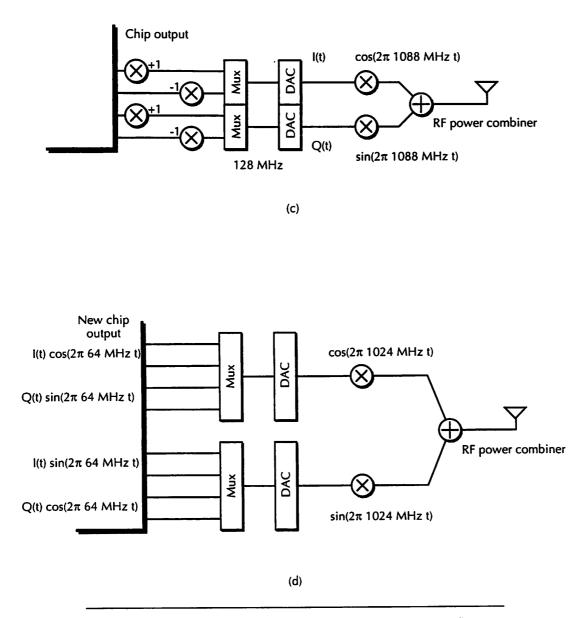

| Figure 4.16: | Measured modulator output 104                                                                  |

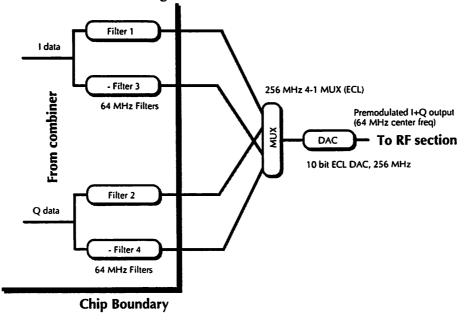

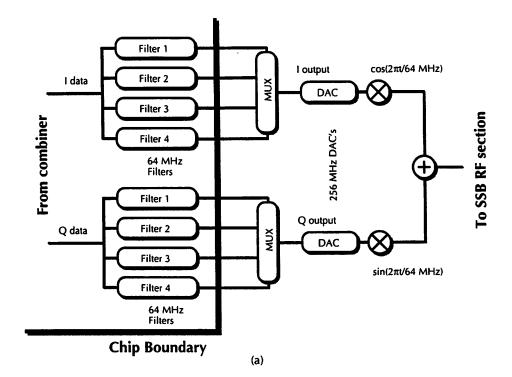

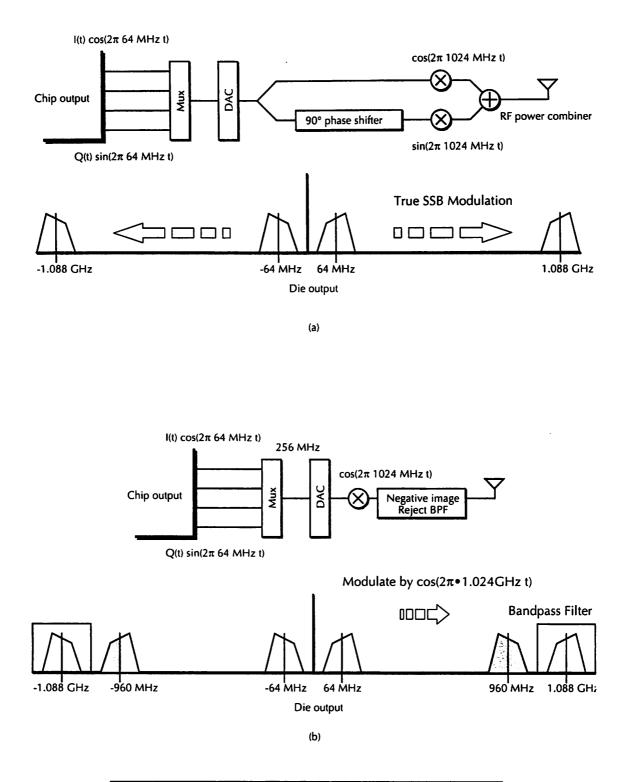

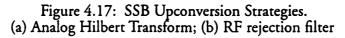

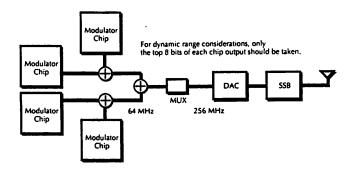

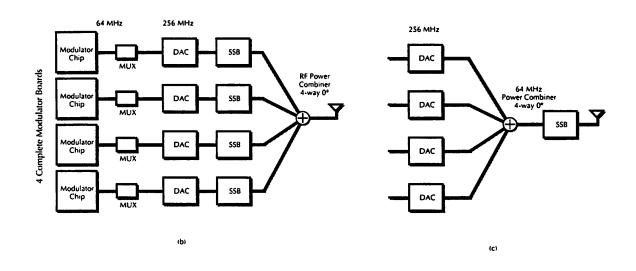

| Figure 4.17: | SSB Upconversion Strategies.                                                                   |

|              | (a) Analog Hilbert Transform; (b) RF rejection filter                                          |

|              | (c) Down-Up Method; (d) Digital Hilbert Transform 107-108                                      |

| Figure 4.18: | •                                                                                              |

| Figure 4.19: | Modulator package pinout (209-pin PGA) 92                                                      |

| Table 4.1:   | Modulator pinout arranged by functional group 113                                              |

| Table 4.2:   | Modulator pinout by pin ordering 115                                                           |

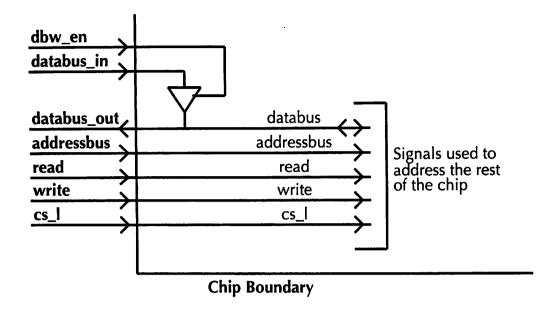

| Figure 4.20: | Physical circuitry of the microprocessor interface                                             |

| Figure 4.21: | Timing of a microprocessor read cycle                                                          |

| Figure 4.22: | Timing of a microprocessor write cycle                                                         |

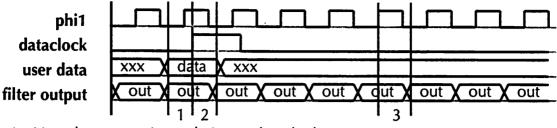

| Figure 4.23: | Timing of signals relative to the 64 MHz clock (phi1) 101                                      |

| Table 4,3:   | Description of Registers 122                                                                   |

| CHAPTER 5    |                                                                                                |

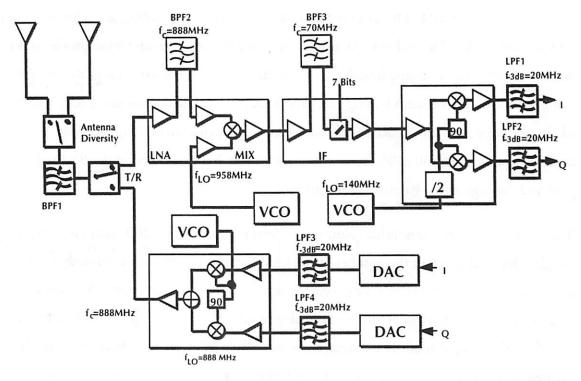

| Figure 5.1:  | Off-the-shelf analog front-end implementation                                                  |

|              | (a) Schematic (b) Semicustom board implementation 111                                          |

| Figure 5.2:  | Monolithic RF Front-End Architecture 113                                                       |

| Figure 5.3:  | Achievable device ft vs. MOSFET drawn L 115                                                    |

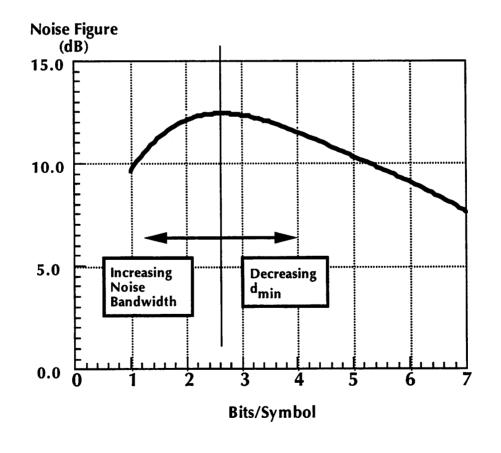

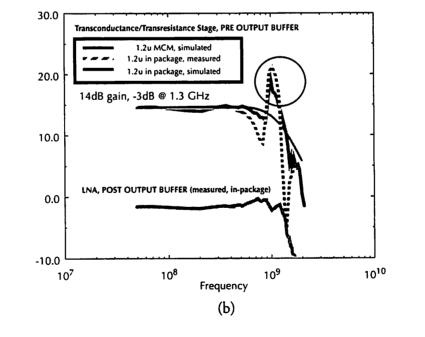

| Figure 5.4:  | System noise figure versus constellation size,<br>for constant BER= 10-4 1                           | 117 |

|--------------|------------------------------------------------------------------------------------------------------|-----|

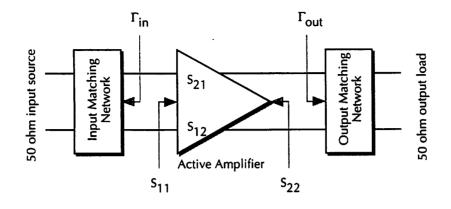

| Figure 5.5:  | Generalized RF amplifier topology 1                                                                  | 118 |

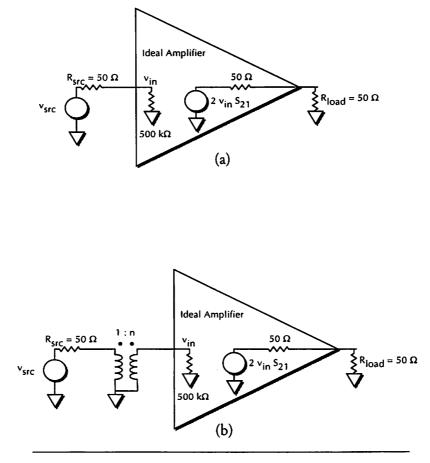

| Figure 5.6:  | Power matching to achieve gain from passive elements.<br>(a) Prototype case (b) Power matched case 1 |     |

| Figure 5.7:  | Broadband-matched LNA topology.                                                                      |     |

| U            | (a) Schematic (b) Measured response                                                                  | 122 |

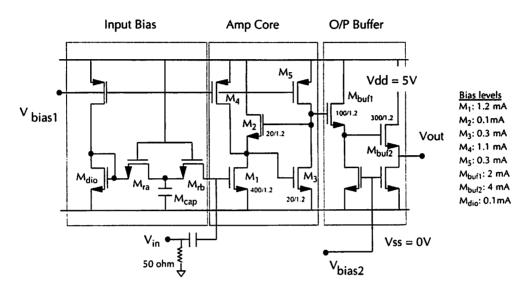

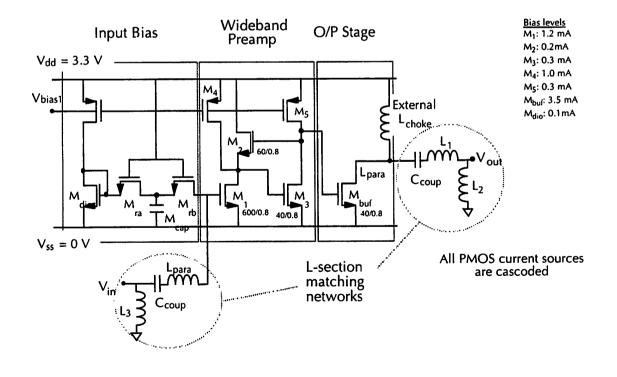

| Figure 5.8:  | Tuned-matching LNA topology                                                                          | 126 |

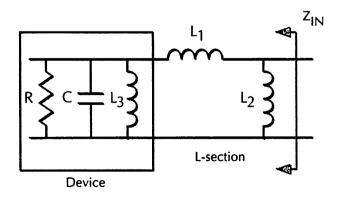

| Figure 5.9:  | Tuned L-section, 50 ohm match                                                                        | 127 |

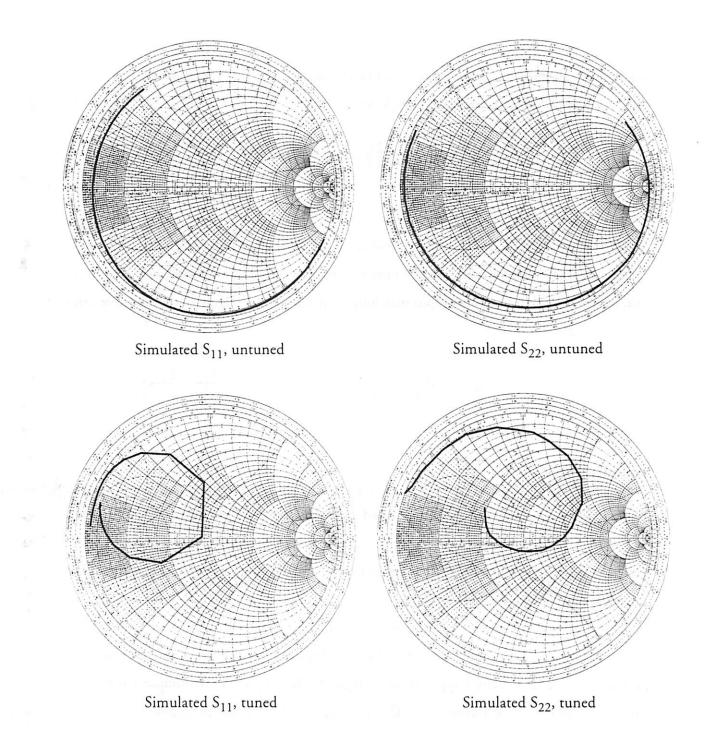

| Figure 5.10: | SPICE-simulated input and output reflection coefficients                                             | 129 |

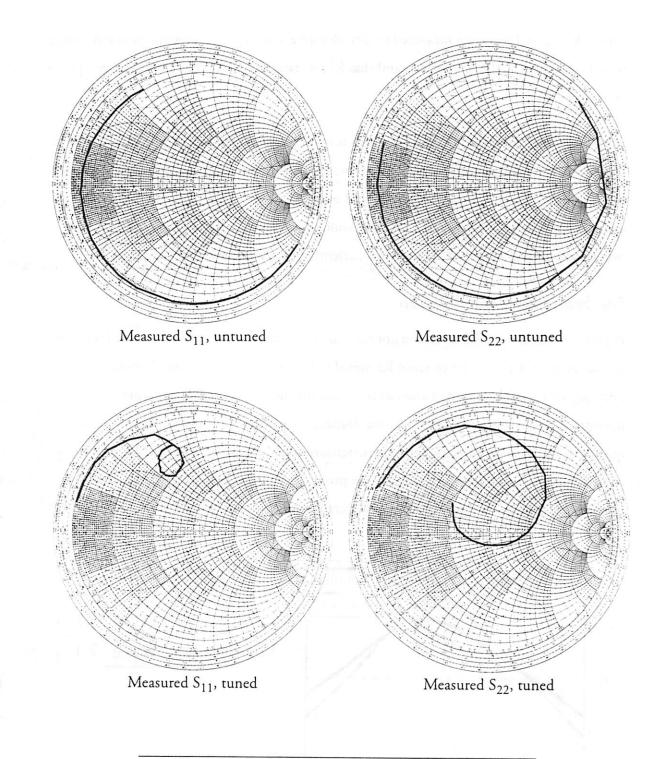

| Figure 5.11: | Measured input and output reflection coefficients                                                    |     |

| Figure 5.12: | Measured and simulated amplifier S21, noise figure                                                   | 132 |

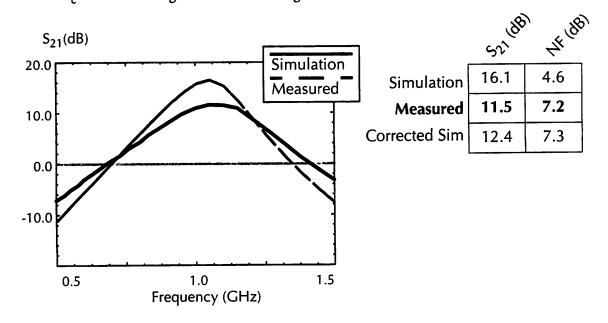

| Figure 5.13: | Sampling Demodulation                                                                                | 134 |

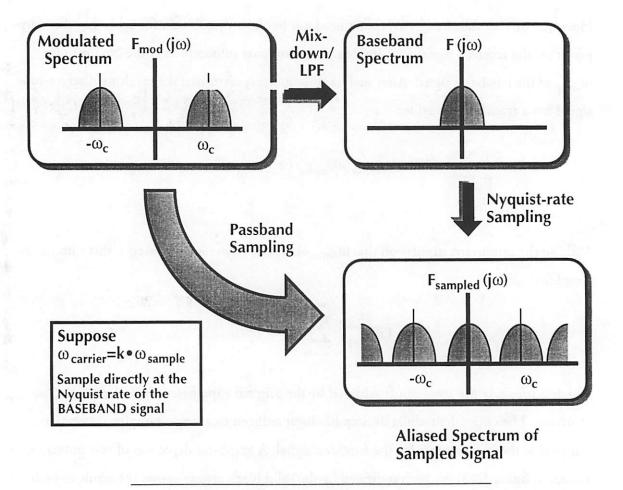

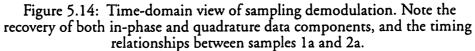

| Figure 5.14: | Time-domain view of sampling demodulation                                                            | 138 |

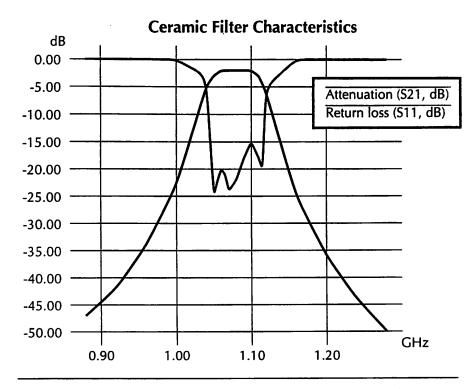

| Figure 5.15: | RF ceramic filter attenuation and return loss characteristics                                        | 160 |

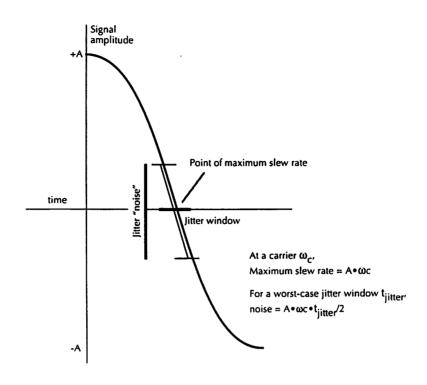

| Figure 5.16: | Translation of phase noise into additive signal noise                                                |     |

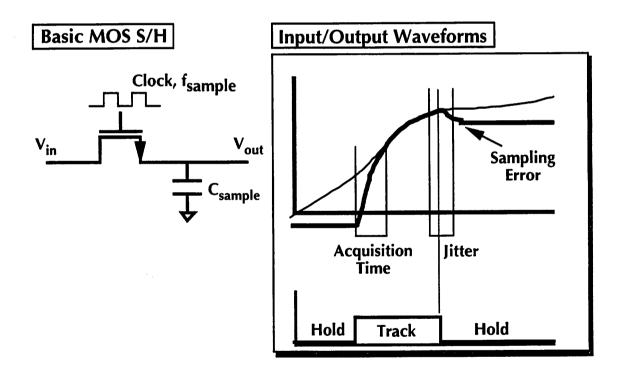

| Figure 5.17: | MOS Sample-and-Hold Characteristics                                                                  | 144 |

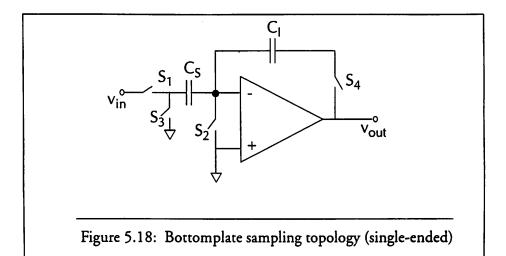

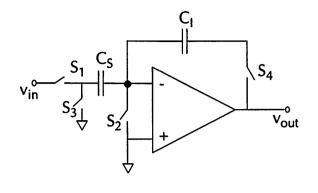

| Figure 5.18: | Bottomplate sampling topology                                                                        |     |

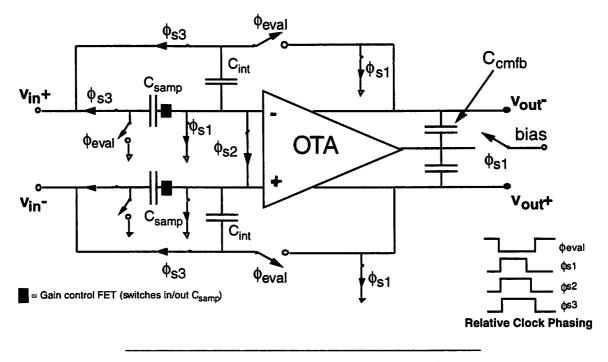

| Figure 5.19: | Variable-gain, bottomplate sampling demodulator topology                                             | 147 |

| Figure 5.20: | Sampling demodulator, track-mode configuration                                                       | 148 |

| Figure 5.21: | Track-mode linearized model of the sampling array                                                    |     |

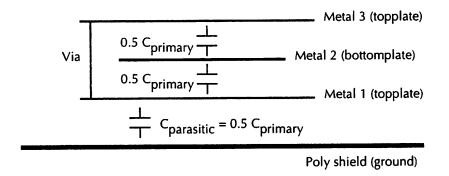

| Figure 5.22: | On-chip capacitor structure                                                                          | 149 |

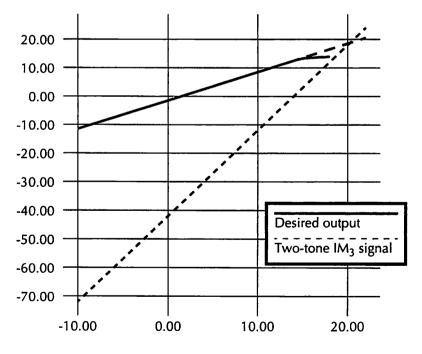

| Figure 5.23: | Simulated distortion characteristics of the sampling demodulator                                     | 170 |

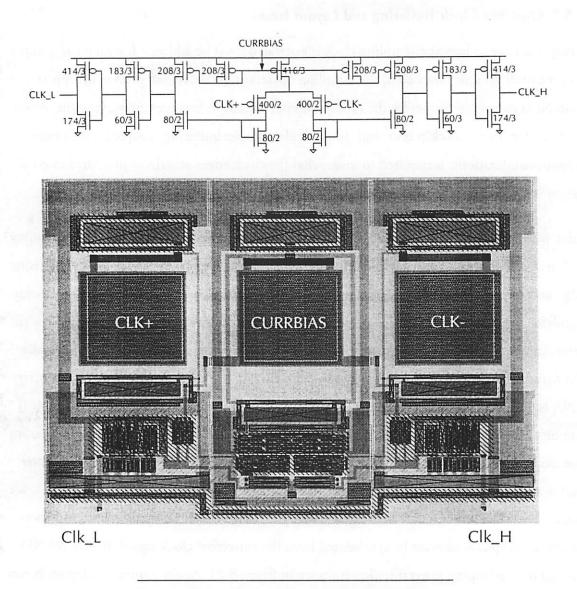

| Figure 5.24: | Schematic and layout of differential input clock buffer                                              |     |

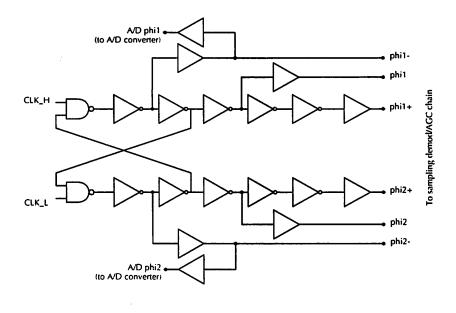

| Figure 5.25: | On-chip nonoverlapping multiphase clock generator                                                    |     |

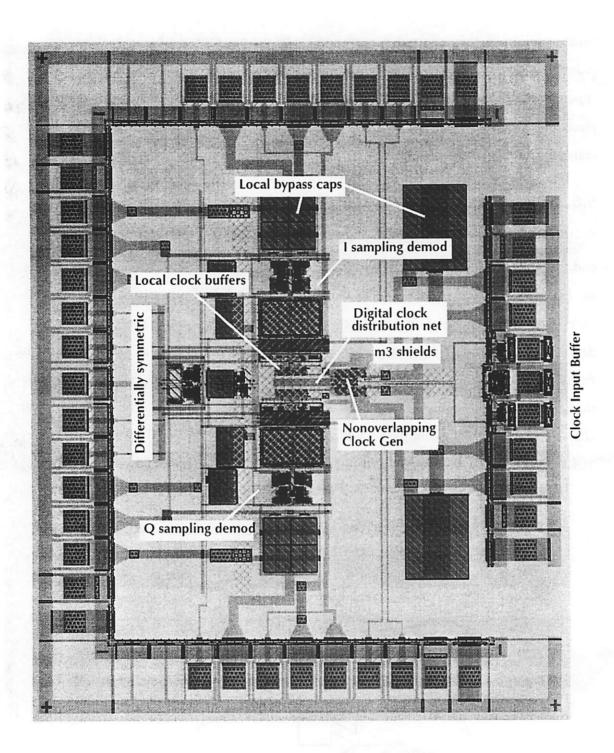

| Figure 5.26: |                                                                                                      |     |

| Figure 5.27: |                                                                                                      |     |

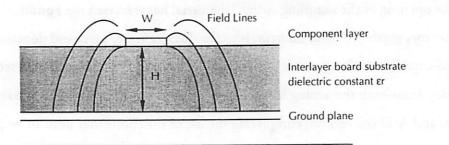

| Figure 5.28: | Available board fabrication materials                                                                |     |

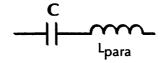

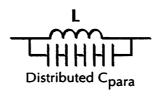

| Figure 5.29: | Parasitics in surface-mount discrete capacitors, inductors                                           | 159 |

| Figure 5.30: | Table of commercially-available surface-mount inductors                                              | 160 |

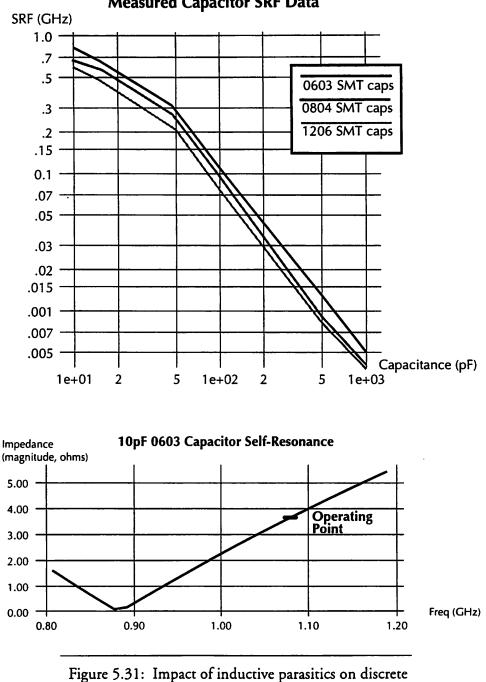

| Figure 5.31: | · · · · · · · · · · · · · · · · · · ·                                                                |     |

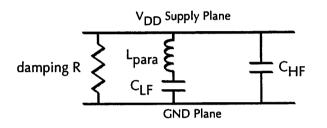

| Figure 5.32: | Board-level bypass strategy                                                                          | 162 |

| Figure 5.33: |                                                                                                      |     |

| Figure 5.34: | •                                                                                                    |     |

| Figure 5.35: | •                                                                                                    |     |

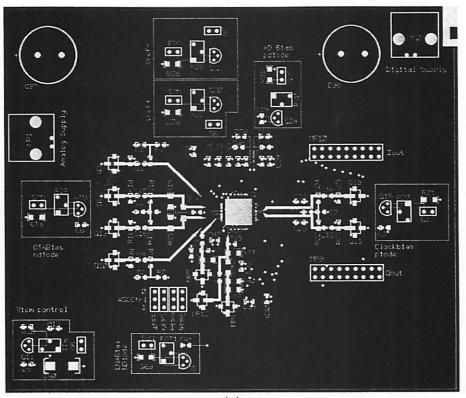

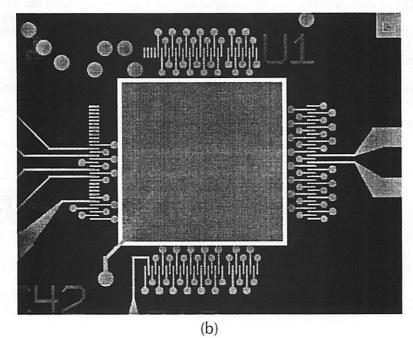

| Figure 5.36: | Fabricated board photograph                                                                          |     |

| ( | CHAPTER 6    |                                                                                     | 169 |

|---|--------------|-------------------------------------------------------------------------------------|-----|

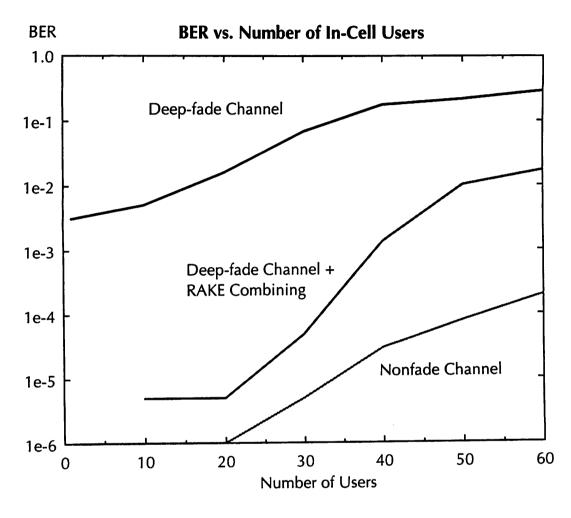

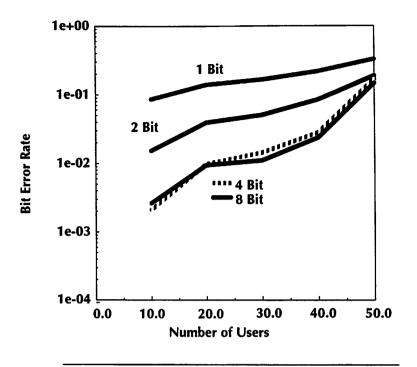

|   | Figure 6.1:  | BER vs. Number of in-cell users, as a function of                                   |     |

|   | U            | A/D bit quantization                                                                | 191 |

|   | Figure 6.2:  | Bottomplate sampling topology                                                       | 172 |

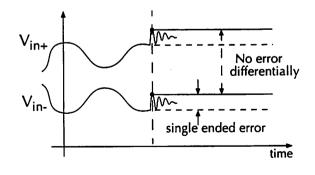

|   | Figure 6.3:  | Coupling of digital ringing into differential signal paths                          | 172 |

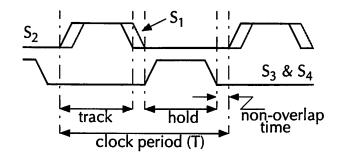

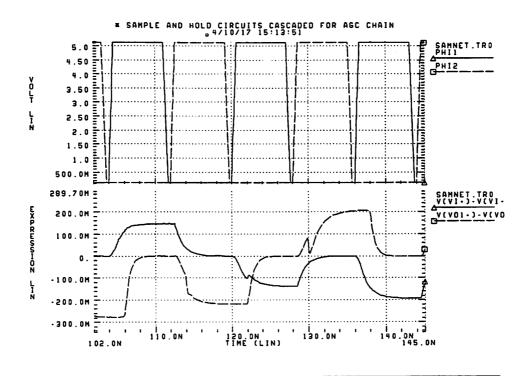

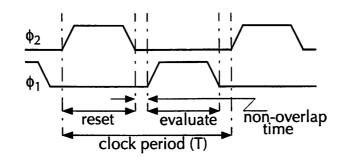

|   | Figure 6.4:  | Non-overlapping clock phases used to control sample & hold                          | 174 |

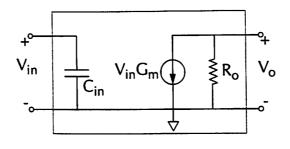

|   | Figure 6.5:  | Two-port representation of the operational transconductance amplifier               | 175 |

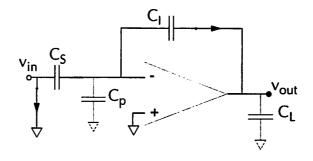

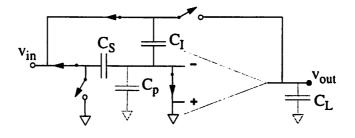

|   | Figure 6.6:  | Amplifier in hold mode (evaluation phase)                                           |     |

|   | Figure 6.7:  | Sample-and-hold topology for sampling onto C <sub>I</sub> as well as C <sub>S</sub> |     |

|   | Figure 6.8:  | Final sample-and-hold topology                                                      |     |

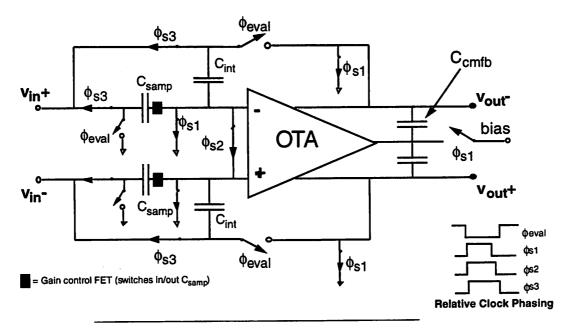

|   | Figure 6.9:  | 2 bit-2 bit pipeline with small interstage gain error                               |     |

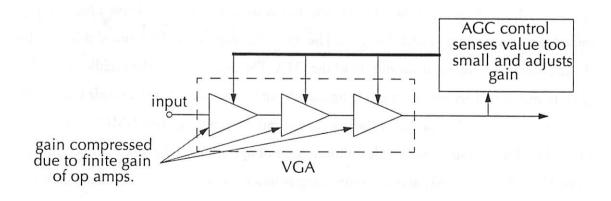

|   | Figure 6.10: | AGC compensation of gain errors.                                                    |     |

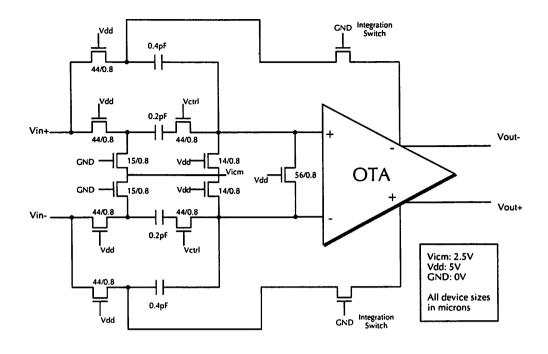

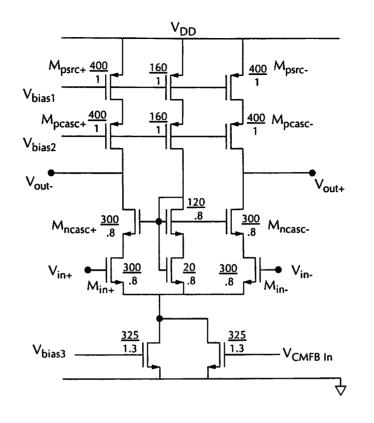

|   | Figure 6.11: | Telescopic cascode amplifier. All device sizes are in microns                       | 180 |

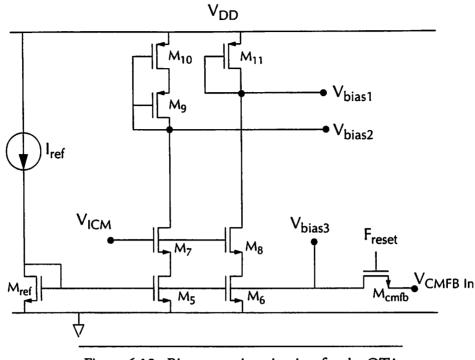

|   | Figure 6.12: | Bias generation circuitry                                                           |     |

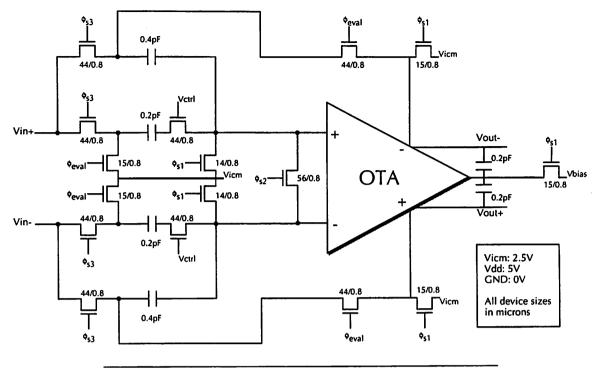

|   | Figure 6.13: | SHA switch sizings                                                                  | 184 |

|   | Figure 6.14: | VGA stage kickback transient                                                        | 185 |

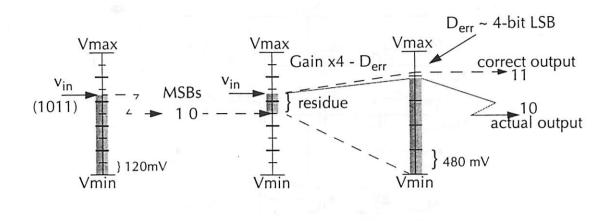

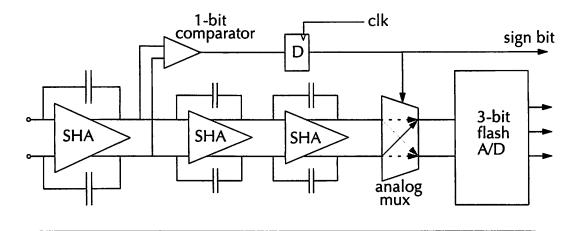

|   | Figure 6.15: | Modified 1 bit- 3 bit pipeline A/D architecture                                     | 187 |

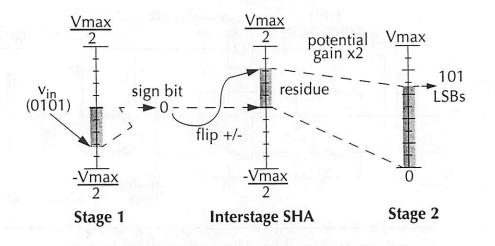

|   | Figure 6.16: | Functional illustration of the 1b-3b pipeline converter                             | 188 |

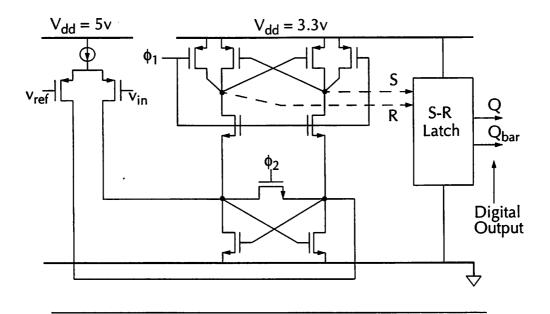

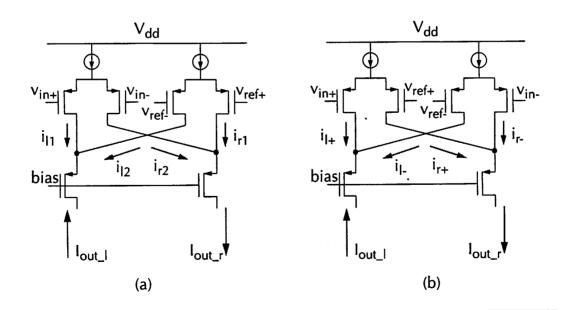

|   | Figure 6.17: | High-speed, low-offset comparator                                                   | 190 |

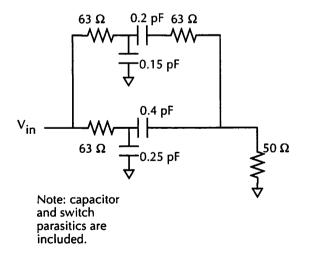

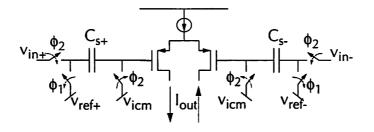

|   | Figure 6.18: | Capacitor-based input-sampling network                                              | 190 |

|   | Figure 6.19: | Differential input sampling network. (a) Standard topology;                         |     |

|   |              | (b) Modified topology employed by the 1b-3b pipeline A/D                            |     |

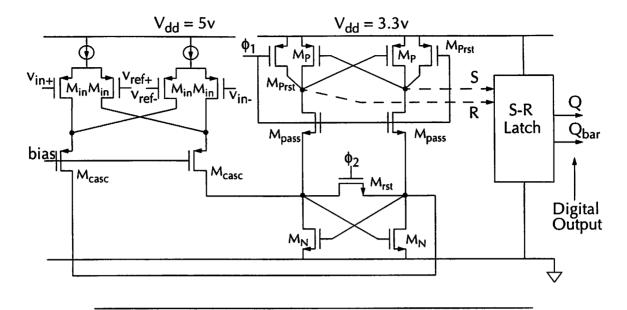

|   | -            | Final high-speed differential comparator                                            |     |

|   |              | Non-overlap clock phasing for the comparator                                        |     |

|   | -            | Comparator during reset phase of operation ( $\phi_1 = 0, \phi_2 = 1$ )             |     |

|   | Figure 6.23: | Comparator during non-overlap period ( $\phi_1 = 0, \phi_2 = 0$ )                   | 195 |

|   | Figure 6.24: | Comparator at the beginning                                                         |     |

|   |              | of the evaluation phase ( $\phi_1 = 1, \phi_2 = 0$ )                                |     |

|   |              | Effect of common-mode shift on the modified input stage                             |     |

|   |              | Comparator device sizing                                                            |     |

|   |              | Single comparator transient analysis                                                |     |

|   | •            | 3-bit flash comparator layout                                                       |     |

|   | •            | Comparator layout                                                                   |     |

|   | -            | 3-bit flash A/D converter testchip                                                  |     |

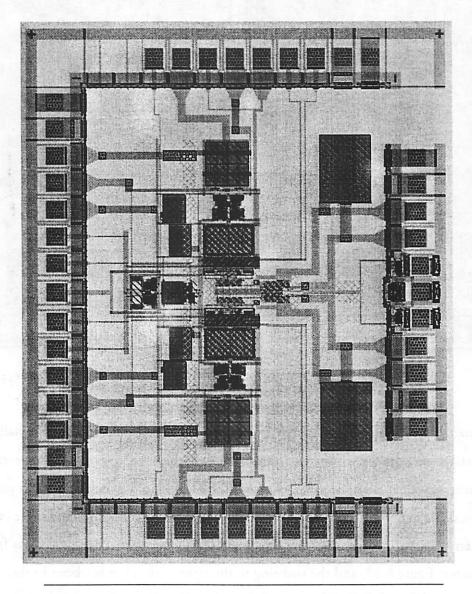

|   | -            | Sampling demodulator testchip                                                       |     |

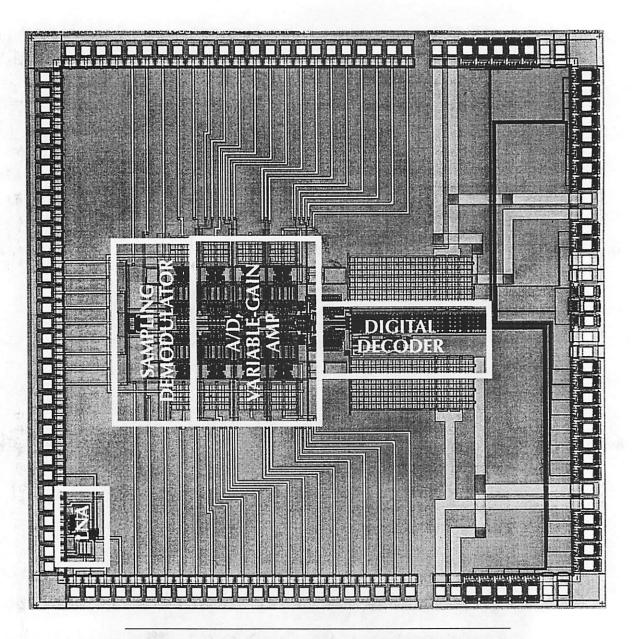

|   | •            | Full analog front-end receiver testchip                                             |     |

|   | 0            | Measured results for the analog front-end receiver testchip                         |     |

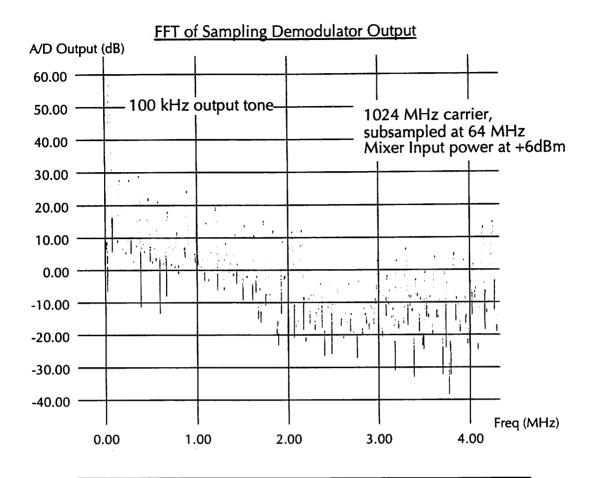

|   | -            | FFT of baseband sampling demodulator output                                         |     |

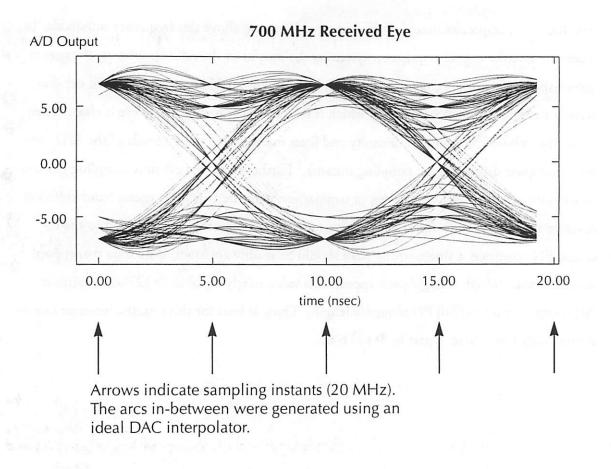

|   | Figure 6.35: | 700 MHz received eye diagram                                                        | 210 |

|   |              |                                                                                     |     |

•

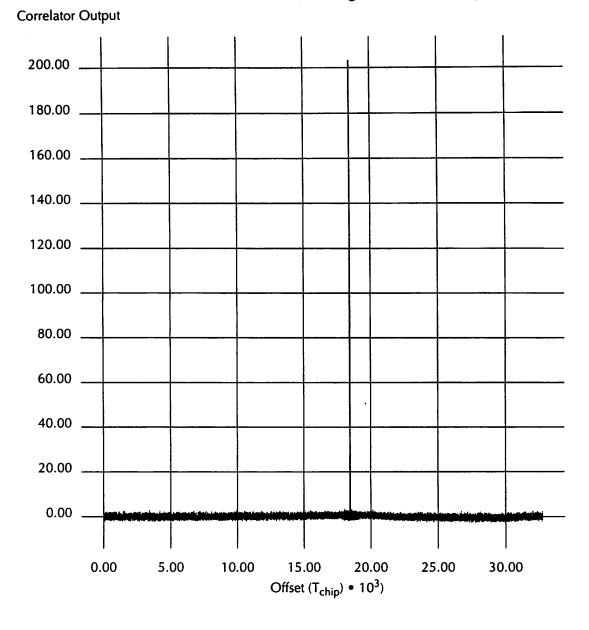

|    | Figure 6.36: | 700 MHz received data, sliding correlation test                                                                  | 211   |

|----|--------------|------------------------------------------------------------------------------------------------------------------|-------|

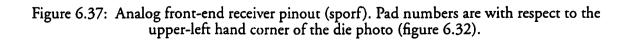

|    | Figure 6.37: | Analog front-end receiver pinout                                                                                 | 213   |

|    | Figure 6.38: | Sampling demodulator testchip pinout                                                                             | 217   |

| CH | APTER 7      |                                                                                                                  | 221   |

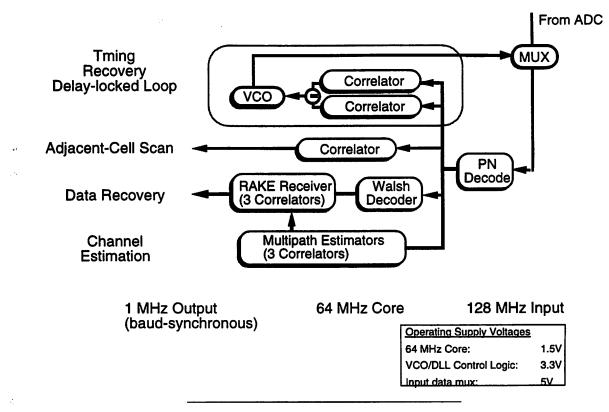

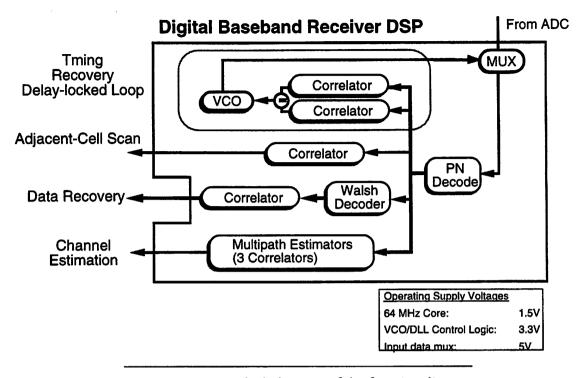

|    | Figure 7.1:  | Receiver DSP Block Diagram                                                                                       | 222   |

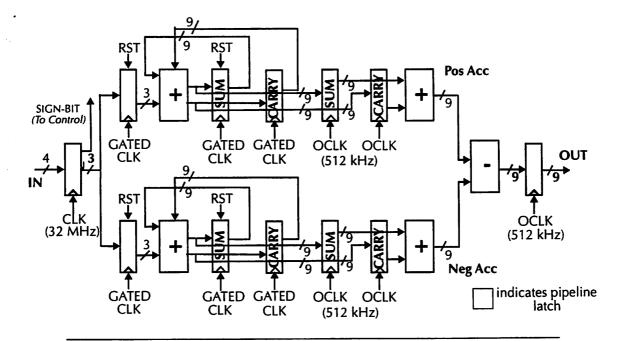

|    | Figure 7.2:  | Basic 64 MHz, length-64 correlator datapath                                                                      |       |

|    | Figure 7.3:  | Comparison of the power dissipation of two's-complement                                                          |       |

|    | -            | vs. sign-magnitude representations                                                                               | 226   |

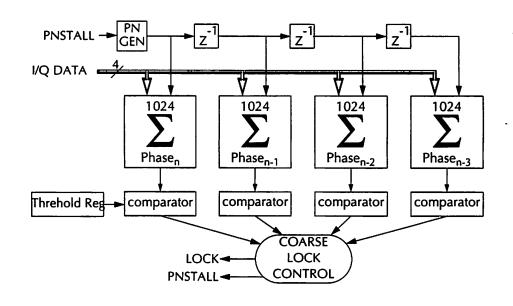

|    | Figure 7.4:  | Block diagram from coarse lock acquisition                                                                       | 227   |

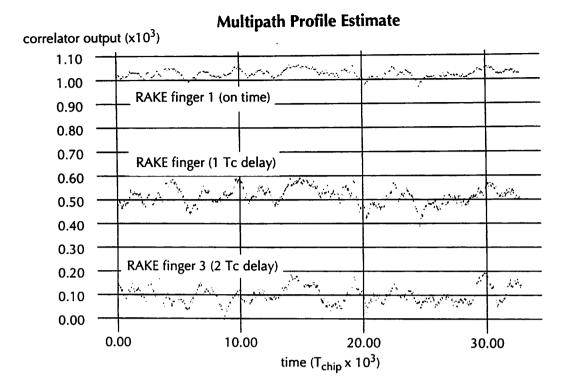

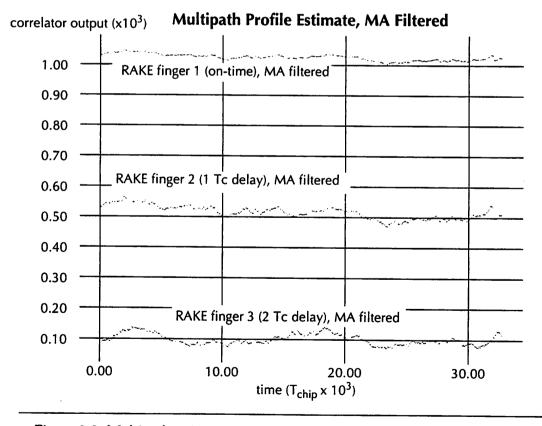

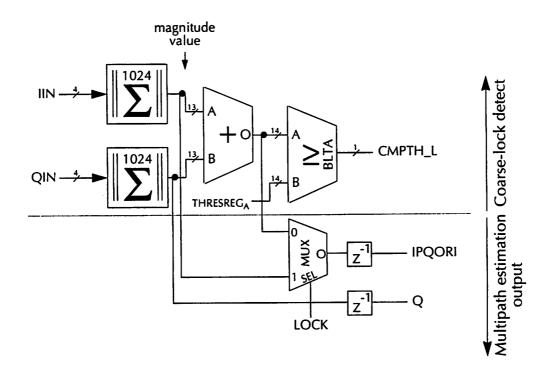

|    | Figure 7.5:  | Block diagram of a multipath correlator                                                                          | 228   |

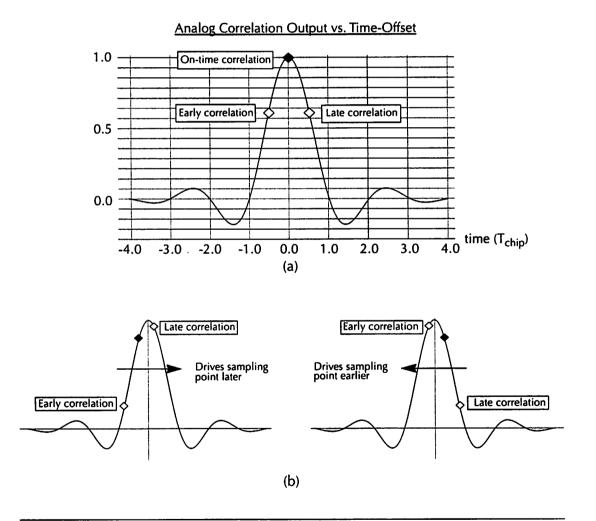

|    | Figure 7.6:  | (a) Correlator outputs as a function of time offset                                                              | າາດ   |

|    | <b>F</b> :   | (b) Early/Late phase sensing in the delay-locked loop                                                            |       |

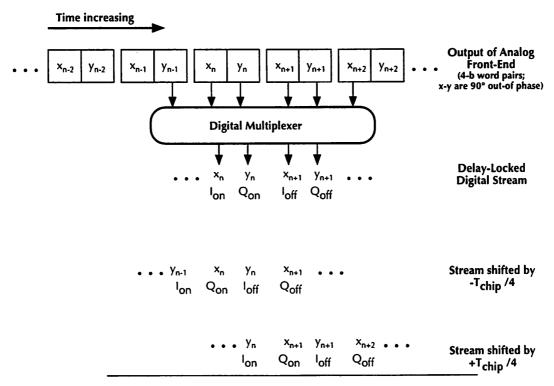

|    | Figure 7.7:  | Mapping of analog front-end outputs                                                                              |       |

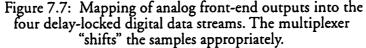

|    | Figure 7.8:  | Block diagram of DLL phase detector                                                                              |       |

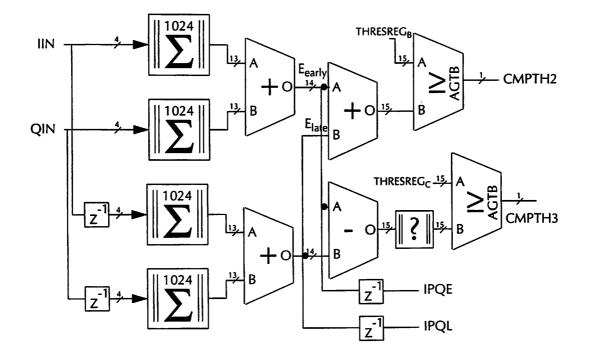

|    | Figure 7.9:  | DLL VCO (data multiplexer) block diagram                                                                         |       |

|    | Figure 7.10: | Variable-phase 64 MHz clock                                                                                      | 204   |

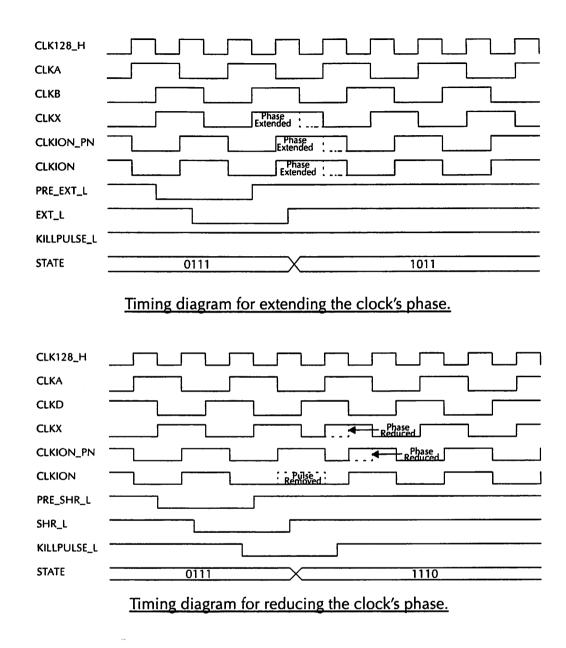

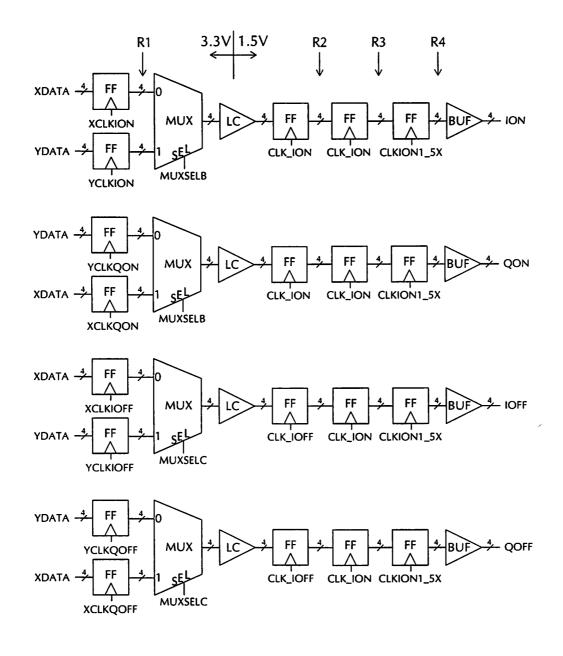

|    | Figure 7.11: | <ul><li>(a) 64 MHz variable-phase clock synthesizer.</li><li>(b) State machine to control clock phase.</li></ul> |       |

|    |              | (c) 4-phase clock generator (derives the four required clocks from C                                             | LKX)  |

|    |              | (d) Timing diagrams                                                                                              |       |

|    | Figure 7.12: |                                                                                                                  |       |

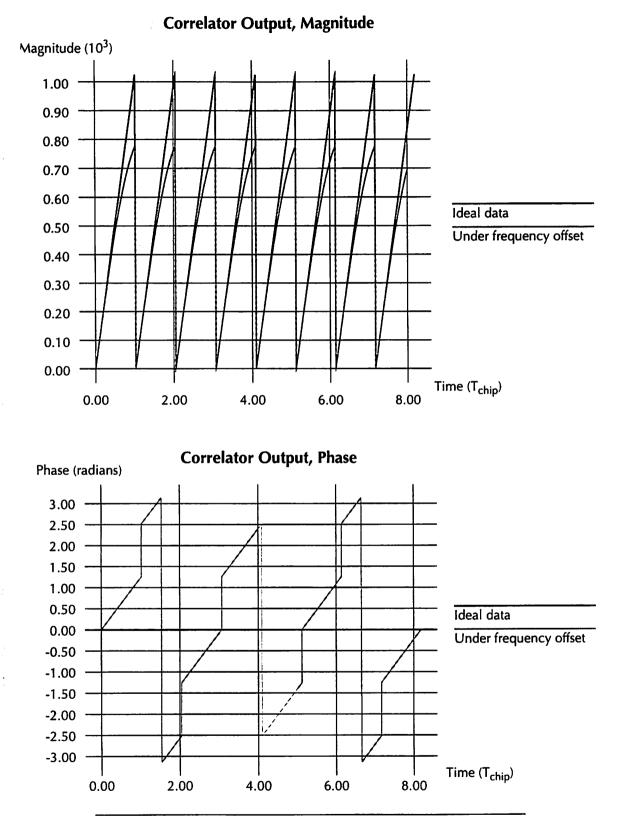

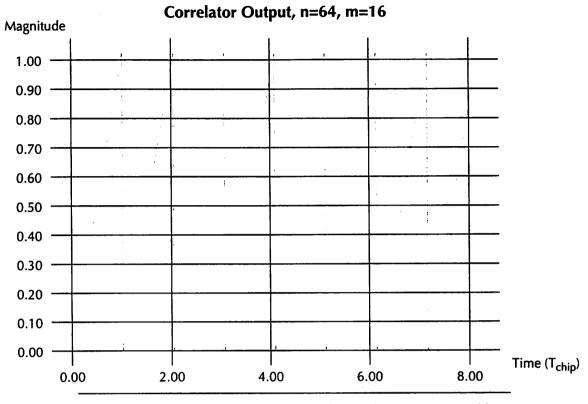

|    | Figure 7.13: | 1024-long correlation output with 25 kHz carrier offset                                                          |       |

|    | Figure 7.14: | Compensated magnitude correlator output.                                                                         |       |

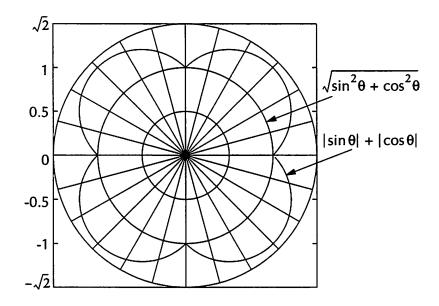

|    | Figure 7.15: | Comparison of the $L_1$ norm against the $L_2$ norm                                                              |       |

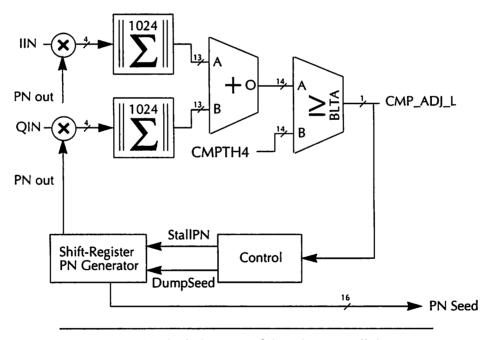

|    | Figure 7.16: | Block diagram of the adjacent-cell detector                                                                      |       |

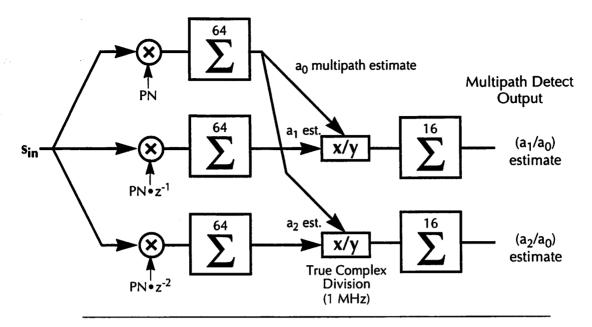

|    | Figure 7.17: | Block diagram of multipath estimator.                                                                            |       |

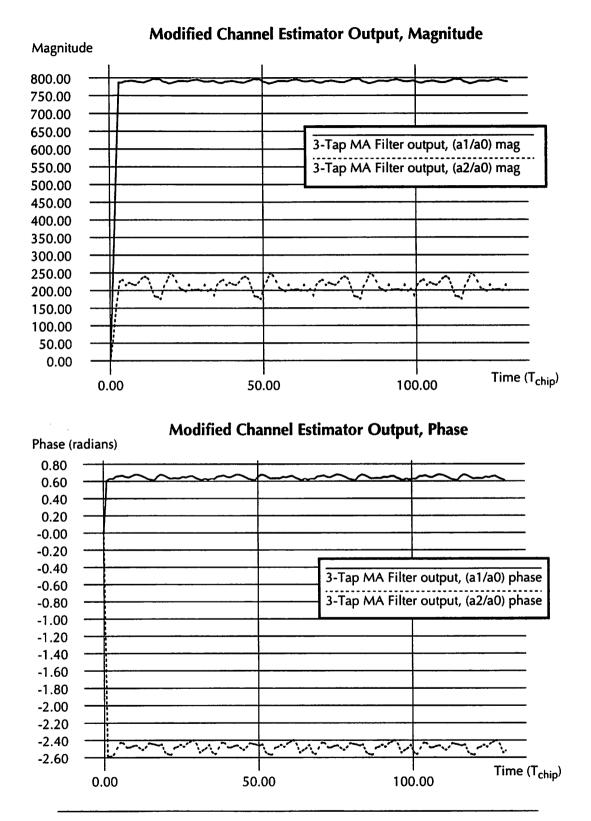

|    | Figure 7.18: | Modified channel estimator output                                                                                |       |

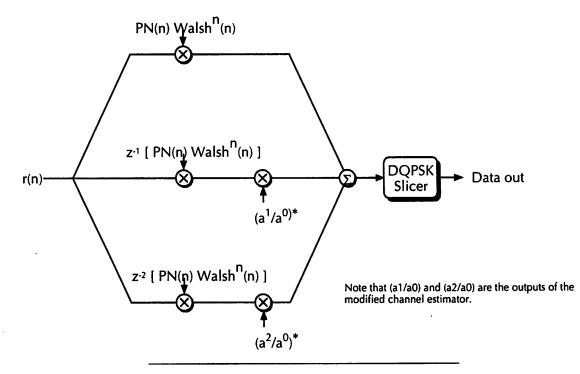

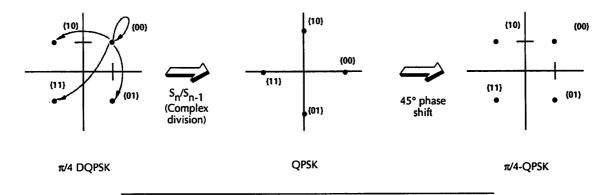

|    | Figure 7.19: | Modified RAKE receiver                                                                                           |       |

|    | Figure 7.20: | Conceptual overview of the DQPSK slicer.                                                                         |       |

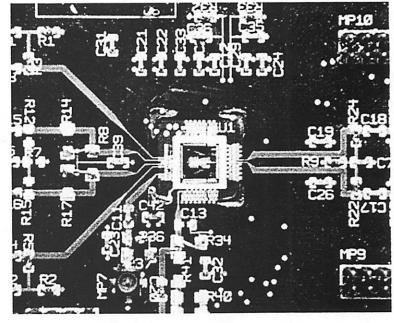

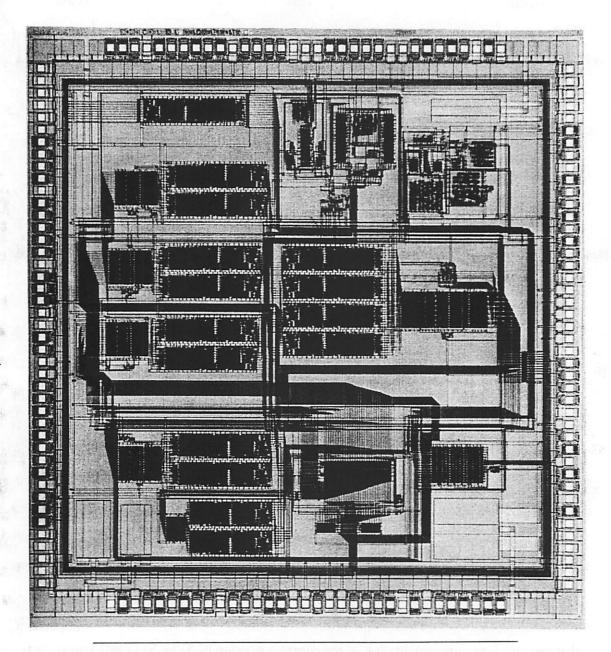

|    | Figure 7.21: | Die photo of the receiver DSP prototype testchip                                                                 | 250   |

|    | Figure 7.22: | Block diagram of the receiver prototype                                                                          | 251   |

|    | Table 7.1:   | Pinout of demodulator chip listed in order of pin number                                                         | . 273 |

|    | Table 7.2:   | Pinout for demodulator chip grouped by signal name                                                               |       |

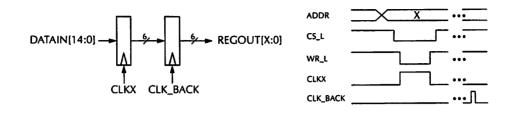

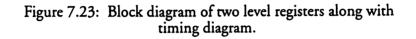

|    | Figure 7.23: | Block diagram of two level registers along with timing diagram                                                   | 256   |

|    | Table 7.3:   | Describes the demodulator's four writable registers                                                              | . 276 |

|    | Figure 7.24: | Receiver DSP output signals                                                                                      |       |

|    | Table 7.4:   | Description of the operating modes for the demodulator                                                           | . 277 |

### Acknowledgments

Otherwise known as the only place in the thesis where nontechnical information can be found. And no, I am not going to begin this with a pithy quotation, although something like "Exeunt Omnes -Shakespeare" would probably suffice, or "Exit: Stage Left - Snagglepuss". When this project was started seven years ago, in some sense its definition and scope was an act of sheer naivete: Mt. Everest doesn't look that big from about 300 miles away. However, in spite of all of the twists and turns, this point has finally been reached: I can finally say that I've more or less done what I set out to do. If nothing else, I've learned more than I can possibly imagine, that's for sure. And maybe it took about 2 years longer than I thought it would, but at least we're here.

Perhaps it's obvious, but I'll say it anyhow: it would be impossible for any single human being to finish a project of this magnitude without some serious help by some seriously talented people. And lots of help I did get. Friends, mentors, and family: all of them played a very large role in making this happen, the impact of which isn't always apparent when reading the next couple of hundred pages or so. Thus, before any technobabble and cryptic three-letter acronyms are thrown out, I'm going to take a brief moment to thank all those who have been such a wonderful part of my life (and also to get a few final digs in for all the ribbing I've gotten over the years). So, without any further adieu:

Justin, Henry, Tetiana, Eric, Elaine, and Rob: we survived undergrad at Berkeley, we survived grad at Berkeley. I guess we'll survive just about anything after this. Allyn, Ryan, Chris, and Laura – my best friends from those halcyon days of childhood: may we stay friends for another twenty years – and twenty more after that. All I can say is, "Yes, I'm finally out. So there." Drs. Wu, Wu, Lo, and Wokurka (otherwise known as Joyce, Allan, Eliza, and Laura): I think watching all of you has finally convinced me that grad school is a lot easier than med school – congrats on all of the M.D.'s! Jenny Wu: for simply being who she is. May you never stop smiling, lest the world be a much unhappier place to live. Andy Burstein, one of the best cubiclemates one could hope for. Grad school would not have been the same without his biting wit (as well as his unfailing support through cooking classes and with ext2spice). Tom Burd, the second of the best cubiclemates one could hope for. I guess I did lose that bet, didn't I? Oh, and by the way, the position of tools manager is still open. Scarlett Wu: for having such a pragmatic view of the world. And for reminding me that there are more important things in life, like taking care of white teddy bears. Jim and Amy Tso: winners in the best roommates' category. May you two have many happy years together, and hopefully I won't keep Jim up any more playing video games. Peggy Huang – just remember: "Change is good." I won't forget, so long as you don't. Edward "T" Chang: major thanks for all of the years. And I promise that we *will* end up trekking across Europe someday: count on it. And Jennie Chen: for all of the time, support, and care she's given me (not to mention being the third of the best cubiclemates one could hope for).

Kevin Zimmerman, sysadmin extraordinaire: for many, many interesting conversations, for unfailingly rising above and beyond the call of duty, and for saving my tail more times than I can count. Peggye Brown and Tom Boot: if I could give each of them a penny for every time I troubled them for something, they'd probably be bazillionaires by now. Brian Richards: for all of the times I've troubled him with silly questions about board design, tools, layout, cifplot generation, and few million other things.

To the members, past and present, of "BJGroup" and "PRGgroup": thanks for all of the support and encouragement over the years, and for the many discussions (technical and otherwise) I've had with all of you – if I had to choose, I'd have to say that they truly were the best part of being in graduate school. Greg Uehara and Cormac Conroy: both friends and mentors. You guys really taught me the practical ins and outs of analog design; I'm looking forward to working with you both again. Randy Allmon: the contributions he made during his short stay as an industrial visitor were astounding. Kevin Stone and Jim Peroulas: the digital duo. Thanks for all of the hard work on this project, and I can honestly say I hope we never have to pull another all-nighter getting a chip out again. Lastly, to the one person who made the most difference: Lapoe Lynn. All I can say is, I owe you one for saving my bacon. Big time. Without his dedication, discipline, and sheer ability, this project never would have been completed; of that, I am absolutely certain. To Professor Paul Gray: a true gentleman and scholar. Thank you for all of the time spent fielding questions, teaching about analog design, and for the patience and interest you've shown in this project over the years.

Finally, special thanks must be given to the Fannie and John Hertz Foundation, for their generous financial support on this project.

See? I said there were a lot of people. However, there are a two very special dedications that need to be made. I'm really not certain that this will do them justice, but here goes:

To my family: Mom, Dad, Amy, and Susie. Words cannot begin to describe how thankful I am to be able to call the four of you "family." I love you all dearly.

And last, but hardly least, to Professor Robert Brodersen: for the vision, for his many years of guidance and advice, and for challenging me to do this project in the first place. What he has taught me goes far, far beyond the merely technical.

Samuel Sheng 28 July 1996 PS: And now for something completely different. The following is one of the all-time great grad student survival necessities, and I highly recommend it to anyone embarking upon the quest for a graduate degree [Fields92]:

2.5C all-purpose flour, 0.5 tsp baking soda, 0.25 tsp salt, 1c firmly packed dark brown sugar, 0.5c white sugar, 1c softened unsalted butter, 2 large eggs, 2 tsp vanilla extract, 2C semisweet chocolate chips. Preheat oven to 300° F; in a medium bowl, combine flour, soda, and salt, mixing well with a wire whisk. Set aside. In a large bowl, with an electric mixer blend sugars at medium speed; add butter to form a grainy paste, scraping down the sides of the bowl. Add eggs and vanilla extract, and mix at medium speed until light and fluffy. Add the flour mixture and chocolate chips, blend and low speed until just mixed. Do not overmix. Drop by rounded tablespoons onto an ungreased cookie sheet, 2 inches apart. Bake for 22-24 minutes until golden brown (cookies should still be quite soft). Transfer cookies immediately onto a cool surface with a spatula. Yields 3.5 dozen.

# **I** Introduction

Over the past several years, wireless communications have seen dramatic advances in two distinct areas. On one hand, the demand for portable voiceband services has resulted in intense research efforts to improve performance and increase capacity through digital transmission. Such systems focus on wide-area narrowband communications, providing low-bandwidth network services to individual users in a portable fashion. On the other hand, the need for more flexible computer networks has led to the advent of wireless LAN's such as the Motorola Altair. Such systems focus on local-area wideband communications, providing networking services to individual computers but usually not easily portable.

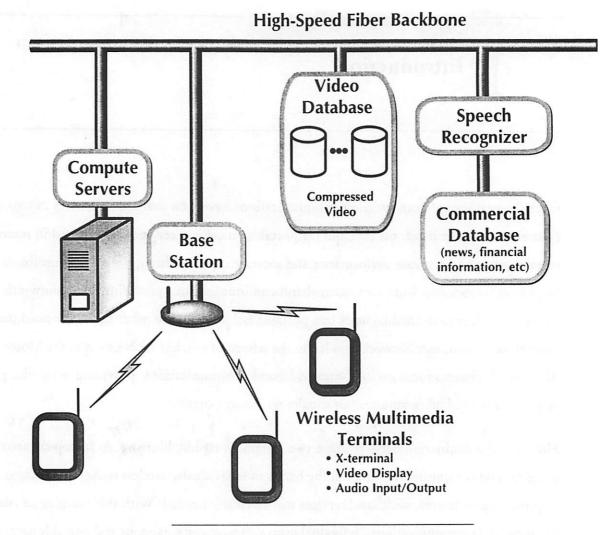

However, the distinction between these two systems is rapidly blurring. As laptop computers place mobile computing resources in the hands of individuals, wireless technologies capable of providing wide-area, wideband services will be clearly needed. With this merging of computation and communications, individual users will have instantaneous and portable access to fixed information networks via a lightweight mobile unit. Furthermore, users will be capable of transferring data to other users and accessing fixed computing resources without any constraints on where or when such access takes place. As shown in figure 1.1, the mobile unit will support a myriad of services, including full-motion digital video and high-quality audio, and combines the functionality of today's analog mobile telephones, radio pagers, and laptop personal computers.

Since portability places severe constraints on the physical weight of the terminal, the available battery power is quite limited. Thus, power minimization is crucial; power reduction in both the digital and analog hardware must be achieved. To this end, the terminal should only carry the minimum of computing resources necessary to support its functionality; user computa-

Figure 1.1: Infopad System Overview

tion should be mainly performed by large, non-portable computing facilities, with the highspeed wireless link serving as the terminal's means of accessing the fixed computation servers and data networks. Direct point-to-point wireless communication is not allowed; the link only provides the final interface into the wired data network, much as a conventional telephone handset serves as the link into the telephony system. Whereas the capability of moving massive amounts of digital data within networks already exists, the problem of easily getting data in and out of those networks is now addressed.

Although placing all computation services back in the wired network has immediate benefits in terms of reducing power consumption, it provides another advantage: data that is highly sensitive to corruption will not be transmitted over the wireless network. Existing distributed computation environments are crucially dependent on the fact that data transmitted over the network has high integrity - i.e., bit-error rates on wired Ethernet are typically on the order of 1 per 10<sup>12</sup> bits and further protection is gained by packet retransmit in the case of an error. However, on wireless networks this is not true; even after extensive error-correction coding, it is still difficult to attain error rates even remotely as low as this. User "computation" data, such as spreadsheets or simulation results, simply cannot be allowed to sustain any corruption. For wireless systems, this translates into an inordinate amount of transmission overhead in terms of coding and data retransmission to compensate. On the other hand, user "multimedia" information, such as voice and image data, is relatively tolerant of bit errors - an error in a single video frame or an audio sample will not significantly change the meaning or usefulness of the data. Thus, the portable unit described above is truly a terminal dedicated to multimedia personal communications, and not simply a notebook computer with a wireless LAN/modem attached to it.

With the shift from computation inside the mobile unit to communications outside, evidently the development of a wideband link capable of supporting the required user bandwidth becomes paramount. If the system is to support digital video, a minimum user data rate of 2 Mbps is required after error correction and coding, even utilizing the best data compression available today [MPEG90]. Due to these high bandwidth requirements, carrier frequencies must be placed in or above the low microwave bands, owing to spectrum congestion at frequencies below 1 GHz. Likewise, since one major objective of personal communications lies in granting each person individual access, a large number of users need to be accommodated by the system simultaneously, densely packed into a small physical area; continuous network access by 1 user every 4 to 10 square meters is typical for an office environment. Ostensibly, a microcellular or even picocellular reuse system must be employed to come remotely close to the required capacity [Lee89]; however, even with cellular reuse and a limited number of users per base station, the required aggregate channel data rates will be in the tens to hundreds of megabits per second. It is extremely important to note that, in this system, broadband video data is only supported in the downlink to the mobile; the uplink is used only for low-rate (32 – 128 kbps/user) speech and control data. Although the system is still full-duplex, this asymmetry must be accounted for in the design, as the bandwidth requirements for maintaining the uplink are considerably less than those for the downlink. Several commercial solutions already exist [Prox94, Symb95] that can satisfy the limited requirements of the uplink; it is the downlink especially the high-bandwidth, low-power receiver in the mobile - that presents the greatest research challenges.

Thus, the following constraints are imposed upon any transmission scheme that is to be used for such a personal communication system:

- The analog circuitry must perform reliably at variable carrier frequencies above 1 GHz, while supporting a sustained per-user data rate in excess of 2 Mbps.

- The system must support simultaneous access by a large number of users, within a small physical area.

- The mobile transceiver cannot consume excessive amounts of power, as the portable terminal must be powered by batteries, nor can it be excessively large.

Existing commercial solutions fall far short of this - the best wireless LAN's of today offer an aggregate channel data rate of 1 Mbps, with power consumption around 1 watt. The ultimate goal is to achieve a thousandfold improvement in the power-throughput ratio over existing hardware - for the receiver, 1 milliwatt per Mbps, while supporting a raw channel capacity in excess of 100 Mbps. The key contribution of this work has been the development of techniques by which such a thousandfold improvement can be achieved: system- level designs that inherently favor complex digital signal processing, and minimize analog complexity and power consumption.

### 1.1. Thesis Overview

In this thesis, the system design and implementation of the broadband downlink will be described, discussing issues ranging from low-level analog design, where a novel receiver structure using passband sampling is presented, up to the multiple access schemes utilized and its impact on the transceiver system. Since such a system will first be utilized as a step beyond conventional wireless LAN's, an indoor microcellular environment will be of primary concern, although many of the techniques are applicable to both the outdoor and indoor environments.

In chapter 2, an overview of the system itself is presented, beginning with a brief description of the indoor radio-frequency (RF) environment and its various impairments, followed by a discussion of multiple access strategies. It will be shown that a design utilizing spread-spectrum, code-division multiple access is ideally suited for such a system, not only as a means to multiplex the various users, but also to relax hardware performance requirements and to ultimately minimize power consumption in the receiver. The actual system specification follows in chapter 3, documenting design decisions made on carrier frequency, channel bandwidth, modulation, multiple access, and spread coding, along with verification by system-level simulation.

In the remainder of the thesis, the actual hardware designed to implement the link will be examined. Chapter 4 examines the base-station transmitter, including a custom integrated circuit that performs user multiplexing, spectrum spreading, and channel pulse-shaping. The analog RF transmitter section is also described, consisting of a semicustom board design to upconvert the signal for transmission. Chapters 5 and 6 describe the custom analog circuit developed for the mobile receiver, consisting of a low-noise amplifier, quadrature homodyne demodulator that utilizes passband sampling to achieve frequency conversion, a multi-stage variable-gain amplifier, and an extremely high-speed analog-to-digital converter. Low power and high integration are emphasized here, in achieving a "single-chip" monolithic CMOS solution for the analog front-end – the tremendous impact of the use of code-division multiple access will be made apparent. Following this, chapter 7 examines the digital aspects of the receiver - the custom spread-spectrum digital demodulator circuit required to perform data and timing recovery, and the low-power techniques employed in its implementation. Lastly, conclusions and a description of future work are presented in chapter 8.

# 2 Modulation, Multiple Access, and How Radio Waves Behave Indoors.

In the design of any RF communications system, three distinct factors must be considered: the propagation environment in question, the multiplexing and modulation of user data streams, and the complexity of hardware required to implement the desired link. None of these three can be allowed to dominate; for example, implementation issues place constraints on answering "How many users?" and "How much bandwidth?", whereas the choice of modulation and multiple access can have dramatic impact on the questions of "How many transistors?" or "How much power?". To being answering these questions, the system design of the high-speed downlink will be discussed in this chapter and the next. First, a description of the indoor radio propagation environment will be presented, followed by a short exposition of the available multiple-access strategies, describing the advantages and disadvantages of each. Second, the actual system specification will be given – in terms of number of users per base-station, transmit bandwidth, modulation strategies – and a discussion of how this specification was arrived at.

It should be mentioned here that verification of the various design tradeoffs was done using the U.C. Berkeley Ptolemy simulator [Buck93]; details of the simulation code are contained in the appendix following this chapter.

### 2.1. Cellular Reuse and the Indoor Propagation Channel

Since the system must support independent full-motion digital video streams to each user, spectrum usage becomes of great concern, requiring a per-user data rate of 2 Mbps. Also, this data rate is clearly not needed on a continuous basis; when regular computation tasks are being performed, such as using a word processor or a spreadsheet, the screen changes only slightly on a frame-by-frame basis and over only a small region, usually on the order of a single character or a few pixels. Hence, it is easily possible that the peak data rate required by a user is much larger than the overall time-average data rate, and minimizing overall system bandwidth consumption while supporting a large number of users accessing data simultaneously is of paramount importance. One technique, applied at the system level, is to utilize cellular networking techniques to achieve spatial frequency reuse.

The advantages in improved spectral efficiency afforded by cellular systems have long been known; having been employed extensively in present-day analog mobile radiotelephony, the large-scale cells utilized only exploit these advantages to a limited extent. By scaling down cell sizes, tremendous increases in spectral efficiency can be achieved. In this section, an analysis of these gains is presented, along with a description of the cellular concept as realized in an indoor environment. A statistical characterization of the indoor picocellular transmission environment and the corresponding model are then described.

#### 2.1.1. Cellular Systems

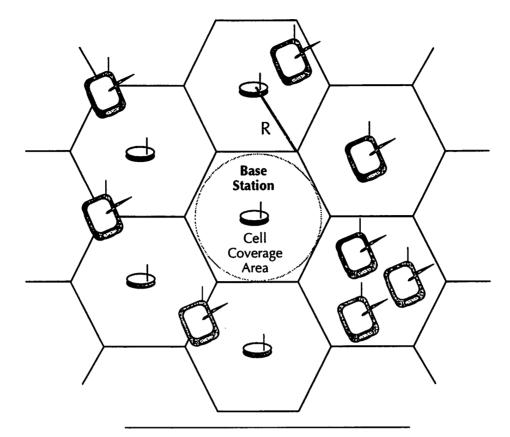

As shown in figure 2.1, a simple cellular scheme consists of dividing the entire service area for the personal communication system into "cells" of radius R, with a single base station serving all mobile users within that cell; each cell utilizes its own distinct set of system resources, different from its surrounding neighbors. As an example of such resource allocation, conventional analog cellular, being a frequency division multiple-access system, allocates different frequency bands to each cell. There is a clear correlation between the method of resource allocation and the multiple access strategy, as we will see later: in time-division multiple access, each cell could be assigned different time slots, and in code-division multiple-access, each cell could be assigned different codes.

As users move from cell to cell, their transactions with the network are "handed off" from base station to base station, reconfiguring the network dynamically as the need arises. Such reconfiguration is thus accomplished locally, since the system itself is responsible for determining where and when handoffs occur. Clearly, the complexity involved with cellular net-

Figure 2.1: Cellular Transmission System

work control is much greater than that required for a classical "umbrella" scheme, with one base antenna for the entire service area, and much of the "intelligence" of the network must be deployed within the base station and the mobile transceivers.

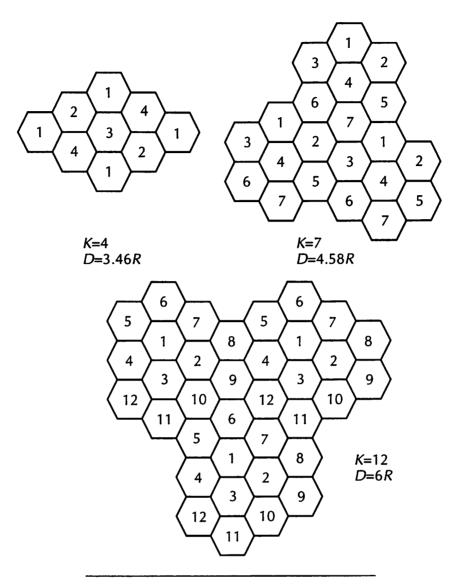

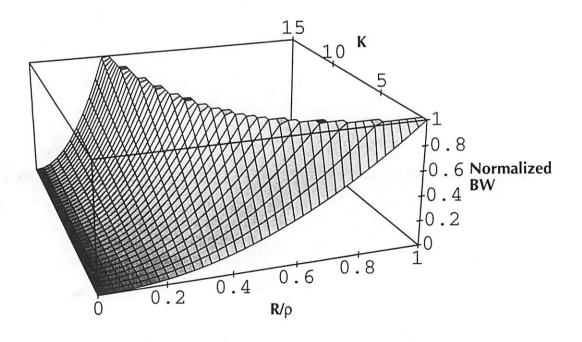

The key advantage to cellular systems is that they allow the network to achieve spatial multiple access of the users. If two cells are separated by sufficient distance, each can use the same channel resources at the same time without resulting in disastrous cochannel interference. Figure 2.2 shows several classical reuse patterns [Lee89]; such patterns are typically characterized by a reuse factor K, which represents the number of distinct sets of resources (either frequencies, or time slots, or codes) that need to be used to cover the entire service area.

From the point of view of spectrum usage, each user effectively consumes only B/N Hz of bandwidth, where B is the raw physical bandwidth needed to support transmission within a single cell, and N is the total number of users in the system. Hence, cellular systems are said

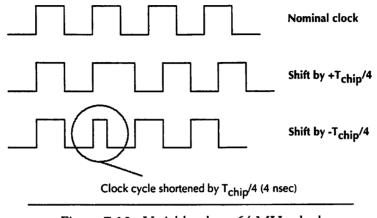

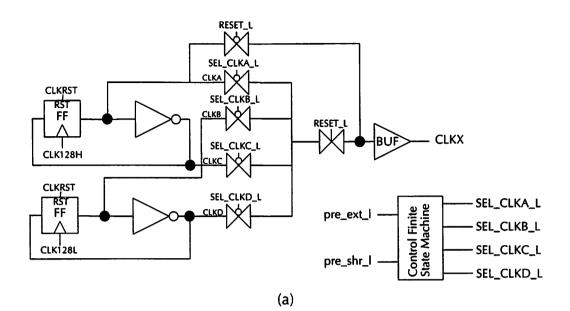

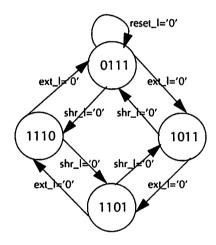

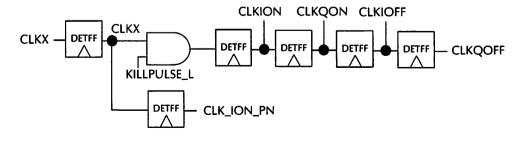

Figure 2.2: Typical Cellular Reuse Patterns