Copyright © 1997, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# STUDY OF INTERCONNECT VARIATION ON CIRCUIT PERFORMANCE

by

Zhihao Jeff Lin

Memorandum No. UCB/ERL M97/80

.

17 October 1997

# STUDY OF INTERCONNECT VARIATION ON CIRCUIT PERFORMANCE

by

Zhihao Jeff Lin

Memorandum No. UCB/ERL M97/80

17 October 1997

# **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

#### Abstract

#### Study of Interconnect Variation on Circuit Performance

by Zhihao Jeff Lin

Electrical Engineering and Computer Sciences University of California at Berkeley

Professor Costas J. Spanos, Advisor

Deep submicron technology makes interconnect one of the main factors determining the circuit performance. Previous work shows that interconnect parameters exhibit a significant amount of spatial variation. In this work, we developed approaches to study the influence of the interconnect variation on circuit performance and to evaluate the circuit sensitivity to interconnect parameters. First, an accurate interconnect modeling technique is presented, and an interconnect model library is developed. Then, we explore an approach using parameterized interconnect models to study circuit sensitivity via a ring oscillator circuit. Finally, we present another approach using statistical experimental design techniques to study the sensitivity of a large and complicated circuit to interconnect variations.

# **Table of Contents**

| 1 | Introduction                                                      |

|---|-------------------------------------------------------------------|

|   | 1.1 Background and Motivation                                     |

|   | 1.2 Thesis Overview                                               |

|   | 1.3 Thesis Organization                                           |

|   |                                                                   |

| 2 | Interconnect Modeling                                             |

|   | 2.1 Introduction                                                  |

|   | 2.2 Background                                                    |

|   | 2.2.1 Interconnect Trends                                         |

|   | 2.2.1.1 Scaling Effects on Interconnect                           |

|   | 2.2.1.2 Coupling Capacitance and Its Effects                      |

|   | 2.2.2 Constructing Equivalent Circuits to Interconnect Structures |

|   | 2.2.2.1 The Nature of the Equivalent Circuit                      |

|   | 2.2.2.2 The Values of the Circuit Elements                        |

|   | 2.3 Interconnect Model Library                                    |

|   | 2.4 Numerical Simulation                                          |

|   | 2.5 Curve-fitting Technique                                       |

|   | 2.5.1 Linear least square regression analysis                     |

|   | 2.5.2 Determining the Necessary Model Terms                       |

|   | 2.6 Example                                                       |

|   | 2.7 Summary and Conclusion                                        |

|   |                                                                   |

| 3 | Sensitivity Study                                                 |

|   | 3.1 Introduction                                                  |

|   | 3.2 Previous Work                                                 |

|   | 3.3 Methodology                                                   |

|   | 3.3.1 Interconnect Wire Model                                     |

|   | 3.3.2 Device Model                                                |

|   | 3.3.3 Circuit Description                                         |

|   | 3.3.4 Circuit Simulation and Optimization                         |

|   | 3.3.5 Statistical Circuit Simulation                              |

|   | 3.3.5.1 Monte Carlo Simulation                                    |

|   | 3.4 Case study: Ring Oscillator Circuit                           |

|   | 3.4.1 Circuit Model                                               |

|   | 3.5 Results and Analysis                                          |

|   | 3.6 Summary and Discussion                                        |

|   |                                                                   |

| 4 | Sensitivity Study Using Statistical Experimental Design           |

|   | 4.1 Introduction                                                  |

|   | 4.2 Methodology                                                   |

|   | 4.3 Screening Experiment                                          |

•

|   | 4.3.1 Experimental Design                         | 6 |

|---|---------------------------------------------------|---|

|   | 4.3.2 Screening Experiment Results and Discussion |   |

|   | 4.3.3 Circuit Loading Analysis                    |   |

|   | 4.4 Second-phase Experiment Design                |   |

|   | 4.5 Central Composite Design and Model Building   |   |

|   | 4.6 Conclusion                                    |   |

| 5 | Conclusion                                        | 7 |

|   | 5.1 Summary                                       | 7 |

|   | 5.2 Future Work                                   | 8 |

|   | References                                        | 9 |

| A |                                                   | 2 |

| B |                                                   | 4 |

| С |                                                   | 0 |

.

.

# **List of Figures**

| Figure 2.1. A simple interconnect model                                                  | .7   |

|------------------------------------------------------------------------------------------|------|

| Figure 2.2. Multi-level metal interconnect cross-section                                 | . 9  |

| Figure 2.3. Tighter pitch and higher height-to-width ratio of new technology             |      |

| Figure 2.4. The coupling capacitance effect                                              | 12   |

| Figure 2.5. Simulation models of interconnect wires                                      | 15   |

| Figure 2.6. The cross section of an interconnect structure                               |      |

| Figure 2.7. Interconnect Modeling Flow.                                                  |      |

| Figure 2.8. Capacitance C <sub>22</sub> versus metal width W with H, T, and S fixed      | 27   |

| Figure 2.9. Capacitance $C_{22}^{22}$ versus inter-wire spacing S with W, H, and T fixed |      |

| Figure 2.10.C <sub>22</sub> versus metal thickness T with W, H, and S fixed              | 28   |

| Figure 2.11.C <sub>22</sub> versus ILD thickness H with W, T, and S fixed.               |      |

| Figure 2.12. Residual of regression model of C <sub>22</sub> as a function of H, W, T, S |      |

| Figure 2.13. Absolute residual of regression model of C <sub>22</sub>                    |      |

| Figure 2.14. Fitted values against simulated data of C <sub>22</sub>                     |      |

| Figure 2.15.Normal plot for residuals.                                                   | 30   |

| Figure 2.16.C <sub>12</sub> versus metal thickness                                       | 31   |

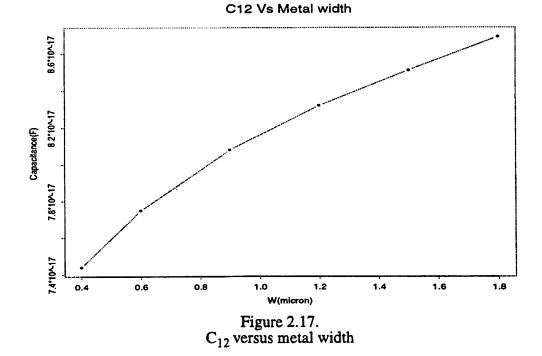

| Figure 2.17.C <sub>12</sub> versus metal width                                           | 31   |

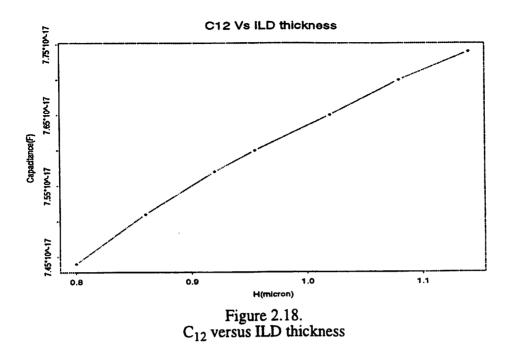

| Figure 2.18.C <sub>12</sub> versus ILD thickness                                         | 32   |

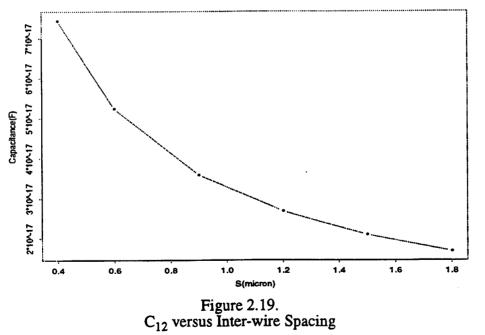

| Figure 2.19.C <sub>12</sub> versus Inter-wire Spacing                                    | 32   |

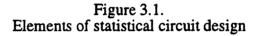

| Figure 3.1. Elements of statistical circuit design.                                      |      |

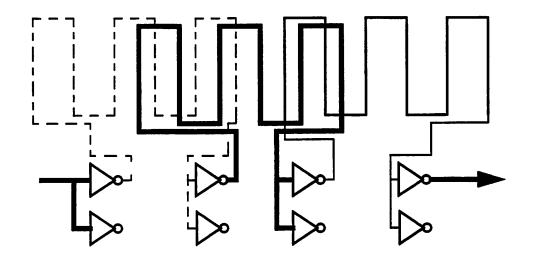

| Figure 3.2. Overview of sensitivity study                                                | 38   |

| Figure 3.3. Circuit diagram of a ring oscillator.                                        | 41   |

| Figure 3.4. Ring oscillator circuit is composed of odd number of inverters               | . 42 |

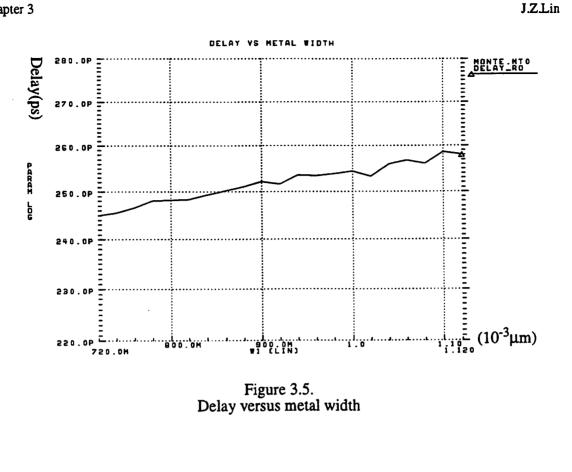

| Figure 3.5. Delay versus metal width                                                     | . 44 |

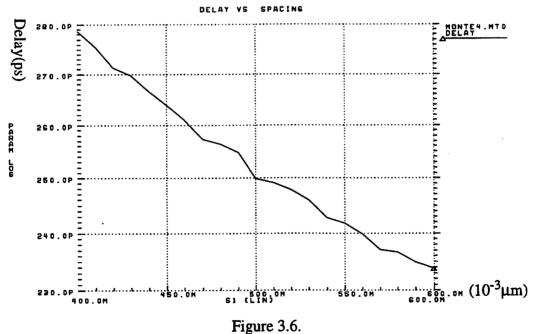

| Figure 3.6. Delay versus inter-wire spacing                                              |      |

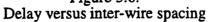

| Figure 3.7. Delay versus ILD thickness                                                   | . 45 |

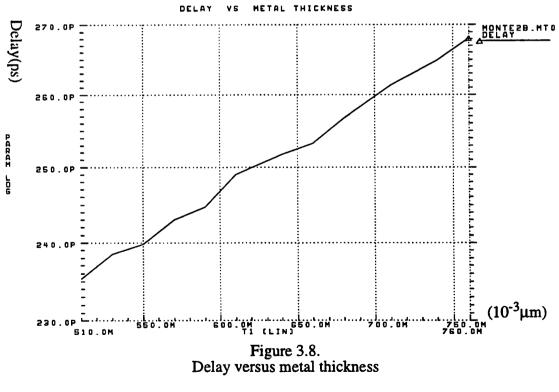

| Figure 3.8. Delay versus metal thickness                                                 |      |

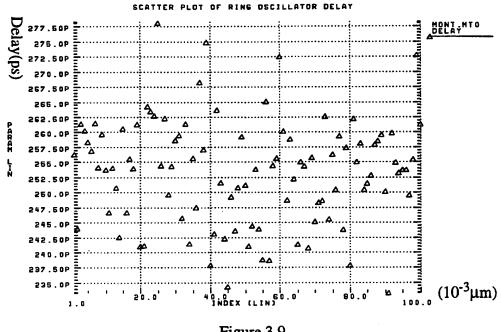

| Figure 3.9. Scatter plot of Monte Carlo simulation                                       | . 47 |

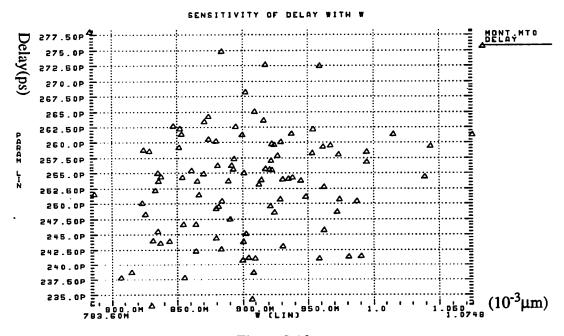

| Figure 3.10.Delay sensitivity to metal width                                             | , 47 |

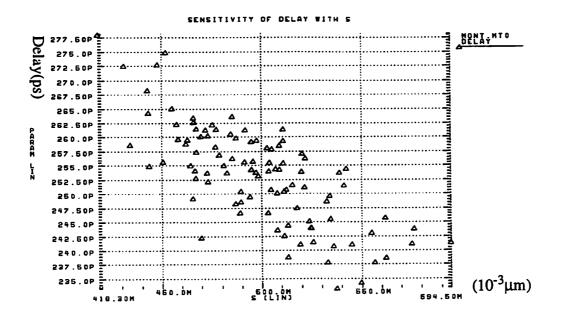

| Figure 3.11.Delay sensitivity to inter-wire spacing                                      |      |

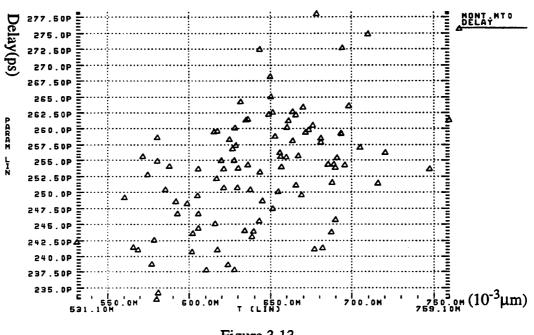

| Figure 3.12.Delay sensitivity to ILD thickness                                           |      |

| Figure 3.13. Delay sensitivity to metal thickness                                        |      |

| Figure 3.14.Delay sensitivity to unit-length inter-wire coupling capacitance             | . 49 |

| Figure 3.15. Sensitivity of delay to unit-length plate capacitance                       |      |

| Figure 3.16. Sensitivity of delay to unit-length wire resistance                         |      |

| Figure 4.1. The methodology of sensitivity study using statistical experimental design . |      |

| Figure 4.2. Illustration of multi-layer interconnect structure                           | . 56 |

•

.

• .

.

# **List of Tables**

| Table 2.1. | Scaling Properties of Device and Interconnect Parameters                         | . 9  |

|------------|----------------------------------------------------------------------------------|------|

| Table 2.2. | Effects of Scaling on Interconnect                                               | 10   |

| Table 2.3. | Input File to Numerical Extractor for the structure depicted in Fig.2.6          | 21   |

| Table 2.4. | Statistics of Modeling Result of C <sub>22</sub> Model                           | 26   |

| Table 3.1. | Sensitivity Simulation Results                                                   | 46   |

| Table 4.1. | Design Matrix of Screening Experiment (unit: µm)                                 | 57   |

| Table 4.2. | Results of Screening Experiment                                                  | . 58 |

| Table 4.3. | Significance Test Results of the Interaction Term, h <sub>2</sub> h <sub>3</sub> | . 59 |

| Table 4.4. | Capacitance loading distribution of the multiplier in the nominal case           | . 62 |

| Table 4.5. | Design Matrix of Second-phase Experiment                                         | . 63 |

| Table 4.6. | Screening of the Main Factors                                                    | . 63 |

| Table 4.7. | Delay Sensitivity to Main Factors.                                               | . 64 |

|            | Additional "Star Point" Recipes                                                  |      |

|            | ANOVA table of regression model.                                                 |      |

|            | Significance Test Result of Main Factors                                         |      |

# Acknowledgments

First, I would like to express my most heartfelt gratitude and appreciation to my research advisor, Professor Costas J. Spanos, for his encouragement, guidance and lasting support in every way. I am grateful of my study experience here in the Berkeley Computer-Aided Manufacturing (BCAM) group. I would also like to thank Professor Andrew Neureuther for his interest in this work and serving as the second reader of this thesis.

I would like to give special thanks to Dr. Linda Milor for her guidance and help throughout this work.

Thanks also give to Dr. Jue-Hsien Chern and TMA Inc. for supplying the interconnect extraction software Raphael.

A warm "thanks" goes out to the past and present members of the Berkeley Computer-Aided Manufacturing (BCAM) group who helped make the experience worthwhile: Roawen Chen, Anna Ison, Nickhil Jakatdar, Greg Luurtesema, Xinhui Niu, Manolis Terrovitis, Haolin Zhang, and Dongwu Zhao.

This work was supported by the Semiconductor Research Corporation (SRC), the state of California Micro program, and participating companies (Advanced Micro Devices, Atmel Corporation, Lam Research, National Semiconductor, Silicon Valley Group, Texas Instruments and AME.).

# **Chapter 1 Introduction**

## **1.1. Background and Motivation**

The continuously increasing scale of integration used in the design and processing of integrated circuits has drawn special attention toward interconnect effects. As the minimum feature size in VLSI systems drops to 0.25 micron and below, interconnect characteristics have become limiting factors on performance, since the time constant associated with interconnect is scaled by a smaller factor compared to those of devices. Future chip complexity and speed advances will depend on the ability to model the electrical behavior of interconnect in an accurate and efficient fashion.

Critical path delays in circuits depend upon the interconnect as well as on the device parameters. The effects of device parameter variations have been widely studied [12] [14] [15] [16]. However, these simulations currently do not take into account the effects of interconnect parameter variations. As a result, the yield estimation and circuit optimization based on these studies may not be able to provide accurate results in current and future technologies, where more and more significant portions of path delays will result from interconnect.

An IC process is a series of steps used to manufacture a semiconductor product which turns a bare silicon wafer into packaged ICs. These steps include the introduction and redistribution of impurities into the silicon, the growth or deposition of layers on the wafer and the patterning of these layers. Finally, the wafer is tested and the die on the wafer is separated and put into packages. Each step of this process requires specific materials and settings on the manufacturing equipment in order to make the circuit functional and meet the performance specifications to be sold by the manufacturer. Process parameters refer to

1

#### Chapter 1

measurable quantities which characterize the results of these steps. These performance specifications will be referred to as the circuit performances.

However, as with any manufacturing process, there are uncontrolled variations in the process which cause product performance to vary. Furthermore, process or equipment variability is not necessarily falling at the same pace as the minimum feature size. This is because while decreasing nominal critical dimensions, processing technologies are being pushed to the limit. So, as device and interconnect dimensions continue to shrink and wafer and die size increase, process uniformity and consistency become a big concern. In [2], it is shown that both layout and process parameters exhibit a significant amount of spatial variation. Most of this variation is deterministic, so there is hope to compensate for it using proper modeling and design techniques.

With current technology, the impact of interconnect parameter variations on signal delays may already be quite significant. Thus, it becomes necessary to comprehend and anticipate the effects of interconnect parameter variation in the design process. Specifically, a methodology to asses the impact of radom and systematic variations in interconnect parameters to circuit performance must be developed.

A modeling framework to study the sensitivity of circuit performance to interconnect parameter variations will allow circuit designers to meet timing targets while taking into account the random and systematic source of interconnect parameter variations. It will also help the process designers to design new technologies while taking the sensitivity information into consideration. Finally, the sensitivity study results will help make the circuit more robust against the variation.

The success of the IC industry has in part been due to the use of a design style, first formalized by Mead and Conway [11], which isolates IC designers from detailed consideration of the technology and the manufacturing process. However, the increasing cost and complexity of a modern IC manufacturing line are necessitating increased interaction among design, manufacturing and technology to deliver profitable products in a timely fashion. Design for Manufacturability (DFM) techniques strive to impact the design and manufacture of an IC product in light of a specific technology and manufacturing processes in order to improve the manufacturability of the product. Indeed, the term "Manufactura-

#### J. Z. Lin

bility" implies the integration of process design, circuit design and manufacturing activities.

The focus of DFM has traditionally been on yield prediction and optimization. The yield of an IC is the fraction of manufactured parts which are functional and meet the specifications. Yield can be further decomposed into the fractions of parts sold at different performance levels, reflecting the distribution of product performance caused by process variation. Previous work in DFM analyzed the distribution of circuit performance, and optimized the circuit design or fabrication process for maximum yield [18] [19] [20]. This is also the underlying motivation for this work.

Also, DFM activity, and in particular enhanced interaction between process, design and manufacturing, can decrease the time required to reach high yield levels, or improve the learning curve. This results into significant and competitive advantages.

Overall, the goal of this thesis is to address the problem of interconnect variation, look for a methodology to model interconnect wires, and develop DFM approaches to quantify and investigate interconnect parameter variations on circuit performance under current and future technologies. The ultimate objective is to facilitate optimal circuit and process design, reduce time-to-yield, and improve the final yield.

### **1.2.** Thesis Overview

Two approaches to study the circuit sensitivity to interconnect parameter variations are developed in this thesis. The first approach is based on a parameterized interconnect model library. The parameterized interconnect models allow us to manipulate interconnect parameters, and to generate a circuit description that is suitable for performance sensitivity study. The second approach uses statistical experimental design techniques to analyze complicated circuits via simulation experiments. The first approach is illustrated with the help of ring oscillation circuits, and the second approach is illustrated on a large multiplier circuit.

# **1.3. Thesis Organization**

Chapter 2 introduces some background on interconnect modeling techniques, and discusses the related issues of interconnect modeling for the purpose of sensitivity study.

#### Chapter 1

A methodology to model interconnect wires and generate the model library was developed based on numerical simulation of interconnect structures. With the models developed in Chapter 2, Chapter 3 shows how a parameterized circuit description can be generated and used for statistical circuit performance simulation. The purpose of the sensitivity study and its related aspects are discussed in detail. The results from the case study of a ring oscillator are presented. In Chapter 4, the advantages and disadvantages of the approach developed in Chapter 3 are discussed and a complementary approach using statistical design techniques is proposed, which was explored using a shift-and-add multiplier. Chapter 5 concludes the thesis with a summary and suggestions for future work.

# **Chapter 2 Interconnect Modeling**

## 2.1. Introduction

The design and development of next-generation electronic products are driven by an increasing demand for greater functionality, higher performance, and shorter design-tomanufacturing cycle time. So the integrated circuit (IC) design trend is toward reduced line widths, larger die size, greater number of interconnect layers and higher clock frequencies. As a consequence, the electrical characteristics of the interconnections are becoming important factors in the behavior of integrated circuits. By mid 1997, the feature size was as small as 0.25 micron and it has been predicted that it would decrease to 0.18 micron soon afterwards. Shrinking silicon geometries affect the electrical properties of the interconnect, and this has a corresponding effect on the IC performance. As a result, factors which have an insignificant effect when the feature size was at one micron or larger, become significant impediments to performance at 0.25 micron and below.

Because transistor sizes are shrinking faster than interconnect distances between transistors, wiring delays dominate the total gate to gate delay. This factor is getting more pronounced as technologies change. For instance, at 2 micron, 80% of the delay is due to transistor or gate delay, and only 20% of the delay is attributed to the wires, that is, the speed of a chip was largely determined by the inherent capacitance of the transistors on the chip, while the effect of interconnections was relatively unimportant. In deep submicron designs, however, interconnect delay may account for 80% to 90% of the total delay for some very high performance circuits, and it plays an ever greater role in the timing of IC chips. Therefore, one must be able to assess the impact of interconnections on signal delay in order to accurately evaluate the timing of current and future integrated circuits. In order to understand and account for interconnect effects in the design process, it is necessary to model the interconnection and extract its parasitic parameters. It is essential that the electrical behavior of interconnect is modeled accurately. The accuracy of interconnect models is the very basis of achieving meaningful predictions of circuit behavior and obtain reliable sensitivity evaluations. The models should also be suitable for statistical circuit simulation and sensitivity analysis, which is the purpose of this work.

One approach to interconnect modeling is to construct an equivalent electrical circuit representation. The equivalent circuits that represent the interconnections can be combined with the equivalent circuits that describe the active devices, and the behavior of the entire circuit can be analyzed with a circuit simulator such as HSPICE.

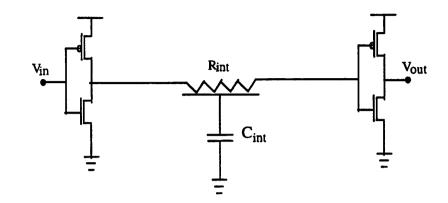

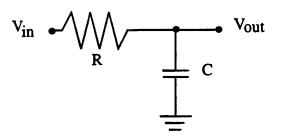

There are two steps to the process of constructing an equivalent circuit model for an interconnect wire. The first step is to determine the nature of the equivalent circuit, that is, what kinds of circuit elements are important, and how many degrees of freedom are required for the level of accuracy desired. A simple example of such an equivalent circuit is shown in Figure 2.1. The second step is to determine the value associated with each element in the equivalent circuit.

## 2.2. Background

#### 2.2.1. Interconnect Trends

#### **2.2.1.1. Scaling Effects on Interconnect**

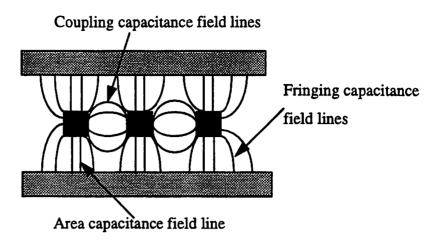

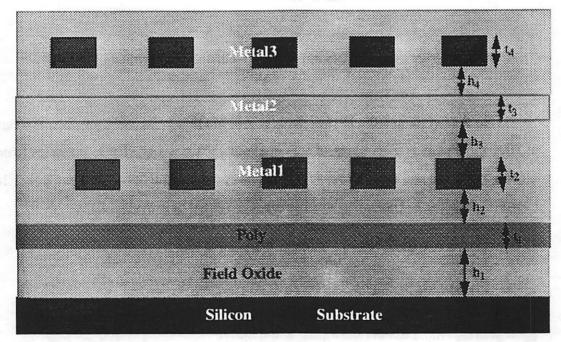

At maximum wiring density, each wire is capacitively coupled to its nearest neighboring wires on the same layer, as well as wires above and below it, as shown in Figure 2.2. As device sizes have been scaled for improved performance and increased density, the interconnect sizing, spacing, and conductor thickness have been reduced as well.

If all of the dimensions of interconnect are scaled in a complete die shrink, then the total RC for the interconnects would remain unchanged. However, as device sizes are

Figure 2.1. A simple interconnect model

reduced, the trend is also to use larger die. Therefore, the average interconnect lengths not only do not scale, but also become longer from one generation to the next.

In a simplified form, the 50 percent delay<sup>1</sup> from the first to second gate in Figure 2.1 can be expressed as

$$t_{50\%} = R_{tr} \bullet C_{gate} + R_{int} \bullet C_{int}$$

(2.1)

where  $R_{tr}$  is the effective on-resistance of the driving gate,  $C_{gate}$  is the input capacitance the receiving gate, and  $R_{int}$  and  $C_{int}$  are the distributed interconnection resistance and capacitance, respectively.

Let S be the scaling factor of the minimum feature size, and  $S_c$  be the scaling factor of the chip size. We define S to be the linear reduction factor and  $S_c$  to be the linear magnification factor. In this way, both are larger than one as technology progress. Table 2.1 shows how the device and interconnect parameters are scaled in the situation of ideal scaling and quasiideal scaling, respectively. Ideal scaling is proposed by Dennard [22] in 1974. In quasi-

<sup>1.</sup> Fifty percent delay is defined as the delay from the time when the input potential reaches the midpoint between Vdd and ground to the time when the output reaches the same midpoint.

Chapter 2

ideal scaling, the vertical dimensions of interconnect are scaled by approximately the square root of the lateral scaling factor S.

From Table 2.1, the scaling properties of the delay components for a critical path that extends across a chip can be found. For the case of ideal scaling, they are listed below:

$$R_{tr} = \frac{1}{\frac{W}{L} \mu C_{gox} (V_{DD} - V_T)} \propto 1$$

(2.2)

$$C_{gate} = \varepsilon_{ox} \frac{(W_n L_n + W_p L_p)}{T_{ox}} \propto 1/S$$

(2.3)

$$R_{int} = \rho \frac{l_{int}}{W_{int}H_{int}} \propto 1/S$$

(2.4)

$$C_{int} = \varepsilon_{ox} \frac{W_{int}^{l}_{int}}{T_{ILD}} \propto S_C$$

(2.5)

Here  $W_n$ ,  $W_p$ ,  $L_n$  and  $L_p$  are the width and length of a n and p transistor, respectively,  $\mu$  and  $C_{gate}$  are the surface mobility of the carriers and the gate oxide capacitance per unit area,  $V_{DD}$  and  $V_T$  are the power supply and threshold voltage,  $T_{ox}$  and  $T_{ILD}$  are the gate and field oxide thicknesses, respectively.  $H_{int}$  is interconnect thickness, and  $l_{int}$  and  $W_{int}$  are the length and width of an interconnection.

| Parameter                                      | Ideal Scaling<br>Result         | Quasi-ideal<br>Scaling<br>Result | Trend with<br>S>1, S <sub>c</sub> >1 |

|------------------------------------------------|---------------------------------|----------------------------------|--------------------------------------|

| W (Gate width)                                 | W/S                             | W/S                              | K                                    |

| L (Gate length)                                | L/S                             | L/S                              | X                                    |

| $T_{ox}$ (Gate oxide thickness)                | T <sub>ox</sub> /S              | $T_{ox}/S$                       | K                                    |

| T <sub>ILD</sub> (ILD thickness)               | T <sub>ILD</sub> /S             | $T_{ILD}/S^{1/2}$                | X                                    |

| lint (Interconnect wire length)                | l <sub>int</sub> S <sub>c</sub> | l <sub>int</sub> S <sub>c</sub>  | メ                                    |

| W <sub>int</sub> (Interconnect wire width)     | W <sub>int</sub> /S             | W <sub>int</sub> /S              | 1                                    |

| H <sub>int</sub> (Interconnect wire thickness) | H <sub>int</sub> /S             | $H_{int}/S^{1/2}$                | イ                                    |

## Table 2.1.

Scaling Properties of Device and Interconnect Parameters

· · · ·

| Parameter                         | Ideal Scaling                              | Quasi-ideal Scaling              | Trend with        |  |

|-----------------------------------|--------------------------------------------|----------------------------------|-------------------|--|

|                                   |                                            |                                  | S >1 and $S_c >1$ |  |

| R <sub>tr</sub>                   | 1                                          | 1                                | $\leftrightarrow$ |  |

| Cg                                | 1/S                                        | 1/S                              | K                 |  |

| R <sub>int</sub> (global)         | S <sup>2</sup> S <sub>c</sub>              | S <sup>3/2</sup> S <sub>c</sub>  | ~                 |  |

| C <sub>int</sub> (global)         | S <sub>c</sub>                             | S <sup>-1/2</sup> S <sub>c</sub> | 7                 |  |

| R <sub>int</sub> C <sub>int</sub> | S <sup>2</sup> S <sub>c</sub> <sup>2</sup> | SS <sub>c</sub> <sup>2</sup>     | 7                 |  |

| Ta | ble | 2.2. |

|----|-----|------|

|    |     |      |

Effects of Scaling on Interconnect

Table 2.2 shows the effects of scaling on FET transistors and interconnects. Given that the resistance of transistors stays the same for a given scale factor, the gate capacitance of the next generation is reduced by 1/S. The gate delay  $(R_{tr}*C_{gate})$  is thus reduced by 1/S, so the device speed is improved, as expected. However, for global interconnect lines, the interconnect resistance  $R_{int}$  increases by  $S^{2}*S_{c}$ .  $S^{2}$  comes into consideration because the wire thickness and width are reduced by 1/S. On the other hand, the interconnect capacitance is only increased by  $S_{c}$ , because the wire capacitance per unit length stays the same and wire length increases by  $S_{c}^{2}$ . The RC time constant of the global interconnect is thus increased by  $S^{2}*S_{c}^{2}$ .

Both S and S<sub>c</sub> have approximately the same values for each new generation. Therefore, the delay of the global line is increased by S<sup>4</sup> with ideal scaling. In practice, ideal scaling is difficult to implement rigorously. Quasi-ideal scaling has been proposed and is followed more or less today by IC industry. Still, the delay of the global line is increased by S<sup>3</sup>. This clearly illustrates why interconnect delay is so dramatically increased with scaling and how it becomes an important issue in submicron technology. J. Z. Lin

Figure 2.3. Tighter pitch and higher height-to-width ratio of new technology

#### 2.2.1.2. Coupling Capacitance and Its Effects

The interconnection capacitance has three components as indicated in Figure 2.2: the area component (also referred to as parallel plate capacitance component), the fringing field component, and the wire-to-wire capacitance component.

In current 0.25 micron technology, the conductor height-to-width ratio is about 1.4, and this ratio is expected to increase to 2.5 in the future, as illustrated in Figure 2.3. At the same time, conductor spacing is comparable to conductor thickness. Because of tighter pitch and the increasing conductor height-to-width ratio, the coupling capacitance between wires is becoming significant, and the fringing field is also responsible for a large portion of the overall capacitance. Combined fringing field and coupling capacitances are usually larger than the parallel plate component. To improve packing density while maintaining a relatively small interconnect RC constant, it is desirable to fix the conductor and oxide thickness, while reducing the wire width and spacing.

Assuming that the wiring layers in Figure 2.2 represent upper and lower level metal layers, it should be noted that the majority of the total capacitance will be between signal

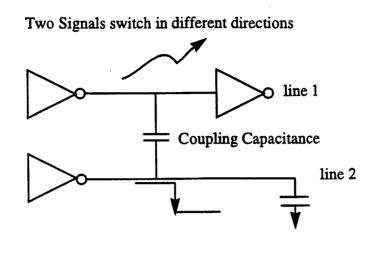

Figure 2.4. The coupling capacitance effect

wires for multi-level technologies, with little coupling capacitance to the substrate. One has to be concerned with the coupling between signal wires, as it degrades the switching speed and causes cross talk between neighboring wires, which can result in faulty operation. For example, two coupled lines are illustrated in Figure 2.4. If one line is switching high, while the other is switching low, the waveform on line one may become non-monotonic, thus increasing the switching delay.

#### J. Z. Lin

#### 2.2.2. Constructing Equivalent Circuits to Interconnect Structures

#### 2.2.2.1. The Nature of the Equivalent Circuit

There is a wide range of equivalent circuits which can be used to model on-chip interconnections. The detailed character of the equivalent circuit for an on-chip interconnect depends on, among other things, the type of technology, the length of the interconnect wire, the amount of current on the interconnect, and the switching speed of the chip.

One fundamental quantity that characterizes the relative importance of interconnection capacitance and inductance for a particular technology is the lossless transmission line impedance level,  $Z_g = \sqrt{L/C}$ , where L and C are inductance and capacitance per unit length. [13] claims that the equivalent circuit for an average length on-chip interconnection in CMOS chips can be constructed using capacitors and resistors. In modern lossy on-chip interconnect, the inductive voltage drop is negligible compared to resistive voltage drop up at clock frequencies of 1-2 GHz. Thus, on-chip interconnect lines may be approximated by an RC line. So, throughout this thesis, all on-chip interconnects are modeled as RC networks.

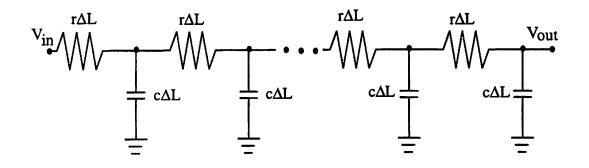

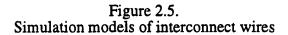

Because of the distributed nature of interconnect wires (see Figure 2.5(b)), once it has been determined what types of circuit elements are required to model a particular class of on-chip interconnections, one must then decide how many circuit elements of each type are needed. For example, it may be determined that the on-chip interconnections are to be modeled as RC ladder networks. Then, one must decide how many resistors and capacitors are needed to accurately model each piece of interconnection. The process of breaking each piece of interconnection into a fixed number of lumped circuit elements will be called the subdivision process. The sub-division into these partial elements is similar to the allocation of elements in a finite-element approach to the solution of partial differential equations. However, since one is typically interested in the overall delay, and not the exact shape of the waveform, the partial elements considered here can be assigned on a relatively coarse scale.

The problem of deciding upon a proper subdivision of interconnect wires is still one whose solution involves more art than science. It is obvious that if the interconnection is

#### Chapter 2

#### J. Z. Lin

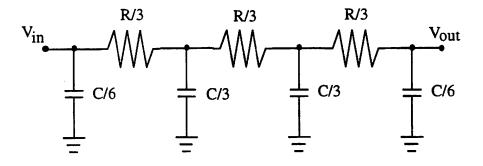

broken up into very many pieces, then the description will be more than adequate. It is equally obvious that if the interconnection is broken up into too few pieces, then the description obtained will be inadequate. In the former case, computational resources are wasted. In the latter case, the accuracy of the results will be questionable. Even if one has an appropriate subdivision scheme, it is difficult to determine its accuracy. Only on intuitive grounds can one make a priori arguments about what degree of subdivision is sufficient. These intuitive arguments can be based partly on the wavelength of propagating signals of the relevant frequency in whatever materials and geometry are under consideration. Portions of the interconnection that are well within one wavelength of each other can likely be treated as part of the same lumped element (Figure 2.5(a)). For lower speed circuits operated at relatively low frequencies (long wavelength), interconnect models are very simple. Each wire is much shorter than the wavelength, and can thus be treated as an individual lumped element. As the operating frequency (switching speed) of a circuit is increased, the wavelength decreases, requiring more distinct lumped elements. In practice, some simplified version of distributed model is used in simulation, such as the  $\pi$ 3 model shown as Figure 2.5(c).

(a) Lumped model

(b) Distributed Model

(c)  $\pi$ 3 Model

## 2.2.2.2. The Values of the Circuit Elements

Once a procedure has been chosen for the sub-division of the distributed interconnections, the effective values of resistance and capacitance for each element must be calculated. The process of obtaining these values is called interconnect parasitics extraction.

There are many ways to extract the parasitics. However, the applications of empirical formulae to general submicron interconnects are rather limited because of the complexity of interconnect configurations in multi-level submicron technology, especially in extracting the coupling capacitances. These formulae can not cover layout configurations having multiple dielectric and metal layers, and most importantly, they are not accurate enough to capture the variations of the layout and technology parameters of interconnect. Furthermore, they are obtained by fixing the values of the technology parameters. So their applicability in our work of sensitivity study over the technology parameters is not appropriate.

In "exact" computations of electrical circuit parameters, one appeals to the theory of electromagnetic fields; that is, "exact" computations involve the numerical analysis of two or three dimensional integral or partial-differential equations for the values of an electromagnetic field. The accuracy of such solutions is limited in theory only by the number of grid points, the availability of computing resources, and by human patience in describing the geometry of actual interconnect structures.

Since multi-level interconnect technologies use multiple conductors with different thicknesses and multiple insulators with possibly different dielectric constants, numerical simulations are mandatory for accurate resistance and capacitance modeling [23] [24] [25]. Numerical techniques have been developed for rigorous interconnect capacitance extractions. They fall into the following three categories [3]:

(1) finite-difference method [4] [5];

- (2) finite-element method [3]

- (3) Green's function method [4].

All these methods use the quasi-transverse electromagnetic approximation and divide the space surrounding the object into meshes, and use local equations at each mesh point.

There are several ready-to-use or commercial extraction tools available, such as Fastcap [23], Space[29], and Raphael [26]. Among these, we found that Raphael is the easiest one to use because of its good user interface, and its capability to perform batch-mode simulation and two-dimensional simulations. So, Raphael is chosen as the extraction tool in this work.

## **2.3. Interconnect Model Library**

We have concluded the necessity of numerically based simulation to perform interconnect parasitics extraction. However, numerical simulation is computationally intensive and real-time simulation is too time-consuming. Furthermore, in our approach to perform sensitivity study, all the interconnect wires are to be modeled using closed-form analytical models, which requires parameterized interconnect models. To cope with this problem, a realistic approach is to construct a parameterized interconnect model library based on numerical simulation. Then the circuit description can be generated with the help of the model library which contains models of typical two-dimensional interconnect structures. The circuit description will thus become the basis of sensitivity study and statistical circuit simulation.

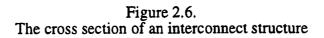

Figure 2.5 shows the flow of this interconnect modeling approach and model library building. First, the possible and typical interconnect configurations are identified. The most common configurations encountered are listed as follows:

a. One conductor above a ground plane.

b. Two conductors above a ground plane.

c. Three conductors above a ground plane.

d. More than three conductors above a ground plane.

e. One conductor between two ground planes.

f. Two conductors side by side between two ground planes.

g. Three conductors side by side between two ground planes.

h. More than three conductors side by side between two ground planes.

These interconnect structures are two-dimensional structures, so they are easier to define in terms of both layout and technology parameters than three-dimensional structures.

The sensitivity analysis is performed under the assumption that the variation of technology parameters, interlayer dielectric thickness, conductor thickness, is within  $\pm 20\%$  of its nominal value for a given technology, while the ranges of the layout parameters, such as metal width, inter-wire spacing, are set according to the design rules and their possible design ranges. Each parameter is divided into several levels, and a full factorial design is used to generate the simulation points for each structure. The input file for the numerical simulator which contains all the simulation points is generated, and two dimensional simulations are performed in batch-mode using a numerically based extractor (Raphael) to evaluate the unit length capacitance and resistance values. The numerical data are then fitted with an analytical expression using a special curve-fitting technique which is discussed in more detail in Section 2.5.

### J. Z. Lin

Chapter 2

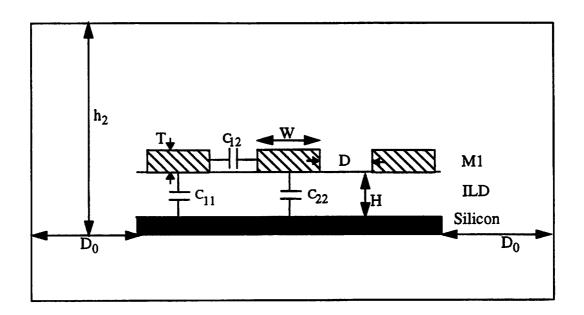

In the following sections, we will use the structure in Figure 2.6 as an example to illustrate the approach in more detail.

Figure 2.7. Interconnect Modeling Flow

# 2.4. Numerical Simulation

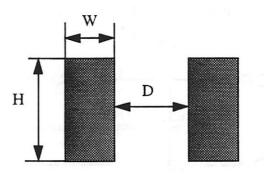

The interconnect structure shown in Figure 2.6 is defined in terms of four parameters, metal width W, inter-wire distance D, metal thickness T and ILD thickness H. The three capacitances,  $C_{22}$ ,  $C_{11}$ , and  $C_{12}$  are of interest and their models are constructed. Notice that all inter-wire spacings are the same in this structure.

The input file to the numerical extractor Raphael is generated as follows: each parameter, W, D, T and H, is set at 6, 6, 7 and 7 levels respectively. Using a full factorial design, a total number of 1764 simulation points (combination of different levels of the four

parameters) are generated, and the input file for Raphael is thus created based on these points.

| Н     | Т    | W   | D   | h <sub>2</sub> | s <sub>0</sub> | ε <sub>1</sub> | ε2  | ρ    |

|-------|------|-----|-----|----------------|----------------|----------------|-----|------|

| 0.955 | 0.51 | 0.9 | 0.5 | 10             | 12             | 3.9            | 3.9 | 0.01 |

| 0.955 | 0.53 | 0.9 | 0.5 | 10             | 12             | 3.9            | 3.9 | 0.01 |

| 0.955 | 0.55 | 0.9 | 0.5 | 10             | 12             | 3.9            | 3.9 | 0.01 |

|       |      |     |     |                |                | •••            |     | •••  |

The created input file which contains one simulation point at each row looks like:

| Table 2.3. |

|------------|

|------------|

Input File to Numerical Extractor for the structure depicted in Fig.2.6.

In the above table,  $h_2$  and  $s_0$  defines the simulation boundaries as indicated in Figure 2.6,  $\varepsilon_1$  and  $\varepsilon_2$  are the dielectric permittivities, while  $\rho$  is the resistivity of the metal. Each row of the table stands for one simulated experiment.

For this structure, it takes about 8 hours for Raphael to finish the 1764 numerical simulations on a Sparc 20 workstation. The next step is to construct an analytical model based on these simulation results. This is discussed in the next section.

## **2.5.** Curve-fitting Technique

#### 2.5.1. Linear least square regression analysis

The objective is to create a model y = F(x) that maps the relationship between the set of parameters defining the physical interconnect and the values of the parasitics of the interconnect. Here y is the n dimensional vector representing the capacitances and resistances to be modeled, and x is the m dimensional input vector containing all the interconnect parameters.

This is implemented using simple polynomial expressions and linear regression. Linear regression postulates a model of the form:

• •

Chapter 2

$$y = \beta_0 + \sum_{i=1}^{M-1} \beta_i x_i + \varepsilon$$

(2.6)

(2.7)

where  $x_i$  stands for the independent variables. The terms that should be included in the model can be of first, second or higher order, or even interaction terms made of the group of parameters which define the interconnect structure. The final expression is determined using a technique discussed in Section 2.5.2. The least squares criteria chooses the  $\beta_i$  values that minimize the sum of squared residuals:

$$\sum_{j=1}^{N} \left\{ y_j - \left[ \beta_0 + \sum_{i=1}^{M-1} \beta_i x_{i,j} \right] \right\}^2$$

(2.8)

where j indexes each of the N simulation points.

The equations can be expressed more compactly in matrix form. Let X be the N by M data matrix; i.e. X looks like

$$\begin{bmatrix} 1 & x_{11} & x_{12} & \dots & x_{1M} \\ \dots & \dots & \dots & \dots & \dots \\ 1 & x_{N1} & x_{N2} & \dots & x_{NM} \end{bmatrix}$$

Also, let y be the N by 1 column of observed responses and let  $\hat{\beta}$  be the M by 1 column of estimated coefficients, with the first element being the intercept. Then any  $\hat{\beta}$  satisfying the normal equations:

$$(\mathbf{X}^{\mathsf{T}}\mathbf{X})\hat{\boldsymbol{\beta}} = \mathbf{X}^{\mathsf{T}}\mathbf{y} \tag{2.9}$$

gives a least squares fit, assuming that  $\mathbf{X}^{T}\mathbf{X}$  is invertible.

Linear regression implies that the model is linear in the coefficients being estimated, that is, linear in  $\beta$ . The models built in this work are linear in this sense. Another

#### J. Z. Lin

common use of the term "linear" is to describe whether the model is linear in the variables. Better referred to as the order of the model, this work does include non-linear terms such as quadratic or interaction terms of the input variables X.

As stated above, the capacitance models include quadratic and higher order terms of the parameters, together with their interaction terms. In order to achieve an accurate model, the first step would be to determine the terms to be included in the final model. After the model terms have been determined, the coefficient of each term can be estimated using the least squares technique. However, choosing the terms of the model is a difficult task. In the following section, we present a systematic way to address this problem.

#### **2.5.2.** Determining the Necessary Model Terms

It is obvious that if the model terms are incorrect or inappropriate, one can not get an accurate capacitance model. Most of the time, the models built by the trial-and-error approach are not good enough to be used for sensitivity analysis. However, one can find an efficient and systematic solution to this problem, guided by the simple physical relationships between the input variables and the resulting capacitance.

First, we select the data points that are obtained by varying one parameter with the other parameters fixed, then these data points are fitted over this parameter using step-wise regression. This is easy since only one variable or parameter is involved. In this way, one will get a separate model related to each of the parameters. These models are simple polynomial functions. In some cases, non-linear data transformations are necessary in order to apply a linear model. Combining these separate models, the final model terms are easy to identify. This is illustrated as follows:

Suppose that capacitance C is an unknown polynomial function of two variables, W and D. That is, C = f(W, D), and the goal is to choose the proper model terms based on discrete data points.

Let us assume that by curve-fitting over W with D fixed, one finds that C is a linear function of W, that is,

$$C = aW + b \tag{2.10}$$

Chapter 2

In the above equation, a and b are constants, and they will take different values when S is fixed at different points. So a and b are only functions of D, such as

$$a = f_1(D) \text{ and } b = f_2(D)$$

(2.11)

then (2.10) can be rewritten as:

$$C = f_1(D) \cdot W + f_2(D)$$

(2.12)

Suppose that C is fitted over D with W fixed, and the fitting result shows C is a second order polynomial function of D. Following the same argument as above, one can conclude that C can also be expressed as:

$$C = g_1(W) \cdot D^2 + g_2(W) \cdot D + g_3(W)$$

(2.13)

Note that (2.12) and (2.13) are equivalent expressions. Since both equations represent capacitance, which must be continuous functions of both D and W, we can take the derivative of these two equations over W, which leads to the following expression:

$$f_1(D) = \frac{\partial}{\partial W} g_1(W) \cdot D^2 + \frac{\partial}{\partial W} g_2(W) \cdot D + \frac{\partial}{\partial W} g_3(W)$$

(2.14)

Thus, the model terms of C(W, D) can be decided. Given the fact that the left-hand side (LHS) of (2.14) does not depend on W, the right-hand side (RHS) should also be independent of W. Then we can conclude that  $g_1(W)$ ,  $g_2(W)$ , and  $g_3(W)$  are linear functions of W, i.e.,

$$g_1(W) = k_1 W + k_2;$$

(2.15)

$$g_2(W) = k_3 W + k_4; (2.16)$$

$$g_3(W) = k_5 W + k_6; \tag{2.17}$$

Here,  $k_i$  (*i* = 1 to 6) are constants. By substituting (2.15), (2.16) and (2.17) into (2.13), the equation can be rewritten as:

$$C(W,D) = (k_1W + k_2) \cdot D^2 + (k_3W + k_4) \cdot D + (k_5W + k_6)$$

(2.18)

To simplify the situation, the above illustration assumes that C is a linear function of W when D is fixed. If C is a second or higher order function of W, the above explanation still applies on taking higher order derivatives, which will lead to similar results. In practice, the above technique is used to choose the terms of the model, while the coefficients of the terms are determined using least squares fitting.

Though only two variables are discussed in the above technique, the approach can be easily generalized to three and more variables. Also, note that even though the above discussion is not a strict mathematical proof, it does provide us with some insight and guidance on data fitting in order to get an accurate capacitance model.

### **2.6. Example**

We now apply this technique to model the results of an array of simulations performed on the example depicted in Figure 2.6.

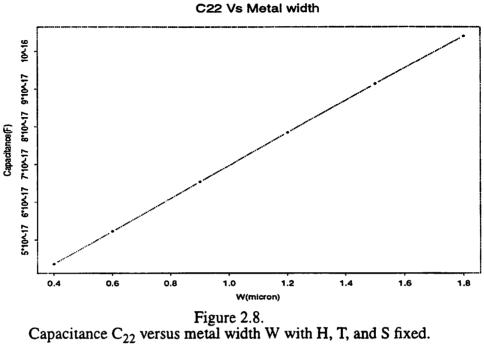

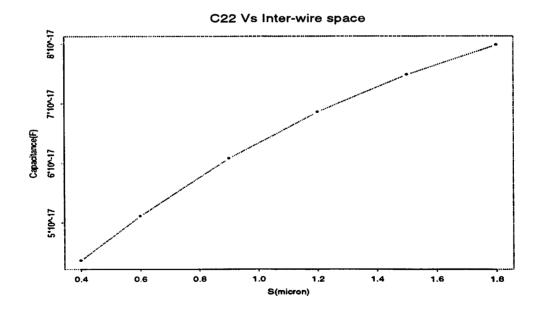

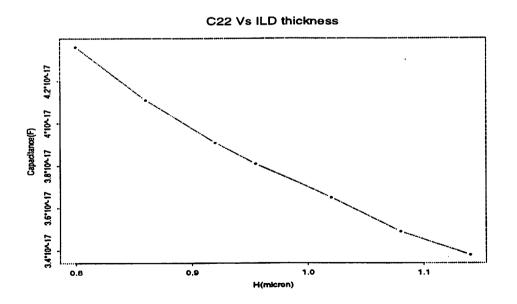

Figure 2.8, Figure 2.9, Figure 2.10, and Figure 2.11 show how the capacitance  $C_{22}$  changes with metal width, inter-wire spacing, metal thickness and ILD thickness, respectively. It is easy to see from Figure 2.8 that  $C_{22}$  is linear with the metal width W and metal thickness T, respectively. The relationships between  $C_{22}$  and the other two variables also agree with physical intuition.

It is also found that  $C_{22}$  can be modeled as a third order polynomial function of inter-wire spacing S. The plot of Figure 2.11 indicates that data transformation will help the modeling of  $C_{22}$  against ILD thickness H. So  $C_{22}$  is modeled as a second order polynomial function of  $H_i^{-1}$ .

Based on the four individual models, the complete analytical model terms are thus chosen, and the coefficients are determined by the least squares criterion. Table 2.4 summarizes the modeling results:

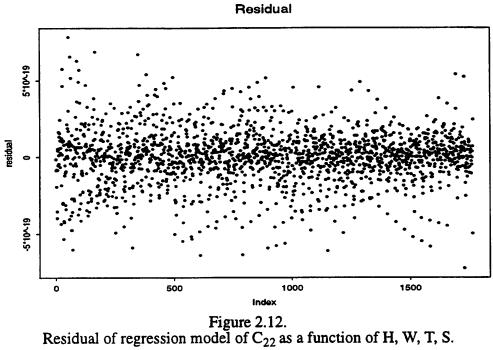

Table 2.4 indicates that multiple  $\mathbb{R}^2$  is 0.9999, which means 99.99% of the variation can be explained by the model. F-ratio is the ratio of the mean square of the regression to the estimated variance, and the zero p-value means the ratio is very significant. However, one can not conclude that the model fits the data well just by looking at this table. Further analysis is necessary to assess the model.

Chapter 2

| Source | Sum of<br>Squares | Degree of<br>Freedom | Mean<br>Squares | F-ratio        | Prob>F |  |

|--------|-------------------|----------------------|-----------------|----------------|--------|--|

| Model  | 91.1037           | 47                   | 1.938376        | 613700         | 0      |  |

| Ептог  | 0.00542           | 1716                 | 3.158eE-6       | $R^2 = 0.9999$ | 999    |  |

| Total  | 91.109            | 1763                 |                 | σ = 0.00177    |        |  |

Statistics of Modeling Result of  $C_{22}$  Model

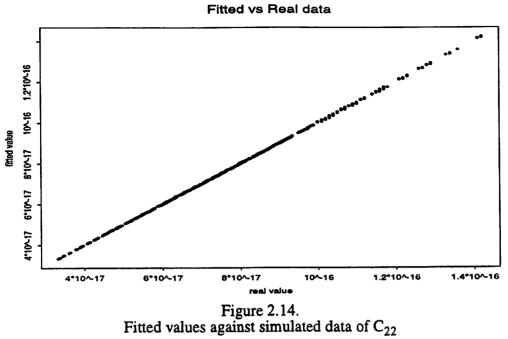

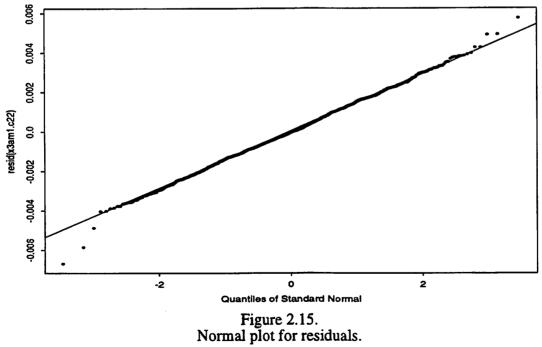

The simplest and most informative method for assessing the fit is to plot the response against the fitted values, and also examine the residuals. Figure 2.14 shows the predicted values versus the simulation data. The straight line indicates good fitting of data. Figure 2.15 is the normal plot of the residual, and it gives no reason to doubt that the residuals are normally distributed. This is further justified by residual plots shown in Figure 2.12 and Figure 2.13. Since the minimum value of  $C_{22}$  is 0.33 (scaled by 1E-16), the ratio of the residual standard error,  $\sigma$  in Table 2.4, over the minimum of simulation data  $C_{22}$  is just 0.5% (0.0017/0.33).

The above analysis shows that the model fits the data very well, the regression is significant, and the residuals appear normally distributed. This underscores the usefulness of the technique.

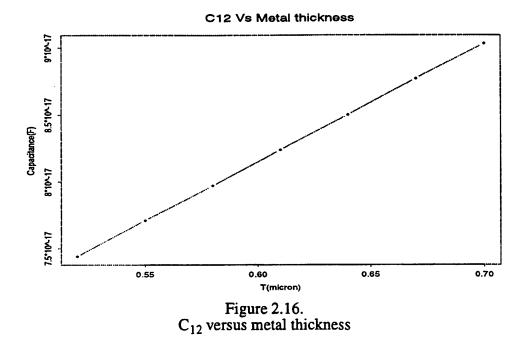

Figure 2.16, Figure 2.17, Figure 2.18 and Figure 2.19 depict the plot of  $C_{12}$  against the four interconnect parameters. The clear patterns of their relationships indicate that we can also use the same fitting technique to find the form of the analytical model of  $C_{12}$ . Since the process is similar, it will not be repeated here.

Figure 2.9. Capacitance  $C_{22}$  versus inter-wire spacing S with W, H, and T fixed.

Figure 2.10.  $C_{22}$  versus metal thickness T with W, H, and S fixed.

Figure 2.11.  $C_{22}$  versus ILD thickness H with W, T, and S fixed.

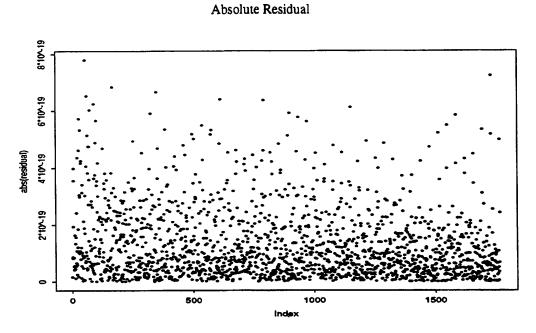

Figure 2.13. Absolute residual of regression model of  $C_{22}$

# 2.7. Summary and Conclusion

In this chapter we discussed the issues of interconnect modeling for the purpose of the sensitivity study, which will be discussed in next chapter. We concluded the necessity of numerical simulation in order to extract accurate interconnect parasitics. An efficient technique of curve fitting is discussed in detail, and a specific fitting problem is solved as an example. We also presented a methodology to build a parameterized interconnect model library.

Based on the interconnect model library built, we are ready to develop an approach to study the circuit sensitivity to interconnect variations. This is discussed in the following chapter.

$(m_{ij}, m_{jj})$

(2) The Receiption of the second second second states in the second s second s second seco

et gelik men national et en finnen het en sonnen fan kommen en en en en en stationer fin. Referense fan geliet sterne finnen in en gike finnen men en sterne en en stationer finnen.

# **Chapter 3 Sensitivity Study**

# **3.1. Introduction**

In Chapter 2, we discussed the problem of interconnect modeling. We built an interconnect model library, so we are now ready to develop an approach to study the effects of interconnect on circuit performance. The goal is to anticipate the effects of processing variation of an IC product, and then characterize and control this variation during production.

The models developed in the last chapter, and the established range values for interconnect parameters are the essential ingredients for the evaluation of the impact on circuit performance. In this chapter, an approach to accomplish this evaluation will be explored. A representative ring oscillator test circuit will be used as a means to test the interconnect models, and the relationships between interconnect parameter variations and circuit performance will be developed.

## **3.2. Previous Work**

The goal of statistical circuit design is to model and improve parametric yield [15]. The underlying concept is that variations in the manufacturing process change the performance of the integrated circuit and therefore cause the performance yield fluctuations seen in the final test. However, previous work is based on the fact that circuit performance is mainly determined by transistors or devices [12] [14] [15] [16], which is not the case in the era of deep submicron. The work only studies the effects of manufacturing line variations on fabricated device variations, and on circuit performance. Most of previous work does not take the interconnect variations into account.

35

For example, early work at Texas Instruments proposed characterizing CMOS processes with four statistical parameters: device width, device length, oxide capacitance, and flat-band voltage [12]. These parameters were identified because they explained most of the observed variations in the process and were determined to be nearly statistically independent. Equations for delay and power dissipation were then computed as a linear function of these parameters, and the resulting equations were then used for yield optimization [17].

Obviously, these efforts can not be applied to the modern submicron CMOS processes if the interconnect dominates the performance of the circuit. Since devices and interconnect wires are different in many aspects, a new approach needs to be developed.

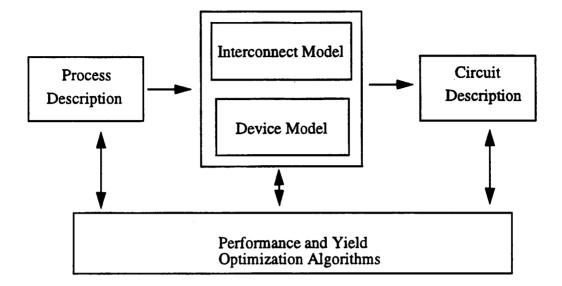

To incorporate the interconnect into the framework, there are four components in the statistical circuit design, as shown in Figure 3.1. The manufacturing process must be described in a way which characterizes the process variations responsible for the yield. The manufacturing line variations must be mapped into the variations of devices and interconnect wires, and then be mapped into the performance variation of circuits, which is achieved by circuit simulation. Finally, an algorithm is used to optimize the yield.

# **3.3. Methodology**

The methodology to perform the sensitivity study will be discussed in detail in this section. Some elements of the simulation will also be discussed.

An overview of our understanding of circuit sensitivity to interconnect variations is shown in Figure 3.2. The basic idea is to model each interconnect wire of a circuit using the parameterized interconnect models developed in Chapter 2, and then generate the circuit description based on a Spice file. The generated circuit description contains closedform analytical expressions for each interconnect capacitance and resistance elements, and it is the basis of the statistical circuit simulation.

Figure 3.2. Overview of sensitivity study

#### **3.3.1. Interconnect Wire Model**

To simulate the effect of process variation on a circuit, the connection between the process parameters and the input file to circuit simulator must be established. So the RC model for each interconnect wire should be expressed in terms of the interconnect parameters. With the help of the interconnect model library developed in the last chapter, the total capacitance and resistance of each interconnect wire can be easily described given the length of each wire, thus a RC model of each wire is built. The resulted description of the interconnect wires in a circuit usually take a form of an RC mesh because of the coupling capacitances among neighboring wires.

#### 3.3.2. Device Model

In this work, the BSIM level 27 MOSFET model is used, which mapped the fabrication line parameters to device characteristics. The model parameters can be separated into three groups. The first group contains physical constants, the second group includes the measurable process parameters, such as gate oxide thickness, and the last group consists of the fitting parameters, which can be extracted to match the measurable process parameters.

#### **3.3.3. Circuit Description**

The circuit description is generated for use in circuit simulation. It contains both the transistors and interconnect wires description with the help of the interconnect and device models discussed above.

#### 3.3.4. Circuit Simulation and Optimization

We use the SPICE circuit simulator to estimate circuit performance. Gradient and computer-based experimental design methods have been used to increase yield by optimizing the transistor sizes or the topology of a circuit for a process. The gradient method is a standard nonlinear optimization technique which can be implemented within a circuit simulator for use in yield optimization [17]. Experimental design techniques have focused on the use of Taguchi Robust Design methods to select optimum transistor sizes [18] [19].

In contrast, our work does not use formal optimization techniques to improve yield as the focus of this work is on the sensitivity analysis. More specifically, our goal is to determine the impact of interconnect related process parameters on performance.

#### 3.3.5. Statistical Circuit Simulation

The variation ranges of interconnect parameters form a multidimensional region which is referred to as a *parameter space*. This parameter space will be mapped to the variation ranges of the performance which is referred to as the *performance space*.

#### 3.3.5.1. Monte Carlo Simulation

The goal is to map the parameter space into the performance space, that is, to determine what will be the corresponding performance for each point in the parameter space.

39

The experiment involves selecting a set of points in parameter space. For each point selected, a circuit simulation is run to find the circuit performance. Monte Carlo simulation is a technique [20] which can cover the parameter space with a reasonable number of experiments. Often, statistical screening experiments, such as orthogonal arrays or factorial design are utilized to screen a large number of potential parameters.

The advantage of Monte Carlo convergence on an estimate of response lies in the fact that its cost is independent of the dimensionality of the problem, depending only on the desired precision of the analysis.

# **3.4. Case study: Ring Oscillator Circuit**

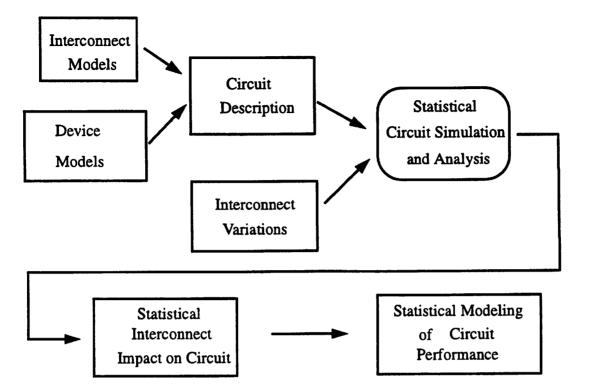

A ring oscillator was used to explore the sensitivity analysis approach. Figure 3.3 shows part of the circuit diagram of the ring oscillator, which emphasizes the interconnect wires between stages. The loading of the circuit is dominated by interconnect wires, as indicated in Figure 3.3. The interconnect length for each stage is 180  $\mu$ m, and is divided into 6 fingers as shown in the figure. Three of the fingers are next to previous stage fingers and the other three are next to next stage fingers, so there is a heavy capacitive coupling effect between neighboring stages.

J. Z. Lin

Figure 3.3. Circuit diagram of a ring oscillator

Figure 3.4. Ring oscillator circuit is composed of odd number of inverters

The ring oscillator is a standard circuit for delay measurements. It consists of an odd number of inverters connected in a circular chain as shown in Figure 3.4. Due to the odd number of inversions, the circuit does not have a stable operating point and oscillates. The period T of the oscillation is determined by the propagation time of a signal transition through the complete chain, or

$$T = 2 \cdot t_p \cdot N , \qquad (3.1)$$

with N the number of stages in the chain and  $t_p$  the propagation delay of each stage. The factor 2 results from the observation that a full cycle requires both a low-to-high and a high-to-low transition.

The ring oscillator circuit used in this study has nine stages, with fan-out of 2. However, the design is such that significant loading is contributed by interconnect wires. In this way, the signal delay  $t_p$  between each stage is mainly determined by the interconnect capacitance and resistance.

#### 3.4.1. Circuit Model

Chapter 3

To study the circuit performance sensitivity to interconnect parameters, we generate the Spice netlist file of the ring oscillator. The netlist generated from the extraction tool is modified so that the interconnect wires of the circuit are modeled in terms of the interconnect parameter. For example, coupling capacitance is modeled explicitly in terms of the length and distance of the wires. The regularity of this relatively simple ring oscillator circuit makes it easier to accomplish this modification. The fingers are parallel and have the same width and the same inter-wire space. By generating the circuit description in this way, a direct link between the circuit performance and interconnect parameters is established. The final circuit model is listed in Appendix C.

# **3.5. Results and Analysis**

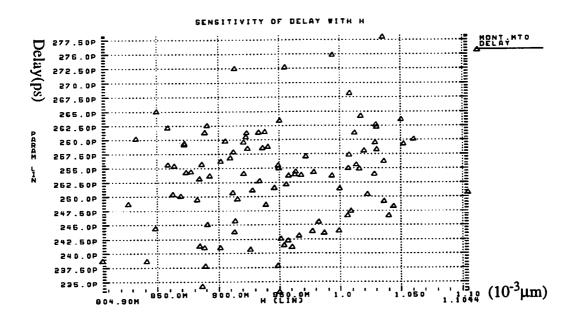

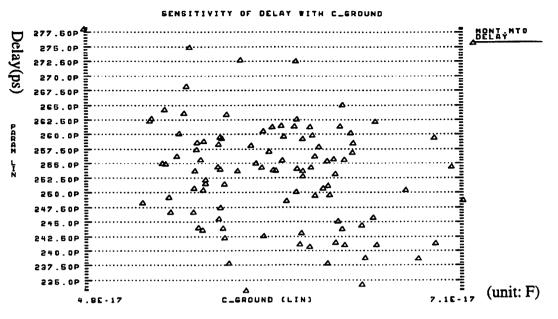

The ring oscillator circuit is simulated using HSPICE. The sensitivity of the delay to a particular parameter is evaluated by varying it over a reasonable range with the other parameters fixed. For example, the delay sensitivity to metal thickness is obtained by fixing the ILD thickness, metal width and metal spacing and varying the metal thickness over  $\pm 20$  % variation range.

Figures 3.5 to 3.8 show the simulation results of the delay sensitivity to the wire width, inter-wire spacing, ILD thickness and metal thickness, respectively. The roughness of the curves are caused by the reading error and the limited numerical resolution of HSPICE. Table 3.1 summarizes these results. It indicates that inter-wire spacing is the most sensitive parameter. 20% variation of the inter-wire spacing from its nominal value will lead to 8.8% deviation of the delay. On the other hand, the circuit is not sensitive to the variation of the ILD thickness in the range of the simulation.

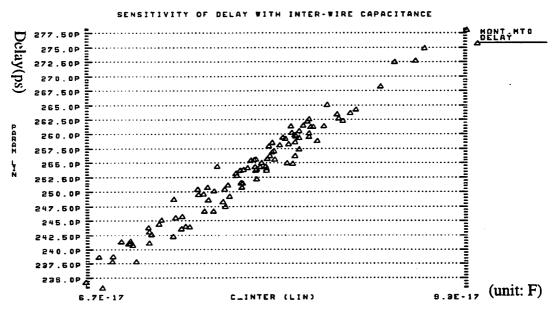

The lack of sensitivity of ILD thickness is because the delay is not sensitive to the plate capacitance. In fact, for this circuit, the delay is mostly sensitive to inter-wire coupling capacitance as can be seen in Figure 3.14. Also, it is because of the fact that resistance does not change along with ILD thickness, and that changing of inter-wire capacitance due to ILD thickness is almost cancelled by that of plate capacitance.

43

Figure 3.5. Delay versus metal width

Figure 3.7. Delay versus ILD thickness

•

| Parameter          | Parameter range (µm)<br>(20% variation) | Impact on Delay |  |

|--------------------|-----------------------------------------|-----------------|--|

| Metal width        | 0.810-0.990                             | 2.6%            |  |

| ILD thickness      | 0.842-1.029                             | 0.0%            |  |

| Metal thickness    | 0.572-0.699                             | 4.6%            |  |

| Inter-wire spacing | 0.450-0.550                             | 8.8%            |  |

# Table 3.1.Sensitivity Simulation Results

To get further insight and generalize the methodology, Monte Carlo simulations are also set up to perform statistical analysis. These statistical simulations closely reflect what happens in the real world. Monte Carlo analysis is an effective way to provide the information for improving circuit robustness to interconnect variation. The results of simulation establish a connection between performance spread and the variation of parameters.

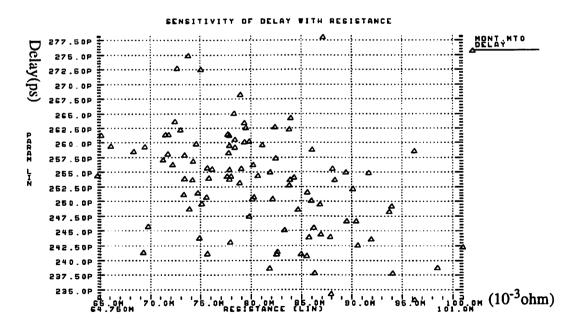

The Monte Carlo simulation is performed based on the assumption that all interconnect parameters (there are four parameters in this study) are normally distributed with 3 sigma equal to  $\pm 20\%$  of their nominal values. Figure 3.9 is the scatter plot of delay which provides the information about the worst and best corners and can be used for centering the design. Figures 3.10 to 3.13 show the sensitivity of delay to metal width, inter-wire spacing, ILD thickness and metal thickness respectively. These results are consistent with the previous deterministic analysis. Particularly, Figure 3.11 shows the significant sensitivity of inter-wire spacing with respect to the delay.

Interconnect variations lead to the change of interconnect resistance and capacitance, including both plate capacitance and coupling capacitance, and affect the delay of the circuit. Figures 3.14, 3.15, and 3.16 show how sensitive the delay is against unit-length inter-wire coupling capacitance, plate capacitance and resistance, respectively. Particularly, Figure 3.14 demonstrates the extreme importance of the coupling capacitance with regard to the delay.

Figure 3.9. Scatter plot of Monte Carlo simulation

Figure 3.10. Delay sensitivity to metal width

Figure 3.11. Delay sensitivity to inter-wire spacing

Figure 3.12. Delay sensitivity to ILD thickness

SENSITIVITY OF DELAY WITH T

Figure 3.13. Delay sensitivity to metal thickness

Figure 3.14. Delay sensitivity to unit-length inter-wire coupling capacitance

Figure 3.15. Sensitivity of delay to unit-length plate capacitance

Figure 3.16. Sensitivity of delay to unit-length wire resistance

Ύρ

# **3.6. Summary and Discussion**

In this chapter, the issues related to statistical circuit design are discussed, and an approach to study circuit sensitivity to interconnect parameter variations is developed using parameterized interconnect model library. The circuit netlist is modified to include explicit parameterized expressions of interconnect parasitics as a function of layout parameter. The results from the study of a ring oscillator circuit reveal that the delay of this ring oscillator is most sensitive to inter-wire spacing while least sensitive to ILD thickness.

The sensitivity study results can not be generalized simply. More circuits of similar type need to be studied in order to collect enough data to reach a general conclusion. The emphasis of this work is to develop an approach rather than to look for a general sensitivity conclusion for a particular type of circuits. However, this does not limit the value of this approach, since very often we may only be interested in a particular circuit during the design process. In the next chapter we show how such an analysis could be carried out for a complex circuit that does not have the regularity of a ring oscillator.

J.Z.Lin

Al par destructure and the call the second state at the second s second sec

# Chapter 4 Sensitivity Study Using Statistical Experimental Design

# 4.1. Introduction

In Chapter 3, we developed an approach which uses parameterized interconnect models to study the circuit sensitivity to interconnect parameter variations. A ring oscillator circuit whose performance is mainly determined by interconnect wires was studied using this approach. All the interconnect wires of this circuit were modeled via closed form analytical models, that is, all the parasitic capacitors and resistors were described in terms of both interconnect technology parameters and layout parameters.

There were several advantages to this approach. Firstly, it made the sensitivity study much easier without going through the time-consuming and error-prone process of on-line whole chip circuit extraction. Secondly, when studying the effect of the spatially distributed variations, this approach will be a good candidate since interconnect wires can be modeled separately using different models at different positions. Thirdly, the sensitivity to circuit design or layout parameters can be evaluated easily via this approach. Fourthly, when studying a complicated large circuit such as a microprocessor, some simple circuits that closely resemble the statistics of a microprocessor circuit can be analyzed using the above approach. In such a way, we can evaluate and forecast the performance spread of the microprocessor resulting from interconnect parameter variations before the manufacturing of the product die.

However, there are some limitations to this approach. It requires manual construction of an RC model for each interconnect wire, so it is not very suitable for studying a complicated and irregular, circuit directly. It is inefficient to manually model the whole circuit.

53

So, an alternative approach is developed in this chapter to study the impact of process variations of interconnect technology parameters on circuit performance.

# 4.2. Methodology

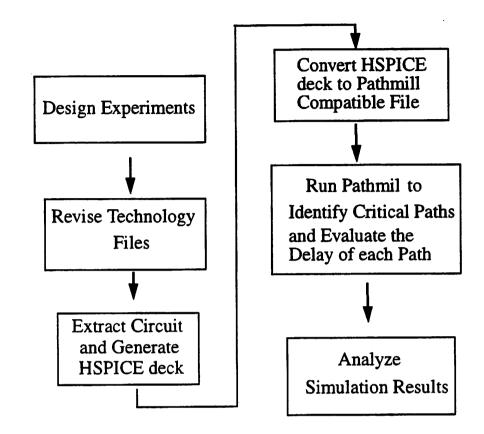

The main idea is that: based on the variation ranges of the technology parameters, the technology file is revised, and different circuit description files are generated from the revised technology files. The circuit description files are HSPICE decks. They are fed into the circuit simulator to evaluate the performance of the circuit.

Since there are many parameters of interest in multi-layer interconnect technology, we use statistical experiment design techniques to carry out the computer simulation experiments. More specifically, the flow of this approach is shown in Figure 4.1 and is listed below:

a. Design the experiments with variables of interconnect parameters, and construct the design matrix.

b. Revise the technology file based on the design matrix for each designed experiment.

c. Extract the parasitics of the circuit from the layout with each revised technology file, and thus generate an HSPICE deck.

d. Convert the HSPICE deck to Epic compatible input file, and run Pathmill<sup>1</sup> to identify the critical paths and evaluate the delay of each critical path.

e. Perform statistical analysis based on the simulation results of the extracted critical paths.

This approach is suitable for studying large, complicated circuits. In this work, a 32-bit shift-and-add multiplier circuit is used as a study case.

<sup>1.</sup> Pathmill is a CAD tool from Epic Inc. The tool can identify the critical paths of a circuit given the source and sink nodes, and evaluate the delay of each path. The script file to generate the input file, a config file, and a script file to run Pathmill are attached in the Appendix.

Figure 4.1. The methodology of sensitivity study using statistical experimental design

From the layout and the Hspice deck, it is found that this multiplier circuit contains about 8000 transistors and occupies an area of about 230k micron<sup>2</sup>. The technology for this circuit is 0.3 micron, and the interconnect wires have three metal layers and one poly layer, as shown in Figure 4.2. The variables of interest are listed below:

a. t<sub>1</sub>, t<sub>2</sub> t<sub>3</sub>, t<sub>4</sub> ----- thickness of poly, metal1, metal2 and metal3, respectively.

b. h<sub>1</sub>----- Field oxide thickness.

c. h<sub>2</sub>----- ILD thickness between poly and metal1.

d. h<sub>3</sub>----- ILD thickness between metal1 and metal2.

e.  $h_4$ ----- ILD thickness between metal2 and metal3.

## J.Z.Lin

It is also possible to examine the impact of layout parameters using this approach. To do this, however, will include a costly circuit extraction step for each of the simulated experiments. With today's CAD technology this will add several days of CPU time to a reasonably sized experiment.

# 4.3. Screening Experiment

# 4.3.1. Experimental Design

We want to investigate the most sensitive and important factors among the eight parameters stated above. This is achieved via a screening experiment. The range of each

Figure 4.2. Illustration of multi-layer interconnect structure

Chapter 4

parameter was chosen to effectively encompass its possible variation range during regular production. A full factorial experiment to determine all effects and interactions for the eight factors would require  $2^8$ , or 256 experiments. However, in order to reduce the experimental budget and simulation cost, the effects of higher order interactions were neglected and a  $2^{8-4}$  fractional factorial design requiring only 16 runs was performed. The design matrix appears in Table 4.1.

| Run | h <sub>1</sub> | h <sub>2</sub> | h3     | h <sub>4</sub> | t <sub>1</sub> | t <sub>2</sub> | t3     | t <sub>4</sub> |

|-----|----------------|----------------|--------|----------------|----------------|----------------|--------|----------------|

| 1   | 0.2520         | 0.4200         | 0.5600 | 1.0400         | 0.2600         | 0.8255         | 0.6545 | 1.2155         |

| 2   | 0.4680         | 0.4200         | 0.5600 | 0.5600         | 0.1400         | 0.8255         | 1.2155 | 1.2155         |

| 3   | 0.2520         | 0.7800         | 0.5600 | 0.5600         | 0.2600         | 0.4445         | 1.2155 | 1.2155         |

| 4   | 0.4680         | 0.7800         | 0.5600 | 1.0400         | 0.1400         | 0.4445         | 0.6545 | 1.2155         |

| 5   | 0.2520         | 0.4200         | 1.0400 | 1.0400         | 0.1400         | 0.4445         | 1.2155 | 1.2155         |

| 6   | 0.4680         | 0.4200         | 1.0400 | 0.5600         | 0.2600         | 0.4445         | 0.6545 | 1.2155         |

| 7   | 0.2520         | 0.7800         | 1.0400 | 0.5600         | 0.1400         | 0.8255         | 0.6545 | 1.2155         |

| 8   | 0.4680         | 0.7800         | 1.0400 | 1.0400         | 0.2600         | 0.8255         | 1.2155 | 1.2155         |

| 9   | 0.4680         | 0.7800         | 1.0400 | 0.5600         | 0.1400         | 0.4445         | 1.2155 | 0.6545         |

| 10  | 0.2520         | 0.7800         | 1.0400 | 1.0400         | 0.2600         | 0.4445         | 0.6545 | 0.6545         |

| 11  | 0.4680         | 0.4200         | 1.0400 | 1.0400         | 0.1400         | 0.8255         | 0.6545 | 0.6545         |

| 12  | 0.2520         | 0.4200         | 1.0400 | 0.5600         | 0.2600         | 0.8255         | 1.2155 | 0.6545         |

| 13  | 0.4680         | 0.7800         | 0.5600 | 0.5600         | 0.2600         | 0.8255         | 0.6545 | 0.6545         |

| 14  | 0.2520         | 0.7800         | 0.5600 | 1.0400         | 0.1400         | 0.8255         | 1.2155 | 0.6545         |

| 15  | 0.4680         | 0.4200         | 0.5600 | 1.0400         | 0.2600         | 0.4445         | 1.2155 | 0.6545         |