Copyright © 1997, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

### DESIGN AND IMPLEMENTATION VERIFICATION OF FINITE STATE SYSTEMS

- ~

by

1

Rajeev Kumar Ranjan

Memorandum No. UCB/ERL M97/99

18 December 1997

## DESIGN AND IMPLEMENTATION VERIFICATION OF FINITE STATE SYSTEMS

by

Rajeev Kumar Ranjan

Memorandum No. UCB/ERL M97/99

18 December 1997

.

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### **Design and Implementation Verification of Finite State Systems**

Copyright © 1997 by

Rajeev Kumar Ranjan

Please cite as

.

•

Rajeev Kumar Ranjan. Design and Implementation Verification of Finite State Systems. PhD thesis, University of California, Berkeley, 1997. Available as UCB/ERL M97/99. http://www.eecs.berkeley.edu/~rajeev/publications/publications.html

Abstract of an elastic state of a seteron, to arnol

Ale and the second states of the

•••••

): L.

#### Design and Implementation Verification of Finite State Systems

1.1.1

by Rajeev Kumar Ranjan

Doctor of Philosophy in Engineering University of California, Berkeley Professor Robert K. Brayton, Chair

WITH the increasing complexity of VLSI circuits, design and implementation verification have become important components in current day design flows and can have major impact on the timely delivery of a functionally correct product. This work investigates a spectrum of techniques targeted towards making the verification process practical for real designs. The key contributions can be divided into three parts.

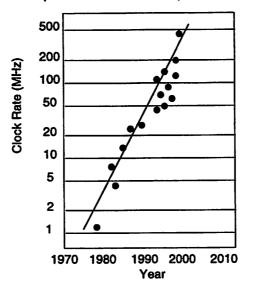

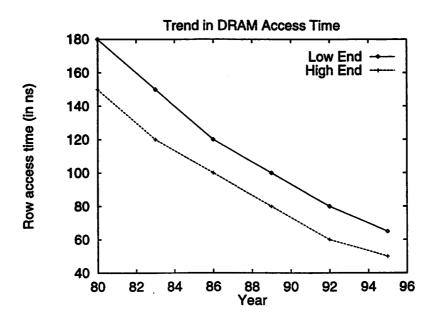

The first part exploits the architecture of a computer system for efficiently manipulating Binary Decision Diagrams (BDDs), the core technology in the symbolic techniques. Various methods are presented to localize the memory accesses and thereby leverage off the highly different access times for different levels of memory hierarchy in a workstation. These are further extended to exploit the main memory of several workstations connected together in a network. It is also shown that the locality of breadth-first manipulation can be merged with the parallel computing power of a shared-memory multiprocessor to efficiently leverage the parallel architecture.

The second part presents efficient BDD-based schemes for the representation and traversal of the state-space of large designs. Key contributions in this area include efficient image and pre-image computations, the core tasks in symbolic synthesis and verification algorithms.

The last part of this work targets the sequential equivalence problem which in its most general form is much harder than the combinational equivalence problem. An algorithm is presented to reduce the sequential equivalence problem to an extended form of combinational equivalence problem for designs which have undergone iterative retiming and resynthesis transformations. This allows the sequential equivalence checking process to leverage off the advancements in the combinational equivalence domain, making it viable for large designs. Further, the optimization potential and the verification complexity of optimization transformations consisting of retiming and combinational synthesis are formally characterized.

R.K. Brayton

نتع

# Table of Contents

• •

-

|                 | Tabl                                | e of Co | ntents                                    | v     |  |  |  |  |  |

|-----------------|-------------------------------------|---------|-------------------------------------------|-------|--|--|--|--|--|

| List of Figures |                                     |         |                                           |       |  |  |  |  |  |

|                 | List of Tables                      |         |                                           |       |  |  |  |  |  |

|                 | List of Definitions and Theorems xx |         |                                           |       |  |  |  |  |  |

|                 | Pref                                | ace     |                                           | xxiii |  |  |  |  |  |

|                 | Ack                                 | nowledg | gements                                   | xxv   |  |  |  |  |  |

| 1               | Intr                                | oductio | n                                         | 1     |  |  |  |  |  |

|                 | 1.1                                 | Goals   | and Scope of the Thesis                   | . 2   |  |  |  |  |  |

|                 | 1.2                                 | Compu   | ater Architecture Trends                  | . 3   |  |  |  |  |  |

|                 |                                     | 1.2.1   | Microprocessors                           | . 3   |  |  |  |  |  |

|                 |                                     | 1.2.2   | Memories                                  | . 4   |  |  |  |  |  |

|                 |                                     | 1.2.3   | Microprocessors vs DRAMs: Performance Gap | . 5   |  |  |  |  |  |

|                 |                                     | 1.2.4   | Disks vs DRAM: Price vs Performance       | . 8   |  |  |  |  |  |

|                 |                                     | 1.2.5   | Parallel Computing                        | . 9   |  |  |  |  |  |

|                 |                                     | 1.2.6   | Computer Architecture: Conclusions        | . 9   |  |  |  |  |  |

|                 | 1.3                                 | Desigr  | and Implementation Verification           | . 10  |  |  |  |  |  |

|                 | 1.4                                 | BDD-I   | based Verification Methodology            | . 14  |  |  |  |  |  |

|                 | 1.5                                 | BDD-I   | based Techniques                          | . 16  |  |  |  |  |  |

|                 |                                     | 1.5.1   | Computer Architecture Based Solutions     | . 16  |  |  |  |  |  |

|                 |                                     | 1.5.2   | Application Specific Solutions            | . 17  |  |  |  |  |  |

|                 |                                     |         |                                           |       |  |  |  |  |  |

### **TABLE OF CONTENTS**

|   |       | 1.5.3   | Algorithmic Solutions                                | 18 |

|---|-------|---------|------------------------------------------------------|----|

|   |       | 1.5.4   | Solutions Based on Modification of Decision Diagrams | 19 |

|   | 1.6   | Structu | aral Technique Based Sequential Circuit Verification | 20 |

|   | 1.7   | Thesis  | Organization                                         | 22 |

| 2 | Preli | iminari | es                                                   | 25 |

|   | 2.1   | Binary  | decision diagrams                                    | 25 |

|   | 2.2   | Synch   | ronous Sequential Circuits                           | 29 |

|   | 2.3   | Finite  | State Machines                                       | 29 |

|   |       | 2.3.1   | State Transition Graph                               | 32 |

|   | 2.4   | Implic  | it Boolean Set Manipulation                          | 32 |

| I | Co    | mpute   | r Architecture and BDD Manipulation                  | 33 |

| 3 | Brea  | dth-Fii | rst BDD Manipulation                                 | 35 |

|   | 3.1   | Introdu | uction                                               | 36 |

|   |       | 3.1.1   | BDDs in Synthesis and Verification Algorithms        | 36 |

|   |       | 3.1.2   | BDD Manipulation                                     | 37 |

|   |       | 3.1.3   | Conventional BDD Manipulation and Limitations        | 37 |

|   |       | 3.1.4   | Breadth-first BDD Manipulation Technique             | 41 |

|   | 3.2   | Previo  | us Work                                              | 47 |

|   | 3.3   | Our A   | pproach                                              | 48 |

|   | 3.4   | Memo    | ry Access Pattern                                    | 49 |

|   | 3.5   | Supers  | scalarity                                            | 52 |

|   | 3.6   | Pipelin | ning                                                 | 54 |

|   |       | 3.6.1   | Application                                          | 58 |

|   | 3.7   | Optim   | ized BDD Algorithms                                  | 60 |

|   |       | 3.7.1   | Substitute                                           | 60 |

|   |       | 3.7.2   | Existential Quantification                           |    |

|   |       | 3.7.3   | Compose                                              | 64 |

|   |       | 3.7.4   | Swapping Variables                                   | 65 |

|   |       |         |                                                      | 66 |

|   | 3.8   | Imple   | mentation Details                                    | 00 |

ŧ

. :, •

|   |   |      | 3.8.1    | Data Structure                                    | 66         |

|---|---|------|----------|---------------------------------------------------|------------|

|   |   |      | 3.8.2    | Memory Management                                 | 69         |

|   |   |      | 3.8.3    | Miscellaneous Details                             | 69         |

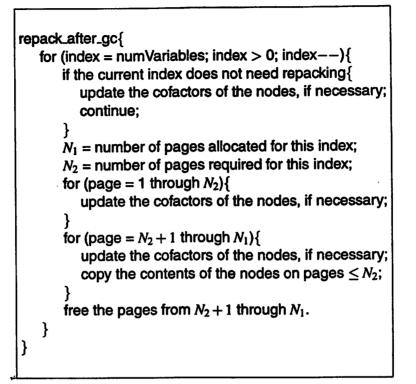

| - |   |      | 3.8.4    | Repacking After Garbage Collection                | 69         |

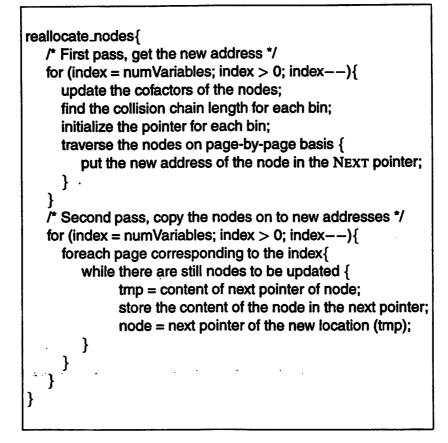

|   |   |      | 3.8.5    | Node Reallocation for Cache Locality              | 71         |

|   |   | 3.9  | Experim  | mental Results                                    | 71         |

|   |   |      | 3.9.1    | Experimental Setup                                | 73         |

|   |   |      | 3.9.2    | Creating Output BDDs for Circuits                 | 74         |

|   |   |      | 3.9.3    | Performance Comparison For Various BDD Operations | 78         |

|   |   |      | 3.9.4    | Performance Enhancement Due to Superscalarity     | 81         |

|   |   |      | 3.9.5    | Performance Enhancement Due to Pipelining         | 83         |

|   |   |      | 3.9.6    | Memory Överhead in the Breadth First Approach     | 85         |

|   |   |      | 3.9.7    | Repacking After Garbage Collection                | 85         |

|   |   |      | 3.9.8    | Some Results with CAL-2.0                         | 86         |

|   |   | 3.10 | Conclu   | sions, Related Work, and Future Directions        | 87         |

|   | 4 | BDD  | on a l   | Network of Workstations                           | 91         |

|   |   | 4.1  | Netwo    | rk of Workstations                                | 91         |

|   |   | 4.2  | BDD A    | Algorithms                                        | 92         |

|   |   | 4.3  | BDDs     | on Network of Workstations                        | 93         |

|   |   |      | 4.3.1    | Issues:                                           | 93         |

|   |   |      | 4.3.2    | Solutions:                                        | 94         |

|   |   | 4.4  | Impler   | nentation Issues                                  | 97         |

|   |   | 4.5  | Experi   | mental Results                                    | <b>9</b> 8 |

|   |   |      | 4.5.1    | Exploiting Collective Main Memories               | 99         |

|   |   |      | 4.5.2    | Exploiting Collective Disk Space                  | 100        |

|   |   |      | 4.5.3    | Analysis of Experiments                           | 101        |

|   |   | 4.6  | Relate   | d Work                                            | 102        |

|   |   | 4.7  | Conclu   | usions                                            | 102        |

|   | 5 | Para | allel BD | D Manipulation                                    | 105        |

|   | - | 5.1  |          | el Computer Architectures                         | 106        |

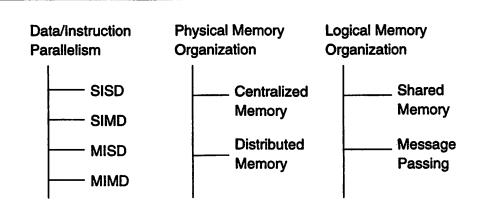

|   |   |      |          | Parallelism in Instruction and Data Streams       |            |

### TABLE OF CONTENTS

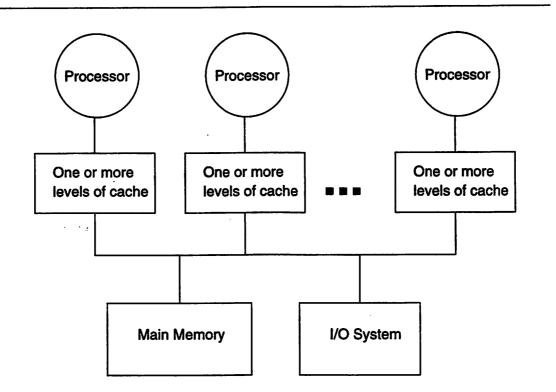

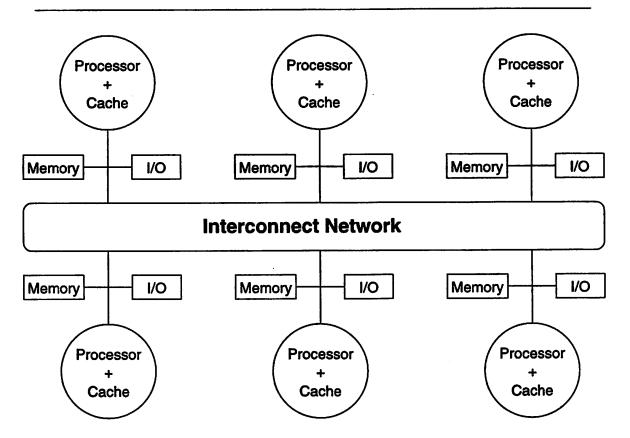

|   |      | 5.1.2   | Memory Organization in Parallel Architecture                                  | 107      |

|---|------|---------|-------------------------------------------------------------------------------|----------|

|   |      | 5.1.3   | Communication Paradigms in Distributed Memory Mach                            | ines 110 |

|   |      | 5.1.4   | Performance Issues in Parallel Computing                                      | 111      |

| - | 5.2  | Using l | Parallel Architecture in BDD Manipulation                                     | 113      |

|   | 5.3  | Previou | as work                                                                       | 114      |

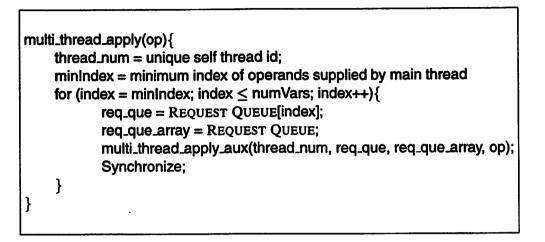

|   | 5.4  | Using l | Multi-threading                                                               | 117      |

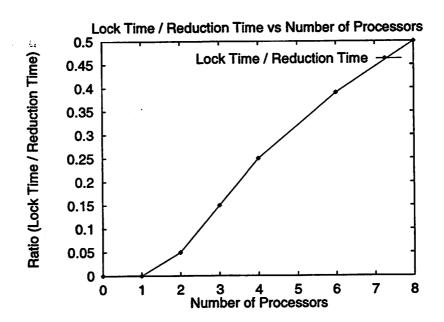

|   |      | 5.4.1   | Bottlenecks in Multi-threading                                                | 119      |

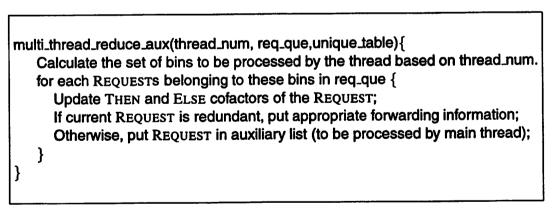

|   | 5.5  | Our Ap  | pproach                                                                       | 119      |

|   |      | 5.5.1   | Analysis                                                                      | 121      |

|   | 5.6  | Related | 1 Work                                                                        | 124      |

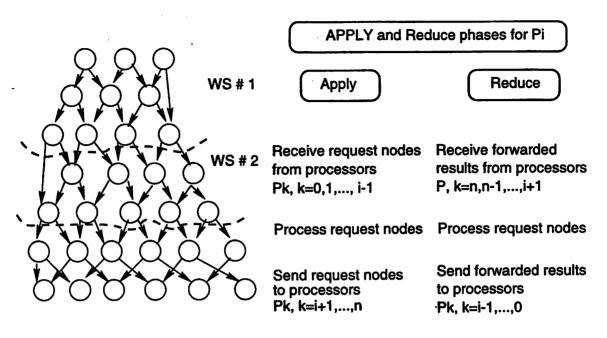

|   |      | 5.6.1   | Parallel Apply and Reduce                                                     | 125      |

|   |      | 5.6.2   | Work Distribution                                                             | 126      |

|   |      | 5.6.3   | Results                                                                       | 126      |

|   | 5.7  | Conclu  | ision                                                                         | 128      |

| 6 | Dyna | mic O   | rdering                                                                       | 129      |

|   | 6.1  | Dynam   | ic Reordering: Background                                                     | 130      |

|   |      | 6.1.1   | Variable Swapping in Depth-First Implementation                               | 131      |

|   | 6.2  | Variab  | le Swapping in Breadth-First Implementation: Problems .                       | 132      |

|   | 6.3  | Solutio | on Approach A                                                                 | 133      |

|   |      | 6.3.1   | Method 1: Keeping <i>index</i> $\leftrightarrow$ <i>page</i> mapping constant | 134      |

|   |      | 6.3.2   | Method 2: Keeping $id \leftrightarrow page$ mapping constant                  | 135      |

|   | 6.4  | Memo    | ry and Computational Overhead Minimization                                    | 136      |

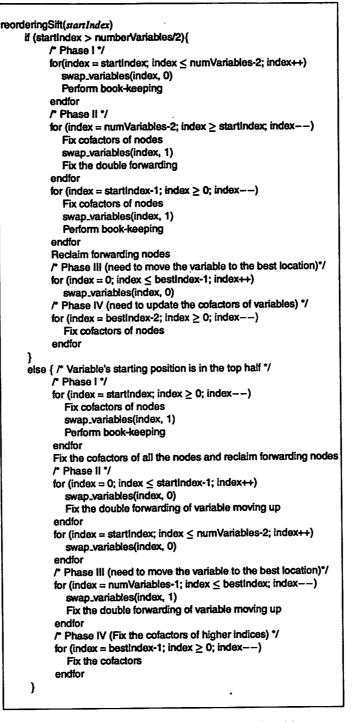

|   | 6.5  | Dynan   | nic Reordering: Sifting Technique                                             | 141      |

|   | 6.6  | Dynan   | nic Reordering : Window Technique                                             | 145      |

|   | 6.7  | Node I  | Packing                                                                       | 146      |

|   | 6.8  | Solutio | on Approach B                                                                 | 147      |

|   | 6.9  | Experi  | mental Results                                                                | 147      |

|   |      | 6.9.1   | Experimental Setup                                                            | 147      |

|   |      | 6.9.2   | Analysis                                                                      | 155      |

|   | 6.10 | Conclu  | usions                                                                        | 155      |

•

•

-

| II | St   | ate Tra  | ansition Graph Representation and Traversal | 157 |  |  |  |

|----|------|----------|---------------------------------------------|-----|--|--|--|

| 7  | Effi | cient Te | chniques for State Space Traversal          | 159 |  |  |  |

|    | 7.1  | Motiva   | Motivation                                  |     |  |  |  |

|    |      | 7.1.1    | Formal Design Verification                  | 160 |  |  |  |

|    |      | 7.1.2    | State Explosion                             | 163 |  |  |  |

|    | 7.2  | Cluste   | red Transition Relations                    | 164 |  |  |  |

|    | 7.3  | Orderi   | ing of Clustered Transition Relations       | 165 |  |  |  |

|    |      | 7.3.1    | Previous Work                               | 168 |  |  |  |

|    |      | 7.3.2    | Our Heuristic                               | 169 |  |  |  |

|    | 7.4  | Netwo    | ork Partitioning                            | 171 |  |  |  |

|    | 7.5  | BDD ]    | Minimization Using Don't Cares              | 173 |  |  |  |

|    | 7.6  | Remov    | ving Redundant Latches                      | 177 |  |  |  |

|    |      | 7.6.1    | Constant Propagation                        | 178 |  |  |  |

|    |      | 7.6.2    | Latch Removal by Retiming                   | 179 |  |  |  |

|    | 7.7  | Experi   | imental Results                             | 182 |  |  |  |

|    |      | 7.7.1    | Clustering                                  | 182 |  |  |  |

|    |      | 7.7.2    | Cluster Ordering                            | 185 |  |  |  |

|    |      | 7.7.3    | Network Partitioning                        | 185 |  |  |  |

|    |      | 7.7.4    | Usage of Don't Cares                        | 187 |  |  |  |

|    |      | 7.7.5    | Redundant Latches                           | 189 |  |  |  |

|    | 7.8  | Summ     | nary                                        | 191 |  |  |  |

| III Sequential Circuit Verification |                    |                                                                  |                                                                                                                                                                                         |  |

|-------------------------------------|--------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Reti                                | iming a            | nd Resynthesis: Complexity Issues                                | 195                                                                                                                                                                                     |  |

| 8.1                                 | Introd             | luction                                                          | 195                                                                                                                                                                                     |  |

| 8.2                                 | Optim              | nization Power                                                   | 197                                                                                                                                                                                     |  |

|                                     | 8.2.1              | Synthesis                                                        | 197                                                                                                                                                                                     |  |

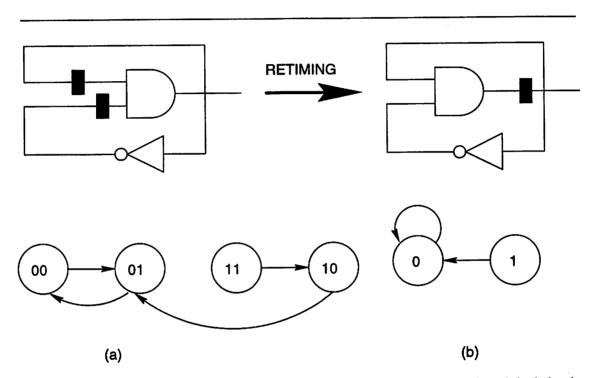

|                                     | 8.2.2              | Retiming                                                         | 197                                                                                                                                                                                     |  |

|                                     | 8.2.3              | Retiming – Resynthesis                                           | 202                                                                                                                                                                                     |  |

|                                     | 8.2.4              | Resynthesis – Retiming                                           | 202                                                                                                                                                                                     |  |

| ]                                   | <b>Reti</b><br>8.1 | Retiming a<br>8.1 Introd<br>8.2 Optim<br>8.2.1<br>8.2.2<br>8.2.3 | Retiming and Resynthesis: Complexity Issues         8.1 Introduction         8.2 Optimization Power         8.2.1 Synthesis         8.2.2 Retiming         8.2.3 Retiming – Resynthesis |  |

### TABLE OF CONTENTS '

|   |      | 8.2.5    | Synthesis – Retiming – Synthesis                           | 203 |

|---|------|----------|------------------------------------------------------------|-----|

|   |      | 8.2.6    | Retiming – Synthesis – Retiming                            | 204 |

|   |      | 8.2.7    | Iterative Retiming and Resynthesis                         | 205 |

| - |      | 8.2.8    | Retiming-Resynthesis vs. General Sequential Optimization 2 | 206 |

|   |      | 8.2.9    | Exposition in Malik's Thesis 2                             | 206 |

|   |      | 8.2.10   | Interpretation and Extensions                              | 209 |

|   |      | 8.2.11   | Sequential Optimization Using Unreachable States           | 218 |

|   | 8.3  | Extend   | ing Notions of Retiming and Synthesis                      | 219 |

|   |      | 8.3.1    | Eliminating Floating Latches                               | 219 |

|   |      | 8.3.2    | Allowing Negative Retiming                                 | 220 |

|   | 8.4  | Verific  | ation Complexity 2                                         | 221 |

|   |      | 8.4.1    | Verification After Retiming                                | 221 |

| • |      | 8.4.2    | Verification After Retiming–Resynthesis                    | 226 |

|   |      | 8.4.3    | Verification After Resynthesis–Retiming                    | 227 |

|   |      | 8.4.4    | Verification After Resynthesis–Retiming–Resynthesis        | 227 |

| • |      | 8.4.5    | Verification After Retiming–Resynthesis–Resynthesis        | 230 |

|   | 8.5  | Summa    | ary and Open Issues                                        | 230 |

|   | 8.6  | Conclu   | ision                                                      | 231 |

| 9 | Veri | ifying R | etimed and Resynthesized Circuits                          | 233 |

|   | 9.1  | Introdu  | action                                                     | 234 |

|   | 9.2  | Previo   | us Work                                                    | 235 |

|   | 9.3  | Prelim   | inaries                                                    | 237 |

|   |      | 9.3.1    | Circuit Model                                              | 237 |

|   |      | 9.3.2    | Notion of Equivalence                                      | 238 |

|   | 9.4  | From S   | Sequential to Combinational2                               | 239 |

|   |      | 9.4.1    | Clocked Boolean function                                   | 239 |

|   |      | 9.4.2    | Event driven Boolean function                              | 241 |

|   | 9.5  | Sequer   | ntial Circuits without Feedback                            | 244 |

|   |      | 9.5.1    | Circuits with Regular Latches                              | 245 |

|   |      | 9.5.2    | Circuits with Load-enabled Latches                         | 247 |

|   | 9.6  | Sequer   | ntial Circuits with Feedback                               | 252 |

|   |      |          |                                                            |     |

.

.

| 9.  | 7 Experi    | mental Setup                                              | 257 |

|-----|-------------|-----------------------------------------------------------|-----|

|     | 9.7.1       | Circuit Modification                                      |     |

|     | 9.7.2       | Retiming                                                  | 257 |

|     | 9.7.3       | Combinational Optimization                                | 257 |

|     | 9.7.4       | Generating Equivalent Combinational Equivalence Problems. | 258 |

| 9.  | .8 Experi   | imental Results                                           | 260 |

|     | 9.8.1       | Analysis                                                  | 264 |

| 9   | 9 Conclu    | usions, Related Work, and Future Directions               | 265 |

| 1   | 0.1 Analy   | sis and Future Directions                                 | 269 |

| IV  | Append      | lix                                                       | 275 |

| A C | AL BDD      | Package                                                   | 277 |

| ΒV  | IS: Verifie | cation Interacting with Synthesis                         | 279 |

| B   | sibliograpl | hy                                                        | 283 |

| I   | ndex        |                                                           | 293 |

.

xi

# List of Figures

-

| 1.1  | Microprocessor clock rate improvement.                             | 3   |

|------|--------------------------------------------------------------------|-----|

| 1.2  | DRAM access time over years                                        | 6   |

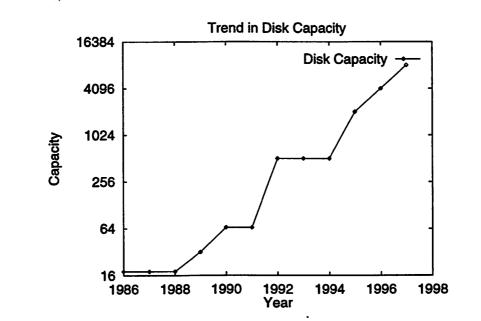

| 1.3  | Trend in disk capacity over the last decade                        | 6   |

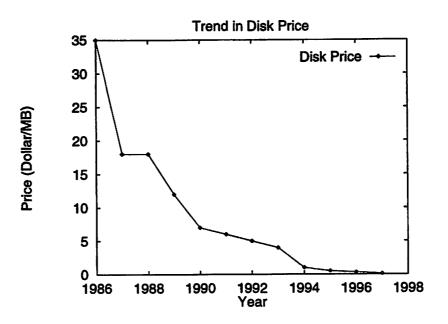

| 1.4  | Trend in disk price over the last decade                           | 7   |

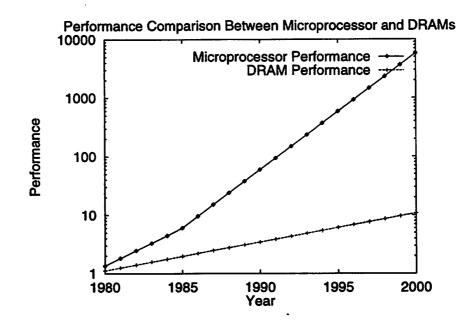

| 1.5  | Performance trend comparison of microprocessors and DRAMs          | 7   |

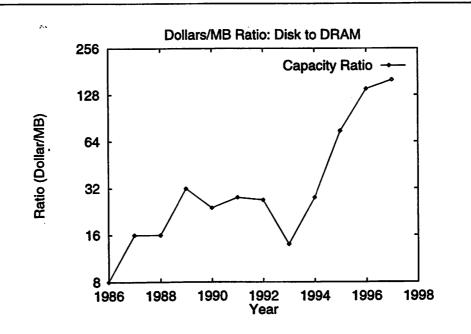

| 1.6  | Disk to DRAM capacity ratio per constant dollar.                   | 8   |

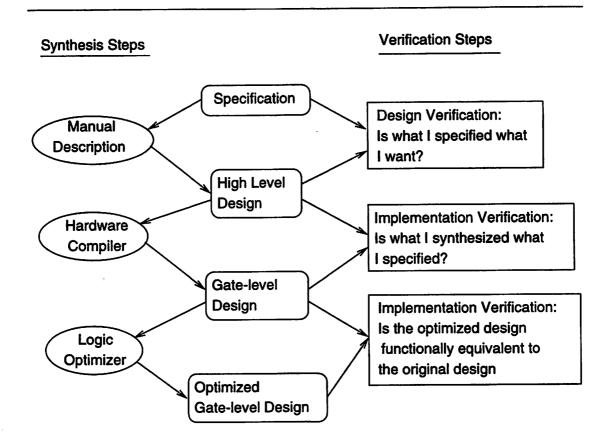

| 1.7  | Typical top-down design methodology                                | 11  |

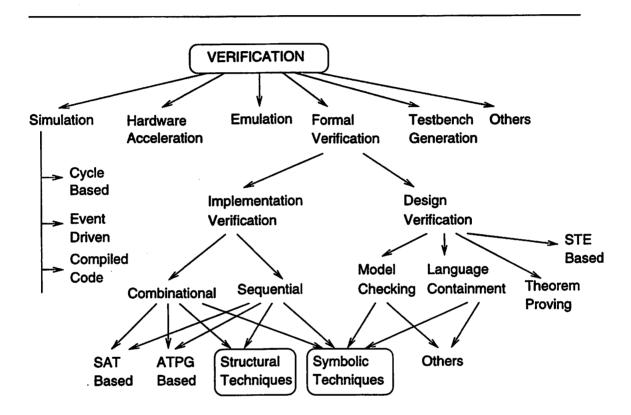

| 1.8  | Overview of verification methodology.                              | 12  |

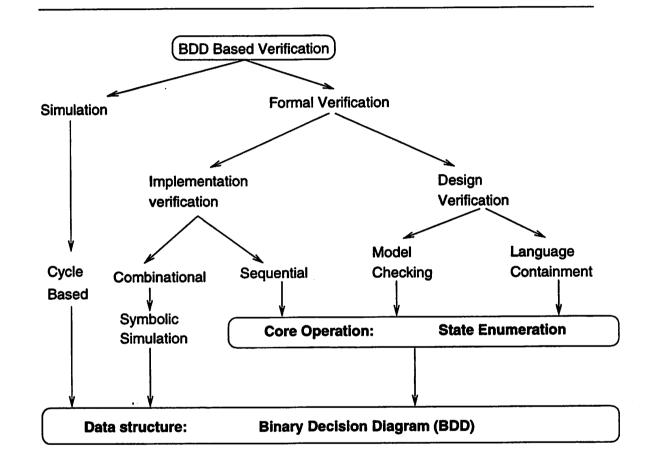

| 1.9  | Overview of BDD-based verification methodology.                    | 15  |

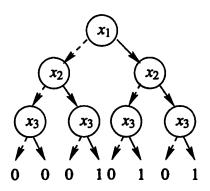

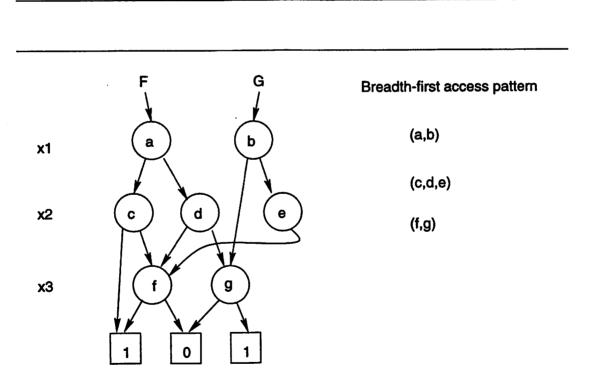

| 2.1  | BDD tree for function $f = x_1x_3 + x_2x_3$                        | 26  |

| 2.2  | BDD graph for function $f = x_1x_3 + x_2x_3$ .                     | 27  |

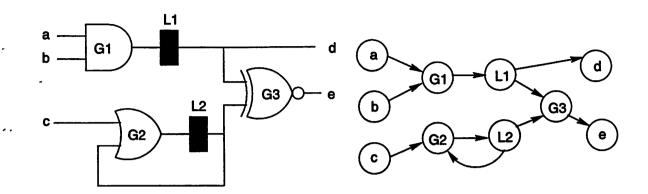

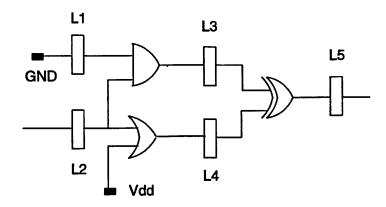

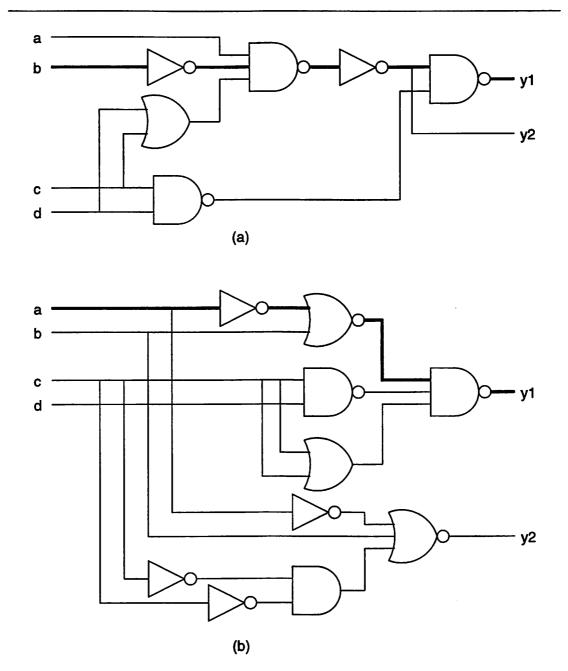

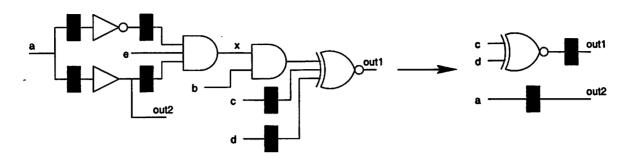

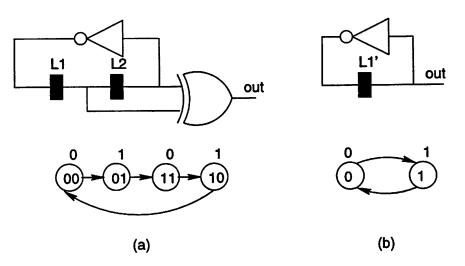

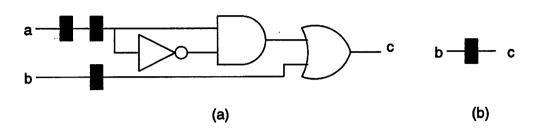

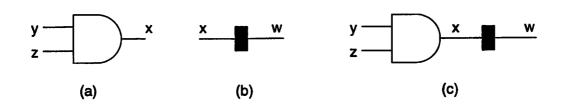

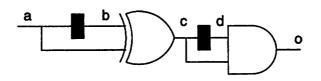

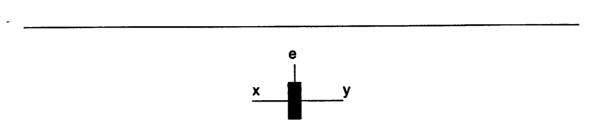

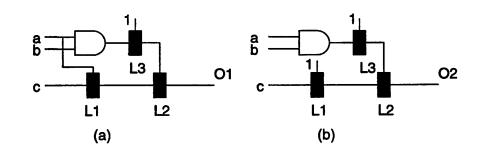

| 2.3  | Example of a sequential circuit and corresponding Boolean network  | 30  |

| • •  |                                                                    | ••• |

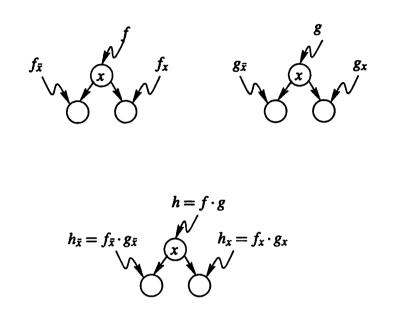

| 3.1  | Computing "AND" of two functions.                                  | 38  |

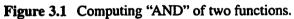

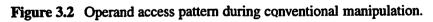

| 3.2  | Operand access pattern during conventional manipulation            | 38  |

| 3.3  | Depth-first traversal of operand BDDs in conventional manipulation | 39  |

| 3.4  | Depth-first BDD manipulation algorithm.                            | 39  |

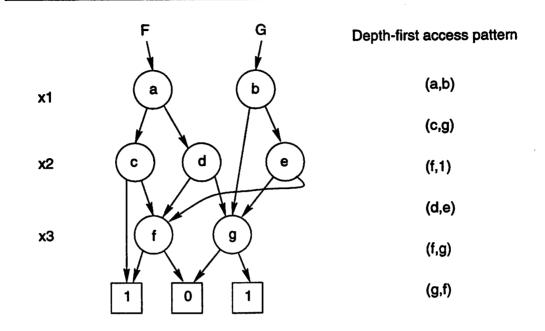

| 3.5  | Problem in localizing memory accesses in depth-first traversal     | 40  |

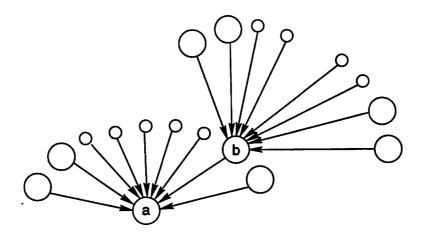

| 3.6  | Operand access pattern during breadth-first manipulation           | 42  |

| 3.7  | Operand nodes access pattern in breadth-first traversal            | 42  |

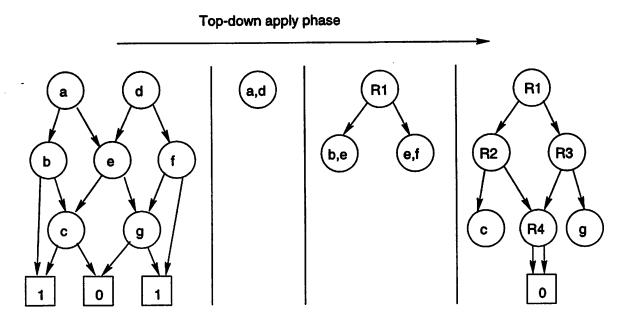

| 3.8  | Illustration of APPLY phase in breadth-first manipulation          | 43  |

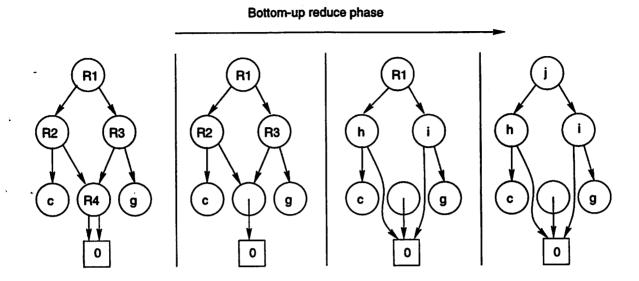

| 3.9  | Illustration of REDUCE phase in breadth-first manipulation         | 44  |

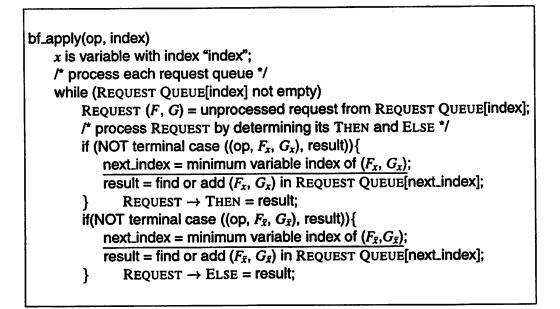

| 3.10 | Breadth-first BDD manipulation algorithm.                          | 45  |

| 3.11 | Breadth-first BDD manipulation algorithm – APPLY                   | 45  |

### LIST OF FIGURES

· -

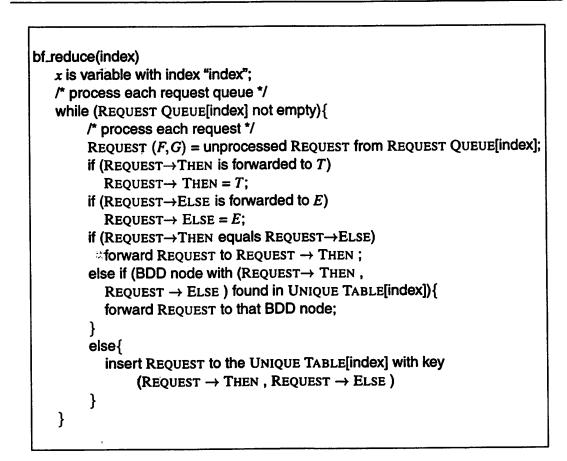

| 3.12 | Breadth-first BDD manipulation algorithm – REDUCE.                                   | 46  |

|------|--------------------------------------------------------------------------------------|-----|

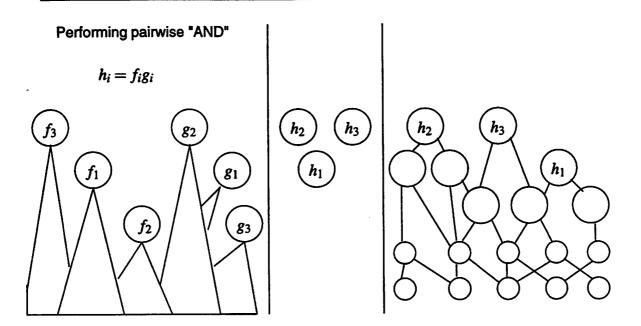

| 3.13 | Multiple independent BDD operations using superscalarity                             | 53  |

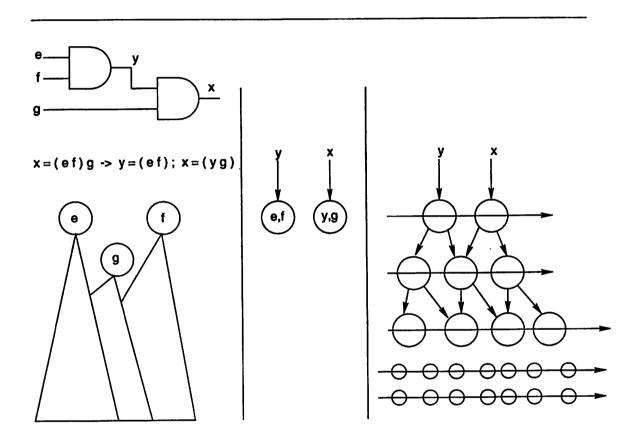

| 3.14 | Multiple dependent BDD operations using pipelining                                   | 57  |

| 3.15 | Depth-first algorithm for SUBSTITUTION.                                              | 60  |

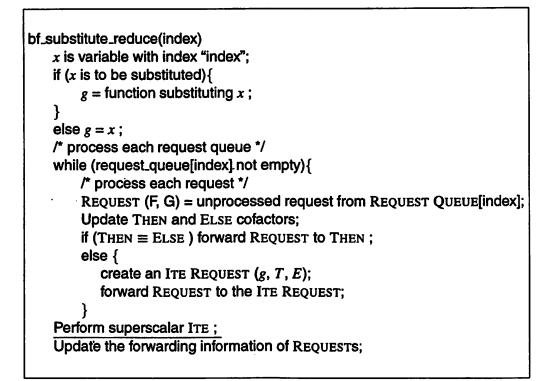

| 3.16 | Breadth-first substitute operation algorithm - REDUCE phase                          | 62  |

| 3.17 | Depth-first algorithm for existential quantification.                                | 63  |

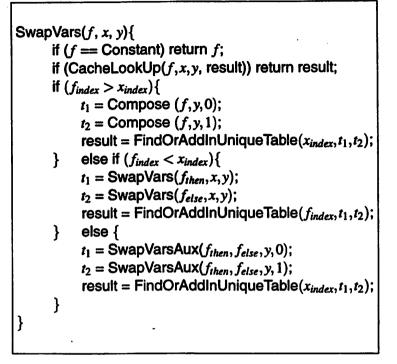

| 3.18 | Depth-first algorithm for swapping variables.                                        | 66  |

| 3.19 | Auxiliary routine for SWAP VARS                                                      | 67  |

| 3.20 | BDD and BDD node data structure.                                                     | 68  |

| 3.21 | Repacking after garbage collection                                                   | 70  |

| 3.22 | Reallocating nodes to achieve cache locality                                         | 72  |

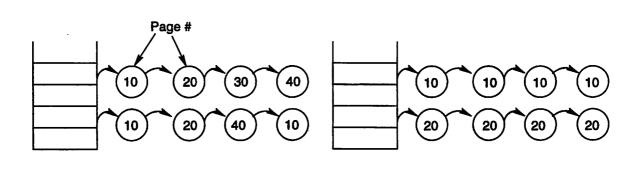

| 3.23 | Node allocation before and after fixing collision chains                             | 72  |

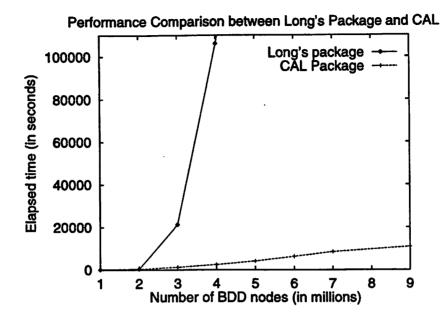

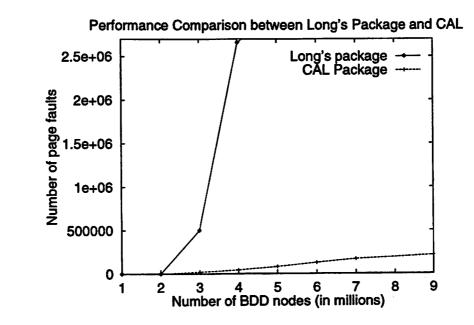

| 3.24 | Variation of elapsed time with example size                                          | 76  |

| 3.25 | Page faults variation with example size.                                             | 77  |

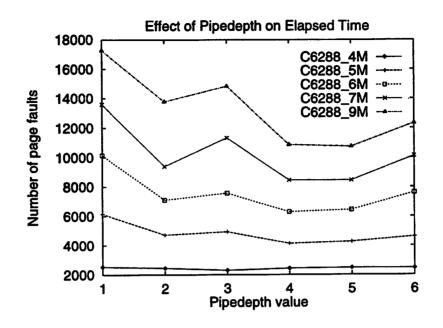

| 3.26 | Variation of elapsed time with pipedepth in creating output BDDs                     | 83  |

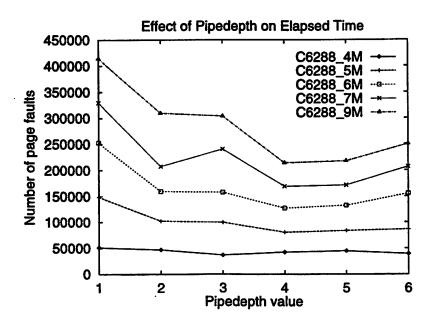

| 3.27 | Number of page faults variation with pipedepth                                       | 84  |

| 4.1  | Breadth-first BDD algorithm on Now.                                                  | 96  |

| 4.2  | Illustration of BDD manipulation algorithm on a NOW.                                 |     |

|      |                                                                                      |     |

| 5.1  | Taxonomy of parallel architectures                                                   |     |

| 5.2  | Basic structure of a centralized shared-memory multiprocessor.                       |     |

| 5.3  | Basic architecture of a distributed-memory machine.                                  | 109 |

| 5.4  | Pre-processing step in multi-threaded BDD manipulation                               |     |

| 5.5  | APPLY step in multi-threaded BDD manipulation                                        |     |

| 5.6  | Request processing during APPLY step.                                                |     |

| 5.7  | REDUCE step in multi-threaded BDD manipulation.                                      |     |

| 5.8  | Request processing during REDUCE step.                                               |     |

| 5.9  | Ratio of lock acquiring time to the total time.                                      | 127 |

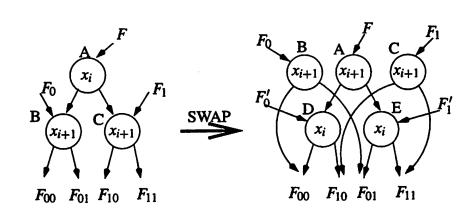

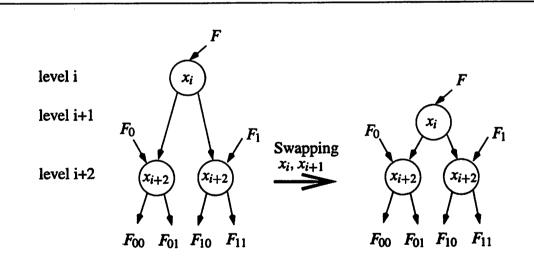

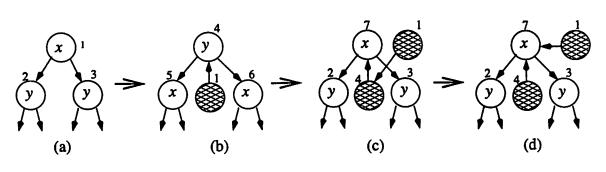

| 6.1  | Variable swapping by overwriting of nodes                                            | 131 |

| 6.2  | Variable swapping in the approach by Ashar <i>et al</i>                              |     |

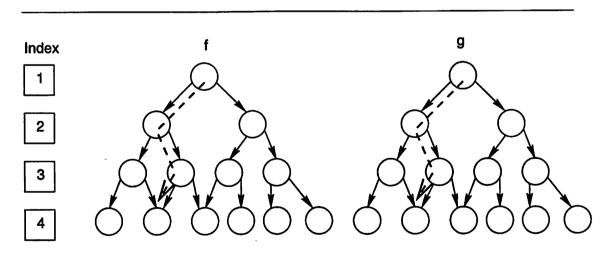

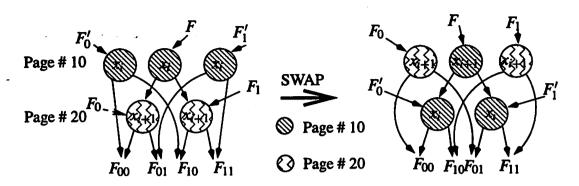

| 6.3  | Variable swapping while keeping <i>index</i> $\leftrightarrow$ page mapping constant |     |

|      |                                                                                      |     |

-

ţ

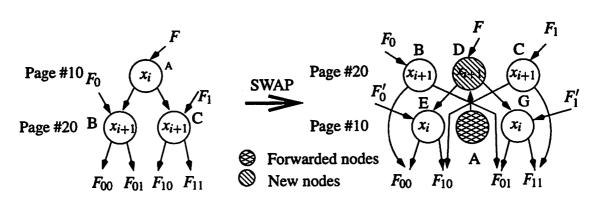

|   | 6.4        | Variable swapping while keeping $id \leftrightarrow page mapping constant$                                  | 135 |

|---|------------|-------------------------------------------------------------------------------------------------------------|-----|

|   | <b>6.5</b> | Algorithm for swapping two variables.                                                                       | 136 |

|   | 6.6        | Variable swapping with no new node                                                                          | 137 |

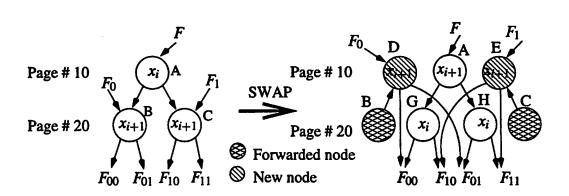

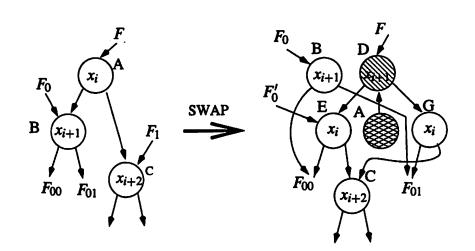

| - | 6.7        | Forwarded node creation during variable swapping.                                                           | 138 |

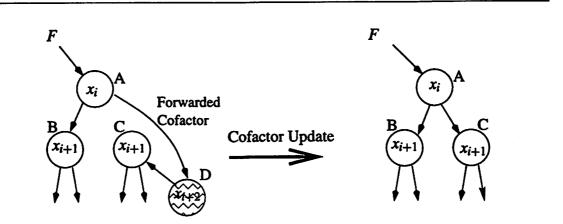

|   | 6.8        | Cofactor updating during variable swapping                                                                  | 139 |

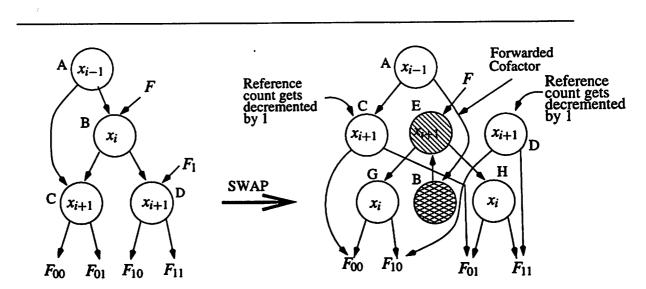

|   | 6.9        | Forwarded cofactors during variable swapping                                                                | 139 |

|   | 6.10       | Double forwarding of nodes.                                                                                 | 140 |

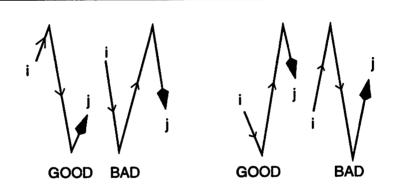

|   | 6.11       | Strategies for sifting variables.                                                                           | 141 |

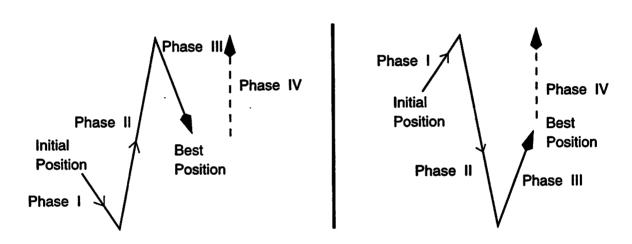

|   | 6.12       | Various phases of sifting a variable                                                                        | 142 |

|   | 6.13       | Pseudo-code for sifting algorithm.                                                                          | 143 |

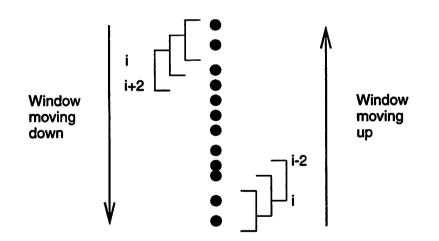

|   | 6.14       | Alternate top-down and bottom-up swapping                                                                   | 145 |

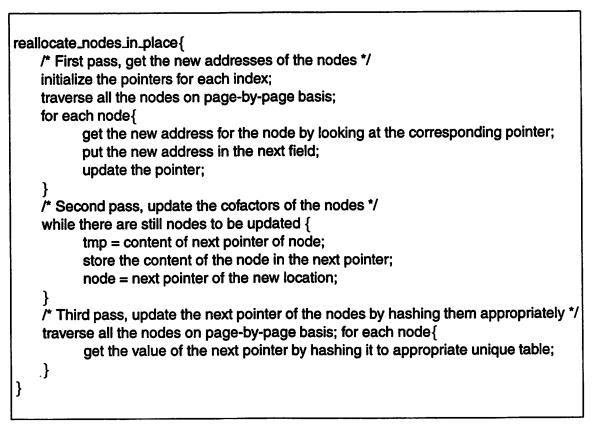

|   | 6.15       | In-place reallocation of nodes to maintain locality.                                                        | 148 |

|   | 71         | An anomala illustratione a Krighta atmostura                                                                | 161 |

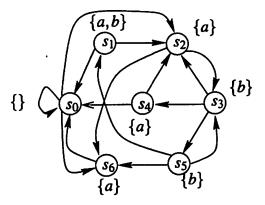

|   | 7.1        | An example illustrating a Kripke structure                                                                  |     |

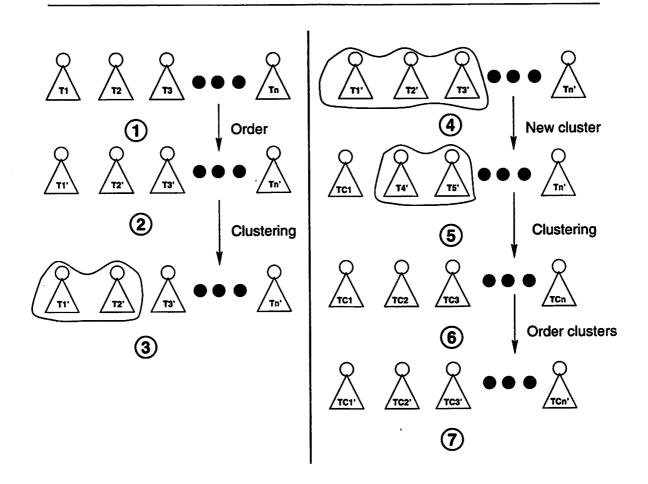

|   | 7.2        | Illustration of ordering and clustering.                                                                    |     |

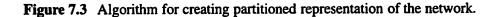

|   | 7.3        | Algorithm for creating partitioned representation of the network                                            |     |

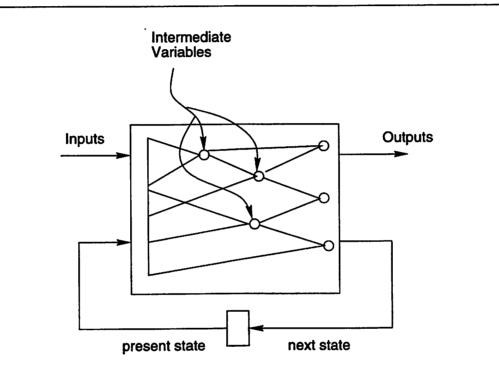

|   | 7.4        | Using intermediate variables to represent transition relation<br>BDD optimization using don't care minterms |     |

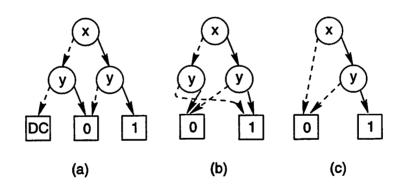

|   | 7.5        | -                                                                                                           |     |

|   | 7.6        | Detecting redundant latches by constant propagation.                                                        |     |

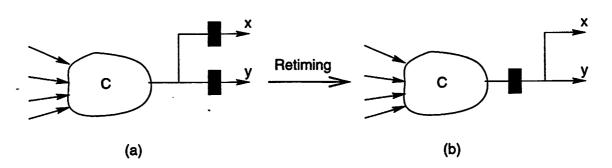

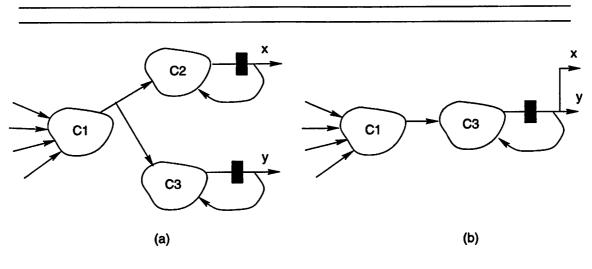

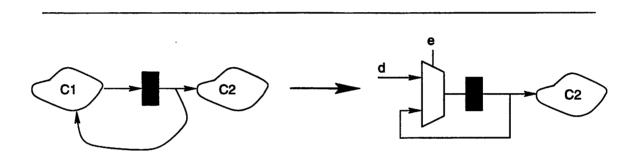

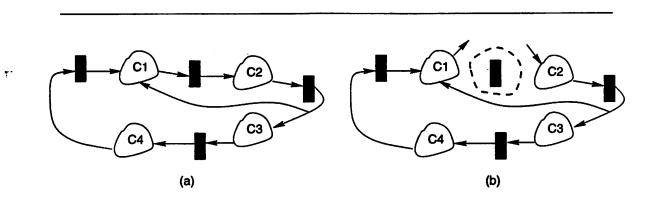

|   | 7.7        | Removing latches by retiming.                                                                               |     |

|   | 7.8        | Removing latch by retiming, a more general case.                                                            |     |

|   | 7.9        | Illustration of effect of partition threshold on the overall BDD size                                       | 190 |

|   | 8.1        | Combinational optimization: area vs. delay trade-off                                                        | 198 |

|   | 8.2        | Retiming: area vs cycle time trade-off                                                                      | 199 |

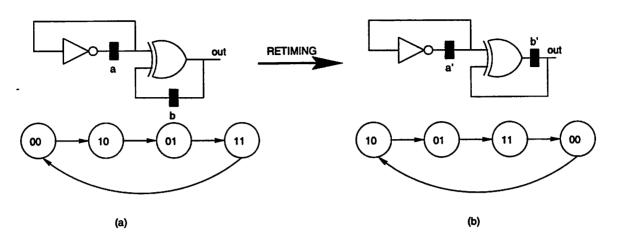

|   | 8.3        | Change in state-encoding during retiming.                                                                   | 200 |

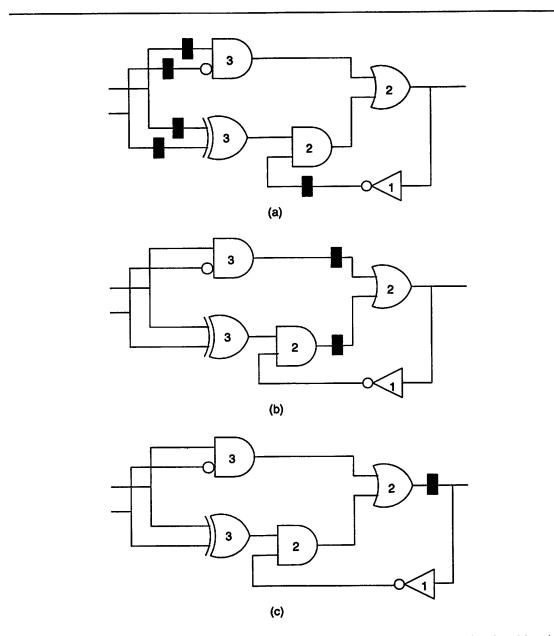

|   | 8.4        | Change in the number of state bits due to retiming                                                          | 201 |

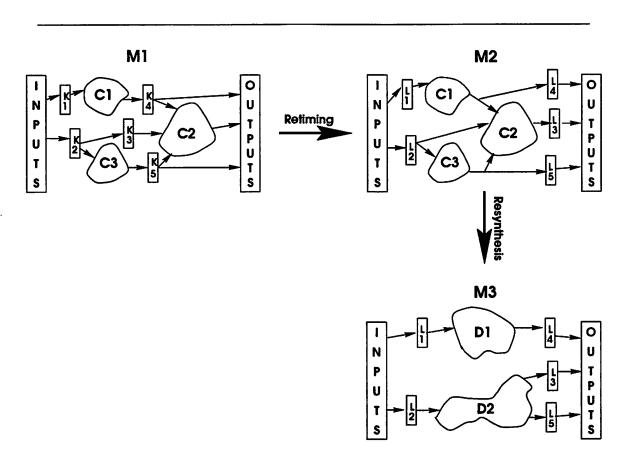

|   | 8.5        | Optimization power of retiming followed by resynthesis.                                                     | 202 |

|   | 8.6        | Optimization power of synthesis followed by retiming                                                        | 203 |

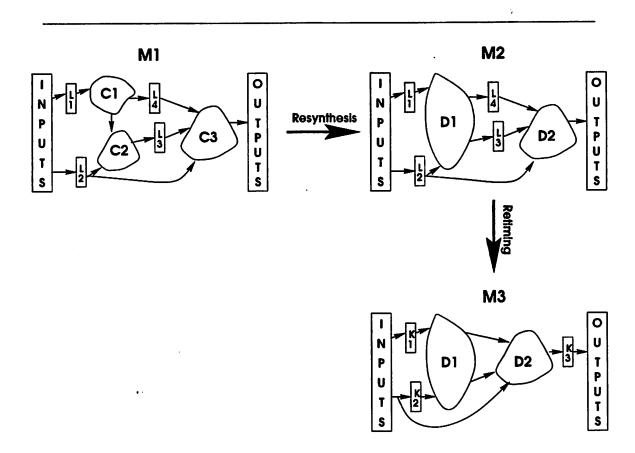

|   | 8.7        | Optimization power of synthesis-retiming-synthesis                                                          | 204 |

|   | 8.8        | Optimization power of retiming-synthesis-retiming                                                           | 204 |

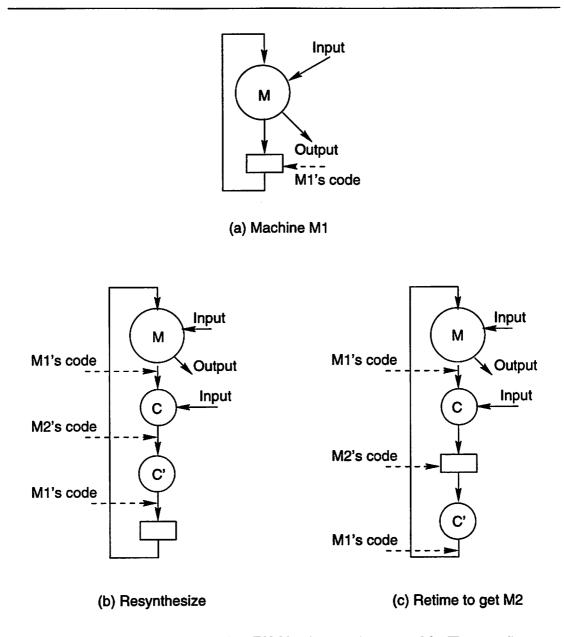

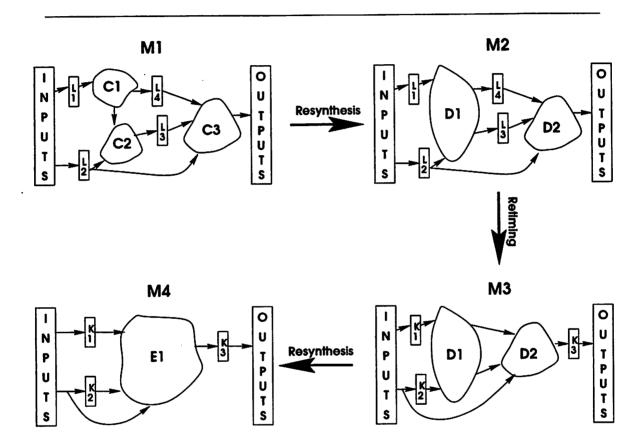

|   | 8.9        | Retiming (R) – synthesis (S) – R – S – R transformations.                                                   | 205 |

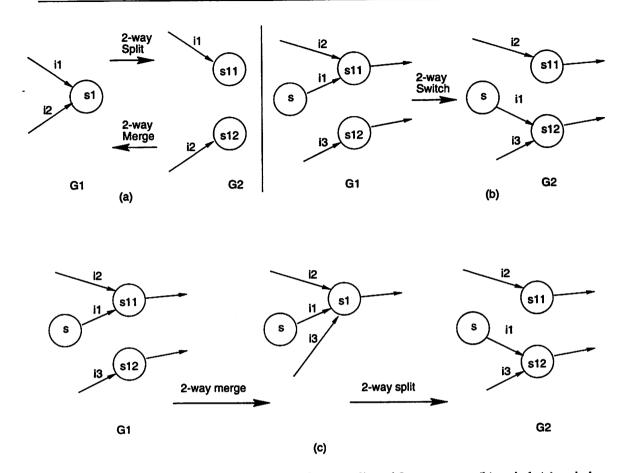

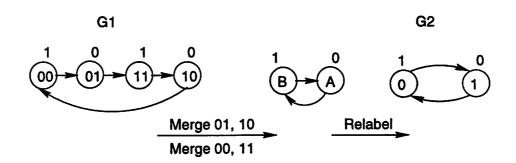

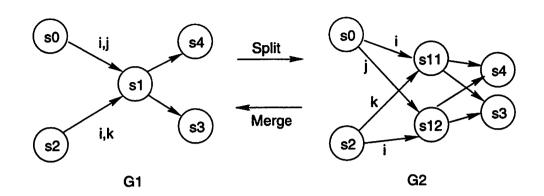

|   | 8.10       | State graph transformations: split, merge, and switch                                                       | 207 |

|   |            |                                                                                                             |     |

#### LIST OF FIGURES

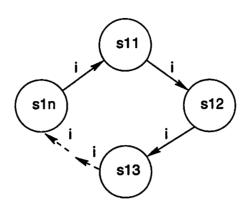

|   | 8.11 | Labeled cycle of equivalent states                                             |

|---|------|--------------------------------------------------------------------------------|

|   | 8.12 | Obtaining equivalent FSM implementations (proof for Theorem 4) 210             |

|   | 8.13 | Counter-example to the assertion in [Mal90] 211                                |

| - | 8.14 | Using CP transformations to obtain the final STG from initial STG. $\dots 212$ |

|   | 8.15 | Counter-example to the proof of the Theorem 4                                  |

|   | 8.16 | Illustration of STG transformation: splitting of states                        |

|   | 8.17 | Illustration of STG transformation: merger of states                           |

|   | 8.18 | Splitting a state with a self-loop                                             |

|   | 8.19 | Non-CP transformations                                                         |

|   | 8.20 | Logic optimization using don't cares derived from unreachable states 219       |

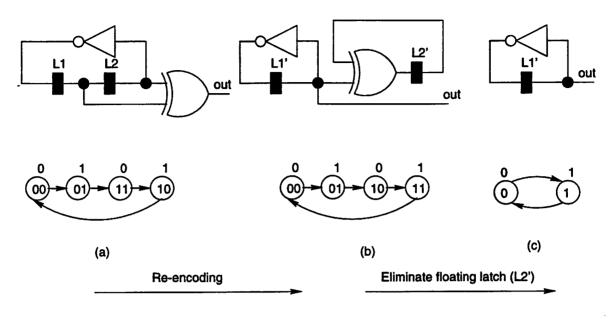

|   | 8.21 | Circuit transformation using floating latch elimination                        |

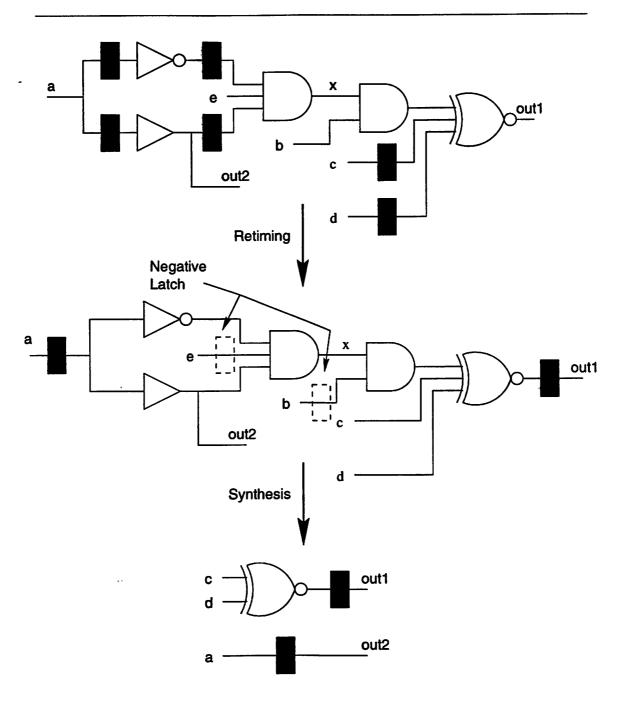

|   | 8.22 | Retiming using negative latches                                                |

|   | 8.23 | Example illustrating optimization using negative latches                       |

|   | 8.24 | Normal retiming has same optimization power as negative retiming 224           |

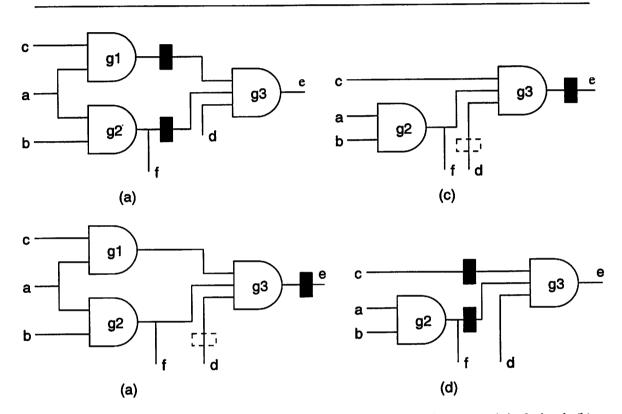

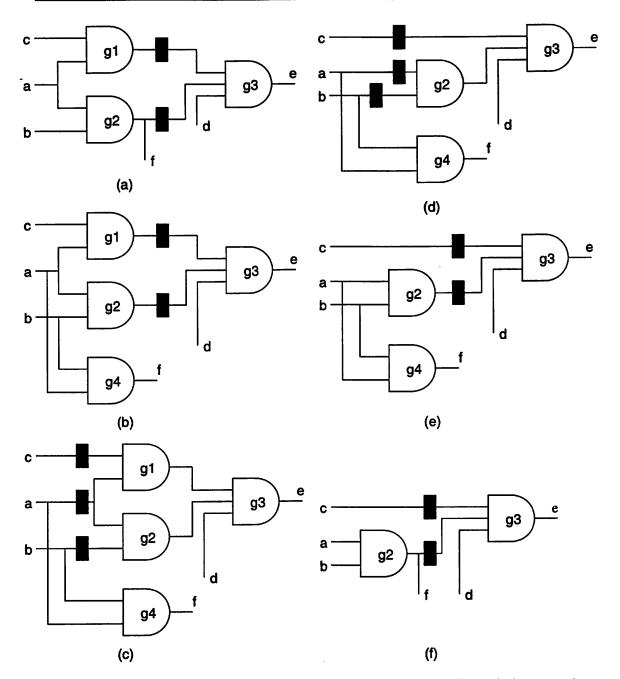

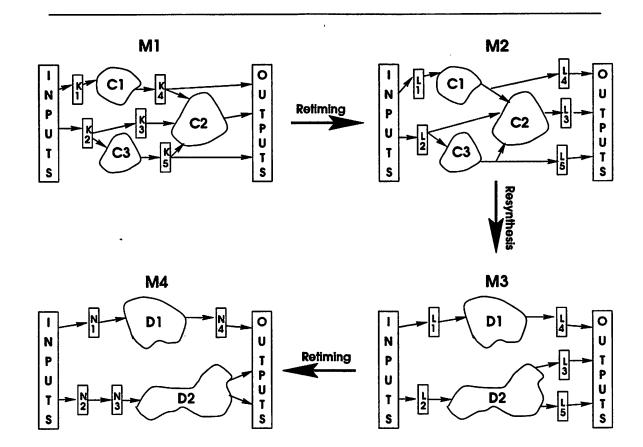

|   | 8.25 | Transformation sequence for retiming followed by resynthesis                   |

|   | 8.26 | Transformation sequence for synthesis followed by retiming 228                 |

|   | 8.27 | Transformation sequence for synthesis (S) – retiming (R) – S 229               |

|   | 8.28 | Transformation sequence for retiming (R) – synthesis (S) – R                   |

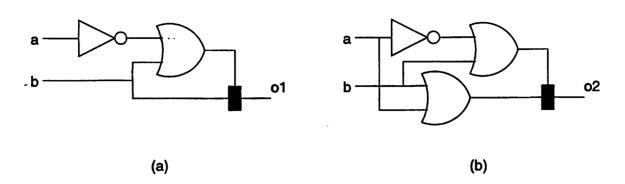

|   | 9.1  | Exact 3-valued equivalence: an illustration                                    |

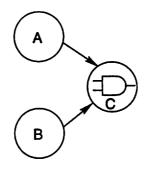

|   | 9.2  | Functionality of AND gate and a latch                                          |

|   | 9.3  | Example of a latch trapped within a combinational block                        |

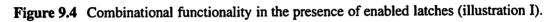

|   | 9.4  | Combinational functionality in the presence of enabled latches: I 243          |

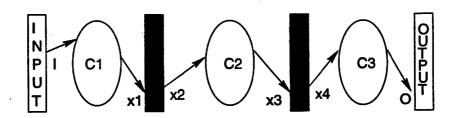

|   | 9.5  | Combinational functionality in the presence of enabled latches: II 243         |

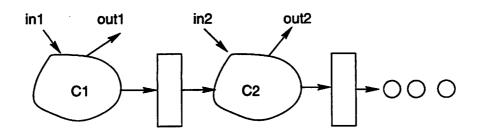

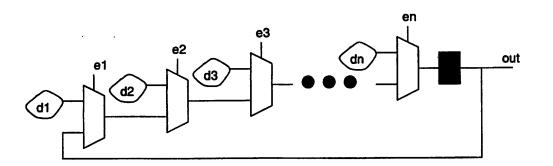

|   | 9.6  | An example of acyclic sequential circuit: pipelined circuit                    |

|   | 9.7  | Computing CBF for outputs of a feedback free circuit                           |

|   | 9.8  | Computing EDBF for the outputs of a circuit                                    |

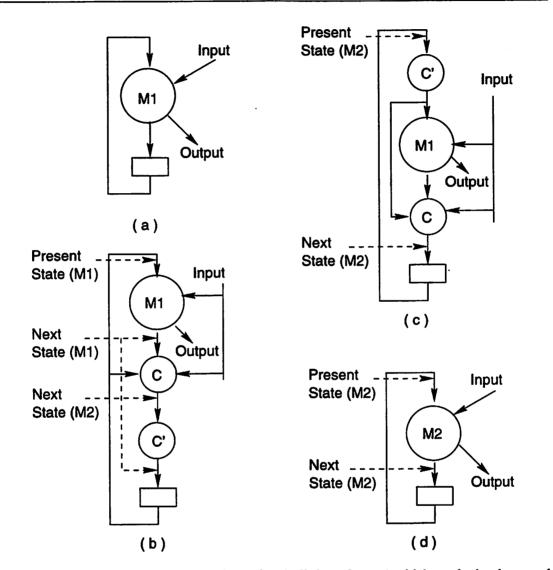

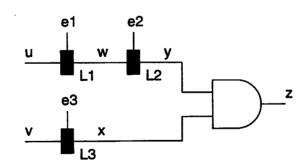

|   | 9.9  | Topological arrangement of latches and combinational blocks                    |

|   | 9.10 | EDBF can lead to false negatives: illustration I                               |

|   | 9.11 | EDBF can lead to false negatives: illustration II                              |

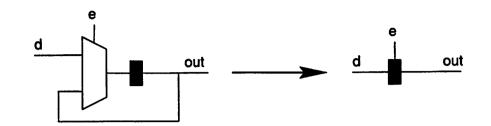

|   | 9.12 | Modeling feedback path for a latch with enable and data signals 252            |

|   | 9.13 | Modeling an enabled latch with extra logic                                     |

|   |      |                                                                                |

,

ċ

| 9.14        | Conditional updating of the latch content                     | 256 |

|-------------|---------------------------------------------------------------|-----|

|             | Making some latches observable to meet the feedback criterion |     |

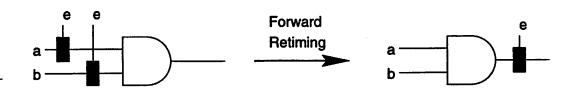

|             | Retiming enabled-latch across gates.                          |     |

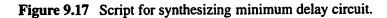

|             | Script for synthesizing minimum delay circuit.                |     |

| 9.18        | Generating equivalent combinational equivalence problems      | 259 |

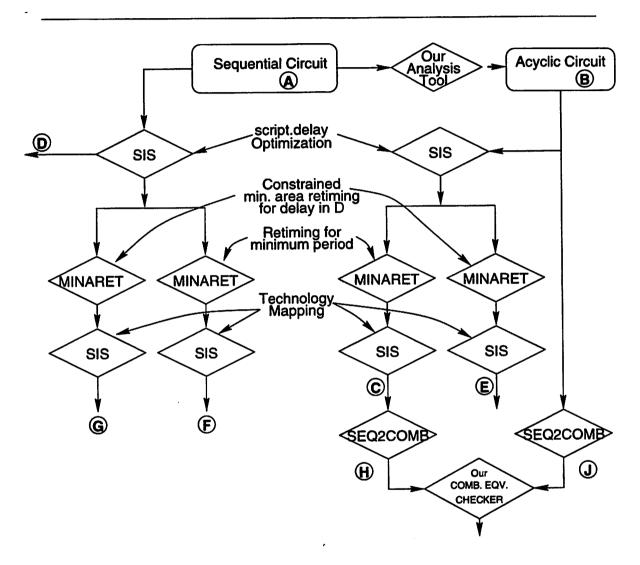

| 9.19        | Flow chart indicating experimental set up                     | 261 |

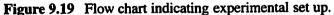

| 9.20        | Feedback paths due to memory and communication layer.         | 262 |

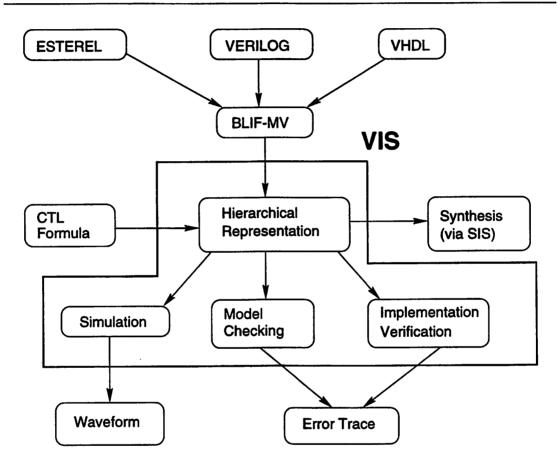

| <b>B</b> .1 | VIS Overview                                                  | 280 |

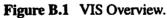

| B.2         | Verification and Synthesis inside VIS.                        | 281 |

|             |                                                               |     |

•

xviii

LIST OF FIGURES

2.932.2 BAT

28 - College Ballachan, and store and state of the store and the state of the store store and the store store at the store of the store And the second ÷Ϋ. and the second : ; · : () **:** 1.1.1.1.1.1

# List of Tables

| 1.1  | Typical levels in memory hierarchy                                 | 5   |

|------|--------------------------------------------------------------------|-----|

| 2.1  | Comparison of expressiveness vs. manipulation complexity           | 28  |

| 3.1  | Performance comparison for creating output BDDs                    | 75  |

| 3.2  | Performance comparison with Long's package                         | 75  |

| 3.3  | Performance comparison on very large sized examples                | 77  |

| 3.4  | Performance comparison with breadth-first approach by Ashar et al  | 78  |

| 3.5  | Performance comparison for various BDD operations.                 | 80  |

| 3.6  | Performance improvement using superscalarity                       | 81  |

| 3.7  | Performance improvement using superscalarity                       | 82  |

| 3.8  | Effect of pipelining on the performance of MULTIWAY AND            | 85  |

| 3.9  | Memory overhead involved with breadth-first manipulation technique | 86  |

| 3.10 | Memory overhead as a function of pipe-depth                        | 87  |

| 3.11 | Reduction in memory consumption due to repacking                   | 88  |

| 3.12 | Comparison between CMU, CU, and CAL-2.0                            | 89  |

| 4.1  | Exploiting collective main memories.                               | 99  |

| 4.2  | BDDs on multiple workstations.                                     | 100 |

| 4.3  | Exploiting remote memory using network RAM (NRAM).                 | 101 |

| 5.1  | Previous work in parallel BDD manipulation: a summary              | 116 |

| 5.2  | Elapsed time for building BDDs with different number of processors | 126 |

| 5.3  | Total number of operations in millions                             | 127 |

| 6.1  | Direct reordering performance comparison.                          | 150 |

| 6.2  | Sifting based reordering: performance and quality comparison       | 151 |

#### LIST OF TABLES

| 6.3 | Window based reordering: performance and quality comparison 152             |

|-----|-----------------------------------------------------------------------------|

| 6.4 | Memory consumption comparison for various packages 154                      |

| 7.1 | Description of industrial examples                                          |

| 7.2 | Results on space-time trade off in clustering by the BDD size approach. 184 |

| 7.3 | Comparison of CPU time for different cluster ordering heuristics 185        |

| 7.4 | Partitioning of the network based on BDD size threshold                     |

| 7.5 | Don't care usage during reachability analysis                               |

| 7.6 | Don't care usage during model checking                                      |

| 7.7 | Effects of redundant latch removal on BDD sizes                             |

| 9.1 | Results on sequential optimization and verification                         |

| 9.2 | Number of latches exposed for some industrial circuits                      |

.

хх

-

.

**1** -

•

÷

# List of Definitions and Theorems

| 1  | Correctness of pipelining                                                                                     | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Image                                                                                                         | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2  | Pre-image                                                                                                     | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3  | Reachable states                                                                                              | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4  | Kripke structure                                                                                              | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2  | Correctness of image computation                                                                              | 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3  | Encoding power of retiming and resynthesis                                                                    | 206                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5  | Labeled cycle of equivalent states                                                                            | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6  | Cycle preserving (CP) transformation                                                                          | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4  | STG transformation via retiming and resynthesis                                                               | 208                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7  | 1-step equivalence                                                                                            | 211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8  | 1-step equivalent transformation                                                                              | 217                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5  | STG transformation via retiming and resynthesis                                                               | 218                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6  | Isomorphism condition                                                                                         | 225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 9  | Exact 3-valued equivalence                                                                                    | 238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 10 | Clocked Boolean Function                                                                                      | 239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11 | Event Driven Boolean Function                                                                                 | 242                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 12 | Sequential depth                                                                                              | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1  | Preservation of latch count and enable sequence                                                               | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7  | Canonicity of CBF                                                                                             | 245                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2  | Latch count and enable sequence                                                                               | 247                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8  | Canonicity of EDBF                                                                                            | 250                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3  | Decomposition condition                                                                                       | 252                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4  | Data-enable decomposition                                                                                     | 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|    | 1<br>2<br>3<br>4<br>2<br>3<br>5<br>6<br>4<br>7<br>8<br>5<br>6<br>9<br>10<br>11<br>12<br>1<br>7<br>2<br>8<br>3 | 1Image2Pre-image3Reachable states4Kripke structure2Correctness of image computation3Encoding power of retiming and resynthesis5Labeled cycle of equivalent states6Cycle preserving (CP) transformation4STG transformation via retiming and resynthesis71-step equivalence81-step equivalence81-step equivalent transformation5STG transformation via retiming and resynthesis6Isomorphism condition9Exact 3-valued equivalence10Clocked Boolean Function11Event Driven Boolean Function12Sequential depth1Preservation of latch count and enable sequence7Latch count and enable sequence8Canonicity of CBF3Decomposition condition |

xxii

and the second secon and the set . • • a thu an Ar • . a service and the service of the ser . . en al 1997 en 1 . and the second second second second second . . • • • ÷ and the state of the 4. State 1. State ... 1 1. T ... · · · · · · · · · • • **.** . and the second

## Preface

THIS thesis has evolved with an aim towards providing efficient techniques targeting the functional verification (i.e., whether the design is specified correctly) and implementation verification (i.e., whether the design is implemented correctly) of finite-state systems.

2

.

The emphasis of the solutions proposed in this work has been more on the practical aspects, in particular their usability and capacity. Keeping usability in mind we have mainly focused on automatic techniques for verifying systems. The underlying motivation behind our work on efficient manipulation of BDDs comes from the fact that most of the current automated design verification algorithms use BDDs as basic data structure.

To establish the capacity of the proposed techniques, we have performed comprehensive experiments with reasonably big instances of designs. In particular, we have been able to build very large BDDs in a order of two less time compared to the state-of-theart techniques. Our technique for sequential circuit verification can verify sequential equivalence of two large ISCAS benchmarks in few minutes.

A significant amount of effort was put in the software implementation aspect of various techniques presented in this thesis. Most of them have been successfully implemented and the software is available in public domain. In particular, our BDD package, named CAL, has also been adopted inside a commercial EDA tool. The package is general enough to be integrated inside any BDD-based system.

I was also involved in the development of the verification tool, VIS, as one of the primary architects. The work on state-space traversal described in this thesis constitutes a fundamental part of model-checking engine of this tool. Over the last 2 years, VIS has been adopted by over 500 people all over the world and has been incorporated as a core engine inside some commercial model checking tools.

—Rajeev Kumar Ranjan Berkeley, California. December 1997.

PREFACE

Alexen - 你还是你不是你了她,你会帮你事儿,你要你们还是你的人,你们不能让你。" n ann a bhailte an Antairte an airt a nas gun a stairte. e de la cale de la contra de la c and a substance of the provident of the second state of the second second second second second second second s • and the state of the second

all is the water of the second second in the skal internet i staljale i se 经推销 化物化合量的 化合理 法法法的法的法 化合金的 化分子子 化化合金合合 and the second distance of the second and the second performance

en la capacitation de constante de la moder de la seconda de la seconda and the Management of the second state of the second second second second second second second second second s a de la sectión de

an io general politica e estandar construction de la presidente en ser e and the an analyzing the first state of a state of the second state of the second state of the second state of the ·新教会教育教育和《新教》的新教会教育。 医白白素 化合成分子 医外外的 动物 副前的 机 er Altreit er en geben der eine Baterne Baterne in der eine Baterne bei der eine Baterne bei der Baterne bei de and the characteristic and the second se

xxiv

$\mathcal{L}_{\mathcal{C}}$

: <u>:</u> :

## Acknowledgements

WHEN I was making plans to write my thesis, I thought that the acknowledgment section would be the easiest one to write. After all, there is a standard format – first of all acknowledge your advisor, other members of your qualifying examination committee, some other faculty members / colleagues you collaborated with, the funding sources – followed by the acknowledgment of your friends for their good company during the long stay for Ph.D. – and finally some sentimental lines for spouse / partner / parents. Mine too would pretty much follow the similar outline. However, what made this process difficult was my intention of succinctly capturing the true essence of my interactions with friends, colleagues, people, and the environment at Berkeley.

In any case, here I go ...\*

÷

First and foremost, I would like to thank my advisor, Prof. Robert K. Brayton, for his guidance, inspiration, encouragement, and support during my graduate years at Berkeley. I consider myself very fortunate to have worked with Bob. His ability to patiently listen to "uncooked ideas" and suggest useful directions is remarkable and so are his perseverance, commitment to work, intellectual curiosity, and technical depth. His constant enthusiasm for everything that the graduate students were involved in is what kept us motivated to achieve higher and higher goals.

I would like to thank Prof. Alberto Sangiovanni-Vincentelli for being the chair of my qualifying examination committee and for his valuable comments on the draft of my thesis. I would like to thank the third reader of this dissertation, Prof. Ilan Adler from IEOR department, for timely review of the thesis. Prof. Paul Hilfinger from Computer Science department and Prof. Adler agreed to serve in my qualifying at a very short notice. I am thankful to them for their consideration.

The continuous sources of funding during the last 5 years have been essential for my survival as a graduate student. First of all, I would like to acknowledge the fellowship

<sup>\*</sup>As a true researcher and to pre-empt any criticism of plagiarism, I would like to mention that similar sentiments have been expressed in the past. In particular [Mur93] and [Swa96] (I got paid to refer to these theses) are worth mentioning.

from Motorola under the URP program. I would also like to acknowledge the funding from California Micro, Fujitsu, and Cadence.

I would like to mention Prof. M. A. Pai from University of Illinios at UrbanaChampaign. He was my advisor at U of I and it was due to his undivided attention to my program that I could finish my M.S. thesis and publish a couple of conference and journal papers, all in less than a year. He always supported me in all my decisions including my transfer to Berkeley. Even after I came to Berkeley, he was always concerned about me and would keep track of my progress throughout my Ph.D.

I take this opportunity to thank my alma-mater Indian Institute of Technology, Kanpur. Getting a Bachelors degree from IIT Kanpur was a turning point in my career, since it opened up a multitude of exciting opportunities.

During my stay at Berkeley, I got a chance to collaborate with a lot of smart people and had the privilege to learn from them. I would like to take this opportunity to express my thanks to my research collaborators.

The work on breadth-first BDD manipulation was done with Jagesh Sanghavi. From him I learned the technique of developing complex software packages using "unit-level debugging". It was with this philosophy that we were able to develop and release an industrial-strength BDD package. Wilsin and I collaborated on the dynamic reordering work inside the CAL package. Often he and I would get together to discuss other research issues. The work on state-space traversal started at Motorola, Austin, where I was an intern in the summer of 1994. I collaborated with Bernard Plessier and Carl Pixley and later with Adnan Aziz. The last part of this dissertation (sequential circuit verification), is the result of my internship at Cadence Berkeley Labs. There I collaborated with Vigyan Singhal and Prof. Fabio Somenzi from University of Colorado at Boulder. I thank them for putting in long hours in brain-storming sessions and discussions.

It was a pleasure being part of the VIS team and I would like to acknowledge the members: Adnan Aziz, Szu-Tsung Cheng, Stephen Edwards, Sunil Khatri, Yuji Kukimoto, Abelardo Pardo, Shaz Qadeer, Sriram Rajamani, Tom Shiple, Gitanjali Swamy, and Tiziano Villa. It was with the group chemistry and team spirit that we managed to put together a high quality model checking tool in just about six months. The success of this project is evidenced by over 500 downloads from various parts of the world in

£

÷

å

÷

ć

the last 2 years. I would also like to thank them for their support and collaboration in organizing the VIS technology-transfer course. It was a great learning experience.

During my stay at Berkeley, going through the myriad of academic requirements would have been very difficult, had it not been for an excellent set of administrative staff to help us. I would like to express my heartful appreciation to the staff at the graduate office. Heather Brown (now Levien), Ruth Gjerde, Mary Byrnes, and Pat Hernan have done an excellent job in patiently dealing with the graduate students' problems and explaining the various intricacies of departmental requirements on a dayto-day basis. I would also like to acknowledge the CAD Group staff for assisting us in various reimbursements, registrations to conferences, business travel, etc. In particular, I would like to mention Flora Oviedo, Kia Cooper, Elise Mills, Gwyn Horn, and Pearl. The last I heard, I was Baby #3 in the Flora's favorite babies' list. I guess I was bumped down since I moved to the South Bay. During my work at Cadence Berkeley Labs, I solicited the assistance of our administrator Kris Lamanno. She is by far the best sysadmin I have come across. I would remember her for her superb efficiency in managing day-to-day activities at the labs and for her sensitive gesture in throwing an impromptu birthday party for me. Thanks to our system administrators Brad and Judd who have done an excellent job in maintaining our huge network of workstations.

I would like to acknowledge all my friends / colleagues / seniors who made work environment a fun place (at 550 Cory, Cadence Berkeley Labs, Synopsys).

Tom Shiple was one of the first few senior graduate students I met in the CAD group. Starting from the days of the logic-synthesis course project for which he was my mentor, we became very good friends. I have always been amazed at his methodical ways in life. I have learned a lot from him. He always found time to listen to my problems – academic or personal – and provide advice as a friend, colleague, or mentor.

I have known Fabio for over 3 years, but it was only during his sabbatical at Cadence Berkeley Labs that I got a chance to closely collaborate with him. Besides him being a true BDD guru, I was quite impressed with his finesse and expertise in Perl, Emacs, deep understanding of ISCAS/MCNC benchmarks, to name a few. Just recently, during ICCAD he asked a question after one of the paper presentation - "How come s1269 is not in the table of results?" I think most of the people in the audience would have been amazed, I was.

"Pre-doctoral qualifying examination" – also known as "prelims" – was the first stressful academic experience I had to go through at Berkeley. I would like to thank my preparation team members – Yuji Kukimoto, Serdar Taşıran, and Harry Hsieh. It would have been difficult going through the whole bunch of conference and journal papers (some of them very boring and irrelevant) without sharing the workload.

Yuji, Serdar, Harry, and I have been good friends since the beginning of graduate years. I admire Yuji's sense of responsibility and ability to deliver on time. So far I have not met anyone else who would consistently turn in the DAC/ICCAD submissions on the advertised date. Serdar was kind enough to bring "Turkish Delights" after every visit to his native country, Turkey. At times, he provided us accompaniment on guitar in our informal singing sessions. Harry enjoyed eating Indian food, and we enjoyed watching him eat. He would love eating spicy food while sweating all over his body.

I would like to acknowledge my cubicle mates. Sriram Krishnan always had passionate ideas on all issues – religion, politics, research – to name a few. Often his outbursts at the tennis court and politically incorrect statements used to be our source of entertainment. Adrian Isles has been a good cubicle mate to me. I was truly impressed by his ability to work long hours in Cory Hall and to combine community service with that. I have known Gitanjali Swamy since IITK days. When she was in the cubicle, she provided us a lot of entertainment in various controversial discussions on feminism, Indian politics, etc., especially those with Sriram Krishnan. After moving to Boston she would call us West coast folks at 7:00am Pacific time. She has done this with me many times and she would start with – "Hope I did not wake you guys up...". Regardless, it is always a pleasure chatting with her.

I also had the privilege of sharing my office space with Dominique Borrione from Grenoble, France. It was great fun celebrating "Bastille Day" at her place. The best part was when people from different countries sang their national anthems. Earlier this year, I had an opportunity to go to Grenoble to teach a VIS tutorial. I will remember Dominique for her hospitality, inviting me over for French cuisine, taking time off to take me around Grenoble and vicinity areas, taking me to the music festival, and not to forget, helping me out in shopping for Renu (my wife).

I had many useful discussions with Desmond Kirkpatrick on various computer related issues – emacs, tcsh, Intel's performance – to name a few. It was refreshing to

-

. .

:..

• •

talk with him about my research, since he always brought in a new perspective. I will remember Chris Lennard for his Australian ways (come to think of it, he IS Australian !!). I remember the time when he threw a party and he and his fellow band members played some rock numbers for the guests. Stephen Edwards was a good source of knowledge about various computer-related things. Arrogant as his attitude may be, we did not hesitate calling him over for dinner and getting some fundamentals on issues like java vs. javascript vs. hotjava. It would always be time effective to know about these things from him (taking into account cooking time, etc.).

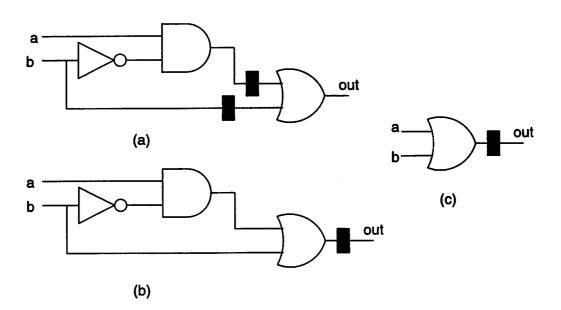

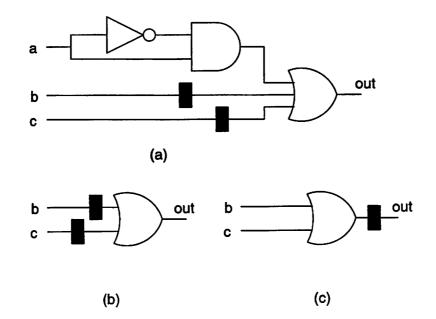

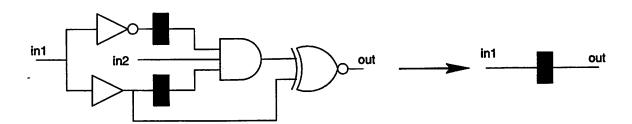

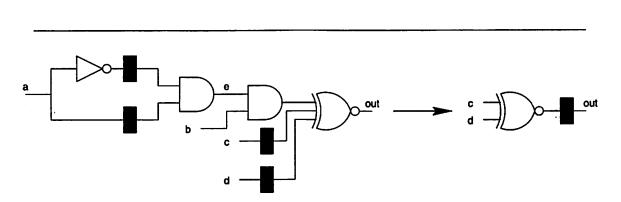

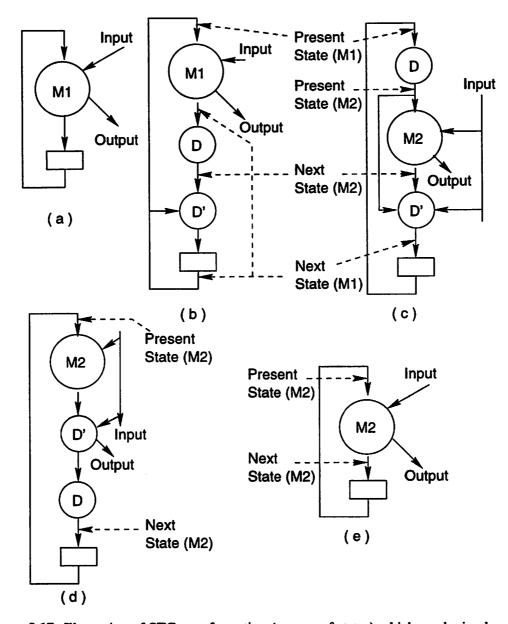

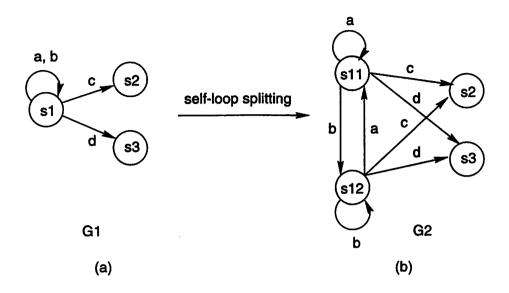

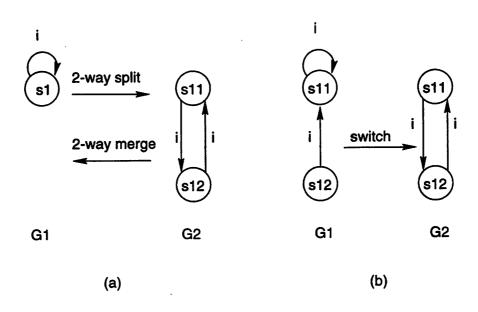

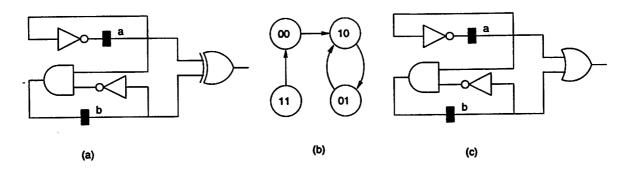

Rajeev Murgai, an "All Time Berkeley Resident", has been a very good friend. His pet peeve with me has been my login name – "rajeev". I would often receive emails from his friends inviting me for some delicious dinner and such and sometimes unpleasant notes from his bosses (hmm... am I lying here?). Anyways, I will remember him most as a wonderful host in parties and for his passion for ballroom dancing. Marco Sgroi was our "Maestro Italiano". I thank him for taking the initiative to teach Italian to some of the enthusiasts in the CAD group. Shaz Qadeer and Amit Mehrotra provided company during bridge sessions. I thank Drs. Alpa and Jagesh Sanghavi for their wonderful Diwali parties which typically involved innumerable delicious dishes. Thanks also to Premal Buch, Luca Carloni, Wilsin Gosti, Harry Hsieh, Sunil Khatri, Gurmeet Singh Manku, Amit Narayan, Roberto Passarone, Mukul Ranjan Prasad, Subarna Rekha, for making 550-Cory a lively place.