# Copyright © 1998, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

#### PROGRAMMABLE, HIGH-DYNAMIC RANGE SIGMA-DELTA A/D CONVERTER FOR MULTISTANDARD, FULLY-INTEGRATED CMOS RF RECEIVER

by

Kelvin Boo-Huat Khoo

Memorandum No. UCB/ERL M98/75

22 December 1998

#### PROGRAMMABLE, HIGH-DYNAMIC RANGE SIGMA-DELTA A/D CONVERTER FOR MULTISTANDARD, FULLY-INTEGRATED CMOS RF RECEIVER

by

Kelvin Boo-Huat Khoo

Memorandum No. UCB/ERL M98/75

22 December 1998

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

# Programmable, High-Dynamic Range Sigma-Delta A/D Converter for Multistandard, Fully-Integrated CMOS RF Receiver

by

Kelvin Boo-Huat Khoo

Master of Science in Electrical Engineering University of California, Berkeley

Professor Paul R. Gray, Advisor

#### Abstract

A major focus of recent RF transceiver IC designs has been to increase both the integration and adaptability to multiple RF communication standards. Performing channel selection on chip at baseband allows the use of high-integration receiver architectures, and enhances programmability to different channel bandwidths and dynamic range requirements of multiple RF standards. A wideband, high-dynamic range sigma-delta modulator can be used to digitize both the desired signal and potentially stronger adjacent-channel interferers. In the digital domain, the decimation filter following the ADC can be easily made programmable.

A 4th-order sigma-delta ADC which is capable of adapting to GSM (cellular) and DECT (cordless) communication standards is described. The ADC achieves 14 bits of resolution at 128x oversampling ratio (200kS/s Nyquist rate) for GSM, and 12 bits of

resolution at 32x oversampling ratio (1.4MS/s Nyquist rate) for DECT. Power reduction strategies are developed at both the sigma-delta architecture and circuit design levels. The experimental prototype, fabricated in a 0.35μm CMOS process, dissipates 70mW from a 3.3V supply.

Approved by:

Paul R. Gray, Advisor

R. Grey

### Acknowledgments

I am grateful to my advisor, Professor Paul R. Gray, for his guidance and support throughout this project. It was both an honor and privilege to work with him. I would also like to thank Professor Bernhard Boser for his invaluable assistance and advice on issues related to the design of sigma-delta modulators. I enjoyed the hours of technical discussions as well as the two graduate-level courses in analog IC design he taught. In addition, I am thankful to Professor Robert Meyer and Professor Robert Broderson for the excellent lectures.

During my two-and-a-half years at Berkeley, I have had the opportunity to work with a number of very talented and interesting individuals. Arnold Feldman, upon whose Ph.D. dissertation a major part of this work has been based, was an excellent mentor. He was always helpful even after his graduation in 1997. I am particularly thankful to Keith Onodera and Andy Abo for sharing their experiences in mixed-signal circuit design and layout issues. Chris Rudell has been a great group leader for this CMOS RF transceiver project and it has been a rewarding experience to work under his leadership. His unique ability to explain complex concepts helped me better understand the system-level receiver architecture design. I am also grateful to Danelle Au for her invaluable assistance on the ADC layout, and for providing comments on this thesis. And to Li Lin, Jeff Ou, Jeff Weldon, Luns Tee, Martin Tsai, Sekhar Narayanaswami, George Chien, Danilo Gerna, Troy Robinson, Todd Weigandt, Masa Otsuka and Carol Barrett for many interesting technical and non-technical discussions.

I would also like to express my gratitude to the many individuals in the department who have made my stay in Berkeley a pleasant and memorable one. Ruth Gjerde in the Graduate Office and Tom Boot have been especially helpful.

Outside of Cory Hall, I am deeply indebted to Terry Heng of Motorola for his unfailing support and guidance throughout my graduate and undergraduate education. He has been an inspirational source for my many daunting undertakings. I am also grateful to my

former professor Terry Sculley who first motivated my interest in analog IC design and who has been a great friend and mentor in the past couple of years. A number of individuals and friends have been particularly helpful on various aspects of my professional and career development. Special thanks to Cormac Conroy, Julian Tham, Keng Fong, Shira Broschat, Mohamed Osman and Kevin Bennett for their time and advice.

Next, I would like to thank my parents, Kuan-Siew Khoo and Poh-Sim Lee, and my brother Melvin for their unyielding love and encouragement. I admire my parents' determination and sacrifice to put me through college. I also wish to express my appreciation to my grandparents for their encouragement and for showing me the virtues of diligence and determination.

Finally, I would like to thank Danelle Au for her special love and friendship through the years. Her patience, support and sense of humor have played an important role in the successful completion of my education at Berkeley.

### **Table Of Contents**

| Chapter 1: Introduction                                                                                     | 1        |

|-------------------------------------------------------------------------------------------------------------|----------|

| 1.1 Motivation                                                                                              | 1        |

| 1.2 Research Goals                                                                                          | 3        |

| 1.3 Thesis Organization                                                                                     | 4        |

| Chapter 2: System Architecture                                                                              | 6        |

| 2.1 Introduction                                                                                            | 6        |

| 2.2 Receiver Architectures  2.2.1 Super-Heterodyne  2.2.2 Direct Conversion  2.2.3 Low-IF Single-Conversion | 7<br>7   |

| 2.2.4 Wideband IF with Double Conversion                                                                    |          |

| 2.3 Baseband Processing                                                                                     | 12<br>12 |

| 2.4 Receiver and ADC Specifications                                                                         | 14       |

| 2.5 Motivations for SD ADCs                                                                                 | 18       |

| Chapter 3: Sigma-Delta Modulators                                                                           | 19       |

| 3.1 Introduction                                                                                            |          |

| 3.2 Quantization Noise                                                                                      | 20<br>21 |

| 3.3 Loop Filter Topologies                                                                                  |          |

| 3.4 Sampled-Data vs. Continuous-Time                                                                        | 26       |

| 3.5 Cascaded (MASH) Architecture                                                                            | 29       |

| 3.6 Summary                                                                                                 | 33       |

| Chapter 4: Modulator Design                                                                                 | 34       |

| 4.1 Introduction                                                                                            |          |

| 4.2 2-2 MASH (Cascaded) Architecture                                                                        | 34       |

| 4.3 Signal Scaling                         | 35 |

|--------------------------------------------|----|

| 4.4 Oversampling Ratio Selection           | 37 |

| 4.5 Power Optimization                     | 37 |

| 4.6 Noise-Shaping and Capacitor Scaling    | 40 |

| 4.7 Linear Settling and Slew Rate          | 41 |

| 4.8 Simulated Results                      | 43 |

| Chapter 5: Integrator and Amplifier Design | 47 |

| 5.1 Introduction                           | 47 |

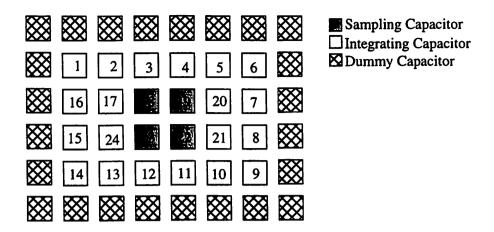

| 5.2 Integrator Design                      | 47 |

| 5.2.1 Switches                             |    |

| 5.2.2 Sampling and Integrating Capacitors  |    |

| 5.3 Operational Transconductance Amplifier |    |

| 5.3.1 Thermal Noise                        | 56 |

| 5.3.2 Flicker Noise                        |    |

| 5.3.3 DC Gain                              |    |

| 5.3.5 Slew Rate                            | 63 |

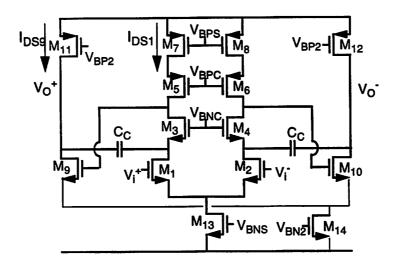

| 5.4 Common-Mode Feedback                   | 63 |

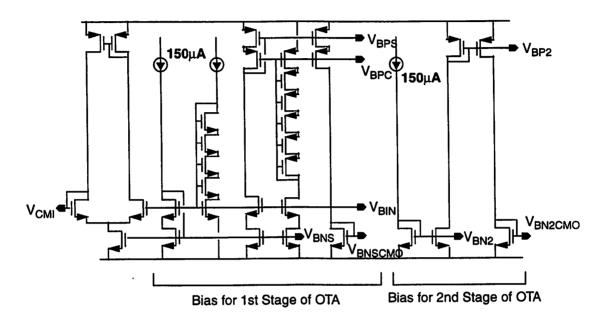

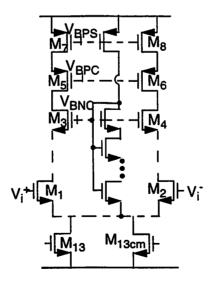

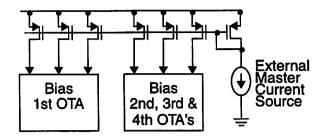

| 5.5 Bias                                   | 64 |

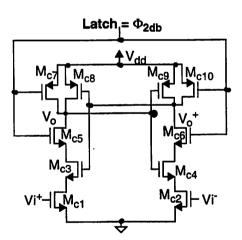

| 5.6 Comparator                             | 66 |

| 5.7 Two-Phase Clock Generator              | 67 |

| 5.8 Output Buffer                          | 68 |

| 5.9 Layout Considerations                  | 69 |

| 5.10 Summary                               | 71 |

| Chapter 6: Simulated Results               | 72 |

| 6.1 Introduction                           | 72 |

| 6.2 Capacitor and Current Values           | 72 |

| 6.3 Dynamic Range                          | 75 |

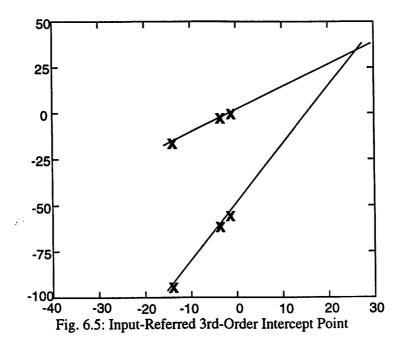

| 6.4 Intermodulation                        | 76 |

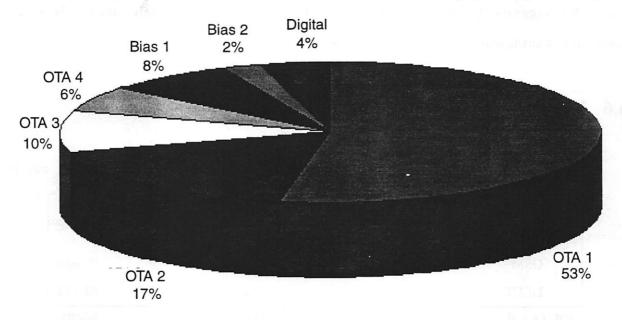

| 6.5 Power Dissipation                      | 77 |

| 6.6 Summary of Simulated Performance       | 79 |

| Chapter 7: Conclusions                     | 82 |

| 7.1 Introduction                           | 82 |

|   | Table Of Contents | vii |

|---|-------------------|-----|

|   | 7.2 Future Work   | 82  |

| : | References        | 84  |

•

•

37

## Chapter 1

# Introduction

#### 1.1 Motivation

The explosive growth in the wireless communications industry has fueled recent research efforts to increase both integration and adaptability/programmability in radio-frequency (RF) transceiver design [1][2][3][4][5][6][7][8][9][10][11].

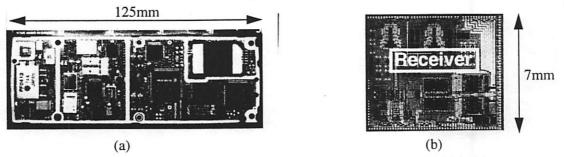

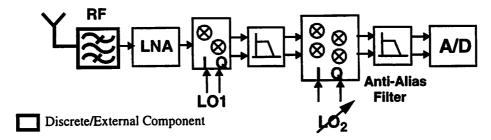

The circuitry of a current cellular telephone is shown in Figure 1.1. It comprises multiple chips and discrete components which are fabricated in different technologies (GaAs, Bipolar and CMOS). One of the goals of this research is to integrate these components onto a single chip in standard CMOS technology, exploiting the performance of modern deep submicron processes. Such a fully-integrated, single-chip solution results in personal communications devices with lower cost and smaller form factor.

Fig. 1.1: RF Receiver Integration. (a) Commercially-implemented multi-chip approach (including DSP) (b) Single-chip solution (without RF filter and DSP)

| Wireless Applications/Services | RF Standards             |

|--------------------------------|--------------------------|

| Cellular Telephony             | GSM, E-GSM               |

|                                | PCS 1900, DCS 1800       |

|                                | CDMA, Wideband CDMA      |

|                                | AMPS                     |

| Cordless Telephony             | DECT, etc.               |

| Wireless LAN                   | IEEE 802.11              |

|                                | Bluetooth, HomeRF        |

| Satellite                      | GPS, Iridium, GlobalStar |

Table 1.1: Major wireless applications and RF standards associated with each application

The increasing variety of wireless applications, coupled with the proliferation of communications standards for these applications--each with its own set of signal bandwidth, blocking profile, and dynamic range and intermodulation requirements--motivate the second goal of this research. Implementing two or more wireless standards in a transceiver design enhances the functionality and flexibility of the personal communications device.

New architectures and circuit techniques need to be explored in the design of fully-integrated, multistandard RF transceivers. One of the more notable challenges lies in the design of low-power, high dynamic range baseband blocks which will coexist on the same substrate as the RF front-end components. The wide dynamic range is necessitated by the elimination of discrete high-Q SAW filters in traditional receivers. In addition, baseband circuits need to adapt to the different dynamic range, linearity and signal bandwidth requirements of multiple communications standards. This programmability can be easily achieved by performing channel selection in the digital domain.

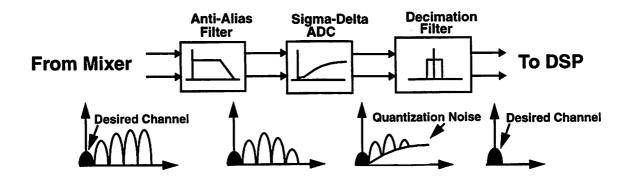

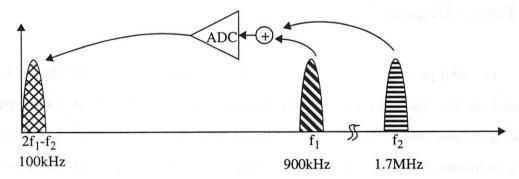

In moving channel selection to the digital domain, a high dynamic range, wideband analog-to-digital converter (ADC) is needed to quantize a small desired signal in the presence of stronger adjacent-channel blockers and interferers. Sigma-delta ( $\Sigma\Delta$ ) modulators are

uniquely suited to this application because the high-pass-shaped quantization noise falls into the same band as the blockers [12]. This implies that a single programmable digital decimation filter following the ADC can attenuate both the quantization noise and blockers.

#### 1.2 Research Goals

The primary aim of this project is to design a programmable, high speed, high dynamic-range sigma-delta ADC for a fully-integrated, multistandard CMOS RF receiver. In particular, the ADC is designed to meet the requirements for (cellular) GSM, PCS 1900, DCS 1800, E-GSM and (cordless) DECT communications standards.

The results of this project are summarized below:

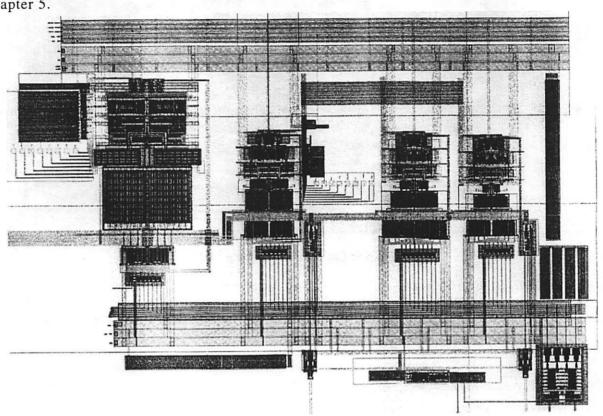

- Designed a sigma-delta modulator which meets the requirements for both cellular (GSM, PCS 1900, DCS 1800, E-GSM) and cordless (DECT) standards. An experimental prototype using a cascade of 2 second-order ΣΔ loops in a MASH configuration. is being fabricated in a 0.35μm double-poly, five-metal CMOS process. The ADC is realized on the same die as the other transceiver blocks (LNA, LO/VCO, mixers, power amplifier, continuous-time filter and DAC). The simulated dynamic range is 95dB and 85dB for GSM/PCS/DCS and DECT, respectively. The modulator dissipates 70mW at Nyquist rates of 200kS/s (GSM/PCS/DCS) and 1.4MS/s (DECT).

- Demonstrated that the same  $\Sigma\Delta$  architecture, differing only in oversampling ratio, can be used to adapt to multiple communications standards.

- Developed a power-saving technique which permits the optimization of the first integrator for each of the standards.

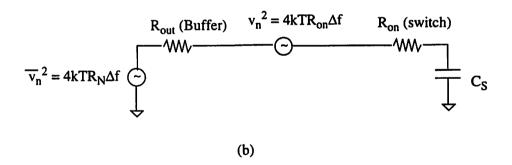

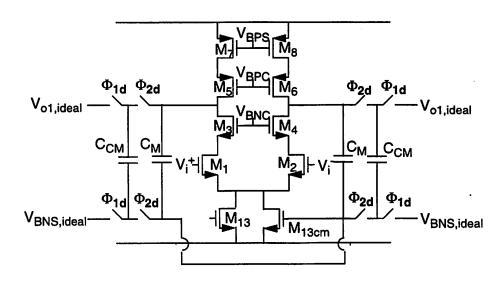

Designed a new fully-differential two-stage transconductance amplifier with an all-NMOS signal path and cascode compensation. This amplifier configuration eliminates the need for a level-shift between the two stages, and allows for the use of a low-power dynamic common-mode feedback.

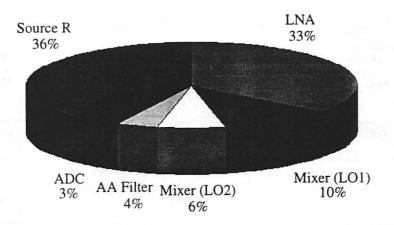

• Showed that the ADC contributes less than 3% toward the receiver noise figure

#### 1.3 Thesis Organization

Following this chapter, Chapter 2 provides an overview of RF system architectures and requirements. It will briefly review the fundamental operation of a conventional superheterodyne receiver, followed by a discussion on receiver architectures which emphasizes high-integration and multi-standard capability. Key receiver specifications and their impact on baseband circuits will be presented. The chapter concludes with motivations for utilizing a  $\Sigma\Delta$  modulator in fully-integrated, multistandard receivers.

Chapter 3 introduces the fundamentals of oversampled sigma-delta modulator design. System-level trade-offs including single-loop versus cascade architectures, and continuous-time versus sampled-data modulators are discussed here.

System-level architecture design of the ADC is presented in Chapter 4. Issues such as the oversampling ratio selection, integrator gain factor, interstage gain mismatch and capacitor scaling are discussed. This is followed by simulated performance of the 2-2 MASH modulator.

Chapter 5 focuses the circuit implementation of the  $\Sigma\Delta$  ADC, with an emphasis on low power optimization. Key trade-offs and challenges in the design of the transconductance amplifier, common-mode feedback network, sampling switches, biasing and digital circuits are discussed.

The simulated results of an experimental prototype of the 4th-order ADC is finally presented in Chapter 6.

Conclusions from this work are given in Chapter 7.

2.1 Introduction 6

### Chapter 2

# System Architecture

#### 2.1 Introduction

This chapter will review fundamental challenges and trade-offs in fully-integrated, multistandard receiver design. A discussion of the conventional Super-Heterodyne receiver architecture will be presented in the next section, followed by a discussion of alternative receiver architectures which are more amenable to single-chip integration and adaptability. The chapter concludes with a summary of receiver specifications and their impact on the baseband sections.

As mentioned in the previous chapter, each communications standard has its own set of requirements. The key figures of merit for wireless receivers are selectivity and sensitivity. Selectivity is a measure of the receiver's ability to select a weak desired channel in the presence of strong adjacent interferers. Sensitivity on the other hand refers to the minimum detectable signal in the presence of electronic noise. Both selectivity and sensitivity are measured at acceptable bit error rate (BER).

A receiver's sensitivity is determined by the RF front-end components while its selectivity by the channel-select blocks. Because channel selection in this project is performed

at baseband, the discussions in subsequent sections will emphasize the effect of the ADC's performance on the receiver selectivity.

#### 2.2 Receiver Architectures

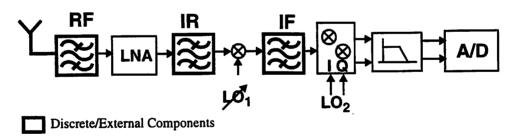

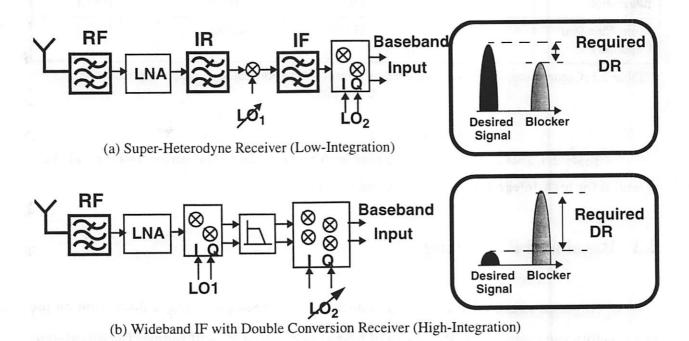

#### 2.2.1 Super-Heterodyne

The conventional Super-Heterodyne architecture, shown in Figure 2.1, is widely implemented in existing commercial designs today. It benefits from the superior performance of external image-reject (IR) and intermediate-frequency (IF) channel-select filters. Because these filters perform channel selection at IF, only low to medium dynamic-range circuits are required at baseband. These discrete components, however, do not make the Super-Heterodyne architecture particularly amenable to higher levels of integration. In addition, the high-Q and low-phase noise associated with discrete inductors and varactor diodes used in the Voltage Controlled Oscillator (VCO) are difficult to realize in an integrated solution [2].

Fig. 2.1: Conventional Super-Heterodyne Receiver Architecture

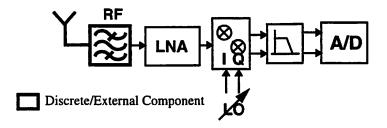

#### 2.2.2 Direct Conversion

An example of a receiver architecture which achieves high levels of integration is Direct Conversion [11]. The virtue of the Direct Conversion architecture is the elimination of discrete IR and IF filters. The incoming RF signal is directly translated down to baseband,

where channel selection is performed. Because no external components (with the exception of the RF filter) are needed in this architecture, and because channel-selection is performed at baseband, Direct Conversion receivers are more amenable to both high-integration and multistandard capabilities.

Fig. 2.2: Direct Conversion (Homodyne) Receiver Architecture

The Direct Conversion architecture has its share of disadvantages. Because the LO is tuned to the same frequency as the incoming RF frequency, there may be LO leakage back to the antenna. This unintentional transmission of the LO signal may reflect off nearby objects and be "re-received." This undesired LO signal then self-mixes with the local oscillator, causing a time-varying or wandering DC offset at the mixer output [2].

Additional DC offsets can be caused by second-order intermodulation of the adjacent-channel blockers. These offsets, coupled with low-frequency 1/f noise, degrade the dynamic range of the receiver. Moreover, a high-frequency, low phase-noise, channel-select frequency synthesizer is difficult to implement with the relatively low-Q elements which are available on-chip.

#### 2.2.3 Low-IF Single-Conversion

The Low-IF architecture [5] alleviates many of the DC offset and low-frequency noise problems of Direct Conversion receivers, while preserving many of the high-integration and multi-mode characteristics. Instead of translating the desired channel down to DC, the Low-IF

architecture mixes the desired band to a low intermediate frequency--typically one or two channel bandwidths away from DC--to avoid the said DC offset and 1/f noise problems.

Fig. 2.3: Low-IF Single-Conversion Architecture

The Low-IF architecture sets a number of constraints on the performance of baseband blocks. Alternate channel blockers are folded in closer to the desired carrier, making it more difficult to filter out the out-of-channel energies. Since the desired signal is a channel or two away from DC, a wider bandwidth ADC is needed to digitize the signal. A higher-order filter and a wider bandwidth ADC result in higher power consumption for the receiver, which is contrary to the goals of this research.

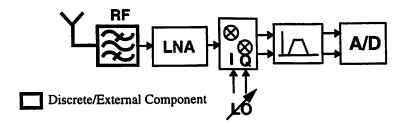

#### 2.2.4 Wideband IF with Double Conversion

The Wideband IF with Double Conversion (WIFDC) architecture [3] used in this research is another example of a receiver which is amenable to high integration and adaptability. Like the conventional Super-Heterodyne architecture, WIFDC employs a two-step conversion from RF to IF and from IF to DC. WIFDC differs from the Super-Heterodyne receiver in that the second, lower frequency LO is made programmable to select the desired band. This somewhat relaxes the phase noise requirements of the local oscillators. At the same time, this architecture mitigates the DC offset errors caused by LO self mixing. This relaxes the offset requirements of the A/D converter at baseband.

Fig. 2.4: Wideband IF with Double Conversion Architecture

|                              | Super-Heterodyne | Direct Conversion | Low-IF Single-<br>Conversion | Wideband IF<br>Double<br>Conversion |

|------------------------------|------------------|-------------------|------------------------------|-------------------------------------|

| Integration                  | LOW              | HIGH              | HIGH                         | HIGH                                |

| Multi-Standard<br>Capability | LOW              | HIGH              | MEDIUM                       | HIGH                                |

Table 2.1: Comparison of Receiver Architectures from a standpoint of Integration and Multi-Standard

Capability

Table 2.1 above summarizes the four architectures described earlier in terms of their potential for high-integration and multi-standard capability.

#### 2.3 Baseband Processing

Now that suitable RF receiver architectures have been presented, a discussion on the functionality and trade-offs in the design of baseband components will follow. The discussions in this section are generic toward any of the high-integration architectures presented in the previous section.

To enhance receiver adaptability, channel selection should be performed at baseband. This indicates that, unlike traditional receivers, both the desired channel and strong adjacent channels will be present at the input to baseband. As a result, the dynamic range required at

baseband is significantly higher than would have otherwise been required in traditional receivers.

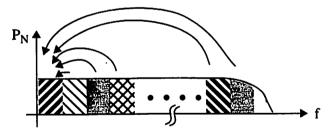

Figure 2.5 illustrates this increased dynamic range requirement for baseband blocks in highly-integrated receivers. In a conventional Super-Heterodyne receiver, the combination of discrete high-Q filters performs channel selection at intermediate frequency (IF) and therefore significantly reduces the required dynamic range of baseband circuits. The elimination of such filters in high-integration architectures like Direct Conversion, Low-IF or WIFDC imposes a more challenging requirement at baseband, where channel selection is performed. The ADC needs to quantize a small desired signal in the presence of strong adjacent blockers.

Fig. 2.5: Increased Baseband Dynamic Range Requirement in Highly-Integrated Receivers

Several options exist for performing channel selection at baseband. The following sections will explore the advantages and disadvantages of the options, with emphasis on low-power, multi-standard design.

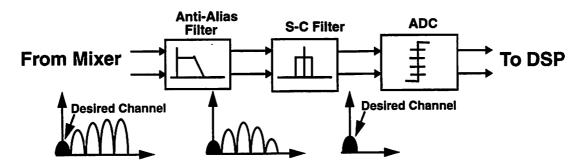

#### 2.3.1 Analog Channel Selection

Channel-select filtering can be done in the analog domain with the use of a high-order, high dynamic range switched-capacitor filter [19]. This filter serves to attenuate adjacent-channel energies while providing some automatic gain control (AGC) on the desired channel in order to further reduce the dynamic range requirement of subsequent stages. Typically, the ADC following the switched-capacitor filter is required to have only 7-8 bits of resolution. A frequency plan of analog channel select is given in Figure 2.6.

Fig. 2.6: Frequency Plan for Analog Channel Selection at Baseband of a Fully-Integrated Receiver

#### 2.3.2 Digital Channel Selection

Alternatively, baseband channel selection can be performed in the digital domain using a digital finite-impulse-response (FIR) filter following the ADC. Because there will be minimal filtering of the RF spectrum prior to the digital filter, we need a wideband ADC which can quantize both the desired signal and the adjacent-channel blockers. In addition, the ADC needs to have a wide dynamic range to accommodate the large blockers described earlier. The advantage of digital channel selection is the increased multi-standard adaptability afforded by the ease of programming the filter in the digital domain.

Fig. 2.7: Frequency Plan for Digital Channel Selection at Baseband of a Fully-Integrated Receiver

#### 2.3.3 Mixed-Signal Channel Selection

A combination of analog and digital filtering may be used to achieve an acceptable compromise between programmability and relaxed ADC requirements. A low- to moderate-dynamic range switched-capacitor filter is typically used to relax the noise and intermodulation requirements of the ADC. This is then followed by a digital programmable filter.

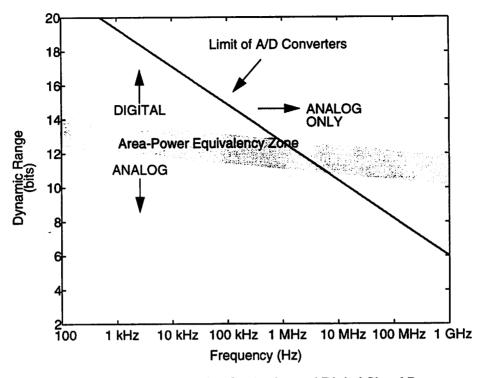

An obvious question is the optimum amount of analog and/or digital filtering for any particular system in order to minimize power dissipation and silicon area. Power and area trade-offs between analog (switched-capacitor) and digital implementations of signal processing functions were examined in detail by Nishimura [20]. His results, shown in Figure 2.8, are applicable for the case of RF baseband processing applications. It should be noted, however, that the graph shows a very generalized trend, and that both power and area are significantly impacted by implementation details such as filter and A/D architectures, circuit techniques and technology.

Fig. 2.8: Preferred Areas of Operation for Analog and Digital Signal Processors

It can be observed that baseband channel selection for GSM, where the signal bandwidth is 100kHz and the required resolution is 14 bits, favors a digital solution. For a wider bandwidth system with lower dynamic range requirements like DECT (12-bit resolution and 700kHz bandwidth), a mixed-signal approach is favorable.

#### 2.4 Receiver and ADC Specifications

The system specifications for various RF communications standards used today are given in Table 2.3 [13]. Based on the noise, intermodulation, and blocking performance requirements of the receiver, the specifications for each individual block in the receiver chain can be derived [13].

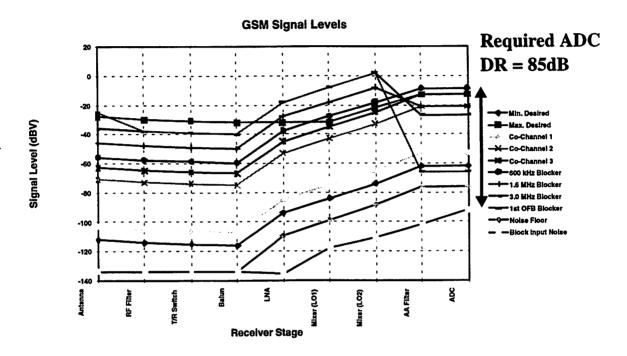

The requirements for the ADC at baseband of the Wideband IF Double Conversion receiver can be determined in a similar fashion by charting out the various signal and blocker

levels going down the receiver chain. Figure 2.9 illustrates this for cellular GSM/DCS/PCS standards. The required dynamic range, for example, is the difference between the largest signal at the ADC input and the allowable noise floor. The noise floor is dictated by the receiver noise figure and the desired ADC noise contribution toward this noise figure. For GSM/DCS/PCS, a receiver noise figure of 3.9dB (from the LNA input to the ADC output) is targeted, and it is desirable that the ADC contribution to the noise figure is minimal.

Fig. 2.9: All possible GSM signal levels at Various Stages of the Receiver Chain

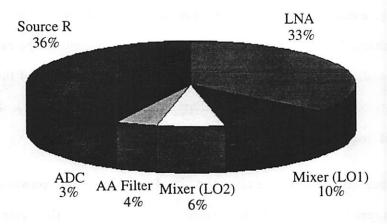

Fig. 2.10: Receiver Noise Contribution

The ADC design specifications for both cellular GSM/DCS1800/PCS1900 and cordless DECT standards at baseband of the WIFDC receiver are given in Table 2.2 below. It can be observed that the dynamic range and intermodulation requirements for the ADC in fully-integrated receivers are significantly higher than those for the conventional Super-Heterodyne receiver.

| *                                                                       | GSM/DCS1800/PCS1900 | DECT     |

|-------------------------------------------------------------------------|---------------------|----------|

| Signal Bandwidth                                                        | 100kHz              | 700kHz   |

| Dynamic Range                                                           | 86dB                | 72dB     |

| Intermodulation: Input-<br>Referred 3rd-Order<br>Intercept Point (IIP3) | 22V                 |          |

| Power                                                                   | Minimize            | Minimize |

Table 2.2: Summary of ADC Design Specifications

| Parameter                        | AMPS                                                   | IS54                                                   | GSM                                | JCP                            | DECT                                    | CT2                                 | PHP                          | 802.11FH            |

|----------------------------------|--------------------------------------------------------|--------------------------------------------------------|------------------------------------|--------------------------------|-----------------------------------------|-------------------------------------|------------------------------|---------------------|

| Origin                           | EIA/TIA                                                | EIA/TIA                                                | ETSI                               |                                | ETSI                                    | UK                                  | Japan                        | IEEE                |

| Access                           | FDD                                                    | FDM/<br>FDD/<br>TDM                                    | FDM/<br>FDD/<br>TDM                |                                | FDM/<br>TDM/<br>TDD                     | FDM/<br>TDD                         | TDM/TDD                      | FH/FDM              |

| Modulation                       | FM                                                     | pi/<br>4QPSK                                           | GMSK,<br>diff                      | pi/<br>4DQPSK                  | GFSK                                    | GFSK                                | pi/4DQPSK                    | (G)FSK              |

| Baseband<br>filter               |                                                        | Root<br>raised<br>cosine                               | Root<br>raised<br>cos.<br>beta=0.3 | Root<br>raised<br>cosine       | Gaussian<br>BT=0.5                      | Gaussian<br>BT=0.5                  | Root<br>Nyquist<br>alpha=0.5 | 500khz LP           |

| Data rate per<br>RF channel      | NA                                                     | 48kb/sec<br>(2bits/<br>symbol)                         | 270.8<br>kb/sec                    | 42kb/sec<br>(2bits/<br>symbol) | 1.152<br>Mb/sec                         | 72kb/sec                            | 384kb/sec                    | 1Mb/sec/<br>2Mb/sec |

| FM Deviation                     | 3kHz                                                   | NA                                                     | NA                                 | NA                             | 288kHz                                  | 14.4-<br>25.2kHz                    | NA                           | ~150kHz             |

| RF Channel frequencies           | 824.04-<br>848.97<br>(Tx)<br>869.04-<br>893.97<br>(Rx) | 824.04-<br>848.97<br>(Tx)<br>869.04-<br>893.97<br>(Rx) | 890-915<br>(Tx)<br>935-960<br>(Rx) |                                | 0:1897.3<br>44Mhz,<br>9:1881.7<br>92Mhz | 1:864.15<br>Mhz<br>40:868.0<br>5Mhz | 1895-<br>1911MHz             | 2.4-2.5GHz          |

| No of RF<br>Channels             | 833                                                    | 833                                                    | 124                                | 1600                           | 10                                      | 40                                  | 52                           | 75                  |

| Channel<br>Spacing               | 30kHz                                                  | 30kHz                                                  | 200kHz                             |                                | 1.728<br>MHz                            | 10kHz                               | 300kHz                       | 1MHz                |

| Synthesizer switching speed      | slow                                                   | slow                                                   |                                    |                                | 30us(BS)<br>450us<br>(HS)               | 1ms<br>(ch-ch)<br>2ms               | 30us(BS)<br>1.5ms(HS)        | several us          |

| Frequency<br>Accuracy            | 2.5ppm                                                 | 200hz                                                  |                                    |                                | 50kHz                                   | 10kHz                               | 3ppm ·                       |                     |

| Speech<br>channels/RF<br>channel | 1                                                      | 3                                                      | 8/16<br>(fuil/haif<br>rt)          | 3/6<br>(full/half<br>rt)       | 12/24<br>(full/half<br>rt)              | 1/1<br>(full/half<br>rt)            | 4/8<br>(full/half rt)        | NA                  |

| Speech<br>coding                 | Analog<br>com-<br>panded                               | VCELP<br>8kb/s                                         | RELP-<br>LTP<br>13kb/sec           | VCELP<br>8kb/sec               | 32kb/s<br>ADPCM                         | 32kb/s<br>ADPCM                     | 32kb/s<br>ADPCM              | NA                  |

| Frame<br>Length                  | NA                                                     | 40ms                                                   |                                    |                                | 10ms(12<br>Tx+12Rx<br>)                 | 2ms<br>(1Tx+1Rx<br>)                | 5ms<br>(4Tx+4Rx)             |                     |

| Peak Power :                     | 3W<br>(6max)                                           | 3W<br>(6max)                                           | 3W<br>(20max)                      |                                | 250mW                                   | 10mW                                | 100mW                        | 1 watt?             |

| Power<br>Control rqmt            | 7 steps                                                | 7 steps                                                |                                    |                                | no                                      | no                                  |                              | no                  |

Table 2.3: Comparison of Wireless RF Standards

#### **2.5** Motivations for $\Sigma\Delta$ ADCs

Sigma-delta modulators are uniquely suited to fully-integrated RF baseband applications for a couple of reasons. First, because their quantization noise is shaped with a high-pass characteristic, most of the noise energies fall in the same band as the undesired blockers. The same digital decimation filter can therefore be used to attenuate both the quantization noise and the blockers [18]. Second, the same  $\Sigma\Delta$  modulator architecture, differing only in oversampling ratio, can be used to adapt to the different dynamic range and bandwidth requirements of multiple RF standards. Chapter 3 reviews the fundamental concepts in sigma-delta modulators.

## Chapter 3

# Sigma-Delta Modulators

#### 3.1 Introduction

This chapter will present a brief overview of key sigma-delta modulator concepts.  $\Sigma\Delta$  modulators trade resolution in time for resolution in amplitude such that the use of imprecise analog circuits can be tolerated. Although commercial sigma-delta A/D and D/A converters have been in existence for more than a decade now, the primary application of such converters has been in digital audio. The narrow bandwidths in digital audio applications have made oversampled converters particularly appealing. It is only recently, as we benefit from the increased speed of submicron devices, that sigma-delta modulators are exploited for wider band systems such as wireless RF communications [12].

The first part of this chapter reviews quantization noise in data converters, and compares the noise spectrum for Nyquist-rate, oversampled, and sigma-delta converters. Different sigma-delta modulator structures are then described, with emphasis on dynamic-range improvement. Finally, trade-offs between single-loop and cascaded (MASH) architectures will be discussed. Readers are referred to [14][15][16][17][18] for a more comprehensive and in-depth review of oversampled ΣΔ design concepts and issues.

#### 3.2 Quantization Noise

#### 3.2.1 Nyquist-Rate Converters

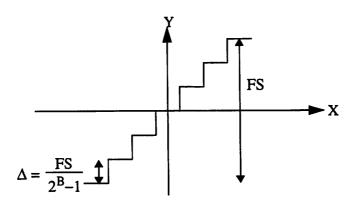

Quantization of amplitude refers to the "mapping" of a continuous amplitude signal to a finite number of discrete levels, is at the heart of all digital modulators. The difference between the original continuous amplitude and the new "mapped" value represents the quantization error. Figure 3.1 illustrates the quantization process. Qualitatively, it can be observed that the quantization error gets smaller as the number of discrete levels increases. The number of levels is in turn proportional to the resolution of the quantizer used in the ADC. Increasing the quantizer resolution will decrease the quantization error.

The error is a strong function of the input; however, if the input changes randomly between samples by amounts comparable to or greater than the spacing of the levels, then the error is largely uncorrelated from sample to sample and has equal probability of lying anywhere in the range of  $\pm \Delta/2$  [15]. Further, if it is assumed that the error has statistical properties which are independent of the signal, the error can then be represented by a noise.

Fig. 3.1: Quantization Process

The quantization noise is given by the mean-square value of the quantization error described above. Using a double-sided spectrum, the quantization noise is given by

$$P_{Q, \text{Nyquist}} = \frac{1}{\Delta} \cdot \int_{-\frac{\Delta}{2}}^{\frac{\Delta}{2}} q^2 dq = \frac{\Delta^2}{12}$$

(Eq 3-1)

and is assumed to fall between  $-f_s/2$  and  $+f_s/2$ , where  $f_s$  is the sampling frequency. In Nyquistrate converters, the sampling frequency is usually twice the signal bandwidth.

#### 3.2.2 Oversampled Converters

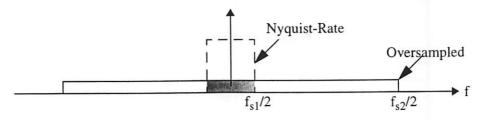

Oversampled converters run at sampling frequencies greater than twice the signal bandwidth. From (Eq 3-1), the quantization noise power is independent of the sampling rate. As such, the quantization noise power in oversampled converters is the same as that for Nyquist-rate converters, but is now distributed over a wider band, as shown in Figure 3.2. The in-band quantization noise is shown by the shaded region, and is given by

$$P_{Q, \text{ Oversampled}} = \int_{-f_{BW}}^{f_{BW}} \frac{\Delta^2}{12} \cdot \frac{1}{f_s} \cdot df = \frac{P_{Q, \text{ Nyquist}}}{\left(\frac{f_s}{2f_{BW}}\right)} = \frac{P_{Q, \text{ Nyquist}}}{M}$$

(Eq 3-2)

where oversampling ratio,  $M = f_s / 2f_{BW}$

Fig. 3.2: Quantization Noise Spectrum in Nyquist-Rate and Oversampled Converters

Increasing the sampling rate therefore reduces the quantization noise power by a fraction M, which is equal to the oversampling ratio. The above analysis assumes that the quantization noise spectrum is white; however, this is not the case in practical systems. A complete modeling of the quantization noise as an additive white-noise source was performed by Bennett [23].

#### 3.2.3 Sigma-Delta Converters

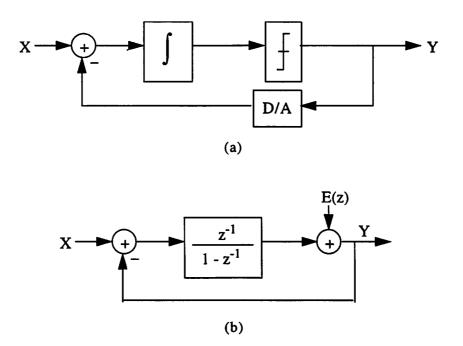

Sigma-delta modulators employs negative feedback in addition to oversampling to further reduce the in-band quantization noise. Figure 3.3 (a) shows a basic first-order sigma-delta modulator. Due to the negative feedback, the output Y will, on average, be force to equal the input signal X. By oversampling the input and then averaging the output, we can very accurately predict the input signal without the need for a high resolution quantizer.

Fig. 3.3: 1st-Order Sigma-Delta Modulator: (a) Simplified Block Diagram (b) Linearized Model

The first-order sigma-delta modulator can be represented by the linearized model shown in Figure 3.3 (b). Since the transfer function from the quantization error source to the

output is given by (1-z<sup>-1</sup>) the noise is shaped by a high-pass characteristic. This suppresses the in-band noise, as quantified by

$$P_{Q, \Sigma\Delta} = \int_{-f_{BW}}^{f_{BW}} \frac{P_{Q, Nyquist}}{M} \cdot (1 - z^{-1}) df \approx \frac{P_{Q, Nyquist}}{M^3} \cdot \frac{\pi^2}{3}$$

(Eq 3-3)

The feedback loop at the heart of sigma-delta modulators is clearly a noise-shaping filter which attempts to cancel the in-band quantization noise by predicting the value of the noise. Higher-order modulators can better predict (and therefore cancel) the in-band quantization noise. A simple feedback theory analysis will show that the transfer function from the quantization noise source to the output is given by  $(1-z^{-1})^L$ , where L is the order of the sigma-delta modulator. This is given by the equation below.

$$P_{Q, \Sigma\Delta} = \int_{-f_{BW}}^{f_{BW}} \frac{P_{Q, Nyquist}}{M} \cdot (1 - z^{-1})^{L} df \approx \frac{P_{Q, Nyquist}}{M^{2L + 1}} \cdot \frac{\pi^{2L}}{2L + 1}$$

(Eq 3-4)

Below is a generalized equation for the in-band quantization in a L-order sigma-delta modulator. The dynamic range (with quantization noise being the only noise source) can be easily derived and is shown below.

$$DR_{\Sigma\Delta} = 10 \cdot \log \left[ \frac{3}{2} \cdot (2^{B} - 1)^{2} \cdot \frac{2L + 1}{\pi^{2}L} \cdot M^{2L + 1} \right]$$

(Eq 3-5)

where B = resolution of quantizer

L = modulator order

M = oversampling ratio

It can be observed that the dynamic range can be increased by increasing the modulator order, the oversampling ratio, or the quantizer resolution. For every doubling of the oversampling ratio, the dynamic range increases by 3(2L+1) dB or (L+0.5) bits.

The disadvantage of using higher-order modulators (3rd-order or higher) is that the modulators may experience limit-cycle oscillations or instability. Techniques to overcome this problem are discussed in [15].

#### 3.3 Loop Filter Topologies

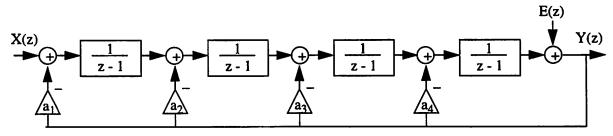

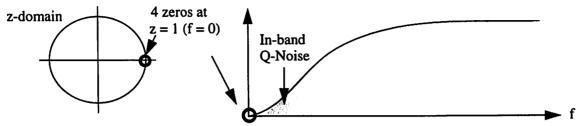

This section aims to review the fundamentals of sigma-delta loop filter design; the topologies presented here are not intended to be an exhaustive in nature; rather, they only represent a cross-section of common commercially-implemented filter designs today. The modulator order is determined by the number of integrator stages in the forward path. In each of the filter topology below, the transfer function from the quantization-noise source to the output will be presented.

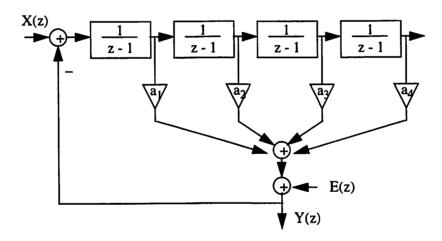

Figure 3.4 illustrates the distributed feedback filter topology for a 4th-order modulator. The output Y(z) is fed back to each of the four integrators through gain stages,  $a_1$ - $a_4$ . The quantization noise transfer function,  $H_e(z)$ , to the output is given by

$$H_{e}(z) = \frac{(z-1)^{4}}{(z-1)^{4} + a_{4}(z-1)^{3} + a_{3}(z-1)^{2} + a_{2}(z-1) + a_{1}}$$

(Eq 3-6)

Note that all the zeros are at z = 1. In the frequency domain, this means the zeros are all at DC. The poles can be implemented using a Butterworth high-pass response for a maximally flat quantization noise spectrum at high frequency.

Fig. 3.4: Distributed Feedback Filter Topology

Fig. 3.5: Frequency Response of Distributed Feedback, Feedforward Summation Topologies

An "inverted" form to the previous topology is shown in Figure 3.6. The output of each integrator is gained and then summed together before feeding into the quantizer. It can be easily shown that the quantization noise transfer function is identical to that for the Distributed Feedback structure, and is given by (Eq 3-6).

Fig. 3.6: Feedforward Summation Topology

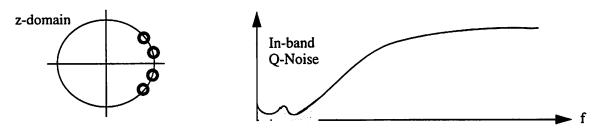

An effective way of suppressing the in-band quantization noise is to spread the zeros over the signal bandwidth instead of placing them all at DC. This can be accomplished by adding local resonator feedback loops in either the distributed feedback or feedforward

summation topologies. The resonators create pairs of complex zeros which allow the use of an Inverse Chebychev response.

Fig. 3.7: Distributed Feedback with Local Resonator Feedback Topology

Fig. 3.8: Frequency Response for Distributed Feedback Topology with Local Resonator Feedbacks

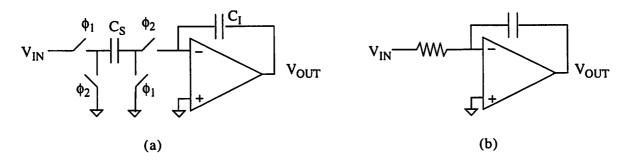

#### 3.4 Sampled-Data vs. Continuous-Time

Sigma-delta modulators can be implemented either as a sampled-data system or in the continuous-time domain. The primary difference is that sampled-data sigma-delta systems employ switched-capacitor integrators while continuous-time systems use active-RC integrators in the modulators. There are a number of advantages and disadvantages associated with each option, as will be discussed below.

Switched-capacitor integrators take advantage of fine-line VLSI capabilities by eliminating the need for physical resistors. On-chip resistors with very high linearity are difficult to achieve in standard CMOS process. In addition, resistors in continuous-time integrators need to be kept small to minimize thermal noise. For the same time-constant,

reducing the resistors implies that the feedback capacitors need to be increased. This may make the area prohibitively large and the capacitors impractical to realize on-chip.

The frequency response of switched-capacitor integrators can be more accurately predicted because the time-constant is a function of capacitor ratios  $(C_S/C_I)$  and of the sampling frequency [22]. The time-constant of continuous-time integrators, on the other hand, is a product of the resistor and the capacitor, and suffers severely from process variations. The absolute value of on-chip poly resistors typically vary by 30% from the nominal/desired value, whereas capacitor ratios are usually more well controlled (typical variation is only 1%).

Fig. 3.9: (a) Switched-Capacitor Integrator (b) Continuous-Time Integrator

Another advantage of switched-capacitor sigma-delta systems is that they are less sensitive to clock jitter and to the manner in which the opamp settles [15]. As long as the opamp settles to the required accuracy, it does not matter whether the opamp slews or linearly settles. Continuous-time integrators, however, must be linear at all times.

Continuous-time systems have their share of advantages over sampled-data systems. Because the opamp in an active-RC integrator does not have to settle to full accuracy every half clock period, a very high oversampling ratio is achievable [21]. The oversampling ratio in switched-capacitor integrators is limited by the achievable bandwidths of the opamps. This makes continuous-time sigma-delta modulators very appealing for high-speed applications.

Finally, continuous-time systems eliminate the need for an anti-alias filter prior to the sigma-delta ADC. The anti-alias filter is needed in sampled-data systems to attenuate energies at multiples of the sampling frequency which may potentially fold down to baseband. The elimination of this filter results in significant power savings for the receiver.

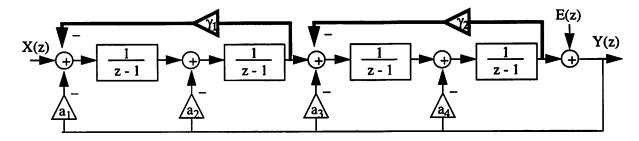

#### 3.5 Cascaded (MASH) Architecture

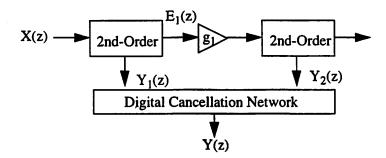

One of the solutions to the instability in high-order modulators is to cascade two or more low-order (1st- or 2nd-order) modulator stages. Stability is guaranteed as long as each individual loops is made stable. Figure 3.10 shows an example of a 2-2 architecture. The cascade of two 2nd-order loops effectively gives a 4th-order noise-shaping performance. With the exception of the first loop, the input to each loop is the quantization error from the preceding loop.

The outputs,  $Y_1$  and  $Y_2$ , are fed into a digital cancellation network prior to the decimation filter. This cancellation network, based on a prediction of the analog interstage gain

Fig. 3.10: Example of a 4th-order (2-2) MASH architecture

g<sub>1</sub>, aims to cancel the quantization error from all but the last stage. The transfer functions from the input and the quantization-noise sources to the output are derived in the equations below.

$$\begin{split} Y_1(z) &= z^{-2} \cdot X(z) + (1-z^{-1})^2 \cdot E_1(z) \\ Y_2(z) &= z^{-2} g_1 \cdot E_1(z) + (1-z^{-1})^2 \cdot E_2(z) \\ Y(z) &= H_1(z) \cdot Y_1(z) + H_2(z) \cdot Y_2(z) \\ &= z^{-4} \cdot X(z) + z^{-2} \cdot (1-z^{-1})^2 \cdot \left(1 - \frac{g_1}{\bar{g}_1}\right) \cdot E_1(z) - \frac{(1-z^{-1})^4}{\bar{g}_1} \cdot E_2(z) \quad \text{(Eq 3-7)} \\ \text{where} \qquad H_1(z) &= z^{-2} \\ H_2(z) &= -\frac{(1-z^{-1})^2}{\bar{g}_1} \end{split}$$

$H_1(z)$  and  $H_2(z)$  are the coefficients of the digital cancellation network which will cancel out the quantization noise from the first modulator loop,  $E_1(z)$ . As can be observed in (Eq 3-7) above, the second term (E<sub>1</sub>) will be effectively cancelled out if the analog gain  $g_1$  matches the digital prediction of the gain  $\overline{g}_1$ .

The following sections will discuss sources of circuit nonidealities which cause the modulator to deviate from the ideal performance given by (Eq 3-5) and (Eq 3-7).

#### 3.5.1 Interstage Gain Mismatch

The variation in the analog interstage gain,  $g_1$ , from its nominal (or digital) value,  $\overline{g}_1$ , is by far the most detrimental source of nonideality in MASH or cascaded modulator structures. From (Eq 3-7), it is clear that any mismatch between  $g_1$  and  $\overline{g}_1$  will not result in a complete cancellation of the quantization noise from the first loop,  $E_1(z)$ . In other words, interstage gain mismatch causes a leakage in quantization noise from the first loop to the output. For a 4th-order modulator, a 2-3% mismatch can result in 20-30dB increase in the in-band quantization

noise. In switched-capacitor circuits, this mismatch is determined by variations in capacitor ratios--and not the absolute values of resistors and capacitors as would be the case for continuous-time implementations.

#### 3.5.2 Finite Opamp DC Gain

The analyses in Section 3.2 assume the use of perfect integrators in the modulator loop(s). The finite DC gain of operational amplifiers, however, causes the integrators to be leaky since the poles are shifted inside the unit circle, as shown in Figure 3.11. This effect can be quantified by

$$\frac{V_{OUT}}{V_{IN}}(z) = \frac{C_S}{C_I} \cdot \frac{z^{-1}}{1 - (1 - \varepsilon) \cdot z^{-1}}$$

where  $(1 - \varepsilon) = \frac{1}{1 + \frac{C_S}{C_I} \cdot \frac{1}{A_{DC}}}$  (Eq 3-8)

From the standpoint of sigma-delta modulators, this translates into the leakage of quantization noise to the output. In addition, insufficient DC gain also degrades the linearity of the system. It should be noted that noise-shaping relaxes the DC gain requirements of the 2nd and subsequent opamps.

Fig. 3.11: Effect of Finite DC OpAmp Gain on Integrator Transfer Function

In a MASH or cascaded architecture, the shift in pole locations results in incomplete cancellation of the quantization noise from the first loop--similar to the effects of interstage

gain mismatch. This can be described by the equations below, where  $\varepsilon_1$ ,  $\varepsilon_2$ ,  $\varepsilon_3$ , and  $\varepsilon_4$  are respectively the errors due to the finite DC gain of opamps 1, 2, 3 and 4.

$$\begin{split} Y_{1}(z) &= z^{-2} \cdot X(z) + [1 - (1 - \varepsilon_{1})z^{-1}] \cdot [1 - (1 - \varepsilon_{2})z^{-1}] \cdot E_{1}(z) \\ Y_{2}(z) &= z^{-2} \cdot g_{1} \cdot E_{1}(z) + [1 - (1 - \varepsilon_{3})z^{-1}] \cdot [1 - (1 - \varepsilon_{4})z^{-1}] \cdot E_{2}(z) \\ Y(z) &= H_{1}(z) \cdot Y_{1}(z) + H_{2}(z) \cdot Y_{2}(z) \\ &= z^{-4} \cdot X(z) + \left\{ z^{-3}(1 - z^{-1})(\varepsilon_{1} + \varepsilon_{2}) + z^{-4}(\varepsilon_{1} \cdot \varepsilon_{2}) \right\} \cdot E_{1}(z) - \\ &\left\{ \frac{(1 - z^{-1})^{2}}{\hat{g}_{1}} [(1 - z^{-1})^{2} + z^{-1}(1 - z^{-1})(\varepsilon_{3} + \varepsilon_{4}) + z^{-2}\varepsilon_{3}\varepsilon_{4}] \right\} E_{2}(z) \end{split}$$

#### 3.5.3 Incomplete Linear Settling and Slew Rate Limitation

The finite bandwidth of operational amplifiers translates into incomplete linear settling in the time domain when the amplifiers are used in switched-capacitor integrators (Figure 3.11). This causes an integrator gain error as shown below.

$$\frac{V_{OUT}}{V_{IN}}(z) \approx \frac{C_S}{C_I} \cdot \frac{z^{-1}}{1-z^{-1}} (1-\epsilon_s)$$

$$Ideal \quad Integrator \quad Gain \quad Xfer Funct. \quad Error$$

(Eq 3-10)

where

$$\epsilon_s = e^{-n_\tau} = 2^{-N}$$

(Settling Error)

$$n_\tau = -\ln(2^{-N})$$

(Number of Time Constants)

$$f_{FB} = \frac{C_1}{C_S + C_1}$$

(Feedback Factor)

(Eq 3-10) above suggests that the higher the required resolution (N) of the ADC, the smaller the tolerable settling error will be. As will be shown in later chapters, this means that a higher bias current is needed in the amplifiers.

The gain error due to incomplete linear settling applies not only to the opamp bandwidth but also to the finite bandwidth of the switching network in the integrator, described below.

$$\frac{V_{OUT}}{V_{IN}}(z) = \frac{C_S}{C_I} \cdot \frac{z^{-1}}{1 - z^{-1}} \cdot \left(1 - 2e^{-\frac{T_S}{4R_{ON}C_S}}\right)$$

$$\downarrow \qquad \qquad \uparrow \qquad \uparrow \qquad \uparrow$$

Ideal Integrator Gain

Gain Xfer Funct. Error

where  $T_s$  = Sampling Period  $R_{ON}$  = "On" Resistance of MOS Switch  $C_S$  = Sampling Capacitor

This implies that we need a small switch on-resistance  $R_{ON}$  to minimize the gain error due to incomplete linear settling.

Fig. 3.12: Finite Bandwidth of Integrator Switching Network

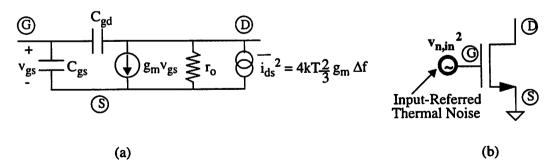

Slew rate, on the other hand, results in harmonic distortion. Note that because the closed-loop unity-gain bandwidth of the amplifier is given by  $(g_m/C_L)f_{FB}$  and its slew rate is given by  $I/C_L$ , and because the  $g_m/I$  ratio is relatively low in short-channel CMOS devices, linear settling requirements usually dictate the required opamp power dissipation.

#### 3.6 Summary

This chapter reviewed important concepts in the design of sigma-delta modulators. The benefits of sigma-delta modulators as data converters were first presented, and were contrasted with conventional Nyquist-rate converters. The concept of noise-shaping was discussed. Next, various options for loop filter design were investigated, with emphasis on strategies to suppress the in-band quantization noise by spreading the zeros over the signal bandwidth. This was followed by a discussion on sampled-data versus continuous-time implementations. The chapter concluded with the MASH or cascaded architecture, and the circuit nonidealities which affect its performance. The implications and severity of the nonidealities will be presented in the next chapter.

## Chapter 4

# Modulator Design

#### 4.1 Introduction

This chapter describes the architecture techniques which can be employed to enhance the system-level modulator performance. The 2-2 MASH architecture used in this design is then presented, along with a discussion on adaptability to both GSM/DCS and DECT standards. This is followed by a discussion on the selection of oversampling ratio and integrator gain factors. Simulation results which show noise shaping, SQNR and dynamic range of the modulator are then presented.

#### 4.2 2-2 MASH (Cascaded) Architecture

A fourth-order modulator was selected because it was sufficient to achieve 14 bits of resolution for a 200kS/s Nyquist rate (GSM) and 12 bits of resolution for a 1.4MS/s Nyquist rate. The MASH architecture was selected over a single-loop 4th-order modulator because of its inherent stability. It must be noted, however, that the MASH architecture has its share of disadvantages, most notably its sensitivity to gain mismatch as discussed in Section 3.5.1.

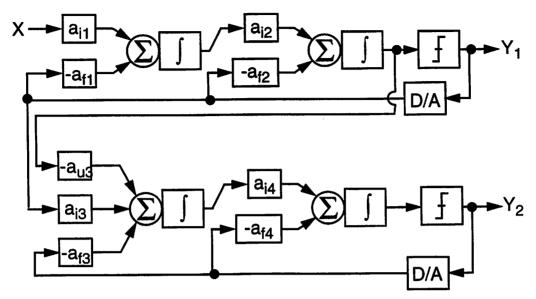

A basic block diagram for the 2-2 architecture was shown in Figure 3.10. This is repeated in greater detail in Figure 4.1 below. Each integrator has a full clock delay between its

Fig. 4.1: 2-2 Cascaded Architecture Implementation

input and output to create a fully pipelined structure. Single-bit quantizers are used in each of the two cascaded loops because of their inherent linearity.

#### 4.3 Signal Scaling

This section will describe strategies for selecting the gain factors in front of each integrator in the modulator. It is necessary to place appropriate attenuation factors to avoid clipping for large input signals. The goal of this signal scaling process is to maximize the overload level of the modulator by using all of the available swing at the output of each integrator without clipping [17].

| Coefficient     | Value |

|-----------------|-------|

| a <sub>i1</sub> | 0.2   |

| a <sub>f1</sub> | 0.2   |

| a <sub>i2</sub> | 0.5   |

| a <sub>f2</sub> | 0.25  |

| a <sub>u3</sub> | 0.5   |

| a <sub>i3</sub> | 0.1   |

| a <sub>f3</sub> | 0.2   |

| a <sub>i4</sub> | 0.5   |

| a <sub>f4</sub> | 0.25  |

Table 4.1: Integrator Gain Coefficients

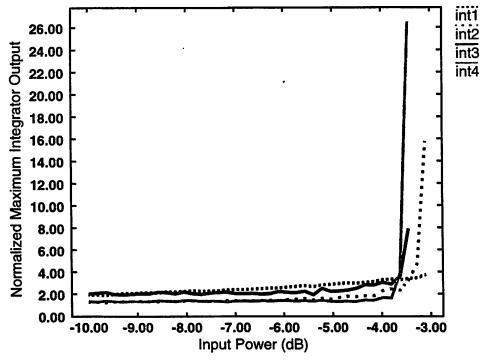

The gain coefficients selected for the 2-2 cascaded modulator is summarized in Table 4.1 [18]. For this set of gain factors, it can be observed that all four integrators have approximately the same output overload level.

Fig. 4.2: Maximum Integrator Output Levels as a function of Input Power

#### 4.4 Oversampling Ratio Selection

As mentioned in Chapter 3, increasing the oversampling ratio improves the dynamic range of the modulator. In switched-capacitor circuits, however, increasing the oversampling ratio also implies that the amplifier bandwidth needs to increase since the available time for settling  $(T_s/2 \text{ minus rise}, \text{ fall}, \text{ and } 2\text{-phase nonoverlap time})$  is reduced. The maximum achievable amplifier bandwidth is finite and is determined by the process technology.

The key is to therefore select the minimum oversampling ratio which yields the required performance. Circuit nonidealities which degrade the modulator performance should be included in any simulations to determine the required oversampling ratio. In addition, sufficient margins should be allocated for thermal and flicker noise if the system-level simulations account for quantization noise only. It is also worth mentioning that the oversampling ratio should be an integer which is a power of two, i.e.  $OSR = 2^x$ , to minimize power dissipation in the decimation filter following the ADC.

From system-level simulations, the required oversampling ratio to achieve 86dB of dynamic range for GSM is 128x, while that for DECT (72dB dynamic range) is 32x. The clock frequencies for GSM and DECT are 25.6MHz and 44.8MHz, respectively.

#### 4.5 Power Optimization

One of the goals of any portable electronics systems is to minimize power dissipation.

It is therefore important to identify the factors which affect the power budget in a sigma-delta

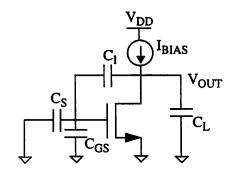

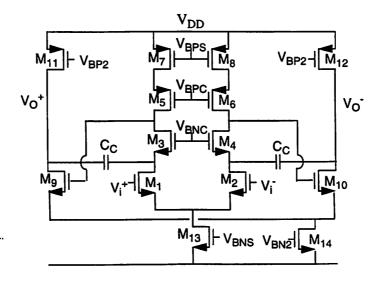

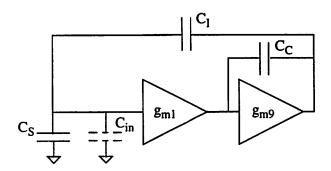

modulator. Most practical implementations employ the class A operational transconductance amplifier, the simplest form of which is the common-source amplifier shown in Figure 4.3.

Fig. 4.3: Simplified Class A Amplifier Model

The static power dissipated in the amplifier is proportional to the supply voltage and the bias current.

$$P \propto V_{DD} \cdot I_{RIAS}$$

(Eq 4-1)

Assuming that the device is biased at a fixed  $V_{GS}$ - $V_{TH}$ , the bias current  $I_{BIAS}$  is therefore proportional to the device transconductance,  $g_m$ , as shown by the equation below.

$$P \propto V_{DD} \cdot g_m$$

(Eq 4-2)

The closed-loop unity-gain bandwidth,  $\omega_{UT}$ , of the amplifier is given by

$$\omega_{\rm UT} = \frac{g_{\rm m}}{C_{\rm OUT}} \cdot f_{\rm FB} \tag{Eq 4-3}$$

where  $C_{OUT}$  is the total capacitance at the output of the amplifier, and  $f_{FB}$  is the feedback factor of the integrator.

$$C_{OUT} = \frac{C_I(C_S + C_{GS})}{C_I + C_S + C_{GS}} + C_L \approx \frac{C_I C_S}{C_I + C_S}$$

(Eq 4-4)

$$f_{FB} = \frac{C_1}{C_1 + C_S} \tag{Eq 4-5}$$

Substituting (Eq 4-4) and (Eq 4-5) into (Eq 4-3) yields

$$\omega_{\text{UT}} = \frac{g_{\text{m}}}{C_{\text{S}} + C_{\text{GS}}} \approx \frac{g_{\text{m}}}{C_{\text{S}}}$$

(Eq 4-6)

Substituting (Eq 4-6) back into (Eq 4-2) allows us to rewrite the power dissipated in the amplifier as a function of the unity-gain bandwidth and the sampling capacitor, as shown below.

$$P \propto V_{DD} \cdot \omega_{UT} \cdot C_S$$

(Eq 4-7)

The dynamic range of the integrator is the ratio of the input signal power to the noise power. Assuming that the input can swing from ground to V<sub>DD</sub>, and that the noise floor is dominated by thermal noise, the dynamic range can be approximated by

$$DR = \frac{P_{IN}}{P_{NOISE}} \approx \frac{\left(\frac{V_{DD}^2}{8}\right)}{\left(\frac{kT}{M \cdot C_S}\right)}$$

(Eq 4-8)

where M, the oversampling ratio, is the ratio of the sampling frequency to the Nyquist frequency  $(f_s/f_N)$ .

The unity-gain bandwidth,  $\omega_{\text{UT}}$ , can be rewritten in terms of the sampling frequency as shown below.

$$\omega_{\text{UT}} = \frac{1}{\tau} = \frac{1}{\left(\frac{T_s}{2n_\tau}\right)} = 2n_\tau f_s = 2[-\ln(2^{-N})]f_s$$

(Eq 4-9)

By reorganizing terms and substituting (Eq 4-8) and (Eq 4-9) back into (Eq 4-7), the static power limit can be written in the form

$$P \propto \frac{DR \cdot f_N}{V_{DD}}$$

(Eq 4-10)

The static power is proportional to the required dynamic range and the Nyquist frequency, and is inversely proportional to the supply voltage. It is interesting to consider the different requirements for GSM and DECT standards, and their implications on the power consumption. The required dynamic range for GSM is approximately four times (12dB) greater than that for DECT, but the Nyquist rate for DECT signals is seven times greater than that for GSM. (Eq 4-10) suggests that, using the same ADC for the two standards, the power dissipation in the ADC will be limited by the DECT standard due to its wider bandwidth.

The latter suggests that the trend toward lower supplies favored by digital circuits and required by deep submicron CMOS process will have an adverse effect on power dissipation of the modulator [18]. It is interesting to note that the power is independent of the sampling frequency and oversampling ratio, assuming the devices operate in the forward active region.

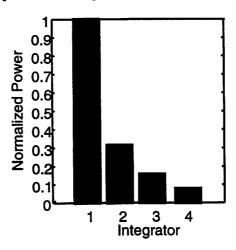

#### 4.6 Noise-Shaping and Capacitor Scaling

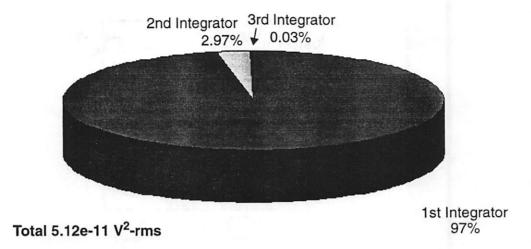

One strategy to minimize power dissipation is to take advantage of noise-shaping in sigma-delta modulators to scale down the capacitors (and bias currents) in later integrators in the modulator chain. The thermal and flicker noise of the 2nd integrator, when referred to the ADC input, is shaped with a 1st-order high-pass characteristic; the noise from the 3rd integrator has a 2nd-order shaping, and so on. In general, the minimum sampling capacitors is determined by the required kT/C noise, without being limited by parasitic capacitors.

The total input-referred thermal noise as a function of the input-referred thermal noise of each integrator is given by

$$P_{N, \text{ tot}} = P_{N1} \left( \frac{1}{M} \right) + P_{N2} \left( \frac{\pi^2}{3A_2^2 M^3} \right) + P_{N3} \left( \frac{\pi^4}{5A_3^2 M^5} \right) + P_{N4} \left( \frac{\pi^6}{7A_4^2 M^7} \right)$$

(Eq 4-11)

where  $P_{Ni}$  = Input-referred noise of i-th integrator  $A_i$  = DC gain from ADC input to input of i-th integrator

The integrator input-referred thermal noise will be discussed later in Section 5.2.2.

Increasing the oversampling ratio M significantly relaxes the noise requirement of subsequent stages. In a system like GSM where the low bandwidth permits a high oversampling ratio of 128x, only the first stage in the cascade contributes significantly to the total thermal noise of the ADC. Wider bandwidth systems like DECT do not allow the luxury of a high oversampling ratio. As such, more than one integrator will contribute to the ADC input-referred thermal noise.

Besides thermal noise, noise shaping in sigma-delta modulators also relaxes flicker noise and settling requirements of later integrators in the cascade. This further permits the scaling of capacitors, transistor sizes and bias currents in the 2nd, 3rd and 4th integrators. Figure 4.4 shows that the capacitor scaling technique results in a net power savings of 250%.

Fig. 4.4: Power Savings afforded by Noise Shaping

In the next section, the relaxed settling requirements in sigma-delta modulators will be illustrated.

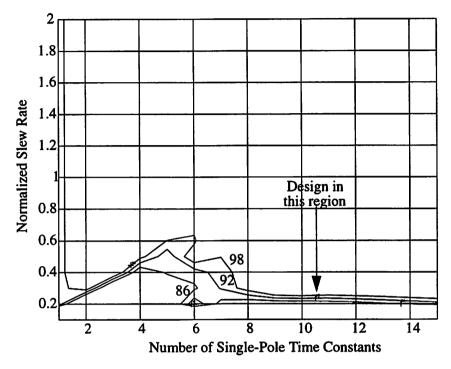

#### 4.7 Linear Settling and Slew Rate

The linear settling and slew rate requirements of each of the integrators in the cascade can be quantified by system level simulations [17]. For simplicity, a single-pole model of the

opamp is used for the simulations; actual designs which employ more complicated 2-stage amplifiers must leave significant margins from these results. Figure 4.5 shows the peak SNDR

Fig. 4.5: Contours of Peak SNDR as a function of Slew Rate and Settling Time for 1st Integrator

of the first integrator as a function of various combinations of slew rate and linear settling accuracy for an oversampling ratio of 128x. It is desirable for the integrator to be designed for the flat region where performance is independent of small shifts in amplifier settling accuracy.

The settling error is defined to be the departure of the output from the value it would achieve with an infinite amount of time for settling. From (Eq 3-10), this settling error is given by

$$\varepsilon_{\rm S} = {\rm e}^{-{\rm n}_{\rm T}}$$

(Eq 4-12)

4.8 Simulated Results 43

The slew rate shown in Figure 4.5 can be denormalized to a physical slew rate specification for the amplifier by

$$SR = 2(SR_N)V_{DAC}f_s (Eq 4-13)$$

V<sub>DAC</sub> denotes the differential DAC reference levels and f<sub>s</sub> the sampling frequency.

A summary of the required slew rate and the tolerable settling error for each of the integrators are summarized in Table 4.2 for both GSM and DECT.

|         | GSM Standard |                | DECT Standard |                |

|---------|--------------|----------------|---------------|----------------|

|         | Slew Rate    | Settling Error | Slew Rate     | Settling Error |

| OpAmp 1 | 150V/μs      | 0.0061%        | 260V/μs       | 0.0244%        |

| OpAmp 2 | 150V/μs      | 1.83%          | 260V/μs       | 0.248%         |

| OpAmp 3 | 135V/μs      | Negligible     | 230V/μs       | 1.83%          |

| OpAmp4  | 120V/μs      | Negligible     | 200V/μs       | Negligible     |

Table 4.2: Summary of Slew Rate and Linear Settling Specifications

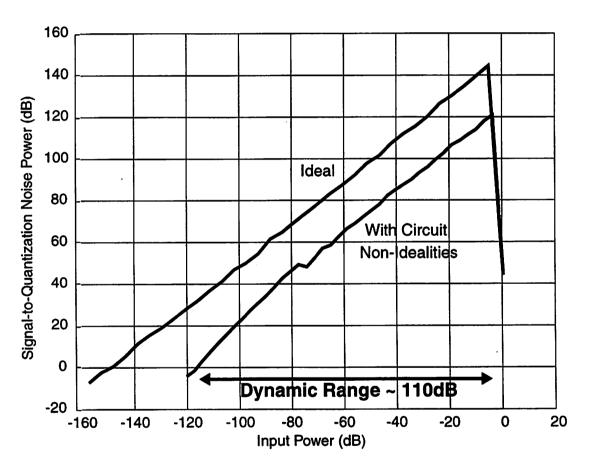

#### 4.8 Simulated Results

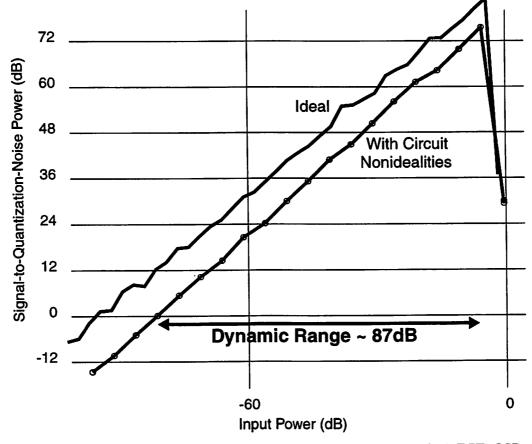

The simulated performance of the 2-2 MASH or cascaded architecture will now be presented. Recall that the required oversampling ratio for GSM is 128x and that for DECT is 32x. The left curve in Figure 4.6 illustrates the signal-to-quantization-noise (SQNR) as a function of input power for an ideal 4th-order modulator. The peak SQNR is approximately 145dB while the simulated dynamic range is 140dB.

As discussed in Section 3.5, a number of circuit imperfections cause the modulator performance to deviate from this ideal prediction. The right curve on the same figure takes into account such circuit imperfections. It assumes a finite opamp DC gain of 66dB, a settling error of 0.003% in the first opamp, a slew rate of 150V/µs and an interstage gain mismatch of 2.5%.

This results in a degradation of about 35dB in dynamic range. It should be noted that the dominant cause of dynamic range degradation is the interstage gain mismatch. With a dynamic range of 110dB, the quantization noise floor is still ensured to be at least 20dB below the thermal noise floor. This margin will accommodate any possible in-band "tones" in the quantization noise spectrum.

Fig. 4.6: Simulated Signal-to-Quantization Noise of 2-2 MASH Architecture for GSM (OSR = 128x)

A similar plot of SQNR for the DECT standard is shown in Figure 4.7. The left curve illustrates the ideal performance of the 2-2 cascade modulator with an oversampling ratio of 32x. The same nonidealities as those described in the previous paragraph were then included in

45

Fig. 4.7: Simulated Signal-to-Quantization Noise of 2-2 MASH Architecture for DECT (OSR = 32x) the simulations. The nonideal modulator performance is shown on the right curve. The quantization noise floor is kept about 15dB below the required thermal noise floor.

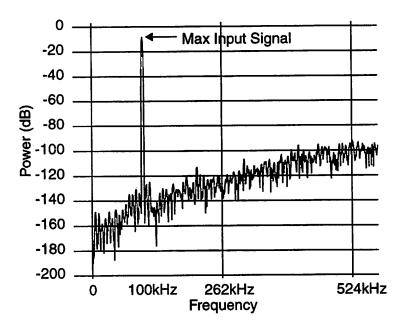

Finally, the FFT plot for the modulator with a 100kHz-input is shown in Figure 4.8.

Fig. 4.8: FFT Output Plot of the 2-2 Cascade Architecture for GSM (M = 128)

### Chapter 5

# Integrator and Amplifier Design

#### 5.1 Introduction

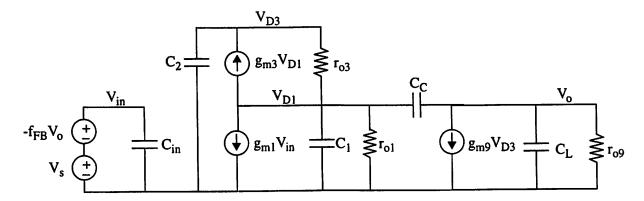

This chapter explores design tradeoffs and power-optimization strategies for key circuit blocks which are at the heart of the sigma-delta modulator. These include switched-capacitor integrators, operational transconductance amplifiers (OTA), bias networks, comparators, digital output buffers, and two-phase clock generation circuitry. An experimental prototype of the 2-2 MASH  $\Sigma\Delta$  modulator implemented in a 0.35 $\mu$ m double-poly, five-metal 3.3V CMOS process will be described.

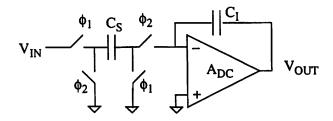

#### 5.2 Integrator Design

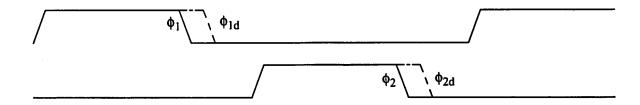

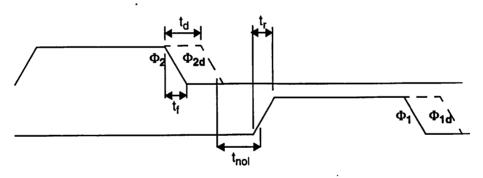

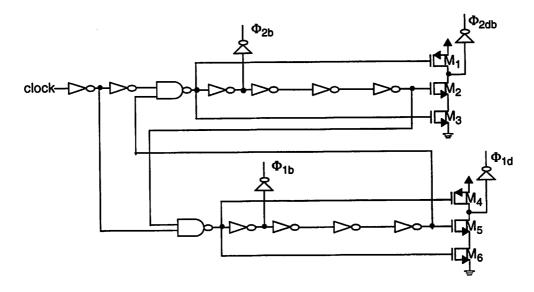

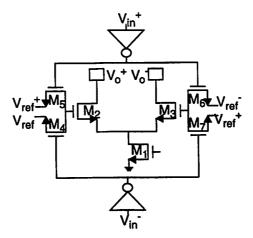

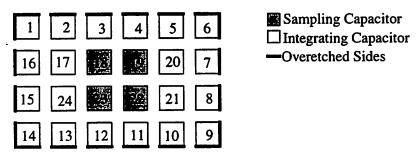

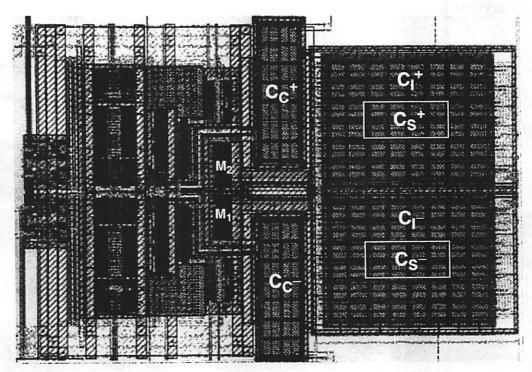

The experimental prototype comprises four switched-capacitor integrators. Figure 5.1 illustrates the first integrator in the cascade. The integrator is implemented in a fully-differential configuration and employs a two-phase nonoverlapping clock, the latter of which is shown in Figure 5.2. The input is sampled during phase 1 ( $\phi_1$  and  $\phi_{1d}$ ). During phase 2, the charge is transferred from the sampling capacitor ( $C_S$ ) to the integrating capacitor ( $C_1$ ). At the same time, depending on the output value, the appropriate DAC reference level is applied by closing either switches labeled  $\phi_{2d1}$  or  $\phi_{2d2}$ .

Fig. 5.1: Fully-differential switched-capacitor integrator

The integrator employs the bottom-plate sampling technique to minimize signal-dependent charge-injection [22]. This is achieved through delayed clocks:  $\phi_{1d}$ ,  $\phi_{2d1}$  and  $\phi_{2d2}$ . When switches labeled  $\phi_1$  are first turned off, the charge injection from those switches remains, to a first order, independent of the input signal. Because one of plates is now floating, turning off switches labeled  $\phi_{1d}$  shortly after does not introduce charge-injection errors.

Recall from Figure 4.1 and Table 4.1 that the feedforward and feedback gains of the first integrator are respectively 0.2 and -0.2. This allows the sharing of the sampling capacitors for the feedforward and feedback paths in order to minimize the loading on the amplifier summing node and maximize the feedback factor. This reduces power dissipation in the amplifier.

Fig. 5.2: 2-Phase Nonoverlap Clock

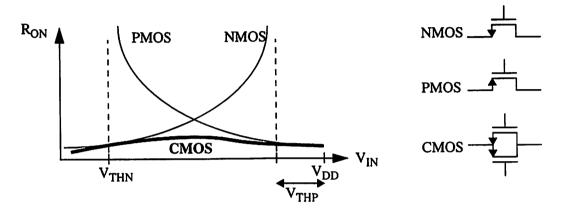

#### 5.2.1 Switches

Linearity is an important factor in the design of the switches. From Figure 5.3, it is desirable to operate in a region where the on resistance of the switch is independent of the input voltage. The switches used in the integrator are implemented with complementary MOS devices because the DC voltages are biased at mid-supply. Alternatively, gate boasting

Fig. 5.3: Switch On-Resistance as a Function of the Input Voltage

techniques using charge pumps may be employed to keep a constant on resistance [18]; however the process for which this experimental prototype is designed does not permit voltages above  $V_{\rm DD}$ .

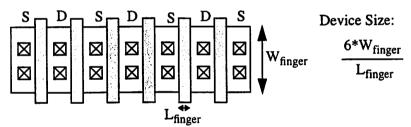

In CMOS switches, the sizing of the NMOS and PMOS devices is critical. The parallel combination of the NMOS and PMOS devices yields an effective resistance given by

$$R_{ON, CMOS} = \left[ \mu_N C_{ox} \left( \frac{W}{L} \right)_N (V_{GSN} - V_{THN}) + \mu_P C_{ox} \left( \frac{W}{L} \right)_P (V_{SGP} - |V_{THP}|) \right]^{-1}$$

(Eq 5-1)

For linearity reasons, the input switches, labeled  $\phi_{1d}$ ,  $\phi_{2d1}$  and  $\phi_{2d2}$  in Figure 5.1, should be designed for equal impedances. This means the PMOS should be made larger than the NMOS by a factor equal to the ratio  $\mu_N/\mu_P$  as shown below.

$$\frac{\left(\frac{W}{L}\right)_{P}}{\left(\frac{W}{L}\right)_{N}} = \frac{\mu_{N}}{\mu_{P}}$$

(Eq 5-2)

The bottom-plate switches, labeled  $\phi_1$  and  $\phi_2$  in Figure 5.1, should be designed for a first-order cancellation of charge-injection errors. The error is given by

$$\Delta V_{OUT} = -\frac{1}{2} \cdot \frac{(Q_{chan})_{N}}{C_{S}} + \frac{1}{2} \cdot \frac{(Q_{chan})_{P}}{C_{S}}$$

$$= -\frac{1}{2} \cdot \frac{C_{ox}}{C_{S}} \cdot \{W_{N}L_{N}(V_{DD} - V_{IN} - V_{THN}) - W_{P}L_{P}(V_{IN} - V_{THP})\}$$

(Eq 5-3)

For a partial cancellation of charge-injection error, the NMOS and PMOS devices should be designed to have equal sizes.

$$W_N L_N = W_P L_P (Eq 5-4)$$

The fully-differential configuration of the integrator further mitigates the effects of signal-dependent charge injection.

In addition to sizing the switches for linearity and charge-injection reasons, the sampling network also needs to be designed for sufficient bandwidth. Increasing the switch sizes decreases the resistance but increases the parasitic capacitance of the network. An optimum value of the switch size which yields a minimum R-C time constant can be determined.

#### 5.2.2 Sampling and Integrating Capacitors

The sizes of the sampling and integrating capacitors are dictated by the noise requirements. The ideal input-referred thermal noise of the integrator is given by

$$P_{Ni} = 4 \cdot \frac{kT}{C_S}$$

(Eq 5-5)

Ideally, during phase 1, a noise sample with variance  $2kT/C_S$  ( $kT/C_S$  on each of the differential path) is captured across the sampling capacitors when the switches labeled  $\phi_1$  are open. Another  $2kT/C_S$  is sampled across the sampling capacitors during phase 2. However, because of nonideal effects described below, the total input-referred noise will be larger than that predicted by (Eq 5-5).

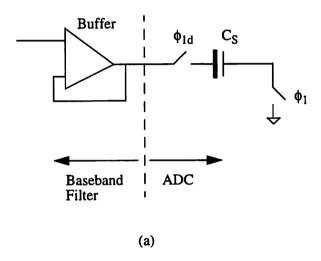

The switches labeled  $\phi_1$  are not driven by an ideal input voltage source; rather, it is driven by a buffer stage in the preceding baseband filter, as shown in Figure 5.4(a). The simplified noise model is shown in Figure 5.4(b). The noise sampled across  $C_S$  during  $\phi_1$  is therefore given by

$$P_{Ni,\phi 1} = 4kT(R_N + R_{on})\Delta f \cdot \left| \frac{1}{1 + s(R_{out} + R_{on})C_S} \right|^2$$

where

$$R_N \approx \frac{2}{3} \cdot \frac{1}{g_{m, buffer}} \cdot n_{sc}$$

$$R_{out} \approx \frac{1}{g_{m, buffer}}$$

(Eq 5-6)

The factor  $n_{sc}$  refers to additional noise in short-channel devices. Because the noise resistance and output resistance of the buffer driving the sampling network are not the same,

the result does not yield a simple kT/C value. Reorganizing (Eq 5-6), the total input-referred noise power can be written as

$$P_{Ni, \phi 1} = \frac{R_{N} + R_{on}}{R_{out} + R_{on}} \cdot 4kT(R_{out} + R_{on})\Delta f \cdot \left| \frac{1}{1 + s(R_{out} + R_{on})C_{S}} \right|^{2}$$

$$= \frac{R_{N} + R_{on}}{R_{out} + R_{on}} \cdot \frac{kT}{C_{S}}$$

(Eq 5-7)

Fig. 5.4: (a) Filter-to-ADC Interface (Single-Sided Representation) (b) Noise Model during Phase 1

During phase 2, due to thermal noise from the operational transconductance amplifier (OTA), the noise captured across  $C_S$  when the switches labeled  $\phi_2$  open can be greater than

2kT/C<sub>S</sub>. The OTA in-band flicker noise, when referred to the input of the integrator, simply adds on to the total input-referred noise power.

It is interesting to note that although the noise power is doubled in differential architectures, the input signal power is quadrupled. This results in a net gain of 3dB in dynamic range. Moreover, fully-differential integrators are more immune toward power-supply, common-mode and substrate-coupled noise.

$$DR = \frac{P_{IN}}{P_{NOISE}}$$

(Eq 5-8)

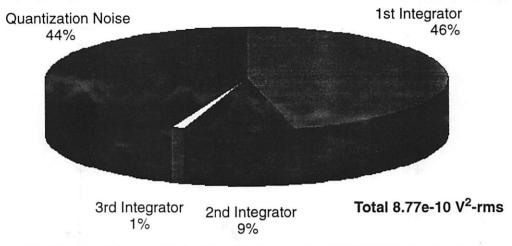

Because of noise shaping, later integrators will have relaxed noise requirements. This suggests that the capacitors in later integrators in the cascade will be selected based on parasitic considerations rather than noise.

#### 5.2.3 Multi-Standard Adaptability