# Copyright © 2000, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# A DETERMINISTIC NONLINEAR CAPACITOR MODEL FOR SINGLE-ELECTRON TUNNELING JUNCTIONS

by

Martin Haenggi and Leon O. Chua

Memorandum No. UCB/ERL M00/16

19 April 2000

# A DETERMINISTIC NONLINEAR CAPACITOR MODEL FOR SINGLE-ELECTRON TUNNELING JUNCTIONS

by

Martin Haenggi and Leon O. Chua

Memorandum No. UCB/ERL M00/16

19 April 2000

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# A Deterministic Nonlinear Capacitor Model for Single-Electron Tunneling Junctions

#### Martin Haenggi and Leon O. Chua

Electronics Research Laboratory

Departement of Electrical Engineering and Computer Science

University of California at Berkeley

Berkeley, CA 94720

E-mail: haenggi@computer.org

#### Abstract

Single-electron tunneling junctions (SETJs) have intriguing properties which make them a primary nanoelectronic device for highly compact, fast, and low-power circuits. However, standard models for SETJs are based on a quantum mechanical approach which makes them very impractical for the analysis and design of SETJ-based circuitry, where a simple, preferably deterministic model is a prerequisite. We verify by physics-based Monte Carlo simulations that the tunneling junction can in fact be modeled by a piecewise linear voltage-charge relation, which, from the circuit-theoretic perspective, is a nonlinear capacitor.

### 1 Single-Electron Tunneling Junctions

To explain single-electron effects, an "orthodox theory" based on a phenomenological Hamiltonian approach with a tunneling term and the electrostatic energy has proved successful. To analyze circuits with single-electron junctions (SETJs), however, simplified models of the junction characteristics are required. One example is the Monte Carlo model in which classical electrons tunnel through the junctions stochastically with a probability that is a function of the temperature and the change in electrostatic energy. In the limiting case of zero temperature and small average current, it further reduces to a deterministic model where electron tunneling occurs as soon as it decreases the overall electrostatic energy of the system.

Based on these considerations, a deterministic model for the junction characteristics has been proposed which avoids any unnecessary complexities due to the stochastic nature of quantum mechanics and thermal fluctuation [1].

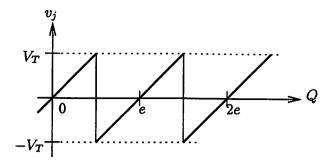

Figure 1: Linear-periodic voltage-charge relation for a SETJ.

In this model, it is assumed that an electron tunnels when the junction voltage  $v_j$  reaches the tunneling voltage

$$V_T = \frac{e}{2C_j} \,. \tag{1}$$

The behavior of the junction can therefore be modeled by a single-valued piecewise linear voltage-charge relation (Fig. 1). This model has been applied for the investigation of phase-locked single-electron tunneling elements [1, 2], but has not been verified so far. In this note, we confirm the model by simulations and put it in a new perspective: we demonstrate that it can be interpreted as a nonlinear capacitor – a viewpoint which greatly simplifies the analysis and design of SETJ-based circuits.

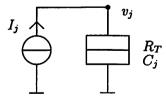

## 2 Simulation of a Current-Biased Single-Electron Tunneling Junction

To verify the validity of this piecewise linear model, we use a very simple test circuit (Fig. 2) consisting of a constant current source and a SETJ characterized by its tunneling resistance  $R_T$  and its junction capacitance  $C_j$ . For our calculcations, we use SIMON2.0, which is the latest version of a single-electron circuit simulator based on a Monte Carlo simulation of tunneling events. Note that  $R_T$  does not have an influence for these simulations provided that its value is larger than  $h/e^2 \approx 25.8 \mathrm{k}\Omega$ . The current is assumed to

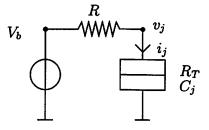

Figure 2: Current-biased SET junction.

be zero for t < 0 and constant for  $t \ge 0$ , and the charge is therefore proportional to the

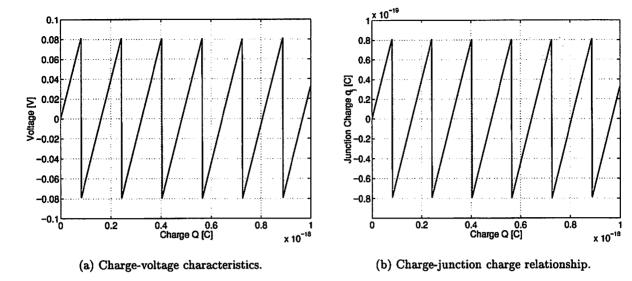

Figure 3: Simulation of a single tunneling junction (SIMON2.0).

time, i.e.,  $Q(t) = I_j t$ . This allows us to establish a charge-voltage relationship for the tunneling junction.

For the graphs in Fig. 3, we used a junction capacitance of  $C_j = 1$ aF, which leads to a tunneling voltage of  $V_T \approx 0.08V$ . Note that the horizontal axis does *not* represent the actual junction charge but the *integrated current* through the junction, i.e.,

$$Q(t) = \int_{-\infty}^{t} i_j(\tau) d\tau.$$

(2)

Based on the physics of the SETJ, the device is a linear capacitor until the voltage reaches the threshold  $V_T$ . Hence, the actual junction charge is given by  $q_j(t) = C_j v_j(t)$ , where  $v_j$  is the junction voltage,  $|v_j| < V_T$ . Observe that  $q_j$  cannot grow larger than e/2 since this is the threshold junction charge for tunneling. The simulation in Fig. 3 (b) shows the relationship between Q and  $q_j$  and confirms the proportionality between junction charge and junction voltage. Mathematically, the junction charge can be described by

$$q_j = f(Q) = Q - ne \quad \text{for} \quad \left(n - \frac{1}{2}\right)e \leqslant Q < \left(n + \frac{1}{2}\right)e, \quad \forall n \in \mathbb{Z}.$$

(3)

As expected,  $\frac{dq_j}{dQ} \equiv 1$  except at the discontinuities (n+1/2)e, and f(Q) does not depend on the junction capacitance.

Since the junction charge cannot be measured directly, it is desirable to express the junction voltage as a function of the integrated current Q:

$$v_j(Q) = \int_{Q_0}^{Q} \frac{1}{C(q)} dq \tag{4}$$

We use the letter C to emphasize that the integrand's denominator is, in fact, a capacitance, i.e., the ratio between charge and voltage.

Taking the derivative of (4) yields

$$\frac{dv_j}{dQ} = \frac{1}{C(Q)},\tag{5}$$

and, together with (3) and Fig. 3, we get

$$\frac{1}{C(Q)} = \frac{1}{C_j} - 2\delta\left(\left(n + \frac{1}{2}\right)e - Q\right)V_T, \quad n = \{0, \pm 1, \pm 2, ...\}$$

(6)

and

$$C(Q) = \frac{C_j}{1 - 2C_j \delta\left(\left(n + \frac{1}{2}\right)e - Q\right)V_T}, \quad n = \{0, \pm 1, \pm 2, ...\},$$

(7)

where  $\delta(.)$  denotes the Dirac delta function.

Eq. (7) demonstrates that the tunneling junction is, in fact, nothing else than a nonlinear capacitor whose capacitance C(Q) depends on the integrated current flowing through it. Its value is equal to the tunneling capacitance  $C_j$  except at points Q = (n+1/2)e,  $\forall n \in \mathbb{Z}$ .

# 3 Simulation of a Voltage-Biased Single-Electron Tunneling Junction

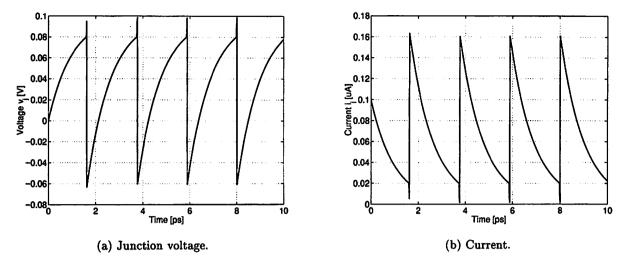

For practical circuits such as in [1], the SETJ is often voltage-biased. In this section, we investigate the circuit shown in Fig. 4. The bias voltage  $V_b$  is 0.1V, the value of the resistor is  $R = 1M\Omega$ , and the junction capacitance is again  $C_j = 1aF$ . We expect the

Figure 4: Voltage-biased tunneling junction.

"time constant" of the system to be in the ps range, since  $RC_j = 1$ ps, which is confirmed by the simulations in Fig. 5. At t = 0, when the voltage source is assumed to be switched on, the current is  $i_j(0) = V_b/R$ , and it decays exponentially to zero, proportional to  $\exp(-t/RC_j)$ . However, when the junction voltage reaches  $V_T$ , the capacitance (7) becomes discontinuous, and the current jumps to a value of about  $2i_j(0)$ .

Figure 5: Simulation of a voltage-biased single tunneling junction (SIMON2.0).

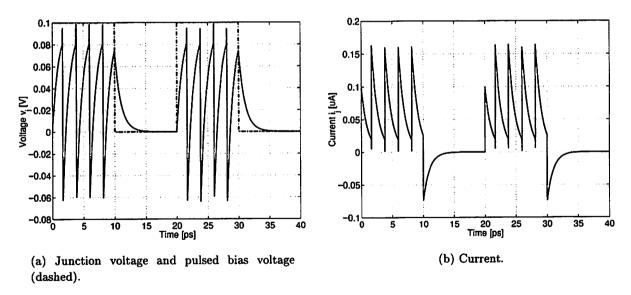

For our last experiment, we replace the constant bias voltage by a pulsed source (cf. dashed curve in Fig. 6 (a))

$$\forall n \in \mathbb{N}_0: V_b(t) = \begin{cases} 0.1 \text{V} & \text{for } n \, 20 \text{ps} \leqslant t < \left(n + \frac{1}{2}\right) 20 \text{ps} \\ 0 \text{V} & \text{for } \left(n + \frac{1}{2}\right) 20 \text{ps} \leqslant t < (n+1) \, 20 \text{ps} \end{cases}$$

(8)

The graphs in Fig. 6 prove, once again, the validity of the nonlinear capacitor model.

Figure 6: Simulation of a pulsed voltage-biased single tunneling junction (SIMON2.0).

For periods with  $V_b(t) = 0$ , the junction capacitance is discharged like a conventional capacitor, causing a negative current  $i_j$ .

### 4 Concluding Remarks

The foundation of nonlinear circuit theory is based on the axiomatic definition of 4 basic (two-terminal and multi-terminal) circuit elements [3, 4] from which all electronic devices are modeled. A 2-terminal circuit element defined by a relationship between the voltage v(t) and the charge q(t) is called a two-terminal capacitor. Hence the model presented in this note for a SETJ is precisely a 2-terminal nonlinear capacitor with a "sawtooth" v-q characteristic.

It is important to bear in mind that in the axiomatic definition of circuit elements, the charge q(t) is defined by the time integral of the current flowing into the terminal of the element, namely,  $q(t) = \int_{-\infty}^{t} i(\tau)d\tau$ . Observe that if we apply a constant dc current  $I_0$  across an initially uncharged capacitor, we will get

$$q(t) = I_0 t, \quad t \geqslant 0. \tag{9}$$

Hence, the unbounded charge

$$\lim_{t \to \infty} q(t) \longrightarrow \infty \tag{10}$$

should be interpreted merely as a dc current flowing over the infinite time interval  $[0, \infty)$ , and not as the amount of physical charge stored in the junction, as would have been in the case of a linear capacitor.

#### Acknowledgment

This work is partly supported by the DOD Office of Naval Research under grant number N00014-98-1-0594.

#### References

- [1] T. Ohshima and R. A. Kiehl, "Operation of bistable phase-locked single-electron tunneling logic elements," *Journal of Applied Physics*, vol. 80, pp. 912–923, July 1996.

- [2] T. Yang and L. O. Chua, "Single-Electron Tunneling Junction Cellular Neural Networks," Memorandum UCB/ERL M00/10, Electronics Research Laboratory, University of California, Berkeley, 2000.

- [3] L. O. Chua, Introduction to Nonlinear Network Theory. McGraw-Hill, 1969.

- [4] L. O. Chua, "Device Modeling via Basic Nonlinear Circuit Elements," *IEEE Transactions on Circuits and Systems-I*, vol. CAS 27, pp. 1014-1044, Nov. 1980.