Copyright © 2001, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# RF CMOS CLASS C POWER AMPLIFIERS FOR WIRELESS COMMUNICATIONS

by

Ramakrishna Sekhar Narayanaswami

Memorandum No. UCB/ERL M01/37

12 December 2001

# RF CMOS CLASS C POWER AMPLIFIERS FOR WIRELESS COMMUNICATIONS

by

Ramakrishna Sekhar Narayanaswami

Memorandum No. UCB/ERL M01/37

12 December 2001

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering

University of California, Berkeley

94720

### RF CMOS Class C Power Amplifiers for Wireless Communications

by

#### Ramakrishna Sekhar Narayanaswami

B.S. (University of California, Berkeley) 1993 M.S. (University of California, Berkeley) 1998

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy in

Engineering - Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Paul R. Gray, Chair Professor Robert G. Meyer Professor J. Karl Hedrick

Fall 2001

The dissertation of Ramakrishna Sekhar Narayanaswami is approved:

Chair Date

Nov. 6 2001

Date

Date

University of California, Berkeley

Fall 2001

## RF CMOS Class C Power Amplifiers for Wireless Communications

Copyright © 2001

by

Ramakrishna Sekhar Narayanaswami

#### Abstract

### RF CMOS Class C Power Amplifiers for Wireless Communications

by Ramakrishna Sekhar Narayanaswami

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Paul R. Gray, Chair

Recent efforts in the design of integrated circuits for RF communication transceivers have focussed on achieving higher levels of integration by including more and more analog functional blocks onto a single silicon CMOS chip. One of the final blocks that has yet to be successfully integrated is the Power Amplifier (PA). The PA is the final functional block in the transmit path; its function is to amplify the signal to be transmitted to the required transmit power level. In general, PAs are difficult to integrate in CMOS because of technology limitations that severely limit the efficiency of the PA.

This thesis describes theoretical analysis and circuit techniques for the design and implementation of RF Class C PAs in CMOS technologies. To date, very few methods exist for designing Class C PAs; in the past, much of the design process has been empirical. The theoretical work in this thesis attempts to describe a method for designing a Class C PA in CMOS without resorting to blind use of a circuit simulator. Using fourier series analysis, the drain current waveform of a CMOS Class C PA (which is dependent both on the input and output voltage waveforms) is determined to first-

order in order to generate an approximate solution to the design goal before a circuit analysis tool is required. Circuit techniques used to combat the technology limitations imposed by CMOS technologies include the use of differential circuits in the signal path, cascoded stages and a modified tuning method which allowed for the use of extremely large output devices but not requiring passive devices that were not feasible in a CMOS technology.

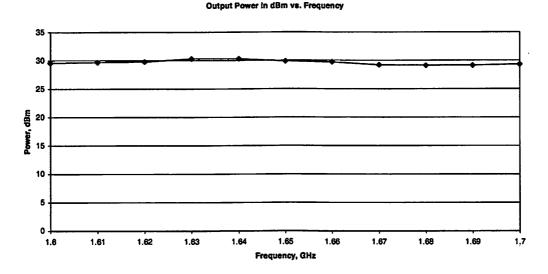

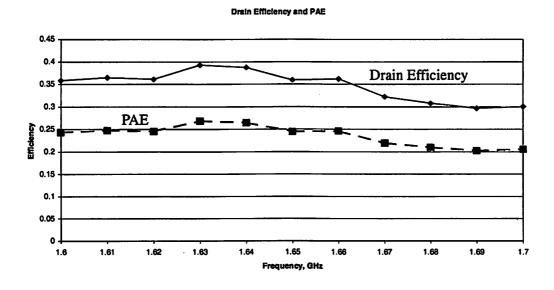

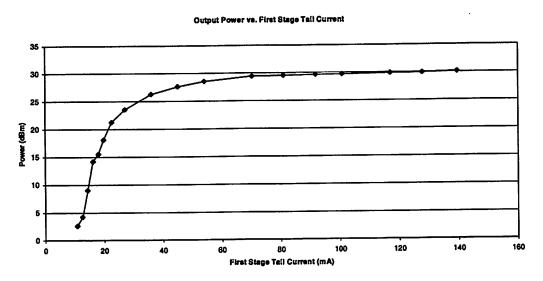

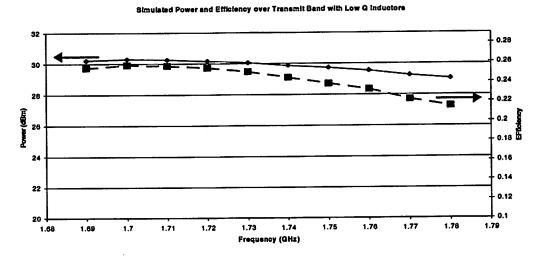

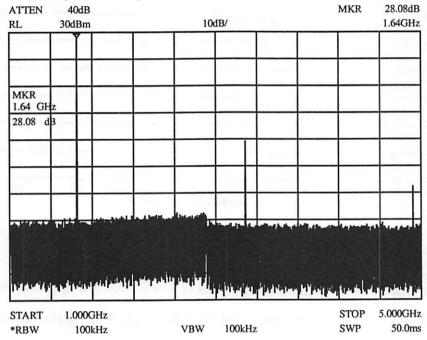

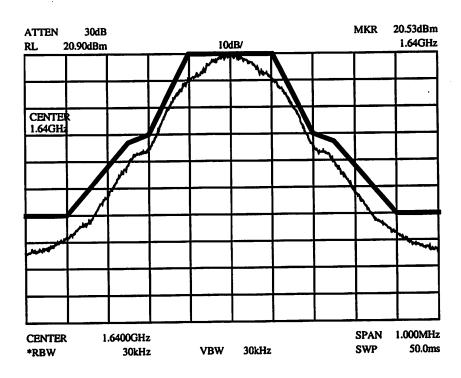

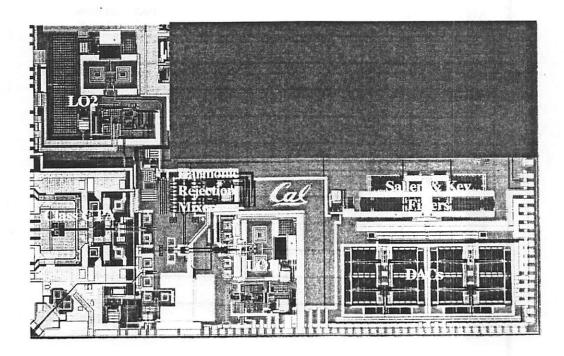

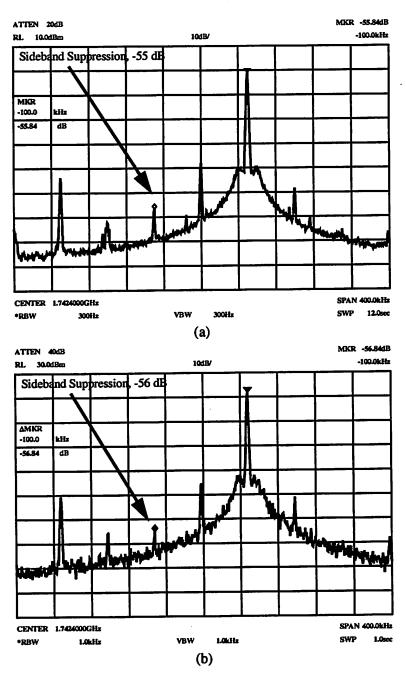

A 1.75-GHz, 1.7W CMOS PA was designed in an STMicroelectronics 0.35-µm, five-metal doubly-poly CMOS process and implemented both as a stand-alone chip and as part of a fully-integrated transmitter chip. In simulation, the peak efficiency of the PA was 40%. Due to an over-estimation of the quality factors of the on-chip spiral inductors used in the design, the evaluation of the PA revealed a peak power of just over 1-W and a peak efficiency of 27%. The PA did meet the spectral mask requirements of the DCS1800 cellular communications system for which it was designed, and comparison of the PA output of the integrated version indicated that the PA amplified the desird signal without too much degradation of the signal.

Paul R. Gray, Chairman of Committee

# **Table of Contents**

|      | _                          | ments                                              |                                        |  |  |

|------|----------------------------|----------------------------------------------------|----------------------------------------|--|--|

| Chap | ter 1: I                   | ntroduction                                        | 1                                      |  |  |

| 1.1  | Background                 |                                                    |                                        |  |  |

| 1.2  | Transceiver Architecture   |                                                    |                                        |  |  |

| 1.3  | Power Amplifiers           |                                                    |                                        |  |  |

| 1.4  | Research Goals             |                                                    |                                        |  |  |

| 1.5  | Thesis Organization        |                                                    |                                        |  |  |

| Char |                            | Power Amplifier Background                         |                                        |  |  |

| 2.1  | Introduction               |                                                    |                                        |  |  |

| 2.2  | Transmitter Basics         |                                                    |                                        |  |  |

| 2.3  | Power Amplifier Basics     |                                                    |                                        |  |  |

| 2.4  | PA Classes                 |                                                    |                                        |  |  |

| 2.4  | 2.4.1                      | "Linear" or Amplification-mode PAs                 |                                        |  |  |

|      | 2.4.2                      | "Nonlinear" or Switch-mode PAs                     | 23                                     |  |  |

| 2.5  | Class C Power Amplifiers   |                                                    |                                        |  |  |

|      | 2.5.1                      | Idealized Analysis                                 | 26                                     |  |  |

|      | 2.5.2                      | Class C PA Non-Idealities                          |                                        |  |  |

|      | 2.5.3                      | Benefits of Class C PAs                            |                                        |  |  |

|      | 2.5.4                      | What Is Needed                                     |                                        |  |  |

| Chaj |                            | Class C Theoretical Analysis                       |                                        |  |  |

| 3.1  | Introd                     | luction                                            | 34                                     |  |  |

| 3.2  | CMOS Device Model          |                                                    |                                        |  |  |

|      | 3.2.1                      | CMOS Device Basics                                 |                                        |  |  |

|      | 3.2.2                      | Validity of Model                                  |                                        |  |  |

|      |                            | 3.2.2.1 Short Channel Effects on Threshold Voltage | 39                                     |  |  |

|      |                            | 3.2.2.2 Short Channel Effects on Drain Current     |                                        |  |  |

| 3.3  | Class                      | C Circuit Basics                                   |                                        |  |  |

|      | 3.3.1                      | The Circuit                                        |                                        |  |  |

|      | 3.3.2                      | The Input                                          |                                        |  |  |

|      | 3.3.3                      | The Output                                         | 46                                     |  |  |

|      |                            | 3.3.3.1 The Output Network                         |                                        |  |  |

| •    | <b>~</b> :                 |                                                    |                                        |  |  |

| 3.4  | Class C Design Methodology |                                                    |                                        |  |  |

|      | 3.4.1                      | The Initial Estimate                               |                                        |  |  |

|      | 3.4.2<br>3.4.3             | Iterating to reach final value                     |                                        |  |  |

|      | 3.4.3                      | A Design example                                   | ······································ |  |  |

| 3.5         | Earlier Stages                         |                                         |     |  |  |

|-------------|----------------------------------------|-----------------------------------------|-----|--|--|

| 3.6         | Conclusion                             |                                         |     |  |  |

| Chap        | ter 4: CI                              | MOS Technology Limits                   | 61  |  |  |

| 4.1         | Introduction                           |                                         |     |  |  |

| 4.2         | Breakdown Voltage In Sub-Micron CMOS62 |                                         |     |  |  |

| 4.3         | CMOS Transconductance                  |                                         |     |  |  |

| 4.4         | Current Consumption6                   |                                         |     |  |  |

| 4.5         | Output Stage Device Sizes70            |                                         |     |  |  |

| 4.6         | CMOS Substrate Issues                  |                                         |     |  |  |

| 4.7         | Solving the Technology Issue           |                                         |     |  |  |

|             |                                        | ircuit Design Techniques                |     |  |  |

| 5.1         |                                        | action                                  |     |  |  |

| 5.2         | Circuit Solutions                      |                                         |     |  |  |

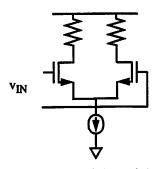

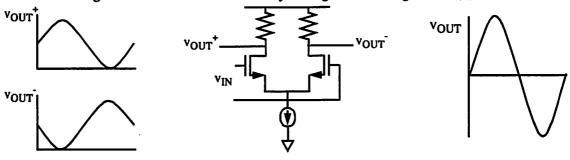

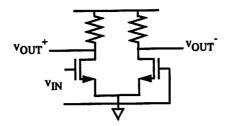

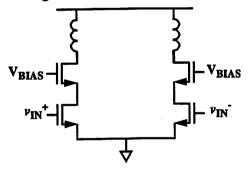

| J. <b>2</b> | 5.2.1                                  | Differential Structure                  |     |  |  |

|             | 5.2.2                                  | Cascode Structure                       | 84  |  |  |

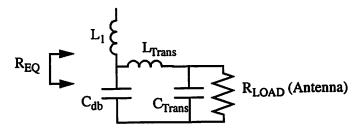

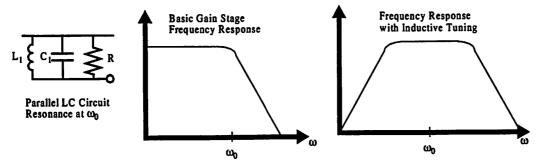

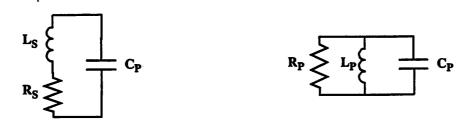

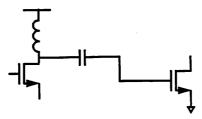

|             | 5.2.3                                  | Inductive Tuning using Bond Wires       | 87  |  |  |

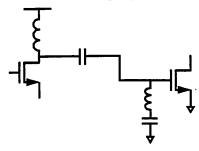

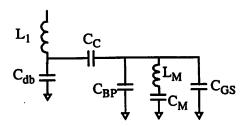

|             | 5.2.4                                  | Input tuning of final stage             | 94  |  |  |

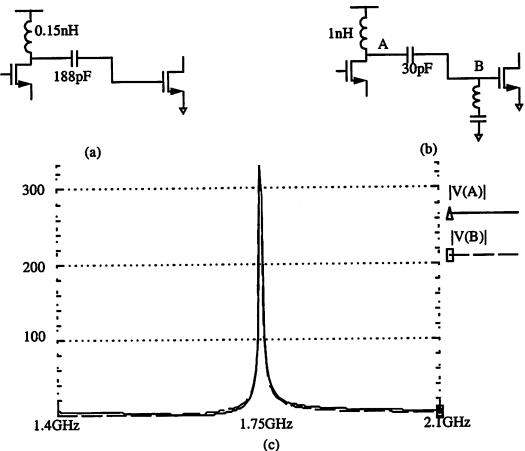

|             | 5.2.5                                  | Cascode Inductors                       | 98  |  |  |

| 5.3         | Conclu                                 | usion                                   | 100 |  |  |

| Chaj        | pter 6: Po                             | ower Amplifier Prototype Implementation | 102 |  |  |

| 6.1         |                                        | uction                                  |     |  |  |

| 6.2         | Power                                  | Amplifier Specification                 | 103 |  |  |

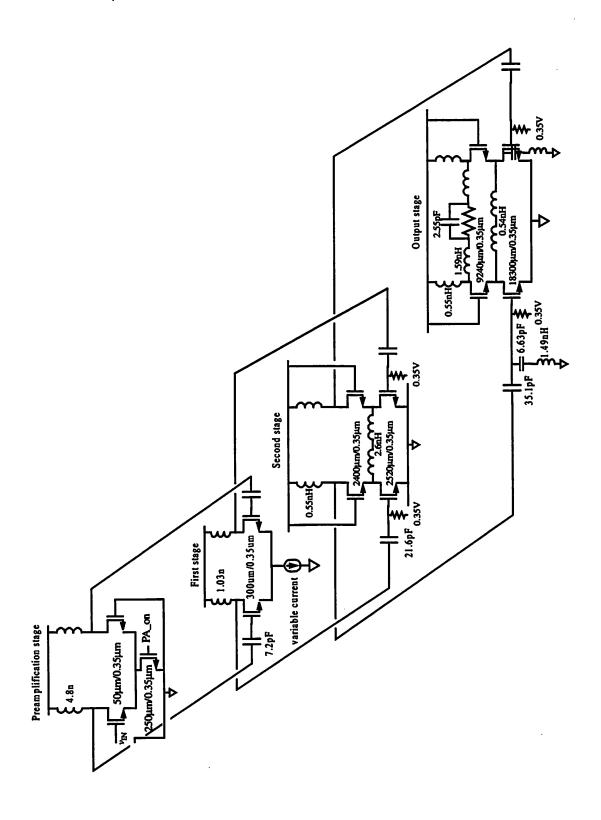

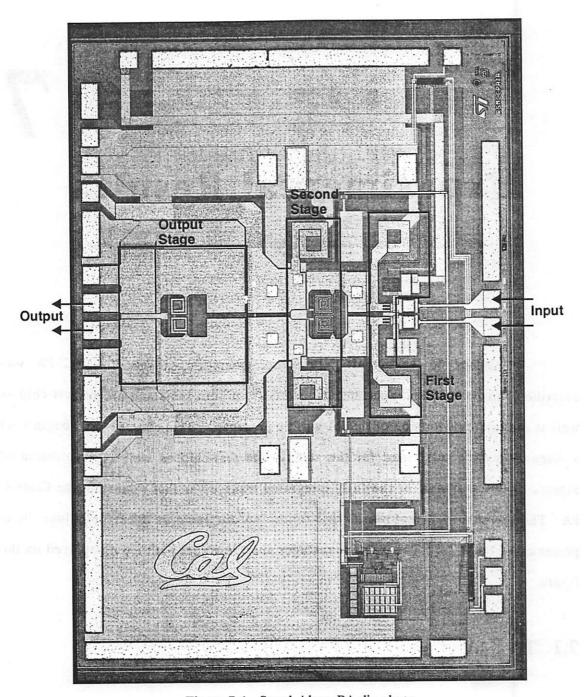

| 6.3         | Circuit Design                         |                                         |     |  |  |

|             | 6.3.1                                  | Process                                 |     |  |  |

|             | 6.3.2                                  | Output Impedance Transformation Network | 105 |  |  |

|             | 6.3.3                                  | Output Stage                            | 106 |  |  |

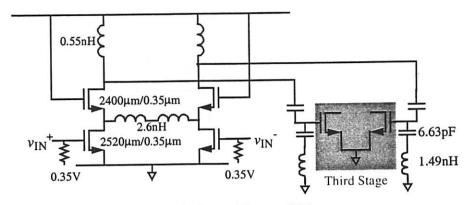

|             | 6.3.4                                  | Second Stage                            |     |  |  |

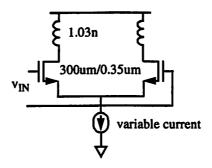

|             | 6.3.5                                  | First Stage                             | 111 |  |  |

|             | 6.3.6                                  | Power Control Scheme                    |     |  |  |

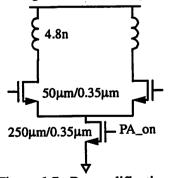

|             | 6.3.7                                  | Preamplifier                            | 113 |  |  |

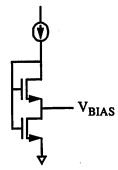

|             | 6.3.8                                  | Biasing                                 | 114 |  |  |

|             | 6.3.9                                  | Power-Down Mode                         |     |  |  |

|             | 6.3.10                                 | Final Circuit Topology                  |     |  |  |

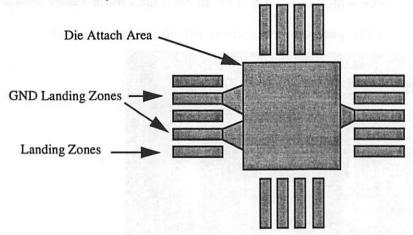

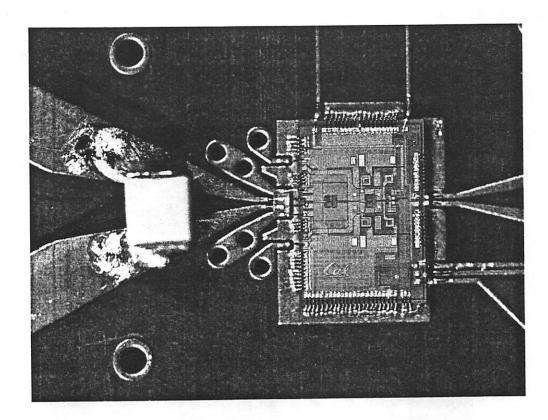

| 6.4         | Layout and Fabrication                 |                                         |     |  |  |

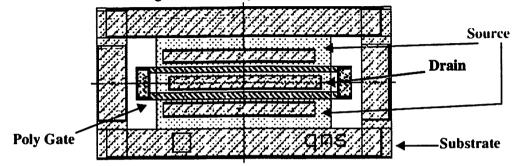

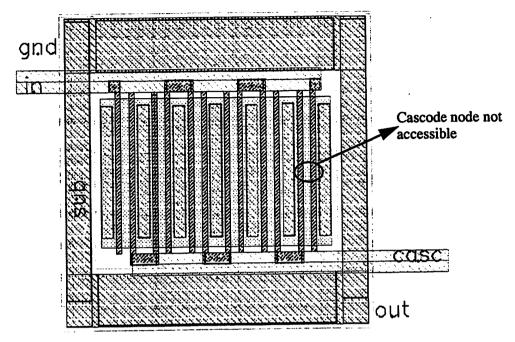

|             | 6.4.1                                  | Basic Transistor Cell                   |     |  |  |

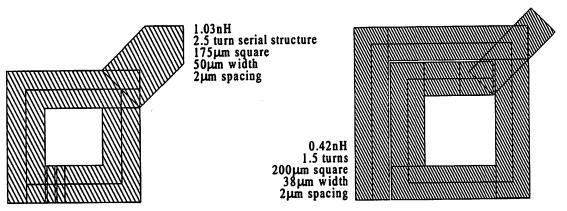

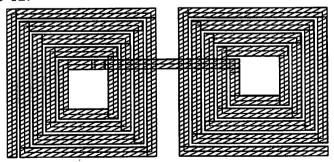

|             | 6.4.2                                  | Spiral Inductor Design                  | 119 |  |  |

|             | 6.4.3                                  | Substrate Coupling                      |     |  |  |

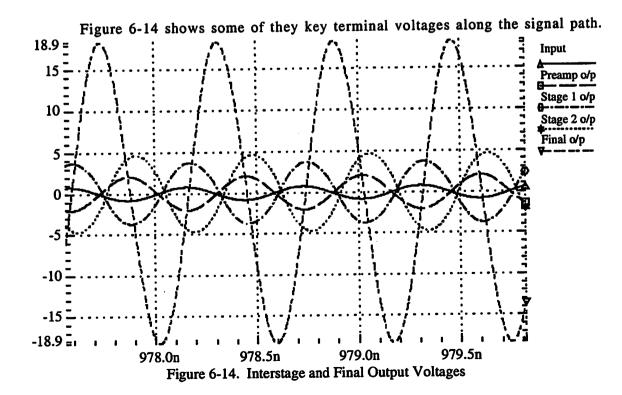

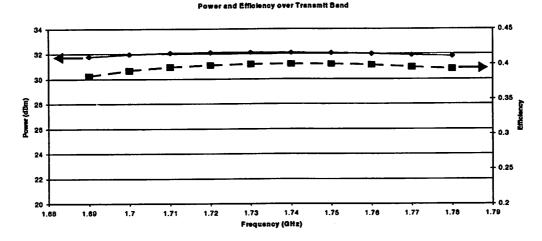

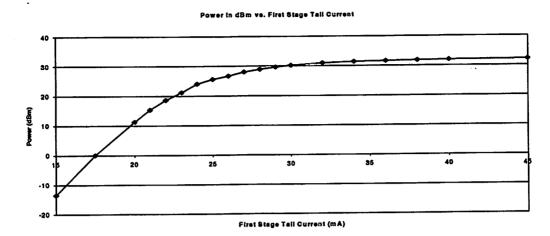

|             |                                        | ation Results                           | 122 |  |  |

Table of Contents

| 6.6  | Stand-alone Test Chip        | 125 |

|------|------------------------------|-----|

| 6.7  | Conclusion                   |     |

| Char | pter 7: Experimental Results |     |

| 7.1  | Test Board                   | 127 |

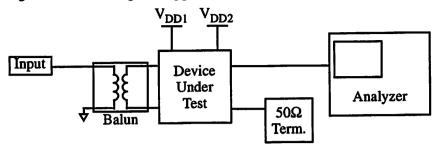

| 7.2  | Experimental Test Setup      |     |

| 7.3  | Results                      |     |

|      | 7.3.1 Stand-alone Test-chip  | 132 |

|      | 7.3.2 Integrated PA          | 137 |

| 7.4  | Conclusions                  |     |

| Cha  | pter 8: Conclusions          |     |

|      | 145                          |     |

# Acknowledgments

When starting the long road towards obtaining a Ph.D., I was told that getting an M.S. (at least at a university that requires a research project for the M.S.) would give one an idea of what doing research was like; it was not necessary to get a Ph.D. for that purpose. Rather, the Ph.D. was more a labor of love than an introduction to research, and that one should be well aware of that before embarking on such a long journey. More than eight long years later, I can say without hesitation that the above is true, and, as such a labor, this dissertation and all the work that went into it would not have been possible without the assistance and support of a great many people.

First and foremost, I would like to thank my advisor, Professor Paul Gray, for his support over the years. His advice on technical matters was invaluable, and his guidance both on my individual project as well as the larger GSM transceiver project was critical to the project's success. I would also like to thank Professor Robert Meyer for his assistance along the way, as his knowledge and experience were also extremely valuable. Along with Professors Gray and Meyer, I would also like the thank Professor Seth Sanders and Professor Karl Hedrick for serving on my qualifying exam committee. Further, I would like to thank Professors Gray, Meyer, and Hedrick for reading this dissertation.

In any endeavor of this magnitude, the work at hand could definitely not have been completed without significant input and assistance from my fellow students. Jeff Weldon, who coordinated much of the work on the transmit side of the GSM transceiver project, was a great friend and colleague throughout this work, and of significant assistance along the way. I don't know that I can ever forget the countless hours required to put together the transmitter and then test it once it had been fabricated. Jeff's help in both discussing technical issues as well as keeping things light with discussions about sports and other "less-critical" topics was invaluable. Others

involved with the project who were extremely helpful include Chris Rudell, Jeff Ou, Li Lin, Martin Tsai, and Luns Tee, as well as the visiting industrial fellows Masa Otsuka, Danilo Gerna, and Sebastien Dedieu.

More generally, my colleagues in Professor Gray's research group were extremely helpful as well. Those mentioned in the previous paragraph were definitely of great assistance, but a few others need to be mentioned here. First, my cube-mates from cube 550-C5 were a great group of guys to have as cube-mates. Andy Abo, Keith Onodera, and Jeff Ou made the long days and nights of work in Cory Hall pass by much more quickly, and offered much relief from the tedium of graduate school through long discussions on Cal Athletics and life in general as well as far too many meal and coffee breaks (and poker nights!). Jeff Ou's insights into RF modelling and devices in general were especially helpful. And Keith and Andy always had their own technical insights that they were willing to offer when I needed it. Overall, I couldn't have asked for a better group of cubemates.

Earlier in my career, the senior graduate students of the time, including Ken Nishimura, Greg Uehara, Cormac Conroy, Robert Neff, Thomas Cho, Todd Weigandt, and Dave Cline were kind enough to impart some of their experience and wisdom to me. Those who joined the group with me as well as newer students who joined later were always ready to discuss topics both technical and non-technical, and their contributions were invaluable. Srenik Mehta, Arnold Feldman, George Chien, Carol Barrett, and Troy Robinson were always available for discussions and exchanging ideas, whether it was circuits or exchanging ideas about our favorite science fiction and fantasy authors. Finally, in the later years, several newer graduate students have entered the group, and I hope I was able to be as helpful to them as some of the senior graduate students were to me when I started, and to wish them good luck in their careers. They include Ryan Bocock, Yun Chiu, Cheol-Woong Lee, and Tim Wongkomet.

Several graduate students in other research groups were also very helpful along the way. Tom Burd and Dennis Yee deserve great thanks, for being great friends as well as helping technically. Ali Niknejad and Manolis Terrovitis from Professor Meyer's group were always available to discuss technical concerns, as were the RF group from Professor Brodersen's research group: Chinh Doan, Dave Sobel, Brian Limketkai, Sayf Alalusi, Johan Vanderhaegen, and Dennis Yee.

I'd also like to recognize a couple of graduate students who were not in my technical field, but definitely added to the overall experience of my time here at Cal. They include Adrian Isles, who has been a good friend ever since I convinced him to come to Cal (isn't that right, Adrian?), and Sunil Khatri, who increased my appreciation for the blues and who helped me with my attempts to retain the Hindi I learned.

Any discussion of my time here at Cal (at least as a graduate student) would most certainly not be complete without acknowledging 920 Keeler, the house where I lived for most of my tenure as a graduate student, and my housemates in that house. Special thanks must go to all the people who graced that house, as all my housemates have become good friends and provided me with some great memories along the way. Andy Abo was not only my cubemate but my housemate, and I will always remember his love for video games and his enjoyment at talking back to the TV, as well as his "textbook" basketball jump shot (which was indeed out of a textbook!). I will also remember his "curious" means for obtaining a Costco card for me. I will always remember Srenik Mehta living in the kitchen for a month, Tony Stratakos' joy for life (and his numerous snapple bottles), and Chris Rudell's 30th birthday party, which was definitely the party to end all parties. I will also always remember I have lived in the same house as Chris longer than anyone outside my immediate family; the fact that I was able to live in the same house as these guys for such a long time is a credit to our friendships and the caliber of their character. I can't continue without mentioning the my newer housemates: Joe Seeger, who first introduced the concept of housemates having schedules that were totally out of phase with each other and with whom I had many good technical discussions, Justin Black, who took the concept of schedules out of phase to the next level, and my newest roommate, Shyam Lakshmin, who has infused the house with his youthful energy (and his love for all things FSU). All my housemates are deserving of a great deal of my appreciation for making my home life a great joy and making the path to my Ph.D. that much easier.

It is certainly not feasible to thank all my friends in this space, but a few of the more important friends who helped me throughout my Ph.D. career should be acknowledged here. Vikram and Dipanwita Amar have been exceptional friends and deserve more thanks than I can express here. Lapoe Lynn, Kevin Stone, Jennifer Cheng, and Manish Mehta, all friends from my undergraduate days (and some from my early graduate days), have also been great friends, and also have my greatest appreciation.

Finally, it is absolutely true that none of this Ph.D. would have been possible without the love and support of my family: my parents and my sister, Kala. Their love and overwhelming support in the face of any obstacle or adversity I faced was not only instrumental but essential in the completion of this work. I would not be where I am today without their contributions and the foundation that they have provided throughout the years.

Funding for this work was provided by the National Defense Science and Engineering Graduate Fellowship, as well as the National Science Foundation. Fabrication facilities and support were provided by STMicroelectronics.

1

# Introduction

#### 1.1 Background

In recent years, the level of interest in wireless communication links and the devices which can support those links has exploded[1]. New standards are being both approved and designed in order to tap into the exploding market; many of these new standards attempt to connect devices and/or appliances in the home using lower-performance radio transceivers. In addition, the desire for Internet connectivity using cellular phones or Personal Digital Assistants (PDAs), i.e. Palm or Windows-CE based handheld devices, has dramatically increased the demand for universal wireless connectivity. In order for these standards and the companies that support them to stay competitive, low-cost, small form-factor portable wireless communications devices are a critical component; in order to attract a large group of users, cost is a very important concern. As such, the desire for a low-cost wireless device with reasonable performance has exploded as well.

Current implementations of wireless communications devices, such as cellular phones or cordless phones, employ several chips implemented in different semiconductor technologies in order to implement the analog radio-frequency (RF)

components and lower frequency components as well as the digital components. As an example, photos of the inner workings of two cellular phones are shown in Figure 1-1..

Figure 1-1. Cellular Phones

The two photos show that each of these phones is comprised of several distinct chips as well as a large number of discrete components (often passive components). Often times the chips included in the analog section of the transceiver will include separate chips for the radio frequency (RF) functions (usually at least two distinct chips, if not more), the intermediate frequency (IF) functions, and the baseband analog sections. The blocks required to convert the analog signals to digital signals (and vice versa) may also be separate from the sections listed above, so there may be as many as five chips or more required to perform the functions of the analog functionality from RF to baseband. Furthermore, these chips are normally designed in different fabrication and device technologies, where each of the chips is designed in a technology which is best suited for the particular function being implemented. This multi-chip solution to

implementing these portable wireless devices limits the minimum cost and size of the final devices. Further adding to the cost and size is the fact that passing signals between chips is generally more complex than passing signals around on a single-chip, especially at radio frequencies. Issues of matching and driving signals between chips add to the number of discrete components required and also increase the power consumption of the overall implementation, reducing the performance of the overall device. The current implementations, while they are becoming smaller, are still extremely complex and not conducive to significant reductions in cost and size without a radical change in thinking with regards to the implementation of the transceiver.

To that end, the amount of investigation into the feasibility of using CMOS processes in the implementation of the circuitry used in these devices has dramatically increased as well. While CMOS processes are already used for many, if not all, of the lower frequency and digital functions, their acceptance as a reliable and feasible alternative on which to build the high-frequency high-performance analog blocks has been limited. In general, CMOS is an extremely poor technology for high-frequency, high-performance analog functions. For reasons that will be detailed in this work, and have been detailed in others, CMOS is much better suited to low-frequency analog implementations or digital functions; a CMOS transistor models an ideal switch very well, which is extremely useful for digital functions or switched-capacitor analog functions, but it in general has poor current drive and large associated parasitic capacitances, reducing its usefulness in higher-frequency analog functions.

However, what CMOS does provide is an extremely low-cost technology in which to implement circuit blocks, along with the added benefit of potential large-scale integration. Because the baseband analog and digital chips are generally CMOS chips, building the high-frequency, high-performance chips in CMOS would allow those functions to be included in comprehensive, single-chip solutions. Currently, most commercially-available wireless solutions are multi-chip implementations, in which

several different technologies, including silicon CMOS (Si-CMOS), silicon bipolar, Gallium Arsenide (GaAs), and/or Silicon Germanium (SiGe). In general, the higher-frequency blocks are done in one of the listed technologies, with the exception of CMOS. A CMOS implementation of the high-frequency analog section would facilitate the integration of all of the radio functions (including high-frequency analog, baseband analog, A/D conversion, and DSP) onto a single-chip.

#### 1.2 Transceiver Architecture

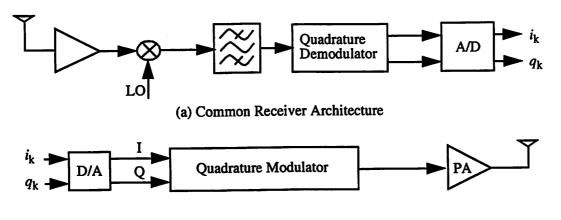

In order to accomplish this, there must be an understanding of what functions must be implemented in the high-frequency analog portion of the RF transceiver, or radio. Figure 1-2. shows the basic architecture of a radio transceiver, which contains

(b) Common Transmitter Architecture

Figure 1-2. Radio Transceiver Architectures

two main functions: that of the receiver and that of the transmitter. The function of the analog portion of the receive chain is to take a radio-frequency (RF) analog signal and convert that into the digital bitstream which it represents. The basic blocks in the receive path are a low-noise amplifier (so called because it is critical to amplify the incoming signal without contributing any significant noise), a frequency translation block (generally also known as a mixer), and a block which demodulates the signal and

outputs the desired digital bits. A block that is required but which is not directly in the signal path is the local oscillator (LO), which is used by the mixer to frequency translate the signal to low-frequency.

On the transmit side, essentially the reverse path is followed. First, the digital bitstream is modulated and converted to an analog signal. The resulting analog signal is frequency translated by an up-conversion mixer, and the final signal is amplified to the power level that the antenna needs to radiate, as required by the standard. This final block is generally known as a Power Amplifier (PA).

### 1.3 Power Amplifiers

In RF transceivers, the PA takes a small-amplitude signal at the output RF frequency as its input and drives a high power representation of the input into a low-impedance load (generally the antenna, which is nominally  $50\Omega$ ). Because the peak power levels required will be significantly higher than the mixer can supply on its own, a separate functional block is required. So the key purpose of the block is high-frequency amplification; as mentioned earlier, CMOS is not ideally suited to this function. While many of the other functional blocks have been implemented in CMOS reliably, the PA is one of the final blocks to be implemented and integrated with the other blocks onto a single CMOS chip.

One of the key reasons for the general industry-wide reluctance to move the implementation of the PA to CMOS is the fact that while the PA is on, it can dominate the power consumption of the entire transceiver. Since most of these portable wireless devices will be powered by a battery with a finite energy reserve, the amount of power is consumed by any given block can be a critical factor in determining the usability of a particular part. As a result, optimizing the power-performance of the PA has been a far more important goal than that of integrating the PA into a transceiver. While the CMOS

1.4 Research Goals

realization of the PA might reduce the cost of the PA itself, if it significantly reduces the battery-life of the wireless device, there is really no gain (and there might be a potential loss) in that implementation.

Although the implementation of the PA in CMOS has not reached reliable production levels yet, there is a great deal of ongoing research into making the CMOS PA a realizable goal. Why? Because the cost and form-factor benefits from a high-performance CMOS PA are dramatic. If one can avoid having to use a GaAs or SiGe PA in favor of a CMOS PA, there is an inherent cost reduction in that switch. Second, the potential for including that PA in a single-chip CMOS transceiver, or in fact, in a single-chip that would serve as the entire analog and digital processing unit for a cellular phone would dramatically reduce the cost and form factor of the PA, allowing for the placing of cellular phone transceivers/processors in almost anything, including something as small as a watch.

#### 1.4 Research Goals

The focus of this research, and this dissertation, is the realization of a high-performance, integrated PA in CMOS. Through the use of PA architecture, or class, as well as circuit design techniques, this work will try to show the feasibility of a CMOS PA implementation, as well as its usefulness in an integrated transceiver. More generally, a key goal of this research is the development of a design methodology for the design of Class-C PAs in CMOS technologies. A few of the key results of this research are listed here:

• A simplified design methodology has been developed for the design of Class-C PAs in CMOS technologies. The design methodology uses a fourier series analysis of the drain current along with an iterative procedure in order to predict the drain current of Class-C PA in which the device operates in all three MOS regions of operation.

- Several different circuit techniques were used in order to overcome the limitations inherent to CMOS technologies, such as limited voltage swing and poor transconductance. New techniques, including the use of cascode inductors and the use of a modified tuning method in order to peak the impedance and therefore the gain at the input to the final drive stages, allowed the use of extremely large devices which facilitated the high output power required for the prototype designed in this work.

- A 1.7-W, 1.75-GHz PA has been designed in this work in a 0.35-\mu CMOS process, using a Class-C architecture. Experimental results indicated that the PA actually delivered 1-W of output power to the load, due to lower-than-expected Qs from the on-chip spiral inductors.

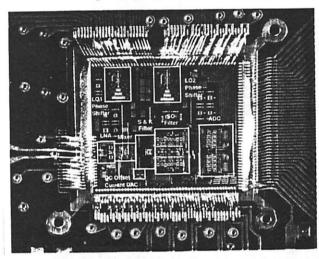

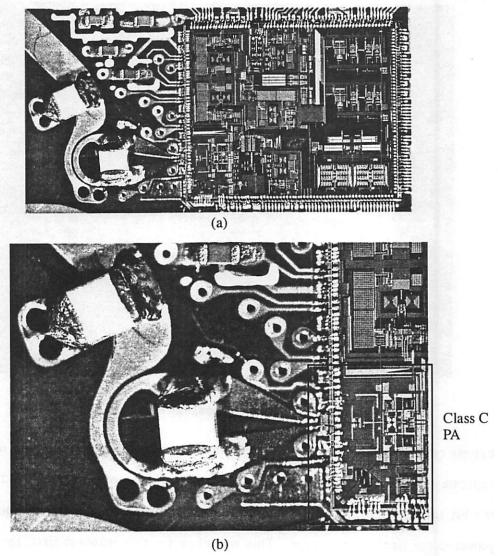

- The PA was also integrated into a single-chip CMOS transmitter that implemented all the transmitter blocks from the digital-to-analog converters through the PA as well as two frequency synthesizers. The PA in that implementation also suffered from lower than expected gain due to the lower-than-expected spiral inductor Qs; however, the PA was shown to have a minimal impact on the transmitted signal when compared with the output of the transmitter prior to the PA (after the mixers).

#### 1.5 Thesis Organization

This dissertation is organized as follows. In the next chapter, background information on both transmitters and PAs will be covered. The discussion on transmitters will briefly discuss a new transmitter architecture that allows the use and integration of a non-linear PA; the PA discussion includes PA uses, different classes, key metrics, and an in-depth background on Class C PAs. Chapter 3 will cover a theoretical approach to designing Class C PAs in CMOS, which has previously been missing. Chapter 4 will present an analysis of the limitations of CMOS processes with respect to the implementation of PAs. Chapter 5 will cover the techniques used in this work to combat the limitations described in Chapter 4. Chapter 6 will describe the PA that was included in the integrated transceiver, as well as the corresponding single-chip experimental prototype, and present some simulation results. Chapter 7 will cover the experimental results and performance of the single-chip PA prototype as well as some results from the integrated transceiver. Furthermore, Chapter 7 will also include some discussion on the deviation of the simulated and experimental results and the causes for

that deviation. Finally, some conclusions drawn from this effort will be presented in Chapter 8.

2

# Power Amplifier Background

#### 2.1 Introduction

In this chapter, a little background information will be provided, both on transmitters and on power amplifiers themselves. First, in order to be able to integrate a non-linear PA in a transmitter that attempts to satisfy a cellular standard, a transmitter architecture that is amenable to PA integration must be used. While the architecture advancements are not apart of the effort detailed in this dissertation but the work of another student[3], the ability to integrate a non-linear PA is contingent on the use of an architecture such as the one described in the next section. Because it is a necessary condition to the use of this non-linear PA, a basic explanation of the concepts is presented here.

The rest of the chapter will discuss PAs in further detail. A basic background on PAs and their function will first be given, followed by a brief introduction to the different classes of PA. Finally, the final section will fully investigate what is known

about Class-C PAs, and provide an idea of what else needs to be done to implement a Class-C PA today.

#### 2.2 Transmitter Basics

In today's world, the end goal for many research efforts in implementing low-cost wireless transceivers is the single-chip radio. Currently, most two-way radios, especially those designed for high-performance wireless systems like cellular phone systems, are implemented with multi-chip solutions. The RF, IF, and baseband sections may be comprised of different chips in different technologies, and there may even be further subdivisions within those groups. In order to implement the single-chip radio, a single technology must be chosen, and architectures that enable the integration of all the different blocks onto a single chip must be used.

On the receiver side, there has already been significant research into such architectures, including well-known architectures such as direct-conversion[4]. Newer architectures have also found significant interest, including Low-IF[5] and Wideband-IF-with-Double-Conversion (WIFDC)[6]. On the transmitter side, the level of interest has lagged behind that of the receiver side; however, more and more work is being focused on the transmitter.

One of the key issues in transmitter integration is that significant amounts of filtering are generally needed in the signal path in order to ensure that the output of the PA is free of both spurs and spectral regrowth that would violate either the spectral mask or the level of spurs which a given standard specifies. This is especially true if the PA to be used in the transmit chain is a non-linear PA, in which the level of distortion in the PA input will generally be amplified. If two simple transmitter architectures are examined, it will be apparent that neither is particularly well-suited to full-scale integration. The first of these architectures is the transmitter implementation

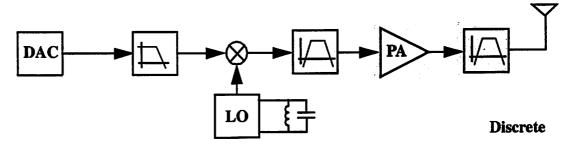

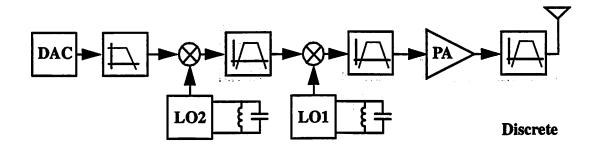

of the direct-conversion architecture; a block diagram is shown in Figure 2-1. In the

Figure 2-1. Direct Conversion Transmitter

direct-conversion transmitter,, the baseband digital bits representing the in-phase and quadrature channels are converted to analog signals in a digital-to-analog converter (DAC), filtered, then upconverted directly to the RF carrier frequency in one frequencytranslation step. In general, at this stage, the signal needs to be filtered before passing through the PA. This is for two reasons: first, the noise outside the transmit band must be reduced, which reduces the filtering required after the PA, and second, third-order intermodulation between frequency components at the input of the PA could mix and sit on top of the desired signal. This filter is difficult to integrate since it must have a narrow pass-band and a large amount of rejection, which cannot be achieved with the low quality-factor (Q) passive components available in a silicon CMOS technology. Furthermore, the frequency synthesizer used to generate the LO frequency needs to be a tunable frequency synthesizer which can tune between a large number of steps which are several orders of magnitude below the center frequency. As a result, the frequency synthesizer will need a high quality-factor LC tank in order to generate a clean LO signal (i.e. one with very low phase-noise); like the filter, this high-Q tank will not be able to be integrated.

A second popular architecture is the transmitter version of the superheterodyne receiver, which can be thought of as a transmitter using two steps to convert the frequency from baseband to the RF carrier frequency. The block diagram of this architecture is shown in Figure 2-2. In this architecture, once the digital bits are 12 2.2 Transmitter Basics

Figure 2-2. Two-Step Transmitter

converted to analog signals in the DACs, the signal is frequency-translated to a fixed intermediate frequency (IF). There, the signal is filtered by a narrow-band filter, which serves the purpose of removing the harmonics of the lower frequency local oscillator (LO2). The LO2 frequency is usually relatively low, when compared with the RF carrier frequency, and as a result, the harmonics of LO2 will cause intermodulation distortion in both the mixers and the PA which can give rise to significant errors in the transmitted signal. Because the LO2 frequency is generally low, the filter will have to have a narrow pass-band as well as lots of suppression in the stop-band, necessitating a high-O filter. This IF filter is normally implemented as a discrete component. Once the signal has been filtered at IF, it is then frequency translated to the RF carrier frequency. Again, the high frequency local oscillator used in this second mixing (LO1) is the one used to select the channel, and since it must be able to select between a number of closely-spaced channels, the LC tank required for this synthesizer will again likely be discrete. Finally, a pre-PA filter is, like the direct-conversion case, required in the signal path in order to reject the noise and potential for intermodulation. Finally, the signal is passed through the PA. As in the direct-conversion case, the LC tank used in the frequency synthesizer and the pre-PA filter need to be discrete; furthermore, in this super-heterodyne implementation, another discrete element, the IF filter, is added to the signal path. If anything, this architecture is even less amenable to integrating the entire signal path.

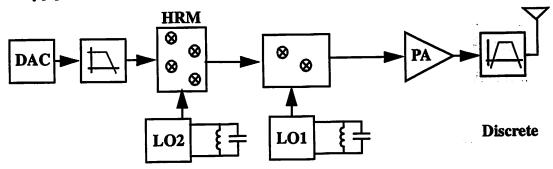

An architecture that attempts to solve these problems was presented recently[2] and will be described in more detail shortly[3], and is shown in Figure 2-3...

Figure 2-3. Harmonic Rejection Transmitter

This architecture, known as the Harmonic Rejection Transmitter (HRT), includes a special set of mixers known as Harmonic Rejection Mixers (HRM). architecture allows for the elimination of all of the discrete components required in the previously described architectures, except for the post-PA RF filter. As a result, the entire signal path from the DACs to the output of the PA can be included on a singlechip. The two key innovations in the transmitter include the use of the HRMs and the roles of the frequency synthesizers used. The HRT performs the frequency translation from baseband to the RF carrier frequency in two steps. However, unlike the superheterodyne transmitter mentioned previously, the roles of the local oscillators are swapped; the high-frequency LO (LO1) is nominally fixed in frequency, and the lower frequency LO (LO2) is the tunable, channel-select oscillator. The benefit of this arrangement is that it allows the use of a wide-bandwidth PLL in LO1, which can be designed to provide low phase noise even if a low-Q LC tank is used[7]. Furthermore, because the channel-selection is performed at a lower frequency, the output of LO2 will inherently have lower phase noise, again allowing the use of low-Q on-chip components. Thus the need for the high-Q discrete components required in the VCOs have been eliminated. Furthermore, the use of the HRMs helps to eliminate the need for the filters used in the signal path before the PA. In standard active mixers (such as the Gilbert Cell-style mixers), the LO signal is applied to the mixers as a square wave. As is well-known, the square wave has large frequency components at the third and fifth harmonics of the fundamental frequency. In the super-heterodyne transmitter, the harmonics of the LO input mix with the baseband signal in the first mixing step. The IF filter is required in the super-heterodyne transmitter in order to prevent those harmonic components from producing distortion in the high-frequency mixers or the PA. In the Harmonic-Rejection Mixers (HRM), however, the LO input is applied not as a squarewave but as a staircase function. The staircase function can be thought of as a three-bit, amplitude-quantized sine wave (similarly, the square-wave can be thought of as a onebit amplitude-quantized sine wave). This staircase function has no third or fifth harmonic component, and thus there will be no mixing products at those frequencies after the first mixing stage. If the LO2 frequency is low (on the order of 10 MHz or less), the seventh harmonic may still be problematic, as it would only be 70 MHz away, and may still produce intermodulation distortion that mixes with the desired signal. However, if the frequency plan is designed to use a higher LO2 frequency, the harmonic products existing after the first mixing stage would not exist at frequencies which may distort the output signal, and thus the need for the IF filter is eliminated. Furthermore, with the low phase-noise of LO1 and the removal of the harmonic components from the HRM, the pre-PA filter is also not required, and thus the entire signal-path from beginning to end can be integrated if the Harmonic-Rejection Transmitter is used. For more detail on this architecture, the references [2] and [3] should be consulted.

The HRT architecture facilitates the use of a non-linear power amplifier (PA) in the integrated transmitter, and furthermore facilitates the integration of the entire transmit path, from the DACs all the way through the PA, including the frequency synthesizers used. In the next section, PAs will be discussed in significantly more detail, in order to provide a basis from upon which the remainder of this work will be built.

## 2.3 Power Amplifier Basics

Power Amplifiers (PAs) are used in the transmit chain of communications devices, in order to amplify the signal to the desired power level. That power level is determined by the communications system; it must be high enough such that the amount of power that the receiver is able to sense (taking into account the losses in the communication medium) is adequate to recover the desired signal. For different applications, the order of magnitude of the transmitted power can very greatly. For base-stations used in cellular systems, this can be on the order of tens to hundreds of watts. For satellite communications, this can be on the order of thousands of watts. For portable wireless communications devices, the peak transmitted power is often significantly less; it will vary from tens to hundreds of milliwatts in cordless systems to hundreds of milliwatts to a few watts in cellular systems. Finally, in many of the emerging standards for wireless connectivity in the home (such as Bluetooth or HomeRF), the power will vary between tens of milliwatts and hundreds of milliwatts. When speaking of the power output of these blocks, one common unit used is dBm, which is the output power in dB referenced to 1-mW. That is, the output power in dBm is given by

$$P_{dBm} = 10log \frac{P}{0.001W},$$

Eq. 2-1

where P is defined in watts. Thus 1-W is equivalent to 30dBm, 100-mW is equivalent to 20 dBm, etc.

In the cases where the power output is on the order of hundreds of milliwatts or more, the power that the PA needs to deliver to its load in itself is a large percentage of the total power consumed by the entire transmitter. The power that needs to be delivered will be taken from the source that powers the PA; in the case of a portable unit, this will be the battery. In essence, the PA converts the DC power from the battery into RF power delivered to the load. Unless that power conversion is lossless, which is

possible only as an ideal abstraction, the PA itself will consume power, over and above what it delivers.

The measure of how much power a PA consumes in this conversion is one of the key performance parameters used to gauge PAs, especially those PAs used for portable applications. Because PAs in portable applications are driven from a source with a finite amount of available energy, power consumed in the PA directly goes to reducing the battery life. This metric is known as the PA's efficiency, given by

$$\eta = efficiency = \frac{Power\ Delivered\ to\ Load}{Power\ Drawn\ from\ Supply}$$

Eq. 2-2

Since the PA is really converting the DC power of the supply into the RF power delivered to the load, the maximum efficiency is 1, or 100%. That is, if there is no power consumed in the PA - all the power from the supply is sent to the load - both the numerator and the denominator in Eq. 2-2 are the same. However, since this is only ideally possible, the biggest issue in PAs today is maximizing this metric.

Furthermore, there are variations on this metric that give us more information about the PA. The *drain efficiency* is defined as

$$\eta_D = drain \ efficiency = \frac{Power \ Delivered \ to \ Load}{Power \ Consumed \ in \ Final \ Stage}$$

Eq. 2-3

This tells us how efficient the final stage, often referred to as the power stage, is. The most common efficiency metric used, though, is the Power-Added Efficiency (PAE). The one thing missing in the previous two versions of efficiency is any idea of how much power is needed to drive the input to the PA. In a real-world PA implementation, the power needed to drive the PA is also drained from the power source, and while that power loss can be accounted for in the previous stage, including it in the PA performance metric allows for two different PAs to be compared. If one PA has a better PAE for the same output power level and same overall efficiency than a second PA, it would be preferable to use the first PA; overall, less power would be drawn from the power source. PAE is defined as

$$PAE = \frac{P_{RF_{OUT}} - P_{RF_{IN}}}{P_{DC}}$$

Eq. 2-4

So the PA that delivers 1W to the output, consumes 2W, and must be driven by a 100 mW input (PAE=45%) is not as good as the PA that delivers 1W, consumes 2W, but needs only 1mW of input drive (PAE=49.95%). Since most PAs on the market are discrete components, the input drive is a critical concern for designers who plan to drop these discrete components into their designs. At RF, most discrete components are input-matched and output-matched to  $50\Omega$ , potentially requiring a large amount of power to drive the input of one of these components. Conversely, if a component is being designed in a single-chip, integrated environment, the input to the component can be made nominally capacitive (especially in CMOS, where the gate input is capacitive), and very little "real" power needs to be consumed to drive it.

Another key issue in the design of PAs is the issue of linearity. With efficiency being so dominant a concern in the end, designers look to boost the efficiency by any means necessary, even if it comes at the expense of another design parameter, like the linearity. In many systems, however, that is not an unreasonable trade-off; the reason being that many communications systems in use today utilize modulation schemes that allow for reduced linearity performance in PAs. In general, modulation schemes can be separated into two basic categories: constant-envelope and non-constant-envelope. In the former, there is no symbol information contained in the amplitude of the transmitted signal, and thus there does not need to be a linear relationship between the input and the output; the output signal will contain only one magnitude at a given time. In the non-constant-envelope case, there is symbol information contained in the transmitted signal, so the PA must accurately amplify the amplitude of the signal that it is driven with. Non-linearity in the PA can cause the transmitted signal to contain the incorrect information, corrupting the communications link.

In the constant-envelope modulation scheme, the symbol information is transmitted in the phase of the transmitted signal. Therefore, what is important is that the signal path not distort the phase of the signal. Unlike the non-constant-envelope case, the signal to be transmitted will have a constant amplitude, since no information is contained therein, and the PA will convert that to a constant amplitude output signal. Even if the PA does not linearly amplify differing input amplitudes, that is acceptable; only one amplitude will be present at any given time. In general, PAs for cellular systems must be able to control their output power level, meaning that they will have to supply different levels of power at different times, but as long as the input-output relationship is known, the input level (an be varied to reach the desired output level (which will still be constant amplitude). The power level variations in the mobile unit usually only vary in between frames (transmit times) for constant-envelope modulation schemes; in a given frame, the power level is constant.

Phase distortion in cellular PAs is a concern among designers. In cellular PAs, especially those in the mobile units, phase distortion manifests itself as spectral regrowth [11], which is often characterized by the Adjacent Channel Power Rejection (ACPR) of the PA. In the frequency domain, the power of the desired signal, which is mostly contained in a specified band, will be spread outside that specified band if the phase information is distorted. Unfortunately, most cellular standards have stringent requirements on the amount of power that can be transmitted in adjacent channels, in order to prevent interference between mobile units. It can be shown, however, that the cause of phase modulation in PAs is AM-PM distortion, or Amplitude Modulation-Nonlinear PAs will convert possible amplitude Phase Modulation distortion. modulation in the signals at the input into phase modulation in the output, which will cause phase distortion[11], but if the input is constant amplitude, the phase information will be converted without distortion. For different amplitudes, the phase delay may be different, but because the amplitude is constant in a given frame, the relative phase between symbols will be unchanged, and the signal will be correctly transmitted. As a

result; PAs with heavy nonlinearities can be investigated for use in systems using constant-envelope modulation schemes.

#### 2.4 PA Classes

In general, PAs can be placed into two different categories: one in which the device nominally acts as a current source (i.e. in its amplifying mode), and one in which the device acts as a switch. One common convention is to refer to the former group as the "linear" class of PAs, even though the specific implementation may have a very nonlinear relationship between input and output. The second category is then usually referred to as the "nonlinear" or "switch-mode" class mode of PAs. Each of the categories has several different sub-classes, which are used to identify the topology used in a particular implementation. Other works go into great detail regarding the different PA classes[8][9][10][13], so that work is not repeated here. A brief look at the different categories and sub-classes will be presented here for the sake of background, but the references should be used for a deeper understanding.

## 2.4.1 "Linear" or Amplification-mode PAs

The term "linear" is enclosed in quotes because the actual input-output relationship of PAs in this category does not have to be linear; as stated earlier, this just identifies the group of PAs in which the device is intended to operate in its amplifying region. For FET devices, that would be the saturation region, whereas for bipolar devices, that would be the forward-active region. Since the devices are meant to operate in their amplifying region, it should be apparent that there will be some relationship between the magnitude of the input and output, regardless of how linear that is.

The big issue in the design of "linear" PAs is the trade-off between linearity

20 2.4 PA Classes

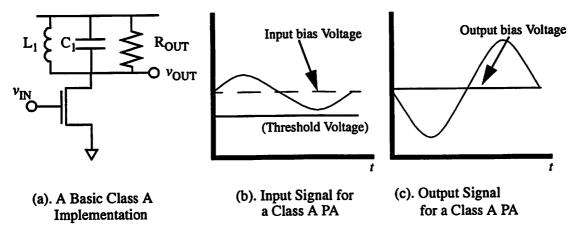

(i.e. the linearity of the input-output relationship) and efficiency. The most linear PAs are those in which the amplification device is always conducting current; the instantaneous current through the device is a function of the instantaneous input, to first order. However, in order for this to be true, the DC bias of the input signal must be quite high, to allow for the device to still conduct current when the input swing is at its lowest point. As a result, the average power that is consumed, even when no signal is applied, can be quite high, and the efficiency will suffer. The above description describes the group of PAs known as Class A PAs, in which the amplifying device conducts current for the entire input sinusoid cycle. Figure 2-4. shows the basic

Figure 2-4. Class A PA Operation

implementation and operating conditions of a Class A PA. The amplifying device (shown here as an FET device) is biased in such a way that it always remains in its amplification region, even under maximum input signal conditions. The input bias voltage is set such that the maximum input swing keeps the input signal above the threshold voltage required to keep the device on (Figure 2-4.b). The output voltage swings around its bias point; in general this is the voltage supply, V<sub>DD</sub>. In an ideal view, the maximum amplitude of the output swing is just VDD, which can help us determine the peak efficiency of the Class A configuration. If we consider that

then the peak efficiency is given by

$$\eta = \frac{\frac{1}{2}V_{DD}\hat{I_o}}{V_{DD}\hat{I_o}} = \frac{1}{2} = 50\%$$

Eq. 2-6

So the peak efficiency of the Class A PA is 50%. However, this is in general not approachable in a realistic implementation. First, most components (both passive and active) will have some amount of real resistive loss in them, and thus there will be some measure of resistive loss due to the current flowing through these parasitic resistances. Moreover, in practice, getting a peak voltage swing of  $V_{DD}$  is usually not possible, as the amplification device will leave its amplification region and enter its resistive region (linear for FETs, saturation for bipolar devices). As a result, the peak voltage swing is reduced; these and other real issues limit the attainable efficiencies of fully Class A PA implementations to about 30%.

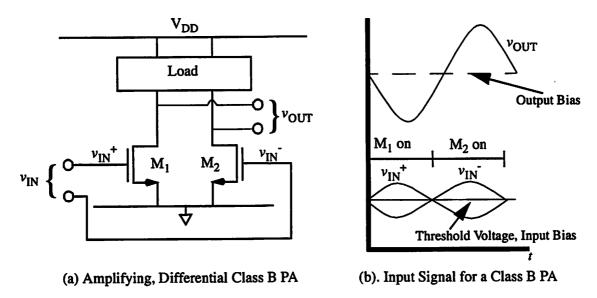

The next possibility would be to consider a PA with a device that was not conducting current all the time. This is the idea behind the Class B PA, sometimes also referred to as a "push-pull" output stage. In standard implementations, two amplification devices are used, each of which amplifies the signal for half the sinusoidal period. The easiest way to accomplish this is to bias the devices such that they are on the edge of conduction in the quiescent state, and then to have the voltage excursions in each direction turn the appropriate device on. That is, as the voltage starts to go above its steady-state value, one of the devices will turn on; as the voltage falls below its steady-state value, that first device turns off and the second device turns on. Figure 2-5. depicts a common implementation and the standard waveforms of the Class B PA. Because each of the devices is only conducting for one half of the input cycle (and not consuming power for the other half of the cycle), the efficiency of this implementation is greater than that of the Class A implementation. The theoretical peak efficiency of the Class B PA can be calculated to be

$$\eta = \frac{\pi}{4} = 0.78 = 78\%$$

[12].

2.4 PA Classes

Figure 2-5. Class B PA Implementation

In practice, efficiencies of the Class B implementation can reach 50% or slightly more. However, the linearity of the PA is degraded in this implementation. Not only are there issues of matching between the two devices (if the gain through the devices is not exactly the same, the output will not be a smooth sinusoid), but if the two devices are not biased exactly at their threshold voltages, the issue of crossover distortion arises. Crossover distortion occurs when both devices are in their off-states when the input signal crosses zero. So while the efficiency of the stage has increased, the linearity has decreased.

One method of achieving somewhat better linearity is to compromise between the Class A and Class B implementations. This is known as the Class AB implementation. The PA is now biased such that it is on for more than half the cycle (but not the entire cycle). In this case, the issue of a "dead" period when the crossover point is reached is avoided, because there is a portion when both devices in a push-pull implementation are on. In narrowband RF implementations, Class B and AB PAs can also be implemented using a single device, as an RF filter at the output can be used to extract the fundamental frequency component of the output waveform. Normally, a

single device implementation would pose a problem, in that the device would be off for part of the input cycle, giving a chopped, and thus extremely distorted, waveform. However, through the use of narrowband RF filters, the component of the output waveform at the fundamental frequency can be extracted, and the amount of distortion can be reduced.

It is precisely because of this narrowband nature that it is possible to use a PA in which the bias voltage is further reduced, below the turn-on voltage of the device. This is the Class C PA, the focus of this work. The Class C PA will be discussed in great detail in Section 2.5, but briefly, the PA is biased below its turn-on voltage, and the input drives the device on for a small portion (less than half) of the input cycle. This creates a pulsed current in the device; this pulsed current is then filtered, so as to extract the fundamental frequency component, which is then passed to the resistive load, creating an output waveform that is at the fundamental frequency. Again, this will be discussed in more detail in Section 2.5.

## 2.4.2 "Nonlinear" or Switch-mode PAs

The group of Nonlinear PAs is also known by a more descriptive name: switch-mode PAs. These are the PAs in which the device is meant to act as a switch. For RF PAs, the two classes of switched mode PAs which have received the most attention are Class D PAs and Class E PAs. If the process of signal amplification is thought of as a power conversion process, then switched mode techniques used in power conversion systems, such as DC-DC converters or regulators, can be used in these PA applications. That is the heart of the Class D and Class E architectures.

The Class D PA is the first of these switched-mode classes of PAs, and has recently been implemented in a CMOS implementation[15]. In the Class D PA, current from the supply is steered between the device, when the switch is closed, and the load, when the switch is open. The Class D architecture is similar to what is used in a bridge

DC-DC converter[13]. In that style of DC-DC converter, devices acting as switches change the polarity of the input voltage onto the load, and the resulting output is averaged to create a output voltage that is some fraction of the input voltage, depending on the duty cycle of the switching. This push-pull action can also be used in the design of an RF PA, where the load is connected to switches which switch the voltage across the load. If the switching is done at the output carrier frequency, the narrowband nature of the transmitted signal allows the use of the RF filters to pass only the fundamental frequency component. Again, because of the ability to filter out unwanted components of the output signal, this type of amplification can be done with only one device, in which case the power from the supply is either sunk in the device or the load. Because of the use of a series L-C circuit tuned to the output frequency, the current in the device will be a sinusoid for the period that it conducts current. If two devices are used, each will carry a half-sinusoidal current waveform (each will be on for half of each cycle). If the implementation of the switch is assumed to be ideal, i.e. no on-resistance and the output voltage is exactly zero when the switch is closed, the ideal maximum efficiency of the power stage can be 100%, as no power will be consumed in the transistor. However, due to non-zero on-resistance, the maximum attainable efficiencies can be dramatically reduced, especially in CMOS implementations; one published result of a Class D PA in CMOS shows a drain efficiency of 62%[15].

The Class E PA, while like the Class D PA, uses the idea of soft switching in order to further reduce any power consumed by the device in the switched-mode PA. This class of PA has also been recently implemented in a CMOS implementation[16]. Essentially, the Class E PA tries to force the voltage on the output node to zero at the instant that the switch is closed, so that there is ideally no time at that transition when both the output voltage and current are non-zero[14]. Not only that, but there is also no CV<sup>2</sup> energy loss from the output capacitance discharging as the switch is turned on. Similarly, the Class E PA is designed to force the current flowing in the switch to be zero at the instant that the switch opens. Again, this is to ensure that there is no period

of time around that transition when both the current and voltage are non-zero. Also, in order to account for timing errors in the switching instants, the slope of the output voltage waveform should also be zero at the instant of that the switch closes. Thus if there is any timing error in when the switch closes, the power consumed because of any overlap in the output current and voltage waveforms will be minimal; since the slope of the output voltage at the correct instant is zero, the value of the output voltage at instants close to the output voltage will be very small. The basic operation and voltage

Figure 2-6. Class E PA Implementation and Waveforms

waveforms of the Class E PA can be seen in Figure 2-6[16]. In the figure, the switch is used to represent the transistor. Like the Class D PA, the theoretical peak efficiency of the Class E PA is 100%; again, practical considerations, especially in CMOS limitations, have limited the efficiency to about 50%[16], although GaAs implementations have reached close to 60% efficiency[17].

# 2.5 Class C Power Amplifiers

The focus of this work is the design and implementation of Class C Power Amplifiers; in this section, the operation of Class C PAs will be discussed in detail. As state earlier, the Class C PA takes the progression from Class A to Class B PAs and

carries it even further. The simple explanation is to say that the device is biased below its threshold or turn-on voltage; the input drive turns the device on for a small portion of the input sinusoidal cycle. However, in order to completely understand what happens in the Class C PA, a deeper investigation must be undertaken; this investigation must not only include the Class C mode of operation as well as what happens when a specific type of device is operated under those conditions.

## 2.5.1 Idealized Analysis

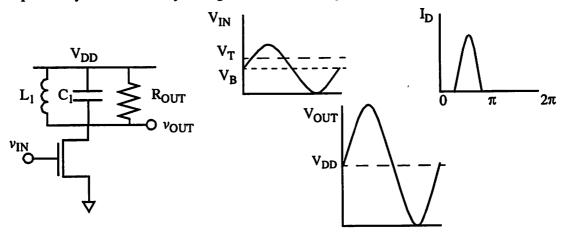

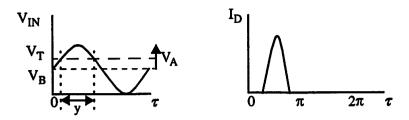

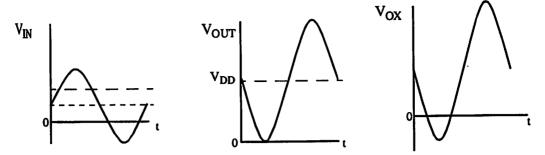

The basic implementation and operation of the Class C PA is shown in Figure

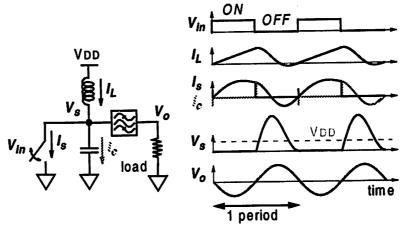

Figure 2-7. Class C PA Implementation and Waveforms

2-7. The PA is biased below its threshold voltage, and the input signal drive turns the device for a fraction of the input signal cycle. This in turn generates a current that is pulsed in the device; the current is then filtered, with the fundamental frequency component going through the desired load. Unlike a switched-mode PA, the theoretical maximum efficiency is not 100%, which can be seen from the fact that the current and output voltage waveforms are both non-zero at the same time; the device does consume power. However, it can be seen that this overlap region is considerably smaller than that in the Class A or B cases, and the voltage is close to zero while the current is non-

zero, if the output voltage is indeed swinging almost down to ground. As a result, the efficiency can be considerably higher than in the other "linear" cases.

To further understand the operation of the Class C PA, a simple analysis can be done, using an idealized model. First assume that the device to be used has some function that relates the output current and the input voltage, as in Eq. 2-8:

$$I_{DEVICE} = K f(v_{IN}).$$

Eq. 2-8

Assuming further that the input is sinusoidal, the current over one period can be defined by the following piecewise equation:

$$I_{DEVICE} = \frac{0}{K f(v_{IN})}$$

for  $v_{IN} < turn-on \ voltage$  Eq. 2-9

In the narrowband RF case, the assumption is made that a narrowband RF filter can be used to extract the fundamental frequency component of the current while suppressing the higher order harmonics. Thus, using a Fourier Series expansion, the current delivered to the load is given by

$$I_{LOAD} = \frac{1}{T} \int (\sin \tau) (I_{DEVICE}) = \frac{1}{2\pi} \int_{\tau_I}^{\tau_2} (\sin \tau) (K f(v_{IN})) d\tau , \qquad \text{Eq. 2-10}$$

where  $\tau_2$  and  $\tau_1$  are the endpoints of the period during the cycle when the voltage is above the turn-on voltage and thus current flows through the device.

Ideally, the load is a resistive one, so the output voltage is known to be

$$v_{OUT} = I_{LOAD}R_{LOAD}sin\tau$$

. Eq. 2-11

Knowing this, the output power and efficiency can be calculated. The output power is simply

$$P_{OUT} = \frac{I_{LOAD}^{2}}{2} R_{LOAD}$$

Eq. 2-12

Finally, in order to calculate the efficiency, the total power drawn from the supply must be calculated. The active device is the only element of the circuit that draws current from the supply, so the total power consumed from the supply is

$$P_{DC} = V_{DD}I_{AVG} = \frac{V_{DD}}{2\pi} \int_{\omega_I}^{\omega_2} K f(v_{IN}) d\omega.$$

Eq. 2-13

As stated earlier, the efficiency is just the ratio of  $P_{OUT}$  to  $P_{DC}$ . However, as will be seen in the next section, this is purely an ideal and theoretical analysis. Device non-idealities make the full analysis much more difficult.

#### 2.5.2 Class C PA Non-Idealities

Stated simply, there are many nonidealities in the Class C PA that are present when a real device is used in the implementation. Among the factors that must be accounted for are the finite gain in the device, region of operation of the device, and the nonlinear output capacitance of the device. Each of these factors will be discussed in detail in this section.

First, the finite gain of any real device which is used in this class of PAs becomes a problem because the amount of current that is generated in the device is small. An examination of the output current waveform makes this easy to understand.

Figure 2-8. Class C PA Current Waveforms

Sample waveforms are shown in Figure 2-8.  $\theta_c$  is defined as the conduction angle, which defines the portion of the cycle that the device is on, or conducting; it is equivalent to the difference between  $\tau_2$  and  $\tau_1$  used in the previous section. As the

conduction angle is reduced, the amount of current through the device is reduced as well. More importantly, the magnitude of the fundamental frequency component, which determines the power delivered to the load, is reduced as well. However, the efficiency is increased at the same time. Taken to its logical extension, this says that as  $\theta_c$  approaches zero, the efficiency tends to 100%, but the power delivered to the load tends to zero as well! Since this extreme case is more of a quirk than anything else, a realistic Class C PA will never get 100% efficiency and any semblance of output power; essentially, infinite gain would be needed to get non-zero output power in that case.

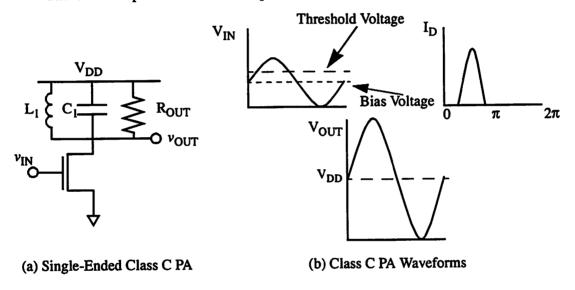

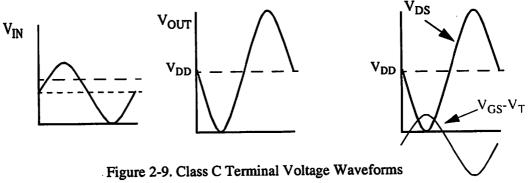

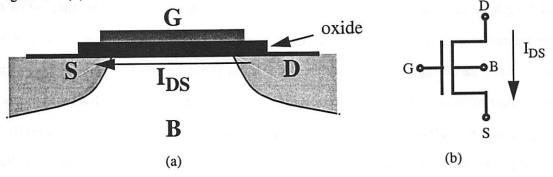

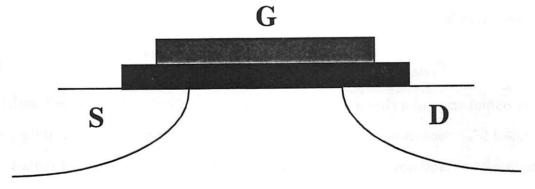

The second issue that must be considered is the region of operation of the device, which becomes especially critical in the case of a MOS implementation. To a first approximation, the region of operation of a MOS device is determined by its terminal voltages. Assuming that the source and bulk are at the same potential, the device conducts current when its gate-source voltage,  $V_{GS}$ , is greater than its threshold voltage  $V_T$ . It is in the saturation region (in which it is best used as an amplifier) when its  $V_{GS}$  is greater than  $V_T$  and its drain source voltage,  $V_{DS}$ , is greater than the difference between the  $V_{GS}$  and  $V_T$ . When  $V_{DS}$  is less than the difference between the  $V_{GS}$  and  $V_T$ , the device is in the triode or linear region. Ideally, an MOS PA which is supposed to be a "linear" PA should have its device in the saturation region while it is on. However, under conditions where the output swing is at its maximum, the terminal

voltages may violate that rule, as shown in Figure 2-9. Under conditions of maximum swing, the output voltage, and thus the  $V_{\rm DS}$  of the device, will be less than the

difference of the  $V_{GS}$  and the  $V_{T}$  of the device, forcing the device into the triode region for a portion of the input cycle. As a result, the operation of the entire circuit is affected during this peak condition, and cannot be so easily described. This mode of Class-C operation is known as mixed-mode Class C operation[10], as opposed to "true" Class C operation, or the case described in the idealized section (the device is always in its amplification mode when on).

#### 2.5.3 Benefits of Class C PAs

In the previous sections, it has been established that Class C PAs can not, even theoretically, reach 100% efficiency with any real power output, and that at maximum power output conditions, the Class C PA so deviates from ideal operation that it is very difficult to accurately describe the operation. The question that arises next is why such a PA should be investigated then; switched-mode PAs may offer equal or better efficiencies, without the design complexities and uncertainties that come with the Class C PA. The answer to this lies in the relationship between input amplitude and output amplitude of the respective PAs. In the Class C case, while the input-output relationship is nonlinear, the output amplitude still varies with a varied input level. However, in the case of switched-mode PAs, the output amplitude is fixed relative to the input amplitude. Since the device used in the PA is meant to act like a switch, the input signal, once large enough to close the switch, does not further affect the output amplitude, to first order. Because switched-mode PAs work by "switching" the voltage across the load between the supply and ground, the only way to control the level of the output is by controlling the supply voltage; therefore, in switched-mode PAs, an agile voltage regulator is needed in order to control the output power level. That is one more block that needs to be designed, and one more block that directly reduces the efficiency of the PA. While constant-envelope modulation schemes have constant power while transmitting in a given frame, most cellular communications schemes require that the mobile PA be able to transmit different power levels at different times, depending on the conditions around the mobile user. The Class C PA can do this simply by varying its input signal level. This advantage, added to the efficiency improvement that can be gained over standard Class A or B PAs, makes this investigation important.

Even more importantly, the future of communications systems is moving towards non-constant envelope modulation schemes. As the demand for higher datarates in wireless systems becomes overwhelming, the next generation systems are moving towards including data in both the amplitude as well as phase of the transmitted signals, requiring very linear PAs. There are two ways to improve PA linearity. The first is to use an extremely linear, but highly inefficient PA, like a Class A PA. This solves the linearity problem, but dramatically reduces the battery life of a portable unit. The second solution is to continue to use a higher efficiency PA architecture (like Class C or higher), but then to try to improve the linearity of the PA or the entire transmitter. There are several schemes for transmitter linearization, including Cartesian Feedback [18], Digital Predistortion[19][20], and Feed Forward[21], among others. One benefit of the Class C PA over the switched-mode PAs in this case is that because of the input-output amplitude relationship, Class C PAs can be used with methods like Cartesian Feedback, which vary the amplitude of the input.

Therefore, an investigation into the design of a Class C PA is needed; the Class C PA does have benefits over the more linear types of PAs (i.e. better efficiency), as well as over the switched-mode classes of PAs, as stated above.

#### 2.5.4 What Is Needed

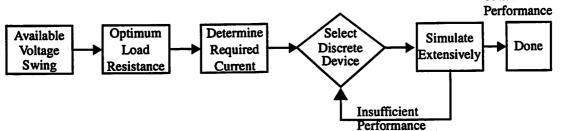

In order to design and implement a Class C PA, a lot of work is needed. First and foremost, the issue of the mixed-mode PA must be addressed. To this point, no clear method exists to design a mixed-mode Class C PA. It would be beneficial if some type of design methodology or design guidelines existed, whereby a designer could avoid the blind utilization of circuit analysis software as the sole means of reaching the

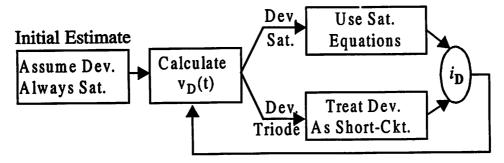

desired design goal. Currently, the method used to design extremely non-linear amplification-mode PAs is extremely empirical. A simple flow chart indicating the standard procedure is shown in Figure 2-10. An optimum load resistance is determined Sufficient

Figure 2-10. Standard Non-linear PA Design Procedure

from the voltage swing available of the output of the device. In general, these PAs are designed using discrete transistor devices; as a result, each of these devices is extremely well-categorized and its performance is well-known. A device is selected, and a corresponding output matching network is selected as well. The PA is simulated; if the performance meets the desired requirements, the design is done. If not, a different device is chosen (or different design parameters, such as bias, etc.) and the process is started again.

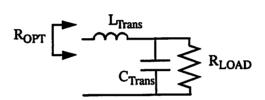

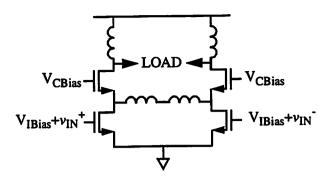

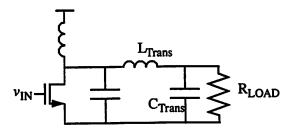

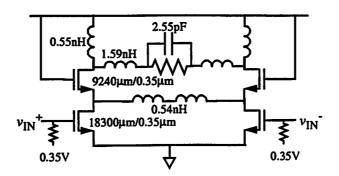

In the case of an integrated CMOS implementation, however, this is not really a viable solution to the problem of PA design. The type of characterization available for the discrete devices mentioned above is not available for integrated devices. Furthermore, while in the case of discrete devices the set of devices to choose from is finite, in the case of a CMOS PA, a whole continuum of possible devices is available, as the device size (both width and length) is an entirely free variable in the design. As a result, a less exact, scalable model is the only one that is available. Using the method described above in this process would be extremely difficult, as there is no a priori method of limiting the device choices as there is in the discrete case. As a result, another method more suited to the CMOS case must be investigated. While the large-signal operation of the circuit may be too complex to come up with a single simple,