Copyright © 2001, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

## PROPOSITIONAL SATISFIABILITY ALGORITHMS IN EDA APPLICATIONS

by

Mukul Ranjan Prasad

Memorandum No. UCB/ERL M01/39

1 December 2001

### PROPOSITIONAL SATISFIABILITY ALGORITHMS IN EDA APPLICATIONS

by

Mukul Ranjan Prasad

Memorandum No. UCB/ERL M01/39

1 December 2001

#### ELECTRONICS RESEARCH LABORATORY

College of Engineering University of California, Berkeley 94720

#### Propositional Satisfiability Algorithms in EDA Applications

by

Mukul Ranjan Prasad

B. Tech. (Indian Institute of Technology, New Delhi) 1995

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

#### GRADUATE DIVISION of the UNIVERSITY of CALIFORNIA at BERKELEY

Committee in charge:

Professor Robert K Brayton, Chair Professor Alberto L Sangiovanni-Vincentelli Professor Ilan Adler

Fall 2001

The dissertation of Mukul Ranjan Prasad is approved:

Chair

.

Date

Date

Date

University of California at Berkeley

2001

## Propositional Satisfiability Algorithms in EDA Applications

Copyright 2001 by Mukul Ranjan Prasad

,

#### Abstract

#### Propositional Satisfiability Algorithms in EDA Applications

by

Mukul Ranjan Prasad

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California at Berkeley

Professor Robert K Brayton, Chair

Recent years have seen a dramatic growth in the application of SAT solvers to problems in electronic design automation. This trend is due in part to recent developments in SAT algorithms which have revolutionized the field of satisfiability testing. SAT has grown from a problem of academic interest to a core computational resource of immense value.

However, despite the significant progress in this domain there is considerable room for improvement in several areas. The goal of this dissertation is to advance the theory, practice and core technology of SAT algorithms in the context of EDA applications. The success of a SAT algorithm in a given EDA application may be ensured by a realistic quantitative assessment of the projected performance of the overall algorithm in a practical setting, by carefully orchestrating the use of SAT in the application and by improving the SAT algorithm per se. This dissertation addresses these three issues.

The first part of the dissertation presents a framework for analyzing the complexity of a SAT based formulation of the combinational ATPG problem, in a practical setting. We introduce the concept of cut-width of a circuit and characterize the complexity of ATPG in terms of this property. We present theoretical results and empirical evidence to argue that a large class of practical circuits can be expected to have cut-width characteristics conducive to an efficient solution of ATPG on them. These results also help to reconcile the intractability of ATPG, as predicted by traditional worst case analysis results, with the relative ease of solving practical instances of the problem.

The second part of the dissertation focuses on the optimum orchestration of SAT methods for a given EDA application. We revisit the application of SAT algorithms to the combinational equivalence checking (CEC) problem. We argue that SAT is a more robust and flexible engine of Boolean reasoning for the CEC application than binary decision diagrams (BDDs), which have traditionally been the method of choice. Preliminary results on a simple framework for SAT-based CEC show a speedup of up to two orders of magnitude over previous methods for SAT-based CEC. Further, the prototype implementation is only moderately slower and sometimes faster than a state-of-the-art BDD-based mixed-engine commercial CEC tool.

The third and final part of the dissertation is aimed at enhancing the core techniques used in current SAT solvers. We introduce the notion of *problem symmetry* in search based SAT algorithms. We develop a *theory of essential points* to formally characterize the potential search space pruning that can be realized by exploiting problem symmetry. We unify several powerful search pruning techniques used in modern SAT solvers under a single framework, by showing them to be special cases of the theory of essential points. We also propose a new pruning rule exploiting problem symmetry. Preliminary experimental results validate the efficacy of this rule in providing additional search space pruning over the pruning realized by techniques implemented in leading-edge SAT solvers.

> Professor Robert K Brayton Dissertation Committee Chair

To Mummy & Papa ...

en en la companya de la comp La companya de la comp

## Contents

| Lis | st of | Figure  | :S                                                            | vii  |

|-----|-------|---------|---------------------------------------------------------------|------|

| Lis | st of | Tables  | i                                                             | viii |

| Lis | st of | Algori  | thms                                                          | ix   |

| 1   | Intr  | oducti  | on                                                            | 1    |

|     | 1.1   | The P   | ropositional Satisfiability (SAT) Problem                     | 1    |

|     | 1.2   | SAT ir  | EDA Applications                                              | 2    |

|     | 1.3   | Thesis  | Overview & Organization                                       | 3    |

| 2   | Pre   | liminaı | ries                                                          | 8    |

|     | 2.1   | Propos  | sitional Variables & Literals                                 | 8    |

|     | 2.2   | Conju   | nctive Normal Form (CNF) Formulas                             | 8    |

|     | 2.3   | The Sa  | atisfiability Problem                                         |      |

|     | 2.4   | The D   | avis-Putnam-Logemann-Loveland (DPLL) Search Algorithm for SAT | 11   |

|     |       | 2.4.1   | The Unit Literal Rule                                         | 12   |

|     |       | 2.4.2   | The Pure Literal Rule                                         | 14   |

|     | 2.5   | The D   | avis-Putnam Resolution Algorithm for SAT                      |      |

|     | 2.6   | Advan   | ced Pruning Techniques in Search Algorithms                   |      |

|     |       | 2.6.1   | Conflict Based Learning                                       |      |

|     |       | 2.6.2   | Non-chronological Backtracking                                |      |

|     | 2.7   | Transf  | formation of Non-Clausal SAT problems to CNF                  |      |

|     |       | 2.7.1   | CNF Representations of Propositional Formulas                 |      |

|     |       | 2.7.2   | Solving SAT problems on Logic Circuits                        | 22   |

| 3   | SA    | Г Algo  | rithms in EDA: Recent Developments                            | 26   |

|     | 3.1   | SAT A   | Algorithms & Tools                                            |      |

|     |       | 3.1.1   | Complete SAT Solvers                                          |      |

|     |       |         | 3.1.1.1 SAT Solvers based on Propositional Formulas           |      |

|     |       |         | 3.1.1.2 Circuit Based Boolean Reasoning                       |      |

|     |       |         | 3.1.1.3 Other improvements to SAT solvers                     |      |

|     |       | 3.1.2   | Incomplete SAT Solvers                                        |      |

|     | 3.2   | SAT A   | Applications in EDA                                           | . 32 |

|   |      | 3.2.1 SAT in Verification                                                                                 | 32         |

|---|------|-----------------------------------------------------------------------------------------------------------|------------|

|   |      | 3.2.2 Other Applications                                                                                  | <b>34</b>  |

|   | 3.3  | Conclusions                                                                                               | 5          |

|   |      |                                                                                                           |            |

| 4 | The  |                                                                                                           | 6          |

|   | 4.1  |                                                                                                           | 8          |

|   | 4.2  | 11.2.20                                                                                                   | 1          |

|   |      |                                                                                                           | 1          |

|   |      | 4.2.2 k-bounded Circuits $\ldots \ldots 4$ | 3          |

|   |      | 4.2.3 Average-Time Analysis                                                                               | 3          |

|   | 4.3  |                                                                                                           | 6          |

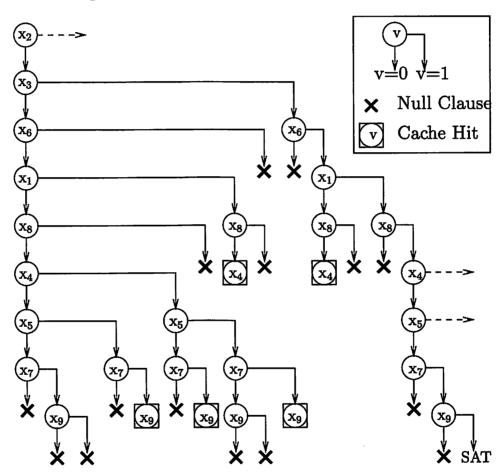

|   |      | 4.3.1 Caching-Based Backtracking for CIRCUIT-SAT                                                          | 8          |

|   |      |                                                                                                           | 51         |

|   |      | 4.3.3 Extension to Multi-output Circuits                                                                  | 57         |

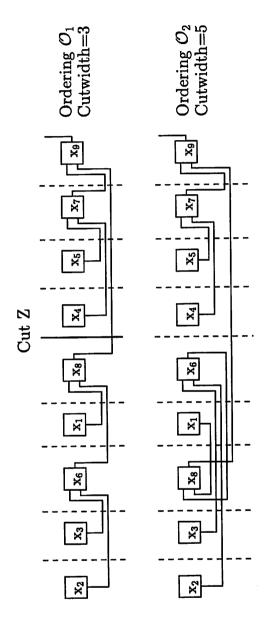

|   | 4.4  | Cut-width Properties of Circuits                                                                          | <b>i</b> 9 |

|   |      | 4.4.1 Log-bounded-width Circuits                                                                          | <b>i</b> 9 |

|   |      |                                                                                                           | 51         |

|   |      | 4.4.2.1 Experimental Setup                                                                                | 51         |

|   |      | -                                                                                                         | <b>i</b> 3 |

|   |      | • •                                                                                                       | 3          |

|   |      | 4.4.2.4 Experimental Results                                                                              | 5          |

|   | 4.5  | BDDs and CIRCUIT-SAT                                                                                      | '1         |

|   | 4.6  | Conclusions                                                                                               | 2          |

|   |      |                                                                                                           |            |

| 5 | SAJ  |                                                                                                           | <b>'4</b>  |

|   | 5.1  | The Combinational Equivalence Checking Problem                                                            | 6'         |

|   | 5.2  | Previous Approaches                                                                                       | 78         |

|   | 5.3  | SAT Vs. BDDs in CEC                                                                                       | <b>'</b> 9 |

|   |      | 5.3.1 Locality and robustness of cutpoint resolution                                                      | <b>'</b> 9 |

|   |      | 5.3.2 Use of previously deduced equivalences                                                              | 30         |

|   |      | 5.3.3 Learning more general relationships                                                                 | 31         |

|   | 5.4  | Proposed Methodology                                                                                      | 32         |

|   |      | 5.4.1 Segment sweeping based deduction                                                                    | 32         |

|   |      | 5.4.2 Global hypothesis based deduction                                                                   | 34         |

|   |      | 5.4.3 Overall Algorithm                                                                                   | 35         |

|   | 5.5  | Experimental Results                                                                                      | <b>36</b>  |

|   | 5.6  | Conclusions and Future Directions                                                                         | 88         |

| ~ | ** • |                                                                                                           | 1          |

| 6 |      | -8                                                                                                        | )1         |

|   | 6.1  |                                                                                                           | )3<br>)4   |

|   | 6.2  |                                                                                                           | )4         |

|   | 6.3  |                                                                                                           | 97         |

|   | 6.4  | - · · · · · · · · · · · · · · · · · · ·                                                                   | 99         |

|   |      |                                                                                                           | 99         |

|   |      | 6.4.2 Non-Chronological Backtracking (NCB) 10                                                             | JU         |

|    |              | 6.4.3  | Conflict Clause Recording                                        | 102 |  |  |

|----|--------------|--------|------------------------------------------------------------------|-----|--|--|

|    | 6.5          | Symme  | etry Based Pruning through Supercubing                           | 103 |  |  |

|    | 0.0          | 6.5.1  | Supercubing Procedure & Pruning                                  | 103 |  |  |

|    |              |        | Proof of Correctness                                             | 104 |  |  |

|    |              |        | Supercubing and Other Pruning Techniques                         | 105 |  |  |

|    | 6.6          |        | mental Results                                                   | 106 |  |  |

|    | 6.7          |        | usions & Future Directions                                       | 108 |  |  |

| 7  | Con          | clusio | ns & Future Directions                                           | 110 |  |  |

| •  | 7.1          |        | • Directions                                                     | 112 |  |  |

|    |              | 7.1.1  | Input-distribution based complexity analysis of EDA-SAT problems | 112 |  |  |

|    |              | 7.1.2  | Using SAT methods in EDA problems                                | 113 |  |  |

|    |              | 7.1.3  | Improvements to SAT algorithms and tools                         |     |  |  |

| Bi | Bibliography |        |                                                                  |     |  |  |

•

# List of Figures

.

| 1.1  | SAT in a typical IC Design & Verification flow                             |

|------|----------------------------------------------------------------------------|

| 1.2  | Research overview                                                          |

| 2.1  | An Example of Non-chronological Backtracking [MSS99]                       |

| 2.2  | CNF formulas for 2-input & 1-input simple gates 25                         |

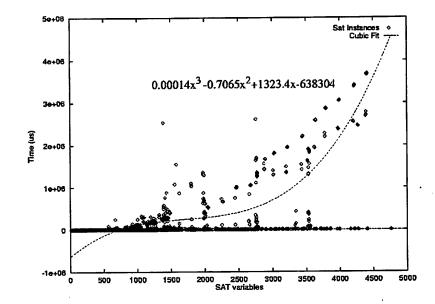

| 4.1  | Results of TEGUS on ATPG-SAT instances                                     |

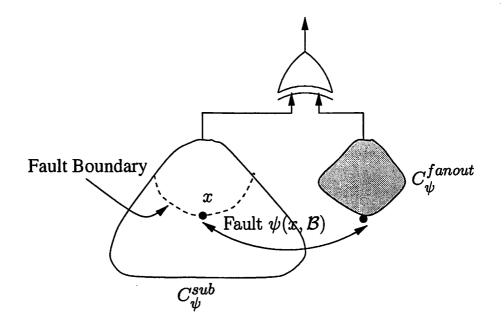

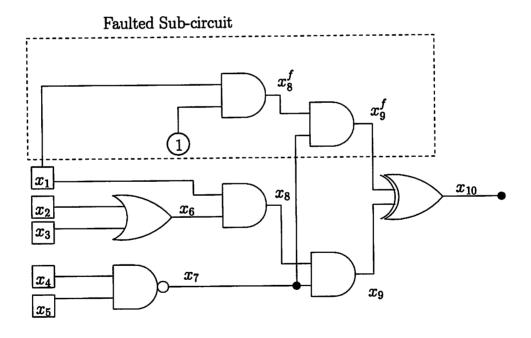

| 4.2  | Circuit $C_{\psi}^{ATPG}$ used for ATPG-SAT                                |

| 4.3  | A simple sub-circuit $C_{sub}$ that produces a non-q-Horn formula          |

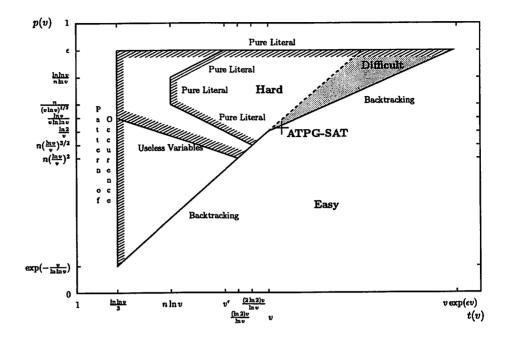

| 4.4  | Average Time Analysis (from [PB87]) 44                                     |

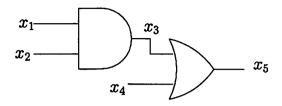

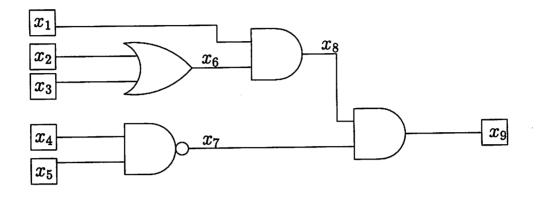

| 4.5  | Example Circuits                                                           |

| 4.6  | Caching-based backtracking for Formula 4.2                                 |

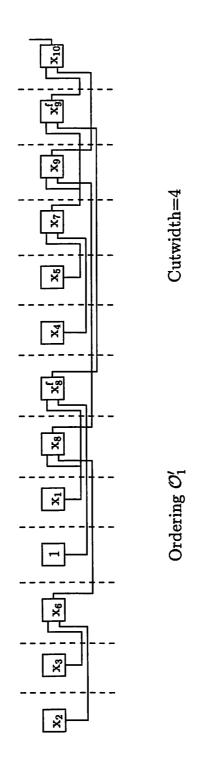

| 4.7  | Example cut-widths for the circuit of Figure 4.5(a)                        |

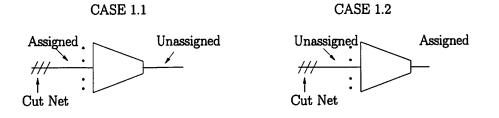

| 4.8  | Case 1 for generating injured clauses                                      |

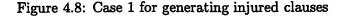

| 4.9  | Case 2 for generating injured clauses                                      |

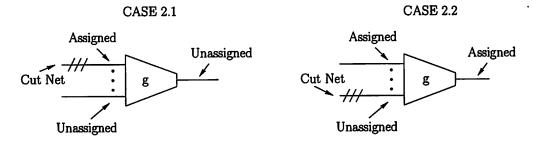

| 4.10 | Proof for ATPG circuit width vs. original circuit width 57                 |

| 4.11 | Example cut-width, ATPG circuit of Figure 4.5(b)                           |

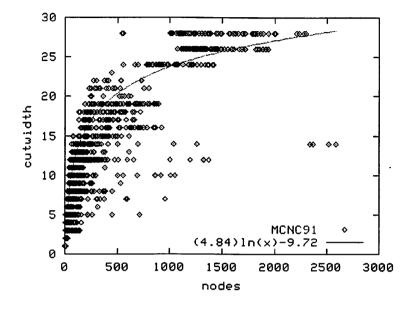

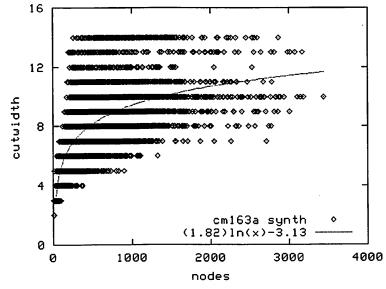

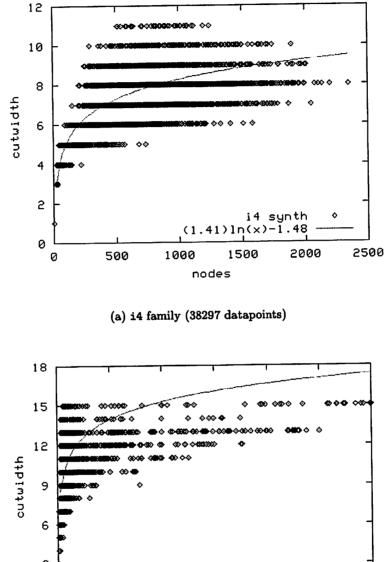

| 4.12 | Cut-width results for benchmark circuits                                   |

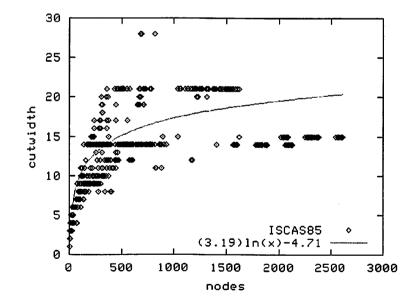

| 4.13 | Cut-width results for generated circuits                                   |

|      | Cut-width results for generated circuits                                   |

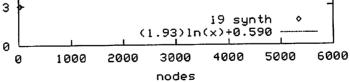

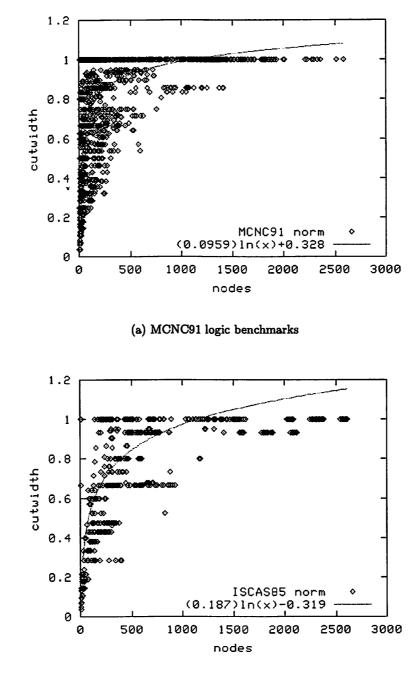

| 4.15 | Normalized cut-width results                                               |

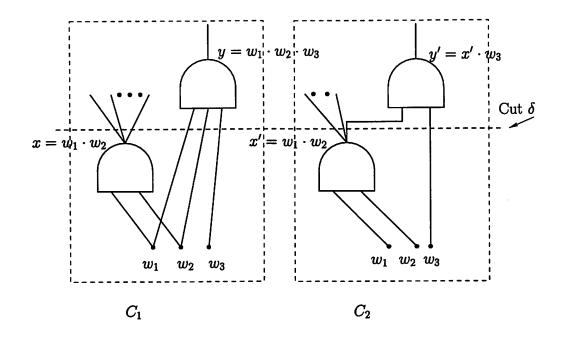

| 5.1  | False Negatives can be resolved by local BCP                               |

| 5.2  | Previously deduced equivalences as shallow witnesses of false negatives 81 |

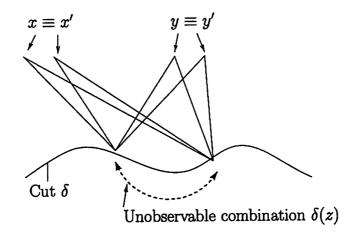

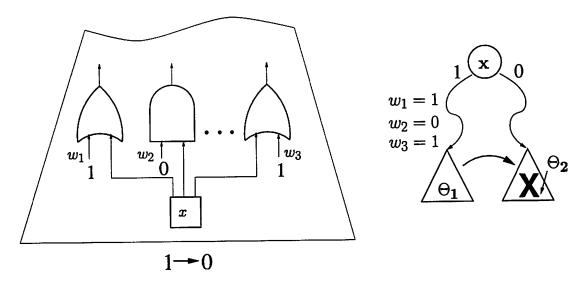

| 6.1  | Illustration of Symmetry in Search                                         |

| 6.2  | Example of Symmetry in SAT on circuits                                     |

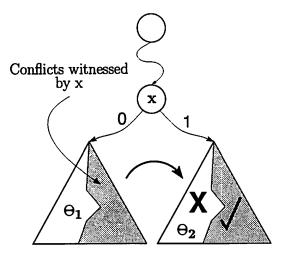

| 6.3  | Example of Symmetry in backtrack search                                    |

## List of Tables

| 2.1        | The disjunction operator over $\{0,1,X\}$                                      | 10  |

|------------|--------------------------------------------------------------------------------|-----|

| 22         | The conjunction operator over $\{0, 1, X\}$                                    | 11  |

| 2.2<br>2.3 | CNF formulas for simple gates                                                  | 24  |

| 4.1        | Sum of squared errors for various functional fits on each data set (Normalized |     |

|            | by a factor of $10^5$ )                                                        | 68  |

| 5.1        | Verifying original vs. irredundant circuits                                    | 87  |

| 5.2        | Verifying original vs. optimized circuits                                      | 88  |

| 6.1        | Experimental results with Supercubing                                          | 107 |

# List of Algorithms

| 2.1 | DPLL Algorithm for SAT                                          | 13 |

|-----|-----------------------------------------------------------------|----|

| 2.2 | $BCP(A_{curr})$                                                 | 14 |

| 2.3 | $\mathrm{DP}_{\mathrm{Resolve}}\operatorname{Variable}(\phi,x)$ | 15 |

| 4.1 | Satisfiability through Caching-Based Backtracking               | 49 |

| 5.1 | Global Hypothesis Deduction                                     | 85 |

#### Acknowledgements

First and foremost I would like to thank my research advisor Prof. Robert K Brayton for his invaluable support and guidance. Bob continues to inspire me with his dedication, perseverance, integrity and professionalism. I am grateful to him for giving me the freedom to choose a research area best suited to my interests and aptitude and for moulding my research efforts into a meaningful contribution.

I am grateful to Prof. Alberto Sangiovanni-Vincentelli for his support and encouragement during my stay at Berkeley. I have had the good fortune of interacting with him in several capacities and have immensely benefited from this association. I would also like to thank Prof. Kurt Keutzer for his constructive feedback as chair of my qualifying examination committee. The research presented in this dissertation was seeded through a class project under his guidance.

I would also like to thank Prof. Ilan Adler and Prof. Shmuel Oren for their insightful comments and feedback as members of my dissertation committee and qualifying examination committee respectively.

My research efforts at Berkeley have given me the opportunity to interact and collaborate with several bright individuals. A special word of gratitude for Eugene Goldberg who has worked with me as my mentor, colleague and friend over the last two years. The research presented in Chapters 5 and 6 is a result of collaborative work with him. My close interaction with him has helped me appreciate the value of unconventional and fundamental thinking. I would like to thank Philip Chong for his contribution to the work presented in Chapter 4. I have been fortunate to collaborate with Gurmeet Singh Manku, Desmond Kirkpatrick, Sunil Khatri, Amit Mehrotra and Freddy Mang on various other research problems, although that research is not included in this dissertation. I would also like to acknowledge Prof. João Poalo Marques-Silva of the Technical University of Lisbon and Dr. Andreas Kuehlmann of Cadence Berkeley Labs. for the many interesting and fruitful discussions I have had with them regarding my research.

The CAD group at Berkeley provided a stimulating and friendly environment for me during my student life at Berkeley. Several individuals in this group have contributed to making my stay here a memorable one. I would like to thank Rajeev Murgai, Harry Hsieh, Shaz Qadeer, Sriram Rajamani, Premal Buch, Amit Narayan, Alok Agrawal, Sriram Krishnan, Adnan Aziz, Edoardo Charbon and Yuji Kukimoto for their constructive advice and guidance, my cubicle-mates Mark Spiller, Claudio Pinello and Marco Sgroi for putting up with me and Lixin Su, Wilsin Gosti and Luca Carloni for their support and company. I would also like to thank my friends and colleagues Kaustav Banerjee, Rizwan Rahmani, Kiran and Jawahar Jain for their tangible and intangible contributions to both personal and professional aspects of my life at Berkeley.

I am grateful to the administrative and support staff in the EECS department at Berkeley for promptly and efficiently attending to my needs over the years. Ruth Gjerde, Brad Krebs, Flora Oviedo and Diane Chang deserve a special word of thanks for their assistance.

The research presented in this dissertation was supported by the California MI-CRO program and Cadence Berkeley Laboratories. Their generous support is gratefully acknowledged.

Finally, I would like to thank my family for their love and support. My father Dr. Girish Prasad and my mother Prabha Prasad have always been my role models and sources of inspiration. It was they who encouraged me to pursue a career in engineering and to come to the US to further my aspirations. Their love, guidance, sacrifice, support and unflinching belief in my capabilities have always helped me surmount the toughest of challenges with ease. I owe all my achievements, past, present and future to them. The past year has been the most challenging and rewarding periods of my professional career, thus far. I would like to thank my wife Shuchi for her love, encouragement, sacrifice and support which helped me get through this time and come out stronger. I would also like to thank my sister and brother-in-law Meenakshi and Atul Garg, my parents-in-law Prof. R.C. Jain and Saroj Jain and the rest of my extended family in the San Francisco Bay area for their love and support over the years. Last but not least I would like to thank God almighty.

## Chapter 1

## Introduction

### 1.1 The Propositional Satisfiability (SAT) Problem

The Propositional Satisfiability (SAT) problem is a core problem in mathematical logic and computing theory. The SAT problem is known to be NP-Complete [GJ79], one of the first problems to be proven NP-Complete. Thus it is generally accepted that any algorithmic technique for solving an arbitrary instance of SAT could require, in the worst-case, computational resources exponential in the size of the problem. In other words it is highly unlikely that there exists an algorithm for SAT that can solve an arbitrary instance of the problem, efficiently<sup>1</sup>.

Over the years, several interesting problems from various applications in logic and computer science have been modeled as satisfiability problems. Moreover, several instances of such problems, arising in practise, can be efficiently solved by SAT solvers. Thus, any advance in SAT solver technology may translate into significant improvements in several practical applications. This potential coupled with the simple formulation of the satisfiability problem and its inherent intractability has continued to interest theoreticians and practitioners alike, over the last four decades.

There have been significant advancements in SAT solver technology since the first complete algorithm for Boolean Satisfiability proposed by Davis and Putnam [DP60] in 1960. In current practice SAT is fundamental in solving several problems in areas as diverse as automated reasoning, computer-aided manufacturing, machine vision, databases, robotics,

<sup>&</sup>lt;sup>1</sup>By efficiently we mean that the algorithm uses computational resources polynomial in the size of the problem.

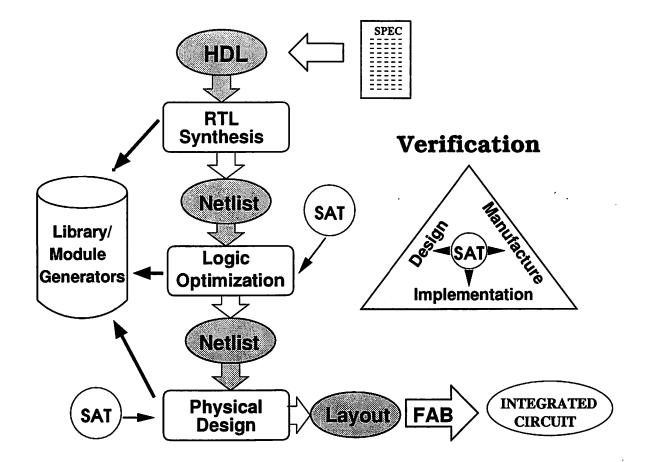

Figure 1.1: SAT in a typical IC Design & Verification flow

computer architecture and computer network design [GPFW97]. This ever-widening gamut of SAT applications continues to fuel further research in this area.

#### **1.2 SAT in EDA Applications**

The design and manufacture of integrated circuits is a complex process. Its richness and complexity translates into a number of challenging problems in electronic design automation which offers a fertile ground for application of optimization and decision procedures such as Boolean Satisfiability.

The use of SAT procedures for EDA applications is a relatively recent phenomenon. While branch and bound procedures, somewhat similar (although not nearly as powerful) to those used in SAT solvers, have been employed in EDA tools for some time now, the application of SAT solvers per se to EDA problems is only a decade old.

Recent years have seen dramatic improvements in SAT algorithms and tools [Zha97, MSS99, MMZ<sup>+01</sup>], allowing much larger problem instances to be solved. It is not uncommon for current leading-edge SAT solvers to efficiently handle problem instances with thousands of variables and tens of thousands of clauses [MMZ<sup>+01</sup>]. This has expanded the realm of applicability of SAT solvers in EDA and fueled the growth of SAT from a problem, primarily of academic interest, to an enabling technology for several EDA applications. Spurred by these recent advancements SAT algorithms have been successfully applied to solve problems from a wide variety of EDA applications such as Automatic Test Pattern Generation (ATPG), timing analysis, sequential and combinational logic optimization, crosstalk noise analysis, FPGA routing, functional vector generation, combinational equivalence checking, reachability analysis, model checking and microprocessor verification [MSS00].

Figure 1.1 shows the potential role of SAT in a typical design and verification flow for integrated circuits. It shows that SAT formulations can be employed in almost all major steps of the design process and in all aspects of verification *i.e.* design, implementation and manufacture verification. Despite this significant progress much ground remains to be covered in several areas.

The current level of understanding regarding the strengths and weaknesses of SAT in the context of various EDA problem settings is limited. A deeper theoretical as well practical understanding of these issues may lead to more effective ways of using SAT for EDA problems. This has been an impediment in making SAT the method of choice for certain applications or having it work with more established engines such as structural ATPG and BDD methods. The other aspect is of course to develop more effective core SAT methods to expand the scope of SAT to emerging EDA applications.

#### **1.3 Thesis Overview & Organization**

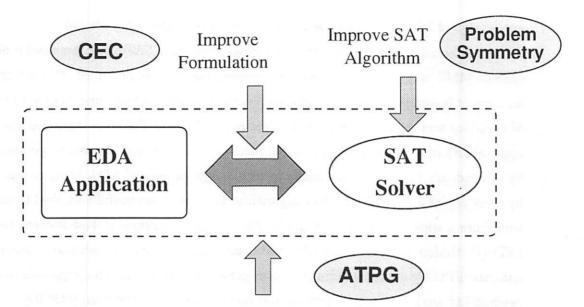

The research described in this dissertation is aimed at advancing the theory, practice and core technology of SAT algorithms in the context of EDA applications. Figure 1.2 shows the general setting in which this research is based. The scenario is that of a SAT solver being applied to solve or aid in the solution of EDA applications such as combinational verification, ATPG *etc.* The various components of this dissertation focus on different aspects of enhancing the efficacy of such a combination. Specifically, this work addresses

Input-Based Complexity Analysis

Figure 1.2: Research overview

the following three aspects:

1. Input Distribution Dependent Complexity Analysis: The first step in trying to solve a given application through a certain algorithm is to perform a formal quantitative analysis of the complexity of the problem and the expected performance of the algorithm on the given problem<sup>2</sup>. In practice, and specifically in the EDA community, the kind of performance analysis that is done is a worst case complexity analysis. By definition, it is pessimistic. This fact assumes greater relevance in our context, *i.e.* SAT used in an EDA application. SAT is known to be NP-Complete [GJ79] and probably the EDA application it is being used in is also NP-Complete or even harder<sup>3</sup>. Thus worst case complexity analysis might imply that there is little hope of any practical success. The reality is quite the contrary. The answer lies in the fact that SAT instances coming from EDA applications are a specialized and structured subset of the general class of SAT instances. Traditional worst-case complexity cannot make

<sup>&</sup>lt;sup>2</sup>These two entities are not identical since the problem may have an inherent complexity different from the algorithm employed to solve it.

<sup>&</sup>lt;sup>3</sup>Such is the case with most EDA problems.

this distinction. Therefore, what is required is an analysis that models and accounts for the characteristics of SAT instances arising from EDA applications, in a practical setting.

- 2. SAT formulation: A SAT formulation of a problem determines "how" the solver is being used to solve the application at hand. The formulation determines the number, the nature and the specific CNF representation of SAT instances generated by a single instance of the EDA application as well as the sequence in which these instances are solved by a SAT solver. For example, a single instance of combinational ATPG<sup>4</sup> is typically formulated as a single SAT instance [Lar92] whereas a single instance of a Bounded Model Checking application [BCCZ99] produces a set of SAT instances. In combinational ATPG, the specific CNF representation is key. It has been shown [Lar92, SBSV96] that the addition of fault propagation information to the CNF in the form of clauses known as active clauses can have a dramatic impact to the ease of solving the SAT instance, and hence the solvability of the original ATPG instance. The formulation also determines the configuration of the SAT solver such as the variable ordering heuristic, the information (if any) passed between the SAT solver and other components of the application tool etc. Usually, the formulation stems from insights about the EDA application and empirical guidelines from what works in practice.

- 3. The SAT Solver: Another obvious mode of enhancing the efficiency of an EDA application is to improve the SAT solver itself. This may be general enhancements to the SAT algorithm which may benefit any application using such a solver. For example, recent developments in SAT algorithms such as *conflict based learning* and *non-chronological backtracking* [MSS99] have been shown to be beneficial in most SAT applications. Alternatively, these enhancements could be algorithmic features that more directly benefit the specific application at hand, *e.g.* a recursive learning enhanced SAT solver aimed at learning equivalences [MSG99] is particularly useful for combinational verification but not so effective in other EDA applications.

This dissertation is organized as follows. Chapter 2 develops the notational framework used in the rest of the dissertation. It also presents some fundamental SAT algorithms

<sup>&</sup>lt;sup>4</sup>A single instance refers to the task of testing a particular single stuck-at fault in the circuit

and some recently proposed pruning techniques. These form the foundation on which most of the theoretical results and algorithms developed in this research are based.

Chapter 3 surveys some more recent developments in SAT algorithms and applications, particularly the ones relevant to EDA. These developments have acted as catalysts for SAT research in EDA. Comprehensive surveys on some of the earlier developments on these subjects can be found in [GPFW97] and [MSS00].

The research contribution of this dissertation is organized in three chapters, each addressing one of the three axes of contribution described above.

The first part of the research, presented in Chapter 4 is an attempt at input distribution based complexity analysis of an EDA SAT application. The problem analyzed is a SAT based formulation of the *combinational ATPG* problem. The results shed light on the following paradox. Empirical observation shows that practically encountered instances of combinational ATPG are efficiently solvable. However, it has been known for more than two decades that ATPG is an NP-complete problem [IS75]. The presented analysis is one of the first attempts to reconcile these results. We introduce the concept of *cut-width* of a circuit and characterize the complexity of SAT based ATPG in terms of this property. We introduce the class of *log-bounded width* circuits and prove that SAT based combinational ATPG is efficiently solvable on members of this class. The class of *log-bounded width* circuits is shown to strictly subsume the class of *k-bounded circuits* introduced in [Fuj88]. We provide empirical evidence which indicates that an interestingly large class of practical circuits is expected to have *log-bounded width*. The analysis framework presented is fairly general and could be used to perform a similar analysis of other SAT-EDA problems.

Chapter 5 presents a SAT based algorithmic framework to address the combinational equivalence checking (CEC) problem. This addresses the second aspect described above *i.e.* developing improved methods of using SAT in a typical EDA application. The contributions of this work are twofold. First, it offers a qualitative understanding of aspects or parts of the CEC problem that are best suited to be handled by a SAT solver rather than BDDs, which currently form the computational core of most CEC tools. Second, it develops improved methods of using SAT algorithms for CEC which dramatically outperform previous approaches for SAT based CEC.

Chapter 6 addresses improvements to the core technology of SAT solvers. Specifically, we introduce the notion of *problem symmetry* in search-based SAT algorithms. A *theory of essential points* is developed to characterize the potential search-space pruning that can be realized by exploiting problem symmetry. Several search-pruning techniques used in modern SAT solvers are shown to be special cases of the general theory of essential points. We also propose a new pruning rule exploiting problem symmetry. Preliminary experimental results validate the efficacy of this rule in providing additional search-space pruning beyond the pruning realized by techniques implemented in current leading-edge SAT solvers.

Chapter 7 summarizes the main results and conclusions of this research and presents avenues for improvement and directions for future research.

## Chapter 2

## **Preliminaries**

#### 2.1 Propositional Variables & Literals

Throughout this dissertation, propositional variables (interchangeably referred to as Boolean variables or just variables) will be denoted by symbols drawn from the set of symbols  $[rstuwxyz]_{[0-9]^*}$ . A propositional variable, x can assume a logic value, denoted  $\nu(x)$ , with  $\nu(x) \in \{0, 1, X\}$ . When  $\nu(x) = 1$  (the proposition is **TRUE**) or  $\nu(x) = 0$ (the proposition is **FALSE**), x is said to be assigned and when  $\nu(x) = X$ , x is said to be unassigned. X is also used to denote that the value of the variable is either unknown or undecided.

A literal, l, is an instance of a variable or its complement. e.g. if x is a propositional variable,  $\overline{x}$  and x represent, respectively the complemented and un-complemented literals derived from it, *i.e.* the propositions x = 0 and x = 1 respectively.

The following treatment will assume a set of variables  $V = \{x_1, x_2, \dots, x_N\}$ , the cardinality of which is N or simply |V|.

#### 2.2 Conjunctive Normal Form (CNF) Formulas

A conjunctive normal form (CNF) is comprised of clauses. A clause,  $\omega$  is defined as a disjunction of literals,

$$\omega = \sum_{i=1}^{|\omega|} l_i \tag{2.1}$$

where each  $l_i$  is a literal and the clause  $\omega$  is comprised of  $|\omega|$  literals. Alternatively, a clause can be represented as a set of literals,  $\omega = \{l_1, l_2, \ldots, l_{|\omega|}\}$ .

A CNF formula  $\phi$  is defined as a conjunction of clauses,

$$\phi = \prod_{i=1}^{|\phi|} \omega_i \tag{2.2}$$

where each  $\omega_i$  is a clause and the CNF formula  $\phi$  is comprised of  $|\phi|$  clauses. Alternatively, a CNF can be represented as a set of clauses,  $\phi = \{\omega_1, \omega_2, \dots, \omega_{|\phi|}\}$ .

**Example 2.1** An example of a CNF formula is  $\phi_1 = (x_1 + x_2 + \overline{x_3}) \cdot (\overline{x_1} + x_3) \cdot (x_1 + \overline{x_2} + x_3)$ . Alternatively, in set notation  $\phi = \{\omega_1, \omega_2, \omega_3\}$ , where  $\omega_1 = \{x_1, x_2, \overline{x_3}\}$ ,  $\omega_2 = \{\overline{x_1}, x_3\}$  and  $\omega_3 = \{x_1, \overline{x_2}, x_3\}$ .

The CNF of Example 2.1 is based on a set of three propositional variables,  $x_1, x_2, x_3$ and is comprised of three clauses,  $\omega_1, \omega_2$  and  $\omega_3$ . Clause  $\omega_3$  is composed of three literals,  $x_1, \overline{x_2}$  and  $x_3$ .

#### 2.3 The Satisfiability Problem

Given a set of variables V, an assignment A is a function that maps a set  $U \subseteq V$ to  $\{0,1\}$ . A is interpreted as a set  $A \subseteq U \times \{0,1\}$  of variable value pairs  $(x, \nu_x)$ . A variable  $y \notin U$ , not assigned a value by A assumes a value X by default. Assignment A is said to be complete if every variable  $x \in V$  is assigned a value by A, *i.e.* |A| = |V|, otherwise Ais said to be partial (|A| < |V|).

Given an assignment V (partial or complete), and a literal  $l_y$  of variable y, the value of  $l_y$  under V, denoted  $l_y \mid_A$  is given by

$$l_{y}|_{A} = \nu_{y} \qquad \text{if } l_{y} = y \text{ and } (y, \nu_{y}) \in A \qquad (2.3)$$

$$= \neg \nu_{y} \qquad \text{if } l_{y} = \overline{y} \text{ and } (y, \nu_{y}) \in A$$

$$= X \qquad \text{otherwise}$$

Given a clause  $\omega$  the value of  $\omega$  under assignment A is denoted by  $\omega |_A$  and computed as:

$$\omega|_A = \sum_{i=1}^{|\omega|} l_i|_A$$

| x | y        | x + y |

|---|----------|-------|

| 0 | 0        | 0     |

| 0 | 1        | 1     |

| 0 | X        | X     |

| 1 | 0        | 1     |

| 1 | $1 \\ X$ | 1     |

| 1 |          | 1     |

| X | 0        | X     |

| X | 1        | 1     |

| X | X        | X     |

Table 2.1: The disjunction operator over  $\{0, 1, X\}$

The definition of the disjunction operator  $(+ \text{ or } \vee)$  over  $\{0, 1, X\}$  is given by Table 2.1. If  $\omega|_A = 1$  then  $\omega$  is said to be *satisfied*. If  $\omega|_A = 0$  then  $\omega$  is said to be *unsatisfied*. Otherwise  $\omega$  is said to be *unresolved*. The unassigned literals of  $\omega$ , if any, are called *free literals*. An unresolved clause with only one free literal is called a *unit clause*. The *empty clause ()* or *contradiction* is a clause with no literals (or all literals unsatisfied and removed) and is a shorthand representation for the unsatisfiable clause (0).

The value of a CNF formula,  $\phi$  (defined as per Equation 2.2) is denoted by  $\phi|_A$ and computed as

$$\phi|_{\boldsymbol{A}} = \prod_{j=1}^{|\phi|} \omega_j|_{\boldsymbol{A}}$$

The definition of the conjunction operator  $(\cdot \text{ or } \wedge)$  over  $\{0, 1, X\}$  is given by Table 2.2. If  $\phi|_A = 1$  then  $\phi$  is said to be *satisfied*. If  $\phi|_A = 0$  then  $\phi$  is said to be *unsatisfied*. Otherwise  $\phi$  is said to be *unresolved*. It is easily verified that a CNF,  $\phi$  is satisfied under assignment A if and only if at least one literal in each clause of  $\phi$  assumes value 1 under A.

**Definition 2.1 (The SAT Problem)** Given a CNF formula  $\phi$ , the Satisfiability problem posed on  $\phi$ ,  $SAT(\phi)$  seeks to determine if there exists an assignment A under which  $\phi$  is satisfied. Such an assignment, if one exists, is called a satisfying assignment for  $\phi$  and the formula  $\phi$  is termed satisfiable. Otherwise  $\phi$  is termed unsatisfiable.

It can be verified that the formula  $\phi_1$  of Example 2.1 is satisfiable and that the assignment  $A = \{(x_1, 1), (x_3, 1)\}$  is a satisfying assignment for  $\phi_1$ .

| _ |   |         |             |  |  |  |

|---|---|---------|-------------|--|--|--|

| x | ; | y       | $x \cdot y$ |  |  |  |

|   |   | 0       | 0           |  |  |  |

|   |   | 1       | 0           |  |  |  |

|   |   | X       | 0           |  |  |  |

| 1 | . | 0       | 0           |  |  |  |

| 1 |   | 1       | 1           |  |  |  |

| 1 |   | X       | X           |  |  |  |

| X | ۲ | 0       | 0           |  |  |  |

| X | ۲ | 1       | X           |  |  |  |

|   | ( | $X_{-}$ | X           |  |  |  |

| _ |   |         |             |  |  |  |

Table 2.2: The conjunction operator over  $\{0, 1, X\}$

## 2.4 The Davis-Putnam-Logemann-Loveland (DPLL) Search Algorithm for SAT

The Davis-Putnam-Logemann-Loveland or DPLL algorithm  $[DLL62]^1$  is a search based algorithm for SAT. It is one of the earliest complete algorithms for the Satisfiability problem and also the backbone of almost all successful SAT solvers. A brief description of the algorithm is presented in the following. It is, in essence, very similar to the original version that appeared in [DLL62] but specifically based on current implementations of the DPLL algorithm.

The DPLL algorithm for SAT is a branch and bound search algorithm. Given a CNF  $\phi$  based on the variable set V the algorithm searches all possible partial assignments to V for a satisfying assignment. The search terminates either on finding a satisfying assignment or after all partial assignments have been exhausted.

The search tree is organized by exploring possible extensions of the current partial assignment,  $A_{curr}$ . An unassigned variable, y is chosen and  $A_{curr}$  is extended by branching on the two disjoint possibilities  $A_{curr} \cup (y, 0)$  and  $A_{curr} \cup (y, 1)$ . The variable y is called a *decision variable* and an assignment made to it, a *decision assignment*. The search is pruned whenever the current partial assignment results in a clause of  $\phi$  being unsatisfied (*i.e.*  $\phi|_{A_{curr}} = 0$ ). Such a situation is termed a *conflict condition* or simply a *conflict* and denoted by  $\mathcal{X}$ . The particular clause unsatisfied under  $\mathcal{X}$ , through which the conflict was detected,

<sup>&</sup>lt;sup>1</sup>H. Putnam is not one of the authors of the article proposing the algorithm but is still credited with this algorithm since the procedure draws heavily from the Davis-Putnam algorithm [DP60] which was a predecessor to this work.

is called the *conflict clause* and denoted by  $\omega(\mathcal{X})$ . A particular conflict  $\mathcal{X}$  is identified by its conflict clause  $\omega(\mathcal{X})$ . A *decision level*  $\lambda(x)$  is associated with each instance of a decision variable x. This is the level of the decision node in the search tree explored by the algorithm. The root of this tree has decision level 1. The search tree explored by the algorithm can be graphically represented as a tree graph, where the decision variables are the nodes and edges from these nodes, labeled with Boolean values, denote decision assignments to the respective variables. In keeping with this graphical representation, the two assignments to a decision variable x are called the *left branch* and *right branch* assignments of x, where the left branch conventionally denotes the assignment explored first by the algorithm.

The above simple branch and bound scheme is augmented with two other pruning rules, called the *unit literal rule* and the *pure literal rule*. The pseudo code for the DPLL algorithm is shown in Algorithm 2.1.

#### 2.4.1 The Unit Literal Rule

According to this rule, if at any point in the search a unit literal clause,  $\{l_x\}$  is derived then the assignment  $(l_x, 1)$  can be immediately made, without having to branch on the variable x. This rule follows from the fact that the opposite assignment  $(l_x, 0)$  will render the above clause, and hence  $\phi$ , unsatisfied. Obviously there is no solution for  $SAT(\phi)$  in that subspace. Hence that subspace can be pruned away. Iterated application of the Unit Literal rule is called *Boolean Constraint Propagation (BCP)* and is a powerful component of all DPLL based SAT algorithms. The pseudo code for BCP appears in Algorithm 2.2.

Variable assignments derived through BCP are referred to as deduced assignments or implied assignments (also implications or deductions in short). With each deduced variable y (and the corresponding deduced assignment l) it is convenient to associate a clause,  $\omega_{\mathcal{I}}(y)$  from which the implication was derived. As with decision variables, deduced variables are also assigned a decision level  $\lambda(y)$  which is recursively defined as:

$$\lambda(y) = \max_{x \in \omega_{\mathcal{I}}(y), x \neq y} \lambda(x)$$

It is easy to show that under a given partial assignment,  $\lambda(x)$  is unambiguously defined for each assigned variable x by the above definitions. Henceforth, the notation  $x = \nu @\lambda$  will be used to denote that variable x is assigned a value  $\nu$  at decision level  $\lambda$ . Occasionally, it is useful to annotate a set of assignments with decision levels for each assignment, using the above notation.

```

Algorithm 2.1 DPLL Algorithm for SAT

procedure DPLL_main(\phi)

A_{curr} \leftarrow \emptyset

x \leftarrow \emptyset

\nu_x \leftarrow "NULL"

return DPLL_recursive(\phi, A_{curr}, x, \nu_x)

procedure DPLL_recursive(\phi, A_{curr}, x, \nu_x)

A_{curr} \leftarrow A_{curr} \cup (x, \nu_x)

// Extend A_{curr} by setting x \leftarrow \nu_x

```

if All clauses satisfied then

return "SAT"

else if Exists an unsatisfied clause  $\omega_{unsat}$  then

return "UNSAT"

else

$status \leftarrow "OPEN"$

end if

```

bcp\_status \leftarrow BCP(A_{curr})

```

if  $bcp\_status \neq$  "OPEN" then

return bcp\_status

end if

```

Apply_PureLiteral_Rule(A_{curr})

```

if All clauses satisfied then

return "SAT"

end if

```

x_{next} \leftarrow \text{Choose\_Next\_Variable}(\phi, A_{curr})

```

```

left\_branch\_status \leftarrow \mathbf{DPLL\_recursive}(\ \phi, \mathbf{A}_{curr}, x_{next}, 0)

```

if *left\_branch\_status* = "SAT" then

return "SAT"

#### else

```

right_branch_status \leftarrow DPLL_recursive(\phi, A_{curr}, x_{next}, 1)

if right_branch_status = "SAT" then

```

return "SAT"

else

```

return "UNSAT" // Both branches of x_{next} unsatisfiable

```

end if

| Algorithm 2.2 $BCP(A_{curr})$                                          |                                 |  |  |  |  |

|------------------------------------------------------------------------|---------------------------------|--|--|--|--|

| $status \leftarrow$ "OPEN"                                             |                                 |  |  |  |  |

| while unit clauses in $\phi$ AND status == OPEN do                     |                                 |  |  |  |  |

| if exists unit clause $\omega_{unit} = l_x$ then                       |                                 |  |  |  |  |

| $\boldsymbol{A_{curr}} \leftarrow \boldsymbol{A_{curr}} \cup (l_x, 1)$ | // Make unit literal assignment |  |  |  |  |

| end if                                                                 |                                 |  |  |  |  |

| if exists an unsatisfied clause $\omega_{unsat}$                       | then                            |  |  |  |  |

| $status \leftarrow$ "UNSAT"                                            |                                 |  |  |  |  |

| else if all clauses satisfied by $oldsymbol{A}_{curr}$                 | then                            |  |  |  |  |

| $status \leftarrow$ "SAT"                                              |                                 |  |  |  |  |

| end if                                                                 |                                 |  |  |  |  |

| end while                                                              |                                 |  |  |  |  |

| return status                                                          |                                 |  |  |  |  |

#### 2.4.2 The Pure Literal Rule

The pure literal rule states that if a variable x appears only as literals of one polarity, say  $l_x$  in the currently unresolved clauses of the CNF  $\phi$  then the assignment  $(l_x, 1)$  can be immediately effected, without needing to branch on the variable x.

This rule is based on the result that if a solution for  $SAT(\phi)$  lies in the subspace of the current partial assignment,  $A_{curr}$  extended with the assignment  $(l_x, 0)$  then there must be a solution for  $SAT(\phi)$  in the subspace  $A_{curr} \cup (l_x, 1)$ . Thus from the point of view of testing satisfiability of  $\phi$  it is sufficient to explore just the latter subspace.

#### 2.5 The Davis-Putnam Resolution Algorithm for SAT

The Davis-Putnam algorithm [DP60] was one of the first complete algorithms for CNF satisfiability. The basic operation used in this algorithm is the consensus [Qui55] operation over clauses. Consider clauses  $\omega_1$  and  $\omega_2$  which contain a literal of variable x, instantiated in opposite polarities in  $\omega_1$  and  $\omega_2$ . Say,  $\omega_1 = (\omega'_1 + x)$  and  $\omega_2 = (\omega'_2 + \overline{x})$ . Then the consensus of  $\omega_1$  and  $\omega_2$  with respect to variable x, denoted  $c(\omega_1, \omega_2, x)$ , is defined as

$$c(\omega_1, \omega_2, x) = \omega'_1 + \omega'_2 \tag{2.4}$$

In theorem proving terminology [Rob65, Lov78] consensus over clauses is commonly referred to as *ground resolution* or simply *resolution*. Resolution and its derivatives form an integral component of theorem proving algorithms.

| Algorithm 2.3 DP_Resolve_Variable( $\phi, x$ )                                                         |                                                                |

|--------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| $\phi_x \leftarrow \{\omega   x \in \omega \lor \overline{x} \in \omega\}$                             | // clauses with literal $x$ or $\overline{x}$                  |

| $arphi_1 \leftarrow \{\omega - \{x\}   \omega \in \phi \land \{x\} \in \omega\}$                       | // x-literal clauses with $x$ dropped                          |

| $arphi_0 \leftarrow \{\omega - \{\overline{x}\}   \omega \in \phi \land \{\overline{x}\} \in \omega\}$ | // $\overline{x}$ -literal clauses with $\overline{x}$ dropped |

| $\phi^r_x \leftarrow \{\omega_0 \cup \omega_1   \omega_0 \in \varphi_0, \omega_1 \in \varphi_1\}$      | // resolve out variable $x$                                    |

| $\phi \leftarrow (\phi - \phi_x) \cup \phi_x^r$                                                        |                                                                |

| return $\phi$                                                                                          |                                                                |

The Davis-Putnam procedure is an iterative algorithm. Variables of the CNF  $\phi$  are resolved out one at a time, as per Algorithm 2.3, until the empty clause is derived or the formula becomes a *tautology*. The former condition happens when two unit-clauses of opposite polarity (*e.g.*  $\{x\}$  and  $\{\overline{x}\}$ ) are resolved and indicates that the original CNF  $\phi$  is unsatisfiable. The latter condition occurs when all clauses are resolved out without encountering an empty clause and indicates that  $\phi$  is satisfiable.

This basic procedure is augmented with a few other rules to simplify the CNF, particularly the *pure literal rule* and the *unit clause rule*. These rules, discussed earlier (Sections 2.4.2 and 2.4.1 respectively) were first proposed in the Davis-Putnam algorithm [DP60] and later adapted for use in the DPLL procedure [DLL62]. Simply put, using the *pure literal rule* and the *unit clause rule*<sup>2</sup> in the DP procedure amounts to applying the variable resolution procedure (Algorithm 2.3) on pure-literal variables and unit-literal variables before other variables.

The biggest and most obvious drawback of the Davis-Putnam algorithm is that it is fairly space intensive. The DPLL backtracking algorithm, whose space complexity is linear in the size of the SAT instance, is the preferred alternative for most practical SAT solvers. Another minor drawback of the Davis-Putnam algorithm is that when it returns with the answer that the CNF is satisfiable, a witness satisfying assignment is not provided<sup>3</sup>. From a practical point of view such an assignment could be important in the target application

<sup>&</sup>lt;sup>2</sup>To be precise, the unit literal rule is a two step procedure of first resolving out the variable appearing in the unit literal and then simplifying the new clauses generated by resolution through *clause subsumption*.

<sup>&</sup>lt;sup>3</sup>The procedure can be augmented to derive such an assignment albeit at the cost of an additional computational overhead.

from which the SAT instance was derived. *e.g.* a test vector in the case of SAT-based ATPG. In DPLL based SAT, satisfying assignments are free by-products of the algorithm itself.

#### 2.6 Advanced Pruning Techniques in Search Algorithms

Much of the success of SAT solvers in EDA applications can be attributed to recent advancements in search pruning techniques. Two prominent contributions in this area are *conflict based learning* and *non-chronological backtracking*. These concepts had been used in constraint satisfaction problem (CSP) solvers [Dec90, SV93] but were adapted to the propositional satisfiability problem and popularized by the **RELSAT** [BS97] and **GRASP** [MSS99] SAT solvers.

Central to both these techniques is the notion of conflict analysis. Given a conflict condition  $\mathcal{X}$  encountered by the SAT algorithm during the search and the current set of assignments  $A_{curr}$ , conflict analysis seeks to determine a subset  $A_{\mathcal{R}}(\mathcal{X}) \subseteq A_{curr}$  which can be held responsible for the conflict  $\mathcal{X}$ . Specifically, the assignments  $A_{\mathcal{R}}(\mathcal{X})$  should be such that if just these assignments are made on the CNF  $\phi$  (accompanied by the ensuing BCP) then the original conflict clause  $\omega(\mathcal{X})$  of conflict  $\mathcal{X}$  would still be unsatisfied without having made the remaining assignments of  $A_{curr}$ . What makes this analysis important is the observation that in practice only a small fraction of the assignments leading up to a conflict actually influence or cause the conflict. The following example taken from [MSS99] illustrates the notion of conflict analysis.

**Example 2.2** [MSS99] Consider the following set of clauses that form part of a CNF  $\phi$ ,

| $\omega_1$ | = | $(\overline{x_1} + x_2)$              | $\omega_6$ | = | $(\overline{x_5} + \overline{x_6})$                 |

|------------|---|---------------------------------------|------------|---|-----------------------------------------------------|

| $\omega_2$ | = | $(\overline{x_1}+x_3+x_9)$            | $\omega_7$ | = | $(x_1+x_7+\overline{x_{12}})$                       |

| $\omega_3$ | = | $(\overline{x_2}+\overline{x_3}+x_4)$ | $\omega_8$ | = | $(x_1 + x_8)$                                       |

| $\omega_4$ | = | $(\overline{x_4}+x_5+x_{10})$         | $\omega_9$ | = | $(\overline{x_7}+\overline{x_8}+\overline{x_{13}})$ |

| $\omega_5$ | = | $(\overline{x_4} + x_6 + x_{11})$     |            |   |                                                     |

Suppose the current assignment is given by

$$A_{curr} = \{x_9 = 0@1, x_{10} = 0@3, x_{11} = 0@3, x_{12} = 1@2, x_{13} = 1@2, \dots\}$$

Now make the decision assignment  $x_1 = 1@6$ . This decision assignment and ensuing BCP implications produce a conflict  $X_1$  on the given clauses. The specific conflict analysis algorithm presented in [MSS99] when applied to this example produces

$$A_{\mathcal{R}}(\mathcal{X}_1) = \{x_1 = 1@6, x_9 = 0@1, x_{10} = 0@3, x_{11} = 0@3\}$$

Thus this conflict does not depend on any decisions or implications made at decision levels 2,4 or 5.

Conflict analysis is performed by analyzing the chronology of decision and deduced assignments leading up to the conflict, to determine an appropriate  $A_{\mathcal{R}}(\mathcal{X})$ . A given conflict  $\mathcal{X}$  can have several possible  $A_{\mathcal{R}}(\mathcal{X})$  which can act as sufficient reasons for that conflict [MSS99]. Depending on the specific nature of the conflict analysis procedure, one or more specific  $A_{\mathcal{R}}(\mathcal{X})$  sets out of the many possibilities may be examined on a given conflict. While it is generally accepted that the particular choice (or choices) of  $A_{\mathcal{R}}(\mathcal{X})$  can have a significant impact on the performance of the SAT algorithm the problem of determining the most suitable  $A_{\mathcal{R}}(\mathcal{X})$  for a given  $\mathcal{X}$  (both in terms of the efficiency of computing  $A_{\mathcal{R}}(\mathcal{X})$ and the potential search space pruning it can eventually provide) remains an open question. Recent work by Zhang *et al.* [ZMMM01] addresses this problem and provides some empirical guidelines. However, much work remains to be done on both the theoretical and practical aspects of this problem.

#### 2.6.1 Conflict Based Learning

Conflict based learning is the notion of recording information, on encountering a conflict condition, with the objective of using the recorded information to avoid future occurrences of the same or related conflicts. The recorded information is an implicate of the CNF  $\phi$  which is unsatisfied under the given conflict condition. A trivial candidate for this purpose would be the conflict clause  $\omega(\mathcal{X})$ . However, this clause does not add any additional value to the CNF since it is already a part of  $\phi$ . Therefore, the added clause,  $\omega_{\mathcal{R}}(\mathcal{X})$  is a clause derived from the set  $A_{\mathcal{R}}(\mathcal{X})$  obtained through conflict analysis. Specifically,

$$\omega_{\mathcal{R}}(\mathcal{X}) = \bigvee_{l \in A_{\mathcal{R}}(\mathcal{X})} \bar{l}$$

(2.5)

Hence conflict based learning is also known as conflict clause recording or simply clause recording. For the conflict  $\mathcal{X}_1$  of Example 2.2 the recorded clause would be  $\omega_{\mathcal{R}}(\mathcal{X}_1) =$

$(\overline{x_1} + x_9 + x_{10} + x_{11})$ . From the definition of conflict analysis, it follows that adding  $\omega_{\mathcal{R}}(\mathcal{X})$  to  $\phi$  ensures that the search will not regenerate the conflicting assignment that led to  $\mathcal{X}$ . Further, adding  $\omega_{\mathcal{R}}(\mathcal{X})$  has the potential of identifying future implications that are not derivable otherwise.

#### 2.6.2 Non-chronological Backtracking

Backtracking, in the context of a search based SAT algorithm like DPLL, is the operation of undoing or erasing one or more decision assignments (as well as the associated implications) from the current set of assignments  $A_{curr}$  with the aim of exploring unexplored partial assignments to the variables. Backtracking is performed when the CNF  $\phi$  has been proved to be unsatisfiable in the sub-space under  $A_{curr}$ , e.g. by means of one or more conflicts.

In the DPLL algorithm (Algorithm 2.1) the backtracking performed is chronological backtracking. This has the following meaning. Say, x and y are two decision variables in  $A_{curr}$  such that  $\lambda(x) < \lambda(y)$ . Further, suppose x and y were currently being explored in their left branch assignment. Then the right branch assignment of y will always be explored before attempting the right branch assignment of x. Operationally, the DPLL algorithm, on encountering a conflict, would undo assignments from  $A_{curr}$  in reverse chronological order of decision level until it reached the *first* left branch assignment. At this point the assignment of this variable would be flipped and the search would resume.

Non-chronological backtracking (NCB) is based on the observation that it may be possible to establish that the sub-space under an unexplored right branch (*i.e.* the variable is currently being explored in its left branch in  $A_{curr}$ ) cannot contain a solution for  $\phi$ . Such a determination may be made by analyzing the current (and previous conflict conditions) and proving that the current conflict condition would continue to exist or repeat in this sub-space. Operationally, one way to do this<sup>4</sup> is to perform conflict analysis on the current conflict condition  $\mathcal{X}$  and determine the lowest variable  $x_{lowest}$  (*i.e.* the one that has the decision level with the highest numerical value) in the set  $A_{\mathcal{R}}(\mathcal{X})$ . By the above argument the search can directly jump to  $\lambda(x_{lowest})$  erasing all assignments between the current decision level (*i.e.* the level of the current conflict) and  $\lambda(x_{lowest})$  and thereby bypassing or "jumping over" any explored right branches in these intermediate levels. In

<sup>&</sup>lt;sup>4</sup>This is the method used by almost all SAT solvers implementing NCB.

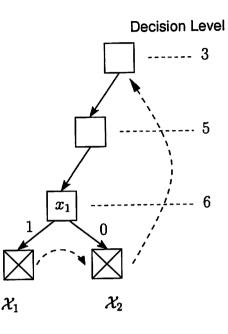

Figure 2.1: An Example of Non-chronological Backtracking [MSS99]

this sense the backtracking is non-chronological.

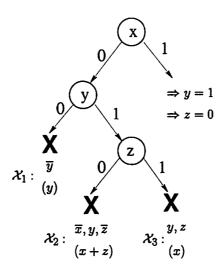

An instance of non-chronological backtracking can be seen on the CNF of Example 2.2. Figure 2.1 illustrates this. Consider conflict  $\mathcal{X}_1$  from the example. Conflict analysis on  $\mathcal{X}_1$  generates  $A_{\mathcal{R}}(\mathcal{X}_1) = \{x_1 = 1, x_9 = 0, x_{10} = 0, x_{11} = 0\}$ . From the above discussion on NCB we can deduce the backtrack level of the current conflict to be 6 *i.e.* the current level. Therefore, we simply flip the value of  $x_1$  from 1 to 0. Note, that up to this point the backtracking is still chronological. However, the new assignment  $x_1 = 0$  will immediately lead to another conflict  $\mathcal{X}_2$  (this can be confirmed from the CNF given in Example 2.2). Analysis of this conflict yields

$$A_{\mathcal{P}}(\mathcal{X}_2) = \{x_9 = 0@1, x_{10} = 0@3, x_{11} = 0@3, x_{12} = 1@2, x_{13} = 1@2\}$$

From this the backtrack level can be deduced to be 3 which is indeed a non-chronological jump (the chronological backtrack level would have been 5).

## 2.7 Transformation of Non-Clausal SAT problems to CNF

For certain classes of Satisfiability problems the native representation is not conjunctive normal form. Since most SAT techniques and solvers are based on CNF representations, efficient procedures to convert instances from non-clausal forms to CNF are an essential component of SAT methodologies. In the following we discuss two such transformations which are especially relevant in the context of EDA applications.

## 2.7.1 CNF Representations of Propositional Formulas

Let V be a set of propositional variables. Well formed propositional formulas based on the set V are defined as follows [DW83, MS95]:

1. Any propositional variable  $x \in V$  is a well formed formula.

- 2. If  $\rho$  is a well-formed formula, then so is  $\overline{\rho}$ .

- 3. If  $\rho$  and  $\sigma$  are well formed formulas then so are  $(\rho \cdot \sigma)$ ,  $(\rho + \sigma)$  and  $(\rho \leftrightarrow \sigma)$ .

From the above definition it is clear that CNF formulas are a special case of well formed propositional formulas. A simple procedure to convert an arbitrary well formed propositional formula to a CNF representation is as follows [DW83, MS95].

- 1. Express equivalence operations in terms of conjunction, disjunction and negation operations through the transformation:  $(\rho \leftrightarrow \sigma) \equiv ((\overline{\rho} \cdot \overline{\sigma}) + (\rho \cdot \sigma)).$

- 2. Apply De Morgan's laws to expand out all negations, other than those associated with single variables.

- 3. Absorb double negations over single variables using the identity:  $\overline{\overline{x}} \equiv x$ .

- 4. Repeatedly apply the distributive law:  $((l_1 \cdot l_2) + (l_3 \cdot l_4)) \equiv (l_1 + l_3) \cdot (l_1 + l_4) \cdot (l_2 + l_3) \cdot (l_2 + l_4)$  till a CNF is obtained.

**Example 2.3** The formula  $\phi = \overline{(x \leftrightarrow y)} + \overline{(y \leftrightarrow z)}$  is a well formed propositional formula. It can be converted to a CNF representation using the above procedure. Applying Step 1 gives  $\phi = \overline{(\overline{xy} + xy)} + \overline{(\overline{yz} + yz)}$  which after Steps 2 & 3 transforms to  $(x+y)(\overline{x}+\overline{y}) + (y+z)(\overline{y}+\overline{z})$ . Finally, applying Step 4 and simplifying using basic axioms of Boolean Algebra<sup>5</sup>, yields the CNF  $\phi = (x + y + z)(\overline{x} + \overline{y} + \overline{z})$ .

**Example 2.4** Consider the propositional formula  $\phi_1 = (\dots (x_1 \leftrightarrow x_2) \dots) \leftrightarrow x_N)$ . It can be shown that applying the above procedure will yield a CNF with  $2^{N-1}$  clauses.

$<sup>\</sup>overline{x} + x = x, x \cdot x = x, 1 \cdot x = x \text{ and } x + \overline{x} = 1$

This example illustrates that the above procedure to convert a well formed propositional formula to CNF can sometimes result in a CNF representation that is exponentially larger than the size of the original propositional formula. In Example 2.4 the size of the original  $\phi$  is linear in N while the CNF is exponential in N. A transformation procedure proposed by G. Tseitin [Tse68] addresses this problem. Tseitin's transformation is defined as follows.

**Definition 2.2 (Tseitin's Transformation [Tse68])** Let  $\phi$  be the given well formed propositional formula.

- 1. Associate a new propositional variable  $x_{\eta}$  with each sub-formula  $\eta$  contained in  $\phi^{6}$ , such that  $x_{\eta}$  and  $\eta$  always assume the same propositional value.

- 2. For each operation in  $\phi$ , i.e. for each sub-formula of  $\phi$  (including  $\phi$  itself) create a set of clauses as follows:

- If  $\eta = \rho \cdot \sigma$  (where  $\eta$ ,  $\rho$  and  $\sigma$  are all sub-formulas of  $\phi$ ) define clauses  $(\overline{x_{\eta}} + x_{\rho}) \cdot (\overline{x_{\eta}} + x_{\sigma}) \cdot (x_{\eta} + \overline{x_{\rho}} + \overline{x_{\sigma}}).$

- If  $\eta = \rho + \sigma$  define clauses  $(x_{\eta} + \overline{x_{\rho}}) \cdot (x_{\eta} + \overline{x_{\sigma}}) \cdot (\overline{x_{\eta}} + x_{\rho} + x_{\sigma})$ .

- If  $\eta = \rho \leftrightarrow \sigma$  define clauses  $(\overline{x_{\eta}} + x_{\rho} + \overline{x_{\sigma}}) \cdot (\overline{x_{\eta}} + \overline{x_{\rho}} + x_{\sigma}) \cdot (x_{\eta} + x_{\rho} + x_{\sigma}) \cdot (x_{\eta} + \overline{x_{\rho}} + \overline{x_{\sigma}})$ .

- If  $\eta = \overline{\rho}$  define clauses  $(\overline{x_{\eta}} + \overline{x_{\rho}}) \cdot (x_{\eta} + x_{\rho})$ .

- 3. Finally add a unit-literal clause ( $\phi$ ) to assert that the formula is required to be true.

- 4. The conjunction of all clauses generated above defines the desired CNF representation of  $\phi$ , whose satisfiability we seek to determine.

Consider the CNF  $\phi_1$  from Example 2.4. Let us apply Tseitin's transformation, described above, to this formula.  $\phi_1$  has N-1 sub-formulas,  $\eta_1, \ldots, \eta_{N-1}$  defined as  $\eta_i = \eta_{i-1} \leftrightarrow x_{i+1}$  for  $i = 2, \ldots, N-1$  and  $\eta_1 = x_1 \leftrightarrow x_2$ . Hence, N-1 new propositional variables  $x_{\eta_1}, \ldots, x_{\eta_{N-1}}$  are created and for each  $\eta_i$  the clauses  $(\overline{x_{\eta}} + x_{\eta_{i-1}} + \overline{x_{i+1}}) \cdot (\overline{x_{\eta}} + \overline{x_{\eta_{i-1}}} + x_{i+1}) \cdot (x_{\eta} + x_{\eta_{i-1}} + \overline{x_{i+1}}) \cdot (\overline{x_{\eta}} + \overline{x_{\eta_{i-1}}} + x_{i+1}) \cdot (x_{\eta} + x_{\eta_{i-1}} + \overline{x_{i+1}})$  are added to the CNF. Thus, the resulting CNF has  $4 \times (N-1)+1$  clauses and is linear in the size of the original propositional formula.

$<sup>^{6}\</sup>phi$  is also a sub-formula of itself.

Tseitin's transformation is the most popular method for transforming general propositional formulas into CNF. However, other polynomial size transformations have also been developed. The interested reader is referred to [MS95] for more details on these methods.

## 2.7.2 Solving SAT problems on Logic Circuits

Many EDA applications using SAT models involve SAT problems posed on logic circuits<sup>7</sup>. Most of the work on SAT formulations of logic circuit EDA problems has focused on combinational logic circuits and such will be the focus of the research presented in this dissertation as well. Therefore, in the following discussion and in the rest of the dissertation the term *logic circuit* will be used to refer to a combinational logic circuit, unless explicitly noted otherwise.

Traditional solutions to EDA problems have sometimes employed algorithms that worked off the native representation of the logic circuit, often performing a branch-andbound search similar to a DPLL-like algorithm, *e.g.* the **PODEM** algorithm for combinational ATPG [Goe81]. However, recent advancements in CNF based SAT solvers have prompted the formulation of such EDA problems in terms of CNF based SAT. In the following we review the essential elements of some popular techniques for transforming SAT problems on logic circuits to CNF.

For the purpose of solving SAT problems posed on combinational logic circuits, it is adequate to work with an abstract representation of a multi-level combinational logic circuit, known as a *Boolean network* [BRSVW87]. In this dissertation a given combinational logic circuit C is indistinguishable from its corresponding Boolean network.

A Boolean network is a directed acyclic graph (DAG), where a node without any incoming edge represents a primary input and a node without any outgoing edge represents a primary output. All other nodes represent intermediate gates<sup>8</sup>. A Boolean function is associated with each intermediate node. There is an edge from node  $n_i$  to a node  $n_j$  if the function associated with  $n_j$  explicitly depends on  $n_i$ . If there is an edge from node  $n_1$  to node  $n_2$ ,  $n_1$  is said to be a fanin node of  $n_2$  and  $n_2$  is said to be a fanout node of  $n_1$ . If there is a directed path from  $n_1$  to  $n_2$  in the Boolean network,  $n_1$  is said to be in the transitive fanin of  $n_2$  and  $n_2$  is said to be in the transitive fanout of  $n_1$ .

<sup>&</sup>lt;sup>7</sup>An exception are SAT formulations of physical design problems in EDA e.g. [WR98].

<sup>&</sup>lt;sup>8</sup>It is assumed that primary inputs and outputs do not compute any non-trivial function.

Further, every node in the Boolean network (including primary inputs, primary outputs and the outputs of internal gates) is associated with a propositional variable. For a node n whose output variable is y, I(y) denotes the famin of the node (*i.e.* the input variables of the gate) and  $f_y(I(y))$  denotes the Boolean function implemented by the gate.

Most SAT problems arising from combinational logic circuits, such as combinational ATPG, combinational equivalence checking *etc.* can be posed as a generic satisfiability problem on a *suitable* circuit. This generic satisfiability problem is known as *CIRCUIT-SAT*. In the following we define this problem on a circuit with a single primary output and present methods to transform such a problem into a CNF based SAT problem. While a discussion describing the transformation of every known logic circuit based SAT problem into CNF is beyond the scope of this discussion, the transformation methods for *CIRCUIT-SAT* apply to most such problems and provide a good starting point for the remaining problems.

**Definition 2.3 (CIRCUIT-SAT)** Given a single output Boolean circuit C, the circuit satisfiability problem on C, denoted as CIRCUIT-SAT(C), seeks to determine a logic value assignment (partial or complete) to the primary inputs of C under which the primary output of C evaluates to 1. Such an assignment, if one exists, is called a satisfying assignment of C, otherwise the instance CIRCUIT-SAT(C) is said to be unsatisfiable.

Given a CIRCUIT-SAT problem on a logic circuit C one naive method to transform this into a CNF SAT problem would be the following. First construct a single propositional formula for the function of the primary output of C by starting with the primary output (say y) and recursively substituting  $f_w(I(w))$  into  $f_y(I(y))$  for each  $w \in I(y)$ . Then this propositional formula can be transformed into CNF using one of the methods outlined in Section 2.7.1. The problem with this approach is that the propositional formula obtained can be exponentially larger than the circuit representation C, thus making the approach impractical.

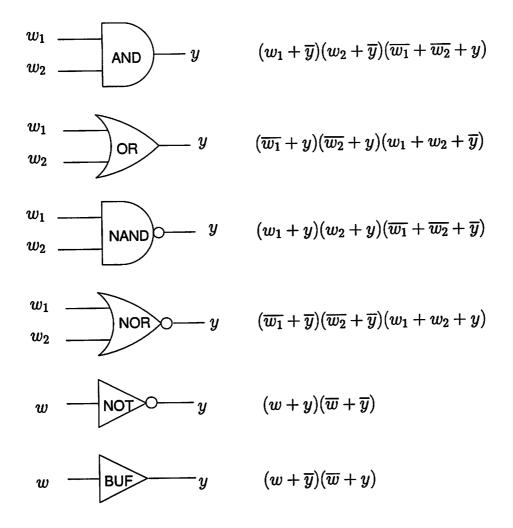

What is used in practice is essentially an adaptation of Tseitin's transformation to combinational circuits. For each gate in C, with output y, we construct a consistency function,  $\xi_y$  [MS95] defined as follows.

$$\xi_{y}(I(y), y) = [\overline{g(I(y)) \oplus y}]$$

(2.6)

| Gate type | Gate Function                | ξ                                                                                                        |

|-----------|------------------------------|----------------------------------------------------------------------------------------------------------|

| AND       | $y = AND(w_1, \ldots, w_k)$  | $\left(\prod_{i=1}^k (w_i + \overline{y})\right) \cdot \left(\sum_{i=1}^k \overline{w_i} + y\right)$     |

| OR        | $y = OR(w_1, \ldots, w_k)$   | $\left(\prod_{i=1}^k (\overline{w_i} + y)\right) \cdot \left(\sum_{i=1}^k w_i + \overline{y}\right)$     |

| NAND      | $y = NAND(w_1, \ldots, w_k)$ | $\left(\prod_{i=1}^k (w_i+y)\right)\cdot \left(\sum_{i=1}^k \overline{w_i}+\overline{y}\right)$          |

| NOR       | $y = NOR(w_1, \ldots, w_k)$  | $\left(\prod_{i=1}^{k} (\overline{w_i} + \overline{y})\right) \cdot \left(\sum_{i=1}^{k} w_i + y\right)$ |

| NOT       | y = NOT(w)                   | $(w+y)\cdot (\overline{w}+\overline{y})$                                                                 |

| BUFFER    | y = BUFFER(w)                | $(w+\overline{y})\cdot(\overline{w}+y)$                                                                  |

Table 2.3: CNF formulas for simple gates

The Boolean function  $\xi_y(I(y), y)$  evaluates to 1 when the values of the inputs of I(y) are consistent with the value of the output y as per the Boolean function  $f_y$  associated with the node. To construct the CNF for CIRCUIT-SAT(C) we construct the CNF representation for the consistency function of each node in C, take the conjunction of all these CNFs and add an additional unit-literal clause asserting the primary output of C to 1. The resulting representation is the CNF SAT formula corresponding to the instance CIRCUIT-SAT(C).