## Copyright © 2002, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# AN INTERNATIONAL STANDARD MODEL FOR SOI CIRCUIT DESIGN

by

Pin Su

Memorandum No. UCB/ERL M02/40

16 December 2002

# AN INTERNATIONAL STANDARD MODEL FOR SOI CIRCUIT DESIGN

by

Pin Su

Memorandum No. UCB/ERL M02/40

16 December 2002

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

### An International Standard Model for SOI Circuit Design

by

Pin Su

B.S. (National Chiao Tung University, Taiwan) 1992 M.S. (National Chiao Tung University, Taiwan) 1994

A dissertation submitted in partial satisfaction of the

requirements for the degree of

**Doctor of Philosophy**

in

**Engineering - Electrical Engineering And Computor Sciences**

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Chenming Hu, Chair Professor Tsu-Jae King Professor Luke P. Lee

Fall 2002

## An International Standard Model for SOI Circuit Design

Copyright 2002

by

Pin Su

#### **Abstract**

#### An International Standard Model for SOI Circuit Design

by

#### Pin Su

## Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

#### University of California, Berkeley

#### Professor Chenming Hu, Chair

Scaling and high performance advantages make SOI an important CMOS technology. However, the main barrier to full exploitation of SOI performance and power is that the design of an SOI chip is a relatively risky process because the relative lacking of design experience makes it difficult to achieve fast turnaround and high probability of first-pass success. To surmount this barrier, a robust and physically accurate SPICE model is needed. SPICE modeling is the standard approach for precise design of standard cell libraries and critical-path sub-circuits in all large systems, as well as the basis for computing the look-up tables used in higher-level timing simulators. IP blocks are in turn designed using the speedier simulations. A compact SOI MOSFET model is crucial to the wide use of SOI technology.

The goal and the accomplishment of this work is to establish a standard SOI model for the semiconductor industry. This dissertation presents the approaches and

essential results of the research. First, we introduce BSIMPD (Berkeley Short-Channel IGFET Model - Partial Depletion), a derivative of the industry-standard bulk BSIM, for PD SOI design. We describe the three SOI-specific modules: floating-body model, self-heating model and body-contact model in BSIMPD. Besides, we propose a parameter extraction methodology for BSIMPD. We also demonstrate the ability of BSIMPD to capture the history effect. In addition, the simulation efficiency of BSIMPD is analyzed. BSIMPD has been selected by the EIA Compact Model Council as the standard model for SOI circuit design. Members of the council include Intel, IBM, TI, Motorola, TSMC, Philips, ST, Hitachi, AMD, and so on.

We have conducted research on the mechanism responsible for low voltage impact ionization in deep-submicrometer MOSFETs. This work is important to not only the prediction of the SOI floating-body effect, but also the understanding of hot carrier physics in both bulk and SOI MOSFETs at low voltage. We propose a *thermal activation energy* concept to explain the occurrence of impact ionization and thus the SOI kink effect at sub-bandgap drain voltage. The new concept suggests that self-heating induced impact ionization is the answer to the longstanding puzzle of anomalous gate bias dependence of the SOI substrate current. It also leads to a new and accurate compact impact ionization model in BSIMPD.

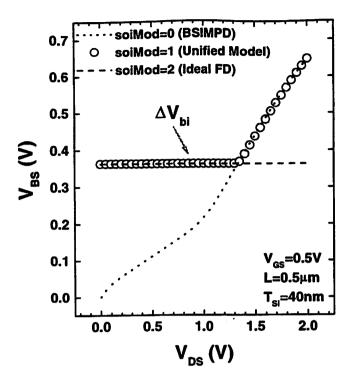

Finally, we present our approach to developing a Full Depletion (FD) SOI MOSFET model using BSIMPD as a foundation. We introduce the concept of body-source built-in potential lowering to unify the PD and FD models. With a single variable,

the same model can now represent both the PD and the FD devices. The unified BSIMSOI model is crucial to the SOI circuit design due to the coexistence of PD/FD devices in a single chip, and the coexistence of PD and FD behaviors in a single device depending on voltage bias.

To My Family

or the control of the

and the state of the first term of the control of t

### **Table of Contents**

| Chapter 1 | Introduction                                                       | 1             |  |

|-----------|--------------------------------------------------------------------|---------------|--|

| Chapter 2 | BSIMPD: A Partial-Depletion SOI MOSFET Deep-Submicron CMOS Designs |               |  |

| 2.1       | Introduction                                                       |               |  |

| 2.2       | Floating-Body Model                                                | 9             |  |

|           | 2.2.1 DC Model                                                     | 11            |  |

|           | 2.2.2 AC/Transient Model                                           | 12            |  |

| 2.2       | Self-Heating Model                                                 | 15            |  |

|           | 2.3.1 Self-Heating Model in BSIMPD                                 | 17            |  |

|           | 2.3.2 Impact of Self-Heating on SOI modeling                       | 19            |  |

| 2.4       | Body-Contact Model                                                 | 21            |  |

|           | 2.4.1 Case Study – Impact of Body Contact on Output I              | Resistance 21 |  |

|           | 2.4.2 Body-Contact Model in BSIMPD                                 | 26            |  |

| 2.5 Si    | imulation Efficiency                                               | 35            |  |

| 2.6 St    | ummary                                                             | 35            |  |

| 2.7 R     | References                                                         | 36            |  |

| Chapter 3 | Impact Ionization in Deep-Submicron MOSFETs                   |

|-----------|---------------------------------------------------------------|

| 3.1       | Introduction                                                  |

| 3.2       | Self-Heating Enhanced Substrate Current                       |

| 3.3       | A Thermal Activation View of Low Voltage Impact Ionization in |

|           | MOSFETs 48                                                    |

| 3.4       | An Impact Ionization Model for SOI Circuit Simulation 56      |

| 3.5       | Summary 61                                                    |

| 3.6       | References 61                                                 |

| Chapter 4 | Impact of Gate-Body Tunneling on SOI CMOS                     |

| 4.1       | Introduction 66                                               |

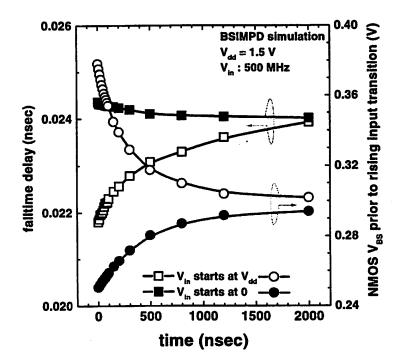

| 4.2       | History Effect Modeling in BSIMPD 67                          |

| 4.3       | Studying the Impact of Gate Tunneling on Dynamic Behaviors of |

|           | Partially-Depleted SOI CMOS using BSIMPD 69                   |

|           | 4.3.1 Tunneling Mechanism70                                   |

|           | 4.3.2 Impact on Transient Responses of MOSFETs71              |

|           | 4.3.3 Impact on Dynamic Behaviors of CMOS Circuits            |

| 4.4       | Tendency toward Full Depletion due to Gate-Body Tunneling 80  |

| 4.5       | Summary 84                                                    |

| 4.6       | References 85                                                 |

| Chapter 5 | BSIMPD Parameter Extraction Methodology                                           |

|-----------|-----------------------------------------------------------------------------------|

| 5.1       | Introduction 87                                                                   |

| 5.2       | Modeling Solution to Self-Heating                                                 |

| 5.3       | Determination of Thermal Resistance                                               |

| 5.4       | Proposed BSIMPD Parameter Extraction Strategy                                     |

| 5.5       | Summary 100                                                                       |

| 5.6       | References                                                                        |

| Chapter 6 | BSIMSOI: A Unified Model for Partial-Depletion and Full-<br>Depletion SOI MOSFETs |

| 6.1       | Introduction                                                                      |

| 6.2       | Body-Source Built-in Potential Lowering Concept 104                               |

| 6.3       | BSIMSOI Framework and Built-in Potential Lowering Model 111                       |

| 6.4       | Verification - Index of Full Depletion                                            |

| 6.5       | Summary                                                                           |

| 6.6       | References 118                                                                    |

| Chapter 7 | Conclusion                                                                        |

#### Acknowledgments

I would first like to express my deepest gratitude to Professor Chenming Hu, who has been my advisor over the past five years. Without his guidance, support and encouragement, this work would not have been possible. His insight and standard of rigor throughout my Ph.D. study have made my time at Berkeley a rewarding and invaluable experience. Besides research, I am very grateful for his advice regarding many other aspects of my life. His attitude and manner as a distinguished professor has profound impact on me.

I would also like to thank Professor Tsu-Jae King for serving as the chair of my qualifying exam committee and member of my dissertation committee. I am also grateful to Professor Luke Lee of the Bioengineering Department, Professor Jan Rabaey, and Professor Phil Spector of the Statistics Department for serving on my dissertation or qualifying exam committee. Their valuable input has benefited this dissertation work significantly.

I am extremely grateful to my industrial mentor, Dr. Samuel Fung. I would like to express my deepest appreciation for both his advice and his keen friendship. Several of the chapters in this dissertation were performed with his help. He has played a crucial role in establishing the industry-standard BSIMSOI.

I would also like to express my gratitude to the IBM Corporation for the long-term support of BSIMSOI. Especially I am thankful to Drs. Fariborz Assaderaghi, Josef Watts, Richard Williams and many of their colleagues who have contributed to the BSIMSOI development. The BSIMSOI project will not be fruitful without their advice and help.

Thanks to the SRC and CMC for their long-term support of BSIMSOI. I would like to acknowledge the help I received from all of the BSIMSOI industrial liaisons. Thanks also to the DARPA and Dr. Peter Wyatt and his colleagues at the MIT Lincoln Laboratory for supporting and helping the development of BSIMSOI.

I am also thankful to Dr. Kenichi Goto of the Fujitsu Corporation and Dr. Hajime Nakayama of the Sony Corporation for their contribution in the BSIMSOI project and their friendship. I consider myself fortunate to have had the opportunity to work with these outstanding visiting industrial fellows from Japan.

I am grateful to Professor Mansun Chan of Hong Kong UST for his lively advice. Thanks also to Professor Ali Niknejad who co-directs the BSIM team. I would like to acknowledge the tremendous help I received from all of the former BSIMSOI developers, especially Drs. Samuel Fung, Dennis Sinitsky and Stephen Tang. Thanks also to former and present BSIM team members for sharing their experience and knowledge during numerous discussions. I would like to sincerely thank Judy Fong for the administration of the BSIMSOI project.

I am especially indebted to Dr. Weidong Liu and Dr. Jeffery Ou for their help and their warm friendship. I would also like to thank all of my colleagues in the UC Berkeley Device Group for their invaluable input during the past five years and most important of all, their friendship. They have made my tenure at Berkeley a wonderful experience.

Finally, I would like to thank my parents for their constant encouragement and support throughout the years. Their confidence in my abilities and their encouragement has really helped me get through all the difficulties I encountered during this work.

## Chapter 1

### Introduction

SOI (Silicon-On-Insulator) CMOS is emerging as a mainstream technology for high performance microprocessor [1]-[3] due to high speed and low power advantages. In addition, almost all major IC manufacturing companies have SOI on their roadmap. The remaining question is which technology generation to insert SOI for those companies. The importance of SOI rises as the scaling of bulk CMOS faces increasing difficulty [4].

SOI also offers better device scalability than its bulk counterpart. For a Partial Depletion (PD) SOI technology, thinning the SOI thickness in every generation allows the rise of channel doping concentration for better short channel control and device performance [5]. A superior subthreshold slope can be obtained for not only thin film Full Depletion (FD) devices, but also floating-body PD devices due to the beneficial gate-to-body capacitive coupling [6]. It is also worth noting that the forward body bias condition, typical of the operation of SOI devices, may reduce the built-in potential and therefore the short channel effect [7].

As the SOI technology gets mature, the main barrier to full exploitation of SOI performance and power is that the design of an SOI chip is a relatively risky process because a relative lacking of design experience makes it difficult to achieve fast turnaround and high probability of first-pass success. To surmount this barrier, a robust and physically accurate SPICE (compact) model is needed. SPICE modeling is the standard approach for precise design of standard cell libraries and critical-path subcircuits in all large systems, as well as the basis for computing the look-up tables used in higher-level timing simulators. IP blocks are in turn designed using the speedier simulations. A compact SOI MOSFET model is crucial to SOI circuit design.

The goal of this work, therefore, is to establish a standard SOI model for semiconductor industry. This dissertation presents the essential research results and the approaches we have taken in developing this model. The organization is as follows.

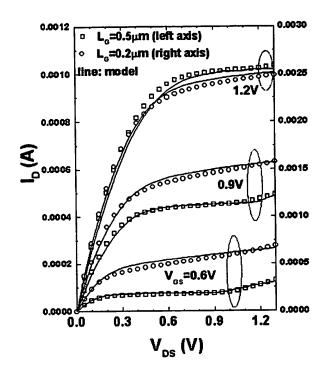

Chapter 2 presents our BSIMPD (Berkeley Short-Channel IGFET Model - Partial Depletion) model, a sophisticated derivative of the industry-standard bulk BSIM [8][9]. BSIMPD [10][11] is already being used in production by major semiconductor companies such as IBM. It has contributed to the successful implementation of the 660-MHz 64-bit PowerPC [12] at its first design [13]. It was selected by the EIA Compact Model Council [14] as the standard SOI MOSFET model in December 2001. This chapter mainly describes the three SOI-specific modules: floating-body model, self-heating model and body-contact model in BSIMPD. Since we emphasize in this chapter

the physical mechanism behind the model, this chapter also serves as a complement of the BSIMPD users' manual [11]. It is worth noting that the simulation efficiency of BSIMPD, a crucial element for quality electronic design and a challenge for SOI modeling, is provided and analyzed.

Chapter 3 presents our research on the impact ionization phenomenon in state-of-the-art MOSFETs. This work is important in not only the prediction of the SOI floating-body effect, but also the fundamental hot carrier physics universal to both bulk and SOI deep-submicron MOSFETs. Our proposed thermal activation energy concept explains the occurrence of impact ionization and thus the SOI kink effect at sub-bandgap drain voltage. Notice that the supply voltage for the 65-nm (n+2) technology node is around 0.85 V. The thermal activation energy concept predicts the self-heating induced impact ionization and solves the longstanding difficulty in modeling the gate bias dependence of the SOI substrate current. The new concept also predicts a drain bias dependence of the low voltage ionization rate that is different from the classical model [15]. A generalization of both the thermally assisted model and the classical model results in the compact impact ionization model in BSIMPD.

Starting from the 0.13-µm technology node with around 20-Å equivalent oxide thickness, the oxide tunneling becomes significant. How might the gate tunneling current impact the dynamic behavior of SOI CMOS? Chapter 4 attempts to assess this question using BSIMPD. We first demonstrate the ability of BSIMPD to capture the history effect, a main concern for SOI circuit design and a challenge for SOI modeling. Then we can

investigate the impact of gate-body tunneling on dynamic behaviors of SOI CMOS with the aid of the proven BSIMPD model. This study is representative of technology generations with supply voltage above 1 V. For scaled SOI CMOS with sub-1V power supply, another case study via device simulation is used to predict the depletion trend of thin film SOI due to gate tunneling.

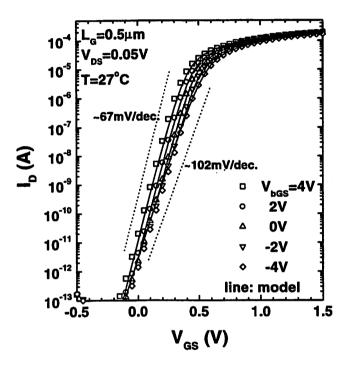

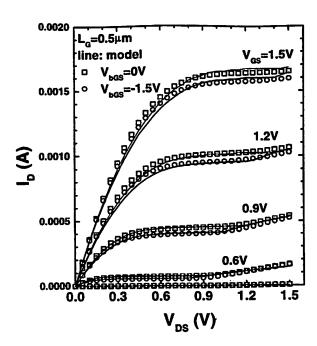

Since it is the model card (parameter set) that represents a specific SOI technology to circuit design, accurate parameter extraction for BSIMPD is crucial to creating designs that work the first time. Chapter 5 presents our strategy to attack the complication caused by the SOI-specific self-heating and floating-body effects in parameter extraction. The proposed methodology has been verified through the comparison between model and experimental data. The systematic parameter extraction approach as well as the satisfactory model accuracy is crucial to this industry standard model.

For the 65-nm (n+2) technology node and beyond, the SOI thickness is projected to be below 30 nm and the SOI device may get into full depletion easily. There is a need for an FD SOI MOSFET model. Chapter 6 presents our approach to developing the FD SOI model using BSIMPD as a foundation. We introduce the concept of *body-source* built-in potential lowering to consolidate both PD and FD models. This concept is important because it serves as a measure of the floating-body behavior of SOI devices. It is also the basis of the BSIMSOI framework. The unified BSIMSOI model is crucial to

the SOI circuit design due to the coexistence of PD/FD devices in a single chip, which has become one of the biggest challenges in the scaling SOI CMOS.

Chapter 7 summarizes essential research results and contributions of this dissertation work.

#### References

- [1] G. G. Shahidi et al., "Partially-depleted SOI technology for digital logic," ISSCC Tech. Digest, p. 426, Feb. 1999.

- [2] D. Bearden, "SOI design experiences with Motorola's high-performance processors," 2002 IEEE International SOI Conference Proceedings, pp. 6-9.

- [3] M. Celik et al., "A 45 nm gate length high performance SOI transistor for 100 nm CMOS technology applications," *Technical Digest of 2002 Symposium on VLSI Tech*, pp. 166-167.

- [4] C. Hu, "SOI and device scaling," 1998 IEEE International SOI Conference Proceedings, p. 1.

- [5] S. K. H. Fung et al., "Gate length scaling accelerated to 30 nm regime using ultra-thin film PD-SOI technology," *IEDM Tech. Digest*, pp. 629-633, 2001.

- [6] S. K. H. Fung et al., "Controlling floating-body effects for 0.13μm and 0.10μm SOI CMOS," Tech. Digest IEDM, pp. 231-234, 2000.

- [7] C. Wann et al., "CMOS with active well bias for low-power and RF/analog applications," Technical Digest of 2000 Symposium on VLSI Tech.

- [8] C. Hu, "BSIM model for circuit design using advanced technologies," *Technical Digest of 2001 Symposium on VLSI Tech*, p. 5.

- [9] http://www-device.eecs.berkeley.edu/~bsim

- [10] P. Su, S. Fung, S. Tang, F. Assaderaghi and C. Hu, "BSIMPD: A partial-depletion SOI MOSFET model for deep-submicron CMOS designs", *Proceedings of the IEEE* 2000 Custom Integrated Circuits Conference, Orlando, FL, May 2000, pp.197-200.

- [11] http://www-device.eecs.berkeley.edu/~bsimsoi

- [12] T. Bucholtz et al., ISSCC Tech. Digest, 2000.

- [13] S. K. H. Fung et al., "A partially-depleted SOI compact model formulation and parameter extraction," *Technical Digest of 2000 Symposium on VLSI Tech*, pp. 206-207.

- [14] http://www.eigroup.org/cmc

- [15] C. Hu, S. Tam, F. Hsu, P. Ko, T. Chan and K. Terill, "Hot-electron-induced MOSFET degradation model, monitor and improvement," *IEEE Trans. Electron Devices*, vol. ED-32, p. 375, 1985.

## Chapter 2

### **BSIMPD:**

## A Partial-Depletion SOI MOSFET Model

## for Deep-Submicron CMOS Designs

#### 2.1 Introduction

Four technological trends set the stage for Partially-Depleted SOI (PDSOI) to become an important IC technology for the 21st century: (1) High performance. PDSOI provides a performance gain of 20 to 35 percent over bulk CMOS [1] due to the reduction of junction capacitance and the absence of the body-bias effect in series connected devices, e.g. in NAND and NOR gates. (2) Low power. With the same performance SOI can operate at a lower voltage and therefore lower power. (3) Mixed and Embedded Technologies. SOI provides a way to isolate analog circuits from substrate noise and provides high-Q inductors. It may be beneficial to embedded DRAM because of good

signal isolation from the logic circuit blocks. (4) Process simplicity. SOI may reduce some future bulk-technology's manufacturing difficulties such as isolation, shallow junction, and latchup sensitivity.

As PDSOI technology becomes more widely used, a robust and physically accurate SPICE model is sorely needed to reduce the risk of inadequate circuit designs.

BSIMPD (Berkeley Short-Channel IGFET Model - Partial Depletion) attempts to serve as this critical communication vehicle between IC design and manufacturing.

BSIMPD [2] was jointly developed by University of California at Berkeley and IBM, and its source code may be downloaded from the web [14]. This model is a derivative of the industry-standard bulk-MOSFET model BSIM3v3 [3]. Three important additions are made to the SOI model: floating-body model, self-heating model and body-contact model.

In this chapter, we describe these SOI-specific modules as well as the BSIMPD simulation efficiency, a critical element to an industry-standard SOI MOSFET model [15]. The parameter extraction methodology for BSIMPD will be proposed in Chapter 5.

#### 2.2 Floating-Body Model

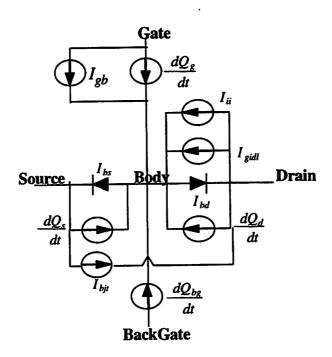

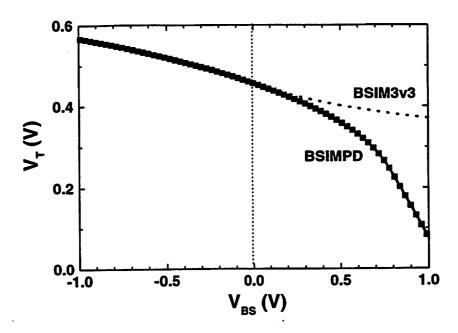

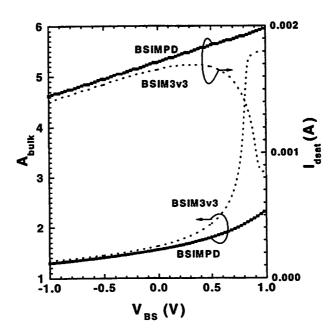

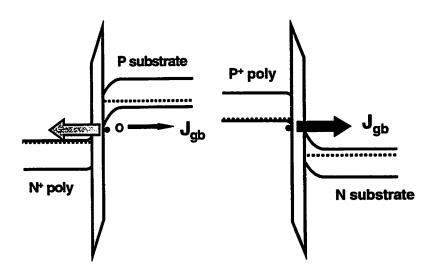

To accurately model the potential of the floating body, which has strong impact on the device behavior, the circuit shown in Figure 2-1 is solved for the body voltage (V<sub>BS</sub>). In DC, this voltage is determined by the various body current components. For AC/transient simulation, the displacement currents originating from capacitive couplings will also contribute. Once the body potential is found, the impact of the floating body on drain current (I<sub>D</sub>) can be captured through an accurate threshold voltage model (Figure 2-2) and bulk charge model (Figure 2-3) in the high forward body-bias regime.

Figure 2-1. Circuit representation of the floating body.  $I_{gb}$ : oxide tunneling current.  $I_{ii}$ : impact ionization current.  $I_{gidl}$ : gate induced drain leakage.  $I_{bjt}$ : bipolar current.  $I_{bs}$ : recombination current.  $I_{bd}$ : junction leakage.

Figure 2-2. An accurate threshold voltage model in the high forward body-bias regime [7] is crucial to a PDSOI model.

Figure 2-3. The model behavior of bulk charge effect  $(A_{bulk})$  in the high forward bodybias regime [7] is critical to the model behavior of drain current  $(I_{dsat})$  and thus simulation convergency.

#### 2.2.1 DC Model

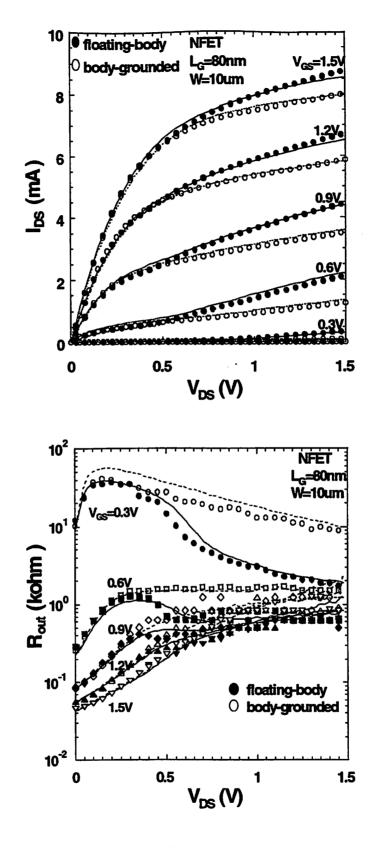

The IV characteristics in Figure 2-4 show kinks in the high drain-bias regime due to the rise in body voltage that is caused by the impact-ionization current ( $I_{II}$ ). The excess  $I_D$  is a major source of performance gain of SOI over bulk and thus needs to be well modeled. Since the steady-state body potential is determined by the counter-balance of  $I_{II}$  and the body-source diode current, accurate  $I_{II}$  (detailed in Chapter 3) and diode current models [7], which takes into account the tunneling effect in the high-field halo (pocket implant) region of the junctions, are developed to achieve the accuracy of the BSIMPD model.

Figure 2-4. BSIMPD (line) accurately models the IV characteristics of a PDSOI transistor showing excess current drive due to floating-body kink effect [18].

#### 2.2.2 AC/Transient Model

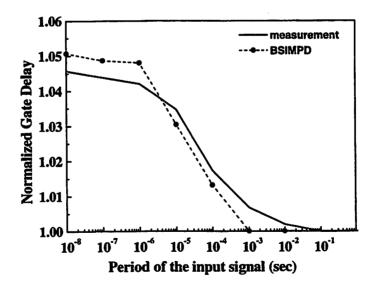

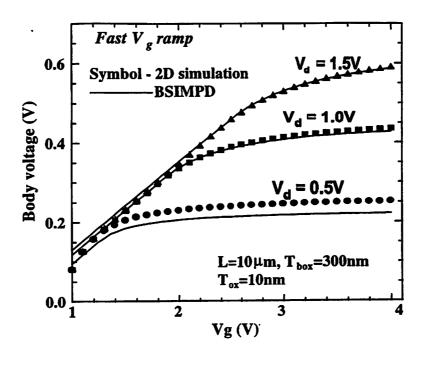

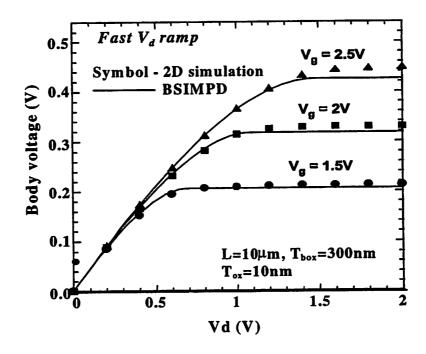

During switching, the body potential is determined by the initial state of the body charge as well as the body-to-gate/drain/source/backgate capacitive coupling. This results in the history dependence of gate delay shown in Figure 2-5. To catch this delay variation, an accurate modeling of the capacitances and the body time constant is required (detailed in Chapter 4). As shown in Figure 2-6, the model-prediction of the body potential for fast gate/drain voltage ramp shows good agreement with 2D device simulation. As the gate oxide thickness is scaled down, the impact of gate-to-body tunneling on the history effect (detailed in Chapter 4) as well as the impact of quantum effects on the gate capacitance becomes significant. A charge-thickness model (CTM) [4], which considers the quantization of inversion charges and poly-gate depletion in the capacitance model, is embedded in BSIMPD to support deep-submicron CMOS designs.

Figure 2-5. Delay per stage of a PDSOI unloaded inverter chain shows history dependence due to dynamic variations of the stored body charges and thus variation of  $V_T$ .

Figure 2-6. The body potential predicted by BSIMPD for fast gate/drain voltage ramp agrees well with 2D device simulation.

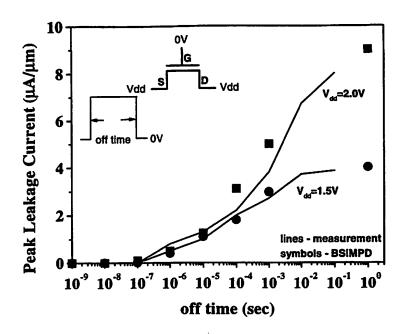

Figure 2-7. Peak leakage current of a pass-gate transistor following a fast pull down of the source voltage demonstrates another floating body effect, which is captured by BSIMPD.

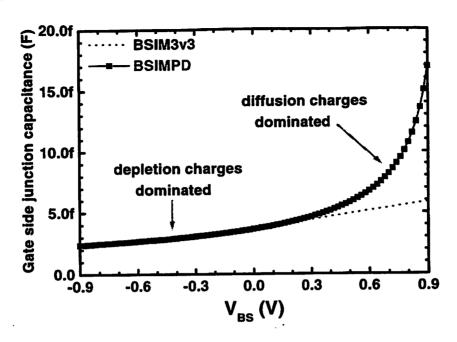

The pass-gate leakage shown in Figure 2-7 is another consequence of the floating-body effect and can cause circuit failures. Since  $V_{BS}$  can be very high during a fast pull-down of the source voltage, a significant lateral bipolar current develops and gives rise to the leakage current. Therefore, an accurate bipolar current model [7] is important to pass-gate circuit simulation. Besides, the junction diffusion capacitance, which dominates the total junction capacitance in the high  $V_{BS}$  regime (Figure 2-8), plays an important role in the determination of  $V_{BS}$  during the fast pull-down of the source voltage. Therefore, a junction diffusion charge model [7] has been developed and implemented in BSIMPD.

Figure 2-8. The junction diffusion charge/capacitance is crucial to a PDSOI model.

### 2.3 Self-Heating Model

Due to the low thermal conductivity of the buried oxide underneath the active device (about two orders of magnitude less than that of silicon), SOI MOSFETs are susceptible to the local thermal heating generated in the channel. This self-heating phenomenon varies the device temperature and thus the current drive. It has significant impact on analog parts of the design such as static I/O and PLL.

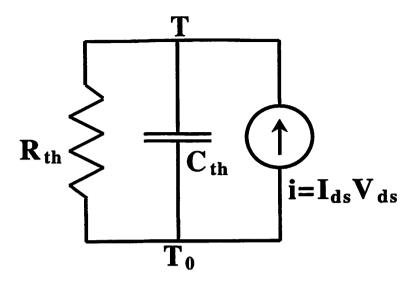

Figure 2-9. BSIMPD uses this self-heating equivalent circuit driven by the transistor power to model the device temperature (node-voltage of T).

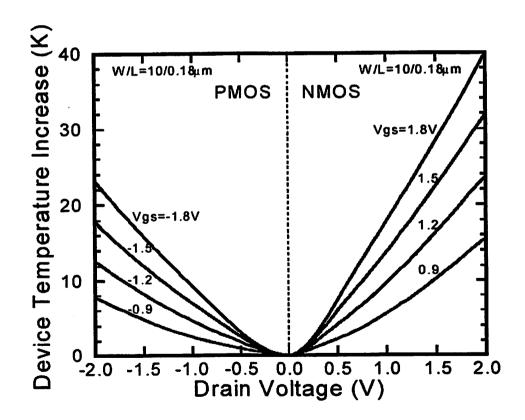

Figure 2-10. The device temperature rise due to self-heating is larger in NMOSFET than in PMOSFET for a given device geometry and bias condition [17].

#### 2.3.1 Self-Heating Model in BSIMPD

To keep track of the device temperature rise ( $\Delta T$ ) with the bias, an auxiliary  $R_{th}C_{th}$  circuit driven by a current source equal to the power dissipation (Figure 2-9) is employed in BSIMPD. Here  $R_{th}$  and  $C_{th}$  represent thermal resistance and thermal capacitance of the device, respectively. Figure 2-10 shows the calculated  $\Delta T$  after the convergence between device temperature and the drain current is achieved. Notice that the impact of self-heating is larger in NMOS than in PMOS due to the difference in current drive capability.

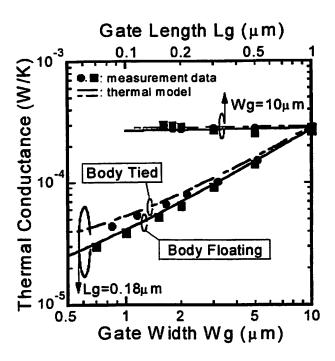

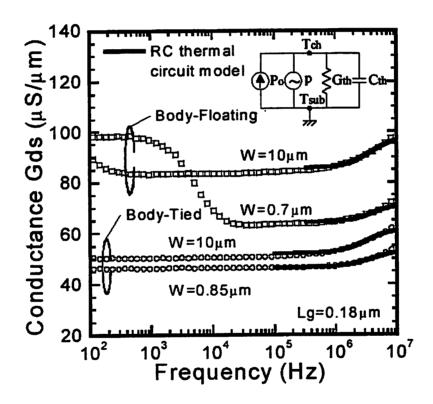

As shown in Figure 2-11, the thermal conductance,  $G_{th}$  (=  $R_{th}^{-1}$ ), is dependent on the gate width,  $W_g$ , of the device. The dependence has been modeled in BSIMPD as

$$G_{th} = W_g \cdot G_{th1} + G_{th0}$$

(2-1).

Here the first term represents the heat dissipation via source/drain films and is proportional to  $W_g$  with a slope  $G_{thl}$ . The second term, a constant, is introduced to account for the heat dissipation via gate electrode and body contact region (additional for body-contacted devices) [17]. Notice that  $G_{th0}$  dominates the total thermal conductance for narrow width devices and explains the difference in  $G_{th}$  between body-contacted and floating-body devices.

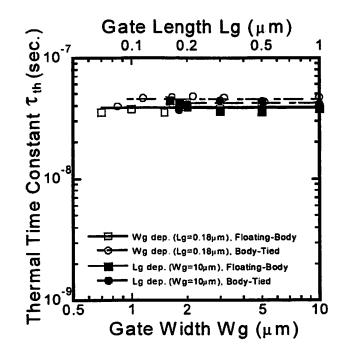

However, the thermal time constant,  $\tau_{th}$  (=  $R_{th}C_{th}$ ), is nearly a constant for a given technology, as shown in Figure 2-12. In other words, the thermal capacitance  $C_{th}$  is

proportional to the thermal conductance  $G_{th}$  with a slope  $\tau_{th}$ .

Figure 2-11. The geometry dependence of thermal conductance for NMOS devices with floating-body and body-contact structures, respectively [17].

Figure 2-12. The geometry dependence of thermal time constant for NMOS devices with floating-body and body-contact structures, respectively [17].

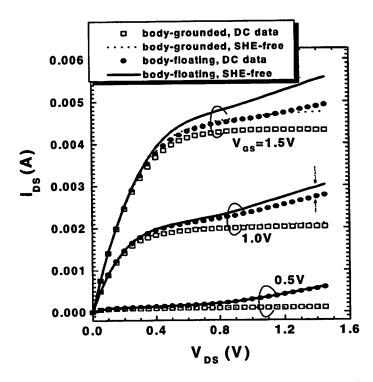

#### 2.3.2 Impact of Self-Heating on SOI Modeling

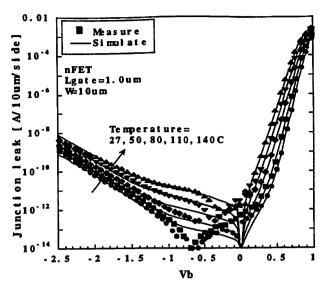

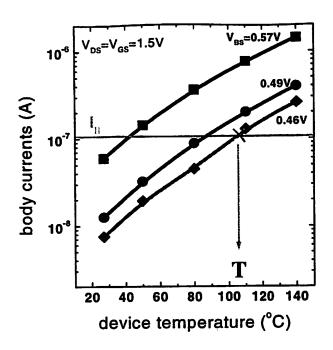

In DC, the device temperature rise due to self-heating reduces the body potential by inducing more diode leakage and thus degrades the current drive beyond the usual bulk-MOSFET temperature sensitivity, as shown in Figure 2-13. In other words, self-heating complicates the prediction of the floating-body effect through temperature-sensitive body-current components, which determine the body potential. The interplay of self-heating and floating-body effects imposes a much higher requirement in modeling the temperature dependence of the body currents for SOI than bulk. Therefore, an accurate temperature-dependence model for the junction leakage (Figure 2-14) has been developed [7] and implemented in BSIMPD to capture the floating-body effect coupled by self-heating.

Figure 2-13. Self-heating effect (SHE) causes more drain current degradation for SOI devices through the floating-body effect. The SHE-free concept/method will be described in Chapter 5.

Figure 2-14. Self-heating interacts with the floating-body effect through the diode current, which is sensitive to device temperature [18].

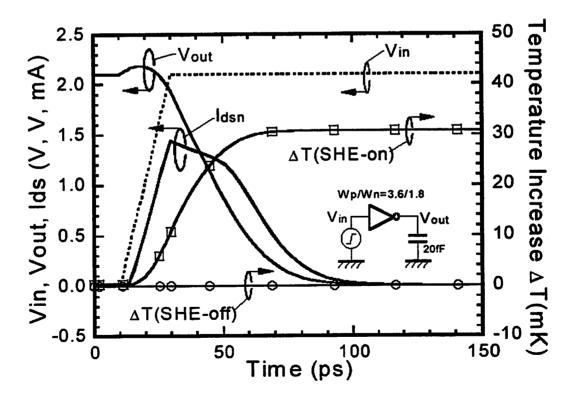

Under dynamic operating conditions typical of digital circuit operation, however, the self-heating effect is generally insignificant. Since the average power consumption per device is low and its switching time (~10 ps) is much shorter than the thermal time constant ( $\tau_{th}$  ~ 100 ns as shown in Figure 2-12) [17] for state-of-the-art high performance SOI CMOS, the time averaged temperature rise due to self-heating is quite small. For example, considering a chip with power consumption of 10 W, 10 million transistors, and  $R_{th}$  of 10<sup>4</sup> °C/W, the average device temperature increase can roughly be estimated as 0.01 °C and negligible. As a result, there is a gap between the self-heating-suffered modeling data measured in DC and the self-heating-free current drive present in most logic circuits.

In other words, self-heating is a modeling rather than performance issue for devices in low power logic circuits. The self-heating modeling solution along with the

BSIMPD parameter extraction methodology will be described in Chapter 5.

#### 2.4 Body-Contact Model

Since the body-contact (BC) is widely used in critical circuits (e.g., PLL and other analog circuits), an accurate model that can represent the non-idealities of the contact is essential to precision-oriented simulations. Here we first present the impact of body-contact on the output conductance of SOI MOSFETs to demonstrate the need of a body-contact model. The complete body-contact model [5] implemented in BSIMPD is then described subsequently.

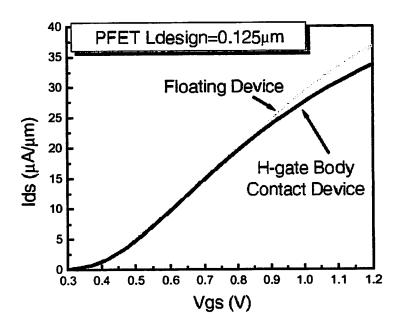

### 2.4.1 Case Study - Impact of Body Contact on Output Resistance

Floating Body Effect (FBE) in PDSOI MOSFETs has become a major concern, and body-contact is the most straightforward way to avoid FBE. However, the body resistance increases and has a distributed nature as the channel width is increased, the efficiency of the body tie is limited [8][9]. Here we report a degradation of AC output resistance ( $R_{out}$ ) in PD devices due to the capacitive coupling between body-contact and drain. The effect should be taken into account in device design and circuit simulation.

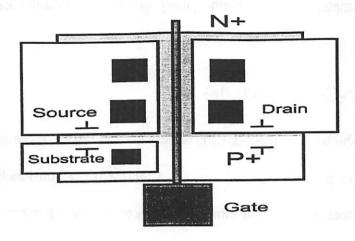

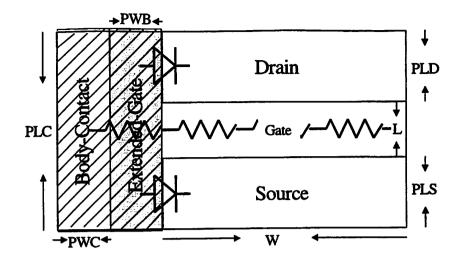

All the four-terminal SOI devices used in this study adopt the side-contact scheme as shown in Figure 2-15. These PD nMOSFETs are fabricated on SIMOX wafer with 85 nm buried oxide and 160 nm film thickness.  $R_{out}$  is measured by the HP4194A gain phase analyzer with the HP4145B supplying the DC bias.

Figure 2-15. Layout of the four-terminal side-body contact scheme used in this measurement. Note the capacitor between drain and body-contact, which causes  $R_{out}$  degradation.

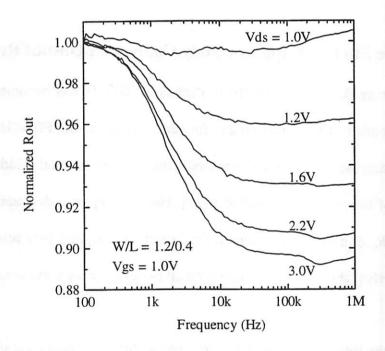

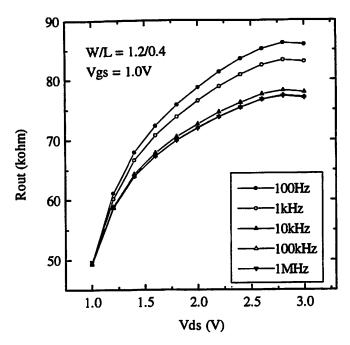

Figure 2-16.  $R_{out}$  versus frequency for various drain biases.

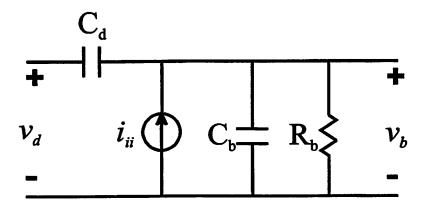

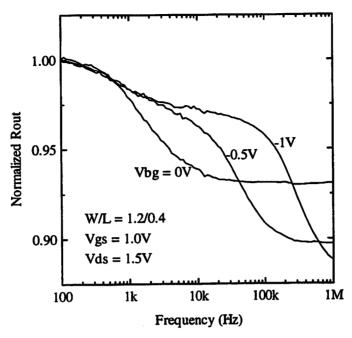

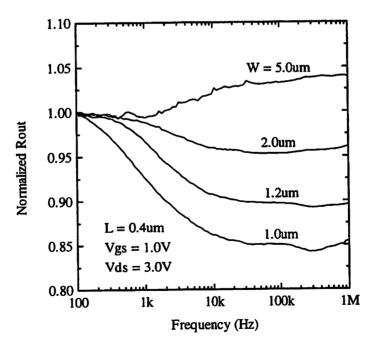

The  $R_{out}$  versus frequency characteristics with different drain bias  $V_{ds}$  are shown in Figure 2-16.  $R_{out}$  is normalized to its DC value. The  $R_{out}$  at saturation decreases with increasing frequency to a certain value, which depends on  $V_{ds}$ . Figure 2-17 shows  $R_{out}$ versus  $V_{ds}$  for various frequencies. It is noted that  $R_{out}$  stops dropping at a frequency around 10 kHz. The effect can be explained by the body potential fluctuation under the influence of drain coupling caused by body-contact. When a small signal  $v_d$  is applied, the floating body potential  $v_b$  can be estimated with the small-signal equivalent circuit shown in Figure 2-18 [10]. The capacitance C<sub>d</sub> is composed of the intrinsic junction capacitance and the parasitic capacitance between the body-contact and the drain. The latter dominates when the device dimension becomes small. It causes an increase in the output conductance (i.e., a decrease in  $R_{out}$ ) through the body effect. This drain coupling effect is insignificant at very low frequencies when the body resistor R<sub>b</sub> provides an effective discharging path for the capacitive current from the drain. So, the value of R<sub>b</sub> will affect the frequency  $f_c$  at which the  $R_{out}$  degradation appears. This can be verified by changing the substrate bias  $V_{bg}$  so that the thickness of neutral-body region and therefore  $R_b$  is modulated. Figure 2-19 shows that  $f_c$  increases as  $R_b$  decreases, as expected.  $C_b$ represents the equivalent capacitance from body to AC ground. It consists of the front gate, body-source diode and buried oxide capacitances. At high enough frequency (e.g., 10 kHz)  $v_b$  is determined by the voltage divider that is made of  $C_b$  and  $C_d$ , so  $R_{out}$ becomes a constant at high frequency. This constant value still depends on  $V_{\text{bg}}$  because  $C_b$  and  $C_d$  depends on  $V_{bg}$ .

Figure 2-17.  $R_{out}$  versus drain bias for various frequencies.

Figure 2-18. Small signal equivalent circuit for the floating body.  $C_d$  is dominated by the capacitance between drain and body-contact.  $C_b$  represents the equivalent capacitance from body to AC ground.  $R_b$  is the body resistance.  $i_{ii}$  is the impact ionization current.

Figure 2-19.  $R_{out}$  versus frequency for various substrate biases showing the effect of  $R_b$ .  $R_b$  decreases as  $V_{bg}$  becomes negative.

Figure 2-20.  $R_{out}$  versus frequency showing the width dependence of this drain coupling effect.

Figure 2-20 shows the width dependence of this effect. Instead of decreasing,  $R_{out}$  increases with frequency when W = 5 um. Since the drain coupling effect becomes negligible compared to the front gate coupling when the channel width is increased,  $v_b$  is mainly influenced by impact ionization current  $i_{ii}$  as has been reported previously [11]. The effect of  $i_{ii}$  decreases with frequency since fewer holes are generated during a half period as frequency increases. Hence  $R_{out}$  increases with frequency.

In conclusion, the drain coupling effect due to the body-contact structure will cause  $R_{out}$  degradation as channel width is narrowed down. This effect should be taken into account in device design and modeling. An accurate SOI circuit model accounting this width effect will be helpful to sensitive analog circuit design if a body-contact technology is used.

## 2.4.2 Body-Contact Model in BSIMPD

Making contact to the body of a PDSOI transistor offers another degree of design freedom. For example, DTMOS [12] has demonstrated that the body-contact can be used to enhance the power/delay performance. It has also been shown that the body-contact plays an important role in eliminating the floating-body instability [13] for sensitive circuits. As demonstrated in the previous section, however, the body-contact effect may be significant. Therefore, a complete SPICE model that explicitly addresses the non-idealities of the body-contact is surely needed for SOI circuit design. Here we present a compact body-contact SOI MOSFET model that has been implemented in BSIMPD [2][14] for circuit simulation.

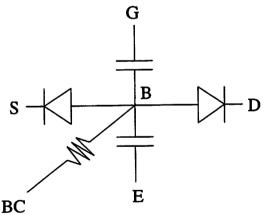

Figure 2-21. Layout representation illustrating the body-contact model of BSIMPD. Distributed body resistance as well as geometry-dependent parasitic source/drain diodes, gate-to-body (gray area) and body-to-backgate (hashed area) overlap capacitances are considered.

Figure 2-22. The equivalent circuit used in BSIMPD to model the non-ideal body contact. G: gate, E: substrate, S: source, D: drain, B: body, BC: body-contact. The diodes between B and S/D are the gated diodes at the sides of source/drain (in Figure 2-21 where "Extended-Gate" and "Source" / "Drain" intersect). The capacitance between G and B is the gate-to-body overlap capacitance in the "Extended-Gate" region. The capacitance between E and B is the substrate-to-body overlap capacitance in both the "Body-Contact" and the "Extended-Gate" region.

#### Model:

The model can be described using a transistor with the T-gate layout shown in Figure 2-21. The body-contact provides the transistor a resistive path for charging/discharging of the body. However the associated body-contact diffusion and the "Extended-Gate" region interact with other electrical terminals as well and may be represented by the equivalent circuit shown in Figure 2-22. The lumped resistance between B node and BC node consists of the intrinsic body resistance  $R_b$  and the extrinsic body resistance  $R_{bext}$ .  $R_b$  is modeled by  $R_{body}$  W/L, where  $R_{body}$  is the body sheet resistance along the channel width.  $R_{bext}$  is modeled by  $R_{bsh}$   $N_{rb}$ , where  $R_{bsh}$  and  $N_{rb}$  are the body sheet resistance and the number of squares in the "Extended-Gate" region, respectively.

The parasitic diodes between B and S/D are characterized by the parameters  $P_{sbcp}/P_{dbcp}$ , the perimeter length of body-contact at the sides of source/drain. Similarly, the parasitic capacitances between B and G/E are characterized by the parameters  $A_{gbcp}/A_{ebcp}$ , which stand for the gate/substrate-to-body overlap. Since these parameters are layout-dependent, they are specified in a per-instance manner. According to the layout geometry of Figure 2-21, we have  $P_{sbcp}=PLS$ ,  $P_{dbcp}=PLD$ ,  $A_{gbcp}=PWB\cdot PLC$  and  $A_{ebcp}=(PWB+PWC)\cdot PLC$ .

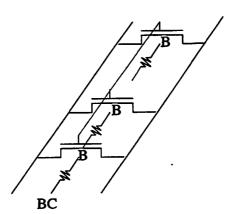

Due to the distributed nature of  $R_b$ , a lumped resistor is no longer satisfactory for sensitive circuits. Therefore, an accessible B node is provided in BSIMPD so that users can perform distributed simulation by partitioning a wide transistor and cascading the

body resistors of the sub-transistors (Figure 2-23). For each sub-transistor, the partition number,  $N_{seg}$ , should be specified so that the transistor current and charge can be scaled by  $N_{seg}$  without over-estimating the narrow-width effect. Note that the width can be non-uniformly partitioned as long as the sum rule  $\Sigma N_{seg}^{-1} = 1$  is fulfilled.

Figure 2-23. An accessible B node is provided in BSIMPD to facilitate the distributed simulation.

#### **Impact on Device Parametrics:**

The importance of body-contact model can be demonstrated from another perspective: Since most of the model parameters of floating-body transistors have to be extracted from body-contacted devices, the non-ideal body-contact effect needs to be taken into account in parameter extraction. Its impact on the key device parametrics in the high body-bias regime, which is essential to PDSOI operations, is investigated using a typical body-contact device with  $W = 5 \ \mu m$ ,  $L_{eff} \cong 0.1 \ \mu m$ .

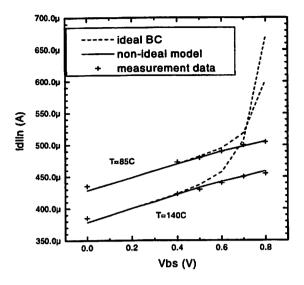

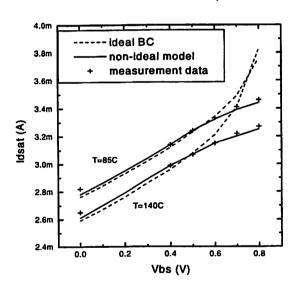

Figure 2-24.  $I_{dlin}$  ( $I_{ds}$  @  $V_{gs} = V_{dd}$ ,  $V_{ds} = 0.05$  V) and  $I_{dsat}$  ( $I_{ds}$  @  $V_{gs} = V_{dd}$ ,  $V_{ds} = V_{dd}$ ) versus  $V_{bs}$  showing the importance of body-contact model in the high body-bias regime.

Figure 2-24 shows that the drain current at high  $V_{bs}$  is much lower than what the ideal body-contact simulation predicts (steep increase). It is mainly due to the IR drop of body potential caused by the forward-biased diode current flowing through the distributed body resistance. Since the diode current increases with temperature, the discrepancy becomes larger at  $140^{\circ}$ C. It can be seen that the simulation result agrees very well with the measurement data after considering the non-ideal body-contact effect.

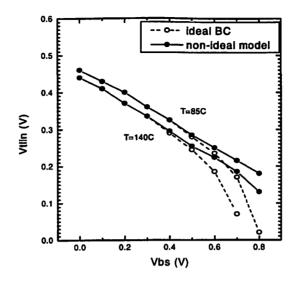

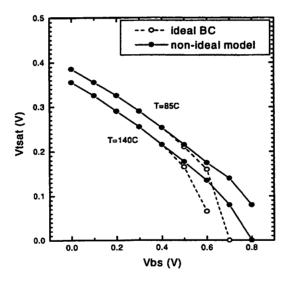

Figure 2-25 shows the correction of the threshold voltage in the high body-bias regime made by the non-ideal body-contact model. As expected, the threshold voltage drops much more slowly and smoothly in the non-ideal case. This implies that the ideal body-contact assumption in parameter extraction may lead to a wrong body-effect ( $V_T$  as a function of  $V_{bs}$ ) prediction, which is crucial to the noise margin of the pass-gate and dynamic logic design.

Figure 2-25.  $V_{tlin}$  ( $V_T @ V_{gs} = V_{dd}$ ,  $V_{ds} = 0.05 \text{ V}$ ) and  $V_{tsat}$  ( $V_T @ V_{gs} = V_{dd}$ ,  $V_{ds} = V_{dd}$ ) versus  $V_{bs}$  showing the significant threshold-voltage roll-off in the high body-bias regime without considering the non-ideal body-contact effect.

#### **Impact on Performance Prediction:**

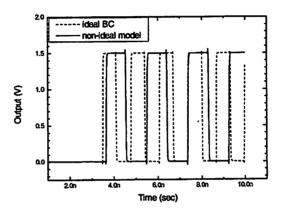

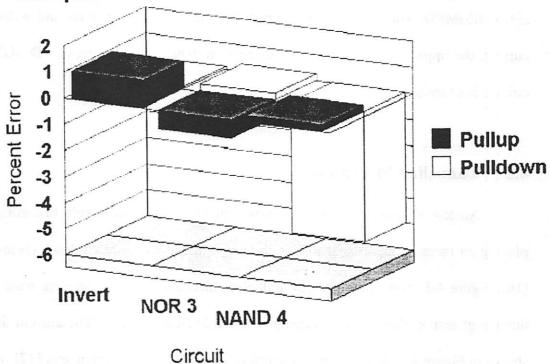

Figure 2-26 shows the impact of the non-ideal body-contact effect on the transistor switching speed. Due to the parasitic capacitances caused by  $A_{gbcp}/A_{ebcp}$ , and the extra junction charges induced by  $P_{sbcp}/P_{dbcp}$ , the speed performance of an inverter gate is approximately degraded by 30% in this case.

Figure 2-26. The output waveforms of an unloaded 51-stage ring oscillator showing the optimistic performance-prediction made by the ideal body-contact assumption. The error of switching speed is around 30% in this case.

In conclusion, since the body-contact is widely used in not only critical circuit design but also test structures for parameter extraction, a compact SOI body-contact model which can accurately capture the body potential is crucial to the accuracy of circuit simulation. A body-contact model, including layout-dependent parasitic diodes and capacitances, as well as an accessible body node for high-precision segmented-transistor simulation, has been developed and implemented in BSIMPD. The impact of the non-ideal body-contact effect on the device parametrics and performance are also investigated based on this model.

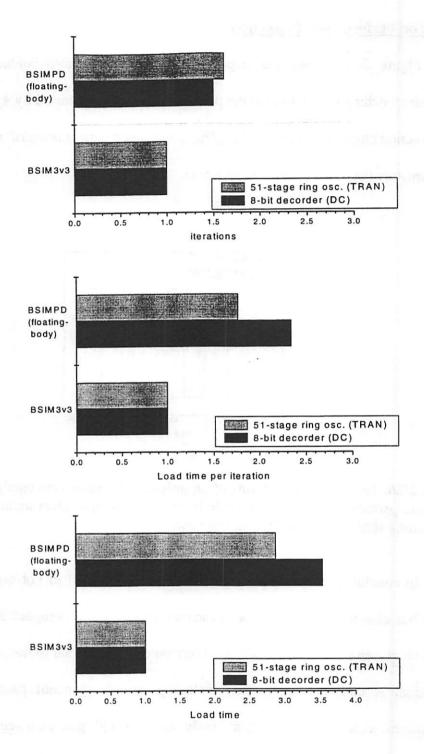

Figure 2-27. Comparison of simulation efficiency between BSIMPD and BSIM3v3 performed by Berkeley SPICE3f4.

## 2.5 Simulation Efficiency

Efficiency in circuit simulation impacts the productivity of circuit designers, and therefore is one important performance metric to a device model. To investigate the simulation efficiency of BSIMPD, two benchmark circuits: a 8-bit decorder and a 51-stage ring oscillator are employed to assess the model performance in DC and transient operation, respectively. As shown in Figure 2-27, the run-time statistics obtained from Berkeley SPICE3f4 are normalized based on the results of BSIM3v3 bulk model. The ~1.5X total iteration number (convergency) of BSIMPD originates from the stiff nature of the long floating-body time constant. While the ~2X load time per iteration (complexity) of BSIMPD is mainly due to the complex equations (e.g., exponential function) utilized in modeling the various body current components. The overall load time (efficiency) of the floating-body simulation is around 3X compared with the bulk BSIM3v3 model.

## 2.6 Summary

A physics-based partially-depleted SOI MOSFET model has been developed to support deep-submicron CMOS designs for SOI technologies of the 21st century. Based on the industry-standard BSIM3v3 bulk model, BSIMPD models the PDSOI-specific floating-body, self-heating and body-contact effects. This model is able to capture the various dynamic behaviors in the PDSOI circuitry by the floating-body simulation.

BSIMPD has been tested extensively within IBM on state-of-the-art high speed SOI technologies [6][16][19]. The accuracy of BSIMPD has also been verified by other semiconductor companies [17][18]. The average error of drain current at all bias conditions is comparable to what is normally achieved for bulk technologies [16]. This model has been implemented in Berkeley SPICE3f4 as well as many commercial circuit simulators such as HSPICE, SPECTRE, SmartSPICE and ELDO. Finally, BSIMPD was selected by the EIA Compact Model Council (CMC) [15] as the standard SOI MOSFET model in December 2001 after a year-long evaluation process.

### 2.7 References

- [1] G. G. Shahidi et al., "Partially-depleted SOI technology for digital logic," ISSCC Tech. Digest, p. 426, Feb. 1999.

- [2] P. Su, S. Fung, S. Tang, F. Assaderaghi and C. Hu, "BSIMPD: A partial-depletion SOI MOSFET model for deep-submicron CMOS designs", *Proceedings of the IEEE* 2000 Custom Integrated Circuits Conference, Orlando, FL, May 2000, pp.197-200.

- [3] Y. Cheng et al., "A physical and scalable I-V model in BSIM3v3 for analog/digital circuit simulation," *IEEE Tran. on Elec. Dev.*, vol. 44, no. 2, p. 277, Feb. 1997.

- [4] W. Liu et al., "An efficient and accurate compact model for thin-oxide-MOSFET intrinsic capacitance considering the finite charge layer thickness," *IEEE Trans. on Elec. Dev.*, vol. 46, no. 5, p. 1070, May 1999.

- [5] P. Su, S. Fung, F. Assaderaghi and C. Hu, "A body-contact SOI MOSFET model for circuit simulation," 1999 IEEE International SOI Conference Proceedings, Rohnert Park, CA, Oct. 1999, pp. 50-51.

- [6] E. Leobandung et al., "Scalability of SOI technology into 0.13 μm 1.2 V CMOS generation," *Tech. Digest IEDM*, p. 403, Dec. 1998.

- [7] BSIMSOI Users' Manual. (http://www-device.eecs.Berkeley.edu/~bsimsoi)

- [8] J. Gautier et al., Tech. Digest IEDM, p. 407, 1997.

- [9] W. Redman-White et al., 1996 IEEE International SOI Conference Proceedings, p. 6.

- [10] D. Sinitsky et al., "AC output conductance of SOI MOSFETs and impact on analog applications," *IEEE Electron Device Letters*, vol. 18, no.2, p. 36, Feb. 1997.

- [11] S. K. H. Fung et al., "Frequency dispersion in partially depleted SOI MOSFET output resistance," 1996 IEEE International SOI Conference Proceedings, p. 146.

- [12] F. Assaderaghi et al., Tech. Digest IEDM, p. 809, 1994.

- [13] C. T. Chuang, 1998 IEEE International SOI Conference Proceedings, p. 5.

- [14] http://www-device.eecs.berkeley.edu/~bsimsoi

- [15] http://www.eigroup.org/cmc

- [16] S. K. H. Fung et al., "A partially-depleted SOI compact model formulation and parameter extraction," *Technical Digest of 2000 Symposium on VLSI Tech*, pp. 206-207.

- [17] H. Nakayama, P. Su, C. Hu, M. Nakamura, H. Komatsu, K. Takeshita and Y. Komatsu, "Methodology of self-heating free parameter extraction and circuit simulation for SOI CMOS," *Proceedings of the IEEE 2001 Custom Integrated Circuits Conference*, San Diego, CA, May 2001, pp. 381-384.

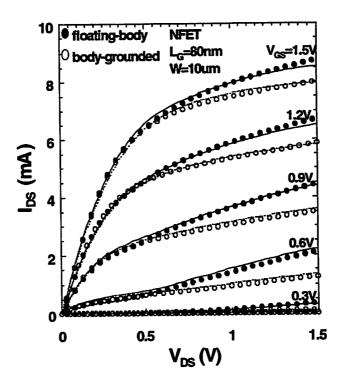

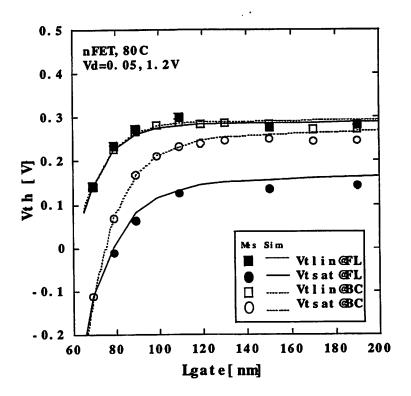

- [18] K. Goto, P. Su, Y. Tagawa, T. Sugii and C. Hu, "80nm SOI CMOS parameter extraction for BSIMPD," 2001 IEEE International SOI Conference Proceedings, Durango, CO, Oct. 2001, pp.55-56.

[19] J. Watts, "How to build an SOI compact model without violating the laws of physics," Technical Proceedings of the Fifth International Conference on Modeling and Simulation of Microsystems NanoTech 2002 - MSM 2002, pp. 726-729.

# Chapter 3

# **Impact Ionization in**

## **Deep-Submicron MOSFETs**

## 3.1 Introduction

Impact ionization current (I<sub>II</sub>) plays an important role in the determination of the floating-body behavior of partially-depleted SOI MOSFETs. In addition, it has been suggested that the impact ionization current remains crucial even for double-gate SOI MOSFETs by enhancing the subthreshold leakage [1]. Therefore, a physical understanding and modeling of the impact ionization phenomenon in state-of-the-art SOI devices is critical to a standard SOI MOSFET model.

$I_{II}$  has long been closely related to the maximum channel electric field,  $E_m$ , near the drain [2]. According to the classical model, the probability that a carrier will gain sufficient energy to cause impact ionization without suffering any scattering in the channel is  $\exp(-\Phi_i/q\lambda E_m)$ , where  $\Phi_i$  is the energy required for impact ionization, and  $\lambda$  is

the mean free path. With the scaling of channel length and supply voltage, nevertheless, I<sub>II</sub> may be determined by other non-scalable factors. Therefore, the classical carrier-phonon scattering mean-free path concept has difficulty in modeling the temperature, gate bias and drain bias dependence of the impact ionization rate.

In this chapter, we first demonstrate an observation of enhanced substrate currents in SOI MOSFETs [3]. The implications are presented subsequently. We then unveil the underlying mechanism using the *thermal activation energy* concept [4]. Finally, we present a compact impact ionization model for SOI circuit simulation based on the proposed thermal activation energy theory.

## 3.2 Self-Heating Enhanced Substrate Current

As SOI CMOS offers an alternative to bulk technology for device scaling, the hot-carrier effect that increases with device miniaturization is another important scaling issue that has to be considered for SOI MOSFETs. The hot-carrier effect is usually monitored by the substrate current (I<sub>SUB</sub>) [2]. I<sub>SUB</sub> results from impact ionization caused by energetic carrier in the channel. The impact ionization current may charge up the transistor body and vary the threshold voltage if the body charge is not readily dissipated. Therefore, measured I<sub>SUB</sub> data from body-contacted devices also plays a crucial role in modeling the current drive of floating-body SOI MOSFETs [5][6].

I<sub>SUB</sub> has long been closely related to the high channel electric field near the drain [2]. Accordingly, electric field has always been a main gauge of hot-carrier effects when

one-to-one comparisons between SOI and bulk devices are made [7]. With the scaling of channel length and supply voltage, however, a new source other than electric field for carrier heating may be present and may determine impact ionization. In this work, we demonstrate an enhanced I<sub>SUB</sub> phenomenon in SOI MOSFETs. We describe the underlying physical mechanism and explain why this phenomenon affects the hot-carrier lifetime prediction as well as SOI modeling.

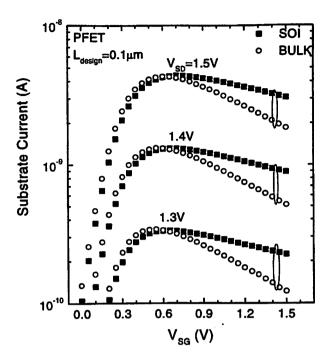

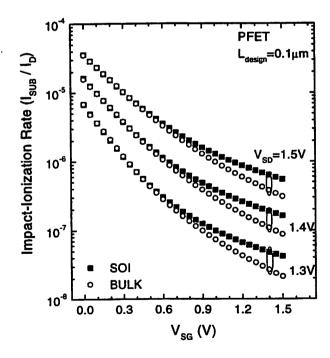

Co-processed bulk and body-contacted partial-depletion SOI MOSFETs using a 0.13 µm technology [8] are investigated in this study. For SOI, the thicknesses of the gate oxide, silicon film and buried oxide are 2.8 nm, 100 nm and 360 nm, respectively. Note that although all date shown in this paper are for PFETs, NMOS behave similarly, but with all voltages at opposite polarity.

Figure 3-1(a) shows that the substrate current in the SOI MOSFET is larger than the bulk counterpart at high gate bias. The impact-ionization rate defined as the ratio of the substrate current to the drain current,  $I_{SUB}/I_D$ , may be used to understand the underlying mechanism. As shown in Figure 3-1(b), the identical  $I_{SUB}/I_D$  at low gate bias demonstrates that the co-processed bulk and SOI samples are nearly identical. As gate bias increases, however, the impact-ionization rate of the SOI MOSFET becomes larger than the bulk one.

Figure 3-1(a). Larger substrate current is observed for the SOI transistor at high gate bias.

Figure 3-1(b). The impact-ionization rate of the SOI MOSFET is larger than the bulk counterpart at high gate bias, even though the two transistors are nearly identical.

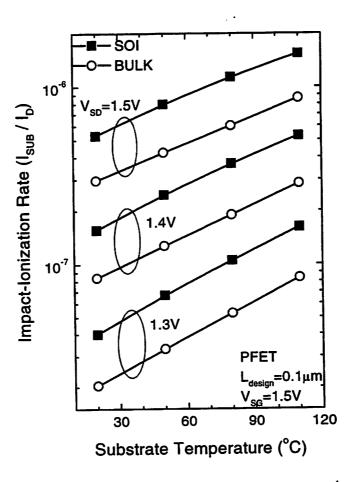

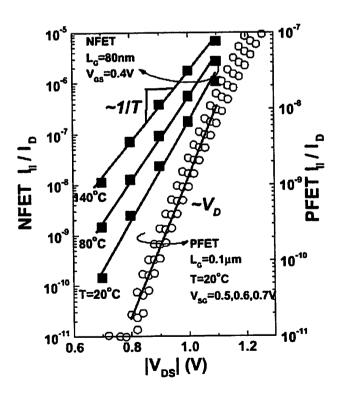

As gate bias increases, the power and therefore the device temperature of the SOI MOSFET rises due to self-heating [9], a consequence of the low thermal conductivity of buried oxide (about two orders of magnitude less than that of silicon). In Figure 3-2 we show measured temperature dependence of the impact-ionization rate for both bulk and SOI devices by varying the substrate temperature using a variable temperature chuck. The increase of I<sub>SUB</sub>/I<sub>D</sub> with temperature explains the phenomenon observed in Figure 3-1. The SOI-specific self-heating effect provides a source for carrier heating in the channel and enhances impact ionization.

Figure 3-2. The impact-ionization rate increases as temperature rises. This explains the self-heating enhanced substrate current occurring at high gate bias in the SOI MOSFET.

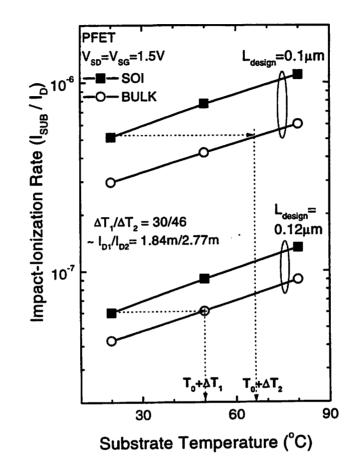

The temperature rise ( $\Delta T$ ) due to self-heating in SOI devices is linear proportional to the static power dissipation with a slope, which can be interpreted as a thermal resistance from the channel to the chuck [9]. Since a larger current drive gives bigger power consumption, for a given technology the temperature rise and therefore the  $I_{SUB}/I_D$  enhancement is more significant for the SOI MOSFET with shorter channel length, as shown in Figure 3-3. For a given bias and substrate temperature ( $T_0$ ), the SOI device temperature and thus  $\Delta T$  can be projected by finding the corresponding temperature which gives the same amount of impact-ionization rate in the bulk device as illustrated in Figure 3-3. In this experiment,  $\Delta T_1$  and  $I_{D1}$  for the 0.12  $\mu$ m device are 30 °C and 1.84 mA, respectively, while  $\Delta T_2$  and  $I_{D2}$  for the 0.1  $\mu$ m device are 46 °C and 2.77 mA, respectively. The equivalence between the extracted  $\Delta T_1/\Delta T_2$  and the measured  $I_{D1}/I_{D2}$  proves that the self-heating effect is indeed responsible for the excess substrate current in the SOI MOSFET.

The self-heating enhanced impact ionization present in DC bias conditions will be absent in most logic circuits. Since the average power consumption per device is low and its switching time (~10 ps) is much shorter than the thermal time constant (~100 ns) [7][8] for state-of-the-art high performance SOI CMOS, the time-averaged and transient device-temperature rises due to self-heating are quite small. For example, considering a chip with power consumption of 10 W, 10 million transistors, and thermal resistance of 10<sup>4</sup> °C/W, the average device temperature increase can roughly be estimated as 0.01 °C and negligible. Therefore, extrapolating device dynamic lifetime by use of static lifetime,

a common practice in hot-carrier reliability stress testing, will underestimate the actual lifetime of SOI MOSFETs in most logic circuits [9].

Figure 3-3. The  $I_{SUB}$  enhancement is more pronounced for the SOI MOSFET with shorter channel length. The SOI temperature rise ( $\Delta T$ ) due to self-heating can be projected by finding the corresponding temperature which gives the same amount of impact-ionization rate in the bulk counterpart. The equivalence of  $\Delta T_1/\Delta T_2$  and  $I_{D1}/I_{D2}$  proves self-heating is responsible for the excess substrate current observed in the SOI MOSFET.

Similarly, the DC  $I_{SUB}$  data measured from body-contacted SOI MOSFETs may not represent the dynamic impact-ionization charging characteristics of rapidly switching floating-body devices in a digital circuit due to this effect. Self-heating-free  $I_{SUB}$  data, in

addition to heating-free I<sub>D</sub> data [10]-[12], should be used and modeled for accurate logic circuit simulation. As shown in Equation (3-1),

$$I_{SUB,non-selfheated} = I_{SUB,DC} - \frac{\Delta I_{SUB,DC}}{\Delta T} R_{th} I_{DS} V_{DS}$$

(3-1),

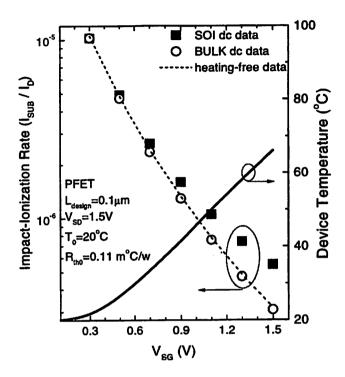

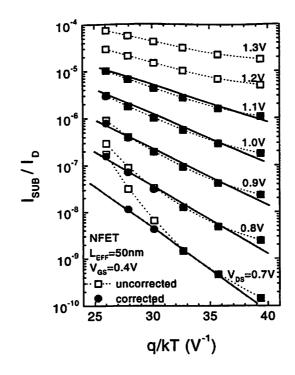

non-self-heated I<sub>SUB</sub> characteristics can be reconstructed by establishing the device-temperature dependence of the substrate current for each bias point. Device temperature can be calculated by (T<sub>0</sub> + thermal resistance × power). Thermal resistance can be measured by several methods such as the poly gate resistance method [10], pulse measurement [11] and the AC output conductance method [12]-[14]. As shown in Figure 3-4, the constructed self-heating-free I<sub>SUB</sub> characteristics using this approach agree well with bulk data. It can be clearly seen that the SOI device temperature and DC I<sub>SUB</sub> data increase significantly at high gate bias.

The self-heating enhanced  $I_{SUB}$  phenomenon stems from the increase of the impact-ionization rate with temperature at low drain bias (Figure 3-2) [15][16], which contradicts the classical electron-phonon scattering mean-free path concept [17]. Further, for a given high gate bias this  $I_{SUB}$  enhancement does not decrease with the supply drain voltage ( $\approx$  power  $\approx$   $\Delta T$ ), as demonstrated in Figure 3-1. It means that the temperature sensitivity of the impact-ionization rate actually increases as the drain bias decreases. Several explanations regarding the temperature dependence of the impact-ionization rate in the low drain bias regime were proposed in the past, including quasi-ballistic transport characteristics performed by deep-submicrometer devices [18]-[20], temperature-

dependent bandgap energy [18][19] and the memory effect [20]. This issue, nevertheless, deserves further experimental study and will be addressed in the next section.

Figure 3-4. The SOI device temperature can be calculated by thermal resistance ( $R_{th0}$ ) and used for the reconstruction of self-heating-free  $I_{SUB}$  characteristics, which should be modeled for most logic-circuit applications.

In conclusion, we report an enhanced substrate current phenomenon in state-of-the-art SOI MOSFETs. Due to self-heating, excess impact ionization is induced for the SOI transistor biased at high gate DC voltage. Since the temperature rise does not follow the instantaneous power dissipation under dynamic operating conditions typical of digital circuit operation, self-heating-free I<sub>SUB</sub> characteristics should be reconstructed and used for the SOI dynamic lifetime prediction as well as circuit simulation of floating-body devices. This effect should also be taken into account when comparisons between SOI and bulk MOSFETs regarding hot-carrier effects are made.

# 3.3 A Thermal Activation View of Low Voltage Impact Ionization in MOSFETs

As the MOSFET dimensions and the power-supply voltage ( $V_D$ ) are continuously scaled down, the hot-carrier effect that increases with device miniaturization is an important issue that demands further investigation at low supply voltages. The hot-carrier effect is usually monitored by the substrate current ( $I_{SUB}$ ) [2] that results from impact ionization caused by energetic carrier in the channel. Previous report [3] on the self-lattice-heating enhanced substrate current, a manifestation of the increased impactionization rate ( $I_{SUB}/I_D$ ) with lattice temperature at low drain bias [15][16], contradicts the classical carrier-phonon scattering mean-free path concept [17][21].

This paradoxical result casts some doubt on the understanding of the hot-carrier effect and the prediction of the long-term reliability of MOSFETs. Therefore, a great deal of Monte Carlo simulations concerning the temperature dependence of the impactionization rate in the low drain bias regime near the silicon bandgap were carried out in the past [7]-[9]. Several explanations have been proposed, including quasi-ballistic transport characteristics performed by deep-submicrometer devices [18]-[20], temperature-dependent bandgap energy [18][19], and the memory effect [20].

However, there has been little experimental assessment on the mechanisms responsible for low voltage impact ionization in state-of-the-art deep-submicrometer MOSFETs. In this work, we present a thermal activation perspective for impact ionization at low drain bias. By directly tackling the measured I<sub>SUB</sub> data based on the

thermal activation viewpoint, we demonstrate the role lattice temperature plays in determining low voltage impact ionization experimentally.

The deep-submicrometer bulk MOSFETs used in this study were fabricated using a 0.13  $\mu$ m technology [3][8][22][23]. The electrical oxide thickness is 2.8 nm. The test devices have a physical gate length of 0.08  $\mu$ m and 0.1  $\mu$ m for NMOS and PMOS, respectively. The substrate currents were measured at various substrate temperatures using a variable temperature chuck. The temperature range (20 °C < T < 170 °C) examined in this work is of special interest to high performance applications.

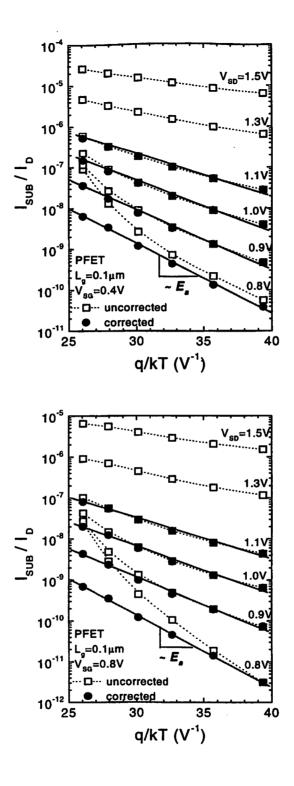

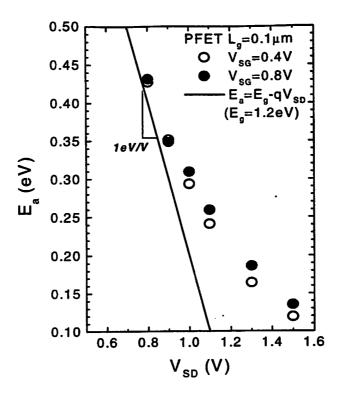

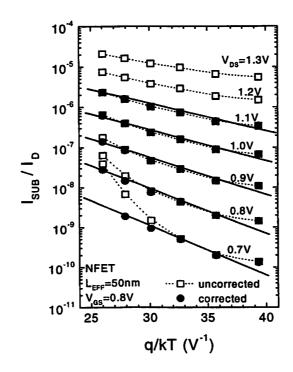

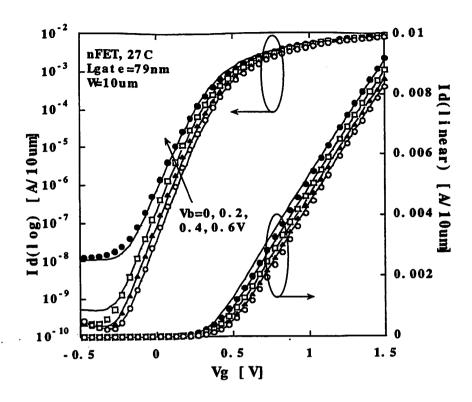

Figure 3-5 shows measured  $I_{SUB}/I_D$  versus reciprocal temperature for the PFET. It demonstrates that  $I_{SUB}/I_D$  increases with temperature. After we carefully subtract the junction leakage that may affect the measurement accuracy of impact ionization current at low drain bias (e.g.  $V_{SD} = 0.8 \text{ V}$ ) and high temperature, a linear relationship between  $log(I_{SUB}/I_D)$  and reciprocal temperature can be observed in Figure 3-5. This Arrhenius behavior reveals the thermally assisted nature of impact ionization at low drain bias. As depicted in Figure 3-5, the slope of the Arrhenius plot determines the activation energy,  $E_a$ , of the underlying mechanism and is plotted against the drain bias in Figure 3-6. Notice that  $E_a$  increases as the drain bias decreases.

Figure 3-5. Measured  $I_{SUB}/I_D$  versus reciprocal temperature at  $V_{SG} = 0.4$  V and  $V_{SG} = 0.8$  V, respectively, for the PFET demonstrating the Arrhenius behavior of low voltage impact ionization. Junction leakage was carefully subtracted at each bias and temperature based on  $log(I_{SUB})$  versus  $V_{SD}$  characteristics.

Figure 3-6. Activation energy versus  $V_D$  for the PFET demonstrating that the driving force of impact ionization is in a transition from the electric field to the lattice temperature with the power-supply scaling.

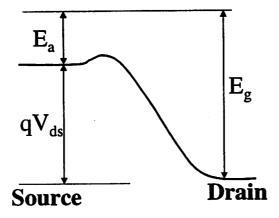

Figure 3-7. Band diagram showing for an electron traveling from the conduction band edge at the source to the drain, an additional energy is required to cause impact ionization.

As depicted in Figure 3-7, the activation energy can be interpreted as the energy in excess of that provided by the supply for the carrier traveling from the source to the drain. In the ballistic limit,  $E_a = E_g - qV_D$  ( $E_g \sim 1.2$  eV [24][25]) is the extra energy that must be acquired from the lattice for the carrier to cause impact ionization. As shown in Figure 3-6, the experimentally determined activation energy approaches this theoretical prediction as  $V_D$  is scaled down (notice the approach of the 1 eV/V theoretical limit of  $\Delta E_a/\Delta V_D$ ). It indicates that the driving force of impact ionization transitions from the electric field to the lattice temperature with power-supply scaling below 1.2 V.

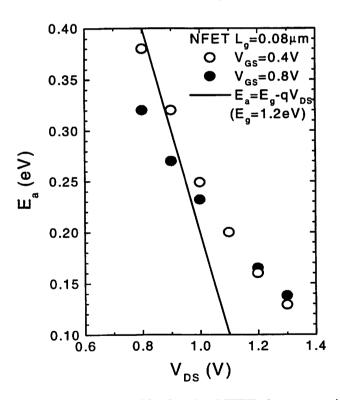

Figure 3-8. Activation energy versus  $V_D$  for the NFET demonstrating the signature of other energy gain mechanisms for low voltage impact ionization based on the activation energy lowering (e.g.,  $V_{GS} = 0.8 \text{ V}$ ).

This thermal activation view also provides a way to experimentally monitor other energy gain mechanisms that may cause impact ionization at sub-bandgap drain bias. As shown in Figure 3-8, the measured activation energy for the NFET at  $V_{GS}=0.4~V$  still follows the simple  $E_a=E_g-qV_D$  model as  $V_D$  is scaled down. At  $V_{GS}=0.8~V$ , nevertheless, the experimentally determined activation energy is smaller than the theoretical prediction at sub-bandgap drain bias, where other energy gain mechanisms play roles in the determination of impact ionization. It has been proposed [18][26][27] that electron-electron scattering may provide an additional source for carrier heating in the channel and enhance impact ionization at sub-bandgap drain bias. Notice that raising the gate bias (e.g. from 0.4 V to 0.8 V), and thus the channel electron concentration, causes a higher electron-electron scattering rate. In other words, the Arrhenius behavior of low voltage impact ionization may be shadowed by electron-electron scattering (especially at high gate bias) as shown in Figure 3-9.

Figure 3-9. Measured  $I_{SUB}/I_D$  versus reciprocal temperature at  $V_{GS} = 0.4$  V and  $V_{GS} = 0.8$  V, respectively, for the NFET. The junction leakage has been subtracted.

The thermally-assisted impact ionization model ( $I_{SUB}/I_D \sim \exp(-(E_g - qV_D) / kT)$ ) predicts a linear relationship between  $\log(I_{SUB}/I_D)$  and  $V_D$  at sub-bandgap drain bias, as verified in Figure 3-10. Recall that the drain bias dependence of  $\log(I_{SUB}/I_D)$  has been previously modeled as  $-1/V_D$  [2] under the maximum electric field framework. The transition of driving force for impact ionization as  $V_D$  is scaled down, therefore, changes the drain bias dependence of the impact-ionization rate. This effect is crucial to accurate modeling of the MOSFET output characteristics, especially the SOI floating-body charging phenomenon [5], for low voltage applications. In addition, the gap of the drain bias dependence of the impact-ionization rate may potentially lower the accuracy of the long-term lifetime extrapolation based on the accelerated hot-carrier stressing. This issue deserves further experimental study in the future.

Figure 3-10.  $V_D$  dependence of the ionization rate at sub-bandgap drain bias.

In conclusion, we provide a thermal activation view of the low voltage impact ionization in deep-submicrometer MOSFETs. Based on this perspective, we experimentally assess the role lattice temperature plays in the determination of low voltage impact ionization. Our experimental result, the Arrhenius I<sub>SUB</sub>/I<sub>D</sub> behavior characterized by the lattice temperature at sub-bandgap drain bias, indicates that the main driving force of impact ionization is changing from the electric field to the lattice temperature with power-supply scaling below 1.2 V. This transition of driving force results in a linear relationship between log(I<sub>SUB</sub>/I<sub>D</sub>) and V<sub>D</sub> at sub-bandgap drain bias, as predicted by the proposed thermally-assisted impact ionization model.

## 3.4 An Impact Ionization Model for SOI Circuit Simulation

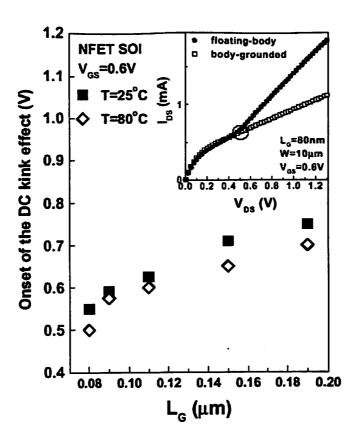

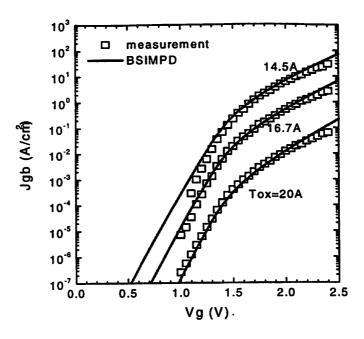

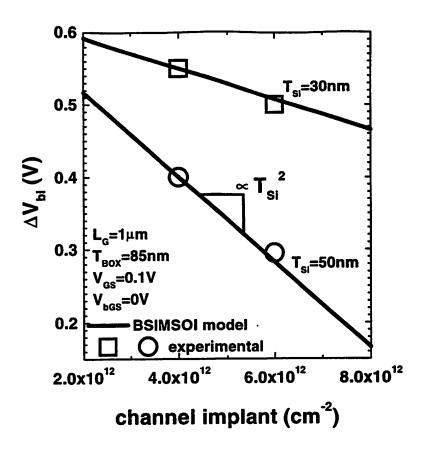

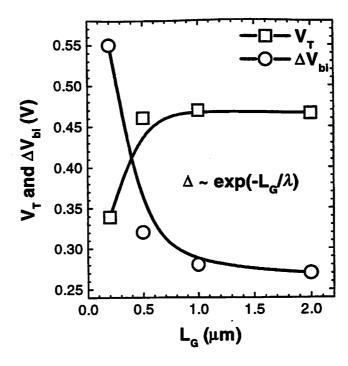

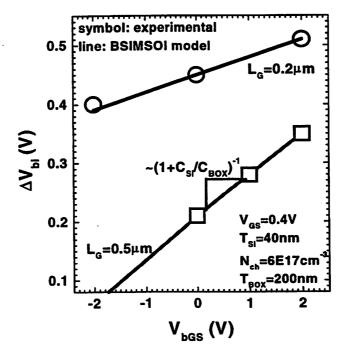

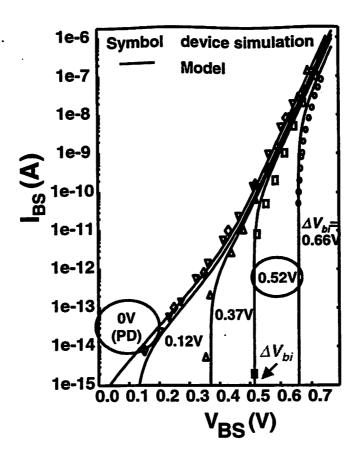

Beside the hot-carrier reliability, impact ionization current ( $I_{II}$ ) plays an important role in the determination of the SOI floating-body behavior. It was suggested that the  $I_{II}$  remains crucial even for double-gate MOSFETs by enhancing the subthreshold leakage [1]. An observation (Figure 3-11) shows that the onset of kink for state-of-the-art SOI devices is well below the silicon bandgap ( $E_g \sim 1.2$  eV). The underlying low voltage ionization mechanism cannot be explained by the conventional wisdom of impact ionization driven by electric field. Based on the thermal activation energy theory [4] proposed in the previous section, we present a compact impact ionization model for SOI circuit simulation [28].

Figure 3-11. Onset voltage of the IV kink (inset) vs. gate length for a  $0.13\mu m$  SOI technology.

According to our thermal activation energy theory [4], the cause of the sub-bandgap drain-voltage impact ionization and thus kink effect in SOI MOSFETs is attributed to the lattice temperature. In addition, thermally-assisted impact ionization in SOI MOSFETs cannot be considered alone, but together with self-heating. The impact ionization current versus gate voltage has been shown in Figure 3-1, indicating an increase of ionization rate at high gate bias due to self-heating [29]. The observation further confirms the thermal nature of the extra impact ionization current.

From the thermally-assisted impact ionization model [4], impact ionization current can expressed by

$$I_{II}/I_D \sim \exp(-(E_g - qV_D) / kT)$$

(3-2).

Equation (3-2) predicts a linear relationship between  $log(I_{II}/I_D)$  and  $V_D$  in the subbandgap drain voltage, and has been verified in Figure 3-10. Recall that under the maximum electric field framework,  $log(I_{II}/I_D)$  has been previously modeled to vary with -  $1/V_D$  [2], which is still applicable at high  $V_D$ . At some intermediate  $V_D$ , the dominant mechanism for impact ionization changes from electric-field driven to thermally driven. To capture both effects and their relative strength, the impact ionization current as a function of drain voltage can be modeled by the following unified expression:

$$I_{II}/I_D \sim \exp(V_D/(\beta_0 + \beta_1 V_D + \beta_2 V_D^2))$$

(3-3),

where  $\beta_0$ ,  $\beta_1$  and  $\beta_2$  are model parameters [30]. The  $V_D$  dependence of this expression approaches the thermally-assisted model (Equation (3-2)) at low  $V_D$ , while returns to the classical model (i.e., -1/ $V_D$ ) at high  $V_D$ .

Figure 3-12. Substrate current fitting at  $V_D=E_g/q$ . Symbols are measurement and lines are simulation.

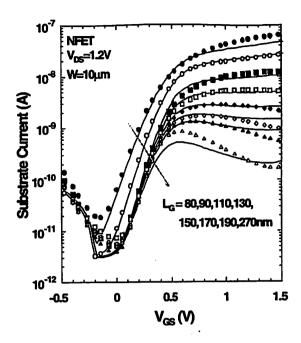

The accuracy of the model has been verified by experimental data. Figure 3-12 shows the fitting of the substrate current data of SOI MOSFET with different dimension and bias condition showing the accuracy of the proposed model at  $V_D=E_g/q$ . After including the thermally-assisted impact ionization current into the substrate current calculation, the body voltage can be correctly calculated using the floating-body model in BSIMPD [5][30], and the low voltage kink in the output characteristics of SOI transistors can be correctly captured as shown in Figure 3-13.

Figure 3-13. BSIMPD accuracy in modeling the SOI output characteristics. Symbols are measurement and lines are simulation.

### 3.5 Summary

In this chapter we discuss the mechanism responsible for low voltage impact ionization in deep-submicrometer MOSFETs. Our study indicates that the driving force of impact ionization transitions from the electric field to the lattice temperature with power-supply scaling below 1.2 V. Due to its thermally assisted nature, the ionization rate in self-heated SOI MOSFETs is enhanced at high gate DC bias. This effect needs to be considered in SOI modeling as well as hot-carrier reliability due to the gap between the fast logic switching and the long thermal time constant. The low voltage impact ionization behavior can be predicted by the proposed thermal activation energy theory, which also explains the sub-bandgap kink in SOI out characteristics. In addition, a compact model has been developed based on the thermal activation energy theory to capture the SOI device characteristics with both thermally assisted impact ionization and electric field induced impact ionization accounted for. This model has been implemented in BSIMPD [5][30].

### 3.6 References

- [1] J. Park et al., IEEE International SOI Conference, p. 147, 2001.

- [2] C. Hu, S. Tam, F. Hsu, P. Ko, T. Chan and K. Terill, "Hot-electron-induced MOSFET degradation model, monitor and improvement," *IEEE Trans. Electron Devices*, vol. ED-32, p. 375, 1985.

- [3] P. Su, K. Goto, T. Sugii and C. Hu, "Enhanced substrate current in SOI MOSFETs," *IEEE Electron Device Letters*, vol. 23, no. 5, pp. 282-284, May 2002.

- [4] P. Su, K. Goto, T. Sugii and C. Hu, "A thermal activation view of low voltage impact ionization in MOSFETs," *IEEE Electron Device Letters*, vol. 23, no. 9, September 2002.

- [5] P. Su, S. Fung, S. Tang, F. Assaderaghi and C. Hu, "BSIMPD: A partial-depletion SOI MOSFET model for deep-submicron CMOS designs," in *Proceedings of IEEE Custom IC Conference*, pp. 197-200, 2000.

- [6] S. Fung, L. Wagner, M. Sherony, N. Zamdmer, J. Sleight, M. Michel, E. Leobandung,

- S. Lo, T. Chen and F. Assaderaghi, "A partially-depleted SOI compact model formulation and parameter extraction," in *Symposium on VLSI Tech.*, pp. 206-207, 2000.

- [7] J. P. Colinge, Silicon-on-insulator technology: materials to VLSI, 2<sup>nd</sup> edition, 1997.

- [8] Y. Momiyama, T. Hirose, H. Kurata, K. Goto; Y. Watanabe and T. Sugii, "A 140 GHz f<sub>T</sub> and 60 GHz f<sub>MAX</sub> DTMOS integrated with high-performance SOI logic technology," in *IEDM Tech. Dig.*, pp. 451-454, 2000.

- [9] P. Su, K. Goto, T. Sugii and C. Hu, "Excess Hot-Carrier Currents in SOI MOSFETs and Its Implications," 2002 IEEE International Reliability Physics Symposium Proceedings, Dallas, April 2002, pp. 93-97.

- [10] L. Su, J. Chung, D. Antoniadis, K. Goodson and M. Flik, "Measurement and modeling of self-heating in SOI NMOSFET's," *IEEE Trans. Electron Devices*, vol. 41, no. 1, p. 69, 1994.

- [11] K. Jenkins and J. Sun, "Measurement of I-V curves of silicon-on-insulator (SOI) MOSFET's without self-heating," *IEEE Electron Device Letter*, vol. 16, no. 4, pp. 145-147, April 1995.

- [12] H. Nakayama, P. Su, C. Hu, M. Nakamura, H. Komatsu, K. Takeshita and Y. Komatsu, "Methodology of self-heating free parameter extraction and circuit simulation for SOI CMOS," in *Proceedings of IEEE Custom IC Conference*, pp. 381-384, 2001.

- [13] W. Jin, S. Fung, W. Liu, P. Chan and C. Hu, "Self-heating characterization for SOI MOSFET based on AC output conductance," in *IEDM Tech. Dig.*, pp. 175-178, 1999.

- [14] R. Tu, C. Wann, J. King, P. Ko and C. Hu, "An AC conductance technique for measuring self-heating in SOI MOSFET's," *IEEE Electron Device Letter*, vol. 16, no. 2, pp. 67-69, Feb. 1995.

- [15] B. Eitan, D. Frohman-Bentchkowsky and J. Shappir, "Impact ionization at very low voltages in silicon," *Journal of Applied Physics*, vol: 53(2), pp. 1244-1247, Feb. 1982.

- [16] D. Esseni, L. Selmi, E. Sangiorgi, R. Bez and B. Ricco', *IEEE Electron Device Letter*, vol. 16, no. 11, pp. 506-508, Nov. 1995.

- [17] S. M. Sze, Physics of Semiconductor Devices, 2<sup>nd</sup> edition, 1981.

- [18] M. Fischetti and S. Laux, "Monte Carlo study of sub-band-gap impact ionization in small silicon field-effect transistors," in *IEDM Tech. Dig.*, pp. 305-308, 1995.

- [19] N. Sano, M. Tomizawa and A. Yoshii, "Temperature dependence of hot carrier effects in short-channel Si-MOSFET's," *IEEE Trans. Electron Devices*, vol. 42, no. 12, p. 2211, Dec. 1995.

- [20] M. Mastrapasqua, J. Bude, M. Pinto, L. Manchanda and K. Lee, "Temperature and channel length dependence of impact ionization in P-channel MOSFETs," in *Symposium on VLSI Tech.*, pp. 125-126, 1994.

- [21] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, Cambridge University Press, 1998.

- [22] K. Goto, M. Kase, Y. Momiyama, H. Kurata, T. Tanaka, M. Deura, Y. Sanbonsugi and T. Sugii, "A study of ultra shallow junction and tilted channel implantation for high performance 0.1 µm pMOSFETs," *IEDM Tech. Dig.*, pp. 631-634, 1998.

- [23] K. Sukegawa, M. Yamaji, K. Yoshie, K. Furumochi, T. Maruyama, H. Morioka, N. Naori, T. Kubo, H. Kanata, M. Kai, S. Satoh, T. Izawa and K. Kubota, "High-performance 80-nm gate length SOI-CMOS technology with copper and very-low-k interconnects," *Symposium on VLSI Tech.*, pp. 186-187, 2000.

- [24] E. Cartier, M. V. Fischetti, E. A. Eklund and F. R. McFeely, "Impact ionization in silicon," *Applied Physics Letters*, vol. 62, no. 25, pp. 3339-3341, June 1993.

- [25] C. L. Anderson and C. R. Crowell, "Threshold energies for electron-hole pair production by impact ionization in semiconductors," *Physical Review B*, vol. 5, no. 6, pp. 2267-2272, 1972.

- [26] S. Rauch, F. Guarin and G. LaRosa, "Impact of e-e scattering to the hot carrier degradation of deep submicron NMOSFET's," *IEEE Electron Device Letters*, vol. 19, no. 12, pp. 463-465, December 1998.

- [27] P. Childs and C. Leung, "A one-dimensional solution of the Boltzmann transport equation including electron-electron interactions," *Journal of Applied Physics*, vol. 79, no. 1, pp. 222-227, January 1996.

- [28] P. Su, S. Fung, H. Wan, A. Niknejad, M. Chan and C. Hu, "An impact ionization model for SOI circuit simulation," 2002 IEEE International SOI Conference Proceedings, Williamsburg, VA, Oct. 2002, pp. 201-202.

[29] P. Su, K. Goto, T. Sugii and C. Hu, "Self-heating enhanced impact ionization in SOI MOSFETs", 2001 IEEE International SOI Conference Proceedings, Durango, CO, Oct. 2001, pp.31-32.

[30] BSIMSOI Users' Manual. (www-device.eecs.berkeley.edu/~bsimsoi)

## Chapter 4

## Impact of Gate-Body Tunneling on SOI

### **CMOS**

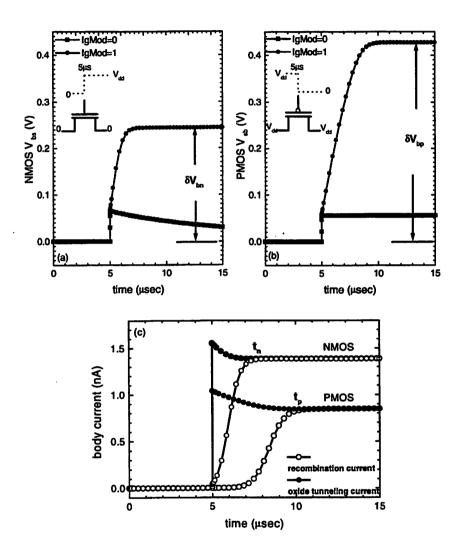

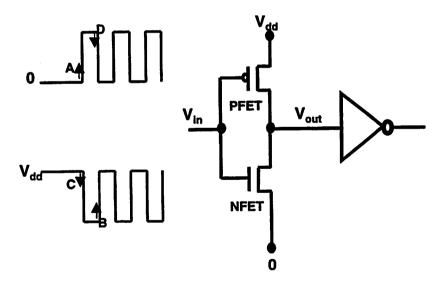

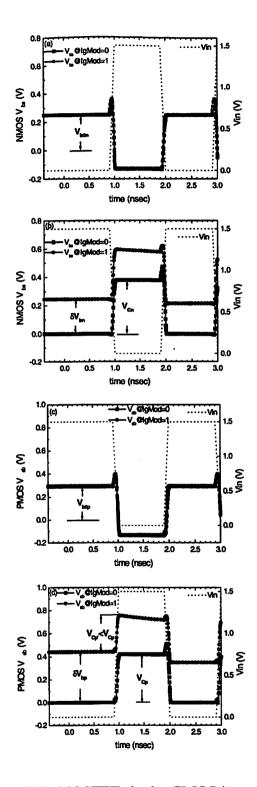

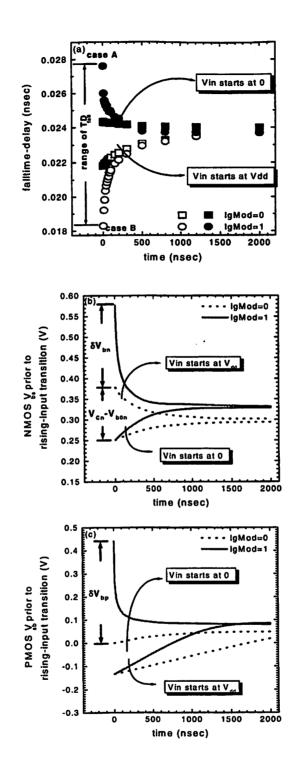

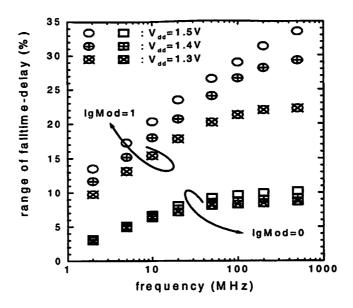

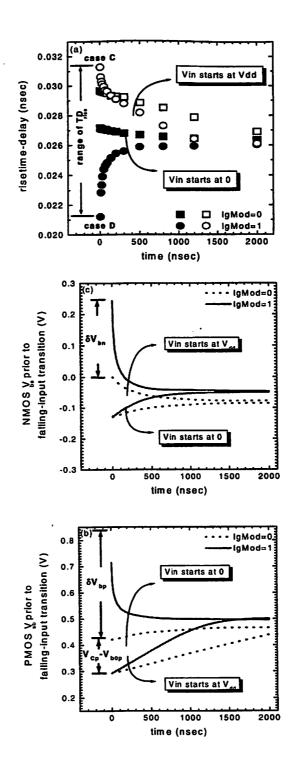

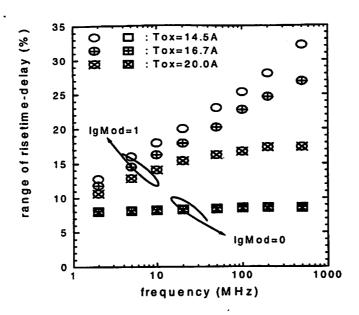

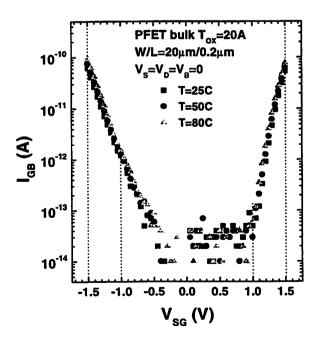

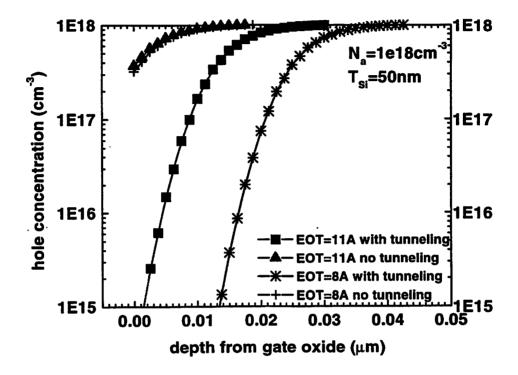

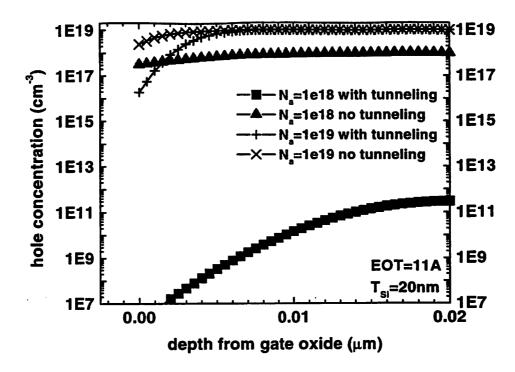

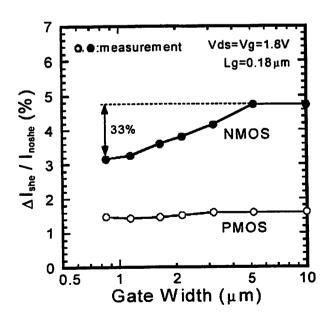

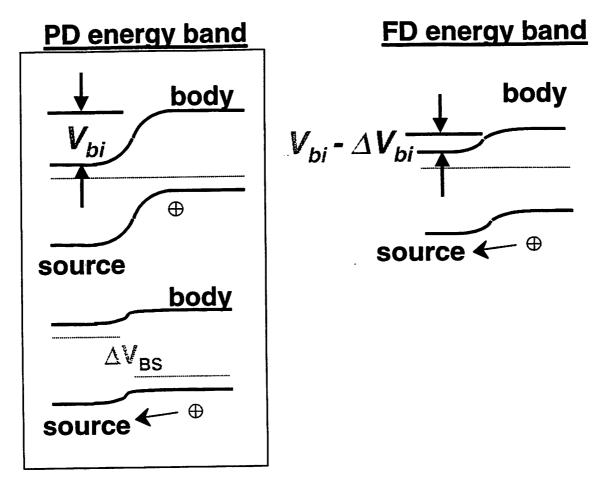

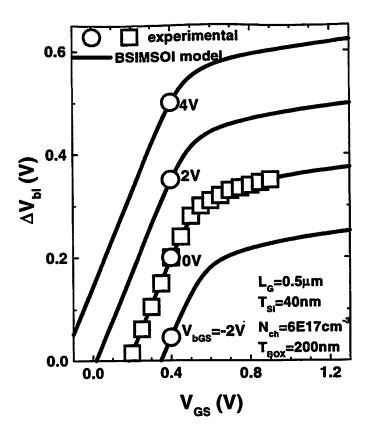

### 4.1 Introduction