# Copyright © 2002, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# ULTRA WIDE-BAND BASEBAND DESIGN AND IMPLEMENTATION

by

Mike Shuo-Wei Chen

Memorandum No. UCB/ERL M02/42

18 December 2002

# ULTRA WIDE-BAND BASEBAND DESIGN AND IMPLEMENTATION

by

Mike Shuo-Wei Chen

Memorandum No. UCB/ERL M02/42

18 December 2002

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# **Ultra Wide-band Baseband Design and Implementation**

by Mike Shuo-Wei Chen

# **Research Project**

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II.

Approval for the Report and Comprehensive Examination:

| Committee:                    |  |  |

|-------------------------------|--|--|

|                               |  |  |

|                               |  |  |

| Professor Robert W. Brodersen |  |  |

| Research Advisor              |  |  |

|                               |  |  |

| (Date)                        |  |  |

|                               |  |  |

| ****                          |  |  |

|                               |  |  |

|                               |  |  |

| Professor David Tse           |  |  |

| Second Reader                 |  |  |

|                               |  |  |

| (Date)                        |  |  |

# Ultra Wide-band Baseband Design and Implementation

by Mike Shuo-Wei Chen

# Research Project

Submitted to the Department of Electrical Engineering and Computer Sciences, University of California at Berkeley, in partial satisfaction of the requirements for the degree of Master of Science, Plan II.

Approval for the Report and Comprehensive Examination:

Committee:

Professor Robert W. Brodersen

Research Advisor

(Date)

Professor David Tse

Second Reader

(Date)

# TABLE OF CONTENTS

| • CHAPTER I INTRODUCTION I                      |     |

|-------------------------------------------------|-----|

| 1.1 MOTIVATION                                  | 1   |

| 1.2 SCOPE OF THIS WORK                          | 2   |

| 1.3 Organization of This Thesis                 | 2   |

| • CHAPTER 2 UWB COMMUNICATION BACKGROUND 3      |     |

| 2.1 Introduction                                | 3   |

| 2.2 Channel Capacity                            | 3   |

| 2.2 Maximize System Throughput                  | 5   |

| 2.2.1 Modulation Schemes                        | 5   |

| 2.2.2 Spectral Efficiency and Processing Gain   | 6   |

| 2.3 Power Spectral Density                      |     |

| • CHAPTER 3 SYSTEM SPECIFICATION 11             |     |

| 3.1 Introduction                                | 11  |

| 3.2 DETECTION RULE                              | 11  |

| 3.3 DERIVATION OF RECEIVED SIGNAL STATISTICS    | 14  |

| 3.4 Processing gain and Threshold Determination | 17  |

| 3.5 MONTE-CARLO SIMULATION                      | 18  |

| 3.5 FINITE WORD LENGTH                          | 20  |

| • CHAPTER 4 FLEXIBLE UWB BASEBAND DESIGN 23     |     |

| 4.1 Introduction                                | 23  |

| 4.2 Brief System Overview:                      | 23  |

| 4.3 FLEXIBLE SYSTEM PARAMETERS                  | 25  |

| 4.4 OPERATION MODES (SYNCHRONIZATION):          | 27  |

| 4.4.1 Receiving Chain:                          | 28  |

| 4.4.2 Acquisition Mode:                         | 29  |

| 4 4 3 Code Tracking                             | 3,8 |

| 4.5 UWB BASEBAND COMPONENTS                           | 43 |

|-------------------------------------------------------|----|

| 4.5.1 Matched Filtering                               | 44 |

| 4.5.2 Correlation Block                               | 46 |

| 4.5.3 Peak Detector                                   | 46 |

| 4.5.4 Data Recovery                                   | 47 |

| 4.5.5 Symbol Clock Generation                         | 48 |

| 4.5.6 Control Logic                                   | 50 |

| • CHAPTER 5 IMPLEMENTATION OF ASIC DIGITAL BACKEND 53 |    |

| 5.1 Pulse Matched Filter                              | 53 |

| 5.2 PN CORRELATOR AND DOWNSAMPLER                     | 61 |

| 5.3 COEFFICIENTS REGISTERS                            | 64 |

| 5.4 PN GENERATOR                                      | 65 |

| 5.5 PEAK DETECTOR                                     | 66 |

| 5.6 CONTROL LOGIC                                     | 67 |

| 5.7 PMF CONTROL SIGNAL DECODER                        | 69 |

| 5.8 Top level I/O                                     | 70 |

| • CHAPTER 6 SYSTEM SIMULATION 72                      |    |

| 6.1 Introduction                                      | 72 |

| 6.2 COMMUNICATION CHAIN MODELING                      | 72 |

| 6.3 XILINX IMPLEMENTATION OF BASEBAND                 | 76 |

| 6.3 FUNCTIONALITY SIMULATION                          | 81 |

| • CHAPTER 7 CONCLUSIONS 85                            |    |

| • REFERENCES 87                                       |    |

# LIST OF FIGURES

| FIGURE 2-1 MODULATION SCHEMES AFFECT INPUT SNR V.S. THROUGHPUT                 | 8     |

|--------------------------------------------------------------------------------|-------|

| FIGURE 2-2 FCC REGULATION ON INDOOR SYSTEMS                                    | 10    |

| FIGURE 3-1 BINARY DETECTION FOR SIGNAL PLUS NOISE                              | 11    |

| FIGURE 3-2 NEYMAN-PEARSON TEST                                                 | 14    |

| FIGURE 3-3 FINITE WORD LENGTH V.S. EBNIN                                       | 21    |

| FIGURE 4-1 UWB COMMUNICATION SYSTEM OVERVIEW                                   | 23    |

| FIGURE 4-2 TARGET PARAMETERS OF THE SYSTEM                                     | 27    |

| FIGURE 4-3 COHERENT DETECTOR                                                   | 28    |

| FIGURE 4-4 A) GPS SYSTEM SEARCH PATTERN. B) UWB SEARCH PATTERN                 | 29    |

| FIGURE 4-5 MULTIPLE-DWELL DETECTION FLOW                                       | 32    |

| FIGURE 4-6 A) ACQUISITION TIME V.S. SEARCHING PHASE B) SIZE V.S. SEARCHING PHA |       |

| FIGURE 4-7 PRODUCT OF ACQUISITION TIME AND AREA                                | 38    |

| FIGURE 4-8 EARLY-LATE TRACKING PROFILE A) RX PULSE MATCHES ON TIME PHASE I     | 3) Rx |

| PULSE COMES EARLIER                                                            | 40    |

| FIGURE 4-9 A) DLL TRACKING LOOP B) UWB TRACKING LOOP                           | 41    |

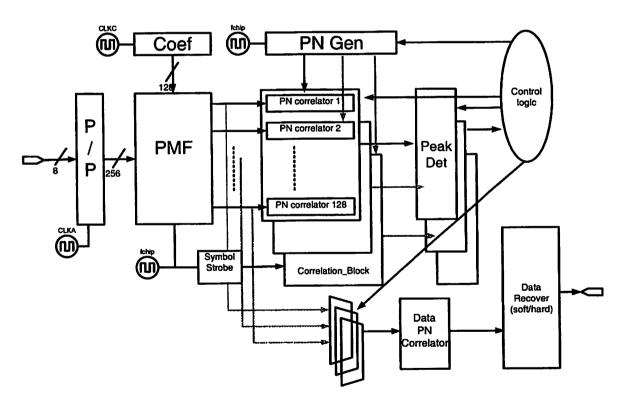

| FIGURE 4-10 BASEBAND OVERVIEW                                                  | 43    |

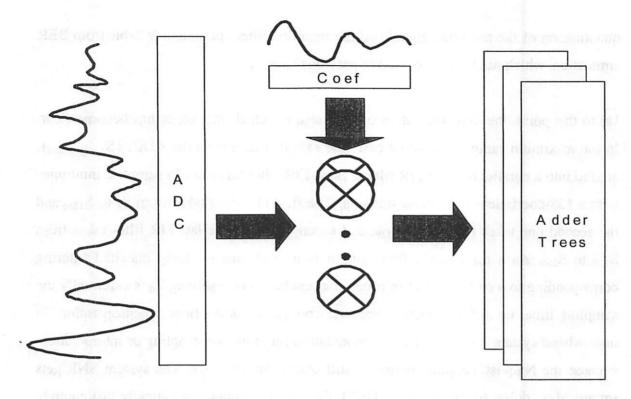

| FIGURE 4-11 PULSED MATCHED FILTER                                              | 46    |

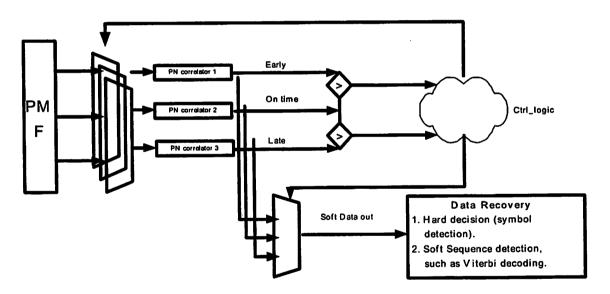

| FIGURE 4-12 DATA RECOVERY DIAGRAM                                              | 47    |

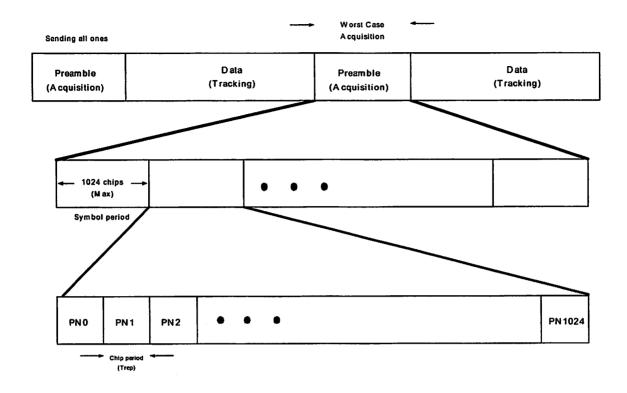

| FIGURE 4-13 PROPOSED PACKET FORMAT                                             | 49    |

| FIGURE 4-14 SYMBOL BOUNDARY                                                    | 49    |

| FIGURE 4-15 SYMBOL CLOCK GENERATION                                            | 50    |

| FIGURE 4-16 EXAMPLE OF MAIN CONTROL LOGIC                                      | 52    |

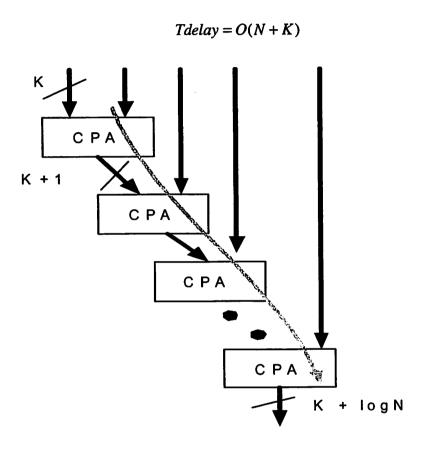

| FIGURE 5-1 SEQUENTIAL ADDER.                                                   | 54    |

| FIGURE 5-2 LINEAR ADDER ARRAY                                                  | 55    |

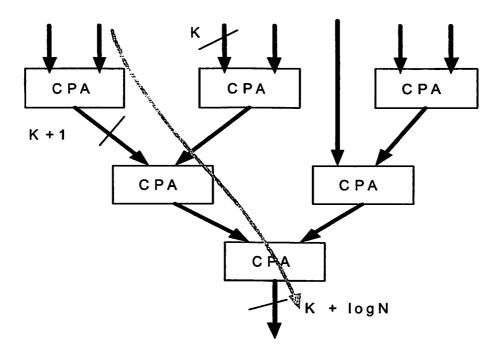

| FIGURE 5-3 BINARY ADDER TREE                                                   | 56    |

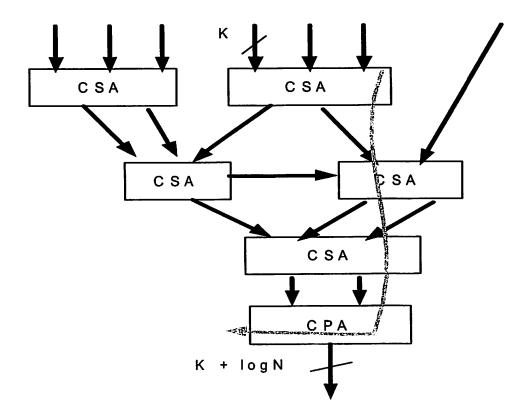

| FIGURE 5-4 CARRYSAVE ADDER TREE                                                | 57    |

| FIGURE 5-5 ARCHITECTURE EXPLORATION FOR CORRELATOR                             | 61    |

| FIGURE 5-6 DOWNSAMPLER ARCHITECTURES                                           | 62    |

| FIGURE 5-7 ARCHITECTURES OF PN GENERATOR                                       | 65    |

| FIGURE 6-1 COMMUNICATION CHAIN OVERVIEW                                        | 73    |

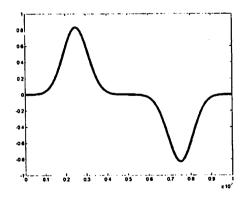

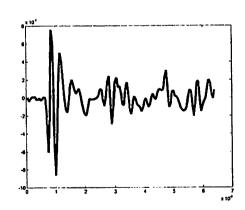

| FIGURE 6-2 A) IDEAL DOUBLET PULSE BY CURRENT LOOP ANTENNA B) MONOC | CYCLE PULSE |

|--------------------------------------------------------------------|-------------|

| BY MONOPOLE ANTENNA                                                | 73          |

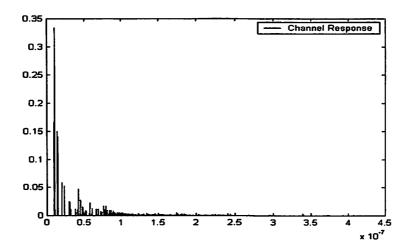

| FIGURE 6-3 MULTI-PATH CHANNEL MODEL AT CORY 2ND FLOOR              | 74          |

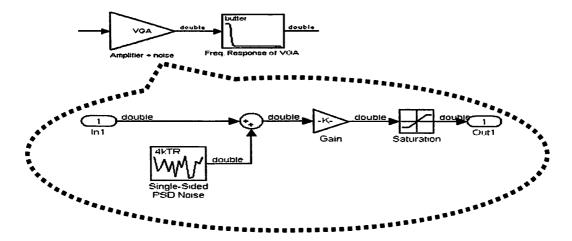

| FIGURE 6-4 FRONT END AMPLIFIER MODELING                            | 74          |

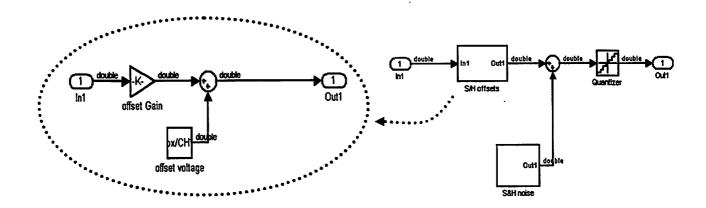

| FIGURE 6-5 SAMPLE AND HOLD CIRCUIT AND QUANTIZER                   | 75          |

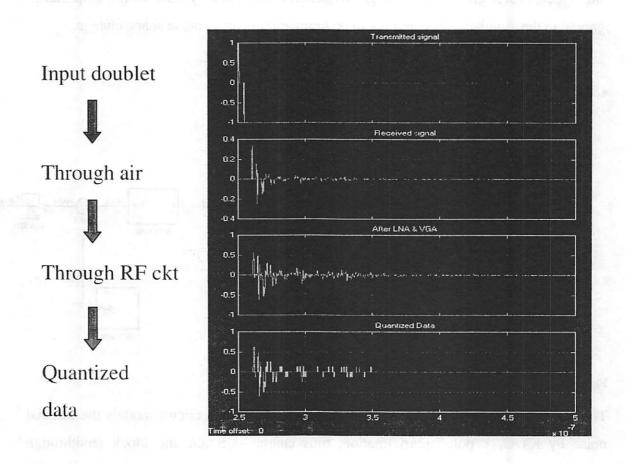

| FIGURE 6-6 SIGNAL WAVEFORM ALONG THE CHAIN                         | 76          |

| FIGURE 6-7 XILINX IMPLEMENTATION OVERVIEW                          | 77          |

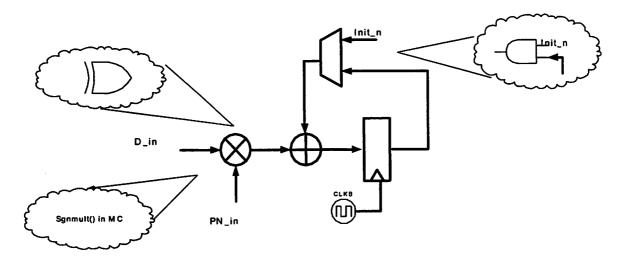

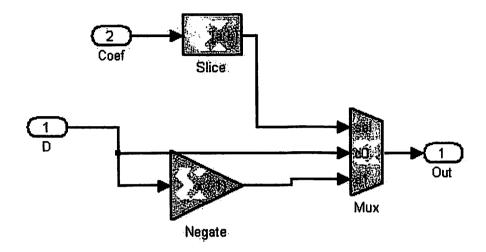

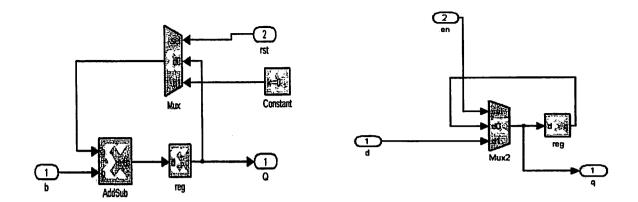

| FIGURE 6-8 1-BIT MULTIPLICATION                                    | 78          |

| FIGURE 6-9 PMF BLOCK                                               | 79          |

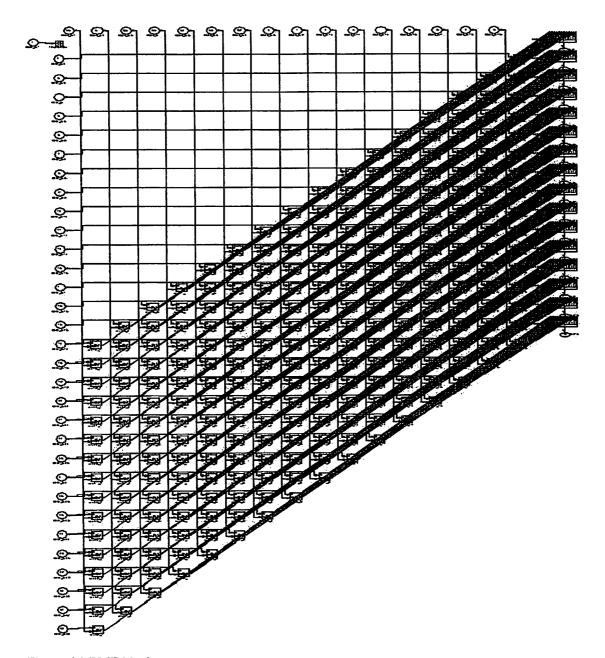

| FIGURE 6-10 A) ACCUMULATOR B) DOWNSAMPLER                          | 80          |

| FIGURE 6-11 XILINX DATA RECOVERY BLOCK                             | 80          |

| FIGURE 6-12 A) MAX CELL B) MAX CELL TREE (PEAK DETECTOR)           | 81          |

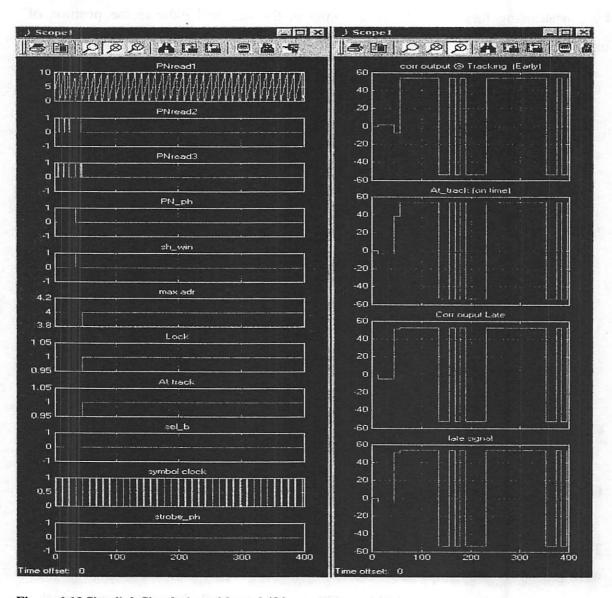

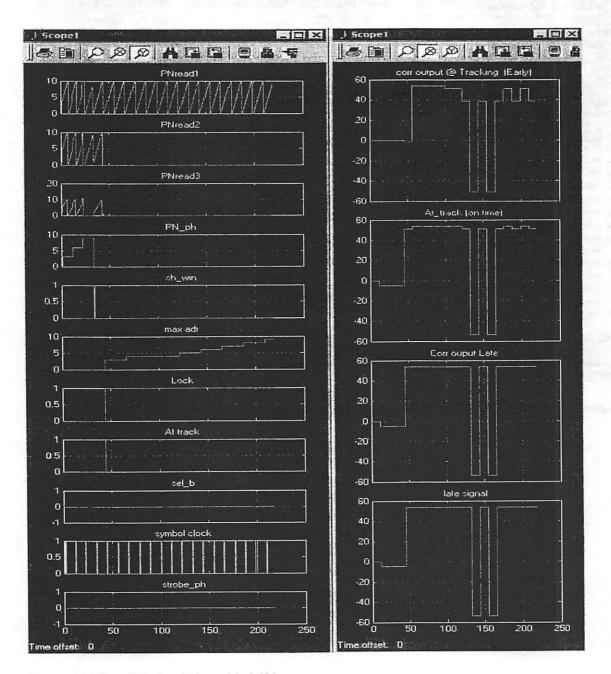

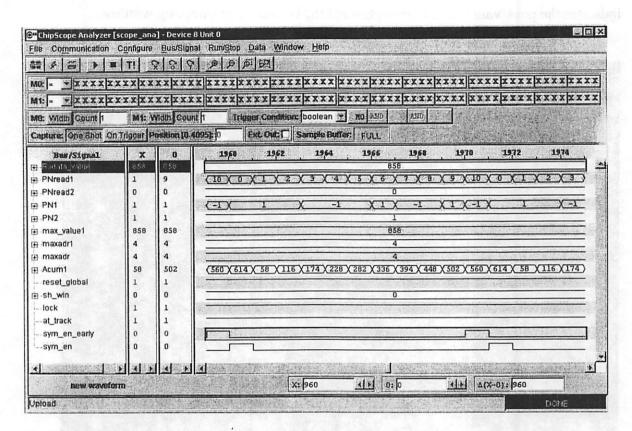

| FIGURE 6-13 SIMULINK SIMULATION WITHOUT DRIFTING                   | 82          |

| FIGURE 6-14 SIMULINK SIMULATION WITH DRIFTING                      | 83          |

| FIGURE 6-15 RESULTS FROM FPGA SIMULATION                           | 84          |

# LIST OF TABLES

| TABLE 3-1 BER SIMULATION                                      | 19 |

|---------------------------------------------------------------|----|

| TABLE 3-2 PROBABILITY OF ERROR SIMULATION IN ACQUISITION MODE | 19 |

| TABLE 3-3 FINITE WORD LENGTHS AT PMF OUTPUT V.S. BER          | 22 |

| TABLE 5-1 ARCHITECTURE COMPARISON OF ADDER TREE               | 58 |

| TABLE 5-2 AREA/DELAY VERSUS SIZE AND BIT WIDTH OF PMF         | 60 |

| TABLE 5-3 I/O of PMF                                          |    |

| TABLE 5-4 AREA/DELAY OF PN CORRELATOR                         |    |

| TABLE 5-5 I/O of PN CORRELATOR                                |    |

| TABLE 5-6 I/O OF MAIN CONTROL BLOCK                           |    |

| TABLE 5-7 I/O OF READOUT BLOCK                                |    |

| TABLE 5-8 TOP LEVEL I/O                                       |    |

# Acknowledgment

There is no way I could come through the course of the project without the help from these people and institutions. First of all, I would like to thank my advisor Professor Bob Brodersen for his support and guidance ever since I joined the group. His trust and insight has helped me out at the various time of this project. Also his personality and vision has offered me a great model of being a good researcher. The environment of BWRC that Bob and Jan have created is really unbeatable for graduate studies. I would also like to thank Prof. David Tse, who had many useful discussions with me. His lectures solidified my communication background, which proved to be very useful for this project.

Next, I would like to thank my great colleagues in BWRC. I'd like to thank our UWB fellows, Ian O'Donnell, and Stanley Wang. Ian has kindly helped me a lot in many aspects during the course, including carefully proofreading this thesis. His wide knowledge and unique viewpoints made this research project more interesting. Stanley was a great partner of both research and class projects. I also thank Engling Yeo for almost instantaneous response to all my questions in many digital chip implementation issues. I enjoyed very much to join his mountain biking team. Of course, I have to thank Ada Poon for many useful advice and discussions. There are of course these intelligent people that I could always discuss with. They are Yun Chiu, Chinh Doan, Brian Limketkai, Luns Tee, and Hans-Martin Bluethgen. People who have been kindly helping me use the in-house design flows, Rhett Davis, Brian Richards, Chen Cheng, Kimmo Kuusilinna, and Tina Smilkstein.

Last but not the least, my parents, younger brother, and my girlfriend, Wan-Hsuan, have always been the best supports in my life. Without their endless care and love, it is impossible for me to accomplish these tasks. I am so fortunate to be born in this family and have my brother, Wei-Ming, to grow up together and also Wan's accompany makes my life more complete and enjoyable. Of course, I will not forget all my best friends in Taiwan and those great times we had created together before. Thank you all.

# **Chapter 1 Introduction**

#### 1.1 Motivation

Ultra-Wideband (UWB) technology has gradually drawn people's attention recently. The technology itself already existed since the 1980's, and was mostly used for radar applications. In 1998, the FCC first proposed UWB transmission under Part 15 rules (limits on intentional and unintentional radiators in unlicensed bands), and asked for the comments from the industry. In Feb. 2002 it issued a First Report and Order [FCC02] that permits the marketing and operation of certain types of new products incorporating ultra-wideband. UWB becomes promising in various application areas, such as imaging systems, vehicular radar systems, and communication and measurement systems.

UWB was first defined by FCC as communication bandwidth that is more than 25% of the carrier frequency. This is much wider than any existing communication system. This wide bandwidth allows UWB to not only have a fine timing resolution but also more degree of freedom to use. Thus, one application in positioning has been under progress [Aetherwire]. Another main consumer application is targeting short-range and high-speed communication [XtremeSpectrum] due to the larger degree of freedom for UWB.

From a hardware implementation perspective, an UWB transceiver inherently has lower complexity given the fact that RF carrier is eliminated. The information is directly modulated on the pulses. It reduces the cost for both analog front-end and baseband design. Building a low power and low cost UWB system is the goal of this project. Another concern about UWB is the interference with other systems that reside within the same bandwidth. Therefore, our focus is so called "undetectable" UWB, which is transmitting the pulses under noise floor to avoid degrading existing systems.

### 1.2 Scope of This Work

One objective of this project is to implement the UWB digital backend. The system is mainly digital, and analog data is sampled with sub-nanosecond spacing. The basic functionality of digital backend is to do signal acquisition and data tracking. Among the many issues, this report will cover from system design to hardware implementation in Module Compiler and FPGA.

The research target of the baseband design is low power consumption and high flexibility. Low power consumption comes from the low duty-cycle communication mode where one could slow down the pulse transmission rate and relax timing constraint for baseband. Then, we could reduce the supply voltage and push the unused blocks into sleep mode for power saving. The flexibility issue arises from our desire to experiment with UWB, such as changing the data rate or pulse shape, etc. The baseband has to fulfill these missions.

# 1.3 Organization of This Thesis

The remainder of the thesis has six chapters. The structure of this report starts from communication perspectives and turns into circuit design. Chapter two gives a basic communication background for UWB, such as data rate and modulation scheme. Chapter three determines the system specifications for the baseband. Issues like number of PN chips and the detection threshold required for the baseband will be covered. Chapter four focuses on system design. It first describes the functionality and operational modes of the baseband and then brings out how we implemented the system. Chapter five goes into the core of each system block including the architectural explorations in Module Compiler. Chapter six provides an implementation on FPGA and Simulink system simulation. Finally, chapter seven concludes with the status of the current work and future tasks.

# Chapter 2 UWB Communication Background

#### 2.1 Introduction

This chapter will give some background about UWB communication. Since UWB communication makes use of an ultra-wide bandwidth, the first question would be how fast it could communicate. What kind of modulation should we use to approach this capacity? These issues will be discussed in the following sections.

### 2.2 Channel Capacity

In order to get some idea how fast UWB could communicate, let's start from AWGN channel. The capacity is already given by well-known Shannon capacity equation,

$$C = W \log_2(1 + \frac{Pav}{W \cdot No})$$

If we transmit at the thermal noise level for 1 GHz bandwidth, the transmission power, Pav, is -84 dBm given a 50-Ohm front-end [Razavi98]. Constant noise power spectral density, No, depends on the receiving antenna. From some measurement data taken in the Berkeley Wireless Research Center (BWRC) lab (courtesy of Ian and Stanley), the noise power integrated from 0 to 1GHz band is about -56 dBm and is treated as white Gaussian noise. Under this scenario, the channel capacity is about 2 Mbps.

As a matter of fact, the noise is colored due to those narrowband interfers such as cellular phones, wireless TV channels, etc. Assume the transmitted power is evenly distributed over the entire band, the channel capacity is calculated as,

$$C = \int_{W} \log_2(1 + \frac{Pav}{W \cdot N(f)}) df$$

The channel capacity goes up to 20 Mbps, almost ten times faster than AWGN channel.

Furthermore, if the transmitter knows the channel response, the channel capacity could be higher according to information theory, using "water-filling" [Cover91]. The idea is to put more power on those bands whose noise is lower while remain the total transmission power the same.

$$C = \int_{-w}^{w} \log(1 + S(f) |C(f)|^{2}) df$$

where,

$$S(f) = (\lambda - \frac{1}{|C(f)|^2})^+$$

while satisfies,

$$\int_{-\infty}^{\infty} S(f)df = P$$

the total transmission power

$\lambda$  is the water level for weighting transmission power, while C(f) is the channel response. The channel capacity according to the measured data is about 40 Mbps as long as the transmitter could do power budgeting over different frequency bands. Of course, the channel measurement should be done in advance and be known to the transmitter. Power control in pulse-based communication is difficult to implement. Therefore, this water filling method simply gives us an idea how fast such a wideband system can transmit at the time being.

### 2.2 Maximize System Throughput

In the following sections, we will discuss the method to approach AWGN channel capacity calculated from previous section. This will depend on different modulation techniques and spectral efficiency we choose.

#### 2.2.1 Modulation Schemes

For this pulse-based digital communication, the modulation schemes considered here are PAM (Pulse amplitude modulation), PPM (Pulse position modulation) and Biorthogonal signaling (PAM plus PPM) [Proakis00].

#### PAM

PAM modulates the information on the amplitude of a transmitted pulse. 2-PAM, also known as antipodal signaling or BPSK, sends a positive pulse when bit "one" is sent, and negative one for bit "zero". Due to its simplicity compared to M-PAM, antipodal signaling is the targeted modulation in order to avoid pulse amplitude control and automatic gain control circuitry. Under 2-PAM modulation, a processing gain may be needed to reduce error probability. This is achieved by adopting direct sequence spread spectrum (DSSS) technique [Proakis00]. The transmitted signals are modulated with a certain pseudo random code. At the receiver side, it correlates with the same code, thus gaining more energy than just a single pulse.

#### • PPM

PPM is an orthogonal signaling technique in time. The information modulates on the position of pulses [Scholtz93]. The more positions it has, the more information contained per pulse. Because the signal set is orthogonal, the Euclidean distance between any two signals is less than BPSK. Therefore, the processing gain required for PPM should be larger than BPSK in order to keep the same performance. However, PPM is more

difficult to get acquired and has a more stringent constraint on timing since the information is carried by the timing offset. Processing gain in PPM is achieved by modulating the position of pulses with a certain pseudo random code, as with PAM above.

#### BIORTHOGONAL SIGNALING

M-ary biorthogonal signaling is constructed from 1/2M orthogonal signals by including the negatives of those. In our case, the modulation is using positive and negative 1/2M PPM signals. Thus, the information carried on a single pulse is doubled compared to purely PPM. And the pseudo random code could be modulated on both amplitudes and positions.

#### 2.2.2 Spectral Efficiency and Processing Gain

In this section, we will try to relate the data transmission rate with pulse rate, Rc = 1/Trep, and input SNR. First of all, the processing gain needs to be determined.

The signal to noise ratio per bit, Eb/No, is the parameter people use to relate to error probability, which will be discussed more thoroughly in the next chapter. The figure that shows the relation between the two is known as waterfall curve. From the curve, we can know the detection Eb/No that receiver has to achieve for a certain error probability. For instance, one needs 7 dB Eb/No at the correlator output for 1e-3 error probability in BPSK modulation scheme [Proakis00]. Obviously, the required processing gain depends on input SNR. The stronger the received signal is, the less processing gain is needed. The following equation tells the relationship between the input SNR, Pav/(W\*No), and the corresponding input Eb/No. Rc is pulse rate, and W is transmission bandwidth.

$$\frac{Eb}{N_c} = \frac{W}{Rc} \left( \frac{Pav}{W \cdot No} \right)$$

Rc/W is also known as spectral efficiency,  $\rho$ . As the pulse rate Rc goes low, the efficiency drops due to the lower usage of bandwidth (degree of freedom). However, this provides some extra gain,  $1/\rho$ , to input Eb/No.

The gap between input SNR and detection Eb/No (10 dB in BPSK) should be compensated for by the DSSS technique, i.e. PN spreading. In other words, one information bit spreads over several pulses or chips. For example, if the gap is 20 dB, the system will require a hundred PN chips. Consequently, the data rate is a function of pulse rate and processing gain. When the required processing gain is not larger than unity, the data rate is equal to Rc, pulse rate.

$$Data\_rate = \frac{Rc}{num\_PN\_chips}$$

Therefore, given a fixed input SNR, if Rc is halved, the processing gain required will also be halved as long as it is still larger than unity such that the data rate remains the same. Note that in order to keep the same input SNR, the pulse energy should increase by the same ratio as Rc is decreased. This will keep the power spectral density the same. FCC regulates UWB emission according to power spectral density profile, which will be discussed in the next section.

So far, we have already gained enough background for thinking about how to maximize the throughput: PPM modulates the information on the pulse position within one pulse repetition period. The longer the repetition period, the more positions can be used for modulation. Plus, when we decrease the pulse rate, the required processing gain is also less (because the energy per pulse could scale up proportionally to keep the same power spectrum density). Therefore, in order increase the throughput, one should reduce the pulse repetition rate, and do biorthogonal signaling on the positions within the period. The optimal throughput would be achieved when the required processing gain is equal to unity.

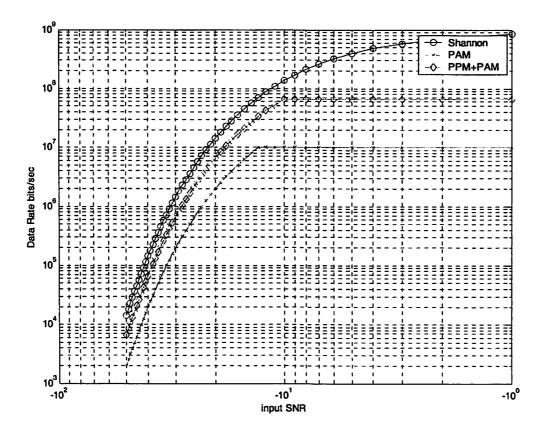

Figure 2-1 shows the relationship between input SNR and throughput using different modulation schemes. The pulse rate was 10 MHz and Shannon capacity here is simply using AWGN channel model. Note that as the input SNR goes higher than a certain level, the data rate saturates. The reason is that no process gain is needed beyond that point, where the optimal throughput is achieved at that particular input SNR. If we keep reducing the pulse rate, the saturation point will move towards lower input SNR.

Figure 2-1 Modulation schemes affect input SNR v.s. throughput

# 2.3 Power Spectral Density

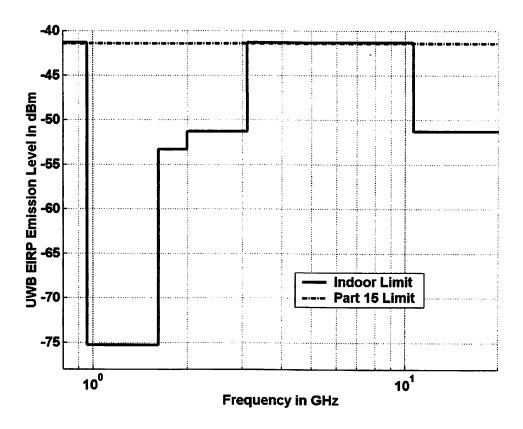

From the previous section, we learn that one should increase the pulse energy while decreasing the pulse rate in order to enhance capacity. However, the power spectral density is regulated by the FCC [FCC02]. Figure 2-2 shows the emission limit for indoor systems. Therefore, one has to reduce any spikes in the frequency domain.

Since the pulses are sent periodically, it could be expressed as,

$$s(t) = \sum_{n} an \cdot p(t - nT)$$

The power spectral density of these pulse train is the Fourier transform of the autocorrelation function of s(t), and could be expressed as,

$$\Phi(f) = FT\{Rss(t)\} = \frac{\sigma_a^2}{T} |P(f)|^2 + \frac{\mu_a^2}{T^2} \sum_{n=-\infty}^{\infty} |P(\frac{n}{T})|^2 \delta(f - \frac{n}{T})$$

P(f) is the Fourier transform of p(t). From the equation, one has to decrease the mean of  $a_n$  in order to suppress those spikes. If the spectral density is flat, then the transmission power can be maximized under the FCC regulation. This is another reason we introduce a pseudo random code to modulate with pulse amplitudes if PAM is used. Furthermore, these frequency spikes could be flattened even more if a pseudo random code is modulated on the position of pulse train (PPM).

Figure 2-2 FCC regulation on indoor systems

# **Chapter 3 System Specification**

# 3.1 Introduction

This chapter will go through the determination of system specifications, including the number of PN chips, detection threshold, and effect of finite word length. The work has been done via hand calculation and Monte-Carlo simulation.

#### 3.2 Detection Rule

From a communications point of view, the receiver is essentially a binary detection problem or two hypotheses testing given the BPSK modulation scheme. At the transmitter side, it sends "one" or "zero". During the synchronization mode, "one" means the presence of the signal while "zero" means absence. During data recovery mode, "one" and "zero" represent the information bit "one" and "zero" individually.

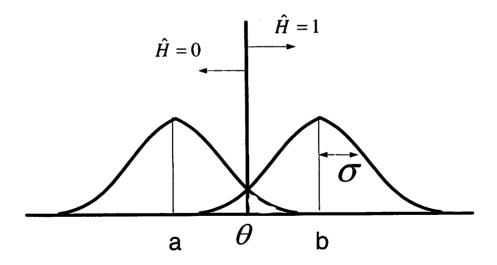

Figure 3-1 Binary detection for signal plus noise

Shown in Figure 3-1 is an illustration of the probability profile for two hypotheses testing. If "one" is sent, the detector will have value b. However, additive noise adds to the error probability. Here, we assume the noise is white and Gaussian, which is the worst-case scenario. Therefore, in UWB communication, the total power of interferers is approximated with a Gaussian noise of same power. The error probability is categorized as follows:

$$Pr(\hat{H} = 1 | H = 0)$$

False alarm probability;

$Pr(\hat{H} = 0 | H = 1)$  Miss detection probability:

The area under the little triangular area shown in Figure 3-1 is exactly the error probability. Now, the problem is how to set the detection threshold to minimize the aggregate error probability or any cost function of the system. Several detection schemes are commonly used. They are MAP detection, ML detection and Neyman-Pearson Test for optimizing a certain cost function [Tse01]. A generic detection problem setup is observing a random vector Y, and makes the best guess on the transmitted signal, H.

#### MAP DETECTION

The maximum a posteriori probability (MAP) rule is to maximize the probability of guessing correctly. The rule may be written as a mathematical equation:

$$\hat{H}(\vec{y}) = \arg\max_{i} [P_{H\vec{y}}(i \mid \vec{y})]$$

$$\Rightarrow \Lambda(\vec{y}) = \frac{P_{\vec{y}|H}(\vec{y}|1)}{P_{\vec{y}|H}(\vec{y}|0)} \ge \frac{P_0}{P_1} = \eta$$

MAP detection assumes the detector knows the prior probability of sending "one" or "zero". Comparing the likelihood ratio,  $\Lambda(y)$ , to a certain threshold is called likelihood ratio test (LRT). Since the noise is Gaussian, we could replace the likelihood ratio with an exponential function, and take logarithmic of both sides. Then we could get a formula

for detection threshold  $\theta$ . Whenever observation, y, is larger than  $\theta$ , the receiver will choose "one", and vice versa.

$$y \ge \frac{\sigma^2 \ln(\eta)}{b-a} + \frac{b+a}{2} = \theta$$

A slight deviation from the MAP rule is the Bayes test, which includes the cost function that the system may have. The MAP rule tries to minimize the total error probability. However, the false alarm and miss detection may cause different severity of penalty to the system. This is the reason why the Bayes test should be adopted. MAP rule suppresses both error probability to the minimum possible extent; however, it is possible to trade-off one of them while keeping the final cost function as small as possible. In UWB communication, this cost function could be acquisition time or power consumption. Once the cost function has been determined, one could set an optimal threshold.

Let Cij be the cost function of guessing i while sending j. Then Bayes test is:

$$\hat{H}(\vec{y}) = \arg\min_{i} [C_{i0}P_{H\vec{y}}(0|\vec{y}) + C_{i1}P_{H\vec{y}}(1|\vec{y})]$$

$$\Rightarrow \Lambda(\vec{y}) = \frac{P_{\vec{y}|H}(\vec{y}|1)}{P_{\vec{y}|H}(\vec{y}|0)} \ge \frac{P_0(C_{10} - C_{00})}{P_1(C_{01} - C_{11})} = \eta$$

#### ML DETECTION

Similar to the MAP detection rule, but when the prior probability is unknown; the best thing that the receiver could do is simply depend on the maximum likelihood ratio,  $\Lambda(y)$ .

If  $\Lambda$  is larger than one, then receiver guesses one and vice versa.

#### Neyman-Pearson Test

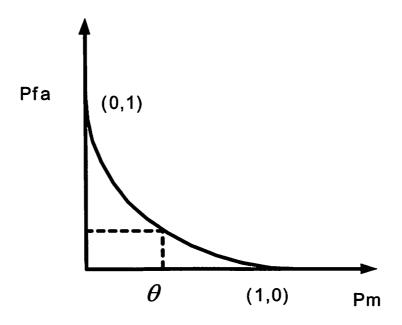

This is similar to the Bayes test except the prior probability is unknown. The Neyman-Pearson test fixes an upper bound for either one of the error probabilities, because one of them may have a much higher cost than the other one. For example, if the miss detection probability has a certain upper bound,  $\theta$ ; the problem is how to minimize the false alarm probability. It turns out that LRT is still the best rule to use. From LRT, if we vary the detection  $\eta$ , we could draw a tradeoff curve between miss detection and false alarm, Figure 3-2. When  $\eta$  is zero, Pfa is always one, and vice versa. Since Pm is bounded by  $\theta$ , in this case. We should sweep  $\eta$  from infinity to zero until Pm meets the bound. Then the LRT based on this  $\eta$  is the optimal detection rule.

Figure 3-2 Neyman-Pearson Test

# 3.3 Derivation of Received Signal Statistics

Before we could really apply those detection rules described in the previous section, one needs to know the statistics of the received signal, i.e. mean and variance if the noise is

Gaussian distributed In other words, a, b and  $\sigma$  has to be determined. So as to prior probability P0 and P1, it's optional to the designer. In UWB, this prior probability depends on the pulse rate and sampling window size during the acquisition mode. If it is not that obvious what the prior probability is, one could simply use those detection rules without prior knowledge. To calculate a, b, and  $\sigma$  is the topic of this section. Let's start from the infinite precision case and then examine 1-bit quantizer case.

Before we go, some parameters are used in the following derivation.

N: number of PN chips

L: number of matched filter taps

Si: ith sampled value from quantizer

Pi: ith coefficient of matched filter (Pi=Si, if matched filter is perfect)

Eb: signal energy

$\sigma_n$ : square root of noise power

Corr: final correlation output assuming totally synchronized

#### Infinite precision

The final stage correlator output, Corr, could be written as follows:

$$Corr = \sum_{i=1}^{N} \sum_{j=1}^{L} (Sj + nj)Pj$$

The 1<sup>st</sup> and 2<sup>nd</sup> moment of the random variable, Corr, could be derived very straightforwardly:

$$E(Corr) = N \sum_{j=1}^{L} (Sj \cdot Pj)$$

$$Var(Corr) = E((Corr - \overline{Corr})^{2}) = N\sigma_{n}^{2} \sum_{j=1}^{L} Pj^{2}$$

The mean of Corr will be equal to (N\*Eb) as long as Pi is Si, i.e. a perfect matched filter. Therefore, the output SNR at this perfect situation is:

$$SNR_{out} = \frac{[E(Corr)]^2}{Var(Corr)} = N(\frac{Eb}{\sigma_n^2}) = N \cdot SNR_{in}$$

This equation tells exactly how DSSS could help the system performance. The SNR is proportional to the number of chips.

#### ONE BIT QUANTIZER (SLICER)

As the quantizer moves from infinite precision to lower precision, the impairment to the system could be modeled as another additive white Gaussian noise source (quantization noise). As it is eventually reduced to 1-bit quantizer, the system will become nonlinear. A more detailed derivation of mean and variance values is required.

-Calculate ||a|| (only AWGN noise existed):

$$Corr = \sum_{i=1}^{N} \sum_{j=1}^{L} sign(nj)Pj$$

$$E(Corr) = N \sum_{j=1}^{L} (E(sign(nj) \cdot Pj = 0 = || a ||$$

-Calculate ||b||

$$E(Corr) = N \sum_{j=1}^{L} (E(sign(Sj + nj) \cdot Pj)$$

$$E(sign(Sj + nj)) = 1 \cdot \Pr(nj \ge -Sj) + (-1) \cdot \Pr(nj < Sj)$$

$$\Pr(nj \ge -Sj) = Q(\frac{-Sj}{\sigma_n})$$

$$\Rightarrow Q(x) = \int_{x}^{\infty} \frac{1}{\sqrt{2\pi}} \exp(\frac{-z^2}{2}) dz$$

$$\|b\| = N \cdot \sum (Q(\frac{-Sj}{\sigma_n}) - (1 - Q(\frac{-Sj}{\sigma_n}))Pj = N \cdot \sum (2 \cdot Q(\frac{-Sj}{\sigma_n}) - 1)Pj$$

-Calculate Var(a)

$$\sigma_a^2 = E(N \sum_{j=1}^{L} E(sign^2(nj)) \cdot Pj^2) = N \sum_{j=1}^{L} P_j^2$$

-Calculate Var(b)

$$\sigma_{b}^{2} = E(\sum_{i=1}^{N} \sum_{j=1}^{L} [(sign(Sj + nj)Pj - \overline{sign(Sj + nj)Pj})^{2}]$$

$$= \sum_{i=1}^{N} (\sum Pj^{2} - \sum \overline{sign(Sj + nj)Pj}^{2}) = N \cdot [\sum Pj^{2} - \sum ((2 \cdot Q(\frac{-Sj}{\sigma_{n}}) - 1)Pj)^{2}]$$

So far, ||a||, ||b||, Var(a), Var(b) have been derived. These values correspond to the binary detection plot shown in Figure 3-1.

# 3.4 Processing gain and Threshold Determination

Given the input statistics, we've already gained enough information to determine the number of chips required and the detection threshold. They are all related to each other.

The first thing to do is to decide what the error probability is targeted. This probability has a slightly different meaning in the two operational modes. In tracking mode, this error probability is translated into BER. Since the modulation scheme is BPSK, the output SNR could be determined by looking into waterfall curve given a certain BER. The output SNR can be expressed as,

$$SNR_{out} = \frac{\parallel b \parallel^2}{\sigma_b^2} = f(N, Sj)$$

Therefore, given a certain waveform, one could decide the number of PN chips that the system requires. This detection rule is simply doing sign detection, in other words, the threshold equals to zero since the transmitted signal is either one or negative one.

In acquisition mode, the probability of error means missing detection or false alarm. The error probability depends on the detection threshold, number of PN chips and pulse shape. If one wants to keep the same error rate as tracking mode, usually it requires double PN chips because the system has to choose between one and zero, instead of one and negative one. In other words, the Euclidean distance is halved. The determination of miss detection or false alarm probability should depend on the cost function of the system, such as average acquisition time, which will be described in the next chapter. In the baseband design, we keep the threshold programmable by the user so that we can test out different detection rules.

#### 3.5 Monte-Carlo Simulation

If we constraint ourselves to hide the UWB pulse spectrum under the thermal noise floor, the peak value of UWB pulse in time would be comparable to RMS value of the noise floor.

For the worst case of doing synchronization, we first treat thermal noise and interferers as white Gaussian noise, which is proved to be the worst-case scenario for the capacity of a channel. Therefore, we measure the power spectrum received by the receiving antenna that we are going to use in the Lab. And sum up the total noise power over the interested band, as the variance of white Gaussian noise.

As we mentioned in the previous section, for reliable communication, BPSK requires a 7dB input Eb/No for BER of 10^-3. However, in order to keep the acquisition error probability at roughly the same level, one needs 3 dB more signal energy. In allowance for a safe margin, the targeted output Eb/No is set to be 10 dB. Therefore, (10dB - input Eb/No) is the extra processing gain required by using DSSS. Once we have the worst-case input Eb/No, then the maximum PN chips required for the baseband will be determined as well.

Running the BER simulation for a monopole antenna and testing for 50000 information bits, the signal energy, Eb is equal to 3.6727e-16 (V^2), which corresponds to a peak of 1mv. From the oscilloscope, the noise plus interference floor is mostly around 10 mV. That is, we transmit the signal underneath the thermal noise floor, which should be under the sensitivity of most narrowband systems. The noise power is measured from spectrum analyzer, and we found the noise power density is around -70dBm/MHz. Therefore, the Eb/No used in this Monte-Carlo simulation is -11.34 dB. Table 3-1 shows how precision of PMF and number of chips affect BER.

Another long run simulation for miss detection and false alarm probability has been done in Table 3-2 assuming receiver could lock the signal once it's present. There, we simply set the threshold to be the middle point of ||a|| and ||b|| in order to get an idea of how system performs. As described in detection rule, one could optimize the performance even more by tuning the detection threshold.

| Chips | BER(perfect pmf) | BER(5-bit pmf) | BER(3-bit pmf) |

|-------|------------------|----------------|----------------|

| 1     | 0.38             | 0.3424         | 0.3842         |

| 10    | 0.165            | 0.1663         | 0.1849         |

| 100   | 0.0011           | 0.0011         | 0.0069         |

| 200   | ~0               | 2e-5           | ~0             |

| 1000  | ~0               | ~0             | ~0             |

**Table 3-1 BER simulation**

| Chips | False alarm rate | Miss detectoin rate | EbNo@ detection |

|-------|------------------|---------------------|-----------------|

| 300   | 0.0041           | 0.0037              | 14.4245 dB      |

| 400   | 0.0013           | 0.00086             | 15.6643 dB      |

Table 3-2 Probability of error simulation in acquisition mode

If we start from input Eb/No ~ -10dB, the simulation shows that 400 chips are needed to suppress the miss lock rate below 1e-3. Once the signal gets locked, then we could

simply apply BPSK, meaning we could reduce the required spreading gain to 100 chips. The reason why false alarm probability is higher than miss detection is because the variance of noise-only inputs is larger than that of signal plus noise inputs, which matches to the hand calculation.

### 3.5 Finite Word Length

Up to this point, we have specified the input signal to be 1-bit and the PMF coefficients 5-bit wide. And we are summing 128 5-bit numbers in PMF while correlating over a maximum of 1024 chips. If we do not have the prior knowledge about the input statistics, one needs a (5+7+10)=22-bit precision at the correlator output in order to prevent overflow.

Since we have already derived the input statistics in section 3.3, we should be able to save some hardware. Usually we use the three-sigma rule for finite word length determination. Equivalently, if the signal on a certain node has a standard deviation,  $\sigma$ , the finite word length should keep a range of +3 $\sigma$  to -3 $\sigma$ . The probability of overflow will be kept to less than 1% given a Gaussian distribution. For those who are interested in more details in finite word length effects, [Shi02] is a good reference.

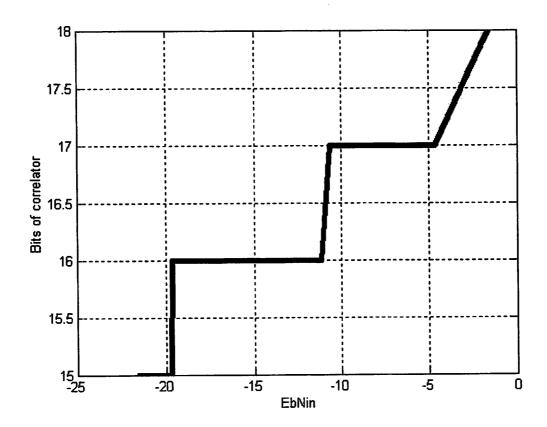

Input statistics (mean and variance since we assume a Gaussian distribution) depends on pulse shape, the number of chips and the input SNR. Under the three-sigma rule and with a PN length of 1024 chips, one needs 16 bits for the correlator and 6 bits for the PMF output with the input waveform previously used for BER simulation. However, it varies with the input noise level and pulse shape. Given the same pulse shape and BER, bit widths increase from 15 bits to 18 bits as the SNR increases, shown in Figure 3-3. Bit width does not increase too much over the input SNR variation. If input Eb/No is around -10 dB, the bit width is around 17.

Figure 3-3 Finite word length v.s. EbNin

However, if the received pulse shape changes, it will cause the most variation on the bit precision. Say the environment has more multipaths or the pulse width is wider, then the bit width could grow to 22 bits at most.

Since the simulated signal to noise ratio at the output is roughly 15 dB. The number of bits required at the PMF and PN correlator do not need to keep the full precision. Therefore, we could simply keep several MSBs at the output of PMF while not deteriorates the performance too much. Table 3-3 is the long run simulation for 100 chips. It shows 5 bits is enough given the pulse shape. Note there is a growing discrepancy between miss detection and false alarm owing to the fact that slicing the LSB of PMF outputs will make the value smaller than expected. In order to balance the two error probabilities, again, one could simply tune down the threshold. Here, the threshold is somewhat too large.

| Bits @ PMF | BER    | Miss detection | False alarm |

|------------|--------|----------------|-------------|

| output     |        |                |             |

| 8          | 0.0018 | 0.0729         | 0.0699      |

| 7          | 0.0018 | 0.0777         | 0.0655      |

| 6          | 0.0019 | 0.0822         | 0.0624      |

| 5          | 0.0019 | 0.0934         | 0.0541      |

| 4          | 0.0023 | 0.1254         | 0.0415      |

| 3          | 0.0049 | 0.2267         | 0.0263      |

| 2          | 0.0513 | 0.7173         | 0.0069      |

Table 3-3 Finite word lengths at PMF output v.s. BER

# Chapter 4 Flexible UWB Baseband Design

#### 4.1 Introduction

This chapter will first give a brief system overview of the project, from transmitter through multipath channel, and analog frontend to the digital backend. A system simulation environment has been built in Simulink and will be discussed in Chapter 6. The emphasis of this chapter is designing a low power and flexible baseband. System parameters will be defined first as a basis for designing the UWB baseband. And then the most important issue, i.e. synchronization, will be brought up with a thorough discussion of operation modes, i.e. signal acquisition and data tracking, and how one could coordinate between the two. After understanding how the system synchronize, we will go through each functional block of the whole baseband, including the pulse matched filter, PN correlation block, peak detector, control logic, and data recovery block, etc.

# 4.2 Brief System Overview:

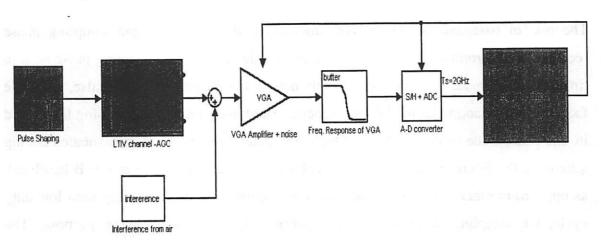

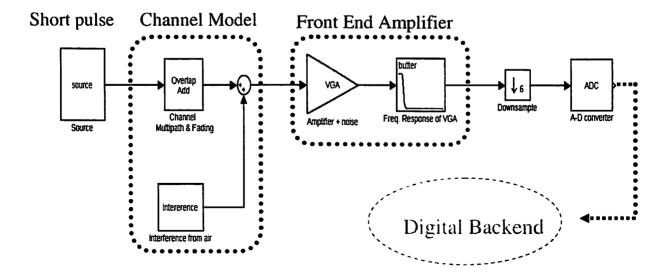

Figure 4-1 UWB communication System Overview

The architecture of this system is essentially a digital radio in the sense that the digital backend is brought to antenna as close as possible. Only amplification, filtering and quantization are left in analog frontend. Figure 4-1 shows the whole chain of UWB communication system. A UWB pulse is generated via a pulser and a wideband antenna. The pulse shape can be a Gaussian-like pulse or a monocycle one, depends on which type of antenna being used (current mode versus voltage mode antenna). The bandwidth of the pulse is from 10's of MHz to a couple of GHz range. Such a wideband signal goes through a multipath channel, which may distort the pulse shape but offers the possibility of using Rake receiving. Theoretically, due to the wideband signal, the resolvable paths should be more than narrowband signal, which implies more energy can be collected via Rake receiving.

The signal is received through antenna, then amplified by the LNA, gain stages and finally filter to reduce out of band noise or interference. And the signal is directly sampled at fairly high speed but low resolution. Current specification is aiming at a 2 GHz sampling rate, with 1-bit resolution, which is basically a zero crossing detection. At such a high sampling rate, there is no way to serially feed the data stream into digital backend in 2 Gbps rate. Therefore, the sampled data is buffered right after ADC stage, and feeds into baseband in a parallel array of 1-bit data at pulse repetition rate which may vary from 100 MHz to 1 MHz.

The role of baseband is mainly synchronization, data recovery and sampling phase feedback. Synchronization lines up the reference signal with the incoming pulse both in time and code phase. Data recovery simply detects the polarity of UWB pulse, given the fact that we use antipodal modulation scheme. Hard decision is the one going to be used in this version due to its simplicity. One could extend this to more sophisticated coding scheme in the future. Sampling phase feedback is a different feature of UWB baseband, as opposed to other DSSS ones. Because UWB pulse is sent periodically with low duty cycle, the sampling window activates periodically for power saving purpose. The

sampling phase feedback contains the information of when to activate the sampling window. More details will be covered in the later part of this chapter.

## **4.3 Flexible System Parameters**

In order to test and understand the capability of an impulse-based UWB system, the goal of this project is to build a flexible receiver. Flexibility in baseband includes the following items:

#### 1) Different random codes:

Different codes, such as Barker codes, Gold codes, Frank codes, etc, have their own cross-correlation properties. In terms of good acquisition, the Barker code has a very good cross-correlation, with sidelobe values less than or equal to 1/N in size and uniform distribution [Taylor00].

#### 2) Different length of codes:

From previous chapter, we know the length of code depends on how bad the environment is. If the interference is large, a long PN code will be needed. The worst-case is 1024 chips.

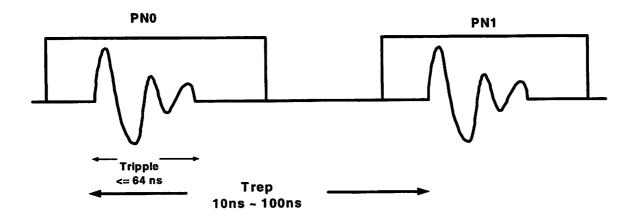

# 3) Pulse Repetition Rate $(1/T_{rep})$ :

The pulse repetition rate may range from 100MHz to 1 MHz. As the pulses are close to each other, the delay spread may overlap with the next chip pulse, which reduces the signal energy the receiver can capture given the topology we use and increases the inter chip interference. Also the periodical on-off type of receiving strategy can be no longer used. Instead, one has to always keep the radio alive all the time. The fastest pulse repetition rate depends on pulse duration. The shortest pulse duration we are targeting could be 10ns, which corresponds to 100MHz maximum rate.

## 4) Pulse Width $(T_{pulse})$ : < 16ns (32 samples)

The pulse width depends on pulser and antenna. If the pulse is Gaussian, then 1 GHz bandwidth corresponds to 2 ns half cycle pulse duration. Plus the duration between the first and second half cycle, the total length of UWB pulse estimated is around 10ns.

## 5) Pulse ripple length (Tripple): <= 64ns (128 samples)

The pulse ripple length is the length of received signal, which is the convolution response of pulse shape with multipath channel response. Some measurements of UWB channel response have been done in [Molisch02], [Scholtz98], [Foerster01] and [Rusch01]. The result shows the RMS delay spread of indoor environment is ranging from 20ns to 60ns. Most of the energy is within 100ns. Again, this delay spread depends on the setup of environment. However, we could still get a rough idea of how long the delay would be.

# 6) Sampling period:

The sampling rate is 2 GHz, due to the 1GHz bandwidth of UWB pulse. Therefore, the system samples at Nyquist rate, which preserves all the sufficient statistics for the digital backend. Recent research explored the possibility of doing sub-Nyquist sampling as shown in [Vetterli02]. Although it inevitably degrades the system performance by some degree, however, it may imply a simpler implementation for receiver. In this project, we still implement Nyquist sampling.

## 7) Sampling window length (Twin): <=128ns (256 samples)

In order to take advantage of repetitive sending pattern of UWB pulse, the sampling circuit should also be activated periodically. The baseband will search through all possible PN code phases given a certain sampling window phase. If no signal has been detected at the current sampling window phase, it will shift by a fixed amount of time offset, and then continue another cycle of the detection procedure.

To avoid losing the incoming signal, the amount of time in the sampling window has to be less than (Twin-Tripple). In this report, the time offset is referred as effective sampling window size,  $T_{weff}$ , because this is the effective time that has been searched through. The procedure of signal acquisition will be discussed more in the next section.

Figure 4-2 Target parameters of the system

# 4.4 Operation Modes (Synchronization):

The most important role of the UWB baseband is synchronization, which is composed of initial acquisition of the signal, and code tracking and the transition between the two. The synchronization mechanism is similar to a GPS receiver [Kaplan96] or a CDMA cellular system (IS-95), due to the usage of DSSS technology. The main difference is the absence of carrier in UWB communication. In narrowband system, like GPS, the acquisition and tracking is a two-dimensional (code and carrier) matching process. One has to consider the carrier frequency offset caused by Doppler effect or oscillator mismatch. Therefore, carrier recovery or frequency compensation could be ignored in UWB, which is one of the simplicities that UWB possess

In this section, we will discuss acquisition and tracking individually, and see how these could dramatically affect our circuit size. But before we dig into the details of synchronization, let's look at the receiver chain first.

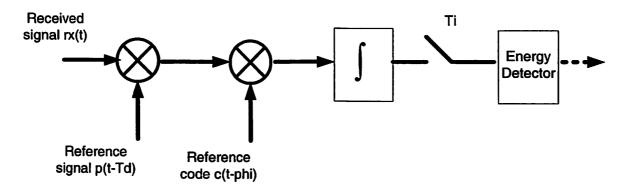

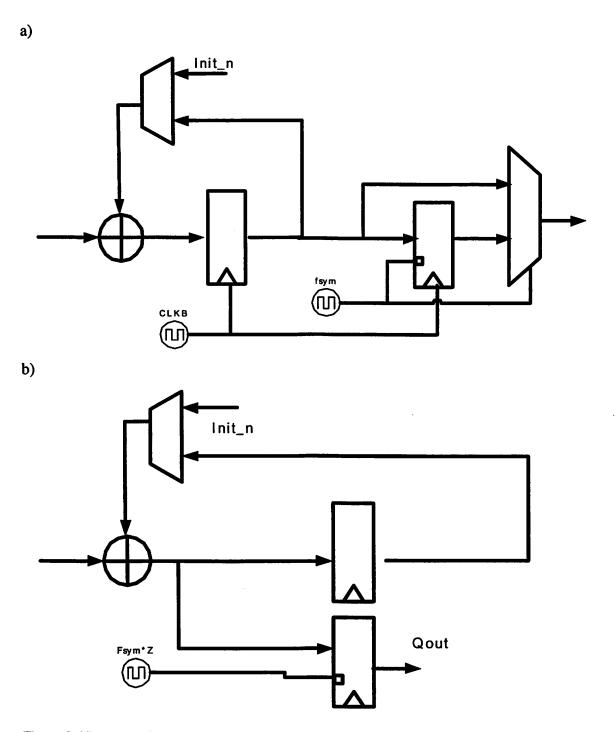

**Figure 4-3 Coherent Detector**

# 4.4.1 Receiving Chain:

Shown in Figure 4-3, is a conceptual flow of a coherent detector. Received signal  $r_x(t)$  is the signal captured by antenna. A UWB pulse, p(t), is generated at the transmitter and sent through the wireless channel, whose impulse response is h(t). Thus, rx(t) is equal to the convolution of p(t) and h(t), assuming the channel is a linear system. In a multipath environment, the pulse may be distorted, no longer maintaining the original shape. That is the reason we need to put extra efforts to do the pulse matched filtering, or adopt Rake receiving. This will be addressed later in pulse matched filter section.

Because the pulse goes through the wireless channel,  $r_x(t)$  has an unknown time delay and code phase. Time delay,  $T_d$ , is due to the physical propagation latency through the wireless channel, and unknown code phase,  $\varphi$ , is due the asynchronous property of any communication system. If the spreading code has a length of 1024, it will then have 1024 possible code phases. Therefore, as the length of spreading code gets longer, the more time it will be required to get synchronized. After two de-spreading mixers, the signal integrates over a period of time,  $T_i$ , also named as dwell time or correlation time. The integrated value will be compared with a threshold.

The first task of the receiver is trying to determine the existence of an incoming signal. If there is a signal, the correct time offset and code phase needs to be determined. As shown in Figure 4-3, the first de-spreading mixer is actually a pulse match filter, while the second one is a PN correlator. Therefore,  $T_d$  will be resolved via PMF, and PN correlators will help to determine code phase,  $\phi$ .

# 4.4.2 Acquisition Mode:

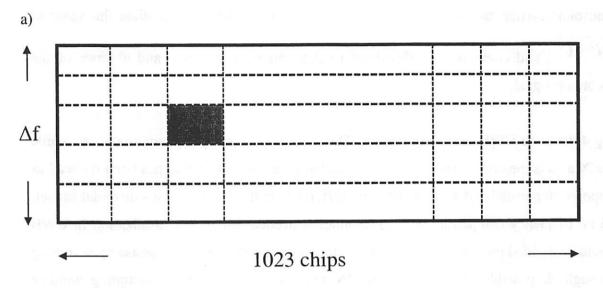

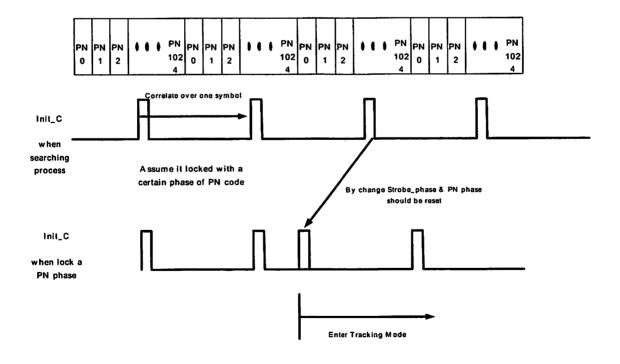

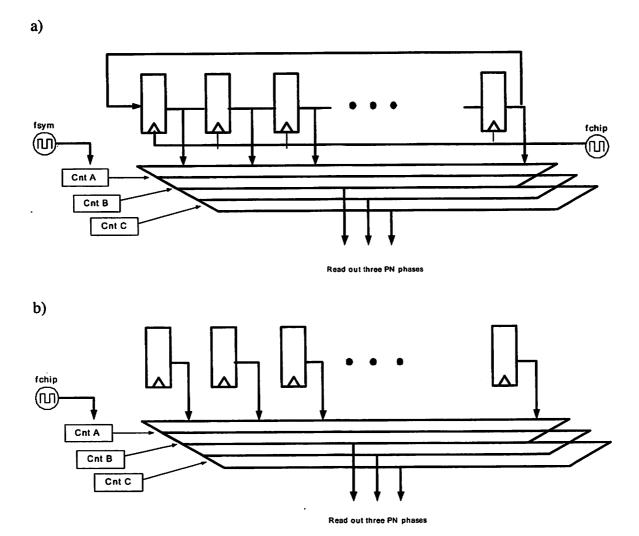

Figure 4-4 a) Gps system search pattern. b) UWB search pattern.

Acquisition is essentially a searching process. Shown in Figure 4-4a, is an example of the GPS 2-D searching pattern. The Y-axis is the carrier frequency, while the X-axis is the code phase. A GPS receiver has to search over all possible carrier frequencies along with

a certain code phase. Let's say the shaded cell is the actual receiving frequency and phase. The searching process begins with a certain cell, and then goes through all possible cells in some way, finally locking with the correct one via the detection threshold. Once the correlation value is above the threshold, then the receiver is assumed to be synchronized. In narrowband system, there are I and Q channels due to the use of sinusoidal carrier, therefore, an envelope detector is required to calculate the value of  $\sqrt{I^2+Q^2}$ , and compare to a threshold to determine the presence and absence of the incoming signal.

Fig 4-4b is the UWB searching pattern. The Y-axis is the sampling window phase, while the X-axis is the code phase. The effort needed to acquire the signal has been reduced as opposed to narrowband system. The key difference is the absence of a sinusoidal carrier, so no frequency compensation or Q channel is needed. Initial synchronization in UWB could be divided into two steps. The first step is to find the right code phase by searching through all possible orderings of the PN sequence given a certain sampling window phase. After locking the code phase, the second step is to find the sample that gives the peak energy within the sampling window. If we draw an analogy to narrowband synchronization, the first step is like coarse timing recovery, while the second one is fine timing recovery.

Several acquisition schemes are used in DSSS technique: serial searching and parallel searching [Ziemer85]. And then a hybrid version of the two will be used in this project due to the limited die size.

## **4.4.2.1 Serial Searching Scheme**

The most commonly used scheme is a serial search. Basically, the receiver serially evaluates each cell, shown in Figure 4-4, until the correct one is found. The different code phase is due to the different time that receiver begins to listen. Therefore, the probability of each code phase is assumed to be equal, a uniform distribution. Uniform distribution implies that no matter which phase you begin with, or which searching pattern will be

used, the acquisition time should be the same on average. That is the reason, in this project, the search pattern is simply one chip delay offset between any two subsequent cells. The receiver goes through every cell in the row, and repeats the same sequence if all the cells are dismissed, i.e. no signal is detected.

Besides the sequential searching pattern, other important issues are how to determine UWB signal is present or absent within a cell, and when to dismiss a cell and move into the next one. Three different schemes are usually used in serial search technique.

## 1) Fixed correlation time detector

This method fixed the correlation time or dwell time,  $T_i$  shown in Figure 4-3. The integrated signal is compared to a fixed threshold  $V_t$ . If the value is above  $V_t$ , the signal is regarded present, and absent otherwise.

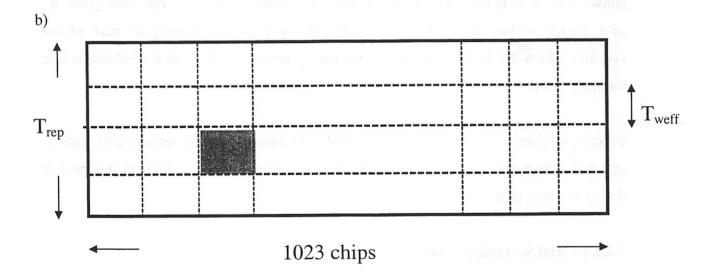

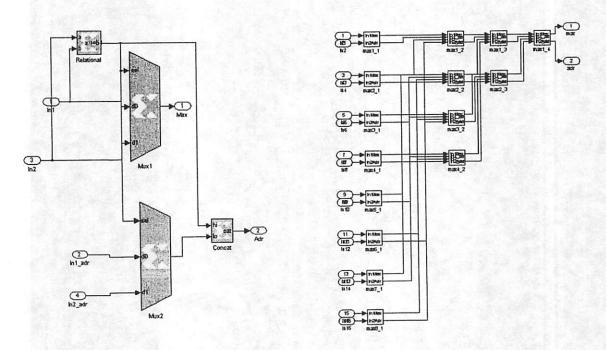

## 2) Multiple-dwell detector

As opposed to fixed correlation time, one could do something smarter than using only Ti and V<sub>t</sub> as the system parameters, which affect detection probability and average acquisition time, etc. The synchronization process is essentially trying to locate the signal-presented cell and reject all other noise-only cells. Therefore, we don't need to put equal amount of efforts into every cell. Instead, one could reject most of the cells rapidly using shorter correlation time, T1 shown in Figure 4-5, and then turn into the second round of re-evaluation to reduce the false-alarm probability with a longer correlation time, T2, and so on so forth until the final Pfa is satisfactory. It can be shown that the average acquisition time goes down by choosing several different length of integration time (PN sequence). After the system gets locked, it enters tracking mode. The data detection is based on correlation (T3, Vt3). To avoid miss detection, it adds another longer correlation (T4, Vt4), because the penalty of miss detection is serious (system has to go through all searching procedures). The detection flow is shown in Figure 4-5. Some modifications could be made to detection flow, like miss detection of correlation (T2, Vt2) can be connected back to correlation (T1, Vt1) instead of assigning new code phase.

Figure 4-5 multiple-dwell detection flow

## 3) Sequential detector

The idea of doing sequential detection is to calculate the logarithmic likelihood ratio of every de-spreading sample instead of integrating over a certain period. After de-spreading mixers, the samples are \$1, \$2, ..., \$n, and the likelihood ratio of detection is as follows:

$$\Lambda(s1, s2..., sn) = \prod_{i=1}^{n} \frac{Ps(si)}{Pn(si)}$$

Ps is the probability of presence of signal plus noise, while Pn is the probability of the noise-only case. If  $\Lambda$  is greater than one, one will have more confidence to claim that signal is present than absent. In a sequential detector, there are two thresholds, HI and LO. If  $\Lambda$  is above HI, the signal is assumed to be acquired, similarly, when  $\Lambda$  is lower than LO, the system will dismiss the current cell and move into the next one. However,

this technique requires more complex computation, log function, which has to be taken into account.

## **4.4.2.2 Fully Parallel Searching Scheme**

## 1) Correlator based

A fully parallel searching scheme is similar to the serial searching scheme, except the system searches all of the cells at the same time. By using the same receiver structure, one simply duplicates the correlators in order to search all possible code phases at the same time. Not hard to imagine, this trades-off a lot more circuit size with the fastest possible acquisition time.

## 2) Matched-filter based

The output of the correlator, y(t) could be written as a linear function of input signal, x(t) and code phase c(t),

$$y(t) = \int_{0}^{\tau_{i}} x(t) \bullet c(t) dt$$

The equation is essentially the same with a linear filter response, except the time-reversed filter response,

$$y(t) = \int_{0}^{t} x(\tau) \bullet c(t - \tau) d\tau$$

The similarity gives us a hint that the implementation of a correlator could be replaced with a filter whose response is the time reversed code sequence. The biggest advantage is that the MF continuously correlates the input sequence with an expected spreading code sequence. It outputs a new correlation value whenever a new sample comes in. It will generate a maximum value whenever the incoming signal coherently matches with the code phase. Over the period Ti, the MF equivalently searches over all the possible code

phases, which is fully parallel searching scheme. Therefore, as long as the speed of data stream is not prohibitively too fast, MF is a very promising method of doing acquisition.

## 4.4.2.3 Hybrid Searching Scheme

This design decision comes along with the trade-offs between the chip size and acquisition time. One could achieve the fastest acquisition time using a fully parallel design. In a correlator-based, fully parallel design one could either duplicate correlators for each code phase or adopt time sharing technique to reduce the chip size. But in terms of keeping the flexibility of pulse rate, we didn't use any time-sharing technique so that we could push to the limit of the communication speed. On the other hand, if we use a MF acquisition scheme, the filter has to run at the sample rate, i.e. 2GHz. Of course, it is still impractical in the current CMOS technology and also has too much power consumption. As a result, we adopted a correlator-based design in UWB baseband.

For detection, a fixed correlation time detector is used for the ease of testing and design. Given this scheme, the length of the PN sequence and the threshold setting have been determined in the previous chapter. They are all related to the system specification, such as BER, false alarm probability, etc.

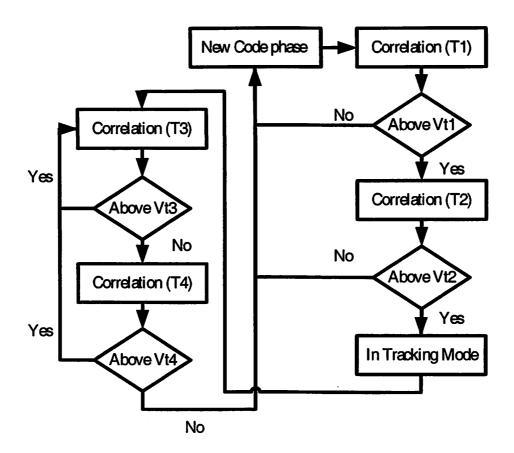

A hybrid searching scheme, i.e. duplicate correlators for several cells (code phases) searching simultaneously, can be adopted in the acquisition as opposed to serial or fully parallel searching strategy. Thus, we could get a compromise between the acquisition time and chip size. The tradeoff compromise is made using the first order acquisition time estimation and chip area estimated by Module Compiler.

# Acquisition Time v.s. Hybrid Strategy

The mean acquisition time is a function of the probability of detection, Pd, probability of false alarm, Pfa, number of parallel searching cells, and length of PN sequence. It is a bit complex since many parameters are involved. Let's focus on the worst-case acquisition

time given the Pd and Pfa are zero in order to get a quick idea of how fast the system could get locked. The parameters are (please refer to section 4.3 for more details):

N: length of PN code;

M: number of code phases being searched simultaneously;

T<sub>rep</sub>: pulse repetition rate;

Tweff: effective sampling window period;

Ts: sampling period;

$$Tacq\_worst = N \bullet \left[\frac{Trep}{Tweff}\right] \bullet \frac{N}{M} \bullet Trep$$

$$Tacq\_ave = \frac{Tacq\_worst}{2}$$

The average acquisition time is half of the worst-case time given the assumption that the probability distribution of each searching cell is uniform. If the distribution is not uniform, one should start from the most likely cell and then spread out from the center of the mean value so that the average acquisition time is reduced.

Certainly, it's possible to derive a more accurate equation considering more parameters to a first-order analysis.

$P_{\text{false}}$ : false alarm probability;

T<sub>false</sub>: extra time required to reject the cell when a false alarm happens;

$P_{miss}$ : miss detection probability;

$C_{total}$ : total cells on 2D searching matrix (=  $T_{rep}/T_{weff}*N$ );

Ti: correlation time (= $N*T_{rep}$ );

$$Tacq\_ave = \frac{Ctotal \bullet Ti}{2M} + \sum_{j} Ctotal \bullet Ti \bullet j \bullet Pmiss^{j} (1 - Pmiss) / M + Tfalse \bullet \sum_{k} {Ctotal \choose k} \bullet Pfalse^{k} (1 - Pfalse)^{Ctotal - k}$$

A more accurate acquisition time analysis can also be done; however, it's already beyond the scope of this thesis. Some analysis has been done using Markov model, [Holmes77] [Simon94]. The first order estimation is good enough for making design decisions, and more exploration with different algorithms could be done in the future.

## Size v.s. Hybrid Strategy

The amount of circuit required is estimated using Module Compiler. In chapter 5, we will dig into more details. In order to investigate how hybrid strategy could affect the chip size, the area report for each fundamental slice was done in MC. For example, we get the area for one correlator, and then assume the area scales up proportionally with the number of correlators we put on the chip. Thus, the total transistors on the chip could be parameterized by number of simultaneous searching cells.

#### Simulation Results

The design decision has been made using the first-order average acquisition time analysis and size reports from MC. The question is simply how many correlators we could fit on chip, given the PMF is taking 256 samples, which corresponds to a sampling window of 128 ns.

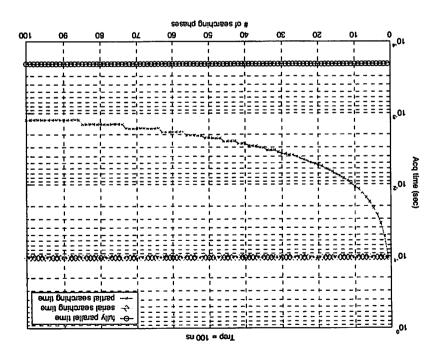

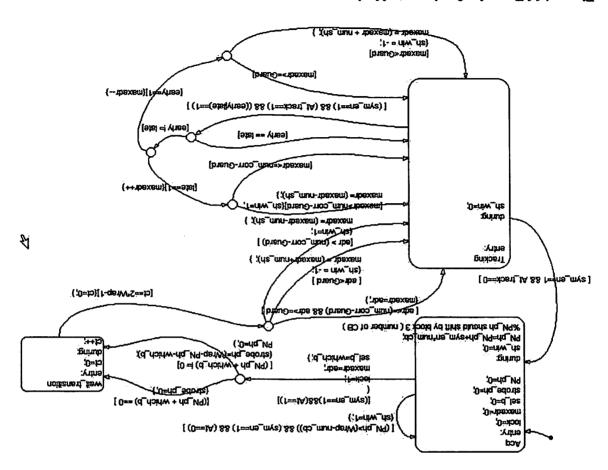

Figure 4-6a shows a fully parallel searching scheme will only require 0.1 ms, given the pulse rate ( $T_{rep}$ ) of 10 MHz. A serial searching scheme gives a 0.1 second acquisition time. The effect of the acquisition time affects the QoS of the communication network, the target here is trying to achieve as fast as possible acquisition time given a reasonable area cost.

Figure 4-6 a) Acquisition time v.s. searching phase b) Size v.s. searching phase

(q

y)

Figure 4-6b shows 500 mm<sup>2</sup> chip size is required for fully parallel correlator based acquisition scheme, while serial searching takes only 5.8 mm<sup>2</sup>, roughly a hundred times smaller.

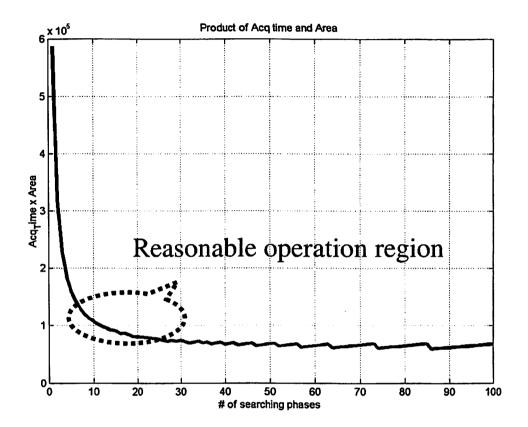

Figure 4-7 Product of acquisition time and area

If we consider only the tradeoffs between area and acquisition time,

Figure 4-7 shows that as searching phase goes beyond ten, the acquisition time saturates. Therefore, in our design, we chose eleven searching phases, which corresponds to eleven correlation blocks. Under this design decision, the correlators and detection blocks together are nearly of equal size as the PMF block.

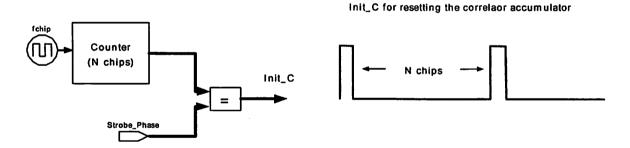

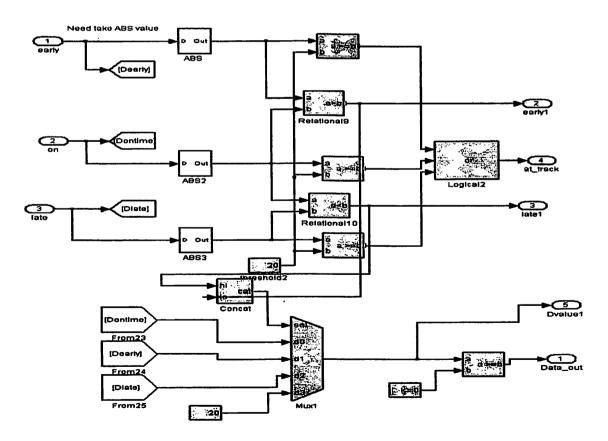

## 4.4.3 Code Tracking

Once the system passes the acquisition mode, it enters into the code tracking mode. During acquisition, the receiver has an estimated signal arrival time and code phase. However, due to the discrepancy of the transmitter and receiver clock frequencies, and movement of the user or environment, the signal arrival may drift over time. The previously estimated arrival time may be no long valid. Therefore, we need a mechanism to track the drifting of the signal, so called code tracking. The tracking strategy in this project is essentially early-late tracking, which will keep the reference signal within a fractional of chip period.

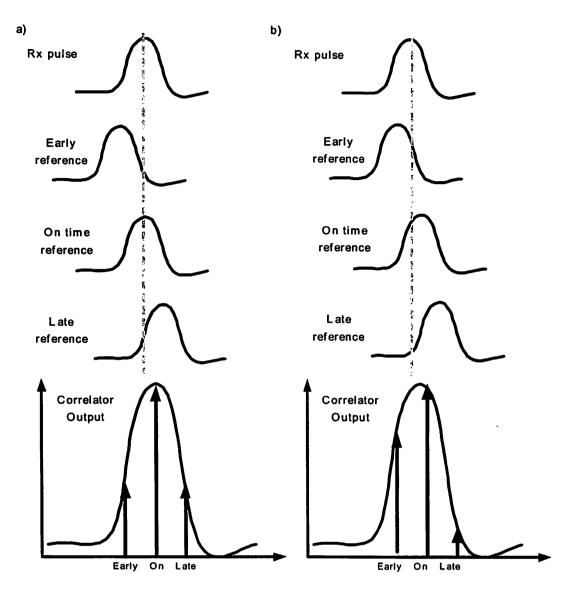

In order to track the direction of a drifting signal, let's first look at the autocorrelation function of the incoming pulse. In Figure 4-8, the received pulse is correlated against a reference signal with different time offset: on-time, early and late. After the correlator, the value of on-time correlation has the maximum value, while early and late correlation has smaller value (usually around half). If the received pulse matches the on time reference, shown in Figure 4-8a, the early and late correlation values are equal. As the received pulse drifts towards the early reference signal, shown in Figure 4-8b, the early correlation value starts to be larger than the late one. And the reference signal should be shifted back.

Figure 4-8 Early-late tracking profile a) Rx pulse matches on time phase b) Rx pulse comes earlier

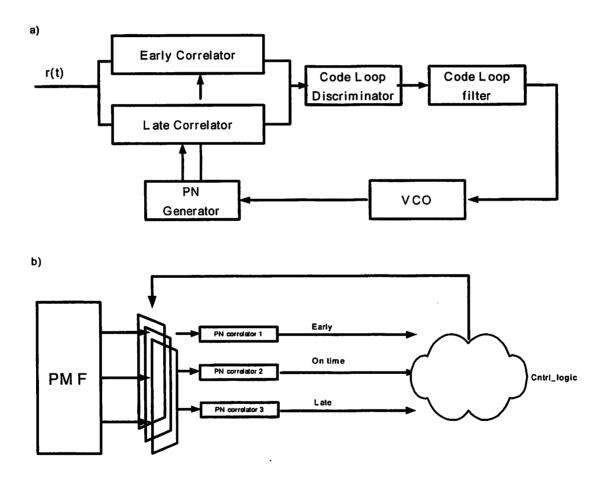

The performance of the tracking loop could be described bt the dynamic locking range and tracking jitter. Given the early and late correlation, somehow, we need to tell the direction of the drifting signal. In the code tracking loop of a DSSS system, this is done by a code loop discriminator, loop filter, VCO, and PN generator, shown in Figure 4-9a. It is essentially a DLL. Tracking range and tracking jitter are used to describe the loop performance. Tracking range is the maximum allowable input delay error that system could still trace back. And the tracking jitter is the variation of delay error due to the input noise.

Usually, the relationship between the delay error and discriminator output should be found first. Based on this relationship, one could correct the input signal by making use of discriminator output together with appropriate loop gain and bandwidth. The delay error should be subtracted from the original signal. This is the way a system could keep tracking the incoming signal with the reference within a close enough time value. Not surprisingly, different discriminator and loop filters will lead the system to different tracking performance. For more details, readers are referred to [Kaplan96].

Figure 4-9 a) DLL tracking loop b) UWB tracking loop

In UWB baseband, we don't drive the PN generator with a clock, since the PN sequence is stored in registers, not a shift register array. Instead of shifting the phase of PN

sequence by the VCO, we shift the reference signal by selecting a different set of outputs from PMF, because each output of PMF corresponds a specific timing phase. If the received signal comes before the on-time reference signal, the early correlation will be larger than late correlation. Note that the time duration of the UWB pulse autocorrelation function is at the nano-second range, which is quite small compared to a narrowband system. Given the same moving environment and oscillator instability, UWB system is more vulnerable to drifting. Since the time spacing between early and late correlators is much closer. As a consequence, if the control logic shifts the phase of an incoming signal whenever the early (/late) correlation goes beyond (/below) the on time correlation value, one should expect to see the selector goes back and forth frequently. Sometimes this may be caused by noise, inducing a false drifting alarm. A remedy to this problem is that the selector shift the phase of incoming signal when the early (/late) goes beyond the on-time value for N consecutive times. This way, the system moves the tracking phase only when it gains enough confidence. This method could reduce the tracking jitter; however, the tracking range will be decreased, since the tracking loop responds more slowly to the drifting, i.e. the loop bandwidth is narrower. Alternatively, we could do something like a discriminator. If we know the relationship between delay error and discriminator output, like for a narrowband system, we can use this information to determine how much the phase needs be shifted given a certain discriminator output. Since the tracking performance heavily depends on pulse shape and the channel response, we need to keep the tracking strategy flexible enough that we can play with it in the future testing. The method finally used in this project is to trigger the selector when early/late correlation goes beyond the on-time correlation for a consecutive N times, where N is a flexible parameter. Of course, N could be one, which gives the maximum loop bandwidth and worst jitter performance.

How do we choose the early and late samples? In narrowband system, the early/late points are usually chosen to be half of the chip time apart from the on-time point, so that the correlation value of early/late should be half of the on-time correlation value as in the perfect synchronized case. Indeed, it depends on the link budget of the system. The more SNR degradation is allowed for sampling, the farther it could be between the early and

late samples. In UWB, the spacing between early and late point depends on the pulse autocorrelation function. Since the pulse shape is still unknown, the spacing between the early / late will be another flexible system parameter that can be set externally.

Theoretically, in acquisition mode, the receiver could simply take one sample within a correlation period since the samples are all correlated within that lobe. However, the UWB pulse duration is so short that the autocorrelation profile is also very short and steep. If the receiver only looks at one or even two samples within that correlation lobe, they can be sitting at the bottom of profile. Certainly, we don't want to risk losing such a significant SNR. Therefore, we still look at all correlation samples at the Nyquist rate.

# **4.5 UWB Baseband Components**

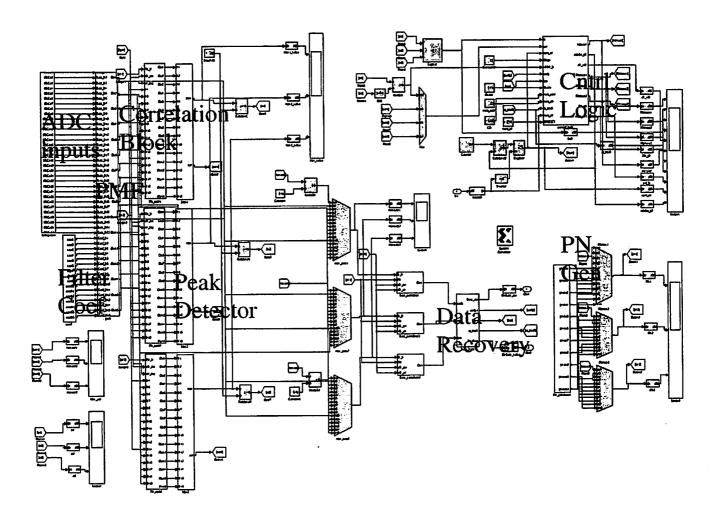

Figure 4-10 Baseband overview

Figure 4-10 is an overview of the whole system, which includes the pulse matched filter, correlation block, peak detector, control logic and data recovery block In this section, we

will go through the design of each block. The parallel inputs from ADC are the samples within a sampling window of 256 samples (128 ns) after buffering in the analog front end. The baseband will then try to demodulate the sending data out of these inputs.

## **4.5.1 Matched Filtering**

If the transmitted signal, s(t), is corrupted by additive white Gaussian noise, n(t), the optimal detection will be passing the received signal through a matched filter, whose filter response is h(t)=s(T-t) [Proakis00]. Thus, the output SNR obtained from matched filter will be maximized. If the input noise has a power spectral density of No/2 and transmitted signal has the energy of Es, output SNR of matched filter is Es\*2/No. Alternatively, from a signal space perspective, matched filtering could also be viewed as a projection onto the signal dimension, which will then transform the waveform detection into a 1-D detection problem [Tse01]. The signal dimension is where all signal information is contained. Therefore, by projection onto this direction, the receiver already rejects most of the noise, which is orthogonal to the transmitted signal. In other words, the SNR is maximized.

In UWB, the noise could be colored owing to narrowband interferers. The optimal receiving strategy is to whiten the noise first, and then apply the matched filtering. However, the whitening filter requires the prior knowledge of channel response, which complicates the current design. Therefore, we treat the noise to be white for now, and leave the whitening story in the future.

In this project, we did the matched filtering in the digital domain, therefore, the signal has to be sampled at least at the Nyquist rate, which preserves all the sufficient statistics for detection. If quantization could be infinite precision, i.e. no quantization noise, then the sampled version of matched filter should be exactly the same as analog matched filtering. Given the "undetectable UWB" scenario, the specification of the system is to do 1-bit

quantization of the receiving signal and the matched filter coefficient is 5-bit from BER simulation, which has been discussed in previous chapter.

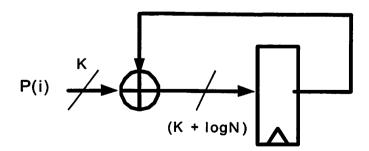

Up to this point, the implementation of the pulse matched filter block has become clear. In the maximum sampling window case, the sampled data from the ADC,  $\{S_1 \dots S_{256}\}$ , are fed into a parallel bank of FIR filters. Each FIR filter takes in 128 samples, multiplies with a 128-coefficient vector and sums up. The first FIR filter takes from  $S_1$  to  $S_{128}$ , and the second one takes from S<sub>2</sub> to S<sub>129</sub>, and so on so forth. The last FIR filter takes from S<sub>129</sub> to S<sub>256</sub>. As a result, each filter output is an outcome of doing matched filtering corresponding to a certain offset in time. The resolution of resolving T<sub>d</sub> is essentially the sampling time, i.e. 0.5ns, which is accurate enough for doing finer synchronization. In narrowband system, usually finer synchronization requires oversampling or interpolation, because the Nyquist sampling period is still comparatively large. The system SNR gets improved by doing so. However, in UWB, the Nyquist samples are already fast enough, there won't be too much improvement in an even finer resolution, like fractional of nanosecond. Therefore, in PMF, there are a hundred and twenty-eight 128-tap FIR filters with a sampling time offset between any two consecutive ones. The basic idea of PMF is shown in Figure 4-11. From the derivation of matched filtering, the more deviation between matched filter response and received signal, the more SNR loss it would cause to the system. In a time-invariant channel, once we get an accurate enough signal shape for the filter coefficients, the system essentially becomes a Rake receiver, which collects all multipath energy within a 64 ns range. It is certainly possible to modify the current system with some adaptive algorithms. Some initial thought about making an adaptive receiver is done in [ChenShi01]. There, they use the LMS algorithm and a training sequence to implement Rake receiving. MMSE detection is also compared in that report. More detailed studies of adaptive reception will require more knowledge about UWB channel modeling, which could be one of the interesting topics for future research.

Figure 4-11 Pulsed Matched Filter

## 4.5.2 Correlation Block

The PN correlators are used to offer enough processing gain in order to keep low BER. There are 128 outputs from the PMF, thus we need 128 correlators for one correlation block. Each correlation block is associated with one PN phase. During the acquisition mode, one correlation block will search one cell in Figure 4-4. In our hybrid acquisition mode, we need eleven correlation blocks so that we could search 11 cells per dwell time.

## 4.5.3 Peak Detector

The peak detector (energy detector in Figure 4-3) goes after correlation block. The goal is to select the maximum value out of these 128 correlation values, and compare it to a predetermined threshold set externally (threshold calculation is referred to chapter 3). If the signal does exist in any of these eleven cells, one of the peak detectors should output

"high". This is when the system ends acquisition mode. Besides selecting the maximum value, the peak detector needs to locate the correlator with the maximum value for data recovery.

Since the impulse response of an FIR filter is programmed to be the pulse shape convolved with channel response, all the signal information is contained in the peak value. However, one could also program the impulse response to be the pulse shape, thus the output profile of the correlation block becomes the channel response. The peak value is simply the strongest multipath. The better strategy is to collect all the multipaths, which is so called maximum ratio combining.

# 4.5.4 Data Recovery

Figure 4-12 Data recovery diagram