# Copyright © 2003, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# TOMOGRAPHY AS A METROLOGY TECHNIQUE FOR SEMICONDUCTOR MANUFACTURING

by

Michiel Victor Paul Krüger

Memorandum No. UCB/ERL M03/11

25 April 2003

# TOMOGRAPHY AS A METROLOGY TECHNIQUE FOR SEMICONDUCTOR MANUFACTURING

by

Michiel Victor Paul Krüger

Memorandum No. UCB/ERL M03/11

25 April 2003

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Tomography as a Metrology Technique for Semiconductor Manufacturing

by

## Michiel Victor Paul Krüger

Ingenieurs Diploma (Delft University of Technology, Netherlands) 1998

A dissertation submitted in partial satisfaction of the requirements for the degree of Doctor of Philosophy

in

Engineering - Mechanical Engineering

in the

GRADUATE DIVISION

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Kameshwar Poolla, Co-chair Professor Costas J. Spanos, Co-chair Professor Andrew Packard Professor John Strain

Spring 2003

## The dissertation of Michiel Victor Paul Krüger is approved:

Co-chair 04 - 18 - 2003

$\frac{1}{\text{Co-chair}} \frac{(.3.5)^2 A N O 5}{\text{Date}}$

Jule le Vole April 18 2003

Date

4/21/03

University of California, Berkeley

Spring 2003

# Tomography as a Metrology Technique for Semiconductor Manufacturing

Copyright Spring 2003 by Michiel Victor Paul Krüger

#### Abstract

Tomography as a Metrology Technique for Semiconductor Manufacturing

by

Michiel Victor Paul Krüger

Doctor of Philosophy in Engineering - Mechanical Engineering

University of California, Berkeley

Professor Kameshwar Poolla, Co-chair Professor Costas J. Spanos, Co-chair

This dissertation is concerned with exploring the feasibility of a class of sensors which provide temporally and spatially resolved wafer state information during semi-conductor manufacturing. The common theme shared by this class of sensors is that they are based on Electrical Impedance Tomography (EIT). EIT is a non-destructive in vivo imaging technique principally used in medical applications.

The basic idea of Electrical Impedance Tomography is to image the conductivity distribution in the interior of a conductive object by performing simple electrical measurements on the periphery of the object. In a semiconductor manufacturing context, physical and chemical effects during semiconductor manufacturing can induce a change in conductivity in the interior of a wafer. EIT techniques can be used to infer these conductivity changes. In turn, these changes can be related to the physical and chemical effects using appropriate models.

In this thesis, we first discuss the *status quo* of metrology methods in use in the semiconductor manufacturing industry. This discussion is followed by a thorough introduction to Electrical Impedance Tomography. We then argue that Electrical Impedance Tomography can be a compelling technique to obtain spatially and time-

2

resolved wafer state information during wafer processing. To illustrate these ideas,

we design and analyze two EIT based sensors for use during semiconductor manufac-

turing.

Our first sensor is a device to measure etch rates or film thicknesses. We have de-

signed, fabricated and tested this sensor. We use standard EIT techniques to estimate

the conductivity distribution of a thin film of conductive polysilicon across a wafer.

The estimated conductivity distribution can, in turn, be related to the thickness of the

polysilicon film from first principles. Differential thickness measurements from our

prototype etch rate sensor correlate very well with optical thickness measurements.

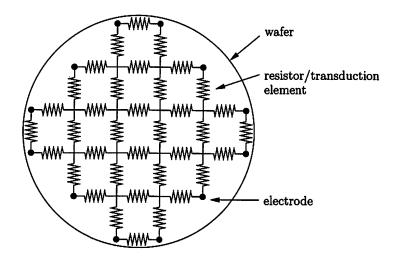

Next, we propose a novel EIT based sensor which can provide temporal and spatial

wafer surface potential information during plasma processing. Our design relies on

a resistive network containing discrete transduction elements whose conductivity is

modulated by the variable of interest. To assess our idea, we performed simulation

studies on a prototype sensor which uses depletion mode NMOSFETs as transduction

elements. We have obtained promising simulation results with this novel EIT based

metrology technique.

Professor Kameshwar Poolla

Kaneshin Poulle

Dissertation Committee Co-chair

Professor Costas J. Spanos Dissertation Committee Co-chair

[.3.11/1 NOS

To Michelle.

Charles Million and Carlo Charles

han be not sold to the minimal field.

- Marie Alexandro and Alexandro and Alexandro Alexandr

and the second s

A Prince of the Control of the Contr

The second se

and the supplication in appropriate control of the control of the

n di serangan seb<del>angan Kab</del>i Kabibe pin **bili**k b**i**k

# Contents

| Li | ist of | Figures                                          | v              |

|----|--------|--------------------------------------------------|----------------|

| Li | ist of | Tables                                           | viii           |

| Li | ist of | Symbols                                          | ix             |

| Li | st of  | Acronyms                                         | xi             |

| 1  | Intr   | oduction and Motivation                          | 1              |

|    | 1.1    | Introduction                                     | 1              |

|    | 1.2    | The Holy Grail of metrology                      | $\overline{2}$ |

|    | 1.3    | Our metrology approach                           | 3              |

|    | 1.4    | Related work summary                             | 4              |

|    | 1.5    | Contributions of this dissertation               | 5              |

|    | 1.6    | Thesis overview                                  | 6              |

| 2  | Sem    | niconductor Manufacturing Metrology: an overview | 7              |

|    | 2.1    | Semiconductor manufacturing                      | 7              |

|    | 2.2    | The role of metrology                            | 11             |

|    | 2.3    | Metrology: the status quo                        | 13             |

|    | 2.4    | Metrology: the future                            | 19             |

| 3  | Elec   | ctrical Impedance Tomography: an overview        | 22             |

|    | 3.1    | Operating principle                              | 23             |

|    | 3.2    | The governing equations                          | 24             |

|    |        | 3.2.1 The generic EIT experiment                 | 24             |

|    |        | 3.2.2 Notation                                   | 25             |

|    |        | 3.2.3 The continuum model                        | 25             |

|    |        | 3.2.4 Modeling assumptions                       | 27             |

|    | 3.3    | The forward problem                              | 28             |

|    |        | 3.3.1 Analytical solution                        | 28             |

|    |        | 3 3 2 Finite element modeling                    | 30             |

|   |      | 3.3.3  | Finite element example                               | 3 |

|---|------|--------|------------------------------------------------------|---|

|   |      | 3.3.4  | Simulation example                                   | 1 |

|   | 3.4  | The in | verse problem                                        | 5 |

|   |      | 3.4.1  | Degrees of freedom                                   | j |

|   |      | 3.4.2  | Parameterizing the conductivity profile              | 7 |

|   |      | 3.4.3  | Kriging                                              | 7 |

|   |      | 3.4.4  | Optimization                                         | ) |

|   | 3.5  | EIT e  | cample                                               | 2 |

| 4 | EIT  | based  | Sensors for Semiconductor Manufacturing 48           | 3 |

|   | 4.1  | The ba | asic idea                                            | ) |

|   | 4.2  | An ex  | ample                                                | ) |

|   | 4.3  | Three- | stage approach                                       | 2 |

|   | 4.4  | Design | and implementation issues                            | 1 |

| 5 | Etcl | n proc | esses in Semiconductor Manufacturing: an overview 57 | 7 |

|   | 5.1  | Etch p | processes                                            | 7 |

|   | 5.2  | Wet et | ching                                                | 3 |

|   | 5.3  | Plasm  | a etching                                            | ) |

| 6 | EIT  | based  | Etch Rate Sensors 62                                 | ? |

|   | 6.1  | Motiva | ation                                                | 3 |

|   | 6.2  | Relate | d work                                               | 5 |

|   |      | 6.2.1  | Optical methods                                      | 5 |

|   |      | 6.2.2  | Sensor wafers                                        | 7 |

|   | 6.3  | Etch r | ate sensor: design and operation                     | 3 |

|   |      | 6.3.1  | Wafer design                                         | 3 |

|   |      | 6.3.2  | Process flow                                         | ) |

|   |      | 6.3.3  | Experimental setup and hardware                      | L |

|   | 6.4  | Exper  | imental results: $XeF_2$ etchant                     | 2 |

|   |      | 6.4.1  | Wafer design                                         |   |

|   |      | 6.4.2  | $XeF_2$ etcher                                       | 3 |

|   |      | 6.4.3  | Experimental details                                 | 1 |

|   |      | 6.4.4  | Results                                              | į |

|   | 6.5  | Exper  | imental results: wet silicon etchant                 | ; |

|   |      | 6.5.1  | Wafer design                                         | ì |

|   |      | 6.5.2  | Experimental details                                 | 7 |

|   |      | 6.5.3  | Results: absolute measurements                       | 7 |

|   |      | 6.5.4  | Results: differential measurements                   | L |

|   | 6.6  | Discus | sion of results                                      | 1 |

| 7            | EIT      | based Plasma Potential Sensors                                    | 89  |

|--------------|----------|-------------------------------------------------------------------|-----|

|              | 7.1      | Motivation                                                        | 90  |

|              | 7.2      | Related work                                                      | 93  |

|              | 7.3      | EIT: a resistive network approach                                 | 96  |

|              |          | 7.3.1 Downsides continuous EIT problem                            | 96  |

|              |          | 7.3.2 Resistive networks                                          | 97  |

|              | 7.4      | Sensor design and operation                                       | 98  |

|              |          | 7.4.1 Three stage approach                                        | 98  |

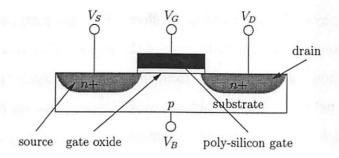

|              |          | 7.4.2 MOSFET operation                                            | 99  |

|              |          | 7.4.3 Depletion-mode NMOSFET                                      | 101 |

|              |          | 7.4.4 Wafer design and operation                                  | 104 |

|              | 7.5      | Simulation results                                                | 105 |

|              |          | 7.5.1 Experimental details                                        | 106 |

|              |          | 7.5.2 Algorithm details                                           | 107 |

|              |          | 7.5.3 Simulation 1                                                | 107 |

|              |          | 7.5.4 Simulation 2                                                | 109 |

|              | 7.6      | Conclusions                                                       | 111 |

| 8            | Con      | clusions                                                          | 113 |

| J            | 8.1      | Dissertation summary                                              | 113 |

|              | 8.2      | Future research                                                   | 114 |

|              | 0.2      |                                                                   | 117 |

| Bi           | bliog    | raphy                                                             | 116 |

| A            | Gale     | erkin Method for a Single Triangular Element                      | 129 |

| В            | Extr     | apolation and Interpolation Using Kriging                         | 133 |

| $\mathbf{C}$ | Cod      | e used in Hspice EIT Algorithm                                    | 136 |

|              | C.1      | runtotal: main program to perform EIT estimation (Perl)           | 136 |

|              | C.2      | runspicetotal: update and run spice simulation (Perl)             | 138 |

|              | C.3      | matbg: run Matlab in background (Shell script)                    | 139 |

|              |          | runmatlab.m: update gate potentials after each iteration (Matlab) | 140 |

|              |          | main.sp: main netlist (Hspice)                                    | 141 |

|              | $\alpha$ |                                                                   |     |

|              | C.b      | vgate_org.sp: original gate potentials (Hspice)                   | 142 |

# List of Figures

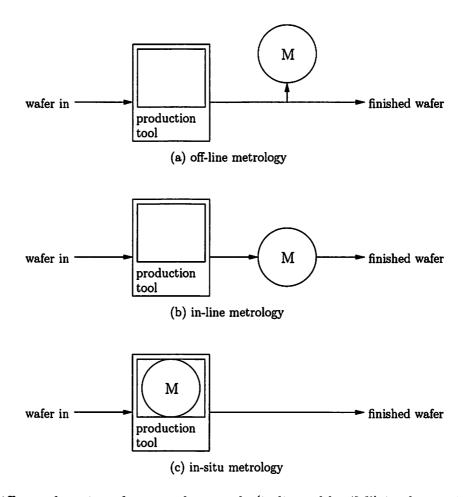

| 2.1        | Different locations for metrology tools (indicated by 'M') in the semi-<br>conductor manufacturing process                                  | 15 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

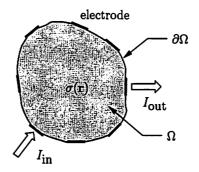

| 3.1        | The generic EIT setup                                                                                                                       | 25 |

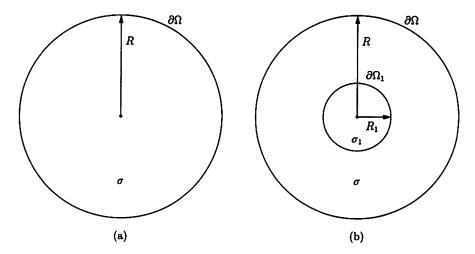

| 3.2        | A disc of uniform conductivity (a) and a disc with a circular anomaly                                                                       |    |

|            | centered around the origin (b)                                                                                                              | 29 |

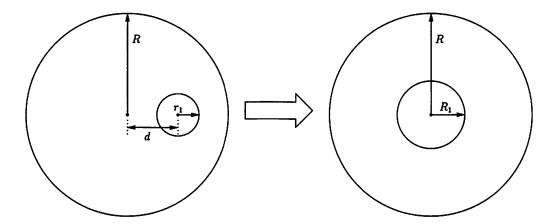

| 3.3        | A conformal mapping can map an off-centered circular anomaly to a                                                                           | 00 |

| o 4        | centered anomaly.                                                                                                                           | 30 |

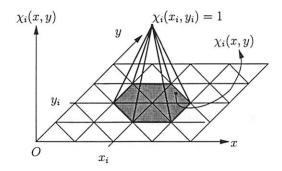

| 3.4        | Characteristic function $\chi_i$ for an arbitrary triangular finite element                                                                 | 31 |

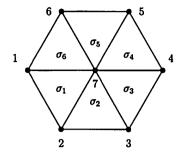

| 3.5        | discretization                                                                                                                              | 33 |

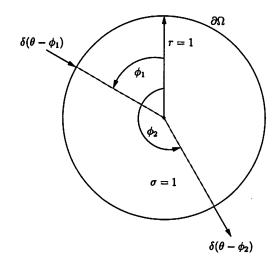

| ა.ა<br>3.6 | Simple hexagonal object containing 6 equilateral finite elements A disc of uniform conductivity with two point current sources on the       | JJ |

| J.U        | boundary                                                                                                                                    | 34 |

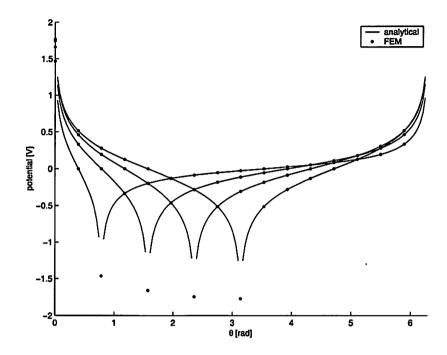

| 3.7        | Analytical and numerical solution to the Laplace equation on a circle                                                                       | 0. |

| 0          | for different Neumann boundary conditions.                                                                                                  | 35 |

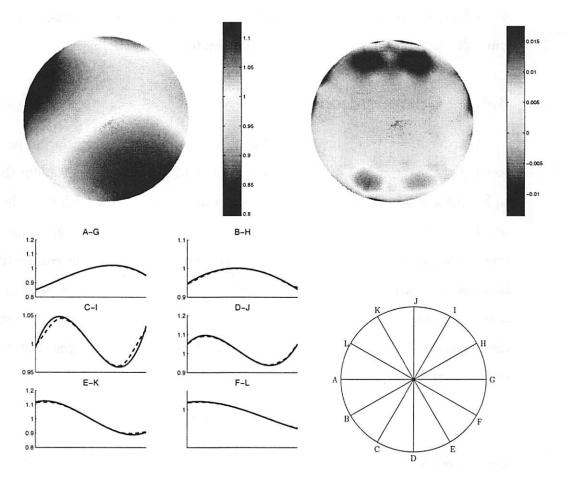

| 3.8        | Top: the left panel shows the real conductivity in Equation (3.13) across the unit disk; the right panel shows the spatial error between    |    |

|            | the true conductivity and the conductivity estimated with the Kriging algorithm. Bottom: the left panel shows the true (solid) and estimate |    |

|            | (dashed) conductivity along various cross sections of the unit disk (see                                                                    |    |

|            | right panel).                                                                                                                               | 39 |

| 3.9        | Generic process flow in EIT to estimate the conductivity profile inside                                                                     | 40 |

| 0 10       | the object of interest                                                                                                                      | 43 |

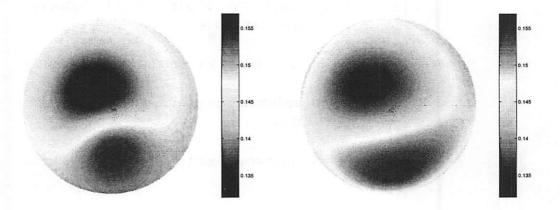

| 3.10       | The true conductivity distribution (left) and the estimated conductivity distribution (right)                                               | 44 |

| 3.11       |                                                                                                                                             | 44 |

| J.11       | ductivity distribution, as well as the least squares projection (dotted)                                                                    |    |

|            | along various cross sections of the unit disc (see right panel)                                                                             | 46 |

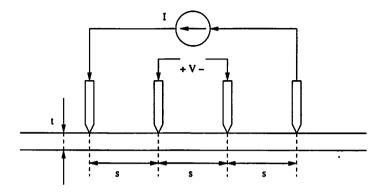

| 4.1        | Schematic of four-point probe setup.                                                                                                        | 51 |

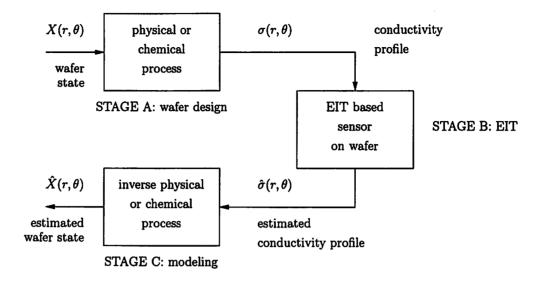

| 4.2        | Schematic of three-stage approach.                                                                                                          | 53 |

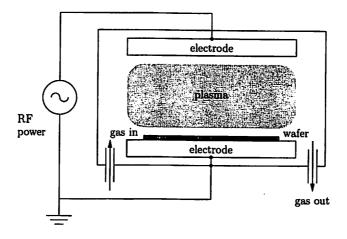

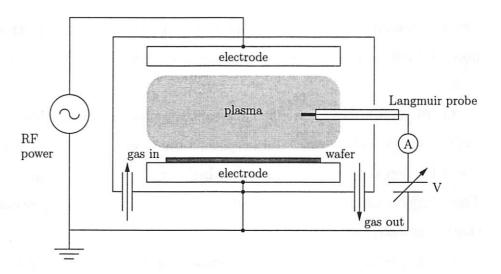

| 5.1         | Basic plasma etching system [80]                                                                                                                      | 60        |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

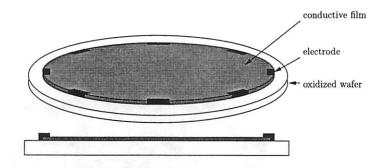

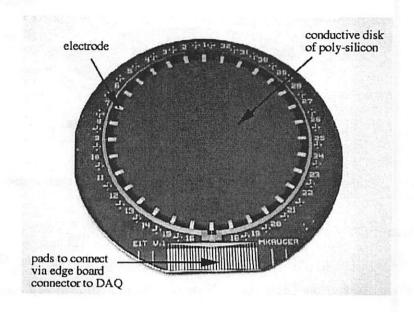

| 6.1<br>6.2  | Schematic of EIT based etch rate sensor                                                                                                               | 69<br>70  |

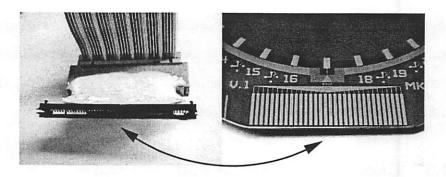

| 6.3         | An edgeboard connector (left) connects the DAQ system to special pads at the perimeter of the wafer (right)                                           | 72        |

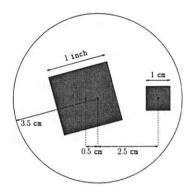

| 6.4         | Mask used in XeF <sub>2</sub> experiment. Dark areas are etched in the experiment and should, hence, show a decrease in conductivity over time.       | 73        |

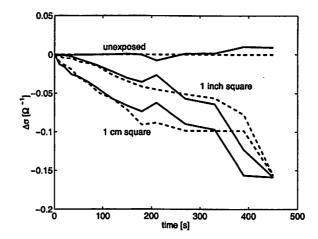

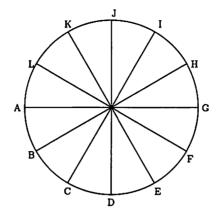

| 6.5         | Change in conductivity for different areas on wafer: estimated (solid) and four-point probe data (dashed)                                             | 76        |

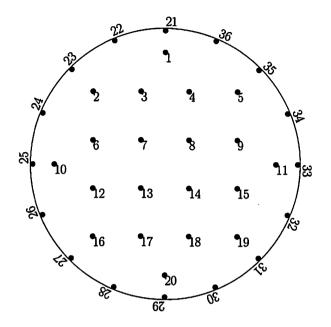

| 6.6         | Location of thickness measurement sites                                                                                                               | 78        |

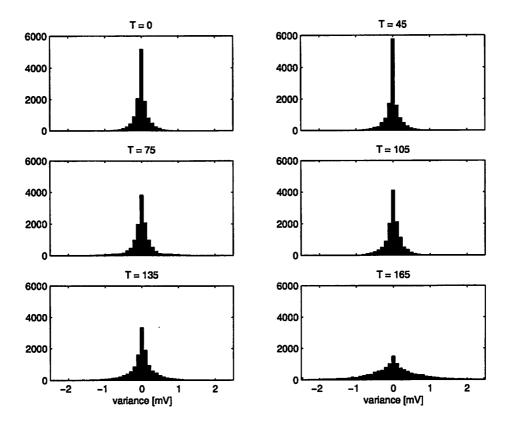

| 6.7         | Noise distribution around mean potential pattern for different etching                                                                                |           |

| c o         | times                                                                                                                                                 | 79        |

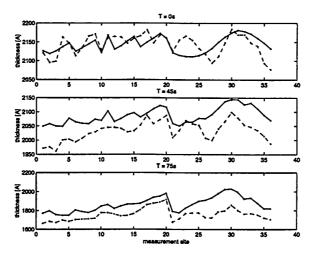

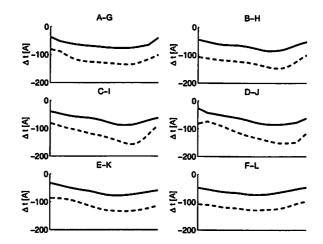

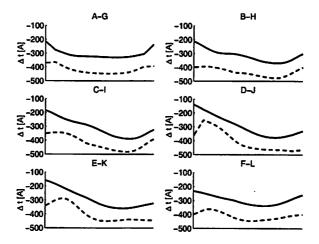

| 6.8         | Thickness at measurement sites according to optical metrology (solid) and EIT sensor (dashed)                                                         | 80        |

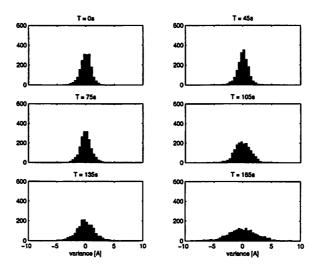

| 6.9         | Distribution around mean of the estimated parameters for different                                                                                    | OU        |

|             | etching times                                                                                                                                         | 81        |

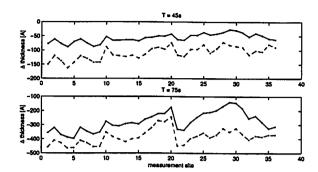

| 6.10        | Change in thickness at measurement sites according to optical metrol-                                                                                 |           |

|             | ogy (solid) and EIT sensor (dashed)                                                                                                                   | 82        |

| 6.11        | To assess the spatial measurement capabilities of our sensor, we analyze                                                                              |           |

|             | the change in thickness along the cross sections of the polysilicon disk                                                                              |           |

|             | shown here.                                                                                                                                           | 83        |

| 6.12        | Cross sectional view of change in thickness after 45 sec: optical (solid),                                                                            |           |

| <i>C</i> 19 | EIT (dashed)                                                                                                                                          | 84        |

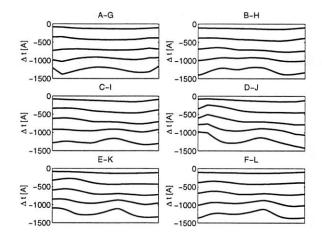

| 0.13        | Cross sectional view of change in thickness after 75 sec: optical (solid), EIT (dashed)                                                               | 85        |

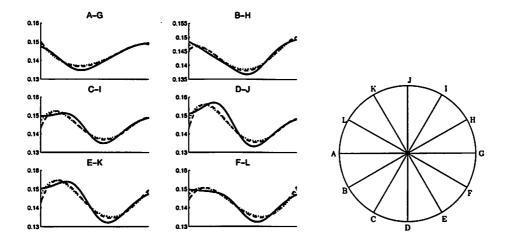

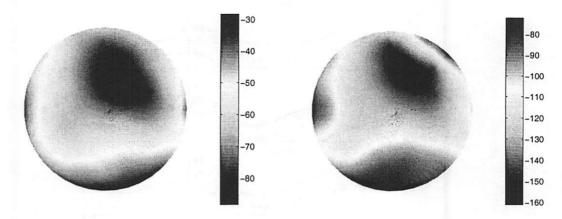

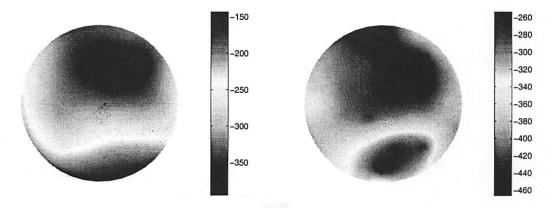

| 6 14        | Change in thickness in Å after 45 sec; optical (left), EIT sensor (right).                                                                            | 86        |

|             | Change in thickness in A after 75 sec; optical (left), EIT sensor (right).                                                                            | 87        |

|             | Cross sectional view of change in thickness as measured with EIT sen-                                                                                 | 01        |

| 0.20        | sor after 45, 75, 105, 135 and 165 seconds.                                                                                                           | 87        |

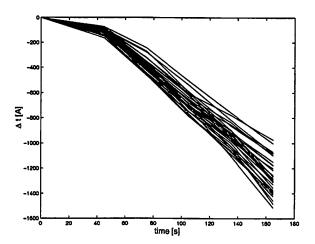

| 6.17        | Change in thickness, estimated by the EIT sensor at the 36 measure-                                                                                   | •         |

|             | ment sites, vs time                                                                                                                                   | 88        |

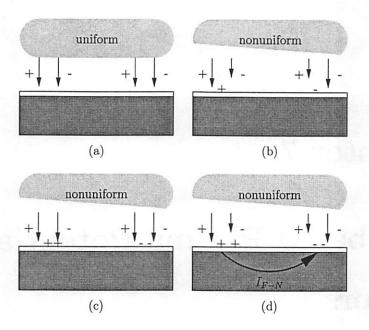

| 7.1         | A uniform plasma is characterized by a balanced flow of ion and elec-                                                                                 |           |

|             | tron fluxes across the sheath (a). In a nonuniform plasma, these fluxes                                                                               |           |

|             | are, at least initially, not balanced (b). Accumulation of charge at the                                                                              |           |

|             | wafer surface can balance the ion and electron fluxes (c) or it can result                                                                            | 00        |

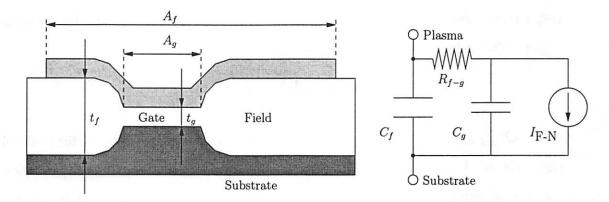

| 7.2         | in a Fowler-Nordheim current through the dielectric material (d) [35]. Antenna effect (left) and its electrical circuit equivalence (right) [35, 33]. | 90<br>91  |

| 7.3         | Schematic of Langmuir probe used for plasma diagnostics                                                                                               | 93        |

| 7.4         | Generic resistive network on wafer.                                                                                                                   | 98        |

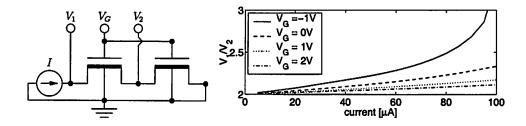

| 7.5         |                                                                                                                                                       | 00<br>100 |

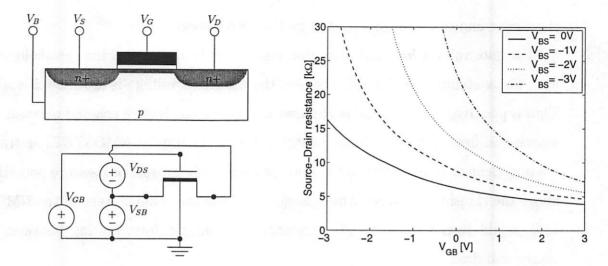

| 7.6        | Schematic cross section of depletion NMOSFET (top left). Circuit diagram utilized in Hspice simulations (bottom left) to compute the resistance of the depletion mode NMOSFET for different values of $V_{GB}$ and $V_{BS}$ , $V_{DS} = 0.01$ volts (right) | 102 |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.7        | Simulations revealing nonlinear behavior of depletion-mode NMOSFET                                                                                                                                                                                          |     |

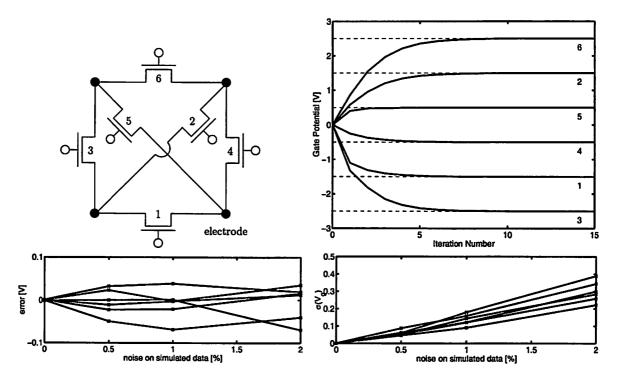

| 7.8        | Simulation results with the resistive network of 6 depletion mode NMOS-                                                                                                                                                                                     |     |

|            | FETs shown in the top left panel. The top right panel shows the es-                                                                                                                                                                                         |     |

|            | timated gate potential after each iteration in the nominal case, i.e.                                                                                                                                                                                       |     |

|            | without noise. The bottom left panel shows the error between the                                                                                                                                                                                            |     |

|            | mean gate potential and the "true" gate potential for different noise                                                                                                                                                                                       |     |

|            | levels. The bottom right panel shows the standard deviation of the                                                                                                                                                                                          |     |

|            | estimated gate potentials versus the noise level                                                                                                                                                                                                            | 109 |

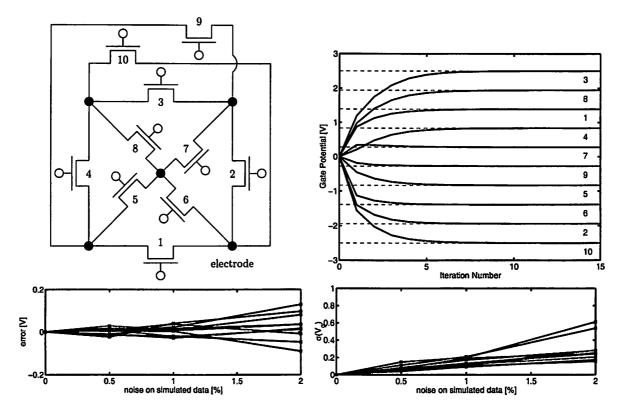

| 7.9        | Simulation results with the resistive network of 10 depletion mode                                                                                                                                                                                          |     |

|            | NMOSFETs shown in the top left panel. The top right panel shows                                                                                                                                                                                             |     |

|            | the estimated gate potential after each iteration in the nominal case,                                                                                                                                                                                      |     |

|            | i.e. without noise. The bottom left panel shows the error between the                                                                                                                                                                                       |     |

|            | mean gate potential and the "true" gate potential for different noise                                                                                                                                                                                       |     |

|            | levels. The bottom right panel shows the standard deviation of the                                                                                                                                                                                          |     |

|            | estimated gate potentials versus the noise level                                                                                                                                                                                                            | 110 |

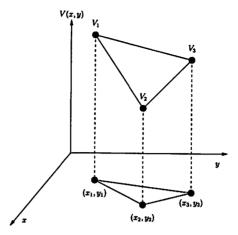

| <b>A.1</b> | Linear interpolation function used in single finite element                                                                                                                                                                                                 | 130 |

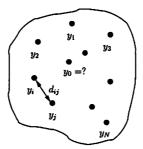

| B.1        | Kriging is concerned with predicting the optimal value for $y_0$ at an unobserved location, given measurements $y_i$ , $i = 1,, N$ at selected                                                                                                              |     |

|            | locations.                                                                                                                                                                                                                                                  | 133 |

# List of Tables

| 3.1 | Hot spot parameters used in the EIT example                                    | 44  |

|-----|--------------------------------------------------------------------------------|-----|

| 3.2 | Estimated parameter values $\alpha_{ij}$ for the various experiments discussed |     |

|     | in the text.                                                                   | 47  |

| 7.1 | Estimated gate potentials in volts for the various simulations per-            |     |

|     | formed on the resistive network containing 6 depletion mode NMOS-              |     |

|     | FETs                                                                           | 108 |

| 7.2 | Estimated gate potentials in volts for the various simulations per-            |     |

|     | formed on the resistive network containing 10 depletion mode NMOS-             |     |

|     | FETs                                                                           | 111 |

# List of Symbols

| $\boldsymbol{A}$                | Ratio of $A_f$ to $A_g$                                          |

|---------------------------------|------------------------------------------------------------------|

| $A_f$                           | Antenna area above field oxide                                   |

| $A_g$                           | Antenna area above gate oxide                                    |

| $\mathbf{B}(\mathbf{r})$        | Magnetic field vector at <b>r</b>                                |

| $C_f$                           | Capacitance of antenna structure over field oxide                |

| $C_{g}$                         | Capacitance of antenna structure over gate oxide                 |

| $C_{ m total}$                  | Total capacitance of antenna structure over field and gate oxide |

| δ                               | Dirac pulse                                                      |

| $e_l$                           | Portion of $\partial\Omega$ covered by $l$ -th electrode         |

| $\mathbf{E}(\mathbf{r})$        | Electrical field vector at r                                     |

| $\mathrm{E}(oldsymbol{\sigma})$ | Cost function in inverse EIT problem                             |

| $\epsilon$                      | Electrical permittivity                                          |

| $\epsilon_{ox}$                 | Electrical permittivity of oxide                                 |

| $I_{	ext{F-N}}(V_{ox})$         | Fowler-Nordheim current                                          |

| $I_{m{k}}$                      | Current entering or leaving through the $k$ -th electrode        |

| J                               | Jacobian matrix                                                  |

| $J_k$                           | Current density at k-th electrode                                |

| $\mathbf{J}(\mathbf{r})$        | Current density vector at <b>r</b>                               |

| L                               | Number of electrodes placed at periphery of object               |

| $\lambda$                       | Lagrange Multiplier                                              |

Magnetic permeability  $\mu$  $\hat{\mathbf{n}}(\mathbf{r})$ Unit normal at points on  $\partial\Omega$ N Number of unknown parameters in inverse EIT problem  $N_n$ Number of nodes used in FEM approximation  $\Omega$ Interior of the object  $\partial\Omega$ Boundary of the object Total accumulated charge per unit area  $Q_{\text{total}}$ r Position vector of a point in  $\Omega$ RResidual in FEM approximation  $R_s$ Sheet resistance Resistivity of material or film ρ  $\sigma$ Parameterized conductivity distribution  $\sigma(\mathbf{r})$ Conductivity of the object at r tFilm thickness  $t_f$ Field oxide film thickness  $t_{q}$ Gate oxide film thickness  $u(\mathbf{r})$ Electrical potential at r  $\mathbf{U}(\boldsymbol{\sigma})$ Vector of predicted electrode potentials  $\mathbf{v}$ Vector of observed electrode potentials  $V_q$ Potential across gate oxide  $V_{ox}$ Potential across oxide Weighting function used in FEM approximation  $\boldsymbol{w}$ *i*-th characteristic function  $\chi_i$

Conductance matrix

Y

# List of Acronyms

AC Alternating Current

BEM Boundary Element Method

CD Critical Dimension

COO Cost of Ownerhsip

CMOS Complementary Metal Oxide Semiconductor

CMP Chemical Mechanical Polishing

CCW Counter Clock Wise

DAQ Data Acquisition

DOF Degrees of Freedom

DC Direct Current

DUV Deep Ultra Violet

EEPROM Electrically Erasable Programmable Read-Only Memory

EIT Electrical Impedance Tomography

FDM Finite Difference Method

FEM Finite Element Method

FET Field Effect Transistor

$F-N \hspace{1cm} Fowler-Nordheim \\$

IC Integrated Circuit

ICP Inductively Coupled Plasma

LS Least Squares

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NMOSFET N-type MOSFET

OEE Overall Equipment Efficiency

PDE Partial Differential Equation

PM Preventive Maintenance

PMOSFET P-type MOSFET

RF Radio Frequency

RIE Reactive Ion Etching

RtR Run-to-Run

SEM Scanning Electron Microscope

SPC Statistical Process Control

TC Thermocouple

UV Ultra Violet

## Acknowledgements

In the last four years I had the opportunity to meet and work together with many excellent and interesting people, making my stay here in Berkeley both enjoyable and memorable. Most of them contributed directly to my research through helpful discussions, comments and suggestions. Many others provided distraction and support when needed, allowing me to maintain my sanity. I am very thankful for this. While I cannot include everyone here, I will try to be as thorough as possible.

First, and foremost, I would like to thank my advisors, Kameshwar Poolla and Costas Spanos for their guidance, support and friendship. Ever since I joined their research group, they generously supported me both intellectually and financially and gave me the freedom to pursue a variety of projects both within and outside academia. They cordially shared their knowledge, wisdom, humor and time with me and helped me, in every way they could, to get to where I am right now. For this I'm deeply indebted to them.

I am also grateful to Professors Andrew Packard, John Strain, Nathan Cheung, Kristofer Pister, Andrew Neureuther and Andrew Isaacs for their assistance with my class projects and/or research. Some of them also generously helped with my pursuits outside academia and I'm very thankful for that.

It was a pleasure to work together with the current and former members of the BCCI lab and the BCAM Group (KJ Al-Ali, Mareike Claassen, Dave Faris, Ryan Feeley, Darin Fisher, Andrew Flores, Mason Freed, Lance Hazer, Ken Hsu, Zachary Jarvis-Wloszek, Deborah Jue, Alpay Kaya, Zach Lerner, Lun Li, Rodney Martin, Matt Onsum, Peter Sedivec, Pete Seiler, Elain Shaw, Kunpeng Sun, Weehong Tan, Eric Wemhoff, Junwei Bao, Jason Cain, Tiger Chang, TK Chen, Scott Eitapence, Ralph Foong, Paul Friedberg, Andy Gleckman, Anna Ison, Nickhil Jakatdar, Charlotte Jones, Payman Jula, Jae-Wook Lee, Linda Manly, Jiangxin Wang, Jing Xue, Dong Wu Zhao, Charlie Zhang, Haolin Zhang). They provided me with great suggestions which helped shape my research and their presence made it fun coming into

lab every day.

Wafer processing for this research was done in the UC Berkeley Microfabrication Laboratory. This lab and its members are a great resource for anybody interested in semiconductor manufacturing. I am very thankful for all the help I received from staff and student members. In particular, I would like to acknowledge the advice and expertise of Katalin Voros, Bob Hamilton, Sia Parsa, Marilyn Kushner, Joseph Donelly, Patrick Wehrly and Laszlo Voros.

I would also like to thank Randy Mundt and Vebjorn Nilsen for their helpful suggestions and discussions. They provided valuable insight in the challenges and needs of the semiconductor manufacturing industry.

This research was supported by the National Science Foundation under grants ECS-99-07584 and ECS-96-28420, and by the UC SMART program, under contract SM99-10051.

I am very grateful to my mom for her continuing love and support. She has always been there for me, my sister and my twin brother and created for us a stimulating and supportive environment to grow up in. Letting me go to another continent to pursue my Ph.D. wasn't easy for her. Nevertheless, she was very happy for me and encouraged me to take this opportunity. I also want to thank my twin brother Xander and my sister Marie-Leontine for their continuing friendship.

Finally, I would like to express my deepest gratitude to my girlfriend Michelle for her love, help, advice and support. She tolerated my grouchy behavior when things didn't work out the way I wanted, and helped me focus on the positive things in life. She also inspired me and gave me confidence and strength.

# Chapter 1

# Introduction and Motivation

## 1.1 Introduction

Over the last three decades, we have witnessed increasing productivity in semiconductor manufacturing at a pace unprecedented in industrial history. The semiconductor industry has shown the remarkable and sustained capability to continuously increase the number of transistors per unit area without additional cost. This trend was first observed by Intel's co-founder George E. Moore and is often referred to as Moore's law [70].

The semiconductor industry uses highly specialized, advanced production tools and processes to print millions of transistors on each chip. With each new generation, the complexity and cost of these tools and processes increase rapidly. If the industry is to continue Moore's law, it must adopt advanced monitoring and control technologies to maintain equipment and processes within tight operating specifications. For this, there is widespread consensus that metrology will play an *enabling* role [91]. This is critical for 300 mm substrates where maintaining across-wafer process uniformity is particularly challenging.

Currently, off-line, in-line, and in-situ metrology techniques are used to monitor, diagnose, and control semiconductor manufacturing processes. Off-line metrology

inspects occasional wafers sampled from production runs. In-line metrology inspects every wafer upon completion of the process. In-situ metrology offers the ability to monitor conditions during actual processing.

These existing metrology choices have proven to be invaluable in reducing wafer-to-wafer and lot-to-lot product variability through improved process monitoring. These choices do not adequately address within wafer process variability. Within wafer uniformity becomes increasingly vital as the industry moves towards larger substrates and finer linewidths. This manufacturing requirement can only be met by a novel metrology paradigm: sensors that can provide spatially and time-resolved wafer state information.

# 1.2 The Holy Grail of metrology

The semiconductor industry is risk sensitive and reluctant to adopt novel metrology technologies unless they provably address concerns of process stability, tool contamination and ownership costs. To realize widespread adoption in high-volume semiconductor manufacturing facilities, novel metrology technologies must offer the following attributes:

## • Spatial and temporal wafer state information

Current in-line and in-situ metrology provide the necessary process state information to obtain wafer-to-wafer and lot-to-lot uniformity. However, as feature sizes shrink even further, within wafer uniformity becomes critical. As a result, spatially resolved wafer state information has now become necessary.

## • Cost effective reliable integration

The integration of metrology tools with process tools often requires significant software and hardware modifications. This can be time-consuming, expensive, and can compromise equipment reliability. It can also affect process stability

and can make production tools more vulnerable to false alarms due to metrology errors. Consequently, the large initial capital investment and the increased operating costs of metrology integration must be justified by the anticipated financial gains resulting from improved process capabilities and increased yields.

#### Ease of deployment

In many processes periodic wafer state measurements suffice to ensure process uniformity and repeatability. In these situations, the costs associated with permanent integration of the necessary metrology can not be justified. However, taking the tool off-line for inspection and calibration can also be prohibitively expensive. Hence, there is a need for simple and rapid metrology techniques which can be periodically deployed without making any modifications to the process tool.

### • No influence on process

The semiconductor industry expends considerable resources on maintaining an ultra-clean production environment to prevent catastrophic yield loss due to contamination. Any serious metrology choice should not contaminate the process being sensed. In addition, the metrology tool itself should not affect the process or distort the variables being sensed.

# 1.3 Our metrology approach

In this dissertation, we will investigate the feasibility of a class of sensors for semiconductor manufacturing applications. The common theme shared by this class of sensors is that they are based on Electrical Impedance Tomography (EIT), an *in vivo* imaging technology that has found widespread use in biomedical applications.

The basic idea of Electrical Impedance Tomography is to image the conductivity distribution in the interior of a conductive object by performing simple electrical measurements on the periphery of the object. For example, in the human body different tissues and organs are characterized by different conductivity values. Hence, being able to image the conductivity distribution inside the human body allows us to pinpoint the locations and geometry of different organs and/or tissues.

In a semiconductor manufacturing context, physical and chemical effects during semiconductor manufacturing can induce a change in conductivity in the interior of a wafer. If we can measure these conductivity changes in the interior of the wafer with EIT techniques, we can infer the physical and chemical effects which cause these changes. The principle objective of this dissertation is to investigate the feasibility of metrology methods based on Electrical Impedance Tomography techniques to provide real-time, spatially resolved wafer state information.

# 1.4 Related work summary

The need for spatially resolved wafer state information has led to the development of a variety of sensor wafers. Simple wafer designs that employ an array of passive sensors to measure peak wafer state values during processing have been studied [62, 106, 76]. These wafers are easy to employ and are attractive for use in high volume manufacturing facilities. However, these wafer cannot provide time-resolved wafer state information. To address this drawback, a variety of tethered wafers have been developed to measure wafer states such as temperature, potential, etch rate and ion flux [92, 63, 6, 40, 53]. However, the tether prohibits facile loading of the sensor wafer with standard wafer handling robotics. Consequently, their use is limited to tool development and scheduled preventive maintenance. This serious shortcoming can be addressed by recently developed autonomous sensor wafers. The feasibility of this approach was demonstrated with several proof-of-concept wafer designs [41, 42, 40]. In addition, issues which have been addressed or which are currently under investigation by other groups are the power supply [18], encapsulation [112] and communication

schemes [78, 58]. Autonomous sensor wafers for temperature metrology are now commercially available [75].

## 1.5 Contributions of this dissertation

In this dissertation, we have developed a novel class of sensors for use during semiconductor manufacturing. These sensors exploit the spatial imaging capabilities of Electrical Impedance Tomography (EIT) to obtain spatially resolved wafer state information. EIT is a non-destructive in vivo imaging technique principally used in biomedical applications. To the best of our knowledge, the use of EIT techniques in semiconductor manufacturing applications as suggested in this dissertation is novel.

The essential idea in our approach is to place electrodes at the periphery of a wafer. We then perform simple electrical measurements. From these measurements, we infer the conductivity distribution inside the wafer, which, in turn, can be related to the variable of interest through simple physical or chemical models.

To illustrate our ideas, we discuss the design, fabrication and operation of a prototype etch rate sensor. Measurement data from this prototype etch rate sensor corresponds well with optical film thickness measurements. In contrast with traditional EIT applications, in our sensor wafer context we have the luxury of designing the interior of the object being imaged. In this dissertation we exploit this observation by applying EIT techniques to a resistive network containing discrete transduction elements. This approach allows us to circumvent some of the drawbacks associated with traditional EIT techniques. To illustrate our approach, we have designed a prototype sensor to measure the potential induced by a plasma at the wafer surface. We offer promising simulation results with this novel approach to EIT to validate our ideas.

# 1.6 Thesis overview

The remainder of this thesis is organized as follows. In Chapter 2 we provide an overview of the various metrology methods currently used in semiconductor manufacturing. We also summarize the challenges faced by the industry, and the role metrology will play to address these challenges. In Chapter 3 we offer a thorough introduction to Electrical Impedance Tomography. We discuss both theoretical and numerical aspects and illustrate our discussion with several simple examples. In Chapter 4 we describe how EIT techniques can be used in the context of semiconductor manufacturing. In particular, we discuss a class of autonomous sensor wafers which employ EIT techniques to obtain spatially and temporally resolved wafer state information. In Chapter 5 we provide a brief overview of etching processes in semiconductor manufacturing, and discuss the principal technological challenges that arise in this context. This discussion offers a compelling case for the development of spatially resolved sensor wafers for use during semiconductor manufacturing. In Chapter 6 we describe the design, fabrication and testing of such a prototype sensor wafer: an EIT based etch rate sensor. In Chapter 7 we discuss our results in developing a second prototype sensor employing EIT techniques: a sensor which measures the potential at the wafer surface during plasma etching. Finally, in Chapter 8 we offer a summary of this dissertation and draw some conclusions based on our research experience. We close by suggesting recommendations for future research.

# Chapter 2

# Semiconductor Manufacturing

Metrology: an overview

This chapter offers an overview of semiconductor manufacturing metrology. After a brief discussion of the industry trends, the role of metrology in this industry is discussed. This is followed by a survey of currently available metrology choices. Finally, the future of metrology is discussed. In particular, the concept of autonomous sensor wafers is introduced.

## 2.1 Semiconductor manufacturing

Semiconductor manufacturing is a complex process involving the selective deposition and removal of thin films of different materials in order to create devices with millions of three-dimensional components (transistors, capacitors, resistors etc.). On completion of these individual components, similar fabrication techniques are used to interconnect them to create Integrated Circuits (ICs). The integration of enormous numbers of components onto a single chip results in higher circuit performance, greater functionality, and increased reliability, all at very low unit cost.

For more than three decades, the semiconductor manufacturing industry has been

able to reduce the smallest printable features on the wafer, allowing them to double the number of transistors per device at no additional cost every 18 months [70, 91]. This trend is called Moore's law, after Intel's co-founder George E. Moore. Moore's law has become a self-fulfilling prophesy and competitive forces compel the IC industry to maintain this trend. To this end, the IC industry is continuously improving the performance of the manufacturing processes and tools. These performance enhancements focus principally on the ability to consistently print smaller features, more reliably, and across larger substrates.

The following trends are discernible in modern semiconductor manufacturing:

#### 1. More advanced processing tools

Equipment manufacturers spend billions of dollars on the development of advanced production tools which are capable of printing smaller features. The development of plasma etching tools is a good illustration of this trend. A simple plasma etching tool applies an RF power between two parallel plates to create a plasma discharge. The chemical and ionic species in this plasma will then selectively etch a wafer which is placed on one of the electrodes (see Chapter 5 for more details). Reducing the pressure in the etch chamber improves the directionality of the ionic species which bombard the wafer surface, resulting in more vertical profiles. However, lower operating pressures result in lower plasma densities, which, in turn, reduce the etch rate. Increasing the RF power between the parallel plates to compensate for the decrease in etch rate can cause undesirable damage at the wafer surface. To counteract this coupling between plasma density and ion energy, the semiconductor industry has adopted highdensity plasma etchers. These etchers employ an Inductively Coupled Plasma (ICP) source to generate a high density plasma. A second RF source controls the energy of the ions bombarding the substrate by adjusting the bias between the wafer and the plasma. These high density plasma etchers can operate at lower pressure, resulting in more vertical sidewalls, while maintaining high ion fluxes and etch rates.

#### 2. New materials

In addition to smaller features, IC manufacturers also rely on new, exotic materials to boost the performance of their devices. For example, aluminum is replaced by copper to reduce resistive losses in long wires and low-k dielectric materials are used instead of  $SiO_2$  to reduce the parasitic capacitance and cross talk between conductors. These new materials, however, often require completely new and innovative fabrication processes and tools, further increasing the costs of IC manufacturing.

#### 3. Larger wafers

Processing costs per wafer are relatively independent of wafer size. Hence, in order to compensate for the rising costs, the semiconductor industry has steadily moved to larger diameter wafers, allowing more chips to be fabricated simultaneously. Currently, 200 mm wafers are the standard in most production facilities, while 300 mm wafers are gradually being adopted in state-of-the-art facilities. These larger substrates offer 240% more die per wafer, 30% lower costs per die, all while reducing energy and chemical consumption by 40% [49]. This has the added and important benefit of reducing the environmental impact of semiconductor manufacturing.

Previous trends have helped the semiconductor manufacturing industry to keep pace with Moore's law. However, the emerging consensus is that Moore's law may break down in the near future if the industry does not adequately deal with the following two challenges:

#### • Reliable pattern transfer

High volume production facilities are currently capable of printing 0.13  $\mu$ m lines while research groups have recently shown that it is possible to print features

as small as 15 nm. Hence, further device scaling is technically feasible. However, efficient and cost-effective fabrication of these smaller devices will prove extremely challenging. The focus in the near future will, therefore, be on the reliable pattern transfer of smaller features on larger wafers.

#### • Shorter time-to-market

The current IC market is characterized by intense competition and short product cycles. This results in rapid price erosion of new products, providing IC manufacturers with a small window of opportunity to recoup their large capital investments. Therefore, minimizing the time-to-market is particularly critical in this industry. To this end, IC manufacturers will have to ramp up production of new generations of devices quickly, while achieving high production yields.

In order to address these challenges, it is very important to obtain a thorough understanding of how equipment and processes affect the wafer surface. This information can then be used to adjust equipment and processes, improving product uniformity, throughput and yield. In addition, it is imperative to monitor processes vigilantly allowing early detection of undesirable process drifts. In current practice, IC manufacturers sample a few wafers per batch with high end metrology tools. However, as process specifications tighten, it will be necessary to sample each wafer in order to detect small process disturbances. Spatial wafer metrology can also reveal deterministic offsets and disturbances, enabling advanced feedforward and feedback control algorithms to compensate for these effects. Hence, there is widespread agreement that the IC industry will become more dependent on accurate, real-time metrology to improve their processes and to accelerate time-to-market and time-to-yield. In fact, in its latest technology roadmap, SEMATECH (an international consortium of IC manufacturers and tool suppliers) calls metrology an enabler for the introduction of future technology generations [91].

# 2.2 The role of metrology

Metrology is an indispensable ingredient of the semiconductor manufacturing process. It provides valuable wafer state information during and after each processing step. This information is used for:

#### • Process design

Every process has to be thoroughly characterized before it is adopted by IC manufacturers in high-volume production. As a result, large numbers of test wafers are subjected to different processing conditions and the resulting state of each test wafer is recorded. A properly designed experiment can then provide the process engineer with a model which relates the variable of interest to the different processing parameters. For example, the etch rate in a plasma etcher depends on many variables such as gas flows, pressures, RF powers and wafer temperature. In order to characterize this process, process engineers perform factorial design experiments, changing process parameters one at a time. The observed etch rate information then yields a model which relates processing parameters to the etch rate. This model can, in turn, assist process engineers in optimizing the process and establishing the sweet spot where throughput is maximized while maintaining a stable and uniform process across the wafer.

#### • Process validation

Processing tools are designed to be very repeatable. However, small disturbances invariably cause the process to drift over time. Therefore, a small number of production wafers in each batch is sampled to ensure that the process is still within specifications. For example, during plasma etch and deposition processes the walls of the reactor are in direct contact with the plasma. As a result, changes in wall conditions due to residue build-up can affect plasma properties such as ion density, reactive species concentrations and electron temperatures [44]. These changes in plasma properties can cause a shift in etch rate and/or

uniformity, selectivity and anisotropy.

#### Process control

In the early days of semiconductor manufacturing, IC manufacturers relied on the robustness of the process and the repeatability of production tools to keep their processes within specifications. Once dialed in, recipes remained fixed until a large excursion of a critical parameter was detected. However, shrinking critical dimensions (CDs) forced the IC industry to take a more proactive approach to improve yield and to reduce variability in the process. This has led to the adoption of Statistical Process Control (SPC) [69] and Run-to-Run (RtR) control algorithms [74, 83, 57]. Here, a small number of wafers in each batch is measured and the observed data is used to make small adjustments to critical processing parameters, closing the control loop around the process. RtR techniques allow IC manufacturers to make small adjustments to their processes more frequently, reducing process variance, improving disturbance rejection and enhancing overall process yield. Successful applications of RtR control include chemical mechanical polishing (CMP), etching and lithography [13, 47, 12]. Larger diameter wafers and tighter process specifications increase the economical risks of process drifts, failures and nonuniformities. Consequently, the IC industry is moving rapidly towards ubiquitous process control.

### • Equipment diagnosis and maintenance

During IC manufacturing equipment characteristics change as parts wear out or age, causing a slow drift in process performance. Early detection of these drifts is vital to minimize the number of lost product wafers. In addition, a rapid assessment of the root cause can reduce tool-downtime, increasing overall equipment efficiency. To this end, sensors built into the tool continuously record the tool state during processing. Tool failures often cause abrupt changes in tool states. Consequently, tool state sensors can often detect tool failures as

they happen, minimizing lost lots.

Preventive maintenance (PM) results in tool-downtime. However, a prolonged time without tool maintenance increases the risk of an abrupt tool failure. Thus, PM scheduling is a challenging task, trading lost production for tool reliability. Slow variations and drifts in tool states within certain bounds are in general acceptable. However, as certain tool states approach or exceed those bounds PM is necessary. Hence, tracking of tool states over many process runs provides a means of scheduling the PM events.

#### • Equipment design

Minor changes in tool geometries can significantly affect the overall process performance and uniformity. Ideally, numerical simulations could be used to reveal these effects, allowing tool manufacturers to quickly optimize their design. However, process and tool complexity often preclude accurate and rapid numerical simulations [81]. Hence, in many cases tool manufacturers continue to rely on test wafers to assess their tool designs.

The variety of applications discussed above clearly shows the importance of metrology during semiconductor manufacturing. From initial tool design to high-yield volume production, metrology provides vital wafer state information. It assists process engineers in optimizing both equipment and processes and it reduces time-to-yield and the associated costs of lost products in high volume manufacturing facilities.

# 2.3 Metrology: the status quo

Both IC manufacturers and equipment suppliers rely on metrology to characterize and optimize equipment and processes, allowing larger wafers to be uniformly processed while increasing throughputs. In response, metrology vendors have developed a variety of tools to meet the different market needs. This section will discuss in more detail the various metrology choices currently available. Traditionally, the semiconductor manufacturing industry has used off-line metrology to verify proper operation of the fabrication tools and to control the fabrication process. Here, from every batch production a select number of wafers is inspected with special, very accurate metrology tools, see Figure 2.1(a). However, these tools are expensive, occupy valuable real-estate within the fabrication facility and introduce a significant delay in the overall fabrication process. In addition, some metrology tools are destructive, resulting in yield-loss. A cross-sectional Scanning Electron Microscope (SEM) is a good example of an off-line metrology tool. This tool employs a focused beam of high energy electrons to obtain cross-sectional images of a processed wafer with a resolution below 5 nm [80]. These images provide valuable profile information to process engineers, allowing them to adjust and/or optimize the process appropriately.

Over the last five years, semiconductor manufacturing practice has evolved from using off-line metrology to using in-line metrology. Where possible, stand-alone metrology tools have been replaced with integrated metrology tools which are placed in proximity to or mounted on production tools, see Figure 2.1(b). These integrated metrology tools allow every wafer to be inspected after processing as opposed to just a fraction as is the case with off-line metrology. The benefits of this shift are numerous: the large amount of process data allows continual process monitoring, earlier fault detection and more frequent adjustments to the process, resulting in reduced process variance. In-line metrology also results in improved throughput: instead of removing selected wafers for off-line metrology, all wafers can, after inspection, continue to the next processing step.

Optical techniques such as scatterometry and ellipsometry are the technologies of choice for integration as they provide the desired precision and accuracy without impacting the tool throughput or affecting the process itself. Consequently, metrology vendors work closely with equipment manufacturers to incorporate optical metrology capabilities into production tools.

Figure 2.1: Different locations for metrology tools (indicated by 'M') in the semiconductor manufacturing process.

Although in-line metrology offers significant benefits, the associated ownership and operating costs can be significant. In addition, equipment engineers are often reluctant to deploy additional sensors and associated hardware to existing tools as these changes could affect process stability and possibly void equipment warranties. Processing tools also become more vulnerable to false alarms due to metrology errors and/or failure.

Both off-line and in-line metrology provide information about the *time-integrated* effect of the process of interest on the wafer, i.e. they can not detect within-process transients. For example, the pattern in DUV photoresists after post-exposure bake is very sensitive to the total thermal budget of the baking step: small variations in tran-

sient temperature characteristics can have a significant influence on the final profile [80]. In order to characterize the post-exposure bake step, test wafers covered with photoresist and the desired pattern are baked at different temperatures over different times. Post-exposure bake profile information is then used to deduce the effect of temperature and time on the photoresist profile. In this analysis it is assumed that the wafer temperature is constant during the bake. However, in reality the wafer will experience some heating and cooling transient effects when placed on and removed from the bake plate. This will translate into small variations in photoresist profiles across the wafer. This test-wafer approach cannot adequately address these transient effects. Real-time wafer temperature measurements offer a superior solution as they offer the time-resolved data necessary to account for and control these transient temperature effects.

Today, most processing tools are equipped with sensors to measure process variables such as pressures, gas flows, RF powers and wall/chuck temperatures in-situ, see Figure 2.1(c). Changes in these variables can seriously affect the resulting process near the wafer and these variables must therefore be controlled within tight specifications. However, the relation between tool state and wafer state is rather complex and requires extensive experimental modeling [8].

Active monitoring and control of process states is necessary to obtain uniform results between wafers and lots. However, this approach is insufficient for sub 0.15  $\mu$ m linewidths on 300 mm wafers. For these dimensions, within wafer uniformity control becomes critical. For example, during plasma etching micro-loading effects become more pronounced as CDs shrink, i.e. dense line patterns exhibit reduced etch rates compared to isolated line patterns. Aggregate plasma state information is too coarse to reveal these effects. Consequently, there is a need to monitor the wafer state, i.e. process conditions at the wafer surface.

Recent research efforts have focused on the development of in-situ wafer state metrology, see Figure 2.1(c). Where possible, wafer state information is acquired in

real-time during wafer processing, for example by optical and acoustic techniques. Among the wafer variables measured with these techniques are wafer temperature and etch/deposition rate [85, 8, 79, 59].

Both optical and acoustic techniques provide accurate wafer state information. However, both technologies require hardware changes to the tool. Optical techniques require viewports for direct line-of-sight access to the wafer. Acoustic techniques rely on intimate mechanical contact between the backside of the wafer and a transducer/receiver pair mounted on rods. This requires the use of a modified wafer chuck. In addition, neither technique readily provides spatially resolved wafer state information. Optical techniques focus in general on a small area of the wafer surface while acoustic techniques obtain an average value of the wafer state due the large distance between the transducer/receiver pair.

With the widespread adoption of larger wafers, it becomes increasingly critical to maintain process uniformity across these larger substrates. Edge effects become critical with devices being produced within 2 mm of the wafer's edge. Consequently, IC manufacturers devote significant resources to optimize process recipes to guarantee across-wafer uniformity. For this, spatially resolved wafer state information is essential. This interest in spatially resolved wafer state information has led to the development of special passive sensors to measure peak wafer state values during processing. These passive sensors rely on a physical or chemical effect to induce a permanent change in sensor properties once the variable of interest exceeds a threshold value. An array of these sensors is then mounted or fabricated onto a test wafer and subjected to the process of interest. Upon completion, each sensor can be inspected and the maximum spatial wafer state can be assessed.

For example, CHARM II wafers have been developed to provide information about wafer charging damage due to non-uniform plasma processes. Non-uniform wafer charging can have a serious impact on process yields (see Chapter 7) and is, therefore, a major concern for high volume IC manufacturers. CHARM II wafers employ floating

gate EEPROM devices which are sensitive to electro-static charging and UV effects, causing a change in EEPROM threshold voltages [106]. Arrays of EEPROMS are fabricated across the surface of a special test wafer. After wafer processing, changes in threshold voltages can be electrically detected, providing spatial information of wafer charging effects.

Test wafers employing passive sensors are easy to use and can provide useful information about the peak wafer states achieved during processing. IC manufacturers can introduce these wafers into their processing tools with standard wafer handling robotics and without any equipment modifications, making them attractive for use in high volume manufacturing facilities. However, passive sensor wafers require additional post-processing time to obtain the wafer state information. In addition, many passive sensor wafers are single-use, requiring a new sensor wafer for each run. The principal shortcoming of passive sensor wafers is that, by their very nature, they can only record extremes over time and do not have the capability to monitor the time-resolved behavior of the variable of interest.

The demand for real-time spatially resolved wafer temperature information has led to the development of tethered TC-wafers These are standard silicon wafers with small thermocouples (TCs) embedded into their surface [92]. Real-time temperature information during wafer processing can then be obtained through a cable which connects the TCs on the wafer to a data acquisition system outside the processing tool.

Unfortunately, process tools do not readily accept these tethered TC wafers as the cable prohibits the TC wafer from being loaded with standard wafer handling robotics. As a result, the process tool has to be taken off-line and opened to provide loading access. In addition, a special feedthrough is required to thread the tether to the outside of the chamber. This results in significant tool-downtime and high cost-of-ownership. Hence, these wafers are mostly used for tool development or scheduled PM but not for routine process monitoring in production facilities.

#### 2.4 Metrology: the future

Autonomous sensor wafers offer a promising alternative to in-line and/or in-situ metrology. These are sensors that externally resemble standard silicon wafers with embedded power, communications, and transduction elements. These autonomous sensor wafers can be introduced into equipment with existing wafer-handling robotics in cassette-to-cassette operations as regular product wafers. This eliminates the need to open the tool for sensor wafer loading and unloading. Sensor wafers can access wafer and process state information during processing as is available from equipment-based in-situ sensors. An added benefit is that sensor wafers can be significantly less complex and more cost-effective when compared with in-situ or in-line alternatives. In addition, autonomous sensor wafers can provide process engineers with temporal and spatial wafer state information, making it possible to fine tune the process rapidly while minimizing test wafers usage.

The feasibility of sensor wafers for semiconductor manufacturing applications has been shown in [41, 42, 40]. Several proof-of-concept designs to measure film-thickness, temperature and heat flux have been developed. These sensor wafers are capable of measuring the wafer state in real-time during selected IC processing steps. In order to obtain spatial wafer state information, several transduction elements are placed at the wafer surface. However, a large number of these elements have to be used to obtain satisfactory spatial resolution, particularly for 300 mm substrates.

An "ideal" sensor wafer must resemble a regular product wafer as closely as possible in order to avoid interference with the variable to be measured. Thus the thermal mass and topology of each transduction element should be minimized. In addition, the sensor wafer should strictly avoid exposing the process to any exotic materials which are incompatible with semiconductor manufacturing processes as this may result in unacceptable contamination of the tool. Hence, it is very desirable to fabricate sensor wafers with standard semiconductor processing techniques, if possible.

Processes in semiconductor manufacturing equipment often take place in harsh environments. For example, during plasma etching the wafer is exposed to high electro-magnetic fields and strong chemical etchants. In addition, many processes are performed at elevated temperatures, up to 1100 °C. Hence, an autonomous sensor wafer must be properly shielded to protect the on-board electronics and power supply. Temperature shielding is particularly challenging and may entail the design of a vacuum chamber around the electronics to eliminate thermal conduction and convection. However, this will severely complicate the overall design and it is therefore unlikely that any autonomous sensor wafer will be able to operate at temperatures above 150 °C. This limits their use to low temperature applications such as post-exposure bake plates and some plasma etchers.

We do not suggest that autonomous sensor wafers will replace all metrology currently in place. Compared to off-line and in-line metrology, the accuracy and precision of autonomous sensor wafers are limited. For example, state-of-the-art metrology tools that employ optical techniques to measure wafer properties such as film thicknesses, linewidths and sidewall profiles are irreplaceable, and they cannot be supplanted by autonomous sensor wafers. A further shortcoming is that on-board data storage will pose a limit on the maximum sampling rate and number of data points collected. Hence, the need for test wafers, while diminished, will remain.

Despite these challenges, we feel that IC manufacturers will adopt autonomous sensor wafers in the near future to obtain previously unaccessible wafer state information. Autonomous sensor wafers will be particularly vital during the ramp up phase of new production facilities or for rapid fault detection and isolation. In addition, they can also be used to quickly assess or validate the performance of individual processing tools, enhancing process uniformity and reducing the risks and associated costs of lost product.

We should remark that the IC industry is rather conservative in adopting new technologies to improve performance because of the concern that these may adversely affect process stability. However, we remain optimistic that the successful use of autonomous sensor wafers in various applications such as etch and lithography will eventually drive their widespread acceptance in high volume manufacturing facilities.

### Chapter 3

# Electrical Impedance Tomography: an overview

Electrical Impedance Tomography is an *in vivo* imaging technique, principally used in medical applications. It has also found application in non-destructive product testing [52], fluid flow imaging [25, 109] and geophysics [26]. The technique consists of injecting electrical currents into an object and measuring the induced potentials at the surface of the object. These surface measurements are used to estimate the conductivity distribution in the interior of the object. The estimated conductivity distribution can then be directly related to different features within the object (organs in humans, processing faults in finished products) and can, therefore, be used as a diagnostic tool. The principal advantage of this technique is that it uses fairly inexpensive hardware and is non-destructive.

The remainder of this chapter offers a survey of Electrical Impedance Tomography (EIT). After a brief introduction, we derive the governing partial differential equations which model the electrical behavior of the object being imaged. This model forms the basis for any EIT algorithm. The following two sections treat computational aspects of simulating the EIT model, and inverting this model respectively. These computational problems form the core of all EIT algorithms. Finally, we offer a simple

numerical example to illustrate the ideal developed in this chapter.

#### 3.1 Operating principle