# Copyright © 2003, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# HIGH THROUGHPUT VLSI ARCHITECTURES FOR ITERATIVE DECODERS

bу

Engling Yeo

Memorandum No. UCB/ERL M03/39

16 October 2003

# HIGH THROUGHPUT VLSI ARCHITECTURES FOR ITERATIVE DECODERS

by

**Engling Yeo**

Memorandum No. UCB/ERL M03/39

16 October 2003

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# High Throughput VLSI Architectures for Iterative Decoders

By

#### Engling Yeo

B.S. (University of California, Berkeley) 1994M.S. (University of California, Berkeley) 1995

A dissertation submitted in partial satisfaction of the

requirements for the degree of

Doctor of Philosophy in

Engineering – Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY of CALIFORNIA, BERKELEY

Committee in charge:

Professor Borivoje Nikolić, Chair Professor Venkatcha Anantharam Professor Jasmina L. Vujić

Fall 2003

# The dissertation of Engling Yeo is approved:

Borivoje Nikolić (Chair)

O 15/2003

(Date)

Venkatachalam Anantharam (Date)

Jasmina L. Vujić 10107/2003

(Date)

#### **ABSTRACT**

## High Throughput VLSI Architectures for Iterative Decoders

by

#### **Engling Yeo**

Doctor of Philosophy in Engineering – Electrical Engineering and Computer Sciences

University of California, Berkeley

Professor Borivoje Nikolić, Chair

This project addresses the algorithms for and implementations of iterative decoders for error control in communication applications. The iterative codes are based on various concatenated schemes of convolutional codes, and low-density parity check (LDPC) codes. The decoding algorithms are instances of message passing or belief propagation algorithms, which rely on the iterative cooperation between soft-decoding modules known as soft-input-soft-output (SISO) decoders.

Iterative decoding is a recent advance in communication theory that is applicable to wireless, wireline, and optical communications systems. It promises significant advantage in bit error rate performance at signal to noise ratios very close to the theoretical capacity bound. However, a direct mapping of the decoding algorithms leads to a multifold increase in the implementation complexity. As deep submicron technology matures, there is a possibility of implementing these applications that were once thought to be too complex to fit onto a single silicon die. We investigate the architectural and implementation issues related to building iterative decoders in VLSI.

In this research, the computational hardware and memory requirements of magnetic storage applications provide a platform for evaluation of iterative decoders. The accomplishments include modifications of algorithms, their simulation, efficient mapping into architectures, and VLSI implementations provide the final measure of

complexity in terms of power, size, and speed. The VLSI implementations of iterative decoders based on concatenated convolutional codes or LDPC codes will demonstrate the effectiveness of various methods for reduced-complexity decoding and reduced control logic. Besides storage applications, these research results are applicable to wireless, wireline and optical communications systems.

Professor Borivoje Nikolić

Dissertation Committee Chair

| 1. | Introduction                                            | 1  |

|----|---------------------------------------------------------|----|

|    | 1.1. Motivation                                         | 1  |

|    | 1.2. Objective                                          | 2  |

|    | 1.3. Scope of work                                      | 4  |

|    | 1.4. Development work in error correction codes         | 5  |

|    | 1.5. Related Work                                       | 12 |

| 2. | Transmission Channels and Coding                        | 14 |

|    | 2.1. Channel capacity                                   | 15 |

|    | 2.2. Partial response channel                           | 17 |

|    | 2.3. Partial response maximum likelihood (PRML) systems | 20 |

|    | 2.4. Concatenated codes in partial response channels    | 22 |

| 3. | Message Passing Algorithms                              | 24 |

|    | 3.1. Constrained coding and SISO decoders               | 24 |

|    | 3.2. SISO algorithms                                    | 27 |

|    | 3.2.1. Maximum a-posteriori decoder                     | 27 |

|    | 3.2.2. Soft-output Viterbi algorithm (SOVA)             | 33 |

|    | 3.2.3. Message passing algorithm used in LDPC decoder   | 35 |

|    | 3.3. Requirements of iterative decoders                 | 38 |

|    | 3.3.1. Computational requirements                       | 38 |

|    | 3.3.2. Message-passing requirements for iterative codes | 41 |

|    | 3.4. Summary                                            | 44 |

| 4. | Architectures of SISO decoders for turbo codes          | 46 |

|    | 4.1. System level considerations                        | 46 |

|    | 4.2. MAP decoder                                        | 47 |

|    | 4.2.1. Forward and backward recursion                   | 48 |

|    | 4.2.2. Combining forward / backward state metrics       | 54 |

|    | 4.2.3. Memory requirements                              | 56 |

|    | 4.3. Soft output Viterbi decoder                        | 61 |

|    | 4.3.1. SOVA decoder architecture                        | 61 |

|    | 4.3.2.      | Add-Compare-Select structures                     | 62  |

|----|-------------|---------------------------------------------------|-----|

|    | 4.3.3.      | Survivor path decoding                            | 67  |

|    | 4.4. S      | ummary                                            | 71  |

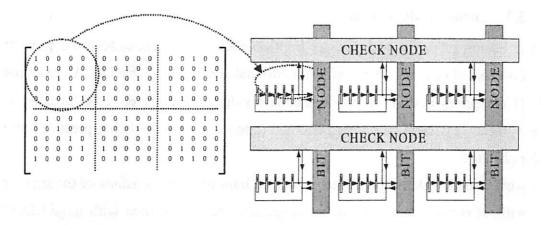

| 5. | LDPC dec    | oder Architectures                                | 73  |

|    | 5.1. P      | arallel architectures                             | 73  |

|    | 5.2. Se     | erial architectures                               | 76  |

|    | 5.3. S      | hared memory architectures and partitioned matrix | 79  |

|    | 5.4. C      | computation blocks                                | 82  |

|    | 5.4.1.      | Fixed-point implementation of lookup table        | 85  |

|    | 5.4.2.      | Fixed-point LDPC decoder building blocks          | 91  |

|    | 5.5. E      | ffects of code construction on implementation     | 92  |

|    | 5.5.1.      | Finite field constructions                        | 92  |

|    | 5.5.2.      | Latin rectangles and improved Ramanujan graphs    | 93  |

|    | 5.5.3.      | Turbo product codes                               | 95  |

|    | 5.6. S      | ummary                                            | 95  |

| 6. | Processing  | g schedules of LDPC decoders                      | 96  |

|    | 6.1. O      | Original concurrent schedule                      | 96  |

|    | 6.2. N      | lew staggered schedule                            | 97  |

|    | 6.3. S      | imulation analysis                                | 100 |

|    | 6.4. P      | ipelined processing elements                      | 102 |

|    | 6.5. S      | ummary                                            | 104 |

| 7. | Physical in | mplementations                                    | 105 |

|    | 7.1. F      | PGA implementation of a MAP decoder               | 106 |

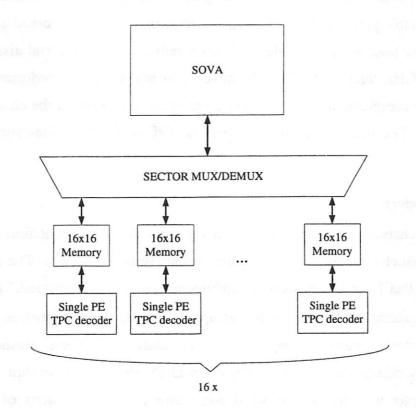

|    | 7.2. A      | ASIC implementation of a SOVA decoder             | 107 |

|    | 7.2.1.      | Design flow                                       | 107 |

|    | 7.2.2.      | Design parameters                                 | 109 |

|    | 7.2.3.      | Physical Tests                                    | 110 |

|    | 7.3. I      | mplementation of an LDPC decoder                  | 115 |

| •  | 7.3.1.      | LDPC decoder based on finite field construction   | 115 |

|    | 7.3.2.      | Design input                                      | 118 |

|     | 7.3    | 3.3. FPGA implementation                 | 122 |

|-----|--------|------------------------------------------|-----|

|     | 7.3    | 3.4. ASIC implementation                 | 122 |

|     | 7.4.   | Other state of the art implementations   | 124 |

|     | 7.5.   | Summary                                  | 125 |

| 8.  | Conclu | usions                                   | 126 |

|     | 8.1.   | Future                                   | 127 |

| 9.  | Appen  | dix A: Pin list for SOVA decoder         | 130 |

|     | 9.1.   | Pad Frame                                | 130 |

|     | 9.2.   | Pin List                                 | 130 |

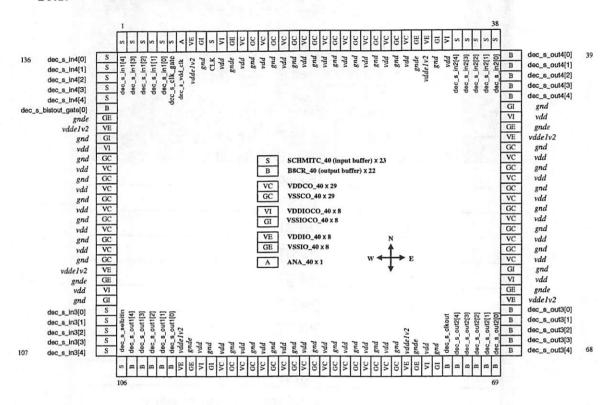

| 10. | Appen  | dix B: PIN LIST FOR LDPC DECODER         | 133 |

|     | 10.1.  | Pad Frame                                | 133 |

|     | 10.2.  | Pin List                                 | 133 |

| 11. | Appen  | dix C: Modifications to ASIC DESIGN FLOW | 138 |

|     | 11.1.  | Design Synthesis                         | 138 |

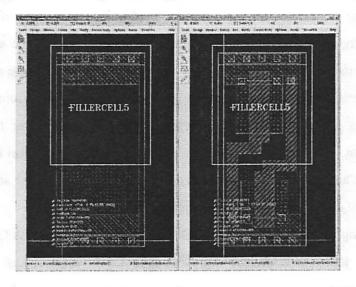

|     | 11.2.  | Placement                                | 139 |

|     | 11.3.  | I/O pad placement                        | 139 |

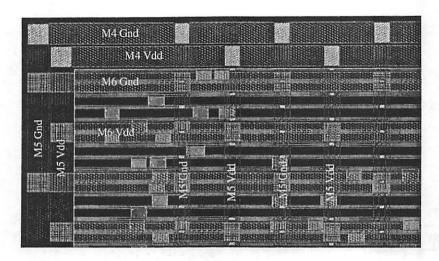

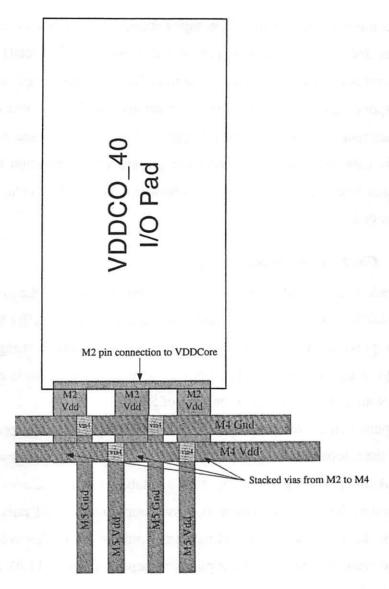

|     | 11.4.  | Power routing                            | 141 |

|     | 11.5.  | Clock tree generation                    | 145 |

|     | 11.6.  | Detailed routing                         | 145 |

|     | 11.7.  | Cadence Opus dfII                        | 147 |

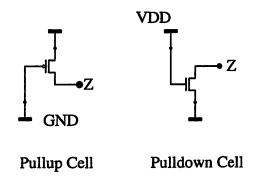

|     | 11.8.  | Pullup and Pulldown Cells                | 148 |

|                         | Turbo (a) encoder and (b) decoder consisting of serial concatenation of a code with EPR4 channel       | .7       |

|-------------------------|--------------------------------------------------------------------------------------------------------|----------|

| Figure 1-2.             | Complexity comparisons between various coding schemes.                                                 | .9       |

|                         | Generic representation of communication systems                                                        |          |

|                         | Plot of relationship between minimum rate of code and available SNR for a d binary transmission.       |          |

| Figure 2-3.             | Various types of partial response channels.                                                            | 18       |

|                         | Impulse response for a PR4 system.                                                                     |          |

| Figure 2-5.             | Impulse response for an EPR4 system.                                                                   | 19       |

| Figure 2-6.             | Rate $\frac{1}{2}$ convolutional encoder; code polynomial is $(1, \frac{1+D}{1+D^2})$                  | 20       |

| Figure 2-7. encoder     | Finite state machine (a) and trellis (b) representation of convolutional                               | 21       |

|                         | Serially concatenated codes that make use of a partial-response channel as a                           | ın<br>23 |

| Figure 2-9.             | Iterative decoder system for serially concatenated codes                                               | 23       |

| Figure 3-1              | Bi-partite graph representation of a 4-state trellis code.                                             | 25       |

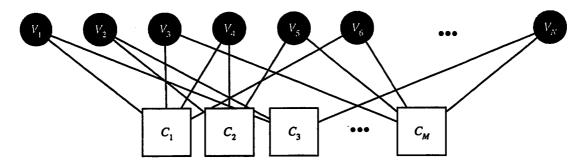

| Figure 3-2.             | Bi-partite graph representation of LDPC codes.                                                         | 26       |

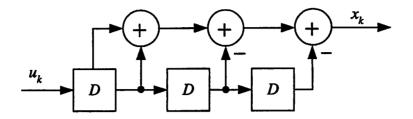

| Figure 3-3.             | Convolutional encoder for $1+D-D^2-D^3$                                                                | 28       |

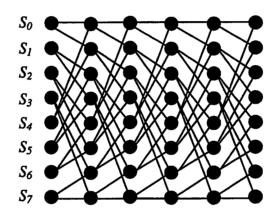

| Figure 3-4.             | Trellis of an 8-state convolutional code                                                               | 28       |

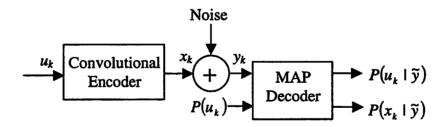

| Figure 3-5.             | Convolutional encoder with MAP decoder                                                                 | 28       |

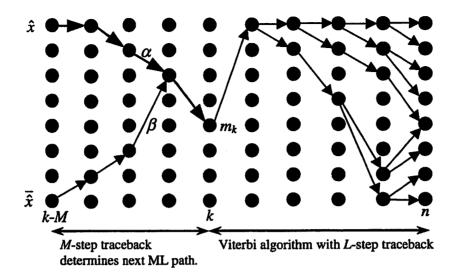

| Figure 3-6.             | Two-stage traceback in a SOVA decoder to determine the two ML paths, $\alpha$                          | ;<br>34  |

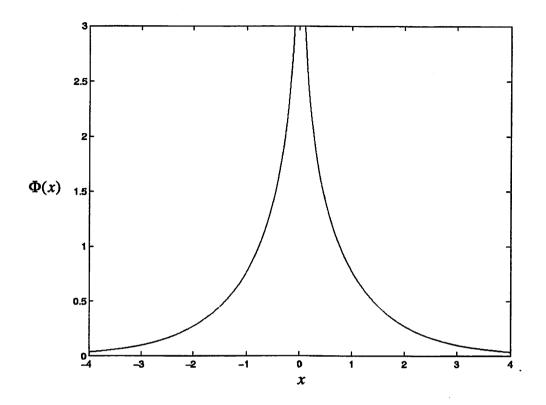

| Figure 3-7.             | Plot of $\Phi(x)$ against x                                                                            | 37       |

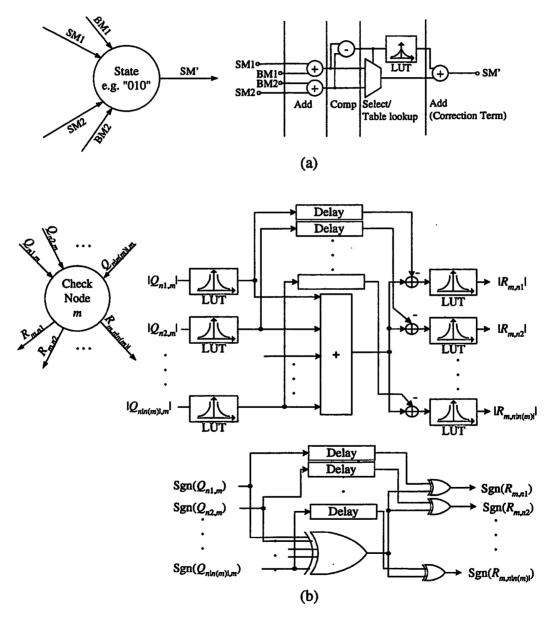

| Figure 3-8. convolution | Arithmetic computation associated with nodes in factor graphs of (a) a nal code, and (b) an LDPC code. | 40       |

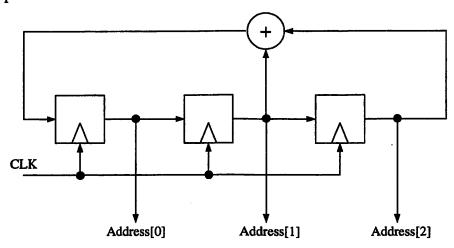

| Figure 3-9.             | Pseudo random interleaver realized with three single-bit registers                                     | 43       |

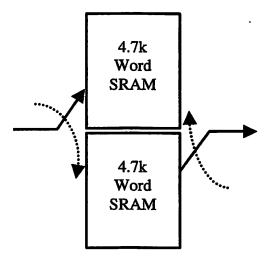

| Figure 3-10 buffers     | ). Interleavers and deinterleavers implemented using alternating read/write                            | 43       |

| Figure 4-1.             | Pipelined blocks in a generic communications receiver.                                                 | 47       |

| Figure 4-2.             | MAP algorithm defines operations on a vertical slice of trellis                                        | 48       |

| Figure 4-4. Retimed ACSA that hides penalty of final addition                                                                                           | 50                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Figure 4-5. Radix-2 trellis and AACS structure.                                                                                                         | 51                 |

| Figure 4-6. Radix-4 trellis and AACS structure.                                                                                                         | 51                 |

| Figure 4-7. Radix-2 concurrent AACS structure.                                                                                                          | 52                 |

| Figure 4-8. Radix-2 compare-select-add-add (CSAA) structure                                                                                             | 53                 |

| Figure 4-9. Transformed add-compare-select-add (ACSA) structure                                                                                         | 53                 |

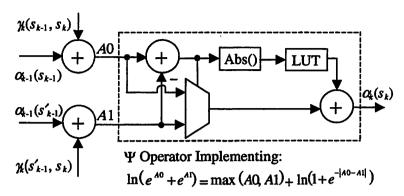

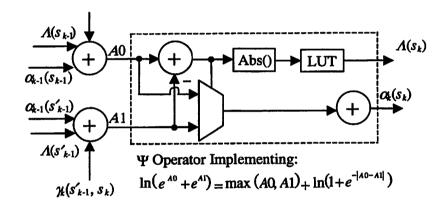

| Figure 4-10. $\xi$ block makes use of a binary tree of $\Psi$ (.) operators                                                                             | 55                 |

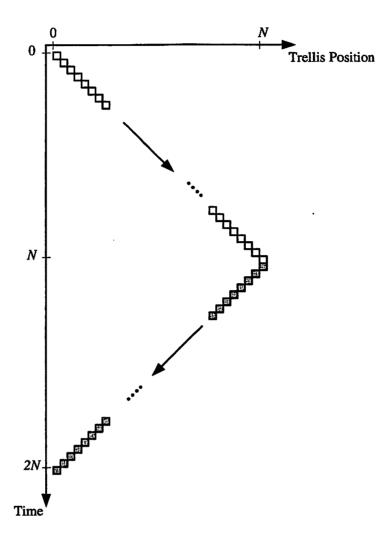

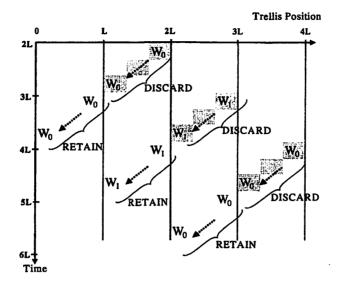

| Figure 4-11. Direct implementation of BCJR requires memory storage of p corresponding to each node in the trellis for the entire length of the block co | oath metrics ode57 |

| Figure 4-12. Backward iteration using 2 overlapping windows, $W_0$ and $W_1$ algorithm. The shaded outputs are not used in the ensuing $\xi$ block      |                    |

| Figure 4-13. State-slice of a MAP decoder structure                                                                                                     | 59                 |

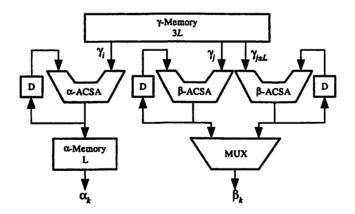

| Figure 4-14. Memory read and write access of branch metrics $\gamma_k$                                                                                  | 60                 |

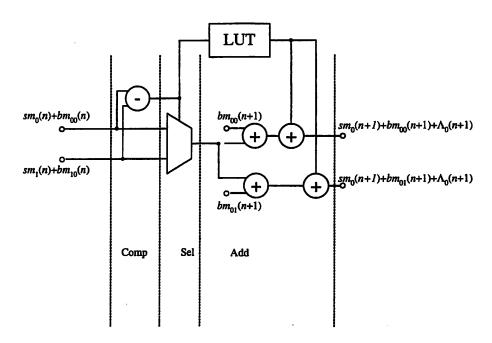

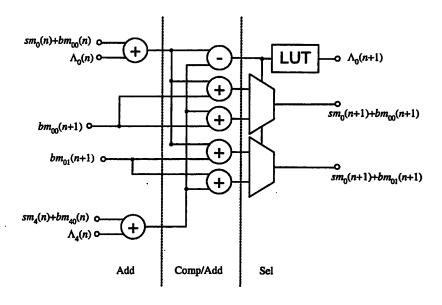

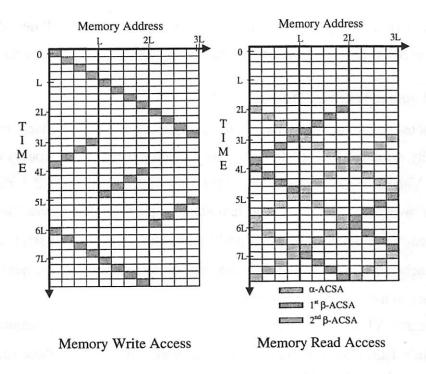

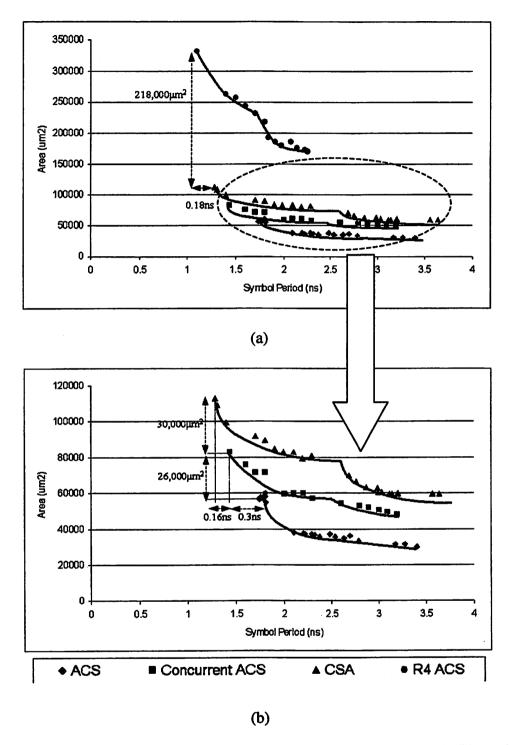

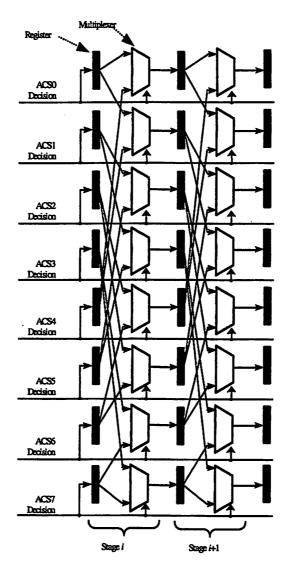

| Figure 4-15. System architecture of 8-state SOVA decoder                                                                                                | 63                 |

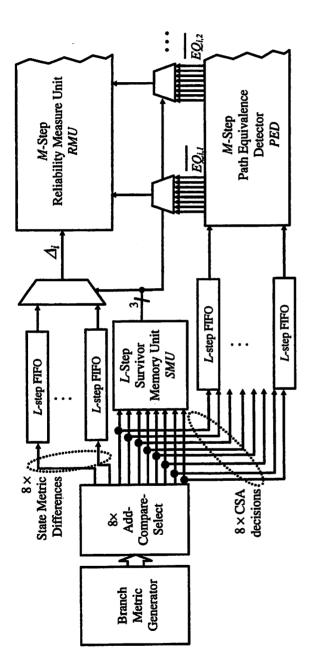

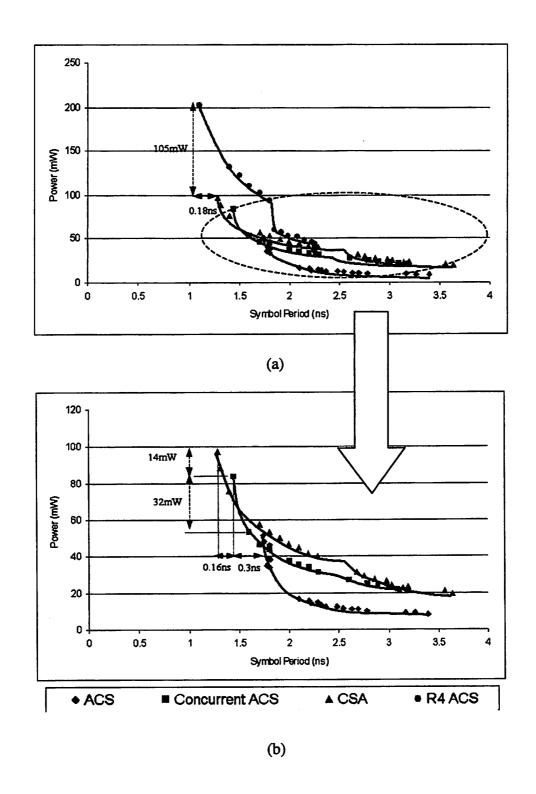

| Figure 4-16. Area comparisons of (a) various ACS structures and (b) a detamagnification of the ACS, concurrent ACS, CSA comparison                      |                    |

| Figure 4-17. Power comparisons of (a) various ACS structures and (b) a demagnification of the ACS, concurrent ACS, CSA comparison                       |                    |

| Figure 4-18. Example 8-state register-exchange survivor memory unit used                                                                                | l in VA-SMU.<br>69 |

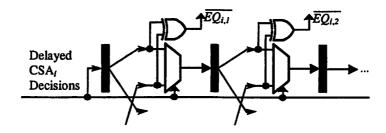

| Figure 4-19. State-slice of register-exchange used in the path-equivalence of                                                                           |                    |

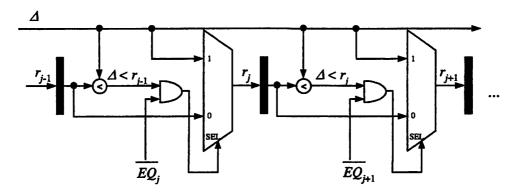

| Figure 4-20. Pipelined section of reliability measure unit (RMU)                                                                                        | 71                 |

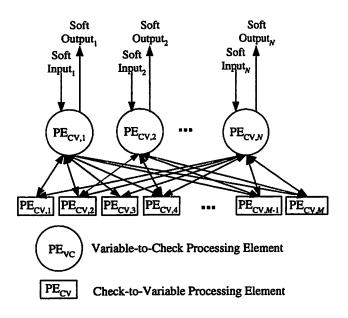

| Figure 5-1. Parallel architecture                                                                                                                       | 74                 |

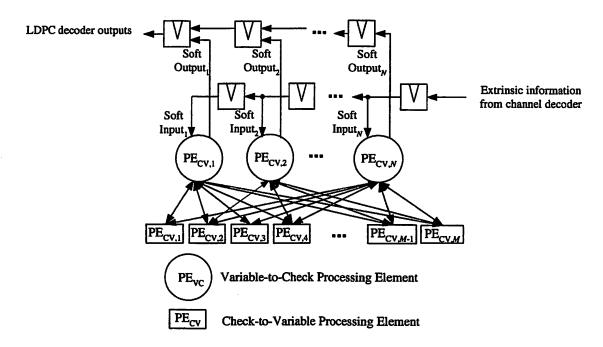

| Figure 5-2. Parallel LDPC decoder with serial input stream from channel d                                                                               | lecoder75          |

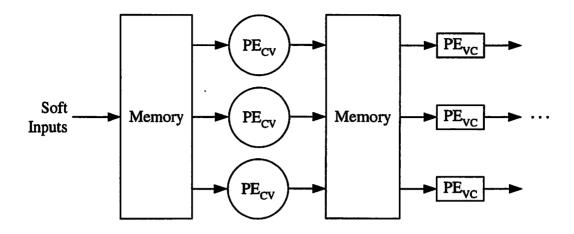

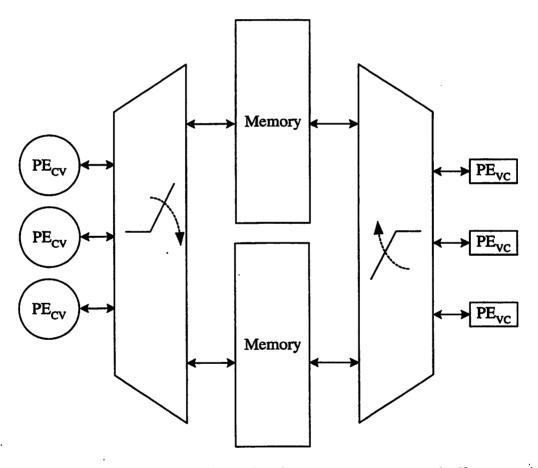

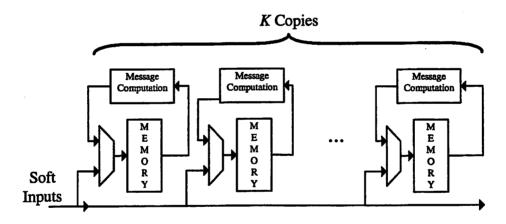

| Figure 5-3. Serial architecture                                                                                                                         | 77                 |

| Figure 5-4. Serial decoding by alternating between two memory buffers coconsecutive blocks of data                                                      | -                  |

| Figure 5-5. Tracing dependencies through a bipartite graph                                                                                              | 79                 |

| Figure 5-6. $M \times N$ parity check matrix partitioned into $j \times k$ subblocks                                                                    | 90                 |

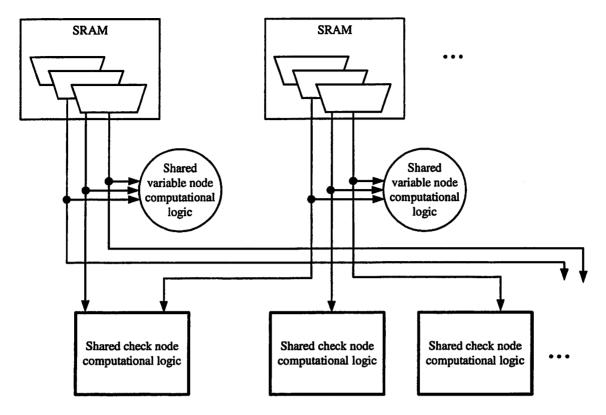

| Figure 5-7. Shared memory architectures with shared computational logic, and interconnect82                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------|

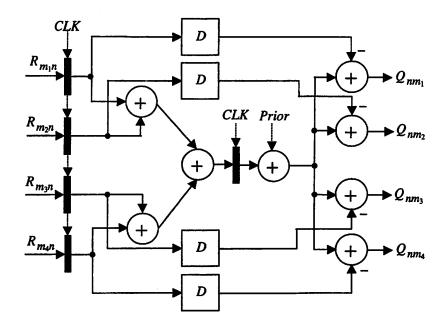

| Figure 5-8. Binary adder tree to compute $Q_{nm}$ messages in a multi-stage pipeline84                                                     |

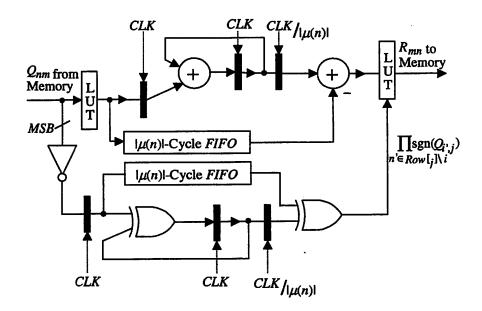

| Figure 5-9. Recursive pipelined implementation to compute $R_{mn}$ messages84                                                              |

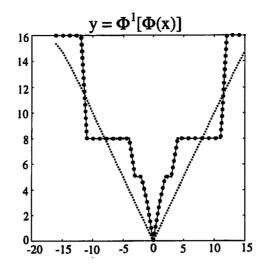

| Figure 5-10. the $\Phi^{-1} \cdot \Phi$ mapping86                                                                                          |

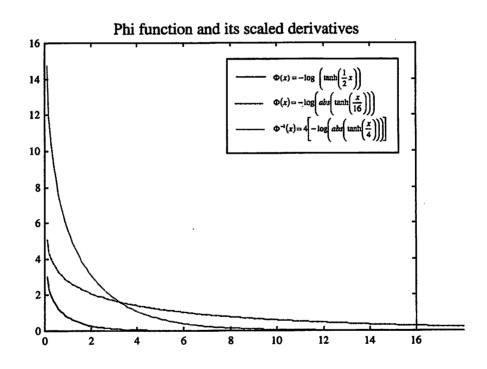

| Figure 5-11. The original $\Phi(\cdot)$ function, and its scaled derivatives86                                                             |

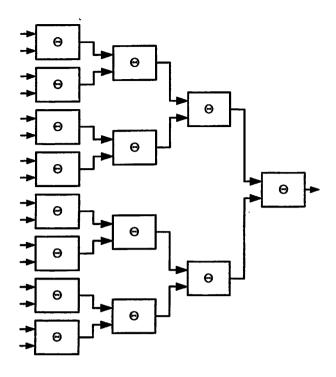

| Figure 5-12. Tree structure of 2-input Θ operators evaluate check-to-variable messages.                                                    |

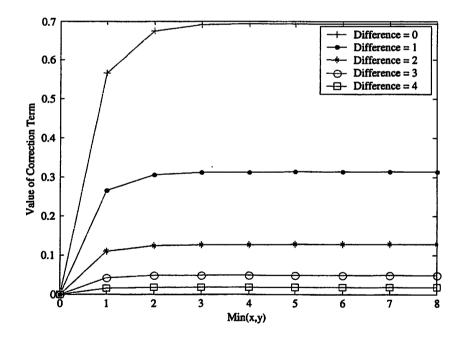

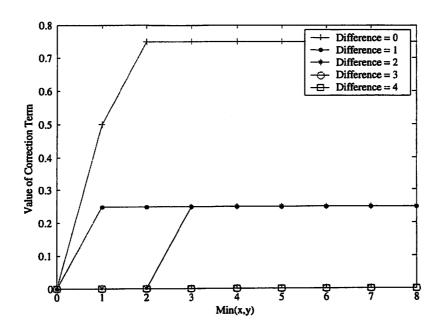

| Figure 5-13. Correction terms $f(x, y)$ plotted against 3-bit integer inputs x and y89                                                     |

| Figure 5-14. Evaluation of correction terms rounded to 0.25 levels90                                                                       |

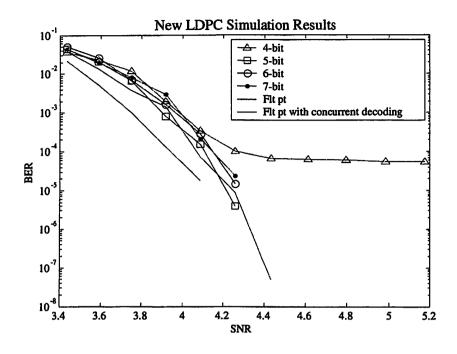

| Figure 5-15. Simulation results with a rate $3/4$ 4095-bit LDPC code based on finite-field construction, with the $\Theta$ approximation91 |

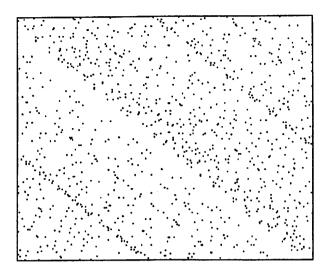

| Figure 5-16. Rendition of 1023×4092 parity check matrix used in codes based on finite fields. Black dots represent non-zero entries93      |

| Figure 5-17. Shared memory decoder architecture for LDPC codes based on Latin rectangles                                                   |

| Figure 5-18. Architecture of TPC decoder partitions the code into 16×16 blocks94                                                           |

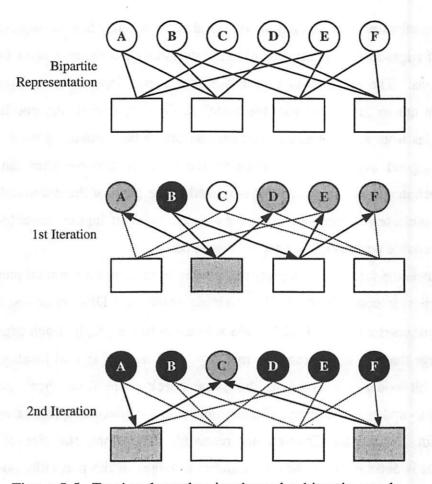

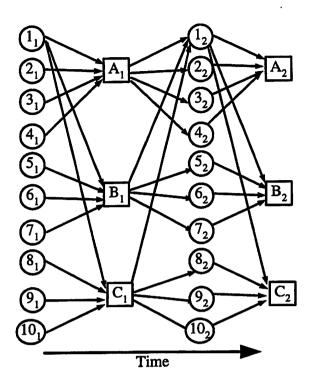

| Figure 6-1. Concurrent decoding schedule of the message passing algorithm; circles represent variable nodes; boxes represent check nodes   |

| Figure 6-2. Staggered decoding schedule of the modified message passing algorithm with $ S(t) =1$ 99                                       |

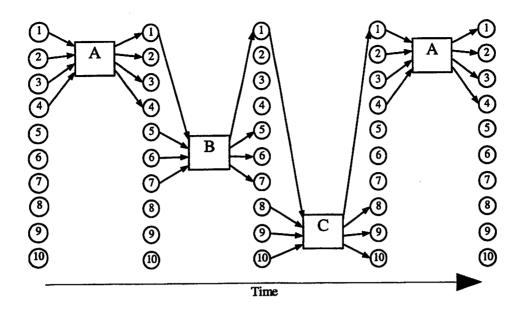

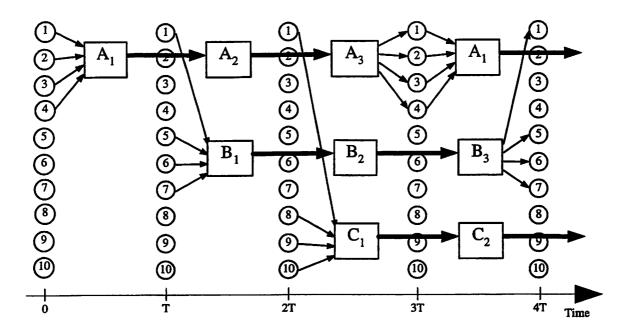

| Figure 6-3. Architecture for random LDPC decoder with <i>K</i> iterations of staggered schedule                                            |

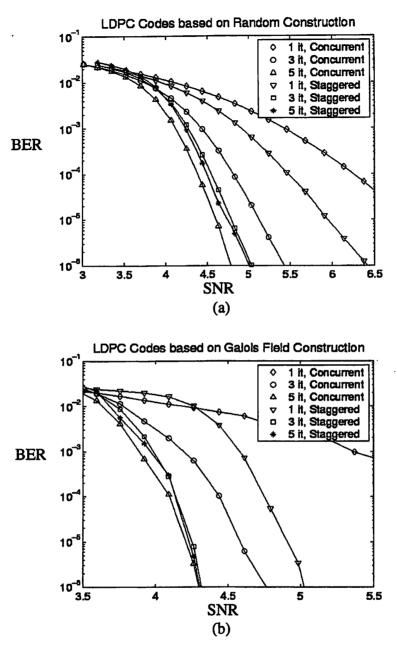

| Figure 6-4. Simulation results from random codes (a), and GF codes (b) with concurrent vs. staggered decoding schedule                     |

| Figure 6-5. Staggered decoding schedule using one processing element with a 3-stage pipeline                                               |

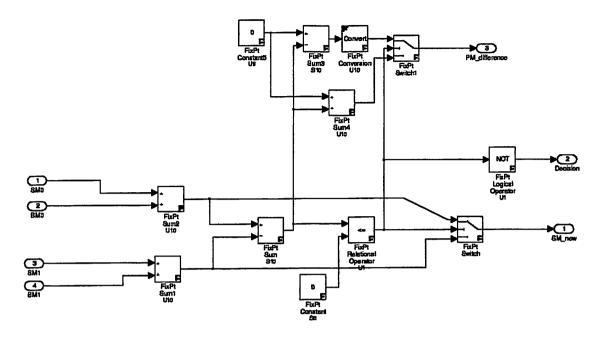

| Figure 7-1. Dataflow graph of the ACS of a SOVA decoder design in Matlab Simulink <sup>TM</sup>                                            |

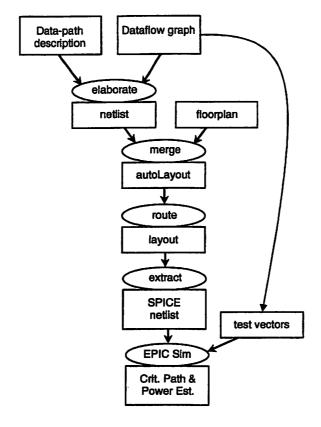

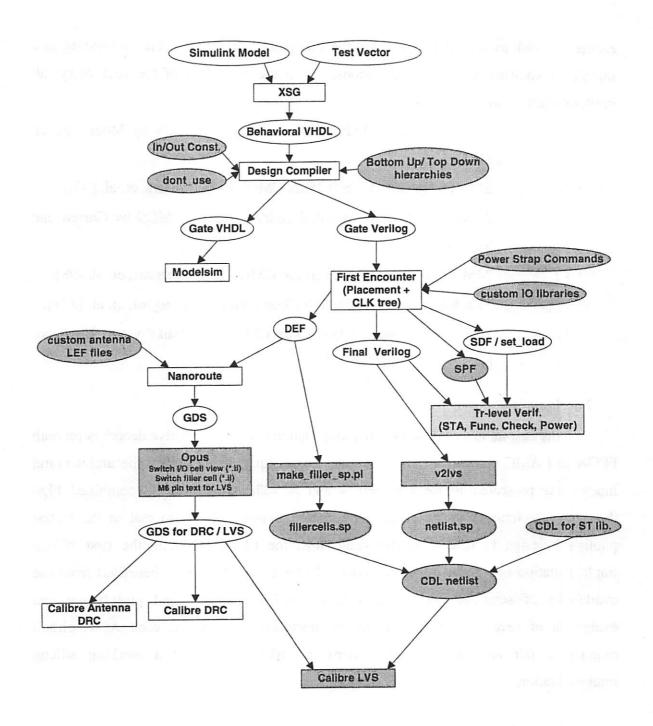

| Figure 7-2. High-level dependency graph for the automated design flow [74]109                                                              |

| Figure 7-3. Printed circuit board used for testing of SOVA decoders110                                                                     |

| Figure 7-4. Setup for logical verification of SOVA decoders111                                                                             |

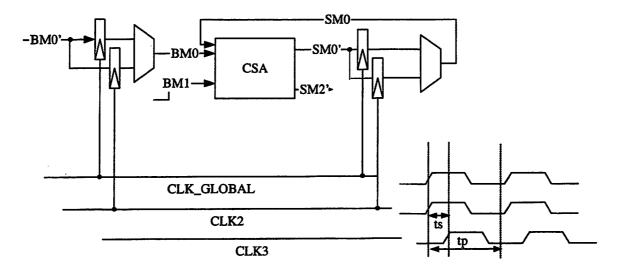

| Figure 7-5. Test structure around CSA for critical path analysis112                                                                        |

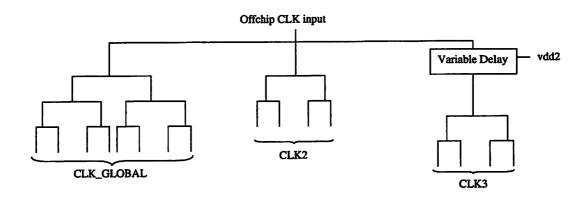

| Figure 7-6. Separate clock trees reduce parasitic effects of additional speed test requirements                                                         | 112    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

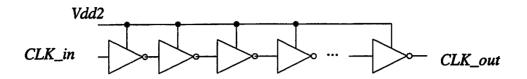

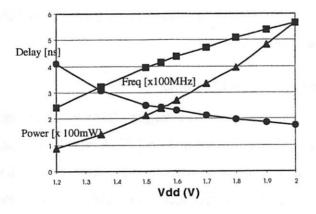

| Figure 7-7. Variable delay controlled by <i>Vdd</i> 2                                                                                                   |        |

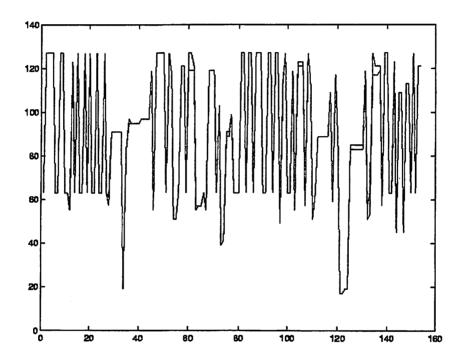

| Figure 7-8. Plot of correct output vectors (blue) and actual vectors output by chip (rskew delay of 1.6ns                                               | ed) at |

| Figure 7-9. Die micrograph                                                                                                                              |        |

| Figure 7-10. Performance of EPR4 SOVA decoder.                                                                                                          |        |

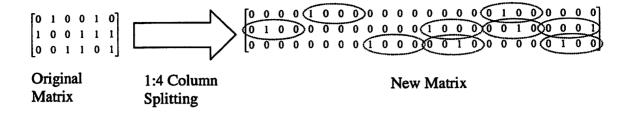

| Figure 7-11. Example of 1:4 column splitting                                                                                                            |        |

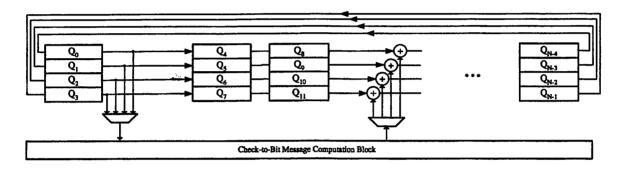

| Figure 7-12. Shift register-based implementation of LDPC code generated from 2D GF(2M) with 1:4 column splitting and a message computation latency of 2 |        |

| Figure 7-13. Horizontal partitioning of the 1023×4092 parity check matrix                                                                               | 117    |

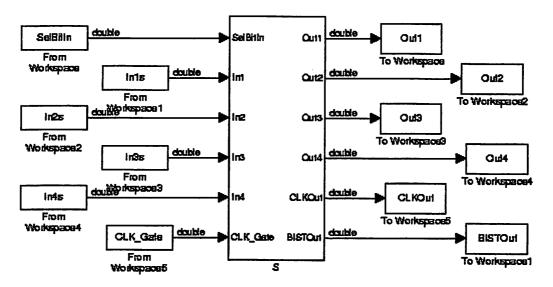

| Figure 7-14. Top level design entry view in Mathworks Simulink                                                                                          | 119    |

| Figure 7-15. Screen capture of top-level LDPC decoder design in Simulink                                                                                | 121    |

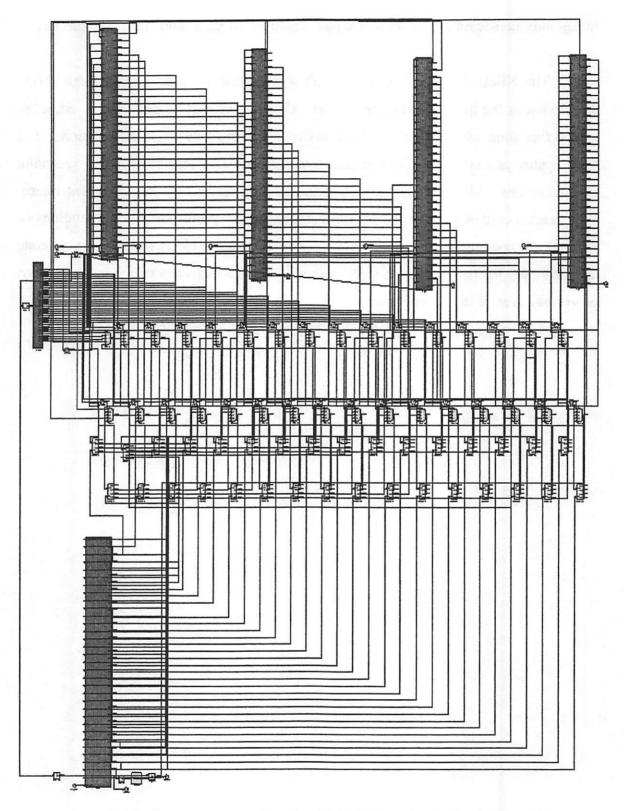

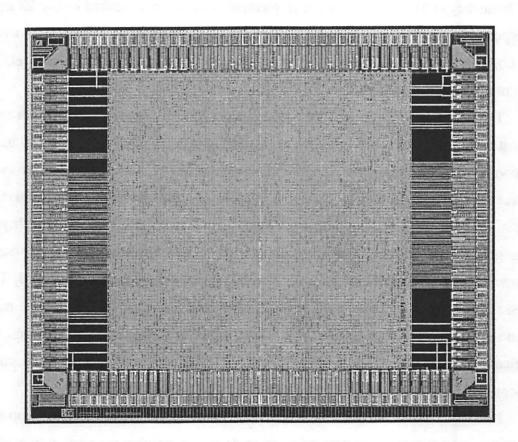

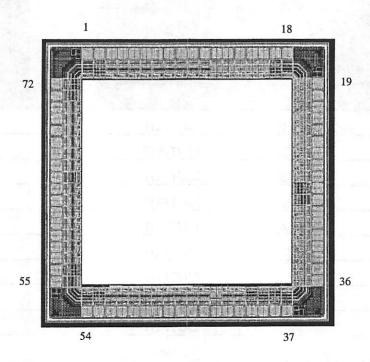

| Figure 7-16. Layout of LDPC decoder in 0.13µm CMOS, occupying 3.2mm × 2.7mm                                                                             |        |

| Figure 7-17. Design methodology. Shaded symbols indicate steps modified from the standard Insecta flow.                                                 | е      |

| Figure 11-1. I/O Pad arrangement                                                                                                                        | 142    |

| Figure 11-2. Power and ground supply grid.                                                                                                              | 143    |

| Figure 11-3. Connection between supply I/O pads and metal4 supply rings                                                                                 | 144    |

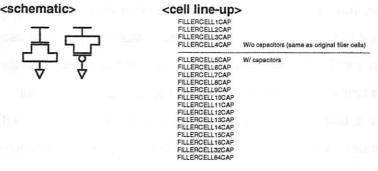

| Figure 11-4. Filler cells with decoupling capacitors                                                                                                    |        |

| Figure 11-5. Pullup and pulldown cells inserted during synthesis.                                                                                       |        |

#### ACKNOWLEDGEMENTS

My lovely wife, Ailee, has supported me in much more ways than meets the eye. She put down everything she had in Singapore, to start a new life with me in United States. She took care of all administrative details, including the final spell check of every journal I ever published. She volunteered to take care of my mother when she was hospitalized. Her happy disposition and composed demeanor calmed my nerves in difficult times. She had made the last four years the best of my life. In short, she has given me more than what I could ever hope to give in return.

I would like to thank my parents, Ng Yoke Foon and Yeo Hoon Chor, my sister, Lou Miang, and brother Eng Khiew, for their constant support and encouragement through every major decision in life, including the choice to return to college after a three-year stint in Singapore. I like to thank my parents-in-law, Ho Choon Meng and Ong Ngoh for their love and financial help. Despite the distance, support from family has remained strong. This has kept Ailee and I motivated throughout this experience.

My advisor, Professor Borivoje Nikolic, played an enormous role in helping me learn more than what I have set out to accomplish. He has been mentor and friend to me. Although working with him can hardly be described as a smooth ride, the results have been more than rewarding. I would also like to thank Professor Venkat Anantharam for providing technical advice over the length of this research, as well as Professor Bob Brodersen and Professor Phil Spector for contributing valuable suggestions to my research.

I survived the pressures and rigors of graduate school, thanks to support from the group of Kangngee Chia, Kinkok Chan, Youyenn Teo, Boonkiat Law, Yeechia Yeo, Ruolei Ng, and alas, four-year-old Sheyuan. These folks were family to me. Incidentally, they were the first people on earth to celebrate my passing of the qualifying examination; the party conveniently took place on the weekend *before* the examination, and proceeded without me. Thanks also to Joshua Garrett, Benny Warlick, Fujio Ishihara, Mike Chen, and Liangteck Pang for riding with me almost every other weekend. For a number of years, I have preached the benefits of mountain biking to everybody I

met at Cory Hall. Little did this group realize that my intentions were to get these weekend warriors to share the burden of carrying emergency bike equipment.

My research has had no shortage of help coming from the students and staff at Cory Hall and the Berkeley Wireless Research Center. Thanks to Payam Pakzad, in particular, for providing most of the theoretical background at the early stages of this work. Thanks to Rhett Davis, Stephanie Augsburger, Tina Smilkstein, and Brian Richards for the help in the SSHAFT design flow, which led to the first tapeout. Thanks to Chen Chang, Kimmo Kuusilinna, Nathan Chan, Joshua Garrett and Fujio Ishihara for help in the BEE design flow, which led to the second tapeout. Radu Zlatanovici, Socrates Vamvakos, Stephanie Augsburger, Isaac Sever, Ben Wild, Dejan Markovic, Roy Sutton, and Kostas Sarrigeoridis, thanks for the constructive criticisms for many of my practice talks. In addition, Tom Boot and Brenda Vanoni have been extremely helpful with purchase reimbursements and last-minute courier packages.

I also had the opportunity to work with a number of distinguished undergraduates from UC Berkeley and University of Wisconsin. Melinda Ler, Jane Nguyen, Steve Fang, Henry Lam, and Allen Chen volunteered their time to work on my project, and contributed in many aspects.

Finally, this research has benefited from the generosity extended from beyond the Berkeley campus. Thanks to Kiyoshi Fukahori, Tom Souvignier, and David Gruetter of Texas Instruments for sponsoring the UC Micro project, and supervising my summer internship in 2000. Thanks to Brian Marcus, Bruce Wilson, and Yuan Xing Lee of IBM for technical advice. Thanks to Pantas Sutardja, Nersi Nazari, Toai Doan, and Zining Wu of Marvell for sponsoring the UC Micro project, and feedback on the progress of the work. Thanks to Bhusan Gupta, Ben Coates and Srikanth Muroor of STMicroelectronics for advice with physical IC design and fabrication of test chips.

#### 1. INTRODUCTION

#### 1.1. Motivation

The development of the communications industry is characterized by exponential growth in volume of data and throughput rates. These growths are accompanied by reduced signal-to-noise ratios at which data is detected. In order to maintain the signal integrity, the level of sophistication in error correction methods is required to keep pace with the communication applications. Modern communication systems employ various forms of redundancies to achieve resilience against interference and noise arising out of a multitude of sources.

The complexity of integrated circuits for signal processing has historically tracked the progress in silicon process technology. Each new silicon process generation has allowed integration of increasingly more complex signal processing schemes into a chip, constrained by cost and power requirements. For example, detectors used in disk-drive read channel integrated circuits have moved from 8-state conventional Viterbi decoders, common in 0.35µm technology, to current, state of the art 0.13µm detectors that incorporate 32-state noise-predictive decoders. Despite an exponential growth in implementation complexity, there is diminishing marginal improvement in bit error rate (BER) performance. The situation is thus ripe for revolutionary changes to the coding and signal processing techniques to challenge currently prevalent classes of error-correction algorithms.

Recently, a new class of error correcting codes has demonstrated performance within 0.5dB of the theoretical limits. These codes comprise two or more concatenated block codes with corresponding decoders that iteratively exchange messages reflecting the confidence of each decoded bit. The messages are based on a probability measure rather than the decisions of the decoded bits. Known as the 'soft' information', the value of this measure is repeatedly accessed and refined over the several iterations of decoding. This approach to decoding represents a departure from traditional error-correction algorithms. These methods are collectively known as *iterative decoding*.

Although various forms of iterative decoding have existed for four decades, the discovery of turbo codes [11] and methods for their decoding in 1993 were largely acknowledged to be the raison d'être for the current surge in iterative decoding research and development, both in academia and industry. A large number of publications have appeared in the areas of code design and ultimate code performance, but somewhat less attention has been paid to decoding architectures, implementation and system issues. As the communication industry begins to explore the deployment of iterative codes that operate at the capacity of a given channel, a detailed understanding of the physical requirements is necessary to provide an unbiased evaluation. Comparison between BER performance and implementation complexities are indispensable, but will require detailed analysis of the intrinsic requirements for implementation of iterative decoders.

#### 1.2. Objective

Effective error correction can reduce the signal-to-noise ratio (SNR) requirement for an end-to-end reliable communication. Lower SNR requirements in a communication system result in a variety of implementation advantages. Each 3dB of coding gain is capable of doubling the system throughput or transmission range, or reducing the required bandwidth by ½. To an end-user, these benefits can translate into extended battery life in portable wireless devices by lowering transmit power, improved range in high throughput wireline systems such as very high speed digital subscriber lines (VDSL), or increased storage densities on magnetic media.

With this in mind, there is a necessity to explore implementation issues of iterative decoders based on turbo codes or low-density parity check codes [56] for future generation of communication systems. The realization of an iterative decoder will weigh the tradeoffs between coding gain performance and factors affecting the implementation: namely, power, throughput and area. A number of platforms are evaluated for their suitability towards realization of the decoder requirements. In particular, the focus will be on viable high-performance ASIC architectures.

The introduction of any new error-correction scheme on silicon must preserve the manufacturability and testability of today's digital systems. Although initial iterative

decoders [111], [120] were based on analog signal processing, these early implementations are sensitive to process and temperature variations, and are difficult to test in production. On the other hand, successful digital implementations, being less susceptible to these adverse effects, will quickly displace the analog predecessors. Hence, the analysis of iterative decoder architectures will be centered on digital implementations.

Iterative decoders are based on block codes, and both encoding and decoding are processed in the context of a block of data. Depending on the application, the number of bits in each block ranges between a few hundred (wireless) to a few thousand (magnetic storage). The soft information exchanged between decoders is typically stored as a three to five-bit fixed-point number. In general, large block sizes and multiple-bit messages combine to form a memory requirement that is an order of magnitude larger than a comparable Viterbi decoder.

The necessity to perform multiple decoding iterations implies that the complexity of the overall decoder is several times larger than traditional decoders. In order to keep the area of implementation and power consumption within practical limits, reduced-complexity methods for the implementation of these decoders will be proposed. In addition, complexity reduction methods are often advantageous towards improving the throughput of the decoders. The analysis explores the tradeoffs between throughput, area and power of implementation, as well as the effects on BER performance of the decoders.

This work demonstrates the effectiveness of the proposed iterative decoder architectures on field-programmable gate arrays (FPGA) and application-specific integrated circuits (ASIC). An FPGA implementation will offer flexibility in code design and effective emulation of iterative decoding algorithms with fixed-point representations. The simulation or run time of an FPGA is expected to be at least an order of magnitude faster than the use of microprocessor-based programs. ASIC implementations offer the best balance between performance, power, and area of implementation. Using the latest process technology, iterative decoding at throughput rates between 500Mb/s and 1Gb/s will be shown.

#### 1.3. Scope of work

This research is aimed at combining the knowledge of iterative decoders at both algorithmic and architectural levels. The results will be presented in three different facets: architectural analysis of decoder structures, code construction exploration with emphasis on hardware implications, and physical demonstration of decoder implementations.

Architectural analysis will permit the realization of iterative decoding hardware with reduced complexities. Effective architectural modifications provide the most impact on the operating performance of the final decoder implementations. The types of structures studied include high throughput decoders applying the Maximum A-Posteriori (MAP) [45] algorithm or the soft-output Viterbi algorithm (SOVA) [38]. These decoders form the building blocks of a turbo decoder. The throughput bottleneck is identified to be the one-step recursion known as the Add-Compare-Select (ACS). This is followed by an evaluation of several competing micro architectures, which demonstrates the optimal range of decoding frequencies that are associated with each option. The architectural evaluations will also include comparisons between serial and parallel structures. The issues and difficulties related to implementation of a parallel or serial architecture are particularly significant to the realization of an LDPC decoder. The decoding algorithm of the LDPC decoder has inherent parallelism, which promotes the implementation of a fully-parallel decoder capable of high-throughput with a low clock rate and low power consumption. In practice, the interconnect properties of LDPC codes exacerbates the exploitation of this parallelism. Alternate architectures, including fully and partially serial LDPC decoders are therefore examined.

The exploration of new code construction techniques will produce LDPC codes that can be efficiently implemented with reasonable amounts of parallel hardware. These new codes combine properties that enhance the feasibility of the decoder implementation, as well as good error-correction performance. Reduced complexity algorithms are also proposed to replace the standard message-passing algorithm that is commonly used with LDPC codes.

The results will be demonstrated on FPGAs and ASICs. The proposed architectures are mapped onto Xilinx Virtex-E FPGAs, and successful implementations of SOVA and LDPC decoders are achieved in 0.18µm and 0.13µm CMOS technologies, respectively. The physical ASIC design includes logical synthesis and back-end placement, routing, and final verification steps. The silicon chips are fabricated and tested on custom-designed digital test-boards.

The magnetic recording channel is used as a demonstration platform. Current trends in magnetic recording demand throughput rates near 1Gb/s. Magnetic read channels typically employ partial response signaling, which influences the choice of iterative decoders. As previously alluded, developments in the magnetic storage industry are centered about improving the storage density. Increased linear densities on magnetic media lead to degraded SNR. However reliability with very low BER must be maintained by the error correction mechanisms.

## 1.4. Development work in error correction codes

During the period from the 1950's to 1993, the development of code construction techniques has largely obtained incremental results in terms of coding gain performance. The historical milestones achieved by various rate-1/2 codes can illustrate this. In 1960's, a Bose-Chaudhuri-Hocquenghem (BCH) code, [113-114], demonstrated BER less than 10<sup>-5</sup> with a SNR that is 5.4dB away from the theoretical limit. With the rise in popularity of the Viterbi decoder [3], these codes were replaced with convolutional codes in the 70's, which achieved similar performance at 4.5dB. By the late 80's, the combination of convolutional codes with Reed-Solomon decoding in magnetic recording applications provided less than 10<sup>-15</sup> BER at 3.9dB from the theoretical limit. Table 1-1 shows that the BER performance has progressed at a rate of less than 1dB per decade between 1960 and 1990.

In 1993, turbo codes demonstrated the ability to achieve 10<sup>-5</sup> BER at only 0.7dB away from the theoretical limit. The impact was revolutionary. Not only has BER performance jumped by 3dB, it has also proven that the theoretical limit of a

transmission channel, based on the communication principles pioneered by Shannon in 1948 [97], was within reach of less than 1dB.

The birth of turbo codes renewed interests in the class of low-density parity check (LDPC) codes. These codes were first proposed in 1962 [56], but were largely ignored because the size of the code, in tens of thousands bits, made it intractable for practical applications. The advent of faster microprocessors in the late 90s paved the way to more effective design and evaluation of both turbo codes and LDPC codes.

In the decade that followed the introduction of turbo codes, iterative decoding has been a subject of continual interest in the communications community. This is evident in the number of new communication standards that have been specified of late. Table 1-2 lists some recent communication standards that have adopted iterative decoding for forward error correction. In addition, iterative decoding is also currently being considered for high performance storage applications that require above 1Gb/s throughput, as well as 10Gb/s optical communications.

TABLE 1-1.

HISTORY OF RATE ½ CODES

| Year | Rate ½ code                        | SNR required for 10 <sup>-5</sup> BER |

|------|------------------------------------|---------------------------------------|

| 1948 | Shannon Limit                      | 0 dB                                  |

| 1967 | (255,123) BCH                      | 5.4dB                                 |

| 1977 | Convolutional Code                 | 4.5dB                                 |

| 1990 | Convolutional + Reed-Solomon Codes | 3.9dB                                 |

| 1993 | Iterative Turbo Code               | 0.7dB                                 |

| 2001 | Iterative LDPC Code                | 0.00245dB                             |

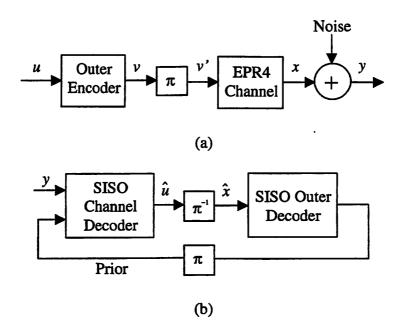

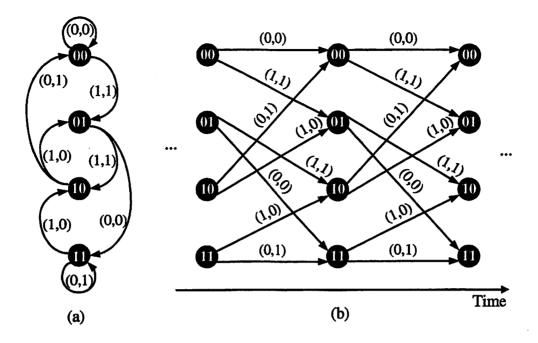

Figure 1-1. Turbo (a) encoder and (b) decoder consisting of serial concatenation of a convolution code with EPR4 channel.

TABLE 1-2

STANDARD SPECIFICATIONS FOR TURBO DECODING

| Standard     | Application               | Iterative Code                         | Throughput                                              |

|--------------|---------------------------|----------------------------------------|---------------------------------------------------------|

| DVB-RCS      | Digital Video Broadcast   | Parallel conc. of 8-state conv. codes  | 68Mb/s (rate 7/8)                                       |

| DVB-S2       | Digital Video Broadcast   | LDPC (block size = 64800 bits)         | 165Mb/s (rates 1/2, 2/3, 3/4, 4/5, 5/6, 7/8, 8/9, 9/10) |

| IEEE 802.16  | Wireless Networking (MAN) | Turbo product codes                    | 25Mb/s (rate 5/6)                                       |

| 3GPP<br>UMTS | Wireless Cellular         | Parallel conc. of 8-state conv. codes  | 2Mb/s (rate 1/3)                                        |

| CCSDS        | Space Telemetry           | Parallel conc. of 16-state conv. codes | 384kb/s (rate 1/2)                                      |

Turbo codes are formed using two or more component convolutional encoders, arranged either in a parallel or serial concatenation, and separated by interleavers. The interleavers construct a long code from short memory convolutional codes. Decoding relies on the iterative passing of posterior-probabilities between two or more soft-input-soft-output (SISO) decoders separated by interleavers and de-interleavers. An example of a serially concatenated turbo code is shown in Figure 1-1. The interleaver and deinterleaver are shown as  $\pi$  and  $\pi^{-1}$  respectively.

One other class of codes that will be analyzed in detail are LDPC codes. These codes are constructed from bipartite graphs consisting of variable nodes and constraint nodes. Each variable node represents a bit, while each constraint node represents a parity checksum of the subset of variable nodes adjacent to it. A sequence of bits that satisfy all the parity constraints is a valid codeword. The iterative decoding of LDPC codes computes messages corresponding alternatively to the variable nodes and the constraint nodes, and passes these messages along edges defined by the underlying graph.

The bipartite graph of an LDPC decoder defines the network for messages to be passed between a large number of nodes. Similar to the interleaver, a direct mapping of the network using hard-wired routes leads to congestion in the interconnect. The congestion can be circumvented through the use of memory. However, unlike the interleavers used in turbo codes, which have a one-to-one connectivity, LDPC graphs have at least a few edges emanating from each variable node. The number of edges is several times larger than that in an interleaver network, and results in higher cost of memory requirement and placing the memory access in the critical path of the decoder.

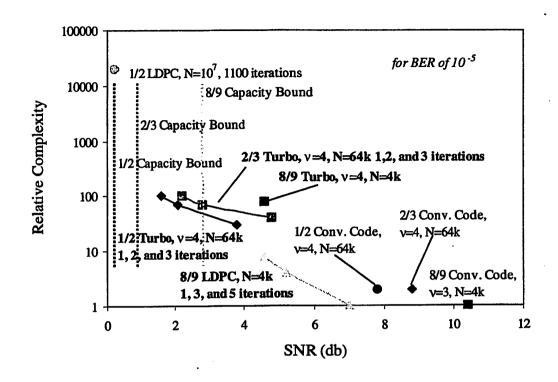

Figure 1-2. Complexity comparisons between various coding schemes.

Although interests have flourished in the development of iterative decoding techniques based on turbo or low-density parity-check codes, difficulties persists at incorporating iterative decoding systems into commercial products. Figure 1-2 shows the relative computational complexity and memory requirement comparisons between conventional convolutional codes and the iterative codes, based on the number of additions required. The plotted values are obtained through 64 iterations of decoding. Both turbo and low-density parity check decoders require soft-input-soft-output decoders, which are about 3 to 5 times the complexity of a convolutional decoder. Additionally, the iterative nature of the decoding leads to overall complexities that are at least an order greater than that of existing convolutional decoders.

The choice of platforms for the implementation of iterative decoding is dictated primarily by the performance constraints such as throughput, power, area, and latency, as well as two often understated and intangible considerations: flexibility and scalability. Flexibility of a platform represents the ease with which an implementation can be

updated for changes in the target specification. Scalability captures the ease of using the same platform for extensions of the application that may require higher throughputs, increased code block sizes, higher edge degrees for low density parity check codes, or increased number of states in the constituent convolutional code of the turbo system.

General-purpose microprocessors and digital signal processors (DSPs) have a limited number of single-instruction-per-cycle execution units but provide the most flexibility. These platforms naturally implement the serial architecture for iterative decoding. Microprocessors and DSPs are used as tools by the majority of researchers in this field to design, simulate, and perform comparative analysis of iterative codes. Performing simulations with BER below 10<sup>-6</sup>, however, is a lengthy process on such platforms. Recently, there has been increased momentum in the use of DSPs in wireless devices built to standards specified by the third generation partnership program (3GPP). These specifications require turbo decoding at throughputs up to 2Mb/s, which is an order of magnitude faster than rates that are typically achievable by a handful of execution units. The advanced DSPs include a "turbo coprocessor" [118], which is essentially an ASIC accelerator with limited programmability.

FPGAs offer more opportunities for parallelism with reduced flexibility. However, fully parallel decoders face mismatch between the routing requirements of the programmable interconnect fabric and edges in a factor graph. FPGAs are intended for datapath intensive designs, and thus have an interconnect grid optimized for local routing. The disorganized nature of an LDPC or interleaver graph, for instance, requires global and significantly longer routing. Existing implementations of iterative decoders on FPGA continue to circumvent this problem by using time-shared hardware and memories in place of interconnect.

Custom ASIC is well suited for direct mapped architectures, offering even higher performance with further reduction in flexibility. An LDPC decoder [1] implemented in 0.16µm CMOS technology achieves a 1Gb/s throughput by fully exploiting the parallelism in the LDPC decoding algorithm. The logic density of this implementation is limited to only 50% to accommodate a large on-chip interconnect. In addition, the parallel architecture is not easily scalable to codes with larger block sizes. For decoding

within 0.1dB of the capacity bound, block sizes with tens of thousands of bits are required [93]. With at least 10 times more interconnect wires, a parallel implementation will face imminent routing congestion, and may exceed viable chip areas.

Current ASIC implementations of turbo decoders [98] are serial, targeting wireless applications. Decoding throughput is 2Mb/s with 10 iterations of the two constituent convolutional decoders. A high throughput ASIC turbo decoder, limited by the interleaver memory access, should be able to decode at throughputs over 500Mb/s. Table 1-3 provides a summary of related implementations on different computational platforms.

Table 1-3

SUMMARY OF PLATFORMS FOR ITERATIVE DECODERS

| Platform               | Architecture | Example                                           | Implementation difficulty                                                                                                                                         |  |

|------------------------|--------------|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                        |              | implementations                                   | •                                                                                                                                                                 |  |

| Microprocessor/<br>DSP | Serial       | 133kb/s rate-1/2 LDPC decoder on DSP [110]        | Limited number of processing units (ALU)                                                                                                                          |  |

| FPGA                   | Parallel     | None                                              | Mismatch of interconnect requirements and capabilities                                                                                                            |  |

| FPGA                   | Serial       | 56Mb/s rate-½ LDPC decoder [109]                  | Control for memory access                                                                                                                                         |  |

|                        |              | 6.5Mb/s 8-state MAP decoder [108] (3 windows)     |                                                                                                                                                                   |  |

| Custom ASIC            | Parallel     | 1Gb/s rate-½ LDPC decoder [1] 1024-bit code block | Routing congestion; Not scalable                                                                                                                                  |  |

| Custom ASIC            | Serial       | 2Mb/s 8-state MAP decoder [33]                    | Interleaver addresses computed on<br>the fly. Implementation was<br>optimized for low power. 500Mb/s<br>high throughput MAP decoder is<br>theoretically feasible. |  |

| Custom ASIC            | Parallel     | Analog MAP decoder in                             | Interleavers not included.                                                                                                                                        |  |

| (Analog)               |              | BiCMOS technology [111]                           | Sensitive to process and temperature variations. Difficult to test in production. Not scalable with improvements in process technology                            |  |

#### 1.5. Related Work

Currently, a handful of research implementations of the Maximum A-Posteriori decoder (used in turbo decoders) [33], [89], [98], soft-output Viterbi decoders [14], [16], and LDPC decoders [31], [96] are available. The industry [1], [113], [114] has also been active in the development of iterative decoders. In general, these efforts are targeted towards wireless applications. Low rate codes such as rate-1/2, or 2/3 codes, are considered, and the decoders have throughput requirements in the order of a few Mb/s and stringent power constraints. In addition, higher throughputs in the neighborhood of Gb/s have been achieved using analog methods [111] [120]. Although these efforts differ from the objective of this work (high-throughput digital implementations with high code rates), they provide valuable data points for comparison of the various architectures.

To date, most efforts in implementations of iterative decoders pay little attention to the construction of the code. Conversely, notable results from [87], [88], and [93] have demonstrated very successful methods for code construction techniques, but with little considerations towards the implementation issues of the decoders. The discontinuity between code construction and decoder implementations often leads to conflicts between the requirements of high performance error-correction codes and the practical constraints that limit the realizations of the decoders. This research is a deliberate departure from the above methodology by considering both code construction and its implications on the decoder architectures. We combine properties that lead to good performing codes with structural designs that permit the practical implementation of the decoders. In this light, the approach has similar objectives with ongoing efforts in LDPC implementations by Mansour and Shanbhag [96], though the detailed approaches are tangential with respect to one another.

Iterative decoding has been considered for use in magnetic recording [37], [66], [68] [69] applications. The codes considered have high code rates (e.g. 8/9, 16/17), and decoder throughput requirements are above 500Mb/s. The prevalent use of a partial response signaling has driven the use of the transmission channel as a rate-1 convolutional encoder. The next chapter will provide details of such a channel model. The partial response channel is described and evaluated for its suitability towards

different types of iterative codes. A number of current channel detection methods are also introduced.

## 2. TRANSMISSION CHANNELS AND CODING

This chapter defines characteristics of a binary communication channel that will be used as a demonstration platform for the proposed iterative decoder architectures. The properties of the channel model are motivated by requirements from magnetic storage application. Conventional magnetic hard disk channels employ partial response maximum likelihood detection methods. As areal recording densities rise towards 100Gb/inch² and beyond, the detection will be required to operate at lower SNRs. Perfect channel equalization, which used to be the basis of forward error correction, becomes increasingly difficult to achieve. Hence there is a requirement for advanced signal processing that will be able to maintain the integrity of the system.

Iterative decoding techniques based on turbo or low-density parity-check codes promise substantial gains in SNR performance. The main difficulties in incorporating iterative decoding systems in existing commercial products are the complexity of the decoder, its size, and implementation of timing recovery, as well as possible byte-error propagation. The successful implementation of these systems will allow the use of iterative decoders in magnetic disk drive read channels with data throughputs that significantly outperform that of current commercial systems, while maintaining manufacturability and testability.

As a vehicle for the performance analysis, a common channel model is described in the following sections. The sector size comprises 4096 user bits, which is a representative block size for most iterative decoding applications such as high-speed wireline and optical communications.

#### 2.1. Channel capacity

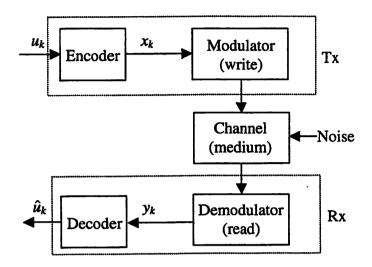

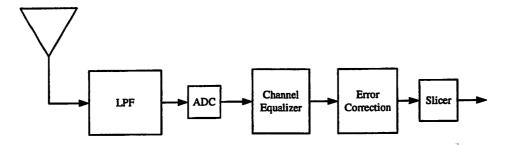

Figure 2-1. Generic representation of communication systems

The classical communication system can be categorized into a number of broad areas depicted in Figure 2-1. The *user* bits,  $u_k$ , are encoded through a pre-determined coding scheme. The output,  $x_k$ , is passed through the modulator and demodulator, which perform physical transmission of the encoded information through a non-ideal channel, which introduces noise, attenuation, phase delay and other detrimental effects. Forward error correction commonly assumes additive white Gaussian noise. This affects the design of the demodulator, which usually includes a channel detector and equalizer.

In 1948, Shannon introduced the general theory of coding. The objectives are two-fold. First, the number of bits required for representation of a given sequence of user bits is minimized (source coding). Secondly, the transfer rate achievable with error-free transmission is maximized (channel coding). The following discussion is restricted to discrete-time systems with discrete-inputs and continuous outputs. This model is relevant for the majority of digital communication systems in which the encoders operate on binary inputs, while the decoders are subject to thermal noise from the channel.

Source coding is based on a statistical model of a generator for the user bits,  $u_k$ . Assuming the simplified special case that these input samples are drawn from a random process  $U_k$  with independent and identically distributed (i.i.d) samples, the average

number of bits required to represent each user bit without distortion is given by the entropy of U, defined in 2.1, with  $\Omega_U$  as the alphabet space of U. Sampling the source is at r repetitions per second, the rate of the source, R, is given by 2.2. The theorem then states the source can be encoded into a bit stream with minimum bit rate of R.

$$H(U) = -\sum_{u \in \Omega_U} p(U_k = u) \log_2 p(U_k = u)$$

(2.1)

$$R = rH(U) \tag{2.2}$$

Likewise, the output of the communication system shown in Figure 2-1 can be considered as a random process  $\hat{U}_k$ . The concept of channel coding defines the capacity per symbol,  $C_S$ , of a channel to be the maximum mutual information, I, between the input random variable U and the output random variable  $\hat{U}$ .

$$I(U\hat{U}) = H(U) - H(U \mid \hat{U})$$

(2.3)

$$C_s = \underset{p(U_k=u)}{Max} I(U,\hat{U})$$

(2.4)

Transmitting at a rate of s symbols per second, the capacity of the channel, C, is given by

$$C = sC_s \tag{2.5}$$

The source coding and channel coding theorems can be combined to form a general channel capacity theorem. Given a source with rate R, and a channel with capacity C, there exist encoders that will ensure asymptotically error-free transmission if R < C.

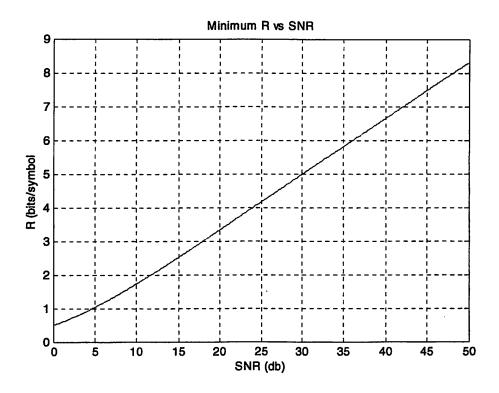

From an implementation perspective, it is often more useful to define the capacity of a channel in terms of the available SNR. For example, the capacity of a band-unlimited channel for binary transmission is defined in 2.6 as a function of the signal power, P, and noise variance, N. A plot of the relationship is shown in Figure 2-2.

$$R \le C = \frac{1}{2} \log_2(1 + P/N) \tag{2.6}$$

Figure 2-2. Plot of relationship between minimum rate of code and available SNR for a band-limited binary transmission.

#### 2.2. Partial response channel

Magnetic read channel systems make use of non-return-to-zero invert (NRZI) modulation. Each binary bit is stored by magnetizing the medium with one of two possible magnetic field directions. The read head contains a ferromagnetic material that hovers less than 20 $\mu$ m above the rotating medium. Changes in magnetic fields induce in a pulse. A positive pulse corresponds to a  $0\rightarrow1$  transition and vice-versa. The isolated pulse shown in Figure 2-3 is modeled as a Lorentzian, with the 50% pulse-width,  $PW_{50}$ , defined as the interval over which the height of the pulse is greater or equal than 50% of its maximum value. As data rates increase, consecutive analog pulses may be overlapped due to the smoothening effect of the bandwidth limitations in the receiver. This phenomenon causes simple peak detection techniques to fail.

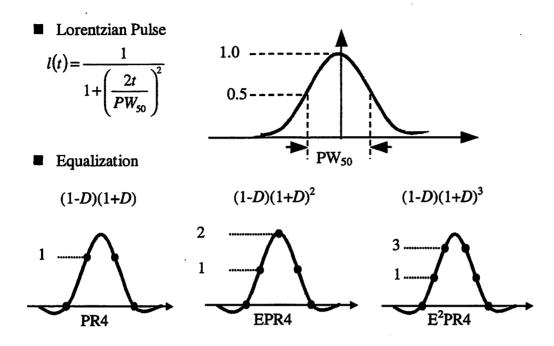

Figure 2-3. Various types of partial response channels.

Partial response systems equalize the isolated pulse to preset response targets shown in Figure 2-3. The sampled sequence of an isolated pulse in a partial response class 4 (PR4) system is [0 1 1 0]. Likewise, an enhanced partial response class 4 (EPR4) system is sampled as [0 1 2 1 0], and a double-enhanced partial response class 4 (EPR4) system, as [0 1 3 1 0].

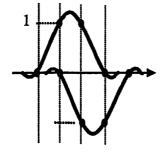

These partial response systems correspond to convolutional codes with different equivalent polynomials. The impulse response of the channel is given by the superimposition of a pair of positive and negative pulses, separated by a sampling period. Figure 2-4 and Figure 2-5 illustrate such behavior and provide the equivalent code polynomials for the two example partial response channels.

Stored bits: 0 0 0 1 0 0 0 Magnetic field:

$$\rightarrow \rightarrow \rightarrow \leftarrow \rightarrow \rightarrow \rightarrow$$

Generated pulses:

Sampled sequence: 0 0 1 0 -1 0 0 0 0 Polynomial:  $1 - D^2 = (1+D)(1-D)$

Figure 2-4. Impulse response for a PR4 system.

Generated pulses:

Sampled sequence:  $0 \ 1 \ 1 \ -1 \ -1 \ 0 \ 0 \dots$ Polynomial:  $1 + D - D^2 - D^3 = (1-D)(1+D)^2$

Figure 2-5. Impulse response for an EPR4 system.

#### 2.3. Partial response maximum likelihood (PRML) systems

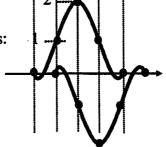

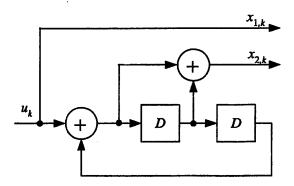

Figure 2-6. Rate ½ convolutional encoder; code polynomial is  $(1, \frac{1+D}{1+D^2})$ .

Since the 1990's 'Partial Response Maximum Likelihood' (PRML) detectors have been the choice detectors for uncoded, linear, intersymbol-interference (ISI) magnetic channels. PRML systems convert the continuous-time signal into discrete-time samples that are sufficient statistics for decoding. Under this conversion, the ISI channel can be treated as a convolutional encoder, with coefficients that are extracted from the equalized pulse shape. This permits the channels to be decoded with the Viterbi algorithm, which is used with convolutional codes to detect the sequence of input bits. The operation of a convolutional encoder and the Viterbi decoder is briefly explained.

Convolutional encoders make use of  $\nu$  shift-registers to store a short history of the input bits. The specific wiring between the shift registers is defined by the code polynomial. A rate ½ convolutional encoder with a polynomial of  $(1, \frac{1+D}{1+D^2})$  is shown in Figure 2-6. The code polynomial contains a recursive feedback loop. For applications that require other code rates, the sequence of  $x_k$  and  $x'_k$  can be punctured accordingly.

Figure 2-7. Finite state machine (a) and trellis (b) representation of convolutional encoder.

The configuration of the registers of a convolutional encoder define a finite state machine. For a binary convolutional encoder with  $\nu$  registers, there are up to  $2^{\nu}$  states. Figure 2-7(a) shows this finite-state-machine with each transition edge labeled with an input/output pair. The demodulator decodes by recreating the sequence of states traversed in the encoder. This introduces an additional time dimension, and the encoder is represented as a time-expanded state-machine, also known as a trellis (Figure 2-7b).

The trellis is a convenient way to represent the evolution of the finite-state machine. In addition, the function of a Viterbi decoder is very often explained as a search for the most likely path through a trellis. The nodes found along this path reflect the sequence of input bits. The binary decisions produced by this decoder are known as 'hard' outputs. These differ from 'soft' output decoders that provide an additional numerical value measuring the confidence of each decoded bit. Soft output decoders are introduced briefly in the next section, and will be elaborated in the context of building blocks for iterative decoding in the following chapters.

In PRML systems, the equivalent code polynomials indicate the number of states required in the Viterbi decoder. For example, the PR4 and EPR4 systems shown in Figure 2-4 and Figure 2-5 require 4-state and 8-state decoders respectively. As the amount of ISI increases with higher recording densities, state-of-the-art detectors evolve to 16-state and 32-state systems. This causes an exponential growth in the complexity of the detectors despite improvements in error correction performance that are measured in less than 0.5dB increments.

# 2.4. Concatenated codes in partial response channels

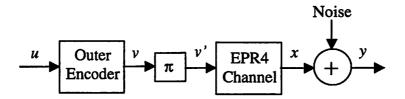

Partial response systems are particularly well suited for implementation of serially concatenated forward error correction codes [68]. Figure 2-8 shows an application of turbo code with an outer encoder serially concatenated with an inner channel encoder.

An interleaver,  $\pi$ , separates and decorrelates the sequence of bits between the two encoders. This allows an iterative suboptimum-decoding algorithm based on uncorrelated information exchange between the two component decoders to be applied. The interleaver improves the coding gain through constructing a long code from short memory convolutional codes. Long codes have larger minimum distance and lower number of low-weight codewords. Interleavers also make the overall code more resilient against burst errors. The minimum sizes of the interleavers that will result in substantial improvement in error performance is in the order of a few hundred bits.

Iterative decoders rely on the repetitive exchange of information and cooperation between two or more soft-input soft-output (SISO) decoders that are matched to the inner or outer codes. Soft-output decoders for convolutional codes implement the Bahl-Cocke-Jelinek-Raviv (BCJR) [4] or Soft-Output Viterbi algorithms (SOVA) [5]). Both algorithms are instances of a larger class of message-passing algorithms, which exploit the linear structure of convolutional codes. An example configuration is shown in Figure 2-9.

Figure 2-8. Serially concatenated codes that make use of a partial-response channel as an inner encoder.

Figure 2-9. Iterative decoder system for serially concatenated codes.

The outer code can be replaced with a LDPC code. Systems employing LDPC encoding do not require explicit interleaver/deinterleavers. By construction, each LDPC code introduces random ordering of at least a few thousand bits. These codes generally have less ordered structures, which leads to increased routing-complexity in LDPC decoders.

In the following chapter, the message-passing algorithm will be discussed in detail. The decoding algorithms for both turbo codes and LDPC codes will be elaborated. These will reveal the implementation requirements of the corresponding decoders.

# 3. MESSAGE PASSING ALGORITHMS

This chapter introduces the concept of constrained coding, which is the basis of all iterative decoding. Iterative decoders rely on the cooperation between two or more SISO decoders. Each SISO decoder implements a message-passing algorithm, which is defined according to the type of coding constraint(s). These concepts are presented in the context of turbo codes and LDPC codes.

The computational complexities and message-passing network requirements associated with realization of message passing algorithms are introduced. These algorithms are analyzed in terms of their VLSI requirements and limitations, and the impact of complexity-reduction techniques on BER performance. For example, the messages are represented in log-likelihood form for the benefit of reduced hardware complexity. These issues will be examined within a unified graphical framework that consists of an interconnected network of variable nodes and constraint nodes [7].

## 3.1. Constrained coding and SISO decoders

Constrained coding is loosely defined as the conversion of a block of user bits into a codeword comprising intersecting subsets of coded bits. The elements in each subset are bounded by a constraint, such as an even parity or a valid codeword under BCH encoding. For instance, consider the two convolutional encoders used in the serially concatenated turbo scheme, which was presented in the last chapter. Each output bit of a convolutional encoder is constrained by an even parity with respect to a small number of bits in the input sequence. As the parity results from the outer encoder feed through the interleaver and into the inner encoder implemented by the EPR4 channel, the sequence of neighboring bits is further constrained.

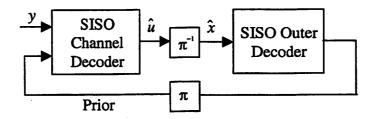

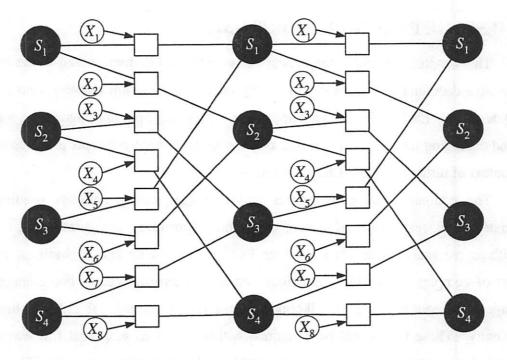

Figure 3-1 Bi-partite graph representation of a 4-state trellis code.

SISO decoders operate with respect to one or more of these constraints specified by the construction of the code. This explains the intuitive use of the two SISO decoders matched to the convolutional codes. In general, the relationship between the variables in the code and the constraints that bind them together can be represented by a bi-partite graph. This graph consists of two classes of nodes: variable nodes and constraint nodes.

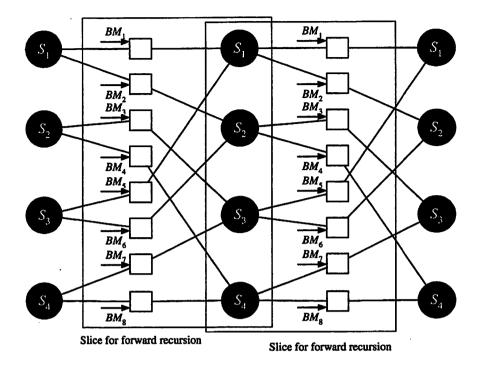

Each variable node is connected to a group of check nodes, and vice-versa. Variable nodes symbolize the outcome of either individual bits, or groups of bits. Each constraint node represents a particular rule that is applied on the adjacent variable nodes. An example bi-partite graph representation of a turbo convolutional code is shown in Figure 3-1. It has the form of a trellis, which characterizes the time-indexed finite state machine within a convolutional encoder. The circles correspond to variable nodes. Dark circles ( $S_{1-4}$ ) represent the states in the trellis, which are formed by stored input values in the encoder, while the light circles ( $X_{1-8}$ ) represent the output values of the encoder. Each constraint node (white squares) binds two adjacent states with the output of the encoder. In other words, by observing the starting and ending states, the corresponding transmitted output of the encoder can also be determined.

Figure 3-2. Bi-partite graph representation of LDPC codes.

The linear structure of the trellis provides an implementation advantage, which is exploited by SISO decoders implementing either the MAP algorithm or the SOVA. The trellis is partitioned into cascading sections of identical slices. Each slice is representative of a sample period. The decoders employ recursive algorithms to implement the decoding operations in a serial fashion. Over time, a number of possible paths through the trellis of the code are reconstructed, and the most-likely outcome will provide a decoded decision. The soft values, or confidence measures relating to each decoded bit, are based on the differences between the aggregate weights associated with these paths.

Another bipartite graph representation, which is used for representing LDPC codes, is shown in Figure 3-2. The variable nodes (dark circles) represent the coded bits (including both user and parity bits) while the constraint nodes (squares) represent even-parity checksum constraints. In general, LDPC codes are described by sparse graphs with far less structure than the previous trellis example.

SISO decoders used with LDPC codes have a finer granularity, and are organized as check node or variable node processing elements (PE) according to the bipartite graph. The edges in the graph correspond to interconnect between the PEs. In the above example, a check node PE,  $C_1$ , inputs a list of messages from the adjacent variable node PEs,  $V_1$ ,  $V_3$ ,  $V_4$ , and  $V_6$ . The computation evaluates a list of posterior probabilities, which are returned to the same set of adjacent variable nodes. Likewise, an example variable node PE,  $V_2$  will be evaluating messages that are passed between  $V_2$  and the adjacent

check node PEs,  $C_2$  and  $C_3$ . These PEs implement the message-passing algorithm, which will be described in Section 3.2.3.

In both turbo codes and LDPC codes, the decoding process begins by initializing each variable node with a prior probability. The prior probabilities are based on some initial assessment provided by the demodulator, such as the sampled signal obtained at the receiver, or any a-priori information of the probability distribution of the set of information bits. The iterative nature is reflected by the repeated evaluation and relay of messages between the two classes of nodes. The process of decoding with respect to distinct constraints and information exchange effectively propagates information throughout the entire graph. It eventually results in a solution based on the weighted inter-dependencies between all variables in the block code.

# 3.2. SISO algorithms

Three particular SISO algorithms are discussed: The MAP decoder and a SOVA decoder, which are used in turbo codes, and the message-passing algorithm used with decoding LDPC codes and block product codes.

# 3.2.1. Maximum a-posteriori decoder

A MAP decoder implements the BCJR algorithm [45]. It is used to obtain the a-posteriori information for partial response channel decoding, as well as outer decoding when a convolutional code is employed as the outer code. A MAP decoder provides the log-likelihood of each bit received from a convolution encoder. Convolutional encoders are typically described by a discrete, causal, linear, time-invariant transfer function, such as the  $1+D-D^2-D^3$  encoder shown in Figure 3-3.  $D^n$  represents an input delayed by n sample periods.

The encoder implements each delay with a single-bit register. A finite state machine, whose states are given by the contents in the registers, can model the entire encoder. An L-delay encoder with binary inputs will therefore have  $2^L$  states. An example of a radix-2 trellis for a binary input system is shown in Figure 3-4.

Figure 3-3. Convolutional encoder for  $1+D-D^2-D^3$ .

Figure 3-4. Trellis of an 8-state convolutional code

Figure 3-5. Convolutional encoder with MAP decoder.

The operation of the MAP decoder is explained in the context of a single convolutional encoder/decoder system, as shown in Figure 3-5. In general, the MAP decoder is a two-input, two-output discrete-time system that is applied to a block of N bits. The inputs are the received symbols  $y_k$ , and prior probabilities,  $p(u_k)$ , of the encoder inputs,  $u_k \in \{0,1\}$ . The time indices are represented by  $k \in \{1, \dots, N\}$ .

Define the set of received symbols as  $\tilde{y} = \{y_1, y_2, y_3, ..., y_N\}$ . Based on the observations,  $\tilde{y}$ , the decoder outputs the conditional probabilities of  $x_k$  and  $u_k$ , expressed as  $p(x_k \mid \tilde{y})$  and  $p(u_k \mid \tilde{y})$  respectively. Recall the trellis representation of the encoder finite state machine. The sequence of  $x_k$  can be deterministically derived from a given sequence of  $u_k$ . Therefore, this discussion will focus on the evaluation of probability measures for  $u_k$ .

In particular, for binary inputs,  $p(u_k \mid \tilde{y})$  comprises two components:  $p(u_k = 0 \mid \tilde{y})$  and  $p(u_k = 1 \mid \tilde{y})$ . The evaluation of these values is simplified using a combination of Bayes' theorem and a different representation of the probabilities, known as the *likelihood ratio*. Bayes' theorem defines that

$$p(u_{k} = 1 \mid \widetilde{y}) = \frac{p(u_{k} = 1, \widetilde{y})}{p(\widetilde{y})}$$

$$p(u_{k} = 0 \mid \widetilde{y}) = \frac{p(u_{k} = 0, \widetilde{y})}{p(\widetilde{y})}$$

(3.1)

In many cases, the only inputs available to the decoder are the observations,  $\tilde{y}$ . Without any a-priori knowledge of the source of user bits,  $u_k$ , it is impossible to determine the denominator,  $p(\tilde{y})$ , in 3.1. The likelihood ratio removes the necessity to compute this value by defining

Likelihood ratio =

$$\frac{p(u_k = 1 \mid \widetilde{y})}{p(u_k = 0 \mid \widetilde{y})}$$

$$= \frac{p(u_k = 1, \widetilde{y})}{p(u_k = 0, \widetilde{y})}$$

(3.2)

Hence the decoder is required to evaluate the joint probabilities,  $p(u_k = 1, \tilde{y})$  and  $p(u_k = 0, \tilde{y})$ . These values are expressed as the sum of transition probabilities in 3.3. A transition between each pair of states,  $(s_{k-1}=S_i, s_k=S_j)$ , is possible only when there is a corresponding connection in the trellis. Each valid transition uniquely defines  $u_k$  and  $x_k$ .

$$p(u_{k} = 1, \tilde{y}) = \sum_{S_{i}, S_{j}} p(u_{k} = 1, s_{k-1} = S_{i}, s_{k} = S_{j}, \tilde{y})$$

$$p(u_{k} = 0, \tilde{y}) = \sum_{S_{i}, S_{j}} p(u_{k} = 0, s_{k-1} = S_{i}, s_{k} = S_{j}, \tilde{y})$$

$$S_{i}, S_{j} \in \{S_{1}, S_{2}, S_{3} \dots S_{2^{L}}\}$$

(3.3)

Given a particular state,  $s_k$  subsequent outputs of the encoder,  $x_{k+1}, x_{k+2}, \ldots$ , are independent of internal state of the encoder prior to step k. This observation provides the following expansion of the individual terms in (3.3). The symbol  $y_k^l$  is defined as the set of received symbols between step k and step l,  $\{y_k, y_{k+1}, y_{k+2}, \ldots, y_l\}$ .

$$p(u_{k}, s_{k-1} = S_{i}, s_{k} = S_{j}, \widetilde{y})$$

$$= p(s_{k-1} = S_{i}, y_{1}^{k-1}) \cdot p(u_{k}, s_{k} = S_{j}, y_{k}^{N} \mid s_{k-1} = S_{i})$$

$$= p(s_{k-1} = S_{i}, y_{1}^{k-1}) \cdot p(u_{k}, s_{k} = S_{j}, y_{k} \mid s_{k-1} = S_{i}) \cdot p(y_{k+1}^{N} \mid s_{k} = S_{j},)$$

$$= \alpha_{k-1}(S_{i}) \cdot \gamma(u_{k}, S_{i}, y_{k}, S_{j}) \cdot \beta_{k}(S_{j})$$

(3.4)

where  $\alpha$ ,  $\beta$ , and  $\gamma$  are defined as:

$$\alpha_{k}(S_{i}) = p(s_{k} = S_{i}, y_{i}^{k})$$

$$= \sum_{j} \alpha_{k-1}(S_{j}) \cdot \gamma(u_{k-1}, S_{j}, y_{k-1}, S_{i})$$

$$\beta_{k}(S_{j}) = p(y_{k+1}^{N} \mid s_{k} = S_{j})$$

$$= \sum_{i} \beta_{k+1}(S_{i}) \cdot \gamma(u_{k+1}, S_{j}, y_{k+1}, S_{i})$$

(3.5)

$$\gamma(u_{k}, S_{j}, y_{k}, S_{i}) = p(u_{k}, s_{k} = S_{i}, y_{k} | s_{k-1} = S_{j})$$

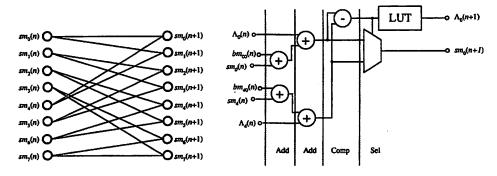

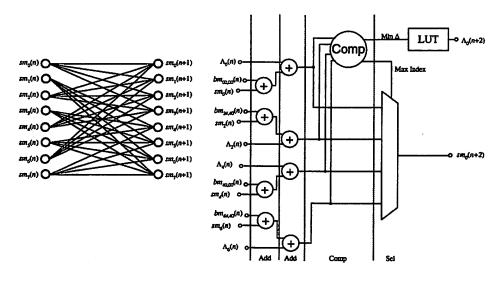

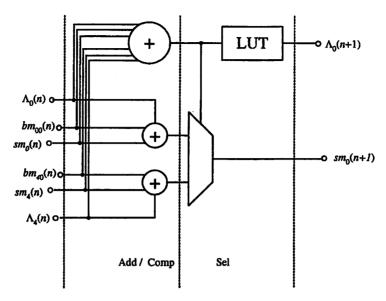

$$= p[u_{k} = f(S_{i}, S_{j})] \cdot p(y_{k} | x_{k} = g(S_{i}, S_{j}))$$