# Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# INTEGRATED CMP METROLOGY AND MODELING WITH RESPECT TO CIRCUIT PERFORMANCE

by

Runzi Chang

Memorandum No. UCB/ERL M04/11

21 May 2004

# INTEGRATED CMP METROLOGY AND MODELING WITH RESPECT TO CIRCUIT PERFORMANCE

by

Runzi Chang

Memorandum No. UCB/ERL M04/11

21 May 2004

#### **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

# Integrated CMP Metrology and Modeling With Respect To Circuit Performance

by

#### Runzi Chang

B.E. (Tsinghua University, Beijing, China) 1996M.S. (University of California, Berkeley) 2001

A dissertation submitted in partial satisfaction of the requirement

for the degree of

Doctor of Philosophy

in

Engineering - Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Costas J. Spanos, Chair Professor Nathan Cheung Professor David Dornfeld

Spring 2004

## The dissertation of Runzi Chang is approved:

Chair Date

Chair Choung 5/11/04

Date

Date

Date

Date

Date

University of California, Berkeley Spring 2004

# Integrated CMP Metrology and Modeling With Respect To Circuit Performance

Copyright © 2004

By

Runzi Chang

#### **Abstract**

Integrated CMP Metrology and Modeling With Respect To Circuit Performance

by

#### Runzi Chang

Doctor of Philosophy in Engineering - Electrical Engineering and Computer Sciences

University of California, Berkeley

#### Professor Costas J. Spanos, Chair

As the semiconductor industry keeps its scaling efforts down to the sub-90nm technology node on the roadmap, the process and materials in the integration are being pushed to the limits. Integrated Circuits (IC) designers nowadays require more than 30% performance improvement from interconnects each technology generation. The introduction of copper and low-k materials in the last few years has been the key move toward that objective. Particularly Chemical-Mechanical Polishing (CMP) has been the enabling technique to planarize the metal surface and define metal layer thickness in contemporary copper Back-End-of-Line (BEOL) technology. However, CMP also introduces undesirable side-effects, including dielectric erosion and metal dishing, which degrade the process quality, cause significant yield losses in BEOL, and negatively affect interconnect performance.

The central theme of this thesis is the integrated metrology and modeling analysis in copper Chemical Mechanical Polishing (CMP) process towards optimizing interconnect and circuit performance. This work pursues special testing mask design and data analyzing techniques that are used to identify and model the sources of yield limiting factors in

copper CMP – namely oxide erosion and copper dishing. The main contributions of the thesis are the following: by applying special test structures design and data analysis, we developed and validated a model for copper dishing, and use that as the basis for process optimization and interconnect performance estimation. As the prerequisite and benefit of our effort, we applied the library-based scatterometry to monitor oxide CMP profile evolution; realized the model-based profile extraction using the e-test data in copper CMP. We set up the process optimization framework based on the contemporary models. Finally, we linked these CMP technology issues to circuit and interconnect design considerations through simulation work.

The validated dishing model integrated with other models and optimization frameworks serve the goal of design for manufacturability in the Back-End-of-the-Line Process. The process models and optimization framework developed in this thesis provide insight into the observables in the state-of-the-art CMP process. By transferring theses principles into the realm of production, these building blocks can provide the opportunity for the process and integrated circuit designers to integrate and fuse information from both perspectives, thus improve the fabrication yield and circuit efficiency in the long term.

Professor Costas J. Spanos

Committee Chairman

# **Table of Contents**

| Chap   | oter 1. | Introduction1                                          |

|--------|---------|--------------------------------------------------------|

| 1.1    | Motiva  | ation1                                                 |

| 1.2    | Thesis  | Organization4                                          |

| Refere | nces    | 5                                                      |

|        |         |                                                        |

| Chap   | oter 2. | Background6                                            |

| 2.1    | Backg   | round on Chemical Mechanical Planarization6            |

| 2.2    | Backg   | round on CMP Metrology9                                |

|        | 2.2.1   | Spectroscopic Reflectometry                            |

|        | 2.2.2   | Spectroscopic Ellipsometry10                           |

|        | 2.2.3   | Scanning Electron Microscopy (SEM)                     |

|        | 2.2.4   | Atomic Force Microscopy (AFM)13                        |

|        | 2.2.5   | Scatterometry14                                        |

|        | 2.2.6   | Monitoring CMP Processes in a Production Environment15 |

| 2.3    | Backg   | round of CMP Process Modeling17                        |

|        | 2.3.1   | Inter-Layer Dielectric (ILD) CMP Process Modeling17    |

|        | 2.3.2   | Copper CMP Process Modeling22                          |

| Refere | nces    | 24                                                     |

| Chap   | oter 3. | Integrated Characterization of Layout Dependency in       |

|--------|---------|-----------------------------------------------------------|

| Copp   | per Da  | amascene Process27                                        |

| 3.1    | Introd  | uction27                                                  |

| 3.2    | Test P  | attern Design30                                           |

| 3.3    | Design  | of Experiments35                                          |

| 3.4    | Metro   | logy41                                                    |

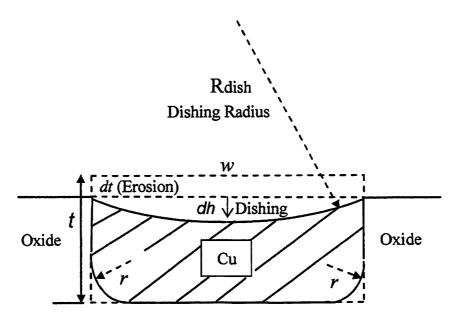

| 3.5    | Coppe   | r CMP Process Modeling Using the Dishing Radius Concept44 |

|        | 3.5.1   | Erosion Modeling45                                        |

|        | 3.5.2   | Dishing Modeling53                                        |

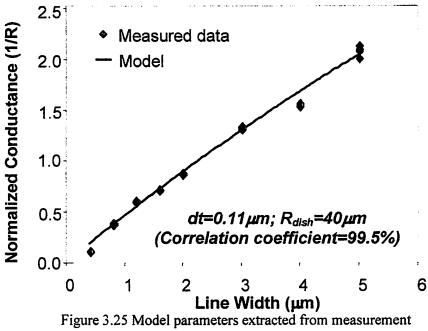

| 3.6    | Model   | -Based 2D Profile Extraction54                            |

|        | 3.6.1   | Key Ideas55                                               |

|        | 3.6.2   | Profile Modeling56                                        |

|        | 3.6.3   | Measurements and Validation57                             |

| Refere | ences   | 62                                                        |

|        |         |                                                           |

| Chap   | oter 4. | Model-Based CMP Process Optimization65                    |

| 4.1    | CMP I   | Process Performance Metrics67                             |

|        | 4.1.1   | Material Removal Rate (MRR)68                             |

|        | 4.1.2   | Selectivity68                                             |

|        | 4.1.3   | Inter-layer Dielectric (ILD) Erosion70                    |

|        | 4.1.4   | Metal Dishing70                                           |

| 4.2   | Frame    | work of Proce    | ess Performance Optimization                     | 71      |

|-------|----------|------------------|--------------------------------------------------|---------|

|       | 4.2.1    | Models Used      | l in the Framework                               | 71      |

|       |          | 4.2.1.1          | MRR and Erosion Model                            | 71      |

|       |          | 4.2.1.2          | Metal Dishing Model                              | 73      |

|       |          | 4.2.1.3          | Selectivity Model                                | 76      |

|       | 4.2.2    | Weighting C      | coefficients and Optimization Discussion         | 77      |

| 4.3   | Exam     | ples on Proces   | s Optimization                                   | 81      |

|       | 4.3.1    | Linear Optin     | nization                                         | 83      |

|       | 4.3.2    | Application      | of Taguchi's Method                              | 86      |

| Refer | ences    |                  |                                                  | 92      |

| Cha   | nter 5   | Effects o        | f CMP-Related Process Variations on              |         |

|       |          |                  |                                                  |         |

| Inte  | rconne   | ect/Circuit      | Performance                                      | 96      |

| 5.1   | Desig    | n for Manufac    | turability Overview                              | 96      |

| 5.2   | The E    | affect of Proces | ss Variations on Circuit Performance from CMP Pr | ocess   |

| Techr | nology F | Perspective      |                                                  | 99      |

| 5.3   | Mode     | l-Based Interc   | onnect Performance Simulation Results and Discus | sion106 |

| Refer | ences    |                  |                                                  | 118     |

| Cha   | pter 6. Conclusions and Future Work | 123 |

|-------|-------------------------------------|-----|

| 6.1   | Conclusions                         | 123 |

| 6.2   | Future Work                         | 125 |

| Refer | rences                              | 126 |

# **List of Figures**

| Figure 1.1    | Typical chip cross section of hierarchical scaling of interconnects2          |

|---------------|-------------------------------------------------------------------------------|

| Figure 2.1    | A 90nm copper and low-k interconnect technology (source: NEC)7                |

| Figure 2.2    | Typical components in a CMP system                                            |

| Figure 2.3    | Spectroscopic reflectometry measurements10                                    |

| Figure 2.4    | Spectroscopic Ellipsometry Measurements11                                     |

| Figure 2.5    | A cross-sectional view of a sample using SEM12                                |

| Figure 2.6    | A top-down view of an E-beam Lithography sample using SEM13                   |

| Figure 2.7    | MIT oxide CMP characterization mask set20                                     |

| Figure 2.8    | Window used to calculate effective density21                                  |

| Figure 3.1    | Complex copper interconnects fabricated with IBM's damascene process          |

|               |                                                                               |

| Figure 3.2    | Single (right side) and dual (left side) damascene process flow illustrations |

|               |                                                                               |

| Figure 3.3    | Illustration of oxide erosion and copper dishing problems during copper       |

| damascene pr  | ocess                                                                         |

| Figure 3.4    | Cell design for the electrical characterization of dishing effect in copper   |

| damascene pr  | ocess 31                                                                      |

| Figure 3.5    | Schematic representation of the four point measurement method32               |

| Figure 3.6    | Mask #1 layout33                                                              |

| Figure 3.7    | Mask #2 layout34                                                              |

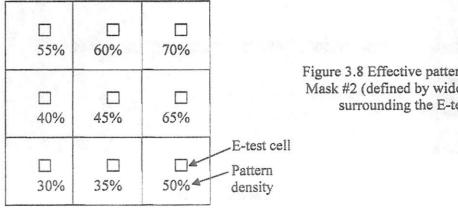

| Figure 3.8    | Effective pattern densities of Mask #2 (defined by wider metal lines          |

| surrounding t | he E-test cells34                                                             |

| Figure 3.9                | Process flow chart of the single damascene fabrication                  | 5 |

|---------------------------|-------------------------------------------------------------------------|---|

| Figure 3.10               | Surface of the perforated IC1000 pad39                                  | 9 |

| Figure 3.11               | The standard IC1400 pad with K-groove                                   | 9 |

| Figure 3.12               | Comparison of the pre and post-CMP images evaluated by an optical       |   |

| microscope.               | 4                                                                       | 2 |

| Figure 3.13               | Post-CMP images evaluated by an optical microscope for two different    |   |

| masks #1 (to <sub>l</sub> | p picture) and #2 (bottom picture)43                                    | 3 |

| Figure 3.14               | Calculation of the maximum deflection of the pad (at the center of the  |   |

| beam)                     | 4                                                                       | 5 |

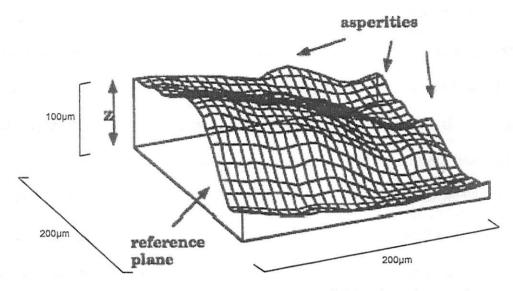

| Figure 3.15               | Topology scan of a commercially available polyurethane pad4             | 7 |

| Figure 3.16               | Proposed wafer pad contact mechanism under typical Chemical             |   |

| Mechanical F              | Polishing setup4                                                        | 7 |

| Figure 3.17               | Illustration of the Dishing Radius concept4                             | 9 |

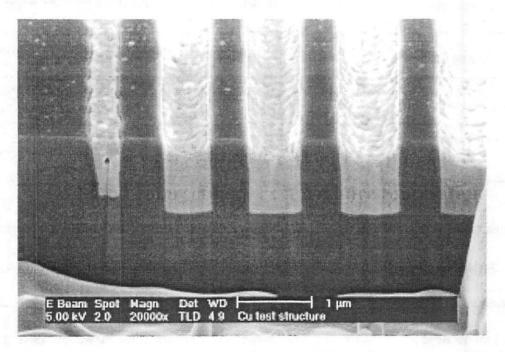

| Figure 3.18               | Post-CMP cross-sectional pictures of copper lines (1.6 and 0.4 microns) |   |

|                           | 5                                                                       | 0 |

| Figure 3.19               | Surface profiling curves validate post-CMP surface dishing shape5       | 1 |

| Figure 3.20               | Line profilometry scans of post-CMP features (Experiments No. 1 and 3)  | ŀ |

|                           | 5                                                                       | 2 |

| Figure 3.21               | The measured amount of oxide erosion as a function of copper pattern    |   |

| density on M              | ask #254                                                                | 4 |

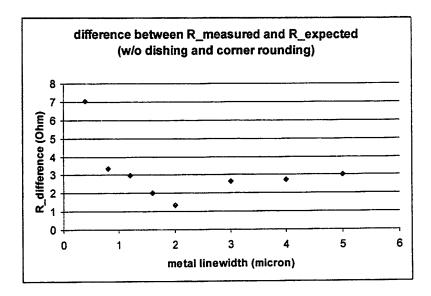

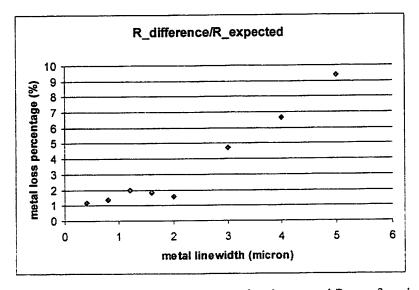

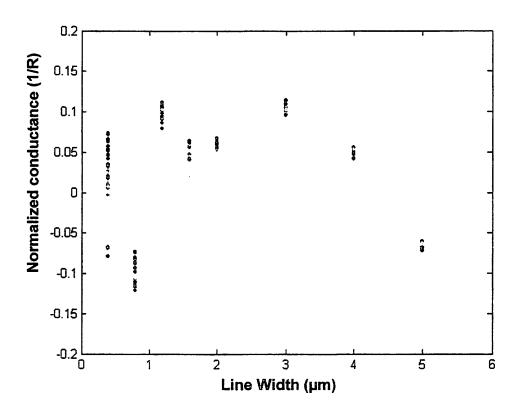

| Figure 3.22               | The difference between measured and expected R as a function of metal   |   |

| linewidth                 | 55                                                                      | 5 |

| Figure 3.23     | The difference between measured and expected R as a function of metal          |

|-----------------|--------------------------------------------------------------------------------|

| linewidth nor   | malized by R_expected55                                                        |

| Figure 3.24     | Profile modeling for post-CMP metal lines57                                    |

| Figure 3.25     | Model parameters extracted from measurement61                                  |

| Figure 3.26     | Residues plot after the extraction61                                           |

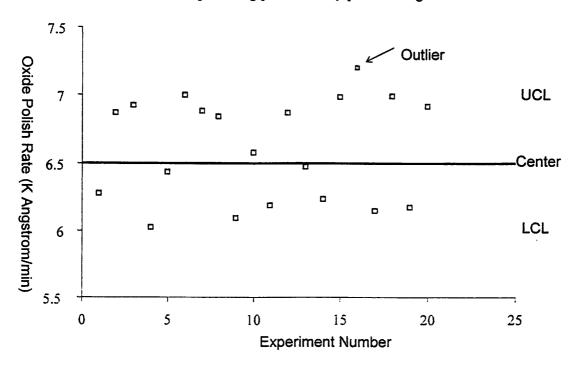

| Figure 4.1      | Illustration of the basic components of the control chart using Oxide          |

| polish rate as  | an example: data points, center line, Upper Control Limit (UCL), Lower         |

| Control Limit   | (LCL) and Outlier66                                                            |

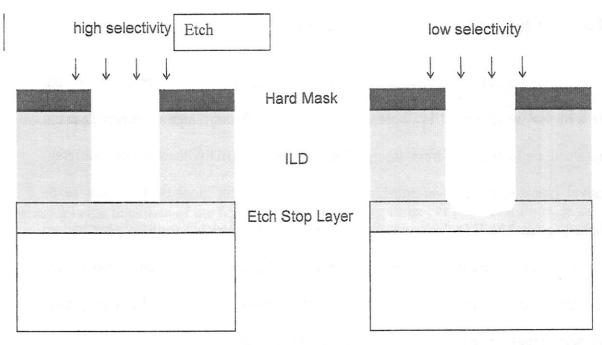

| Figure 4.2      | Illustration of the concept of selectivity - the scenario in plasma etching    |

| where high se   | lectivity is desired69                                                         |

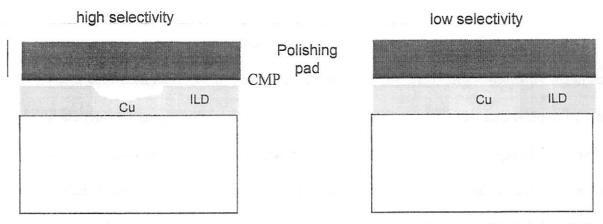

| Figure 4.3      | Illustration of the concept of selectivity – the scenario in the overpolishing |

| step of the dan | mascene process where low selectivity will be helpful in reducing metal        |

| dishing         | 69                                                                             |

| Figure 4.4      | During the overpolishing step in damascene process, the bulk ILD area has      |

| no erosion by   | definition72                                                                   |

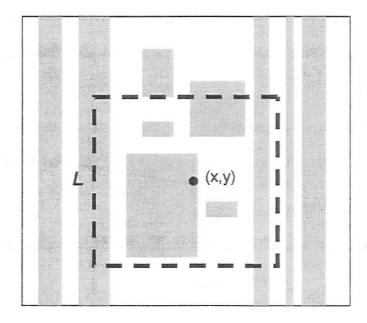

| Figure 4.5      | Illustration of the effective pattern density calculation for the point of     |

| interest (x,y)  | using a square window (size L) in damascene process73                          |

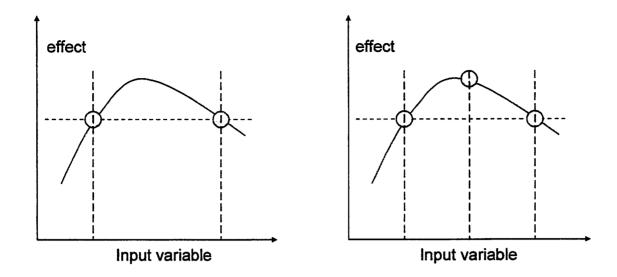

| Figure 4.6      | Cases when a three or more level becomes necessary: A two level study          |

| (the left) will | give the illusion of no effect from the factor while a three level study (the  |

| right) will und | cover the curvature effect75                                                   |

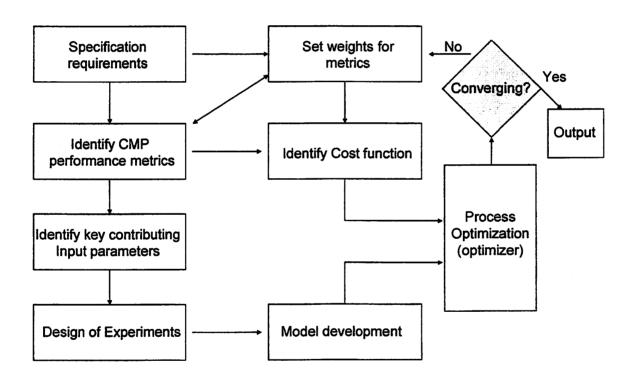

| Figure 4.7      | Flowchart of the CMP process optimization framework80                          |

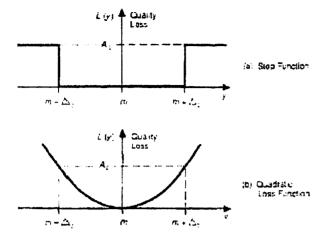

| Figure 4.8      | The quadratic loss function82                                                  |

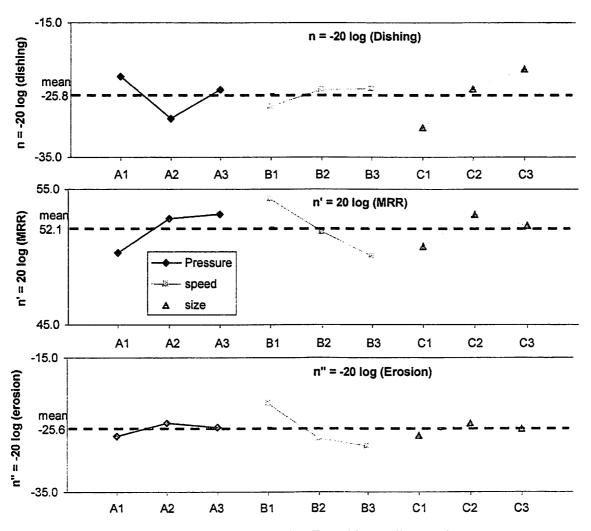

| Figure 4.9      | Data analysis using Taguchi's quality metrics90                                |

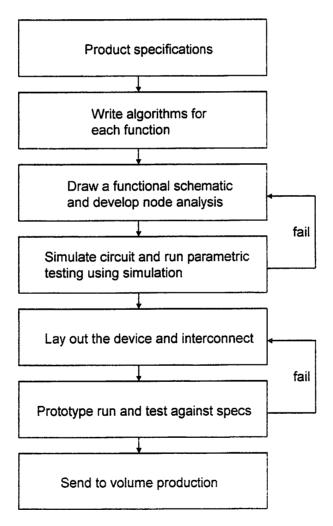

| Figure 5.1     | A typical modern computer-aided integrated circuit design flow97          |

|----------------|---------------------------------------------------------------------------|

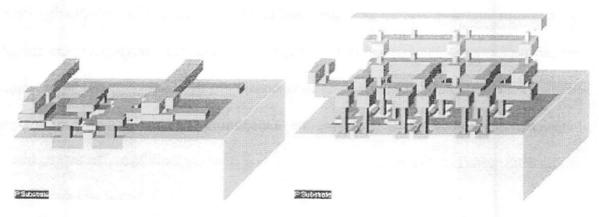

| Figure 5.2     | Interconnect complexity increases in 0.25 µm technology (right) compared  |

| with the 0.7µ  | m technology (left)100                                                    |

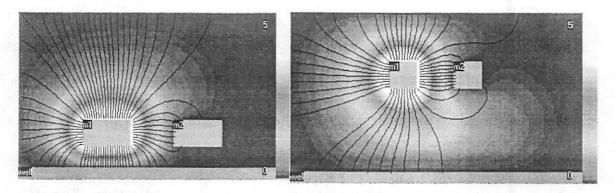

| Figure 5.3     | Simulation results illustrate the increased crosstalk between neighboring |

| wires as techr | nologies shrink 0.7μm (left) to 0.25μm (right)100                         |

| Figure 5.4     | 10% post-CMP ILD thickness variation observed101                          |

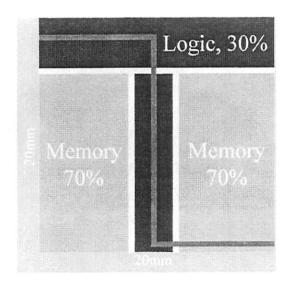

| Figure 5.5     | Pattern density difference on the mask between the logic and memory area  |

|                | 101                                                                       |

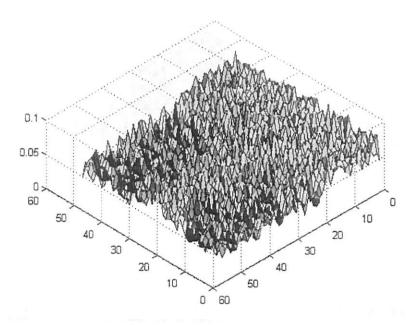

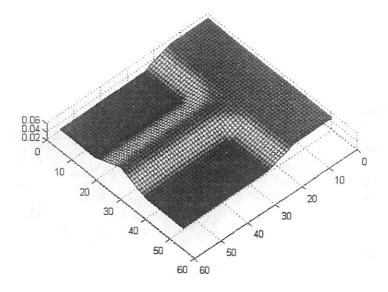

| Figure 5.6     | Systematic ILD thickness variations due to pattern density difference102  |

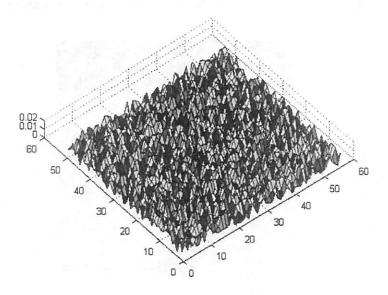

| Figure 5.7     | The truly random ILD thickness variations due to process uncertainty 102  |

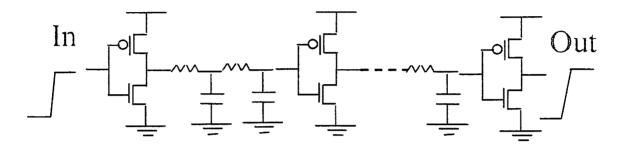

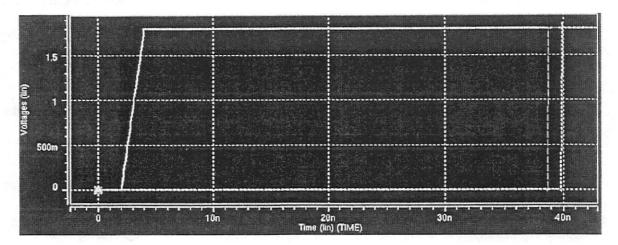

| Figure 5.8     | 128-stage inverter simulations with long interconnect                     |

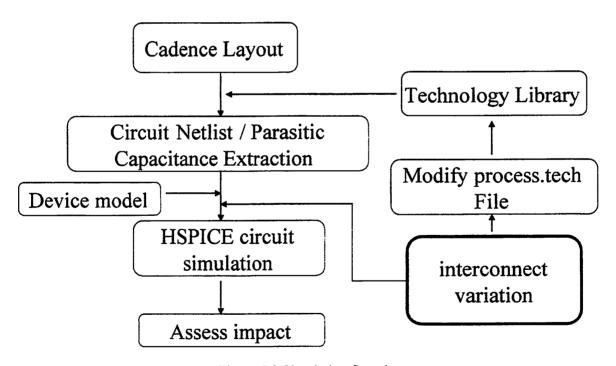

| Figure 5.9     | Simulation flowchart                                                      |

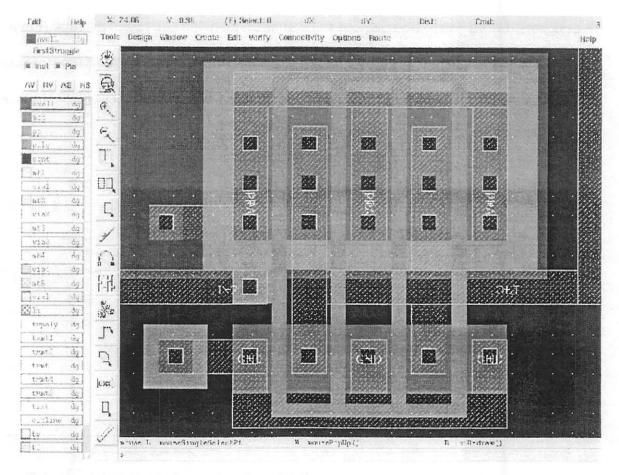

| Figure 5.10    | Basic inverter layout (0.18µm TSMC technology)104                         |

| Figure 5.11    | Circuit delay for the ideal (no CMP process variation) case105            |

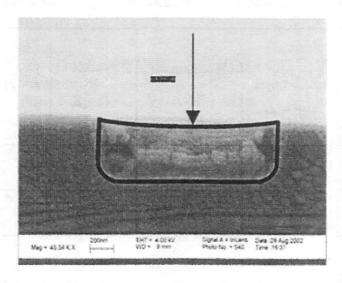

| Figure 5.12    | Copper dishing on deep sub-micron metal lines (picture courtesy of        |

| Technical Un   | iversity of Dresden, Germany)106                                          |

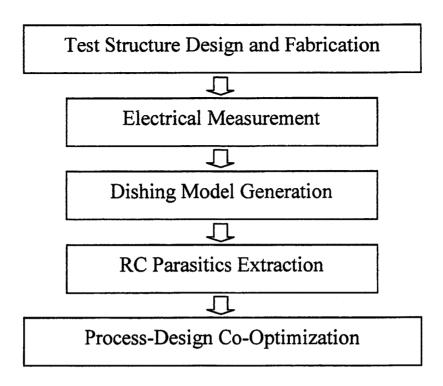

| Figure 5.13    | Overall process flow for the investigation of the metal dishing impact on |

| interconnect p | performance107                                                            |

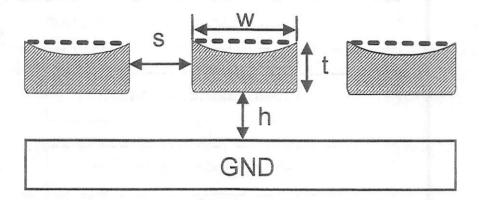

| Figure 5.14    | Interconnect structure used for the investigation of the metal dishing    |

| impact on per  | formance108                                                               |

| Figure 5.15    | Metal dishing model used to generate the interconnect profiles in         |

| simulation     | 109                                                                       |

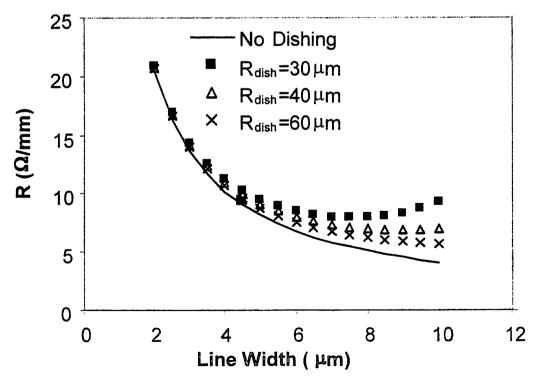

| Figure 5.16    | Dependence of metal line resistance on dishing radius as a function of     |

|----------------|----------------------------------------------------------------------------|

| metal line wid | ith109                                                                     |

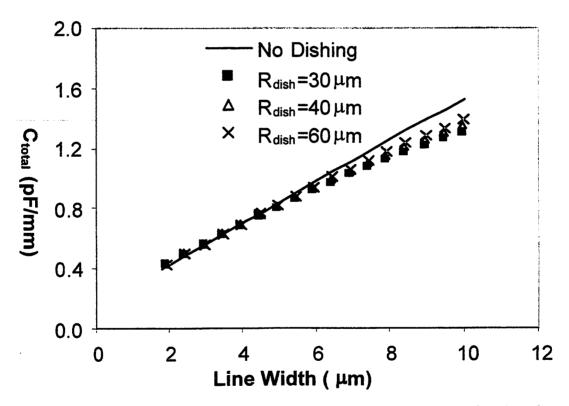

| Figure 5.17    | Dependence of metal line capacitance on dishing radius as a function of    |

| metal line wid | dth (C <sub>total</sub> =C <sub>ground</sub> +2*C <sub>coupling</sub> )110 |

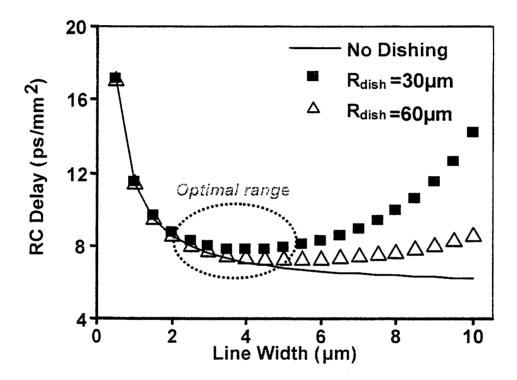

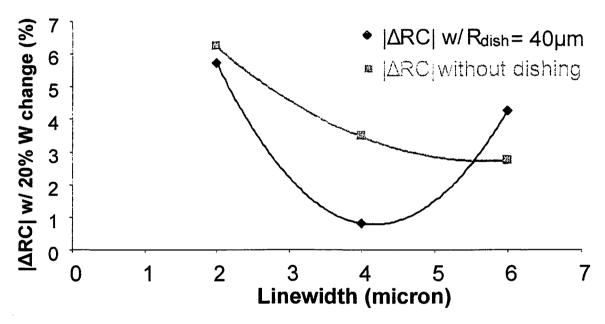

| Figure 5.18    | RC delays as a function of line width with dishing (the optimal linewidth  |

| to achieve mi  | nimum RC delay is around 4 microns)111                                     |

| Figure 5.19    | RC delay sensitivity (20% linewidth change) as a function of metal line    |

| width          | 112                                                                        |

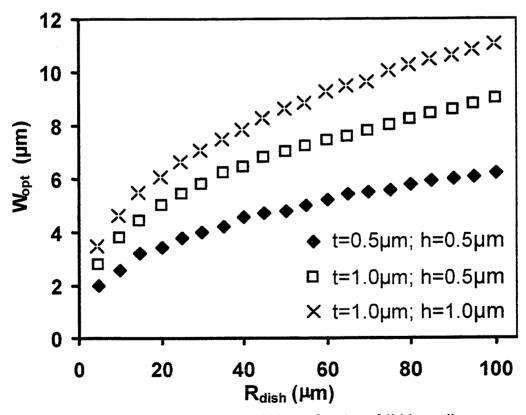

| Figure 5.20    | Optimal linewidth as a function of dishing radius113                       |

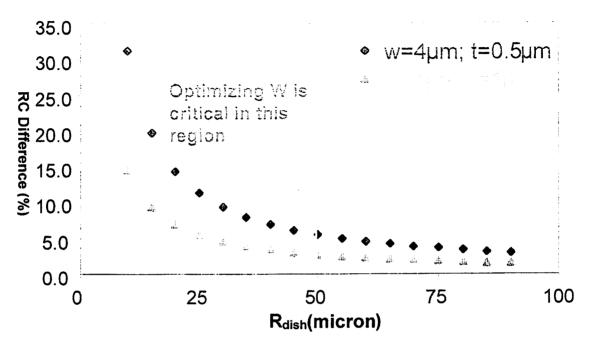

| Figure 5.21    | Efficiency of process improvement for different metal thickness as a       |

| function of di | ishing radius115                                                           |

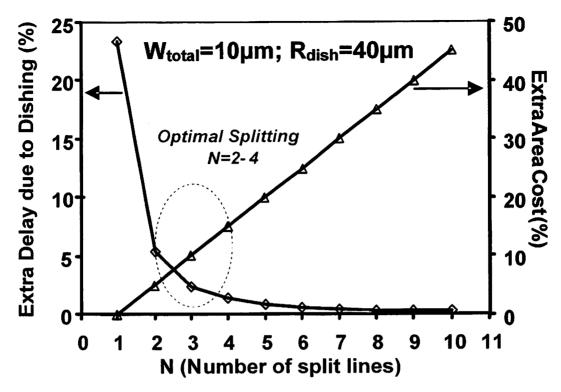

| Figure 5.22    | Illustration of the line-splitting idea (W = Wtotal/N, N is the number of  |

| lines; s=smin  | =0.5micron)116                                                             |

| Figure 5.23    | RC delay gain and area penalty tradeoff117                                 |

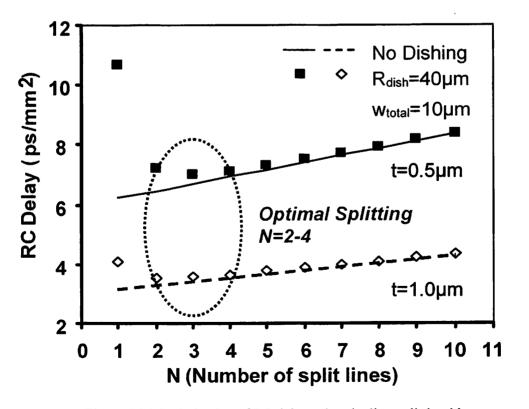

| Figure 5 24    | Ontimization of RC delay using the line-splitting idea 117                 |

## **List of Tables**

| Table 3.1   | Conditions for Sputtering of Tantalum and Copper                             | 36    |

|-------------|------------------------------------------------------------------------------|-------|

| Table 3.2   | Typical Cu CMP process parameters                                            | 37    |

| Table 3.3   | Typical Cu CMP Conditioner settings (for step-1 and step-2)                  | 38    |

| Table 3.4   | Input parameters, their variations, and coding                               | 39    |

| Table 3.5   | Design of Experiments (DOE) for copper CMP processes                         | 40    |

| Table 3.6   | Theoretical and measured copper line resistances                             | 49    |

| Table 3.7   | Dishing values of 5µm wide lines for different experimental parameter        | rs 53 |

| Table 4.1   | Design of Experiments (DOE) in modeling the dishing effect in co             | ppe   |

| CMP process |                                                                              | 74    |

| Table 4.2   | DOE measurement Results                                                      | 75    |

| Table 4.3   | Copper CMP Process characterization Results                                  | 83    |

| Table 4.4   | Integrated CMP Optimization Results                                          | 85    |

| Table 4.5   | Experimental Design using Orthogonal Array L <sub>9</sub> (3 <sup>3</sup> )  | 87    |

| Table 4.6   | Control Factor Levels                                                        | 88    |

| Table 4.7   | Experimental Results using Orthogonal Array L <sub>9</sub> (3 <sup>3</sup> ) | 89    |

| Table 4.8   | Optimization using the Taguchi's Method                                      | 91    |

| Table 5.1   | Circuit delays for three cases                                               | .105  |

## **Acknowledgements**

First and foremost, I would like to express my deepest gratitude and appreciation to my research advisor, Professor Costas J. Spanos, the real professor in my life, for his superexcellent guidance and tremendous support, and for the opportunities he has created for me during my graduate study and research at Berkeley. His vision and leadership in the semiconductor manufacturing industry has been inspiring to both my research work and career development. I thank him for his consistent supervision and enlightenment in every detail of my research and education at Berkeley.

I would also like to thank Professor David Dornfeld and Professor Nathan Cheung for their insightful inputs to this work and for reviewing my dissertation. Their expertise in the field of semiconductor processing technology has provided me strong support throughout my graduate study. I thank Professor Kameshwar Poolla for teaching me interesting control theory and reviewing my master's thesis. I thank Professor Andrew Neureuther and Professor Borivoje Nikolic for serving as committee members in my preliminary and qualifying exams. I also would like to thank Professor Ronald Gutmann at Rensselaer Polytechnic Institute for his mentoring and support to some of the experimental work in this thesis.

Special thanks to the past and present members at the Berkeley Computer Aided Manufacturing (BCAM) group, Junwei Bao, Jason Cain, Mareike Claassen, Weng Loong Foong, Mason Freed, Paul Friedberg, Anna Ison, Nickhil Jakatdar, Michiel Kruger, Jae-

Wook Lee, John Musacchio, Xinhui Niu, Jiangxin Wang, Jing Xue, Haolin Zhang, Qiaolin Zhang, Dongwu Zhao, for their best friendship, help and support. I thank Dr. Frederick Dill from Hitachi Global Storage Technologies for his long-term mentoring and valuable brainstorms. I thank Professor Fiona Doyle at the Material Science department of UC Berkeley and Professor Jan Talbot from the Chemical Engineering program of UC San Diego for their long-term collaboration and mentoring to my research, which was part of the Small Feature Reproducibility (SFR) project led by Costas. Many thanks to the staff members of the Berkeley Microfabrication Laboratory, Katalin Voros, Sia Parsa, Yu Su, Kim Chan, Joseph Donnelly, for their support on some of the experimental work. I thank Dr. Anurag Jindal at the RPI Center for Integrated Electronics for his collaboration and discussions. I thank Dr. Bhanwar Singh at AMD, Professor Eray Aydil and Dr. Brian Thibeault at UC Santa Barbara for their help on accessing AFM and surface profiling tools. I also acknowledge the staff of the Berkeley EECS department and Electronics Research Laboratory, Ruth Gjerde, Dianne Chang, Vivian Kim, Linda Manly, Charlotte Jones, T.K. Chen, Tim Duncan, for their help and support.

I acknowledge many valuable discussions and collaborations with my former industry colleagues, Andreas Wiswesser, Lei Ping Lai, Quan Tran, Qing Ma, Tsung-Kuan (Allen) Chou, John Heck, Joseph Hayden, Dong Shim, Li-Peng Wang and Valluri Rao, for sharing their precious knowledge and experience with me during my internships at Applied Materials and Intel Corporation.

I deeply thank all my Chinese and international friends from different parts of the small world. They made my life in the United States colorful and enjoyable.

I would like to thank my mom and dad and other dear members in my big family for their love during my years in graduate school. Their care always provides the warmest support to my life and work, wherever I am.

Most importantly, I would like to thank my dear wife Jinghua, for her companion and love during the last a few years. Together we have managed to get lots of meaningful things done and overcome many difficulties. I thank her for her love, understanding and consistent support. Without her love and encouragement, this thesis wouldn't be possible. I look forward to enjoying a better and better life with her and our incoming children.

This work was funded by the State of California SMART program under research contract SM97-01, and by the following participating companies: Advanced Energy, ASML, Atmel Corp., Advanced Micro Devices, Applied Materials, Asyst Technologies Inc., BOC Edwards, Cymer, Etec Systems Inc., Intel Corporation, KLA-TENCOR, Lam Research Corp., Nanometrics, Inc, Nikon Research Corp., Novellus Systems Inc., Silicon Valley Group, Texas Instruments Inc., and Tokyo Electron America.

# **Chapter 1 Introduction**

### 1.1 Motivation

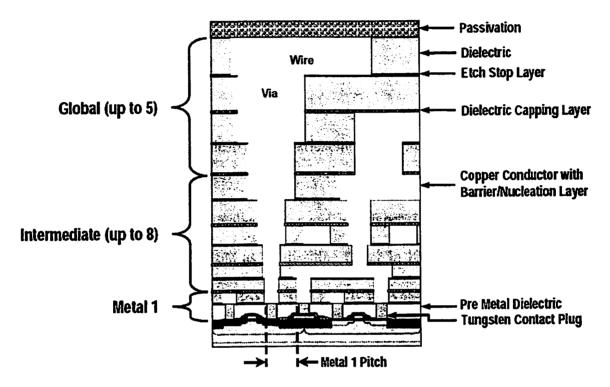

The semiconductor industry is experiencing an unprecedented growth over the last 40 years. As the technology advances in deep-submicron process geometries, enabling companies to build smaller, faster and less-expensive transistors, interconnect delay has moved to the forefront as the limiting factor in IC performance, replacing a longtime concern with switching speeds. Today there are cases where interconnect delay accounts for more than 50% percent of total path delay [1-3]. Figure 1.1 illustrates the complexity of the interconnect layers for a state-of-the-art chip. Based on these observations, optimizing the interconnect performance from the processing technology's perspective becomes an indispensable component of the global efforts of advancing the Moore's Law even further.

Chemical mechanical polishing (CMP) is currently being used in the fabrication of state of the art integrated circuits, and has been identified as an enabling technology for the semiconductor industry in its drive toward multi-gigabit chips and sub-90nm feature sizes. At the present time, it appears that the global planarization necessary for establishing reliable multilevel copper interconnects can only be achieved by using CMP. As with many processes that stand in the critical path of IC development, this technology

has moved into production without the benefit of integrated and optimized models. In the long run, the availability of such models and optimization frameworks will help optimize the operation of CMP and permit the users to define the best operating conditions for each specific application.

Figure 1.1 Typical chip cross section of hierarchical scaling of interconnect

This work focuses on the development of a fundamental understanding of the systematic variations mechanism during copper CMP, in both the feature-scale and wafer-scale level. This understanding is supported by careful experimental design and implementation. In the long term, this research will facilitate CMP technology development and Integrated Circuit designers in at least the following aspects:

(1) It will aid in identifying the dominant relationships between the material and process parameters and the effectiveness (measured by quality and integrity of the

finished surface) and efficiency (measured by material removal rate) of a CMP process. Such a model will facilitate process optimization.

- (2) In addition to providing a fundamental understanding of the CMP process, the value of the proposed experimental and modeling efforts lies in its enhanced capability for exploration of the "design space." Currently, many process design options (e.g., optimum selection of slurry and pad properties) remain trial-and-error propositions due to lack of reliable models depicting those effects. The proposed model will aid in identifying such unexplored process parameters and guide us toward new and novel avenues for designing CMP processes.

- (3) To the circuit designers, these models will provide a realistic estimation of the interconnect performance, given the proper process input parameters and mask layout patterns. The motivation for this can be explained by the challenges of obtaining high yields at the 90nm node, concerns about reliability and potentially vastly differing yields for designs of similar size that are all design rule compliant for a particular process. The contributions from this work will be more precise than the traditional worst-case estimation.

To achieve the above objectives, we utilize a combination of experimental and analytical methods. The first phase of this work is to investigate the feasibility of developing a non-destructive, low-cost metrology method to monitor the profile evolution during the ILD CMP process. The second phase is to develop oxide erosion and copper dishing models by using specially designed masks and extensively explore the information contained in the collected data. We find that it is possible to extract the 2D profile for the post-CMP metal wires. This is noteworthy in that it provides the possibility

to develop inexpensive metrology techniques in copper CMP. We also develop the framework for the multiple objectives optimization in the CMP environment. Finally we link the findings from the experiments and analytical work to interconnect performance and explore the possibility of improving BEOL fabrication yield through decisions taken at both the process and design stages.

## 1.2 Thesis organization

This thesis presents an integrated framework to fuse the aspects of metrology, modeling and optimization for the state-of-the-art copper CMP process. We begin with Chapter 2 reviewing the modern metrology and modeling work in copper damascene process. Chemical mechanical polishing has shifted from "black art" to an "engineering science" by the continuing efforts from both academia and industry. This chapter will review the general trends in this field in recent years.

Chapter 3 focuses on the experimental work that we performed in order to model the origins of layout-dependent non-uniformity in a classical copper damascene process. Started from basic ideas applied in the mask design, this chapter elaborates the design of experiments, basic metrology tools used and the development of an empirical model for copper dishing. The chapter finishes with a demonstration of a model-based 2D profile extraction method, which has the potential of being utilized as non-destructive and fast metrology for BEOL process further down the roadmap.

Chapter 4 presents a framework for efficient multiple objective optimization in a copper damascene process. Processing engineers can only devote limited resources to take measurements, calibrate the tool and make decisions. This framework can thus

reduce the reliance on experimentation to some extent. After discussions on the process performance metrics, the chapter sets up the performance optimization framework based on classical multi-objective optimization theory. Experimental results from Chapter 3 are used to calibrate the model predictions from the optimizer.

Chapter 5 presents the effects of CMP-related process variations on interconnect and circuit performance, by performing extensive simulations and analysis. The simulation results show that dishing will be a concern for global layer interconnects if the dishing radius is less than 50µm. This chapter closes with a discussion on one application of the Design for Manufacturability (DFM) concept -- the tradeoffs between the die area, BEOL yield and interconnect performance.

Chapter 6 provides some concluding remarks for this thesis and future work in the areas of copper CMP process metrology, modeling, optimization and BEOL Design for Manufacturability.

#### References:

- [1] International Technology Roadmap for Semiconductors, International SEMATECH, Austin, TX, 2003.

- [2] J. Rabaey, A. Chandrakasan and B. Nikolic, "Digital Integrated Circuits: A Design Perspective", 2nd Edition, Prentice Hall 2003.

- [3] Z. Lin, C. Spanos, L. Milor, and Y.-T. Lin, "Circuit Sensitivity to Interconnect Variation," IEEE Transactions on Semiconductor Manufacturing, Vol. 11, No. 4, pp. 557-568, Nov. 1998.

## **Chapter 2 Background**

The function of interconnect is to distribute clock and other signals, and to provide power/ground, to the various subcomponents of an Integrated Circuit. The fundamental development requirement for interconnect is to meet the high-speed transmission needs of chips despite further scaling of feature sizes. In the context of manufacturing these interconnects with a reasonably high yield, Chemical Mechanical Planarization (CMP) is used in-between critical patterning and deposition steps. CMP has proven to be indispensable, and it has been recognized as the enabling technology for Copper and Low-k based Back-End-of-the-Line (BEOL) processes.

## 2.1 Background of Chemical Mechanical Planarization

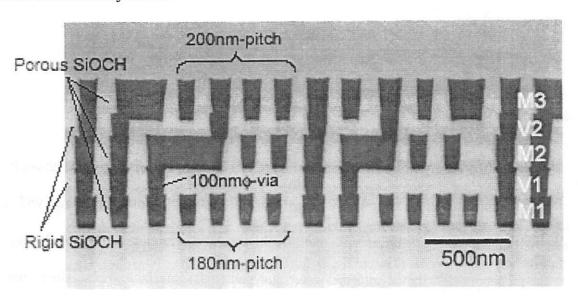

Rapid device scaling has been the factor governing the growth of the semiconductor industry, which has produced devices with ever-better performance characteristics in terms of high speed and low power. The semiconductor industry has been experiencing an average growth rate of 15% annually over the past four decades [1]. With this fast growth has come a reduction in average cycle time between introductions of new technologies from the traditional 3-year cycle towards an approximate 2-year cycle. Current (2004) production is being done employing 90nm technology, with 65nm technology expected to be introduced in the year 2005. Figure 2.1 shows a chip cross-

section using 90nm copper interconnect technology. Advances in integrated circuit (IC) manufacturing have also increased device density to about one billion transistors per cm<sup>2</sup> of chip area (for memory). The corresponding increase in circuit functionality requires many layers of metal interconnect to facilitate device and module communication. Up to ten levels of metal interconnect have been reported to date. It is note worthy that as late as 2001, industry experts thought that this number would not be achievable until the year of 2011 [2]. Now the experts predict 14 levels of metal interconnect by 2011. The ability to effectively and efficiently planarize the metal layers and the dielectric layers which are used to insulate these complex interconnect levels is indispensable for the realization of these ambitious objectives.

Figure 2.1 A 90nm copper and low-k interconnect technology (source: NEC)

While critical dimensions (CD) continue to shrink, modern photolithography tools continue to reduce their depth of focus. Especially for the future projected Extreme-Ultra-Violet (EUV) lithography where the wavelength is only about 13nm, the across-field depth of focus requirement will be at the nanometer level. Slight irregularities on the wafer surface—or on deposited films—can distort semiconductor patterns as they are

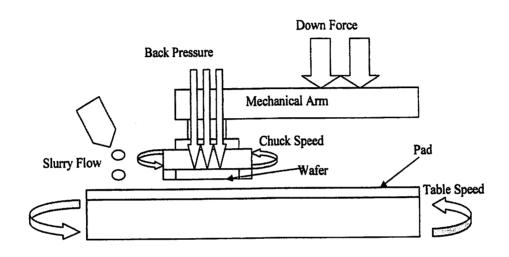

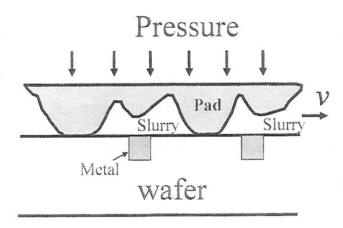

transferred by a lithographic process to the wafer surface. Chemical mechanical planarization has become the process of choice for preventing distortion, and it works by planarizing the wafer surface to a flat, uniform finish. To planarize the wafer, CMP systems use abrasive particles suspended in chemical slurry. Figure 2.2 shows the components in a simple rotary CMP system.

Figure 2.2 Typical components in a CMP system

In the configuration depicted in Figure 2.2, a silicon wafer is rotated about its axis while being pressed face-down by a carrier against a rotating platen covered with a soft polymer pad (belt). Slurries with nano-scale abrasive particles and specially designed chemicals are distributed into the wafer and pad (belt) interface. These slurry particles and chemicals work together with the pressures applied on the backside of the wafer and the relative movement between the wafer and the pad to remove some of the wafer materials and planarize its surface.

CMP is a technology that emerged during the last decade. It has become one of the most widely used planarization techniques in inter-level dielectric (ILD) planarization, shallow trench isolation (STI), and metal damascene processes. Because of

its high throughput and wide applicability, CMP is quickly replacing the traditional insitu etch-back techniques and becomes one of the key fabrication processes in the manufacturing of advanced IC chips.

## 2.2 Background on CMP Metrology

Although CMP is a versatile process, it is often quite difficult to maintain without actively compensating for key parameter changes over time. Because of this, there is a string interest to maintain good visibility of its progress, and this is typically done by measuring the status of the thin films and the evolving wafer topography before, during and after each CMP step. In this section, we introduce several types of metrology tools that are relevant to CMP and are widely used in either research or the industry.

### 2.2.1 Spectroscopic Reflectometry

This is a method used to measure the thickness and the optical properties of a thin, transparent film, such as oxides, nitrides, polysilicon, etc. In spectroscopic reflectometry, the reflected light intensities are measured in a broadband wavelength range. In most setups, non-polarized light is used at normal incidence. The biggest advantage of spectroscopic reflectometry is its simplicity and low cost. Figure 2.3 shows the setup of conventional spectroscopic reflectometry.

In reflectometry, only light intensities are measured, so only the amplitude of the complex reflection coefficient is of interest.  $R = |r|^2$ .

Figure 2.3 Spectroscopic reflectometry measurements.

This method is simple and easy for implementation. Its main application will be introduced in section 2.2.5 where we will also discuss its advantages and limitations.

### 2.2.2 Spectroscopic Ellipsometry

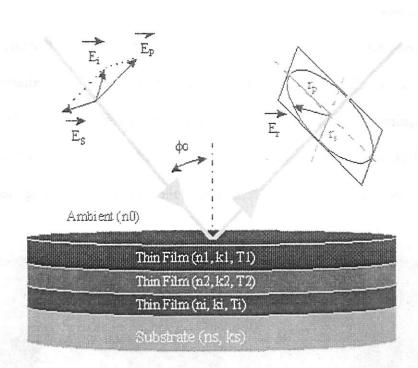

This is a method commonly used to analyze the optical properties and the thickness of one or multiple transparent films. This method is based on the characteristics of light upon reflection from multiple surfaces. The component waves of light, which are linearly polarized with the electric field parallel (p or TM) or perpendicular (s or TE) to the plane of incidence, behave differently upon reflection. The component waves experience different amplitude attenuations as well as different absolute phase shifts upon reflection; as such, the overall state of polarization changes. Ellipsometry refers to the measurement of the state of polarization before and after reflection for the purpose of determining the properties of the reflecting boundary. The measurement is usually expressed in the form

$$\rho = \tan \Psi e^{j\Delta} = \frac{r_p}{r_s}, \qquad (2.1)$$

where  $r_p$  and  $r_s$  are the complex reflection coefficients for TM and TE waves respectively.

Ellipsometry derives its increased sensitivity over reflectometry from the fact that the polarization-altering properties of the reflecting boundary are modified significantly even when ultra-thin films are present. Further, unlike reflectometry, ellipsometry can derive both the thickness and the refractive index of the target film. Spectroscopic ellipsometry can do so over multiple wavelengths. Consequently, ellipsometry has become the rigorous method of characterizing thin films. An illustration of the basics of ellipsometry is presented in Figure 2.4 below:

Figure 2.4 Spectroscopic Ellipsometry Measurements

The advantage of ellipsometry over reflectometry is better accuracy. As mentioned before, ellipsometry measures the polarization state of light by looking at the ratio of values rather than the absolute intensity of the reflected light. This property is especially useful in the DUV wavelength range, where very little light is typically available. Additionally, ellipsometry can gather the phase information in addition to plain

magnitude reflectivity information. Phase information provides more sensitivity to thinfilm variations.

## 2.2.3 Scanning Electron Microscopy (SEM) [21]

The scanning electron microscope (SEM) is currently the main method used in production for measuring lateral sub-micron features because of its nanometer-scale resolution, precision as well as its relatively high throughput. SEM comes in many flavors, cross-sectional and top-down being the most common.

Cross-sectional SEM can provide profile information for structures on a wafer in the form of a direct image. This image can be used immediately for process characterization. However, obtaining a cross-sectional SEM image requires breaking a wafer and is very time-consuming; also there is the possibility of the presence of systematic profile errors dependent upon the image processing technique being employed.

Figure 2.5 A cross-sectional view of a sample using SEM

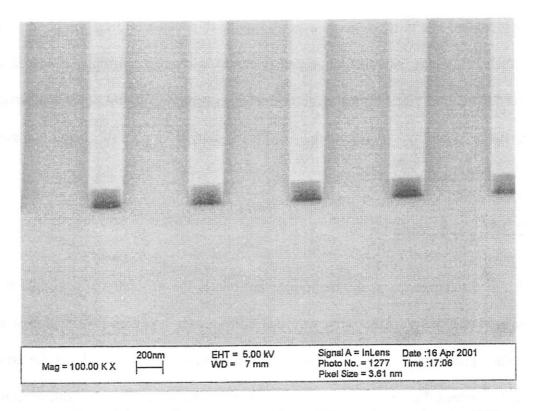

Figure 2.6 A top-down view of a E-beam Lithography sample using SEM

The top-down SEM, more commonly referred to as the CD-SEM, measures the CD of a profile at a somewhat arbitrary height and does not take into account the slope associated with the profile that results in a constantly changing profile CD. Another problem associated with this method is the build-up of charge in the sample under the electron beam. The CD-SEM, being a surface scanning technique, is also unable to provide information on underlying layers of the structure as well as undercut features. The state-of-the-art SEMs can measure sub-100nm CDs with a precision of about 2nm.

## 2.2.4 Atomic Force Microscopy (AFM) [22]

Atomic force microscopy (AFM) is a means for measuring nm-scale profiles with a resolution between 0.1nm and 5nm, depending on the hardness of the material being scanned. For typical semiconductor profiles, this translates into exceptionally high

vertical and lateral resolutions, which combine to provide information about a patterned structure's width, sidewall slope and thickness. However, current AFM scan rates are very slow, and measurement accuracy and precision are highly dependent upon the tip shape and stability. At present, the AFM is too slow to be used for imaging to support the CMP process during production

#### 2.2.5 Scatterometry

Scatterometry is the metrology that relates the geometry of a sample to its light scattering effects. In the same way that ellipsometry analyzes polarization-state-in and polarization-sate-out of light incident on thin film, scatterometry adopts the same theory and measures the polarization-state-in and polarization-state-out of light, incident not on a blanket thin film, but rather on periodic surface structures. The  $Tan \Psi$  and  $Cos \Delta$  values are measured after reflection and matched to the responses of known profiles.

Much work has been done on scatterometry in recent years. McNeil et al have explored the idea of variable-angle scatterometry, which uses angle-resolved diffracted light analysis to measure etched samples with line width dimensions as small as 150nm and poly-Si thickness on the order of 250nm [3].

Niu et al. have explored the idea of spectroscopic scatterometry, in which the responses for multiple wavelengths are taken into account [4]. This method consists of measurements taken at a fixed incident angle as opposed to variable-angle scatterometry. The lack of external moving parts, and hence simpler implementation, gives spectroscopic scatterometry the potential of being employed in in-line, in-situ process control. Niu et al also developed a simulation engine, known as the gtk (Grating Tool

Kit) based on well known method of Rigorous Couple-Wave Analysis [5, 6]. It was demonstrated that the simulated and measured diffracted light responses based on this technique correspond to profiles that closely match those obtained through the AFM method.

## 2.2.6 Monitoring CMP Processes in a Production Environment

Accurate thickness measurements in chemical mechanical polishing (CMP) are difficult to achieve consistently on complex state-of-the-art computer chips, so frequent monitoring is needed. This requires high-speed film thickness measurement of both thick films and ultra-thin films at multiple sites across the wafer surface. In order to make film removal uniformity measurements on product wafers, the metrology tool must have a small measurement spot and fast, robust pattern recognition to reliably guide the measurement spot to the film thickness test structures.

Spectroscopic reflectometers have been used to measure thick films because they can determine film thickness very rapidly. They also can operate with measurement spots as small as ~50µm in diameter. However, reflectometer accuracy degrades significantly when measuring films thinner than 500-1,000 Å. The ability to measure very thin films is important in determining if over-polishing has occurred. On the other hand, measurement accuracy and reliability for thick films are challenging qualities in a production CMP metrology system. Inaccurate measurements resulting from the phenomenon known as "order skipping" for instance, lead to mis-processing and costly scrapping of damaged wafers.

Scatterometry is one of the few metrology candidates that have true *in-situ* potential for deep sub-micron oxide CMP profile analysis. In previous work, we have demonstrated the possibility of using a library-based scatterometry method to match the closest profile in oxide CMP [6]. In that project, the specular spectroscopic scatterometry is designed to measure the 0<sup>th</sup> diffraction order at a fixed angle of incidence and multiple wavelengths. The term "spectroscopic" means that multiple wavelengths are under used simultaneously. Due to its fixed angle, specular spectroscopic scatterometry is easy to deploy. Specular spectroscopic scatterometry can make use of a conventional spectroscopic ellipsometer, and can be installed *in-line* or *in-situ*. Conventional spectroscopic ellipsometry equipment can be directly used in this type of metrology.

Specular spectroscopic scatterometry, when implemented with a library of generated profiles, is about 100 times faster than the SEM and the speed advantage is even more significant when compared with the AFM. It is non-destructive, inexpensive and easy to implement *in-line* in a production CMP system.

Metrology methods which can overcome the slow throughput and meet the requirements of state-of-the-art CMP process-control are needed. For research purposes, metrology methods which can monitor the profile evolution would be crucial for the development and verification of a rigorous, first principle model for the state-of-the-art CMP process for both oxide and copper.

#### 2.3 Background on CMP Process Modeling

The main feature of CMP, namely the removal of the material, is described by the Preston's Equation [7]:

$$\frac{dT}{dt} = K \cdot \frac{N}{A} \cdot \frac{ds}{dt} \tag{2.2}$$

where T denotes the thickness of the wafer, N/A denotes the pressure caused by the normal force N on the area A. s is the total distance traveled by the wafer, and t denotes the elapsed time. This means that the material removal rate is proportional to the pressure and the velocity of the rotation. Any physical considerations are put into the Preston's Constant K, which is often considered the proportionality constant (i.e. independent of pressure and velocity), but may also contain chemical effects. However, the chemical reaction effects seem to dominate in real-life situations.

#### 2.3.1 Inter-Layer Dielectric (ILD) CMP Process Modeling

Cook's model [8] is applicable to CMP for bare silicon wafers. However, many ideas are also applicable to the more general case of CMP for ILD. Cook starts from Preston's Equation. The slurry is assumed to be a viscous Newtonian fluid with a viscosity of around  $10^9$ P with particles in it. The mechanical part of the interaction between polishing particles and the wafer surface can be described by a model with a spherical particle of diameter  $\Phi$ , which penetrates the surface with force  $F_s$  under the uniform load N. For a standard Hertzian penetration Preston's constant becomes  $(2 \cdot E)^{-1}$ , where the E denotes Young's modulus. The surface roughness is the penetration depth given by

$$R_s = \frac{3}{4} \cdot \Phi \cdot \left(\frac{P}{2 \cdot k \cdot E}\right)^{2/3}, \qquad (2.3)$$

where k is the particle concentration (unity for a fully-filled closed packing) and  $P = \frac{N}{A}$  is the pressure.

Impingement of particles carried in the turbulent liquid leads to Hertzian penetration of the surface, converting kinetic energy into strain energy. Local bonding during contact leads to weakening of binding forces at the surface, which allows atomic removal to occur without introducing lattice dislocations.

An extensive study of the chemical part is presented in Cook's paper. However, a discussion of it is beyond the scope of this thesis.

Cook's model is the most general modeling work for polishing so far. In particular, it deals with the mechanics of the polishing particles and with the chemical reactions. It covers almost all interesting topics and the method is explained by an example (SiO<sub>2</sub> polished by SiO<sub>2</sub>-particles). This model is based on a smaller feature length compared to the Preston's model, as it deals with the particles and the particle size in the slurry fluid. In the future, additional work is necessary to combine Cook's model with other models in order to get a sufficiently general model for the entire CMP process.

J. Luo and D.A. Dornfeld have explored the material removal mechanism in chemical mechanical polishing recently [9]. Based on the assumptions of plastic contact over wafer-abrasive and pad-abrasive interfaces, the normal distribution of abrasive size and the periodic roughness of the pad surface, a novel model were developed for predicting the material removal in CMP. The basic model predicts the material removal

rate (MRR):  $MRR = \rho_w N \cdot Vol_{removed}$ , where  $\rho_w$  is the density of the wafer, N the number of active abrasives and  $Vol_{removed}$  is the volume removed by a single abrasive.

Compared with previous modeling approaches, such as Preston's equation, the model proposed by Luo and Dornfeld integrates not only the process parameters of pressure and velocity, but also other input parameters including the wafer hardness, pad hardness, pad roughness, abrasive size and abrasive geometry into the same formulation to predict the material removal rate. A link between the chemical and the mechanical effect has been captured through a fitting parameter in the model. It reflects the influence of chemicals on the mechanical material removal. The fluid effect in the current model is attributed to the number of active abrasives. The nonlinear down pressure dependence of material removal rate is related to a probability density function of the abrasive size and the elastic deformation of the pad. Compared with experimental results, the proposed model predicts the material removal rate fairly accurately.

At this point it is appropriate to mention the MIT work on pattern dependency effects [10-11]. Several models had been proposed to account for pattern effects in CMP before the MIT Model but their applicability had been limited [12]. The limitations range from being based on non-representative test structures to probing of small process windows which limit the utility of the models beyond the scope of the original experimental conditions. Most of the models before the MIT model, however, did not apply across a whole die but rather focused on individual features.

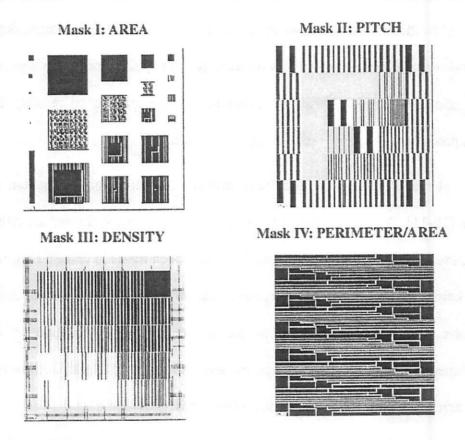

As a prelude to effective modeling of CMP for oxide planarization, the MIT metrology group performed polishing experiments for a wide range of die topography patterns. A set of four masks shown in Figure 2.7 was used to generate the die patterns.

Mask I explores the effects of area and consists of blocks of sizes ranging from 20μm to 3000μm. It also contains blocks which mimic realistic circuit layouts. Mask II examines the effect of pitch. The pattern density – defined as the ratio of line width to pitch – is maintained at 50% while the pitch is varied from 2μm to 1000μm in the 2mm x 2mm blocks. Mask III explores the effect of density which is increased from 4% to 100% in steps of 4%. Pitch is maintained at 250μm in each of the 25 2mm x 2mm blocks. Mask IV explores the effects of block perimeter. It consists of blocks of constant area (1mm x 1mm) but with different perimeter/area ratios. The mask is divided into six sections and the spaces between the blocks are decreased from 60μm at the bottom to 10μm at the top.

Figure 2.7 MIT oxide CMP characterization mask set

These masks were used in a single-mask fabrication process to generate surface topographies on 6" wafers to be planarized using CMP. The fabrication process consisted

of 1000nm LPCVD TEOS deposition, metal deposition, and pattern and etch followed by 2000nm TEOS deposition.

The experimental results led to two important conclusions which are becoming the basis for the later MIT CMP model: (1) the pitch (line width and line space), area and perimeter are all minor effects to the final oxide thickness; (2) effective density is the key layout parameter. That is, the oxide-polishing rate at each point is inversely proportional to the effective pattern density. The effective pattern density depends on the nearby topography and density. A certain window, whose side is so called the "planarization length", can determine the pattern density. Please see Figure 2.8 for the illustration.

Figure 2.8 Window used to calculate effective density

Planarization length is the approximate length of the "ramp" joining areas of different removal rates, as determined by locally different pattern densities. However, the planarization length must be characterized for a given process. In figure 2.8, the effective density at X for a square constant weight window can be calculated as the following:

$$effective - pattern - density = \frac{Raised - Area - in - the - window}{Total - Area - in - the - window}$$

(2.4)

The long range "moving average" density calculation corresponds to a simple convolution picture:

$$d(x, y) = p(x, y) * l(x, y),$$

(2.5)

where d(x, y) is the effective pattern density at (x, y), p(x, y) is the "planarization impulse response" (weighting function) to raised features, l(x, y) is the local (feature scale) density.

#### 2.3.2 Copper CMP Process Modeling

The mechanism of CMP of metal is less understood and more complex than that of oxide polishing. It has been conjectured that a metal polishing model should employ both chemical etching and a passivation mechanisms [13-14]. For metal CMP, the polishing slurry must contain three important constituents: the fine slurry particles, a corrosion (etching) agent, and an oxidant. Planarization is achieved by the mechanical rigidity of the polishing pad similar to oxide polishing.

Copper CMP processes have been studied at the MIT statistical metrology group led by Prof. Duane Boning [15-18]. The research has been helpful in establishing the pattern density and planarization length concept. They have been focusing on multi-layer interconnect stacks, chip or wafer level variations in copper CMP. One aspect that requires significant improvement however is the understanding of the feature-level, multiple process and layout input parameters interactions in damascene process.

Recently, Lakshminarayanan et al. proposed design rule modifications in order to improve the manufacturability by a reduction of the within-die resistance/thickness variation based on experimental data [19]. Smith et al reported the effect of barrier layer and dishing in copper interconnects using a fine Greek cross test structure [20]. Both

projects see the opportunity of improving manufacturability in the backend by a better understanding of the damascene process.

Copper metallization, which has replaced traditional aluminum technology for the state-of-the-art IC's, is expected to have ten levels of metal with as small as 50 Å of copper thickness loss for minimum feature arrays and less than 150 Å of wide copper line loss by year 2010. This is a challenging future requirement for the current chemical mechanical polishing process, especially when current planarization technology often exceeds 1000 Å of copper loss in dense regions. The constraint on copper planarization is made more difficult by the incoming integration difficulties coming from ultra-low-k materials. The integration will impact CMP performance directly by causing varying removal rates of copper on different pattern regions.

As we addressed before, while dielectric erosion has been extensively studied, practical and quantitative understanding of the dishing effect is still at the developing stage. The international technology roadmap for semiconductors calls for a full CMP model in the near future with 10% topography accuracy of specification limits. Thus, it is critical to have a systematic methodology for the characterization and modeling of pattern dependent issues and problems in copper CMP process. This characterization will enable an optimization framework to handle the CMP performance metrics in a balanced way. These are the objectives of this thesis.

#### References:

- [1] "International Technology Roadmap for Semiconductors", 2003 Edition, Semiconductor Industry Association (SIA).

- [2] <a href="http://www.semiconductor.net/semiconductor/reference/reference.asp">http://www.semiconductor.net/semiconductor/reference/reference.asp</a> "Editorial Archives", May 2001.

- [3] C. J. Raymond, S. S. H. Naqvi, J. R. McNeil, "Scatterometry for CD measurements of etched structures," Proceedings of SPIE, vol. 2725, 720-728, March 1996.

- [4] X. Niu, N. Jakatdar, J. Bao, C. Spanos, S. Yedur, "Specular spectroscopic scatterometry in DUV lithography", Proceedings of the SPIE The International Society for Optical Engineering, vol.3677, pt.1-2, (Metrology, Inspection, and Process Control for Microlithography XIII, Santa Clara, CA, USA, 15-18 March 1999.

- [5] X. Niu, "An Integrated System of Optical Metrology for Deep Sub-Micron Lithography", Ph.D Dissertation, U.C. Berkeley, 1999.

- [6] R. Chang, "Full Profile Oxide CMP Metrology", Master's Thesis, University of California at Berkeley, May 2001.

- [7] F.W. Preston, "The Theory and Design of Plate Glass Polishing Machine," Journal of the Society of Glass Technology, Vol. 11, pp. 214-256, 1927.

- [8] L.M. Cook, "Chemical Processes in Glass Polishing", J. of Non-Crystalline Solids, vol. 120, pp152-171, 1990

- [9] J. Luo and D.A. Dornfeld, "Material Removal Mechanism in Chemical Mechanical Polishing: Theory and Modeling", IEEE Transactions on Semiconductor Manufacturing, vol. 14, no. 2, May 2001.

- [10] D. O. Ouma, B. Stine, R. Divecha, D. Boning, J. Chung, I. Ali, and M. Islamraja,, "Using Variation Decomposition Analysis to Determine the Effect of Process on Wafer and Die-Level Uniformities in CMP," First International Symposium on Chemical Mechanical Planarization (CMP) in IC Device Manufacturing, Vol. 96-22, pp. 164-175, 190th Electrochemical Society Meeting, San Antonio, TX, Oct. 6-11, 1996.

- [11] Divecha, R., B. Stine, D. Ouma, J. Yoon, D. Boning, J. Chung, O.S. Nakagawa, S-Y Oh, "Effect of Fine-Line Density and Pitch on Interconnect ILD Thickness Variation in Oxide CMP Processes," 1997 Chemical Mechanical Polish for ULSI Multilevel Interconnection Conference (CMP-MIC), p. 29, Santa Clara, February, 1997.

- [12] G. Nanz and L. E. Camilletti, "Modeling of Chemical-Mechanical Polishing: A Review," IEEE Trans. Semiconductor Manufacturing, Vol. 8, No. 4, November 1995.

- [13] J.-Q. Lu, Y. Kwon, G. Rajagopalan, M. Gupta, J. McMahon, K.-W. Lee, R.P. Kraft, J.F. McDonald, T.S. Cale, R.J. Gutmann, B. Xu, E. Eisenbraun, J. Castracane, and A. Kaloyeros, "A Wafer-Scale 3D IC Technology Platform Using Dielectric Bonding Glues and Copper Damascene Patterned Inter-Wafer Interconnects," in Proceedings of the 2002 IEEE International Interconnect Technology Conference (IITC), 78-80, San Francisco, 2002.

- [14] S.P. Murarka, I.V. Verner, and R.J. Gutmann, Copper Fundamentals for Microelectronic Applications, John Wiley & Sons Inc., New York, 1997.

- [15] T. Park, T. Tugbawa, J. Yoon, D. Boning, J. Chung, R. Muralidhar, S. Hymes, Y. Got-kis, S. Alamgir, R. Walesa, L. Shumway, G. Wu, F. Zhang, R. Kistler, and J. Hawkins, "Pattern and Process Dependencies in Copper Damascene Chemical

- Mechanical Polishing Processes," Proc. VLSI Multilevel Interconnect Conference, Santa Clara, CA, June 1998.

- [16] T. Tugbawa, T. Park, D. Boning, T. Pan, P. Li, S. Hymes, T. Brown, and L. Camilletti, "A Mathematical Model of Pattern Dependencies in Copper CMP Processes," Proc. CMP Symposium, Electrochemical Society Meeting, Honolulu, HI, pp. 605-615, Oct. 1999.

- [17] T. Park, T. Tugbawa, D. Boning, S. Hymes, T. Brown, K. Smekalin, and G. Schwartz, "Multi-Level Pattern Effects in Copper CMP," Proc. CMP Symposium, Electrochemical Society Meeting, Honolulu, HI, pp. 94-100, Oct. 1999.

- [18] T. Tugbawa, T. Park, and D. Boning, "Framework for Modeling of Pattern Dependencies in Multi-Step Cu CMP Processes," SEMICON West, July 2000.

- [19] S. Lakshminarayanan et al, "Electrical characterization of the copper CMP process and derivation of metal layout rules", IEEE Transactions on Semiconductor Manufacturing, vol. 16, no. 4, pp. 668-676, Nov. 2003.

- [20] S. Smith, et al., "Evaluation of sheet resistance and electrical line width measurement techniques for copper damascene interconnect," IEEE Transactions on Semiconductor Manufacturing, vol. 15, no. 2, pp. 214-222, May 2002.

- [21] Banerjee, I.; Tracy, B.; Davies, P.; McDonald, B., "Use of advanced analytical techniques for VLSI failure analysis," Reliability Physics Symposium, pp. 61-68, 1990

- [22] Neubauer, G.; Dass, M.L.A.; Johnson, T.J., "Imaging VLSI cross sections by atomic force microscopy," Reliability Physics Symposium International, pp. 299-303, April 1992

# Chapter 3 Integrated Characterization of Layout Dependency in Copper Damascene Process

#### 3.1 Introduction

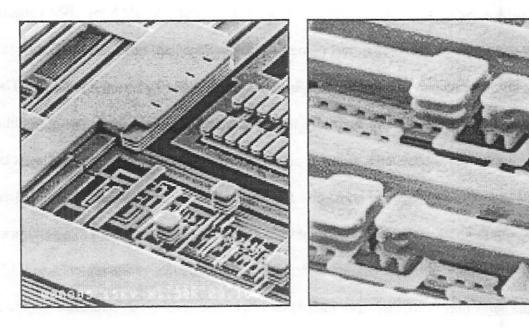

For the sub-90nm CMOS nodes, Chemical-Mechanical Polishing (CMP) is widely used as the primary technique to planarize the Inter-Layer Dielectric (ILD) and metal surface. Since the introduction of copper metallization in 1998 by IBM (Figure 3.1), CMP has been the enabling technology for the copper damascene process with the high metal removal rate that is necessary in this kind of trench-first integration [1]. The damascene process derives its name from the ancient metal decorating art of the Middle East involving inlaying metal in ceramic or wood for decoration. Historically, the art of damascene was practiced for centuries by Egyptians, Greeks, and Romans. The modern damascene process was found to be a viable process to support the idea of using copper to replace aluminum around the 0.35 micron technology node. As shown in Figure 3.2, after the via plug process, the inter-level dielectric (ILD) is deposited without planarization, since the surface is already flat. Trenches for metal lines are then defined,

etched in the ILD, and filled with a metal such as copper. The excess metal on the surface is removed and a planar structure with metal inlays in the dielectric is achieved [2]. The damascene process eliminates the difficulty in filling small gaps between metal wires as well as in metal etching, especially for Cu and other hard-to-etch metals. A dual damascene process is demonstrated in the left side of Figure 3.2. In this process, vias and trenches are defined using two lithographic and RIE steps, but the via plug is filled in the same step as the metal line. Dual damascene minimizes the number of processing steps by reducing the barrier layer depositions from two to one and by eliminating the CVD W plug processes.

By replacing aluminum with copper, the metal wire resistance is reduced by about 30% and its electro-migration resistance also improves dramatically. Figure 3.2 shows the process flow for a single (the right side) and dual (the left side) damascene process, respectively.

Figure 3.1 Complex copper interconnects fabricated with IBM's damascene process

Figure 3.2 Single (right side) and dual (left side) damascene process flow illustrations

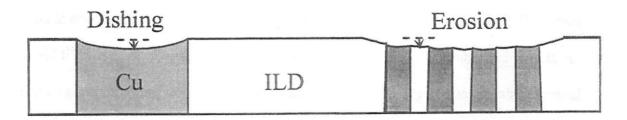

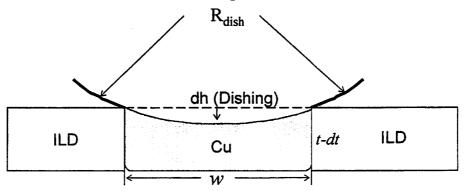

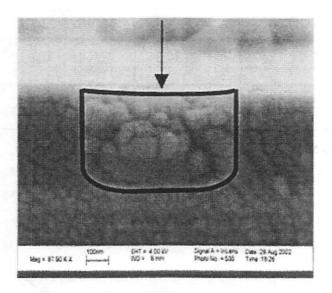

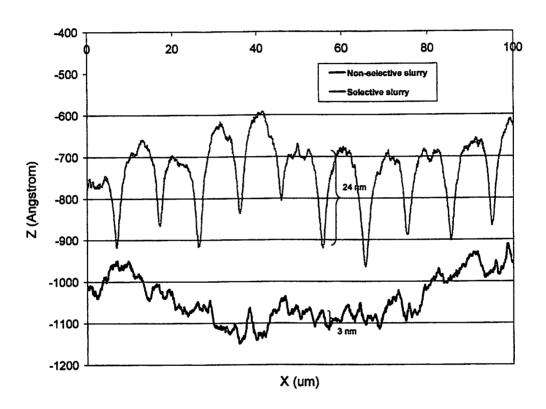

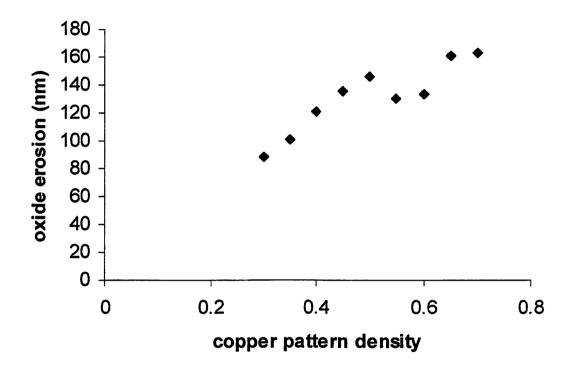

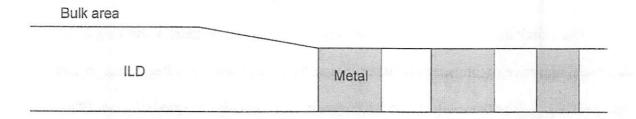

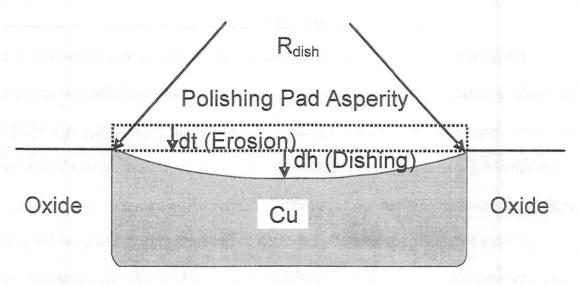

However, the CMP damascene process also introduces undesirable side-effects, including dielectric erosion and metal dishing. Fig. 3.3 illustrates their influences on metal line cross-sections after CMP. Both effects originate from the material property differences between dielectrics and metal under chemical and mechanical stresses. Both erosion and dishing degrade the process quality, cause significant yield losses in the Back-End-Of-the-Line (BEOL), and negatively impact interconnect performance, especially for very wide global interconnects and metal layers that have a wide distribution of pattern densities [3-5].

Figure 3.3 Illustration of oxide erosion and copper dishing problems during copper damascene process

In this chapter, we design and measure test patterns to investigate the correlations between the side effects existing in damascene process (e.g. oxide erosion and copper dishing) and the layout characteristics. We develop a model that well captures the correlation between the metal linewidth and the amount of dishing, given input parameters such as speed, pressure, chemicals and pad information. After model validation, we utilize the electrically tested conductance data to extract the useful parameters, such as oxide erosion and dishing radius.

#### 3.2 Test Pattern Design

Characterization of the pattern dependent non-uniformities in copper damascene process is needed to understand the fundamental limitations of each process and assist in new process development efforts. As we discussed in Chapter 2, some work has already been done in this area [6-8]. In this work, we focused out study on one topic that people have limited knowledge on — metal dishing. Based on that, we integrate the effects of oxide erosion and copper dishing and attempt to present a general picture of the CMP performance in correlation with the special layout on the mask and process input parameters.

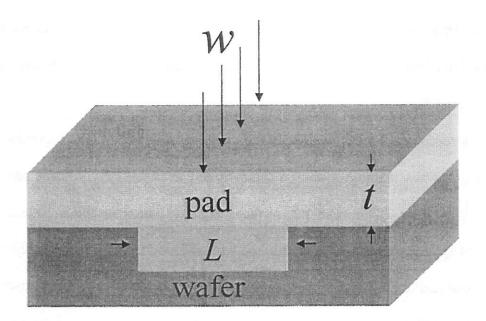

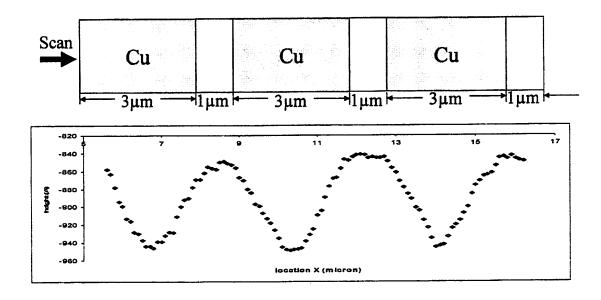

In our experiments, the impact of metal dishing is characterized by measuring post-CMP line resistance (R). Since the dishing effect causes a non-planar metal surface (as shown in Figure 3.3), and since it reduces the conductive cross-section it leads to larger resistance, as compared to the theoretical value of R for a line with planar surface. Therefore, in the design of test structures, the key consideration is its suitability for electrical testing of R (E-test). Furthermore, since metal thickness loss caused by dishing

exhibits strong correlation to metal width (e.g., wider lines suffers dishing more severely), the design of test cells particularly focuses on the relationship between the amount of dishing and line width (w).

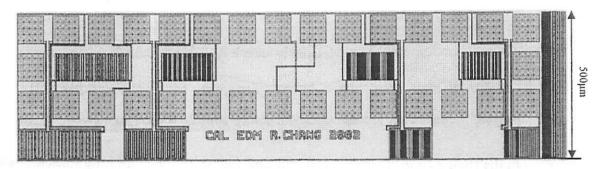

Figure 3.4 Cell design for the electrical characterization of dishing effect in copper damascene process

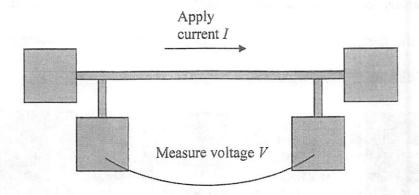

Figure 3.4 shows the layout of a test cell. Each cell contains eight serpentine-shaped metal lines that vary in line width (0.4 $\mu$ m, 0.8 $\mu$ m, 1.2 $\mu$ m, 1.6 $\mu$ m, 2.0 $\mu$ m, 3.0 $\mu$ m, 4.0 $\mu$ m, and 5 $\mu$ m); the line length is 4mm; and the target line thickness is 0.4 $\mu$ m. These dimensions are chosen from typical global on-chip interconnect parameters. Depending on the linewidth, the estimated line resistance is within the range of 30 $\Omega$  to 650 $\Omega$ , so that R can be easily extracted by an automatic impedance test. For each line, there are two pads at each end that are used as probe contacts during E-test. Four-point measurement, which applies a known current through the two outer pads and measures voltage difference between the two inner pads, is employed to measure the resistances of the post-CMP lines (Figure 3.5). This enables reliable measurements of the resistance for the straight line between the two middle pads without suffering the parasitic noise coming from contact resistance variation.

Figure 3.5 Schematic representation of the four-point measurement method

On the right side of the E-test cell, multiple copies of the eight long lines are laid out for the scanning electron microscopy (SEM) test, which can provide the crosssectional view of metal lines after CMP. Overall, an E-test cell has a dimension of 1900μm by 525μm. In order to decouple dishing effect from erosion, pattern densities are approximately uniform across the cell, so that metal thickness loss caused by erosion is similar to different test lines. Moreover, the cell footprint is small but arguably comparable to the characteristic length of ILD erosion during Cu Damascene polishing. To ensure that oxide erosion was about the same throughout the various electrical patterns, we established a wide area around the electrical patterns, where the pattern density was carefully controlled by means of a grating. In addition, we measured the post-CMP oxide erosion and found it to be constant within each group of electrical patterns. Thus, for test lines with different widths on the same cell, their differences in the increment of R after CMP are mainly caused by dishing. We expect at a large multimillimeter die or wafer scale, the amount of oxide erosion is a strong function of the effective pattern density [9-10].

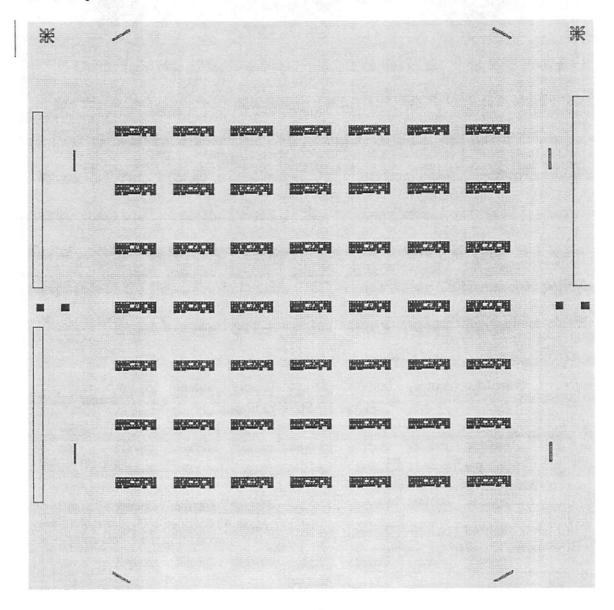

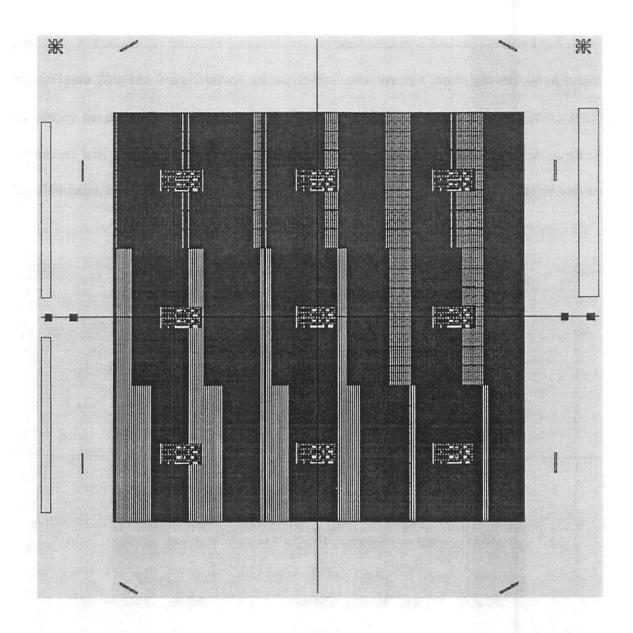

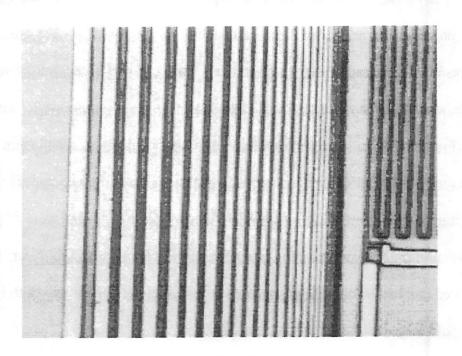

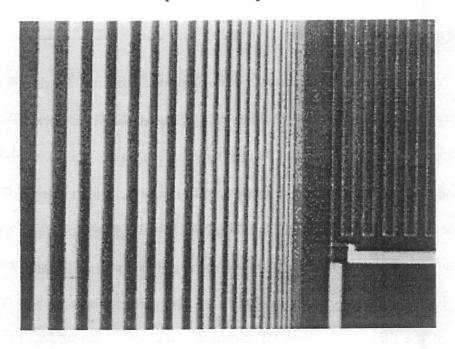

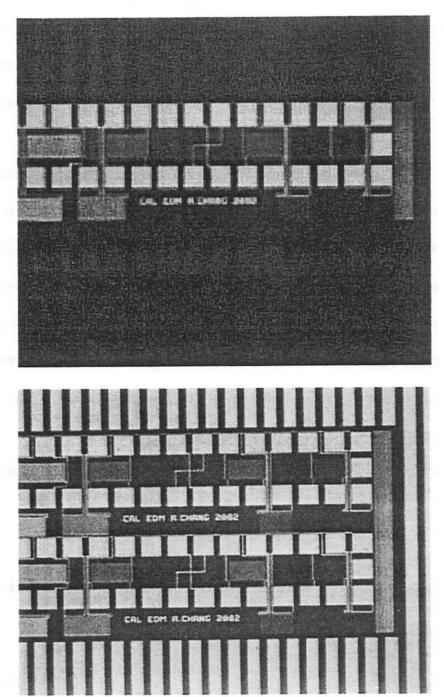

Based on the considerations above, we designed two masks. Mask #1 (as shown in Figure 3.6) has 7 by 7 arrays of the E-test cells. In this mask, the effective pattern density for each cell is approximately constant. Differences in the percentage resistance change will only come from dishing effect. Mask #2 (as shown in Figure 3.7), on the other hand, has 3 by 3 structures with different pattern densities set by the line widths and the interspaces.

Figure 3.6 Mask #1 layout

Figure 3.7 Mask #2 layout

Figure 3.8 Effective pattern densities of Mask #2 (defined by wider metal lines surrounding the E-test cells

On Mask #2, the pattern densities range from 30% to 70% with a 5% step. At the center of each structure, however, the pattern density remains constant as defined by the uniformly distributed wide metal lines (>20 microns). Two basic E-test cells were placed at the center of each of the structures. So the differences in the resulted sheet resistance change (after polishing) will come from both the erosion and the dishing effects. The equivalent pattern density of mask #2 is illustrated in Figure 3.8.

The pre-CMP test wafers using these masks are fabricated at the Berkeley and the RPI Micro-fabrication laboratories as we will present in the next section.

### 3.3 Design of Experiments

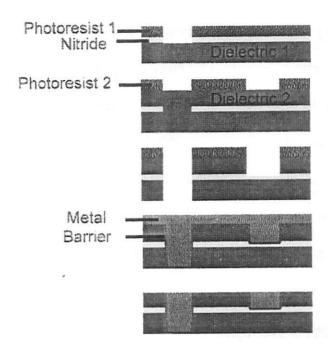

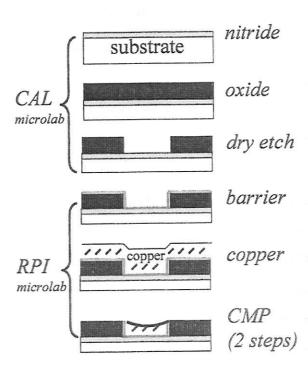

After the masks were ready, we started the preparation for CMP with 150 mm (6") prime silicon wafers. The process flow is schematically shown in Figure 3.9.

Figure 3.9 Process flow chart of the single damascene fabrication

As shown in the Figure 6, nitride and silicon dioxide chemical vapor deposition (CVD) was done in the micro-fabrication lab at University of California Berkeley. Photolithography was also performed at Berkeley using the ASML DUV Stepper Model 5500/90 which is capable of printing 0.35μm features. In the next step, dry oxide etching was done using the single wafer silicon oxide plasma etcher. Subsequently, the wafers were transported to the Micro-fabrication Clean Room (MCR) at the Center for Integrated Electronics, Rensselaer Polytechnic Institute (RPI). After proper process qualification, a thin barrier/adhesion promoter layer of Ta (~20nm) and bulk copper (~1.5μm) layer were deposited using CVC magnetron sputtering tool at RPI MCR. Sputtering conditions for the Ta and Cu layers are as given in Table 3.1.

**Table 3.1 Conditions for Sputtering of Tantalum and Copper**

| Metal                     | Tantalum           | Copper             |  |

|---------------------------|--------------------|--------------------|--|

| Power (kW)                | 1.95               | 2.3                |  |

| Base Pressure (Torr)      | 1x10 <sup>-6</sup> | 1x10 <sup>-6</sup> |  |

| Operating Pressure (Torr) | 5x10 <sup>-3</sup> | 5x10 <sup>-3</sup> |  |

| Plasma Gas                | Ar                 | Ar                 |  |

| Sputtering Time (minutes) | 0.5                | 15                 |  |

| Sputtering Rate (nm/min)  | 4                  | 100                |  |

The output of the process flow was 18 wafers (with 9 of each utilizing mask 1 and mask 2, respectively) available for the copper damascene CMP process.

The wafers thus prepared were polished on an IPEC-372M rotary polisher. A typical baseline process for step-1 and step-2 Cu damascene polishing is tabulated in Tables 3.2 - 3.3:

Table 3.2 Typical Cu CMP process parameters

| Parameters       | Step-1 Settings                 | Step-2 Settings                            |  |

|------------------|---------------------------------|--------------------------------------------|--|

| Down pressure    | 5 psi                           | 5 psi                                      |  |

| Back pressure    | 0.5 psi                         | 0.5 psi                                    |  |

| Platen speed     | 90 rpm                          | 75 rpm                                     |  |

| Carrier speed    | 90 rpm                          | 75 rpm                                     |  |

| Slurry           | Commercial Step-1 slurry        | Commercial non-<br>selective step-2 slurry |  |

| Slurry flow rate | 180 ml/min                      | 180 ml/min                                 |  |

| Pad type         | Rodel IC-1400 with k<br>grooves | Rodel IC-1400 with k<br>grooves            |  |

Table 3.3 Typical Cu CMP Conditioner settings (for step-1 and step-2)

| Parameters            | Settings                  |

|-----------------------|---------------------------|

| Conditioner           | automated 9" diamond grit |

| Conditioning pressure | 0.1 psi                   |

| Conditioning Time     | 30 seconds                |

| Conditioning sequence | ex-situ before polishing  |

The effect of four input parameters, namely, the pad, the polish pressure during step-2 polishing, the step-2 slurry, and the damascene patterns, on damascene CMP was studied in this work. Standard parameters as listed above were used during step-1 polishing; whereas these parameters were varied during step-2 polishing. One exception, however, is that the same kind of pad was used in step-1 as required for step-2 polishing. The variation in the parameters and their respective coding are listed in Table 3.4.

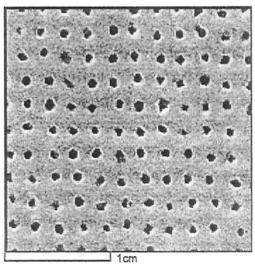

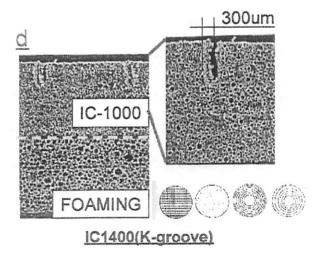

The pictures of the perforated IC1000 pad and the standard IC1400 K-groove pad are shown in Figure 3.10 and Figure 3.11, respectively.

Table 3.4 Input parameters, their variations, and coding