## Copyright © 2004, by the author(s). All rights reserved.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. To copy otherwise, to republish, to post on servers or to redistribute to lists, requires prior specific permission.

# LINKING TCAD AND EDA THROUGH PATTERN MATCHING

by

Frank Edward Gennari

Memorandum No. UCB/ERL M04/31

3 August 2004

# LINKING TCAD AND EDA THROUGH PATTERN MATCHING

by

Frank Edward Gennari

Memorandum No. UCB/ERL M04/31

3 August 2004

## **ELECTRONICS RESEARCH LABORATORY**

College of Engineering University of California, Berkeley 94720

## Linking TCAD and EDA through Pattern Matching

by

#### Frank Edward Gennari

B.S. (Carnegie Mellon University) 2000 M.S. (University of California, Berkeley) 2001

A dissertation submitted in partial satisfaction of the requirements for the degree of

Doctor of Philosophy

in

Engineering-Electrical Engineering and Computer Sciences

in the

**GRADUATE DIVISION**

of the

UNIVERSITY OF CALIFORNIA, BERKELEY

Committee in charge:

Professor Andrew R. Neureuther, Chair Professor Alberto Sangiovanni-Vincentelli Professor Kameshwar Poolla

Fall 2004

| Chair | Date | _ |

|-------|------|---|

|       | Date | _ |

|       | Date | _ |

The dissertation of Frank Edward Gennari is approved:

## Linking TCAD and EDA through Pattern Matching

Copyright © 2004 by Frank Edward Gennari

#### Abstract

#### Linking TCAD and EDA through Pattern Matching

by

#### Frank Edward Gennari

Doctor of Philosophy in Engineering-Electrical Engineering and Computer Sciences

University of California, Berkeley

#### Professor Andrew R. Neureuther, Chair

As the critical dimension in optical lithography shrinks to 90nm and below, determining where the layout is most affected by non-ideal process conditions is increasingly important. In many cases, combinations of local layout geometries that produce or are sensitive to residual effects can be found by locating theoretically problematic configurations of shapes. This dissertation explores the architectural, physical, and algorithmic feasibility of a prototype pattern matching approach as a novel Technology Computer Aided Design (TCAD) tool for linking to Electronic Design Automation (EDA).

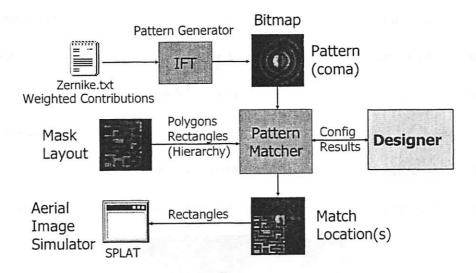

The pattern matcher software architecture was created as a standalone Design for Manufacturability (DFM) tool that fits easily into the design flow and can be applied to many areas of lithography and integrated circuit processing. The development was motivated by the need to relate residual lens aberration effects back to the layout design. For this application, the pattern generator first reads a set of Zernike polynomials and takes the inverse Fourier transform (IFT) of the aberrated pupil function in order to generate the pattern bitmap. The pattern matcher then loads the pattern, a user input parameter file, and a multilayer mask layout in CIF or GDSII format. The match factor is computed along each edge and at each corner of interest, and a resulting sorted table of highest match factors for each pattern is

output. The matching geometry is extracted for more rigorous process simulators such as SPLAT. The system also supports an interactive graphical display of the layout with pattern images drawn over the match locations.

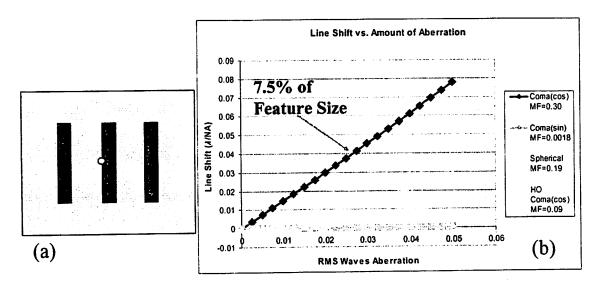

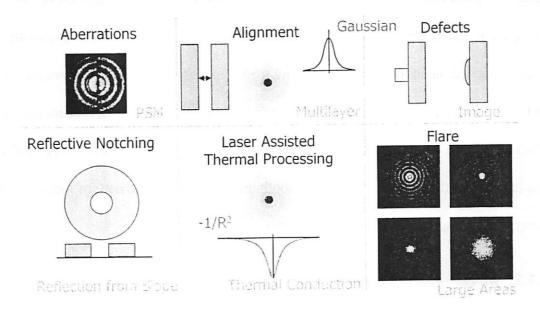

In assessing the physical feasibility of this approach, it has been determined that aberrations produce half the line edge shift as optical proximity effects, and the pattern matcher has been verified to accurately predict electric field change through comparison with SPLAT simulations. Other applications of pattern matching include analyzing effects of misalignment, defects, reflective notching, laser-assisted thermal processing, Chemical-Mechanical Polishing (CMP) dishing, and flare, some of which involve processing multiple layers and performing Boolean layer operations.

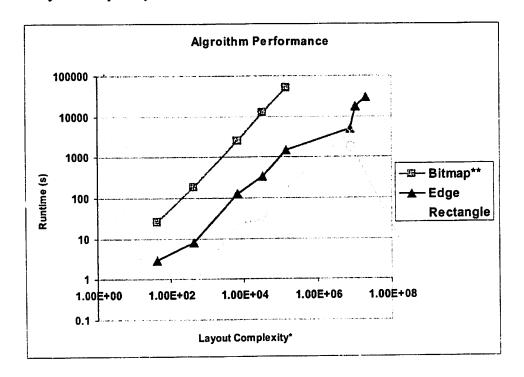

The key contribution to this thesis is the collection of data structures and algorithms that implement pattern matching. The algorithm requirements of searching for images in layouts differ significantly from image correlation, video compression, and geometric matching methods due to the enormous search space, large groups of identical pixel values, complex pixel and layer weights, inexact matching, and filtering methods used. The novel techniques developed for pattern matching include spatial sorting and subdivision of the layout, pre-integration of the pattern, triangulation of polygons, layer Boolean operations, and pre-filtering of match locations. The most efficient matching algorithm uses rectangle and triangle primitives and can efficiently process an entire chip in less than an hour on a standard desktop computer with near perfect scaling on parallel processor machines. This runtime is two orders of magnitude faster than Optical Proximity Correction (OPC).

Professor Andrew R. Neureuther, Committee Chairman

## **Acknowledgements**

This research was funded by the Semiconductor Research Corporation (SRC) contract 01-MC-460 and DARPA grant MDA972-01-1-0021. I would like to thank Professor Andrew Neureuther and his research group for their help in writing the software and explaining various lithography concepts. I would like to thank Garth Robins, Michael Lam, and Kostas Adam for their help with the pattern generation and theory, and Scott Hafeman for his assistance with SPLAT and flare. I would also like to thank Matt Moskewicz for his assistance with the C++ programming, and Shariq Rizvi, and Guille Diez-Canas for their help with the parallel pattern matcher code. I would like to thank Jonathan Hsu, Sachan Madahar, and the other undergraduate system administrators/web developers for creating the web interfaces to the pattern matcher.

## **Table of Contents**

| Acknowle | dgements                                    | 1  |

|----------|---------------------------------------------|----|

|          | ontents                                     |    |

|          | igures                                      |    |

|          | cronyms                                     |    |

|          | uction                                      |    |

| 1.1 On   | rientation                                  |    |

| 1.1.1    | Motivation                                  |    |

| 1.1.2    | Problem                                     |    |

| 1.1.3    | Approach                                    |    |

| 1.2 C    | ontributions of this Dissertation           |    |

| 1.2.1    | Pattern Matching Approach                   | 4  |

| 1.2.2    | Architecture                                |    |

| 1.2.3    | Algorithms                                  |    |

| 1.2.4    | Physical Testing                            | 8  |

|          | issertation Organization                    |    |

|          | round                                       |    |

| 2.1 Li   | thography                                   | 10 |

|          | ptical Proximity Effects                    |    |

|          | ens Aberrations                             |    |

| 2.4 In   | nage Processing & Shape Recognition         | 16 |

|          | n Matching Theory                           |    |

|          | berration Effects                           |    |

|          | berration Pattern Generation                |    |

|          | redicting ΔE and ΔI from ΔX for Aberrations |    |

|          | latch Factor Definition                     |    |

|          | ILTP Definition                             |    |

|          | are System                                  |    |

| 4.1 In   | put and Output Files                        |    |

| 4.1.1    | Patterns                                    |    |

| 4.1.2    | Layout                                      |    |

| 4.1.3    | Layers                                      |    |

| 4.1.4    | Match Requirements                          |    |

| 4.1.5    | Output File Matches                         |    |

| 4.1.6    | Graphical Images                            |    |

|          | ore Pattern Matcher                         |    |

|          | attern Generator                            |    |

|          | ayout Import/Converter                      |    |

| 4.5 Ir   | teractive Display Tools                     |    |

| 4.5.1    | Pattern Matcher Graphical Output            |    |

| 4.5.2    | Simpl_display                               |    |

| 4.5.3    | Display3D                                   |    |

| 4.6 Ir   | nterface to SPLAT Simulator                 | 47 |

| 4.7 Us    | sage of Results                                | 48    |

|-----------|------------------------------------------------|-------|

| 5 Softwa  | are Evolution                                  | 49    |

| 5.1 Ca    | adence DFII/SKILL                              | 49    |

| 5.2 Te    | ext-Based Executable                           | 50    |

| 5.3 O     | penGL Graphical Interface                      | 51    |

| 5.4 H     | ierarchical Layout Import                      | 52    |

|           | arallel Pattern Matcher                        |       |

| 5.6 L     | AVA Website                                    | 54    |

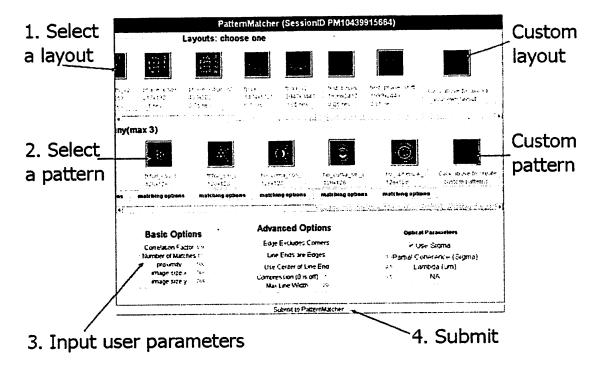

| 5.6.1     | Java Applet                                    | 55    |

| 5.6.2     | Forms/PHP Web Application                      |       |

| 6 Pattern | n Matching Algorithms                          |       |

|           | imitives                                       |       |

| 6.2 Bi    | tmap Algorithm                                 | 63    |

| 6.2.1     | • •                                            |       |

| 6.3 E     | dge Algorithm                                  |       |

| 6.3.1     | 1D Pre-Integration                             |       |

| 6.3.2     | Edge Algorithm Details                         |       |

| 6.4 R     | ectangle Algorithm                             |       |

| 6.4.1     | 2D Pre-Integration                             | 73    |

| 6.4.2     | Rectangle Algorithm Details                    | 73    |

| 6.4.3     | Sorting                                        | 77    |

| 6.4.4     | Inner Matching Loop                            | 78    |

| 6.5 Tr    | riangle Algorithm                              | 79    |

| 6.5.1     | 8-way Pre-Integration                          | 80    |

| 6.5.2     | Clipping                                       | 83    |

| 6.5.3     | Extensions for non 45 Triangles                | 84    |

| 6.6 O     | ther Algorithms                                |       |

| 6.6.1     | FFT-Based Algorithms                           | 89    |

| 6.6.2     | Statistical Sampling Algorithms                | 90    |

| 6.6.3     | Learning Algorithms                            |       |

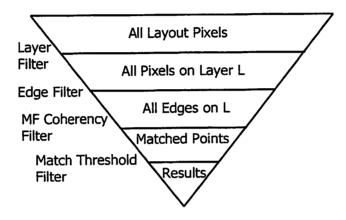

| 6.6.4     | Rejection Algorithms (Inverted Pyramid)        | 92    |

| 6.6.5     | Video and Image Compression Algorithms         |       |

|           | verview and Algorithm Computational Complexity |       |

|           | are Details                                    |       |

|           | DSII File Read                                 |       |

|           | ierarchy                                       |       |

|           | artitioning                                    |       |

| 7.4 G     | eometry Processing                             |       |

| 7.4.1     | Polygon Splitting                              |       |

| 7.4.2     | Shape Merging                                  |       |

| 7.4.3     | Overlap Removal                                |       |

| 7.5 N     | Satch Filtering                                |       |

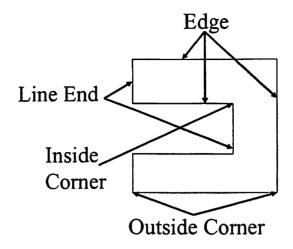

| 7.5.1     | Corners                                        |       |

| 7.5.2     | Edges/Line Ends                                |       |

| 7.5.3     | Layers                                         | . 115 |

| 7.5.4   | Match Factor Prediction Filter                | 115 |

|---------|-----------------------------------------------|-----|

|         | ver Booleans                                  | 118 |

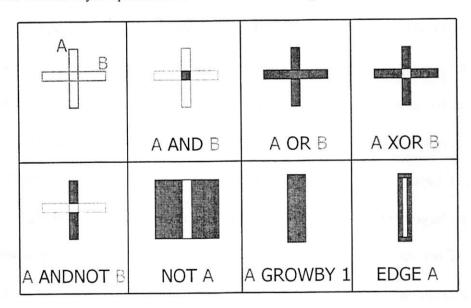

| 7.6.1   | AND, OR, XOR, NOT, ANDNOT                     | 119 |

| 7.6.2   | Grow-by                                       | 121 |

| 7.6.3   | Edge Extract                                  |     |

| 7.6.4   | Layer Operation Complexity                    | 123 |

|         | tch Proximity Factor                          | 124 |

| 7.8 Par | allel Pattern Matching Algorithms             | 125 |

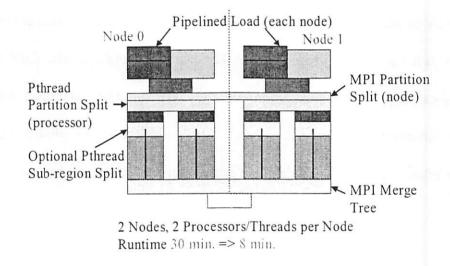

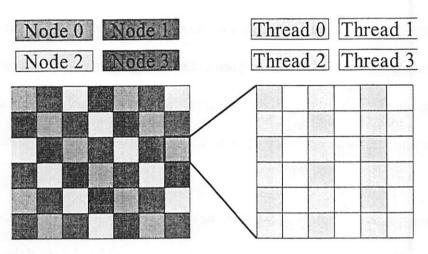

| 7.8.1   | MPI and Parallel Partitioning                 | 130 |

| 7.8.2   | Pthreads Dual Processor Comparison            | 133 |

| 7.8.3   | Dynamic Load Balancing Queue                  | 135 |

|         | Matching Experimental and Performance Results | 140 |

| 8.1 Ex  | perimental Conditions                         | 140 |

| 8.2 Par | tern Matcher SPLAT Verification Procedure     | 141 |

|         | ample Matching Runs                           |     |

| 8.4 Im  | portance of Aberrations                       | 150 |

| 8.4.1   | Effects of Aberrations and Optical Proximity  | 150 |

| 8.4.2   |                                               | 153 |

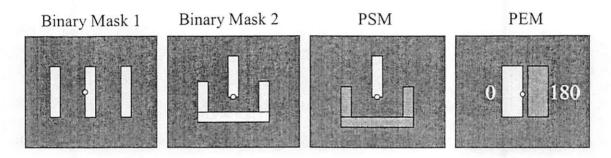

| 8.4.3   | Comparison of Mask Type and Geometry Type     | 154 |

|         | lidation of the Aberration Pattern Matcher    |     |

|         | formance                                      |     |

| 8.6.1   | Algorithm Performance Comparison              |     |

| 8.6.2   | Rectangle Algorithm Performance               | 161 |

|         | mmary of Results                              |     |

|         | onal Applications in Linking Process and EDA  |     |

|         | re                                            |     |

| 9.1.1   | Problem Definition                            | 167 |

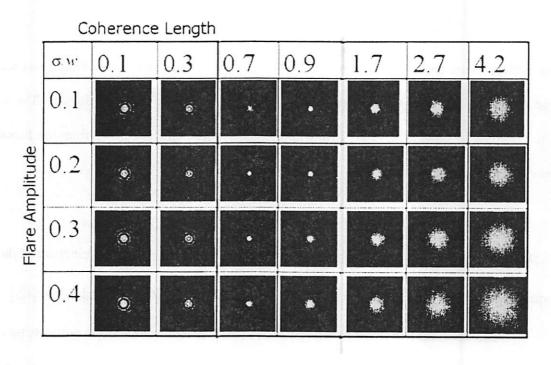

| 9.1.2   | MLTP                                          | 167 |

| 9.1.3   | Flare Results                                 | 169 |

| 9.2 M   | salignment and Defects                        | 170 |

|         | flective Notching                             |     |

|         | ser-Assisted Thermal Processing               |     |

|         | MP Dishing and Erosion and Plasma Etching     |     |

| 9.5.1   | Large Area Patterns                           |     |

| 9.6 Ph  | ase Etch Depth Errors                         |     |

|         | her Applications                              |     |

|         | mmary of Applications                         |     |

|         | clusions                                      |     |

|         |                                               |     |

## Index of Figures

| Figure 1: Pattern matcher system architecture for detecting areas sensitive to lens aberrations                                                                                                                                                                   | . 6      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2: Abacus GDSII layout, 3mm by 3mm, 2μm technology, 14 layers, 5 levels of hierarchy                                                                                                                                                                       | 7        |

| Figure 3: Addition of OPC shapes to layout for improved printed image (image taken from [10])                                                                                                                                                                     | 12       |

| Figure 4: Model-based OPC algorithm flowchart (diagram derived from [10])                                                                                                                                                                                         | 13       |

| Figure 5: Zernike aberration targets (image taken from [29])                                                                                                                                                                                                      | 21       |

| Figure 6: Pattern Matcher Block Diagram                                                                                                                                                                                                                           | 29       |

| Figure 7: Pattern Matcher web applet                                                                                                                                                                                                                              | 56       |

| Figure 8: Custom pattern generation webpage and example custom pattern                                                                                                                                                                                            | 57       |

| Figure 9: New pattern matcher web interface using Forms and PHP                                                                                                                                                                                                   | 58       |

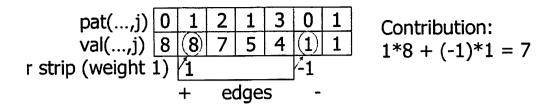

| Figure 10: Demonstration of edge intersection algorithm: pat() is the original pattern matrix, val() is the pre-integrated matrix, and one horizontal rectangle strip is shown. Four bitmap operations have been replaced with two pre-integration matrix lookups | 72       |

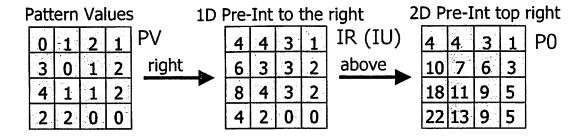

| Figure 11: Illustration of 1D and 2D pre-integration                                                                                                                                                                                                              | 73       |

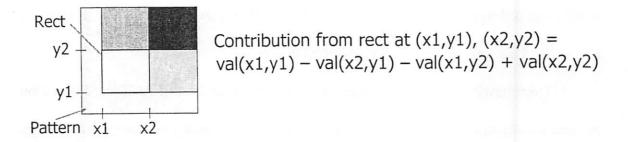

| Figure 12: Illustration of rectangle algorithm                                                                                                                                                                                                                    | 75       |

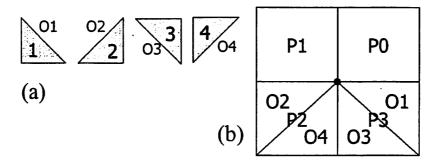

| Figure 13: (a) Four possible triangle orientations and (b) 8-way triangle algorithm pre-integration area                                                                                                                                                          | 81       |

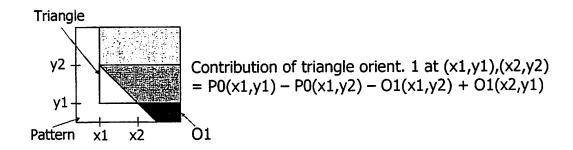

| Figure 14: Illustration of 45-degree triangle algorithm                                                                                                                                                                                                           | 82       |

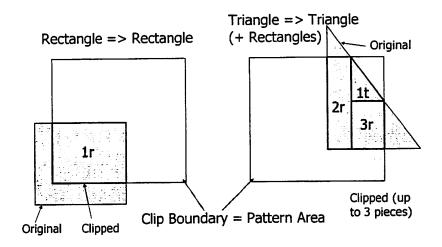

| Figure 15: (a) Rectangle and (b) triangle clipping                                                                                                                                                                                                                | 84       |

| Figure 16: Example of adding the contribution of a rectangle and triangle to the match factor using the (a) bitmap, (b) edge, (c) rectangle, (d) 45-degree triangle, and (e) non-4 degree triangle algorithms                                                     | 5-<br>86 |

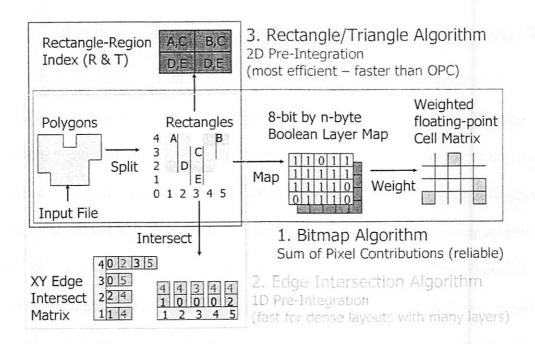

| Figure 17: Pattern matcher data structures for the bitmap, edge intersection, and rectangle/triangle algorithms                                                                                                                                                   | 95       |

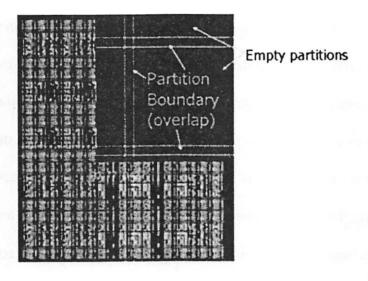

| Figure 18: Layout divided into six overlapping partitions                                                                                                                                                                                                         | 03       |

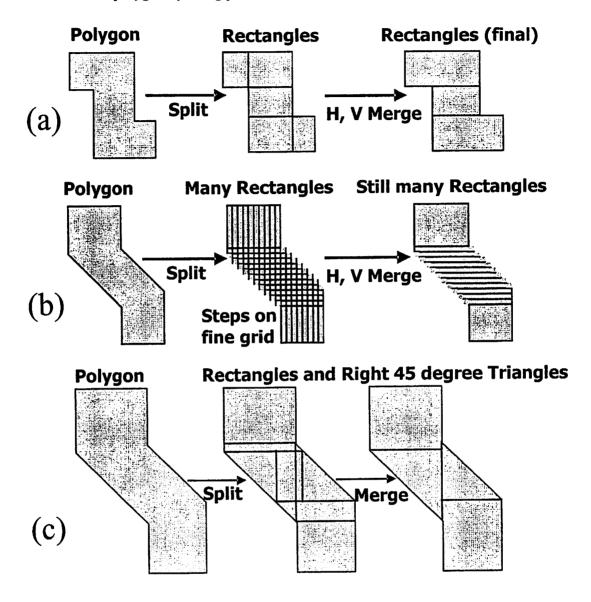

| Figure 19: Splitting of polygons: (a) Manhattan polygon split into rectangles, (b) non-Manhattan polygon split into rectangles, and (c) non-Manhattan polygon split into both rectangles and triangles                                                                                                        | )8  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 20: Multilevel filtering of match locations in the pattern matcher                                                                                                                                                                                                                                     | . 2 |

| Figure 21: Polygon edge and corner classifications                                                                                                                                                                                                                                                            | 5   |

| Figure 22: Illustration of layer Boolean and other operations                                                                                                                                                                                                                                                 | 8   |

| Figure 23: Pattern matching algorithm steps and breakdown of sequential code execution                                                                                                                                                                                                                        |     |

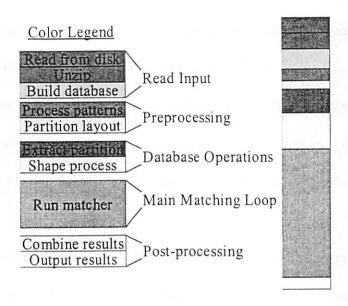

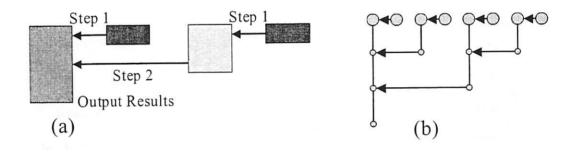

| Figure 24: Breakdown of parallel pattern matcher algorithm                                                                                                                                                                                                                                                    | 27  |

| Figure 25: Spatial layout partitioning strategy for MPI and Pthreads with four nodes and four processors/threads per node                                                                                                                                                                                     |     |

| Figure 26: Binary tree results merge for (a) four and (b) eight processors                                                                                                                                                                                                                                    | 30  |

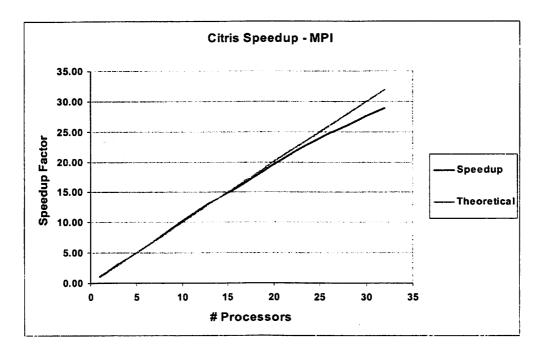

| Figure 27: MPI runtime scalability results for the CITRIS cluster showing a near perfect speedup of 28X on 32 nodes                                                                                                                                                                                           |     |

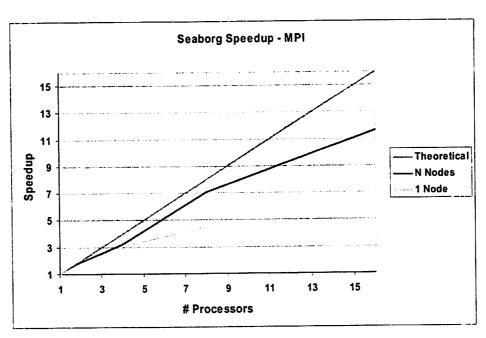

| Figure 28: MPI runtime scalability on the Seaborg machine at NERSC 13                                                                                                                                                                                                                                         | 32  |

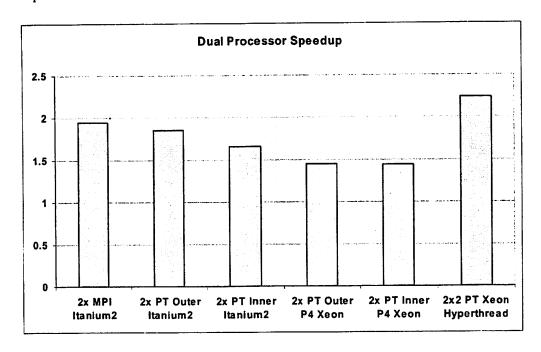

| Figure 29: Pattern matching performance on several dual-processor architectures 13                                                                                                                                                                                                                            | 34  |

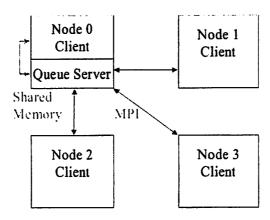

| Figure 30: Dynamic load-balancing queue client/server model including both MPI and Pthreads communication                                                                                                                                                                                                     | 36  |

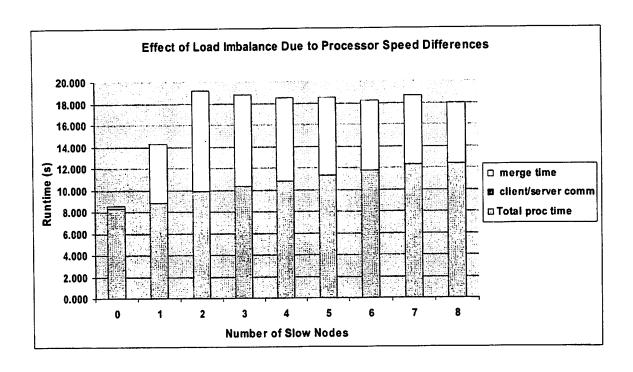

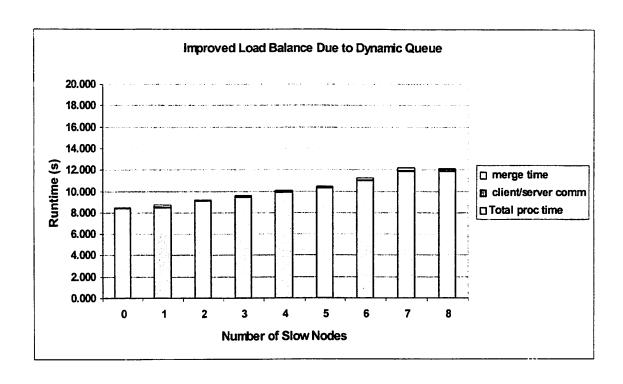

| Figure 31: Parallel pattern matcher runtimes with static load balancing only                                                                                                                                                                                                                                  | 38  |

| Figure 32: Parallel pattern matcher improved runtimes when using dynamic load balancing                                                                                                                                                                                                                       | 39  |

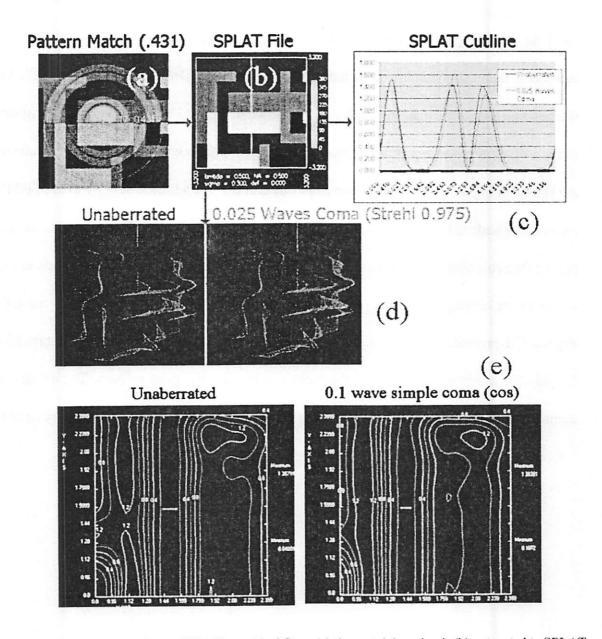

| Figure 33: Pattern matcher to SPLAT graphical flow: (a) the match location is (b) extracted to SPLAT for aerial image simulation, comparison of (c) cutlines and (d) 3D contour plots taken with Display3D with and without 0.025 waves of RMS coma and (e) contour plots with and without 0.1 waves of coma. |     |

| Figure 34: Handcrafted 0/180 PSM test layout for trefoil, coma, and spherical aberration                                                                                                                                                                                                                      |     |

| Figure 35: Example of industry 0/180 PSM used for pattern matching. The match locations indicate locations where optical proximity effects are high                                                                                                                                                           | 15  |

| Figure 36: Coma (cos) match on a clear field binary mask                                                                                                                                                                                                                                                      | 16  |

| Figure 37: Demonstration of a matching run involving several different aberration patterns                                                                                                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 38: Pattern matching run using custom aberration patterns that are a combination of multiple Zernike terms                                                                                                   |

| Figure 39: Trefoil pattern matched over a 0/180 PSM section of "imitation" FPGA layout                                                                                                                              |

| Figure 40: Abacus layout matching run on 45-degree polygon edges                                                                                                                                                    |

| Figure 41: One thousand matches for the runtime "price" of one                                                                                                                                                      |

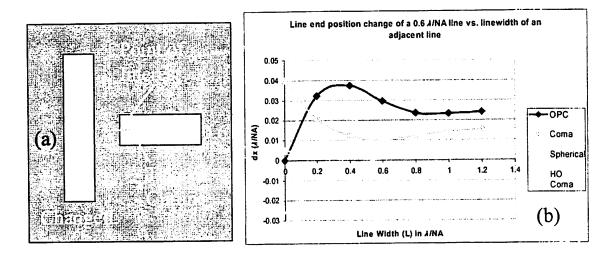

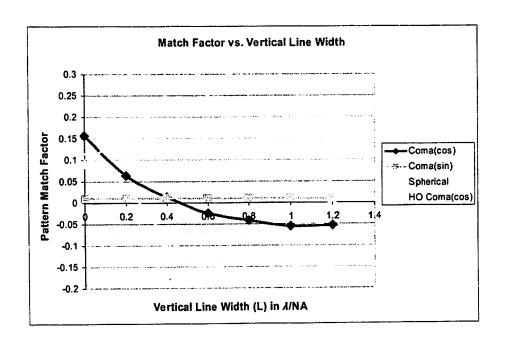

| Figure 42: (a) Binary test layout for measuring aberration and optical proximity effects and (b) simulated line edge shift due to aberrations and optical proximity effects on this test layout                     |

| Figure 43: Match factor sensitivity of vertical line width L in Figure 42a                                                                                                                                          |

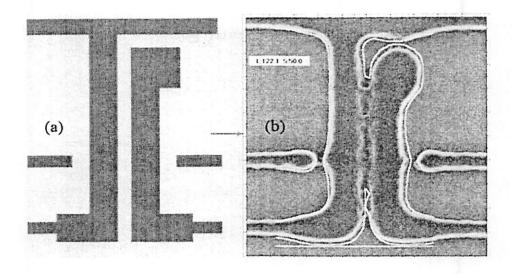

| Figure 44: (a) Clear field binary mask and (b) similar SEM image of printed wafer 153                                                                                                                               |

| Figure 45: (a) Test pattern and (b) corresponding line edge shift due to various lens aberrations on this pattern                                                                                                   |

| Figure 46: Four simple test masks corresponding to the four entries in Table 5 155                                                                                                                                  |

| Figure 47: Comparison of match factor prediction of electric field change with SPLAT simulations                                                                                                                    |

| Figure 48: Pattern matching algorithm runtime comparison,                                                                                                                                                           |

| Figure 49: MLTPs for various pattern matching applications                                                                                                                                                          |

| Figure 50: Flare MLTPs for various values of $\sigma$ and $w$                                                                                                                                                       |

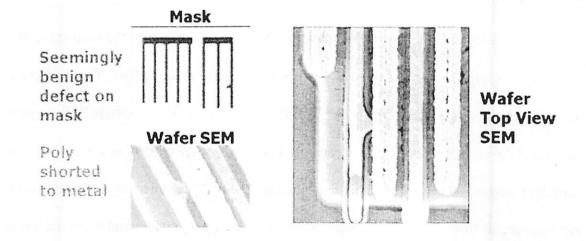

| Figure 51: Example of a defect on a polysilicon gate: (a) SEM of defect on poly mask, (b) bottom view SEM showing polysilicon shorted to metal by defect, and (c) top view SEM                                      |

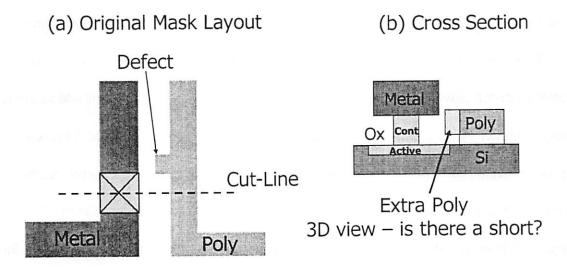

| Figure 52: (a) Drawn mask layout with defect and (b) device cross-section showing potential short due to defect                                                                                                     |

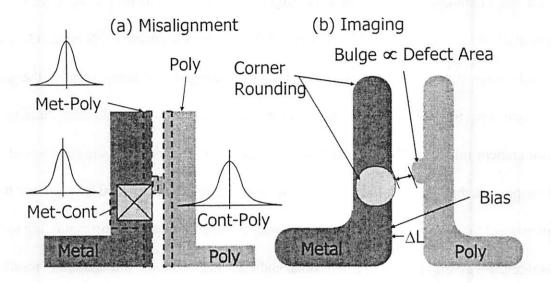

| Figure 53: Defect and misalignment problems may cause shorting between polysilicon and metal. The drawn image is statistically affected by (a) misalignment and (b) imaging when determining the effects of defects |

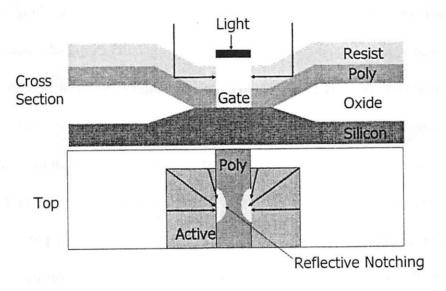

| Figure 54: Demonstration of the reflective notching phenomena                                                                                                                                                       |

| Figure 55: Laser-assisted processing (a) MLTP and (b) demonstration of match location  176                                                                                                                               |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Figure 56: Experimental pattern matching runs on a register cell that locate areas sensitive to (a) polysilicon melting during LAP, and (b) reflective notching                                                          |  |

| Figure 57: Example of CMP dishing of soft material between two supporting posts of harder material                                                                                                                       |  |

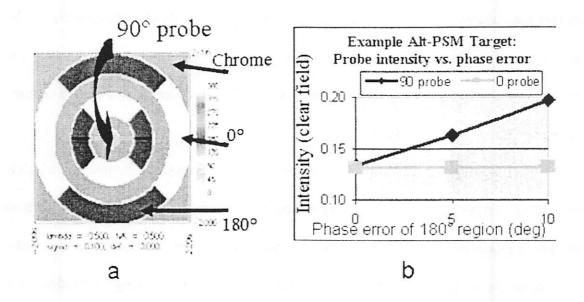

| Figure 58: (a) Example mask pattern to detect errors in mask making and (b) The intensity of the probe compared to a nearby isolated probe is a direct measurement of phase etch error of the 180 degree shifted regions |  |

## **Index of Acronyms**

ACLV Across-Chip Linewidth Variation

BARC Bottom Anti-Reflective Coating

BMP BitMaP

CAD Computer Aided Design

CD Critical Dimension

CGI Common Gateway Interface

CIF Caltech Intermediate Format

CITRIS Center for Information Technology Research in the Interest of Society

CMP Chemical-Mechanical Polishing DFM Design for Manufacturability

DFII Design Framework II

DRC Design Rule Check

EDA Electronic Design Automation

ESF Edge Skip Factor

FFT Fast Fourier Transform

FPGA Field Programmable Gate Array

GDSII Graphical Data Stream II

GLUT Graphics Library UTilities (for OpenGL)

GUI Graphical User Interface

IFFT Inverse Fast Fourier Transform

IFT Inverse Fourier Transform

JPEG Joint Photographic Experts Group

LAP Laser-Assisted Processing

LAVA Lithography Analysis using Virtual Access

LTP Laser Thermal Processing

LOD Level of Detail MF Match Factor

MLTP Maximal Lateral Test Pattern MPI Message Passing Interface

NA Numerical Aperture

NERSC National Energy Research Scientific Computing Center

NGC Normalized Grayscale Correlation

OASIS Open Artwork System Interchange Standard

OPC Optical Proximity Correction

OpenGL Open source Graphics Library

OPD Optical Path Difference OTF Optical Transfer Function

PC Personal Computer PEM Phase Edge Mask

PPC Process Proximity Correction

PSF Point Spread Function PSM Phase Shift Mask Pthreads POSIX threads

RET Resolution Enhancement Technique/Technology

RMS Root Mean Square

SEM Scanning Electron Microscope/Micrograph

SEMI Semiconductor Equipment and Materials International

SIMPL-2 SIMulated Profiles from the Layout version 2

SPIE Society of Photo-Optical Instrumentation Engineers - The International

Society for Optical Engineering

SPLAT Simulation of Profile and Lithography Analysis Topography

STL Standard Template Library

TCAD Technology Computer Aided Design

## 1 Introduction

#### 1.1 Orientation

#### 1.1.1 Motivation

In order to enable the next generation of integrated circuit technology, it is important to find an efficient way of linking residual processing effects back to the circuit design stage. In this way, information can flow back to designers so that problems can be corrected early in the design. This is the fundamental concept of Design for Manufacturability (DFM). Current Electronic Design Automation (EDA) tool features such as Optical Proximity Correction (OPC) typically only deal with first order processing effects and neglect the impact of effects such as lens aberrations on the printed image. As minimum feature sizes continue to shrink to the 90nm node and below, it is becoming increasingly important to take these processing effects into account within the EDA tool environment of the designers. The pattern matching system presented in this dissertation is a valuable way of linking Technology Computer Aided Design (TCAD) with EDA.

#### 1.1.2 Problem

Residual processing effects such as lens aberrations, flare, and reflective notching cause unwanted effects such as line edge shift and critical dimension (CD) variation. EDA tools exist that correct for the optical proximity effects and other well-modeled and predictable problems, but there are relatively few software tools that take into account other difficult to predict, not well understood, or secondary non-idealities in integrated circuit

manufacturing. Predicting the results of these effects requires time-consuming simulations that often cannot be run full chip and otherwise require tedious user input to limit the simulation area. Because of their complexity, standard design rules cannot locate areas sensitive to these effects, especially the statistical problems. Furthermore, many of these process correction tools occur late in the design stage after a significant amount of time and effort have been spent on a problematic design, requiring expensive mask rewrites. In addition, the number of circuit features that need to be taken into account when predicting the results of these processing effects is continuously growing as the layout scales faster than the area of influence. The adoption of phase-shifting masks not only contributes to the complexity of processing effects such as lens aberrations, but it also makes the effects more severe.

These lithographic and processing effects cannot be neglected in the design of modern chip layouts in the sub-100nm, low k1 regime where feature widths are less than a quarter the wavelength of the light used to print them. Ignoring the effects of aberrations and other residual processing effects may result in reduced reliability and yield loss in the fabricated design or an increased number of mask rewrites. B. Grenon [1] reports that masks must often be written three times and, in some cases, as many as seven times. It is becoming more and more critical that these effects be taken into account when designing the circuit layout. Conservative over-specification of the design through tight design rules is not the answer to this problem.

## 1.1.3 Approach

If the geometries that are most susceptible to residual processing effects can be

determined, then a search can be made to locate all areas in an integrated circuit layout design that are similar to these sensitive geometries. This search can be performed for a very general class of physical effects by pattern matching a bitmap representation of the theoretically most sensitive pattern on the layout. All matches found are potential problem areas that must be examined in more detail by the designer or process engineer to determine if action needs to be taken. These problematic geometries can then be modified to reduce the layout's overall susceptibility to process-induced manufacturability issues. This software system allows designers to utilize processing information developed by technologists so as to produce lithography-friendly designs. Pattern matching can thus be used to determine when a design is ready for tape-out. Alternatively, these areas predicted to be most affected by aberrations and other residual processing effects could be recorded and later used to reduce the number of locations that must be inspected in the printed layout.

This pattern-matching procedure can potentially reduce the effects of imperfect optics and other integrated circuit manufacturing equipment on the printing of the image from the mask to the wafer, improving the yield of the design. Patterns can even be generated from the quantitative description of the manufacturing equipment that will be used. This allows a designer to tailor the design to be robust to the limitations of the particular machines that will be used to manufacture it. Non-ideal processing effects can be compensated for in a way similar to OPC.

The pattern matching system is fast enough to be run on a full chip layout and exists entirely in software thus does not require printing of test wafers or other expensive procedures. Pattern matching is therefore a fast and low cost method of improving the robustness of integrated circuit layouts early in the design cycle.

#### 1.2 Contributions of this Dissertation

The goal of this research was to create a complete system based on a sound theoretical background that provides an efficient way of locating layout geometries that are the most affected by physical effects involved in the manufacturing of semiconductors. The contributions of this dissertation can be broken down into three areas: architectural, physical, and algorithmic. The architectural contributions involve the creation of a pattern matching system that allows a user to analytically specify a pattern, import layout geometry in a standard format, process the layout, and receive a list of locations that meet the matching criteria. The physical aspects of this project can be broken down into the theoretical derivation of the patterns used in the matching, testing on various layouts, and verification of the match results against simulation. The algorithmic contributions include the bitmap, edge, rectangle, and triangle algorithms along with their data structures and supporting geometric algorithms. The following sections describe the pattern matching approach, the system architecture used to implement this approach, the algorithms used for efficient pattern matching, and the physical testing used to verify the accuracy and importance of the pattern matching software system.

## 1.2.1 Pattern Matching Approach

This research project began with the pattern matcher theory and the initial application of determining areas in a mask layout sensitive to lithographic lens aberrations. Finding a quantitative method of measuring and reducing the layout's sensitivity to lens aberrations at the design stage had not previously been done and was thus a motivation for this research.

The lens aberration application was the driving force behind the pattern matcher project and defined the initial goals and requirements of the system. Using the theory developed by Robins, Neureuther, and Adam [30] that the inverse Fourier Transform of Zernike polynomials over a circular pupil provides the aberrated point spread function (PSF), a library of patterns has been generated for representing various lens aberration terms. Extensions to the aberration theory have been applied to generate equations used to derive the electric field change, intensity change, and line edge shift from the calculated match factor.

The lens aberration pattern matching idea has been generalized to a Maximal Lateral Test Pattern (MLTP) representing the worst case geometries for a number of residual processing effects. MLTPs have been formulated and patterns generated for applications such as flare, reflective notching, laser-assisted processing, CMP dishing, defects, and misalignment.

#### 1.2.2 Architecture

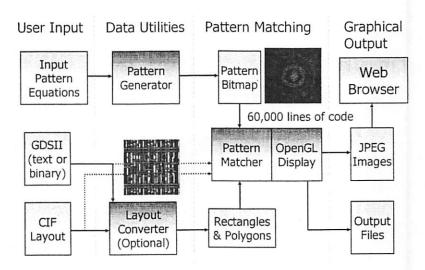

A software system has been written which implements efficient pattern matching algorithms in order to test the pattern matching theory. This system includes a program for generating aberration patterns from the inverse Fourier transform (IFT) of Zernike polynomials and flare patterns from the IFT of scattered light equations. It also includes a tool for loading CIF and GDSII layouts and either storing them hierarchically or converting them to other formats. The core pattern matcher executable then reads the layout and patterns and produces various text files and one or more images of the results. The system utilizes a custom high-performance OpenGL interactive graphical display system developed for

viewing the pattern matching results. Layouts, patterns, and various simulation results can also be viewed with these display programs. Together, these components form a complete software system that directly reads a layout in standard industry formats and a set of pattern equations, producing both textual and graphical results of all locations in the layout that are sensitive to the processing effect described by the pattern equations. Figure 1 gives an overview of the system architecture as used for determining sensitivity to lens aberrations. A more thorough description of the software is given in Chapter 1.

Figure 1: Pattern matcher system architecture for detecting areas sensitive to lens aberrations

## 1.2.3 Algorithms

One of the most important contributions to this research is the set of algorithms that has been implemented in the core pattern matcher executable. Four generations of algorithms have been developed, each much more efficient than the last: the bitmap algorithm, edge-intersection algorithm, rectangle algorithm, and rectangle/triangle algorithm. The algorithms involve pre-integrating the pattern matrices, splitting polygons into smaller primitives, spatially partitioning and sorting the layout geometry, computing Boolean operations on

layers, and filtering match locations by various methods. The novel algorithms that have been developed for efficient pattern matching include not only the core pattern matching components but also the method of computing layer Boolean and other operations on rectangles by recursively spatially subdividing the layout into small areas that can be processed very quickly and stitched back together. The unique polygon splitting algorithm can divide an arbitrary polygon into a minimal set of simpler shapes through repeated horizontal and vertical subdivision into smaller polygons until the sub-polygons are simple rectangles and right triangles. Another important component of this research is the compressed hierarchical database structure that allows for efficient query of pattern matching results, and the related interactive layout graphical display engine.

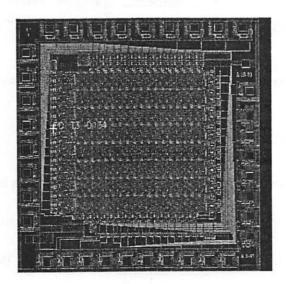

These algorithms combined allow the program to efficiently process a full chip layout in only minutes on a standard desktop PC or workstation. Abacus.gds<sup>1</sup>, one example of a full chip GDSII layout that the pattern matcher has been run on, is shown in Figure 2.

Figure 2: Abacus GDSII layout, 3mm by 3mm, 2µm technology, 14 layers, 5 levels of hierarchy<sup>1</sup>

<sup>1.</sup> Example from Dolphin Integration, http://www.dolphin.fr/medal/socgds/socgds\_free\_overview.html

## 1.2.4 Physical Testing

A significant contribution to this dissertation involves the physical verification of the aberration pattern matcher theory. Experimental simulations have been performed on a number of test layouts that show the effect of lens aberrations on feature edge positions is significant, resulting in as much as half the line edge shift as optical proximity effects even for high-quality optical lenses. SPLAT aerial image simulations have been used to analyze the effects of geometry on line end and line edge shift due to even and odd lens aberrations such as coma.

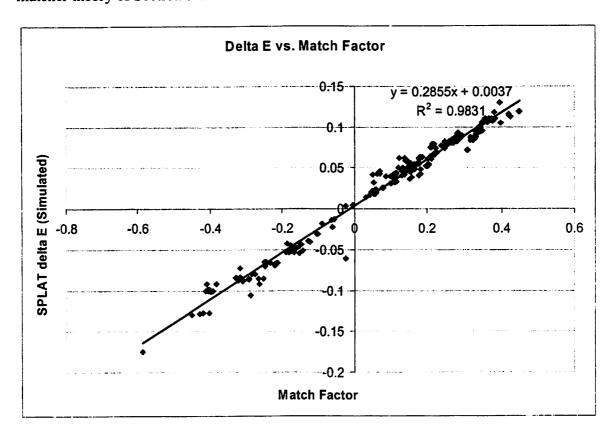

In addition to verifying the importance of aberrations, the accuracy of the pattern matcher in predicting the geometries sensitive to aberrations has been proven through simulation. These experiments involved running the pattern matcher on a large number of hand drawn, script generated, and real industry layouts. The pattern matcher was found to predict electrical field changes that agreed well with SPLAT simulations, and these electric field changes can be extended to the computation of intensity changes and line edge shifts.

Some other pattern matching applications have also been experimentally verified to some extent. The effects of flare at various magnitudes and coherence lengths were analyzed in a number of situations. The pattern matcher was found to locate areas in a layout sensitive to flare as well as optical proximity effects. In addition, pattern matching runs have been performed on hand-crafted test layouts for applications such as laser-assisted processing, reflective notching, and CMP dishing.

### 1.3 Dissertation Organization

This dissertation begins with background information and previous work in the relevant areas of lithography in Chapter 2, including lens aberrations and Optical Proximity Correction. Chapter 3 discusses the theoretical background of pattern matching for the application of lens aberrations, the meaning of the match factor, and the definition of a Maximal Lateral Test Pattern. Chapter 4 describes the pattern matcher software system and how each of the components contributes to a complete EDA tool. Chapter 5 explains how the pattern matching software has evolved from a simple tool that was integrated into the Cadence Design Framework II to a standalone graphical system. Chapter 6 compares in detail the various pattern matching algorithms that were examined and the strengths, weaknesses, and performance of each. Chapter 7 describes the details of the software data structures and algorithms, including some of the novel features of the system. Chapter 8 presents results that show the importance of lens aberrations, verify the accuracy of the match factor prediction, and give performance numbers on real full-chip layouts. Chapter 9 extends the pattern matching idea to other areas of lithography and wafer processing. Finally, concluding remarks are given in Chapter 10.

## 2 Background

This dissertation involves a broad range of topics from several engineering fields, including lithographic issues such as lens aberrations and OPC, computational geometry, computer science algorithms, CAD/EDA tools, and computer graphics. Some of these areas and additional background material are introduced in the following sections.

## 2.1 Lithography

Most of the pattern matching applications discussed in this dissertation are in the area of lithography. The pattern matcher system was designed to locate areas in a layout that are sensitive to problematic effects somewhere in the process of turning a set of polygons stored on a designer's hard drive into a printed image on a wafer. These circuits contain polygons that will eventually be printed as tiny metal and polysilicon lines on the order of 100nm or less in width, or around one thousandth the width of a human hair. Recent technology nodes involve printing line widths smaller than the wavelength of the light used, which requires a significant number of Resolution Enhancement Techniques (RETs) [2, 3, 4]. The polygons representing an integrated circuit layout are first written to a mask, which is then used to print a large number of wafers through an extremely complex lithographic process. The wafers are then cut into individual chips that are packaged into integrated circuits such as microprocessors and memory. The lithographic process involves a stepper or scanner projecting light through the openings on the mask, through a complex system of lenses that reduces the size of the image, and onto the wafer, where the light exposes the photo-sensitive

resist and creates images approximating the original mask polygons.

This process is by no means easy or exact. The lithography process is a limiting factor in determining the critical dimension of the technology, and thus is continuously pushed to its limits to further reduce feature sizes. As these feature sizes shrink, the effects of polygons on their neighbors become increasingly strong. The results of an imperfect optical path and of adjacent feature interactions are difficult to predict at the full chip level, but are extremely important in creating a manufacturable design with good yield. Thus it is critical to determine which geometries are prone to adverse lithographic process effects early in the design cycle, before the expensive masks are even written.

## 2.2 Optical Proximity Effects

Lithographic projection printing systems employ a series of lenses to send light through the mask and produce a de-magnified image in the resist on the wafer. Light entering the openings in the mask produces plane waves that are the Fourier transform of the mask geometry. The lens then low-pass filters and inverse Fourier transforms (IFTs) the transmitted plane waves to reproduce an image in the resist resembling the original mask openings. Several problems arise from the small size of modern integrated circuit device features and the finite size and inherent limitations of the imaging systems. First, since the lens system is diffraction limited, the high spatial frequency components required to reproduce the sharp edges in polygon features fall outside the lens. Secondly, stray light entering the opening from one shape may find its way into another shape in close proximity, leading to a complex interaction of the electric fields of adjacent polygons. Thus the final

shapes will have rounded corners and may bulge towards adjacent shapes, possibly shorting together (bridging) and rendering the chip defective if the situation is severe.

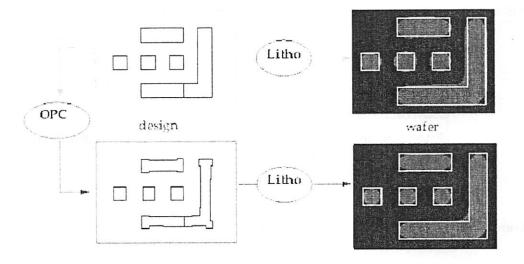

Optical Proximity Correction (OPC) [5, 6, 7] is a step in the manufacturing process that semiconductor manufactures employ to improve the manufacturability of high-performance integrated circuit designs such as microprocessors. OPC is the process of modifying the polygons that are drawn by the chip designers in order to compensate for the limitations of the lithographic process assuming a perfect but finite lens. Given the shapes desired on the wafer, such as exact line widths and sharp corners, the mask is modified to improve the reproduction of the critical geometry [8, 9]. This is done by dividing polygon edges into small segments and moving the segments around, and by adding additional small polygons to strategic locations in the layout. The addition of OPC serifs and scatter bars to a layout is shown in Figure 3 [10]. The addition of OPC features to the mask layout allows for tighter design rules and significantly improves process reliability and yield. However, OPC also increases the data size and may destroy the hierarchy.

Figure 3: Addition of OPC shapes to layout for improved printed image (image taken from [10])

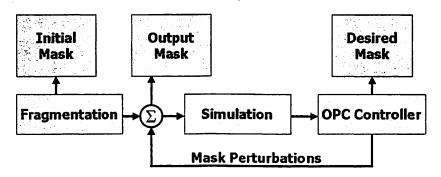

OPC is often run on the entire chip at once and iterated until convergence. There are many different types of OPC algorithms, the two main classifications being rule-based and model-based. Each involves subdividing polygons into smaller shapes or edge segments, known as fragmentation, and moving or adding shapes to other positions. Rule-based OPC is simpler in that various geometries are treated by different rules from a rule library. Modelbased OPC, as demonstrated in Figure 4, is more complex and involves performing fast optical image simulations, which may be accomplished by computing a weighted sum of presimulated "OPC kernels" for simple edges and corners that are stored in a library. The proximity effects due to adjacent shapes is additive in electric field, but since the actual printed feature edges are related to light intensity  $I = E \cdot E^*$ , the nonlinear addition of terms requires multiple kernels and longer computation times. Model-based OPC is an iterative solution involving repeated simulation and modification of geometry to incrementally improve the image. Managing the large geometry database is CPU intensive, and the simulations involved in model-based OPC are even more CPU intensive since there is no closed form solution for the optimal layout.

Figure 4: Model-based OPC algorithm flowchart (diagram derived from [10])

Pattern matching is similar to OPC since it involves predicting the effects of the lithographic process on the printed image. The algorithms are in fact related as well, as both

OPC and pattern matching can look up polygon features in a table to determine the contribution of each feature at some point in the layout. The rectangle and triangle pattern matching algorithms explained in Section 6.4 and Section 6.5 are similar to the edge table lookup used in the OPC algorithm developed by Nick Cobb [10]<sup>2</sup>.

#### 2.3 Lens Aberrations

Ideal lithographic lenses act as low-pass filters, resulting in corner rounding due to the loss of high spatial frequencies. Furthermore, lenses may also have aberrations, or deviations between the real and ideal wavefronts exiting the lens. Aberrations distort light rays so that the reduced image in the wafer is not an exact demagnification of the object. Aberrations correspond to optical path differences due to inhomogeneity in the lens material, imperfect lens shape, or incorrect alignment of optical elements in the tool, which produce phase differences in the resulting plane waves. The Strehl ratio [11] is a measure of the quality of a lens and can be as high as 0.986 in modern lithographic lenses, corresponding to at most 0.014 waves of RMS lens aberration. The human eye typically contains much larger amounts of lens aberration, which results in reduced clarity of vision.

An inherent effect of lens aberrations is that they take light from openings on the mask and redirect it towards incorrect locations on the wafer, decreasing pattern fidelity and reducing the manufacturability of the design. Even the small amounts of aberrations present in modern, high-quality optical lenses can lead to Across-Chip Linewidth Variation (ACLV)

<sup>2.</sup> http://www-video.eecs.berkeley.edu/papers/ncobb/cobb/phd/thesis.pdf

and reliability problems [12]. Common aberrations include coma, astigmatism, spherical, and trefoil. Additional background material on aberrations, their effects on imaging, and their measurement techniques can be found in [13]. Other methods for measuring aberrations include phase-edge focus monitors [14], the Litel mask<sup>3</sup>, Dirksen's phase dots [15, 16, 17], the measurement of side-lobe artifacts on halftone masks by Hayano, Fukuda and Imai [18, 24], and Kirk's double exposure method [13].

Traditional design flows include an OPC step that modifies the polygon edges to take the optical proximity effect due to surrounding shapes into account and correct for low-pass filtering. However, aberrations are additional phase errors in the Fourier spectrum [19] and may be different for each projection printing machine. A significant amount of work is in progress to characterize the aberrations in printing equipment for the purpose of "aberration proximity correction". There is no generalized solution to reducing the effects of all lens aberrations on a layout, and it is often not feasible to run separate corrective runs on each design for every aberration of every stepper or scanner. There is a need for a system that can quickly process the entire layout and locate areas where a known set of lens aberrations will have a significant effect on the printed image. Thus, the pattern matcher was initially created as a solution to this problem.

This dissertation suggests using a multi-prong approach to aberration proximity correction. The first step is to reduce the aberrations in lithographic equipment to the extent possible, which is the responsibility of the equipment manufacturer. The next step is to actually measure the dominant residual aberrations that could not be removed from the tools.

<sup>3.</sup> http://www.litel.net

The final step is to make the layouts less sensitive to these dominant residuals through a pattern matching approach. This is clearly a complex problem involving tool manufacturers, process engineers, and circuit designers.

## 2.4 Image Processing & Shape Recognition

Image processing and shape recognition generally fall under computer science, computer learning, or computer vision. In many cases, the images used are photographs or video camera feeds, and the objectives of computer vision and shape recognition are to locate a certain shape or sub-image in a larger image. In some cases the objective is to determine if two images match.

If the integrated circuit layout is represented as a large image and the pattern is also represented as an image (for purely real-valued patterns), then any generalized image-processing algorithm can be used. Therefore, pattern matching is a form of image processing and image processing theory can be applied. However, most image processing algorithms are inefficient for images as large as an integrated circuit bitmap representation. The reason pattern matching is still a tractable problem is that the layout "images" have certain properties that can be utilized to make pattern matching easier. The pattern matching algorithms developed under this research are compared with standard image processing and shape recognition algorithms in Section 6.6 on the basis of performance, features, and accuracy.

## 3 Pattern Matching Theory

#### 3.1 Aberration Effects

The optical lenses of a non-ideal lithographic system may contain aberrations, which correspond to optical path differences in the lens material that produce phase differences in the resulting plane waves. The pattern matching approach involves determining the geometries which are the most sensitive to a residual processing effect, which is best done through a theoretical analysis of the effect. The patterns used to locate areas sensitive to lens aberrations can be derived from the optical system's parameters and aberration fingerprints of the lenses, which provide a clear representation of the effects of lens aberrations on geometries to be printed. A perturbational analysis [20] of lens aberrations is given below and also provided in [21], and a discussion of the modeling of PSM optics is given in [22]. Portions of the following discussion have been taken from [23].

An integral over the lens pupil is used to determine the optical path difference (OPD) due to aberrations and takes the form of  $e^{jOPD}$ . When aberrations are small, the exponential factor can be linearized [24] by a Taylor series expansion as  $e^{jOPD} \approx 1 + jOPD$ . The constant 1 gives the electric field for an unaberrated image, and the jOPD term represents an additional electric field component that spills outside of the image of a point source and is proportional to the size of the OPD. For a modern lens with a Strehl ratio [11] of 0.975 [25], a two-term Taylor series approximation is reasonable as the total RMS aberration is 0.025 waves, the peak OPD function values are about 0.05 RMS waves, and a third term is at most only 10% as large as the first term. These spillover electric fields from adjacent features must be added,

and in forming the composite it is equivalent to simply determine the similarity of the region surrounding an observation point to the spillover function. This spillover function is the IFT of the OPD function and for the special case of a single Zernike [20] aberration it is the IFT of that Zernike term.

The goal is to determine the additive electric field of the jOPD term from a collection of mask openings in a neighborhood of a central observation point. One approach is to compute the contribution to the electric field from each of the surrounding pixels and then sum them up. A more interesting alternative is to first view the problem in the pupil of the lens and attempt to maximize the spillover from the jOPD term onto the unaberrated image term. In this view the additive field will be largest when the incident electric field is uniform in magnitude and exactly cancels the phase of the OPD. That is, the additive field in the pupil is proportional to  $e^{-jOPD} \approx 1 - jOPD$ . The inverse Fourier transform (IFT) of this function in the pupil can be used to determine the pattern on the mask that will create this maximized spillover onto the unaberrated image of the central pixel. The IFT of the constant term corresponds to a fixed infinitesimal pinhole at the pattern center. The effect of this pinhole is independent of the level of aberrations and so it may be disregarded in studying the additive perturbation due to aberrations.

The IFT of the second term yields the desired composite pattern centered at the observation point on the mask that will produce the greatest spillover onto the observation point for the given set of aberrations making up the OPD. This pattern is zero at the observation point itself due to the fact that the Zernike functions other than the zeroth that are included in aberration measurements individually have zero area when integrated over the pupil. The zeroth order term can be viewed as producing the unaberrated image complete

with optical proximity effects. The contribution of the IFT test pattern at the wafer to an additive aberration-induced electric field  $E_A$  at the central observation point can be calibrated as follows. First compute the IFT for a given jOPD and digitize it into a pattern surrounding the central observation point. Then simulate the aerial image of this pattern in the presence of aberrations and take the square root to convert intensity to electric field. Here  $E_A$  is a complex quantity and its imaginary part comes from even aberrations (such as defocus, spherical, and astigmatism) while its real part comes from imaginary aberrations (such as coma and trefoil). Simulating the image of this pattern under the illumination conditions utilized in printing the wafer is believed to also help account for the reduction in sensitivity with partial coherence. The theory above implicitly assumes coherent illumination rather than the partial coherence used in various illumination schemes in projection printing.

The intensity increase and feature position change can be estimated from the electric field spillover by applying a second perturbational argument developed for assessing defect printability [26, 27]. At an observation point such as a line edge or line end, the unaberrated image of the feature can be taken as the dominant electric field contribution. The aberration spillover then adds a second smaller contribution  $\Delta$ . Say, for example,  $\Delta$  is 0.1. If the spillover is in phase, the intensity will increase as  $(1+2\Delta+\Delta^2)\approx(1+2\Delta)=1.2$ . However, if the addition is in quadrature, the increase will be only  $(1+\Delta^2)=1.01$ . It is anticipated that the former case will occur for odd aberrations and the latter case will occur for even aberrations. The feature position change can then be evaluated by simply assuming that the entire feature intensity shifts upward locally, and then finding the new position of a fixed threshold image intensity.

A method of determining the intensity change and line edge shift from the electric

field change is given in Section 3.3. This method is based on the procedure described in [21] of separating the portion of the electric field into components that are orthogonal to the feature electric field and co-linear with the feature, and by using the fact that intensity can be approximated by the square of the electric field:  $I = E \cdot E^* = |E|^2$ , where \* refers to the complex conjugate operation.

A final theoretical note is that the partial coherence of the illumination plays an important role. In making the calculations for this research, the mutual coherence between the layout contribution point and the match point has been included in summing up the pattern match factor. The pattern is multiplied by the mutual coherence function for a conventional illumination system as a preprocessing step:

$$u_{TOP\_HAT}(r) = \frac{J_1(2\pi\sigma r)}{\pi\sigma r}$$

This effect was included to be more realistic in our assessment as the more incoherent the illumination, the less the spillover and the lower the aberration impact. In so doing we also found a numerical advantage in that the error in truncating the radial integral to a finite size became more acceptable at smaller areas of integration. Results for several illumination functions are available [28].

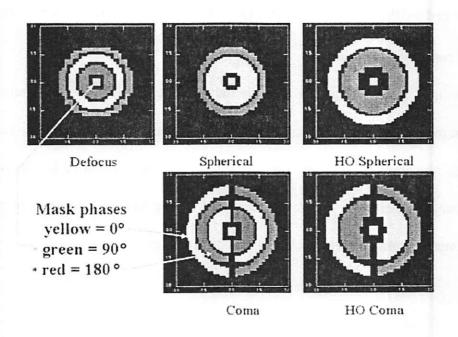

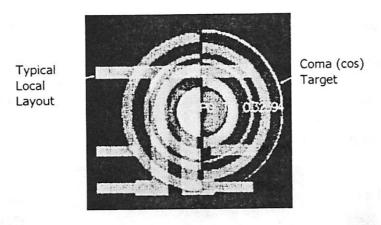

Examples of finite radius approximations to these spillover functions for five Zernike terms are shown in Figure 5. These are actually Zernike monitor patterns and include a separate central phase reference probe for measuring aberration levels [29]. These targets consist of alternating regions of 0- and 180-degree phases, with either a 0-degree or 90-degree probe in the center. The colored phases and positions of the concentric rings and other shapes are computed using the sign of the IFT of the Zernike polynomial, and each region is

separated by a small chrome border. The value of  $\lambda$  for this figure was chosen to be 0.5 $\mu$ m and NA was set to 0.5, so that  $\lambda/NA = 1.0\mu$ m. Each of the five dark boxes containing the targets in Figure 5 is 6.4  $\lambda/NA$  by 6.4  $\lambda/NA$  in size, or 6.4 $\mu$ m square.

Figure 5: Zernike aberration targets (image taken from [29])

It is difficult to predict in advance whether binary or phase-shifting masks (PSMs) will be more prone to aberration effects. Since PSMs have the ability to drive both the positive and negative areas of the spillover function, it is only natural to expect phase-shifted layouts to generate match factors that are potentially twice as large as those of binary masks. On the other hand, the use of phase-shifting regions can result in steeper image slopes, especially in the case of phase-edge masks. Another important factor is the subset of feature attributes of greatest concern to the designer and technologist, which determines the range of image slopes.

The actual Zernike polynomials used to generate match patterns must be determined

from the aberrations present in a specific machine or common to a family of machines, and can be measured with programmed probe-based targets [30] as well as several other methods such as that of Garza [31].

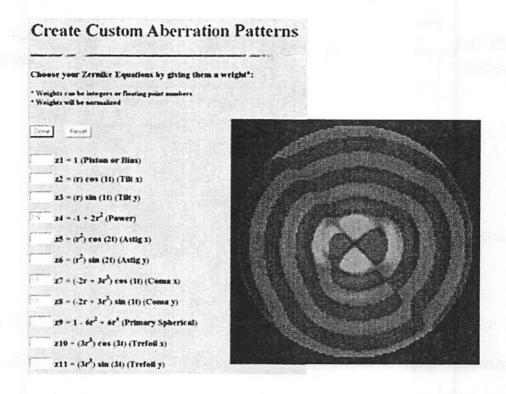

## 3.2 Aberration Pattern Generation

The pattern generator reads a weighted sum of Zernike polynomials as defined in Born and Wolf [20] describing the aberrations present in the optical printing machine or family of equipment of interest. Each Zernike term is in the form of a list of coefficients representing powers of rho, sin and cosine coefficients, and coefficients for phi in both the sin and cosine terms. Zernike polynomials are an orthonormal set that together specify an exact aberration fingerprint. This allows a set of aberrations present in the lens of a particular stepper or other printing system to be summed into a single pattern matrix. In fact, designers can maintain a collection of matching patterns, one for each machine, and select for the matching run the pattern corresponding to the machine(s) intended to be used in printing the design. Since flare is essentially the combination of high-order aberrations, flare components can be modeled in a similar way. The pattern generator then uses these Zernike polynomials to compute the aberrated pupil function in a circular area superimposed on a large rectangular background matrix of zeros for isolation. It then takes the inverse Fourier transform (IFT) of the sum of Zernike terms, and the center portion of the resulting matrix is written out as the pattern matrix of complex numbers. The 2D IFFT computations are implemented with a publicly available FFT package<sup>4</sup> and take only a few seconds per pattern.

The pattern generator reads a number of optical parameters describing the radius of the lens pupil, the size of the background matrix, and the size of the output pattern matrix. The effect of the illumination source can also be included by initializing the matrix to the shape of the pupil before it is multiplied by the Zernike terms. Partial coherence is dealt with inside the pattern matcher itself and not in the pattern generator. The pupil size is based on the wavelength of light and numerical aperture (NA) of the system. A larger background matrix provides a more accurate IFT but requires a larger IFT time and more memory. A background matrix eight times the size of the output pattern matrix is usually sufficient.

The output pattern radius is chosen so that at least 95% of the pattern weight is included in that radius, so that the pattern includes almost the entire aberration fingerprint and is a good approximation of the worst-case geometry due to that combination of lens aberrations. It is important to choose the proper radius of influence of the pattern to be large enough to capture the influence range of the aberration yet small enough to avoid excessive computation time during the matching process. A typical pattern size for  $\lambda$ =0.5 $\mu$ m, NA = 0.5, 50nm pattern matching grid is 128 by 128 pixels, which is 6.4  $\lambda$ /NA on a side.

# 3.3 Predicting $\Delta E$ and $\Delta I$ from $\Delta X$ for Aberrations

The pattern matcher can be used to predict the change in electric field due to lens aberrations with high accuracy, as discussed in Section 8.5. The actual change in electric

<sup>4.</sup> http://momonga.t.u-tokyo.ac.jp/~ooura/fft.html

field at a feature edge is dependent on the electric fields due to the unaberrated feature, the unaberrated optical proximity effect due to surrounding features, the aberrated feature, and the aberrated optical proximity effect. These individual components cannot easily be separated, but some approximations can be made, and simplifying assumptions of mask phase and aberration type will aid in the derivation of the intensity change. The following derivation of the intensity change and line edge shift is an extension to the theory presented in Section 3.1.

After the electric field change is computed, the intensity change must be computed. There are three electric field vectors: Ea, Ep, and R. Ea is the electric field due to aberrations (both from the feature itself and from other adjacent features), which can be determined from the match factor. Ep is the electric field due to the shape that the pattern match lies on, which is in phase with Ea for a simple 0/180 degree phase match with an odd aberration. R is the electric field proximity effect of other shapes, which can be approximated from the match factor of the unaberrated pattern. The vector magnitude of Ep + R is equal to I, the unaberrated intensity at the match location. The vector magnitude of Ep + R + Ea is equal to the aberrated intensity Ia. The intensity change can be calculated with the following equation:

$$\Delta I = Ia - I = mag(Ep + R + Ea)^{2} - mag(Ep + R)^{2}$$

$$= (re\{Ep\} + re\{R\} + re\{Ea\})^2 + (im\{Ep\} + im\{R\} + im\{Ea\})^2 - (re\{Ep\} + re\{R\})^2 - (im\{Ep\} + im\{R\})^2)^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2)^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2)^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{R\})^2)^2 + (im\{Ep\} + im\{R\})^2 + (im\{Ep\} + im\{Ep\} + im\{Ep\} + im\{Ep\} + (im\{Ep\} + im\{Ep\} + im\{Ep\} + im\{Ep\} + (im\{Ep\} + im\{Ep\} + im\{Ep\} + (im\{Ep\} + im\{Ep\} + im\{Ep\} + (im\{Ep\} + im\{Ep\} + im\{Ep\} + im\{Ep\} + (im\{Ep\} + im\{Ep\}$$

If using a 0/180 degree PSM and an odd aberration such as coma, then Ep, Ea, and R are real, and this equation simplifies to:

$$\Delta I = (re\{Ep\} + re\{R\} + re\{Ea\})^2 - (re\{Ep\} + re\{R\})^2$$

$$= Ep^2 + R^2 + Ea^2 + 2 * Ep * R + 2 * Ea * R + 2 * Ep * Ea - Ep^2 - R^2 - 2 * Ep * R$$

$$= Ea^{2} + 2 * Ea * R + 2 * Ep * Ea$$

$$= Ea^{2} + 2 * Ea * (R + Ep)$$

Assuming a small amount of aberration, Ea is small and the Ea<sup>2</sup> term can be neglected:

$$\Delta I = 2 * Ea * (R + Ep) = 2 * Ea *_{Eunaberrated} = 2 * Ea * \sqrt{I_{unaberrated}}$$

Finally, the line-end or line-edge shift is computed from the intensity change, and that is used to calculate the critical dimension (CD) change. The line edge shift can be calculated with the following equation:

$$\Delta X = \Delta I / image\_slope = 2 * Ea * \sqrt{I_{unaberraled}} / image\_slope$$

The CD change of a vertical line can be calculated as:

$$\begin{split} \Delta CD &= \Delta X_{left\_edge} - \Delta X_{right\_edge} \\ &= 2*(Ea_{left}*\sqrt{I_{unaberrated\_left}} + Ea_{right}*\sqrt{I_{unaberrated\_right}})/image\_slope \end{split}$$

Ea can be directly calculated from the match factor. I<sub>unaberrated</sub> can be computed through an aerial image simulation in SPLAT, or can be approximated by computing the match factor of the unaberrated pattern at that location with the pattern matcher or through fast image simulation as is used in model-based OPC. The image slope can be simulated with SPLAT or approximated based on the type of geometry (edge, line end, or corner), mask phases, and optical parameters. Note, however, that the derivation of these equations assumes a purely real phased mask and odd aberrations. The equation for imaginary phased masks and even aberrations can be calculated in a similar manner, but the equation becomes much more complex with combined real/imaginary phased masks or combined even and odd aberrations.

## 3.4 Match Factor Definition

The match factor is a measure of the similarity of the layout geometry to the pattern at a particular location on the mask. The match factor lies in the range [-1.0,1.0], with 1.0 being a perfect positive match, -1.0 being a perfect negative match, and 0.0 having no resemblance to the pattern. The match factor is calculated through a normalized 2D discrete correlation computation, which is similar to an image convolution. The match factor (MF) at layout position (i, j) for an X by Y pattern is calculated as:

$$MF(i+\frac{X}{2},j+\frac{Y}{2}) = \sum_{Y} \sum_{X} Layout(x+i,y+j) * Pat(x,y)$$

In the general case both the pattern and layout values are complex numbers, so the actual result of the raw correlation computation is also a complex number. Normalization consists of dividing the raw correlation number by the best possible match factor given the pattern and set of available layout layers, and then choosing the real value, imaginary value, or magnitude of the resulting complex number, depending on the application.

The match factor is defined so that superposition can be used to independently add linear contributions from each shape overlapping the pattern. Since the correlation computation is performed on a discrete grid, diagonal and curved edges must be approximated on the pixel grid. Since each shape that overlaps the pattern may contribute some value to the final match factor, the time taken to compute the match factor is dependent on the number of overlapping shapes. Thus, the match factor is only efficiently computed when the pattern is much smaller than the overall set of polygons that form the entire layout on which the pattern match is run. This limits the applications of pattern matching where this match factor definition can be used, but fortunately there are ways to speed up the match for

large patterns by reducing the resolution. The match factor at any location is independent of previously computed match factors, so only a subset of the total number of layout locations can be processed without loss of accuracy. Finally, with a typical grid size equal to a fraction of a minimum feature size and a small number of layout layers, the layout "image" consists of large groups of the same set of only a few unique pixel values. This observation can be used to speed up the naive correlation computation, as explained in Chapter 6.

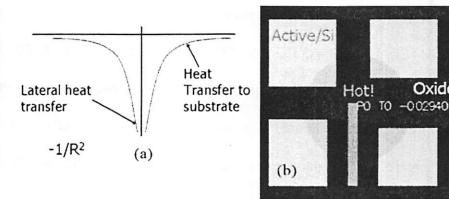

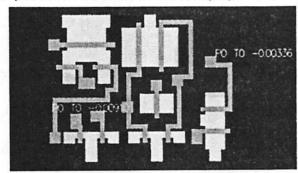

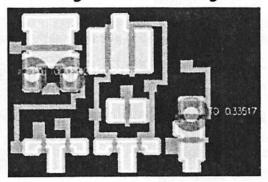

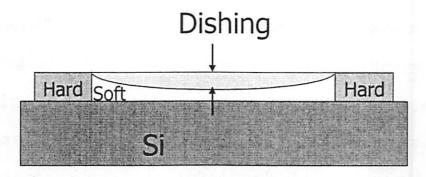

### 3.5 MLTP Definition